Intel® IXP43X Product Line of Network Processors

Hardware Design Guidelines

April 2007

Document Number: 316844; Revision: 001US

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR

OTHERWISE, TO ANY IN TELLEC TUA L PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL ’S TERMS AND CONDITIONS

OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING

TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE,

MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for

use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics

of any features or instructions marked “reserv ed” or “undefined.” Intel reserves these for fut ure definition and shall ha ve no responsibility whatsoever for

conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with

this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published

specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-

4725, or by visiting Intel’s Web Site.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different

processor families. See http://www.intel.com/products/processor_number for details.

BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino logo, Core Inside, FlashFile, i960, InstantIP, Intel, Intel logo, Intel386, Intel4 86 , Inte l7 40 ,

IntelDX2, IntelDX4, IntelSX2, Intel Core, Intel Inside, Intel Inside logo, Intel. Leap ahead., Intel. Leap ahead. logo, Intel NetBurst, Intel NetMerge, I ntel

NetStructure, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel Viiv, Intel vPro, Intel XScale, Itanium, Itanium Inside, MCS, MMX, Oplus,

OverDrive, PDCharm, Pentium, Pentium Inside, skoool, Sound Mark, The Journey Inside, VTune, Xeon, and Xeon Inside are trademarks of Intel

Corporation in the U.S. and other countries.

*Other names and brands may be claimed as the property of others.

Copyright © 2007, Intel Corporation. All rights reserved.

Intel® IXP43X Product Line of Network Processors

HDG April 2007

2 Document Number: 316844; Revision: 001US

Hardware Design Guidelines—Intel

®

IXP43X Product Line of Network Processors

Contents

1.0 Introduction..............................................................................................................9

1.1 Content Overview................................................................................................9

1.2 Related Documentation...................................................................................... 10

1.3 Acronyms.........................................................................................................10

1.4 Overview .........................................................................................................11

1.5 Typical Applications ...........................................................................................14

2.0 System Architecture ................................................................................................15

2.1 System Architecture Description..........................................................................15

2.2 System Memory Map .........................................................................................15

3.0 General Hardware Design Considerations................................................................17

3.1 Soft Fusible Features ......................................................................................... 17

3.2 DDRII/I SDRAM Interface................................................................................... 18

3.2.1 Signal Interface .......................... .. .. .................................. .. .. .................19

3.2.2 DDRII/I SDRAM Initialization ...................................................................20

3.3 Expansion Bus ..................................................................................................21

3.3.1 Signal Interface .......................... .. .. .................................. .. .. .................21

3.3.2 Reset Configuration Straps .................................................................. .... 22

3.3.3 8-Bit Device Interface.............................................................................24

3.3.4 16-Bit Device Interface ...........................................................................25

3.3.5 Flash Interface.......................................................................................26

3.4 UART Interface .................................................................................................26

3.4.1 Signal Interface .......................... .. .. .................................. .. .. .................27

3.5 MII Interface .................................................................................................... 28

3.5.1 Signal Interface MII........................................ .. .................................. .. ..29

3.5.2 Device Connection, MII ............................... .. .. .................................... .... 30

3.6 GPIO Interface..................................................................................................31

3.6.1 Signal Interface .......................... .. .. .................................. .. .. .................32

3.6.2 Design Notes .........................................................................................32

3.7 USB Interface.................................. .. .................................. .............................32

3.7.1 Signal Interface .......................... .. .. .................................. .. .. .................33

3.8 UTOPIA Level 2 Interface ................................................................................... 36

3.8.1 Signal Interface .......................... .. .. .................................. .. .. .................36

3.8.2 Device Connection.................................... .. .. .................................. .. .. .... 40

3.9 HSS Interface................................................................................................... 40

3.9.1 Signal Interface .......................... .. .. .................................. .. .. .................41

3.9.2 Device Connection.................................... .. .. .................................. .. .. .... 41

3.10 SSP Interface ...................................................................................................42

3.10.1 Signal Interface ............................................. .................................. .. .. ..43

3.10.2 Device Connection........................................................... .. .. ...................43

3.11 PCI Interface ....................................................................................................44

3.11.1 Signal Interface ............................................. .................................. .. .. ..45

3.11.2 PCI Interface Block Diagram.................................................................... 46

3.11.3 PCI Option Interface...............................................................................47

3.11.4 Design Notes.........................................................................................49

3.12 JTAG Interface..................................................................................................49

3.12.1 Signal Interface ............................................. .................................. .. .. ..50

3.13 Input System Clock ...........................................................................................50

3.13.1 Clock Signals......................................................................................... 50

3.13.2 Clock Oscillator ...................................................................................... 50

3.13.3 Recommendations for Crystal Selection..................................................... 51

April 2007 HDG

Document Number: 316844; Revision: 001US 3

Intel® IXP43X Product Line of Network Processors

Intel® IXP43X Product Line of Network Processors—Hardware Design Guidelines

3.14 Power ..............................................................................................................52

3.14.1 Decoupling Capacitance Recommendations.................................................53

3.14.2 VCC Decoupling......................................................................................53

3.14.3 VCC33 Decoupling .................................. ................................. ... ............53

3.14.4 VCCDDR Decoupling................................................................................53

3.14.5 Power Sequence............................................. .................................. ......53

3.14.6 Reset Timing..........................................................................................53

4.0 General PCB Guide...................................................................................................55

4.1 PCB Overview ...................................................................................................55

4.2 General Recommendations..................................................................................55

4.3 Component Selection .........................................................................................55

4.4 Component Placement........................................................................................55

4.5 Stack-Up Selection........................................................... ... .. .............................56

5.0 General Layout and Routing Guide ...........................................................................59

5.1 Overview..........................................................................................................59

5.2 General Layout Guidelines...................................................................................59

5.2.1 General Component Spacing ....................................................................60

5.2.2 Clock Signal Considerations......................................................................62

5.2.3 MII Signal Considerations ........................................................................63

5.2.4 USB V2.0 Considerations .........................................................................63

5.2.5 Crosstalk ...............................................................................................63

5.2.6 EMI Design Considerations............................................ .. .. .......................64

5.2.7 Trace Impedance....................................................................................64

5.2.8 Power and Ground Plane..........................................................................64

6.0 PCI Interface Design Considerations........................................................................66

6.1 Electrical Interface............................................. .. .. .................................. .. .. .. ....66

6.2 Topology ..........................................................................................................66

6.3 Clock Distribution ................................................ .................................. .. .. ........67

6.3.1 Trace Length Limits.................................................................................68

6.3.2 Routing Guidelines..................... .. .. .................................. .. .....................69

6.3.3 Signal Loading........................................................................................69

7.0 DDRII / DDRI SDRAM ..............................................................................................70

7.1 Introduction......................................................................................................70

7.2 DDRII/DDRI RCOMP and Slew Resistances Pin Requirements...................................74

7.3 DDRII OCD Pin Requirements..............................................................................75

7.3.1 Signal-Timing Analysis .................................. .. .................................. .. .. ..75

7.3.2 Timing Relationships ...............................................................................78

7.3.3 Routing Guidelines..................... .. .. .................................. .. .....................81

7.3.3.1 Clock Group..............................................................................81

7.3.3.2 Data and Control Groups............................................................82

7.3.3.3 Command Groups .....................................................................84

Figures

1Intel® IXP435 Network Processor Block Diagram ................................ .... .... .... ..............13

2Example: Intel

3 8/16-Bit Device Interface ..........................................................................................25

4 Flash Interface Example............................................................................................26

5 UART Interface Example............................................................................................28

6 MII Interface Example...............................................................................................31

7 Common Mode Choke ................................ .. .. .................................. .........................34

8 USB RCOMP and ICOMP Pin Requirement.....................................................................35

9 USB Host Down Stream Interface Example................... .. .. .. .................................... .. .. ..35

10 UTOPIA Interface Example.........................................................................................40

®

IXP43X Product Line of Network Processors

Intel

HDG April 2007

4 Document Number: 316844; Revision: 001US

®

IXP43X Product Line of Network Processors System Block Diagram..........16

Hardware Design Guidelines—Intel

®

IXP43X Product Line of Network Processors

11 HSS Interface Example........................ .. .................................. .. ...............................42

12 Serial Flash and SSP Port (SPI) Interface Example........................................................44

13 PCI Interface...........................................................................................................47

14 Clock Oscillator Interface Example.............................................................................. 51

15 Recommended circuit design on PCB for crystal oscillator .............................................. 52

16 Component Placement on a PCB.................................................................................56

17 8-Layer Stackup ...................................................................................................... 58

18 6-Layer Stackup ...................................................................................................... 58

19 Signal Changing Reference Planes..............................................................................60

20 Good Design Practice for VIA Hole Placement...............................................................61

21 Poor Design Practice for VIA Placement.......................................................................61

22 Pad-to-Pad Clearance of Passive Components to a PGA or BGA.......................................62

23 PCI Address/Data Topology.......................................................................................67

24 PCI Clock Topology ..................................................................................................68

25 Processor-DDRII/I SDRAM Interface...........................................................................72

26 DDRII/DDRI RCOMP Pin External Resistor Requirements ...............................................74

27 DDRII OCD Pin Requirements....................................................................................75

28 DDR Clock Timing Waveform.....................................................................................75

29 DDR SDRAM Write Timings........................................................................................ 76

30 DDR SDRAM Read Timings ........................................................................................76

31 DDR - Write Preamble/Postamble Duration..................................................................77

32 DDRII Clock Simulation Results: CK Signals.................................................................82

33 DDRII Data and Control Simulation Results: DQ and DQS signals ................................... 83

34 DDRII Command Simulation Results: ADDRESS signals.................................................84

Tables

1 List of Acronyms and Abbreviations ................................................. .. .. .......................10

2 Signal Type Definitions .............................................................................................17

3 Soft Fusible Features................................................................................................17

4 DDRII/I SDRAM Interface Pin Description.................................................................... 19

5 Expansion Bus Signal Recommendations.....................................................................21

6 Boot/Reset Strapping Configuration............................................................................22

7 Setting Intel XScale

8 UART Signal Recommendations.............................................. ....................................27

9 MII NPE A Signal Recommendations ....................................... ... .................................29

10 MII NPE C Signal Recommendations ..................................... .. ....................................29

11 MAC Management Signal Recommendations NPE A and NPE C........................................30

12 GPIO Signal Recommendations.......................................... .................................... .. ..32

13 USB Host Signal Recommendations............................................................................ 33

14 UTOPIA Level 2/MII_A..............................................................................................36

15 High-Speed, Serial Interface 0 ................................................................................... 41

16 Synchronous Serial Peripheral Port Interface................................................................ 43

17 PCI Controller..........................................................................................................45

18 PCI Host/Option Interface Pin Description....................................................................47

19 Synchronous Serial Peripheral Port Interface................................................................ 50

20 Clock Signals...........................................................................................................50

21 Power Supply ..........................................................................................................52

22 PCI Address/Data Routing Guidelines..........................................................................67

23 PCI Clock Routing Guidelines.....................................................................................68

24 DDRII/I Signal Groups..............................................................................................71

25 Supported DDRI 32-bit SDRAM Configurations.............................................................73

26 Supported DDRII 32-bit SDRAM Configurations.................................................. .. .. .. .... 73

27 Supported DDRI 16-bit SDRAM Configurations.............................................................73

28 Supported DDRII 16-bit SDRAM Configurations.................................................. .. .. .. .... 74

®

Processor Operation Speed.........................................................24

April 2007 HDG

Document Number: 316844; Revision: 001US 5

Intel® IXP43X Product Line of Network Processors

Intel® IXP43X Product Line of Network Processors—Hardware Design Guidelines

29 DDR Clock Timings ...................................................................................................75

30 DDRII-400 MHz Interface -- Signal Timings..................................................................77

31 DDR II/I SDRAM Interface -- Signal Timings.................................................................78

32 Timing Relationships.................................................................................................79

33 Signal Package Lengths............................ .. .................................. .............................79

34 Clock Signal Group Routing Guidelines ........................................................................82

35 DDRII Data and Control Signal Group Routing Guidelines...............................................83

36 DDRII Command Signal Group Routing Guidelines ........................................................84

®

IXP43X Product Line of Network Processors

Intel

HDG April 2007

6 Document Number: 316844; Revision: 001US

Hardware Design Guidelines—Intel

®

IXP43X Product Line of Network Processors

Revision History

Date Revision Description

April 2007 001 Initial release

§ §

April 2007 HDG

Document Number: 316844; Revision: 001US 7

Intel® IXP43X Product Line of Network Processors

Intel® IXP43X Product Line of Network Processors—Hardware Design Guidelines

®

IXP43X Product Line of Network Processors

Intel

HDG April 2007

8 Document Number: 316844; Revision: 001US

Hardware Design Guidelines—Intel

®

IXP43X Product Line of Network Processors

1.0 Introduction

This design guide provides recommendations for hardware and system designers who

are developing with the Intel

document should be used in conjunction with the Intel

Network Processors Datasheet and sample schematics provided for the Intel

®

IXP43X Product Line of Network Processors. This

®

IXP43X Product Line of

®

IXP435

Multi-Service Residential Gateway Reference Platform.

Design recommendations are necessary to meet the timing and signal quality

specifications. The guidelines recommended in this document are based on experience

and simulation work done at Intel while developing the Intel® IXP435 Multi-Service

Residential Gateway Reference Platform. These recommendations are subject to

change.

Note: This document discusses all features supported on the IXP43X product line of network

processors. A subset of these features is supported by certain processors in the IXP43X

network processors, such as the Intel

®

IXP432 Network Processor. Refer to the Intel®

IXP43X Product Line of Network Processors Datasheet for detailed information on

various features listed by processor.

1.1 Content Overview

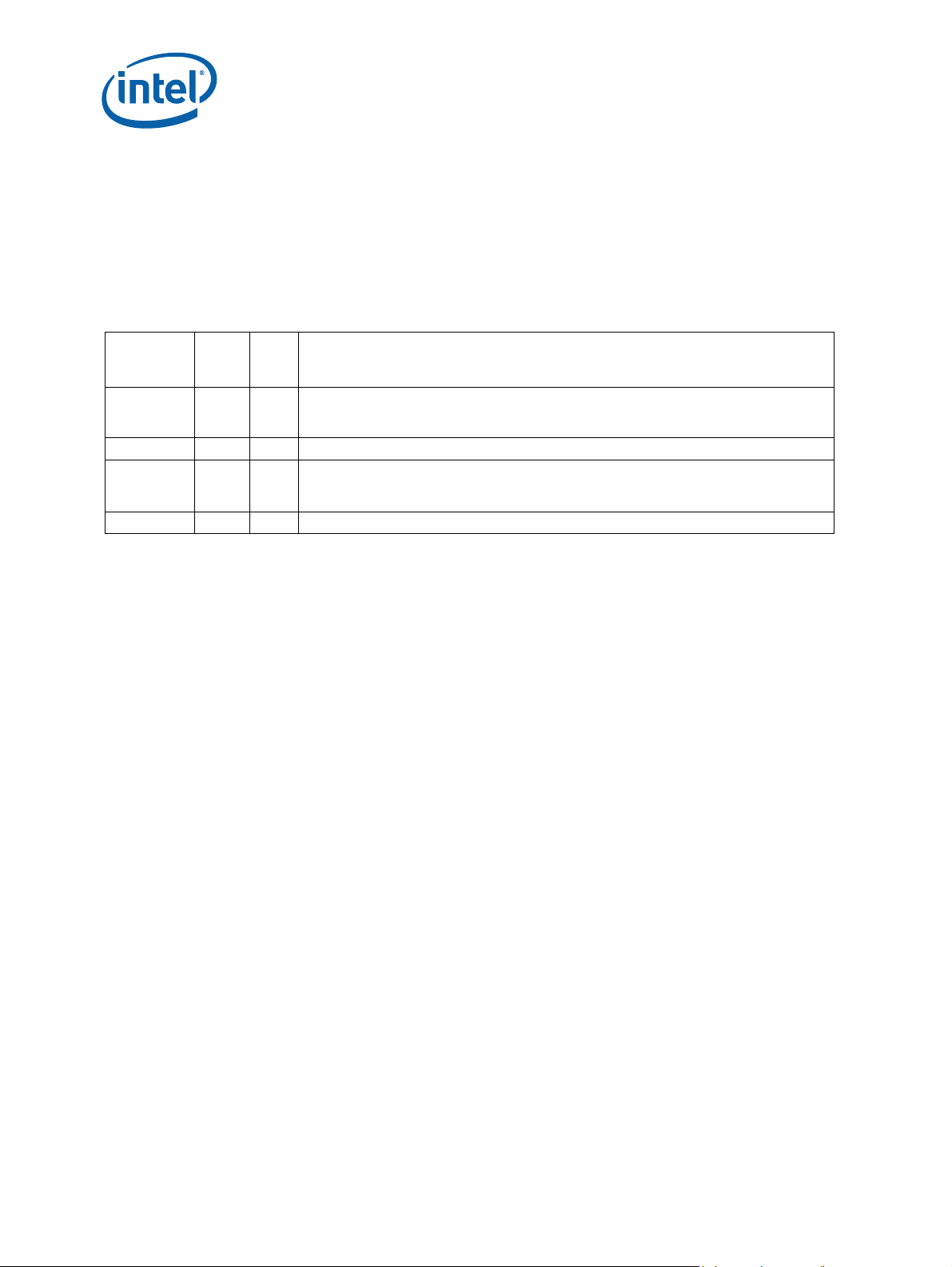

Chapter Name Description

Chapter 1.0, “Introduction” Conventions used in this manual and related documentation

Chapter 2.0, “System Architecture” System architectural block diagram and system memory map

Chapter 3.0, “General Hardware Design

Considerations”

Chapter 4.0, “General PCB Guide” General PCB design practice and layer stack-up description

Chapter 5.0, “General Layout and Routing

Guide”

Chapter 6.0, “PCI Interface Design

Considerations”

Chapter 7.0, “DDRII / DDRI SDRAM”

Graphical representation of most common peripheral interfaces

More specific layout and routing recommendations for board

designers

Board-design recommendations when implementing PCI

interface

Board-design recommendations when implementing

DDRII/I memory interface

April 2007 HDG

Document Number: 316844; Revision: 001US 9

Intel® IXP43X Product Line of Network Processors

Intel® IXP43X Product Line of Network Processors—Hardware Design Guidelines

1.2 Related Documentation

The reader of this design guide should also be familiar with the material and concept

presented in the following documents:

Title Document #

®

Intel

IXP43X Product Line of Network Processors Datasheet 316842

®

Intel

IXP43X Product Line of Network Processors Developer’s

Manual

®

IXP43X Product Line of Network Processors: Migrating from

Intel

the Intel

Intel

Intel

Intel

Intel StrataFlash

Intel XScale

Double Data Rate (DDR) SDRAM Specification, 2004; JEDEC Solid

State Technology Association

IEEE 802.3 Specification

PCI Local Bus Specification, Rev. 2.2

Universal Serial Bus Specification, Revision 2.0

UTOPIA Level 2 Specification, Revision 1.0

®

IXP42X Product Line

®

IXP400 Software Programmer’s Guide 252539

®

IXP400 Software Specification Update 273795

®

XScale™ Core Developer’s Manual 273473

®

Embedded Memory (P30) Application Note __

®

Microarchitecture Technical Summary —

316843

316845

JESD79D

N/A

N/A

N/A

N/A

1.3 Acronyms

Table 1 lists the acronyms and abbreviations used in this guide.

Table 1. List of Acronyms and Abbreviations (Sheet 1 of 2)

Term Explanation

AHB Advanced High-Performance Bus

APB Advanced Peripheral Bus

ATM Asynchronous Transfer Mode

DDR Double Data Rate

EMI Electro-Magnetic Interference

GPIO General Purpose Input/Output

HSS High Speed Serial

IP Internet Protocol

ISA Instruction Set Architecture

LAN Local Area Network

MII Media-Independent Interface

NPE Network Processor Engine

PCB Printed Circuit Board

PCI Peripheral Component Interface

PHY Physical Layer Interface

PLL Phase-Locked Loop

®

IXP43X Product Line of Network Processors

Intel

HDG April 2007

10 Document Number: 316844; Revision: 001US

Hardware Design Guidelines—Intel

®

IXP43X Product Line of Network Processors

Table 1. List of Acronyms and Abbreviations (Sheet 2 of 2)

Term Explanation

PMU Performance Monitoring Unit

SME Small-to-Medium Enterprise

SSP Synchronous Serial Protocol

UART Universal Asynchronous Receiver-Transmitter

USB Universal Serial Bus

VTT Termination Voltage Supply

1.4 Overview

The Intel® IXP43X Product Line of Network Processors is a highly integrated device,

capable of interfacing with most common industry standard peripherals, required for

high-performance control applications.

Note: This document discusses all features supported on the IXP43X network processors.

Refer to the Intel

®

IXP43X Product Line of Network Processors Datasheet for details on

feature support listed by processor.

Some of the key features of the IXP43X network processors, when used as a

single-chip solution for embedded applications are as follows:

•Intel XScale® Processor (compliant with Intel® StrongARM* architecture) up to 667

MHz

• 32-bit PCI interface Master/Target 33 MHz

• Two Universal Serial Bus (USB) V2.0 Host Controller

• DDRI-266 SDRAM or DDRII-400 SDRAM—

— Support for 16 MB, minimum for DDR II/I, 32 MB minimum for DDRII-400;

1 GB, maximum for DDR II/I, 512 MBs maximum for DDRII-400

— User-enabled ECC.

• 16bit Data / 24bit Address Expansion Bus Interface

•One UART interface

•Two NPEs

•UTOPIA Level 2 Interface

• Synchronous Serial Port Interface (SSP)

• One High-Speed Serial Port Interfaces (HSS)

• Network interfaces that can be configured in the following manner:

Note 1

— Two MII interfaces

— One MII interface + 1 UTOPIA Level 2 interface

• MII interfaces are:

Note 1

— 802.3 MII interfaces

— Single MDIO interface to control the MII interfaces

• UTOPIA Level 2 Interface is :

Note 1

— Eight-bit interface

— Up to 33-MHz clock speed

— Five transmit and five receive address lines

April 2007 HDG

Document Number: 316844; Revision: 001US 11

Intel® IXP43X Product Line of Network Processors

Note:

Intel® IXP43X Product Line of Network Processors—Hardware Design Guidelines

• 16 GPIO (General Purpose Input Output)

•Packaging

—460-pin PBGA

— 31 mm by 31 mm

— Commercial temperature (0° to 70° C)

— Lead free support

®

Refer to the Intel

IXP43X Product Line of Network Processors Datasheet for complete

feature list and block diagram description.

1. This feature requires Intel-supplied software. T o determine if this feature is enabled

in a particular software release, refer to the Intel

®

IXP400 Software Programmer’s

Guide.

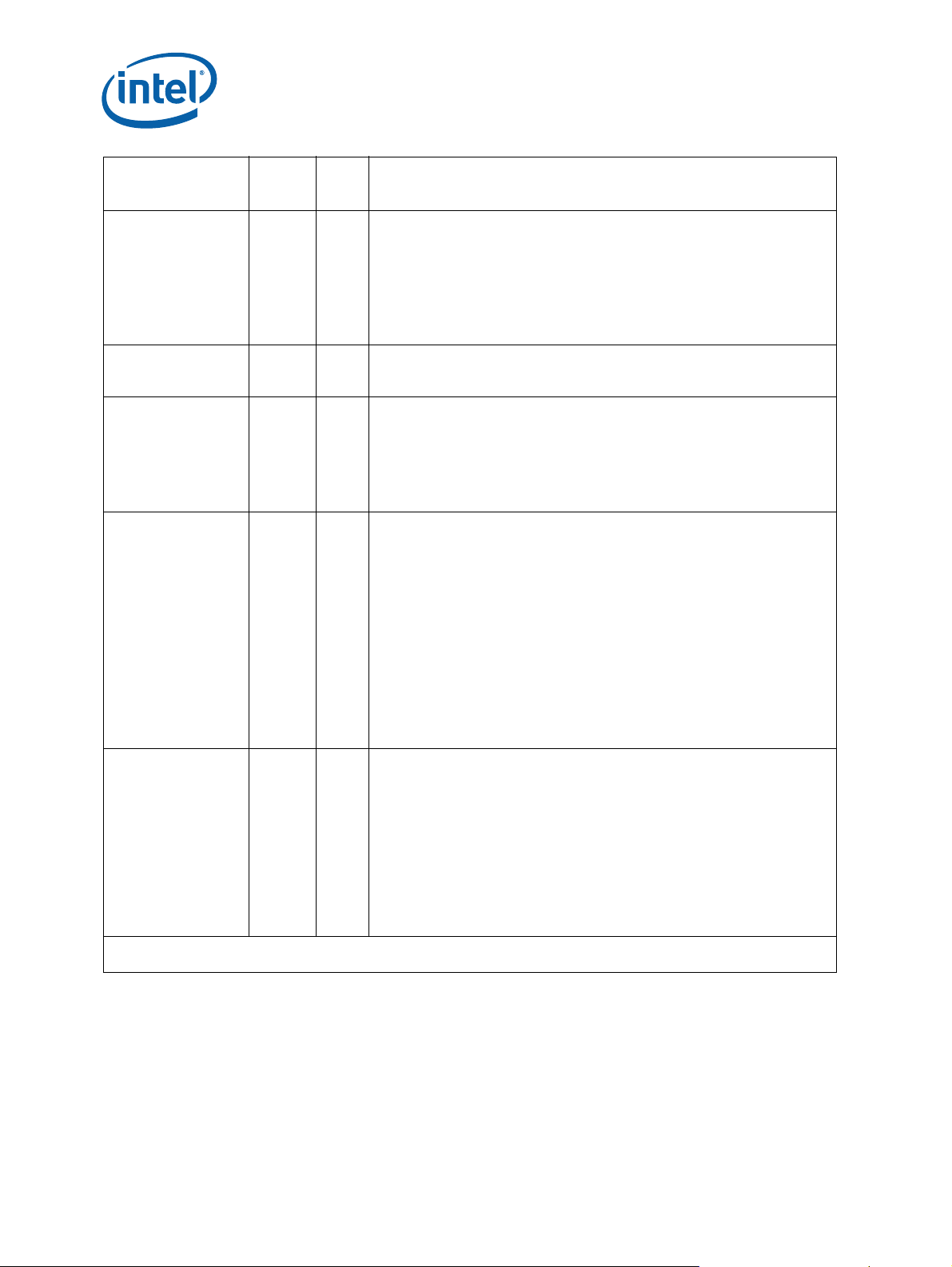

A block diagram of all major internal hardware components of IXP43X network

processors is shown in Figure 1. The illustration also shows how the components

interface with each other through the various bus interfaces such as the North AHB,

South AHB, and APB.

®

IXP43X Product Line of Network Processors

Intel

HDG April 2007

12 Document Number: 316844; Revision: 001US

Hardware Design Guidelines—Intel

®

IXP43X Product Line of Network Processors

Figure 1. Intel® IXP435 Network Processor Block Diagram

HSS

UTOPIA 2/ MII

NPE A

16 GPIO

SSP

High Speed

UART

921 Kbaud

GPIO

Interrupt

Controller

IBPMU

Timers

MII

APB 6 6. 66MHz x 32 bi ts

AHB

Slave /

APB

Master

BRIDGE

CONTROLLER

USB Port

HOST

VERSION 2.0

UTMI

2. 0 P HY

NPE C

AES/ 3DES/

DES/

SHA/ MD -5

North AHB 133. 32 MHz x 32 bits

North AHB

Queue Status Bus

QUEUE

MANAGER

South AHB 133.32 MHz x 32 bits

South AHB

USB Port

HOST

CONTROLLER

VERSION 2.0

UTMI

2.0 PHY

EXPANSION

BUS Controller

8/16 bit 80 MHz

Arbiter

Arbiter

AHB/ AHB

BRIDGE

PCI

CONTROLLER

32 bit 33 MHz

DDRII/ I MEMORY

CONTROLLER

UNIT

266/ 400

z

MPI

64 bits

/200MHzx

133.32MH

XScale Processor

32 KB I - CACHE

32 KB D - CACHE

2KB MINI D- CACHE

266/400/533/667 MHz

16/ 32 BITS

+ ECC

DDR 266 /

DDRII 400

Master on South AHB

Master on North AHB

Bus Arbiters

Slave Only

AHB Slave/APB Master

Note: Figure 1 shows the Intel® IXP435 Network Processor. For details on feature and SKU

support listed by processor, see the Intel

®

IXP43X Product Line of Network Processors

Datasheet.

April 2007 HDG

Document Number: 316844; Revision: 001US 13

Intel® IXP43X Product Line of Network Processors

Intel® IXP43X Product Line of Network Processors—Hardware Design Guidelines

1.5 Typical Applications

• SOHO-Small Business/Residential

• Modular Router

• Wireless Gateway(802.11a/b/g)

• Network-Attached Storage

• Wired/Wireless RFID Readers

• Digital Media Adapter

• Digital Media Player

•VoIP Router

•Video Phone

• Secure Gateway/Router

•Network Printer

• Wireless Media Gateway

• IP Set Top box

§ §

®

IXP43X Product Line of Network Processors

Intel

HDG April 2007

14 Document Number: 316844; Revision: 001US

Hardware Design Guidelines—Intel

®

IXP43X Product Line of Network Processors

2.0 System Architecture

2.1 System Architecture Description

The Intel® IXP43X Product Line of Network Processors is a multifunction processor that

integrates the Intel XScale

®

Processor (ARM* architecture compliant) with highly

integrated peripheral controllers and network processor engines.

The processor is a highly integrated design, manufactured with Intel’s 0.13-µm

production semiconductor process technology. This process technology, along with

numerous, dedicated function peripheral interfaces and many features with the Intel

XScale processor, addresses the needs of many system applications and helps reduce

system costs. The processors can be configured to meet many system application and

implementation needs.

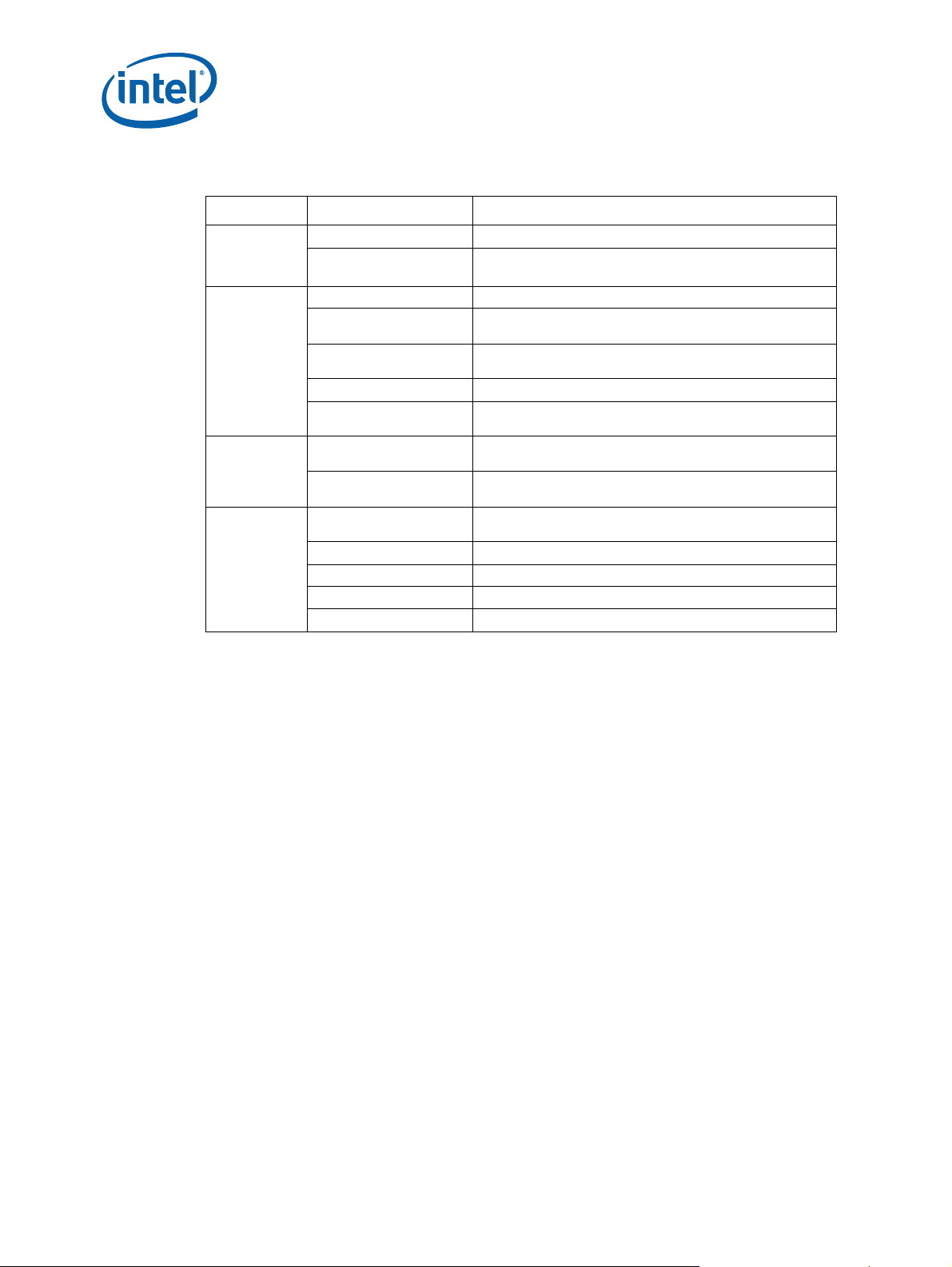

Figure 2 illustrates one of the many applications for which the IXP43X network

processors can be implemented. For detailed functional description, see the Intel

IXP43X Product Line of Network Processors Developer’s Manual.

2.2 System Memory Map

Refer to the Intel® IXP43X Product Line of Network Processors Developer’s Manual for

a complete memory map and register description of each individual module.

®

April 2007 HDG

Document Number: 316844; Revision: 001US 15

Intel® IXP43X Product Line of Network Processors

Intel® IXP43X Product Line of Network Processors—Hardware Design Guidelines

Figure 2. Example: Intel® IXP43X Product Line of Network Processors System Block

Diagram

JTAG

Header

DDR

DDR

DDR

SDRAM

SDRAM

SDRAM

16Mx4x16

DDRII/I

16Mx4x16

16Mx4x16

512 Mbyte

SDRAM

512 Mbyte

512 Mbyte

(Four Chips)

Max 1 Gbyte

(Four Chips)

(Four Chips)

SLIC/CODEC or

T1/E1/J1 FramerHSS 0

A/D

Configuration

Reset Logic

LCD/LED

Diagnostics

Display

Flash

32 Mbyte

Board

Buff

CS_N0

D[1 5: 0]

A[23:0]

Memory Bus

Expansion Bus

Intel® IXP 43X Product

Line of Network

Processors

DDRII/I SDRAM

RAS, CAS, WE, CS,CLK

SSP

SSP CODEC or

CB[7:0]

D[31:0]

BA[1:0]

A[13:0]

DB9

RJ45

Port 0

RJ45

Port 1

RS 232

Serial Port 0

10/100

PHYs

Up to 2 Ports

USB Host

Connector

USB Host

Connector

2-MII

USB v2.0

USB v2.0

PCI Bus

Transparent PCI Bridge

cPCI Bus

cPC I J2

cPC I J1

UTOPIA Level 2

PCI Slots

Ethernet

Clocks

Clock Buff er

5 V

3.3 V

2.5/1.8 V

1.3 V

PCI

Clock

xDSL

xDSL

xDSL

xDSL

PLL

Power Supply

OSC

B4835 -003

§ §

®

IXP43X Product Line of Network Processors

Intel

HDG April 2007

16 Document Number: 316844; Revision: 001US

Hardware Design Guidelines—Intel

®

IXP43X Product Line of Network Processors

3.0 General Hardware Design Considerations

This chapter contains information for implementing and interfacing with major

hardware blocks of the Intel

®

IXP43X Product Line of Network Processors. Such blocks

include DDRII/I SDRAM, Flash, Ethernet PHYs, UART and other peripherals interfaces.

Signal definition tables list resistor recommendations for pull-ups and pull-downs.

Features disabled by a specific part number, do not require pull-ups or pull-downs.

Therefore, all pins can be left unconnected. Features enabled by a specific part number

and required to be Soft Fuse-disabled, only require pull-ups or pull-downs in the

clock-input signals. Other conditions can require pull-up or pull-down resistors for

configuration purposes at power on or reset. In the same way, open-drain outputs must

be pulled high.

Warning: With the exception of USB_V5REF all other I/O pins of the IXP43X network processors

are not 5.0-V tolerant.

Table 2 gives the legend for interpreting the Type field used in the signal-definition

tables that are covered in this chapter.

Table 2. Signal Type Definitions

Symbol Description

I Input pin only

O Output pin only

I/O Pin can be an input or output

OD Open-drain pin

TRI Tri-State pin

PWR Power pin

GND Ground pin

3.1 Soft Fusible Features

Soft Fuse Enable/Disable is a method to enable or disable features in hardware,

virtually disconnecting the hardware modules from the processor.

Some of the features offered in the IXP43X product line of network processors can be

Soft Fuse Enabled/Disabled during boot. It is recommended that if a feature is not used

in the design, the feature be soft disabled. This helps reduce power and maintain the

part running at a cooler temperature. When Soft Fuse Disabled, a pull-up resistor must

be connected to each clock input pins of the disabled feature interface. All other signals

can be left unconnected.

Soft Fuse Enable/Disable can be done by writing to EXP_UNIT_FUSE_RESET register.

For more information refer to the Intel

Developer’s Manual and review the register description.

Table 3. Soft Fusible Features (Sheet 1 of 2)

Name Description

PCI The complete bus must be enabled or disable.

HSS0 Can only be disable as a pair.

UTOPIA

April 2007 HDG

Document Number: 316844; Revision: 001US 17

while enabling UTOPIA, MACs on NPE A is disabled.

while enabling MACs on NPE A, UTOPIA is disabled.

®

IXP43X Product Line of Network Processors

Intel® IXP43X Product Line of Network Processors

Intel® IXP43X Product Line of Network Processors—Hardware Design Guidelines

Table 3. Soft Fusible Features (Sheet 2 of 2)

Name Description

ETHERNET Can enable MII MACs. Enable of MACs can be separately done per each NPE.

USB Host Each USB can be Enable separately.

DDR ECC ECC can be enabled or disabled separately from the rest of the DDR interface.

3.2 DDRII/I SDRAM Interface

The IXP43X network processors support unbuffered, DDRI-266 or DDRII-400 SDRAM

technology, capable of addressing two memory banks (one bank per CS). Each bank

can be configured to support 32/64/128/256/512-Mbyte for a total combined memory

support of 1 Gbyte.

The IXP43X network processors integrate a high-performance, multi-ported Memory

Controller Unit (MCU) to provide a direct interface with its local memory subsystem.

The MCU supports:

• DDR II/I or DDRII-400 SDRAM

• 128/256/512-Mbit, 1-Gbit DDRI SDRAM technology support

• Supports 256/512-Mbit technologies for the DDRII-400

• Only unbuffered DRAM support (No registered DRAM support)

• Dedicated port for Intel XScale processor to the DDRII/DDRI SDRAM

• Between 32 MBs and 1-GB of 32-bit DDRI SDRAM

• Between 64MBs and 512 MBs of 32-bit DDRII SDRAM

• 16MB for 16-bit memory systems for DDRI SDRAM (non-ECC) supporting 128-Mbit

technology only

• 32MB for 16-bit memory systems for DDRII SDRAM (non-ECC) supporting 256-Mbit

technology only

• Single-bit error correction, multi-bit detection support (ECC)

• 32-bit, 40-bit wide memory interfaces (non-ECC and ECC support), and 16-bit wide

memory interfaces (non-ECC)

The DDRII/DDRI SDRAM interface provides a direct connection to a high-bandwidth

and reliable memory subsystem. The DDRII/DDRI SDRAM interface is a 16 or

32-bit-wide data path.

The device supports non-ECC and ECC for error correction, which can be enable or

disable by software as required. Banks have a bus width of 32 bits for non ECC or

40 bits for ECC enable (32-bit data + 8-bit ECC).

An 8-bit Error Correction Code (ECC) across each 32-bit word improves system

reliability. It is important to note that ECC is also referred to as CB in many DIMM

specifications. The pins on the IXP43X network processors are called

DDR_CB[7:0]. ECC is only implemented in the 32-bit mode of operation, while the

algorithm used to generate the 8-bit ECC is implemented over 64-bit.

The ECC circuitry is designed to operate always on a 64-bit data and when operating in

32-bit mode, the upper 32 bits are driven to zeros internally. To summarize the impact

to the customer, the full 8 bits of ECC is stored and read from a memory array for the

ECC logic to work. An 8-bit-wide memory is used when implementing ECC.

®

IXP43X Product Line of Network Processors

Intel

HDG April 2007

18 Document Number: 316844; Revision: 001US

Hardware Design Guidelines—Intel

®

IXP43X Product Line of Network Processors

The memory controller only corrects single bit ECC errors on read cycles. The ECC is

stored into the DDRII/DDRI SDRAM array along with the data and is checked when the

data is read. If the code is incorrect, the MCU corrects the data before reaching the

initiator of the read. ECC error scrubbing is done with software. User-defined fault

correction software is responsible for The value written back into the memory location

contains the 32-bit word with the modified byte and the new ECC value.

Refer to the Intel

®

IXP43X Product Line of Network Processors Datasheet for a detailed

list of features.

General DDRII/I SDRAM routing guidelines can be found in Section 7.3.3, “Routing

Guidelines” on page 82. For more detailed information, see the PC266 and PC400 DDR

SDRAM specification.

3.2.1 Signal Interface

Table 4. DDRII/I SDRAM Interface Pin Description (Sheet 1 of 2)

Name

D_CK[2:0] /

DDR_CK[2:0]

D_CK_N[2:0] /

DDR_CK_N[2:0]

D_CS_N[1:0] /

C_CS_N[1:0]

D_RAS_N /

DDR_RAS_N

D_CAS_N /

DDR_CAS_N

D_WE_N / DDR_WE_N O

D_DM[4:0] /

DDR_DM[4:0]

D_BA[1:0] /

DDR_BA[1:0]

D_MA[13:0] /

DDR_MA[13:0]

D_DQ[31:0] /

DDR_DQ[31:0]

Type

Field

I/O

Device-Pin Connection

Connect a pair of differential clock

signals to every device; When

O

using both banks, daisy chain

devices with same data bit

sequence.

O Same as above No

Use the same CS to control 32-bit

O

data + 8-bit ECC, per bank

The RAS signal must be connected

O

to each device in a daisy chain

manner

The CAS signal must be connected

O

to each device in a daisy chain

manner

The WE signal must be connected

to each device in a daisy chain

manner

Connect to each DM device pin.

For the 8-bit devices connect one

DM signal per device.

O

For the 16-bit devices connect two

DM signal per device (depending

on how many data bits are being

used).

The BA signals must be connected

O

to each device in a daisy chain

manner.

All address signals must be

O

connected to each device in a

daisy chain manner.

Must be connected in parallel to

achieve a 32-bit bus width.

VTT

Terminatio

No

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes Data Bus — 32-bit wide data bus.

n

DDRII/I SDRAM Clock Out — Provides the

positive differential clocks to the external

SDRAM memory subsystem.

DDRII/I SDRAM Clock Out — Provides the

negative differential clocks to the external

SDRAM memory subsystem.

Chip Select — Must be asserted for all

transactions to the DDRII/I SDRAM device.

One per bank.

Row Address Strobe — Indicates that the

current address on D_MA[13:0] /

DDR_MA[13:0] is the row.

Column Address Strobe — Indicates that the

current address on D_MA[13:0] /

DDR_MA[13:0] is the column.

Write Strobe — Defines whether or not the

current operation by the DDRII/I SDRAM is to

be a read or a write.

Data Bus Mask — Controls the DDRII/I SDRAM

data input buffers. Asserting D_WE_N/

DDR_WE_N causes the data on D_DQ[31:0]/

DDR_DQ[31:0] and D_CB[7:0]/DDR_CB[7:0]

to be written into the DDRII/I SDRAM devices.

D_DM[4:0]/DDR_DM[4:0] controls this

operation on a per-byte basis. D_DM[3:0]/

DDR_DM[3:0] are intended to correspond to

each byte of a word of data. D/DM[4]/

DDR_DM[4] is intended to be utilized for the

ECC byte of data.

DDRII/I SDRAM Bank Selects — Controls which

of the internal DDRII/I SDRAM banks to read

or write. D_BA[1:0]/DDR_BA[1:0] are used for

all technology types supported.

Address bits 13 through 0 — Indicates the row

or column to access depending on the state of

D_RAS_N/DDR_RAS_N and D_CAS_N/

DDR_CAS_N.

Description

April 2007 HDG

Document Number: 316844; Revision: 001US 19

Intel® IXP43X Product Line of Network Processors

Intel® IXP43X Product Line of Network Processors—Hardware Design Guidelines

Table 4. DDRII/I SDRAM Interface Pin Description (Sheet 2 of 2)

Name

D_CB[7:0] /

DDR_CB[7:0]

D_DQS[4:0] /

DDR_DQS[4:0]

D_CKE[1:0] /

DDR_CKE[1:0]

D_ODT[1:0]

D_RES[2:1] Refer to Figure 27

D_SLWCRES Refer to Figure 27

D_IMPCRES Refer to Figure 27

D_CRES0 O Tied off to a resistor

D_VREF / DDR_VREF I VCCDDR/2 VCCDDR/2

Type

Field

I/O Connect to ECC memory devices. Yes

I/O

O

Device-Pin Connection

Connect DQS[3:0] to devices with

data signals and DQS[4] to

devices with ECC signals.

Use one CKE per bank, never mix

the CKE on the same bank. Use

CKE[0] for bank0 and CKE[1] for

bank1

VTT

Terminatio

n

Yes

Yes

Tied off to a

resistor

Description

ECC Bus — Eight-bit error correction code

which accompanies the data on D_DQ[31:0]/

DDR_DQ[31:0].

When ECC is disabled and not being used in a

system design, these signals can be left unconnected.

Data Strobes Differential — Strobes that

accompany the data to be read or written from

the DDRII/I SDRAM devices. Data is sampled

on the negative and positive edges of these

strobes. D_DQS[3:0]/DDR_DQS[3:0] are

intended to correspond to each byte of a word

of data. D_DQS[4]/DDR_DQS[4] is intended to

be utilized for the ECC byte of data.

Clock enables — One clock after D_CKE[1:0]/

DDR_CKE[1:0] is de-asserted, data is latched

on D_DQ[31:0]/DDR_DQ[31:0] and

D_CB[7:0]/DDR_CB[7:0]. Burst counters

within DDRII/I SDRAM device are not

incremented. De-asserting this signal places

the DDRII/I SDRAM in self-refresh mode. For

normal operation, D_CKE[1:0]/DDR_CKE[1:0]

must be asserted.

On Die Termination Control — Turns on DDR II

SDRAM termination during writes.

Compensation for DDR OCD (analog) DDRII

mode only. This function is not enable and

special connection is required.

Compensation Voltage Reference (analog) for

DDR driver slew rate control connected

through a resistor to D_CRES0.

Compensation Voltage Reference (analog) for

DDR driver impedance control connected

through a resistor to D_CRES0.

Analog VSS Ref Pin (analog) both D_SLWCRES

and D_IMPCRES signals connect to this pin

through a reference resistor. For DDRII/I

respectively:

- 285 / 387Ohm Resistor connected to

DDR_IMPCRES used for process and

temperature adjustments.

- 825 / 845Ohm Resistor connected to

DDR_SLWCRES used for process and

temperature adjustments.

DDRII/IDDRII/I SDRAM Voltage Reference — is

used to supply the reference voltage to the

differential inputs of the memory controller

pins.

3.2.2 DDRII/I SDRAM Initialization

For instructions on DDRII/I SDRAM initialization, refer to DDR SDRAM Initialization

subsection in the Memory Controller chapter of the Intel

Network Processors Developer’s Manual.

®

IXP43X Product Line of Network Processors

Intel

HDG April 2007

20 Document Number: 316844; Revision: 001US

®

IXP43X Product Line of

Hardware Design Guidelines—Intel

®

IXP43X Product Line of Network Processors

3.3 Expansion Bus

The Expansion Bus of the IXP43X network processors is specifically designed for

compatibility with Intel-and Motorola* style microprocessor interfaces.

The expansion bus controller includes a 24-bit address bus and a 16-bit wide data path,

running at a maximum speed of 80 MHz from an external clock oscillator. The bus can

be configure to support the following target devices:

• Intel multiplexed • Intel non-multiplexed

•Intel StrataFlash

• Motorola non multiplexed • Motorola multiplexed

The expansion bus controller also has an arbiter that supports up to four external

devices that can master the expansion bus. External masters can be used to access

external slave devices that reside on the expansion bus, including access to internal

memory mapped regions within the IXP43X network processors.

All supported modes are seamless and no additional glue logic is required. Other cycle

types can be supported by configuring the Timing and Control Register for Chip Select.

The expansion interface functions support 8-bit or 16-bit data operation and allows an

address range of 512 bytes to 16 MBs, using 24 address lines for each of the four

independent chip selects.

®

• Synchronous Intel StrataFlash

®

Memory

Access to the expansion-bus interface is completed in five phases. Each of the five

phases can be lengthened or shortened by setting various configuration registers on a

per-chip-select basis. This feature allows the IXP43X network processors to connect to

a wide variety of peripheral devices with varying speeds.The expansion interface

supports Intel or Motorola* microprocessor style bus cycles. The bus cycles can be

configured to be multiplexed address/data cycles or separate address/data cycles for

each of the four chip-selects.

The expansion interface is an asynchronous interface to externally connected chips. A

clock is supplied to the IXP43X network processors expansion interface for the interface

to operate. This clock can be driven from GPIO 15 or an external source. Devices on the

expansion bus can be clocked by an external clock at a rate of up to 80 MHz. If GPIO 15

is used as the clock source, the Expansion Bus interface can only be clocked at a

maximum of 33.33 MHz. GPIO 15’s maximum clock rate is 33.33 MHz.

3.3.1 Signal Interface

Table 5. Expansion Bus Signal Recommendations (Sheet 1 of 2)

Name

EX_CLK I No Use series termination resistor, 10Ω to 33Ω at the source.

EX_ALE TRI O No Use series termination resistor, 10Ω to 33Ω at the source.

EX_ADDR[23:0] I/O Yes

EX_WR_N I/O No Use series termination resistor, 10Ω to 33Ω at the source.

EX_RD_N I/O No Use series termination resistor, 10Ω to 33Ω at the source.

Type

Field

Pull

Up

Down

Use 470Ω resistors for pull-downs; required for boot strapping for initial configuration of

Configuration Register 0. Pull-ups are not required as for when the system comes out of

reset, all bits are initially set HIGH. For more details, see Table 6.

For additional details on address strapping, see the Intel

Processors Developer’s Manual.

Recommendations

®

IXP43X Product Line of Network

April 2007 HDG

Document Number: 316844; Revision: 001US 21

Intel® IXP43X Product Line of Network Processors

Intel® IXP43X Product Line of Network Processors—Hardware Design Guidelines

Table 5. Expansion Bus Signal Recommendations (Sheet 2 of 2)

Name

EX_CS_N[3:0] I/O Yes

EX_DATA[15:0] I/O No Expansion-bus, bidirectional data.

EX_IOWAIT_N I Yes Should be pulled high through a 10-KΩ resistor when not being utilized in the system.

Type

Field

Pull

Up

Down

Use series termination resistor, 10Ω to 33Ω at the source.

Use 10KΩ resistors pull-ups to ensure that the signal remains de-asserted.

Recommendations

3.3.2 Reset Configuration Straps

At power up or whenever RESET_IN_N is asserted, the Expansion-bus address outputs

are switched to inputs and the state of the inputs are captured and stored in

Configuration Register 0, bits 23 through 0. This occurs when PLL_LOCKED is deasserted.

The strapping of Expansion-bus address pins can be done by placing external pull-down

resistors at the required address pin. It is not required to use external pull-up resistors,

by default upon reset all bits on Configuration R egister 0 are set High, unless an

external pull down is used to set them Low. For example to register a bit low or high in

the Configuration Register 0, do the following:

Place an external 470Ω pull-down resistor to register a bit LOW in the Configuration

Register 0.

No external pull-up is required; upon reset, bits are set high by default.

The state of the boot-strapping resistor is registered on the first cycle after the

synchronous de-assertion of the reset signal. These bits can be read or written as

needed for desired configurations. It is recommended that only Bit 31, Memory Map, be

changed from 1 to 0 after execution of boot code from external flash.

Refer to the Intel

a complete bit description of Configuration Register 0.

Table 6. Boot/Reset Strapping Configuration (Sheet 1 of 2)

®

IXP43X Product Line of Network Processors Developer’s Manual for

Name Function Description

Intel XScale

EX_ADDR[23:21]

EX_ADDR[20:17] Customer Customer-defined bits. (Might be used for board revision.)

EX_ADDR[16:12] (Reserved) (Reserved)

EX_ADDR[11] DDR_MODE

®

IXP43X Product Line of Network Processors

Intel

HDG April 2007

22 Document Number: 316844; Revision: 001US

Processor

Clock Set[2:0]

®

Allow a slower Intel XScale

But cannot be used to over clock core speed. Refer to Table 7 for additional

information.

DDRI or DDRII mode selection:

0 - DDRII mode (400MHz)

1 - DDRI mode (266MHz)

DDR_mode or DDR clock speed selection bit is read only and strapped in from exp

address bit 11 upon activation of reset_early_n and reset_cold_n.

®

Processor clock speed to override device fuse settings.

Hardware Design Guidelines—Intel

®

IXP43X Product Line of Network Processors

Table 6. Boot/Reset Strapping Configuration (Sheet 2 of 2)

Name Function Description

1 = EX_IOWAIT_N is sampled during the read/write expansion bus cycles for Chip

Select 0.

0 = EX_IOWAIT_N is ignored for read and write cycles to Chip select 0 if

EXP_TIMING_CS0 is configured to Intel mode that is mentioned in Intel

Product Line of Network Processors Datasheet and Intel

Network Processors Developer’s Manual.

Typically, IOWAIT_CS0 must be pulled down to Vss when attaching a Synchronous

EX_ADDR[10] IOWAIT_CS0

Intel StrataFlash

Intel mode and EX_IOWAIT_N is an unknown value for Synchronous Intel

StrataFlash.

If the board does not connect the Synchronous Intel StrataFlash WAIT pin to

EX_WAIT_N (and the board guarantees EX_IOWAIT_N is pulled up), the value of

IOWAIT_CS0 is a don’t-care, since EX_IOWAIT_N will not be asserted.

When EXP_TIMING_CS0 is reconfigured to Intel Synchronous mode during

boot-up (for synchronous Intel chips), the expansion bus controller ignores

EX_IOWAIT_N during read and write cycles since the WAIT functionality is

determined from the EXP_SYNCINTEL_COUNT and EXP_TIMING_CS registers.

EX_ADDR[9] EXP_MEM_DRIVE Refer to table found in EX_ADDR[5].

Controls the USB clock select.

1 = USB Host/Device clock is generated internally

EX_ADDR[8] USB Clock

0 = USB Device clock is generated from GPIO[0].

When generating a spread spectrum clock on OSC_IN, GPIO[1] can be driven from

the system board to generate a 48 MHz clock for the USB Host.

Selects the data bus width of the FLASH memory device found on Chip Select 0.

EX_ADDR[7] 32_FLASH

Refer to 8/16_FLASH bit (Bit 0) of this register as well.

0 = 8 or 16-bit data bus size (must be pulled down during ad dress strapping)

1 = not supported

EX_ADDR[6] (Reserved) (Reserved)

Expansion bus low/medium/high drive strength. The drive strength depends on

EXP_DRIVE and EXP_MEM_DRIVE configuration bits.

EXP_MEM_DRIVE EXP_DRIVE Expansion drive strength

EX_ADDR[5] EXP_DRIVE

----------------------------------------------------------------------------------- 0 0 Reserved

0 1 Medium Drive

1 0 Low Drive

1 1 High Drive

Sets the clock speed of the PCI Interface

EX_ADDR[4] PCI_CLK

0 = 33 MHz (must be pulled down during address strapping)

1 = not supported

EX_ADDR[3] (Reserved)

(Reserved). EX_ADDR[3] must not be pulled down during address strapping. This

bit must be written to ‘1’ if performing a write to this register.

Enables the PCI Controller Arbiter

EX_ADDR[2] PCI_ARB

0 = PCI arbiter disabled

1 = PCI arbiter enabled

Configures the PCI Controller as PCI Bus Host

EX_ADDR[1] PCI_HOST

0 = PCI as non-host

1 = PCI as host

Specifies the data bus width of the FLASH memory device found on Chip Select 0.

EX_ADDR[0] 8/16_FLASH

8/16_FLASH Data bus size

0 16-bit

1 8-bit

®

on Chip Select 0 since the default mode for EXP_TIMING_CS0 is

®

®

IXP43X Product Line of

IXP43X

April 2007 HDG

Intel® IXP43X Product Line of Network Processors

Document Number: 316844; Revision: 001US 23

Intel® IXP43X Product Line of Network Processors—Hardware Design Guidelines

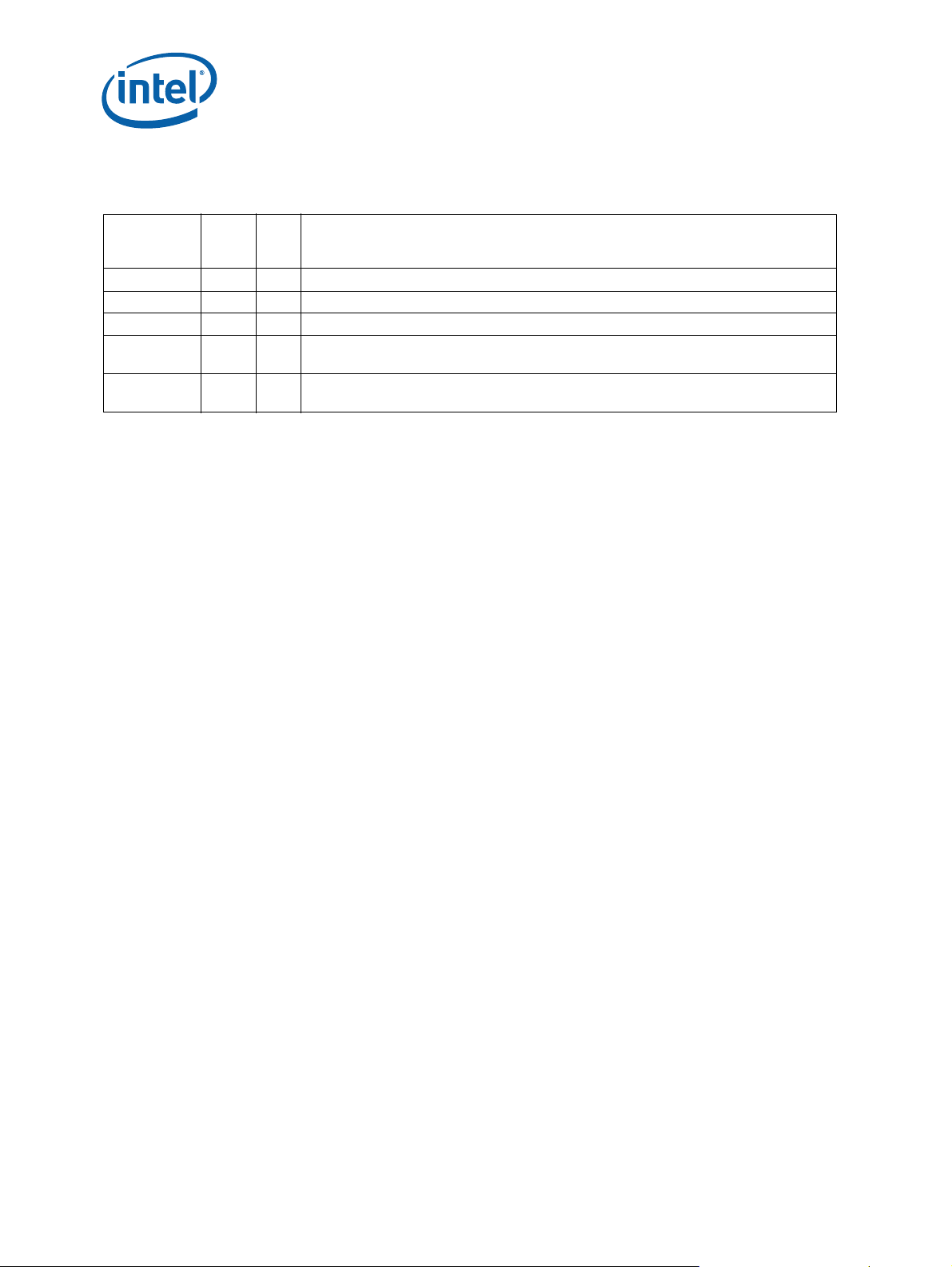

Table 7. Setting Intel XScale

®

Processor Operation Speed

Intel XScale® Processor

Speed

(Factory Part Speed)

667 MHz X X 1 667 MHz

667 MHz 0 0 0 667 MHz

667 MHz 1 0 0 533 MHz

667 MHz 0 1 0 266 MHz

667 MHz 1 1 0 400 MHz

533 MHz X X 1 533 MHz

533 MHz 0 0 0 533 MHz

533 MHz 1 0 0 533 MHz

533 MHz 0 1 0 266 MHz

533 MHz 1 1 0 400 MHz

400 MHz X X 1 400 MHz

400 MHz 0 0 0 400 MHz

400 MHz 1 0 0 400 MHz

400 MHz 0 1 0 266 MHz

400 MHz 1 1 0 400 MHz

266 MHz X X X 266 MHz

Cfg0

EX_ADDR[21]

Cfg1

EX_ADDR[22]

Cfg_en_n

EX_ADDR[23]

Actual Core Speed

(MHz)

Note: The Intel XScale processor can operate at slower speeds than the factory programmed

speed setting. This is done by placing a value on Expansion bus address bits 23,22,21

when PLL_LOCK is deasserted and knowing the speed grade of the part from the

factory. Column 1 above denotes the speed grade of the part from the factory . Column

2, 3, and 4 denotes the values captured on the Expansion Bus address bits when

PLL_LOCK is deasserted. Column 5 represents the speed at which the Intel XScale

processor speed is operating at.

3.3.3 8-Bit Device Interface

The IXP43X network processors support 8-bit-wide data bus devices (byte mode). For

interface cycles, the data lines and control signals can be connected as shown in

Figure 3 on page 26. During byte mode accesses, the remaining data signals not being

used EX_DATA [15:8], are driven by the processor to an unpredictable state on WRITE

cycles and tri-stated during READ cycles.

When booting an 8-bit flash device, the expansion bus must be configured during reset

to the 8-bit mode, bit 0 and 7 of Configuration Register 0 must be set as follows (see

Table 6):

Bit 0 = 1. By default this bit is set high when coming off reset or any time reset is

asserted.

Bit 7 = 0. This can be done by placing an external 470 ohm pull-down resistor to the

pin EX_ADDR[7].

®

IXP43X Product Line of Network Processors

Intel

HDG April 2007

24 Document Number: 316844; Revision: 001US

Hardware Design Guidelines—Intel

®

IXP43X Product Line of Network Processors

Boot-strapping is required in certain address pins of the Expansion bus. If it is required

to change access mode, after the system has booted, and during normal operation; the

Timing and Control Register for Chip Select must be configured to perform the desired

mode access. For a complete description on accomplishing this refer to the Expansion

Bus chapter in the Intel® IXP43X Product Line of Network Processors Developer’s

Manual.

3.3.4 16-Bit Device Interface

The IXP43X network processors support 16-bit wide data bus devices (16-bit word

mode). For Intel interface cycles, the data lines and control signals can be connected as

shown in Figure 3 on page 26.

When booting a 16-bit flash device, the expansion bus must be configured during reset

to the 16-bit mode (see Configuration Register 0).

Bit 0 = 0. This can be done by placing an external 470 ohm pull-down resistor to the

pin EX_ADDR[0].

Bit 7 = 0. This can be done by placing an external 470 ohm pull-down resistor to the

pin EX_ADDR[7].

Boot-strapping is required in certain address pins of the Expansion bus.To change to

access mode after booting the system and during normal operation, the Timing and

Control Register for Chip Select must be configured to perform the desired mode

access. For a complete description on how to accomplish this refer to the Expansion

Bus chapter in the Intel

Manual.

®

IXP43X Product Line of Network Processors Developer’s

April 2007 HDG

Document Number: 316844; Revision: 001US 25

Intel® IXP43X Product Line of Network Processors

Intel® IXP43X Product Line of Network Processors—Hardware Design Guidelines

Figure 3. 8/16-Bit Device Interface

EX_DATA[15:0]

Intel® IXP43X Product

Line of Network

Processors

EX_ADDR[23:0]

EX_CS_N

EX_RD_N

EX_WR_N

EX_DATA[15:0]

Intel® IXP43X Product

Line of Network

Processors

EX_ADDR[23:0]

EX_CS_N

EX_RD_N

EX_WR_N

EX_DATA[7:0]

EX_ADDR[23:0]

CS

OE

WR

EX_DATA[15:0]

EX_ADDR[23:0]

CS

OE

WR

DATA[7:0]

8-Bit Device

Byte Access

ADDR[23:0]

CS_N

OE_N

WR_N

DATA[15:0]

16-Bit Device

16 -Bit-W o r d Access

ADDR[23:0]

CS_N

OE_N

WR_N

B4095-004

3.3.5 Flash Interface

Figure 4 illustrates how a boot ROM is connected to the expansion bus. The flash (ROM)

used in the block diagram is the Intel StrataFlash

32-Mbyte, 16-bit, flash in the 56-TSOP package. The Intel StrataFlash memory

.

®

IXP43X Product Line of Network Processors

Intel

HDG April 2007

26 Document Number: 316844; Revision: 001US

TE28F256J3D is part of the 0.18-µm, 3.3-V Intel StrataFlash memory.

®

memory device TE28F256J3D —

Hardware Design Guidelines—Intel

Figure 4. Flash Interface Example

®

IXP43X Product Line of Network Processors

EX_DATA[15:0]

Intel® IXP43X Product

Line of Network

Processors

EX_ADDR[23:0]

EX_CS_N

EX_RD_N

EX_WR_N

EX_DATA[15:0]

E

X

0 KΩ

_

A

3.3 V

D

D

CS

OE

WR

4.7 KΩ

R

2

[

3

RST#

DATA[15:0]

16-Bit Device

16 -Bit-Word Access

0

:

]

ADDR[23:0]

CE0

OE_N

WR_N

Intel® Flash

RP_N

CE1

CE2

BYTE_N

VPEN_N

4.7 KΩ

B4097- 005

3.4 UART Interface

The UART interface are a 16550-compliant UART with the exception of transmit and

receive buffers. Transmit and receive buffers are 64 bytes-deep versus the 16 bytes

required by the 16550 UART specification.

The interface can be configured to support speeds from 1,200 Baud to 921 Kbaud. The

interface supports the following configurations:

• Five, six, seven, or eight data-bit transfers

• One or two stop bits

• Even, odd, or no parity

The request-to-send (RTS0_N) and clear-to-send (CTS0_N) modem control signals also

are available with the interface for hardware flow control. The hardware supports a

four-wire interface:

• Transmit Data

•Receive Data

•Request to Send

April 2007 HDG

Document Number: 316844; Revision: 001US 27

Intel® IXP43X Product Line of Network Processors

Intel® IXP43X Product Line of Network Processors—Hardware Design Guidelines

•Clear to Send

Note: The UART module does not support full modem functionality. However, this can be

implemented, by using GPIO ports to generate DTR, DSR, RI, and DCD and making

some changes to the driver.

3.4.1 Signal Interface

Table 8. UART Signal Recommendations

Name

RXDATA0 I Yes

TXDATA0 O No Serial data output Port 0.

CTS0_N I Yes

RTS0_N O No Request-To-Send Port 0.

Type

Field

The following figure contain a typical four signal interface between the UART and an

RS-232 transceiver driver, required to interface with external devices. Unused inputs to

the RS-232 driver can be connected to ground. This avoids signals floating to

undetermined states which can cause over heating of the driver leading to permanent

damage.

Pull

Up/

Down

Serial data input Port 0.

When signal is not being used in the system, this pin should be pulled high with a 10-KΩ

resistor.

Clear-To-Send Port 0.

\When signal is not being used in the system, this pin should be pulled high with a 10-KΩ

resistor.

Recommendations

®

IXP43X Product Line of Network Processors

Intel

HDG April 2007

28 Document Number: 316844; Revision: 001US

Hardware Design Guidelines—Intel

Figure 5. UART Interface Example

CTS0_N

RTS0_N

UART

Interface

RXDATA0

TXDATA0

®

IXP43X Product Line of Network Processors

Intel® IXP43X

Intel® IXP43X

Product Line of

Product Line of

Network Processors

Network Processors

OUT4

IN3

OUT1

IN2

Transceiver

IN1

OUT3

OUT2

IN4

RS-232

DB9

Connector (Female)

6

7

8

NC

9

1

2

3

4

5

1 DCD

2 RX

3 TX

4 DTR

5 GND

6 DSR

7 RTS

8 CTS

9 RI

3.5 MII Interface

The IXP43X network processors support a maximum of two Ethernet MACs. Depending

on the part number of the IXP43X network processors, various combinations can be

used. Refer to the Intel

detailed list of features that can be enabled depending upon your requirements.

All MACs contained in the NPEs are compliant to the IEEE 802.3 specification and

handle flow control for the IEEE 802.3Q VLAN specification.

The Management Data Interface (MDI) supports a maximum of 32 PHY addresses. MDI

signals are required to be connected to every PHY chip. Each PHY port is assign a

unique address in the external PHY chip from 0 to 31, totaling a maximum of 32 PHY

addresses. The maximum number of MACs supported by the IXP43X network

processors is two.

The MII interface supports clock rates of 25 MHz for 100-Mbps operation or 2.5 MHz for

10-Mbps operation.

B4099-005

®

IXP43X Product Line of Network Processors Datasheet for a

April 2007 HDG

Document Number: 316844; Revision: 001US 29

Intel® IXP43X Product Line of Network Processors

Intel® IXP43X Product Line of Network Processors—Hardware Design Guidelines

3.5.1 Signal Interface MII

Table 9. MII NPE A Signal Recommendations

Name

ETHA_TXCLK I Yes

ETHA_TXDATA[3:0] O No Transmit Data.

ETHA_TXEN O No Transmit Enable.

ETHA_RXCLK I Yes

ETHA_RXDATA[3:0] I Yes

ETHA_RXDV I Yes

ETHA_COL I Yes

ETHA_CRS I Yes

Notes:

1. Features disabled/enabled by Soft Fuse must be done during the boot-up sequence. A feature cannot be enabled after

being disabled without asserting a system reset.

2. Features disabled by a specific part number, do not require pull-ups or pull-downs. Therefore, all pins can be left

unconnected.

3. Features enabled by a specific part number — and required to be Soft Fus e-disabled , as st ated in Note 1 — only requ ire

pull-ups or pull-downs in the clock-input signals.

Type

Field

Pull

Up/

Down

Transmit Clock.

When this interface/signal is enabled and is not being used in a system design, the

interface/signal should be pulled high with a 10-KΩ resistor.

Receive Clock.

When this interface/signal is enabled and is not being used in a system design, the

interface/signal should be pulled high with a 10-KΩ resistor.

Receive Data.

When this interface/signal is enabled and is not being used in a system design, the

interface/signal should be pulled high with a 10-KΩ resistor.

Receive Data Vali d.

When this interface/signal is enabled and is not being used in a system design, the

interface/signal should be pulled high with a 10-KΩ resistor.

Collision Detect.

If operating in a full duplex mode and there is no requirement to use the Collision

Detect signal, then the pin must be pulled low with a 10-KΩ resistor.

Carrier Sense.

When this interface/signal is enabled and is not being used in a system design, the

interface/signal should be pulled high with a 10-KΩ resistor.

Recommendations

Table 10. MII NPE C Signal Recommendations (Sheet 1 of 2)

Name

ETHC_txclk I Yes

ETHC_txdATA[3:0] O No

ETHC_txen O Yes

®

IXP43X Product Line of Network Processors

Intel

HDG April 2007

30 Document Number: 316844; Revision: 001US

Type

Field

Pull

Up/

Down

Externally supplied transmit clock.

• 25 MHz for 100 Mbps operation

• 2.5 MHz for 10 Mbps

This MAC contains ha rdware hashing capabilities that are local to the interface.

When this interface/signal is enabled and is not being used in a system design, the

interface/signal should be pulled high with a 10-KΩ resistor.

Transmit data bus to PHY, asserted synchronously with respect to ETHC_TXCLK. This

MAC contains hardware hashing capabilities that are local to the interface.

Indicates that the PHY is being presented with nibbles on the MII interface. Asserted

synchronously, with respect to ETHC_TXCLK, at the first nibble of the preamble, and

remains asserted until all the nibbles of a frame are presented. This MAC contains

hardware hashing capabilities that are local to the interface.

Recommendations

Hardware Design Guidelines—Intel

®

IXP43X Product Line of Network Processors

Table 10. MII NPE C Signal Recommendations (Sheet 2 of 2)

Name

ETHC_rxclk I Yes

ETHC_rxdATA[3:0] I Yes

ETHC_rxdv I Yes

ETHC_col I Yes

ETHC_crs I Yes

Notes:

1. Features disabled/enabled by Soft Fuse must be done during the boot-up sequence. A feature cannot be enabled after

2. Features disabled by a specific part number, do not require pull-ups or pull-downs. Therefore, all pins can be left

3. Features enabled by a specific part number — and required to be Soft Fuse-disabled, as stated in note 1 — only require

being disabled without asserting a system reset.

unconnected.

pull-ups or pull-downs in the clock-input signals.

Type

Field

Pull

Up/

Down

Externally supplied receive clock:

• 25 MHz for 100 Mbps operation

•2.5MHz for 10Mbps

This MAC contains hardware hashing capabilities that are local to the interface.

Should be pulled high through a 10-KΩ resistor when not being utilized in the system.

Receive data bus from PHY, data sampled synchronously , with respect to E THC_RXCLK.

This MAC contains hardware hashing capabilities that are local to the interface.

Should be pulled high through a 10-KΩ resistor when not being utilized in the system.

Receive data valid is used to inform the MII interface about data that is being sent by

the Ethernet PHY

This MAC contains hardware hashing capabilities that are local to the interface.

Should be pulled high through a 10-KΩ resistor when not being utilized in the system.

Asserted by the PHY when a collision is detected by the PHY. This MAC contains

hardware hashing capabilities that are local to the interface.

Should be pulled high through a 10-KΩ resistor when not being utilized in the system

When this interface is disabled through the NPE-C Ethernet soft fuse (refer to the

Expansion Bus Controller chapter of the Intel

Processors Developer’s Manual) and is not being used a system design, this interface/

signal is not required for any connection.

Asserted by the PHY when the transmit medium or receive medium are active.

De-asserted when both the transmit and receive medium are idle. Remains asserted

throughout the duration of collision condition. PHY asserts CRS asynchronously and

de-asserts synchronously with respect to ETHC_RXCLK.

This MAC contains hardware hashing capabilities that are local to the interface.

Should be pulled high through a 10-KΩ resistor when not being utilized in the system.

Recommendations

®

IXP43X Product Line of Network

Table 11. MAC Management Signal Recommendations - NPE A and NPE C

Name

ETH_mdio IO Yes

ETH_mdc O No

Type

Field

Pull

Up/

Down

NPE A and NPE C

Management data input output. Provides the write data to both PHY devices connected to

each MII interface. An external pull-up resistor of 1.5K ohm is required on

ETHC_MDIO to properly quantify the external PHYs used in the system. For specific

implementation, see the IEEE 802.3 specification.

Should be pulled high through a 10-KΩ resistor when not being utilized in the system

NPE A and NPE C

Management data clock. Management data interface clock is used to clock the MDIO sig nal as

an output and sample the MDIO as an input. The ETHC_MDC is an input on power up and can

be configured to be an output through Intel APIs documented in the Intel

Programmer’s Guide

Recommendations

®

IXP400 Software

3.5.2 Device Connection, MII

Figure 6 is a typical example of an Ethernet PHY device interfacing to one of the MACs

via the MII hardware protocol.

April 2007 HDG

Document Number: 316844; Revision: 001US 31

Intel® IXP43X Product Line of Network Processors

Intel® IXP43X Product Line of Network Processors—Hardware Design Guidelines

Figure 6. MII Interface Example

Intel® IXP43X

Product Line of

Netw ork Processors

10/100

PHY

ETH_TXEN

ETH_TXCLK

ETH_TXDATA[3:0]

ETH_RXDV

ETH_RXCLK

ETH_RXDATA[3:0]

ETH_COL

ETH_CRS

VCC ( 3.3 V)

ETH_MDIO

ETH_MDC