Page 1

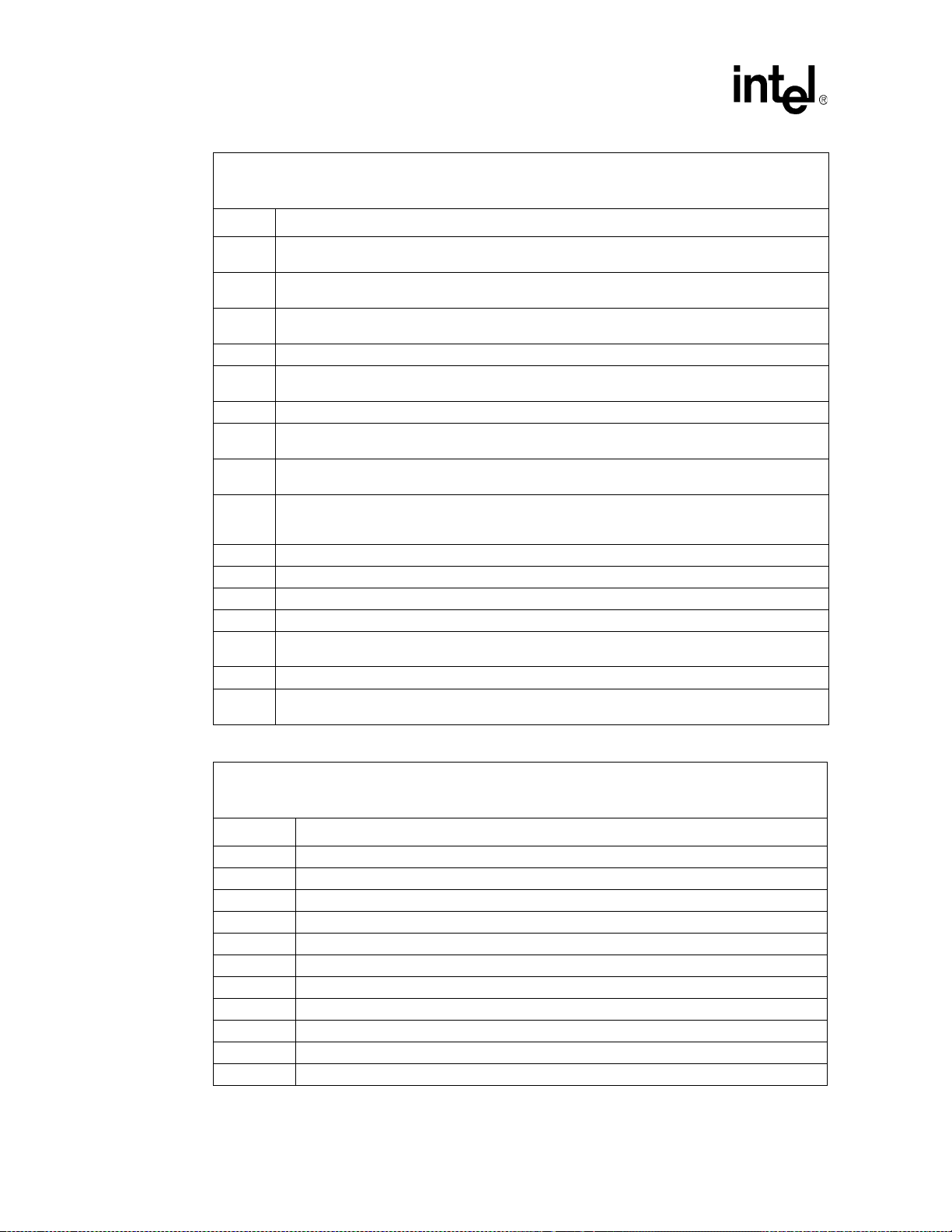

Intel® IXF1104 4-Port Gigabit Ethernet

Media Access Controller

Datasheet

The Intel® IXF1104 4-Port Gigabit Ethernet Media Access Controller (hereafter referred to as

the IXF1104 MAC) supports IEEE 802.3* 10/100/1000 Mbps applications. The IXF1104 MAC

supports a System Packet Interface Phase 3 (SPI3) system interface to a network processor or

ASIC, and concurrently su pports copper and fiber physical layer devices (P HYs).

The copper PHY interface suppo rts the standard and reduced pin-count Gigabit Media

Independent Interface (GMII and RGMII) for high-port-count applications. For fiber

applications the integrated Serializ er/Deseriali zer (SerDes) on each port sup p o r ts direct

connection to opt ical modules to reduce PCB area requirements and s ystem cost.

Product Features

Four Indepe ndent Ethernet MAC Ports for

Copper or Fiber Physical layer connectivity.

—IEEE 802.3 compliant

—Independent Enable/Disable of any port

Copper Mode:

—RGMII for 10/100/1000Mbps links

—GMII for 1000 Mbps ful l-duplex links

—IEEE 802.3 MDIO interface

Fiber Mode:

—Integrated SerDes interface for direct

connection to 1000BASE-X optical modules

—IEEE 802.3 auto-negotiation or forced mode

—Supports SFP MSA-compatible transceivers

SPI3 interface supports data transfers up to

4 Gbps in both mode s:

—32-bit Multi-PHY mode (133 MHz)

—4 x 8-bit Single-PHY mode (125 MHz)

IEEE 802.3-compliant Flow Control

—Loss-less up to 9.6 KB packets and 5 km links

—Jumbo frame suppor t for 9.6 KB packets

Internal per-channel FIFOs: 32 KB Rx, 10 KB Tx

Flexible 32/ 16/8-bit CPU interface

Programmable Packet handling

—Filter broad cast, multicast, unicast, VLAN

and erro red packets

—Automatically pad undersized Tx packets

—Remove CRC from Rx packets

Perform ance Monitoring and Diagnostics

— RMON Statistics

—CRC calculation and error detec tion

—Detection of length error, runt, or overly

larg e packets

—Counters for dropped and errored packets

—Loopback modes

—JTAG boundary scan

.18 μ CMOS process technology

— 1 .8 V core, 2.5 V RGMII, GMII, OMI, and

3.3 V SPI3 and CPU

Operating Temperature Ranges:

—Copper Mode: -40°C to +85°C

—Fiber Mode: 0°C to +70°C

Packag e O p tions:

—552-ball Ceramic BGA (st andard)

—

552-ball Ceramic BGA

—552-ball Plastic FC- B G A

(RoHS-compliant)

(contact your Intel

Sales Representative)

Applications

Load Balancing Systems

MultiService Switches

Web Caching Appliance s

Intelligent Backplane Interfaces

Edge Routers

Redundant Line Cards

Base Station Controllers and Transceivers

Serving GPRS Support Nodes (SGSN)

Gateway GPRS Support Nodes (GGSN)

Packet Data Serving Nodes (PDSN)

DSL Access Multiplexers (DSLAM)

Cable Modem Termination Systems (CMTS)

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

Page 2

®

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL

ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN

INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHA TSOEVER, AND INTEL DISCLAIMS

ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES

RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER

INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety sy ste m s, o r

in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The IXF1104 MAC Media Access Controller may contain design defects or errors known as errata which may cause the product to deviate from

published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling

1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Intel and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

*Other names and brands may be claimed as the property of others.

Copyright © 2005, Intel Corporation

PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY

2 Datasheet

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

Page 3

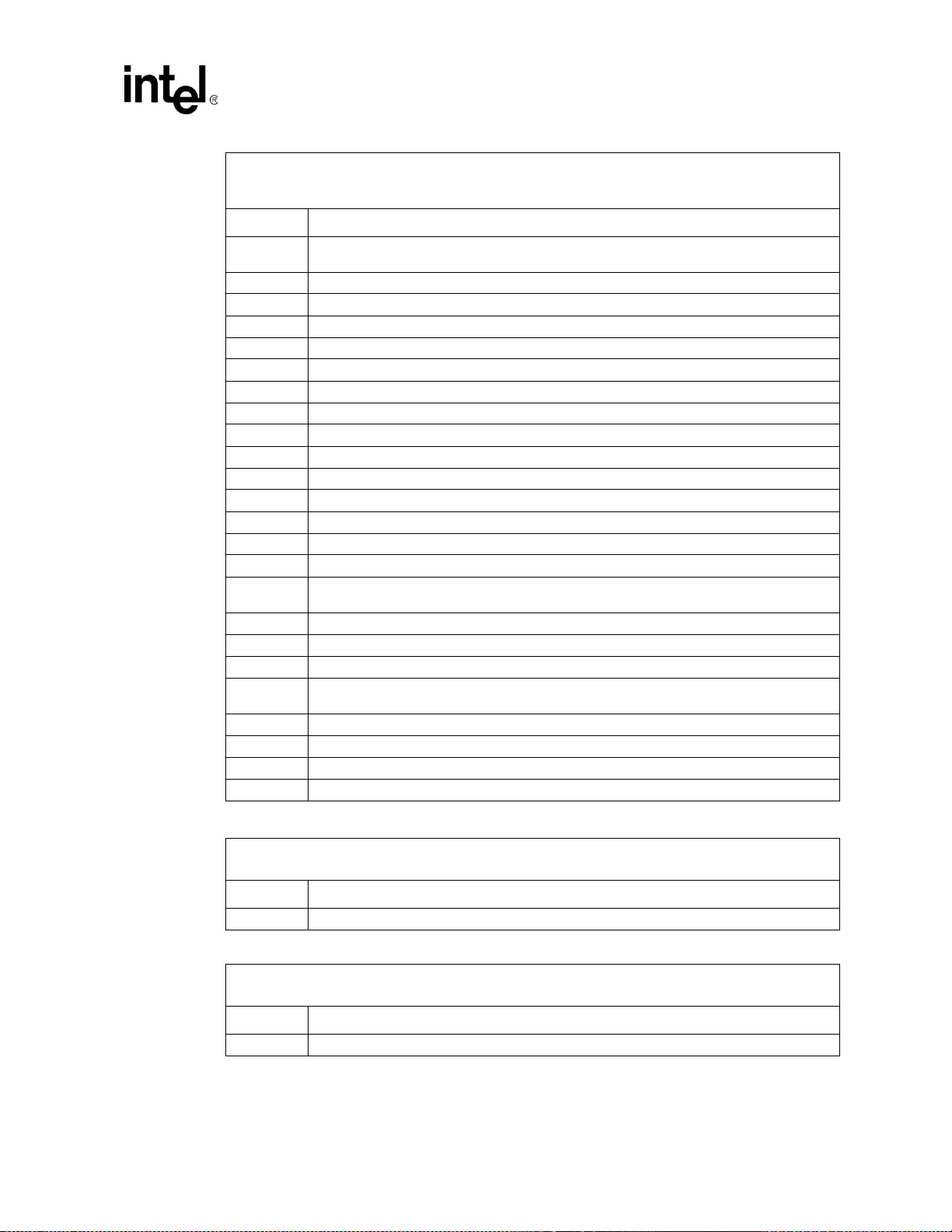

Contents

Contents

1.0 Introduction..................................................................................................................................20

1.1 What You Will Find in This Document ................................................................................20

1.2 Related Documents............................................................................................................20

2.0 General Description ....................................................................................................................21

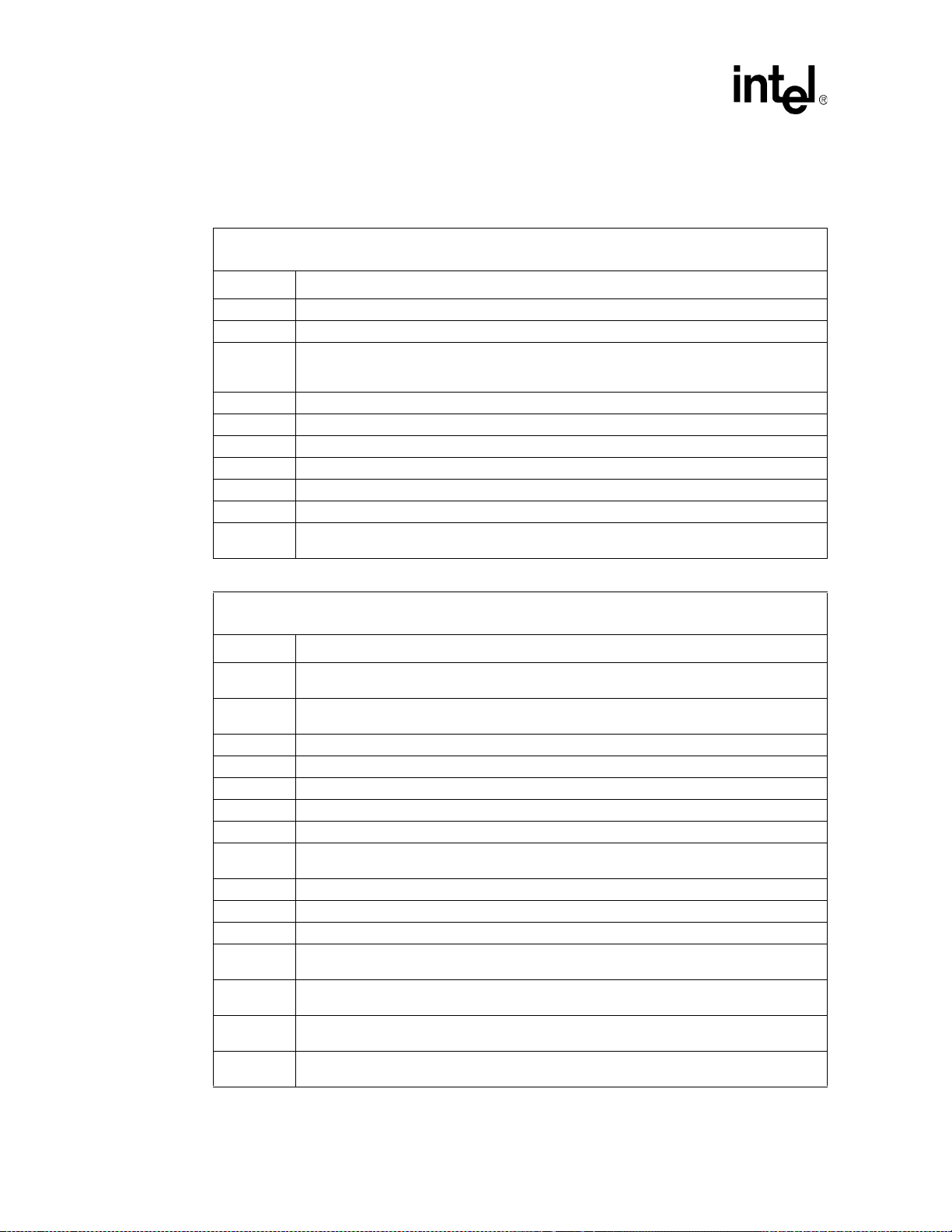

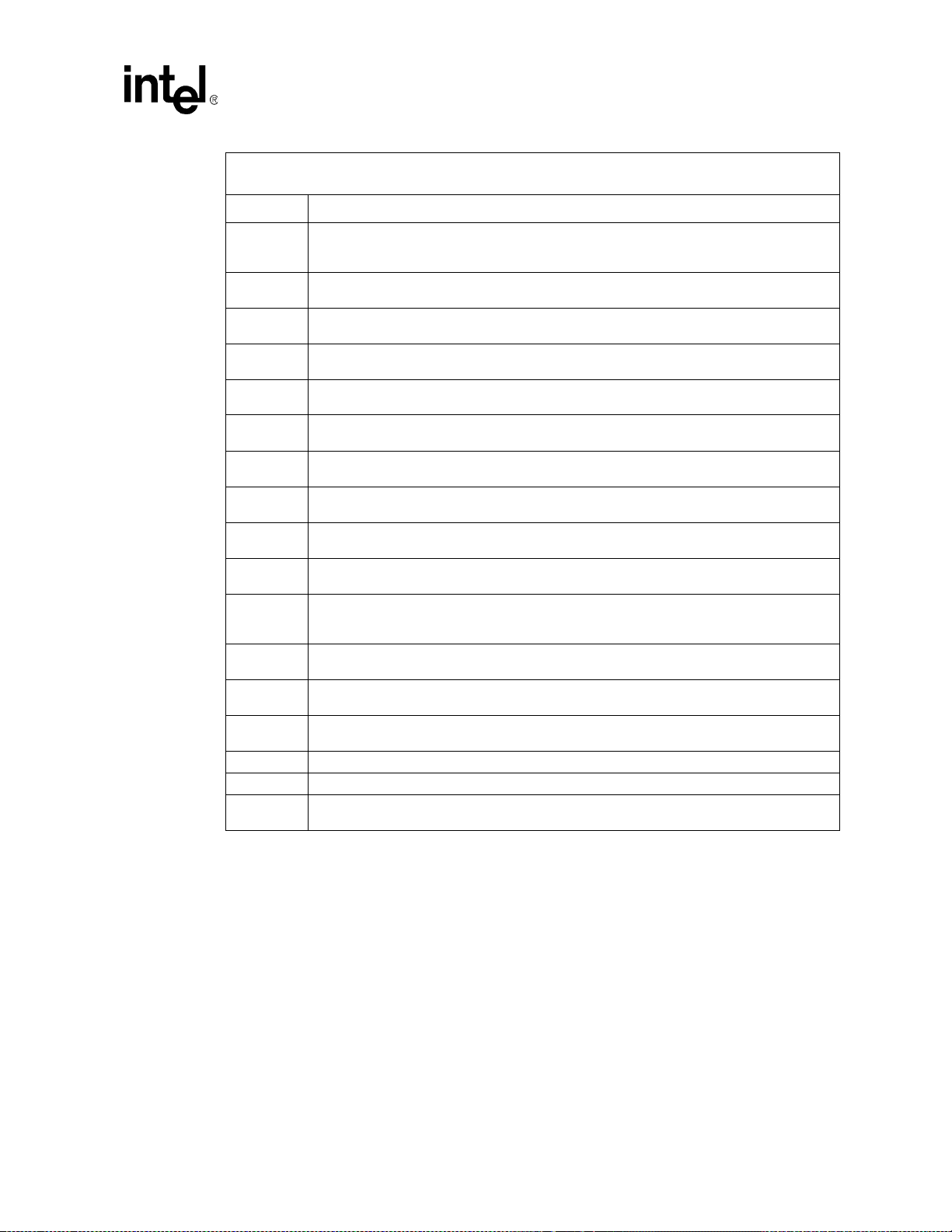

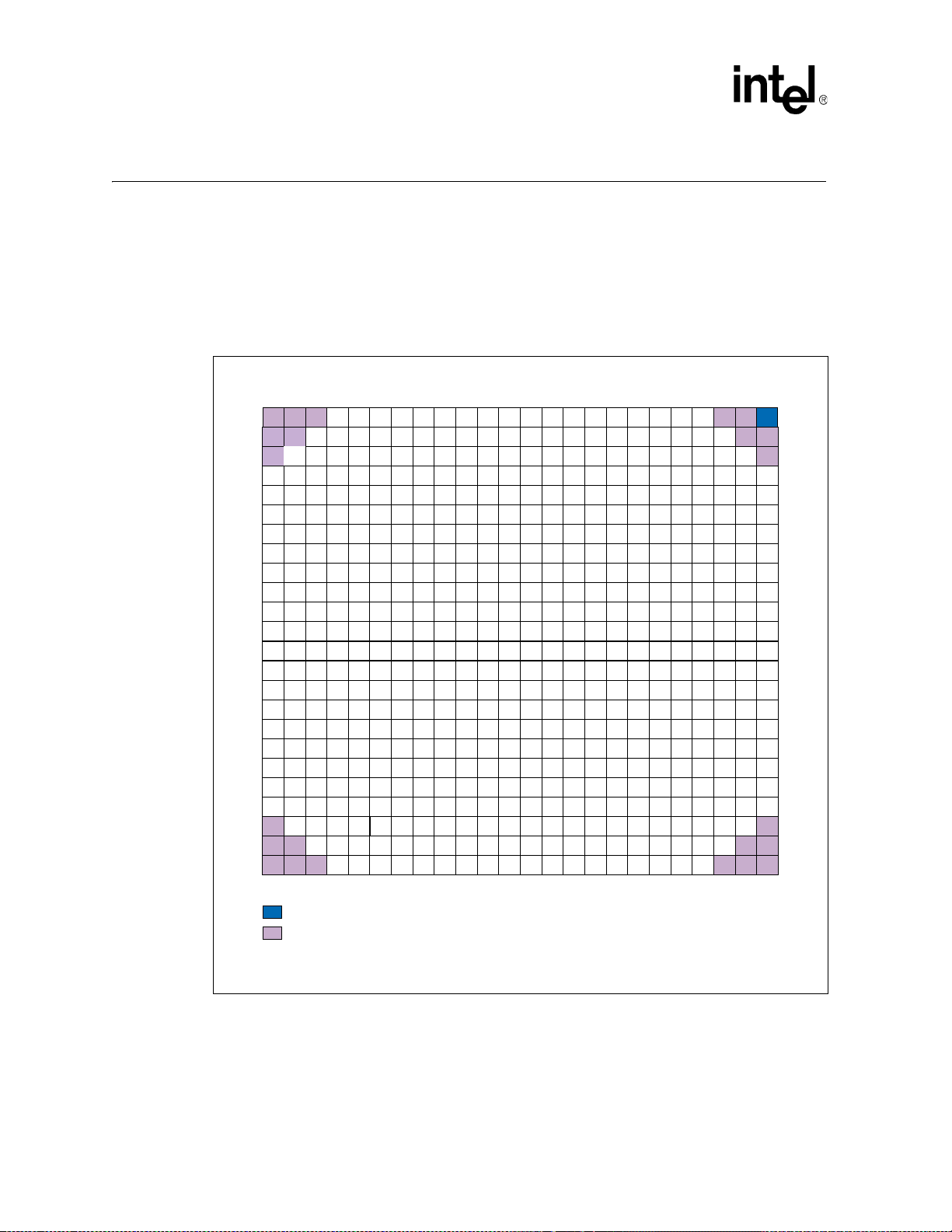

3.0 Ball Assign ments and Ball List Tables......................................................................................23

3.1 Ball Assignments................................................................................................................23

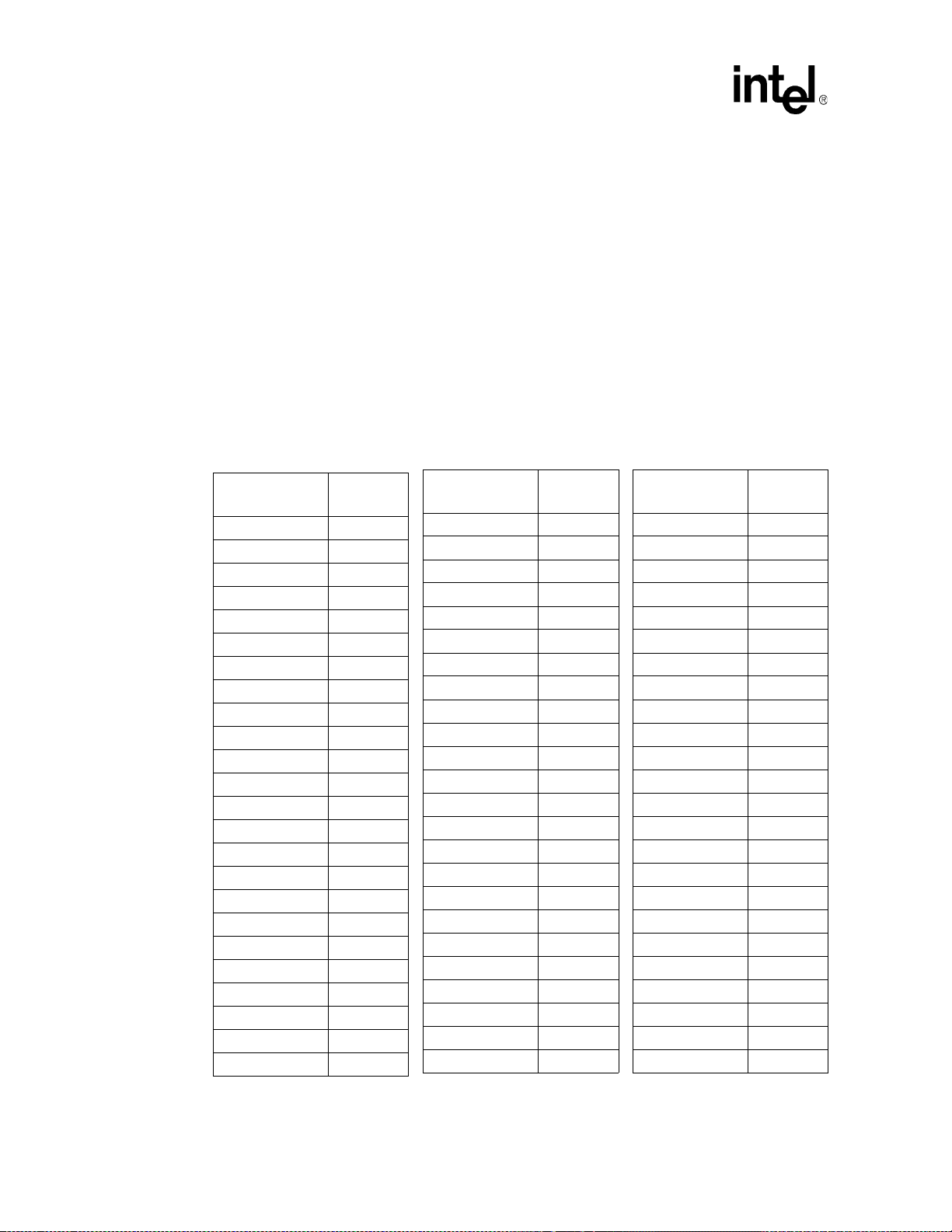

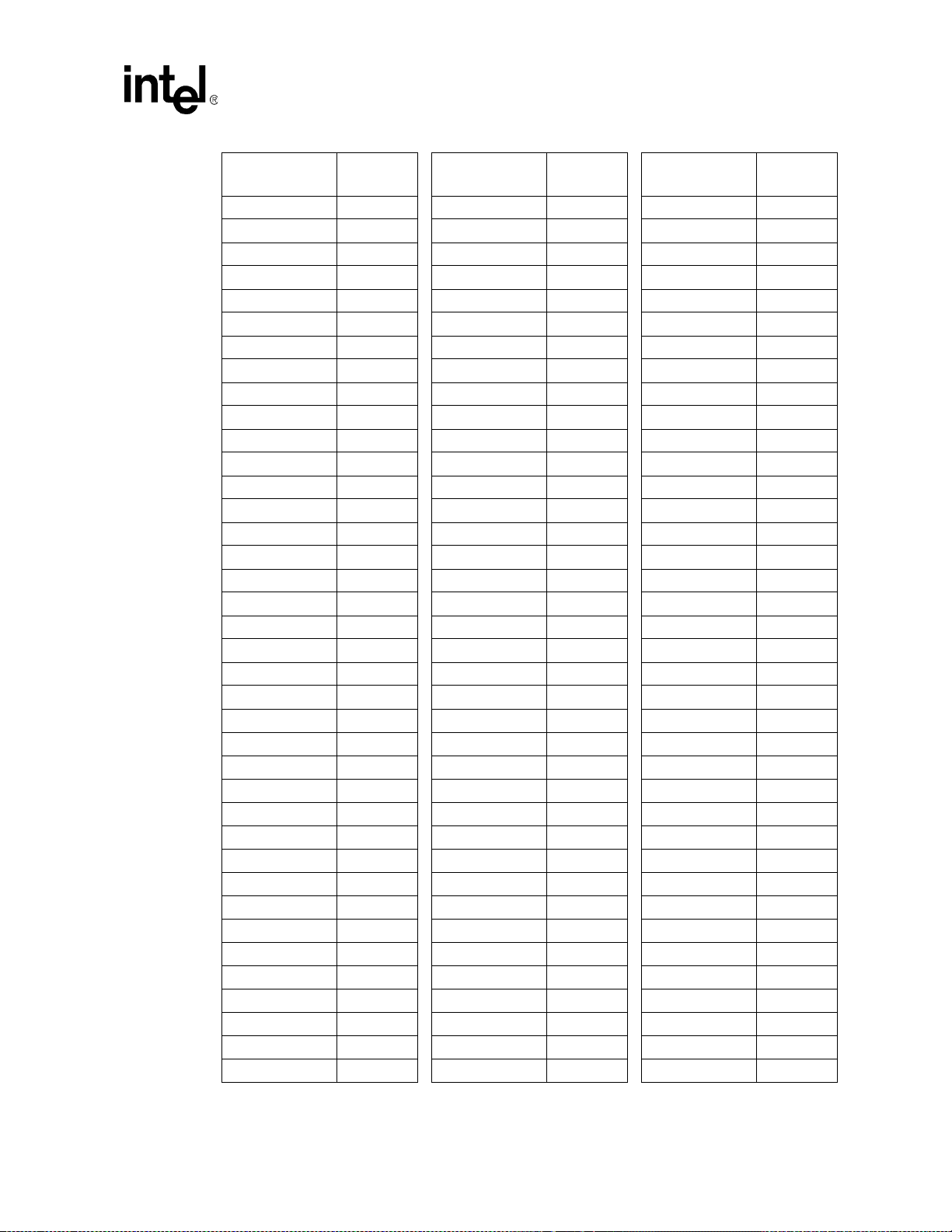

3.2 Ball List Tables...................................................................................................................24

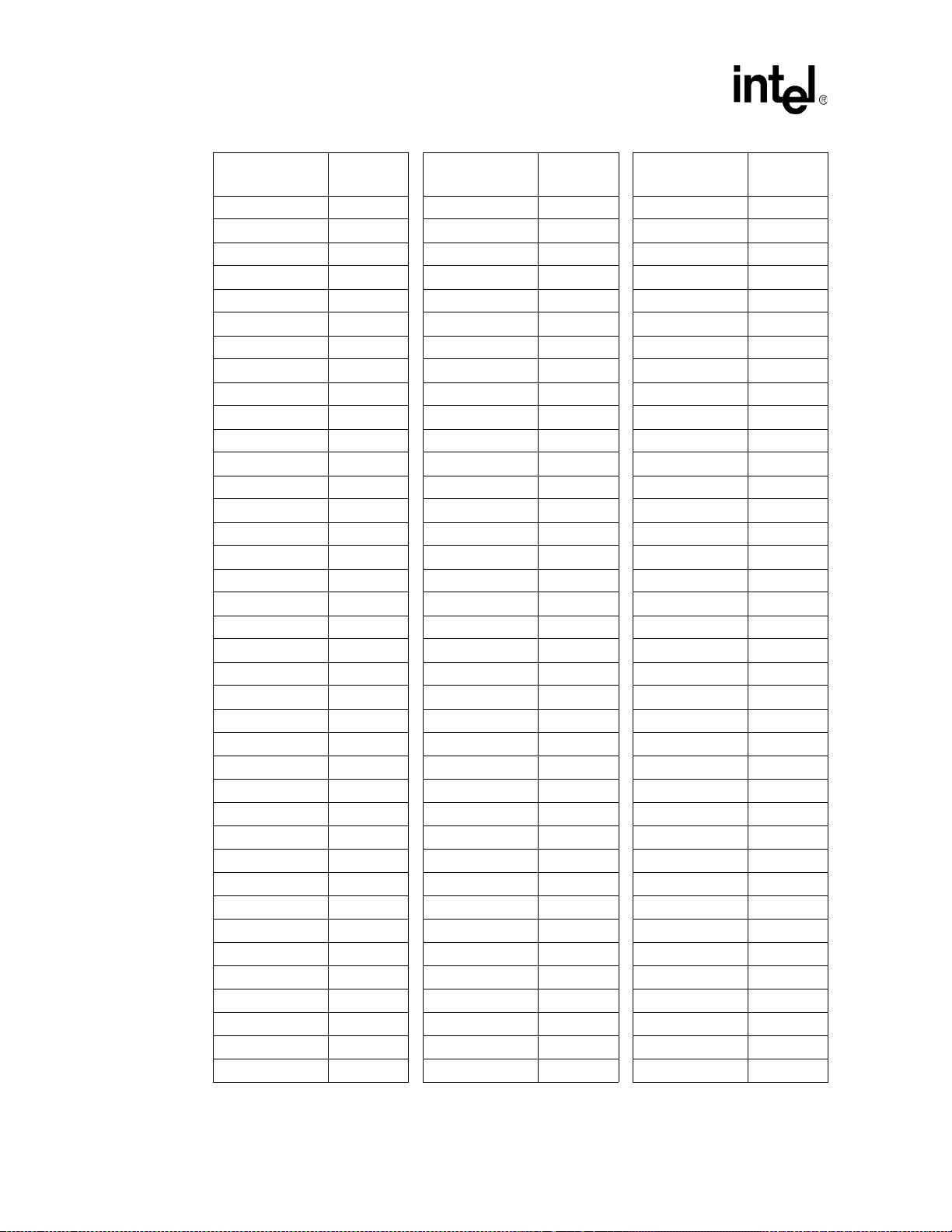

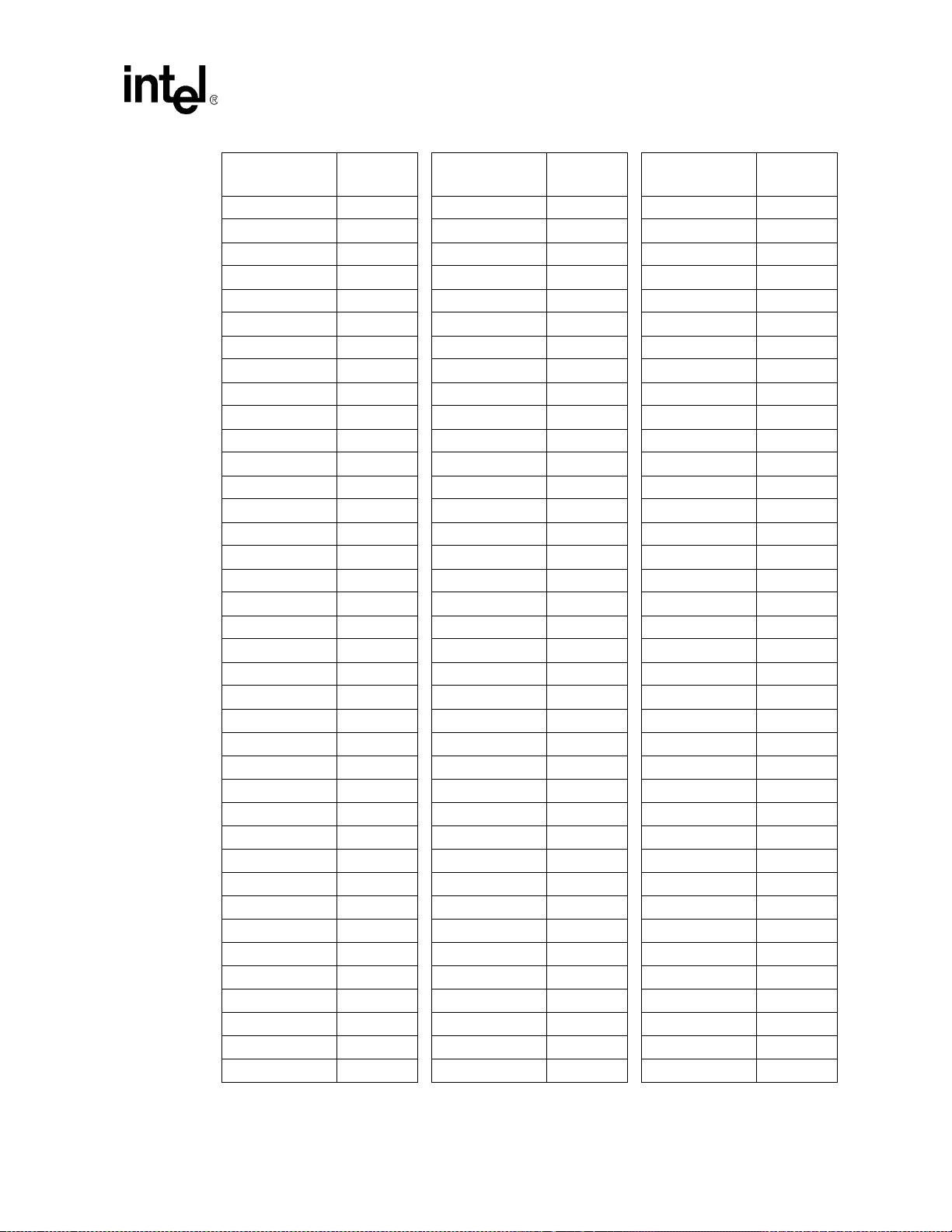

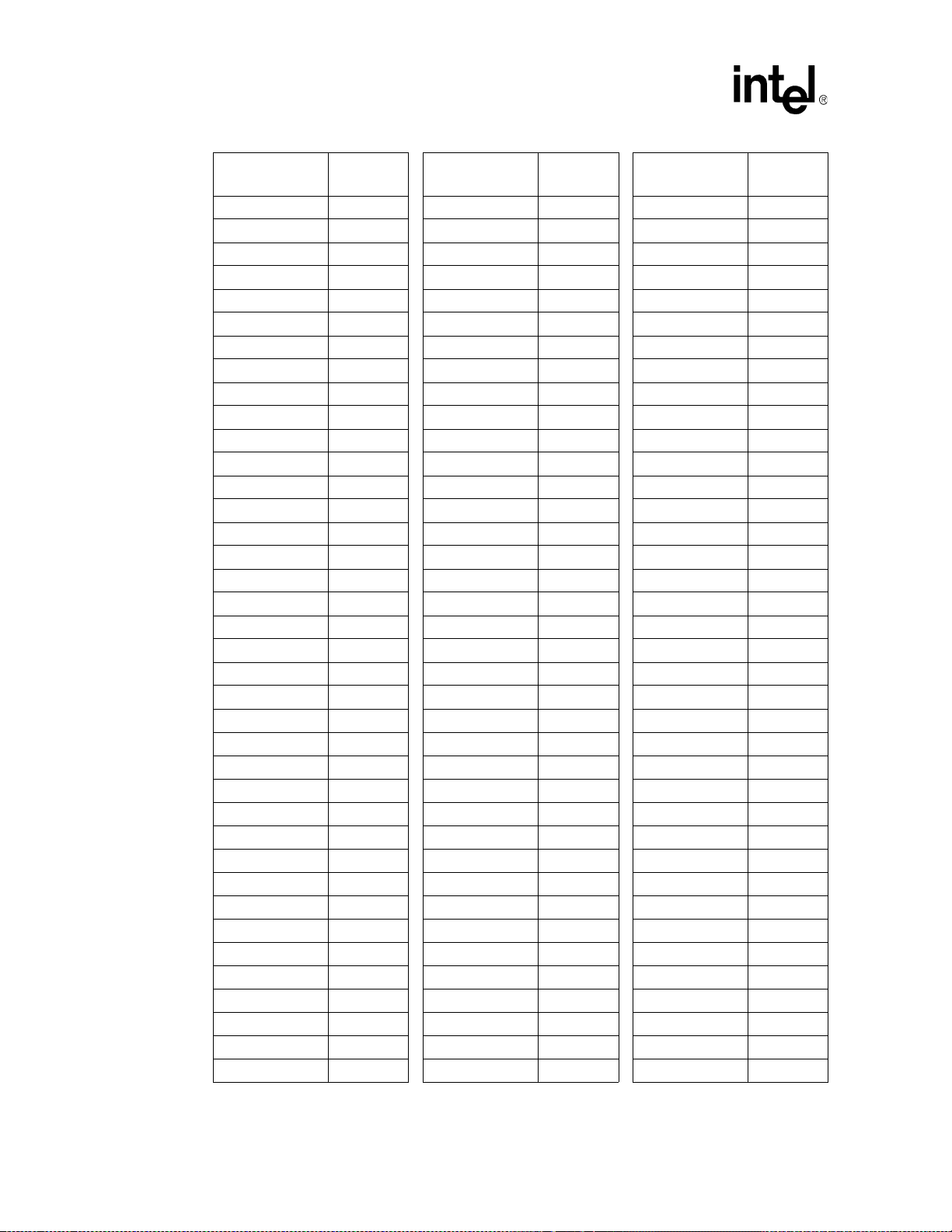

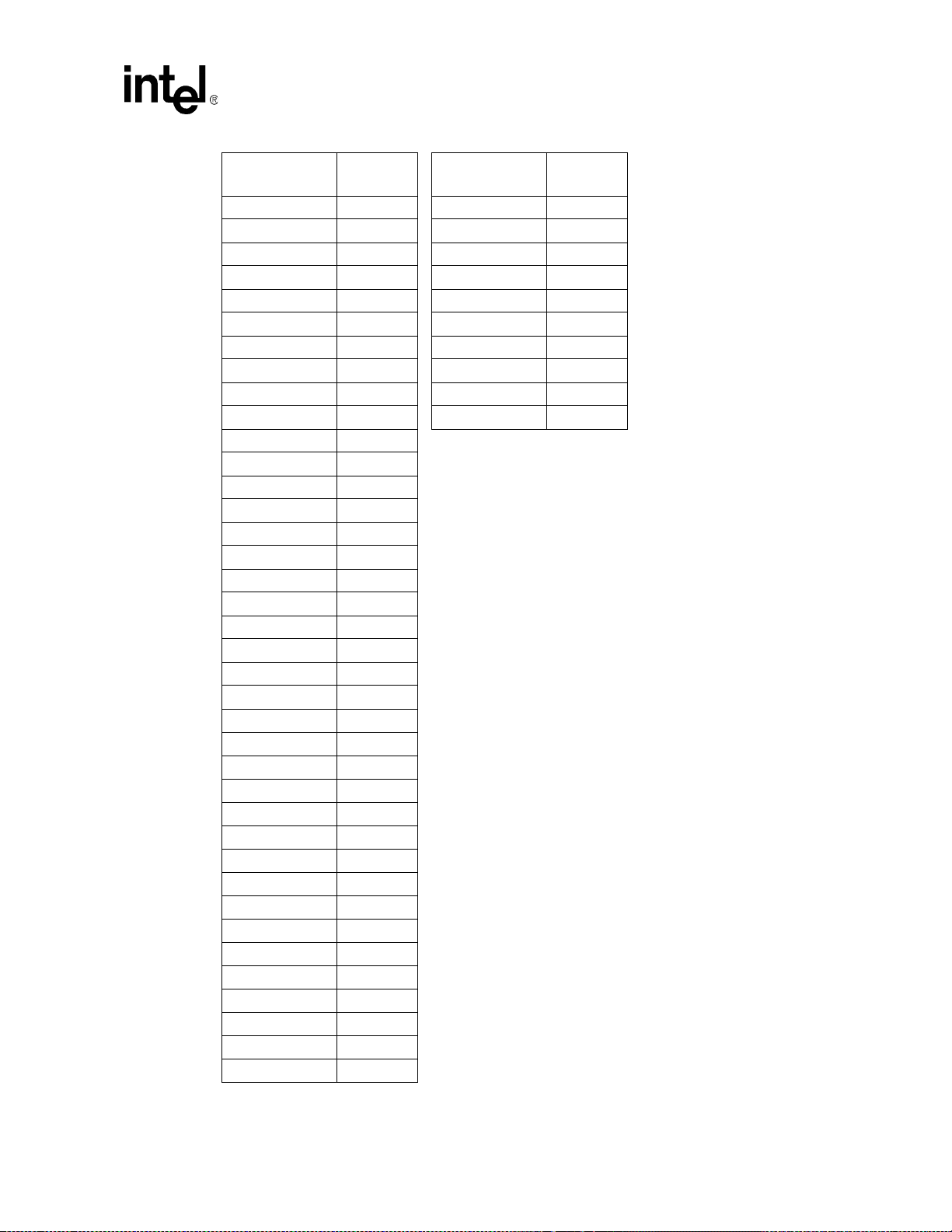

3.2.1 Balls Listed in Alphabetic Order by Signal Name ..................................................24

3.2.2 Balls Listed in Alphabetic Order by Ball Location ..................................................30

4.0 Bal l Assignm ents and Sign al Descrip tions ..............................................................................37

4.1 Naming Conventions ..........................................................................................................37

4.1.1 Signal Name Conventions .....................................................................................37

4.1.2 Regi ste r Ad d ress Conventions ............ ..................................................................37

4.2 Interface Signal Groups........................................... ............ ............ ......... ....... ............ .......38

4.3 Signal Description Tables............................................... ....... ................. ......... ............ .......39

4.4 Ball Usage Summary..........................................................................................................57

4.5 Multiplexed Ball Connections.............................................................................................. 58

4.5.1 GMII/RGMII/SerDes/OMI Multiplexed Ball Connections................................. .......58

4.5.2 SPI3 MPHY/SPHY Ball Connections.....................................................................59

4.6 Ball State During Reset ......................................................................................................61

4.7 Powe r Su p ply Se q uen cing.... ..............................................................................................63

4.7.1 Power-Up Sequence........................................................... .. ....... ....... ..... ....... .......63

4.7.2 Power-Down Sequence................................ .........................................................63

4.8 Pul l-Up/Pull-Down Ball Guide li n e s................................................................. .....................64

4.9 Analog Power Filtering........................................................................................................64

5.0 Function al Descriptions.............................................................................................................. 66

5.1 Me dia Access Controller (MAC) .........................................................................................66

5.1.1 Features for Fiber and Copper Mode ............................................................. .......67

5.1.1.1 Padding of Undersized Frames on Transmit .........................................67

5.1.1.2 Automatic CRC Generation ...................................................................67

5.1.1.3 Filtering of Rece ive Packets ..................... .............................................67

5.1.1.4 CRC Error Detection..............................................................................69

5.1.2 Flow Control.................................................................................... .......................69

5.1.2.1 802.3x Flo w Control (Full-Duplex Operation).........................................70

5.1.3 Mixed-Mode Operation..........................................................................................75

5.1.3.1 Configuration ..........................................................................................75

5.1.3.2 Key Configuration Registers..................................................................75

5.1.4 Fiber Mode.............................................................................................................76

5.1.4.1 Fiber Auto-Negotiation...........................................................................77

5.1.4.2 D eterm ining If Link Is Established in Auto-Negotiation Mode ................77

5.1.4.3 Fiber Forced Mode.................................................................................77

5.1.4.4 Determination of Link Establishment in Forced Mode ...........................77

5.1.5 Copper Mode................................................ .........................................................77

Datasheet 3

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

Page 4

Contents

5.1.5.1 Speed.....................................................................................................78

5.1.5.2 Duplex....................................................................................................78

5.1.5.3 C opper Auto -Negot iation ....................................................................... 78

5.1.6 Jumbo Packet Support ..........................................................................................78

5.1.6.1 Rx Statisti cs...........................................................................................79

5.1.6.2 TX Statistics...........................................................................................79

5.1.6.3 Loss-less Flo w Contro l.............................................................. .............79

5.1.7 Packet Buffer Dimensions........................... ..........................................................80

5.1.7.1 TX and RX FIF O Operation ...................................................................80

5.1.8 RMON Statis tics Support..... ..................................................................................80

5.1.8.1 Conventions...........................................................................................82

5.1.8.2 Advantages............................................................................................83

5.2 SPI3 In te rface.....................................................................................................................83

5.2.1 MPHY Operati o n ....................................................................................................84

5.2.1.1 SPI3 RX Round Robin Data Transmission ............................................84

5.2.2 MPHY Logical Tim i ng........ ....................................................................................84

5.2.2.1 Transmit Timi n g........ .............................................................................85

5.2.2.2 Receive Timing...................................................................................... 85

5.2.2.3 Clock Rates............................................................................................87

5.2.2.4 Parity......................................................................................................87

5.2.2.5 SPHY Mode........................................................................................... 87

5.2.2.6 S PHY Logical Tim ing.............................. ...............................................88

5.2.2.7 Transmit Timi n g (S PHY)............ ............................................................88

5.2.2.8 Receive Timing (SPHY).........................................................................88

5.2.2.9 SPI3 Flow Control..................................................................................91

5.2.3 Pre-Pending Function....................................................... ....... ....... ....... ............ ....93

5.3 Gigabit Media Independent Interface (GMII) ......................................................................93

5.3.1 GMII Signal Multiplexing........................................................................................94

5.3.2 GMII Interface Signal Definition......................................................................... ....94

5.4 Reduced Gigabit Media Independent Interface (RGMII) ....................................................96

5.4.1 Multiplexing of Data and Control.......................................................................... ..96

5.4.2 Timing Specifics.....................................................................................................97

5.4.3 TX_ER and RX_ER Coding...... .............................................................................97

5.4.3.1 In-Band Status ........ ...............................................................................99

5.4.4 10/100 Mbp s Functionality.....................................................................................99

5.5 MDIO Control and Interface........................................................ ........................................99

5.5.1 MDIO Address.....................................................................................................100

5.5.2 MDIO Register Descriptions................................................................................100

5.5.3 Clear When Done................................................................................................100

5.5.4 MDC Generation..................................................................................................100

5.5.4.1 MDC High-Frequency Operation ..................................................... ....100

5.5.4.2 MDC Low-Frequency Operation................ .............. ....... ................. ....100

5.5.5 Management Frames...........................................................................................101

5.5.6 Single MDI Command Operation .........................................................................101

5.5.7 MDI State Machine.......................... ....................................................................101

5.5.8 Autoscan Operation.............................................................................................103

5.6 SerDes Interface...............................................................................................................103

5.6.1 Features...............................................................................................................103

5.6.2 Functional Description.........................................................................................103

5.6.2.1 Transmitter Operational Overview.......................................................104

5.6.2.2 Transmitter Programmable Driver-Power Levels.................................104

4 Datasheet

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

Page 5

Contents

5.6.2.3 R ecei ve r Operational Overv iew .... .......................................................105

5.6.2.4 Selective Power-Down.........................................................................105

5.6.2.5 Receiver Jitter Tolerance.....................................................................105

5.6.2.6 Transmit Jitter ...................................................................................... 1 06

5.6.2.7 Receive Jitt e r.......................................................................................106

5.7 Optical Module Interface...................................................................................................107

5.7.1 Intel® IXF1104 MAC-Supported Optical Module Interface Signal s .....................1 07

5.7.2 Functional Descript i ons.......................................................................................108

5.7.2.1 High-Speed Serial Interface.................................................................108

5.7.2.2 Low-S peed Status Signaling Interface.................................................108

5.7.3 I²C Module Configuration Interface................................................................... ...110

5.7.3.1 I

5.7.3.2 I

5.7.3.3 I

2

C Control and Data Registers............................................................110

2

C Read Operation..............................................................................110

2

C Write Operation ..............................................................................111

5.7.3.4 I²C Protocol Specifics........... ................................................................112

5.7.3.5 Port Protocol Operation .......................................................................113

5.7.3.6 C lo ck and Data Transitions. .................................................................113

5.8 LED In te rface....................................................................................................................115

5.8.1 Modes of Operation.............................................................................................115

5.8.2 LED Interface Signal Description.......................................... ..... ....... .. .......... .. .....116

5.8.3 Mode 0: Detailed Operation.................................................................................1 16

5.8.4 Mode 1: Detailed Operation.................................................................................1 17

5.8.5 Power-On, Reset, Initia li za tion ............................................................................118

5.8.6 LED DATA Decodes............................ ................................................................118

5.8.6.1 LE D Si gnaling Beh av ior .......................................................................1 19

5.9 CPU Inte r face ...................................................................................................................120

5.9.1 Functional Descript i on.........................................................................................121

5.9.1.1 Read Access........................................................................................121

5.9.1.2 Write Access ........................................................................................121

5.9.1.3 CPU Timing Parameters......................................................................1 22

5.9.2 Endian ..................................................................................................................122

5.10 TAP Interfa c e (JTAG ).......................................................................................................123

5.10.1 TAP State Machine........... ...................................................................................123

5.10.2 Instruction Register and Supported Instructions..................................................124

5.10.3 ID Register...........................................................................................................125

5.10.4 B oundary Scan Register................................................................ ......................1 25

5.10.5 Bypass Register ...................................................................................................125

5.11 Loopbac k Modes ..............................................................................................................125

5.11.1 S PI3 Interface Loopbac k ..................................................................................... 125

5.11.2 Line S ide Interface Loopba ck .... ..........................................................................126

5.12 Clocks...............................................................................................................................127

5.12.1 System Interface Reference Clocks.....................................................................1 27

5.12.1.1 CLK125................................................................................................ 1 28

5.12.2 S PI3 Receive and Transm it Clocks .................................................................. ...128

5.12.3 RGMII Clocks.......................................................................................................1 28

5.12.4 MDC Clock.......... .................................................................................................128

5.12.5 JTAG Clock..........................................................................................................129

5.12.6 I

2

C Clock..................................... .........................................................................129

5.12.7 LED Clock...... ......................................................................................................129

Datasheet 5

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

Page 6

Contents

6.0 Applications...............................................................................................................................130

6.1 Change Port Mode Initialization Sequence.......................................................................130

6.2 Disable and Enable Port Sequences.. .............................................................................. 131

6.2.1 Disable Port Sequence..... ...................................................................................131

6.2.2 Enable Port Sequence.........................................................................................131

7.0 Electrical Specifications ...........................................................................................................132

7.1 DC Speci fi c a ti o n s.............................................................................................................133

7.1.1 Undershoot / Overshoot Specifications ...............................................................135

7.1.2 RGMII Elec tr i c a l Char a cte ristics........ ..................................................................135

7.2 SPI3 AC Ti mi ng Spe c i fications.........................................................................................137

7.2.1 Receive In te r face Timing.....................................................................................137

7.2.2 Transmit Interface Timing....................................................................................139

7.3 RGMII AC Ti mi ng Spe c i fication........................................................................................141

7.4 GMII AC Timi n g Spe cification......... ..................................................................................142

7.4.1 1000 Base-T Operation .......................................................................................142

7.4.1.1 1000 B A SE-T Tran smit Interface................... ......................................142

7.4.1.2 1000BASE-T Receive Interface...........................................................143

7.5 SerDes AC Timing Specification.......................................................................................144

7.6 MDIO AC Timing Specification.........................................................................................145

7.6.1 MDC High-Speed Operation Timing.................................................................... 145

7.6.2 MDC Low-Speed Operation Timing.....................................................................145

7.6.3 MDIO AC Timing..................................................................................................146

7.7 Optical Module and I

7.7.1 I

2

C Interface Timing.............................................................................................147

2

C AC Timing Specifi ca tion .............................................................147

7.8 CPU AC Timing Specification........................................................................................... 149

7.8.1 CPU Interface Read Cycle AC Timing.................................................................149

7.8.2 C PU Interface Write Cycle AC Timing.................................................................149

7.9 Transmit Pause Control AC Timing Specification.............................................................151

7.10 JTAG AC Timing Specifi ca tion ......... ................................................................................152

7.11 System AC Timing Specification.......................................................................................153

7.12 LED AC Timing Specification............................................................................................154

8.0 Register Set................................................................................................................................155

8.1 Docu ment Structure..........................................................................................................155

8.2 Graphical Representation................................................................................... .......... .. ..155

8.3 Per Port Registers............................................................................................................156

8.4 Register Map ....................................................................................................................156

8.4.1 MAC Control Registers........................................................................................163

8.4.2 MAC RX Statistics Register Overview.................................................................174

8.4.3 MAC TX Statistics Register Overview.................................................................178

8.4.4 PHY Autoscan Registers.....................................................................................181

8.4.5 Global Status and Configuration Register Overview ...........................................188

8.4.6 R X FIFO Register Overview................................................................................193

8.4.7 TX FIFO Register Over view.................................................................................203

8.4.8 MDIO Register Overview.....................................................................................211

8.4.9 SPI3 Register Overview.......................................................................................213

8.4.10 SerDes Register Overview..................................................................................220

8.4.11 Optical Module Register Overview ...................................................................... 222

6 Datasheet

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

Page 7

Contents

9.0 Mechanical Specifications........................................................................................................2 24

9.1 Overview...........................................................................................................................224

9.1.1 Features...............................................................................................................224

9.2 Package Specifics ............................................................................................................224

9.3 Package Information.........................................................................................................225

9.3.1 CBGA Package Diagrams ....................................................................... ....... .....225

9.3.2 Flip Chip-Plastic Bal l Gr id Arr a y Pa cka g e Diagra m...................................... .......227

9.3.3 Top Label Marking Example......... .......................................................................229

10.0 Product Ordering Informatio n .................................................................................................. 2 30

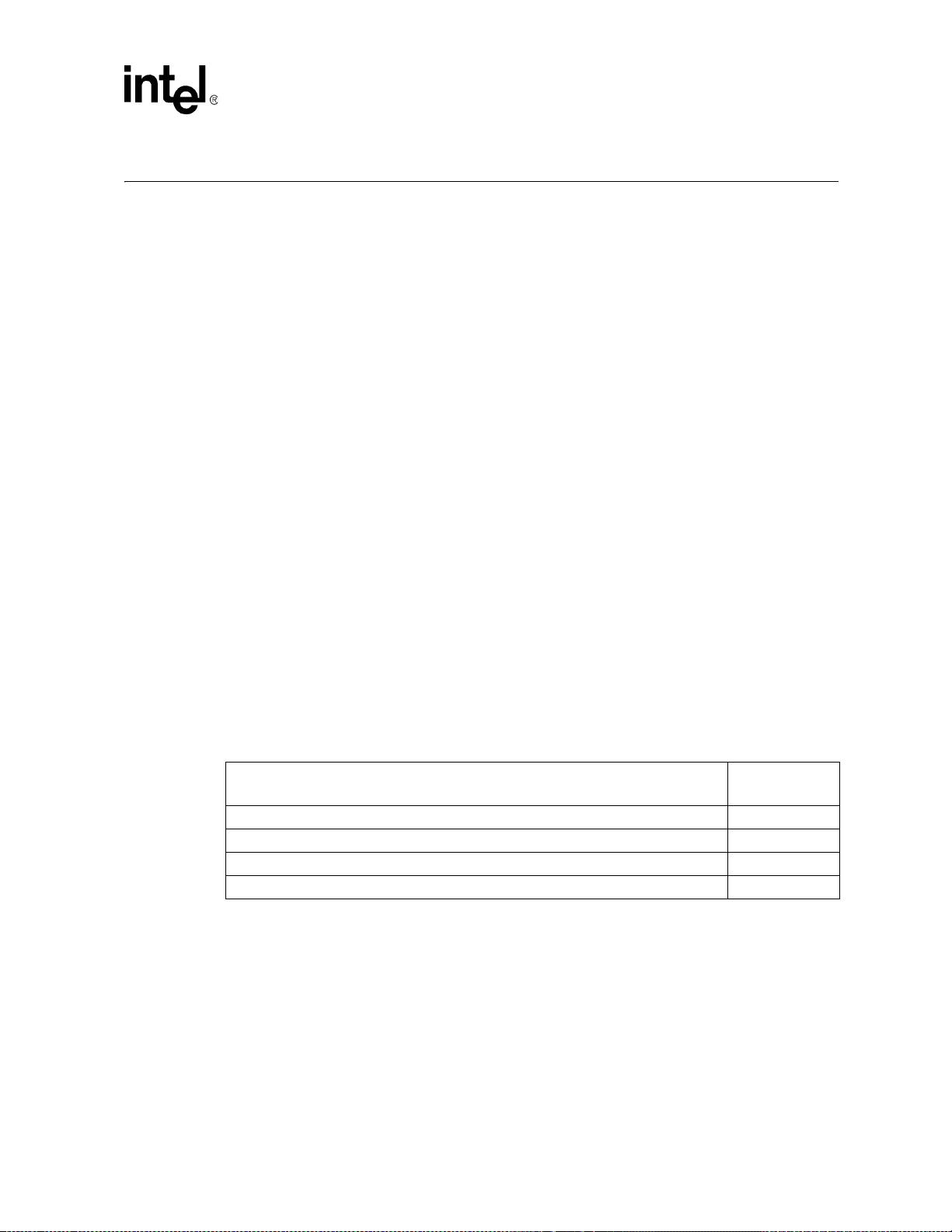

Figures

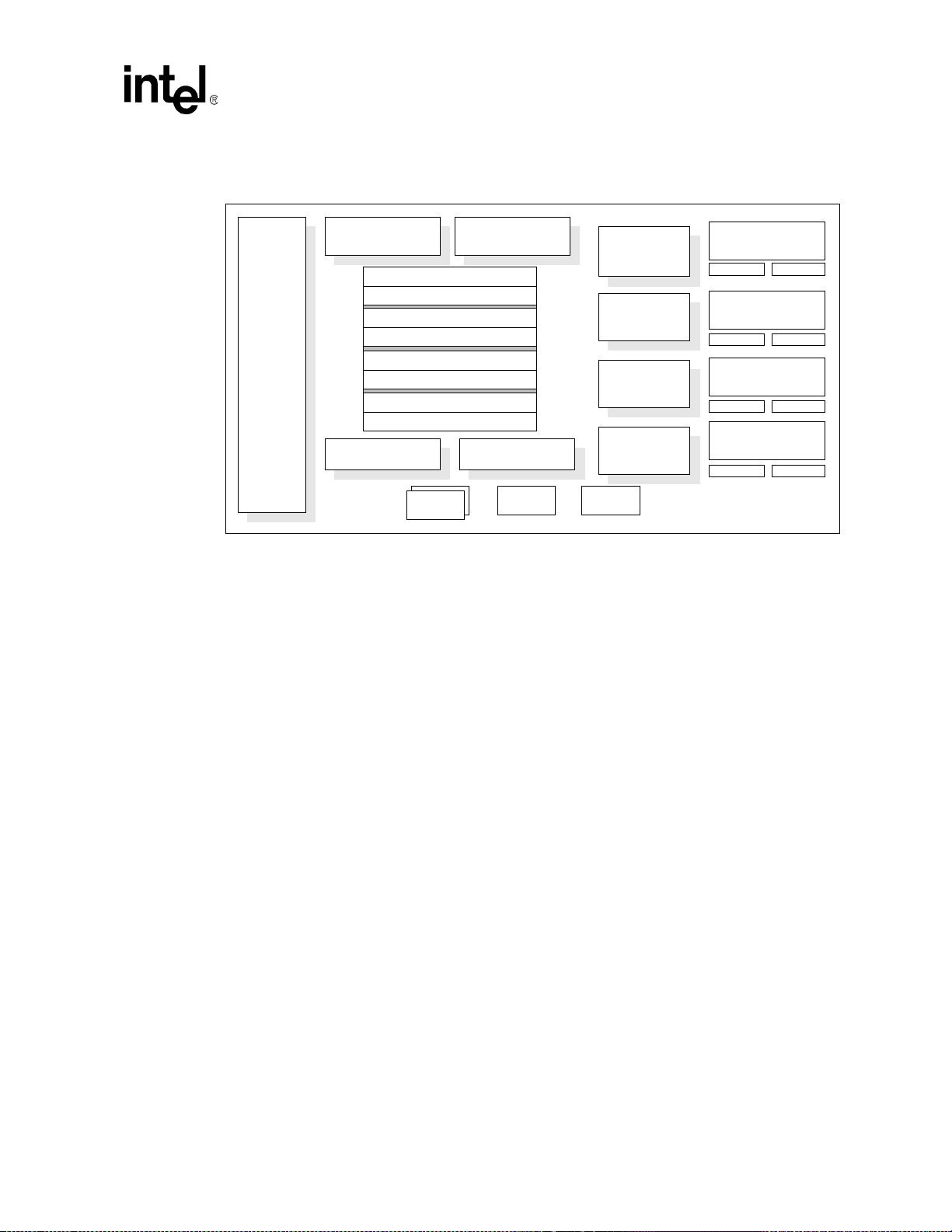

1 Block Diagram ............................................................................................................................21

2 Internal Architecture....................................................................................................................22

3 552-Ball CBGA Assignments (Top View) ...................................................................................23

4 Interface Signals . .......................................................................................................................38

5 Power Supply Sequencing.... ......................................................................................................63

6 Analog Power Supply Filter Network ..........................................................................................65

7 Packet Buffering FIFO................................................................................................................71

8 Ethernet Fram e Forma t..............................................................................................................71

9 PAUSE Frame Format................................................................................................................72

10 Transmit Pause Control Inter fa ce...............................................................................................74

11 MPHY Transmit Logical Timing............... .............................................................................. .....85

12 MPHY Receive Logical Timing....................................................................................... ............86

13 MPHY 32-Bit Interface................................................................................................................86

14 SPHY Transmit Logical Timing...................................................... ................... ................... .......88

15 SPHY Re ce ive Logical Timing....................................................................................................89

16 SPHY Connection for Two Intel

17 MAC GMII Interconnect............................................................. .................................................94

18 RGMII Interface..........................................................................................................................96

19 TX_CTL Behavior........................................... ............................................................................98

20 RX_ C TL Be h av ior...... .................................................................................................................98

21 Management Frame Structure (Single-Frame Format) ............................................................ 101

22 MDI State..................................................................................................................................1 02

23 Se r De s Receiver Jitter Tolerance........ ......................................................................... ............106

2

24 I

C Random Read Transaction .................................................................................. ...............1 11

25 Data Validity Timing..................................................................................................................1 13

26 Start and Stop Definition Timing...............................................................................................113

27 Ackn o w l e d ge Ti mi n g.. ...............................................................................................................114

28 Random Read...........................................................................................................................115

29 Mode 0 Timing..........................................................................................................................116

30 Mode 1 Timing..........................................................................................................................118

31 Read Timing Diagram - Asynchronous Interface....................................................... ...............121

32 W rite Timing Diagram - Asynchronous Interface......................................................................122

33 SPI3 Interface Loopback Path........................................................................................ ..........126

34 Line Side Interface Loopback Path.................................. ............ ............ ....... ......... ............ .....127

35 SPI3 Receive Interface Timing.................................................................................................137

36 SPI3 Transmit Interface Timing................................................................................................139

®

IXF1104 MAC Ports (8-Bit Interface).....................................90

Datasheet 7

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

Page 8

Contents

37 RGMII Interface Timing ............................................................................................................141

38 1000BASE-T Transmit Interface Timing...................................................................................142

39 1000BASE-T Receive In te r face Timing.............................. ......................................................143

40 SerDe s Ti mi n g Diag r a m............. ..............................................................................................144

41 MDC High-Speed Operation Timing................................... ..... .. ....... ..... ....... ..... ....... .. .......... .. ..145

42 MDC Low- Speed Ope ra tion Timing..........................................................................................145

43 MDIO Write Timing Diagram ........... .........................................................................................146

44 MDIO Rea d Timin g Diag r a m............................................................ ........................................146

45 Bus Tim in g Diag ra m.......... ....................................................................................................... 147

46 Write Cycle Diagram.................................................................................................................147

47 CPU Interface Read Cycle AC Timing......................................................................................149

48 CPU Interface Write Cycle AC Timing ......................................................................................149

49 Pause Control Interface Timing....... .........................................................................................151

50 JTAG AC Timing.......................................................................................................................152

51 System Reset AC Timing.........................................................................................................153

52 LED AC Inter fa ce Ti mi n g............ ..............................................................................................154

53 Memory Overview Diagram ......................................................................................................155

54 Regi ste r Overview Diagram.......... ............................................................................................156

55 CBGA Package Diagram.............. ....... ..... ....... ....... ..... ....... ....... ..... ....... ..... ....... .. ....... .......... .. ..225

56 CBGA Package Side View Diagram.........................................................................................226

57 FC-PBGA Package (Top and Bottom Views)...........................................................................227

58 FC-PBGA Mechanical Specific at i ons.......................................................................................228

59 Pack age Mar king Example....................................................................................................... 229

60 Orde r ing Information – Sample ....... .........................................................................................230

Tables

1 Ball List in Alphanumeric Order by Signal Name.......................................... ....... ....... ............ ....24

2 Ball List in Alphanume ric Order by Ball Location........................................................................30

3 SPI3 Interface Signal Descriptions.............................................................................................39

4 SerDes Interface Signal Descriptions......................................................................... .......... .. ....47

5 GMII Interface Signal Descriptions.............................................................................................48

6 RGMII Interface Signal Descriptions ..........................................................................................50

7 CPU Interface Signal Descriptions ............................................................... ..... ....... ....... ....... ....51

8 Transmit Pause Control Interface Signal Descriptions...............................................................53

9 Optical Module Interface Signal Descript ions. ............................................................................53

10 MDIO Interface Signal Descriptions ...........................................................................................54

11 LED Interface Signal Descriptions............ ....... ..... ....... ..... ....... .. ....... ..... ....... ..... ....... .. .......... .. ....55

12 JTAG Interface Signal Descriptions............................................................................................55

13 System Interface Signal Descriptions.................................................................. ....... .......... ......55

14 Power Su p ply Signal Descriptions..............................................................................................56

15 Ball Usage Summary..................................................................................................................57

16 Line Side Interface Multiplexed Balls ..........................................................................................58

17 SPI3 MPHY/SPHY Interface.......................................................................................................59

18 Definition of Output and Bi-directional Balls During Hardware Reset.........................................61

19 Power Supply Sequencing .................................................................... ....... ....... ....... ..... ....... ....64

20 Pull-Up/Pull-Down and Unused Ball Guid e li n e s........................................... ..............................64

21 Analog Power Balls ....................................................................................................................65

22 CRC Errored Packets Drop Enable Behavior.............................................................................69

23 Valid Decodes for TXPAUSEADD[2:0].......................................................................................74

24 Operational Mode Configuration Registers................................................................................76

8 Datasheet

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

Page 9

Contents

25 RMON Additional Statistics.........................................................................................................81

26 GMII Interface Signal Definitions................................................................................................95

27 RGMII Signal Definitions.............................................................................................................97

28 TX_ER and RX_ER Coding Description .. .................................................... ...............................97

29 SerDes Driver TX Power Levels...............................................................................................104

30 Intel

®

IXF1104 MAC-to-SFP Optical Module Interface Connections................................. .......107

31 LED Interface Signal Descriptions ............................................................................................116

32 Mode 0 Clock Cycle to Data Bit Relationship ...........................................................................117

33 Mode 1 Clock Cycle to Data Bit Relationship ...........................................................................118

34 LED_DATA# Decodes..............................................................................................................119

35 LED Behavior (Fiber Mode)......................................................................................................1 19

36 LED Behavior (Copper Mode) ..................................................................................................120

37 Byte Swapper Behavior...................... ......................................................................................123

38 Instruction Register Description................................................................................................124

39 Absolute Maximum Ratings......................................................................................................132

40 Recommended Operating Conditions.......................................................................................133

41 DC Specifications.....................................................................................................................134

42 SerDes Transmit Characteristics..............................................................................................134

43 SerDes Receive Characteristics...............................................................................................135

44 Undershoot / Overshoot Limits.................................................................................................135

45 RGMII Power............................................................................................................................136

46 SPI3 Receive Interface Signal Parameters .......................................... ....................................138

47 SPI3 Transmit Interface Signal Parameters ............................................................................. 1 40

48 RGMII Interface Timing Parameters.........................................................................................1 41

49 GMII 1000BASE-T Trans mit Signal Parameters......................................................................142

50 GMII 1000BASE-T Receive Signal Parameters .......................................................................1 43

51 SerDes Timing Parameters ......................................................................................................144

52 MDIO Timing Parameters.........................................................................................................146

2

53 I

C AC Timing Characteristics..................................................................................................147

54 CPU Interface Write Cycle AC Signal Parameters...................................................................150

55 Transmit Pause Control Inter fa ce Ti mi n g Para me ter s..............................................................151

56 JTAG AC Timing Parameters ...................................................................................................1 52

57 System Reset AC Timing Parameters......................................................................................153

58 LED Interface AC Timing Parameters...................................................................................... 1 54

59 MAC Control Registers ($ Port Index + Offset) ........................... ....... ..... .. ..... ....... .. ..... ..... .......156

60 MAC RX Statistics Registers ($ Port Index + Offset)................................................................ 1 57

61 MAC TX Statistics Registers ($ Port Index + Offset) ................................................................158

62 PHY Autoscan Registers ($ Port Index + Offset)......................................................................159

63 Global Status and Configuration Registers ($ 0x500 - 0X50C)................................................159

64 RX FIFO Registers ($ 0x580 - 0x5 BF)......................................................................................1 59

65 TX FIF O Registers ($ 0x600 - 0x63E)............... .......................................................................160

66 MDIO Registers ($ 0x680 - 0x683)............................................................ ....... ....... ..... ....... .....161

67 SPI3 Registers ($ 0x700 - 0 x716).............................................................................................161

68 SerDes Registers ($ 0x780 - 0x798) ........................................................................................162

69 Optical Module Registers ($ 0x799 - 0x79F) ......................................................... ....... ....... .....162

70 Station Address ($ Port_Index +0x00 – +0x01)........ ................................................................163

71 Desired Duplex ($ Port_Index + 0x02).....................................................................................163

72 FD FC Type ($ Port_Index + 0x03) ....... ...................................................................................163

73 Collision Distance ($ Port_Index + 0x05) .................................................................................1 64

74 Co ll ision Threshold ($ Port_Index + 0x06) ...............................................................................164

Datasheet 9

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

Page 10

Contents

75 FC TX Timer Value ($ Port_Index + 0x07) ...............................................................................164

76 FD FC Address ($ Port_Index + 0x08 – + 0x09)................................................... ...................164

77 IPG Receive Time 1 ($ Port_Index + 0x0A) ............................................................. ............ ....165

78 IPG Receive Time 2 ($ Port_Index + 0x0B) ............................................................. ............ ....165

79 IPG Tr ansm it Time ($ Port_Index + 0x0C)...............................................................................165

80 Pause Threshold ($ Port_Index + 0x0E) ..................................................................................166

81 Max Frame Size (Addr: Port_Index + 0x0F)................ ....... ....... ....... .......... ....... ....... ....... ....... ..166

82 MAC IF Mode and RGMII Speed ($ Port_Index + 0x10)........... ....... .......... ....... ....... ....... .........167

83 Flush TX ($ Port_Index + 0x11)............................................................................. ...................167

84 FC Enable ($ Port_Index + 0x12).............................................................................................168

85 FC Back Pressure Length ($ Port_Index + 0x13)..................................................................... 168

86 Short Runts Threshold ($ Port_Index + 0x14).......................................................................... 169

87 Discard Unknown Control Frame ($ Port_Index + 0x15)..........................................................169

88 RX Config Word ($ Port_Index + 0x16).... ....... ....... .......... .. ....... ....... .......... ....... .. ....... .......... ....169

89 TX Config Word ($ Port_Index + 0x17)....................................................................................170

90 Diverse Config Write ($ Port_Index + 0x18)......... ............ ....... ....... ....... ....... ....... ....... ............ ..171

91 RX Packet Filter Control ($ Port_Index + 0x19) ........................................... ....... ....... .......... ....172

92 Port Multicast Address ($ Port_Index +0x1A – +0x1B) ............................................................ 173

93 MAC RX Statistics ($ Port_Index + 0x20 – + 0x39)..................................................................174

94 MAC TX Statistics ($ Port_Index +0x40 – +0x58)......... ........................................................... 178

95 PHY Control ($ Port Index + 0x60)................................................................. ..........................181

96 PHY Status ($ Port Index + 0x61) ............................................................................................182

97 PHY Identification 1 ($ Port Index + 0x62) ...............................................................................183

98 PHY Identification 2 ($ Port Index + 0x63) ...............................................................................184

99 Auto-Negotiation Advertisement ($ Port Index + 0x64) ............................................................184

100 Auto-Negotiation Link Partner Base Page Ability ($ Port Index + 0x65)...................................185

101 Auto-Negotiation Expansion ($ Port Index + 0x66) . .................................................................186

102 Auto-Negotiation Next Page Transmit ($ Po rt Index + 0x67) ...................................................187

103 Port Enable ($0x500)................................................................................................................188

104 Inte r fa ce Mod e ($0 x5 0 1)..........................................................................................................188

105 Link LED Enable ($0x502) ..................................................................................... ...................189

106 MAC Soft Reset ($0x505).........................................................................................................189

107 MDIO Soft Reset ($ 0 x5 0 6)........... ............................................................................................190

108 CPU Interface ($0x508)................................. ....... ....... ....... ....... ....... .......... ....... ....... ....... .........190

109 LED Contro l ($ 0 x5 0 9)................................................ ...............................................................190

110 LED Flash Rate ( $ 0 x5 0A ).........................................................................................................191

111 LED Fault Disable ($0x50B).....................................................................................................191

112 JTAG ID ($0x50C).................................................................................................................... 192

113 RX FIFO High Watermark Port 0 ($0x580)............................................................ ...................193

114 RX FIFO High Watermark Port 1 ($0x581)............................................................ ...................193

115 RX FIFO High Watermark Port 2 ($0x582)............................................................ ...................193

116 RX FIFO High Watermark Port 3 ($0x583)............................................................ ...................194

117 RX FIFO Low Watermark Port 0 ($0x58A)............................................................................... 194

118 RX FIFO Low Watermark Port 1 ($0x58B)............................................................................... 194

119 RX FIFO Low Watermark Port 2 ($0x58C) ...............................................................................195

120 RX FIFO Low Watermark Port 3 ($0x58D) ...............................................................................195

121 RX FIFO Overflow Frame Drop Counter Ports 0 - 3 ($0x594 – 0x597)....................................195

122 RX FIFO Port Reset ($0x59E)..................................................................................................196

123 RX FIFO Errored Frame Drop Enable ($0x59F) .......................................................................196

124 RX FIFO Overflow Event ($0x5A0) ..........................................................................................197

10 Datasheet

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

Page 11

Contents

125 RX FIFO Errored Frame Drop Counter Ports 0 - 3 ($0x5A2 - 0x5A5)......................................198

126 RX FIFO SPI3 Loopback Enable for Ports 0 - 3 ($0x5B2)........................................................1 99

127 RX FIFO Padding and CRC Strip Enable ($0x5B3) ................................................ .......... .......200

128 RX FIFO Transfer Threshold Port 0 ($0x5B8)..........................................................................201

129 RX FIFO Transfer Threshold Port 1 ($0x5B9)..........................................................................201

130 RX FIFO Transfer Threshold Port 2 ($0x5BA)..........................................................................202

131 RX FIFO Transfer Threshold Port 3 ($0x5BB)..........................................................................202

132 TX FIFO High Watermark Ports 0 - 3 ($0x600 – 0x603)..........................................................203

133 TX FIFO Low Waterma rk Register Ports 0 - 3 ($0x60A – 0x60D)..................................... .......204

134 TX FIFO MAC Threshold Register Ports 0 - 3 ($0x614 – 0x617).............................................205

135 TX FIFO Overflow/Underfl ow/Out of Sequence Event ($0x61E)........ ......................................206

136 Loop RX Data to TX FIFO (Line-Side Loopback) Ports 0 - 3 ($0x6 1F) ................................... 207

137 TX FIFO Port Reset ($0x620)..................... .. ..... ....... ..... .. ....... ..... ....... ..... .. ....... ..... .. .......... .. .....207

138 TX FIFO Overflow Frame Drop Counter Ports 0 - 3 ($0x621 – 0x624)................... .......... .. .....208

139 TX FIFO Errored Frame Drop Counter Ports 0 - 3 ($0x625 – 0x629) ......................................209

140 TX FIFO Occupancy Counter for Ports 0 - 3 ($0x62D – 0x630)...............................................210

141 TX FIFO Port Drop Enable ($0x63D)....................................................... .. ....... ..... .. ..... ....... .....210

142 MDIO Single Command ($0x680).............................................................................................211

143 MDIO Single Read and Write Data ($0x681)............................................................................211

144 Autoscan PHY Address Enable ($0x682)................................................................................. 2 12

145 MDIO Control ($0x683)....... ......................................................................................................212

146 SPI3 Transmit and Global Configuration ($0x700)................... ................................................213

147 SPI3 Receive Configuration ($0x701)......................................................................................2 15

148 Address Parity Error Packet Dr op Counter ($0x70A).... ...........................................................219

149 TX Driver Power Level Ports 0 - 3 ($0x784).............................................................................220

150 TX and RX Power-Down ($0x787) ...........................................................................................220

151 RX Signal Detect Level Ports 0 - 3 ($ 0x793) ............................................... .............................220

152 Clock and Interface Mode Change Enable Ports 0 - 3 ($0x794)..............................................221

153 Optical Module Status Ports 0-3 ($0x799) . ...............................................................................222

154 Optical Module Control Ports 0 - 3 ($0x79A)............................... .. .......... .. ....... ....... ..... ....... .....222

2

155 I

C Control Ports 0 - 3 ($0x79B)............ .......................................................................... .........223

2

156 I

C Data Ports 0 - 3 ($0x79F)................................................................................................... 223

157 Product Information ...................................... ....... .......... ....... ....... ....... ....... ....... ....... .................2 30

Datasheet 11

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

Page 12

Contents

Revision History

Page # Description

71 Modified Figure 8 “Ethernet Fra m e Format” [changed Preamb le byte cou nt to 7 bytes].

136 Section 45, “RGMII Power” [cha ng ed V

Added bullet to

110

227 Replaced Figure 57 “FC-PBGA Package (Top and Bottom Views)” on page 227.

215 Modified Table 147 “SPI3 Receive Configuration ($0x701)”.

222 Modified Table154 “Optical Module Control Ports 0 - 3 ($0x79A)”: changed de fa ult values.

223 Modified Table 155 “I

249 Modified Table 208 “I2 C Data Ports 0 - 9 ($0x79F)” (changed address f rom $0x79C to $0x79F).

229 Added Section 9.3.3, “Top Label Marking Example”.

230

supports random single-byte reads and does not guarantee coherency when reading two-byte

registers.

Modifed Table 157 “Product Information” and Figure 60 “Ordering Information – Sample” under

Section 10.0, “Product Ordering Information”.

Section 5.7.3, “I²C Module Configuration Interface”: The I2C inter face only

Revision Number: 009

Revision Date: 27-Oct-2005

to V

CC

DD in IIH

2

C Control Ports 0 - 3 ($0x79B)”.

and IIL]

Revisio n Date: August 1, 2005 (Sh eet 1 of 2)

Page # Description

1

55

72 Modified Figure 9 “PAUSE Frame Format” [changed Preamble byte count to 7 bytes].

85 Modified Figure 11 “MPHY Transmit Logical Timing” [updated TDAT[31:0]].

86 Modified Figure 12 “MPHY Receive Logical Timing” [updated RDAT[31:0]].

88 Modified Figure 14 “SPHY Transmit Logical Timing” [updated TDAT[7:0]].

89 Modified Figure 15 “S PHY Receive Lo gical Timing” [updated R DAT[7:0] and RPRTY].

121

125 Added paragraphs two and three unde r Section 5.11, “Loopback Modes”.

129 Changed 3.3 V CMOS to 2.5 V CMOS under Section 5.12.5, “JTAG Clock” on page 129.

131 Added Section 6.2, “ Disable and Enable Port Sequences”.

136

138

140

146

Added 552-ball Ceramic Ball Grid Array (CBGA) compl iant with RoHS an d Product Ordering

Number information.

Modified Table 12 “JTAG In ter f ace S i gna l D esc rip t ions” : changed Standard to 3.3 V LVTTL from

2.5 V CMOS.

Modified Figure 31 “Read Timing Diagram - Asynchronous Interface”: changed uPx_ADD[12:0]

to uPx_ADD[10:0].

Modified Table 45 “RGM II Power” [changed V

changed V

Modified Table 46 “SPI3 Re ce iv e In ter f ac e Sig n a l Par a m eters” [changed RFCLK duty cycle to

45 min an d 55 ma x ; Changed Min for R FC L K fre q ue nc y to 90].

Modified Table 47 “SPI3 Transmit Interface Signal Parameters” [changed TFCLK duty cycle to

45 min an d 55 ma x].

Changed MDC to MDIO Output delay max for t3 for 2.5 MHz from 200 to 300 in Ta bl e5 2 “ MDI O

Timing Parameters” on page 146.

value to VDD + .3].

IN

Revision Number: 008

, VOL, VIH, VIL minimum conditions t o V

OH

DD

and

12 Datasheet

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

Page 13

Contents

Revision Date: August 1, 2005 (Sheet 2 of 2)

Page # Description

170

181

182

183

184

184

185

186

187

211

213

215

222

227

229 Replaced Figure 59 “Package Marking Example”.

229 Added Section 9.4, “RoHS Compliance” on page 229.

230

Modified Table 89 “TX Config Word ($ Port_Index + 0x17)” [changed default value f or the

register from “0x00 01A0” to “0x000001A0” and changed default value for bit 6 (Half Duplex)

from 1 to 0].

Modified Table 95 “PHY Control ($ Port Index + 0x60)” [added “ Need one-sentence

descr iptions of re gister” and register default value].

Modified Table 96 “PHY Status ($ Por t Index + 0x61)” [added “Nee d on e-se nt ence desc r ipt io ns

of register” and register default value].

Modified Table 97 “PHY Identification 1 ($ Port Index + 0x62)” [added “Need one-sentence

descr iptions of re gister” and register default value].

Modified Table 98 “PHY Identification 2 ($ Port Index + 0x63)” [added “Need one-sentence

descr iptions of re gister” and register default value].

Modified Table 99 “Auto-Negotiat ion Advertisement ($ Port Index + 0x64)” [ added “Need on e-

sentence descriptions of register” and register default value].

Modified Table 100 “Auto-Negotiation Link Partner Base Page Ability ($ Port Index + 0x65)”

[added “Need one-sentence descriptions of register” and register default value].

Modified Table 101 “Auto-Negotiation Expansion ($ Port Index + 0x66)” [added “Need one-

sentence descriptions of register” and register default value].

Modified Table 102 “ Aut o- Ne goti at i on Next Page T r ans mit ($ Por t Inde x + 0x6 7) ” [a dd ed “Need

one-sentence descr iptions of re gister” and register default value].

Modified Table 143 “MDIO Single Read and Write Data ($0x681)” [changed MDIO write data to

“MDIO write data to external device”].

Modified Tabl e 146 “SP I3 Transm it an d Gl ob al Co nfi gu r at io n ($0x700 )” [changed default value

for bits 3:0 from “0” to “1” and changed default value for entire register from “0x0020000F” to

“0x00200000”].

Modified Table 147 “SPI3 Receive Configuration ($0x701)” [changed default value for bits 11:8

from “0xF” to “0x1”].

Modified Table 154 “Optical Module Control Ports 0 - 3 ($0x79A)” [changed default value for

bits 16:13 from “0xF” to “0x1”].

Added Figure 57 “FC-PBGA Package (Top and Bottom Views)” on page 227 and Figure 58

“FC-PBGA Mechanical Specifications” on page 228.

Added CBGA RoHS-compliant and FC-PBGA ordering information under Table 157 “Product

Information”.

Revision Number: 008

Datasheet 13

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

Page 14

Contents

Revision Number: 007

Revision Date: March 24, 2004

Page # Description

All Globally replaced GBIC with Optical Module Interface.

All Globally edited signal names.

Globally changed SerDes and PLL analog power ball names as follows:

TXAVTT and RXAVTT changed to AVDD1P8_2

TXAV25 and RXAV25 changed to AVDD2P5_2

All

PLL1_V DD A and PLL2_V DD A changed to AVDD1P8_1

PLL3_VDDA changed t o AVDD2P5_1

PLL1_GNDA, PLL2_GNDA, and PLL3_GNDA changed to GND

Reworded and rearranged the Product Features section on page one

1

Changed Jumbo frame support from “10 kbytes” to “9.6 KB”.

21 Changed heading to Section 2.0, “General Description” [was Section 2.0, “Block Diagram”].

23/37

Revers ed sections as follows:

Section 3.0, “Ball Assignments and B all List Tables”

Section 4.0, “Ball Assignments and Signal Descriptions”

Modif ied Table 1 “Ball List in Alphanumeric Order by Signal Name”:

Changed A10 from VCC to VDD

Changed C12 from VCC to VDD

Changed D11 from VCC to VDD

Changed J20 from GND to VDD

24

(Sheet 1 of 5)

Changed Ball A1 from NC to No Pad.

Changed Balls A2, A3, A22, A23, A24, B1, B2, B23, B24, C1, C24, AB1, AB24, AC1, AC2, AC23,

AC24, AD1, AD2, AD3, AD22, AD23, AD24 from NC to No Ball.

Modif ied Table 2 “Ball List in Alphanumeric Order by Ball Location ”

Changed A10 from VCC to VDD

Changed C12 form VCC to VDD

Changed D11 from VCC to VDD

Changed J20 from GND to VDD

30

Changed Ball A1 from NC to No Pad.

Changed Balls A2, A3, A22, A23, A24, B1, B2, B23, B24, C1, C24, AB1, AB24, AC1, AC2, AC23,

AC24, AD1, AD2, AD3, AD22, AD23, AD24 from NC to No Ball.

Updated Figure 4 “In terface Signals” [modified SPI3 interface signals and ad ded MPHY and SPHY

38

categories; modif ied signal names].

Broke old T able 1, “IXF1104 Signal Descriptions” into the following:

39

Table 3 “SPI3 Interface Signal Desc riptions” on page 39 through Table 14 “Power Supply Signal

Descriptions” on page 56

Modif ied Table 3 “SPI3 Interface Signal Descripti ons” on page 39 [edited description for DTPA;

39

added text to TFCLK description; added text to RFCLK description].

Modified Table 6 “RGMII Interface Signal Descriptions” [Added Ball Designators; added notes

50

under descriptions].

51 Modified Table 7 “CPU Interface Signal Descriptions” [UPX_DATA[16]: deleted J10, added M10].

53 M odified Table 9 “Optical Module Interface Si gnal Descriptions” [added Ball Designators].

54 Modified Table 10 “MDIO Interface Signal Descriptions” [moved note from MDC to MDIO].

Modif ied Table 14 “Power Supply Signal Descriptions” [ad ded Ball Designators A4, A21, and AD21

56

to GND; added AVDD1P8_1, AVDD1P8_2, AVDD2P5_1, and AVDD2P5_2].

14 Datasheet

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

Page 15

Contents

Revision Number: 007

Revision Date: March 24, 2004

Page # Description

Modified Section 4.3, “Signal Description Tables” [changed he ading from “Signal Naming

39

Conventions; added new headings Section 4.1.1, “Signal Name Conventions” and Section 4.1.2,

“Register Address Conventions”; and added/enhanced material under headings.

Added new Section 4.5, “Multiplexed Ball Connections” with Table16 “Line Side I nterface

58

Multiplexed Balls” and Table 17 “SPI3 MPH Y/SPHY Interface”.

Modifie d S e ctio n 4 .7 , “ Pow er S u pply Se qu en cing ” [c ha nged la ng ua ge unde r thi s se ct io n and a dde d

63

Section 4.7.1, “Power-Up Sequence” and Section 4.7.2, “Power-Down Sequence”].

Modified Table 5 “Power Supply Sequen cing” [deleted 3.3 V Supplies Stable ; changed Apply 1.8 V

63

to VDD, AVDD1P8_1, and AVDD1P8_2; changed Apply 2.5 V to AVDD2P5_1 and AVDD2P5_2].

Modified Table 18 “Definition of Out put and Bi-directional Balls During Hardw are Reset” [changed

61

comments for Optical Modules].

Modif ied Tab le2 0 “Pu ll -Up/ P ul l-D ow n a nd U nu se d Ba ll Gui d el in es” [c ha ng ed TR ST _L to p ul l- dow n ;

64

added MDIO, UPX_RDY_L, I

Added new Section 4.9, “Analog Pow er Filtering” [including Figure 6 “Analog Power Supply Filter

64

Network” on page 65 a nd Table 21 “Analog Power Balls” on page 65].

Modified/edited text under Section 5.1, “Media A c cess Controller (MAC)” [rearranged and cre ated

66

new bullets].

67 Mo dified first paragraph under Section 5.1.1.1, “Padding of Unders ized Frames on Transmit”.

67 Mo dified entire Section 5.1.1.3, “Filte ring of Receive Packets”.

68 Added new Section 5.1.1.3.6, “Filter CRC Error Packets”.

69 Added note under Table 22 “CRC Errored Packets Drop Enable Behavior”.

Added new Section 5.1.2, “Flow Control” including Figure 7 “Packet Buffering FIFO”, Figure 8

69

“Ethernet Frame Format”, and Figure 9 “PAUSE Frame Format”.

Replace d Sec ti on 5.1. 2. 1.5 , “Transmit Pause Cont rol In ter f ace” [a dded Table2 3 “Valid Deco de s for

73

TXPAUSEADD [ 2:0 ] ” an d mo dified Table 10 “Transmi t P au se Co ntrol Interf ac e” .

74 Modified Figure 10 “Transmit Pause Control Interface”

75 Added note under Section 5.1.3.1, “Configuration”.

76 Added table note to Table 24 “Oper a tio na l Mo de Conf i gu ration Regi s ters ” .

77 Added note under Section 5.1.4.3, “Fiber Forced Mode”.

79 Mo dified Section 5.1.6.2, “TX Statistics” [added text to third sen tence in first paragraph].

Modified Section 5.1.6.3, “Loss-less Flow Contr ol” [changed “two kilometers” to “five kilometers” in

79

last sentence.

80 Mo dified Section 5.1.7.1.2, “RX FIFO” [changed 10 KB to 9.6 KB; added text to la st paragraph].

83 Rewrote/replaced Section 5.2, “SPI3 Interface”.

86 Edited signal names in Figure 13 “ M PHY 32-Bit Interface”.

Edited signal names in Figure 16 “SPHY Connection for Two Intel

90

Interface)”.

Added new Section 5.2.2.9, “SPI 3 Flow Control ”.

91

[Removed old “Packet-Level and Byte-Level Transfers” section.}

94 Mo dified Figure 17 “MAC GMII Interconnect” [edited signal names].

Removed old Section 5.3.3 Electrical Requirements and Table 27 “Electrical Requirements” –

NA

changed Input high current Max from 40 to 15 and Input low curren t Min from -600 to -15.

96 Added a note under Section 5.4, “Reduced Gi gabit Media Independent Interface (RGMII)”.

96 Mo dified Figure 18 “RGMII Inte rface” [edited signal names].

(Sheet 2 of 5)

2

C_DATA_ 3:0, and TX_DISABLE_3:0].

®

IXF1104 MAC Ports (8-Bit

Datasheet 15

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

Page 16

Contents

Revision Number: 007

Revision Date: March 24, 2004

(Sheet 3 of 5)

Page # Description

98 M odified Figure 19 “TX_CTL Behavior” [chan ged signal names].

98 Modified Figure 20 “RX_CTL Behavior” [changed signal names].

Modified Section 5.5, “MDIO Control and Interface” [changed 3.3 us to 3.3 ms in fourth paragraph,

99

third se nt en ce].

103

Modif ied/replaced all text under Section 5.6, “SerDes In terface” on page 103 [added Table29

“SerDes Driver TX Power Levels”].

NA Removed old Section 5.6.2.4 AC/DC Coupling.

NA Remo ved old Section 5.6.2.9 System Jitter.

107

107

Modified Table 30 “Intel

signal names].

Modified/replaced text and deleted old “Figure 19. Typical GBIC Module Functional Diagram” under

Section 5.7, “Optical Module Interface”].

®

IXF1104 MAC-to-SFP Optical Module Interface Connections” [edited

108 Modifie d se c on d se nt e nc e unde r S e c tio n 5. 7. 2 .2 . 1, “MO D _DEF_0:3”.

109 Modifie d se c on d se nt e nc e unde r S e c tio n 5. 7. 2 .2 . 3, “RX_ LO S _ 0 :3” .

109 Removed third paragraph under Se ction 5.7.2. 2.7, “RX_LOS_INT”.

110 Modified first and seco nd par ag r a ph s un de r Section 5.7.3, “I²C Module Co nfiguratio n I nt er f ac e”.

2

111 Modified Section 5.7.3.3, “I

116

119

Modified Table 31 “LED Interface Signal Descriptions” [changed 0.5 MHz to 720 Hz for LED_CLK

under Signal Description].

Modified Table 35 “LED Behavior (Fiber Mode)” [changed links under Description to “Link LED

Enable ($0x502)”].

C Write Operation” [edited portions of text].

NA Removed old Figure 30 “CPU – External and Internal Connections”.

123 Modified Table 37 “Byte Swapper Behavior” [edited/added new values].

123 Modified second paragraph under Section 5.10, “TAP Int erface (JTAG)”

126 Modified Figure 33 “SPI3 Interface Loopback Pat h”.

126 Added note under Section 5.11.2, “Line Side Interface Loopback”.

127 Modified Figure 34 “Line Side Interface Loopback Path”.

127 Changed Section 5.12, “Clocks” [from GBIC output clock to I

2

129 Changed Section 5.12.6, “I

C Clock” [from GBIC Clock to I2C Clock].

2

C Clock].

130 Added new Section 6.0, “Applications”.

Modified Table 39 “Absolute Maximum Ratings” [changed SerDes analog power to AVDD1P8_2

132

and AVDD2P5_2; changed “PLL1_VDDA and PLL2_VDDA to AVDD1P8_1; changed PLL3_VDDA

to AVDD2P5_1.

Modif ied Table 40 “Recommended Oper ating Conditions” [changed SerDes analog power to

133

AVDD1P8_2 and AVDD2P5_2; changed “ PLL1_VDDA and PLL2_VDDA to AVDD1P8_ 1; changed

PLL3_VDDA to AVDD2P5_1.

134

142

143

146

Modif ied Table 42 “SerDes Transmit Characteristics” [included SerDes power driver level

information].

Modified Table 49 “ G MII 1000BASE-T Transmit Signal Parameters” (changed Min values f or t1 and

t2.

Modified Table 50 “GMII 1000BASE-T Receive Signal Parameters” (changed Min values for t1 and

t2.

Replaced old MDIO Timing diagram and table with Figure 43 “MD IO Write Timing Dia gram”, Figur e

44 “MDIO Read Timing Diagram”, and Table 52 “MDIO Timing Parameters”.

16 Datasheet

Document Number: 278757

Revision Number: 009

Revision Date: 27-Oct-2005

Page 17

Revision Number: 007

Revision Date: March 24, 2004

Page # Description

Broke up the old Register Map into Table59 “MAC Control Registers ($ Port Index + Offset)”,

Table 60 “MAC RX Statistics Regist ers ($ Port Index + Offset)”, Table 61 “MAC TX Statistics

156

159 Edited Table 63 “Global Status and Configuration Registers ($ 0x500 - 0X50C)” [no offset].

159 Edited Table64 “RX FIFO Registers ($ 0x580 - 0x5BF)” [no offset].

160 Edited Table 65 “TX FIFO Registers ($ 0x600 - 0x63E)” [no offset].

161 Edited Table66 “MDIO Registers ($ 0x680 - 0x683)” [no offset].

161 Edited Table 67 “SPI3 Registers ($ 0x700 - 0x716)” [no offset].

162 Edited Table68 “SerDes Registers ($ 0x78 0 - 0x798)” [no of fset].

162 Edited Table 69 “Optical Module Registers ($ 0x799 - 0x79F)” [no offset].

163

167

168 Modified Table 84 “FC Enable ($ Port_Index + 0x12)” [changed description for bits 1:0].

169

170

171

172

174

178

193

195

196

198

199

201

Registers ($ Port Index + Offset)”, Table 62 “PHY Autoscan Registers ($ Port Index + Offset)”,

Table 63 “Global Status and Configuration Registers ($ 0x500 - 0X50C)”, Table64 “RX FIFO

Registers ($ 0x580 - 0x5BF)”, Table 65 “TX FIFO Registe rs ($ 0x600 - 0x63E)”, Table 66 “MDIO

Registers ($ 0x680 - 0x683)”, Table 67 “SPI3 Register s ($ 0x700 - 0x716 )”, Table 68 “SerDes

Registers ($ 0x780 - 0x798)”, and Table 69 “Optical Module Registers ($ 0x799 - 0x79F)”.

Modified Table 71 “Desir ed Duplex ($ Por t_Index + 0x02) ” [changed 100 Mbps to 1000 Mb ps in

register description.

Modified Table 82 “MAC IF Mode and RGMII Speed ($ Port_Index + 0x10)” [Added text to register

description.]

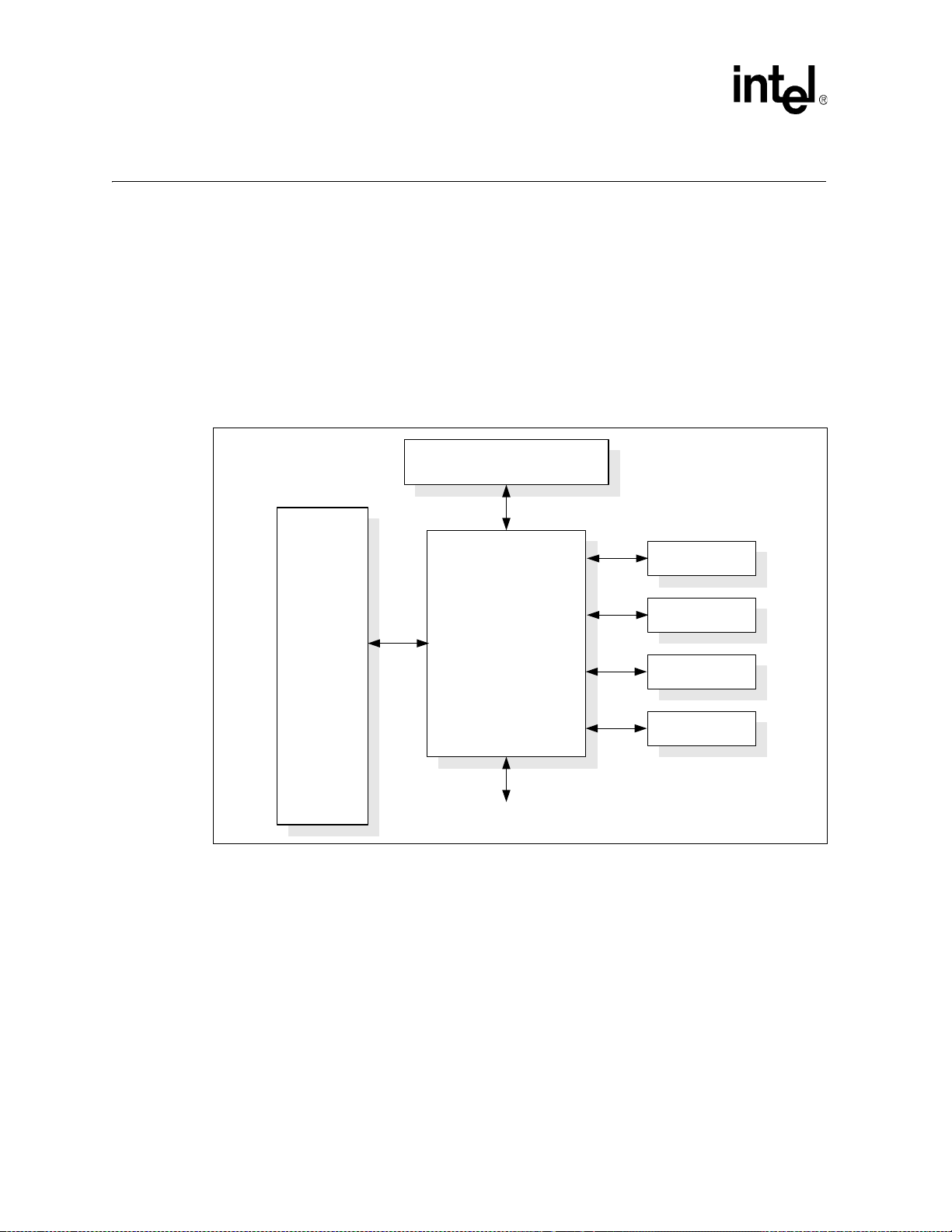

Modified Table 88 “RX Config Word ($ Port_Index + 0x16)” [edited Register Description text;