Page 1

Document Number: 313148-001US

Intel® IXDPG425 Network Gateway

Reference Platform v2.0

Quick Start Guide

October 2007

Page 2

Intel® IXDPG425 Network Gateway Reference Platform v2.0

Quick Start Guide October 2007

2 Document Number: 313148-001US

Legal Lines and Disclaimers

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR

OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS

OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING

TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE,

MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for

use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the

presented subject matter. The furnishing of doc uments and other m aterials and info rmation does no t provide an y license, expr ess or implied, by estoppel

or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different

processor families. See http://www.intel.com/products/processor_number for details.

The Intel

®

IXDPG425 Network Gateway Reference Platform v2.0 may contain design defects or errors known as errata which may cause the product to

deviate from published specifications. Current characterized errata are available on request.

This Quick Start Guide as well as the software described in it is furnished under license and may only be used or copied in accordance with the terms of

the license. The information in this m anua l is fur nish ed for info rmati onal use on ly, is subject to change without noti ce, an d s houl d n ot b e c on s tr ue d a s a

commitment by Intel Corporation. Intel Corporation assumes no responsibility or liability for any errors or inaccuracies that may appear in this document

or any software that may be provided in association with this document.

Except as permitted by such license, no part of this document may be reproduced, stored in a retrieval system, or transmitted in any form or by any

means without the express written consent of Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature may be obtained by calling

1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino logo, Core Inside, FlashFile, i960, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740,

IntelDX2, IntelDX4, IntelSX2, Intel Core, Intel Inside, Intel Inside logo, Intel. Leap ahead., Intel. Leap ahead. logo, Intel NetBurst, Intel NetMerge, Intel

NetStructure, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel Viiv, Intel vPro, Intel XScale, Itanium, Itanium Inside, MCS, MMX, Oplus,

OverDrive, PDCharm, Pentium, Pentium Inside, skoool, Sound Mark, The Journey Inside, VTune, Xeon, and Xeon Inside are trademarks of Intel

Corporation in the U.S. and other countries.

*Other names and brands may be claimed as the property of others.

Copyright © Intel Corporation, 2007.

Page 3

Intel® IXDPG425 Network Gateway Reference Platform v2.0

October 2007 Quick Start Guide

Document Number: 313148-001US 3

Intel® IXDPG425 Network Gateway Reference Platform v2.0

Contents

1.0 Introduction..............................................................................................................5

1.1 Purpose .............................................................................................................5

1.2 Related Documents .............................................................................................5

1.3 Acronyms...........................................................................................................6

1.4 Inspection..........................................................................................................6

1.5 Known Issues ..................................................................................... ................7

1.6 Technical Support................................................................................................7

2.0 Intel® IXDPG425 Platform v2.0 Overview..................................................................8

2.1 Intel

®

IXDPG425 Platform v2.0 Components Placement ...........................................9

2.2 Intel

®

IXDPG425 Platform v2.0 Hardware Settings ................................................10

2.3 PON ONU Daughterboard Modules .......................................................................11

2.3.1 EPON ONU Module..................................................................................11

2.3.2 GPON ONU Module ................................................................................. 13

2.4 Preparing the Platform for Use ............................................................................15

2.4.1 Verifying Jumper Settings........................................................................15

2.5 Starting the Platform ............. ... .. ........................................ .. .. ...........................16

A EPON ONU Board Jumper Description...................................................................... 17

B GPON ONU Board Jumper Description...................................................................... 18

Figures

1Top View: Intel® IXDPG425 Platform v2.0 Component Placement Diagram........................9

2 EPON ONU Board Components...................................................................................12

3 GPON ONU board components ................................................................................... 14

Tables

1 Related Documents ....................................................................................................5

2 Related Acronyms......................................................................................................6

3Intel

®

IXDPG425 Platform v2.0 Jumper Setting Descriptions.......................................... 10

4Intel

®

IXDPG425 Platform v2.0 Baseboard LED Descriptions. .........................................10

5 EPON ONU Board LED Descriptions.............................................................................13

6 GPON ONU Board LED Descriptions.................... .........................................................15

7 UART Communication Configuration............................................................................ 16

8 Jumper Descriptions of EPON ONU (Reference U1)........................................................17

9 Setting of EPON Processor (J3) ..................................................................................17

10 Jumper Descriptions of EPON ONU Board (J4).............................................................. 17

11 Jumper Description of GPON ONU Board (J4)...............................................................18

Page 4

Intel® IXDPG425 Network Gateway Reference Platform v2.0

Intel

®

IXDPG425 Network Gateway Reference Platform v2.0

Quick Start Guide October 2007

4 Document Number: 313148-001US

Revision History

§ §

Date Revision Description

May 2006 001 Initial release

Page 5

Intel® IXDPG425 Network Gateway Reference Platform v2.0

October 2007 Quick Start Guide

Document Number: 313148-001US 5

Intel® IXDPG425 Network Gateway Reference Platform v2.0

1.0 Introduction

1.1 Purpose

This document contains instructions for unpacking, inspecting, setting up, and starting

the Intel

®

IXDPG425 Network Gateway Reference Platform v2.0 (also referred to as the

“platform”). The IXDPG425 platform v2.0 (with optional EPON / GPON, IEEE802.11n

and MoCA module) is a single-box multi-service FTTx gateway with VoIP, routing/

switching.

Caution: Before powering-up the platform for the first time, please take time to familiarize

yourself with the platform. It’s recommended that you carefully read Section 2.0

through Section 4.0, which include:

• Diagram of the platform setup for Quick Start operation, showing the location of

factory-installed mezzanine modules and location of key interfaces to assist with

connection of the console, Ethernet, and power cables.

• Factory default settings of all switches and jumpers — to ensure they were not

accidentally changed during transport, or repositioned by a previous platform user.

• Location and definitions of the LCD display and all the platform LEDs, so that they

can be visually monitored for proper power-up and booting.

Instructions for preparing and starting the platform are in Section 4.0 and the

appendices contain additional jumper information.

It is highly recommended that you print-out and carefully read this Quick Start Guide

prior to preparing and powering up the platform for the first time.

1.2 Related Documents

The documents referenced in Table 1 can be obtained online.

Table 1. Related Documents

Title

Document

Number

Location

Intel® IXDPG425 Gateway Reference Design v2.0

Application Note

313147 Please contact your Intel representative.

Intel

®

IXP4XX Product Line of Network Processors

Specification Update

306428

http://www.intel.com/design/network/

products/npfamily/docs/

ixp4xx.htm#specupdt

Intel

®

IXP42X Product Line of Network Processors

and IXC1100 Control Plane Processor Datasheet

252479

http://www.intel.com/design/network/

datashts/252479.htm

Intel

®

IXP42X Product Line of Network Processors

and IXC1100 Control Plane Processor Developer’s

Manual

252480

http://www.intel.com/design/network/

manuals/252480.htm

Intel

®

IXP400 Software Specification Update 273795

http://www.intel.com/design/network/

products/npfamily/docs/ixp4xx.htm

Intel

®

IXP400 Software Programmer’s Guide 252539

http://www.intel.com/design/network/

products/npfamily/docs/ixp4xx.htm

Page 6

Intel® IXDPG425 Network Gateway Reference Platform v2.0

Intel

®

IXDPG425 Network Gateway Reference Platform v2.0

Quick Start Guide October 2007

6 Document Number: 313148-001US

1.3 Acronyms

1.4 Inspection

Before the contents of the box are unpacked, ensure that all precautions are observed

prior to removing Electrostatic Sensitive Device (ESD) assemblies from their protective

packaging.

Unpack the contents of the box. After all the components are unpacked, verify that all

the items listed in the packing list are present. The packing list is included in the STOP

Readme First document shipped with the kit.

After verifying all items are present:

• Inspect each item for any visible damage.

• Inspect the cable connectors to ensure that none of the pins are bent or damaged.

If any item is damaged or missing, please contact your local Intel representative.

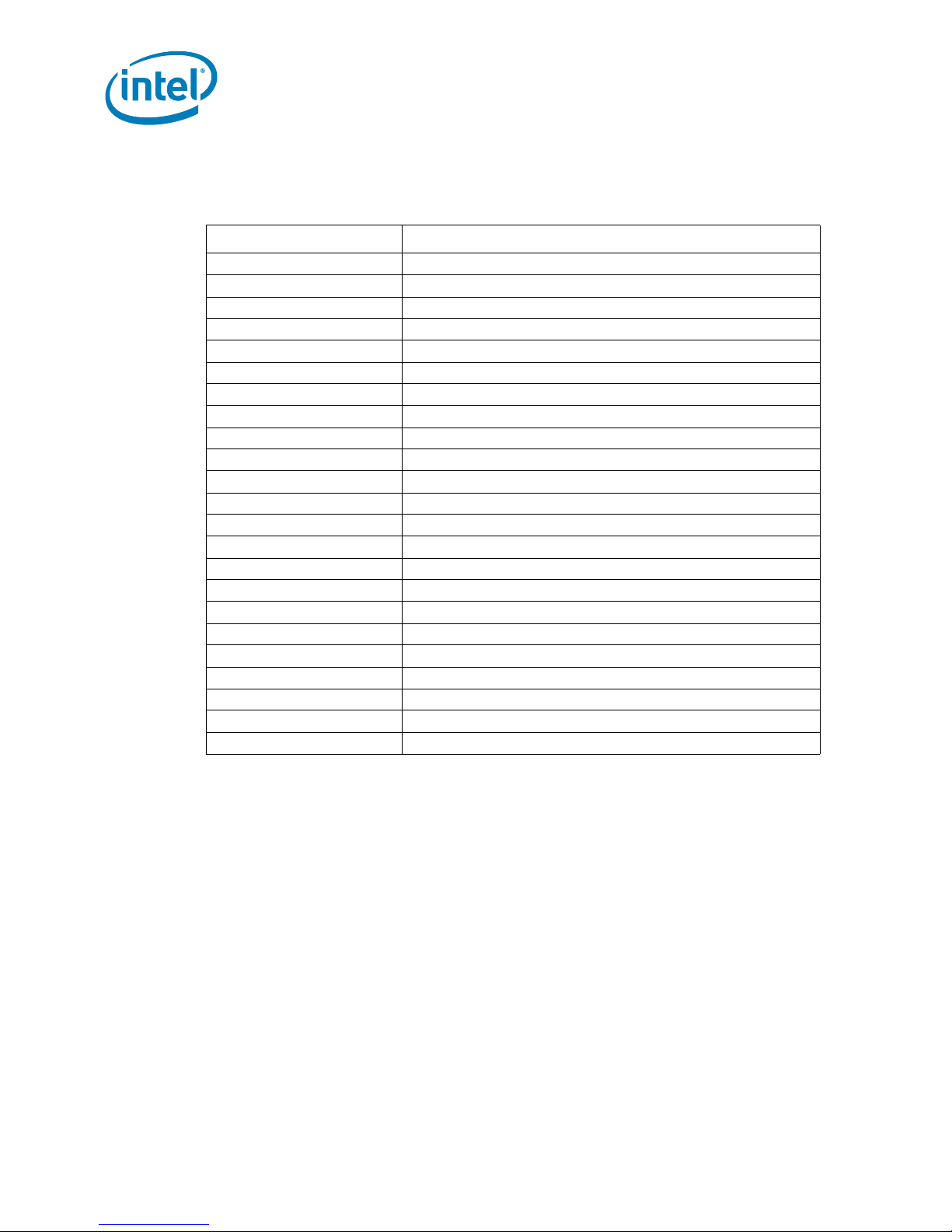

Table 2. Related Acronyms

Acronym/Terminology Description

EEPROM Electronically Erasable Programmable Read Only Memory

EPON Ethernet Passive Optical Network

ESD Electrostatic Discharge

FTTH Fiber To The Home

FTTx Fiber-to-the-x [curb, building, etc.]

FXS Foreign Exchange Station

GPIO General Purpose Input/Output

HSS High Speed Serial

JTAG Joint Test Access Group

LAN Local Area Network

LED Light Emitting Diode

MII Media Independent Interface

NIC Network Interface Card

NPE Network Processor Engine

OLT Optical Line Terminal

ONU Optical Network Unit

PCI Peripheral Component Interconnect

PHY Physical layer

ROM Read Only Memory

SPI Serial Peripheral Interface

UART Universal Asynchronous Receiver-Transmitter

VoIP Voice over Internet Protocol

WAN Wide [or Wireless] Area Network

Page 7

Intel® IXDPG425 Network Gateway Reference Platform v2.0

October 2007 Quick Start Guide

Document Number: 313148-001US 7

Intel® IXDPG425 Network Gateway Reference Platform v2.0

1.5 Known Issues

Silicon and software errata are described in the Intel® IXP4XX Product Line of Network

Processors Specification Update and the Intel

®

IXP400 Software Specification Update.

1.6 Technical Support

If any of the contents are missing or if you have any questions, please contact your

local Intel representative.

§ §

Page 8

Intel® IXDPG425 Network Gateway Reference Platform v2.0

Intel

®

IXDPG425 Network Gateway Reference Platform v2.0

Quick Start Guide October 2007

8 Document Number: 313148-001US

2.0 Intel® IXDPG425 Platform v2.0 Overview

The IXDPG425 platform v2.0 is a multi-service next-generation residential gateway

that consists of the Intel

®

IXP425 Network Processor, Gigabit Switch, and

daughterboards (for example, EPON/GPON ONU, IEEE802.11n and MoCA modules) that

plug into the baseboard.

Caution: All boards are sensitiv e to electrostatic discharge. Handle all static-sensitive boards and

components in a static-safe work area, and observe anti-static precautions at all times.

Page 9

Intel® IXDPG425 Network Gateway Reference Platform v2.0

October 2007 Quick Start Guide

Document Number: 313148-001US 9

Intel® IXDPG425 Network Gateway Reference Platform v2.0

2.1 Intel® IXDPG425 Platform v2.0 Components Placement

Figure 1 shows the main components, jumpers, and connectors of the IXDPG425

platform v2.0.

D

Figure 1. Top View: Intel® IXDPG425 Platform v2.0 Component Placement Diagram

Page 10

Intel® IXDPG425 Network Gateway Reference Platform v2.0

Intel

®

IXDPG425 Network Gateway Reference Platform v2.0

Quick Start Guide October 2007

10 Document Number: 313148-001US

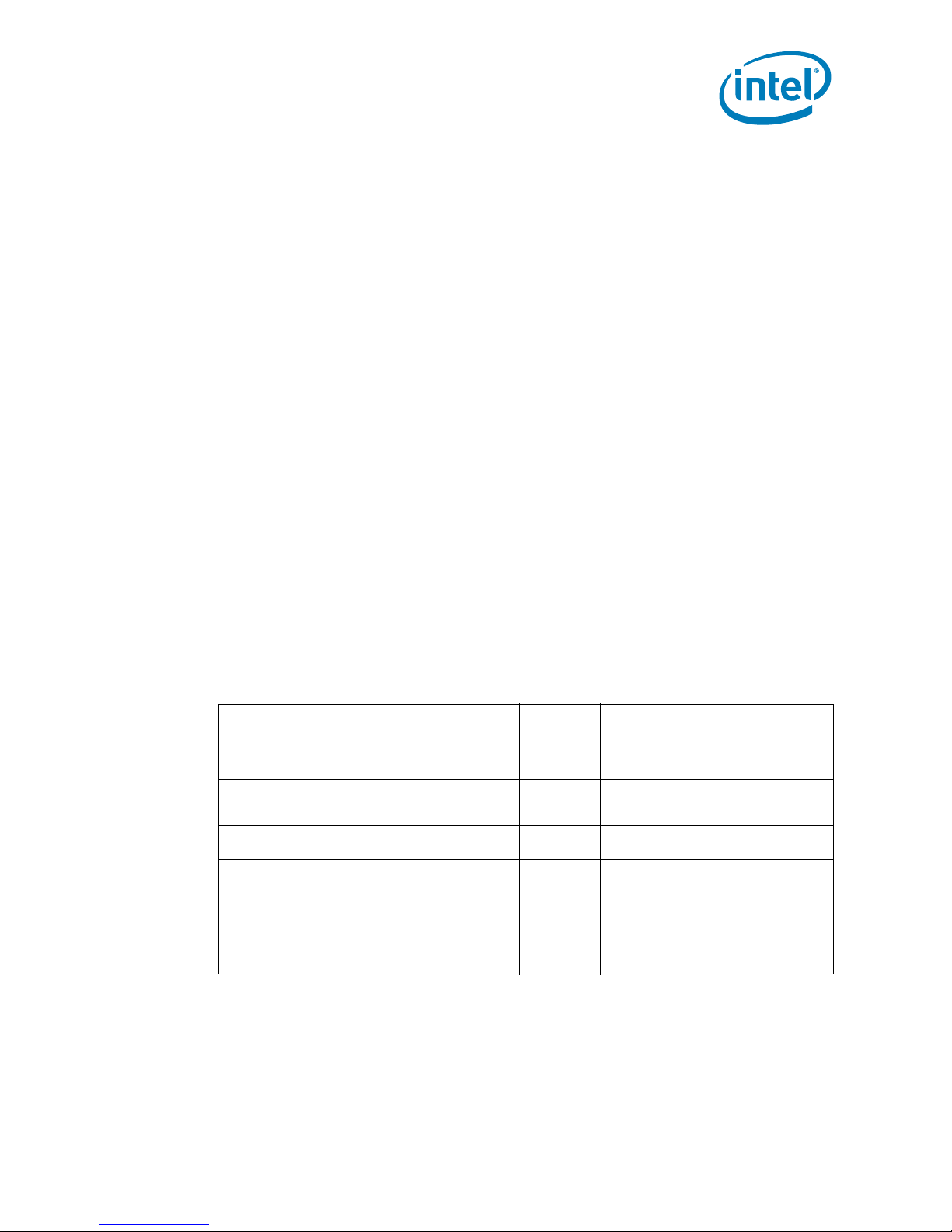

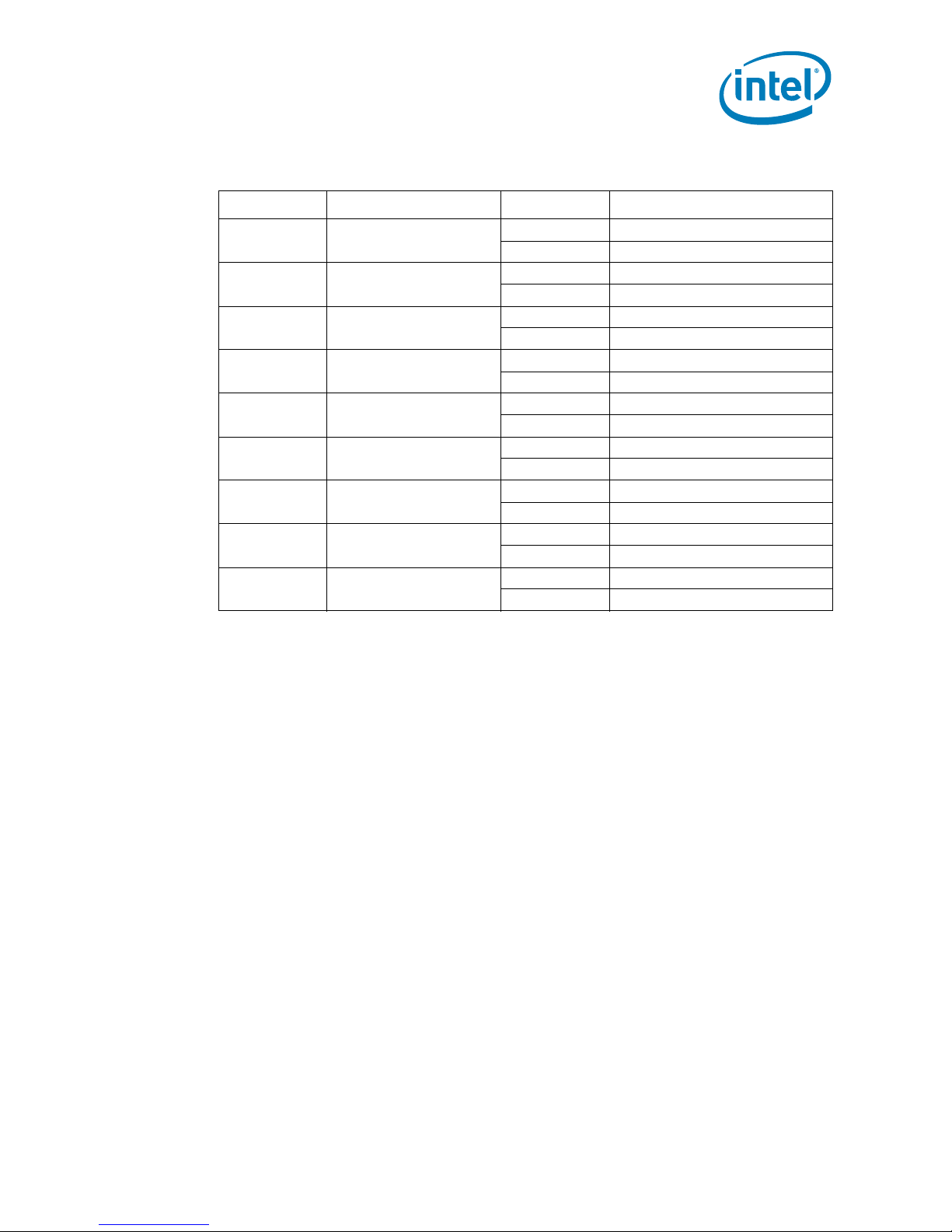

2.2 Intel® IXDPG425 Platform v2.0 Hardware Settings

Table 3 describes the IXDPG425 platform v2.0 jumper settings shown in Figure 1.

Table 4 describes the LEDs shown in Figure 1.

Table 3. Intel

®

IXDPG425 Platform v2.0 Jumper Setting Descriptions

Reference Description Default Setting

J5

Intel

®

IXP425 core speed setting

Set core speed at 533 MHz. (No Shunt)

Set core speed at 400 MHz. (Shunt 1-2, 5-6)

Set core speed at 266 MHz. (Shunt 1-2)

No shunt

J7

Flash memory core Vcc supply

Provide +3.3V

DC

for J3C series. (Shunt 1-2)

Provide +1.85V

DC

for P30 series. (Shunt 2-3)

Shunt 2-3

J13

HSS0 clock setting

Internal clock. (No Shunt)

External clock devices on board. (Shunt 1-2)

No shunt

J15

MII-1 path setting

Interface to on board PHY U20. (No Shunt)

Interface to add-on module J10. (Shunt 1-2)

No shunt

J16

Gigabit Switch configuration path setting

Configuration loaded from external EEPROM. (No Shunt)

Configuration loaded from system SPI Interface. (Shunt 1-2)

No shunt

Table 4. Intel® IXDPG425 Platform v2.0 Baseboard LED Descriptions (Sheet 1 of 2)

Reference Label Status Description

D12 Power

Green +12V

DC

powered up

Light Off +12V

DC

powered down

D13 Reset

Orange System resetting

Light Off System initialization starts

D15 #1 miniPCI status

Green In-Service

Light Off Out-Of-Service

D17 #2 miniPCI status

Green In-Service

Light Off Out-Of-Service

D18 #1 FXS

Green Off-Hook

Green Blinking Receive ringing

Light Off On-hook

D20 #2 FXS

Green Off-Hook

Green Blinking Receive Ringing

Light Off On-hook

D21 MII Module Status

Green Link established

Light Off No Valid Link

Page 11

Intel® IXDPG425 Network Gateway Reference Platform v2.0

October 2007 Quick Start Guide

Document Number: 313148-001US 11

Intel® IXDPG425 Network Gateway Reference Platform v2.0

2.3 PON ONU Daughterboard Modules

The EPON / GPON ONU daughterboard plugs into the J9 connector shown in Figure 1.

2.3.1 EPON ONU Module

Figure 2 shows the main components of the EPON ONU daughterboard. Some of these

components are referred to elsewhere in this document. Please refer to “EPON ONU

Board Jumper Description” on page 17.

D22

D19

D16

D14

D11

LAN port status

Red 1000M link established

Red Blinking 1000M data transferring

Amber 100M link established

Amber Blinking 100M data transferring

Green 10M link established

Green Blinking 10M data transferring

Light Off No valid link

D6 MII-0 <-> LAN

Amber 10/100M link established

Amber Blinking 10/100M data transferring

Green 10M link established

Green Blinking 10M data transferring

Light Off No valid link

D38 MII-1 <-> LAN

Green 10/100M link established

Green Blinking 10/100M data transferring

Light Off No valid link

Table 4. Intel® IXDPG425 Platform v2.0 Baseboard LED Descriptions (Sheet 2 of 2)

Reference Label Status Description

Page 12

Intel® IXDPG425 Network Gateway Reference Platform v2.0

Intel

®

IXDPG425 Network Gateway Reference Platform v2.0

Quick Start Guide October 2007

12 Document Number: 313148-001US

There is no hardware jumper setting required for the EPON ONU board. Please see

“EPON ONU Board Jumper Description” on page 17 for board jumper information.

Table 5 describes the LEDs on the EPON ONU board.

Figure 2. EPON ONU Board Components

Page 13

Intel® IXDPG425 Network Gateway Reference Platform v2.0

October 2007 Quick Start Guide

Document Number: 313148-001US 13

Intel® IXDPG425 Network Gateway Reference Platform v2.0

2.3.2 GPON ONU Module

Figure 3 shows the main components of the GPON ONU daughterboard.

Table 5. EPON ONU Board LED Descriptions

Reference Label Status Description

D2 Power

Green +3.3V

DC

powered up

Light Off +3.3V

DC

powered down

D3 EPON frame reception status

Green Valid frame reception

Light Off No frame reception

D4 EPON link status

Green Link Established

Light Off No Valid Link

D5

EPON frame transmitted

status

Green Frame transmitting to EPON

Light off No frame transmitted

D6

EPON invalid frame reception

status

Green Invalid frame reception

Light Off No invalid frame reception

D7 UNI frame transmitted status

Green Frame transmitting to UNI

Light Off No frame transmitted

D8 UNI link status

Green Link established

Light Off No valid link

D9 EUNI frame reception status

Green Valid frame reception

Light Off No frame reception

D10

UNI invalid frame reception

status

Green Invalid frame reception

Light Off No Invalid frame reception

Page 14

Intel® IXDPG425 Network Gateway Reference Platform v2.0

Intel

®

IXDPG425 Network Gateway Reference Platform v2.0

Quick Start Guide October 2007

14 Document Number: 313148-001US

There is no hardware jumper setting required for the GPON ONU board. Please see

“GPON ONU Board Jumper Description” on page 18 for board jumper information.

Table 6 describes the LEDs on the GPON ONU board.

Figure 3. GPON ONU board components

Page 15

Intel® IXDPG425 Network Gateway Reference Platform v2.0

October 2007 Quick Start Guide

Document Number: 313148-001US 15

Intel® IXDPG425 Network Gateway Reference Platform v2.0

2.4 Preparing the Platform for Use

After unpacking the board and before powering it up, follow the steps below .

2.4.1 Verifying Jumper Settings

To prepare the platform for use, refer to Figure 1 for the location of the jumpers and

verify the settings are set for your operating environment. The label near the jumper

also shows the various options available.

1. Set the IXP425 network processor frequency; 533 MHz is the default setting. If you

would like to set a different frequency, see detail in Table 3.

2. By default, the P30 series flash is mounted on the baseboard, therefore J7 should

always be shunted on pins 2-3.

— J3C series (shunt 1-2)

— P30 series (shunt 2-3)

3. There should (always) no shunt on J13 to set HSS0 internal clock provided by the

platform.

— HSS0-bus internal clock (no shunt).

— HSS0-bus external clock (shunt 1-2).

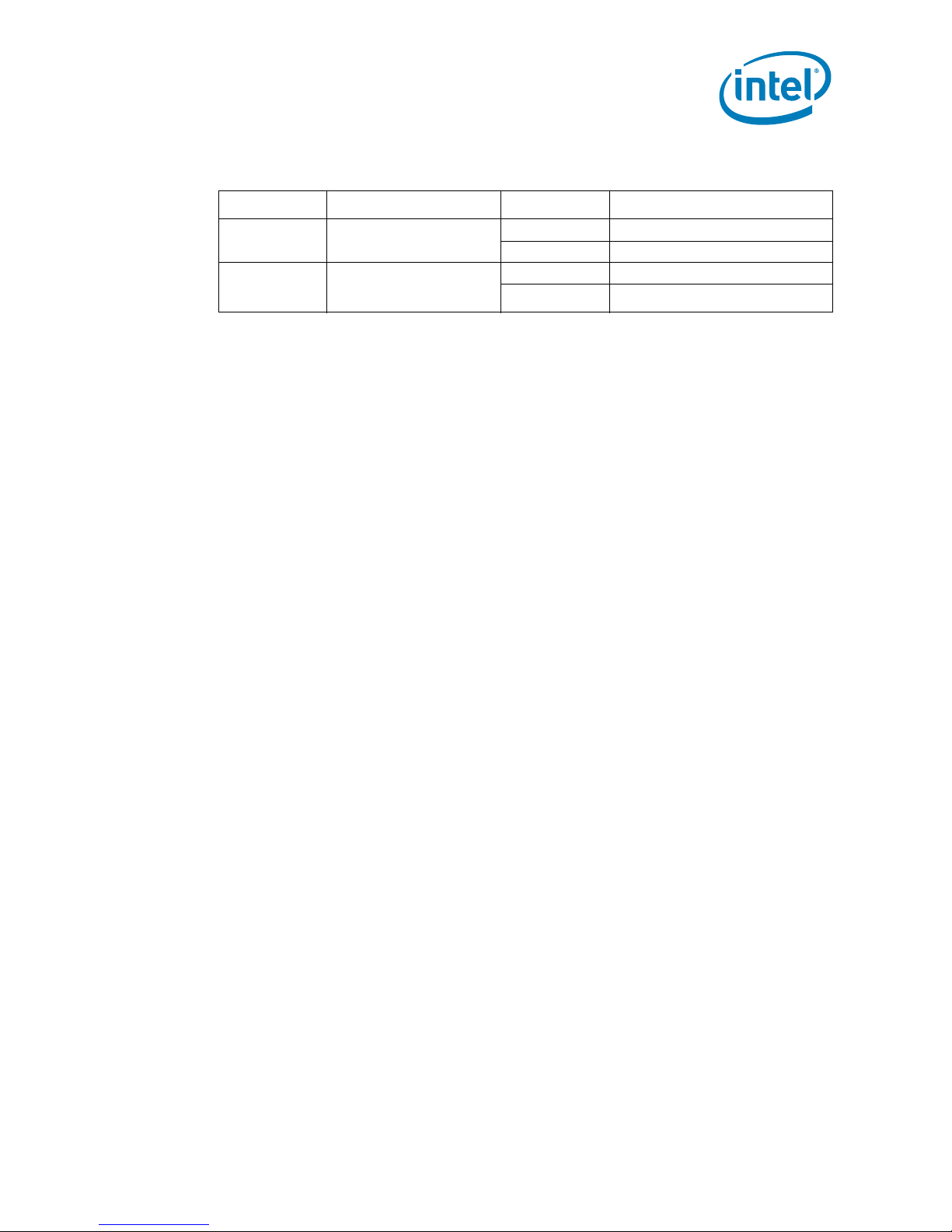

Table 6. GPON ONU Board LED Descriptions

Reference Label Status Description

D3 Power

Green +3.3V

DC

powered up

Light Off +3.3V

DC

powered down

D4

GPON frame receiver signal

status

Green Valid frame reception

Light Off No frame reception

Page 16

Intel® IXDPG425 Network Gateway Reference Platform v2.0

Intel

®

IXDPG425 Network Gateway Reference Platform v2.0

Quick Start Guide October 2007

16 Document Number: 313148-001US

4. There should (always) no shunt on J15 to set MII-1 path routed to PHY on the

board. The auto-detection function had been implemented on current stage.

5. There should (always) no shunt on J16 to set Gigabit Switch configuration loaded

from external EEPROM

— Loading configuration from external EEPROM (no shunt).

— Loading configuration from system SPI interface (shunt 1-2).

2.5 Starting the Platform

The following steps prepare the platform for use:

1. Attach the necessary daughterboard modules (e.g. EPON ONU) to the baseboard

2. Connect the serial cable from COM1 on the host system to UART1. Table 7 lists the

configuration parameters necessary for establishing the console session.

To start the platform, follow these steps:

1. Verify that the power switch is in the OFF position.

2. Connect power supply to the platform power connector J12.

3. Switch the power switch to ON position.

a. Verify the power LED illuminates green on the baseboard.

4. To verify the board is booted properly, observe that the Reset LED turns off,

indicating that the system initialization is in progress.

Table 7. UART Communication Configuration

Parameter Linux* Value

Port UART1

Bits per Second 115,200

Data Bits 8

Parity None

Stop Bit 1

Flow Control None

Page 17

Intel® IXDPG425 Network Gateway Reference Platform v2.0

October 2007 Quick Start Guide

Document Number: 313148-001US 17

Intel® IXDPG425 Network Gateway Reference Platform v2.0

Appendix A EPON ONU Board Jumper Description

The following tables describe the jumper settings of the EPON ONU board.

Table 8. Jumper Descriptions of EPON ONU (Reference U1)

Pin Description Type Remarks

1 PON_TX_DISBABLE Output

Disables optical module indication.

Active-low signal

2 PON_LOSS Output

Indicates LOS of the receive line/path of the

optical interface.

Active-low signal

3RECEIVER_VALID_LINE Output

Indicates valid receive line/path of the optical

interface.

Active-high signal

4 GND Ground

Table 9. Setting of EPON Processor (J3)

Pin Description Type Remarks

1 PAS6201_CRITICAL_EVENT Input

Critical event trigger

Active-high signal

2 +3.3V

DC

Power

3 PAS6201_DYING_GASP Input

DYING GASP trigger

Active-high signal

4 +3.3V

DC

Power

5 PAS6201_GPIO0 Input Reserved

6 GPIO_HI_0 PU Pulled-up

7 PAS6201_GPIO1 Input Reserved

8 GPIO_HI_1 PU Pulled-up

9 PAS6201_JTAG_SELECT Input

JTAG mode select:

• High : ARM debugging (9-10)

• Low: Boundary Scan (No Shunt)

10 +3.3V

DC

Power

Table 10. Jumper Descriptions of EPON ONU Board (J4)

Pin Description Type Remarks

1URT_TXD Output

UART Port for U3 debugging functionality.3 GND Ground

5URT_RXD Input

2URT_TXD Output

UART Port for console functionality.

4 GND Ground

6URT_RXD Input

Page 18

Intel® IXDPG425 Network Gateway Reference Platform v2.0

Intel

®

IXDPG425 Network Gateway Reference Platform v2.0

Quick Start Guide October 2007

18 Document Number: 313148-001US

Appendix B GPON ONU Board Jumper Description

The following tables describe the jumper settings of the GPON ONU board.

Table 11. Jumper Description of GPON ONU Board (J4)

Pin Description Type Remarks

1UART_T1 Output

UART Port for U4’s console & debugging

functionality.

2 GND Ground

3UART_R1 Input

Loading...

Loading...