Intel BX80569Q9550 - Core 2 Quad 2.83 GHz Processor, Itanium 9300 Series, Itanium 9500 Series Datasheet

Page 1

Intel® Itanium® Processor 9300

Series and 9500 Series

Intel® Itanium® Processor Quad-Core 1.86-1.73 GHz with 24 MB L3 Cache 9350

®

Intel

Intel

Intel

Intel

Intel

Intel

Intel

Intel

Datasheet

November 2012

Itanium® Processor Quad-Core 1.73-1.60 GHz with 20 MB L3 Cache 9340

®

Itanium® Processor Quad-Core 1.60-1.46 GHz with 20 MB L3 Cache 9330

®

Itanium® Processor Quad-Core 1.46-1.33 GHz with 16 MB L3 Cache 9320

®

Itanium® Processor Dual-Core 1.60 GHz Fixed Frequency with 10 MB L3 Cache 9310

®

Itanium® Processor Eight-Core 2.53 GHz with 32 MB LLC Cache 9560

®

Itanium® Processor Four-Core 2.40 GHz with 32 MB LLC Cache 9550

®

Itanium® Processor Eight-Core 2.13 GHz with 24 MB LLC Cache 9540

®

Itanium® Processor Four-Core 1.73 GHz with 20 MB LLC Cache 9520

Reference Number: 322821-002

Page 2

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED,

BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS

PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER

AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING T O S ALE AND/OR USE OF INTEL PRODUCT S INCLUDING

LIABILITY OR WARRANTIES RELA TING T O FITNES S FOR A PARTICULAR PURPOSE, MERCHANT ABILITY, OR INFRINGEMENT OF ANY

PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A “Mission Critical Application” is any application in which failure of the Intel Product could result, directly or indirectly, in personal

injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU

SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS,

OFFICERS, AND EMPLOYEES OF EACH, HARM LESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE

AT TORNEY S' FEES ARISING O UT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH

ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS

NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the

absence or characteristics of any features or instructions marked “reserved” or “undefined”. Intel reserves these for future

definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The

information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to

deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained

by calling 1-800-548-4725, or go to: http://www.intel.com/design/literature.htm%20

2

C is a two-wire communication bus /protocol developed by Phillips. SMBus is a subset of the I2C bus/protocol developed by Intel.

I

Implementation of the I

Electronics, N.V. and North American Phillips Corporation.

Intel® Virtualization Technology requires a computer system with an enabled Intel® processor, BIOS, virtual machine monitor

(VMM) and, for some uses, certain computer system software enabled for it. Functionality, performance or other benefits will vary

depending on hardware and software configur ations and may re quire a BIOS update. S oftware applicatio ns may not be compatible

2

C bus/protocol or the SMBus bus/protocol may require licenses from various entities, including Phillips

with all operating systems. Please check with your application vendor.

Intel, Itanium, and the Intel logo are trademarks of Intel Corporation in the U. S. and\or other countries.

*Other names and brands may be claimed as the property of others.

Copyright © 2012, Intel Corporation. All Rights Reserved.

2 Intel® Itanium® Processor 9300 Series and 9500 Series Datasheet

Page 3

Contents

1Introduction..............................................................................................................9

1.1 Overview ...........................................................................................................9

1.2 Architectural Overview.......................................................................................15

1.2.1 Intel® Itanium® Processor 9300 Series Overview .......................................15

1.2.2 Intel® Itanium® Processor 9500 Series Overview .......................................16

1.3 Processor Feature Comparison ............................................................................19

1.4 Processor Abstraction Layer................................................................................20

1.5 Mixing Processors of Different Frequencies and Cache Sizes ....................................20

1.6 Terminology .....................................................................................................20

1.7 State of Data............................................. ............................ ...........................21

1.8 Reference Documents..................... .. .. ...............................................................21

2 Electrical Specifications...........................................................................................23

2.1 Intel

2.2 Signal Groups.......................... ........................... ........................... ...................24

2.3 Reference Clocking Specifications ........................................................................26

2.4 Intel® QuickPath Interconnect and Intel® SMI Signaling Specifications..................... 28

2.5 Processor Absolute Maximum Ratings...................................................................38

2.6 Processor DC Specifications ................................................................................39

2.7 Core and Uncore Voltage Identification.................................................................57

2.8 Cache Voltage Identification (Intel

2.9 RSVD, Unused, and DEBUG Pins..........................................................................63

2.10 Mixing Processors..............................................................................................64

2.11 Supported Power-up Voltage Sequence................................................................64

2.12 Supported Power-down Voltage Sequence ............................................................68

2.13 Timing Relationship Between RESET_N and SKTID.................................................69

®

QuickPath Interconnect and Intel® Scalable Memory Interconnect

Differential Signaling .........................................................................................23

2.4.1 Intel® Itanium® Processor 9300 Series

2.4.2 Intel® Itanium® Processor 9500 Series Requirements for

2.4.3 Intel

2.5.1 Intel

®

Intel

QuickPath Interconnect and

®

SMI Specifications for 4.8 GT/s.......................................................28

Intel

®

QuickPath Interconnect for 4.8 and 6.4 GT/s ....................................32

Intel

®

Itanium® Processor 9500 Series Processor Requirements for

®

Intel

SMI Specifications for 6.4 GT/s.......................................................37

®

Itanium® Processor 9300 Series Absolute Maximum Ratings...............39

2.5.2 Intel® Itanium® Processor 9500 Series Absolute Maximum Ratings...............39

®

2.6.1 Flexible Motherboard Guidelines for the Intel

Processor 9300 Series.............................................................................40

2.6.2 Flexible Motherboard Guidelines for the Intel

Processor 9500 Series.............................................................................43

2.6.3 Intel

®

Itanium® Processor 9300 Series Uncore, Core, and Cache Tolerances.. 44

Itanium®

®

Itanium®

2.6.4 Intel® Itanium® Processor 9500 Series Uncore and Core Tolerances ............. 49

2.6.5 Overshoot and Undershoot Guidelines.......................................................52

2.6.6 Signal DC Specifications............................................. .. .. .. .. .....................53

2.6.7 Motherboard-Socket Specification for VR Sense Point ..................................57

2.7.1 Core and Uncore Voltage Identification for the

Intel® Itanium® Processor 9300 Series....................................................58

2.7.2 Core and Uncore Voltage Identification for the

Intel® Itanium® Processor 9500 Series.....................................................59

®

Itanium® Processor 9300 Series only)...............62

2.11.1 Supported Power-up Voltage Sequence for the

Intel® Itanium® Processor 9300 Series....................................................66

2.11.2 Supported Power-up Voltage Sequence for the

®

Itanium® Processor 9500 Series.....................................................67

Intel

2.11.3 Power-up Voltage Sequence Timing Requirements......................................68

Intel® Itanium® Processor 9300 Series and 9500 Series Datasheet 3

Page 4

2.14 Test Access Port (TAP) Connection..................................... ... .. .............................71

3 Pin Listing................................................................................................................73

3.1 Processor Package Bottom Pin Assignments...........................................................73

3.1.1 Package Bottom Pin Listing by Pin Name....................................................73

3.1.2 Pin Listing by Pin Number........................................................................89

3.2 Processor Package Top Pin Assignments..............................................................105

3.2.1 Top-Side J1 Connector Two-Dimensional Table .........................................105

3.2.2 Top-Side J2 Connector Two-Dimensional Table .........................................108

3.2.3 Top-Side J3 Connector Two-Dimensional Table .........................................111

3.2.4 Top-Side J4 Connector Two-Dimensional Table .........................................114

4 Mechanical Specifications ...................................................................................... 119

4.1 Package Mechanical Drawing.............................................................................120

4.2 Intel® Itanium® Processor 9300 Series...............................................................121

4.3 Processor Component Keepout Zones.................................................................129

4.4 Package Loading Specifications..........................................................................129

4.5 Package Handling Guidelines.............................................................................129

4.6 Processor Mass Specifications............................................................................130

4.7 Processor Materials..........................................................................................130

4.8 Package Markings............................................................................................130

5 Thermal Specifications...........................................................................................133

5.1 Thermal Features..................... ............................ ........................... .................133

5.1.1 Digital Thermometer............................. ........................... .....................134

5.1.2 Thermal Management....................... ............................ .. .. .....................135

5.1.3 Thermal Alert.................................... ... ........................... .....................136

5.1.4 TCONTROL...........................................................................................137

5.1.5 Thermal Warning.......................................... .. .. ............................ .. ......137

5.1.6 Thermal Trip.................................................................................... ....137

5.1.7 PROCHOT............................................................................................138

5.1.8 FORCEPR_N Signal Pin... ... .....................................................................138

5.1.9 Ararat Voltage Regulator Thermal Signals ................................................138

5.2 Package Thermal Specifications and Considerations..............................................139

5.3 Storage Conditions Specifications.......................................................................140

6 System Management Bus Interface........................................................................143

6.1 Introduction....................................................................................................143

6.2 SMBus Memory Component...............................................................................144

6.2.1 Processor Information ROM (PIROM).......................................................144

6.2.2 Scratch EEPROM...................................................................................149

6.2.3 PIROM and Scratch EEPROM Supported SMBus Transactions.......................150

6.3 Memory Component Addressing.........................................................................150

6.4 PIROM Field Definitions.....................................................................................152

6.4.1 General...............................................................................................152

6.4.2 Processor Data.....................................................................................152

6.4.3 Processor Core Data..............................................................................152

6.4.4 Processor Uncore Data ..........................................................................153

6.4.5 Cache Data..........................................................................................154

6.4.6 Package Data.......................................................................................155

6.4.7 Part Number Data.................................................................................155

6.4.8 Thermal Reference Data...................................... .. ... ........................... ..155

6.4.9 Feature Data........................................................................................ 156

6.4.10 Other Data ................................. ..................................................... ....157

6.4.11 Checksums..........................................................................................157

7Signal Definitions...................................................................................................159

4 Intel® Itanium® Processor 9300 Series and 9500 Series Datasheet

Page 5

Figures

1-1 Intel® Itanium® Processor 9300 Series Processor Block Diagram............................. 16

1-2 Intel

1-3 Intel

2-1 Active ODT for a Differential Link Example............................................................23

2-2 Single-ended Maximum and Minimum Levels and Vcross Levels...............................27

2-3 Vcross-delta Definition.......................................................................................27

2-4 Differential Edge Rate Definition..........................................................................28

2-5 VRB and TStable Definitions................................................................................28

2-6 TX Equalization Diagram ............................. ... .. .. .. ..............................................31

2-7 TX Return Loss ............................................................. ............................ ........32

2-8 RX Return Loss ................................................. .. ........................... ...................32

2-9 Processor I

2-10 VCCUNCORE Static and Transient Tolerance for

2-11 VCCCORE Static and Transient Tolerance for

2-12 VCCCACHE Static and Transient Tolerance for

2-13 VCCUNCORE Static and Transient Tolerance for the

2-14 VCCUNCORE Load Line for the Intel

2-15 VCCCORE Load Line for the Intel

2-16 VR Sense Point (Representation).........................................................................57

2-17 Supported Power-up Voltage Sequence Timing Requirements for the

2-18 Supported Power-up Sequence Timing Requirements for

2-19 Supported Power-down Voltage Sequence Timing Requirements.............................. 69

2-20 RESET_N and SKITID Timing for Warm and Cold Resets.........................................70

4-1 Processor Package Assembly Sketch.................................................................. 119

4-2 Intel

4-3 Intel

4-4 Intel

4-5 Intel

4-6 Intel

4-7 Intel

4-8 Intel

4-9 Intel

4-10 Processor Marking Zones.................................................................................. 131

5-1 Intel

5-2 Intel

6-1 Intel® Itanium® Processor 9300 Series and

®

Itanium® Processor 9500 Series Processor Block Diagram............................. 17

®

Itanium® Processor 9500 Series Firmware Diagram......................................18

CC_CORE

®

Intel

Itanium® Processor 9300 Series................................................................45

Load Current versus Time........................................................42

Intel® Itanium® Processor 9300 Series................................................................47

®

Intel

Itanium® Processor 9300 Series................................................................48

®

Intel

Itanium® Processor 9500 Series................................................................50

®

Itanium® Processor 9500 Series .....................50

®

Itanium® Processor 9500 Series ......................... 51

Intel® Itanium® Processor 9300 Series...............................................................66

Intel® Itanium® Processor 9500 Series...............................................................67

®

Itanium® Processor 9300 Series Package Drawing (Sheet 1 of 4)................. 121

®

Itanium® Processor 9300 Series Processor Package Drawing (Sheet 2 of 4)... 122

®

Itanium® Processor 9300 Series Package Drawing (Sheet 3 of 4)................. 123

®

Itanium® Processor 9300 Series Package Drawing (Sheet 4 of 4)................. 124

®

Itanium® Processor 9500 Series Package Drawing (Sheet 1 of 4)................ 125

®

Itanium® Processor 9500 Series Package Drawing (Sheet 2 of 4)................. 126

®

Itanium® Processor 9500 Series Package Drawing (Sheet 3 of 4)................. 127

®

Itanium® Processor 9500 Series Package Drawing (Sheet 4 of 4)................. 128

®

Itanium® Processor 9300 Series and

®

Itanium® Processor 9500 Series’ Thermal States ....................................... 134

Intel

®

Itanium® Processor 9300 Series and

®

Itanium® Processor 9500 Series Package Thermocouple Location................. 140

Intel

Intel® Itanium® Processor 9500 Series Package................................................. 151

Intel® Itanium® Processor 9300 Series and 9500 Series Datasheet 5

Page 6

Tables

1-1 Intel® Itanium® Processor 9300 Series and

Intel® Itanium® Processor 9500 Series Feature Comparison....................................19

2-1 Signals with RTT................................................................................................24

2-2 Signal Groups ...................................................................................................24

2-3 Intel

2-4 Intel® Itanium® Processor 9300 Series Clock Frequency Table.................................29

2-5 Intel

2-6 Intel

2-7 Intel

2-8 Intel

2-9 Intel

2-10 Intel

2-11 Intel

2-12 PLL Specification for TX and RX ...........................................................................38

2-13 Intel

2-14 Intel

2-15 FMB Voltage Specifications for the Intel

2-16 FMB 130W Current Specifications for the Intel

2-17 FMB 155W/185W Current Specifications for the

2-18 FMB Voltage Specifications for the Intel

2-19 FMB 170W and 130W Current Specifications for the

2-20 VCCUNCORE Static and Transient Tolerance for

2-21 VCCCORE Static and Transient Tolerance for

2-22 VCCCACHE Static and Transient Tolerance for

2-23 VCCUNCORE Static and Transient Tolerance for the

2-24 VCCCORE Static and Transient Tolerance for the

2-25 Overshoot and Undershoot Specifications For Differential

2-26 Overshoot and Undershoot Specifications For Differential

2-27 Voltage Regulator Signal Group DC Specifications ..................................................53

2-28 Voltage Regulator Control Group DC Specification ..................................................54

2-29 TAP and System Management Group DC Specifications...........................................54

2-30 Error, FLASHROM, Power-Up, Setup, and Thermal Group DC Specifications................54

2-31 VID_VCCCORE[6:0], VID_VCCUNCORE[6:0] and VID_VCCCACHE[5:0] DC

2-32 SVID Group DC Specifications for the Intel

®

QuickPath Interconnect/Intel® Scalable Memory

‘Interconnect Reference Clock Specifications26

®

Itanium® Processor 9300 Series Transmitter Parameter Values for Intel®

QuickPath Interconnect and Intel SMI Channels @ 4.8 GT/s ....................................29

®

Itanium® Processor 9300 Series Receiver Parameter

Values for Intel® QuickPath Interconnect and Intel® SMI Channels @ 4.8 GT.. ........... 30

®

Itanium® Processor 9500 Series Clock Frequency Table.................................33

®

Itanium® Processor 9500 Series Link Speed Independent Specifications ..........33

®

Itanium® Processor 9500 Series Transmitter and

Receiver Parameter Values for Intel

®

Itanium® Processor 9500 Series Transmitter and

®

QPI Channel at 4.8 GT/s.................................34

Receiver Parameter Values for Intel® QPI at 6.4 GT/s.............................................35

®

Itanium® Processor 9500 Series Transmitter and

Receiver Parameter Values for Intel® SMI at 6.4 GT/s and lower..............................37

®

Itanium® Processor 9300 Series Absolute Maximum Ratings..........................39

®

Itanium® Processor 9500 Series Processor Absolute Maximum Ratings............39

®

Itanium® Processor 9300 Series ................40

®

Itanium® Processor 9300 Series ...... .41

Intel® Itanium® Processor 9300 Series.................................................................42

®

Itanium® Processor 9500 Series ................43

®

Intel

Itanium® Processor 9500 Series.................................................................44

®

Intel

Itanium® Processor 9300 Series.................................................................45

Intel® Itanium® Processor 9300 Series.................................................................46

®

Intel

Itanium® Processor 9300 Series.................................................................48

®

Intel

Itanium® Processor 9500 Series.................................................................49

Intel® Itanium® Processor 9500 Series.................................................................51

®

Intel

QuickPath Interconnect and Intel® SMI and Single-Ended Signals

®

for the Intel

Intel® QuickPath Interconnect and Intel® SMI and Single-Ended

Signals for the Intel

Specifications for the Intel

Itanium® Processor 9300 Series ......................................................52

®

Itanium® Processor 9500 Series ...........................................53

®

Itanium® Processor 9300 Series...................................55

®

Itanium® Processor 9500 Series............55

6 Intel® Itanium® Processor 9300 Series and 9500 Series Datasheet

Page 7

2-33 SMBus and Serial Presence Detect (SPD) Bus Signal Group DC Specifications............ 55

2-34 Debug Signal Group DC Specifications..................................................................56

2-35 PIROM Signal Group DC Specifications .................................................................56

2-36 Intel® Itanium® Processor 9300 Series VCCCORE (VID_VCCCORE) and

VCCUNCORE and (VID_VCCUNCORE) Voltage Identification Definition for Ararat........58

2-37 Intel® Itanium® Processor 9500 Series VCCCORE (VID_VCCCORE)

and VCCUNCORE and (VID_VCCUNCORE) Voltage Identification

Definition for Ararat II .......................................................................................59

2-38 Cache (VID_VCCCACHE) Voltage Identification Definition for Ararat .........................63

2-39 Power-up Voltage Sequence Timing Requirements .................................................68

2-40 RESET_N and SKTID Timing ...............................................................................70

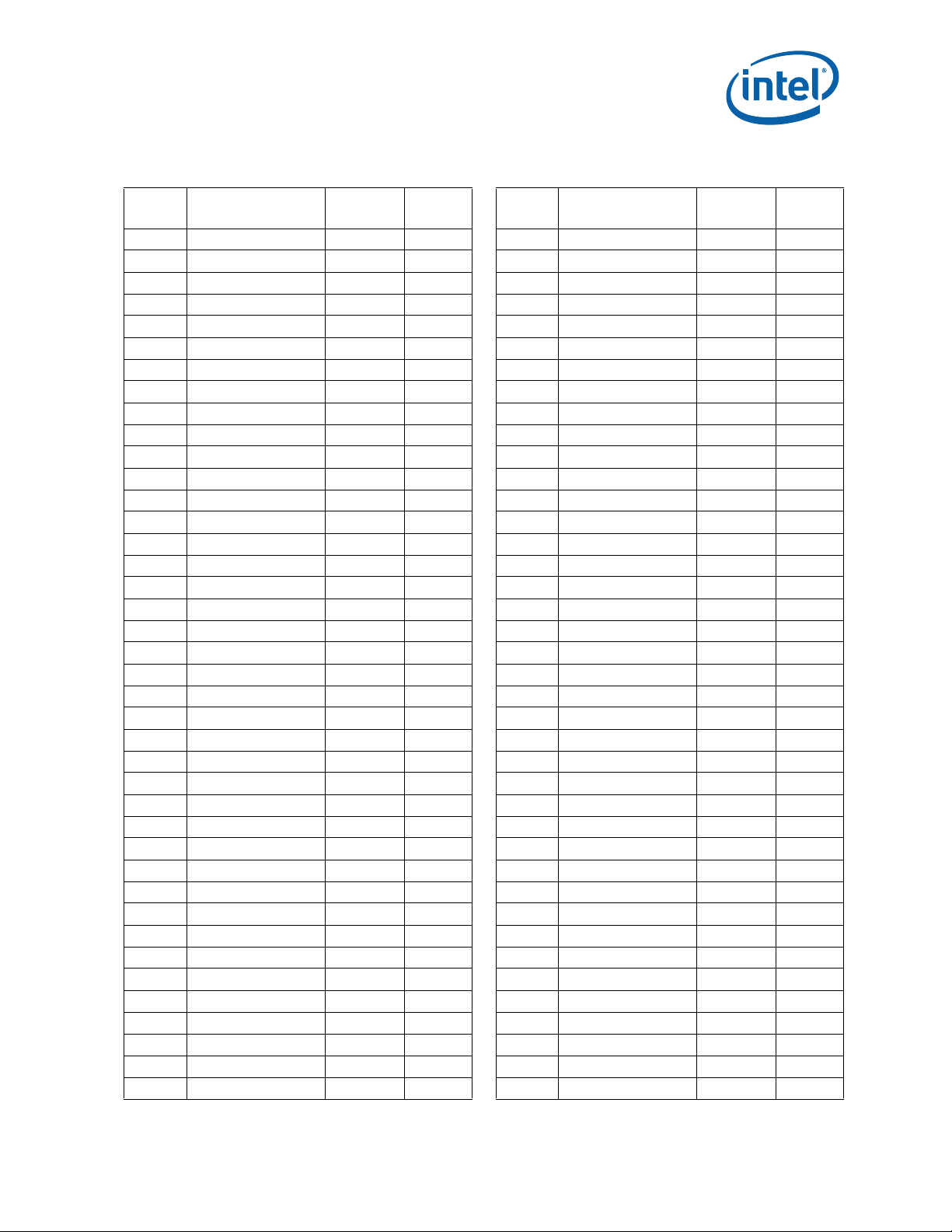

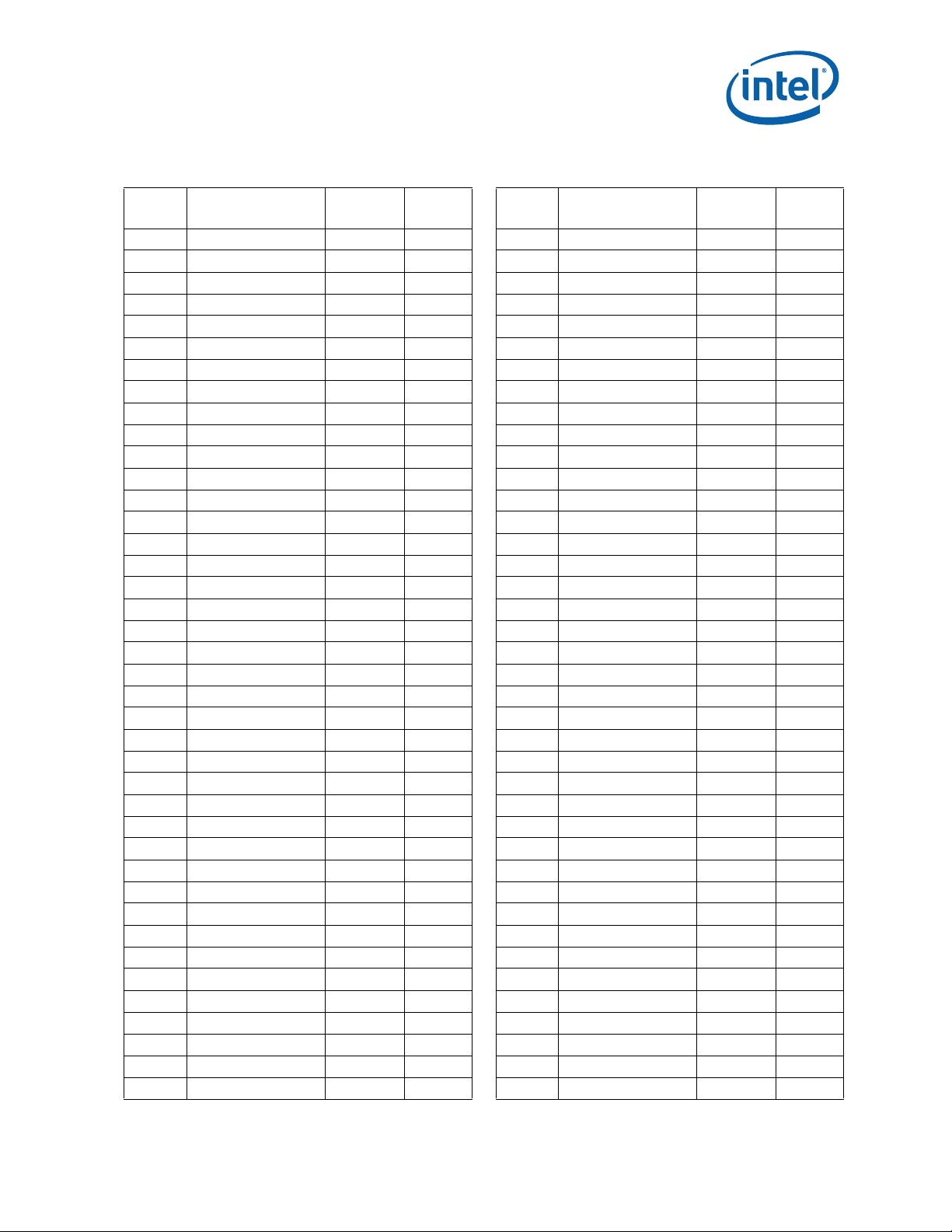

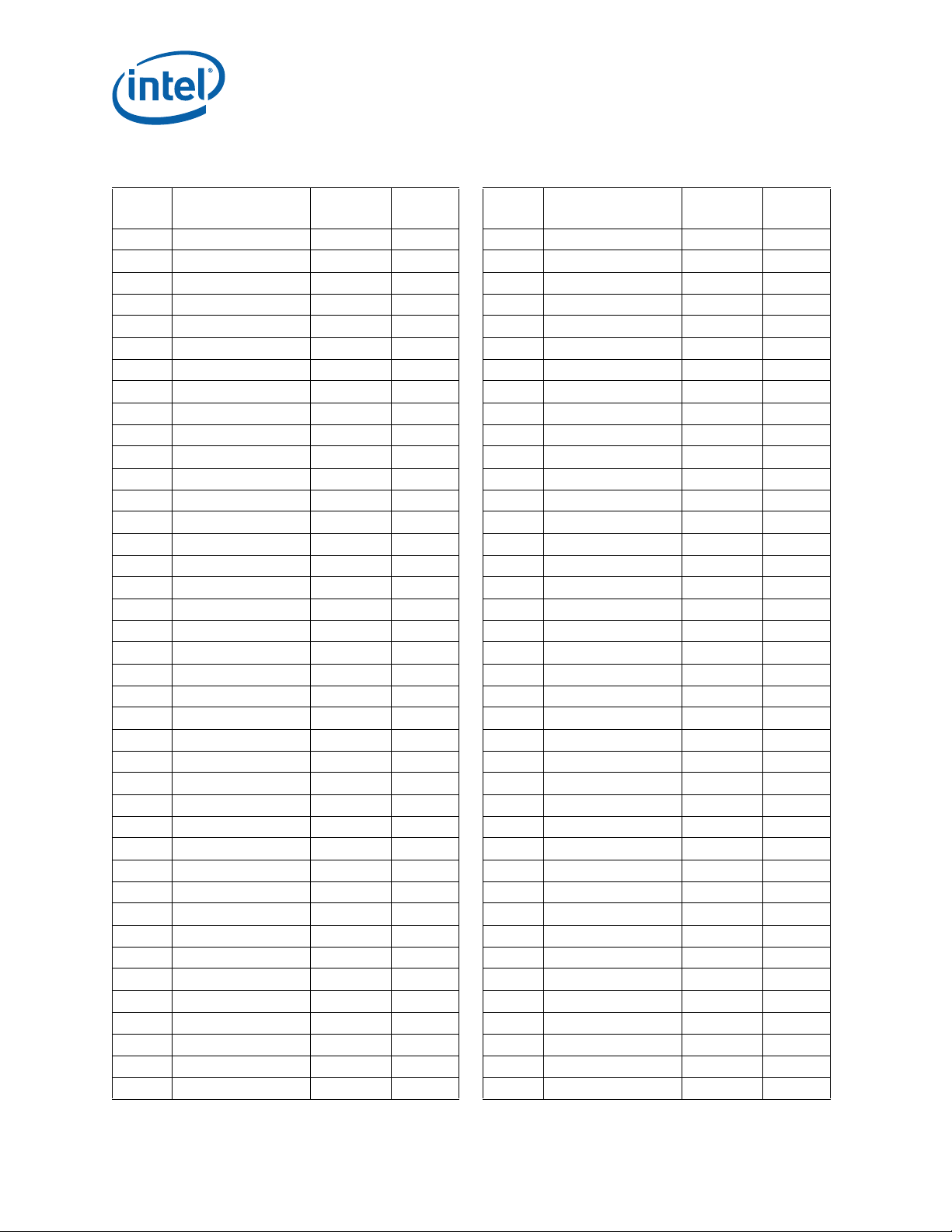

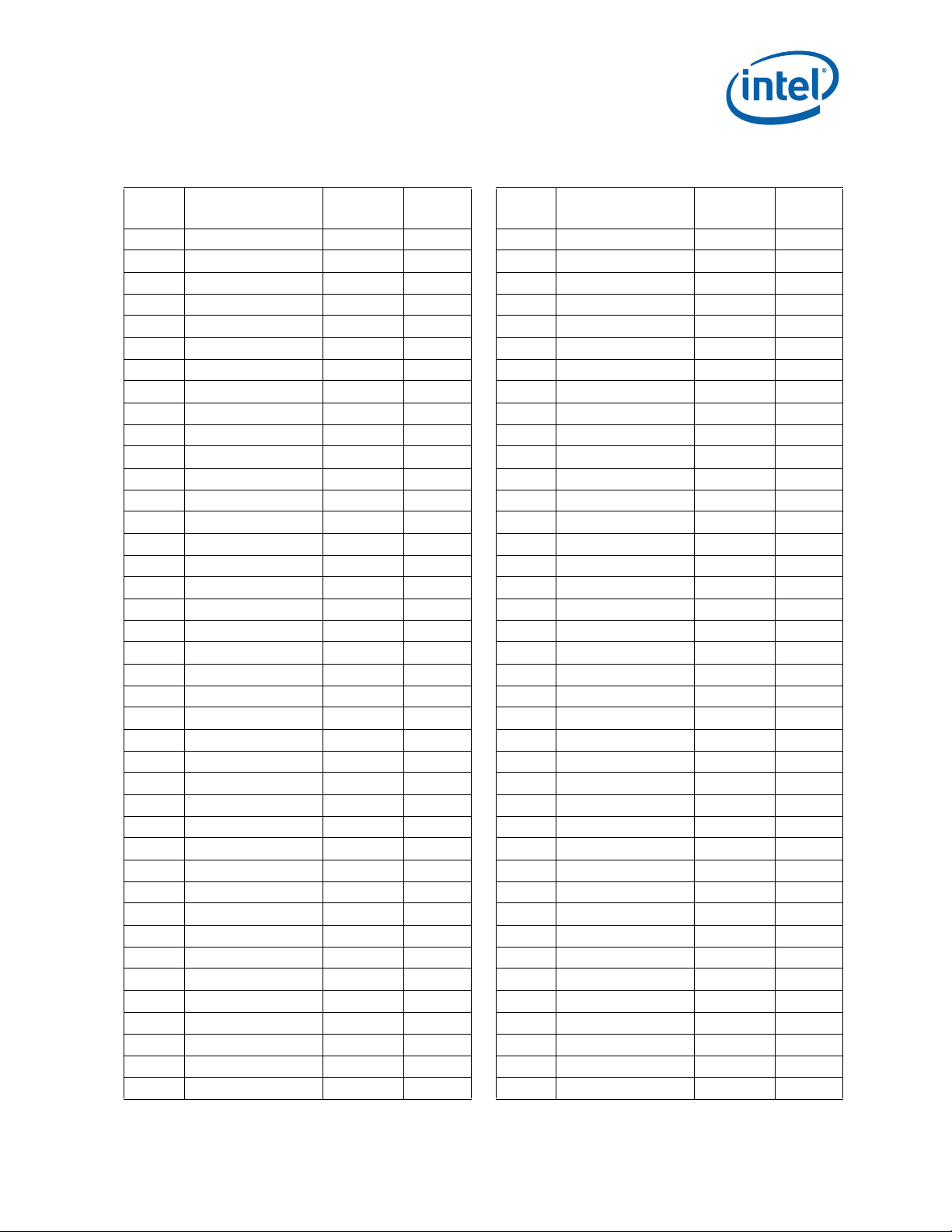

3-1 Pin List by Pin Name..........................................................................................73

3-2 Pin List by Pin Number.......................................................................................89

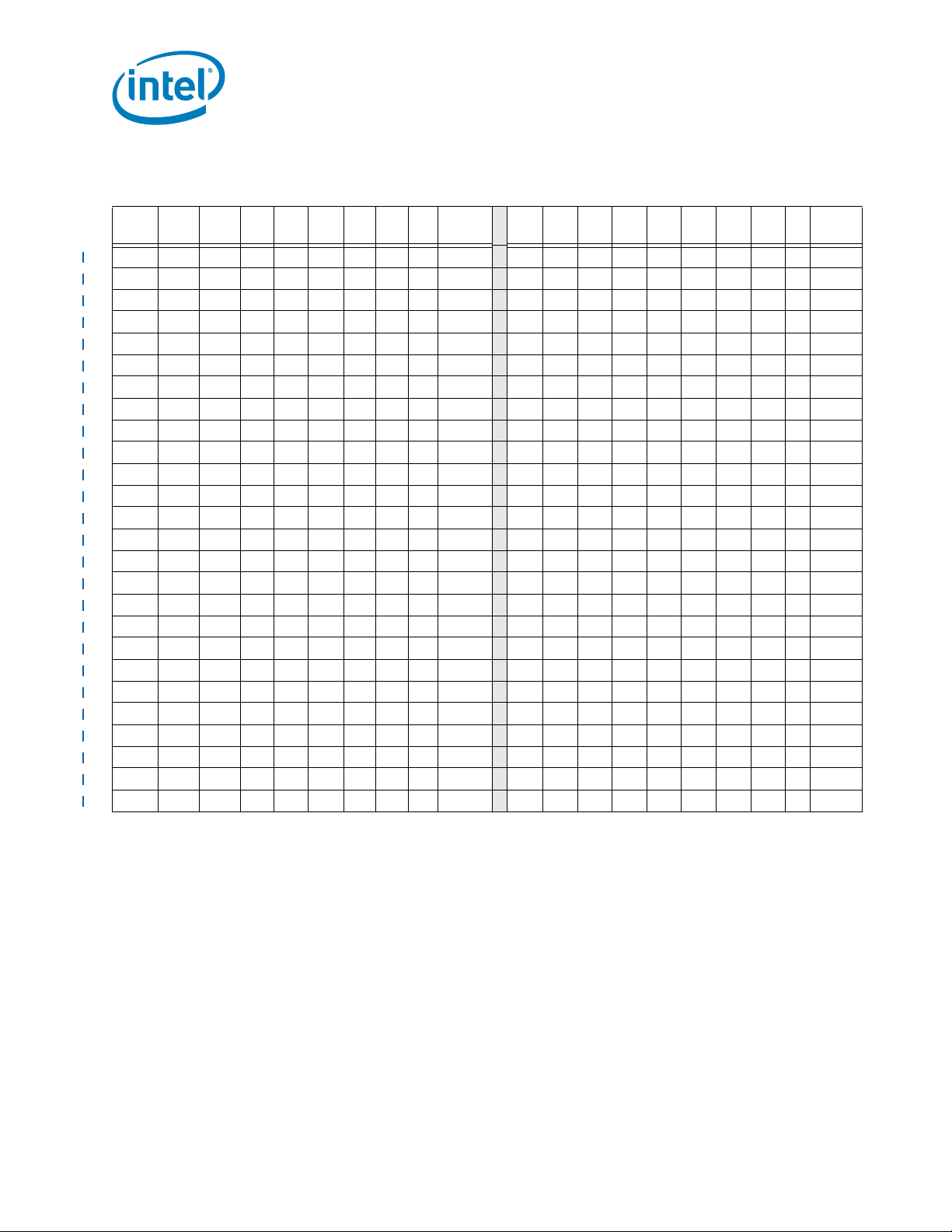

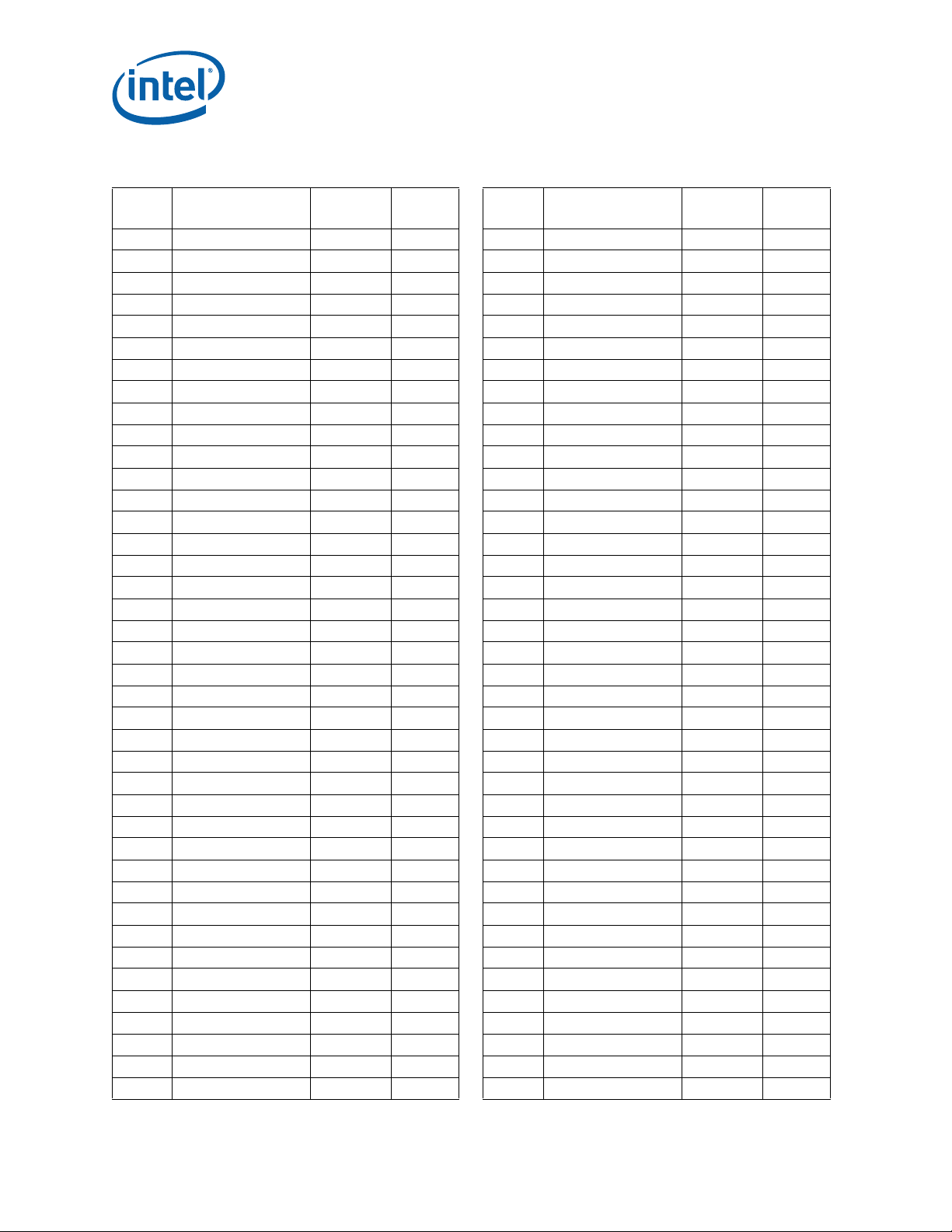

3-3 Top-Side J1 Connector Two-Dimensional Table

3-4 Top-Side J1 Connector Two-Dimensional Table

3-5 Top-Side J2 Connector Two-Dimensional Table

(Intel

(Intel

(Intel

®

Itanium® Processor 9300 Series)............................................................ 105

®

Itanium® Processor 9500 Series)............................................................ 106

®

Itanium® Processor 9300 Series)............................................................ 108

3-6 Top-Side J2 Connector Two-Dimensional Table

(Intel® Itanium® Processor 9500 Series)............................................................ 110

3-7 Top-Side J3 Connector Two-Dimensional Table

3-8 Top-Side J3 Connector Two-Dimensional Table

(Intel

(Intel

®

Itanium® Processor 9300 Series)............................................................ 111

®

Itanium® Processor 9500 Series)............................................................ 113

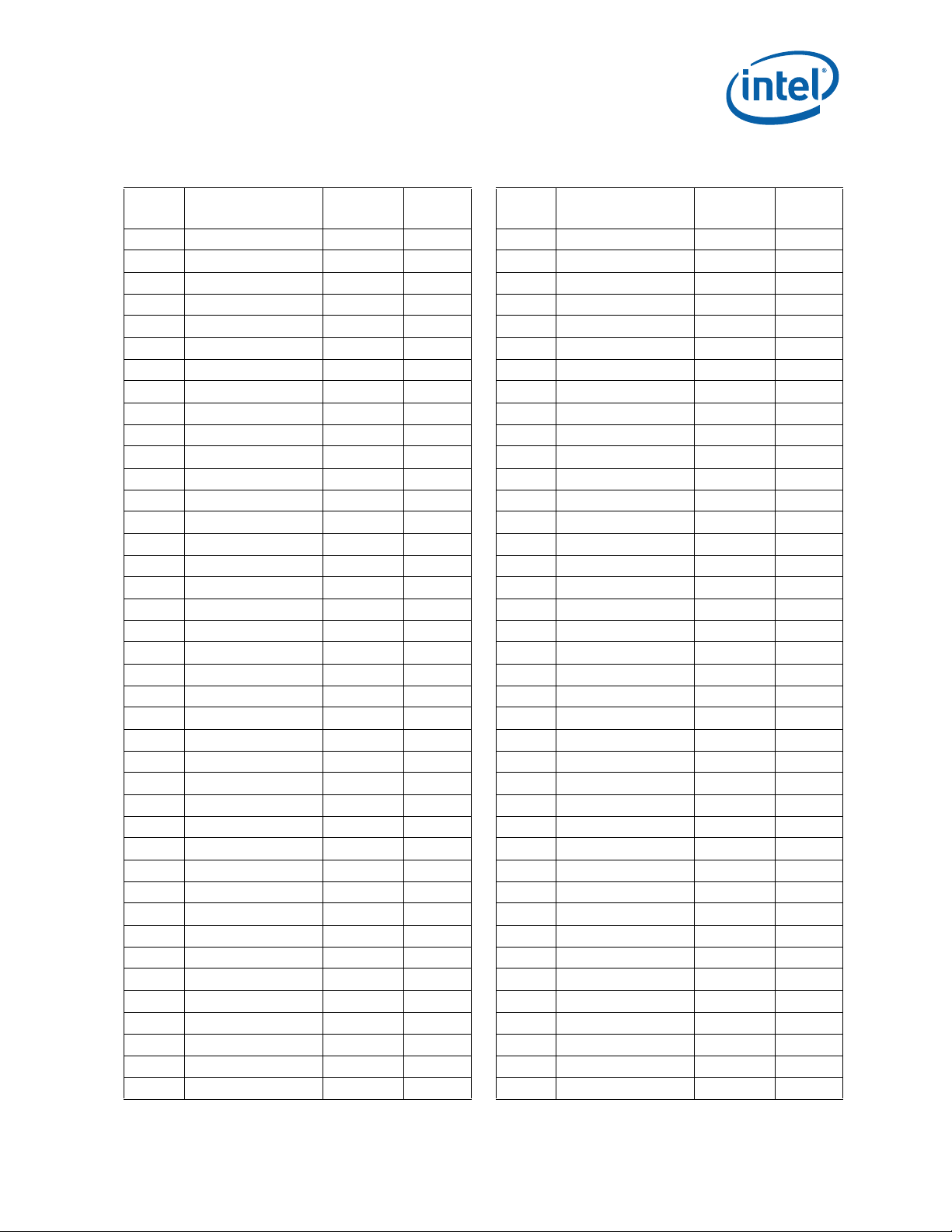

3-9 Top-Side J4 Connector Two-Dimensional Table

(Intel® Itanium® Processor 9300 Series)............................................................ 114

3-10 Top-Side J4 Connector Two-Dimensional Table

(Intel

®

Itanium® Processor 9500 Series)............................................................ 116

4-1 Processor Loading Specifications ....................................................................... 129

4-2 Package Handling Guidelines........................ ... ........................... .. .. ................... 129

4-3 Processor Package Insertion Specification........................................................... 130

4-4 Package Materials..................... .. .. ........................... .. ............................ .. .. ...... 130

4-5 1248 FCLGA Package Marking Zones.................................................................. 130

5-1 Thermal Sensor Accuracy Distribution for the

®

Intel

Itanium® Processor 9300 Series.............................................................. 134

5-2 Thermal Sensor Accuracy Distribution for the

Intel® Itanium® Processor 9500 Series............................................................. 135

5-3 Thermal Specification for the Intel

5-4 Thermal Specification for the Intel

®

Itanium® Processor 9300 Series ..................... 139

®

Itanium® Processor 9500 Series Processor ....... 139

5-5 Storage Condition Ratings ................................................................................ 141

6-1 Processor Information ROM Data....................................................................... 144

6-2 Read Byte SMBus Packet.................................................................................. 150

6-3 Write Byte SMBus Packet ................................................................................. 150

6-4 Offset 78h/79h Definitions............................................ ............................ .. ...... 156

6-5 128 Byte PIROM Checksum Values ..................................................... ............... 157

7-1 Signal Definitions for the Intel

Series and Intel

®

Itanium® 9500 Series............................................................. 159

®

Itanium® Processor 9300

Intel® Itanium® Processor 9300 Series and 9500 Series Datasheet 7

Page 8

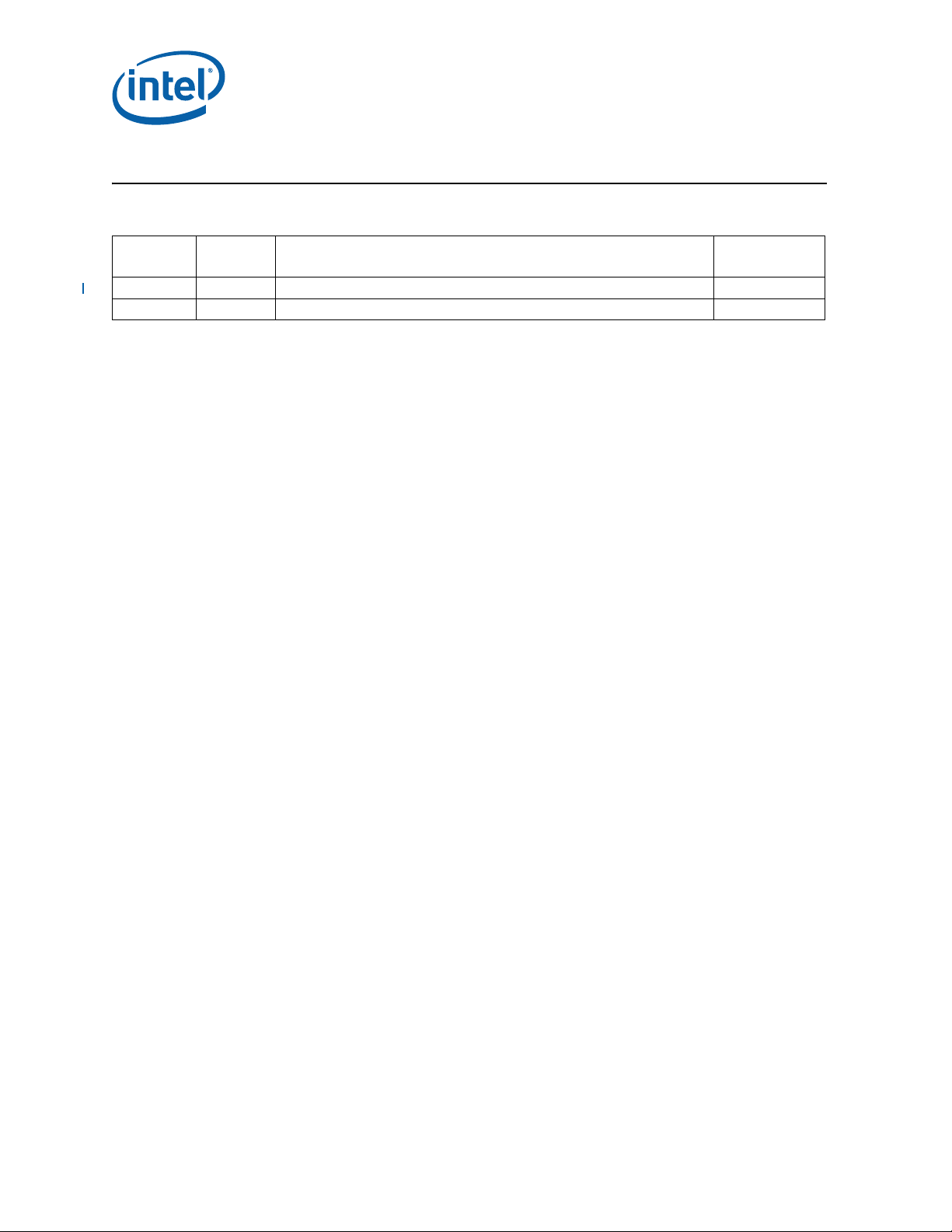

Revision History

Document

Number

322821 -002 • Initial release of the 9300/9500 document. November 2012

322821 -001 • Initial release of the document. February 2010

Revision

Number

Description Date

§

8 Intel® Itanium® Processor 9300 Series and 9500 Series Datasheet

Page 9

Introduction

1 Introduction

1.1 Overview

The Intel® Itanium® Processor 9300 Series and Intel® Itanium® Processor 9500 Series

employ Explicitly Parallel Instruction Computing (EPIC) design concepts for a tighter

coupling between hardware and software. In this design style, the interface between

hardware and software is designed to enable the software to exploit all available

compile-time information, and efficiently deliver this information to the hardware. It

addresses several fundamental performance bottlenecks in modern computers, such as

memory latency, memory address disambiguation, and control flow dependencies. The

EPIC constructs provide powerful architectural semantics, and enable the software to

make global optimizations across a large scheduling scope, thereby exposing available

Instruction Level Parallelism (ILP) to the hardware. The hardware takes advantage of

this enhanced ILP, and provides abundant execution resources. Additionally, it focuses

on dynamic run-time optimizations to enable the compiled code schedule to flow at

high throughput. This strategy increases the synergy between hardware and software,

and leads to greater overall performance.

®

The Intel

system interface, with its 4 full width and 2 half width Intel® QuickPath Interconnects,

enables each processor to directly connect to other system components, thus can be

used as an effective building block for very large systems. The balanced core and

memory subsystem provide high performance for a wide range of applications ranging

from commercial workloads to high performance technical computing.

The Intel

are pin compatible and support a range of computing needs and configurations from a

2-way to large SMP servers (although OEM field upgrade methodologies vary). This

document provides the electrical, mechanical and thermal specifications that must be

met when using the Intel

Processor 9500 Series in your systems.

Itanium® Processor 9300 Series and Intel® Itanium® Processor 9500 Series

®

Itanium® Processor 9300 Series and Intel® Itanium® Processor 9500 Series

®

Itanium® Processor 9300 Series and Intel® Itanium®

Intel® Itanium® Processor 9300 Series and 9500 Series Datasheet 9

Page 10

Introduction

10 Intel

®

Itanium® Processor 9300 Series and 9500 Series Datasheet

Page 11

Introduction

Intel® Itanium® Processor 9300 SeriesIntel® Itanium® Processor 9300 Series

Intel® Itanium® Processor Quad-Core 1.86-1.73 GHz with 24 MB L3 Cache 9350

®

Intel

Intel

Intel

Intel

Itanium® Processor Quad-Core 1.73-1.60 GHz with 20 MB L3 Cache 9340

®

Itanium® Processor Quad-Core 1.60-1.46 GHz with 20 MB L3 Cache 9330

®

Itanium® Processor Quad-Core 1.46-1.33 GHz with 16 MB L3 Cache 9320

®

Itanium® Processor Dual-Core 1.60 GHz Fixed Frequency with 10 MB L3 Cache 9310

Product Features

Quad Core

— Four complete 64-bit processing cores on one

processor.

— Includes Dynamic Domain Partitioning.

Advanced EPIC (Explicitly Parallel Instruction

Computing) Architecture for current and future

requirements of high-end enterprise and technical

workloads.

— Provide a variety of advanced implementations of

parallelism, predication, and speculation,

resulting in superior Instruction-Level Parallelism

(ILP).

®

Intel

Hyper-Threading Technology

— Two times the number of OS threads per core.

Wide, parallel hardware based on Intel

®

Itanium®

architecture for high performance:

— Integrated on-die L3 cache of up to 24 MB; cache

hints for L1, L2, and L3 caches for reduced

memory latency.

— 128 general and 128 floating-point registers

supporting register rotation.

— Register stack engine for effective management

of processor resources.

— Support for predication and speculation.

Extensive RAS features for business-critical

applications, for example:

— Machine check architecture with extensive ECC

and parity protection.

— On-chip thermal management.

— Built-in processor information ROM (PIROM).

— Built-in programmable EEPROM.

—Hot-Plug Socket

— Hot-add and hot removal.

— Double Device Data Correction (DDDC) for x4

DRAMs, plus correction of a single bit error.

— Single Device Data Correction (SDDC) for x8

DRAMs, plus correction of a single bit error.

®

—Intel

—Intel

— Intel QuickPath Interconnect (Intel

— DIMM Sparing, Memory Scrubbing, Memory

QuickPath Interconnect Dynamic Link

Width Reduction.

®

QuickPath Interconnect Clock Fail-Safe

Feature.

Add and Removal.

Mirroring, and Memory Migration.

®

QPI) Hot-

— Architected firmware stack, including PAL and

SAL support.

— Directory-based and source-based coherency

protocol.

— Intel QPI poisoning, viral containment and

cleanup.

On-die Memory Controller

— Each memory controller supports two Intel

Scalable Memory Interconnects.

— Support for one Scalable Memory Buffer per Intel

Scalable Memory Interconnect; four Scalable

®

Memory Buffers per processor.

— High memory bandwidth, thus improved

performance.

— 4.8 GT/s for the Intel

Buffer.

Intel

®

Virtualization T echnology for virtualization for

®

7500 Scalable Memory

data-intensive applications.

— Reduce virtualization complexity.

— Improve virtualization performance.

— Increase operating system compatibility.

Intel

®

Cache Safe Technology ensures mainframecaliber availability.

— Minimize L3 cache errors.

— Disable cache entries that have become hard

errors.

— Improve availability.

High bandwidth Intel

multiprocessor scalability:

®

QuickPath Interconnect for

— 4 full and 2 half width Intel QPI Links

— 4.8GT/s transfer rate.

— Systems are easily scaled without sacrificing

performance.

Features to support flexible platform environments:

— IA-32 Execution Layer supports IA-32 application

binaries.

— Bi-endian support.

— Processor abstraction layer eliminates processor

dependencies.

Intel® Itanium® Processor 9300 Series and 9500 Series Datasheet 11

Page 12

Introduction

The Intel® Itanium® Processor 9300 Series delivers new levels of flexibility, reliability,

performance, and cost-effective scalability for your most data-intensive business and

technical applications. It provides 24 megabytes L3 cache accessed at core speed,

Hyper-Threading Technology for increased performance, Intel

Technology for improved virtualization, Intel

®

Cache Safe Technology for increased

®

Virtualization

availability.

®

The Intel

Itanium® Processor 9300 Series consists of up to 4 core processors and a

system interface unit. Each processor core provides a 6-wide, 8-stage deep execution

pipeline. The resources consist of six integer units, six multimedia units, two load and

two store units, three branch units and two floating-point units each capable of

extended, double and single precision arithmetic. The hardware employs dynamic

prefetch, branch prediction, a register scoreboard, and non-blocking caches to optimize

for compile-time non-determinism. Each core provides duplication of all architectural

state to support hardware multithreading, thus enabling greater throughput. Three

levels of on-die cache minimize overall memory latency. It interfaces with the Ararat

“1” Voltage Regulator Module, which used exclusively with the Intel

®

Itanium®

Processor 9300 Series.

12 Intel

®

Itanium® Processor 9300 Series and 9500 Series Datasheet

Page 13

Introduction

Intel® Itanium® Processor 9500 Series

Intel® Itanium® Processor Eight-Core 2.53 GHz with 32 MB LLC Cache 9560

®

Intel

Intel

Itanium® Processor Four-Core 2.40 GHz with 32 MB LLC Cache 9550

®

Itanium® Processor Eight-Core 2.13 GHz with 24 MB LLC Cache 9540

Intel® Itanium® Processor Four-Core 1.73 GHz with 20 MB LLC Cache 9520

Product Features

Eight Core

— Eight complete 64-bit processing cores on one

processor, with two threads per core.

— Each core provides in-order issue and execution

of up to twelve instructions per cycle.

— Includes dynamic domain partitioning and static

hard partitioning.

Advanced EPIC (Explicitly Parallel Instruction

Computing) Architecture for current and future

requirements of high-end enterprise and technical

workloads.

— Provide a variety of advanced implementations of

parallelism, predication, and speculation,

resulting in superior Instruction-Level Parallelism

(ILP).

®

Intel

Wide, parallel hardware based on Intel

Hyper-Threading Technology

— Dual Domain Multithreading with independent

front end and back end thread domains providing

hardware support for 2 threads per core.

— Support for Intel

Instructions.

architecture for high performance:

— Integrated on-die LLC cache of up to 32MB;

cache hints for FLC, MLC, and LLC caches for

®

Itanium® Processor New-

®

Itanium®

reduced memory latency.

— 160 general and 128 floating-point registers

supporting register rotation.

— Register stack engine for effective management

of processor resources.

— Support for predication and speculation.

Extensive RAS features for business-critical

applications, for example:

— Machine check architecture with extensive ECC

and parity protection with firmware first error

handling.

— End-to-end error detection.

— On-chip thermal management and power

management.

— Built-in processor information ROM (PIROM).

— Built-in programmable EEPROM.

—Hot Plug Socket.

— Hot-add and hot removal support.

— Double Device Data Correction (DDDC) for x4

DRAMs, plus correction support of a single bit

error.

— Single Device Data Correction (SDDC) for x8 and

x4 DRAMs, plus correction of a single bit error.

—Intel

—Intel

—Intel

®

QuickPath Interconnect Dynamic Link

Width Reduction.

®

QuickPath Interconnect Clock Fail-Safe

Feature.

®

QuickPath Interconnect Hot-Add and

Removal.

— Memory DIMM and Rank Sparing, Memory

Scrubbing, Memory Mirroring, and Memory

Migration.

—Intel

®

Turbo Boost Technology, featuring

sustained boost.

— Architected firmware stack, including PAL and

SAL support.

— Directory-based and source-based coherency

protocol.

— Intel QPI poisoning, viral containment and

cleanup.

Two On-die Memory Controllers

— Each memory controller supports two Intel

Scalable Memory Interconnects that operate in

lockstep.

®

— Support for one Scalable Memory Buffer per Intel

Scalable Memory Interconnect; four Scalable

Memory Buffers per processor.

— High memory bandwidth, thus improved

performance.

— 4.8 GT/s for the Intel

Buffer.

— 6.4 GT/s for the Intel

Buffer.

Intel

Intel

®

Instruction Replay Technology to replay core

pipeline for pipeline management and core RAS.

®

Virtualization Technology (Intel® VT) for

Intel® 64 or Itanium ®architecture (Intel ® Vt-i) 3 Virtualization Support Extensions for Intel

®

7500 Scalable Memory

®

7510 Scalable Memory

®

Virtualization Technology.

— Reduce virtualization complexity.

— Improve virtualization performance via hardware

optimization.

— Increase operating system compatibility.

Intel

®

Cache Safe Technology ensure mainframecaliber availability.

— Minimize LLC cache errors.

— Disable cache entries that have become hard

errors.

— Directory Cache covers 33% more cache lines.

— Improve availability.

High bandwidth Intel

®

QuickPath Interconnect for

multiprocessor scalability:

— 4 full and 2 half width Intel QPI Links

— 6.4GT/s transfer rate with aggregate data

bandwidth of 28.8 GB/s.

— Systems are easily scaled without sacrificing

performance.

Features to support flexible platform environments:

— Fully compatible with binaries for the Intel

Itanium processor family with Instruction level

advancements.

— LGA1248 Socket Level compatible wit h the Intel

Itanium® Processor 9300 Series.

— Bi-endian support.

— Processor abstraction layer eliminates processor

dependencies.

®

Intel® Itanium® Processor 9300 Series and 9500 Series Datasheet 13

Page 14

Introduction

The Intel® Itanium® Processor 9500 Series delivers increased levels of flexibility,

reliability, performance, and cost-effective scalability for your most data-intensive

business and technical applications.

®

The Intel

cache, Hyper-Threading Technology for increased performance, Intel

Itanium® Processor 9500 Series processor provides up to 32 megabytes LLC

®

Virtualization

Technology for improved virtualization, Intel® Cache Safe Technology for increased

availability. Intel® Turbo Boost Technology, featuring sustained boost. The Intel®

Itanium

®

Processor 9500 Series employs advanced power monitoring and control to

deliver a higher processor frequency at all times, for maximum performance on all

workloads. The result is a higher thermal envelope utilization for more overall

performance. The Intel

®

Itanium® Processor 9500 Series offers large cache arrays

covered by ECC including the large LLC utilizing double correct/triple detect (DECTED)

and protecting the MLI/MLD with in-line single correct/double detect (SECDED). In

addition, the processor provides extensive parity protection and parity interleaving on

nearly all RFs, end-to-end parity protection with recovery-support on all critical internal

buses and data paths including the ring. Residue protection on Floating Point unit,

along with the adoption of radiation-hardened (RAD) sequential latching elements for

vulnerable architectural and state. The Intel

®

Itanium® Processor 9500 Series

processor interfaces exclusively with the Ararat II Voltage Regulator Module.

®

The Intel

Itanium® Processor 9500 Series consists of up to 8 core processors and a

system interface unit. Each processor core provides a 12-wide, 11-stage deep

execution pipeline. The resources consist of six integer units, one integer multiply unit,

four multimedia units, two load/store units, three branch units and two floating-point

units each capable of extended, double and single precision arithmetic. The hardware

employs dynamic prefetch, branch prediction, a register scoreboard, and non-blocking

caches to optimize for compile-time non-determinism. 32 additional stacked general

registers are provided over the Intel

®

Itanium® Processor 9300 Series, and hardware

support is provided for denormal, unnormal, and pseudo-normal operands for floating

point software assist offloading.

®

New instructions on the Intel

Itanium® Processor 9500 Series simplify common tasks.

They include: clz (count leading zeros), mpy4 and mpyshl4(unsigned integer multiply/

shift and multiply), mov-to-DAHR/mv-from-DAHR (for improved MLD/FLD prefetcher

hinting and performance), and hint@priority (used by the processor to temporarily

allocate more resources to a thread). Advanced Explicitly Parallel Instruction

Computing (EPIC) is enhanced on the Intel

®

Itanium® Processor 9500 Series by

increasing the capacity of retiring instructions per cycle from 6 to a maximum of 12

instructions per cycle per core.

®

Hyper-threading Technology is enhanced in the Intel® Itanium® Processor 9500

Intel

Series with dual domain multithreading, which enables independent front-end and

back-end pipeline execution to improve multi-thread efficiency and performance for

both new and legacy applications. It provides hardware support for two threads per

core, with a threaded 96 entry per thread Instruction Buffer and threaded MLDTLB and

FLDTLB, and a dedicated load return path from the MLD to the integer register file.

Three levels of on-die cache minimize overall memory latency, with 16 KB instruction

cache FLI/16 KB write-through data cache FLD that comprise the FLC and 512 KB MLI/

256 KB writeback data cache MLD that comprise the MLC.

®

The Intel

Itanium® Processor 9500 Series offers a new RAS feature: Intel®

Instruction Replay Technology. Pipeline replay resolves stall conditions that occur when

the microprocessor pipeline encounters a resource hazard that prevents immediate

execution. In a replay , the instruction that encountered the resource hazard is removed

from the pipeline, along with all the instructions that come after it. The instruction is

then read again out of the instruction buffer for replay and re-executed. To ensure a

14 Intel

®

Itanium® Processor 9300 Series and 9500 Series Datasheet

Page 15

Introduction

replay can be initiated for any instruction in the pipeline that encounters a resource

hazard, a copy of each instruction is maintained in the instruction buffer until the

instruction has successfully traversed the pipeline and is no longer needed. If

necessary, an instruction can replay multiple times. As a result, Intel

®

Instruction

Replay Technology automatically detects and many corrects soft errors in the

instruction pipeline. With this technology, soft errors can be identified and corrected in

as few as seven clock cycles, which is fast enough to be invisible to the software

running on the platform.

1.2 Architectural Overview

The sections below give an overview of the Intel® Itanium® Processor 9300 Series and

Intel® Itanium® Processor 9500 Series.

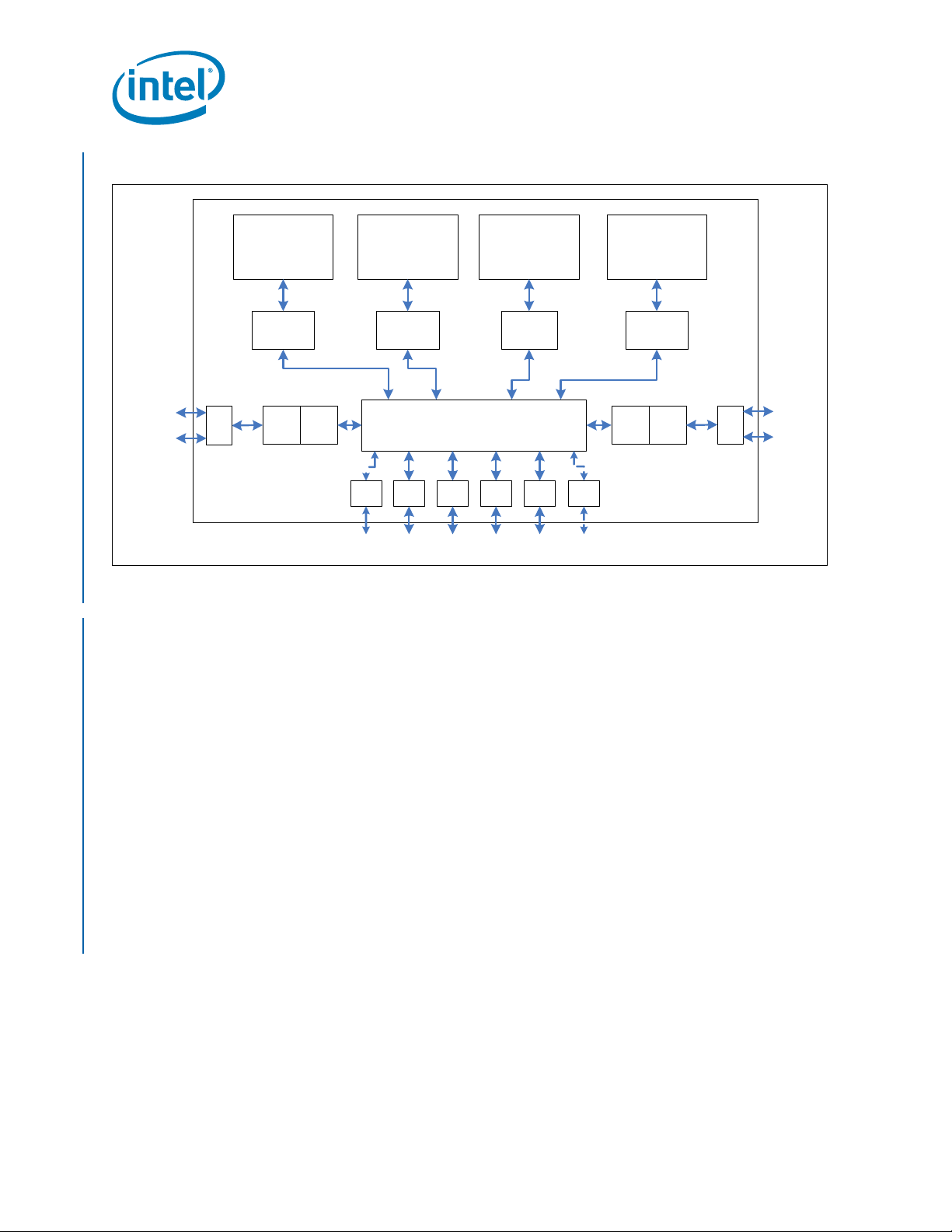

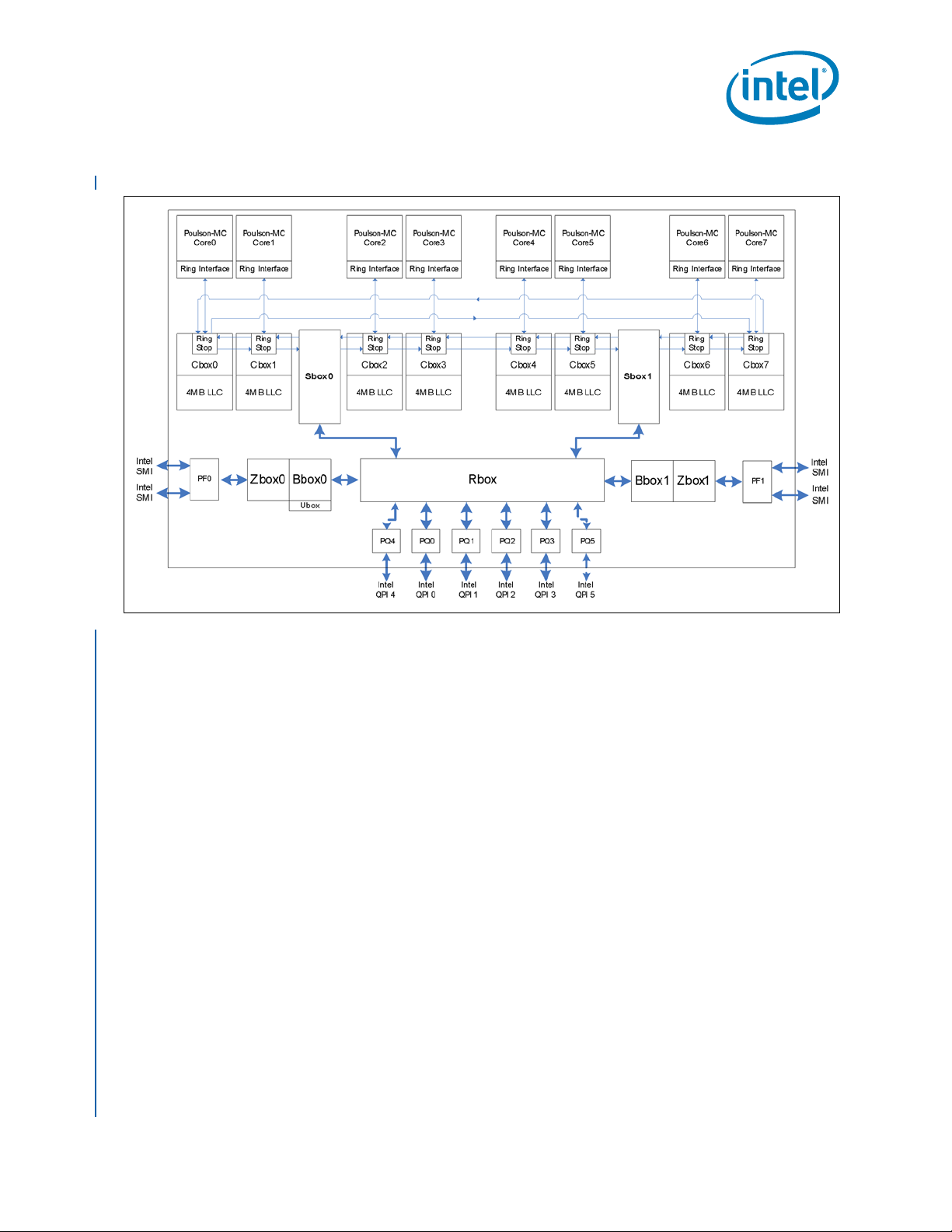

1.2.1 Intel® Itanium® Processor 9300 Series Overview

The Intel® Itanium® Processor 9300 Series processor is a quad-core architecture. It

supports up to four processor cores, each with its own L3, L2, and L1 level cache. Also

supported are the following page sizes for purges or inserts: 4K, 8K, 16K, 64K, 256K,

1M, 4M, 16M, 64M, 256M, 1G, 4G.

The architecture interfacing the cores to the system is referred to as the System

Interface. Each processor core has it own Caching Agent (CPE). The CPE interfaces

between the processor core and the Intel QuickPath Interconnect. The Intel

Processor 9300 Series processor has two Home Agents (Bbox). The Bbox interfaces

between the memory controller and the Intel

directory cache. Each Bbox interfaces with a memory controllers (Zbox). Each memory

controller supports two Intel SMI in lockstep. The Intel SMI are the interconnects to

®

7500 Scalable Memory Buffer. The processor supports six Intel QuickPath

Intel

Interconnects at the socket, four full width and two half width. The Caching Agent,

Home Agent, and Intel QuickPath Interconnects are connected via a 12-port Crossbar

Router, each port supporting the Intel QuickPath Interconnect protocol. Figure 1-1

shows the Intel

®

Itanium® Processor 9300 Series block diagram.

®

QuickPath Interconnect and supports a

®

Itanium®

The Intel QPI viral and poison fields are used to flag corrupted system state and bad

data accordingly. Once it has “gone viral”, an Intel QPI agent will set the viral field

within all packet headers. Viral mode is entered in three ways: receiving a viral packet,

upon a detecting fatal/panic error, or when a global viral signal (from Cboxes) is

asserted. Viral is cleared on Reset. Poisoning is used to indicate bad data on a per-flit

basis. Poison does not indicate corrupted system coherency, but rather that a particular

block of data is not reliable.

Intel® Itanium® Processor 9300 Series and 9500 Series Datasheet 15

Page 16

Introduction

Core0 Core3Core2Core1

CPE0 CPE3CPE2CPE1

RboxBbox0Zbox0 Zbox1Bbox1

Pbox

PZ1

Pbo x

PR1

Pbo x

PR 0

Pbo x

PH4

Pbo x

PH5

Pbo x

PR 3

Pbo x

PR 2

Intel® SM I

Intel® SM I

Intel®

QPI

Intel®

QPI

Intel®

QPI

Intel®

QPI

Intel®

QPI

Intel®

QPI

Pbox

PZ0

Intel® SM I

Intel® SM I

0xA 0

87 3

16 9 5240xB

Figure 1-1. Intel

®

Itanium® Processor 9300 Series Processor Block Diagram

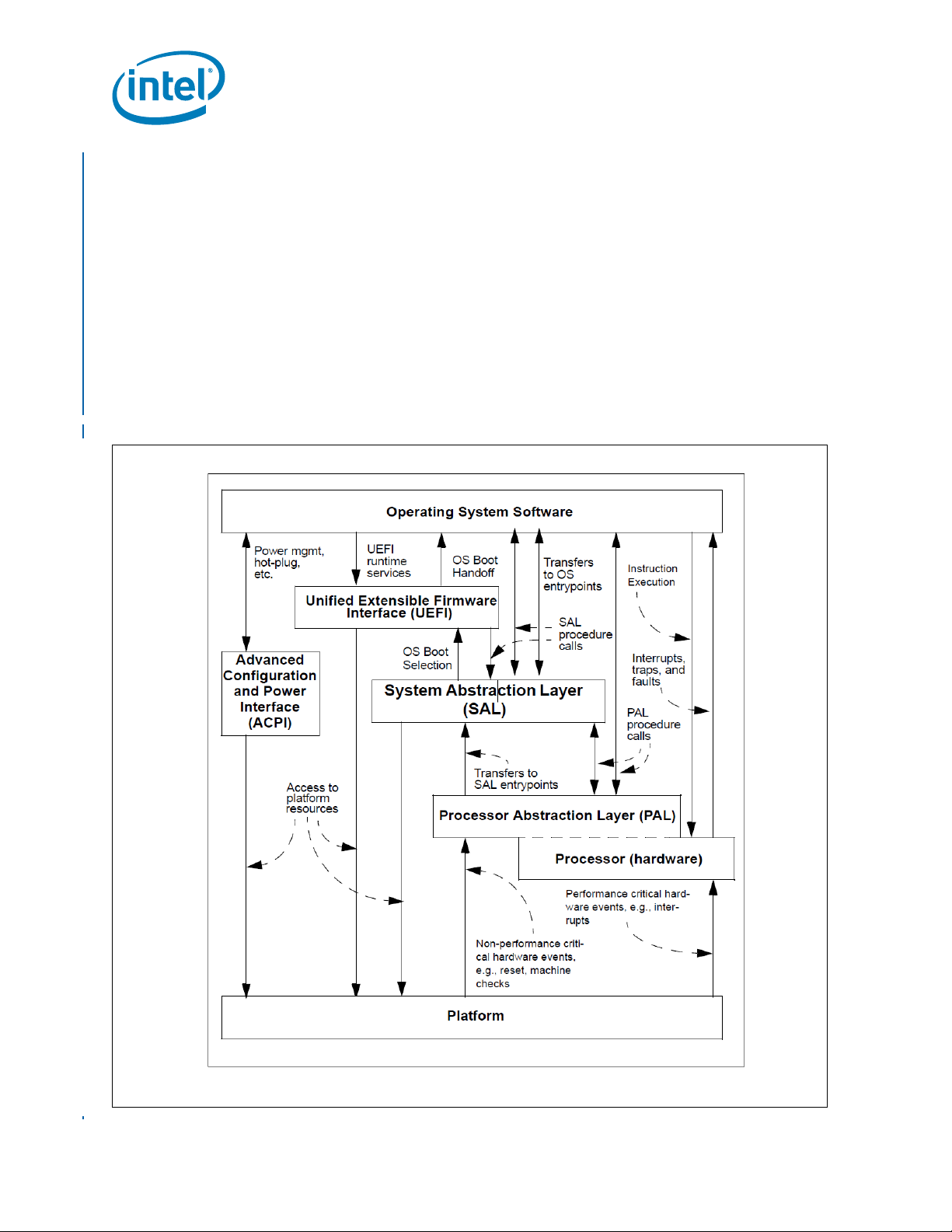

1.2.2 Intel® Itanium® Processor 9500 Series Overview

The Intel® Itanium® Processor 9500 Series is an eight core architecture. It supports up

to eight cores, each with its own First Level Cache (FLC) and Mid Level Cache (MLC),

both of which are split into instruction and data caches (FLI/FLD and MLI/MLD,

respectively). The Last Level Cache (LLC) is shared among the cores and supports up to

32 MB. Also supported are the following page sizes for purges or inserts: 4K, 8K, 16K,

64K, 256K, 1M, 4M, 16M, 64M, 256M, 1G, 4G.

The architecture interfacing the cores to the system is referred to as the uncore. Each

®

Itanium® Processor 9500 Series core interfaces to the Ring. The Ring provides

Intel

connectivity to the Last Level Cache via the Cache Controllers (Cboxes). The Ring also

provides connectivity to Intel QPI via Ring/Sbox. The Sbox and Cbox provide the

supports for the two Intel QPI Caching Agents. The processor has two Home Agents

(Bbox). The Bbox interfaces between the memory controller and the Intel

Interconnect and supports a directory cache. Each memory controller supports two

®

Scalable Memory Interconnects (Intel® SMI) in lockstep. The Intel SMI are the

Intel

interconnects to Scalable Memory Buffer. The Intel

processor supports six Intel® QuickPath Interconnects at the socket, four full width and

two half width. The Caching Agent, Home Agent, and Intel

are connected via a 10-port Crossbar Router, each port supporting the Intel

Interconnect protocol. Figure 1-2 shows the processor block diagram.

®

QuickPath

®

Itanium® Processor 9500 Series

®

QuickPath Interconnects

®

QuickPath

16 Intel

®

Itanium® Processor 9300 Series and 9500 Series Datasheet

Page 17

Introduction

Figure 1-2. Intel

®

Itanium® Processor 9500 Series Processor Block Diagram

The Intel QPI viral and poison fields are used to flag corrupted system state and bad

data accordingly. Once it has “gone viral”, an Intel QPI agent will set the viral field

within all packet headers. Viral mode is entered in three ways: receiving a viral packet,

upon a detecting fatal/panic error, or when a global viral signal (from Cboxes) is

asserted. Viral is cleared on Reset. Poisoning is used to indicate bad data on a per-flit

basis. Poison does not indicate corrupted system coherency, but rather that a particular

block of data is not reliable.

®

Itanium® Processor 9500 Series PAL's Demand Based Switching (DBS) support

Intel

includes implementations of Power/Performance states (P-states) and Halt states (Cstates). For the PAL Halt state interface and architected specifications of the PAL Pstate interface, see the Intel

Volume 2, Section 11.6. PAL controls the Intel

®

Itanium® Architecture Software Developer's Manual,

®

Itanium® Processor 9500 Series

processor power through a special built-in microcontroller that manipulates voltage and

frequency. PAL communicates requested P-states to this controller through internal

registers.

As shown in Figure 1-3, Itanium architecture-based firmware consists of several major

components: Processor Abstraction Layer (PAL), System Abstraction Layer (SAL),

Unified Extensible Firmware Interface (UEFI) and Advanced Configuration and Power

Interface (ACPI). PAL, SAL, UEFI and ACPI together provide processor and system

initialization for an operating system boot. PAL and SAL provide machine check abort

handling. PAL, SAL, UEFI and ACPI provide various run-time services for system

functions which may vary across implementations. The interactions of the various

services that PAL, SAL, UEFI and ACPI provide are illustrated in Figure 1-3. In the

context of this model and throughout the rest of this chapter, the System Abstraction

Layer (SAL) is a firmware layer which isolates operating system and other higher level

software from implementation differences in the platform, while PAL is the firmware

layer that abstracts the processor implementation.

Intel® Itanium® Processor 9300 Series and 9500 Series Datasheet 17

Page 18

Protection Keys provide a method to restrict permission by tagging each virtual page

with a unique protection domain identifier. The Protection Key Registers (PKR)

represent a register cache of all protection keys required by a process. The operating

system is responsible for management and replacement polices of the protection key

cache. Before a memory access (including IA-32) is permitted, the processor compares

a translation’s key v alue against all keys contained in the PKRs. If a matching key is not

found, the processor raises a Key Miss fault. If a matching Key is found, access to the

page is qualified by additional read, write and execute protection checks specified by

the matching protection key register. If these checks fail, a Key Permission fault is

raised. Upon receipt of a Key Miss or Key P e rmission fault, software can implement the

desired security policy for the protection domain. Some processor models may

implement additional protection key registers and protection key bits. Unimplemented

bits and registers are reserved. Please see the processor-specific documentation for

further information on the number of protection key registers and protection key bits

implemented on the processor.

Figure 1-3. Intel

®

Itanium® Processor 9500 Series Firmware Diagram

Introduction

18 Intel

®

Itanium® Processor 9300 Series and 9500 Series Datasheet

Page 19

Introduction

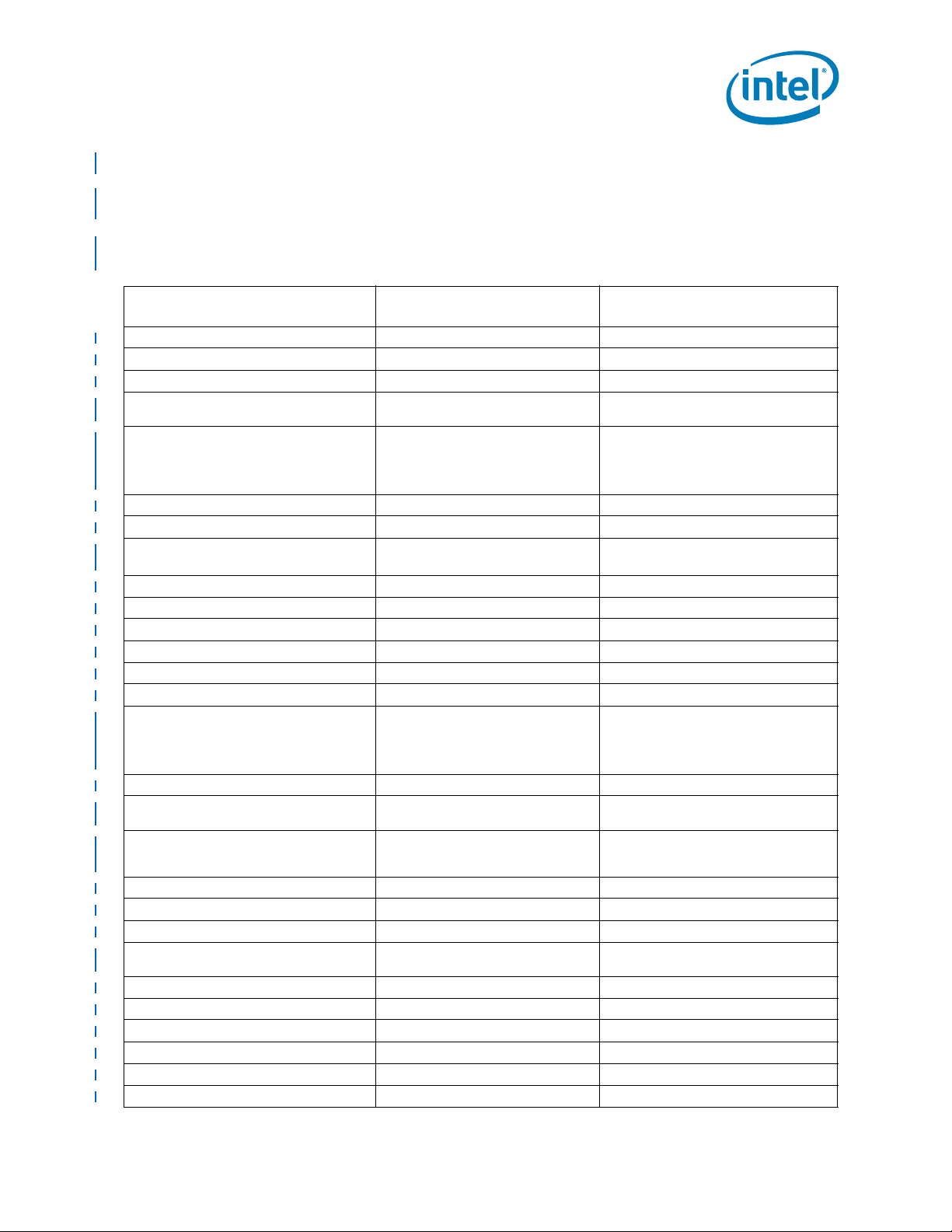

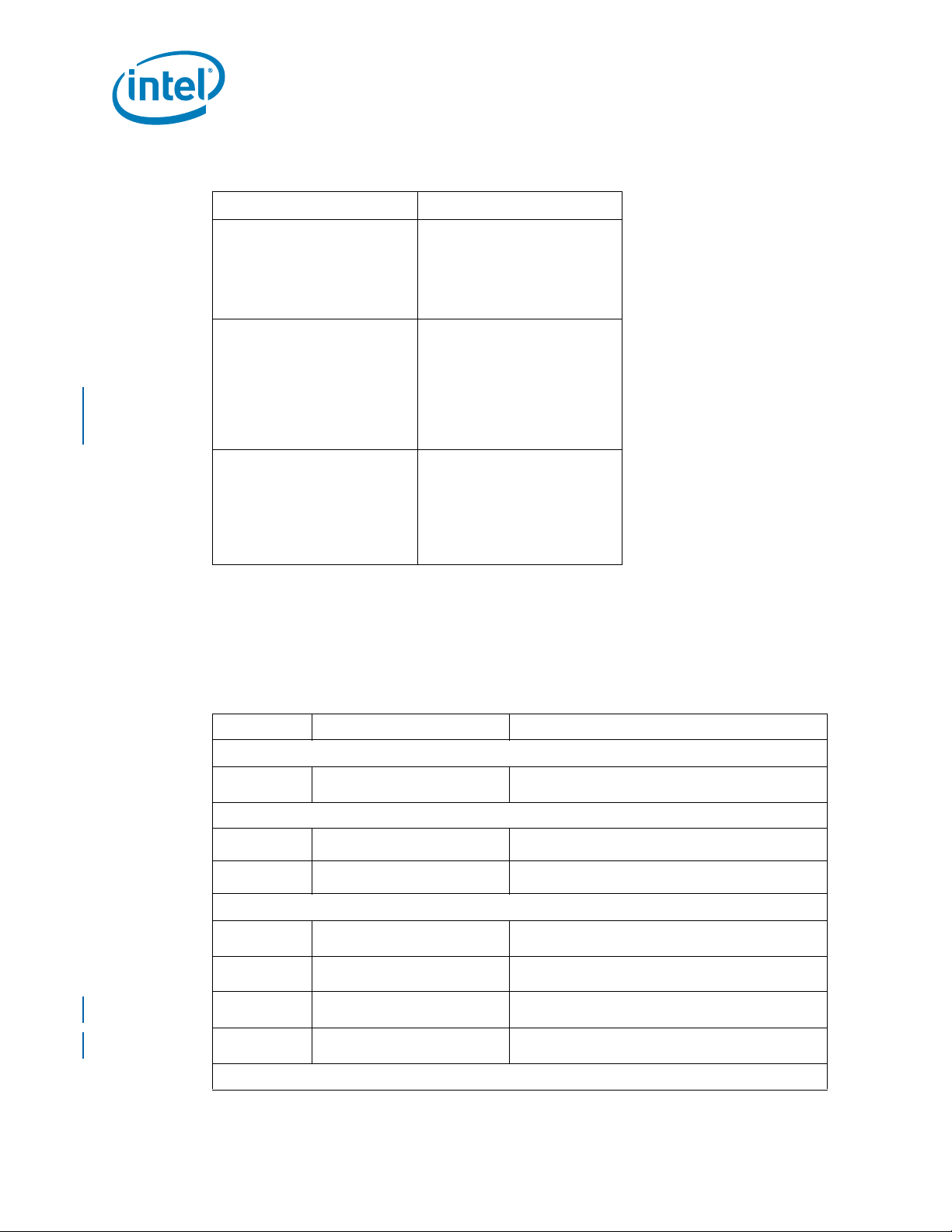

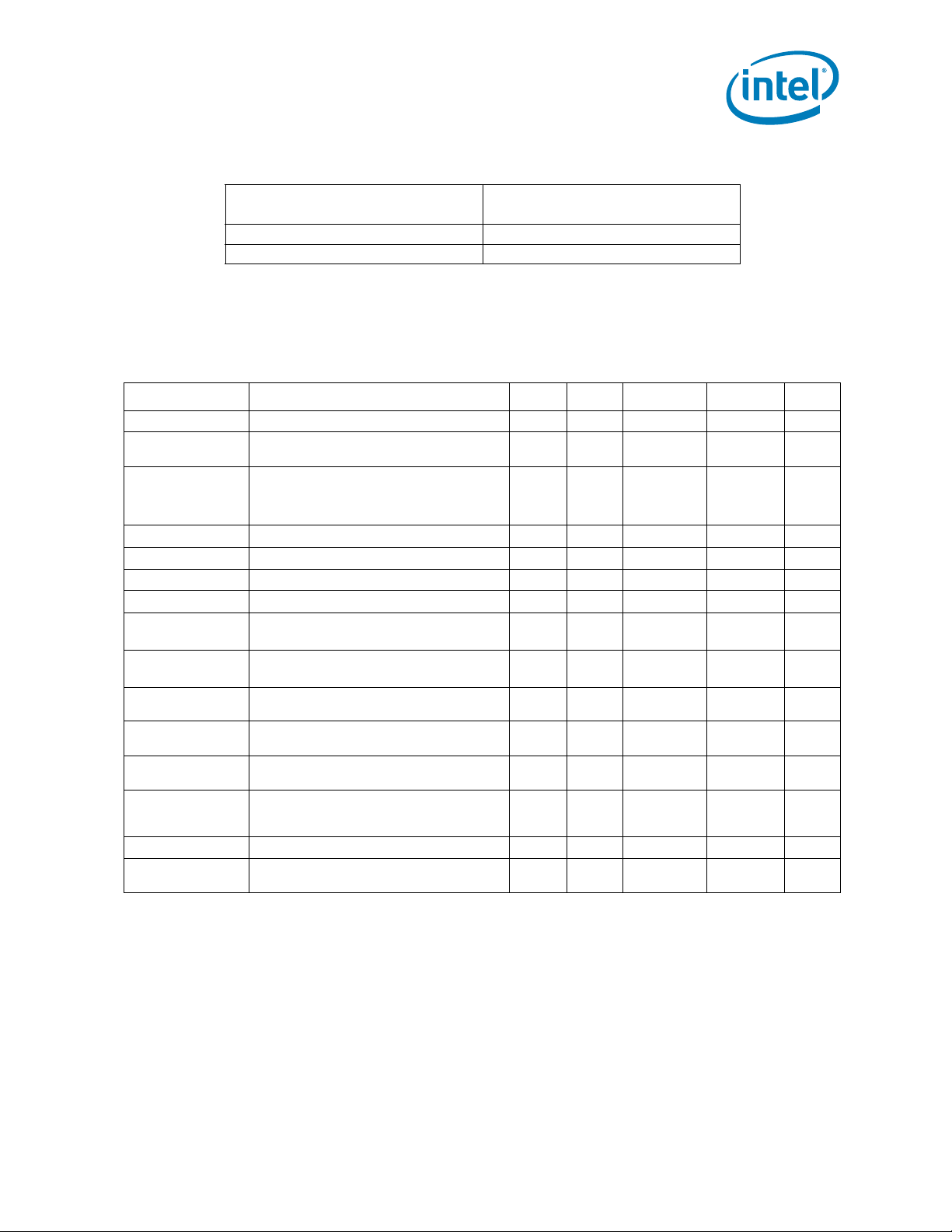

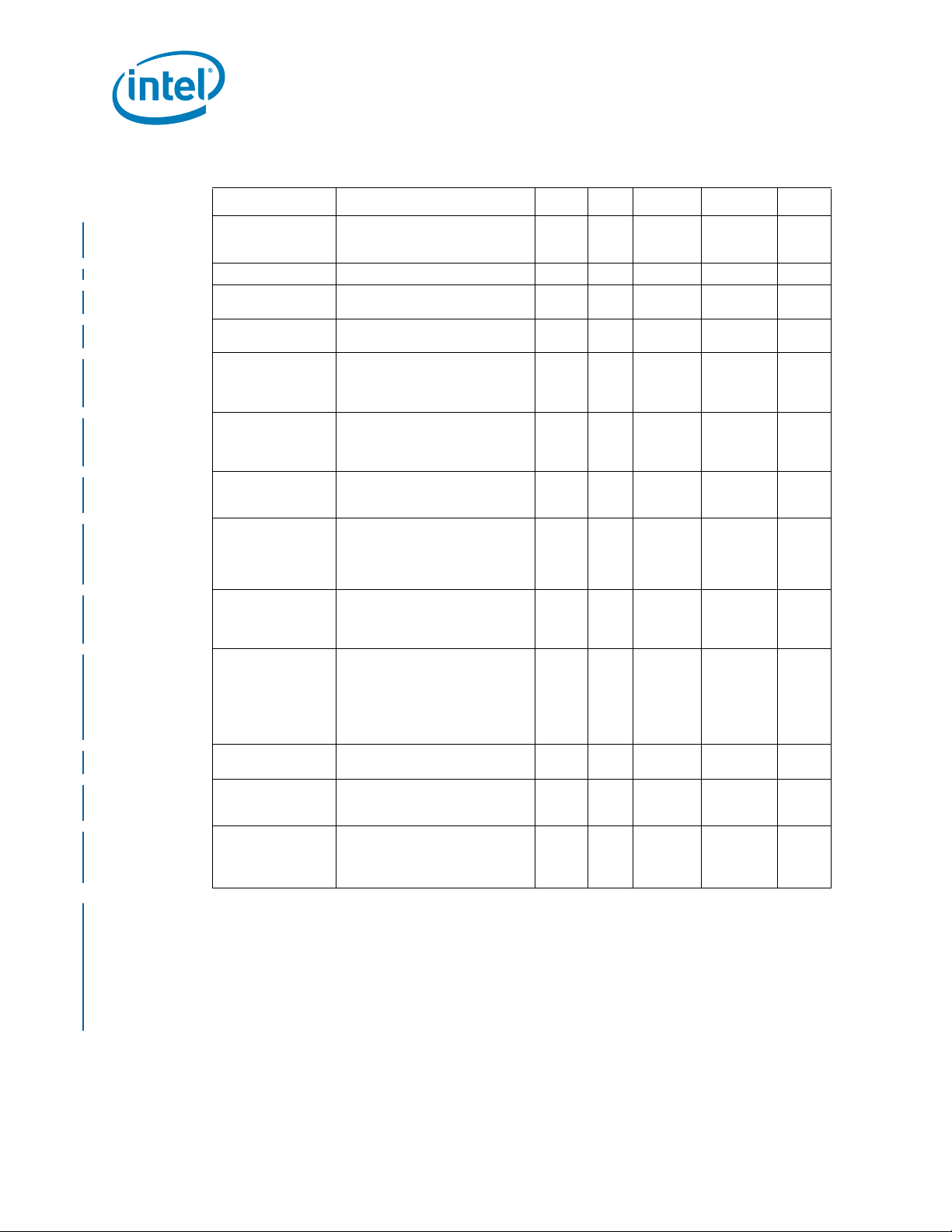

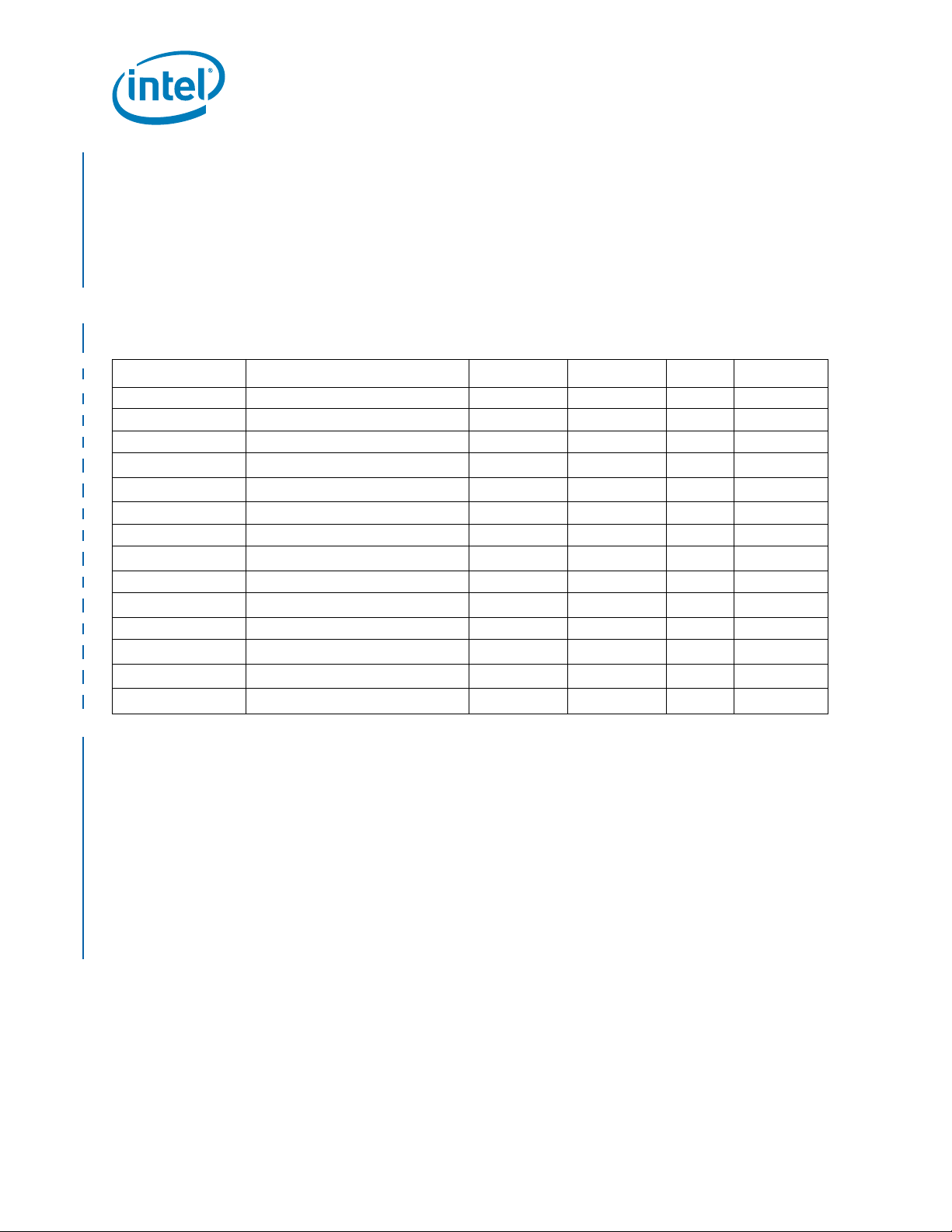

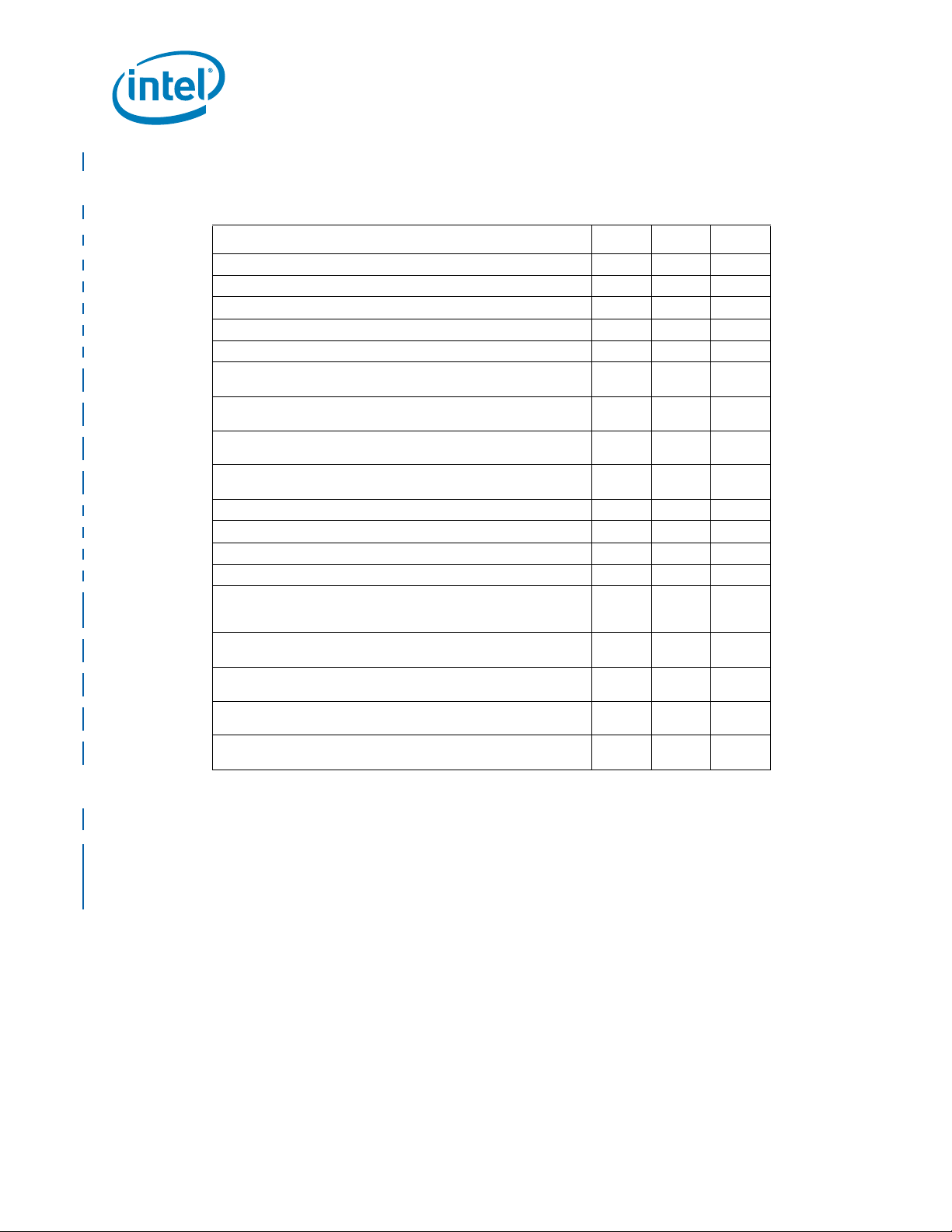

1.3 Processor Feature Comparison

The Intel® Itanium® Processor 9300 Series processor and Intel® Itanium® Processor

9500 Series processor features are compared below in Table 1-1.

®

Table 1-1. Intel

Intel

Description

Socket LG1248 LG1248

Transistors 2 billion 3.1 billion

Cores/Threads up to 4/8 up to 8/16

Clock speeds up to 1.86 GHz via Intel

Integrated on-die cache L1 (L1I 16K/L1D 16K),

Ararat Voltage Regulator Module Support Ararat “I” Ararat II

Supported speeds DDR3-800 DDR3-800 and DDR3-1067

Intel QPI links 6

Intel QPI Hot-plug Supported Supported

Intel QPI Link self-healing Supported Supported

Intel QPI Clock fail-safe Supported Supported

Intel QPI Data scrambling Supported Required

Intel QPI Periodic retraining Not Supported Required

Integrated memory controllers 2 2

®

Intel

SMI Interface Intel® 7500 Scalable Memory Buffer

®

Intel

SMI Hot-plug Supported Supported

Physical address space/virtual address

space

Caching agent architecture four caching agents per socket where

Home agents per socket 2 2

Directory Cache Supported Supported

®

Intel

Virtualization Technology (Intel® VT) Intel® Vt-i 2 Intel® Vt-i 3

Hot add/hot removal at Intel QPI link and

DIMM memory interface

Hot add CPU Supported

Hot add memory Supported

Hot remove/hot replace memory Supported

Memory sparing technique DIMM DIMM and Rank

Memory scrubbing Supported Supported

Memory mirroring Supported Supported

Itanium® Processor 9300 Series and

®

Itanium® Processor 9500 Series Feature Comparison

®

Intel

Itanium® Processor 9300

Series

®

with sustained boost

L2 (L2I 512K, L2D 256K),

inclusive L3 (6 MB per core,

up to 24 MB)

(4 full/2 half width at up to 4.8 GT/s)6 (4 full/2 half width at up to 6.4 GT/s)

(4.8 GT/s)

50 physical/64 virtual 50 physical/64 virtual

each agent is responsible for all of the

address space and dedicated to a core

Supported Supported

T urbo Boost

2,3

2,3

2,3

Intel® Itanium® Processor 9500

FLC (FLI 16K/FLD 16K),

MLC (MLI 512K, MLD 256K),

LLC (shared, up to 32 MB)

Intel® 7500 Scalable Memory Buffer

®

7510 Scalable Memory Buffer

Intel

two caching agents per socket are

responsible for half the address space

and shared among the cores

Series

1.73 - 2.53 GHz

1

(4.8 GT/s)

(6.4 GT/s)

Supported

Supported

Supported

2,3

2,3

2,3

Intel® Itanium® Processor 9300 Series and 9500 Series Datasheet 19

Page 20

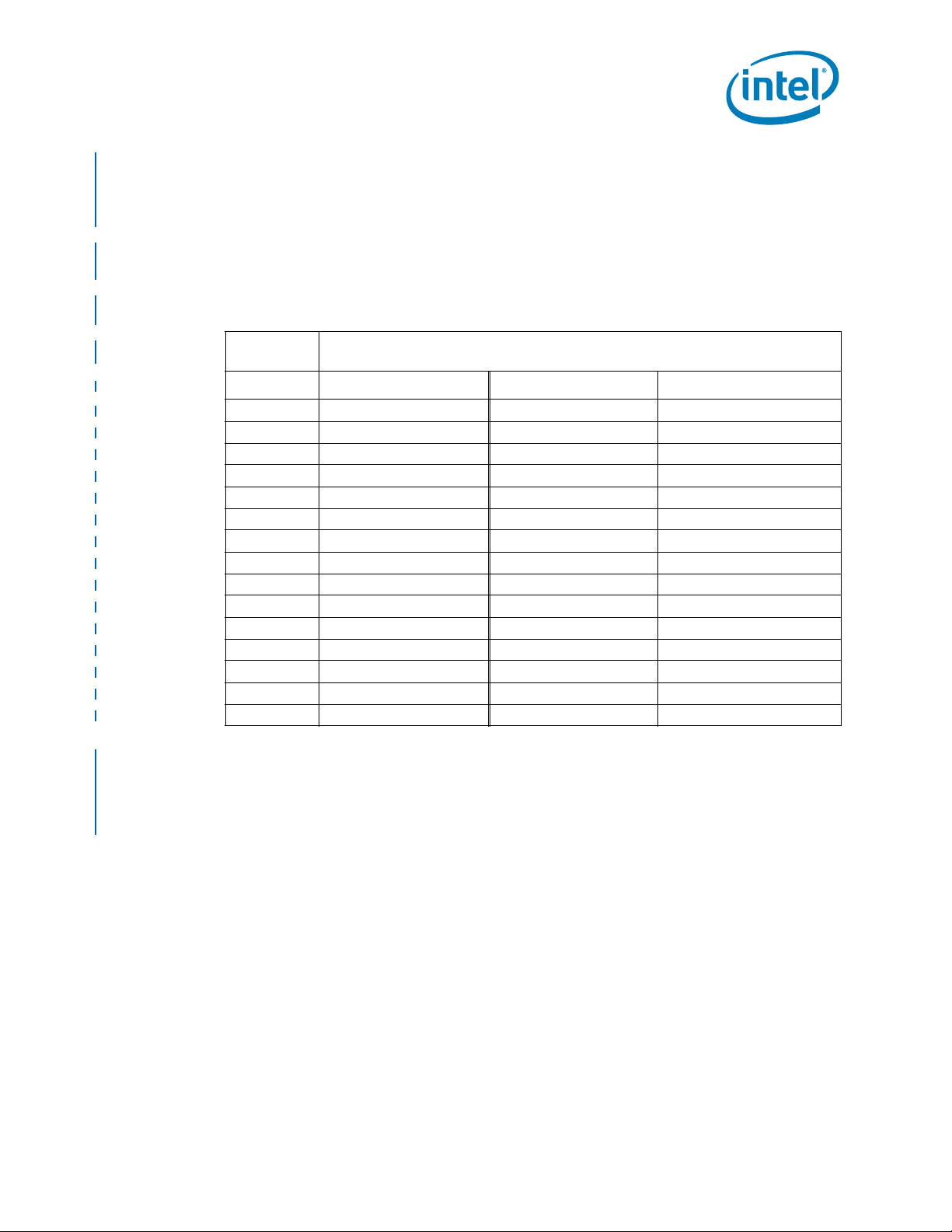

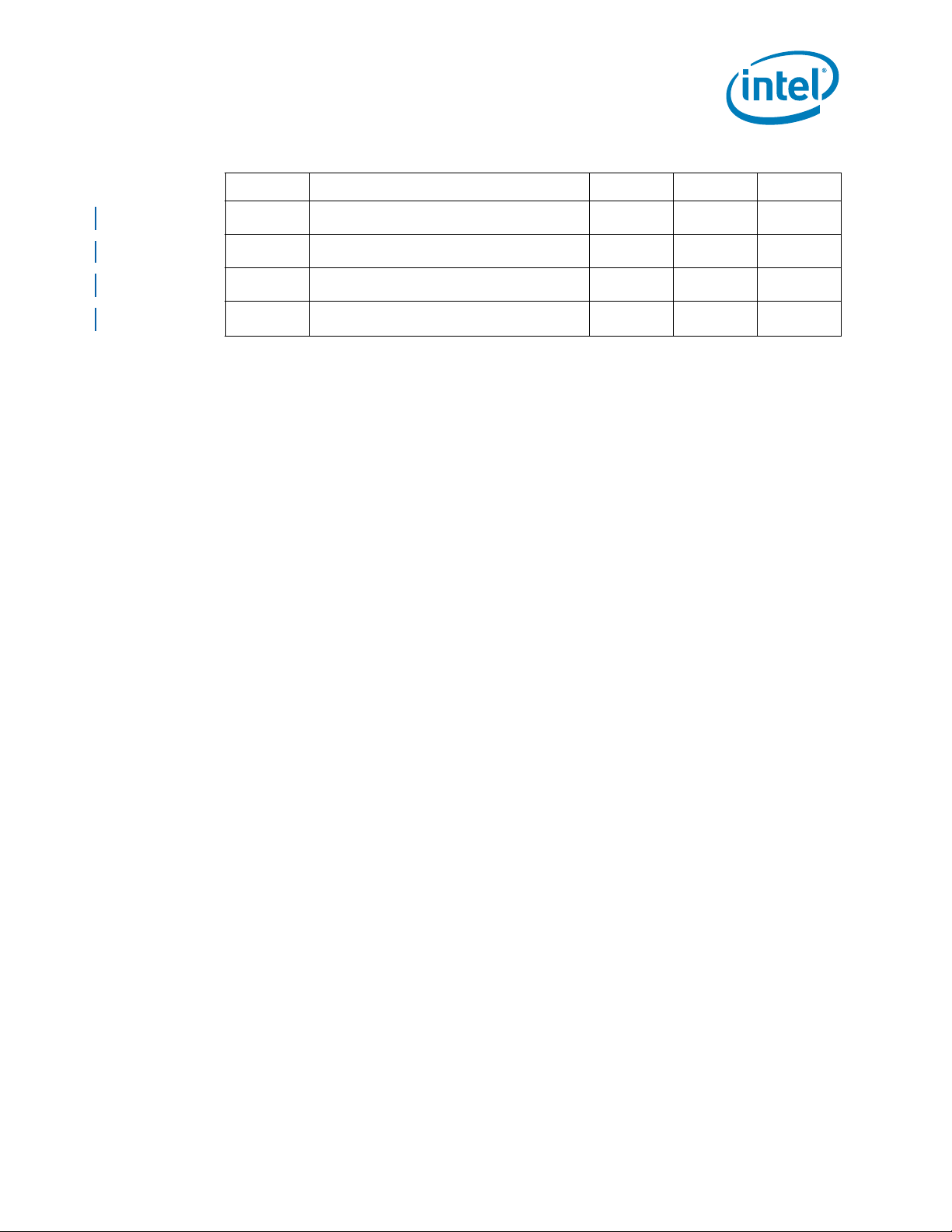

Notes:

®

Itanium® Processor 9300

Description

Memory patrolling Supported Supported

Memory migration Supported Supported

Support for mixing of x4 and x8 on the

same DDR channel

Online/Offline CPU (OS assisted) Supported Supported

Online/Offline Memory (OS assisted) Supported Supported

Online/Offline I/O Hub Supported Supported

Thermal Design Power (TDP) SKUs 130W, 155W, 185W 130W and 170W

1. OEM responsible for specifying platform-specific retraining interval.

2. Electrical isolation only, no physical add/remove supported.

3. Assume spare is installed.

Intel

Series

Not Supported Supported

Intel® Itanium® Processor 9500

Series

1.4 Processor Abstraction Layer

The Intel® Itanium® Processor 9300 Series and Intel® Itanium® Processor 9500 Series

require implementation-specific Processor Abstraction Layer (PAL) firmware. PAL

firmware supports processor initialization, error recovery, and other functionality. It

provides a consistent interface to system firmware and operating systems across

processor hardware implementations. The Intel

Developer’s Manual, Volume 2: System Architecture, describes PAL. Platforms must

provide access to the firmware address space and PAL at reset to allow the processors

to initialize.

®

Itanium® Architecture Software

Introduction

The System Abstraction Layer (SAL) firmware contains platform-specific firmware to

initialize the platform, boot to an operating system, and provide runtime functionality.

Further information about SAL is available in the Intel

®

Itanium® Processor Family

System Abstraction Layer Specification.

1.5 Mixing Processors of Different Frequencies and Cache Sizes

All Intel® Itanium® Processor 9300 Series processors and Intel® Itanium® Processor

9500 Series in the same system partition are required to have the same last level

cache size and identical core frequency . Mixing processors of different core frequencies,

cache sizes, and mixing Intel

®

Itanium® Processor 9300 Series with Intel® Itanium®

Processor 9500 Series is not supported and has not been validated by Intel. Operating

system support for multiprocessing with mixed components should also be considered.

1.6 Terminology

In this document, “the processor” refers to the Intel® Itanium® Processor 9300 Series

and/or Intel

An ‘_N’ notation after a signal name refers to an active low signal. This means that a

signal is in the active state (based on the name of the signal) when driven to a low

level. For example, when RESET_N is low, a processor reset has been requested. When

NMI is high, a non-maskable interrupt has occurred. In the case of lines where the

name does not imply an active state but describes part of a binary sequence (such as

®

Itanium® Processor 9500 Series, unless otherwise indicated.

20 Intel

®

Itanium® Processor 9300 Series and 9500 Series Datasheet

Page 21

Introduction

address or data), the ‘_N’ notation implies that the signal is inverted. For example,

D[3:0] = ‘HLHL’ refers to a Hex ‘A’, and D [3:0] _N = ‘LHLH’ also refers to a Hex ‘A’ (H

= High logic level, L = Low logic level).

A signal name has all capitalized letters, for example, VCTERM.

A symbol referring to a voltage level, current level, or a time value carries a plain

subscript, for example, Vccio, or a capitalized abbreviated subscript, for example, TCO.

1.7 State of Data

The data contained in this document is subject to change. It is the best information

that Intel is able to provide at the publication date of this document.

1.8 Reference Documents

The reader of this specification should also be familiar with material and concepts

presented in the following documents:

Document Name

®

Intel

Itanium® Processor 9300 Series and 9500 Series Specification Update

®

Intel

Itanium® Architecture Software Developer’s Manual, Volume 1:

Application Architecture

®

Itanium® Architecture Software Developer’s Manual, Volume 2: System

Intel

Architecture

®

Itanium® Architecture Software Developer’s Manual,

Intel

Volume 3: Instruction Set Reference

®

Itanium® Architecture Software Developer’s Manual,

Intel

Volume 4: IA-32 Instruction Set Reference

®

Itanium® 9300 Series Processor Reference Manual for Software

Intel

Development and Optimization

®

Itanium® 9500 Series Processor Reference Manual for Software

Intel

Development and Optimization

®

Itanium® Processor Family System Abstraction Layer Specification

Intel

®

Intel

Itanium® Processor 9300 Series and Intel® Itanium® Processor 9500

Series Platform Design Guide

System Management Bus (SMBus) Specification

Note: Contact your Intel representative or check http://developer.intel.com for the latest

revision of the reference documents.

§

Intel® Itanium® Processor 9300 Series and 9500 Series Datasheet 21

Page 22

Introduction

22 Intel

®

Itanium® Processor 9300 Series and 9500 Series Datasheet

Page 23

Electrical Specifications

T

X

R

X

R

TT

R

TT

R

TT

R

TT

Signal

Signal

2 Electrical Specifications

This chapter describes the electrical specifications of the Intel® Itanium® Processor

9300 Series and 9500 Series processors.

2.1 Intel® QuickPath Interconnect and Intel® Scalable Memory Interconnect Differential Signaling

The links for Intel® QuickPath Interconnect (Intel® QPI) and Intel® Scalable Memory

Interconnect (Intel® SMI) signals use differential signaling. The Intel® SMI bus pins are

referred to as FB-DIMM pins on the package. The termination voltage level for the

processor for uni-directional serial differential links, each link consisting of a pair of

opposite-polarity (D+, D-) signals, is V

SS

.

Termination resistors are provided on the processor silicon and are terminated to V

thus eliminating the need to terminate the links on the system board for the Intel®

QuickPath Interconnect and FB-DIMM signals.

When designing a system, Intel strongly recommends that design teams perform

analog simulations of the Intel

refer to the latest available revision of the Intel® Itanium® Processor 9300 Series and

Intel® Itanium® Processor 9500 Series Platform Design Guide.

Figure 2-1 illustrates the active on-die termination (ODT) of these differential signals.

All the differential signals listed in Table 2-1 have ODT resistors. Also included in the

table are the debug signals.

Figure 2-1. Active ODT for a Differential Link Example

®

QuickPath Interconnect and FB-DIMM pins. Please

SS,

Intel® Itanium® Processor 9300 Series and 9500 Series Datasheet 23

Page 24

Electrical Specifications

Table 2-1. Signals with R

CSI[3:0]R[P/N]Dat[19:0]

CSI[5:4]R[P/N]Dat[9:0]

CSI[3:0]T[P/N]Dat[19:0]

CSI[5:4]T[P/N]Dat[9:0]

CSI[5:0]R[P/N]Clk

CSI[5:0]T[P/N]Clk

FBD0NBICLK[A/B][P/N]0

FBD1NBICLK[C/D][P/N]0

FBD0SBOCLK[A/B][P/N]0

FBD1SBOCLK[C/D][P/N]0

FBD0NBI[A/B][P/N][13:0]

FBD1NBI[C/D][P/N][13:0]

FBD0SBO[A/B][P/N][10:0]

FBD1SBO[C/D][P/N][10:0]

XDPOCPD_N[7:0]

TRIGGER_N[1:0]

XDPOCPFRAME_N

XDPOCP_STRB_IN_N

PRBMODE_REQST_N

XDPOCP_STRB_OUT_N

PRBMODE_RDY_N

TT

Signal Termination

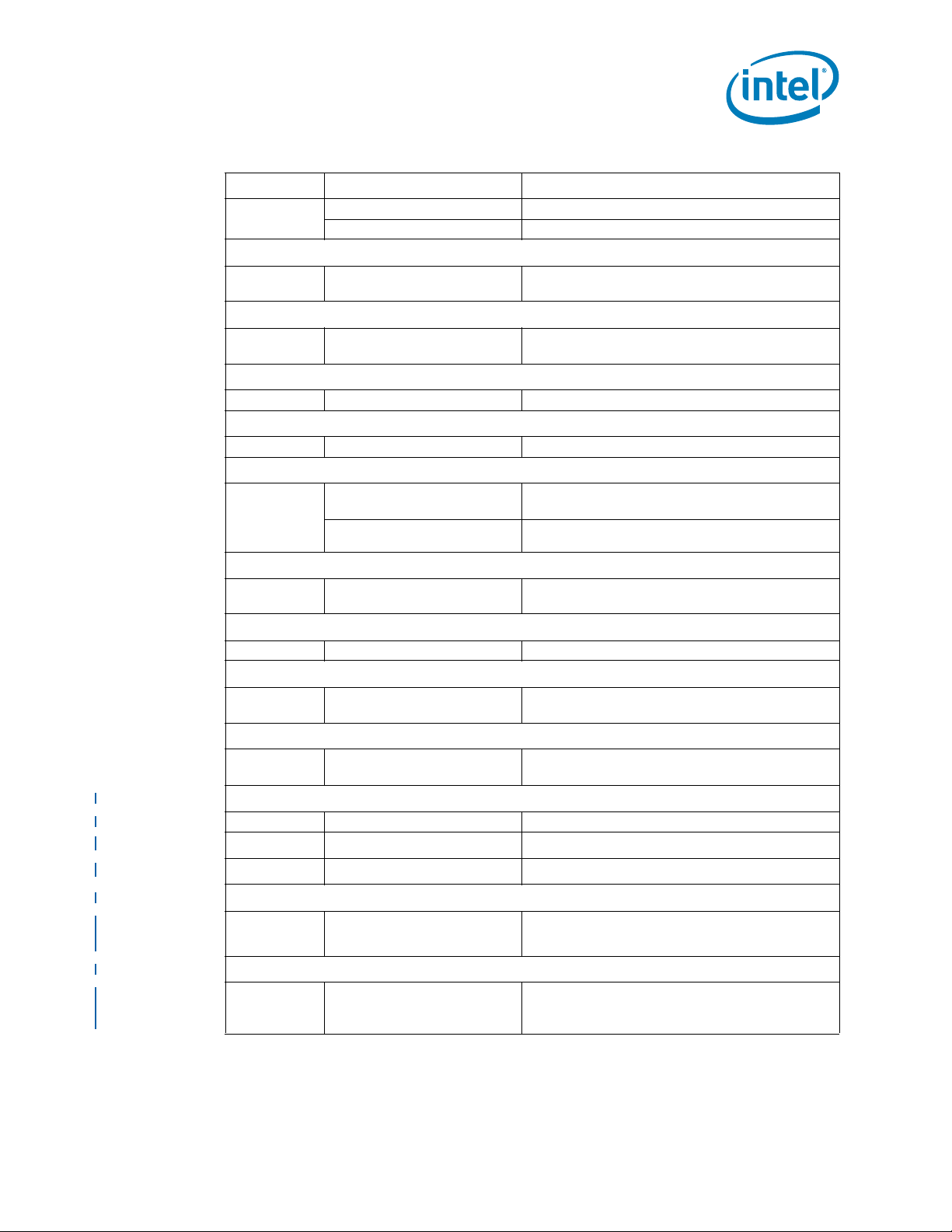

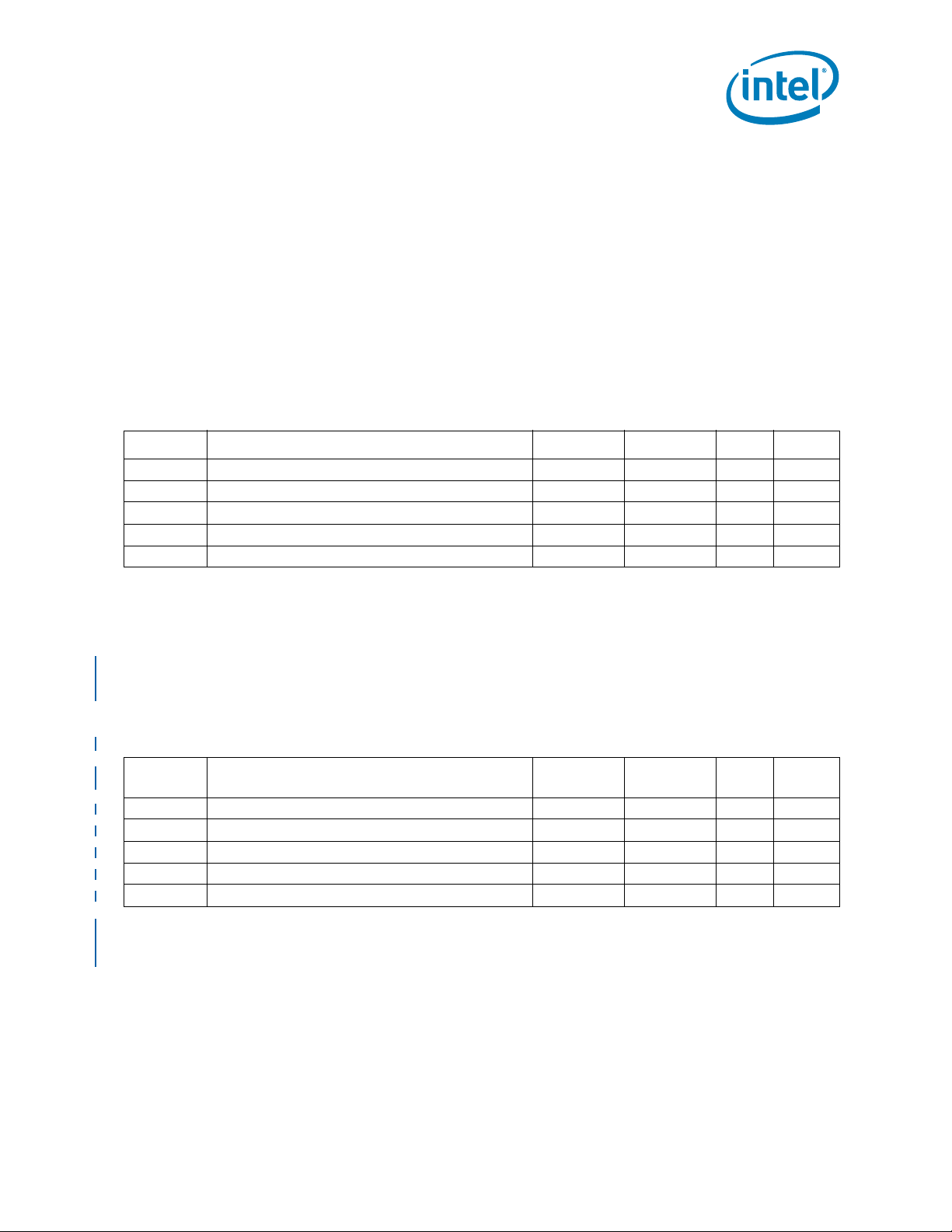

2.2 Signal Groups

VSS

VSS

VCCIO

The signals are grouped by buffer type and similar characteristics as listed in Table 2-2.

The buffer type indicates which signaling technology and specifications apply to the

signals.

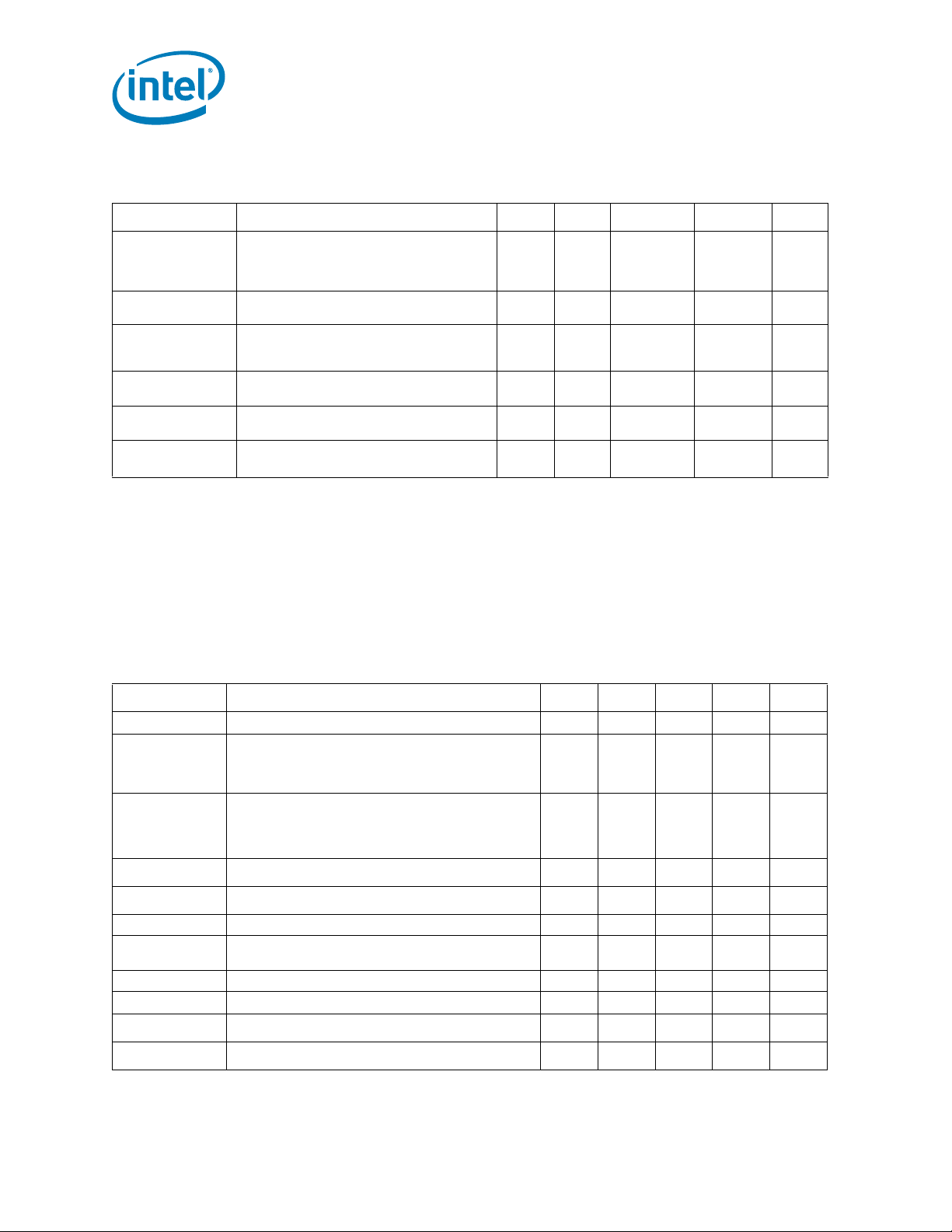

Table 2-2. Signal Groups (Sheet 1 of 3)

Signal Group Buffer Type Signals 1, 2, 3

Differential System Reference Clock

Differential CMOS In Differential Pair SYSCLK, SYSCLK_N;

®

QuickPath Interconnect Signal Groups

Intel

Differential Input CSI[3:0]R[P/N]Dat[19:0], CSI[5:4]R[P/N][9:0]

Differential Output CSI[3:0]T[P/N]Dat[19:0], CSI[5:4]T[P/N][9:0],

FB-DIMM Signals

Differential Input FBD0NBICLK[A/B][P/N]0

Differential Output FBD0SBOCLK[A/B][P/N]0

Differential Input FBD0NBI[A/B][P/N][13:0]

Differential Output FBD0SBO[A/B][P/N][10:0]

TAP

SYSUTST_REFCLK_N, SYSUTST_REFCLK

CSI[5:0]R[P/N]CLK

CSI[5:0]T[P/N]CLK

FBD1NBICLK[C/D][P/N]0

FBD1SBOCLK[C/D][P/N]0

FBD1NBI[C/D][P/N][13:0]

FBD1SBO[C/D][P/N][10:0]

24 Intel

®

Itanium® Processor 9300 Series and 9500 Series Datasheet

Page 25

Electrical Specifications

Table 2-2. Signal Groups (Sheet 2 of 3)

Signal Group Buffer Type Signals 1, 2, 3

Single-ended CMOS Inputs TCK, TDI, TMS, TRST_N

GTL Open Drain Output TDO

SMBus

Single-ended GTL I/O SMBCLK,

SPD Bus

Single-ended GTL I/O SPDCLK

Setup

Single-ended GTL Input BOOTMODE[1:0], SKTID[2:0]

System Management

Single-ended CMOS Input LRGSCLSYS

Flash ROM Port

Single-ended GTL-open Drain Input FLASHROM_CFG[2:0],

GTL-open Drain Output FLASHROM_CS[3:0]_N, FLASHROM_C LK,

ERROR Bus

Single-ended GTL Open Drain Output

Power-up

Single-ended GTL Input PWRGOOD, RESET_N

Thermal

Single-ended GTL-Open Drain Output

VID Port

4

Single-ended CMOS Output VID_VCCCORE[6:0], VID_VCCCACHE[5:0],

SVID Port

Single-ended GTL Output SVID_CLK

GTL Input

GTL Input

(Intel® Itanium® Processor 9300 Series)

4

(Intel® Itanium® Processor 9500 Series)

GTL I/O SVD_DATIO

GTL Input SVID_ALERT_N

SMBDAT

SPDDAT

FLASHROM_DATI

FLASHROM_DATO, FLASHROM_WP_N

ERROR[0]_N, ERROR[1]_N

MEM_THROTTLE_L

PROCHOT_N, THERMTRIP_N, THERMALERT_N

FORCEPR_N

VID_VCCUNCORE[6:0]

Voltage Regulator

Single-ended Open Collector/Drain Output VR_THERMTRIP_N, VRPWRGD (Intel® Itanium®

Voltage Regulator Control

Single-ended CMOS Input

4

4

GTL Input

Open Collector/Drain Output

Processor 9300 Series processor), VR_READY (Intel

®

Itanium

Processor 9500 Series processor), VR_FAN_N

VROUTPUT_ENABLE0

VR_THERMALERT_N

VR_THERMTRIP_N, VRPWRGD, VR_FAN_N

®

Intel® Itanium® Processor 9300 Series and 9500 Series Datasheet 25

Page 26

Notes:

Table 2-2. Signal Groups (Sheet 3 of 3)

Signal Group Buffer Type Si gna l s 1, 2, 3

Debug

GTL I/O XDPOCPD_N[7:0],TRIGGER_N[1:0]

Single-ended

Power Supplies

V

CC33_SM

PIROM

GTL Input XDPOCP_STRB_IN_N, PRBMODE_REQST_N

GTL Output XDPOCP_STRB_OUT_N, PRBMODE_RDY_N

Core V

Uncore V

Cache (Intel® Itanium®

Processor 9300 Series)

Analog V

I/O V

Stand-by V

Pins

Input PIR_SCL

I/O PIR_SDA

Input PIR_A0

Input PIR_A1

Input SM_WP

XDPOCPFRAME_N

4

CCCORE

CCUNCORE

V

CCCACHE

CCA

CCIO

CC33_SM

4

4

Electrical Specifications

1. CMOS signals have a reference voltage (Vref) equal to VCCIO/2.

2. GTL signals have a reference voltage (Vref) equal to VCCIO*(2/3).

3. All single-ended buffer types, including inputs, outputs and input/outputs, include an on-die pull up resistor

between 4 kOhms and 8.7 kOhms. Recommended values for external pull-downs on the inputs and input/

output signals must meet the V

specification for that buffer.

il

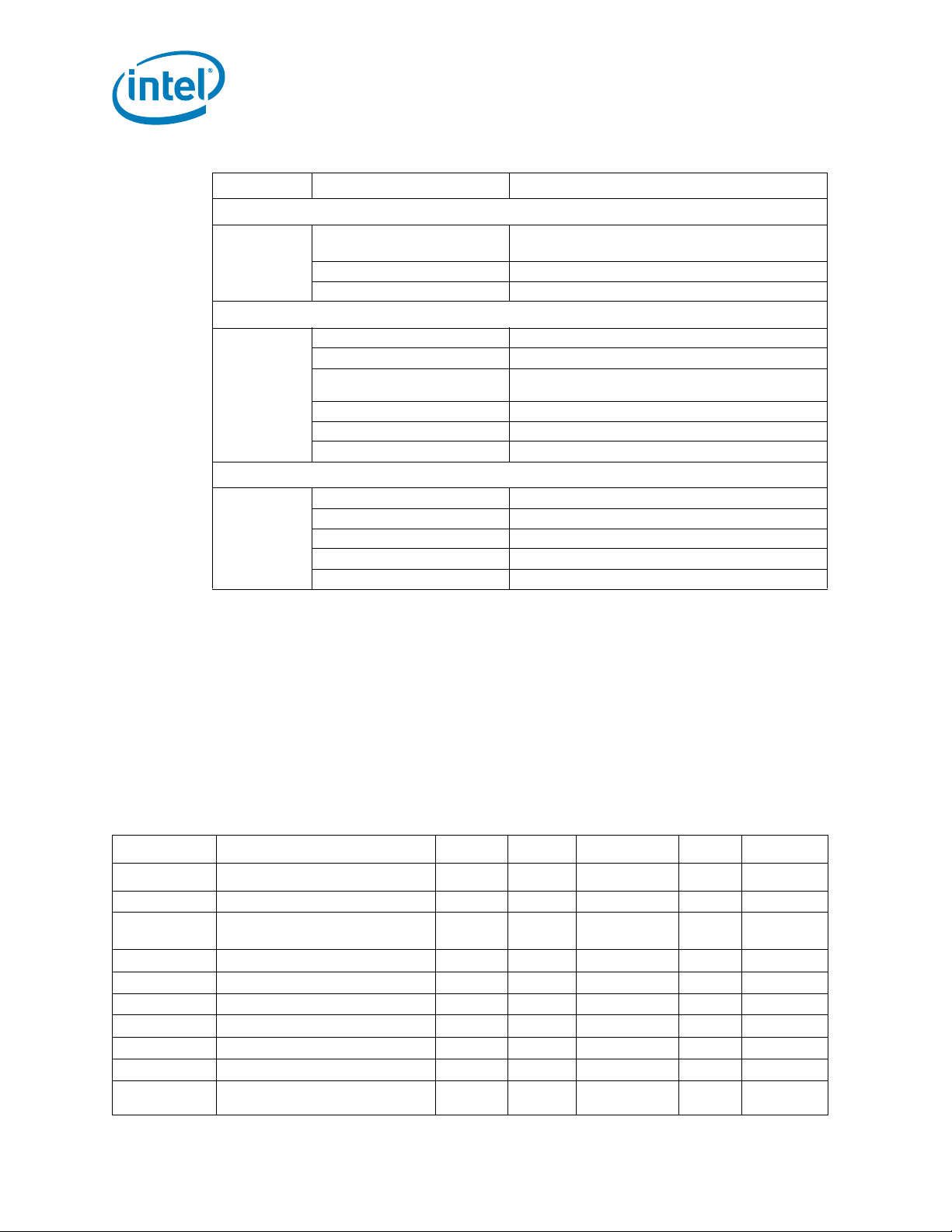

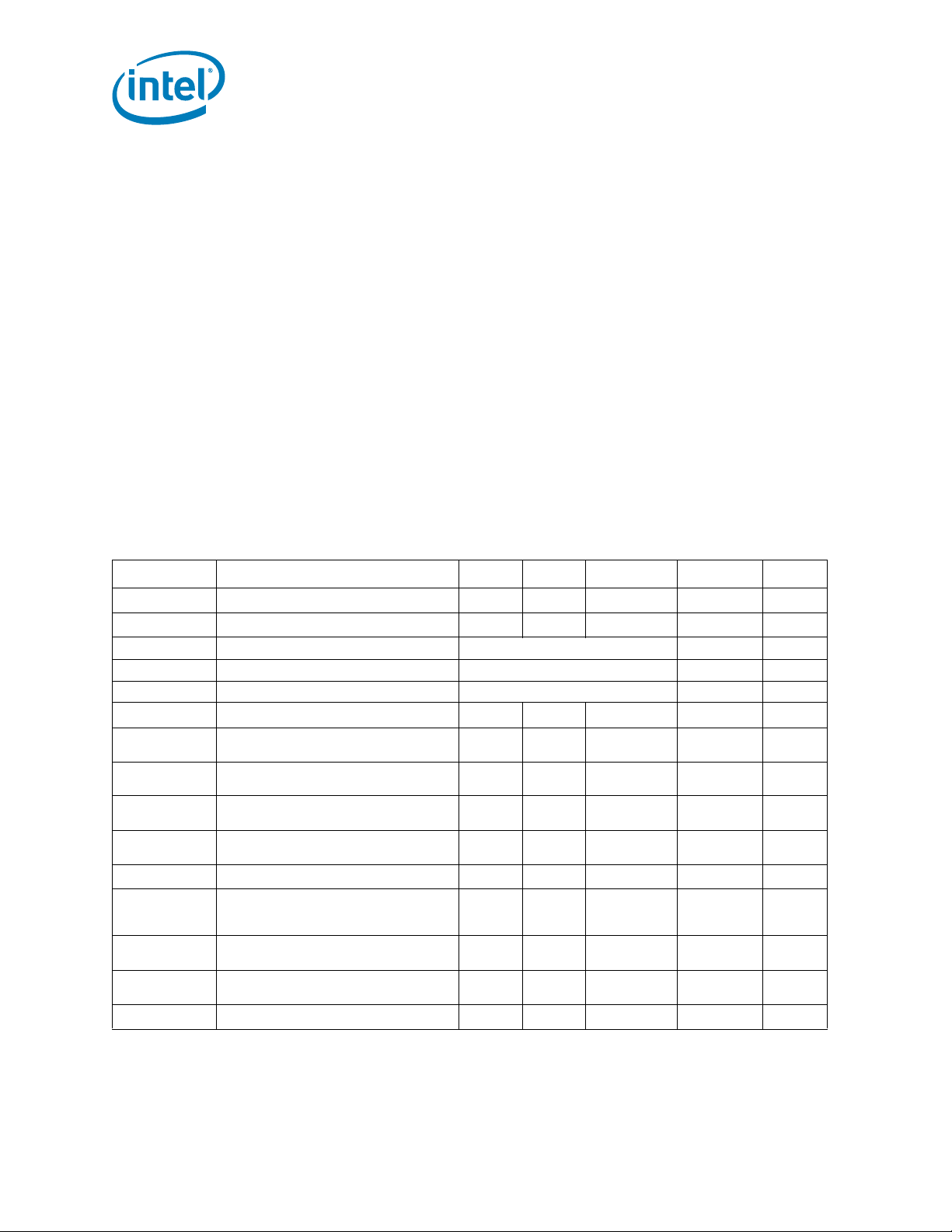

2.3 Reference Clocking Specifications

The processor has one input reference clock, SYSCLK/SYSCLK_N for the Intel® QPI

interface. The processor timing specified in this section is defined at the processor pins

unless otherwise noted.

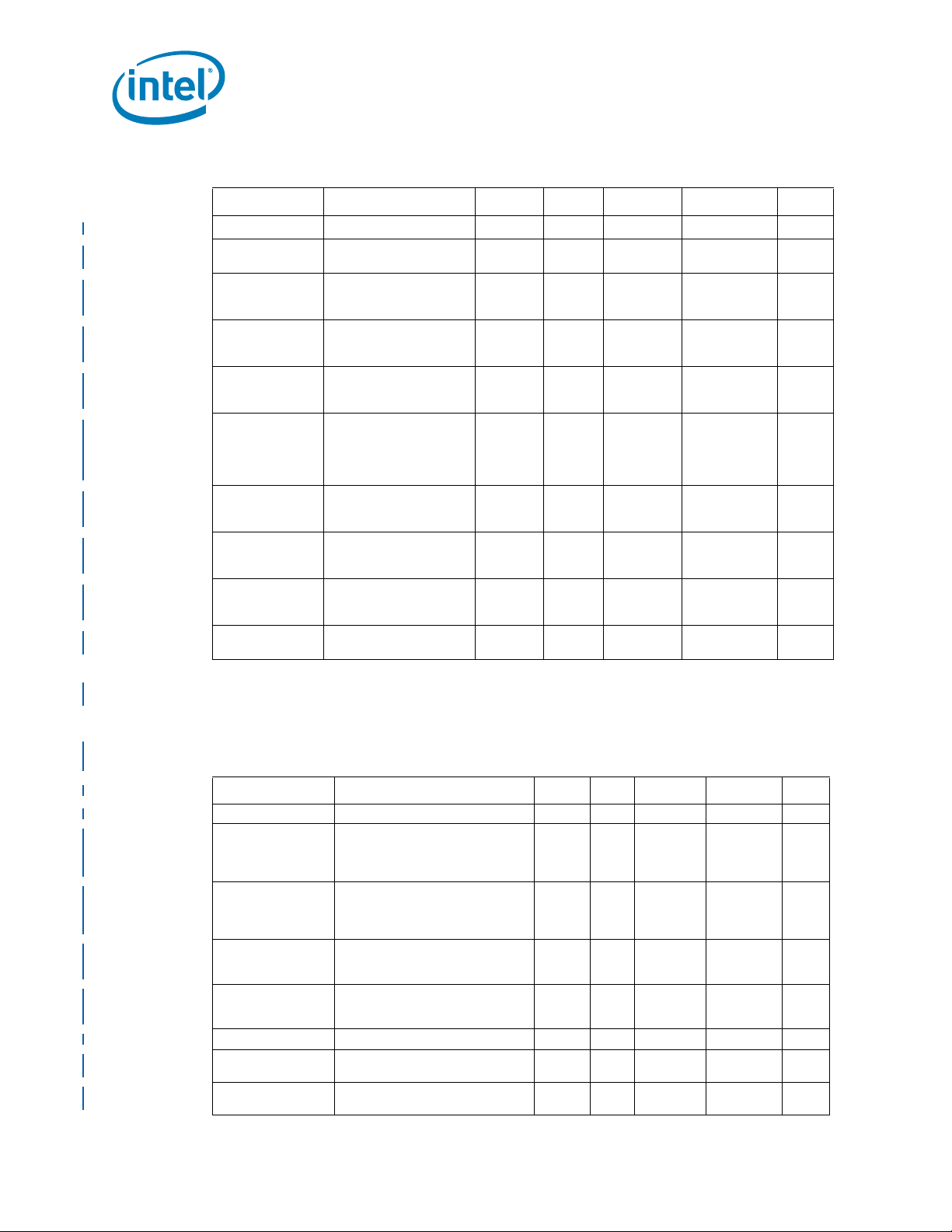

Table 2-3. Intel® QuickPath Interconnect/Intel® Scalable Memory Interconnect

Symbol Parameter Min Nom Max Units Notes

fsysclk (ssc-off) System clock frequency

Fsyclk (scc-on) System clock frequency 132.62 132.99 133.37 MHz

ER

sysclk-diff-Rise,

ER

sysclk-diff-Fall

T

sysclk_dutycycle

C

i-CK

VH Differential High Input Voltage 0.15 V 3

VL Differential Low Input Voltage -0.15 V 3

V

Cross

V

Cross_delta

V

RB-Diff

Reference Clock Specifications (Sheet 1 of 2)

133.31 133.33 133.34 MHz

Differential Rising and Falling Edge

Rates

Duty cycle of Reference clock 40 60 % period 3

Clock Input Capacitance 0.5 2.0 pf

Absolute crossing point 0.25 0.35 0.55 V 1, 5, 6

Peak-peak variation 140 mv 1, 5, 7

Differential Ringback voltage

threshold

1.0 4.0 V/ns 3,4

-100 100 mV 3, 10

26 Intel

®

Itanium® Processor 9300 Series and 9500 Series Datasheet

Page 27

Electrical Specifications

Table 2-3. Intel® QuickPath Interconnect/Intel® Scalable Memory Interconnect

Reference Clock Specifications (Sheet 2 of 2)

Symbol Parameter Min Nom Max Units Notes

T

Stable

T

REFCLK-JITTER-RMS-

ONEPLL

Note:

1. Measurement taken from single-ended waveform.

2. The given PLL parameters are: Underdamping (z) = 0.8 an d natural frequency = fn = 7.86E6 Hz; wn = 2 *fn. N_minUI = 12

for Intel

3. Measurement taken from differential waveform.

4. Measured from -150 mV to +150 mV on the differential waveform (derived from SYSCLK minus SYSCLK_N). The signal must

be monotonic through the measurement region for rise and fall time. The 300 mV measurement window is centered on the

differential zero crossing. See Figure 2-4.

5. Measured at crossing point where the instantaneous voltage value of the rising edge SYSCLK equals the falling edge

SYSCLK_N. See Figure 2-2.

6. Refers to the total variation from the lowest crossing point to the highest, regardless of which edge is crossing. Refers to all

crossing points for this measurement. See Figure 2-3.

7. Defined as the total variation of all crossing voltages of Rising SYSCLK and falling SYSCLK_N. This is the maximum allowed

variance in Vcross for any particular system. See Figure 2-2.

8. Defined as the maximum instantaneous voltage including overshoot. See Figure 2-2.

9. Defined as the minimum instantaneous voltage including undershoot. See Figure 2-2.

10. T

is the time the differential clock must maintain a minimum ±150 mV differential voltage after rising/falling edges

Stable

before it is allowed to droop back into the VRB ±100 mV range. See Figure 2-5.

Allowed time before ringback 500 ps 3, 10

Accumulated rms jitter over n UI of a

given PLL model output in response to

the jittery reference clock input. The

PLL output is generated by conv olving

the measured reference clock phase

jitter with a given PLL transfer

function. Here n=12.

®

QuickPath Interconnect 4.8 Gt/s channel.

0.5 ps 2

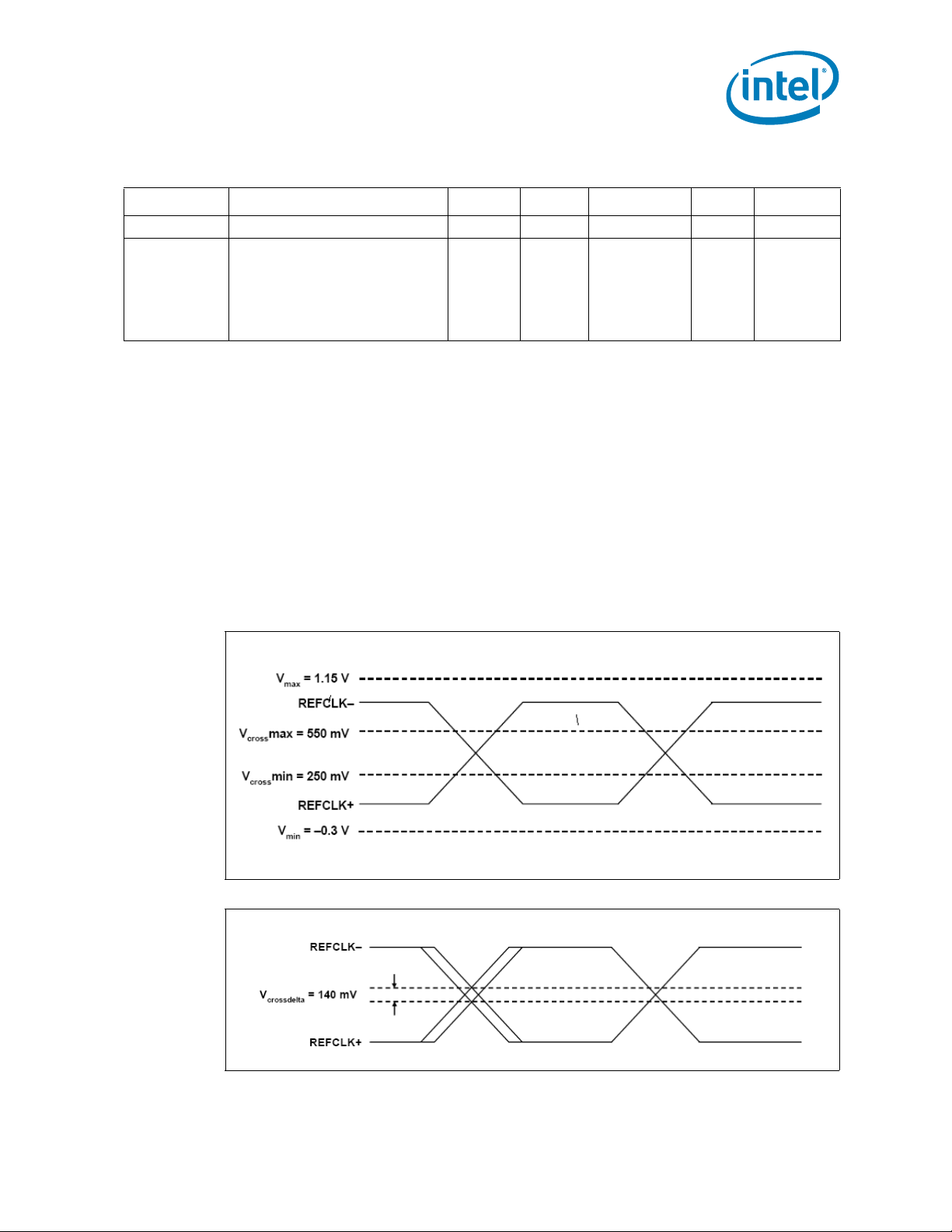

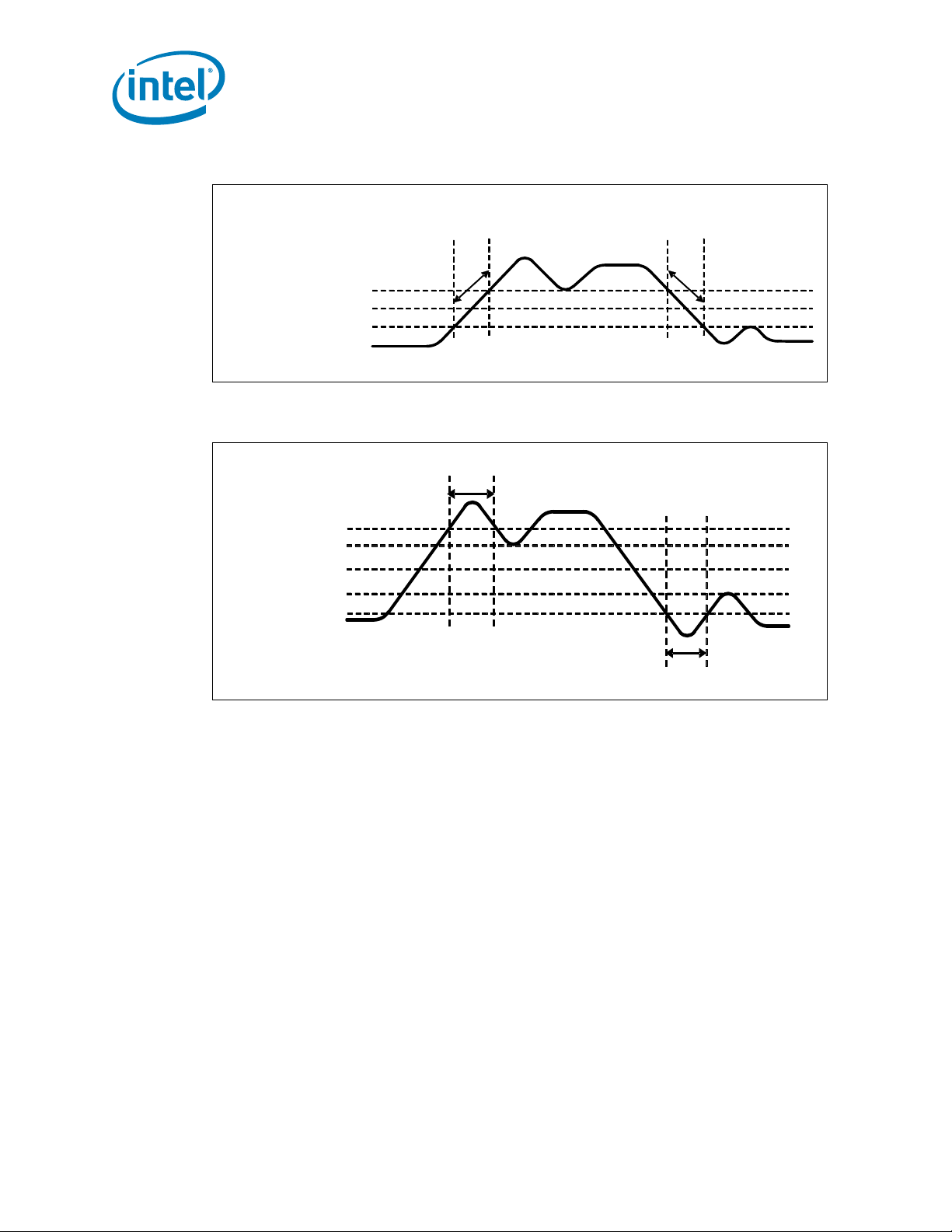

Figure 2-2. Single-ended Maximum and Minimum Levels and V

Figure 2-3. V

cross-delta

Definition

cross

Levels

Intel® Itanium® Processor 9300 Series and 9500 Series Datasheet 27

Page 28

Figure 2-4. Differential Edge Rate Definition

REFCLK

diff

ER

Refclk-diff-Fall

ER

Refclk-diff-Rise

V

Refclk-diff-ih

= 150 mV

V

Refclk-diff-il

= –150 mV

0.0 V

REFCLK

di ff

V

RB- di ff max

100 mV

0.0 V

V

RB-diff min

= – 100 mV

V

Ref cl k-diff-ih

= 150 mV

V

Ref cl k-diff-ih

= – 150 mV

T

Sta bl e

T

Stab le

Electrical Specifications

Figure 2-5. VRB and T

Stable

Definitions

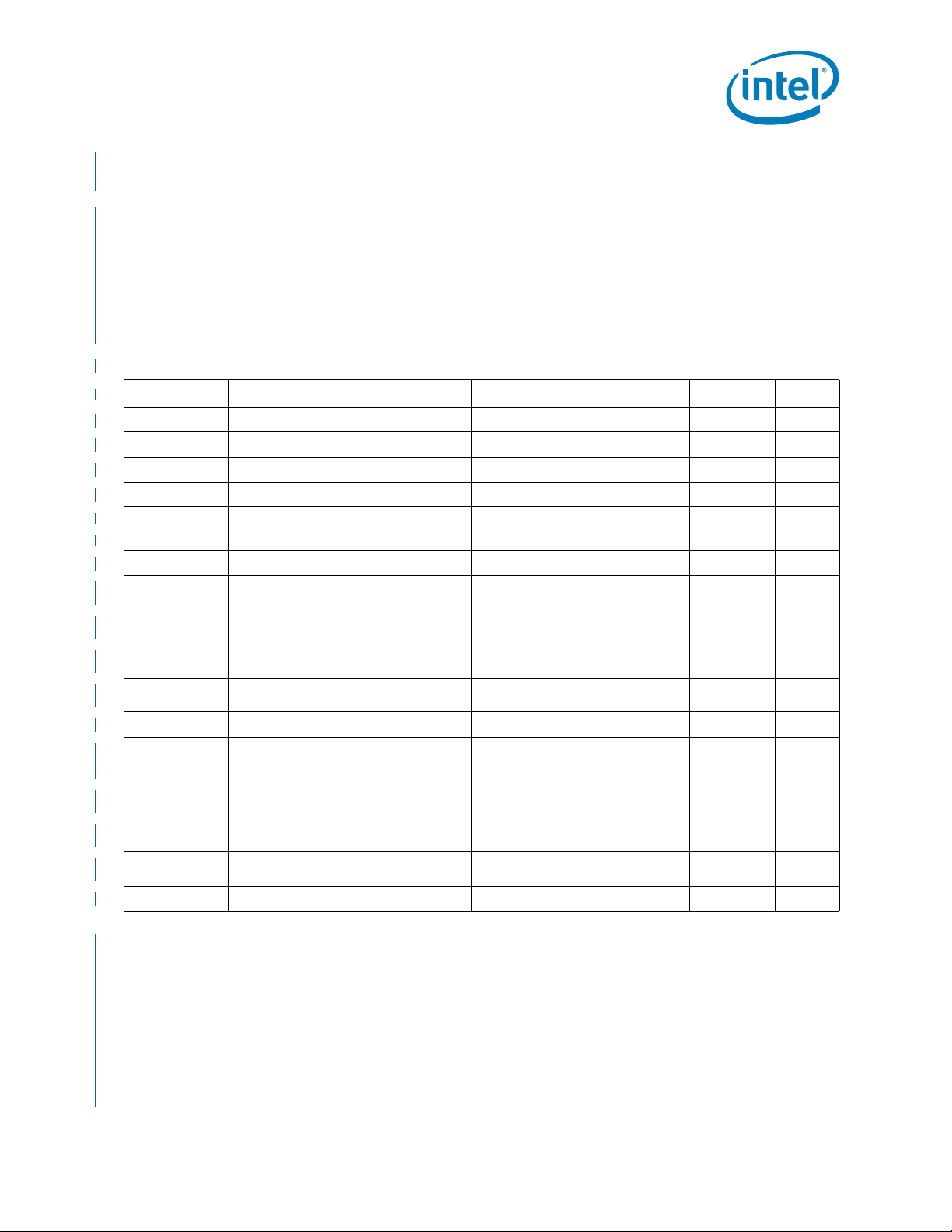

2.4 Intel® QuickPath Interconnect and Intel® SMI Signaling Specifications

.

2.4.1 Intel® Itanium® Processor 9300 Series Intel® QuickPath

Interconnect and Intel

The applicability of this section applies to Intel® QPI for the Intel® Itanium® Processor

9300 Series. This section contains information for Intel

(1/4 frequency of the reference clock) and processor’s normal operating frequency, 4.8

GT/s, for Intel

®

QPI and Intel® SMI.

®

SMI Specifications for 4.8 GT/s

®

QPI slow boot up speed

28 Intel

®

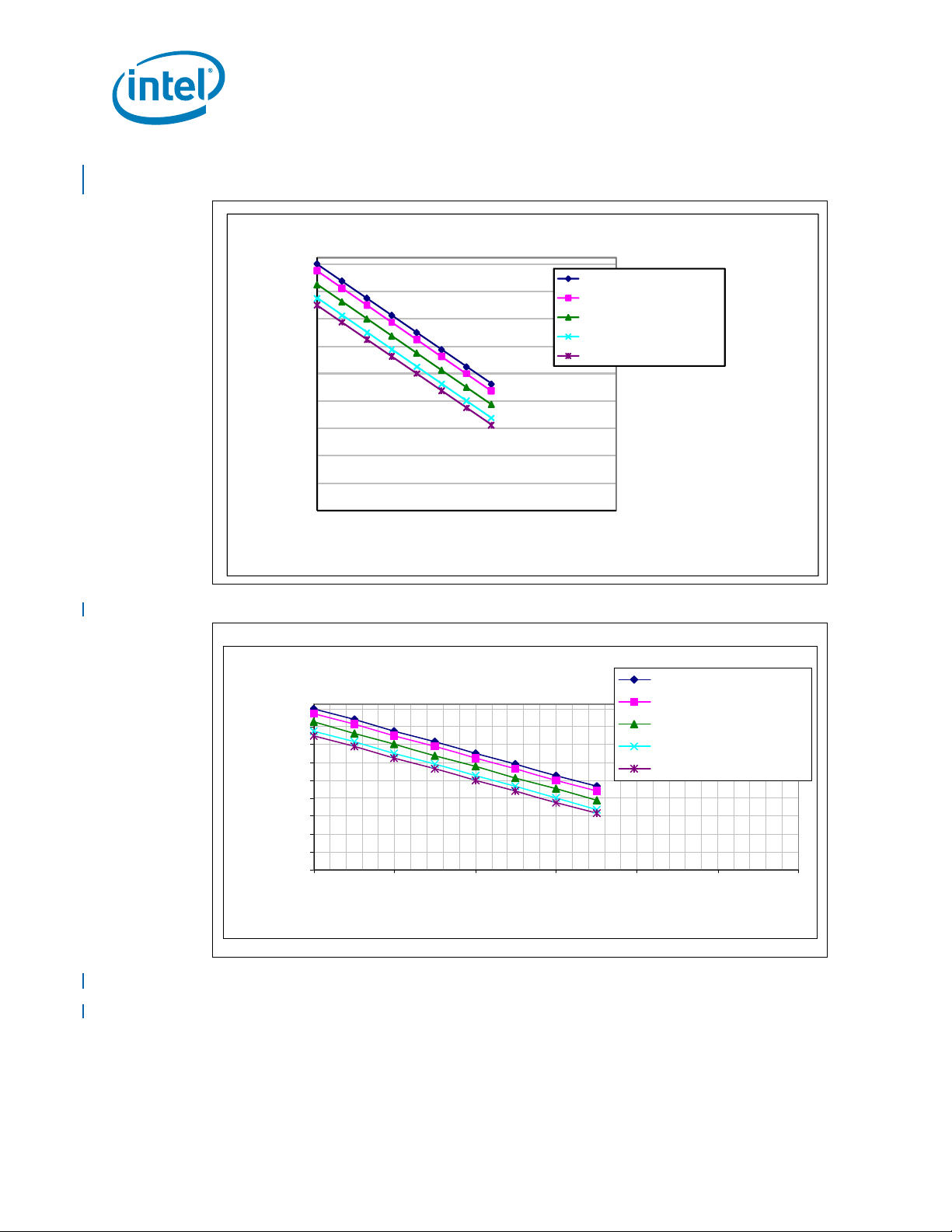

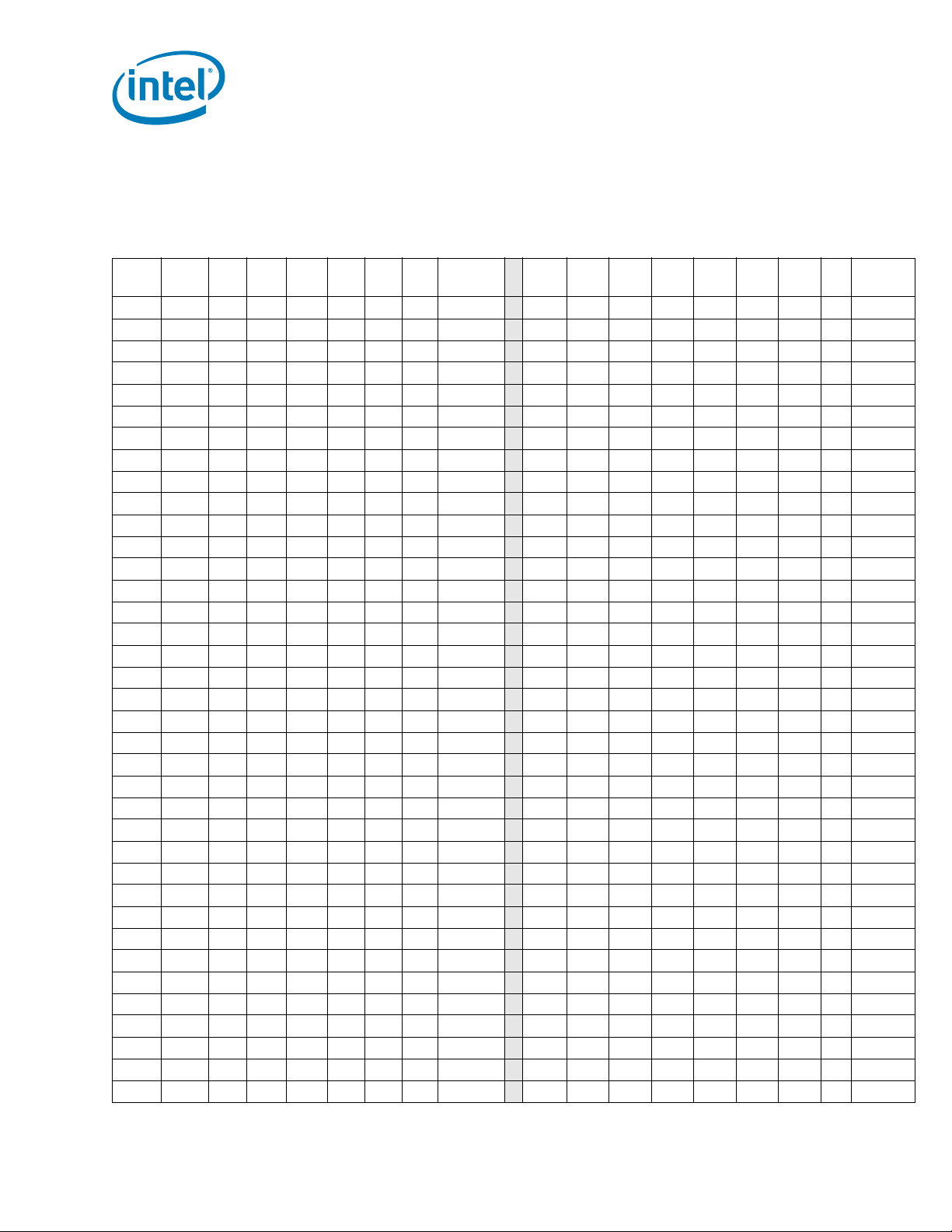

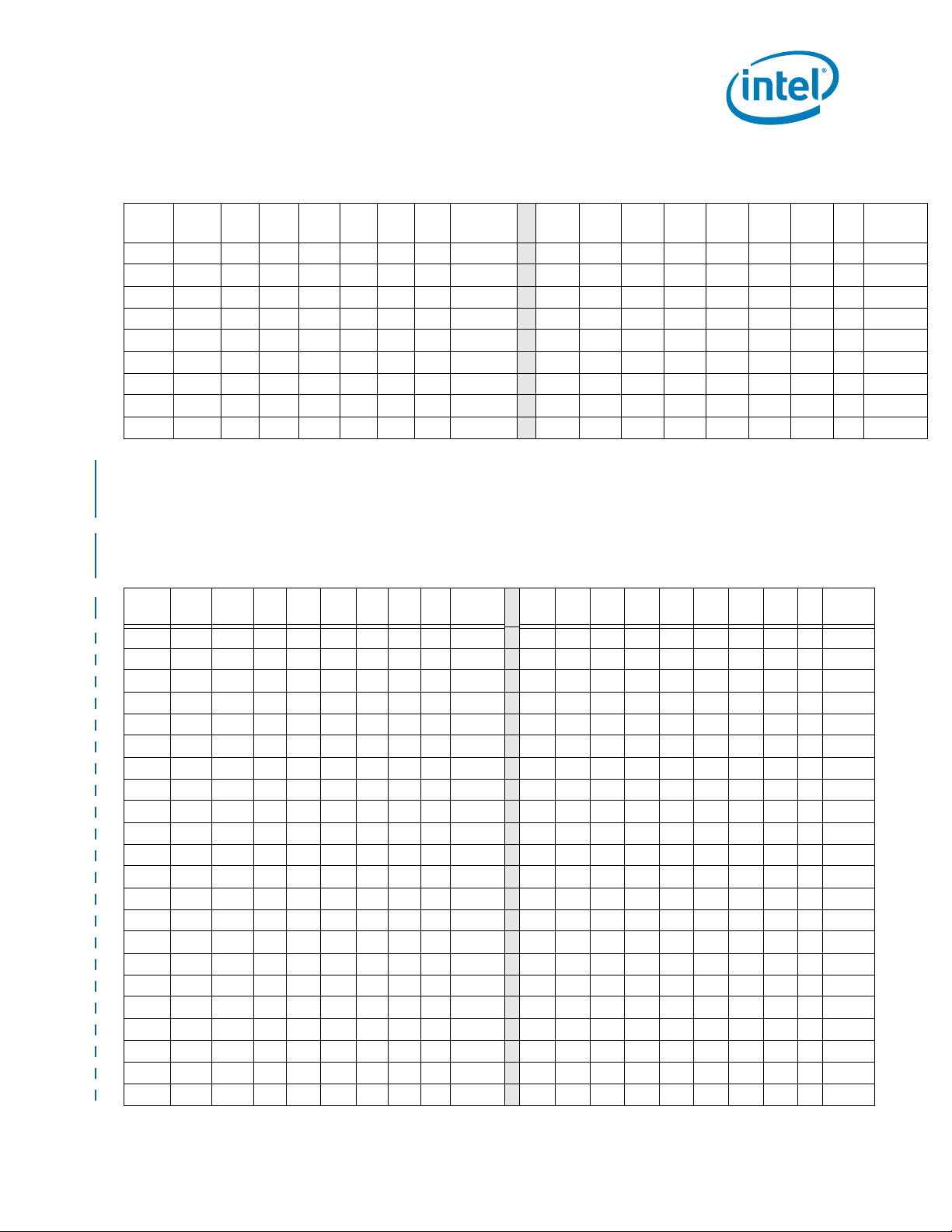

For Intel