Intel® Itanium® 2 Processor

Hardware Developer’s Manual

July 2002

Document Number: 251109-001

Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual

property rights is granted by this document. Except as provided in Intel’s Terms and Conditions of Sale for such products, Intel assumes no liability

whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to

fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not

intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Itanium 2 processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications.

Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling

1-800-548-4725 or by visiting Intel’s website at http://developer.intel.com/design/litcentr.

Intel and Itanium are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

Copyright © 2002, Intel Corporation. All rights reserved.

*Other names and brands may be claimed as the property of others.

I2C is a two-wire communication bus /protocol developed by Phillips. SMBus is a subset of the I2C bus/protocol developed by Intel. Implementation of

the I2C bus/protocol or the SMBus bus/protocol may require licenses from various entities, including Phillips Electronics, N.V. and North American

Phillips Corporation.

ii Intel® Itanium® 2 Processor Hardware Developer’s Manual

Contents

1 Introduction......................................................................................................................1-1

1.1 Itanium

1.2 Processor Abstraction Layer..............................................................................1-1

1.3 Terminology........................................................................................................1-2

1.4 Reference Documents........................................................................................1-2

2 Itanium

2.1 Overview ............................................................................................................2-1

2.2 Instruction Processing........................................................................................2-4

2.3 Execution............................................................................................................2-5

2.4 Control ................................................................................................................2-8

2.5 Memory Subsystem............................................................................................2-8

2.6 IA-32 Execution ................................................................................................2-11

1.4.1 Revision His tor y.......................... .......... ................ .......... ................ ......1-3

®

2.1.1 6-Wide EPIC Core................... ................ .......... ......... ................. ......... .2-1

2.1.2 Processor Pipeline................................................................................2-2

2.1.3 Processor Block Diagram......................................................................2-3

2.2.1 Instructi o n Pre fe tch a nd Fetch ................ .......... ................ .......... ..........2-4

2.2.2 Branch Prediction........................ .......... ................ .......... ................ ......2-5

2.2.3 Dispersal Logic......................................................................................2-5

2.3.1 Floating- Po int Unit (FPU)........................ .......... ................ .......... ..........2-5

2.3.2 Integer Logic. .......... ................. ......... ................. ................ .......... ..........2-6

2.3.3 Register Files ........................................................................................2-6

2.3.4 Register Stack Engine (RSE)................................................................2-7

2.5.1 L1 Instruction Cache.............................................................................2-9

2.5.2 L1 Data Cache ......................................................................................2-9

2.5.3 Unified L2 Cache......................... .......... ................ .......... ................ ......2-9

2.5.4 Unified L3 Cache......................... .......... ................ .......... ................ ......2-9

2.5.5 The Advanced Load Add re ss Tab le (AL AT)........ ................ .......... ........2-9

2.5.6 Translation Lookas ide Buffers (TLBs).. ...............................................2-10

2.5.7 Cache Coheren cy ................................................................................2-10

2.5.8 Write Coalescing.................................................................................2-10

2.5.9 Memory Ordering ................................................................................2-11

®

2 Processor System Bus......... ......... ................. ......... ................. ........1-1

2 Processor Microar ch i te c tu re.. ................. ......... ................. ......... ................. ...2-1

3 System Bus Overvie w........................ ................. ......... ................. ......... ................. ........3-1

3.1 Signaling on the Itanium

3.1.1 Common Clock Signaling............ .......... ................ ................. ......... ......3-1

3.1.2 Source Synchro n ous Si g n al i n g.......... ................. ................ .......... ........3-2

3.2 Signal Overview ......................................................................................... ....... .3-3

3.2.1 Control Signals......................................................................................3-4

3.2.2 Arbitrat ion Signals................ .......... ................ ................. ......... .............3-4

3.2.3 Reque st Signals ....................................................................................3-5

3.2.4 Snoop Signal s .......................................................................................3-5

3.2.5 Response S igna ls .................................................................................3-6

3.2.6 Data Signals................................................................. ....... ............ ......3-7

3.2.7 Defer Signal s........................ .......... ................ .......... ................ .............3-8

3.2.8 Error Signals..........................................................................................3-8

3.2.9 Execution Cont r o l Sig nals........... .......... ................ .......... ................ ......3-9

Intel® Itanium® 2 Processor Hardware Developer’s Manual iii

®

2 Processor System Bus..........................................3-1

3.2.10 IA-32 Compatibility Signals ...................................................................3-9

3.2.11 Platform Signal s........ ......... ................. ......... ................. ................. .....3-10

3.2.12 Diagnostic Signals . ..............................................................................3-10

4 Data Integri ty...................... .......... ................ .......... ................ ................. ......... ...............4-1

4.1 Error Classification.............................................................................................4-1

4.2 Itanium

®

2 Processor System Bus Error Detection............................................4-1

4.2.1 Bus Signals Protected Directly..............................................................4-2

4.2.2 Bus Signals Protected Indirectly . ..........................................................4-2

4.2.3 Unprotected Bus Signals.......................................................................4-3

4.2.4 Itanium

®

2 Processor System Bus Error Code Algorithms ...................4-3

5 Configuration and Initialization........................................................................................5-1

5.1 Configuration Overview......................................................................................5-1

5.2 Configuration Features.......................................................................................5-1

5.2.1 Data Bus Error Checki n g ............. ................ .......... ................ .......... .....5-2

5.2.2 Response/ID Signal Parity Error Checking ...........................................5-2

5.2.3 Address/Reque st Signal Parity Error Checking.....................................5-3

5.2.4 BERR# Assertion for Initiator Bus Errors.............................................. 5-3

5.2.5 BERR# Assertio n for Tar g e t Bu s Err o rs....... .......... ......... ................. .....5-3

5.2.6 BERR# Sampling ..................................................................................5-3

5.2.7 BINIT# Error Assertion..........................................................................5-3

5.2.8 BINIT# Error Sampling..........................................................................5-3

5.2.9 In-Order Queue Pipelining ................................................................. ...5-3

5.2.10 Request Bus Parking Enabled ..............................................................5-3

5.2.11 Symmetric Agent Arbitration ID.............................................................5-4

5.2.12 Clock Frequency Ratios .................................... ....... ....... ..... ....... ....... ...5-5

5.3 Initialization Overview ........................................................................................5-6

5.3.1 Initialization with RESET#.....................................................................5-6

5.3.2 Initialization with INIT............................................................................5-6

6 Test Access Port (TAP)...................................................................................................6-1

6.1 Interface.............................................................................................................6-2

6.2 Accessing The TAP Logic..................................................................................6-2

6.3 TAP Registers................. ................ ................. ......... ................. ......... ...............6-4

6.4 TAP Instructions.............. ......... ................. ......... ................. ................ .......... .....6-4

6.5 Reset Behavior . ..................................................................................................6-5

7 Integration Tools .............................................................................................................7-1

7.1 In-Target Probe (ITP)................................................................... ..... ....... ....... ...7-1

7.2 Logic Analyzer Interface (LAI)............................................................................ 7-1

A Signals Reference..........................................................................................................A-1

A.1 Alphabetical Signals Reference ........................................................................A-1

A.1.1 A[49:3]# ( I/O)........... ......... ................. ......... ................. ................ .........A-1

A.1.2 A20M# (I) ........ ................. .......... ................ ................. ......... ................A-1

A.1.3 ADS# (I/O) ............................................................................................A-1

A.1.4 AP[1:0]# (I/O)....................................................................................... A-1

A.1.5 ASZ[1:0]# (I/O).......... ......... ................. ................. ......... ................. ......A-1

A.1.6 ATTR[3:0] # (I/O)........................... ......... ................. ......... ................. .... A-2

A.1.7 BCLKp/BCLKn (I).................................................................................A-2

A.1.8 BE[7:0]# (I/O)....................................................................................... A-3

iv Intel® Itanium® 2 Processor Hardware Developer’s Manual

A.1.9 BERR# (I/O)................ ......... ................. ......... ................. ................ .....A-3

A.1.10 BINIT# (I/O)....... ................. ................ .......... ................ .......... ..............A-4

A.1.11 BNR# (I/O)............................................................................................A-4

A.1.12 BPM[5:0]# (I/O) ....................................................................................A-4

A.1.13 BPRI# (I)...............................................................................................A-4

A.1.14 BR[0 ]# (I/O) and BR[3:1]# (I)................................................................A-4

A.1.15 BREQ[3:0]# (I/O)..................................................................................A-5

A.1.16 CCL# (I/O) ............................................................................................A-6

A.1.17 CPUPRES# (O)....................................................................................A-6

A.1.18 D[127:0]# (I/O).................................. .. ..... .. .......... .. ..... .. ....... ..... ..... .. .....A-6

A.1.19 D/C# (I/O)............... ................. ......... ................. ......... ................. .........A-6

A.1.20 DBSY# (I/O).................... .......... ................ ................. ......... .................A-6

A.1.21 DBSY_C1# (O)................... ................ .......... ................ .......... ..............A-6

A.1.22 DBSY_C2# (O)................... ................ .......... ................ .......... ..............A-6

A.1.23 DEFER# (I)........................................................................................... A-7

A.1.24 DEN# (I/O)............................................................................................A-7

A.1.25 DEP[15:0]# (I/O)...................................................................................A-7

A.1.26 DHIT# (I)...............................................................................................A-7

A.1.27 DPS# (I/O)................... ................ .......... ................ ................. ......... .....A-8

A.1.28 DRDY# (I/O).........................................................................................A-8

A.1.29 DRDY_C1# (O) ....................................................................................A-8

A.1.30 DRDY_C2# (O) ....................................................................................A-8

A.1.31 DSZ[1:0]# (I/O).....................................................................................A-8

A.1.32 EXF[4:0]# (I/O).....................................................................................A-8

A.1.33 FCL# (I/O)............................ .......... ................ ................. ......... ............A-9

A.1.34 FERR# (O)...........................................................................................A-9

A.1.35 GSEQ# (I).............................................................................................A-9

A.1.36 HIT# (I/O) and HITM# (I/O) ..................................................................A-9

A.1.37 ID[9:0]# (I).......................... ......... ................. ......... ................. ..............A-9

A.1.38 IDS# (I)......... .......... ................. ................ .......... ................ ................. ..A-9

A.1.39 IGNNE# (I)............................................................................................A-9

A.1.40 INIT# (I)................ ................ .......... ................ ................. ......... ............A-9

A.1.41 INT (I).................................................................................................A-10

A.1.42 IP[1:0]# (I)............... ......... ................. ................. ......... ................. .......A-10

A.1.43 LEN[2:0]# (I/O)...................................................................................A-10

A.1.44 LINT[1:0] (I)........................................................................................A-10

A.1.45 LOCK# (I/O) .... ......... ................. ......... ................. ......... ................. .....A-10

A.1.46 NMI (I)................................................................................................A-11

A.1.47 OWN# (I/O) ..................... ................. ......... ................. ......... ...............A-11

A.1.48 PMI# (I)...............................................................................................A-11

A.1.49 PWRGOOD (I).................................................................................... A-11

A.1.50 REQ[5:0]# (I/O) ..................................................................................A-11

A.1.51 RESET# (I).........................................................................................A-12

A.1.52 RP# (I/O)............................................................................................A-12

A.1.53 RS[2:0]# (I).........................................................................................A-13

A.1.54 RSP# (I)...... .......... ................ ................. ......... ................. ......... ..........A-13

A.1.55 SBSY# (I/O)........................................................................................A-13

A.1.56 SBSY_C1# (O)................ .......... ................ ................. ......... ...............A-13

A.1.57 SBSY_C2# (O)................ .......... ................ ................. ......... ...............A-13

A.1.58 SPLCK# (I/O)............................ ................ ................. ......... ...............A-13

A.1.59 STB n[7:0 ]# and STBp[7:0 ]# (I/O) ....................................................... A-14

Intel® Itanium® 2 Processor Hardware Developer’s Manual v

Figures

A.1.60 TCK (I).................. ................. ......... ................. ......... ................. .........A-14

A.1.61 TDI (I)...................... ................ .......... ................ ................. ......... .......A-14

A.1.62 TDO (O) ........ .......... ................ ................. ......... ................. ................A-14

A.1.63 THRMTRIP# (O).......... ................. ......... ................. ......... ................. ..A-14

A.1.64 THRMALERT# (O).............................................................................A-15

A.1.65 TMS (I)........................... ................ .......... ................ .......... ................A-15

A.1.66 TND# (I/O).......................................................................................... A-15

A.1.67 TRDY# (I)...........................................................................................A-15

A.1.68 TRST# (I) ........ ................. .......... ................ .......... ................ ..............A-15

A.1.69 WSNP# (I/O).................. ................ ................. ......... ................. .........A-15

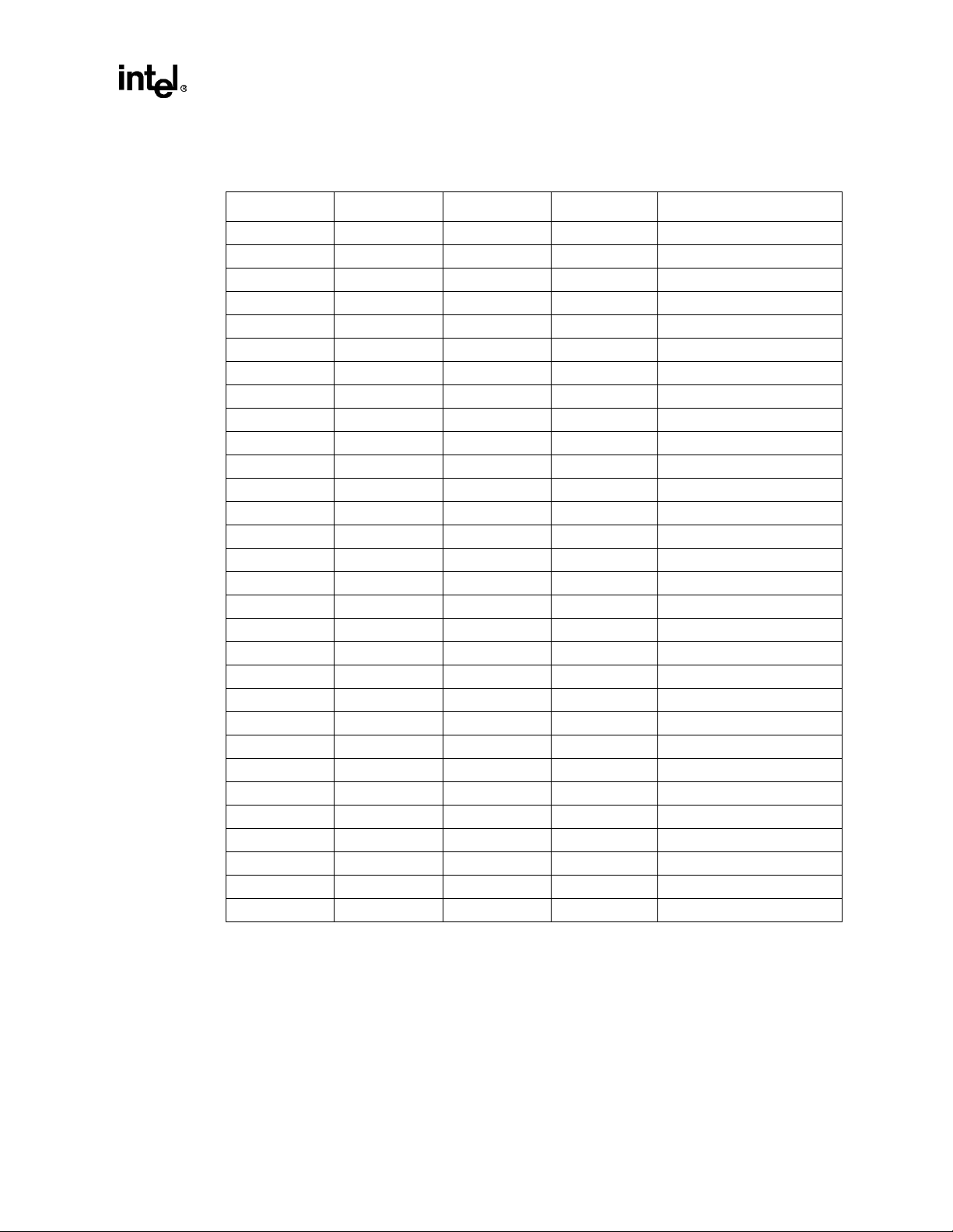

A.2 Signal Summaries...........................................................................................A-15

Tables

2-1 Two Exampl es Illustrating Supported Parallelism ..............................................2-2

2-2 Itanium

2-3 Itanium

2-4 Itanium

2-5 Itanium

®

2 Processor Core Pipeline...................................................................2-3

®

2 Processor Block Diagram.................................................................2-4

®

2 Processor FMAC Units.....................................................................2-6

®

2 Processor Cache Hierarchy .............................................................2-8

3-1 Com mon Clock Latched Protocol.......................................................................3-2

3-2 Source Synchronous Latched Protocol........................................ ....... ............ ...3-3

5-1 BR[3:0]# Physical Interconnection with Four Symmetric Agents .......................5-4

5-2 BR[3:0]# Physical Interconnection with Two Symmetric Agents........................5-5

6-1 Test Access Port Block Diagram........................................................................6-1

6-2 TAP Controller State Diagram............ ................ .......... ................ .......... ............6-2

3-1 Control Signal s..................... ................ ................. ......... ................. ......... .........3-4

3-2 Arbitration Signals ............................................................................................. 3-4

3-3 Request Signals................................................................................................3-5

3-4 Snoop Signals ................................................................................................... 3-5

3-5 Respons e Signals ... ..........................................................................................3-6

3-6 Data Signals.................... ................ ................. ......... ................. ................. ...... 3-7

3-7 STB p[7:0]# and STB n[7:0]# Associations ......................................................... 3-7

3-8 Defer Signals.....................................................................................................3-8

3-9 Error Signals ..................................................................................................... 3-8

3-10 Execution Control Signals.................................................................................3-9

3-11 Platform Signals................... ......... ................. ................ .......... ................ ....... 3-10

3-12 Diagnostic Signals ........................................................................................... 3-10

4-1 Direct Bus Signal Protection ............................................................................. 4-2

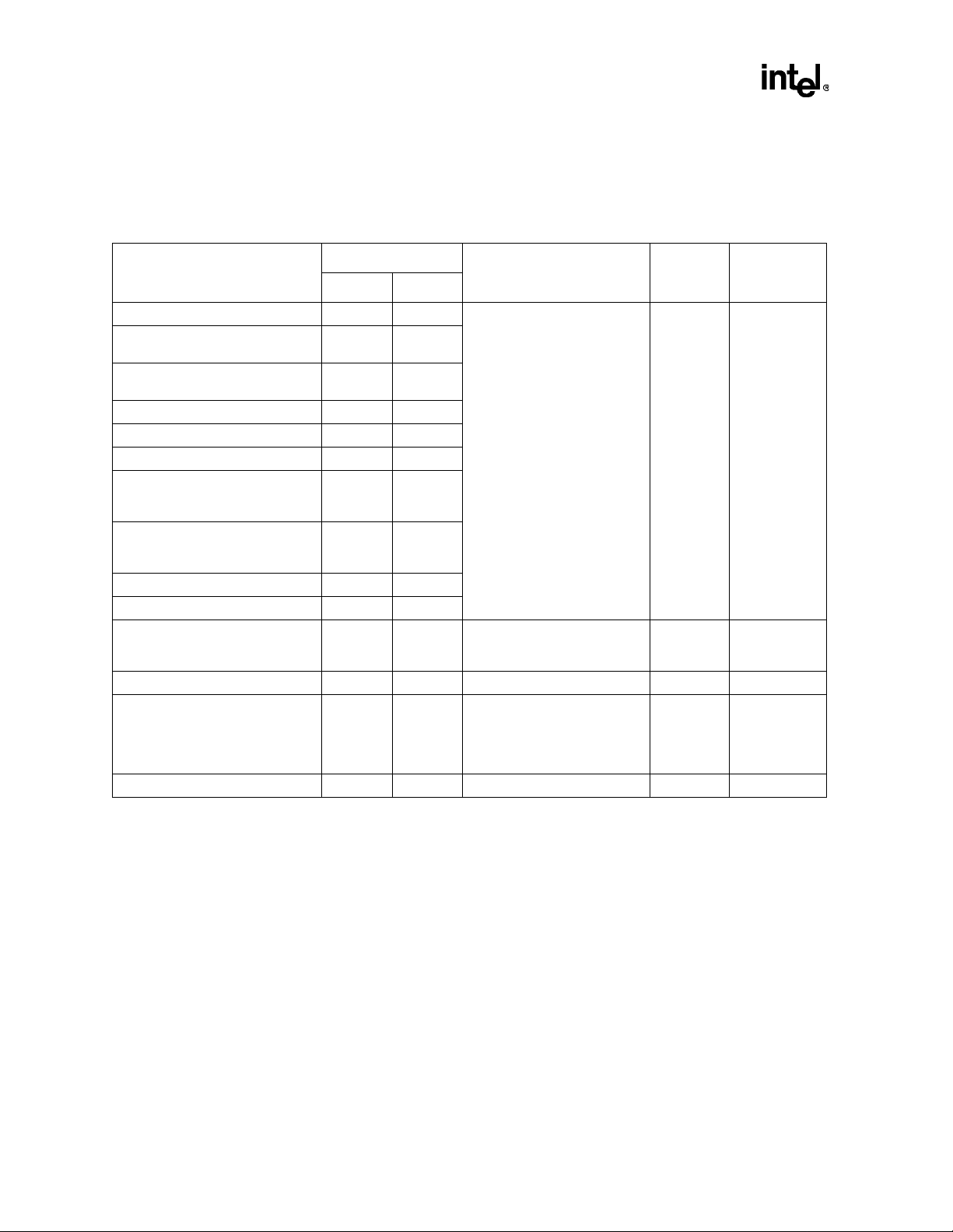

5-1 Power-On Configuration Features .................................................................... 5-2

5-2 Itanium

5-3 Itanium

®

2 Processor Bus BREQ[3:0]# Interconnect (4-Way Processors) ....... 5-4

®

2 Processor Bus BREQ[3:0]# Interconnect (2-Way Processors) ....... 5-4

5-4 Arbitration ID Configuration............................................................................... 5-5

5-5 Itanium

5-6 Itanium

5-7 Itanium

6-1 Instructions for the Itanium

®

2 Processor System Bus to Core Frequency Multiplier Configuration 5-5

®

2 Processor Reset State (after PAL)............... ................. ................ ..5-6

®

Processor INIT State............. .......... ................ .......... ................ .........5-6

®

2 Processor TAP Control l e r.......... ......... .............. 6-4

vi Intel® Itanium® 2 Processor Hardware Developer’s Manual

A-1 Address Space Size............ ......... ................. ......... ................. ................. .........A-2

A-2 Effective Memo ry Type Signal Encoding.. ................. ......... ................. ......... .....A-2

A-3 Special Transaction Encoding on Byte Enables................................................A-3

A-5 BR0# (I/O), BR1#, BR2#, BR3# Signals for 2P Rotating Interconnect.............. A-5

A-4 BR0# (I/O), BR1#, BR2#, BR3# Signals for 4P Rotating Interconnect.............. A-5

A-6 BR[3:0]# Signals and Agent IDs........................................................................A-5

A-7 DID[9:0]# En co din g........ ................. ......... ................. ......... ................. ..............A-7

A-8 Extended Function Signals................................................................................A-8

A-9 Length of Data Transfers.................................................................................A-10

A-10 Transaction Types Defined by REQa#/REQb# Signal s ..................................A-12

A-11 STBp[7:0]# and STBn[7:0]# Associatio ns .......................................................A-14

A-12 Output Signals................................................................................................. A-15

A-13 Input Signals....................................................................... .............. ...............A-16

A-14 Input/Output Signals (Single Driver)................................................................ A-17

A-15 Input/Output Signals (Multiple Driver) .............................................................A-18

Intel® Itanium® 2 Processor Hardware Developer’s Manual vii

viii Intel® Itanium® 2 Processor Hardware Developer’s Manual

Introduction 1

The Intel® Itanium® 2 processor, the second in a family of processors based on the Itanium

archit ecture , is de si gn e d to ad d r ess the need s of h igh - pe r f o rm an c e ser v er s an d wo rk s t at io n s. The

Itanium archite cture goes beyond RISC and CISC approaches by employing Explicit ly P arallel

Instruction Computin g (EP I C) , which pairs ex tensive processing resources with intelligent

compilers that enable parallel execution explicit to the processor. Its large internal resources

combine with pre dic atio n and s pecul ation to e nable opt imizat ion for hi gh perfo rmance a ppli cati ons

running on multiple operating systems, including versions of Micro soft Windows*, HP-UX* and

Linux*. The Itanium 2 processor is designed to support very large scal e s ystems, including thos e

employing thousands of processors, to provide the processing power and performance head room

for the most dem anding e nterpri se a nd tech nic al comput ing a pplic ations . SMBus compa tibili ty a nd

comprehensive reliability, availability and servic ea bility (RAS) features make the It anium 2

processor ideal for applicat ions requiring high up-time. For high performance servers and

workstations, the Itanium 2 processor offers outs tanding performance and relia bility for today’s

applications and the scalability to address the growing e-business needs of tomorrow.

1.1 Itanium® 2 Processor System Bus

Most Itanium 2 processor signals us e the Itanium process or’s Assisted Gunning Transceiver Logic

(AGTL+) signaling technology. The termination voltage, V

and is the system bus high reference voltage. The buf fers that drive most of the system bus signals

on the Itanium 2 processor are actively driven to V

improve rise times and reduce noise. These sign als should still be considered open-drain and

require termination to V

the Itani um 2 syst em bus is te rmina te d to V

at each end of the bus. There is also support of off-die termination in whi ch case the termination is

provided by external resistors connected to V

which provides the high lev el. When on-d ie termina tion is enable d,

CTERM

through acti ve term inati on within the bus age nts

CTERM

CTERM

during a low-to-high transition to

CTERM

.

, is generated on the bas eboard

CTERM

AGTL+ inputs use dif f erential receiver s which require a reference signal (V

the recei vers to determine if a signal is a logical 0 or a logical 1. The Itanium 2 processor generates

on-die, thereby eliminating the need for an off-chip reference voltag e s ource.

V

REF

REF

). V

is used by

REF

1.2 Processor Abstraction Layer

The Itanium 2 processor requires implementat ion-specific Processor Abstraction Layer (P AL)

firmware. PAL firm ware support s proc essor in itial izat ion, e rror recov ery, and othe r funct ionali ty. It

provides a consistent interface to system firmware and operating systems across processor

hardware implementations. The Intel

Vo lume 2: System Architecture, de sc r ibes PAL. Platforms must provide access to the firmware

address space and PAL at reset to allow Itanium 2 processors t o initialize .

The System Abstraction Layer (SAL) firmware contains platform-specific firmware to initialize

the platform, boot to an operating system, and provide runtime functionality. Further information

about SAL is available in the It anium Processor Family System Abstract ion L ayer Specification.

Intel® Itanium® 2 Processor Hardware Developer’s Manual 1-1

®

Itanium™ Architecture Softwar e Dev eloper’s Manual,

Introduction

1.3 Terminology

In this document, a ‘#’ symbol after a signal name refers to an active low signal. This means that a

signa l is in the activ e s ta t e (b ased on th e n a m e of the signal) when dr i ve n to a low le v el . F or

example, when RESET# is low, a processor res et has been requested. When NMI is high, a non maskable interrupt has occurred. In the case o f lines where the name does not imply a n active state

but describes part of a binary sequence (such as address or data), the ‘#’ symbol implies that the

signal is inverted. For example, D[3:0] = ‘HLHL’ refers to a hex ‘A’, and D [3:0] # = ‘LHLH’ also

refers to a hex ‘A’ (H = High logic level, L = Low logic level).

In many cases, signa ls are mappe d one -to-one t o physic al pin s with th e same n ames. In othe r cases,

diffe r ent signals are mapped onto the s ame pin. For example, this is th e ca se with the address pins

A[49:3]#. During the first clock, the addres s pi ns are asserted indicating a valid address. The first

clock is indica ted by the lower case a, or just the pin na me its elf: Aa[49:3]# or A[49:3]#. During

the second clock, other information is asserted on the address pins. These si gnals are referenced

either by their functional signal names, such as DID[9:0]#, or by using a lower case b with the pin

name, such as Ab[25:16]#. Note also that several pins have configuration functions at the asserted

to deasserted edge of RESET#.

The term “system bus” refers to the interface between the processor, system core logic and other

bus agents. The s ystem bus is a multiproce ssing inter face to processors , memory and I / O .

A signal name has all capitalized letters, e.g. VCTERM.

A symbol referring to a vol tage level, current le vel, or a time value carries a plain subscript, e.g.

V

, or a capitalized abbreviated subscript, e.g. TCO.

CC,core

1.4 Reference Documents

The reader of this specification should also b e fa mi liar with material and concepts prese nted in the

following doc um ents:

Title Document Number

®

Intel

Itanium® 2 Processor at 1.0 GHz and 900 MHz Datasheet 250945

®

Itanium® 2 Processor Specificat ion Update 251141

Intel

®

Itanium™ Architecture Software Developer’s Manual

Intel

• Volume 1: Application Architecture

• Volume 2: System Architecture

• Volume 3: Instruction Set Reference

®

Itanium® 2 Processor BSDL Model

Intel

®

Itanium® 2 Processor Refe rence Manu al for Software D evelopment and

Intel

Optimization

®

Intel

Itanium™ Processor Family System Abstraction Layer Specification 245359

®

Itanium™ Processor Family Error Handling Guide 249278

Intel

ITP700 Debug Port Design Guid e 249679

System Management Bus Specification http://www.smbus.org/specs

245317

245318

245319

251110

Contact your Inte l representative or ch eck http://developer.intel.com for the latest revision of the

reference documents.

1-2 Intel® Itanium® 2 Process or Hard ware Develop er’s Manual

1.4.1 Revision History

Introduction

Version

Number

001

Description Date

Initial release of this document. July 2002

Intel® Itanium® 2 Processor Hardware Developer’s Manual 1-3

Introduction

1-4 Intel® Itanium® 2 Process or Hard ware Develop er’s Manual

Itanium® 2 Processor

Microarchitecture 2

This chapter provi des an introduction to the Itanium 2 processor microarchitecture. For detaile d

information on Itanium architecture, please refer to the Intel

Developer’s Manual.

2.1 Overview

The Itanium 2 processor is the second implementatio n of the Ita nium Instruction Set Archi tecture

(ISA). The processor employs EPIC design concepts for a tight er coupling between hardware and

software. In this design s tyle, the interface betwe en ha rdware and software is designed to enable

the softwa r e to exploit all available com p ile-time information, and efficiently deliver this

information to the hardware. It addresses several fundamental performance bottlenecks in modern

computers, such a s memory latency, memory address disambi guation, and control flow

dependencies . Th e EPIC c onstructs provide powerful architectural s emantics, and enable the

software to make global optimizations across a large scheduling scope, thereby exposing avail able

Instruction Level Parallel is m (ILP) to the hardware. The hardware takes advantage of this

enhanced ILP, and provide s abunda nt executi on resourc es. Additiona ll y , it foc uses on dynami c runtime optimiza tions to enable the compiled code schedule to flow through at high throughput. This

strategy increases the synergy betwee n hardware and software, and leads to highe r overall

performance.

The Itanium 2 processor provide s a 6-wide, 8-stage deep pipeline running at either 1.0 GHz or 900

MHz. This provides a combination of both abundant resources to exploit ILP as well as increased

frequency for minimizi ng th e latency of e ach instru ction. The resourc es co nsist of s ix integ er units ,

six multimedia units, two load and two store units, three branch units, two extended-precision

floating-point units, and two additional single-precision floating-point units. The hardware

employs dynamic pref etch, branch prediction, a register scoreboard, and non-blocking caches.

Three levels of on-die cache minimize overall mem ory latency. This includes ei ther a 3 MB or

1.5MB L3 cache, accessed at core speed, providing over 32 GB/cycle of data bandwidth. The

system bus is designed for glueless MP support for up to 4 processors per system bus, and can be

used as an effecti ve building block for very large systems. The balan ce d core and memo ry

subsystem provide high performance for a wide range of applications ranging from commercial

workloads to high performance technical computing.

®

Itanium™ Architecture Software

2.1.1 6-Wide EPIC Core

The Itanium 2 processor provides a 6-wide, 8-stage deep pipeline, based on the EPIC desig n. Th e

pipelines utilize the following e xecution units: six Integer ALUs, six Multimedia ALUs, two

Extended Preci sion Flo ati ng-point Units , two add iti onal Singl e Prec isi on Floa ting-poi nt Unit s, two

Load and two Store Units , and three Branch Units. The machine is capable of fetching, issuing,

executing, and ret iring six instructions, or two instructions bundles, per clock.

An instruction bundle contains three instructions and a template indicator, assigned by the

compiler. Each instruction in the bundle is eventually dispersed into one of the execution pipelines

according to its type: ALU Integer (A), Non-ALU Intege r (I), Memory (M), Float ing-point (F),

Branch (B), or Extended (L). The Itani um 2 processor’s increase in execution units more than

Intel® Itanium® 2 Processor Hardware Developer’s Manual 2-1

Itanium® 2 Processor Microarchitecture

triples the dispersal options for the comp iler over the Itanium proces sor. Please refer to the Intel

Itanium™ Architecture Software Developer’s Manual for more information regarding instructions

and bundles , an d th e Intel

®

Itanium® 2 Processor Refer ence Manual for Soft ware Development and

Optimization for more inform ation regarding Itanium 2 processor instruction dispersal.

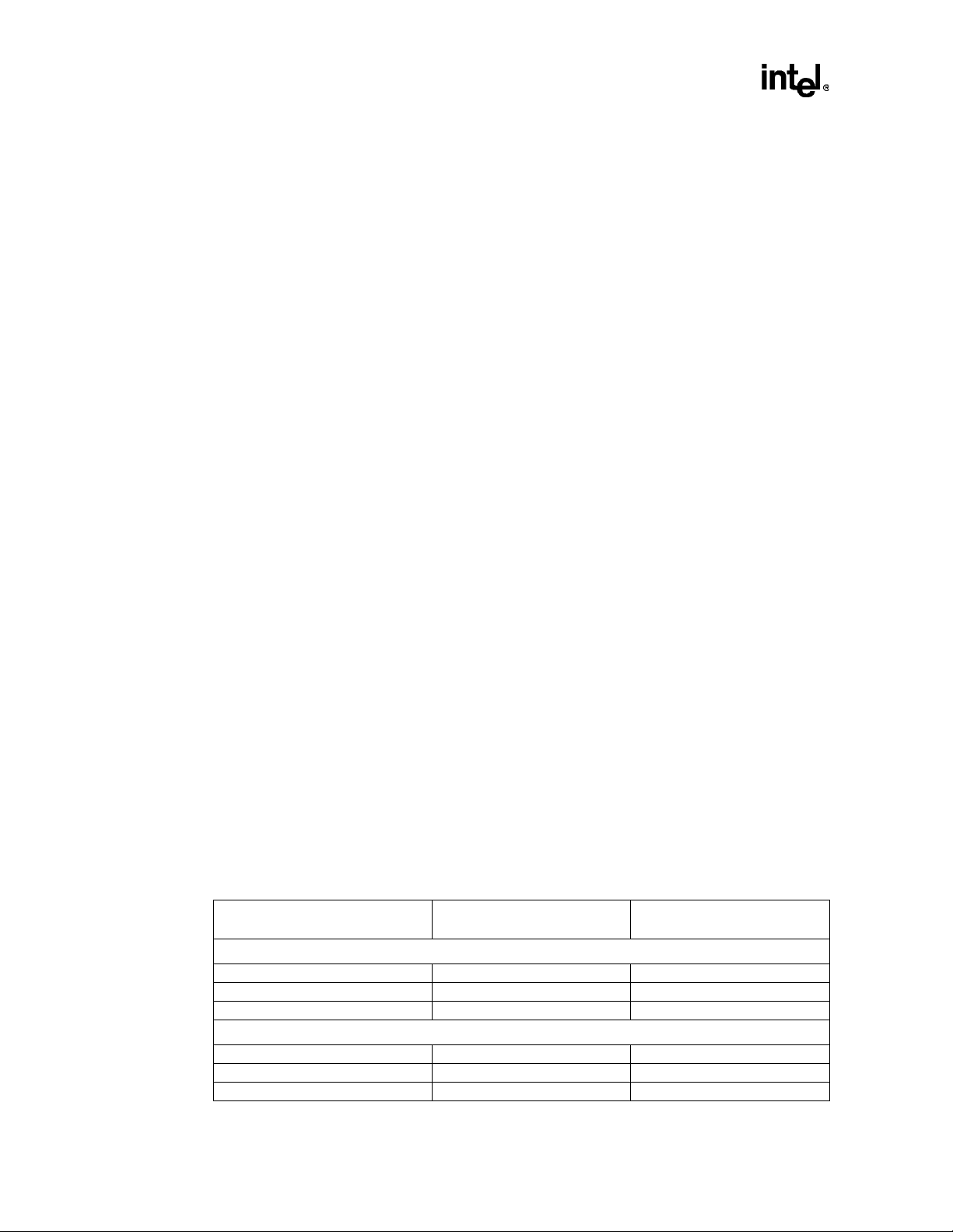

Figure 2-1 illustrates two examples demonstrating the level of parallel operation supported for

various workloads. For enterpris e and commercial codes, the MII /MBB template combinati on in a

bundle pair provides six instructions or eight parallel ops per clock (two load/store, two generalpurpose ALU ops, two post-increment ALU ops, and two branch instructions). Alternatively, an

MIB/MIB pair allows the same mix of operations, but with one branch hint and one branch op,

instead of two branch ops. For scientific code, the use of the MFI template in each bundle enables

twelve paralle l Ops per clock (loading four double -precision operands to the reg isters, executing

four double-precision flops, two integer ALU ops and two post-increment ALU ops). For digital

content cre ation codes that use singl e pre cision floating-p oint, the SIMD features in th e machine

effecti vely provide the capability to perform up to twenty parallel ops per clock (loading e ight

single precision operands, executing eight single precision FLOPs, two integer ALUs, and two

post-incrementing ALU operations).

Figure 2-1. Two Examples Illustrating Supported Paral le lism

M F I

y

Load 4 DP (8 SP)

Ops via 2 Fld-pair

y

2 ALU Ops (Post

incr.)

M F I

4 DP FLOPS

(8 SP FLOPS)

2 ALU Ops

6 Instructions Provide:

y

12 Parallel Ops/Clock for Scientific Computing

y

20 Parallel Ops/Clock for Digital Content

Creation

®

M I I

2 Loads +

2 ALU Ops

(Post incr.)

Note: SP - Single Precision

2 ALU Ops

DP - Double Precision

2.1.2 Processor Pipeline

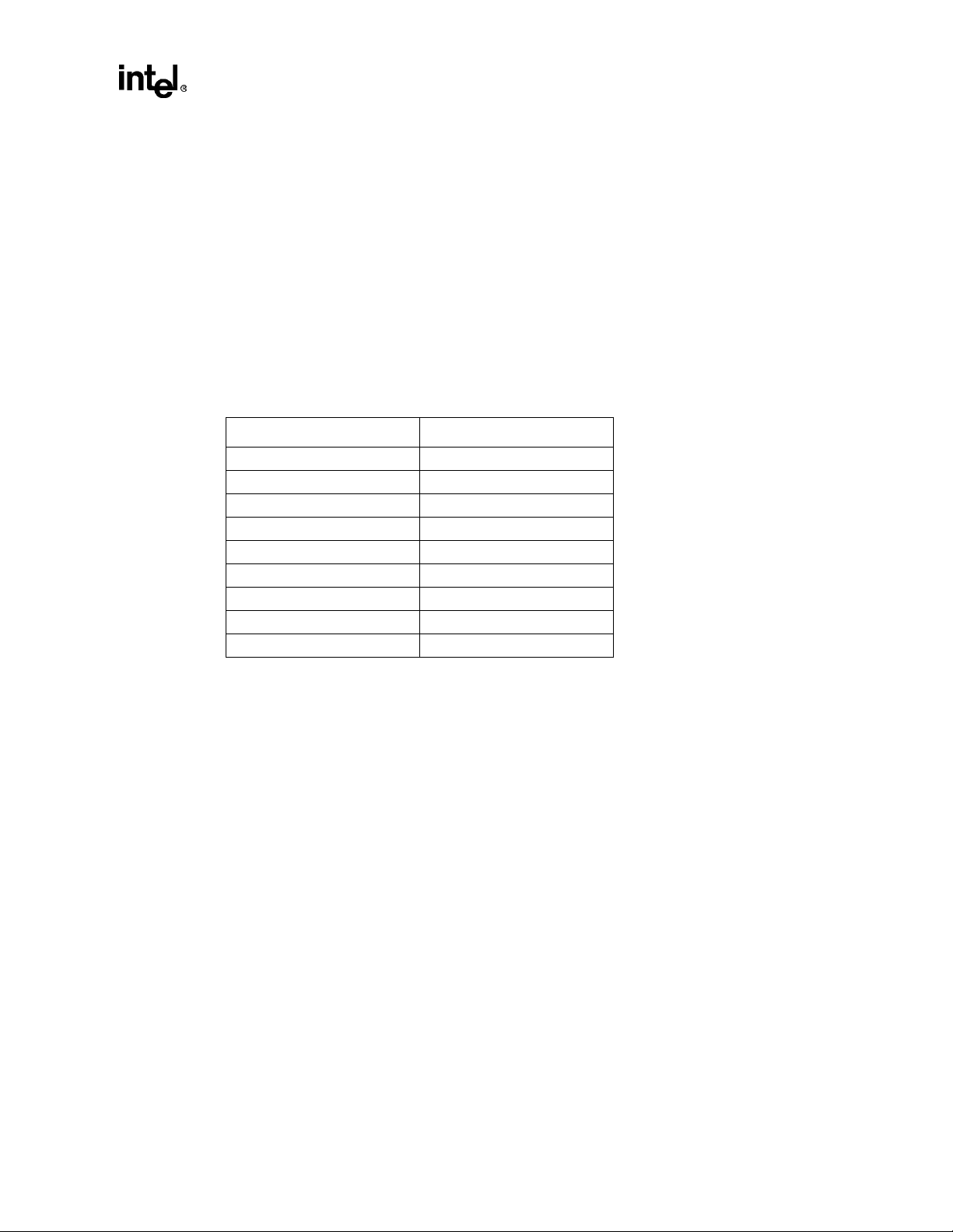

The processor hardware is organized into a eight stage core pipeli ne, shown in Figure 2-2, that can

execute up to six in st ructions in parallel pe r clock. The first two pipeline stages perform the

instruction fetch and deliver the instructions into a decoupling buffer in the instruction rotation

(ROT) stage that enables the front-end of th e machine to operate independentl y from the back end.

The bold line in the middle of the core pipeline indicates a point of decoupling. Dispersal and

register rena mi ng are performed in the next two stages, ex pand (EXP) and register rename (REN).

Opera n d d elivery is accompli shed across the regi ster read (REG) stage, w here the register file is

accessed and data is delivered through the bypass network after processing the predicate control.

Finally, the last three stages perform the wide parallel execution followe d by exception

management and retirement. In particular, the exception detection (DET) stage accommodates

branch resolution as well as memory exception management and speculation support.

®

Please see the Intel

Optimization for more inform ation the Itanium 2 processor pipeline.

Itanium® 2 Processor Reference Manual for Software Development and

M B B

2 Branch Insts.

6 Instructions Provide:

y

8 Parallel Ops/Clock for Enterprise and

Internet Applications

001246

2-2 Intel® Itanium® 2 Process or Hard ware Develop er’s Manual

Figure 2-2. Itanium

®

2 Processor Core Pipeline

Itanium® 2 Processor Microarchitecture

Front-end

Pre-fetch/Fetch of 6 Instruct ions /Cloc k

Hierarchy of Branch Predictors

Decoupling Buffer

IPG ROT EXP REN REG EXE DET WRB

Instruction Delivery

Dispersal of 6 Instructions onto 11 Issue Ports

Register Remapping

Register Save Engine

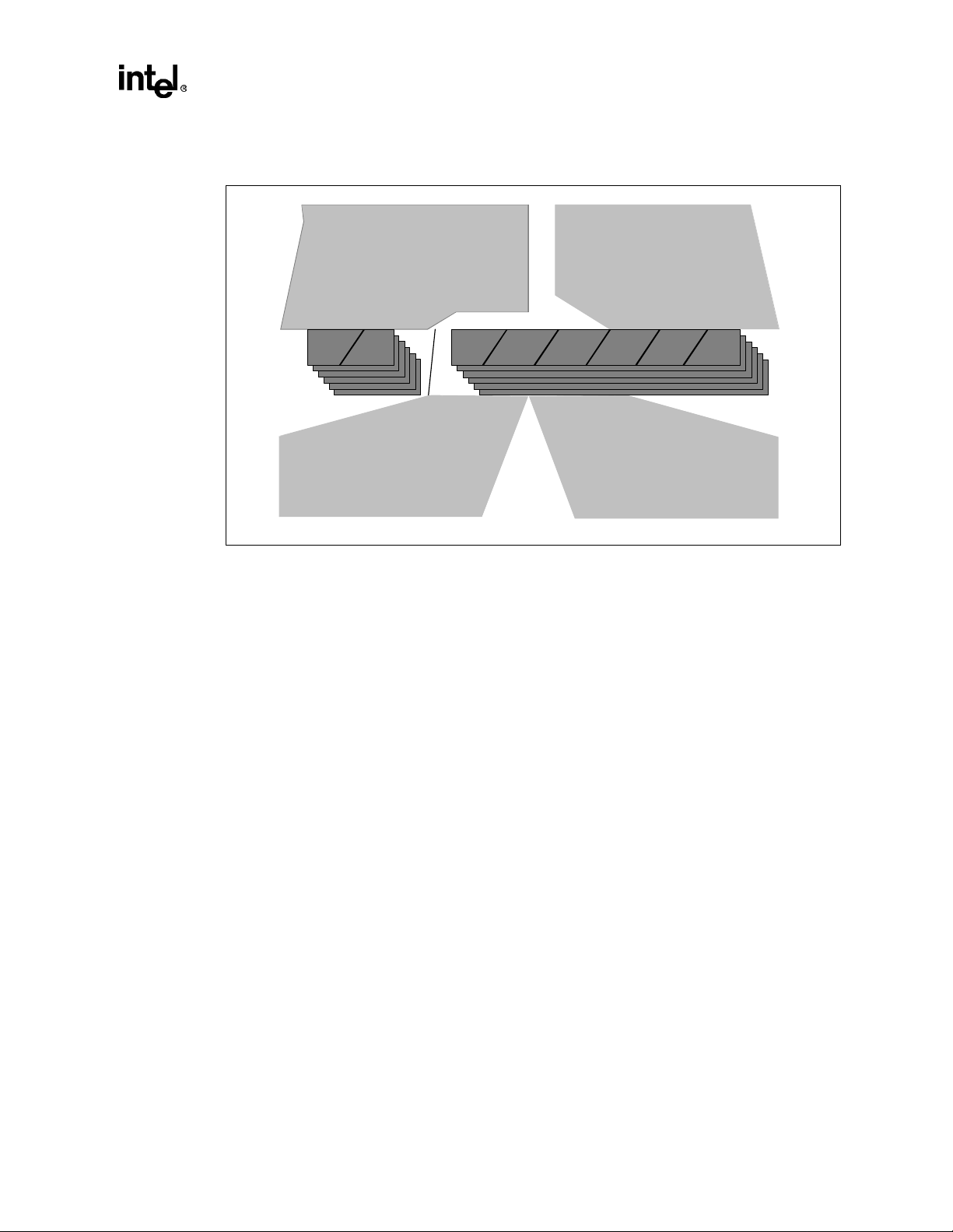

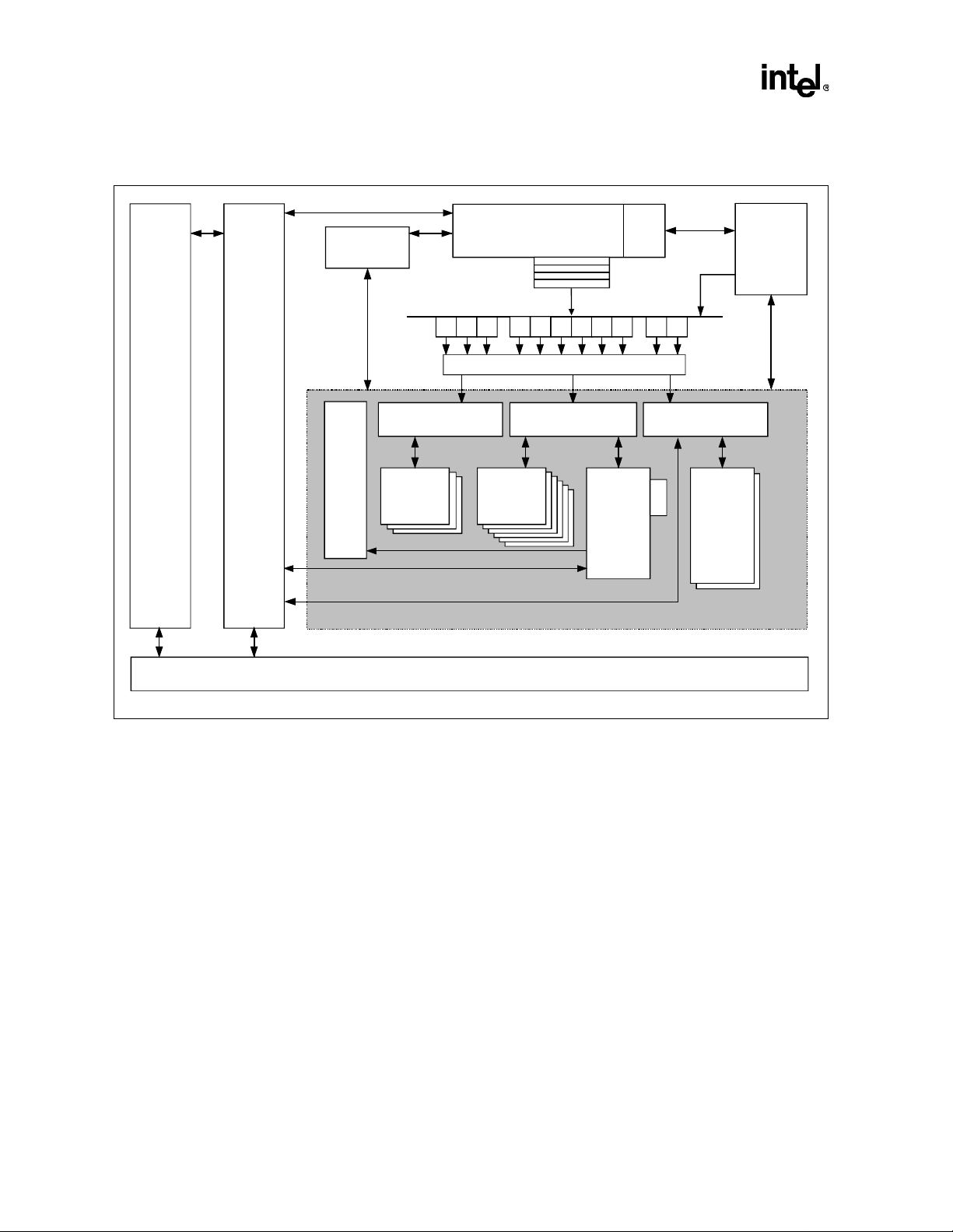

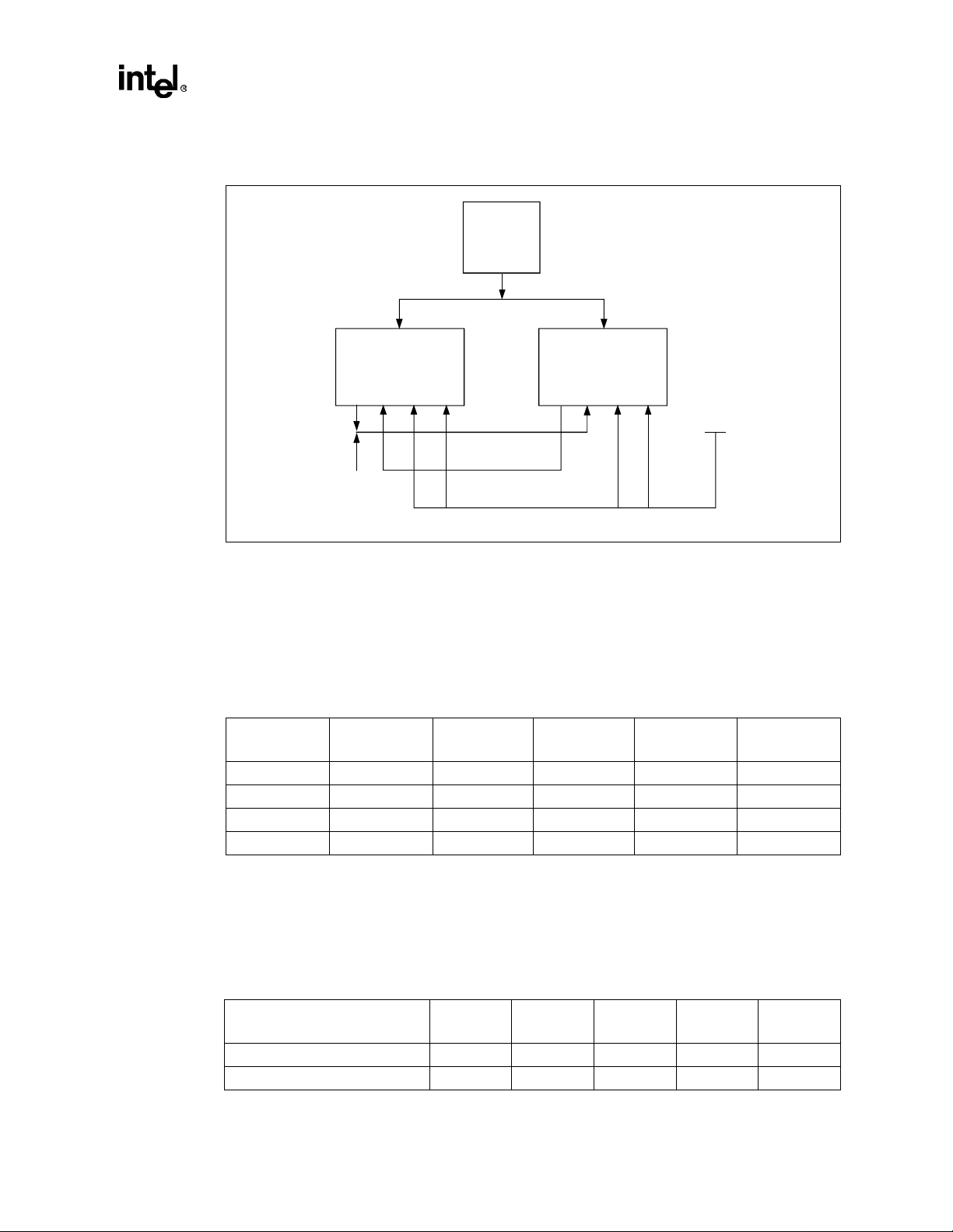

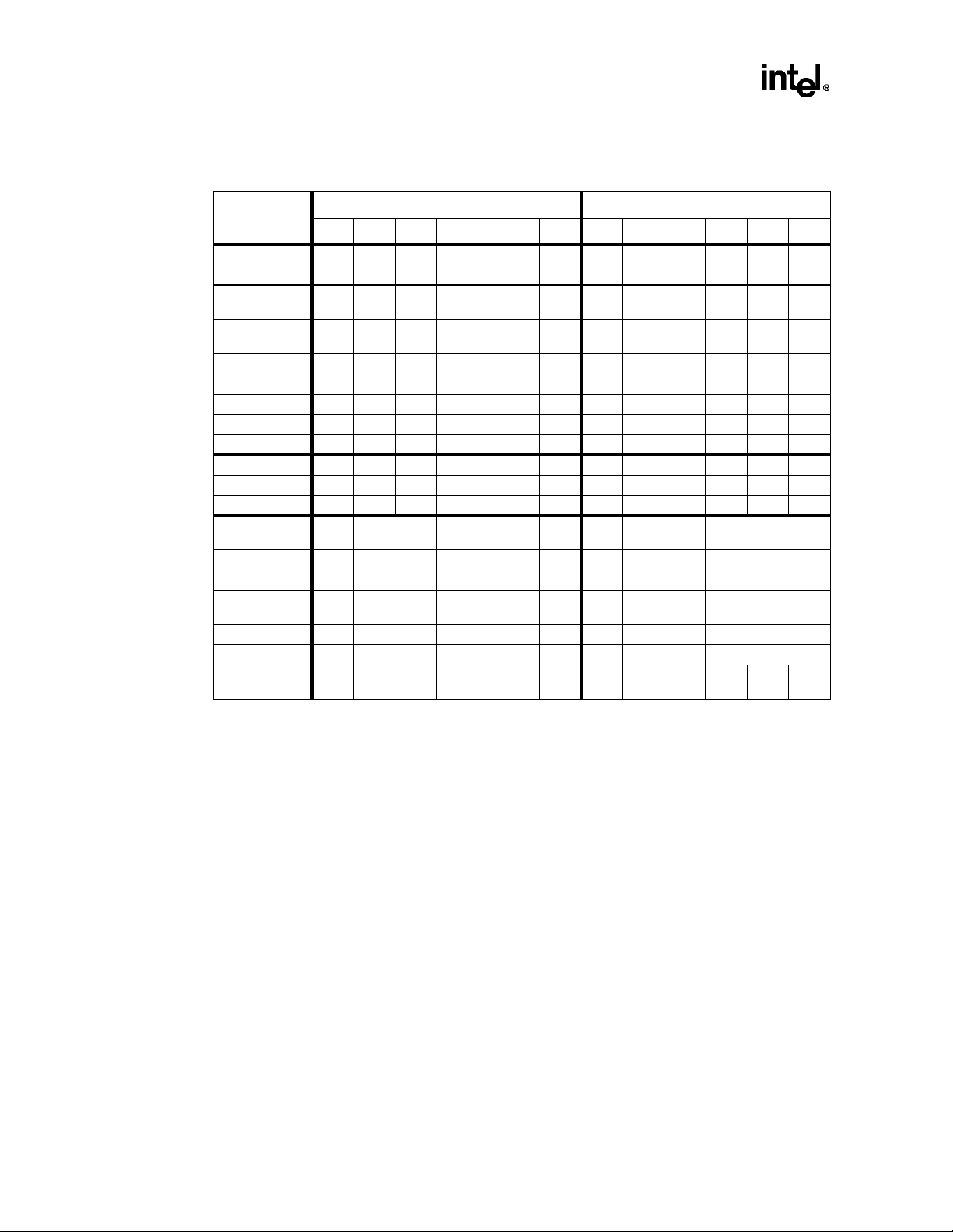

2.1.3 Processor Block Diagram

Figure 2-3 shows a block diagram of the Itanium 2 proce ssor. The function of the processor is

divided into five groups, each summarized below. The following sections give a high-level

description of the operation of each group.

1. Instruction Processing

The instruction processing block contains the logic for instruction prefetch, ins truction fetch,

L1 instruction cache, branch prediction, instruction address generation, instruction buffers,

instruction issue, dispersal and rename.

Execution Core

4 Single Cycle ALU, 2 Load/Stores

Advanced Load Control

Predicate Delivery and Branch

NaT/Exceptions/Retirement

Operand Delivery

Register File Read and Bypass

Register Scoreboard

Predicated Dependencies

001097a

2. Execution

The execution bloc k cons ists of the multimedi a logic, integer ALU execution logic, floatingpoint (FP) execution logic, integer regis ter file, L1 data cache and FP regi ster file.

3. Control

The control block consists of the exception handler and the pipeline control, as well as the

Register St ack Engine (RSE).

4. Memory Subsystem

The memory subsystem con tains the unified L2 cache, on-chip L3 cache, Programmable

Interrupt Controller (PIC), instruction and data Translation Lookaside Buffers (TLB),

Advanced Load Address Table (ALAT) and external system bus interface logic.

5. IA-32 Compatibility Execution Engine

Instructions for IA-32 applications are fetched, decoded and scheduled for execution by the

IA-32 compatibility execution engine.

Intel® Itanium® 2 Processor Hardware Developer’s Manual 2-3

Itanium® 2 Processor Microarchitecture

®

Figure 2-3. Itanium

2 Processor Block Diagram

L1 Instruction Cache

Branch

Prediction

Branch & Predicate

L3 Cache

L2 Cache - Quad Port

NaTs, Exceptions

Scoreboard, Predi cate,

Registers

Branch

Units

Fetch/Pre-fetch Engine

Instruction

Queue

BBB MMI I FF

Register Stack Engine / Re-Mapping

and

MM

128 Integer Registers

Integer

and

MM Units

8 Bundles

Dual-Port

L1

Data

Cache

and

DTLB

ITLB

128 FP Regist ers

ALAT

Floating

Point

Units

IA-32

Decode

and

Control

Bus Controller

2.2 Instruction Processing

2.2.1 Instruction Prefetch and Fe tch

The Itanium 2 processor speculatively prefetches instructions from a pipelined cache into a

decoupling buffer. The Itanium 2 processor uses a sophisticated branch prediction strategy and

compiler hints for speculative prefetches. The ins t ruction sequencing portion of the Itanium 2

processor is responsible for fetching and dispersing instructions to the execution units. The

instruction address generation unit selects the next instruction pointer (IP) . The ins truction pointer

is selected between the next sequent ial address, static and dynamic branch prediction addresses,

instruction a ddresses delivered by the compatibility logic, validated target and address to correct

for mispredicted branches, or the address of exce ption handlers.

The Itanium 2 processor reads two instruction bundle s (three instructions per bundle) from the L1

instruction cache (L1I) and places them in the instru ction buffers. The instruction buffers store

bundles of instructions waiting to be consumed by the execution units. To reduce the effect of

branch predic tion bubbles caused by instruction cache misses, bundles read from the instruction

buf f ers are sent to the inst r u ction issue and renam e logic based on the availability of execu tion

resources.

001096a

2-4 Intel® Itanium® 2 Process or Hard ware Develop er’s Manual

2.2.2 Branch Predi ction

The branch predict ion logi c uses ad vance d predict ion schemes to antici pate t he directi on an d targe t

of each branch read from the ins truct ion cac he. The Ita nium 2 process or featu res a 0-bubbl e branch

prediction algorithm and a backup branch prediction table. Whenever a branch happens, the

branch target will be restored to the instruction pointer generation logic.

The instruction prefetch lo g ic serves as the interface between the L1I and L2 cach e. It prefetches

instructions from L2 before they are needed in order to pre vent L1I mis ses. Prefetchi ng is execut ed

under control of t he c ompiler. If an L1 instruction ca che mis s does occ ur , i t will s tall the instru ction

address generation logic and retrieve the information from the L2 cache. If the ins truction does not

reside in L2 cache, it will proceed to check the L3 cache.

2.2.3 Dispers al Lo g ic

There are twelve te mplates for Itanium instructions. A template contains explicit stop bits to

indicate to th e hardware to stop parallel is su e of su bsequent instructions. There are three

instructions per bundle and the hardware can handle two bundles (i.e. six instructions) per clock.

The dispersal logic sends each instruction to one of the fully pipelined functional units through its

issue ports.

Itanium® 2 Processor Microarchitecture

The instruction buffer holds a maximum of eight instruction bundles. The buffer can present two

bundles to the disp ersal logic every cycl e. In general, instructions are routed to a supporti ng

execution port on a first available basis.

2.3 Execution

The Itanium 2 processor e xecution logic consists of six multimedia units, six integer units, two

floating-point units, three branc h units and four load/store uni ts. The Itanium 2 processor has

general registers and FP registers to manage work in progress. Integer loads are processed by the

L1 data cache but integer stores will be processed by L2. FP l oads and stores are also processed by

the L2 cache. Whenever a lo okup occurs in L1, a speculat ive request is sent to the L2 cac he.

The multimedia engines t r ea t the 64-bit data as 2 x 32-bit, 4 x 16-bit or 8 x 8-bit packed data t ypes .

Three classes of arit hm etic operations can be performed on the packed or Single Instruction

Multiple Data (SIMD) data types: arithmetic, shift and data arra ngement. Meanwhile the integer

engines support up to six non-pa ck ed integer ari thmet ic and logi cal oper ations . Up to six intege r or

multimed ia operations can b e executed each cycle.

2.3.1 Floating-Point Unit (FPU)

The Itanium 2 processor provides high floatin g-point execution bandwidth. The Itanium 2

processor FPU has four pipeline stages. Extra bypa s sing logic allows quick data forwarding from

various FP stages to the FP write back stage. The FP logic also includes an FP Multiply

Accumulate (FMAC) hardware unit, fast rounding logic and support for SIMD formats. The

Itanium 2 processor can i ssue up t o two FP ins t ructio ns, or t wo Intege r multi plica tions , plus two FP

loads and two FP stores (or four FP loa ds) instructions every cl ock c ycle.

Numeric operands are chec ked for possi ble num eric excep tions before the instructi on enter s the FP

pipeline. Results are written back at the end of the pipeline.

Intel® Itanium® 2 Processor Hardware Developer’s Manual 2-5

Itanium® 2 Processor Microarchitecture

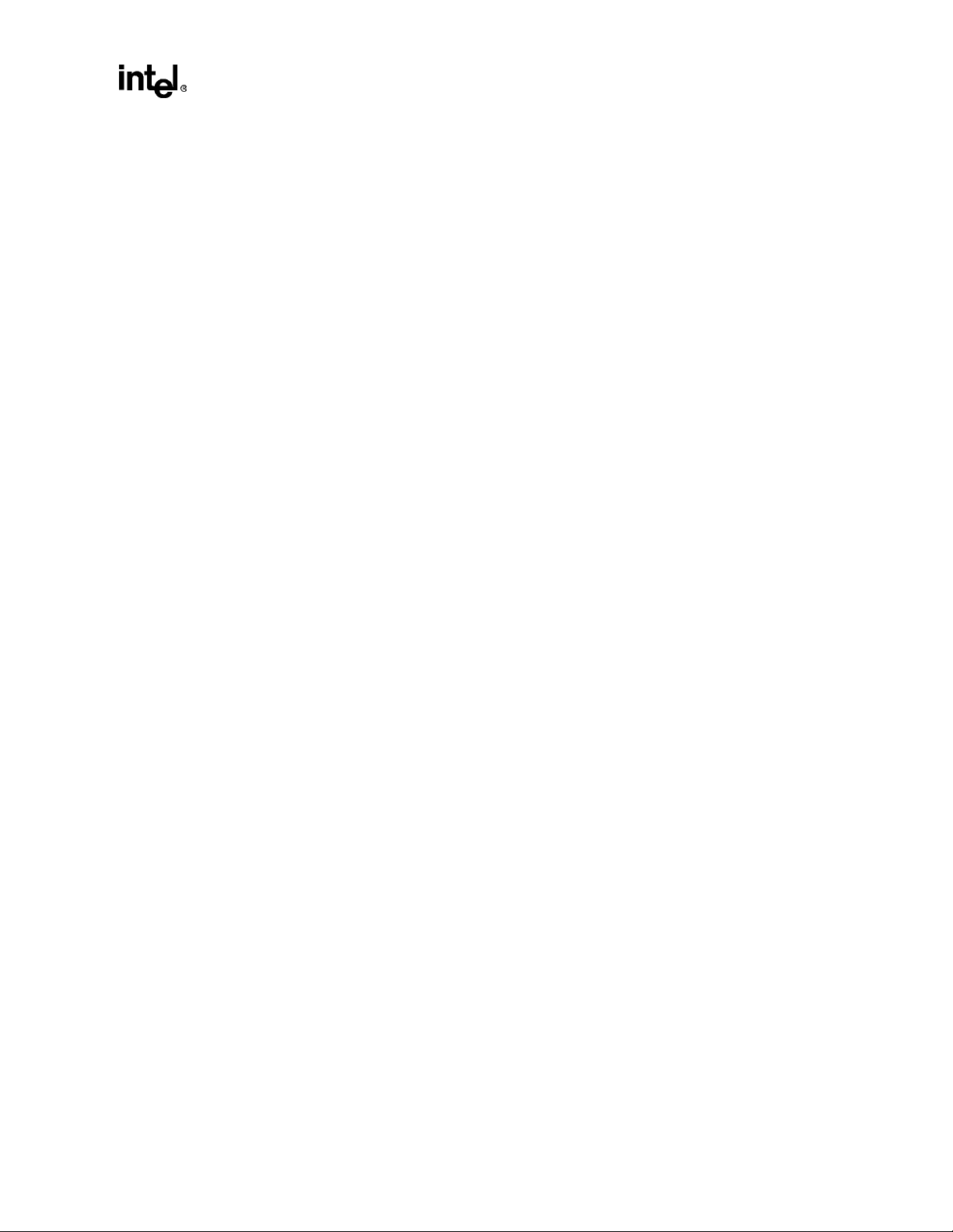

The FPU supports two FMACs that operate on 82-bit values. The FMACs can execute single,

double and dou ble- exten ded precis io n FP ope rations. The FP U has a 128- ent ry FP reg iste r file wi th

eight read and at le as t six write ports. The FP registe rs can support four double prec ision loads

every clock from memory, two 82-bit writebacks from the FMACs and two store ope rations for the

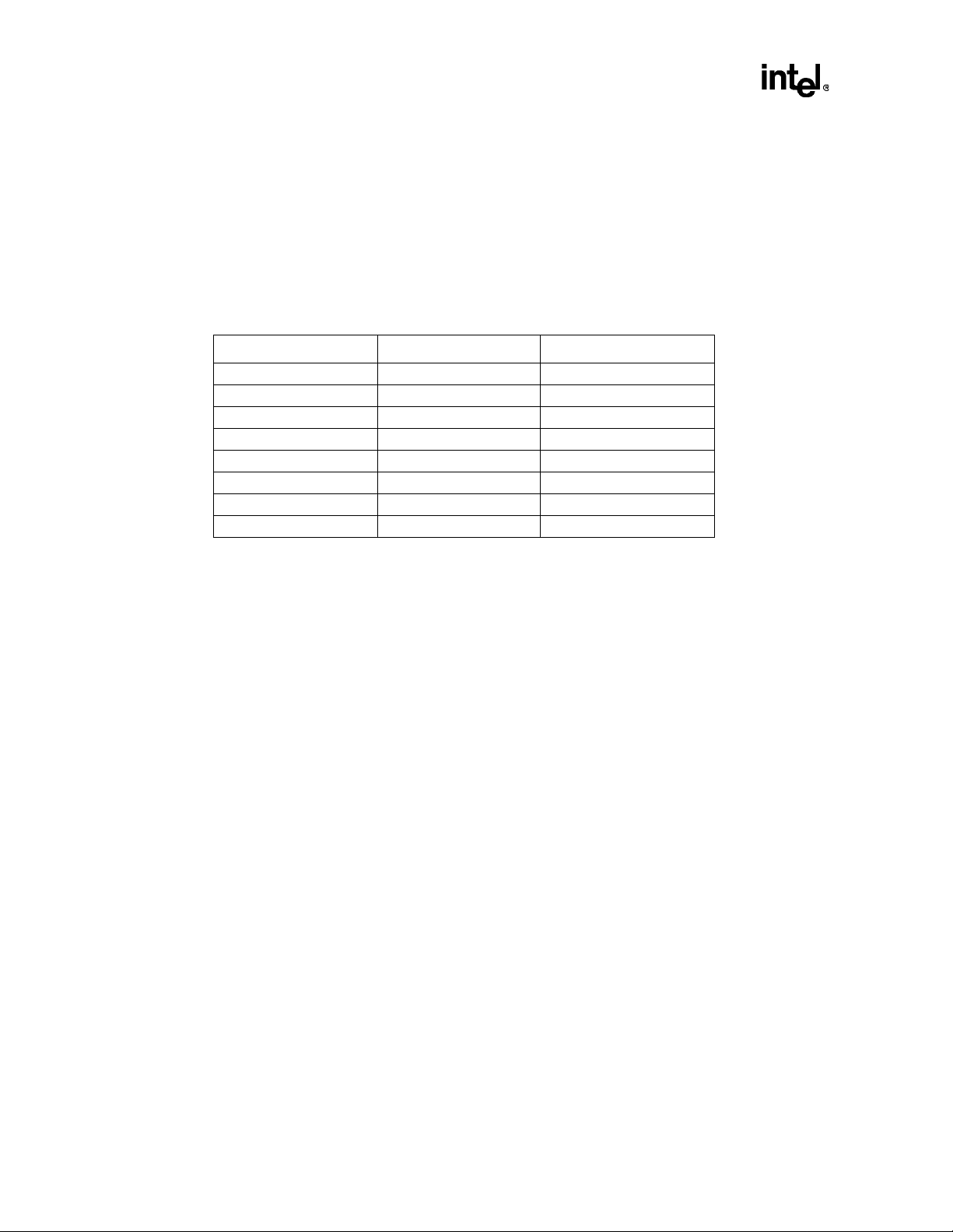

two parallel extended precision FMACs eve ry clock. Refer to Figure 2-4 for a diagram of the

.

Figure 2-4. Itanium

FMAC units.

®

2 Processor FMAC Units

L3

Cache

4 Double-

precision

Ops/Clock

2.3.2 Integer Logic

The six integer execution units execute 64-bit arith me tic, logical, shift and bit-field manipulation

instructions. Additionally it can execute instructions to accelerate operations on

32-bit pointers. Other operations include computing predicates, linear addresses and flag

generation for the IA-32 comp ati ble engine.

The integer logic has six general purpose ALUs and two load and two store ports. The ALUs have

full bypassing capability.

2.3.3 Register Files

2 Stores/Clock

L2

Cache

Even

Odd

4 Double-

precision

Ops/Clock

(2 x ldf-pair)

6 x 82 bits

Register

File

(128-entry

82 bits)

2 x 82 bits

001098a

The Itanium 2 processor implements the massive register resources provided by the Itanium

architec ture. The large number of registers allow many operations to complete without read ing

from or writing to memory. The primary execution registers include: 128 general registers, 128

floating-point registers, 64 predicate registe rs, and 8 branch registers.

2.3.3.1 General Registers

A set of 128 (64-bit) ge neral registers provide the central resource for all in teger and integer

multimedia computation. They are numbered GR0 through GR127, and are available to all

programs at all privilege levels.

The general reg isters are part ition ed into t wo su bsets. Gene ral reg ister s 0 thro ugh 31 are t ermed the

static general registers. Of these, GR0 is special in that it always reads as zero when sourced as an

operand, and attempting to write to GR0 causes an Illegal Operation fault. General registers 32

through 127 are te rme d the stacked general registers. The stacked registers are made availabl e to a

program by allocat ing a register stack frame consist ing of a programmable number of local and

output registers.

2-6 Intel® Itanium® 2 Process or Hard ware Develop er’s Manual

2.3.3.2 Floating-Point Registers

A set of 128 (82-bit) floa ting-point registers are used for all floating-point computation. They are

numbered FR0 through FR127, and are available to all pr ograms at all privilege levels. The

floating-point registers are partitioned into two subsets. Floating-poi nt registers 0 through 31 are

termed the static floating-point registers. Of these, FR0 and FR1 are special. FR0 always reads as

+0.0 when sourced as an operand, and FR1 always reads as +1 .0. When either of these is used as a

destination, a fault is raised.

Floating-point registers 32 through 127 are termed the rotatin g floating-point registers. These

registers can be programmatically renamed to accelerate loops.

2.3.3.3 Predicate Registers

A set of 64 (1-bit) predicate re gisters are used to hold the results of compare instructions. The s e

registers are numbered PR0 through PR63, a nd are available to al l programs at all privilege levels.

These registers are used for conditional ex ec ution of instructions.

The predicate registers are partitione d into two subs ets. Predicate registers 0 through 15 are termed

the static predicate registers. Of these, PR0 always reads as ‘1’ when sourced as an operand, and

when used as a destination, th e r esult is discarded. The static predicate registers are also used in

conditional branching.

Itanium® 2 Processor Microarchitecture

Predicate registers 16 through 63 are termed the rotating predicate registers. These rotating

registers support efficient software pipeline loops.

2.3.3.4 Branch Registers

A set of 8 (64-bit) branch registers are used to hold branching information. They are numbered

BR0 through BR7, and are a v ailable to a ll programs at all privilege levels. The branch registers are

used to s p ec if y th e branch targe t ad d r esses for in d irect branches.

2.3.4 Register Stack Engine (RSE)

The Itanium ISA avoids the spilling and filling of reg is ters at procedure interfaces through a large

register file and a mechanism for accessing the registers through an indirection base. The

indirection mechanism allows stacki ng of register frames and sharing of inter-proc edure variables

through the register file.

When a procedure is called, a new frame of registers is made available to the called procedure

without the need for an explicit save of the caller s’ registers. The old registers remain in the large

on-chip physical register file as long as there is enough physical capacity. When the number of

registers needed overflows the available physical capacity, a state machine called the Register

Stack Engi ne (RSE) saves the regi sters to memory to free up the necessary registers needed f or the

upcoming call. The RSE maintains the illus ion of an infinite number of registers.

On a call r et ur n, th e b ase regi s ter is re st ore d to t he v alu e t hat the ca ll er wa s u sing to acce s s reg ist ers

prior to the call. Often a return is encounte red even before these registers need to be saved, making

it unnecessary to restore them. In cases where the RSE has saved some of the callee’s registers, the

processor stalls on return until the RSE can restore the appropriate number of the callee’s registers.

The Itanium 2 processor im plements the forced lazy mode of the RSE, as described in the Intel

Itanium® 2 Proces sor Reference Manual for Software Development and Op timization.

®

The Intel

Intel® Itanium® 2 Processor Hardware Developer’s Manual 2-7

®

Itanium™ Archit ecture Software Developer’s Manual describes the RSE in more det ail.

Itanium® 2 Processor Microarchitecture

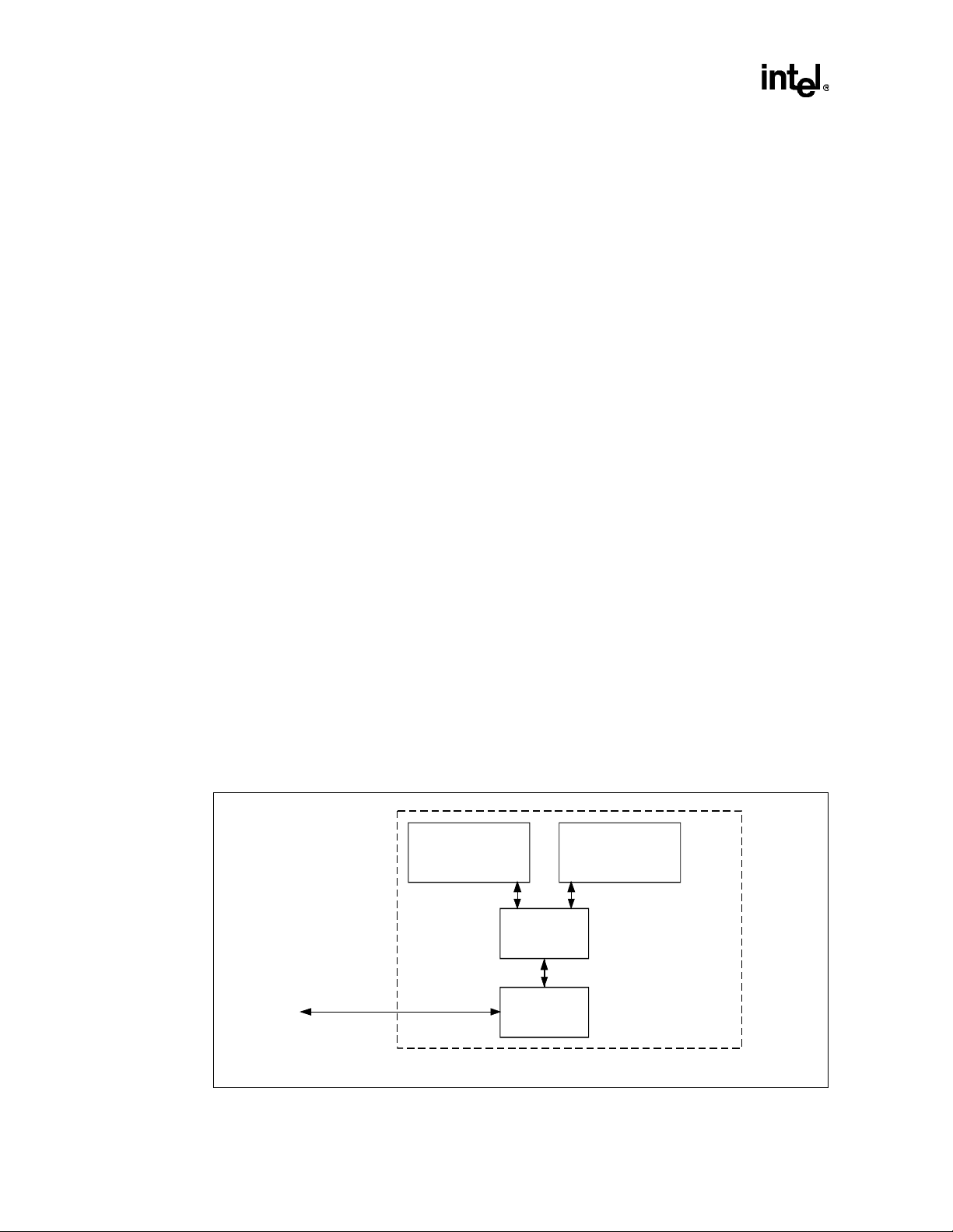

2.4 Control

The control section of the Itanium 2 processor is made up of the exception handler an d pipeline

control. The exception handler imple ments exception prio ritizing. Pipeline control has a

scoreboard to detect register source dependencies and a cache to support data speculation. The

machine stalls only when source operands are not yet available. Pipe line control supports

predicati on via predication regis ters.

The pipeline control section also contains a Performance Monitoring Unit designed to collect data

that can be dumped for analyzing Itanium 2 processor performance.

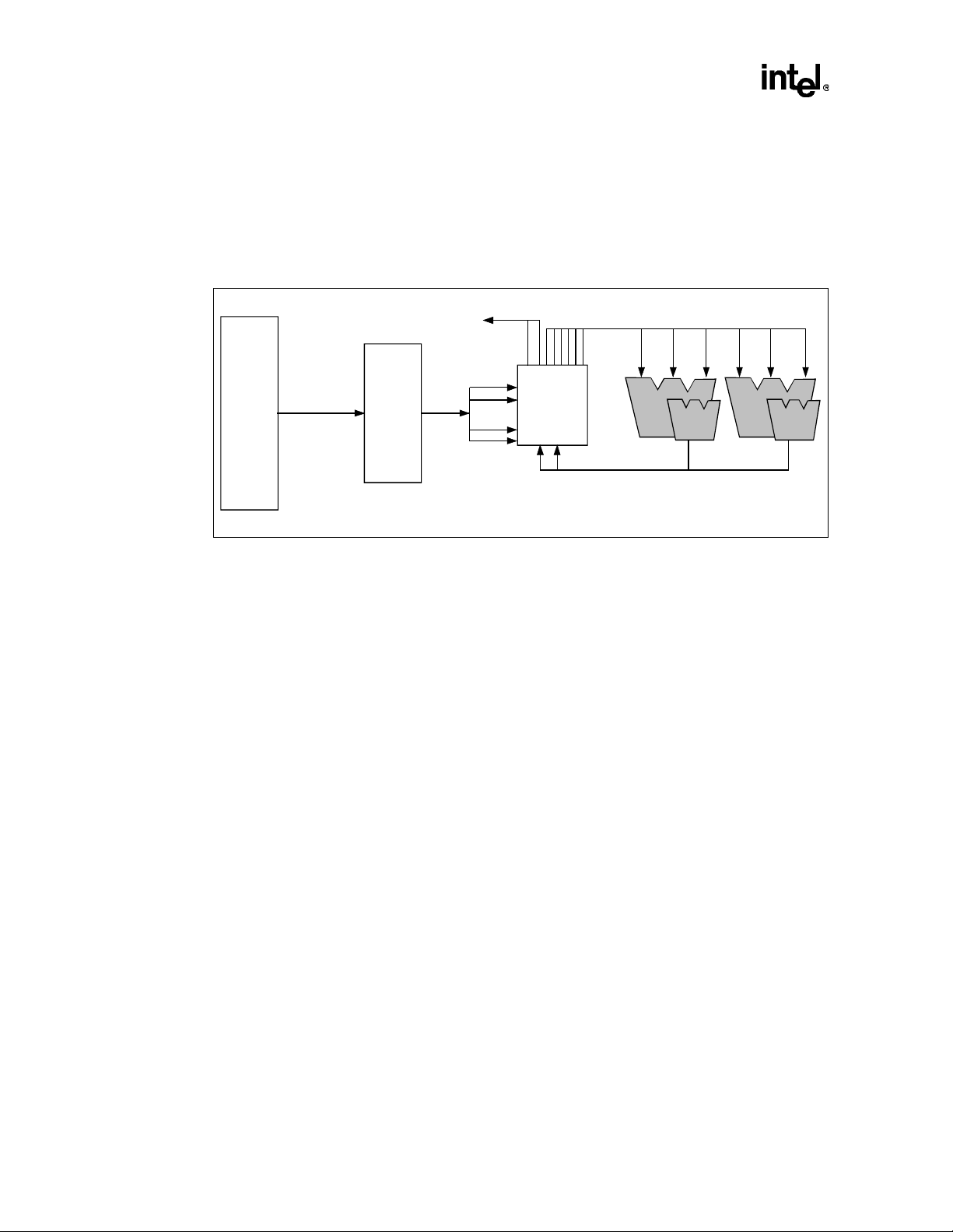

2.5 Memory Subsystem

The main system memory is access ed through the 128-bit syste m bus (refer to Figure 2-5). The

system bus is transaction-oriented and pipelined similar to the Itanium processor system bus. The

memory subsys tem for the Itanium 2 processor cont ains system bus interface logic, the L1D cache,

the L2 cache, the L3 cache, interrupt controller unit, ALAT and TLB.

The Itanium 2 processor supports all non-aligned IA-32 memory accesses. References to memory

in Itanium architecture spanning an 8 byte boundary will result in a n unaligned fault. To avoid

performance degradation associated with unaligned accesses and extra overhead for unaligned data

memory fault handlers, aligned memory ope rands should be used whenever possible.

The L1, L2 and L3 caches are non-blocking. There are separate L1 caches for data and instructions.

The L1 data cache is q u ad p o rted. The L2 cache is a unified cache and co n tains both instr u ctions

and data. It is quad ported and can be accessed at the ful l clock speed of the Itanium 2 processor.

All ports are used when acces s ing instructions in L2 cache, but for data requests one can utilize

either one, two, three or all of the four ports. When a reque st to the L2 cache causes a miss, the

request is quickly forwarded to the L3 cache.

The integrated external interrupt controller interface s to the system bus through the ext ernal bus

logic and receive s both external and internal interrupts from the system bus through its memory

mapped location.

Figure 2-5. Itanium

®

2 Processor Cache Hierarchy

L1I L1D

128b

System Bus

L2

L3

Itanium® 2 Processor

000699a

2-8 Intel® Itanium® 2 Process or Hard ware Develop er’s Manual

2.5.1 L1 Instruction Cache

The Itanium 2 processor L1 instruction (L1I) cache is 16 KB in si ze . It is a single cycle, nonblocking, dual ported 4-wa y set-associative cache mem ory with a 64 byte line si ze (there is no way

prediction). The tag array is dual port ed. One port is for instruction fetches, the other port is shared

among prefetches, snoops, fills, and column invalidates. The data array is also dual ported to

support simult aneous reads (fetches) and fills. The L1I is fully pipeline d and c an del iver two

instruction bundles (six instruct ions) every clock.

The L1I cache is physically indexed and tagged.

2.5.2 L1 Data Cache

The L1 data cache is four-ported (two loads and two stores), 16 KB in size and is non-blocking. It

is organized as 4-way set-associative (no way prediction) with 64 byte line size. It c an support two

concurrent loads and two stores. The L1 data cache only ca che s integer data (does not cache

floating-point load or semaphore load da ta). The L1D cache is write-through with no write

allocation. The L1D cache is physical ly indexed and tagged for loa ds and stores.

Itanium® 2 Processor Microarchitecture

2.5.3 Unifi ed L2 Cache

The unified L2 cache memory is four-ported and supports up to four concurrent accesses via

banking. The L2 cache is 256 KB, 8-way set-associative with a 128 byte line size, made of 16 byte

banks and is non-bloc king and out of order. It has a cache read bandwidth of 64 GB per second.

The L2 cache implement s a write-back with write-al locate policy. It is physically indexed an d

physically tagged.

In addition to servicing all L1I and L1D cache misses, the L2 handles all floating-point memory

accesses (up to four concu rrent floating-point loads per clock). All of the Itanium 2 processor’s

semaph o r e in st r u ct io n s are al s o ha ndled excl u si ve ly by the L2.

2.5.4 Unifi ed L3 Cache

The on chip L3 cache on the Itanium 2 processor is 1.5 MB or 3 MB in size. I t is physically

indexed and phys ically tagged. The L3 cach e is single ported, full y p ipelined non-blocking cache

featuring 12 wa y se t-associative with 128 byte line size. It can su pport 8 outstanding requests, 7 of

which are loads/sto res and 1 is for fil ls. The maximum transfer rate from L3 to core/L 1I/ L1D or L2

is 32 GB/cycle. The L3 protects both tag and data with single bit correc tion and double bit

detection E CC.

2.5.5 The Advanced Load Address Table (ALAT)

A cache s tru cture ca ll ed th e A d v an ce d Load Add r es s Table (AL AT) is used to enab le data

speculation in the Itanium 2 processor. The ALAT keeps information on speculative data loads

issued b y th e mach ine and a ny s tore s tha t ar e al ias ed wit h th es e lo ads . Thi s structure has 32 ent rie s,

is a fully associa tive array that can handle two loads and two stores per cycle . It can provide

aliasin g information for th e ad vance load “check” operations.

Intel® Itanium® 2 Processor Hardware Developer’s Manual 2-9

Itanium® 2 Processor Microarchitecture

2.5.6 Translation Lookaside Buffers ( T LBs)

There are two types of TLBs on the Itanium 2 processor: Data Translation Lookaside Buf fer

(DTLB) and the Instruction Translat ion Lookaside Buff er (IT LB). There are two levels of DTLBs

in the Itanium 2 processor: a L1 DTLB and a L2 DTLB. Only L1D cache loads depend o n the L1

and L2 DTLB hits. Stores and L2/L3 cache hits only de pend on the L2 DTLB hits.

TLB mis ses in eit h er the DTLB or the I TLB are serviced by th e hardware page table walker which

supports the Itanium instruction s et architecture-defined 8B and 32B Virtual Hash Page Table

(VHPT) format. VHPT data is only cached on the L2 and L3 caches, not the L1D.

2.5.6.1 The Data TLB (DTLB)

The first level DTLB (DTLB1) perfo rms virtual to physical addr ess translations for load

transactions that hit in the L1 cache. It has two read ports and one write port. The TLB contains 32

entries and is fully associative. It s upports 4 KB pages, and can also support sub se ts of larger

caches in 4 KB subsec tions.

The second l evel DTLB (DTLB2) handles virtual t o physical address translations for data memory

references during stores, and protection checking on loads. It contains 128 entries and is fully

associative and can support architect ed page sizes from 4 KB to 4 GB. The DTLB2 contains four

ports. Of the 128 entries, 64 can be configured as Translatio n Registers (TR).

2.5.6.2 The Instruction TLB (ITLB)

The first level ITL B (ITLB1) is responsible for virtual to physical address translations to enable

instruction transaction hits in the L 1I cache. It is dual ported, contains 32 entries and is fully

associat ive. It supports 4 KB pages only.

The second level ITLB (IT LB2 ) is res pons ible for virtual to physical address translations for

instruction m emory references that miss the ITLB1. It contains 1 28 entries, is fully associative and

supports page s izes from 4 KB to 4 GB. Of the 128 entries, 64 can be configured as TR.

2.5.7 Cache Coherency

The three-level cache system makes it necessary to maintain the consistency of the data in the

different caches. Every read access to a memory address must always provide the most up-to-date

data at that address. Since the L1 is write-through it maintains a valid bit. The valid bit indicates

whether or not the cache line is valid. The L2 and L3 cache s use the MESI protocol to maintain

cache coh er e n cy.

2.5.8 Write Coalescin g

For increas ed performance of uncacheable references to frame buffers, the Wr ite Coalescing (WC)

memory type coalesces streams of data writes into a single larger bus write transaction. On the

Itanium 2 pr oc essor, WC loads ar e per f o rm ed di r ec tl y fro m m em o ry an d not from the coalescing

buffers.

On the Itanium 2 processor, a separate 2-entry, 128 byte buffer (WCB) is used for WC accesses

exclusively. Each b yte in the line has a valid bit. If all the valid bit s are true, then the line is said to

be full and will be evict ed (flushed) by the processor. Line evictions are initiated in a “first-written-

first-flushed” order even for partially full lines.

2-10 Intel® Itanium® 2 Process or Hard ware Develop er’s Manual

For increased performance to cacheable references to frame buffers or graphic controllers, the

Itani u m 2 processor allows external agents such as a graphics controller to read a line out o f t h e

processor’s cache witho u t altering the state of the cache line.

2.5.9 Memory Or dering

The Itanium 2 proces sor imple ments a relaxe d memory orde ring model t o enhanc e memory sys tem

performance. Memory transactions are ordere d with respect to visibility whereby visibility of a

transaction is defined as a point in time after which no later transactions may affect its operation.

On the Itan ium 2 processor, a tran saction is co n s i de r ed vi si ble when it hi ts th e L 1D ( if th e

instruction is serviceable by L1D), the L2, or the L3, or when it has reached the visibility point on

the system bus.

2.6 IA-32 Execution

The Itanium 2 processor supports IA-32 application binaries. This includes support for running a

mix of IA-32 applications and Itanium-based ap plications on an Itanium-based operating syste m

(OS), in both uniprocessor a nd multiprocessor configurations. The IA-32 engine is designed to

make use of the registers, caches, and execution resources of the EPIC machine. To deliver high

performance on legacy binaries, the IA-32 engine dynamically schedules instructions.

Itanium® 2 Processor Microarchitecture

Intel® Itanium® 2 Processor Hardware Developer’s Manual 2-11

Itanium® 2 Processor Microarchitecture

2-12 Intel® Itanium® 2 Process or Hard ware Develop er’s Manual

System Bus Overv iew 3

This chapter pro vides an overvi ew of the Itani um 2 proce ssor system bus , bus tr ansact ions, and bus

signals. The Itanium 2 processor also supports signals not discussed in this section. For a com plete

signal listing, please refer to the Intel

and Appendix A, “Signals Reference”.

3.1 Signali ng on the Itanium® 2 Processor System Bus

The Itanium 2 processor syst em bus supports common clock signaling as well as source

synchronous data signaling. Section 3.1.1 and Section 3.1.2 describe in detai l the characteristics of

each type of sign aling. The co rrespo nding tim ing figu res us e squ are, tr iangle , and c ircle symbols to

indicate the point at which signals are driven , received, and sampled, respectively. The square

indicates that a signal is driven (asserted or deasser ted) in that cloc k. The triangle indicates that a

signal is received on or before that point. The circle indicates that a signal is sampled (observed,

latched, captured) in that clock. Black bars indicate zero or more clocks are al lowed.

All timing diagrams in this speci f ication show signals as they are asserted o r deasserted. There is a

one-clock del ay in the signal values obser ved by system bus agents. Any signal names that appear

in lowercase letters in brackets {rcnt} are internal signals only, and are not driven to the bus.

Internal state s change one clock after s am pling a bus signal, which is the clock after the bus s ignal

is driven. Uppercase lette rs that appear in brackets represent a group of signals such as the Request

Phase signals [REQUEST]. The timing diagrams sometimes include internal signals to indicate

internal sta tes and show how it affects external signals. Internal states change one clock after

sampling a bus signal. A bus signal is sampled one cl ock after the bus signal is dri ven.

®

Itanium® 2 Processor at 1.0 GHz and 900 MHz Datasheet

3.1.1 Common Clock Signali ng

All signals except the data bus signals on the system bus use a synchronous common clock latched

protocol (1x transf er rate). On the rising edge of the bus clock, all agents on the system bus are

required to drive their active outputs and sample required inputs. No additional logic is located in

the output and input paths betwee n the buf f er and th e la tch s tage, thus keepin g setu p and hold tim es

constant for all bus si gnals following the la tched protocol. The syst em bus requires that (1) every

input be sampled dur ing a valid sampling window on a risin g clock edge and, (2) its eff ect be

driven out no sooner than the next rising clock edge. This approach allows one full cl ock for

driving a signal, flight time, and setup as w ell as at least on e f ull clock at the receiver to compute a

response.

Figure 3-1 illustrates the latched bus protocol as it appe ars on the bus. In later descriptions, the

protocol is desc ribed as “B# is asserted in the clock after A# is observed asserted,” or “B# is

asserted two clocks after A# is asserted .” Note that A# is asserted in T1, but not observed asser ted

until T2. A# has one full clock to propagate (indicated by the straight line with arrows) before it is

observed assert ed. The receivin g age nt uses T 2 to deter mine it s respons e and a sserts B# in T 3 i. e. it

has one full clock cycle from the time it observes A# asserted (at the ri sing edge of T2) to the time

it computes its response (indicated by the curved line with the single ar row) and drives this

response at the rising edge of T3 on B#. Simil arly, an agent observes A# asserted at the rising edge

of T2, and uses the full T2 clock to comput e its respo nse (indi cate d by the lowermos t curved arr ow

during T2). This response would be driven at the rising edge of T3 (not shown in Figure 3-1) on

{c} signals. Although B# is drive n at the ris ing edge of T3, it has the full cloc k T3 to propaga te. B#

is observed asserted in T4.

Intel® Itanium® 2 Processor Hardware Developer’s Manual 3-1

System Bus Overview

Figure 3-1. C om mon Clock Latched Protocol

Full clock allo w ed

for signal propagation

T1 T2 T3 T4

CLK

BCLKp

BCLKn

A#

B#

Assert A#

Latch A#

Full clock allowed

for logic delay s

Assert B#

Change internal state

T5

1100{c}

Latch B#

Signals tha t ar e driv en i n the sa me cl ock by m ultipl e sys t em bus a gents exhibi t a “wired-OR gli tch”

on the ele ctrical low to el ectrica l h ig h tr an si ti o n . To accoun t fo r this sit u ation, th e se s i gn a l state

transitions are specified to have two clocks of settling ti me when deasserted before they can be

safely observed, as shown with B#. The bus signals that must meet this criterion are: BINIT#,

HIT#, HITM # , BN R# , TND #, BERR # .

3.1.2 Source Synchronous Signaling

The data bus operates with a source synchronous latched protocol (2x trans fer rate). The source

synchronous la tched prot ocol (refer to Figure 3-2) sends and latches data with str obes t o allow v ery

high transfe r rate s with reasonable signal f light times. The rest of the sy st em bus always uses the

common clock latched protocol.

The source synchronous latched protocol operates the data bus at twice the “frequency” of the

common clock. Two chunks of data are driven onto the bus in the time it would normally take to

drive one chunk. The worst case flight time is simil ar to the common clock latched protocol, so the

second data tra ns f er m ay be driven before the first is latch ed. On both the rising edge and 50%

point of the bus cl ock, drivers send new data. On both the 25% point and the 75% point of the bus

clock, drivers send centered differential strobes. The receiver captures the data with the strobes

deterministically.

3-2 Intel® Itanium® 2 Process or Hard ware Develop er’s Manual

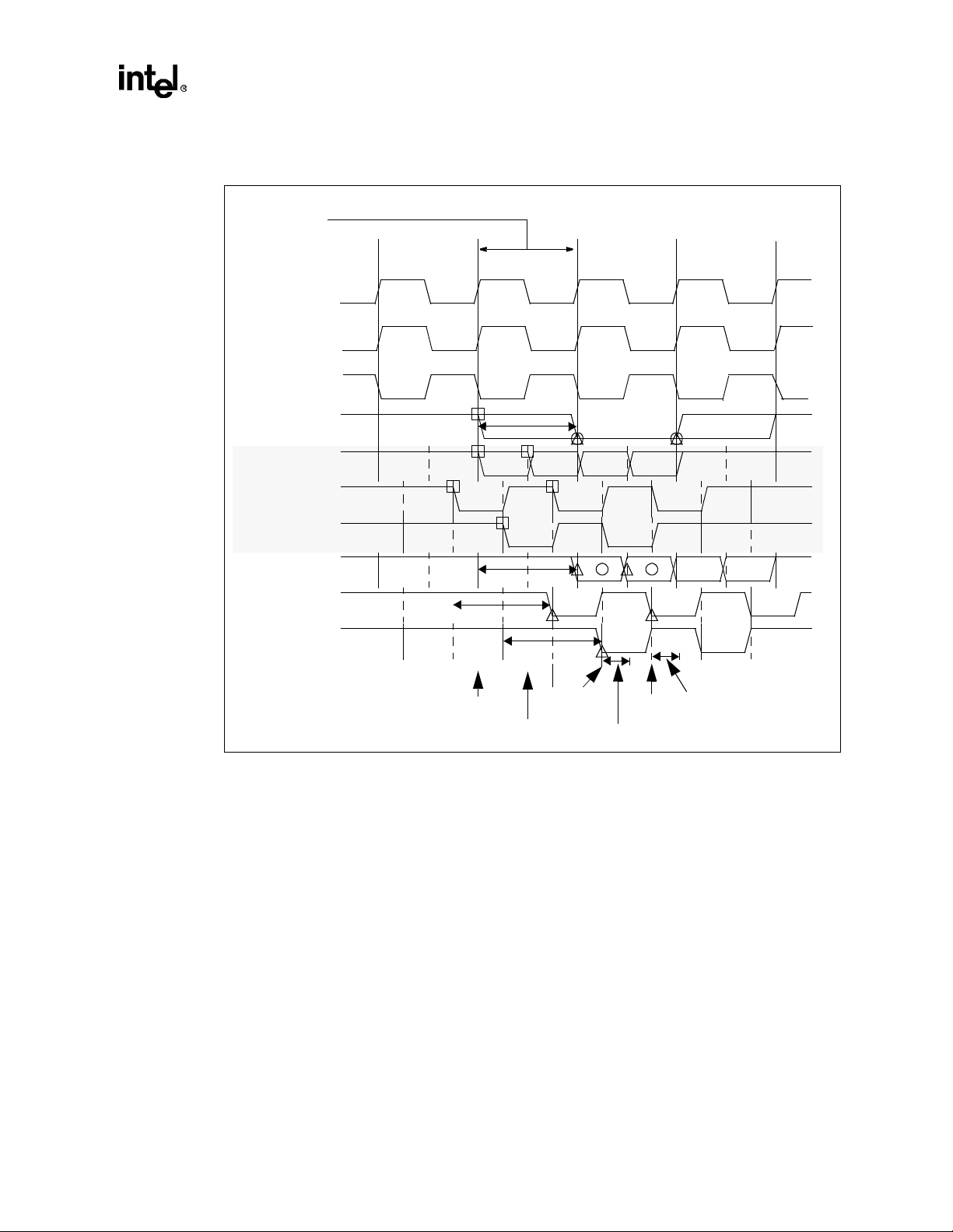

Figure 3-2. So urc e S y nchronous Lat ched Proto col

Full clock allowed

for signal propaga tio n

System Bus Overview

CLK

BCLKp

BCLKn

DRDY#

D# (@driver)

STBp# ( @ driver)

STBn# ( @ driver)

D# (@receiver)

STBp# (@receiver)

STBn# (@receiver)

T1

T2

D1 D2 D3 D4

Capture

Drive D1

Drive D2

T3

D1 D2 D3 D4

D1

Capture

Latch D1

Latch D2

D2

T4

The driver pre-drives S TBp# before driving data. It sends a rising and falling edge on STBp # and

STBn# centered with data. The driver must deassert all strobes after the last data is sent. The

receiver capt ures valid d ata wit h t he dif fe rence of bot h str obe si gnals , async hrono us to the com mon

clock. Data will be latched into the core within one core-cycle after being captured. A signal

synchronous to the common cl ock (DRDY#) indicates to the recei ver that valid data has been sent .

3.2 Signal Overview

This section describes the function of various Itanium 2 processor signals. In this section, the

signals are group ed according to function. For a complete signal list ing, please refer to the Intel

Itanium

Intel® Itanium® 2 Processor Hardware Developer’s Manual 3-3

®

2 Processor at 1.0 GHz and 900 MHz Datasheet.

®

System Bus Overview

3.2.1 Control Signals

The control signals, shown in Table 3-1, ar e us ed to con t r o l ba si c op e r at io n s of th e p r oc essor.

Table 3-1. Control Signals

Signal Function Signal Names

Positive Phase Bus Clock BCLKp

Negative Phase Bus Clock BCLKn

Reset Processor and System Bus Agents RESET#

Power Good PWRGOOD

The Positive Phase Bus Clock (BCLKp) input s ignal is the positive phase of the system bus clock

diffe rent ia l pair. It is also r efe rre d to as CL K in some of th e wa vef orms i n th is ove rvi ew. It specifie s

the bus frequency a nd clock period and is used in the signaling scheme. Each proc essor derives its

internal cl ock from CLK by multiplying the bus freq uenc y by a multiplier determined at

configuration. See Chapter 5, “Configuration and Initialization” for further deta ils.

The Negative Phase Bus Clock (BCLKn) input signa l is the negative phase of the system bus cloc k

differential pair.

The RESET# signal res ets all system bus agents to known states.

Note: The RESET# signal itself does not invalidate the internal caches in th e I tanium 2 processor. A

subsequent PAL call is used to invalidate all internal caches in the Itanium 2 processor. Modified or

dirty cache line s are NOT writ ten back. After RESET# is deasserted, each processor begins

execution at the power-on reset vect or defined during configura tion.

The Power Good (PWRGOOD) input signal must be deasserted during power-on and be as serted

after RESET# is first asserted by the system.

3.2.2 Arbitr ation Signals

The arbitration signals, shown in Table 3-2, are used to arbitrate for ownership of the bus, a

requirement for initiating a bus transaction.

Table 3-2. Arbitration Signals

Signal Function Signal Names

Symmetric Agent Bus Request BREQ[3:0]#, BR[3:0]#

Priority Agent Bus Request BPRI#

Block Next Request BNR#

Lock LOCK#

BR[3:0]# are the physical pins of the processor. All processors assert only BR0#. BREQ[3:0]#

refers to the syste m bus arbitration signals among four processors. BR0# of each of the four

processors is connected to a unique BREQ[3:0]# sign al.

Up to five agent s can simu ltane ously a rbit rate fo r the requ est bu s, one to fou r sy mmetric agents (on

BREQ[3:0]#) and one priority agent (on BPRI#). Processors arbitrate as symmetric agents, while

the priority agent normally arbitrates on behalf of the I/O agents and memory agents. Owning the

request bus is a necessary pre-condition for initiating a transaction.

3-4 Intel® Itanium® 2 Process or Hard ware Develop er’s Manual

The symmetric agents arbitrate for the bus based on a round-robin rotating priority scheme. The

arbit ration is fair and symmetric. A symmetric agent re q u ests the bus by asserting its BR EQ n#

signal. Base d on the values sampled on BREQ[3: 0]#, and the last symmetr ic bus owner, all agents

simultaneously determine the next symmetric bus owner.

The priority agent asks for the bus by asserting BPRI#. The assertion of BPRI# temporarily

overrides, but does not otherwise alter the symmetric arbitration scheme. When BPRI# is sampled

asserted, no symmetric agent issues another unlocked transaction until BPRI# is sampled

deasserted. Th e priority agent is always the next bus owner .

BNR# can be asserted by any bus ag ent to block further transac tions from being issued to the

request bus. It is typic ally asserted when system resources, such as address or data buffers, are

about to become temp orarily busy or filled a nd cannot accommodat e anothe r trans acti on. After bus

initialization, BNR# can be asserted to delay the first transaction until all bus agent s are initia lized.

LOCK# is never asserted or sampled in the Itanium 2 processor system environm ent.

3.2.3 Request Signals

The request signals, shown in Table 3-3, are used to initiate a transaction.

Table 3-3. Request Signals

Signal Fun cti on Signal Nam es

Address Strobe ADS#

Request REQ[5:0]#

Address A[49:3]#

Address Parity AP[1:0]#

Request Parity RP#

System Bus Overview

The assertion of ADS# defines the beginning of the tran sa ction. The REQ[5:0]#, A[49:3]#,

AP[1:0]#, and RP# are valid in the clock that ADS# is asserte d.

In the clock tha t ADS# i s ass erted , the A[ 49:3 ]# sign als pr ovide a n act ive-low a ddress as part o f th e

request. The low three bits of address are mapped into byte enable signals for 0 to 8 byte transfers.