Page 1

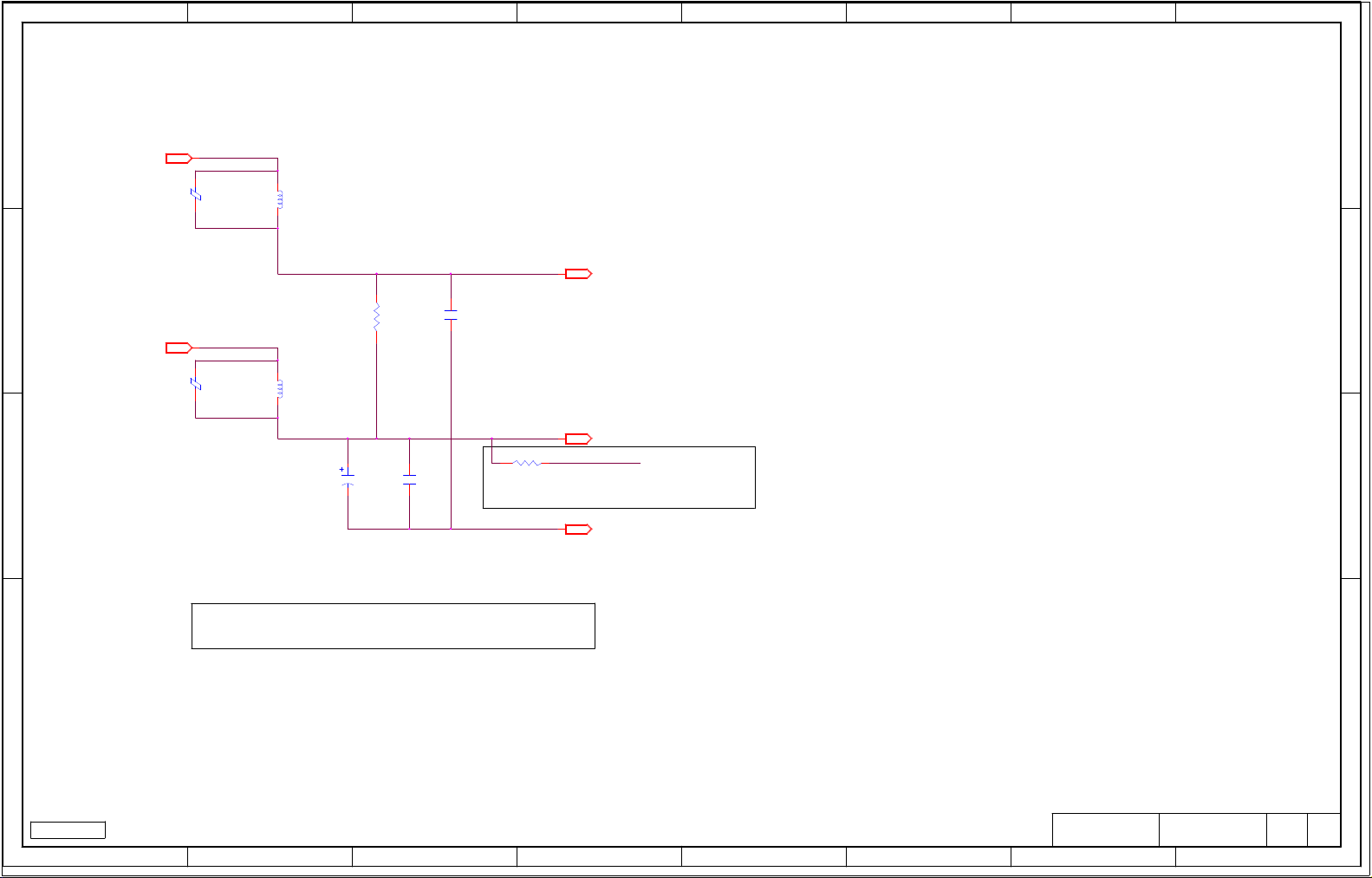

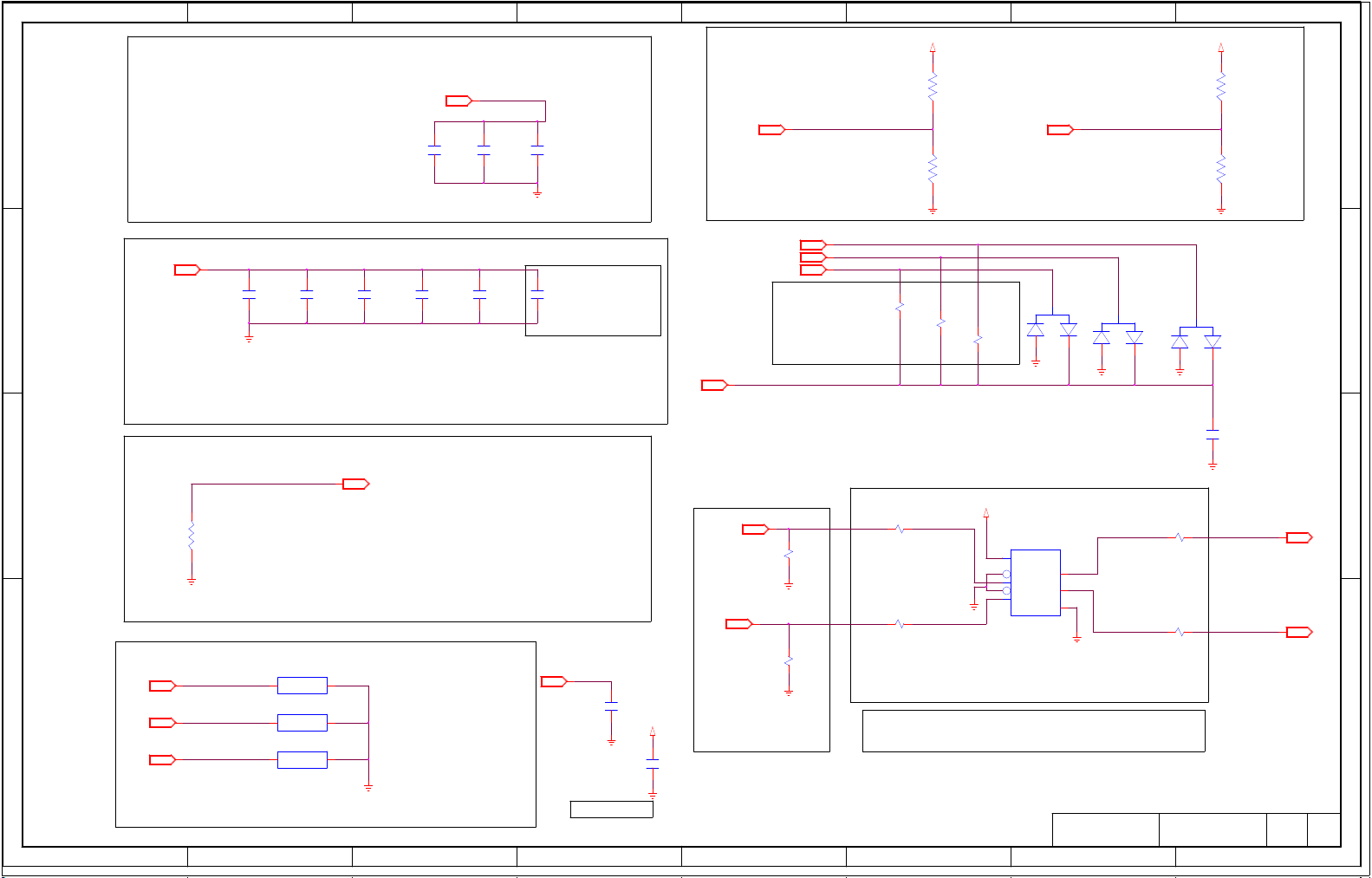

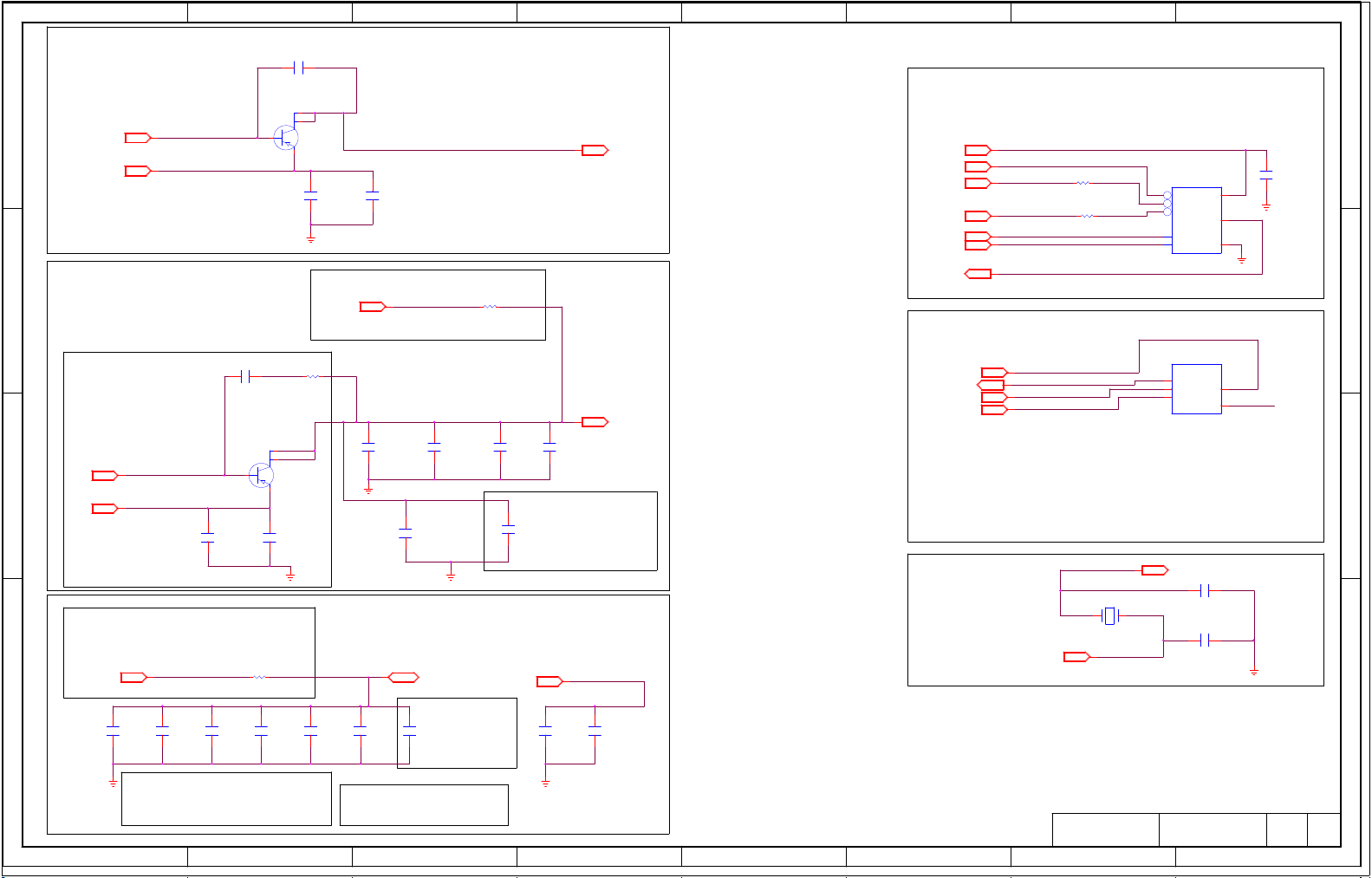

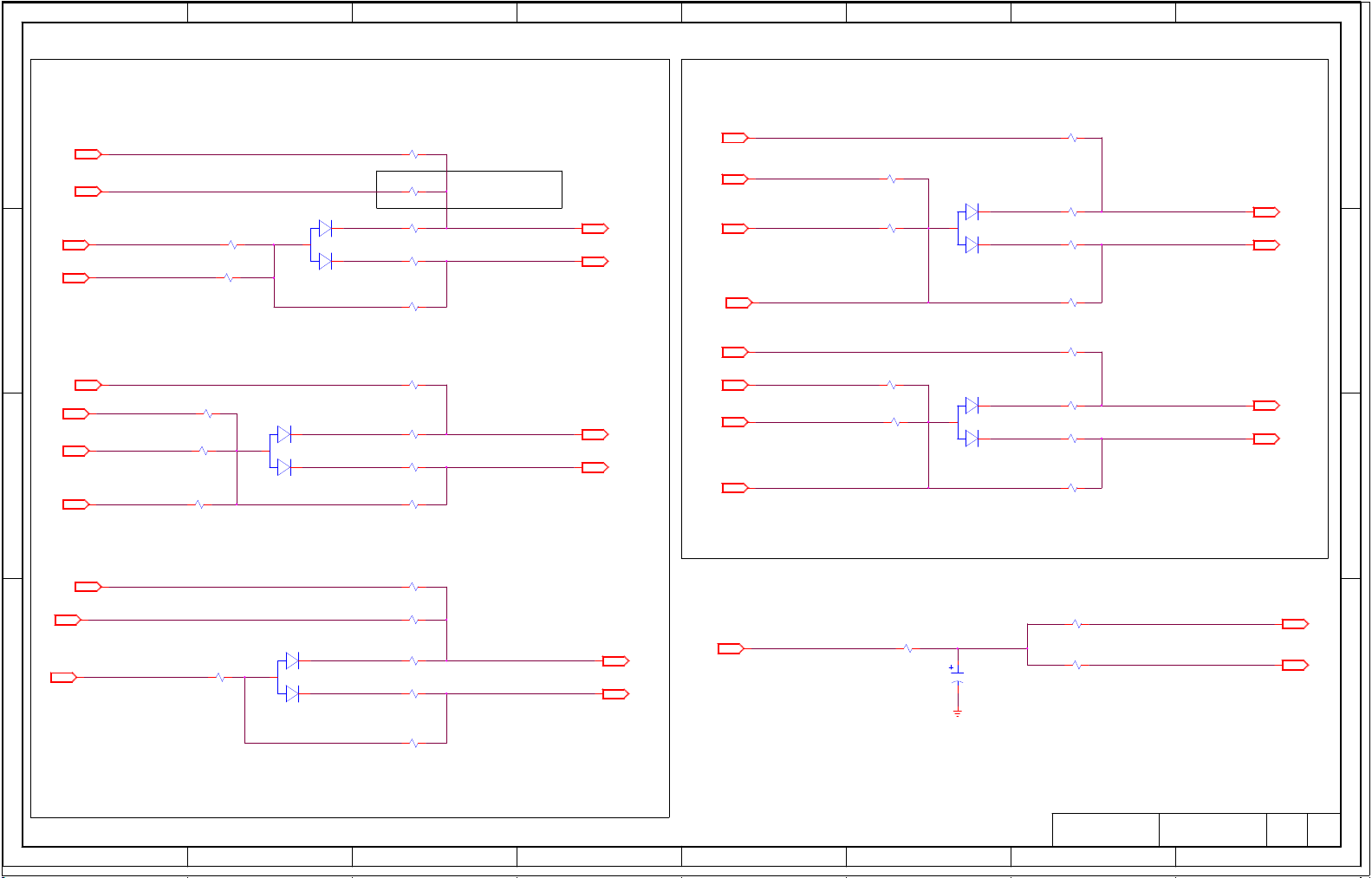

<XR_PAGE_TITLE>

28 7 6 5 4 3 1

PAGE #

COMPONENT/FUNCTION

[1. INDEX]

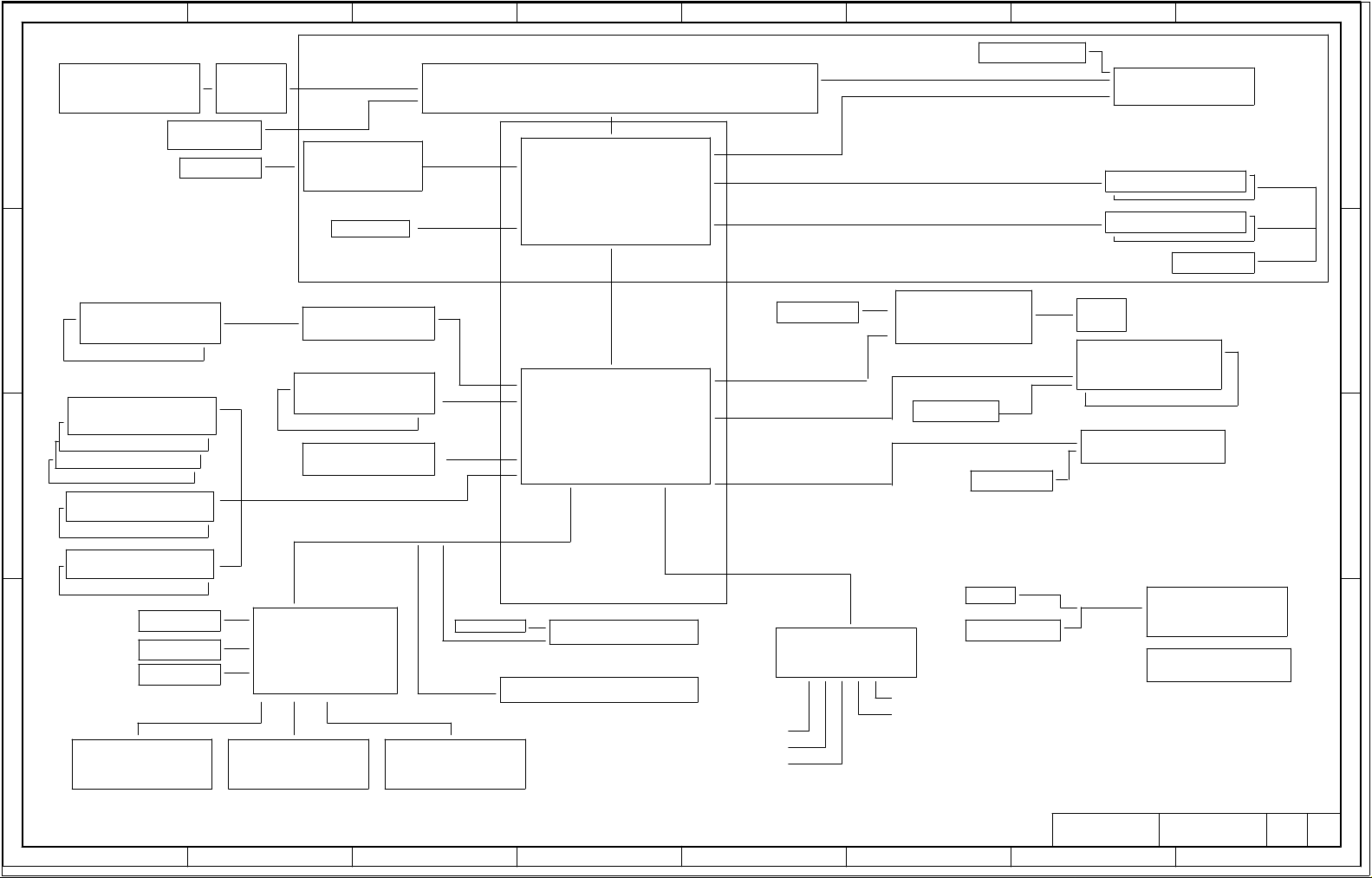

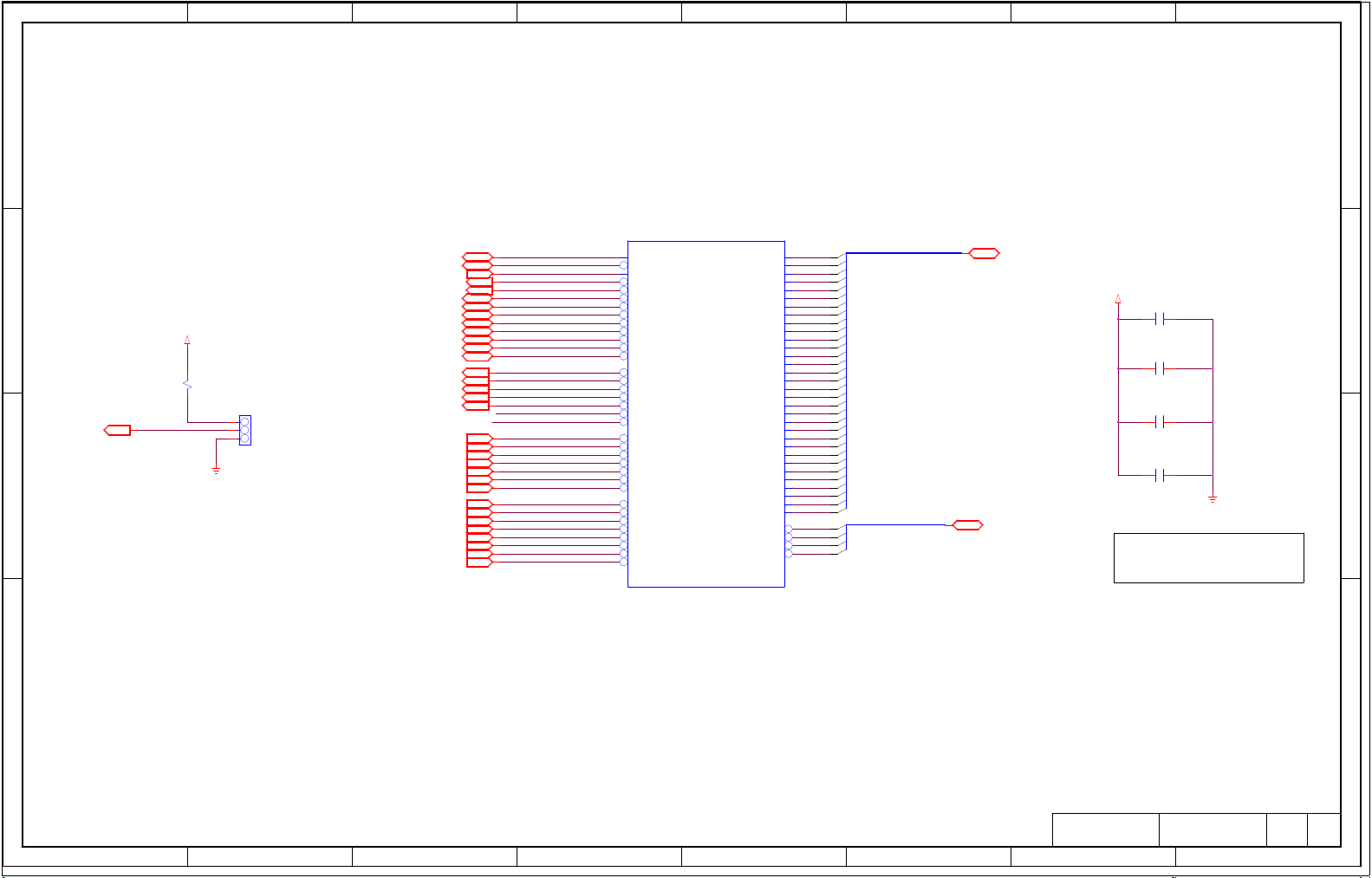

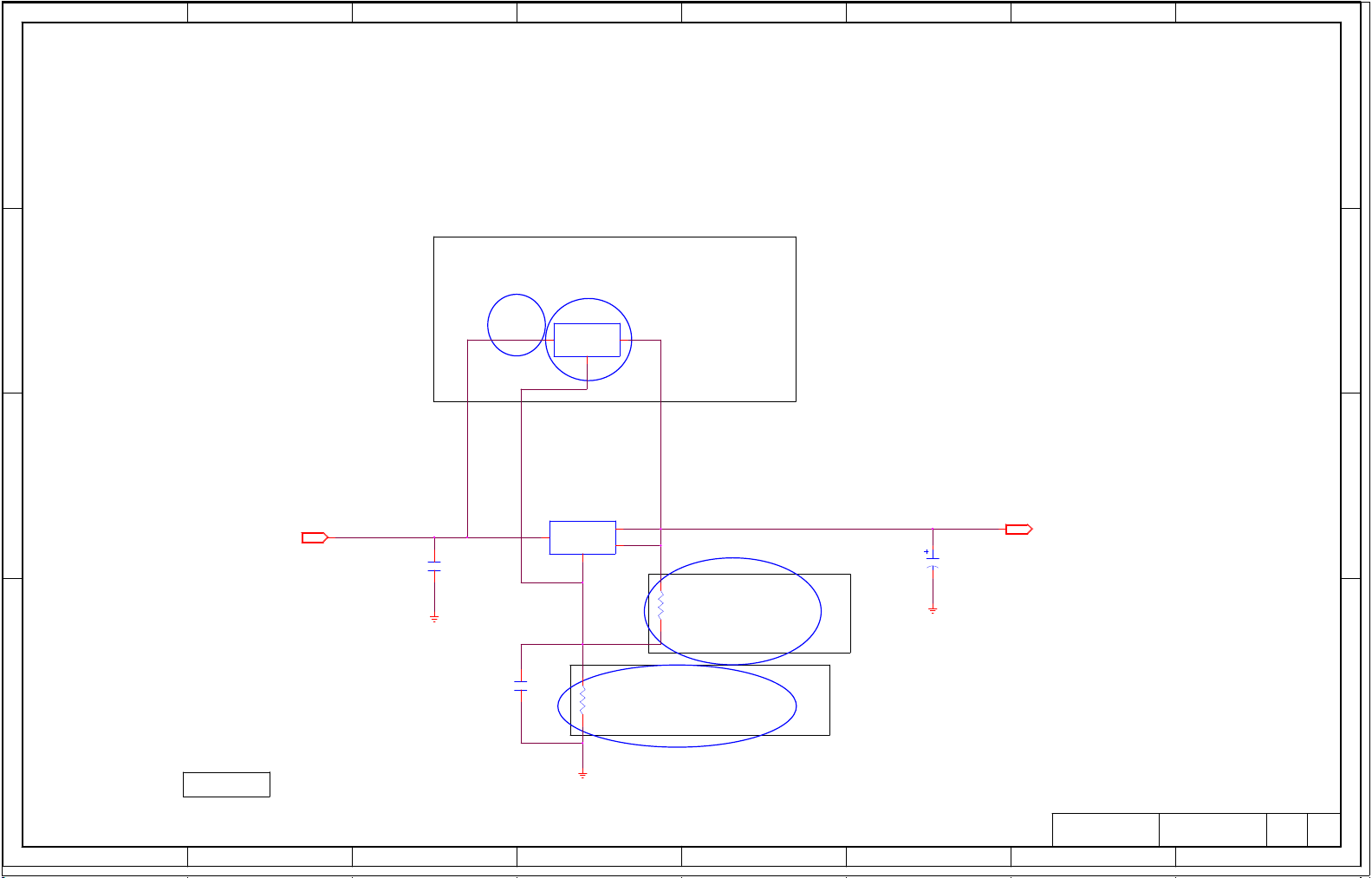

[2. BLOCK DIAGRAM]

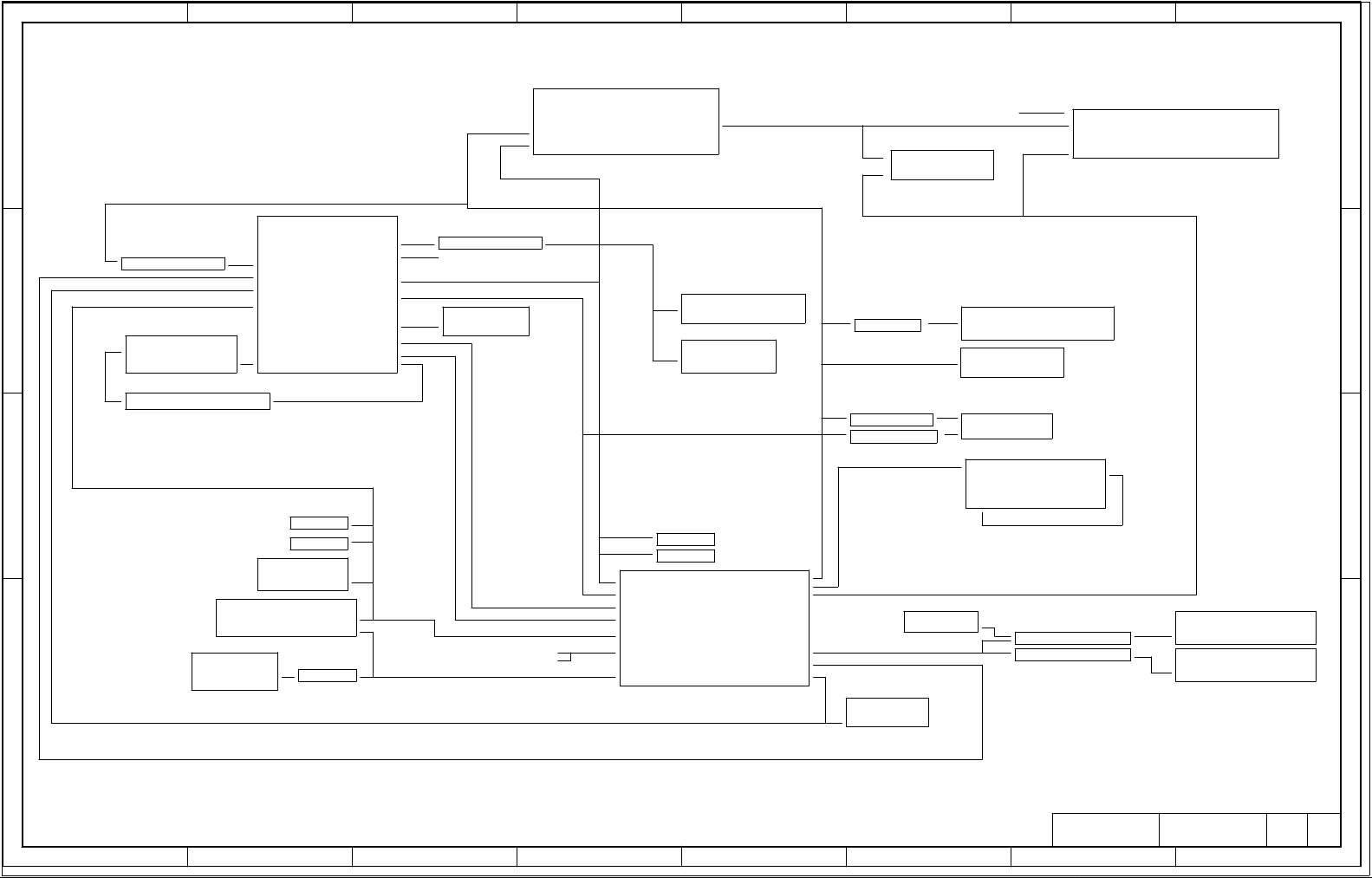

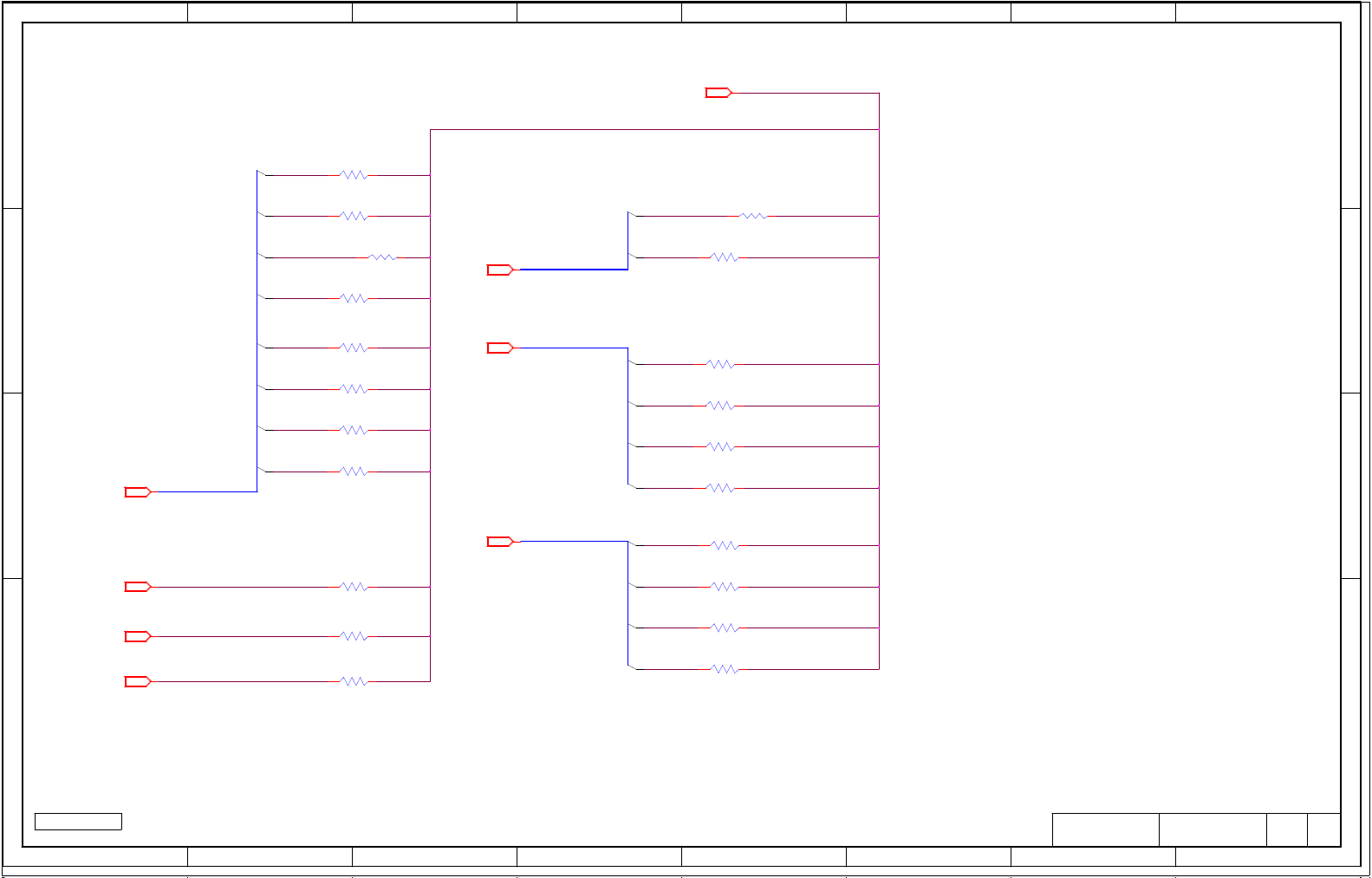

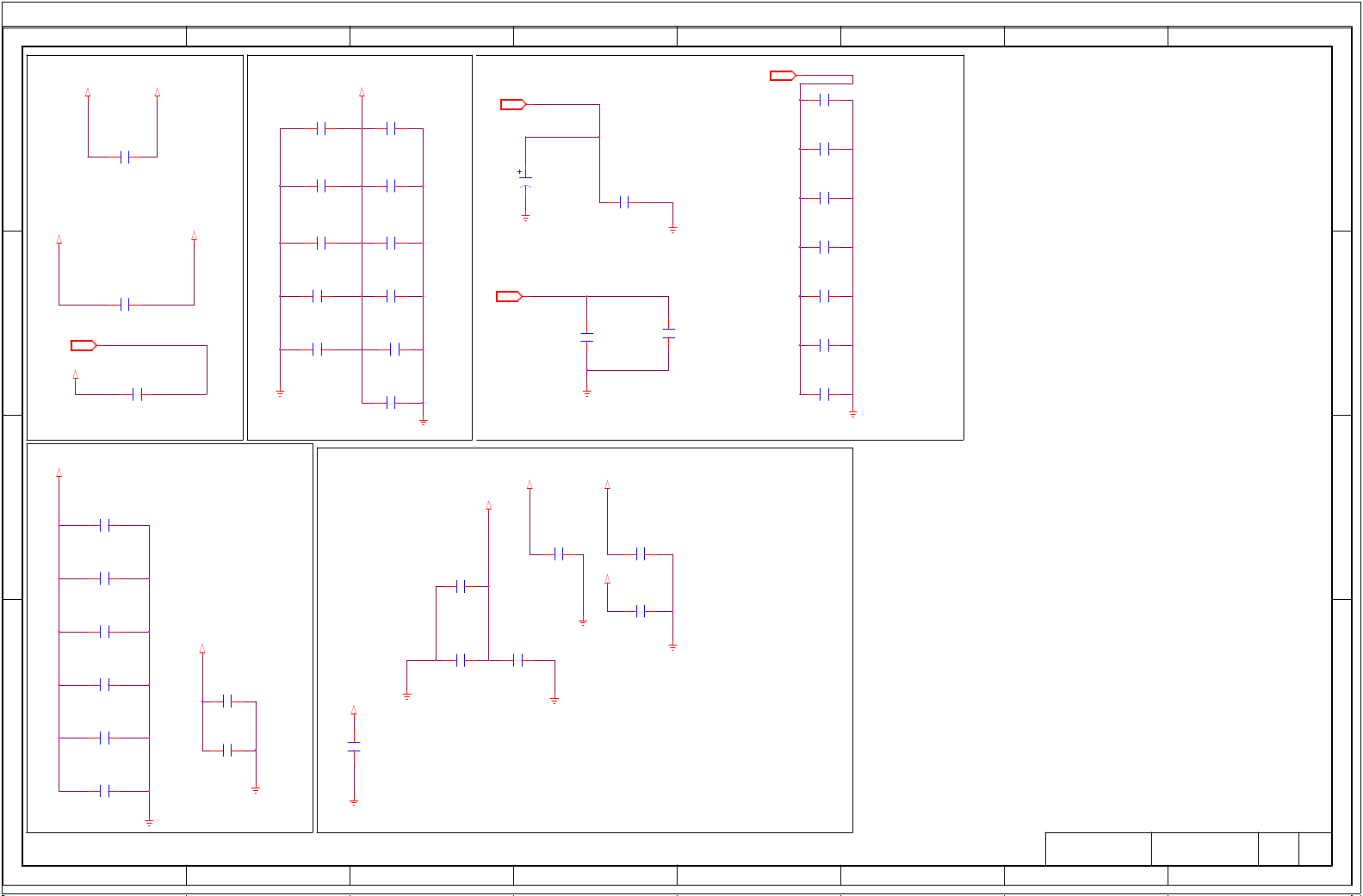

[3. RESET MAP]

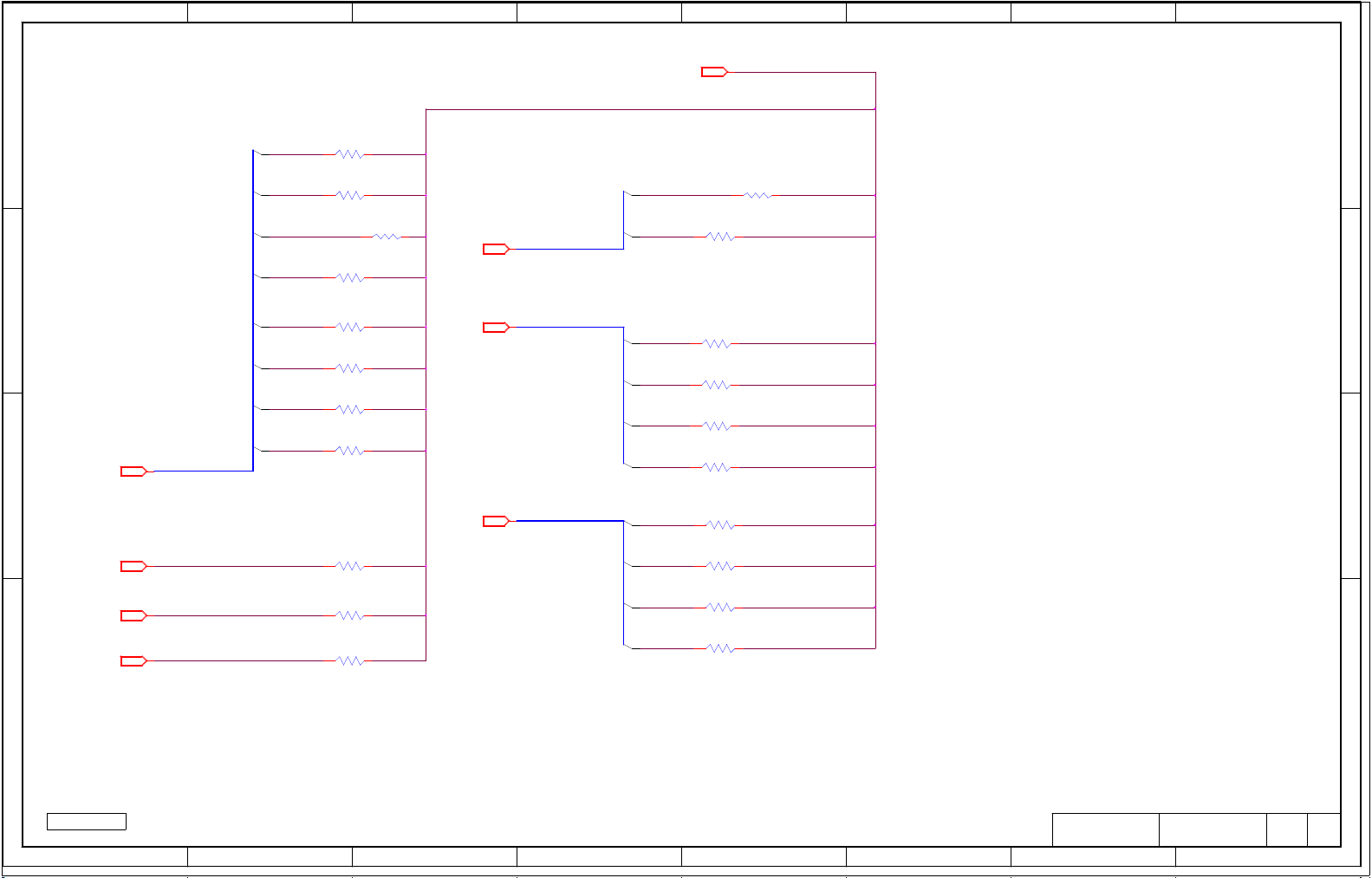

D

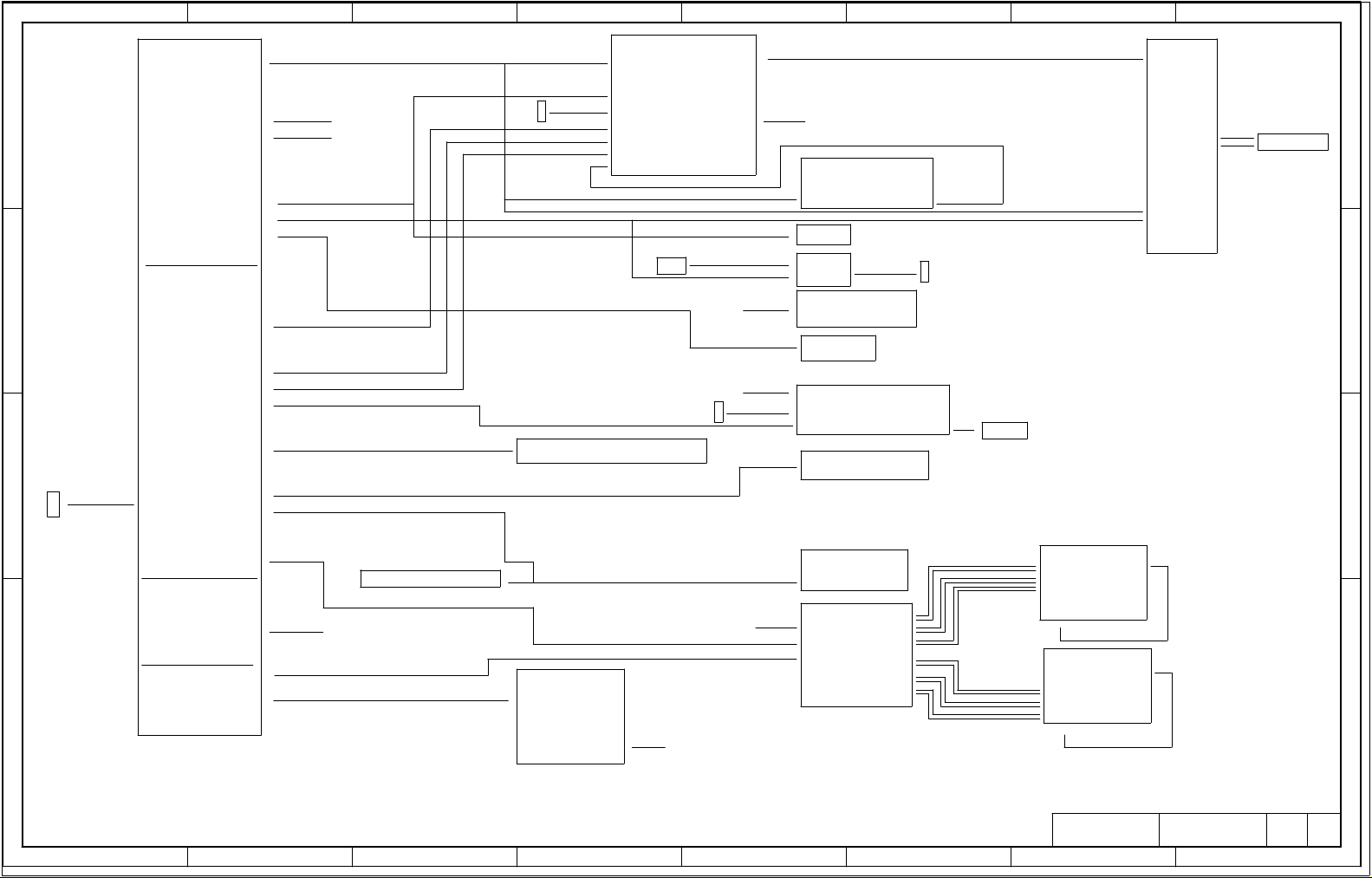

[4. CLOCK DISTRIBUTION]

[5. GPIO, IRQ, IDSEL MAP]

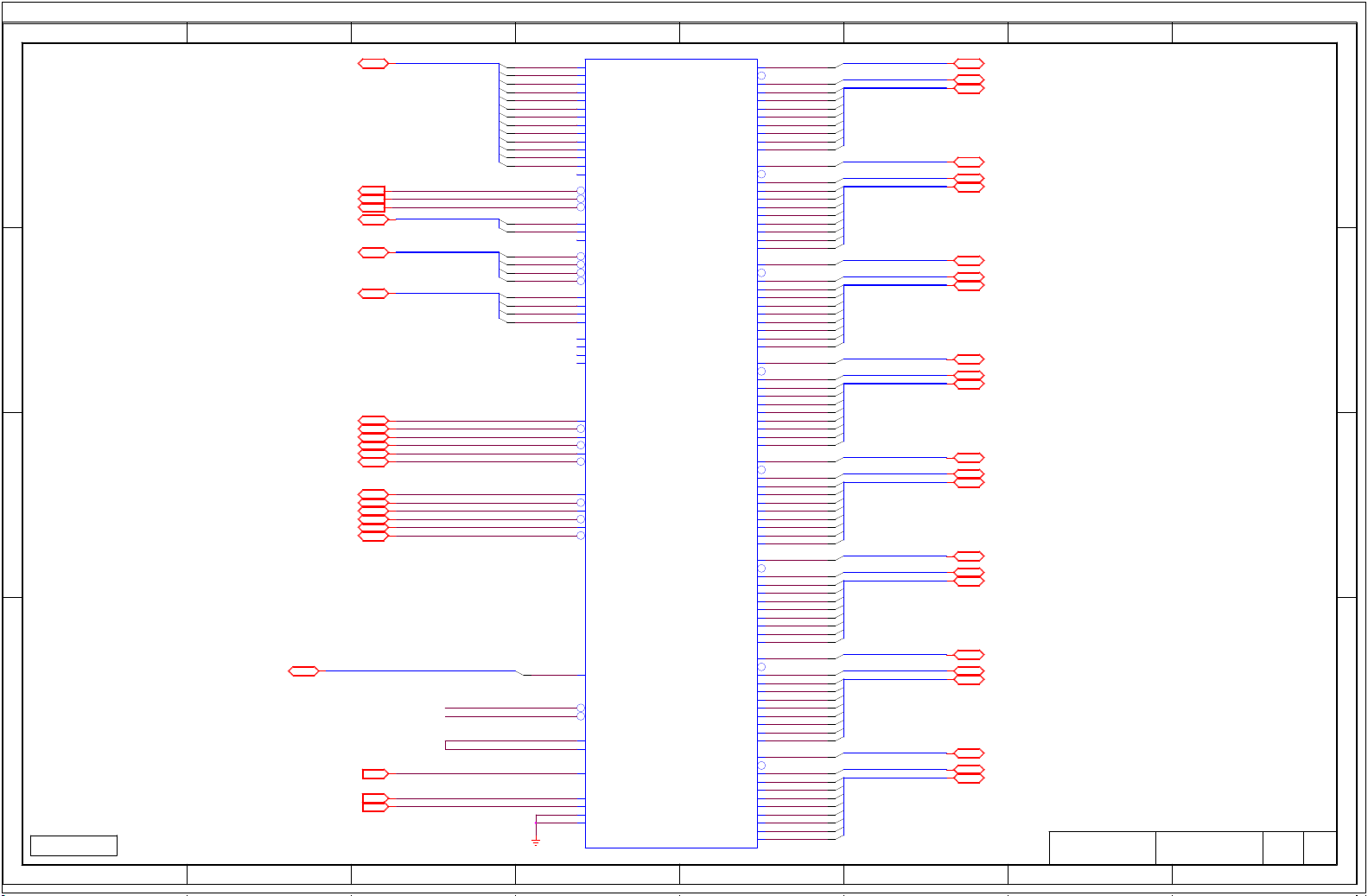

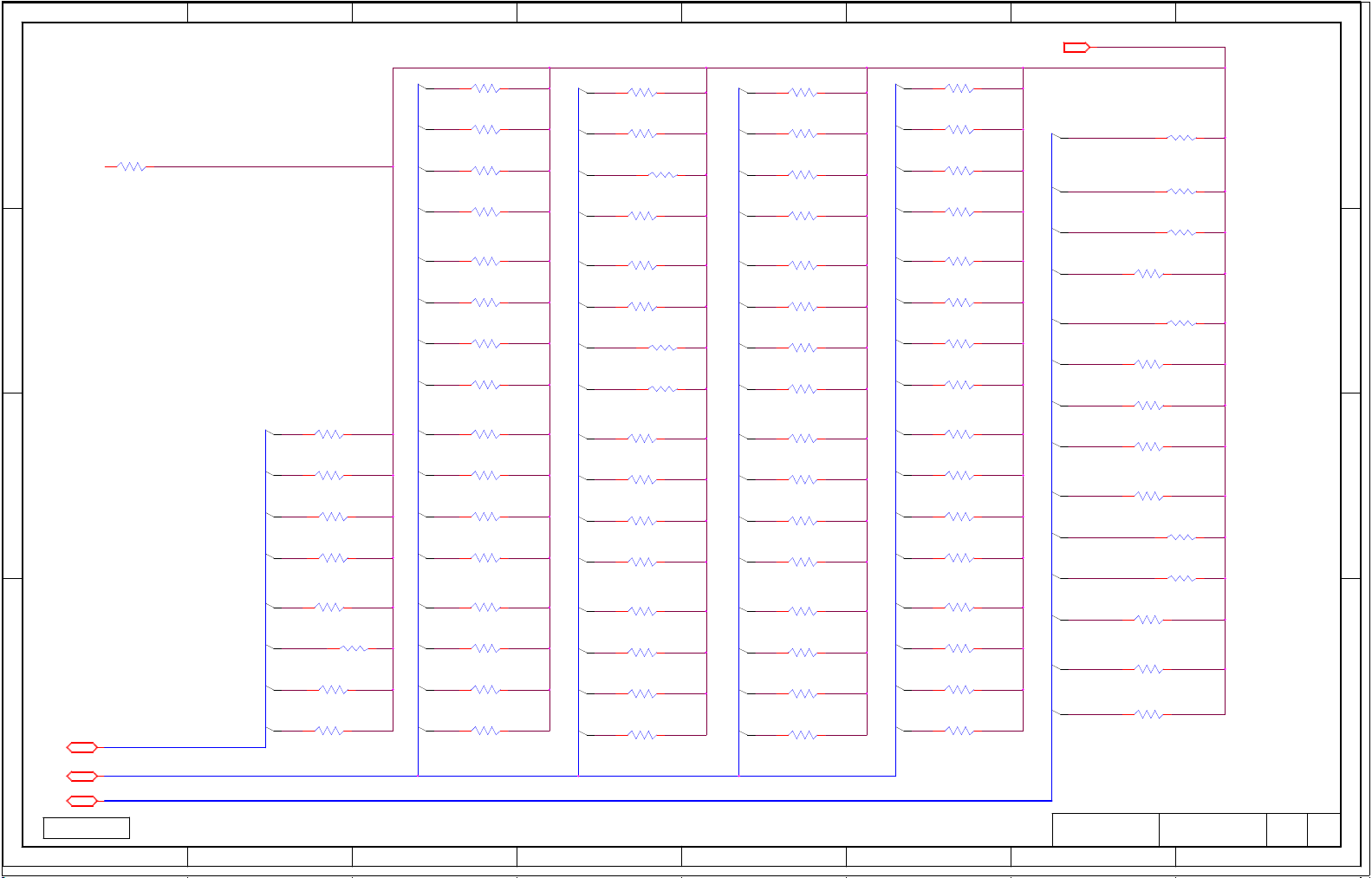

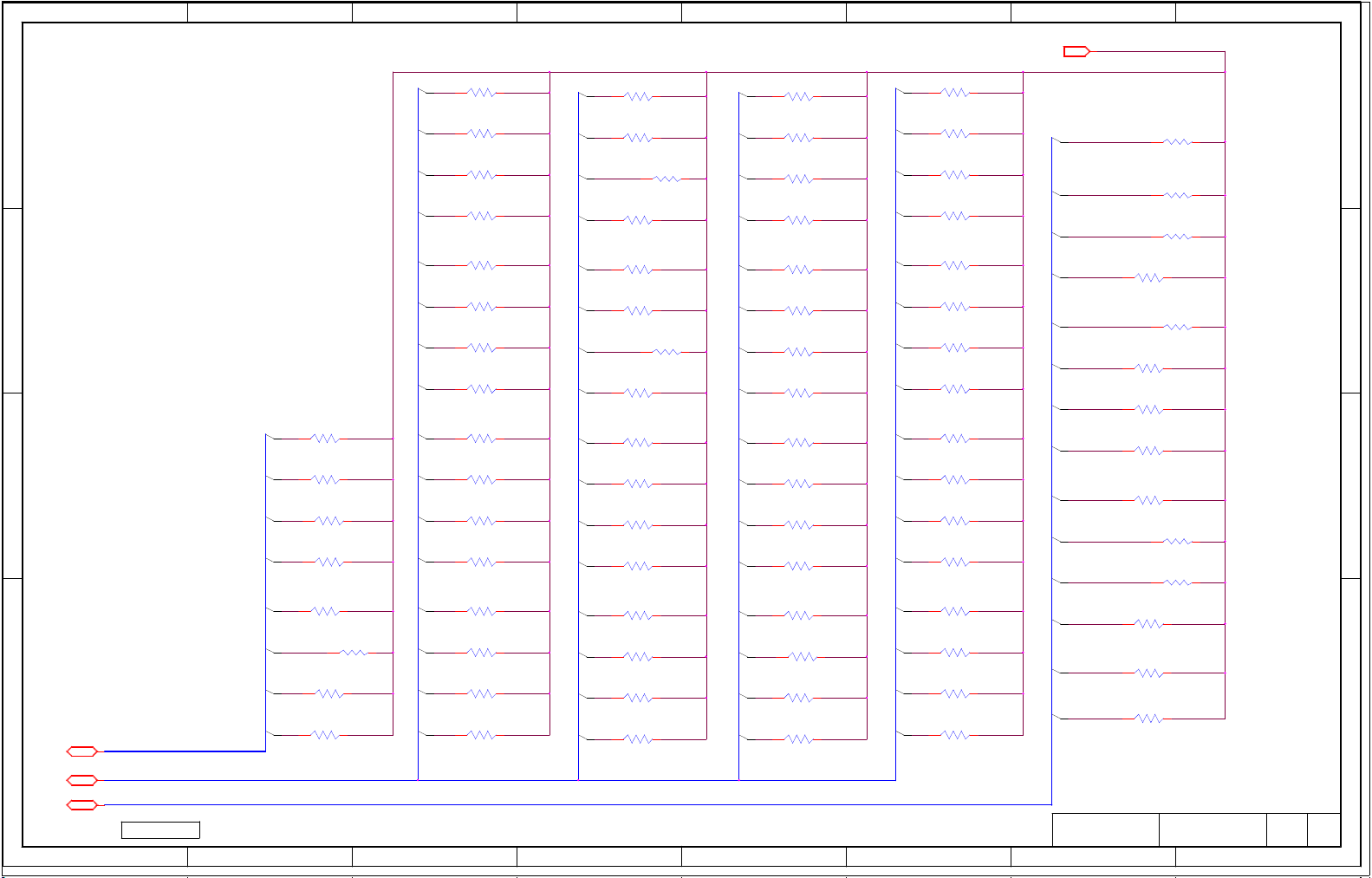

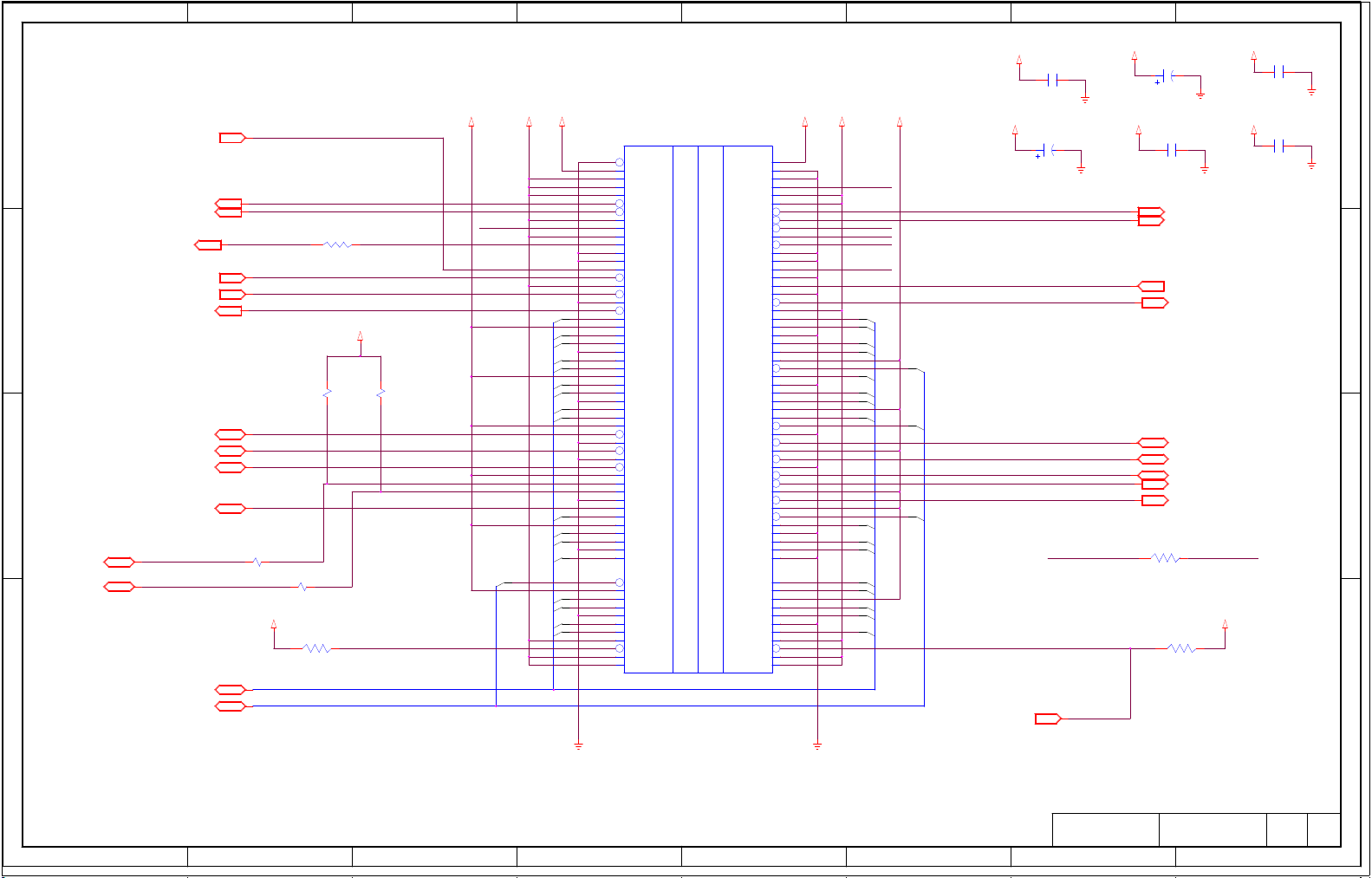

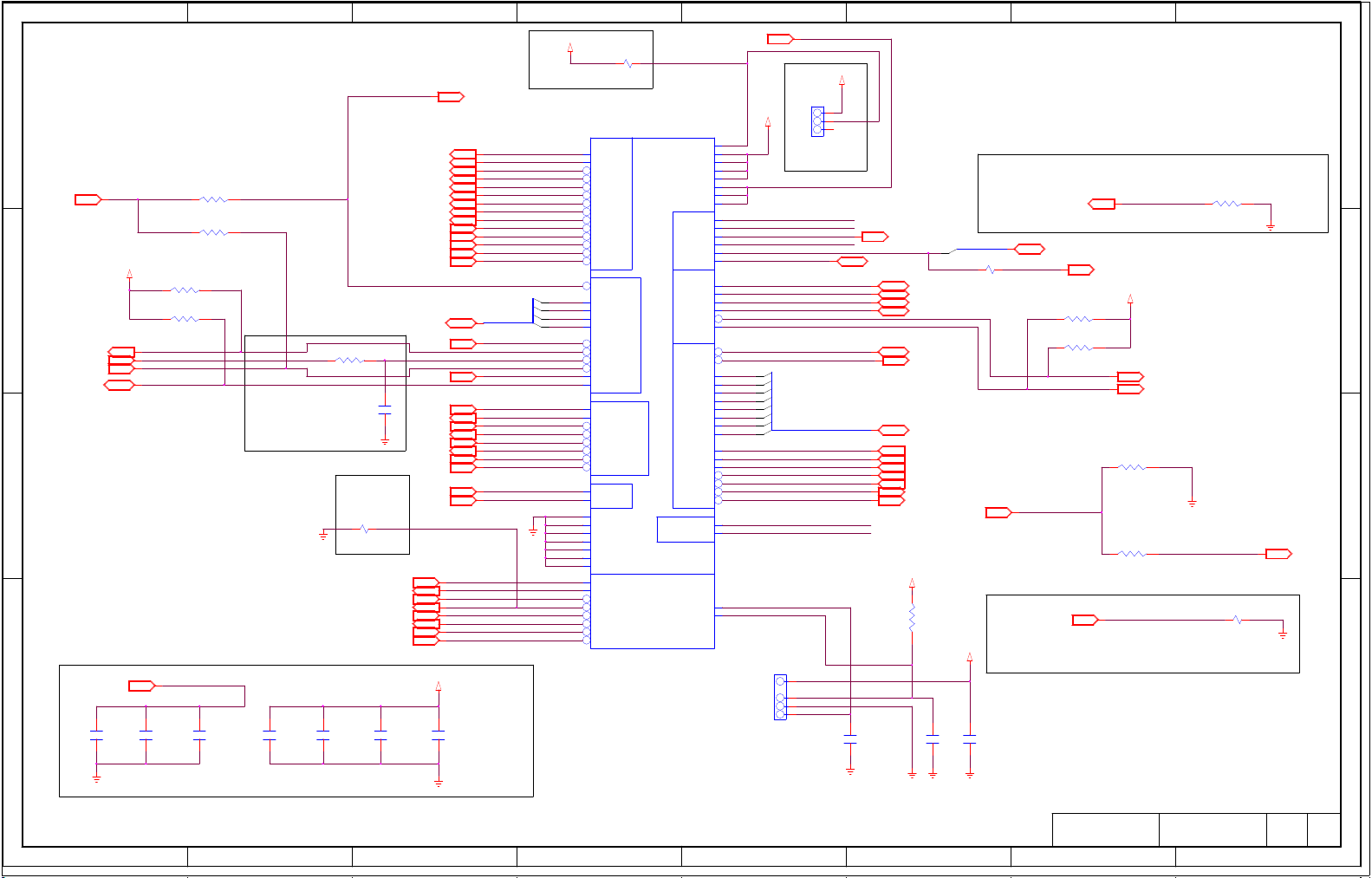

[6. CPU-SOCKET]

[7. CPU-SOCKET]

[8. CPU TERMINATION & MISC P/U P/D]

[9. CPU-VCCP FILTERED ANALOG SUPPLY]

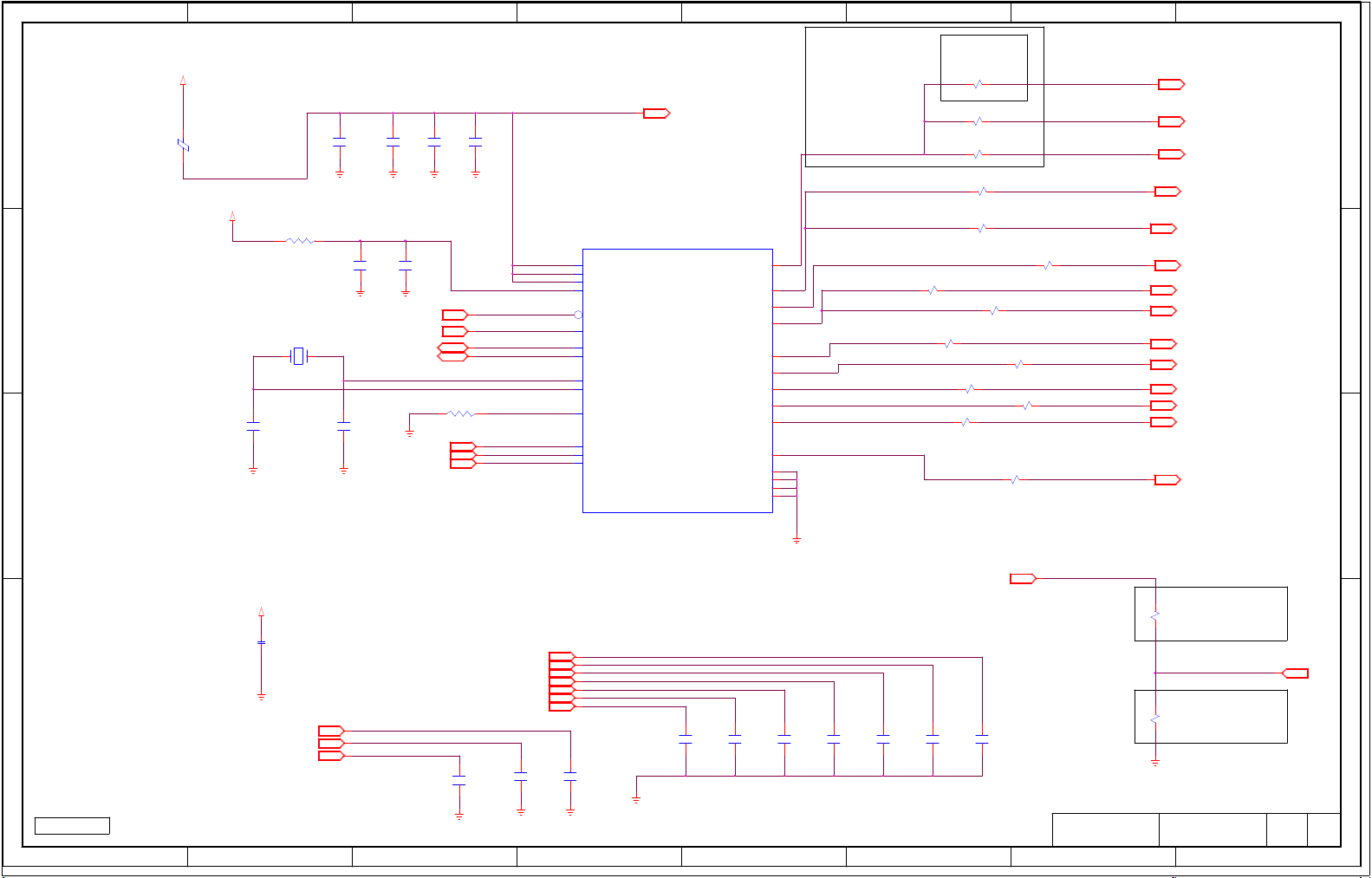

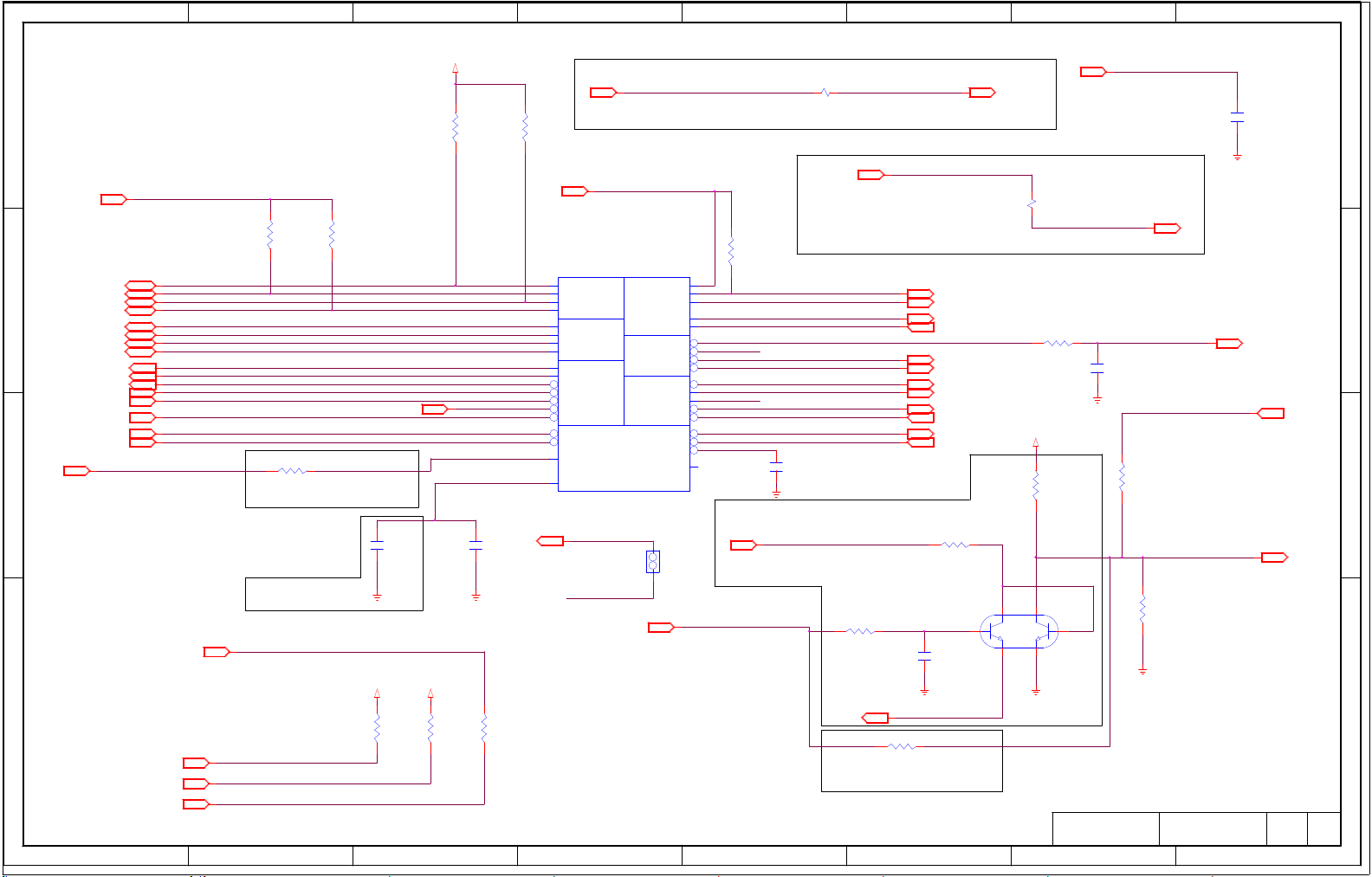

[10. MCH SECTIONS PAGE 1 OF 6]

[11. MCH SECTIONS PAGE 2 OF 6]

[12. MCH SECTIONS PAGE 3 OF 6]

[13. MCH SECTIONS PAGE 4 OF 6]

[14. MCH SECTIONS PAGE 5 OF 6]

[15. MCH SECTIONS PAGE 6 OF 6]

C

[16. MCH 2P5_DAC & 1P5 FILTER]

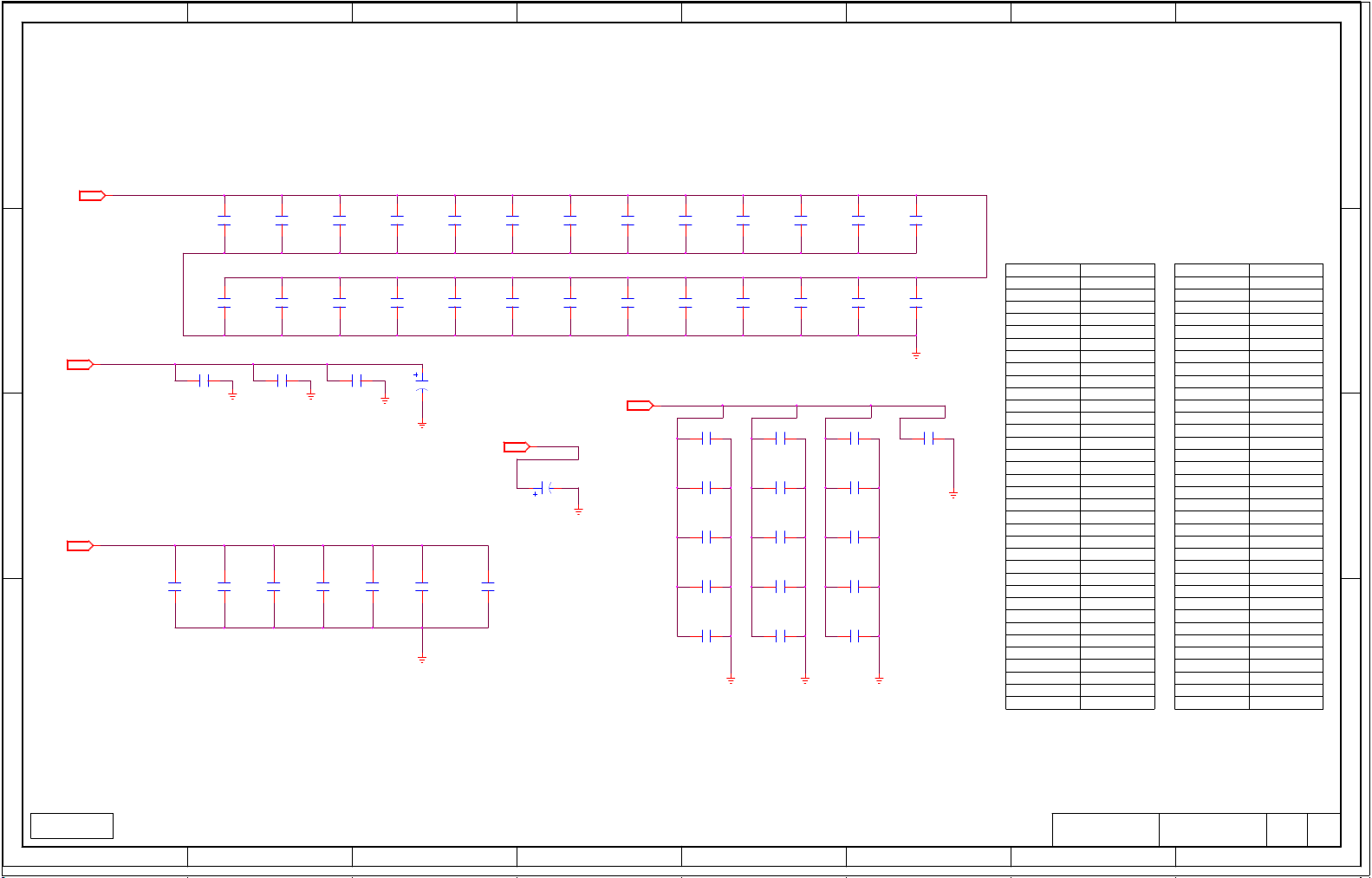

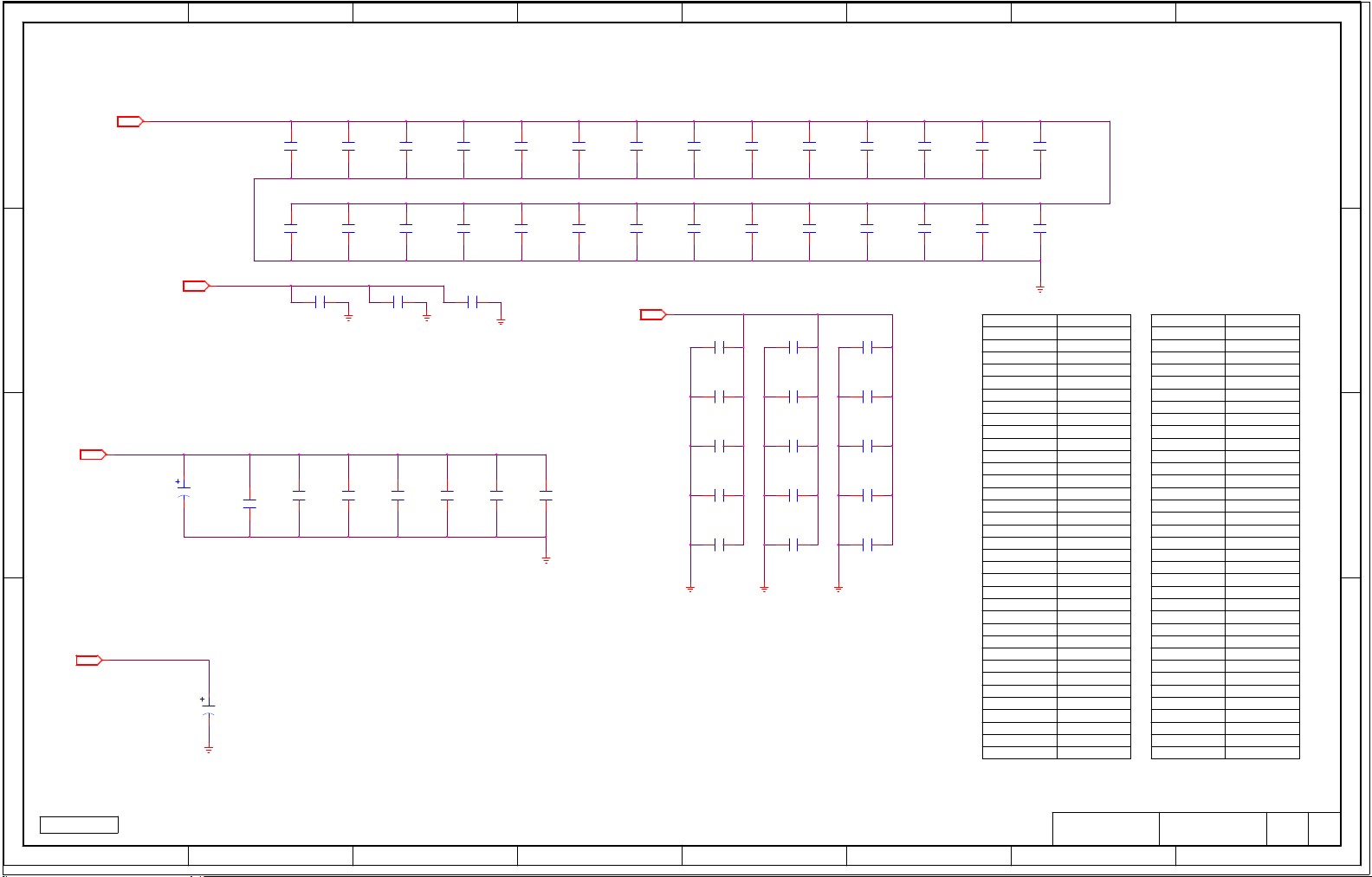

[17. MCH DECOUPLING AND COMP]

[18. MCH DCPL & VGA TERMINATION]

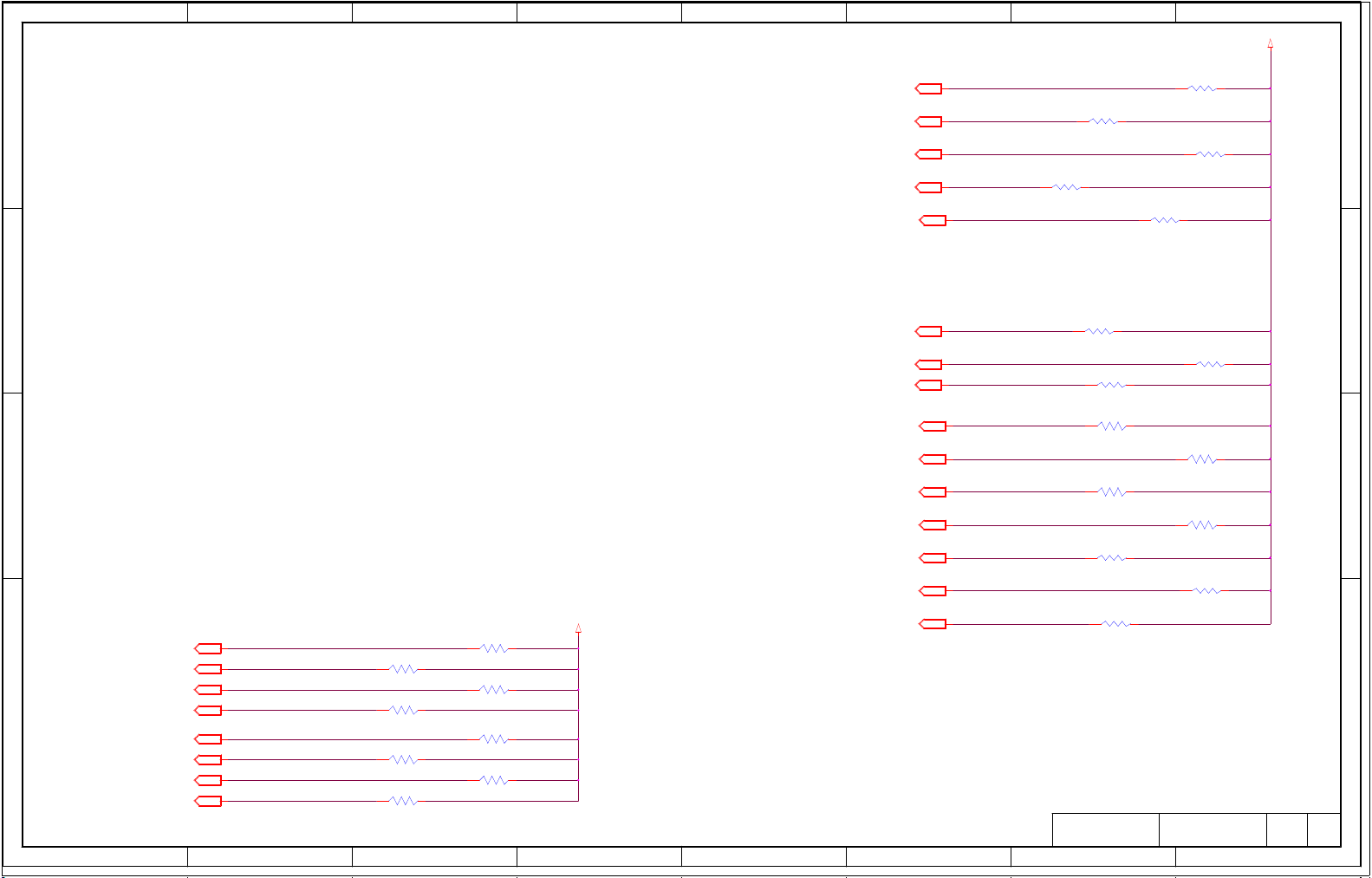

[19. MCH CHIPSET TERMINATION]

[20. VGA CONNECTOR]

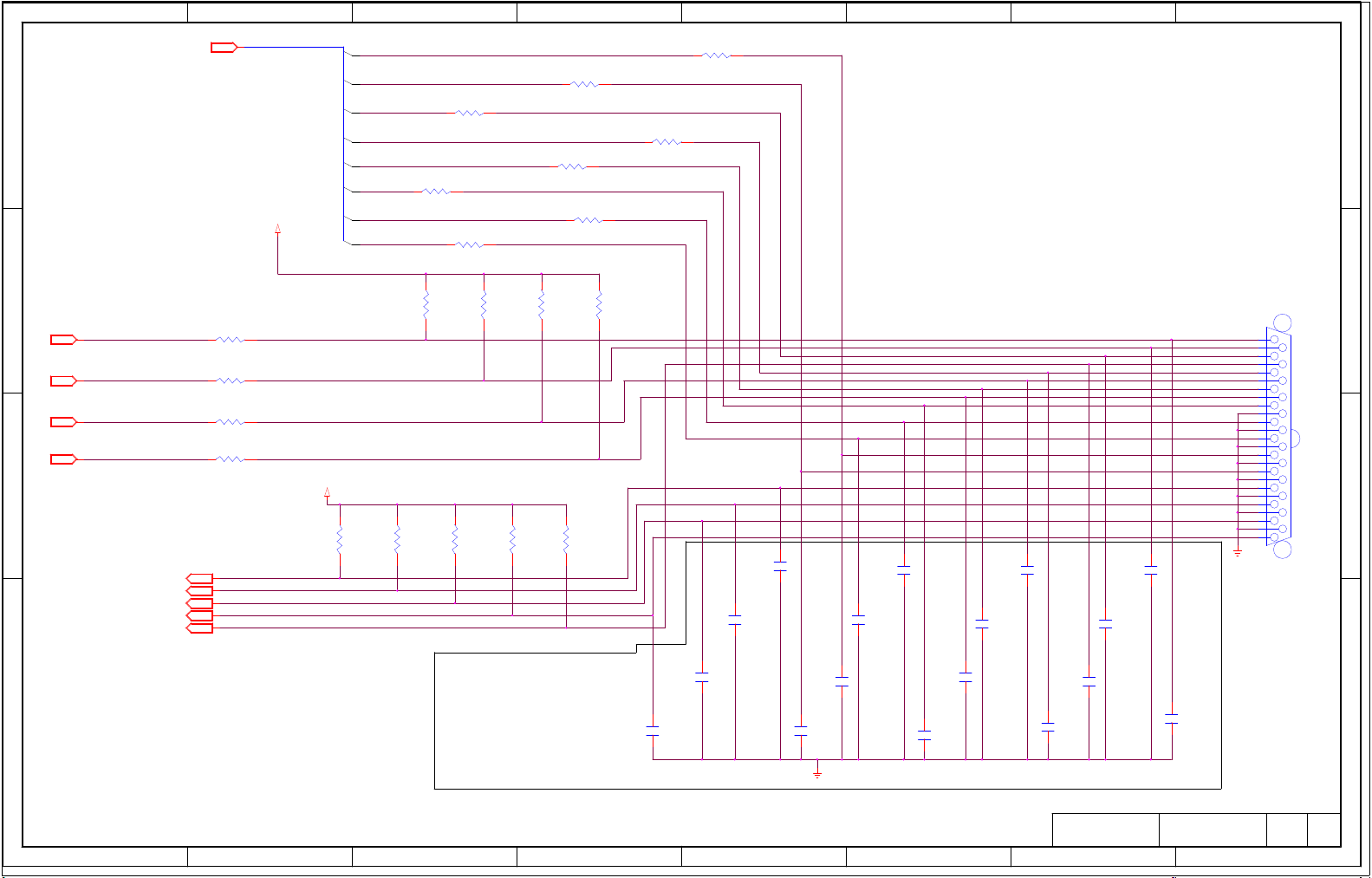

[21. DDR1 DIMM-A 0/1]

[22. DDR1 DIMM-A TERM]

[23. DDR1 DIMM-A TERM]

[24. DDR1 DIMM-A DCPL]

[25. DDR1 DIMM-B 0/1]

[26. DDR1 DIMM-B TERM]

B

[27. DDR1 DIMM-B TERM]

[28. DDR1 DIMM-B DCPL]

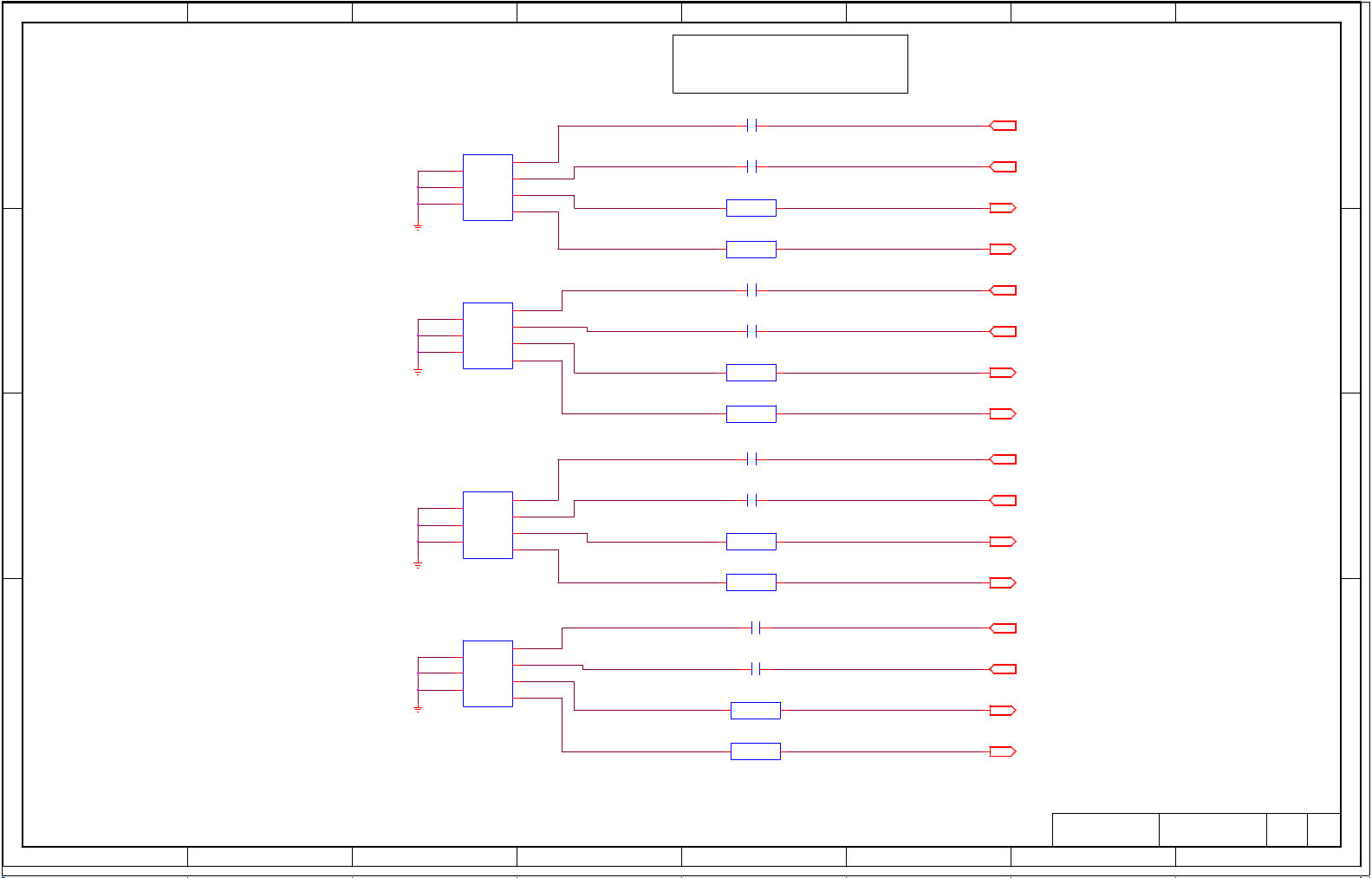

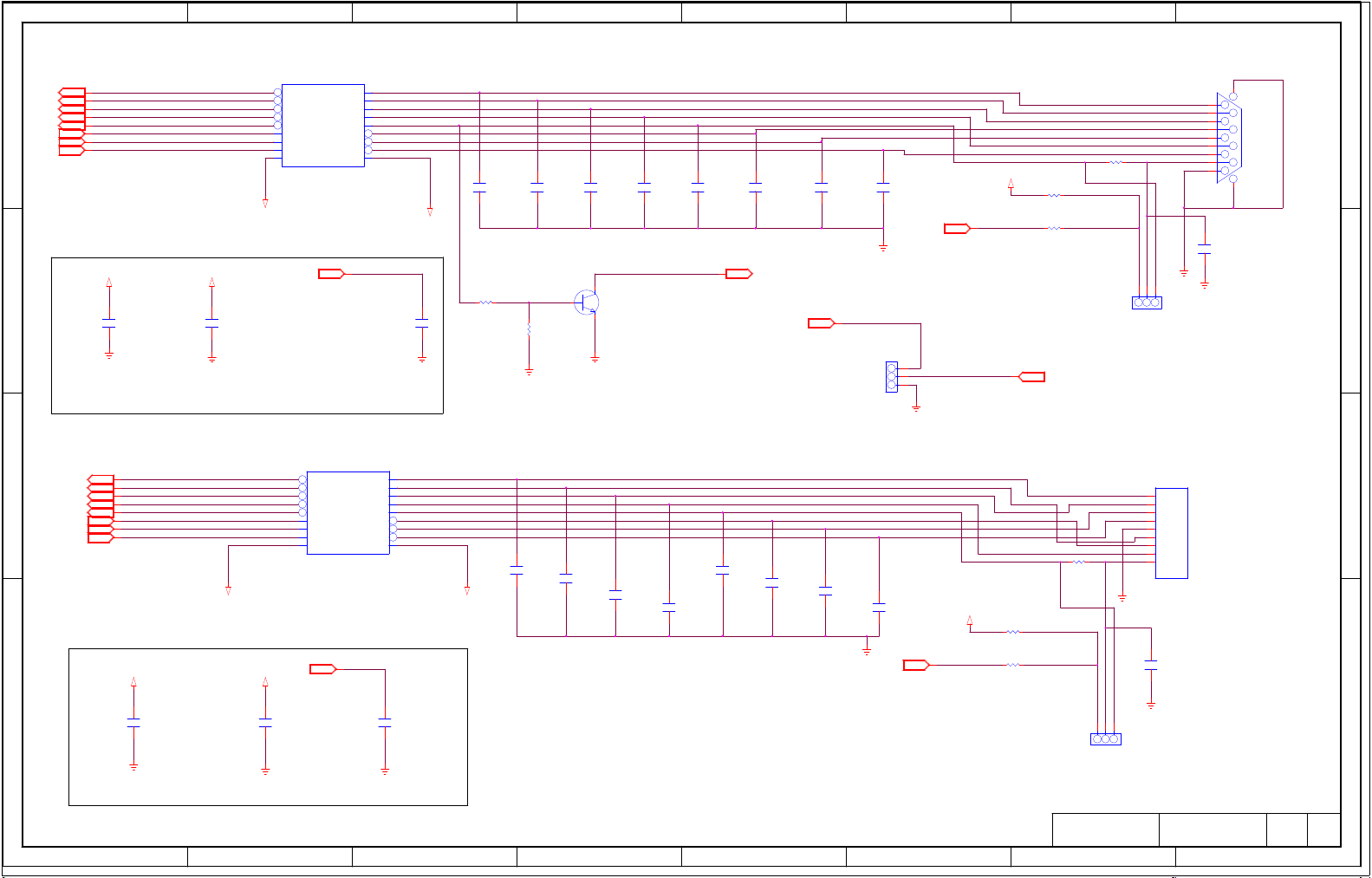

[29. CK410E PAGE 1 OF 2]

[30. CK410E PAGE 2 OF 2]

[31. BLANK PAGE]

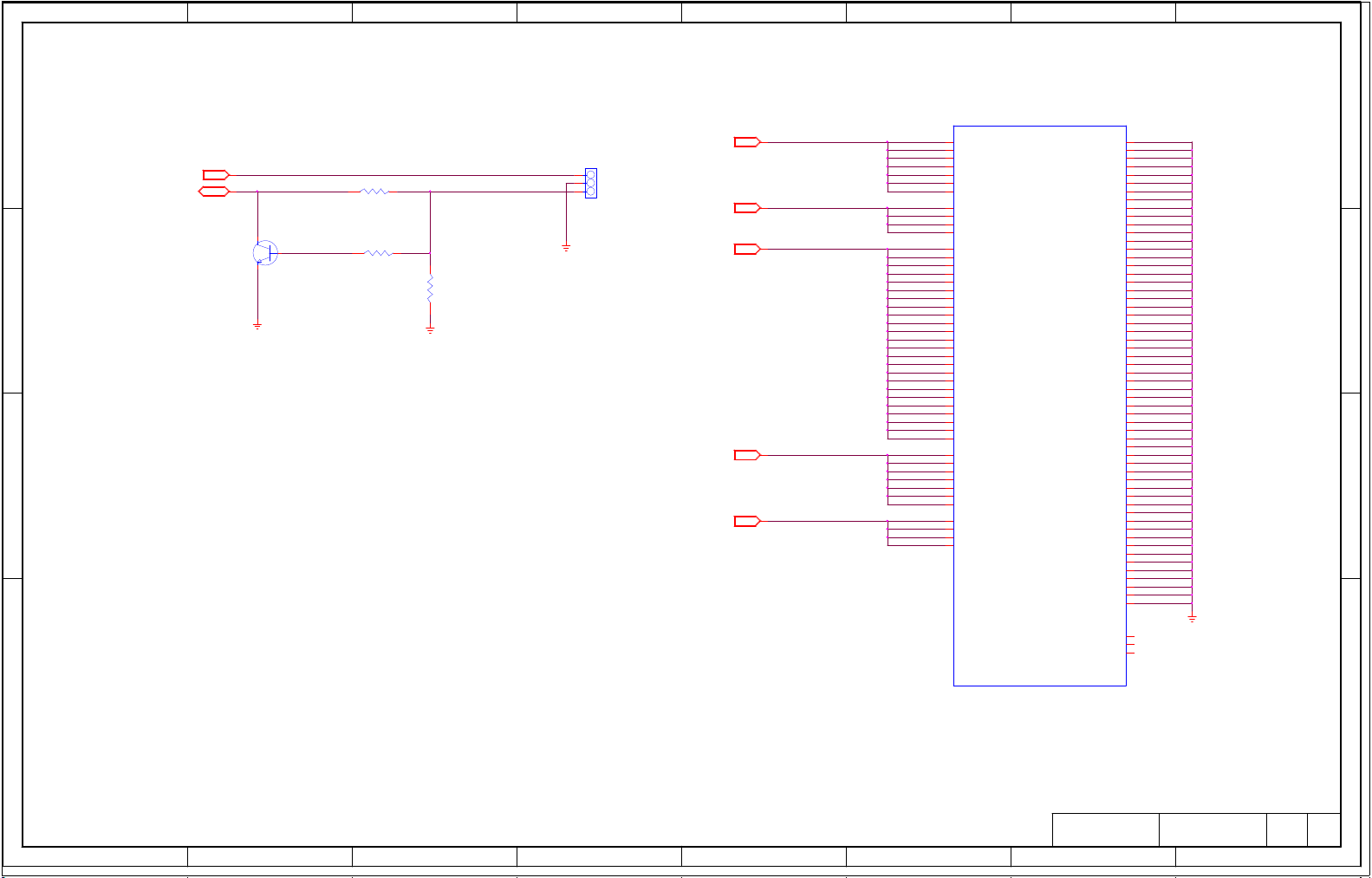

[32. PCIE 16-PORT]

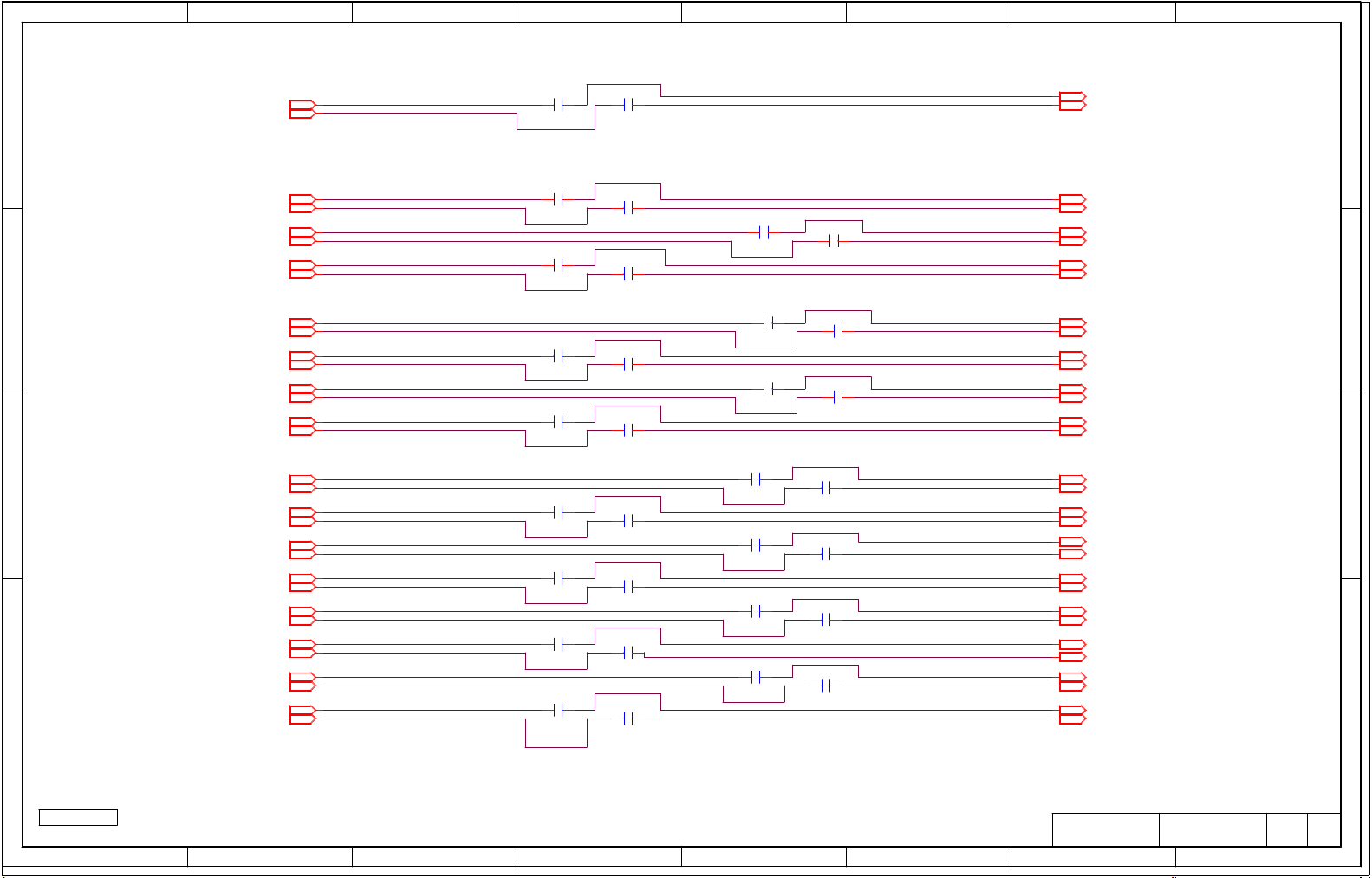

[33. PCIE COUPLING]

[34. BLANK PAGE]

[35. BLANK PAGE]

[36. BLANK PAGE]

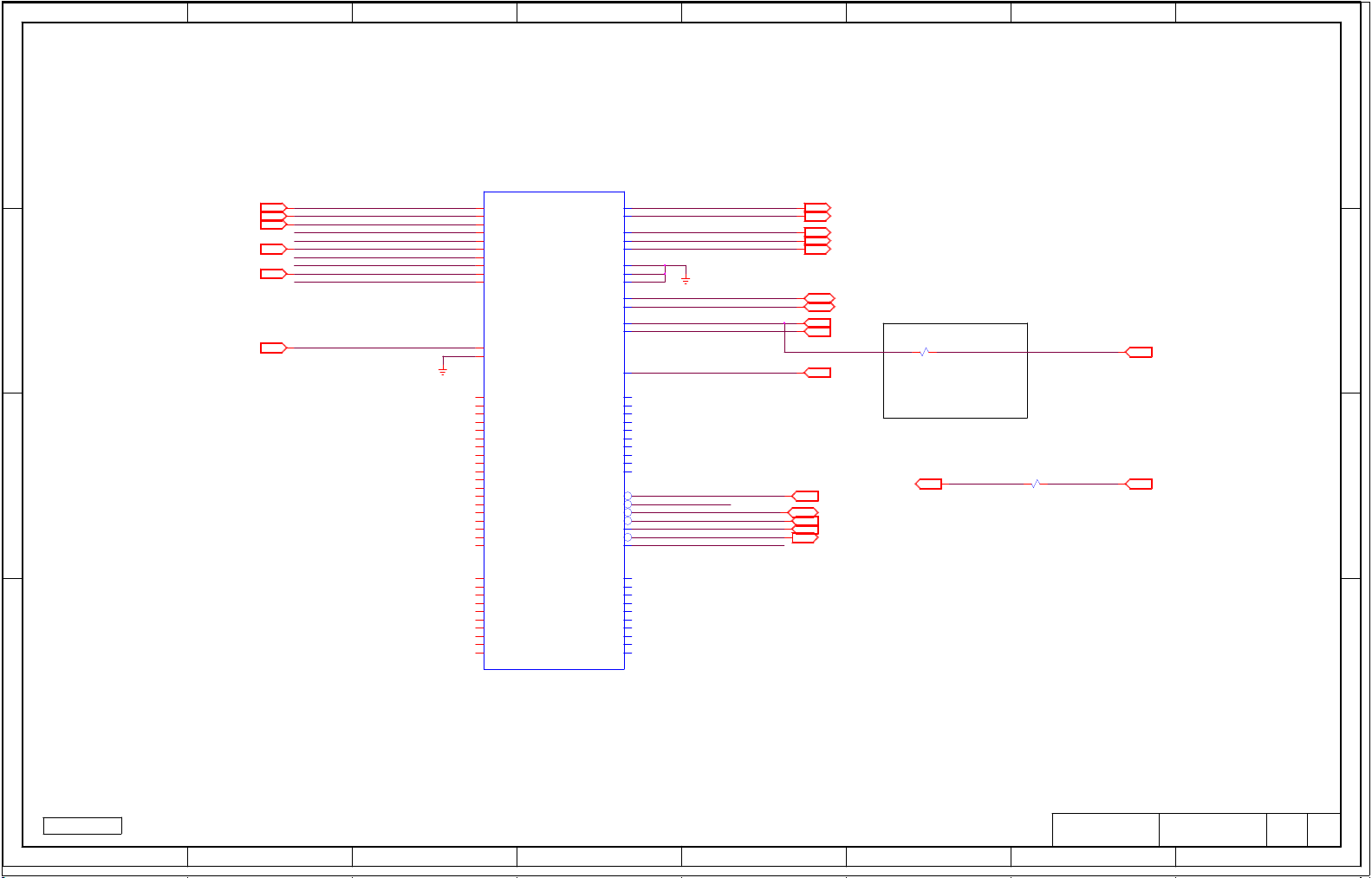

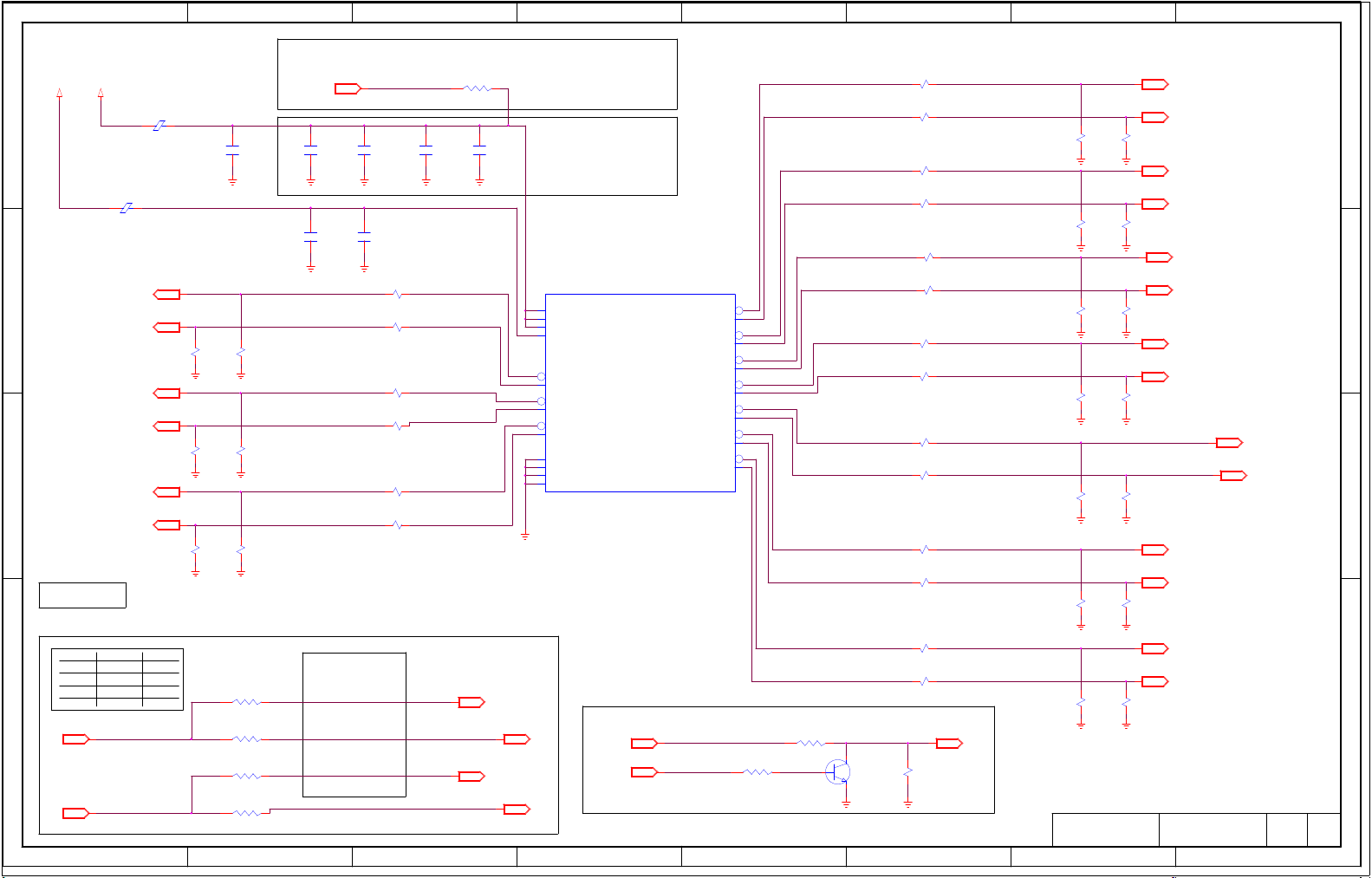

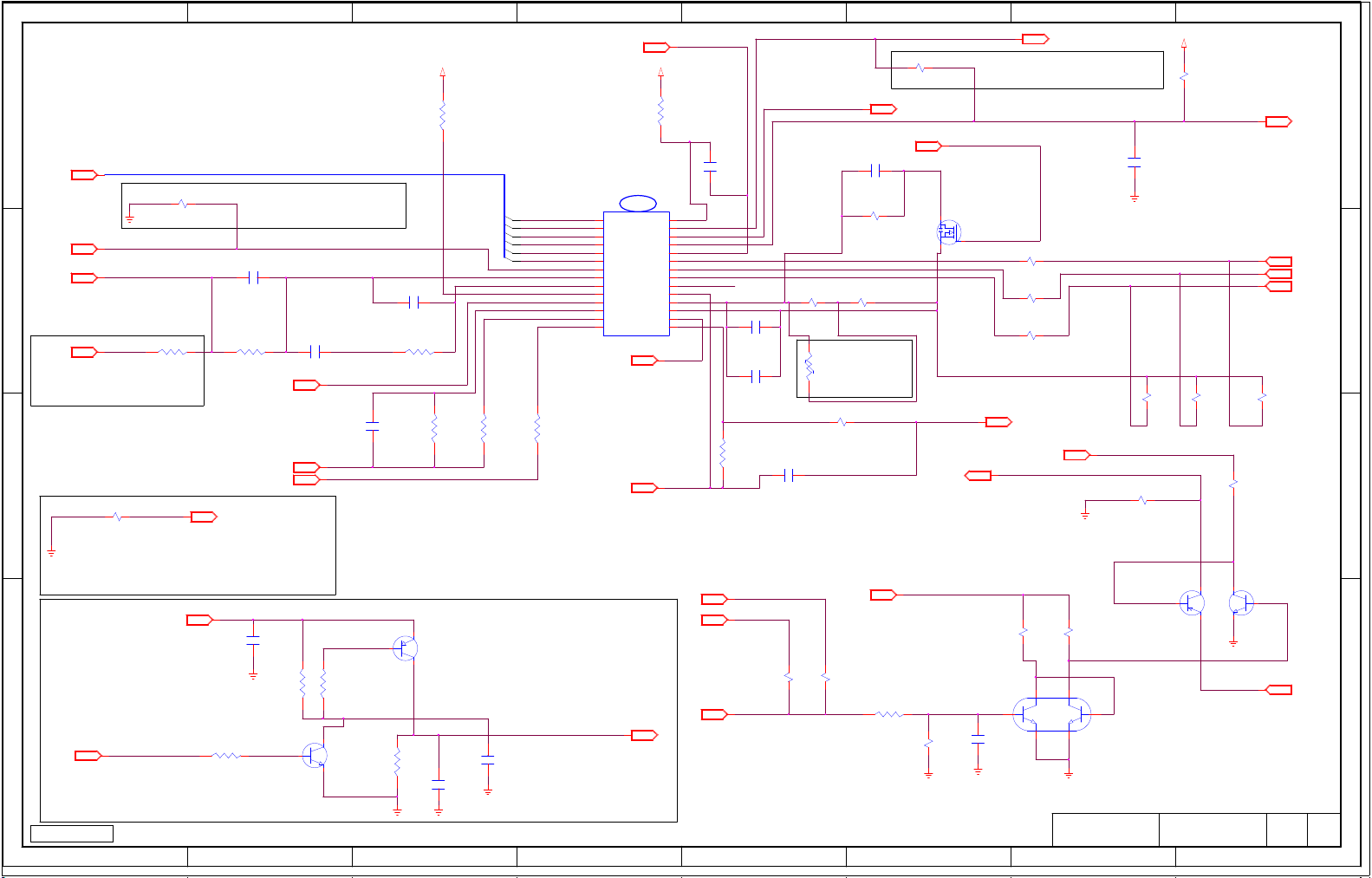

[37. ICH 1 OF 6 - CONTROL]

[38. ICH 2 OF 6 - CONTROL]

A

[39. ICH 3 OF 6 - CONTROL]

[40. ICH 4 OF 6 - CONTROL]

[41. ICH 5 OF 6 - POWER]

[42. ICH 6 OF 6 - GROUND]

[43. ICH TERMINATION]

PAGE #

COMPONENT/FUNCTION

[44. IDE_SOUTH_BRIDGE]

[45. USB_BACKPANEL_CONN]

[46. USB_FP #2 HEADER]

[47. USB_FP_HEADER_POWER 1 & 2]

[48. USB_FP #1 HEADER]

[49. PCI_CONN_1]

[50. PCI_CONN_2]

[51. PCIE_X1_SLOT1]

[52. PCIE_X1_SLOT2]

[53. PCI_CONN_3]

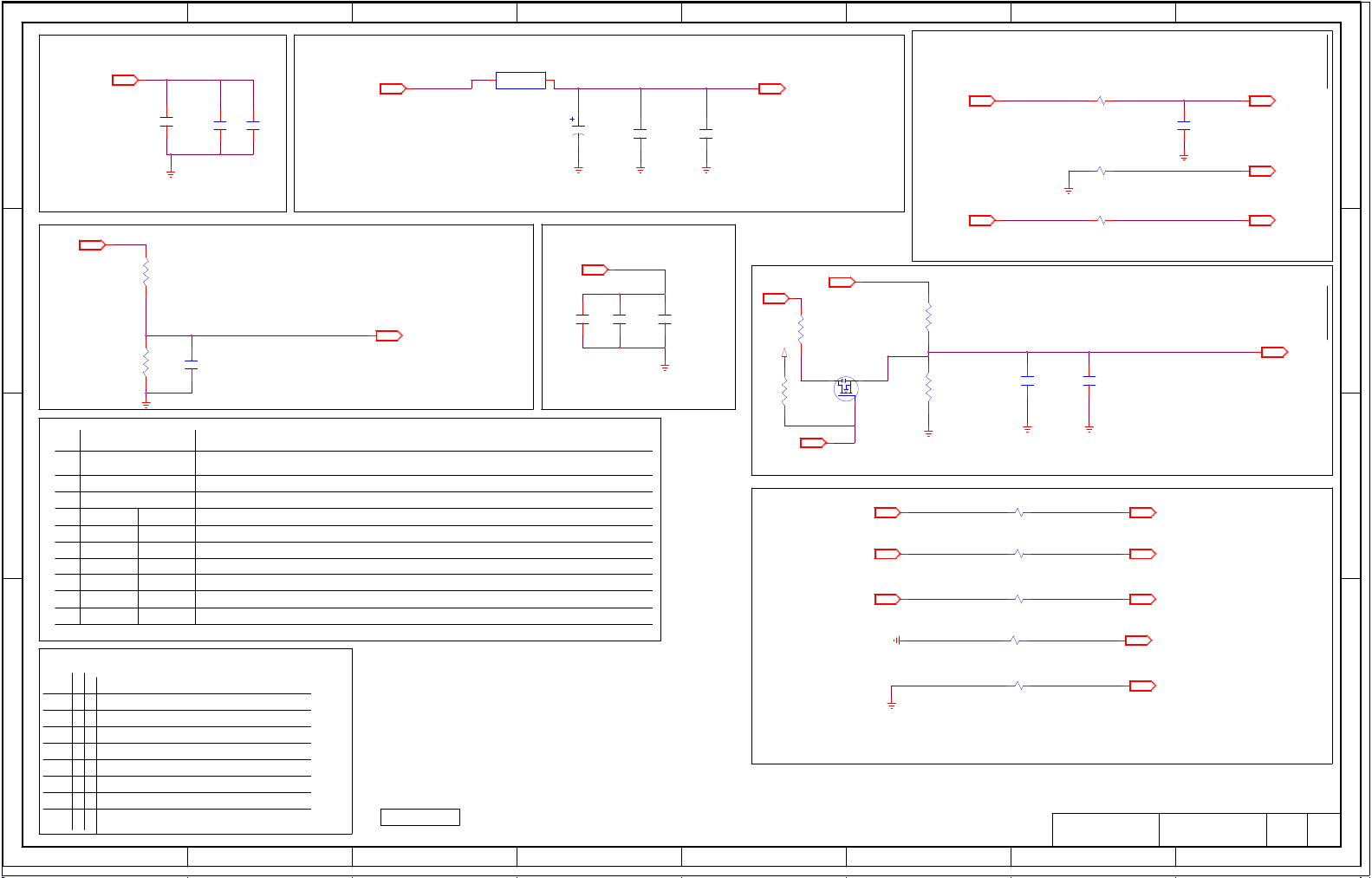

[54. ICH_PCI_TERMINATION]

[55. BLANK]

[56. LAN CONTROLLER, PART 1 OF 2]

[57. LAN EEPROM, DECOUPLING]

[58. BLANK]

[59. LAN CONN]

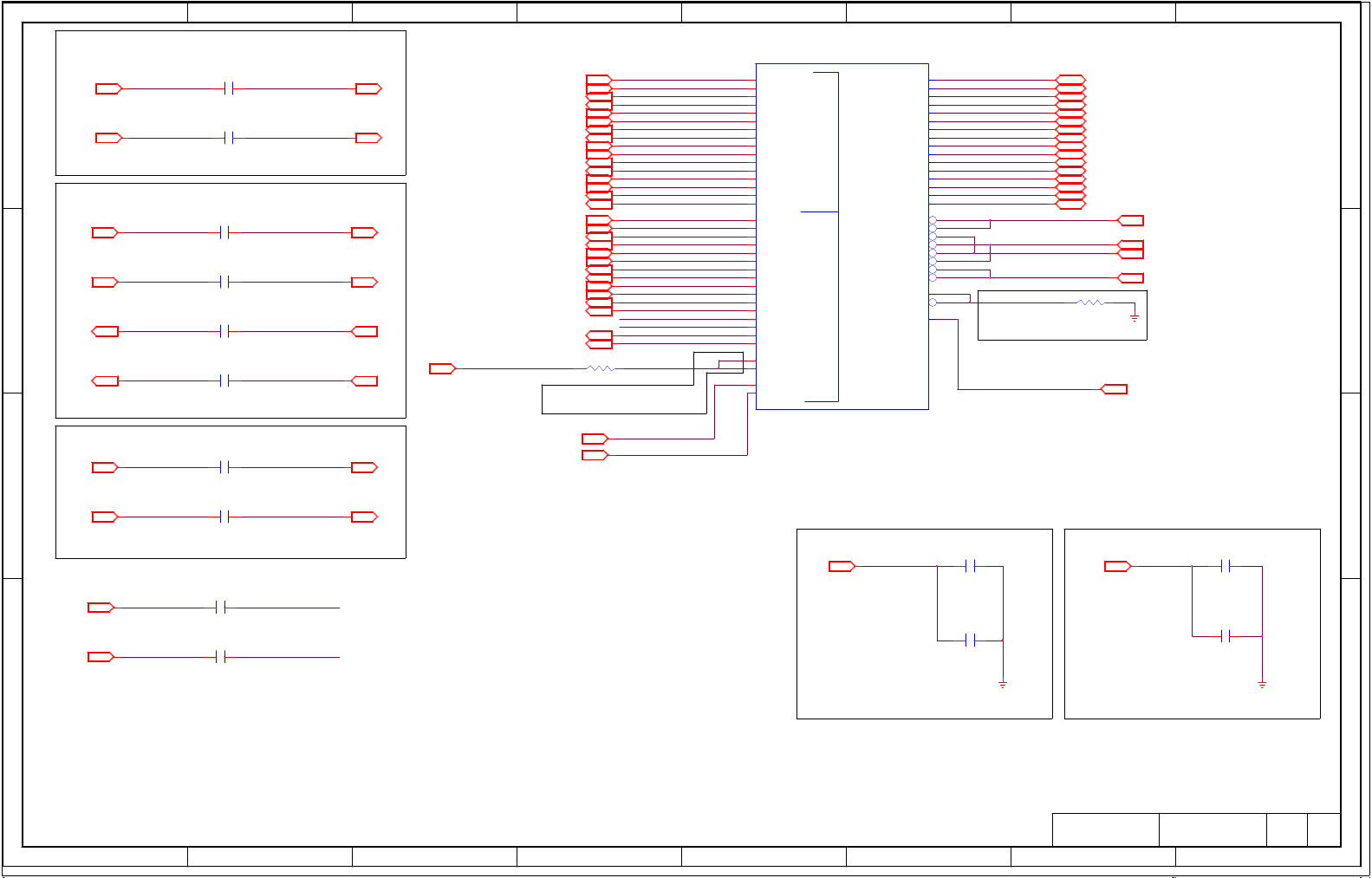

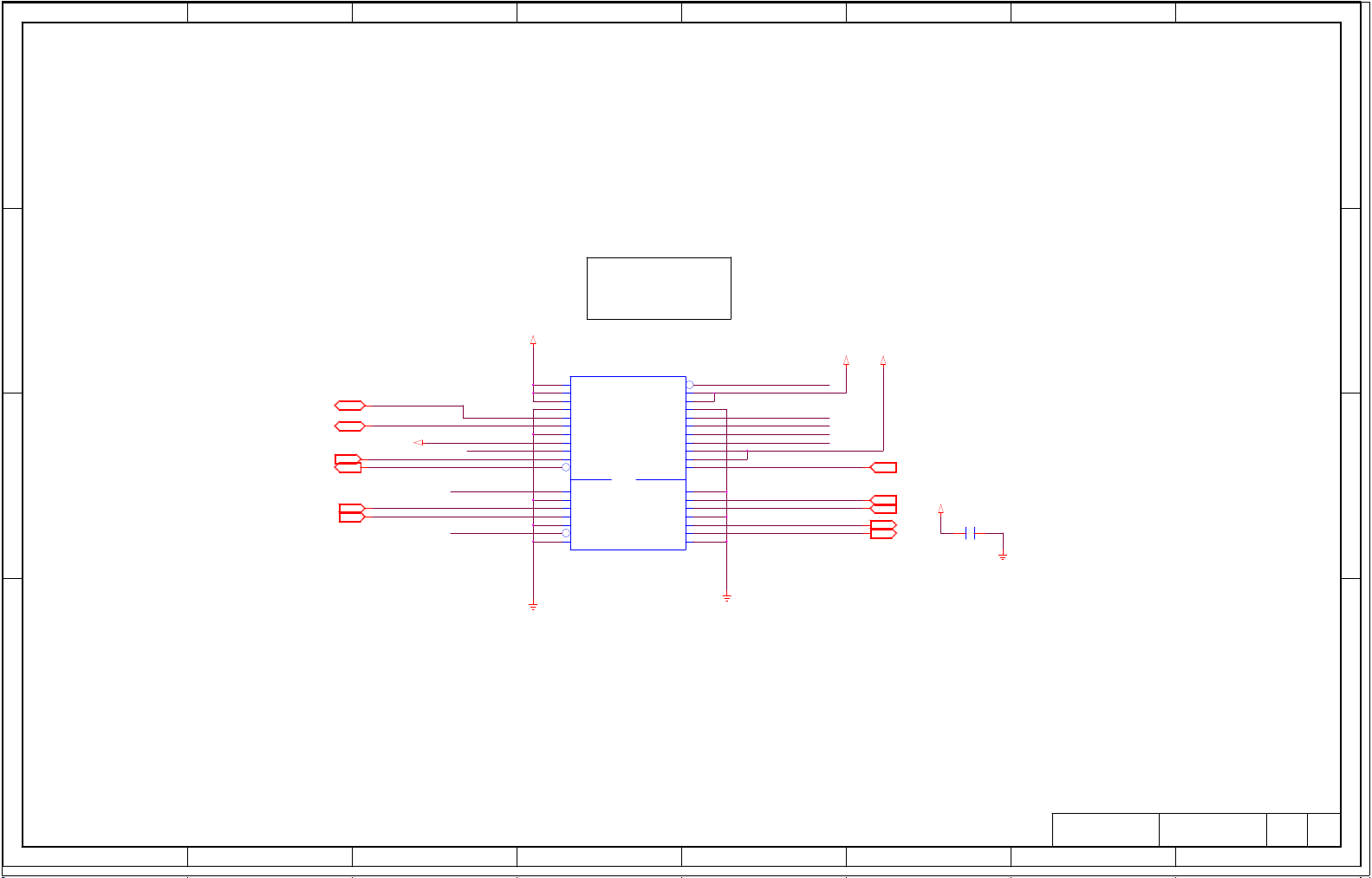

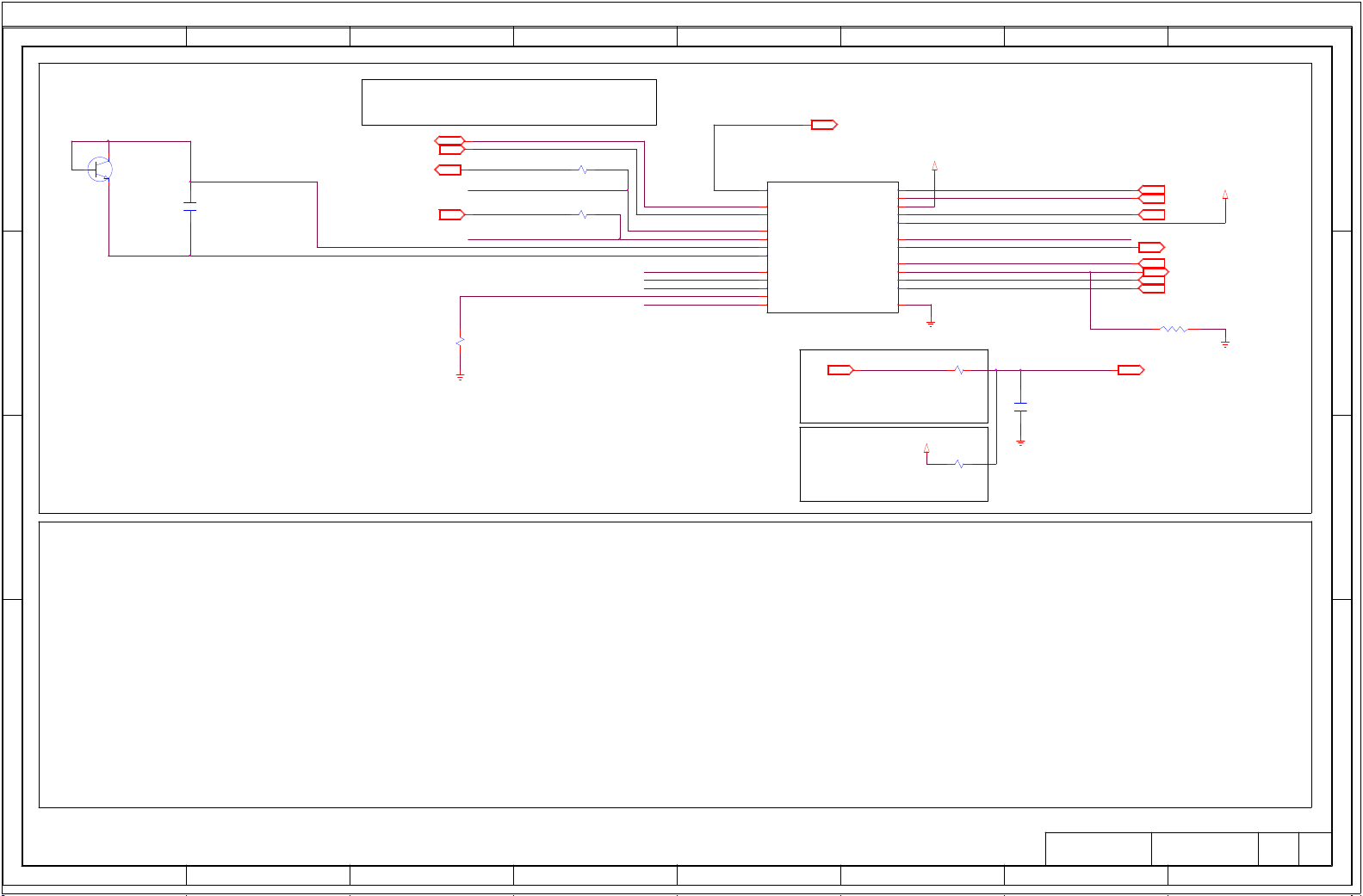

[60. AUDIO CODEC]

[61. AUDIO BYPASS & DECOUPLING CAPS]

[62. ATAPI CD HEADER & SPDIF HEADER]

[63. AUDIO BACK PORT MIC-IN/LINE-IN/OUT]

[64. AC HEADER FRONT PANEL PORT]

[65. AUDIO TERMINATION P/U & VREF NETWORK]

[66. AUDIO VREG]

[67. BLANK]

[68. BLANK]

[69. BLANK]

[70. TPM (TRUSTED PLATFORM MODULE)]

[71. SATA CONNECTORS]

[72. FIRMWARE HUB]

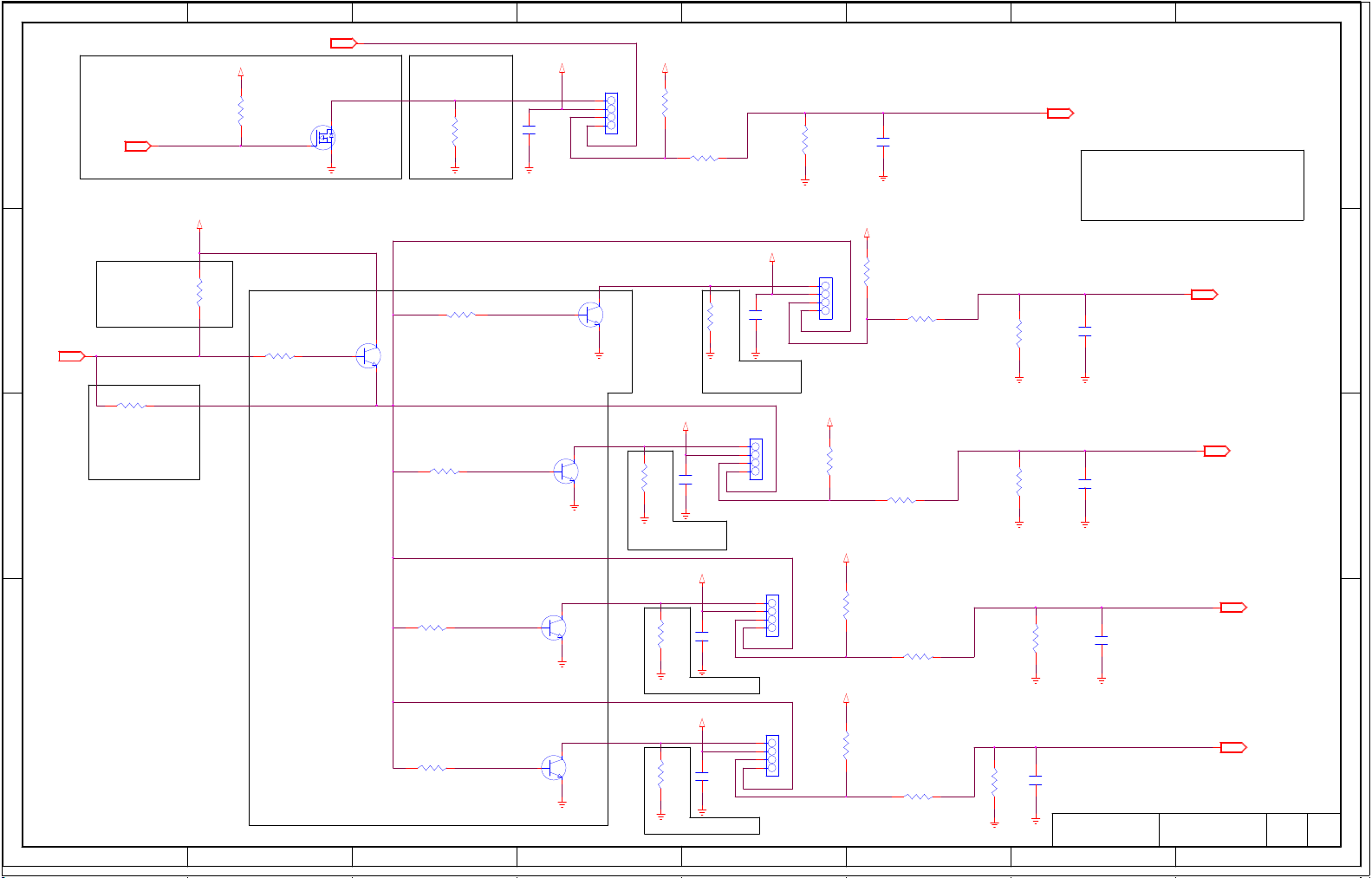

[73. PORT ANGELES (1 OF 2)]

[74. PORT ANGELES (2 OF 2)]

[75. FDD CONN]

[76. PS/2 MOUSE DOUBLE-STACKED]

[77. LPT CONN]

[78. SERIAL PORT A]

[79. HARDWARE MANAGEMENT: HECETA]

[80. SPEAKER & DIAGNOSTIC LED]

[81. STD_FRONT_PANEL_HDR]

[82. MTG_HOLES/LABELS]

[83. FAN CONTROL]

[84. VREG: VOLTAGE DISTRIBUTION]

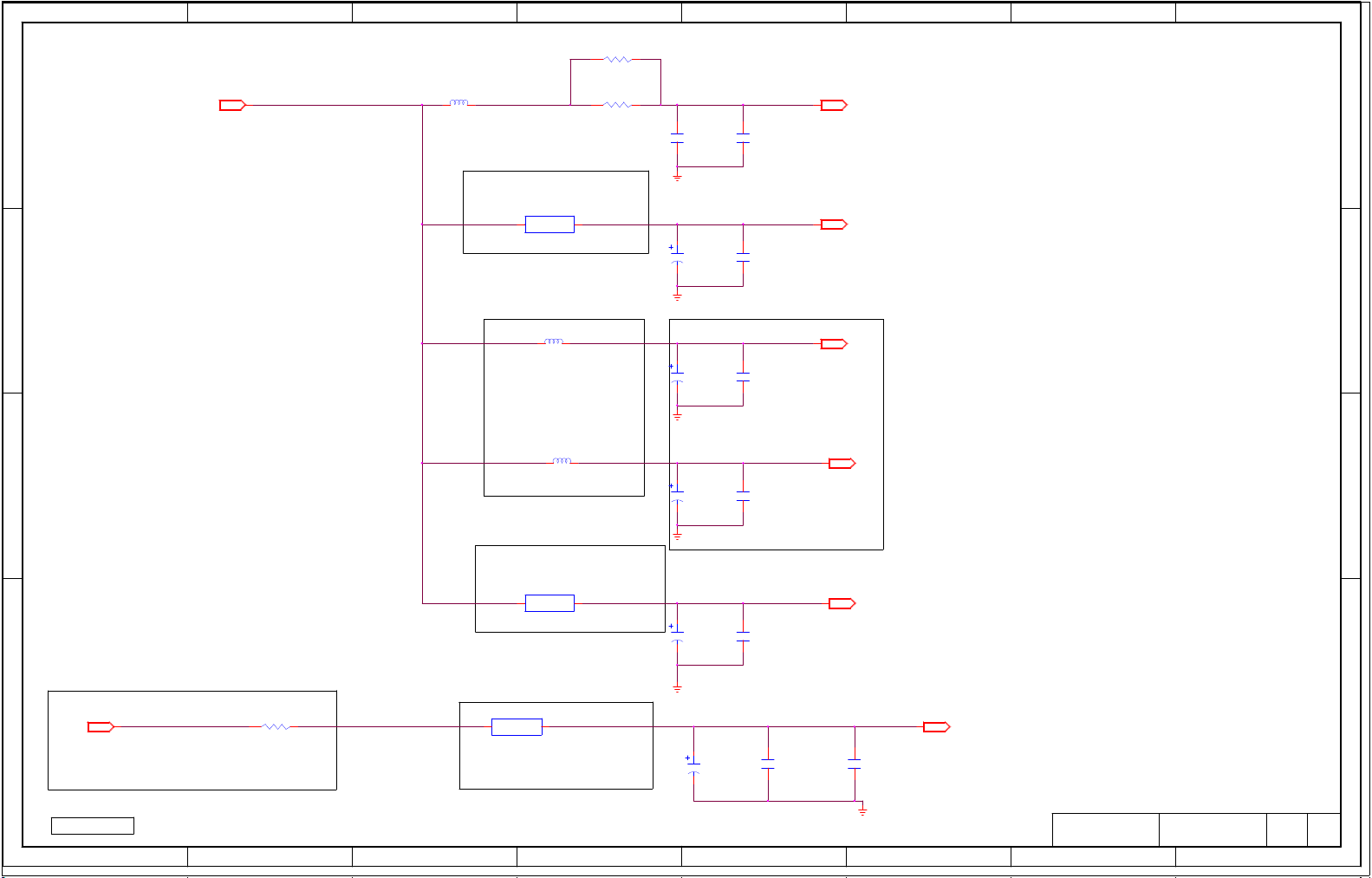

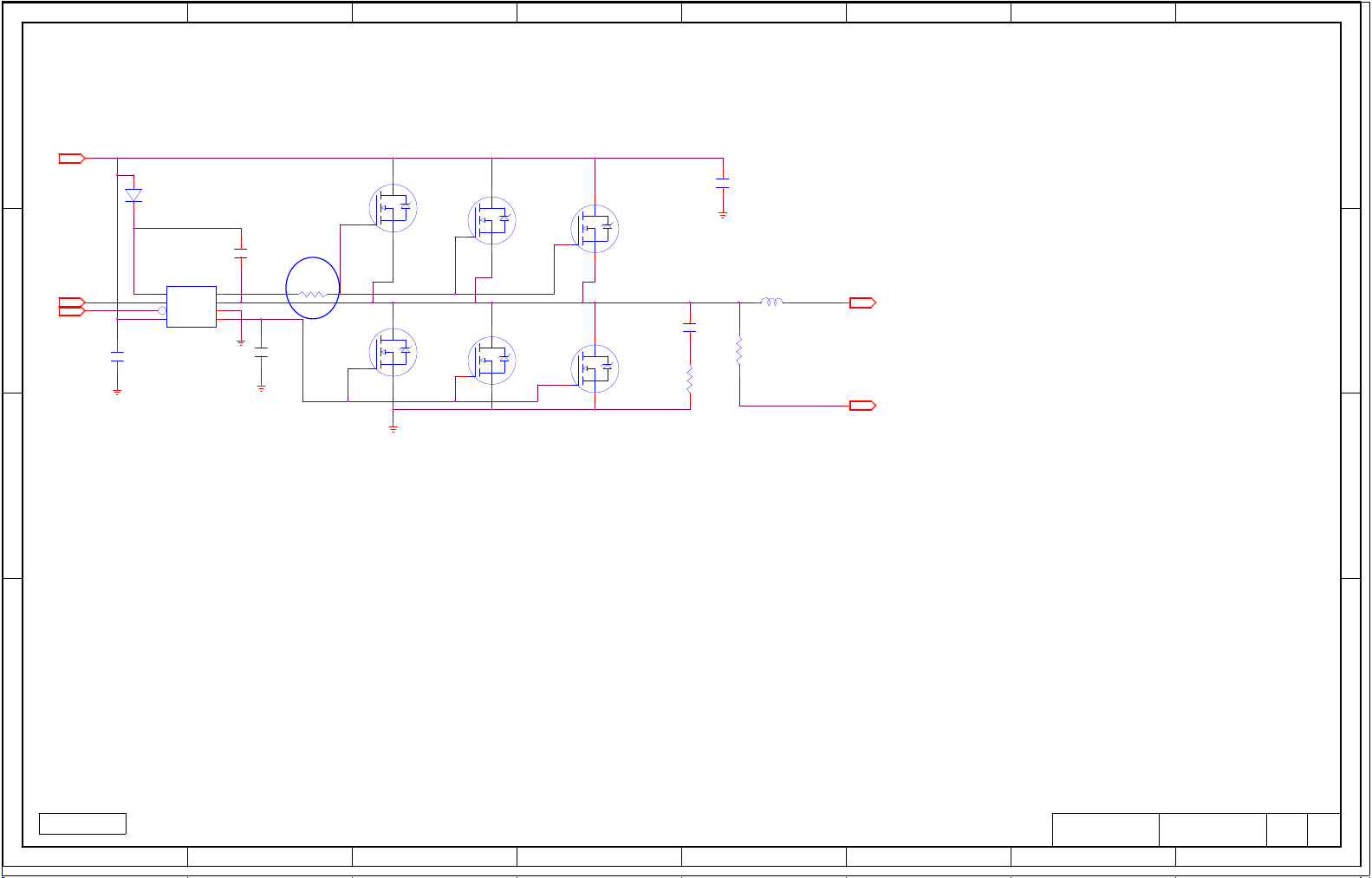

[85. V_SM SWITCHING VREG]

PAGE #

COMPONENT/FUNCTION

[86. STANDARD POWER CONNECTOR]

[87. VREG_1P2_FSB_VTT]

[88. VREG_2P5_MCH]

[89. VREG_SM_VTT]

[90. PCI VAUX/VREG_USB/V_BATTERY]

[91. VREG_USB_BP_RIGHT/LEFT & PS2]

[92. 3.3V STANDBY]

[93. VREG_DCPL_BULK]

[94. 5VDUAL VREG & USB_BP_MID]

[95. VCCP VREG]

[96. VCCP VREG]

[97. VCCP VREG]

[98. VCCP VREG DECOUPLING]

[99. PCI_CONN_4]

[100. DMI LAI PORT]

[101. DEBUG_XDP]

[102. VREG_1P5 CORE]

[103. VR_THERMAL THROTTLE]

[104. TEST SITE CAPS]

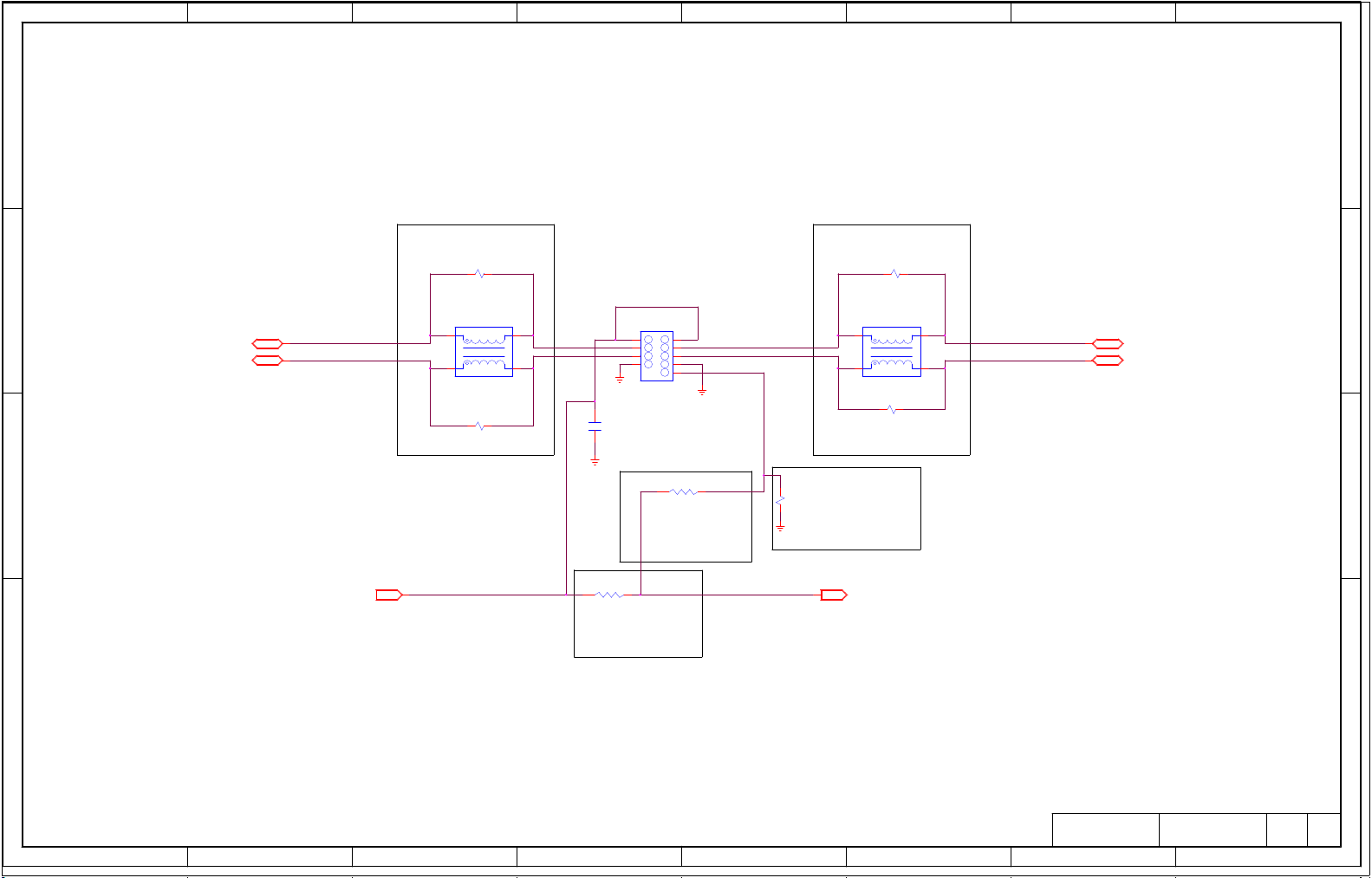

[105. 1394A 1 OF 2]

[106. 1394A 2 OF 2]

[107-116 REFERENCE PAGES]

NOTES:

POWER SYMBOLS USED:

VCC3

VCC

+12V

-12V

1. THIS SCHEMATIC DOCUMENTS THE GENERIC PRODUCT WITH

ALL POSSIBLE CONFIGURATIONS.

PLEASE REFER TO SPECIFIC PRODUCT PBA EPL FOR

ITEMS SHOWN AS OPTIONAL IN THE SCHEMATIC.

2. RESISTORS ARE IN OHMS UNLESS OTHERWISE SPECIFIED.

3. VCC = +5V UNLESS OTHERWISE SPECIFIED.

4. * SUFFIX INDICATES ACTIVE LOW SIGNAL.

5. \I SUFFIX INDICATES SIGNAL EXITS HIERARCHICAL BLOCK.

6. THIS DOCUMENT ALSO EXISTS ON ELECTRONIC MEDIA.

AVALON

GRANTSDALE / DDR1 / ICH6 / UATX

FAB D

REV 4.0

TAPE-OUT:

D

C

B

A

8 7

[PAGE_TITLE=INDEX]

INTEL

45

36

CONFIDENTIAL

2 1

DOCUMENT NUMBER PAGE REV

C77862

1/106

4.0

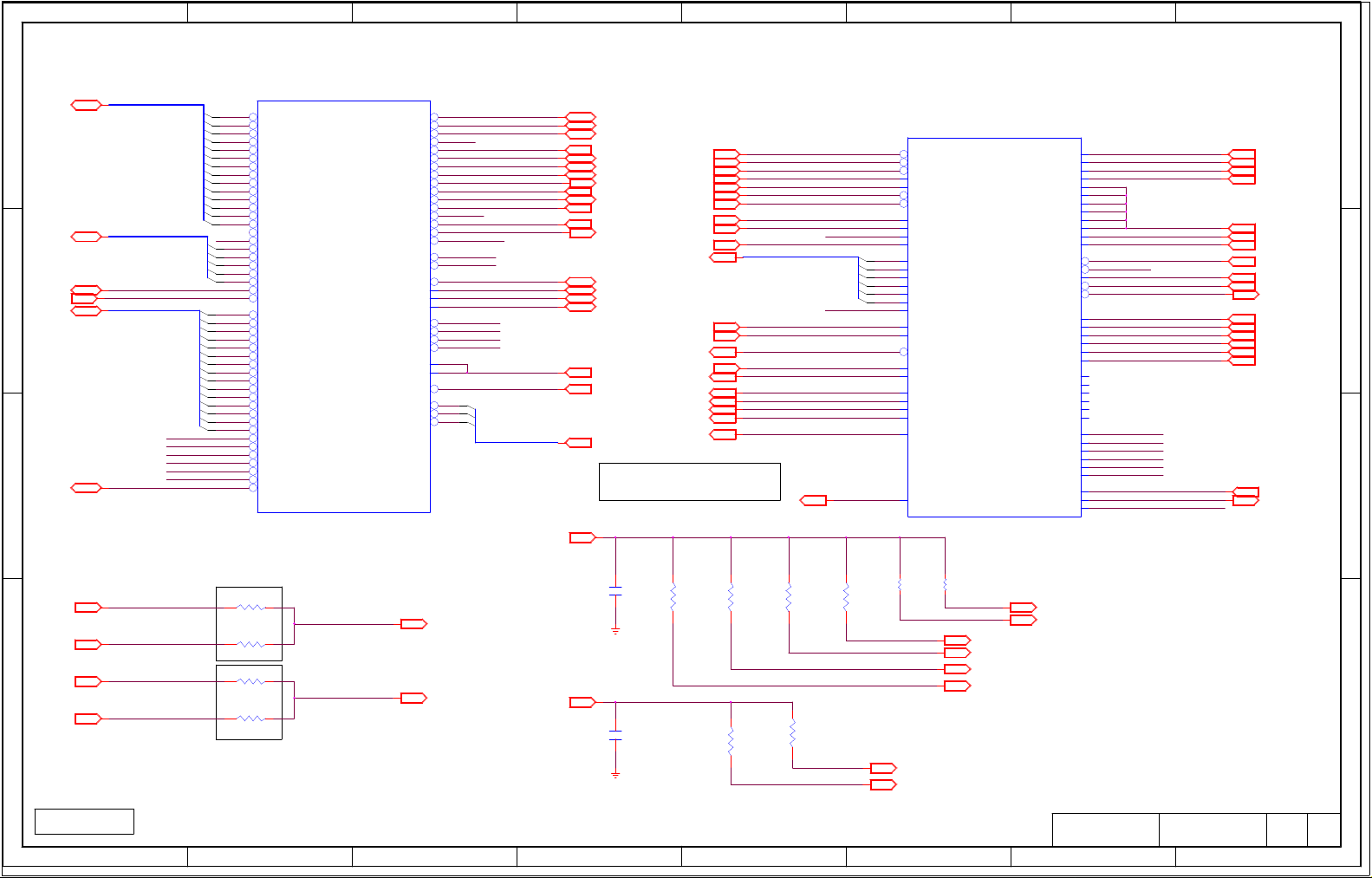

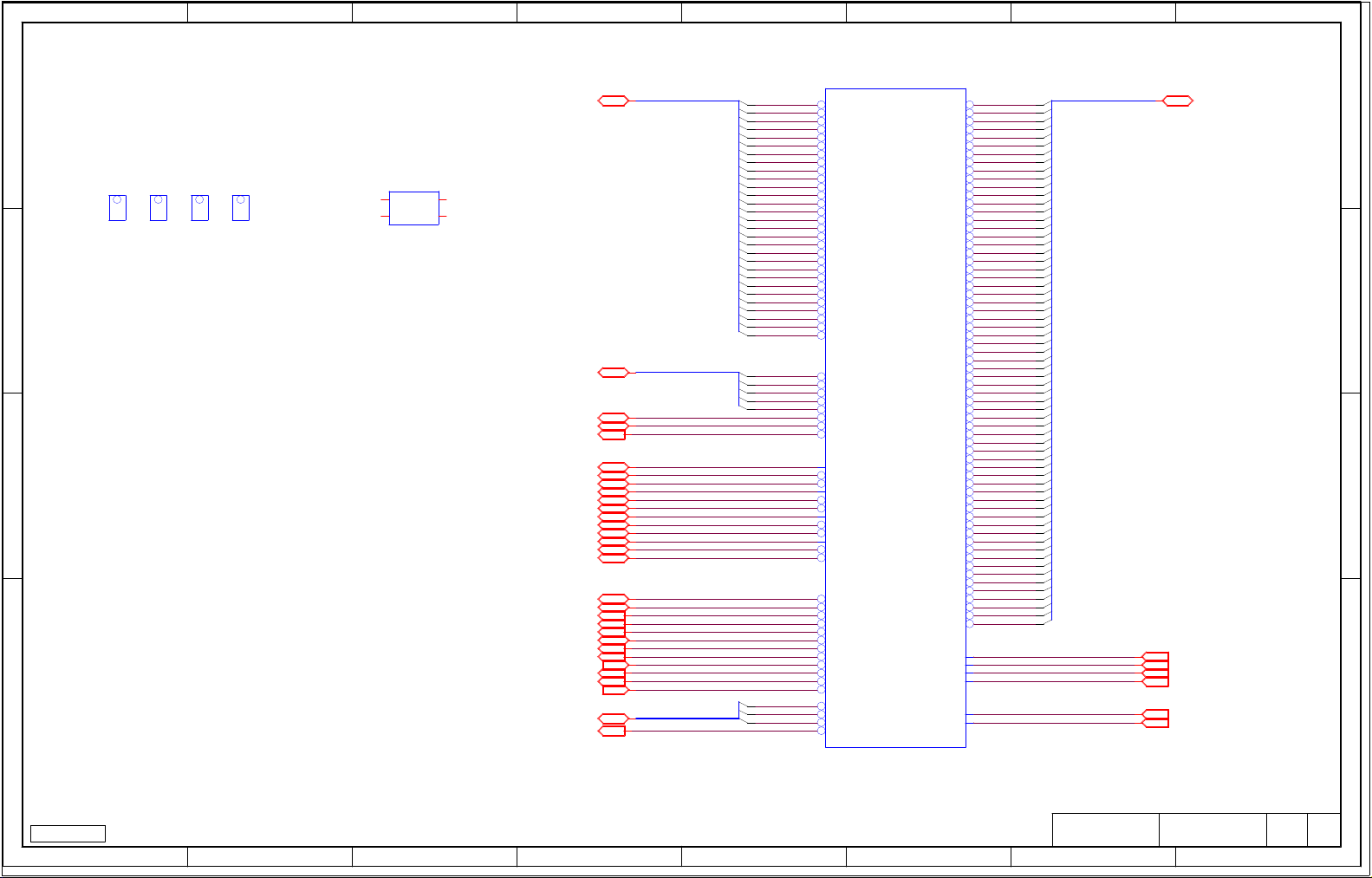

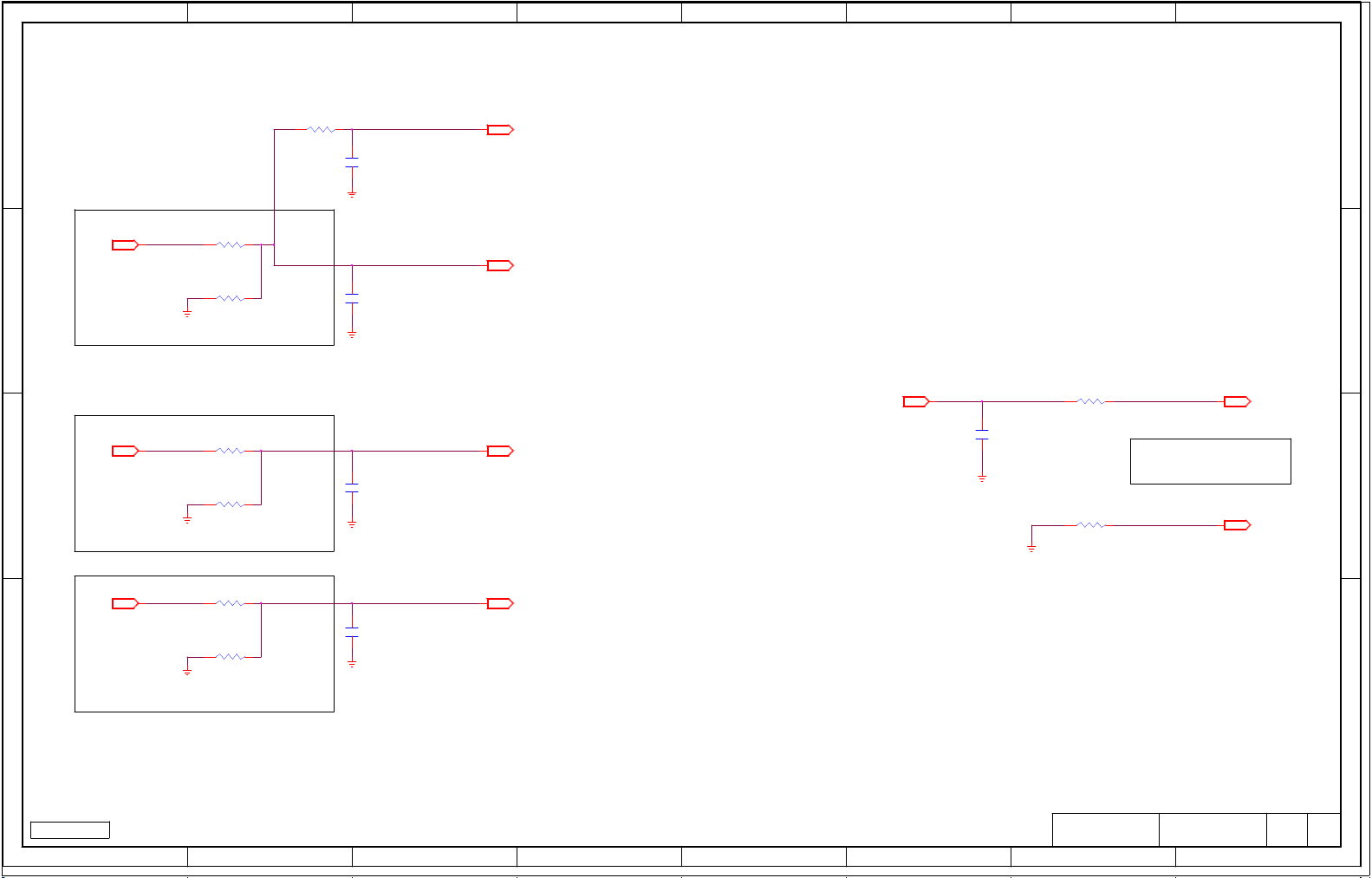

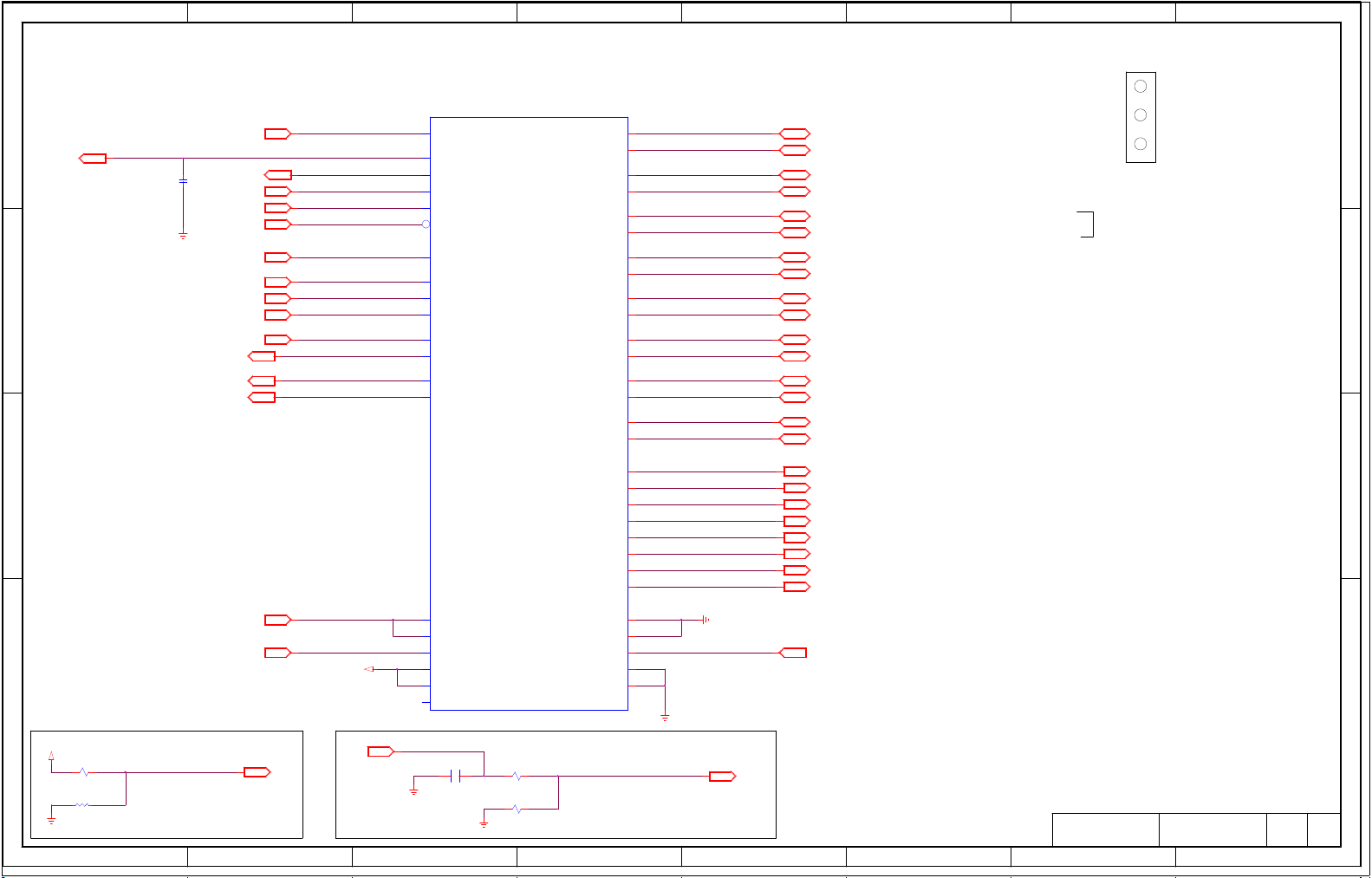

Page 2

<XR_PAGE_TITLE>

28 7 6 5 4 3 1

POWER

D

C

SUPPLY CONN

PORT 1

PORT 2

BACK PANEL(R)

USB PORT 1

USB PORT 2

USB PORT 3

USB PORT 4

B

A

FRONT PANEL 1

USB PORT 5 (1)

USB PORT 6 (2)

FRONT PANEL 2

USB PORT 7 (3)

USB PORT 8 (4)

SENSOR S3

SM BUS S3

SM BUS S0

PS2 MOUSE &

KEYBOARD

COPIED BLOCK DIAGRAM FROM TGRVP_A, 14/10/2003

BLOCK DIAGRAM UPDATED: 12/15/2003

8 7

XDP

(BACK SIDE)

SM BUS S3

VREG

PARALLEL (1)

SERIAL (1)

PORT

ANGELES

SIO

PCIE X16

GRFX CONN

VGA CONN

1394A

SATA CONN

1 & 2

3 & 4

IDE CONN 1

LPC BUS

FLOPPY DISK

DRIVE CONN

GRANTSDALE

SM BUS S3

FWH: FIRMWARE HUB

LAND GRID ARRAY (LGA) CONNECTOR

LGA775

PROCESSOR SOCKET

FSB

GMCH:

GRAPHIC MEMORY

CONTROLLER HUB

DMI: DIRECT MEDIA INTERFACE

ICH6: I/O

CONTROLLER HUB

CHIPSET

TPM: SECURITY

CHANNEL A DDR 333/400

CHANNEL B DDR 333/400

PCIE

PCI (33MHZ)

PCIE

AUDIO LINK

MIC IN

LINE IN

CD IN

45

CORE

SM BUS S3

AZALIA

AUDIO CORE

DUAL DATA RATE SDRAM

(2-DDR SDRAM DIMMS)

DUAL DATA RATE SDRAM

(2-DDR SDRAM DIMMS)

LAN

MARVELL

10/100/1000

SM BUS S3

FRONT PANEL

LINE OUT

36

SM BUS S0

CK_410 CLOCK

DIMM 0:1

DIMM 0:1

RJ45

UATX FORM FACTOR

PCI SLOTS 1

PCI SLOTS 2

PCIE X1 PORT1

SM BUS S3

ICH6

PORT_ANGELES

SM BUS S3

SENSOR S3

BLOCK DIAGRAM

[PAGE_TITLE=BLOCK DIAGRAM]

INTEL

CONFIDENTIAL

2 1

SM BUS S0

HECETA

HARDWARE

MONITOR

DMI LAI HDR

(2X12 BACKSIDE)

DOCUMENT NUMBER PAGE REV

C77862

2

D

C

B

A

4.0

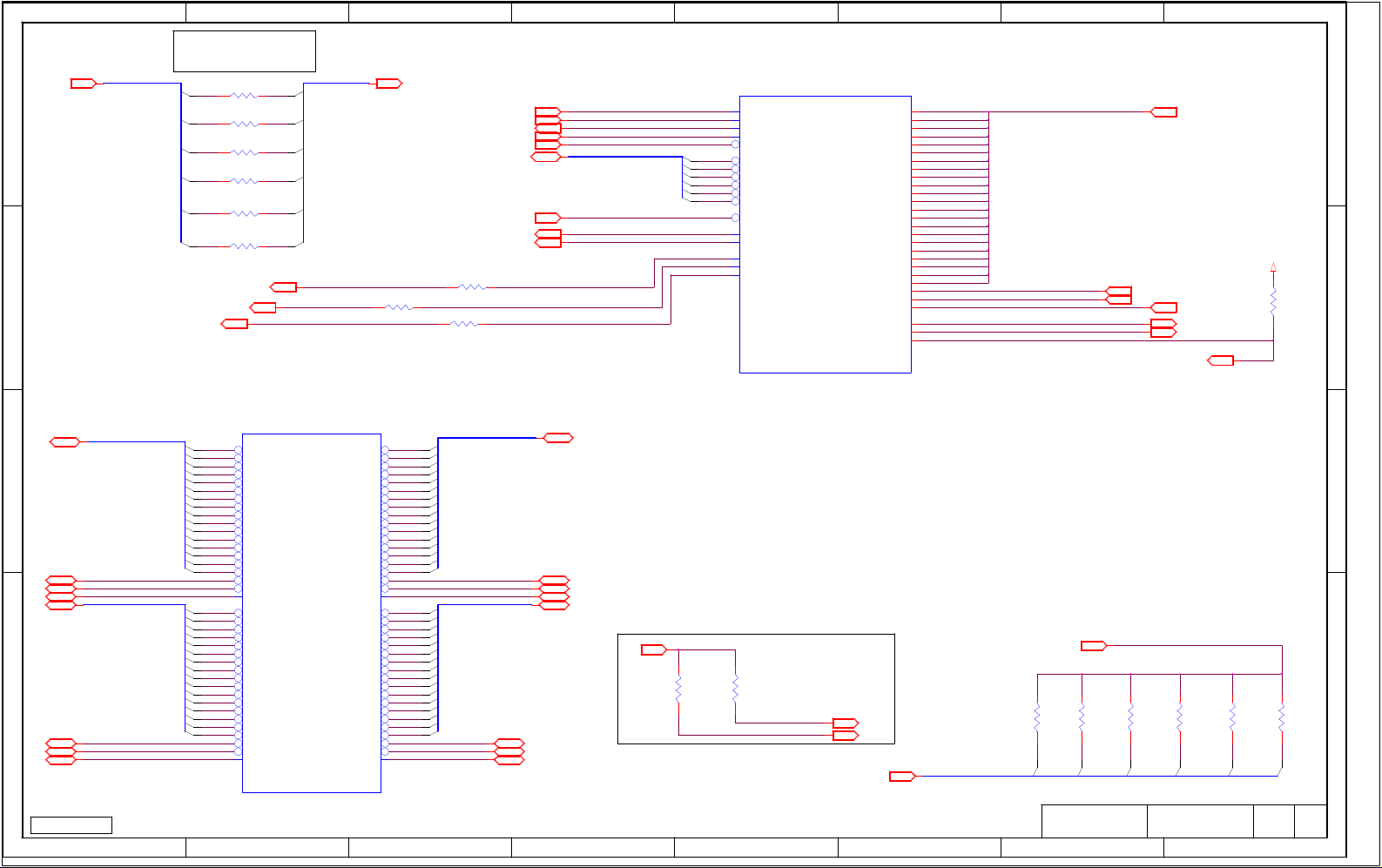

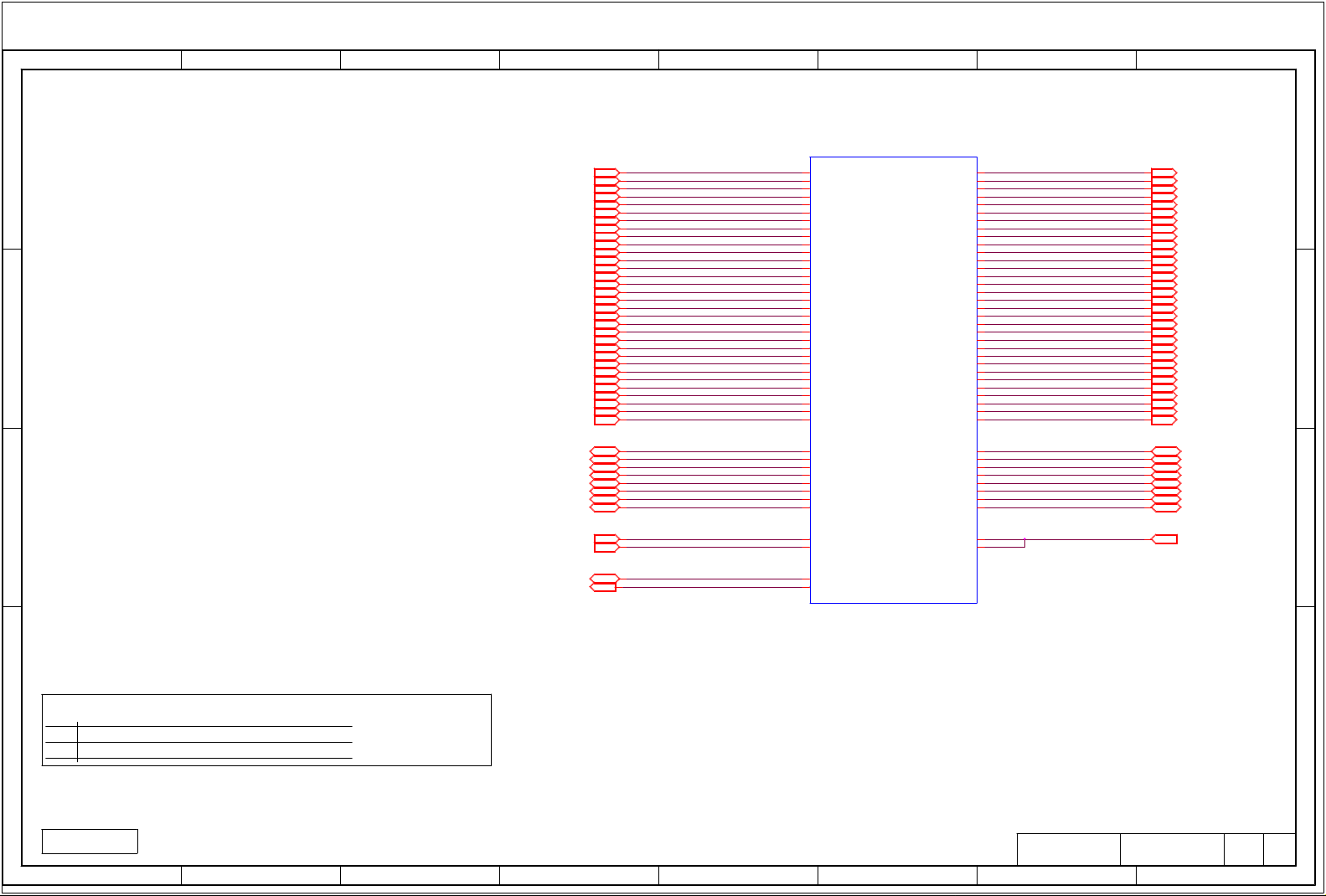

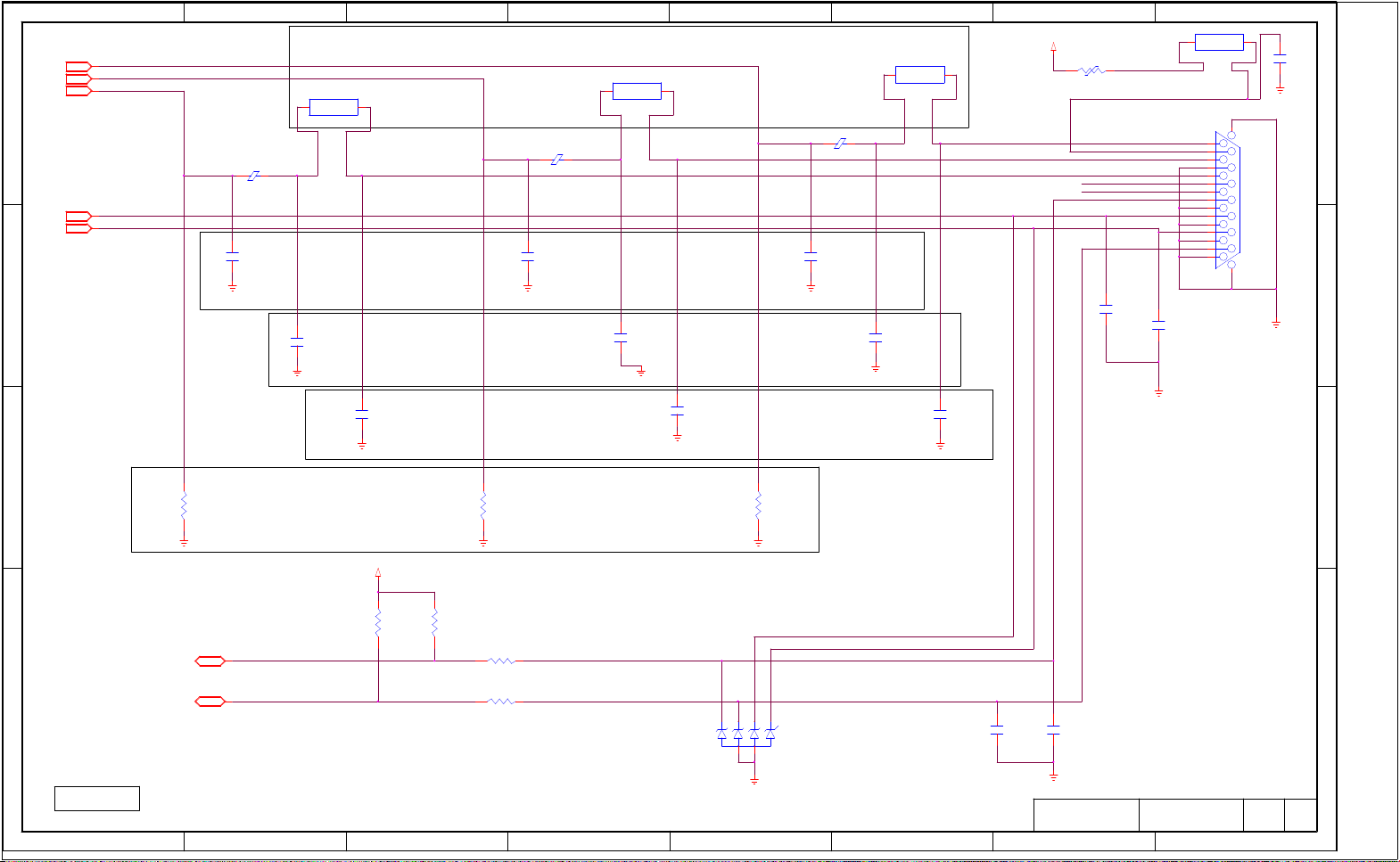

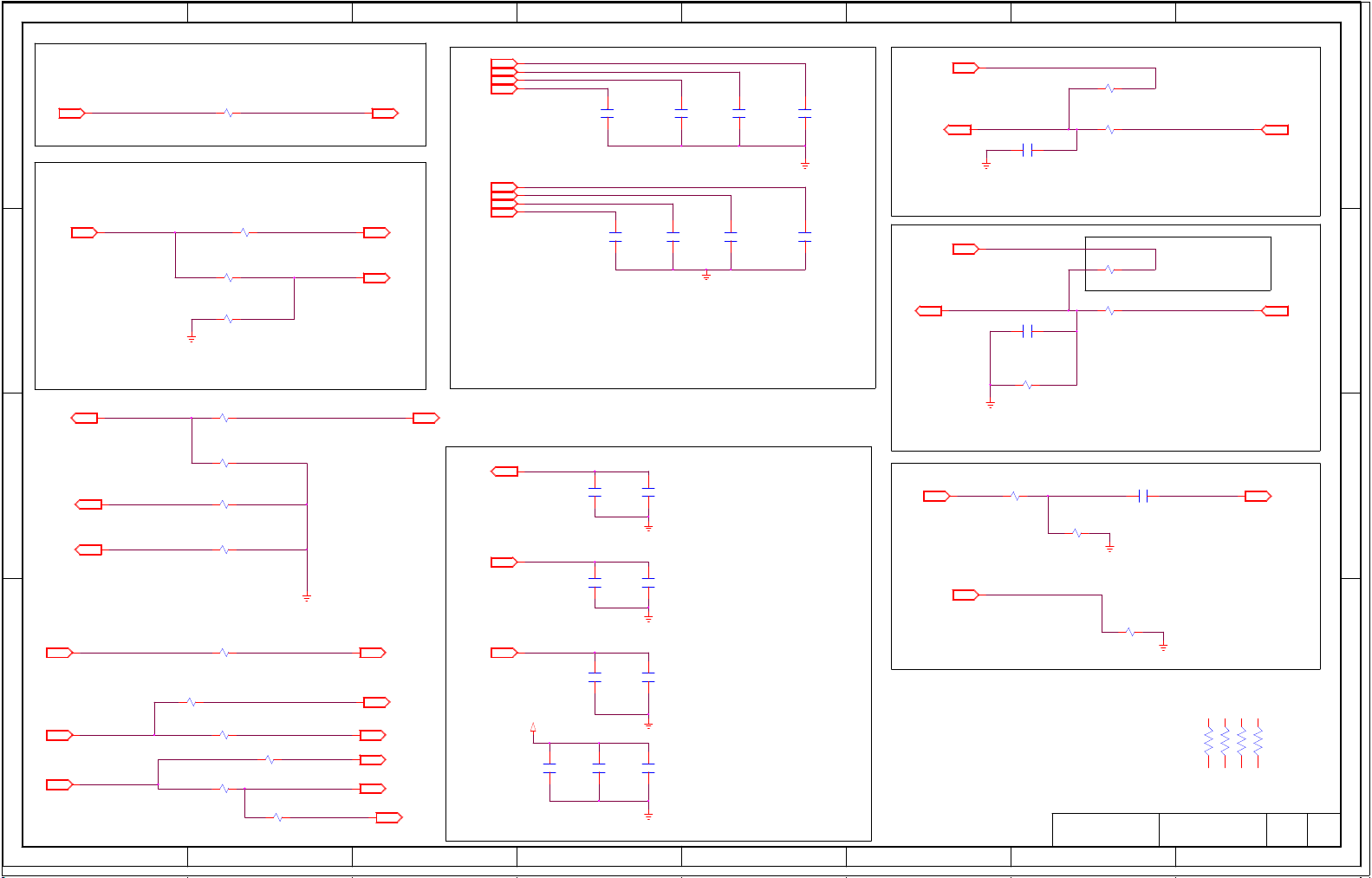

Page 3

<XR_PAGE_TITLE>

AFTER P_PCIRST*, HANDSHAKE (ON HL BUS) BETWEEN ICH/MCH MUST

CORE

D

HAPPEN BEFORE H_CPURST* WILL BE ASSERTED/DE-ASSERTED

MCH: MEMORY

P_PCIRST*

PWRGD_3V

CONTROLLER HUB

H_CPURST*

H_CPURST*

H_PWRGD

PLTRST*

XDP

28 7 6 5 4 3 1

RSTN*

H_CPURST*

H_PWRGD

PGA478 SOCKET

U

D

PORT ANGELES

PCIRST_OUT*

RES: PA_P_TRST*

C

POWER

SUPPLY CONN

P_PCIRST*

SLP_S4/S5*

SLP_S3*

FP_RST*

PWRGP_PSPS_ON* PWRGD_PS

CDC_DWN_RST*

PWRGD_3V

RSMRST*

IDE_RST*

LAN_DSABLE*

KBRST*

PS_ON*

TESTPOINT

IDE_RST*

RES: P_TRST_SLOTS*

IDE CONN1

PCIe GRAPHICS

PWRGD 1X16 CONN

PCIE CONN

X1 PORT 1

PWRGD

RES:FWM_RST*

RST*

RESET

FWH: FIRMWARE HUB

C

TPM (SECURITY)

RES: PS_ON_HEADER*

RES:P_TRST_LAN*

RES:ICH_RSMRST_R*

PE_RST*

LAN_PWRGD

LAN

B

A

COPIED RESET MAP FROM TGRVP_A, 14/10/2003

RESET MAP UPDATED: XX/XX/2003

8 7

FRONT PANEL CONN

PWR ON SWITCH

RESET SWITCH

EV_SW_ON*

XDP

HECETA

RES: SW_ON*

FP_RST*

FP_RST*

DBR*

SW_ON*

JUMPER-STRAP-GND

PULL-UP TERMINATION

PWRGD_3V

RSMRST*

LAN_DISABLE*

RCIN*

SYS_RESET*

RTC_RST*

SW_ON*

FWH

ICH TESTIN

ICH6: I/O

CONTROLLER HUB

45

PLTRST*

P_PCIRST*

H_PWRGD

ACZ_RST*

SLP_S4*

SLP_S3*

VREG SEQUENCING

CONTROL

SLP_S3*

PORT ANGELES

36

CDC_DWN_RST*

P_PCIRST*

PCI SLOT 1

PCI SLOT 2

CONTROL: CDC_DOWN_RST*

RES: AUD_LINK_RST_HDR*

RESET MAP

CONFIDENTIAL

AUDIO CODEC

RESET*

AUD_LINK_RST_HDR*

[PAGE_TITLE=RESET MAP]

INTEL

2 1

DOCUMENT NUMBER PAGE REV

C77862

2X8 Audio HDR

B

A

3

4.0

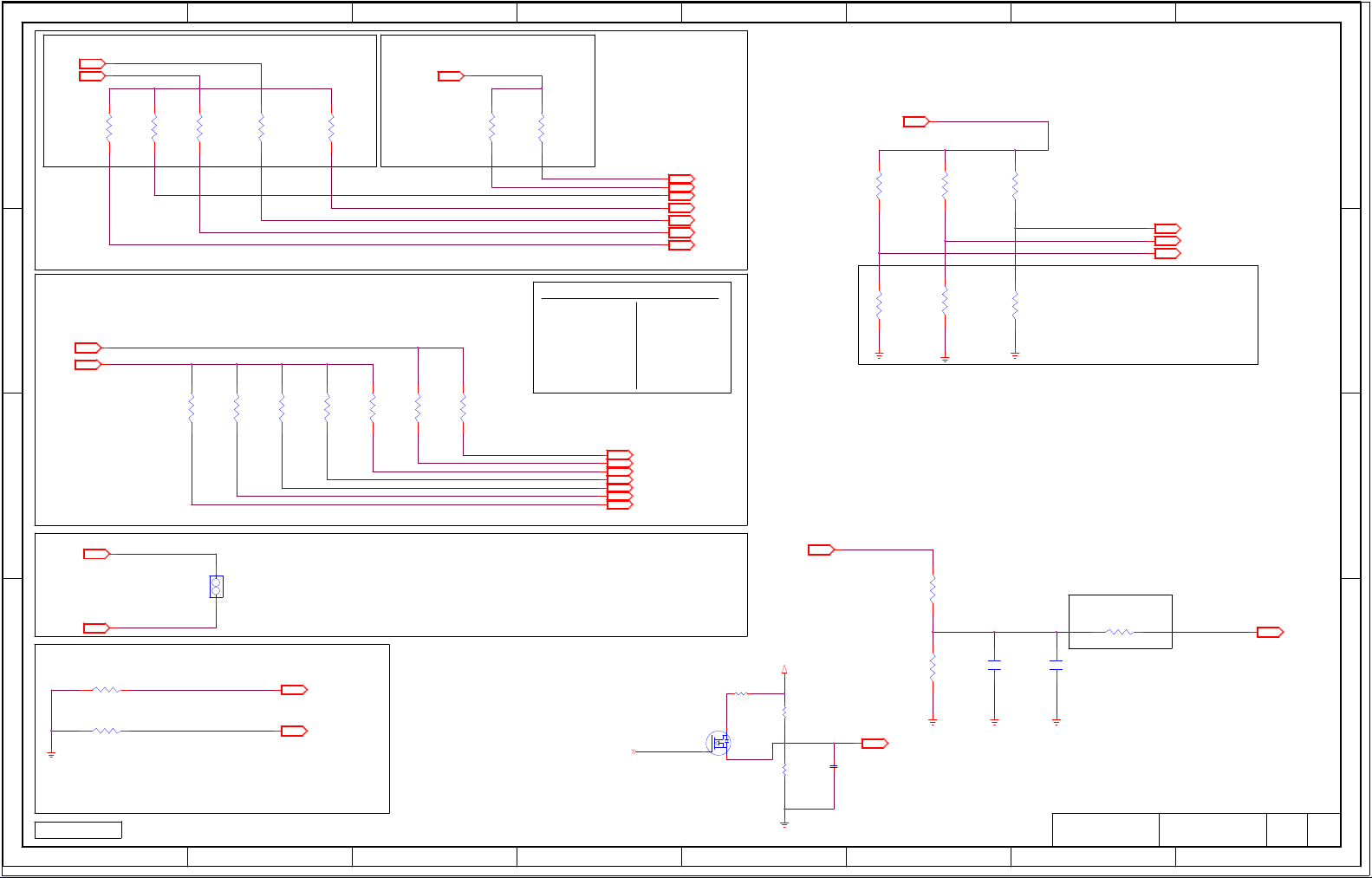

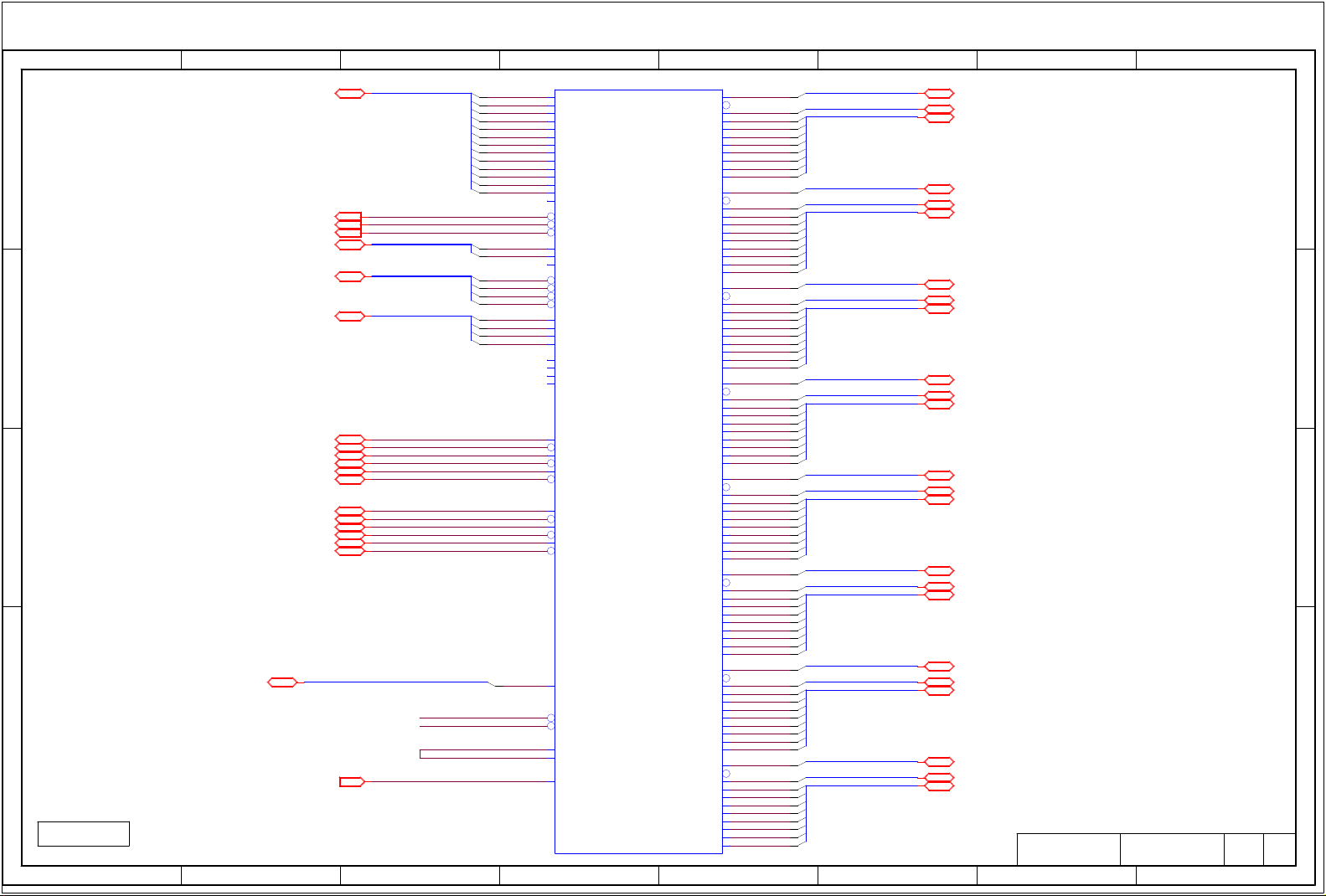

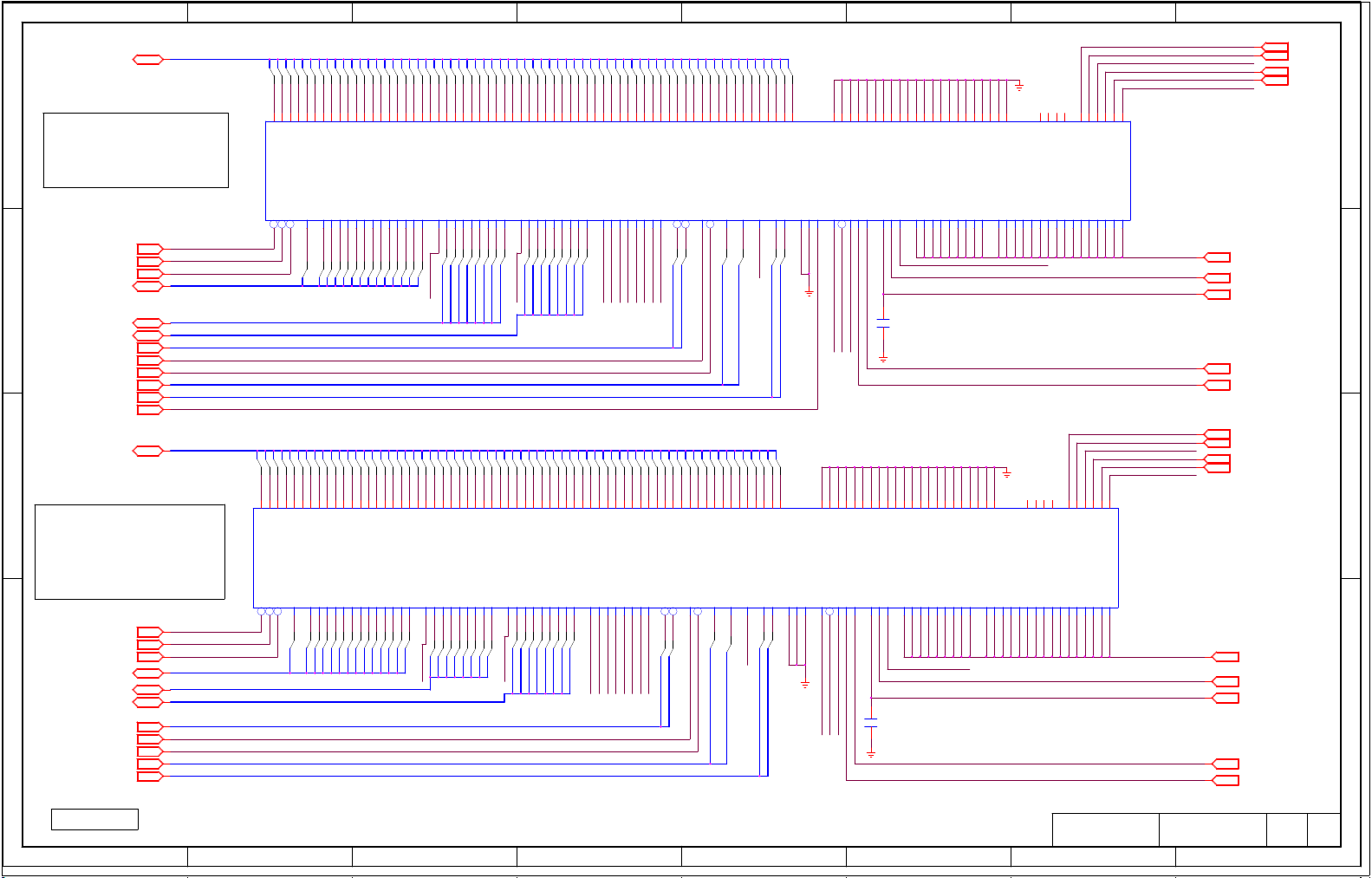

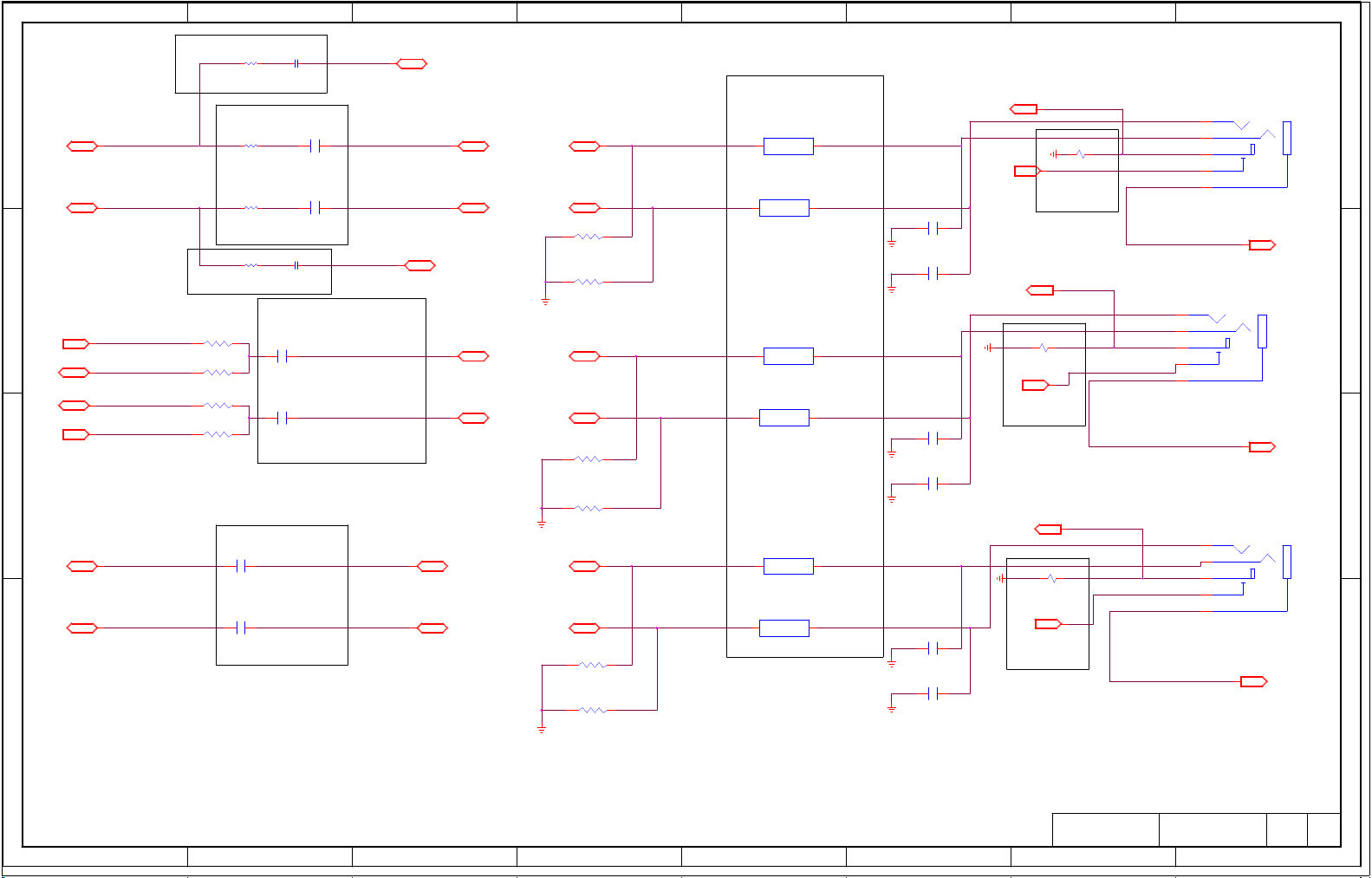

Page 4

<XR_PAGE_TITLE>

28 7 6 5 4 3 1

14.318MHZ

D

C

3.3 VOLT

3.3 VOLT

33MHZ

33MHZ

33MHZ

33MHZ

33MHZ

48MHZ

PCI SLOT 1

PCI SLOT 2

32.7KHZ

LANCLK

CLK14

PCICLK

RTCCLK

USBCLK

DMICLK

SATACLK

AUD_BCLK

ICH 6

SMBUS CLK SCLK

ICH

SCLK

SUSCLK

SUSCLK

32.7KHZ

AUDIO

XTAL-IN

FWH

TPM

HECETA

HARDWARE MANAGEMENT

CODEC

AUD_BCLK

32.7KHZ

12.288 MHZ

PORT

ANGELES

CLK14

33M

KBCLK

MCLK

D

MS/KB

C

1394

100MHZ

100MHZ

CK410E

B

14.318MHZ

100MHZ

100MHZ

100MHZ

100MHZ

X16 PCI-EXPRESS

SCLK

25MHZ

LAN

CRYSTAL

PE_CLK

X1 PCI-EXPRESS #1

EEPROM CLK

PROM

B

A

HOST CLOCK PAIRS

CORE

COPIED CLOCK DISTRIBUTION FROM TGRVP_A, 14/10/2003

CLOCK DISTRIBUTION UPDATED: 12/15/2003

8 7

100MHZ

96MHZ

100/133/167/200 MHZ CPU_CK

100/133/167/200 MHZ CPU_CK

MCH GFX

XDP CLK-OUT OPTION FROM CPU

CPU

CORE

XDP

CLK-OUT

XDP CLK-OUT OPTION

CLOCK DISTRIBUTION

XDP PORT

XDP PORT

MCH

VIDEO TEST

GCLKIN

HOST

DUAL CHANNEL

DDR

CHAN A

DIMM 0

DIMM 1

CHAN B

A

DIMM 0

DIMM 1

[PAGE_TITLE=CLOCK DISTRIBUTION]

INTEL

45

36

CONFIDENTIAL

2 1

DOCUMENT NUMBER PAGE REV

C77862

4

4.0

Page 5

<XR_PAGE_TITLE>

SLOT6

1394

IRQA

DURING

RESET

---

---

---

---

---

---

---

---

HIGH

HIGH

---

---

---

HIGH

HIGH

HI-Z

HI-Z

---

---

---

---

---

---

HIGH

HIGH

--HIGH

HIGH

---

---

---

HIGH

HIGH

HIGH

---

--HIGH

HI-Z

INPUT

INPUT

INPUT

INPUT

INPUT

OUTPUT

INPUT

INPUT

OUTPUT

OUTPUT

OUTPUT

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

OUTPUT

OUTPUT

OUTPUT

5

21

PCIE

X16 X1_1

IRQA

IRQA

S3/S5

DRIVEN

DRIVEN

DEFINED

DEFINED

DEFINED

DEFINED

DEFINED

DEFINED

DEFINED

DEFINED

DEFINED

DEFINED

DEFINED

DEFINED

DEFINED

IRQA

---

---

---

---

---

--OFF

---

---

---

---

--DRIVEN

DRIVEN

DRIVEN

LAN

NOTES

P/U ON PAGE 54, 2.7K TO VCC

P/U ON PAGE 54, 2.7K TO VCC

P/U ON PAGE 54, 8.2K TO VCC3

P/U ON PAGE 54, 8.2K TO VCC3

P/U ON PAGE 54, 8.2K TO VCC3

P/U ON PAGE 54, 8.2K TO VCC3

10K P/D TO 3.3V PG 43

10K P/D TO 3.3V STBY PG 43

10K P/U TO 3.3V STBY PG 43

10K P/D TO GND PG 43

OFF

OFF

---

---

---

---

---

--OFF

---

---

---

--OFF

OFF

OFF

LOW

LOW

OFF

OFF

4.7K P/U TO 3.3V PG 39

10K P/D TO GND PG 43

4.7K P/U TO 3.3V PG 39

4.7K P/U TO 3.3V PG 39

4.7K P/U TO 3.3V PG 39

CONFIG JUMPER

MANUF MODE

HI/LOW BIOS CONFIG FOR IDE PRI (FEATURE IS DEFAULT LOW)

DESIGN FEATURE WITH RESISTOR STRAPPING

DESIGN FEATURE WITH RESISTOR STRAPPING

2X12_DETECT

USB1-F1

USB1-F0

IRQB

USB1-F2

IRQC

USB1-F3

IRQD

USB #2

SMBUS AZALIA

IRQA

IRQB

COPIED INFO FROM TGRVP_A, 10/14/2003

INFORMATION UPDATED: 12/12/2003

GPIO, IRQ, IDSEL MAPS

IRQA

24

IRQA

45

36

PIN NAME

GPI[0]

GPI[2]

GPI[2]

GPI[3]

GPI[4]

GPI[5]

ICH

FWH

GPI[6]

GPI[7]

GPI[8]

GPI[9]

GPI[10]

GPI[11]

GPI[12]

GPI[13]

GPI[14]

GPI[15]

GPO[16]

GPO[17]

GPO[19]

GPO[20]

6

GPO[21]

GPO[22]

GPO[23]

GPIO[24]

GPIO[25]

GPIO[26]

GPIO[27]

GPIO[28]

GPIO[29]

GPIO[30]

GPIO[31]

GPIO[32]

GPIO[33]

GPIO[34]

GPI[40]

GPI[41]

GPO[48]

GPI4

GPI3

GPI2

GPI1

GPI0

GPO0

GPO1

GPO2

D

C

B

WELL

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

MAIN

RESUME

RESUME

CORE

CORE

CORE

CORE

CORE

GPO3

GPO4

GPO5

GPI6

GPI7

PORT

A

GPI010

GPIO11

ANGELES

GPIO12

GPI013

GPI14

IO_PME*

GRN_LED

YLW_LED

IRQ ROUTING TABLE

P_INTA*

P_INTB*

P_INTC*

P_INTD*

P_INTE*

P_INTF*

P_INTG*

P_INTH*

REQ/GNT

IDSEL

USAGE

MAIN

P_REQ6* ---

MAIN

P_REQ5*

MAIN

P_INTE*

MAIN

P_INTF*

MAIN

P_INTG*

MAIN

P_INTH*

MAIN

1X4_DETECT

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

---MAIN

FP_AUD_DETECT

AC_OK (FOR DEBUG HDR) - NOT USED

OC[4]*

OC[5]*

SMBALERT*

SATA HOT SWAP NOT USED

IO_PME*

OC[6]*

OC[7]*

GNT[6]*

GNT[5]*

STP_PCI# NOT USEMAINGPO[18]

OEM_LED0

STP_PCI#

NOT ASSIGN

---1394 ENABLE CTRL

BOARD ID 0

INTERNAL VRM STRAP

SATAGP0

BOARD ID 1

RPS_OFF* (FOR DEBUG HDR) - NOT USED

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

SATAGP1

SATAGP2

SATAGP3

NOT USED

BOARD ID 2

BOARD ID 3

REQ[4]*

LDRQ[1]*

CPUGPO[49]

GNT[4]*

CPUPWRGD

NORM

MFG_MODE*

BSKU4

BAT_WARN (FOR DEBUG HDR) - NOT USED

DMA66_DETECT_PRI

NA

NA

GPO_LAN_DISABLE

NA

BSKU5/1_WATT

NA

FAN_TACH1

FAN_TACH2

5V_DDCSDA

5V_DDCSCL

3V_DDCSDA

3V_DDCSCL

CDC_DWN_ENAB*

IO_PME*

GRN_LED

YLW_LED

SLOT1

IRQD

IRQA

IRQB

IRQC

0

16

PA1.5

SLOT2 SLOT3 SLOT4

IRQC

IRQB

IRQA

IRQD

1

17

PA3.0

SENSOR_SDA

FANTACH3

FANTACH4

FANPWM1

FANPWM2

FANPWM3

FAN_TACH1

FAN_TACH2

5V_DDCSDA

5V_DDCSCL

3V_DDCSDA

3V_DDCSCL

CDC_DWN_ENAB*

SLOT5

8 7

28 7 6 5 4 3 1

[PAGE_TITLE=GPIO, IRQ, IDSEL MAP]

INTEL

DOCUMENT NUMBER PAGE REV

CONFIDENTIAL

2 1

C77862

D

C

B

A

5

4.0

Page 6

<XR_PAGE_TITLE>

28 7 6 5 4 3 1

J3E1D

10

D

10

10

10

C

10

10

B

H_A*[16..3]

BI

H_REQ*[4..0]

BI

H_ADSTB0*

BI

H_PCREQ*

IN

H_A*[31..17]

BI

TP_CPU_AH4

TP_CPU_AH5

TP_CPU_AJ5

TP_CPU_AJ6

TP_CPU_AC4

H_ADSTB1*

BI

TP_CPU_AE4

L5

3

H_A*3

A<3>*

P6

4

H_A*4

A<4>*

M5

5

H_A*5

A<5>*

L4

6

H_A*6

A<6>*

M4

7

H_A*7

A<7>*

R4

8

H_A*8

A<8>*

T5

9

H_A*9

A<9>*

U6

10

H_A*10

A<10>*

T4

11

H_A*11

A<11>*

U5

12

H_A*12

A<12>*

U4

13

H_A*13

A<13>*

V5

14

H_A*14

A<14>*

V4

15

H_A*15

A<15>*

W5

16

H_A*16

A<16>*

N4

RSVD

P5

TP_CPU_P5

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

RSVD

K4

0

H_REQ*0

REQ<0>*

J5

1

H_REQ*1

REQ<1>*

M6

2

H_REQ*2

REQ<2>*

K6

3

H_REQ*3

REQ<3>*

J6

4

H_REQ*4

REQ<4>*

R6

ADSTB<0>*

G5

PCREQ*

AB6

H_A*17

A<17>*

W6

H_A*18

A<18>*

Y6

H_A*19

A<19>*

Y4

H_A*20

A<20>*

AA4

H_A*21

A<21>*

AD6

H_A*22

A<22>*

AA5

H_A*23

A<23>*

AB5

H_A*24

A<24>*

AC5

H_A*25

A<25>*

AB4

H_A*26

A<26>*

AF5

H_A*27

A<27>*

AF4

H_A*28

A<28>*

AG6

H_A*29

A<29>*

AG4

H_A*30

A<30>*

AG5

H_A*31

A<31>*

AH4

A<32>*

AH5

A<33>*

AJ5

A<34>*

AJ6

A<35>*

AC4

RSVD

AE4

RSVD

AD5

ADSTB<1>*

2.0

LGA775

BPRI*

DBSY*

DRDY*

HITM*

IERR*

INIT*

LOCK*

TRDY*

BINIT*

DEFER*

EDRDY*

MCERR*

AP<0>*

AP<1>*

BR<0>*

TESTHI_8

TESTHI_9

TESTHI_10

DP<0>*

DP<1>*

DP<2>*

DP<3>*

GTLREF

RESET*

RS<0>*

RS<1>*

RS<2>*

1 of 4

ADS*

BNR*

HIT*

RSP*

RSVD

D2

H_ADS*

C2

H_BNR*

D4

H_HIT*

H4

TP_RSP*

G8

H_BPRI*

B2

H_DBSY*

C1

H_DRDY*

E4

H_HITM*

AB2

H_IERR*

P3

H_INIT*

C3

H_LOCK*

E3

H_TRDY*

AD3

TP_BINIT*

G7

H_DEFER*

F2

H_EDRDY*

AB3

TP_MCERR*

U2

TP_AP<0>

U3

TP_AP<1>

F3

H_BR0*

G3

H_TESTHI_8

G4

H_TESTHI_9

H5

H_TESTHI_10

J16

TP_DP<0>

H15

TP_DP<1>

H16

TP_DP<2>

J17

TP_DP<3>

H2

H1

CPU_GTLREF

G23

H_CPURST*

0

B3

H_RS*0

1

F5

H_RS*1

2

A3

H_RS*2

H_RS*[2..0]

IC

10

BI

10

BI

10

BI

10

IN

10

BI

10

BI

10

BI

8

OUT

40

IN

10

BI

10

IN

10

IN

10

OUT

8,10

BI

8

BI

8

BI

8

BI

8

IN

8,10,101

IN

10

IN

CAD NOTE:

PLACE CAPS CLOSE TO CPU BEFORE ROUTING

TO CIRCUITS THAT USE THIS VOLTAGE

VTT_OUT_LEFT

7,8,95

IN

J3E1A

LGA775

P2

K3

R3

K1

L1

N2

M3

A23

B23

D23

C23

AM2

0

H_VID_ISOLATE0

AL5

1

H_VID_ISOLATE1

AM3

2

H_VID_ISOLATE2

AL6

3

H_VID_ISOLATE3

AK4

4

H_VID_ISOLATE4

AL4

5

H_VID_ISOLATE5

AM5

F28

G28

AE8

AL1

AK1

AN3

AN4

AN5

AN6

F29

H29

8,40

9

9

9

7

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

OUT

IN

IN

OUT

IN

OUT

OUT

OUT

OUT

OUT

OUT

ICH_H_SMI*

H_A20M*

H_FERR*

H_INTR

H_NMI

H_IGNNE*

H_STPCLK*

H_VCCA

H_VSSA

H_VCCIOPLL

H_VID_ISOLATE[5..0]

CK_H_CPU

CK_H_CPU*

H_SKTOCC*

H_TEMP_RET

H_TEMP_SRC

VCC_SENSE

VSS_SENSE

VCC_PKGSENSE

VSS_PKGSENSE

VTT_PKGSENSE

TP_VCCPLL

TP_VID6

17

RSVD_DET

OUT

40

40

40

40

40

40

30

30

74

79

79

87

2.0

SMI*

A20M*

FERR*/PBE*

LINT0

LINT1

IGNNE*

STPCLK*

VCCA

VSSA

RSVD

VCCIOPLL

VID<0>

VID<1>

VID<2>

VID<3>

VID<4>

VID<5>

RSVD

BCLK<0>

BCLK<1>

SKTOCC*

THERMDA

THERMDC

VCC_SENSE

VSS_SENSE

VCC_MB_REGULATION

VSS_MB_REGULATION

RSVD

GND

3 of 4

TESTHI_0

TESTHI_1

TESTHI_11

TESTHI_12

TESTHI_2

TESTHI_3

TESTHI_4

TESTHI_5

TESTHI_6

TESTHI_7

RSVD

RSVD

SLP*

RSVD

PWRGOOD

PROCHOT*

THERMTRIP*

COMP<0>

COMP<1>

COMP<2>

COMP<3>

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

BOOTSELECT

LL_ID<0>

LL_ID<1>

F26

H_TESTHI_0

W3

H_TESTHI_1

P1

H_TESTHI_11

W2

H_TESTHI_12

F25

G25

G27

G26

G24

F24

AK6

G6

L2

AH2

N1

AL2

M2

A13

T1

G2

R1

J2

T2

N5

AE6

C9

G10

D16

A20

E23

E24

F23

V1

W1

J3

Y1

V2

AA2

TP_H_PSMI*

TP_RSVD_CPU_N5

TP_RSVD_CPU_AE6

TP_RSVD_CPU_C9

TP_RSVD_CPU_G10

TP_RSVD_CPU_D16

TP_RSVD_CPU_A20

H_TESTHI_2_7

RSVD_AK6

RSVD_G6

H_SLP*

H_PWRGD

H_PROCHOT*

H_THERMTRIP_ICH*

H_COMP0

H_COMP1

H_COMP2

H_COMP3

H_RSVD1

H_RSVD2

CPU_BOOT

LL_ID0

TP_LL_ID1

8

IN

8

IN

8

IN

IN

8

IN

IN

IN

40

IN

8,40,101

IN

8,103

IN

8,40

OUT

8

IN

8

IN

IN

IN

IN

IN

IN

95

OUT

D

C

B

IC

A

IN

IN

IN

IN

CORE PAGE

VCC_SENSE

VCC_PKGSENSE

VSS_SENSE

VSS_PKGSENSE

R2F16

0 5%

402 EMPTY

R2F17

0

402 CH

R1F3

0 5%

EMPTY402

R1F2

0

4025%CH

8 7

5%

12

12

12

12

VCC_VRM_SENSE

VSS_VRM_SENSE

C2F6

.1UF

20%

25V

EMPTY

603

C2E1

.1UF

20%

25V

EMPTY

603

2

1

2

1

8,95

OUT

8,95

OUT

VTT_OUT_RIGHT

7,8,95,101

IN

2

1

R2F21

62

5%

EMPTY

402

2

1

R2F4

100

1%

CH

402

2

R3F3

100

1%

CH

402

1

H_COMP2

2

R2F6

62

5%

CH

402

1

H_TESTHI_12

H_COMP2

H_COMP3

RSVD_G6

2

R2F11

62

5%

EMPTY

402

1

2

R2F29

1K

5%

EMPTY

402

1

CPU_BOOT

RSVD_AK6

OUT

OUT

45

12

12

R2F28

R2F18

60.4

60.4

1%

1%

EMPTY

EMPTY

402

402

H_RSVD2

OUT

H_RSVD1

OUT

OUT

OUT

OUT

OUT

A

CPU SOCKET

[PAGE_TITLE=CPU-SOCKET]

INTEL

CONFIDENTIAL

36

2 1

DOCUMENT NUMBER PAGE REV

C77862

6

4.0

Page 7

D

C

B

A

6

10

BI

10

BI

10

BI

10

BI

10

BI

10

BI

10

BI

10

BI

CORE PAGE

<XR_PAGE_TITLE>

BOM NOTE:

H_VID_ISOLATE[5..0]

IN

H_D*[15..0]

H_DBI0*

H_STBN0*

H_STBP0

H_D*[31..16]

H_DBI1*

H_STBN1*

H_STBP1

8 7

0

1

2

3

4

5

8,17,29

ALWAYS STUFF ON

PRODUCT BOARDS

H_VID_ISOLATE0

0

402

H_VID_ISOLATE1

H_VID_ISOLATE2

H_VID_ISOLATE3

H_VID_ISOLATE4

H_VID_ISOLATE5

0 5%

8,17,29

B4

0

H_D*0

C5

1

H_D*1

A4

2

H_D*2

C6

3

H_D*3

A5

4

H_D*4

B6

5

H_D*5

B7

6

H_D*6

A7

7

H_D*7

A10

8

H_D*8

A11

9

H_D*9

B10

10

H_D*10

C11

11

H_D*11

D8

12

H_D*12

B12

13

H_D*13

C12

14

H_D*14

D11

15

H_D*15

A8

C8

B9

G9

16

H_D*16

F8

17

H_D*17

F9

18

H_D*18

E9

19

H_D*19

D7

20

H_D*20

E10

21

H_D*21

D10

22

H_D*22

F11

23

H_D*23

F12

24

H_D*24

D13

25

H_D*25

E13

26

H_D*26

G13

27

H_D*27

F14

28

H_D*28

G14

29

H_D*29

F15

30

H_D*30

G15

31

H_D*31

G11

G12

E12

R1F17

5%

CH

R1F19

5%0

CH402

R1F15

5%0

CH402

R1F18

5%0

CH402

R1F20

5%0

CH402

R1F16

CH402

8,17,29

OUT

OUT

D<0>*

D<1>*

D<2>*

D<3>*

D<4>*

D<5>*

D<6>*

D<7>*

D<8>*

D<9>*

D<10>*

D<11>*

D<12>*

D<13>*

D<14>*

D<15>*

DBI<0>*

DSTBN<0>*

DSTBP<0>

D<16>*

D<17>*

D<18>*

D<19>*

D<20>*

D<21>*

D<22>*

D<23>*

D<24>*

D<25>*

D<26>*

D<27>*

D<28>*

D<29>*

D<30>*

D<31>*

DBI<1>*

DSTBN<1>*

DSTBP<1>

H_VID[5..0]

12

0

H_VID0

12

1

H_VID1

12

2

H_VID2

12

3

H_VID3

12

4

H_VID4

12

5

H_VID5

H_FSBSEL0 H_FSBSEL0_ISOL

OUT

H_FSBSEL1 H_FSBSEL1_ISOL

H_FSBSEL2 H_FSBSEL2_ISOL

J3E1B

LGA775

2.0

D<32>*

D<33>*

D<34>*

D<35>*

D<36>*

D<37>*

D<38>*

D<39>*

D<40>*

D<41>*

D<42>*

D<43>*

D<44>*

D<45>*

D<46>*

D<47>*

DBI<2>*

DSTBN<2>*

DSTBP<2>

D<48>*

D<49>*

D<50>*

D<51>*

D<52>*

D<53>*

D<54>*

D<55>*

D<56>*

D<57>*

D<58>*

D<59>*

D<60>*

D<61>*

D<62>*

D<63>*

DBI<3>*

DSTBN<3>*

DSTBP<3>

95

OUT

101

101

101

101

101

101

40,43,74,81,101

101

101

R4C20

12

5%0

R4C25

12

5%

0

CH

402

G16

32

H_D*32

E15

33

H_D*33

E16

34

H_D*34

G18

35

H_D*35

G17

36

H_D*36

F17

37

H_D*37

F18

38

H_D*38

E18

39

H_D*39

E19

40

H_D*40

F20

41

H_D*41

E21

42

H_D*42

F21

43

H_D*43

G21

44

H_D*44

E22

45

H_D*45

D22

46

H_D*46

G22

47

H_D*47

D19

G20

G19

D20

48

H_D*48

D17

49

H_D*49

A14

50

H_D*50

C15

51

H_D*51

C14

52

H_D*52

B15

53

H_D*53

C18

54

H_D*54

B16

55

H_D*55

A17

56

H_D*56

B18

57

H_D*57

C21

58

H_D*58

B21

59

H_D*59

B19

60

H_D*60

A19

61

H_D*61

A22

62

H_D*62

B22

63

H_D*63

C20

H_DBI3*

A16

H_STBN3*

C17

H_STBP3

R4C21

H_D*[47..32]

H_DBI2*

H_STBN2*

H_STBP2

H_D*[63..48]

CH402

12

5%0

CH402

BI

BI

BI

2 of 4

IC

28 7 6 5 4 3 1

J3E1C

LGA775

TCK

TDI

TDO

TMS

TRST*

BPM<0>*

BPM<1>*

BPM<2>*

BPM<3>*

BPM<4>*

BPM<5>*

DBR*

ITPCLK<0>

ITPCLK<1>

BSEL<0>

BSEL<1>

BSEL<2>

45

2.0

BOM NOTE:

ALWAYS STUFF ON

PRODUCT BOARDS

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT_PWRGD

VTT_OUT

VTT_OUT

VTT_SEL

4 of 4

A29

B25

B29

B30

C29

A26

B27

C28

A25

A28

A27

C30

A30

C25

C26

C27

B26

D27

D28

D25

D26

B28

D29

D30

AM6

AA1

J1

F27

IC

VTT_PWRGD

VTT_OUT_RIGHT

VTT_OUT_LEFT

VTT_SEL

V_FSB_VTT

TPEV_VCCFUSEPRG

TPEV_VIDFUSEPRG

8,9,12,17,18,41,43,87

IN

D

VCC3

IN

IN

95

IN

OUT

OUT

6,8,95,101

6,8,95

OUT

87

2

R4C22

1K

5%

EMPTY

402

1

C

B

IN

VTT_OUT_RIGHT

6,8,95,101

A

2

2

2

R1F26

R1F25

680

680

5%

OUT

OUT

95

H_VID[5..0]

IN

1

5%

CH

CH

402

402

1

H_VID0

H_VID1

0

1

INTEL

CONFIDENTIAL

36

2 1

2

R1F24

R2F42

680

680

5%

5%

CH

CH

402

1

H_VID2

2

402

1

H_VID3

3

DOCUMENT NUMBER PAGE REV

C77862

2

2

1

4

H_VID4

R2F40

680

5%

CH

402

R1F28

680

5%

CH

402

1

H_VID5

5

7

4.0

0

H_BPM*0

1

H_BPM*1

2

H_BPM*2

3

H_BPM*3

4

H_BPM*4

5

H_BPM*5

V_FSB_VTT

2

R4C26

0

5%

CH

402

1

AE1

AD1

AF1

AC1

AG1

AJ2

AJ1

AD2

AG2

AF2

AG3

AC2

AK3

AJ3

G29

H30

G30

2

R4C27

0

5%

CH

402

1

TPEV_VIDFUSEPRG

TPEV_VCCFUSEPRG

H_TCK

IN

H_TDI

IN

H_TDO

OUT

H_TMS

IN

H_TRST*

IN

H_BPM*[5..0]

BI

FP_RST*

IN

XDP_CLKOUT

OUT

XDP_CLKOUT*

OUT

VCCP=AG22,K29,AM26,AL8,AE12,AE11

VCCP=W23,W24,W25,T25,Y28,AL18,AC25,W30,Y30,AN14,AD28,Y26,AC29,M29,U24,J23,AC27,AM18,AM19,AB8

VCCP=AC26,J8,J28,T30,AM9,AF15,AC8,AE14,N23,W29,U29,AC24,AC23,Y23,AN26,AN25,AN11,AN18,Y27,Y25

VCCP=AD24,AE23,AE22,AN19,V8,K8,AE21,AM30,AE19,AC30,AE15,M30,K27,M24,AN21,T8,AC28,N25,AE18,W26

VCCP=AD25,M8,N30,AD26,AJ26,AM29,M25,M26,L8,U25,Y8,AJ12,AD27,U23,M23,AG29,N27,AM22,U28,K28

10

BI

10

BI

10

BI

10

BI

10

BI

10

10

10

VCCP=U8,AK18,AD8,K24,AH28,AH21,AK12,AH22,T29,AM14,AM25,AE9,Y29,AK25,AK19,AG15,J22,T24,AG21,AM21

VCCP=J25,U30,AL21,AG25,AJ18,J19,AH30,J15,AG12,AJ22,J20,AH18,AH26,W27,AL25,AN8,AH14,U27,T23,R8

VCCP=AK22,AN29,AG11,AK26,J10,AJ15,AG26,AN9,AH15,AF18,AL15,J26,J18,J21,AG27,AK15,AF11,AD23,AM15,AF8

VCCP=AK21,AG30,AJ21,AM11,AL11,AJ11,K30,AL14,AN30,AH25,AL12,AJ9,AK11,AG14,N29,AL30,AJ25,AH9,J29,J11

VCCP=K25,P8,K23,AL19,AM8,T26,N28,AH12,AL22,AN15,AJ8,U26,AJ19,T27,AK8,AN12,AG9,N26,AF9,AF22

VCCP=AH11,AJ14,AH19,AH29,AH27,AG28,AL26,AM12,J24,J13,T28,W28,J12,J27,AG19,AL9,AD30,AF21,Y24,AK14

VCCP=J9,M27,AF14,J30,AG18,AA8,AG8,AL29,AD29,W8,AH8,N24,AN22,J14,K26,AF19,N8,AF12,M28,AK9

GND=C10,D12,AM7,C24,K2,C22,AN1,B14,K7,AE16,B11,AL10,AK23,H12,AF7,AK7

GND=H7,E14,L28,Y5,E11,AL16,AL24,AK13,AL3,D21,AL20,D18,AN2,AK16,AK20,AM27,AM1,AL13,AL17,C19

GND=E28,AH7,AK30,D24,AL23,A12,L25,J7,AE28,AE29,K5,J4,AE30,AN20,AF10,AE24,AM24,AN23,H9,H8

GND=H13,AC6,AC7,AH6,C16,AM16,AE25,AE27,AJ28,AJ7,F19,AH13,AD7,AH16,AK17,E17,AH17,AH20,AE5,AH23

GND=AE7,AM13,AH24,AJ30,AJ10,AF3,AK5,AJ16,AF6,AK29,AJ17,F22,AH3,AK10,AM10,F16,AJ23,F13,AG7,F10

GND=L26,AD4,H11,L24,L23,AM23,A15,AH10,B24,L3,H27,A21,AE2,AJ29,A24,AK27,AK28,B20,AM20

GND=H26,B17,H25,H24,AA3,AA7,H23,AA6,H10,H22,H21,H20,H19,H18,AB7,H17,AJ24,AM17,AC3,H14

GND=P28,V6,AK2,P27,P26,AM28,AJ13,W4,P25,AJ20,W7,P23,C7,Y2,L30,L29,D15,AL27,Y7,L27

GND=AA29,N6,N7,AA28,AN13,AA27,AA26,P4,AA25,AA24,P7,E26,V30,R2,V29,V28,R5,V27,R7,E20

GND=AN10,V25,T3,V24,V23,T6,AL7,E25,U1,R29,R28,R27,R26,R25,U7,R24,R23,P30,V3,P29

GND=AF16,AE10,AF13,H6,A18,A2,E2,D9,C4,A6,D6,D5,A9,D3,B1,B5,B8,AJ4,AE26,AH1

GND=E29,V7,C13,AK24,AB30,L6,L7,AB29,M1,AB28,AN17,AB27,AB26,AN16,M7,AB25,AB24,AB23,N3,AA30

GND=F4,AG10,AE13,AF30,H28,F7,AF29,AF28,G1,AF27,AF26,AF25,AN28,AN27,AF24,AF23,AG24,AF17,AN24,H3

GND=AN7,P24,AE20,AE17,E27,T7,R30,AJ27,AB1,AM4,V26,AA23,AL28,AF20,AG23,AG20,E8,AG17,AG16,AG13

NC=F6,Y3,AE3,E7,B13,D14,E6,D1,E5,

8,9,12,17,18,41,43,87

IN

[PAGE_TITLE=CPU-SOCKET]

Page 8

<XR_PAGE_TITLE>

28 7 6 5 4 3 1

VTT_OUT_RIGHT

6,7,95,101

IN

VTT_OUT_LEFT

6,7,95

IN

D

R3F1

62

5%

CH

402

H_BR0*

1 2

C

V_FSB_VTT

7,9,12,17,18,41,43,87

IN

VTT_OUT_LEFT

6,7,95

IN

B

VCC_VRM_SENSE

6,95

IN

NEVER JUMPER

THIS HEADER!!!

VSS_VRM_SENSE

6,95

IN

PRECISION FSB COMPENSATION RESISTORS

A

PLACE RESISTORS OUTSIDE SOCKET CAVITY

IF NO ROOM FOR VARIABLE RESISTOR DON'T PLACE.

R4D1

60.4CH1%

402

R2F5

60.4 1%

402

12

12

CH

CORE PAGE

8 7

2

R4C24

62

5%

CH

402

1

7,9,12,17,18,41,43,87

IN

CAD NOTE: PLACE AT

ICH END OF ROUTE

V_FSB_VTT

2

R7H2

62

5%

CH

402

1

2

R4C23

62

5%

EMPTY

402

1

H_TESTHI_0

H_TESTHI_2_7

H_TESTHI_1

H_TESTHI_8

H_TESTHI_9

H_TESTHI_10

H_TESTHI_11

2

R7H3

62

5%

CH

402

1

H_THERMTRIP_ICH*

H_FERR*

H_IERR*

H_CPURST*

H_PROCHOT*

H_PWRGD

H_BR0*

TESTHI PIN NAME MAPPING

TESTHI[0]

TESTHI[1] ODT

TESTHI[5:2]

TESTHI[7:6]

TESTHI[10:8]

TESTHI[11]

TESTHI[12]

BYPASSEN

MCLK[3:0]

MCLKIO[1:0]

BR#[3:1]

DPSLP#

DT_SVR#

6

OUT

6

OUT

6

OUT

6

OUT

6

OUT

6

OUT

6

OUT

RSVD_DET6,17

RSVD_DET

V_FSB_VTT

7,9,12,17,18,41,43,87

IN

2

6,40

OUT

6,40

OUT

6

OUT

OUT

OUT

6,10,101

OUT

6,103

OUT

6,40,101

6,10

R4C18

470

5%

CH

402

1

2

R4C15

1K

5%

EMPTY

402

1

2

R4C19

470

5%

CH

402

1

2

R4C16

1K

5%

EMPTY

402

1

2

R4C17

470

5%

CH

402

1

2

R4C14

1K

5%

EMPTY

402

1

H_FSBSEL0

H_FSBSEL1

H_FSBSEL2

DESIGN NOTE:

STRAPPING OPTION FOR DEBUG

OUT

OUT

OUT

7,17,29

7,17,29

7,17,29

D

C

B

R4C29

1 2

249

1% 402

Q4C4

SOT23

201924-001

FET

VTT_OUT_RIGHT

GTLREF VOLTAGE SHOULD BE 0.67*VTT = 0.8V

6,7,95,101

IN

2

1

2

VCC3

CH

12

R4C11

110

CH

1%

402

H_TESTHI_0

12

R4C13

61.9

CH

1%

402

OUT

C4C3

.1UF

20%

16V

1 2

Y5V

402

1

6

100 OHMS OVER 210 OHMS RESISTORS

R2F23

100

1%

CH

402

CPU_GTLREF_DIVIDER

R2F24

210

1%

CH

402

2

1

C2F2

1.0UF

20%

10V

Y5V

603

(FOR THIS DESIGN)

EVAL FEATURE

2

C2F1

220PF

10%

50V

1

EMPTY

402

R2F20

12

CPU_GTLREF

5%

30

CH

402

6

OUT

A

CAD NOTE: PLACE AT

CPU END OF ROUTE

2

2

1

R2F31

62

5%

CH

402

R2F2

100

5%

CH

402

1

2

R2F19

62

5%

EMPTY

402

1

2

R2F25

62

5%

CH

402

1

CPU SIGNAL TERMINATION

TESTHI PULLUPS

2

2

2

2

R2F3

62

5%

CH

402

1

1

1

1X2HDR

EMPTY

102276-001

2

H_COMP0

H_COMP1

R3F2

R2F1

62

62

5%

5%

CH

CH

402

402

1

J1F1

6

OUT

6

OUT

2

R3F4

R2F7

62

62

5%

5%

CH

CH

402

1

402

1

DESIGN NOTE:

THE PINS WILL BE USED AS TEST/PROBE POINTS ONLY.

CAD NOTE:

PLACE HEADERS AS CLOSE TO CPU PINS AS POSSIBLE

[PAGE_TITLE=CPU TERMINATION & MISC]

INTEL

CONFIDENTIAL

45

36

2 1

DOCUMENT NUMBER PAGE REV

C77862

8

4.0

Page 9

<XR_PAGE_TITLE>

28 7 6 5 4 3 1

D

D

CPU PLL SUPPLY FILTER

V_FSB_VTT

7,8,12,17,18,41,43,87

IN

1

693286-014

FB4C1

FB

2

C

7,8,12,17,18,41,43,87

IN

1

693286-014

FB4C2

FB

2

B

V_FSB_VTT

1

2

1

2

10UH

L4C2

EMPTY

721891-026

"125 MA"

"0805"

10UH

L4C1

EMPTY

721891-026

"125 MA"

"0805"

"201307-107"

H_VCCIOPLL

2

R4C12

0

5%

CH

402

1

2

C4C5

1.0UF

20%

10V

1

EMPTY

603

"Y5V"

H_VCCA

R4C7

1

C4C1

2

33UF

20%

25V

ALUM

2

RDL

C4C4

1.0UF

20%

10V

1

EMPTY

603

"Y5V"

1 2

0 5%

402

EMPTY

DESIGN NOTE:

ALWAYS EMPTY. DEBUG HOOK.

H_VSSA

OUT

OUT

TP_H_VCCA_STEP

OUT

6

C

6

B

6

A

CORE PAGE

CAD NOTE:

PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

TRACE WIDTH TO CAPS MUST BE NO SMALLER THAN 12MIL

8 7

A

[PAGE_TITLE=CPU ANALOG PLL FILTER]

INTEL

CONFIDENTIAL

45

36

2 1

DOCUMENT NUMBER PAGE REV

C77862

9

4.0

Page 10

<XR_PAGE_TITLE>

U6D1G

GDG_DDR1_1210

6

H_A*[31..3]

D

J4D1

J6F1

J4F1

1

NC

A13494-005

EMPTY

1

NC

EMPTY

1

NC

EMPTY

J6D1

1

NC

EMPTY

HS6D1

GDG_WAVEHS

1 2

NC_2

NC_1

NC_3

NC_4

C44993-001

HEATSINK

34

BI

WAVE SOLDER HEAT-SINK = WSHS

C

6

H_REQ*[4..0]

BI

6

H_ADSTB0*

BI

6

H_ADSTB1*

BI

6

H_PCREQ*

OUT

7

H_STBP0

BI

7

H_STBN0*

BI

7

H_DBI0*

B

A

BI

7

H_STBP1

BI

7

H_STBN1*

BI

7

H_DBI1*

BI

7

H_STBP2

BI

7

H_STBN2*

BI

7

H_DBI2*

BI

7

H_STBP3

BI

7

H_STBN3*

BI

7

H_DBI3*

BI

6

H_ADS*

BI

6

H_BNR*

BI

6

H_BPRI*

OUT

6,8

H_BR0*

OUT

6,8,101

H_CPURST*

OUT

6

H_DBSY*

BI

6

H_DEFER*

OUT

6

H_DRDY*

OUT

6

H_EDRDY*

IN

6

H_HIT*

OUT

6

H_HITM*

OUT

6

H_LOCK*

IN

6

H_RS*[2..0]

BI

6

H_TRDY*

OUT

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

0

1

2

3

4

0

1

2

H29

H_A*3

H_A*4

H_A*5

H_A*6

H_A*7

H_A*8

H_A*9

H_A*10

H_A*11

H_A*12

H_A*13

H_A*14

H_A*15

H_A*16

H_A*17

H_A*18

H_A*19

H_A*20

H_A*21

H_A*22

H_A*23

H_A*24

H_A*25

H_A*26

H_A*27

H_A*28

H_A*29

H_A*30

H_A*31

H_REQ*0

H_REQ*1

H_REQ*2

H_REQ*3

H_REQ*4

H_RS*0

H_RS*1

H_RS*2

HA3*

K29

HA4*

J29

HA5*

G30

HA6*

G32

HA7*

K30

HA8*

L29

HA9*

M30

HA10*

L31

HA11*

L28

HA12*

J28

HA13*

K27

HA14*

K33

HA15*

M28

HA16*

R29

HA17*

L26

HA18*

N26

HA19*

M26

HA20*

N31

HA21*

P26

HA22*

N29

HA23*

P28

HA24*

R28

HA25*

N33

HA26*

T27

HA27*

T31

HA28*

U28

HA29*

T26

HA30*

T29

HA31*

F33

HREQ0*

E32

HREQ1*

H31

HREQ2*

G31

HREQ3*

F31

HREQ4*

J31

HADSTB0*

N27

HADSTB1*

E31

HPCREQ*

E33

HDSTBP0

E35

HDSTBN0*

E34

HDINV0*

H26

HDSTBP1

F26

HDSTBN1*

J26

HDINV1*

J19

HDSTBP2

F19

HDSTBN2*

K19

HDINV2*

B29

HDSTBP3

C29

HDSTBN3*

B26

HDINV3*

M31

HADS*

M35

HBNR*

E30

HBPRI*

R33

HBREQ0*

G24

HCPURST*

L35

HDBSY*

J35

HDEFER*

M32

HDRDY*

P33

HEDRDY*

L34

HHIT*

N35

HHITM*

L33

HLOCK*

K34

HRS0*

P34

HRS1*

J32

HRS2*

N34

HTRDY*

1.0

HD0*

HD1*

HD2*

HD3*

HD4*

HD5*

HD6*

HD7*

HD8*

HD9*

HD10*

HD11*

HD12*

HD13*

HD14*

HD15*

HD16*

HD17*

HD18*

HD19*

HD20*

HD21*

HD22*

HD23*

HD24*

HD25*

HD26*

HD27*

HD28*

HD29*

HD30*

HD31*

HD32*

HD33*

HD34*

HD35*

HD36*

HD37*

HD38*

HD39*

HD40*

HD41*

HD42*

HD43*

HD44*

HD45*

HD46*

HD47*

HD48*

HD49*

HD50*

HD51*

HD52*

HD53*

HD54*

HD55*

HD56*

HD57*

HD58*

HD59*

HD60*

HD61*

HD62*

HD63*

HXSWING

HXSCOMP

HXRCOMP

HVREF

HCLKINP

HCLKINN

1 of 7

J33

H33

J34

G35

H35

G34

F34

G33

D34

C33

D33

B34

C34

B33

C32

B32

E28

C30

D29

H28

G29

J27

F28

F27

E27

E25

G25

J25

K25

L25

L23

K23

J22

J24

K22

J21

M21

H23

M19

K21

H20

H19

M18

K18

K17

G18

H18

F17

A25

C27

C31

B30

B31

A31

B27

A29

C28

A28

C25

C26

D27

A27

E24

B25

A23

D24

B23

A24

M23

M22

IC

0

H_D*0

1

H_D*1

2

H_D*2

3

H_D*3

4

H_D*4

5

H_D*5

6

H_D*6

7

H_D*7

8

H_D*8

9

H_D*9

10

H_D*10

11

H_D*11

12

H_D*12

13

H_D*13

14

H_D*14

15

H_D*15

16

H_D*16

17

H_D*17

18

H_D*18

19

H_D*19

20

H_D*20

21

H_D*21

22

H_D*22

23

H_D*23

24

H_D*24

25

H_D*25

26

H_D*26

27

H_D*27

28

H_D*28

29

H_D*29

30

H_D*30

31

H_D*31

32

H_D*32

33

H_D*33

34

H_D*34

35

H_D*35

36

H_D*36

37

H_D*37

38

H_D*38

39

H_D*39

40

H_D*40

41

H_D*41

42

H_D*42

43

H_D*43

44

H_D*44

45

H_D*45

46

H_D*46

47

H_D*47

48

H_D*48

49

H_D*49

50

H_D*50

51

H_D*51

52

H_D*52

53

H_D*53

54

H_D*54

55

H_D*55

56

H_D*56

57

H_D*57

58

H_D*58

59

H_D*59

60

H_D*60

61

H_D*61

62

H_D*62

63

H_D*63

28 7 6 5 4 3 1

H_D*[63..0]

HXSWING

HXSCOMP

HXRCOMP

MCH_GTLREF

CK_H_MCH

CK_H_MCH*

BI

17

IN

17

IN

17

IN

17

IN

30

IN

30

IN

7

D

C

B

A

CORE PAGE

8 7

[PAGE_TITLE=MCH SECTIONS PAGE 1 OF 6]

INTEL

CONFIDENTIAL

45

36

2 1

DOCUMENT NUMBER PAGE REV

C77862

10

4.0

Page 11

<XR_PAGE_TITLE>

28 7 6 5 4 3 1

D

32

IN

32

IN

32

IN

32

IN

32

IN

32

IN

32

IN

32

IN

32

IN

32

IN

32

IN

32

IN

32

IN

32

IN

32

IN

32

IN

32

IN

32

IN

32

IN

32

IN

32

IN

C

SIGNAL NAMING CONVENTION

EXP: PCI EXPRESS

DMI: DIRECT MEDIA INTERFACE

ITP: ICH TRANSMIT POSITIVE

ITN: ICH TRANSMIT NEGATIVE

B

IRP: ICH RECEIVE POSITIVE

IRN: ICH RECEIVE NEGATIVE

MTP: MCH TRANSMIT POSITIVE

MTN: MCH TRANSMIT NEGATIVE

MRP: MCH RECEIVE POSITIVE

32

IN

32

IN

32

IN

32

IN

32

IN

32

IN

32

IN

32

IN

32

IN

32

IN

32

IN

38,100

BI

38,100

BI

38,100

BI

38,100

BI

38,100

BI

38,100

BI

38,100

BI

38,100

BI

30

IN

30

IN

32

BI

32

OUT

EXP_A_RXP_0

EXP_A_RXN_0

EXP_A_RXP_1

EXP_A_RXN_1

EXP_A_RXP_2

EXP_A_RXN_2

EXP_A_RXP_3

EXP_A_RXN_3

EXP_A_RXP_4

EXP_A_RXN_4

EXP_A_RXP_5

EXP_A_RXN_5

EXP_A_RXP_6

EXP_A_RXN_6

EXP_A_RXP_7

EXP_A_RXN_7

EXP_A_RXP_8

EXP_A_RXN_8

EXP_A_RXP_9

EXP_A_RXN_9

EXP_A_RXP_10

EXP_A_RXN_10

EXP_A_RXP_11

EXP_A_RXN_11

EXP_A_RXP_12

EXP_A_RXN_12

EXP_A_RXP_13

EXP_A_RXN_13

EXP_A_RXP_14

EXP_A_RXN_14

EXP_A_RXP_15

EXP_A_RXN_15

CK_PE_100M_MCH

CK_PE_100M_MCH*

SDVO_CTRL_DATA

SDVO_CTRL_CLK

DMI_ITP_MRP_0

DMI_ITN_MRN_0

DMI_ITP_MRP_1

DMI_ITN_MRN_1

DMI_ITP_MRP_2

DMI_ITN_MRN_2

DMI_ITP_MRP_3

DMI_ITN_MRN_3

E11

F11

J11

H11

F9

E9

F7

E7

B3

B4

D5

E5

G6

G5

H8

H7

J6

J5

K8

K7

L6

L5

P10

R10

M8

M7

N6

N5

P7

P8

R6

R5

U5

U6

T9

T8

V7

V8

V10

U10

A11

B11

K13

J13

EXPARXP0

EXPARXN0

EXPARXP1

EXPARXN1

EXPARXP2

EXPARXN2

EXPARXP3

EXPARXN3

EXPARXP4

EXPARXN4

EXPARXP5

EXPARXN5

EXPARXP6

EXPARXN6

EXPARXP7

EXPARXN7

EXPARXP8

EXPARXN8

EXPARXP9

EXPARXN9

EXPARXP10

EXPARXN10

EXPARXP11

EXPARXN11

EXPARXP12

EXPARXN12

EXPARXP13

EXPARXN13

EXPARXP14

EXPARXN14

EXPARXP15

EXPARXN15

DMIRXP0

DMIRXN0

DMIRXP1

DMIRXN1

DMIRXP2

DMIRXN2

DMIRXP3

DMIRXN3

GCLKINP

GCLKINN

SDVOCTRLDATA

SDVOCTRLCLK

MRN: MCH RECEIVE NEGATIVE

U6D1A

GDG_DDR1_1210

1.0

EXPATXP0

EXPATXN0

EXPATXP1

EXPATXN1

EXPATXP2

EXPATXN2

EXPATXP3

EXPATXN3

EXPATXP4

EXPATXN4

EXPATXP5

EXPATXN5

EXPATXP6

EXPATXN6

EXPATXP7

EXPATXN7

EXPATXP8

EXPATXN8

EXPATXP9

EXPATXN9

EXPATXP10

EXPATXN10

EXPATXP11

EXPATXN11

EXPATXP12

EXPATXN12

EXPATXP13

EXPATXN13

EXPATXP14

EXPATXN14

EXPATXP15

EXPATXN15

DMITXP0

DMITXN0

DMITXP1

DMITXN1

DMITXP2

DMITXN2

DMITXP3

DMITXN3

EXPACOMPO

EXPACOMPI

2 of 7

C10

C9

A9

A8

C8

C7

A7

A6

C6

C5

C2

D2

E3

F3

F1

G1

G3

H3

H1

J1

J3

K3

K1

L1

L3

M3

M1

N1

N3

P3

P1

R1

R3

T3

T1

U1

U3

V3

V5

W5

Y10

W10

EXP_A_TXP_0

EXP_A_TXN_0

EXP_A_TXP_1

EXP_A_TXN_1

EXP_A_TXP_2

EXP_A_TXN_2

EXP_A_TXP_3

EXP_A_TXN_3

EXP_A_TXP_4

EXP_A_TXN_4

EXP_A_TXP_5

EXP_A_TXN_5

EXP_A_TXP_6

EXP_A_TXN_6

EXP_A_TXP_7

EXP_A_TXN_7

EXP_A_TXP_8

EXP_A_TXN_8

EXP_A_TXP_9

EXP_A_TXN_9

EXP_A_TXP_10

EXP_A_TXN_10

EXP_A_TXP_11

EXP_A_TXN_11

EXP_A_TXP_12

EXP_A_TXN_12

EXP_A_TXP_13

EXP_A_TXN_13

EXP_A_TXP_14

EXP_A_TXN_14

EXP_A_TXP_15

EXP_A_TXN_15

DMI_MTP_IRP_0

DMI_MTN_IRN_0

DMI_MTP_IRP_1

DMI_MTN_IRN_1

DMI_MTP_IRP_2

DMI_MTN_IRN_2

DMI_MTP_IRP_3

DMI_MTN_IRN_3

GRCOMP

33

OUT

33

OUT

33

OUT

33

OUT

33

OUT

33

OUT

33

OUT

33

OUT

33

OUT

33

OUT

33

OUT

33

OUT

33

OUT

33

OUT

33

OUT

33

OUT

33

OUT

33

OUT

33

OUT

33

OUT

33

OUT

33

OUT

33

OUT

33

OUT

33

OUT

33

OUT

33

OUT

33

OUT

33

OUT

33

OUT

33

OUT

33

OUT

38,100

BI

38,100

BI

38,100

BI

38,100

BI

38,100

BI

38,100

BI

38,100

BI

38,100

BI

17

IN

D

C

B

IC

A

SDVO CTRL DATA

1 SDVO CARD PRESENT, PEG DISABLED

0 SDVO DISABLED (DEFAULT)

CORE PAGE

8 7

A

[PAGE_TITLE=MCH SECTIONS PAGE 2 OF 6]

INTEL

CONFIDENTIAL

45

36

2 1

DOCUMENT NUMBER PAGE REV

C77862

11

4.0

Page 12

<XR_PAGE_TITLE>

U6D1B

GDG_DDR1_1210

V_1P5_CORE

15..17,38,39,41,79,87,88,102

IN

D

15..17,38,39,41,79,87,88,102

V_1P5_CORE

IN

C

B

A

AC11

AB11

AA13

AA14

AA16

AA18

AA20

AA21

AA22

AA23

AA24

AB13

AB14

AB15

AB16

AB17

AB18

AB19

AB20

AB21

AB22

AB23

AB24

Y20

Y19

Y17

Y16

W20

W16

U20

U16

T20

T19

T17

T16

N13

N14

N15

N16

N18

N20

N21

P13

P14

P15

P17

P19

P21

P22

R13

R14

R15

R16

R18

R20

R22

R23

T13

T14

T15

T21

T23

T24

U13

U14

U22

U24

V13

V14

V15

V21

V23

V24

W13

W14

W22

W24

Y13

Y14

Y15

Y21

Y23

Y24

CORE PAGE

8 7

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

1.0

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

7 of 7

AC25

AB25

AA25

AA11

Y25

Y18

Y11

W25

W11

V25

V20

V16

V11

U25

U11

T25

T18

T11

R25

R11

P25

P11

N25

AD25

N11

M11

AA15

AA17

AA19

N17

N19

P16

P18

P20

R17

R19

R21

T22

U15

U21

U23

V22

W15

W21

W23

Y22

AC12

AC13

AC14

AC15

AC16

AC17

AC18

AC19

AC20

AC21

AC22

N12

NC

N22

NC

N23

NC

N24

NC

P12

NC

P23

NC

P24

NC

R12

NC

R24

NC

T12

NC

U12

NC

V12

NC

W12

NC

Y12

NC

AA12

NC

AB12

NC

AC23

NC

AC24

NC

DESIGN NOTE:

RSRVD PINS DO NOT NEED TO

BE TESTPOINTED IN THIS INSTANCE

15..17,38,39,41,79,87,88,102

15,16,87,88

17

16

16

16

16

16

16,18

IN

IN

IN

IN

IN

IN

IN

IN

IN

V_1P5_CORE

V_1P5_PCIEXPRESS

VCCA_HPLL

VCCA_MPLL

VCCA_DPLLA

VCCA_DPLLB

VCCA_GPLL

V_2P5_MCH

V_2P5_DAC_FILTERED

AD10

AC10

AB10

AD9

AD8

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AC9

AC8

AC7

AC6

AC5

AC4

AC3

AC2

AC1

AB9

AB8

AB7

AB6

AB5

AB4

AB3

AB2

AB1

W18

V19

V17

U18

Y9

Y8

Y7

Y6

Y5

Y4

Y3

Y2

Y1

W9

W8

W7

W6

W4

W3

W2

W1

A17

B17

A12

B13

A14

A13

E13

D13

F13

GDG_DDR1_1210

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC3G

VCC3G

VCC3G

VCC3G

VCC3G

VCC3G

VCC3G

VCC3G

VCC3G

VCC3G

VCC3G

VCC3G

VCC3G

VCC3G

VCC3G

VCC3G

VCC3G

VCCAHPLL

VCCAMPLL

VCCADPLLA

VCCADPLLB

VCCA3GPLL

VCCHV

VCCACRTDAC

VCCACRTDAC

VSSACRTDAC

U6D1C

1.0

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

6 of 7

AR33

AR31

AR26

AR22

AR18

AR14

AR10

AP28

AP24

AP20

AP16

AP12

AN35

AM32

AM28

AM26

AM25

AM23

AM22

AM20

AM19

AM17

AM16

AM14

AM13

AM11

AM10

AK35

H22

VTT

G22

VTT

G21

VTT

F22

VTT

F21

VTT

F20

VTT

E22

VTT

E21

VTT

E20

VTT

E19

VTT

D22

VTT

D21

VTT

D20

VTT

D19

VTT

C22

VTT

C21

VTT

C20

VTT

C19

VTT

B22

VTT

B21

VTT

B20

VTT

B19

VTT

A22

VTT

A21

VTT

A20

VTT

A19

VTT

IC

[PAGE_TITLE=MCH SECTIONS PAGE 3 OF 6]

IC

45

36

28 7 6 5 4 3 1

V_SM

V_FSB_VTT

INTEL

DOCUMENT NUMBER PAGE REV

CONFIDENTIAL

2 1

IN

IN

C77862

18,19,21,24,25,28,85,89

7..9,17,18,41,43,87

D

C

B

A

12

4.0

Page 13

<XR_PAGE_TITLE>

U6D1D

SACS0*

SACS1*

SACS2*

SACS3*

SACKE0

SACKE1

SACKE2

SACKE3

RSVRD

RSVRD

RSVRD

RSVRD

4 of 7

GDG_DDR1_1210

DDRA

1.0

SADQS0

RSVRD

SADM0

SADQ0

SADQ1

SADQ2

SADQ3

SADQ4

SADQ5

SADQ6

SADQ7

SADQS1

RSVRD

SADM1

SADQ8

SADQ9

SADQ10

SADQ11

SADQ12

SADQ13

SADQ14

SADQ15

SADQS2

RSVRD

SADM2

SADQ16

SADQ17

SADQ18

SADQ19

SADQ20

SADQ21

SADQ22

SADQ23

SADQS3

RSVRD

SADM3

SADQ24

SADQ25

SADQ26

SADQ27

SADQ28

SADQ29

SADQ30

SADQ31

SADQS4

RSVRD

SADM4

SADQ32

SADQ33

SADQ34

SADQ35

SADQ36

SADQ37

SADQ38

SADQ39

SADQS5

RSVRD

SADM5

SADQ40

SADQ41

SADQ42

SADQ43

SADQ44

SADQ45

SADQ46

SADQ47

SADQS6

RSVRD

SADM6

SADQ48

SADQ49

SADQ50

SADQ51

SADQ52

SADQ53

SADQ54

SADQ55

SADQS7

RSVRD

SADM7

SADQ56

SADQ57

SADQ58

SADQ59

SADQ60

SADQ61

SADQ62

SADQ63

AG1

AG2

AF2

AE3

AF3

AH3

AJ2

AE2

AE1

AG3

AH2

AL3

AL2

AL1

AK2

AK3

AN4

AP4

AJ1

AJ3

AP2

AP3

AP7

AR7

AN7

AR5

AP6

AP9

AN9

AN5

AP5

AN8

AR8

AF17

AG17

AH16

AL17

AJ17

AF19

AH18

AK16

AF16

AD17

AE19

AM30

AL29

AK29

AK27

AJ28

AL31

AK31

AH27

AL27

AN30

AL30

AG35

AG33

AG34

AH33

AH35

AF33

AE33

AJ33

AJ34

AG32

AF34

AA34

AA35

AA33

AD31

AD35

Y33

W34

AE35

AE34

AA32

Y35

U34

U35

U33

V34

V33

R32

R34

W35

W33

T33

T35

IC

45

BI

OUT

OUT

OUT

BI

BI

BI

21

BI

21

BI

21

BI

21

BI

21

BI

21

BI

21

BI

21

BI

21

BI

21

BI

21

BI

21

BI

19

IN

M_MAA_A[13..0]

M_WE_A*

M_CAS_A*

M_RAS_A*

M_SBS_A[1..0]

M_SCS_A*[3..0]

M_SCKE_A[3..0]

CK_M_166M_P_DDR0_A

CK_M_166M_N_DDR0_A

CK_M_166M_P_DDR1_A

CK_M_166M_N_DDR1_A

CK_M_166M_P_DDR2_A

CK_M_166M_N_DDR2_A

CK_M_166M_P_DDR3_A

CK_M_166M_N_DDR3_A

CK_M_166M_P_DDR4_A

CK_M_166M_N_DDR4_A

CK_M_166M_P_DDR5_A

CK_M_166M_N_DDR5_A

TP_SA_RCVENOUT

TP_SA_RCVENIN

SM_XSLEWIN

MCH_VREF_A

0

1

2

3

4

5

6

7

8

9

10

11

12

0

1

0

1

2

3

0

1

2

3

AN22

M_MAA_A0

M_MAA_A1

M_MAA_A2

M_MAA_A3

M_MAA_A4

M_MAA_A5

M_MAA_A6

M_MAA_A7

M_MAA_A8

M_MAA_A9

M_MAA_A10

M_MAA_A11

M_MAA_A12

M_SBS_A0

M_SBS_A1

M_SCS_A*0

M_SCS_A*1

M_SCS_A*2

M_SCS_A*3

M_SCKE_A0

M_SCKE_A1

M_SCKE_A2

M_SCKE_A3

13

M_MAA_A13

AP22

AN21

AP21

AM21

AP19

AR20

AN16

AN18

AM15

AN23

AP15

AP13

AN31

AP31

AN29

AN28

AP26

AR23

AM34

AK34

AN11

AP11

AR11

AP33

AR24

AR28

AR29

AM24

AN25

AB34

AC33

AP25

AN26

AC35

AC34

AB33

AH15

AE16

AK12

SAMA0

SAMA1

SAMA2

SAMA3

SAMA4

SAMA5

SAMA6

SAMA7

SAMA8

SAMA9

SAMA10

SAMA11

SAMA12

RSVRD

SAWE*

AL34

SACAS*

SARAS*

SABA0

SABA1

RSVRD

AL35

AL33

AL12

SACK0

SACK0*

AN2

SACK1

AN3

SACK1*

SACK2

SACK2*

SACK3

SACK3*

AM2

SACK4

AM3

SACK4*

SACK5

SACK5*

SADDR1MA13

SARCVENOUT*

SARCVENIN*

AJ12

SMXSLEWIN

SMXSLEWOUT

AE7

SMVREF0

21,22

D

21,23

21,23

21,23

21,23

21,23

21,23

C

B

BI

M_MAA_A[13..0]

21,22

A

CORE PAGE

8 7

0

M_DQS_A0

0

M_DQM_A0

0

M_DATA_A0

1

M_DATA_A1

2

M_DATA_A2

3

M_DATA_A3

4

M_DATA_A4

5

M_DATA_A5

6

M_DATA_A6

7

M_DATA_A7

1

M_DQS_A1

1

M_DQM_A1

8

M_DATA_A8

9

M_DATA_A9

10

M_DATA_A10

11

M_DATA_A11

12

M_DATA_A12

13

M_DATA_A13

14

M_DATA_A14

15

M_DATA_A15

2

M_DQS_A2

2

M_DQM_A2

16

M_DATA_A16

17

M_DATA_A17

18

M_DATA_A18

19

M_DATA_A19

20

M_DATA_A20

21

M_DATA_A21

22

M_DATA_A22

23

M_DATA_A23

3

M_DQS_A3

3

M_DQM_A3

24

M_DATA_A24

25

M_DATA_A25

26

M_DATA_A26

27

M_DATA_A27

28

M_DATA_A28

29

M_DATA_A29

30

M_DATA_A30

31

M_DATA_A31

4

M_DQS_A4

4

M_DQM_A4

32

M_DATA_A32

33

M_DATA_A33

34

M_DATA_A34

35

M_DATA_A35

36

M_DATA_A36

37

M_DATA_A37

38

M_DATA_A38

39

M_DATA_A39

5

M_DQS_A5

5

M_DQM_A5

40

M_DATA_A40

41

M_DATA_A41

42

M_DATA_A42

43

M_DATA_A43

44

M_DATA_A44

45

M_DATA_A45

46

M_DATA_A46

47

M_DATA_A47

6

M_DQS_A6

6

M_DQM_A6

48

M_DATA_A48

49

M_DATA_A49

50

M_DATA_A50

51

M_DATA_A51

52

M_DATA_A52

53

M_DATA_A53

54

M_DATA_A54

55

M_DATA_A55

7

M_DQS_A7

7

M_DQM_A7

56

M_DATA_A56

57

M_DATA_A57

58

M_DATA_A58

59

M_DATA_A59

60

M_DATA_A60

61

M_DATA_A61

62

M_DATA_A62

63

M_DATA_A63

M_DQS_A[7..0]

M_DQM_A[7..0]

M_DATA_A[63..0]

M_DQS_A[7..0]

M_DQM_A[7..0]

M_DATA_A[63..0]

M_DQS_A[7..0]

M_DQM_A[7..0]

M_DATA_A[63..0]

M_DQS_A[7..0]

M_DQM_A[7..0]

M_DATA_A[63..0]

M_DQS_A[7..0]

M_DQM_A[7..0]

M_DATA_A[63..0]

M_DQS_A[7..0]

M_DQM_A[7..0]

M_DATA_A[63..0]

M_DQS_A[7..0]

M_DQM_A[7..0]

M_DATA_A[63..0]

M_DQS_A[7..0]

M_DQM_A[7..0]

M_DATA_A[63..0]

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

21,23

21,22

21,22

21,23

21,22

21,22

21,23

21,22

21,22

21,23

21,22

21,22

21,23

21,22

21,22

21,23

21,22

21,22

21,23

21,22

21,22

21,23

21,22

21,22

[PAGE_TITLE=MCH SECTIONS PAGE 4 OF 6]

36

28 7 6 5 4 3 1

INTEL

DOCUMENT NUMBER PAGE REV

CONFIDENTIAL

2 1

C77862

D

C

B

A

13

4.0

Page 14

D

C

B

A

CORE PAGE

<XR_PAGE_TITLE>

8 7

U6D1E

SBCS0*

SBCS1*

SBCS2*

SBCS3*

SBCKE0

SBCKE1

SBCKE2

SBCKE3

RSVRD

RSVRD

RSVRD

RSVRD

SBDDR1MA13

SBRCVENOUT*

SBRCVENIN*

SMYSLEWIN

SMYSLEWOUT

SMVREF1

SMRCOMPP

SMRCOMPN

SMOCDCOMP1

SMOCDCOMP0

3 of 7

GDG_DDR1_1210

DDRB

1.0

SBDQS0

RSVRD

SBDM0

SBDQ0

SBDQ1

SBDQ2SBMA5

SBDQ3

SBDQ4

SBDQ5

SBDQ6

SBDQ7

SBDQS1

RSVRD

SBDM1

SBDQ8

SBDQ9

SBDQ10

SBDQ11

SBDQ12

SBDQ13

SBDQ14

SBDQ15

SBDQS2

RSVRD

SBDM2

SBDQ16

SBDQ17

SBDQ18

SBDQ19

SBDQ20

SBDQ21

SBDQ22

SBDQ23

SBDQS3

RSVRD

SBDM3

SBDQ24

SBDQ25

SBDQ26

SBDQ27

SBDQ28

SBDQ29

SBDQ30

SBDQ31

SBDQS4

RSVRD

SBDM4

SBDQ32

SBDQ33

SBDQ34

SBDQ35

SBDQ36

SBDQ37

SBDQ38

SBDQ39

SBDQS5

RSVRD

SBDM5

SBDQ40

SBDQ41

SBDQ42

SBDQ43

SBDQ44

SBDQ45

SBDQ46

SBDQ47

SBDQS6

RSVRD

SBDM6

SBDQ48

SBDQ49

SBDQ50

SBDQ51

SBDQ52

SBDQ53

SBDQ54

SBDQ55

SBDQS7

RSVRD

SBDM7

SBDQ56

SBDQ57

SBDQ58

SBDQ59

SBDQ60

SBDQ61

SBDQ62

SBDQ63

AK5

AL4

AJ5

AH4

AJ6

AL6

AN6

AG9

AH7

AL5

AM5

AK10

AH10

AH9

AJ8

AL8

AF11

AE11

AJ7

AL7

AG10

AG11

AK13

AL14

AH13

AF13

AH12

AD14

AD15

AD12

AE13

AG14

AF14

AD20

AF20

AG20

AK19

AH19

AH21

AD21

AD18

AL18

AE22

AF22

AH25

AG26

AG24

AF24

AF25

AL26

AJ26

AF23

AD23

AL25

AJ25

AH28

AH30

AH31

AK32

AJ31

AG31

AF28

AJ29

AK33

AG30

AG27

AB31

AC30

AD24

AF27

AE27

AC26

AB26

AE31

AE29

AC28

AB27

W27

Y28

W31

AA28

W29

V28

V29

Y26

AA29

W26

U26

0

M_DQS_B0

0

M_DQM_B0

0

M_DATA_B0

1

M_DATA_B1

2

M_DATA_B2

3

M_DATA_B3

4

M_DATA_B4

5

M_DATA_B5

6

M_DATA_B6

7

M_DATA_B7

1

M_DQS_B1

1

M_DQM_B1

8

M_DATA_B8

9

M_DATA_B9

10

M_DATA_B10

11

M_DATA_B11

12

M_DATA_B12

13

M_DATA_B13

14

M_DATA_B14

15

M_DATA_B15

2

M_DQS_B2

2

M_DQM_B2

16

M_DATA_B16

17

M_DATA_B17

18

M_DATA_B18

19

M_DATA_B19

20

M_DATA_B20

21

M_DATA_B21

22

M_DATA_B22

23

M_DATA_B23

3

M_DQS_B3

3

M_DQM_B3

24

M_DATA_B24

25

M_DATA_B25

26

M_DATA_B26

27

M_DATA_B27

28

M_DATA_B28

29

M_DATA_B29

30

M_DATA_B30

31

M_DATA_B31

4

M_DQS_B4

4

M_DQM_B4

32

M_DATA_B32

33

M_DATA_B33

34

M_DATA_B34

35

M_DATA_B35

36

M_DATA_B36

37

M_DATA_B37

38

M_DATA_B38

39

M_DATA_B39

5

M_DQS_B5

5

M_DQM_B5

40

M_DATA_B40

41

M_DATA_B41

42

M_DATA_B42

43

M_DATA_B43

44

M_DATA_B44

45

M_DATA_B45

46

M_DATA_B46

47

M_DATA_B47

6

M_DQS_B6

6

M_DQM_B6

48

M_DATA_B48

49

M_DATA_B49

50

M_DATA_B50

51

M_DATA_B51

52

M_DATA_B52

53

M_DATA_B53

54

M_DATA_B54

55

M_DATA_B55

7

M_DQS_B7

7

M_DQM_B7

56

M_DATA_B56

57

M_DATA_B57

58

M_DATA_B58

59

M_DATA_B59

60

M_DATA_B60

61

M_DATA_B61

62

M_DATA_B62

63

M_DATA_B63

M_DQS_B[7..0]

M_DQM_B[7..0]

M_DATA_B[63..0]

M_DQS_B[7..0]

M_DQM_B[7..0]

M_DATA_B[63..0]

M_DQS_B[7..0]

M_DQM_B[7..0]

M_DATA_B[63..0]

M_DQS_B[7..0]

M_DQM_B[7..0]

M_DATA_B[63..0]

M_DQS_B[7..0]

M_DQM_B[7..0]

M_DATA_B[63..0]

M_DQS_B[7..0]

M_DQM_B[7..0]

M_DATA_B[63..0]

M_DQS_B[7..0]

M_DQM_B[7..0]

M_DATA_B[63..0]

M_DQS_B[7..0]

M_DQM_B[7..0]

M_DATA_B[63..0]

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

[PAGE_TITLE=MCH SECTIONS PAGE 5 OF 6]

25,27

25,26

25,26

25,27

25,26

25,26

25,27

25,26

25,26

25,27

25,26

25,26

25,27

25,26

25,26

25,27

25,26

25,26

25,27

25,26

25,26

25,27

25,26

25,26

IC

45

36

25,26

25,27

25,27

25,27

25,27

25,27

25,27

25,26

BI

M_MAA_B[13..0]

25

25

25

25

25

25

25

25

25

25

25

25

BI

OUT

OUT

OUT

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

19

IN

19

IN

19