Page 1

Intel® 82854 Graphics Memory

Controller Hub (GMCH)

Datasheet

Revision 2.0

June 2005

Order Number: D15343-003

Page 2

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY

ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN

INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS

ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES

RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER

INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

This manual may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current

characterized errata are available on request.

This manual as well as the software described in it, is furnished under license and may only be used or copied in accordance with the terms of the

license. The information in this document is furnished for informational use only, is subject to change without notice, and should not be construed as a

commitment by Intel Corporation. Intel Corporation assumes no responsibility or liability for any errors or inaccuracies that may appear in this

document or any software that may be provided in association with this document.

Except as permitted by such license, no part of this document may be reproduced, stored in a retrieval system, or transmitted in any form or by any

means without the express written consent of Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling

1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Genuine Intel Processor, Chips, CT Media, Dialogic, DM3, EtherExpress,

ETOX, FlashFile, i386, i486, i960, iCOMP, InstantIP, Intel, Intel Centrino, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel

Create & Share, Intel GigaBlade, Intel InBusiness, Intel Inside, Intel Inside logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel Play, Intel Play

logo, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel TeamStation, Intel Xeon, Intel XScale, IPLink, Itanium, MCS, MMX, MMX logo,

Optimizer logo, OverDrive, Paragon, PC Dads, PC Parents, PDCharm, Pentium, Pentium II Xeon, Pentium III Xeon, Performance at Your Command,

RemoteExpress, SmartDie, Solutions960, Sound Mark, StorageExpress, The Computer Inside., The Journey Inside, TokenExpress, VoiceBrick,

VTune, and Xircom are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

*Other names and brands may be claimed as the property of others.

Copyright © 2005, Intel Corporation

2 D15343-003

Page 3

Contents

Contents

1.0 Introduction.................................................................................................................................... 11

1.1 Overview............................................................................................................................. 11

1.2 Terminology ........................................................................................................................17

1.3 Reference Documents ........................................................................................................19

2.0 Intel

®

82854 GMCH Overview....................................................................................................... 21

2.1 System Architecture............................................................................................................ 21

2.1.1 Intel

2.2 Processor Host Interface ....................................................................................................22

2.3 GMCH System Memory Interface....................................................................................... 22

2.4 Graphics Features .............................................................................................................. 23

2.5 Display Features................................................................................................................. 23

2.5.1 GMCH Analog Display Port ................................................................................... 23

2.5.2 GMCH Integrated DVO Ports ................................................................................ 23

2.6 Hub Interface ...................................................................................................................... 24

2.7 Address Decode Policies .................................................................................................... 24

2.8 GMCH Clocking ..................................................................................................................25

2.9 System Interrupts................................................................................................................ 26

®

82854 GMCH ............................................................................................... 21

3.0 Signal Description.......................................................................................................................... 27

3.1 Host Interface Signals.........................................................................................................28

3.2 DDR SDRAM Interface .......................................................................................................31

3.3 Hub Interface Signals .........................................................................................................32

3.4 Clocks .................................................................................................................................33

3.5 Internal Graphics Display Signals....................................................................................... 35

3.5.1 Digital Video Output B (DVOB) Port ...................................................................... 35

3.5.2 Digital Video Output C (DVOC) Port...................................................................... 36

3.5.3 Analog CRT Display ..............................................................................................37

3.5.4 General Purpose Input/Output Signals .................................................................. 38

3.6 Voltage References, PLL Power......................................................................................... 39

4.0 Register Description ...................................................................................................................... 41

4.1 Conceptual Overview of the Platform Configuration Structure ........................................... 41

4.2 Nomenclature for Access Attributes ................................................................................... 42

4.3 Standard PCI Bus Configuration Mechanism .....................................................................43

4.4 Routing Configuration Accesses......................................................................................... 43

4.4.1 PCI Bus #0 Configuration Mechanism ................................................................... 43

4.4.2 Primary PCI and Downstream Configuration Mechanism......................................44

4.5 Register Definitions............................................................................................................. 44

4.6 I/O Mapped Registers.........................................................................................................45

4.6.1 CONFIG_ADDRESS – Configuration Address Register........................................ 45

4.6.2 CONFIG_DATA – Configuration Data Register .....................................................47

4.7 VGA I/O Mapped Registers ................................................................................................ 48

4.8 Intel 854 GMCH Host-Hub Interface Bridge Device Registers (Device #0, Function #0) ...49

4.8.1 VID – Vendor Identification Register...................................................................... 51

4.8.2 DID – Device Identification Register ...................................................................... 51

4.8.3 PCICMD – PCI Command Register....................................................................... 52

D15343-003 3

Page 4

®

82854 Graphics Memory Controller Hub (GMCH)

Intel

4.8.4 PCI Status Register ............................................................................................... 53

4.8.5 RID – Register Identification.................................................................................. 54

4.8.6 SUBC – Sub Class Code Register ........................................................................ 54

4.8.7 BCC – Base Class Code Register ......................................................................... 55

4.8.8 HDR – Header Type Register................................................................................ 55

4.8.9 SVID – Subsystem Vendor Identification Register ................................................ 55

4.8.10 SID – Subsystem Identification Register ............................................................... 56

4.8.11 CAPPTR – Capabilities Pointer Register............................................................... 56

4.8.12 CAPID – Capabilities Identification Register (Device #0) ...................................... 57

4.8.13 GMC – GMCH Miscellaneous Control Register (Device #0) ................................. 58

4.8.14 GGC – GMCH Graphics Control Register (Device #0) .......................................... 59

4.8.15 DAFC – Device and Function Control Register (Device #0).................................. 60

4.8.16 FDHC – Fixed DRAM Hold Control Register (Device #0)...................................... 60

4.8.17 PAM(6:0) – Programmable Attribute Map Register (Device #0)............................ 61

4.8.18 SMRAM – System Management RAM Control Register (Device #0) .................... 64

4.8.19 ESMRAMC – Extended System Management RAM Control (Device #0) .............65

4.8.20 ERRSTS – Error Status Register (Device #0) ....................................................... 66

4.8.21 ERRCMD – Error Command Register (Device #0)................................................ 67

4.8.22 SMICMD – SMI Error Command Register (Device #0) ......................................... 68

4.8.23 SCICMD – SCI Error Command Register (Device #0) .......................................... 69

4.8.24 SHIC – Secondary Host Interface Control Register (Device #0) ........................... 70

4.8.25 HEM – Host Error Control, Status, and Observation (Device #0).......................... 71

4.9 Intel 854 GMCH Main Memory Control, Memory I/O Control Registers (Device #0, Function

#1)72

4.9.1 VID – Vendor Identification Register...................................................................... 73

4.9.2 DID – Device Identification Register...................................................................... 73

4.9.3 PCICMD – PCI Command Register....................................................................... 74

4.9.4 PCISTS – PCI Status Register .............................................................................. 75

4.9.5 RID – Revision Identification Register ................................................................... 76

4.9.6 RID – Revision Identification Register ................................................................... 76

4.9.7 BCC – Base Class Code Register ......................................................................... 76

4.9.8 HDR – Header Type Register................................................................................ 77

4.9.9 SVID – Subsystem Vendor Identification Register ................................................ 77

4.9.10 SID – Subsystem Identification Register ............................................................... 77

4.9.11 CAPPTR – Capabilities Pointer Register............................................................... 78

4.9.12 DRB – DRAM Row (0:3) Boundary Register (Device #0) ...................................... 78

4.9.13 DRA – DRAM Row Attribute Register (Device #0) ................................................ 79

4.9.14 DRT – DRAM Timing Register (Device #0) ........................................................... 80

4.9.15 PWRMG – DRAM Controller Power Management Control Register (Device #0).. 83

4.9.16 DRC – DRAM Controller Mode Register (Device #0) ............................................ 85

4.9.17 DTC – DRAM Throttling Control Register (Device #0) .......................................... 88

4.10 Intel 854 GMCH Configuration Process Registers (Device #0, Function #3) ..................... 92

4.10.1 VID – Vendor Identification Register...................................................................... 92

4.10.2 DID – Device Identification Register ...................................................................... 93

4.10.3 PCICMD – PCI Command Register....................................................................... 94

4.10.4 PCISTS – PCI Status Register .............................................................................. 95

4.10.5 RID – Revision Identification Register ................................................................... 96

4.10.6 SUBC – Sub-Class Code Register ........................................................................ 96

4.10.7 BCC – Base Class Code Register ......................................................................... 96

4.10.8 HDR – Header Type Register................................................................................ 97

4 D15343-003

Page 5

4.10.9 SVID – Subsystem Vendor Identification Register................................................. 97

4.10.10 ID – Subsystem Identification Register.................................................................. 97

4.10.11 CAPPTR – Capabilities Pointer Register............................................................... 98

4.10.12 HPLLCC – HPLL Clock Control Register (Device #0) ........................................... 98

4.11 Intel

®

82854 GMCH Integrated Graphics Device Registers (Device #2, Function #0).....100

4.11.1 VID – Vendor Identification Register (Device #2) ................................................101

4.11.2 DID – Device Identification Register (Device #2)................................................. 101

4.11.3 PCICMD – PCI Command Register (Device #2) ................................................. 102

4.11.4 PCISTS – PCI Status Register (Device #2) ......................................................... 103

4.11.5 RID – Revision Identification Register (Device #2) .............................................. 103

4.11.6 CC – Class Code Register (Device #2) ...............................................................104

4.11.7 CLS – Cache Line Size Register (Device #2) ......................................................104

4.11.8 MLT – Master Latency Timer Register (Device #2) ............................................. 104

4.11.9 HDR – Header Type Register (Device #2)........................................................... 105

4.11.10 GMADR – Graphics Memory Range Address Register (Device #2)....................105

4.11.11 MMADR – Memory Mapped Range Address Register (Device #2)..................... 106

4.11.12 IOBAR – I/O Base Address Register (Device #2)................................................ 106

4.11.13 SVID – Subsystem Vendor Identification Register (Device #2) ...........................107

4.11.14 SID – Subsystem Identification Register (Device #2) ..........................................107

4.11.15 ROMADR – Video BIOS ROM Base Address Registers (Device #2)..................107

4.11.16 INTRLINE – Interrupt Line Register (Device #2).................................................. 108

4.11.17 INTRPIN – Interrupt Pin Register (Device #2) .....................................................108

4.11.18 MINGNT – Minimum Grant Register (Device #2) ................................................ 108

4.11.19 MAXLAT – Maximum Latency Register (Device #2)............................................ 109

4.11.20 PMCAP – Power Management Capabilities Register (Device #2).......................109

4.11.21 PMCS – Power Management Control/Status Register (Device #2)..................... 110

5.0 Intel

®

82854 GMCH System Address Map.................................................................................. 111

5.1 System Memory Address Ranges ....................................................................................111

5.2 DOS Compatibility Area....................................................................................................112

5.3 Extended System Memory Area ....................................................................................... 114

5.4 Main System Memory Address Range (0010_0000h to Top of Main Memory) ................115

5.4.1 15 MB-16 MB Window .........................................................................................115

5.4.2 Pre-allocated System Memory............................................................................. 115

5.4.3 System Management Mode (SMM) Memory Range............................................118

5.4.4 System Memory Shadowing ................................................................................119

5.4.5 I/O Address Space............................................................................................... 119

5.4.6 GMCH Decode Rules and Cross-Bridge Address Mapping ................................120

5.4.7 Hub Interface Decode Rules................................................................................ 121

Contents

6.0 Functional Description ................................................................................................................. 123

6.1 Host Interface Overview ...................................................................................................123

6.2 Dynamic Bus Inversion ..................................................................................................... 123

6.2.1 System Bus Interrupt Delivery .............................................................................123

6.2.2 Upstream Interrupt Messages ............................................................................. 124

6.3 System Memory Interface.................................................................................................124

6.3.1 DDR SDRAM Interface Overview ........................................................................124

6.3.2 System Memory Organization and Configuration ................................................ 124

6.3.3 DDR SDRAM Performance Description............................................................... 125

6.4 Integrated Graphics Overview .......................................................................................... 126

D15343-003 5

Page 6

®

82854 Graphics Memory Controller Hub (GMCH)

Intel

6.4.1 3D/2D Instruction Processing .............................................................................. 126

6.4.2 3D Engine............................................................................................................ 127

6.4.3 Raster Engine ...................................................................................................... 130

6.4.4 2D Engine............................................................................................................ 133

6.4.5 Planes and Engines............................................................................................. 134

6.4.6 Hardware Cursor Plane (Native Graphic Mode only) .......................................... 134

6.4.7 Overlay Plane ...................................................................................................... 135

6.4.8 Video Functionality .............................................................................................. 137

6.5 Internal Graphic Display Interface .................................................................................... 138

6.5.1 Pipe A Timing Generator Unit.............................................................................. 138

6.5.2 Blend Function..................................................................................................... 141

6.5.3 Interlaced Video Field display.............................................................................. 141

6.5.4 Interlace support for Video Overlay Window ....................................................... 143

6.5.5 Analog Display Port Characteristics .................................................................... 145

7.0 Power and Thermal Management ............................................................................................... 147

7.1 General Description of Supported CPU States................................................................. 148

7.2 General Description of ACPI States ................................................................................. 148

7.3 Internal Thermal Sensor ................................................................................................... 149

7.3.1 Overview.............................................................................................................. 149

7.3.2 Hysteresis Operation ........................................................................................... 149

7.4 External Thermal Sensor Input ......................................................................................... 150

7.4.1 Usage .................................................................................................................. 150

8.0 Intel

®

82854 GMCH Strap Pins ................................................................................................... 151

8.1 Strapping Configuration .................................................................................................... 151

9.0 Ballout and Package Information................................................................................................. 153

9.1 VCC/VSS Voltage Groups ................................................................................................ 154

9.2 Package Mechanical Information...................................................................................... 164

6 D15343-003

Page 7

Contents

Figures

1 Intel® 854 Chipset system block diagram (Native Graphic mode) ............................................. 16

2 Configuration Address Register.................................................................................................. 45

3 Configuration Data Register .......................................................................................................47

4 PAM Registers............................................................................................................................ 62

5 Simplified View of System Address Map .................................................................................. 111

6 Detailed View of System Address Map.....................................................................................112

7 Intel

®

82854 GMCH Graphics Block Diagram (Native Graphic Mode only) ............................. 126

8 ARIB TR-B15 Plane Resolutions .............................................................................................. 139

9 H, V Parameters ....................................................................................................................... 140

10 Interlaced Timing Using HSYNC and VSYNC for Field1/Field2 Downstream Detection..........140

11 Timing Register Switching ........................................................................................................ 144

12 Intel

13 Intel

14 Intel

15 Intel

®

82854 GMCH Ballout Diagram (Top View) ..................................................................... 153

®

82854 GMCH Micro-FCBGA Package Dimensions (Top View) ..................................... 164

®

82854 GMCH Micro-FCBGA Package Dimensions (Side View) ....................................165

®

82854 GMCH Micro-FCBGA Package Dimensions (Bottom View) ................................ 166

Tables

1 Terms and Descriptions..............................................................................................................17

2 Reference Documents ................................................................................................................ 19

3 DDR SDRAM Memory Capacity ................................................................................................. 22

4 Intel

®

82854 GMCH Interface Clocks ......................................................................................... 25

5 Host Interface Signal Descriptions.............................................................................................. 28

6 DDR SDRAM Interface Descriptions ......................................................................................... 31

7 Hub Interface Signals ................................................................................................................ 32

8 Clock Signals .............................................................................................................................. 33

9 Digital Video Output B (DVOB) Port Signal Descriptions ........................................................... 35

10 Digital Video Output C (DVOC) Port Signal Descriptions ...........................................................36

11 DVOB and DVOC Port Common Signal Descriptions ............................................................... 37

12 Analog CRT Display Signal Descriptions.................................................................................... 37

13 GPIO Signal Descriptions ........................................................................................................... 38

14 Voltage References, PLL Power ................................................................................................39

15 Device Number Assignment .......................................................................................................41

16 Nomenclature for Access Attributes ...........................................................................................42

17 VGA I/O Mapped Register List ...................................................................................................48

18 Index – Data Registers ............................................................................................................... 48

19 GMCH Configuration Space - Device #0, Function#0 ................................................................ 49

20 Attribute Bit Assignment ............................................................................................................. 61

21 PAM Registers and Associated System Memory Segments ...................................................... 63

22 Host-Hub I/F Bridge/System Memory Controller Configuration Space (Device #0, Function#1)72

23 Configuration Process Configuration Space (Device#0, Function #3)........................................ 92

24 Intel

®

82854 GMCH Configurations and Some Resolution Examples: Native Graphics Mode.99

25 Integrated Graphics Device Configuration Space (Device #2, Function#0) ............................ 100

26 System Memory Segments and Their Attributes ......................................................................113

27 Table 33. Pre-allocated System Memory.................................................................................. 115

28 SMM Space Transaction Handling ...........................................................................................119

D15343-003 7

Page 8

®

82854 Graphics Memory Controller Hub (GMCH)

Intel

29 Relation of DBI Bits to Data Bits ............................................................................................... 123

30 Data Bytes on DDR DIMM Used for Programming DRAM Registers....................................... 125

31 Dual Display Usage Model (Native Graphic Mode only) .......................................................... 134

32 DVO Control Data Bits.............................................................................................................. 143

33 Strapping Signals and Configuration ........................................................................................ 151

34 Intel

®

82854 GMCH Straps for Frequency/CPU Configuration ................................................ 152

35 Voltage Levels and Ball Out for Voltage Groups ...................................................................... 154

36 Ballout Table ............................................................................................................................ 155

8 D15343-003

Page 9

Revision History

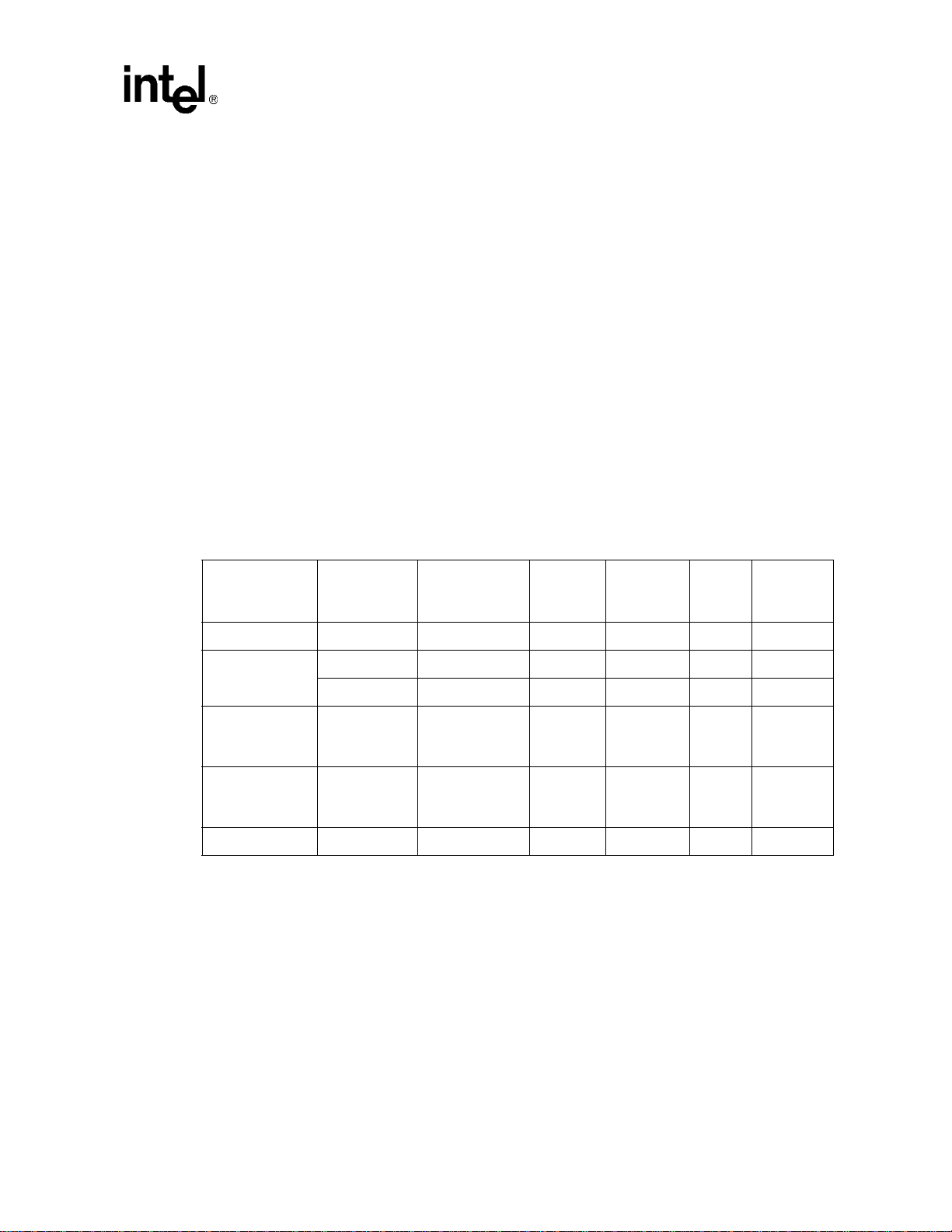

Date Revision Description

March 2005 1.0 Initial release of this document.

June 2005 2.0

Contents

Add support for Genuine Intel® Processor at 1.2 GHz and

Genuine Intel® Processor at 1.5 GHz technology.

§ §

D15343-003 9

Page 10

®

82854 Graphics Memory Controller Hub (GMCH)

Intel

10 D15343-003

Page 11

1.0 Introduction

This document is the datasheet for the Intel® 82854 Graphics Memory Controller Hub (GMCH).

1.1 Overview

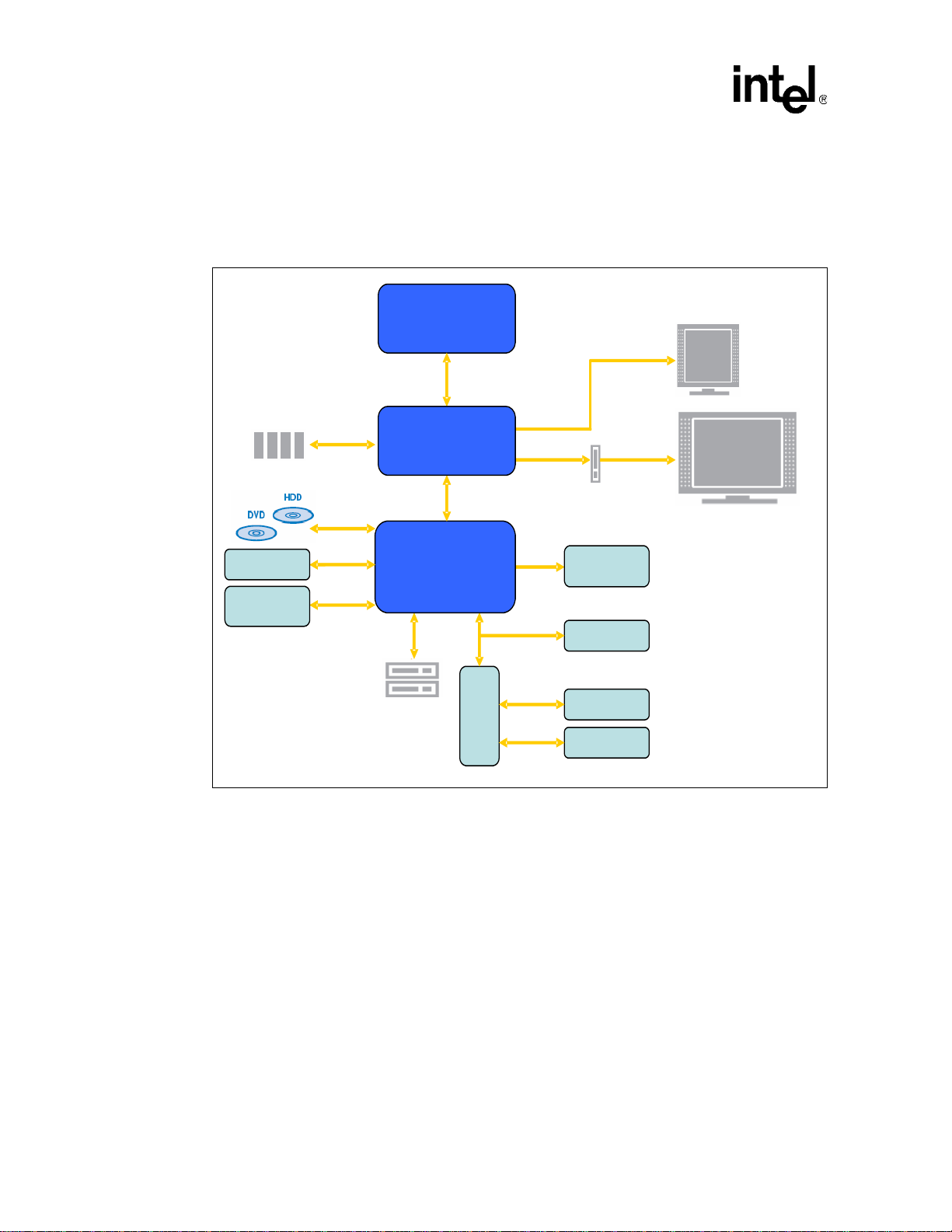

The Intel® 854 chipset is a combination of the Intel® 82854 Graphics Memory Controller Hub

(GMCH) (Graphics Memory Controller Hub) and ICH4-M (I/O Controller Hub). The Intel 854

Chipset is designed to work with the Ultra Low V oltage (ULV) Intel

MHz with 512 KB of on-die L2 cache on an 0.13 micron process, Genuine Intel

GHz, and Genuine Intel

performance, integrated graphics and manages the flow of information. Figure 1 depicts the Intel

854 chipset block diagram.

Processor/Host Bus Support

The Genuine Intel® Processor at 1.2 GHz and Genuine Intel® Processor at 1.5 GHz have the

following key features:

• High performance, low power core

• AGTL+ bus driver technology with integrated AGTL+ termination resistors and low voltage

operation

• Supports Intel Architecture with Dynamic Execution

• 400-MHz, Source-Synchronous processor system bus

• 2x address, 4x data

• On-die, primary 32-Kbyte instruction cache and 32-Kbyte write-back data cache

• On-die, 512-Kbyte second level cache with Advanced Transfer Cache Architecture

• Advanced Branch Prediction and Data Prefetch Logic

• Streaming SIMD Extensions 2 (SSE2)

• Advanced Power Management features

Introduction

®

Celeron® M processor at 600

®

Processor at 1.5 GHz. The Intel® 82854 GMCH provides high-

®

Processor at 1.2

Memory System

Directly supports one DDR SDRAM channel, 64-bits wide

•

• Supports 266/333-MHz DDR SDRAM devices with max of two, double-sided DIMM (four

rows populated) with unbuffered PC2100/PC2700 DDR SDRAM.

• Supports 128-Mbit, 256-Mbit, and 512-Mbit technologies providing maximum capacity of

2 GB with x16 devices

• All supported devices have four banks

• Supports up to 16 simultaneous open pages

• Supports page sizes of 2 kB, 4 kB, 8 kB, and 16 kB. Page size is individually selected for

every row

• UMA support only

D15343-003 11

Page 12

Intel® 82854 Graphics Memory Controller Hub (GMCH)

System Interrupts

Supports Intel 8259 and front side bus interrupt delivery mechanism

•

• Supports interrupts signaled as upstream memory writes from PCI and Hub interface

• MSI sent to the CPU through the system bus

• IOxAPIC in ICH4-M provides redirection for upstream interrupts to the system bus

Video Stream Decoder

• Hardware motion compensation for MPEG2

• All video format decoder (18 ATSC video formats) supported

• Dynamic Bob and Weave support for video streams

• Software DVD at 60 Fields/second and 30 frames/second full screen

• Support for standard definition DVD (i.e., NTSC pixel resolution of 720x480, and so on)

quality encoding at low CPU utilization

Video Overlay

• Single high quality scalable overlay and second Sprite to support second overlay

• Multiple overlay functionality provided via arithmetic stretch BLT (Block Transfer)

• 5-tap horizontal, 3-tap vertical filtered scaling

• Multiple overlay formats

• Direct YUV from overlay to TV-out

• Independent gamma correction

• Independent brightness / contrast/ saturation

• Independent tint/hue support

• Destination colorkeying

• Source chromakeying

12 D15343-003

Page 13

Introduction

Display

Analog display support

•

— 350-MHz integrated 24-bit RAMDAC that can drive a standard progressive scan analog

monitor with pixel resolution up to 1600x1200 at 85 Hz and up to 2048x1536 at 75 Hz

• Dual independent pipe support

— Concurrent: different images and display timings on each display device

— Simultaneous: same images and display timings on each display device

• DVO (DVOB and DVOC) support

— Digital video out ports DVOB and DVOC with 165-MHz dot clock on each 12-bit

interface; two 12-bit channels can be combined to form one dual channel 24-bit interface

with an effective dot clock of 330 MHz

— The combined DVO B/C ports as well as individual DVO B/C ports can drive a variety of

DVO devices (TV-Out Encoders, TMDS and LVDS transmitters, and so on) with pixel

resolution up to 1600x1200 at 85 Hz and up to 2048x1536 at 72 Hz.

— Compliant with DVI Specification 1.0

• Tri-view support through DVO B, C port, and CRT

Internal Graphics Features

• Up to 64 MB of dynamic video memory allocation

• Display image rotation

• Graphics core frequency at 200, 250 MHz

• 2D graphics engine

— Optimized 128-bit BL T engine

— Ten programmable and predefined monochrome patterns

— Alpha Stretch BLT (via 3D pipeline)

— Anti-aliased lines

— Hardware-based BLT Clipping and Scissoring

— 32-bit Alpha Blended cursor

— Programmable 64 x 64 3-color Transparent cursor

— Color Space Conversion

— Three Operand Raster BLTs

— 8-bit, 16-bit, and 32-bit color

— ROP support

— DIB translation and Linear/Tile addressing

— Multiple hardware color cursor support (32-bit with alpha and legacy 2-bpp mode)

— Accompanying I

2

C and DDC channels provided through multiplexed interface

D15343-003 13

Page 14

Intel® 82854 Graphics Memory Controller Hub (GMCH)

• 3D graphics engine

— 3D setup and render engine

— Enhanced Hardware Binning Instruction Set supported

— Zone rendering

— High quality performance texture engine

— Viewpoint transform and perspective divide

— Triangle lists, strips and fans support

— Indexed vertex and flexible vertex formats

— Pixel accurate fast scissoring and clipping operation

— Backface culling support

— Direct 3D support

— Anti-Aliased lines support

— Sprite points support

— Provides the highest sustained fill rate performance in 32-bit color and 24-bit W mode

— High quality performance texture engine

— 266-MegaTexel/s peak performance

— Per pixel perspective corrected texture mapping

— Single pass texture compositing (multi-textures)

— Enhanced texture blending functions

— Twelve level of detail MIP map sizes from 1x1 to 2k x 2k

— Numerous texture formats

— Alpha and Luminance maps

— Texture chromakeying

— Bilinear, trilinear, and anisotropic MIP map filtering

— Cubic environment reflection mapping

— Dot product bump-mapping

— Embossed bump-mapping

— DXTn texture decompression

— FX1 texture compression

— 3D graphics rasterization enhancements

— One Pixel per clock

— Flat and Gouraud shading

— Color alpha blending for transparency

— Vertex and programmable pixel fog and atmospheric effects

— Color specular lighting

— Z Bias support

14 D15343-003

Page 15

— Dithering

— Line and full-scene anti-aliasing

— 16- and 24-bit Z bufferin g

— 16- and 24-bit W buffering

— 8-bit Stencil buffering

— Double and triple render buffer support

— 16- and 32-bit color

— Destination alpha

— Vertex cache

— Optimal 3D resolution supported

— Fast Clear support

— ROP support

Hub Interface to ICH4-M

• 266-MB/s point-to-point Hub interface to ICH4-M

• 66-MHz base clock

Introduction

Graphic Power Management

• Dynamic Frequency Switching

• Memory Self-Refresh during C3

• Intel Display Power Saving Technology

Power Management

• SMRAM space remapping to A0000h (128-kB)

• Supports extended SMRAM space above 256-MB, additional 1-MB TSEG from top of

memory, cacheable (cacheability controlled by CPU)

• APM Rev 1.2 compliant power management

• Supports Suspend to System Memory (S3), Suspend to Disk (S4) and Soft Off (S5)

• ACPI 1.0b, 2.0 support

• Optimized Clock Gating for 3D and Display Engines

• On-Die Thermal Sensor

D15343-003 15

Page 16

Intel® 82854 Graphics Memory Controller Hub (GMCH)

Package

732-pin Micro-FCBGA (37.5 x 37.5 mm)

Figure 1. Intel® 854 Chipset system block diagram (Native Graphic mode)

Intel® Celeron® M

Processor

400 MHz

512 MB DD R

Memory Down

6 USB

LAN

PHY

333 MHz

IDE

USB 2.0/1.1

LCI

Intel® 82854

(GMCH)

Intel® 82801DBM

(ICH 4-M)

AC Link

LPC

VGA

DVO

ADD Slot

Audio

Codec

FWH

VGA

TV

PCI Slots

SIO

PS/2

Serial

16 D15343-003

Page 17

1.2 Terminology

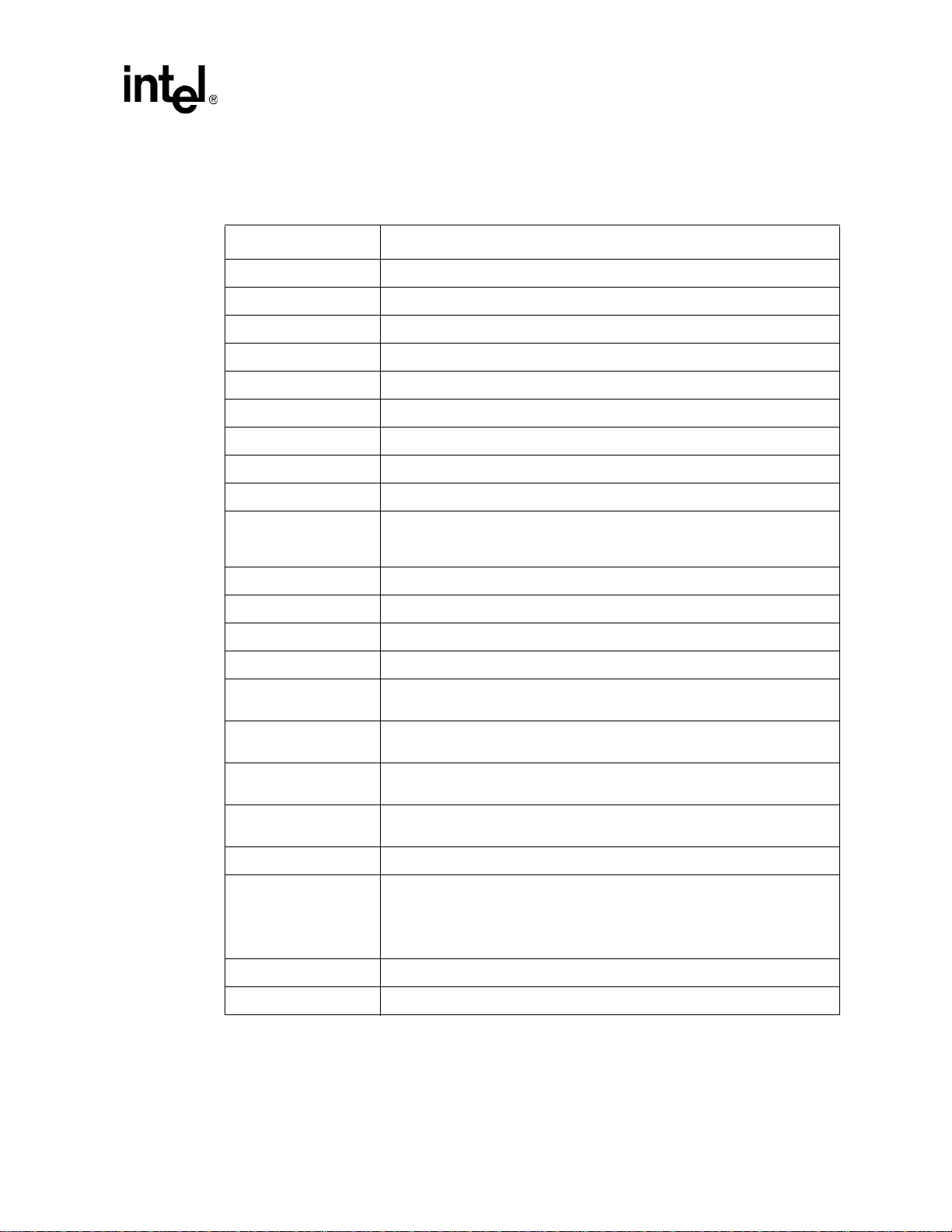

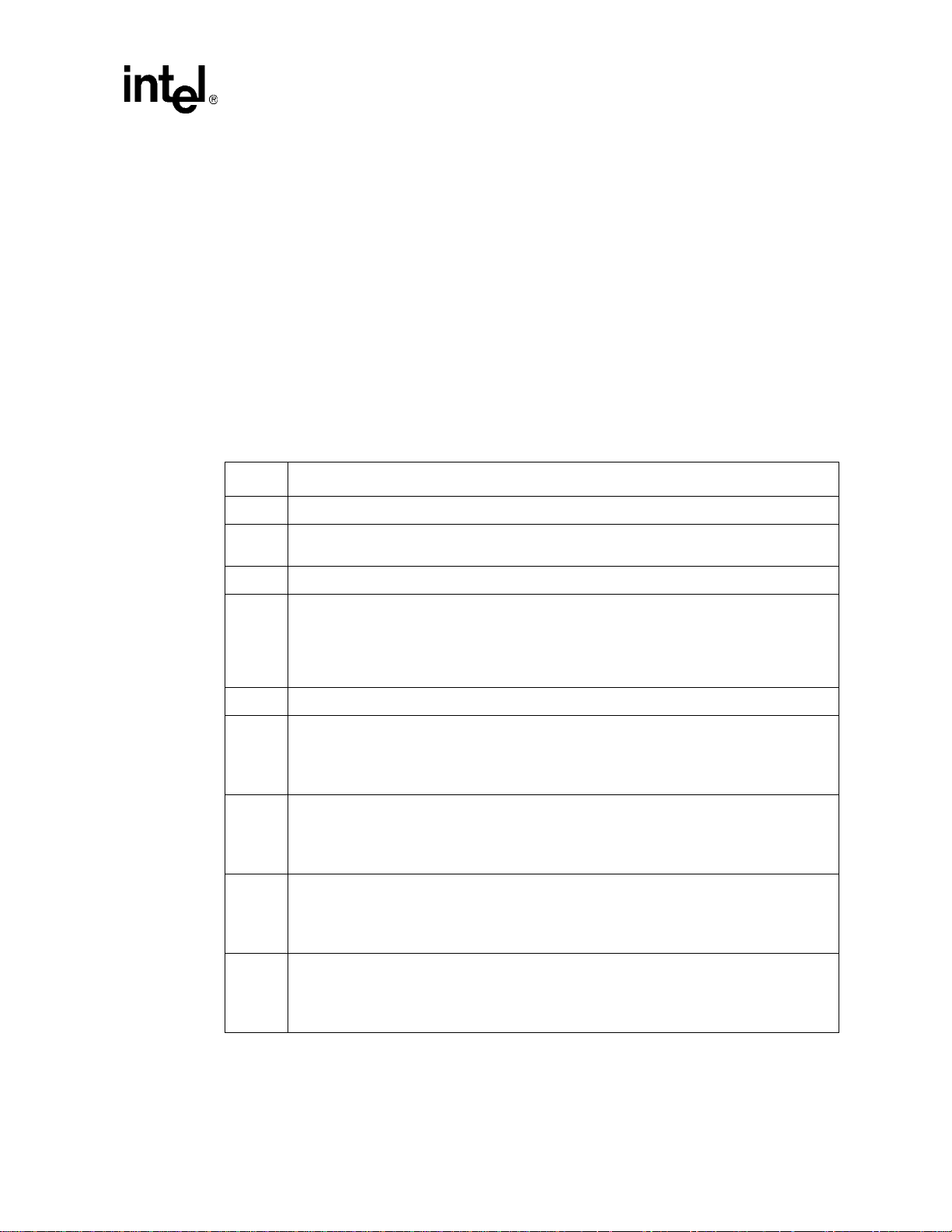

Table 1. Terms and Descriptions

Term Description

AGTL+ Advanced Gunning Transceiver Logic + (AGTL+) bus

BLI Backlight Inverter

Core The internal base logic in the Intel

CPU Central Processing Unit

CRT Cathode Ray Tube

DBI Dynamic Bus inversion

DBL Display Brightness Link

DDC Display Data Channel (standard created by VESA)

DPMS Display Power Management Signaling (standard created by VESA)

®

82854 GMCH

Introduction

DVI* Digital Visual Interface is the interface specified by the DDWG (Digital Display

DVMT Dynamic Video Memory Technology

DVO Digital Video Out

EDID Extended Display Identification Data

EIST Enhanced Intel

FSB Front side bus. Connection between Intel

Full Reset A full Intel

GMCH Refers to the GMCH component. Throughout this datasheet, the Intel

HD High definition, typically MP@HL for MPEG2; Resolution supported are 720p,

Host This term is used synonymously with processor

Hub Interface (HI) The proprietary interconnect between the Intel

2

I

C Inter-IC (a two wire serial bus created by Philips)

Working Group) DVI Spec. Rev. 1.0 utilizing only the Silicon Image developed

TMDS protocol

®

SpeedStep® Technology

®

known as the Host interface

®

asserted

Graphics Memory Controller Hub (GMCH) will be referred to as the GMCH.

1080i and 1080p

component. In this document, the Hub interface cycles originating from or

destined for the ICH4-M are generally referred to as “Hub interface cycles.” Hub

cycles originating from or destined for the primary PCI interface on are

sometimes referred to as “Hub interface/PCI cycles”

82854 GMCH Reset is defined in this document when RSTIN# is

82854 GMCH and the CPU. Also

®

82854

®

82854 GMCH and the ICH4-M

IGD Integrated Graphics Device

D15343-003 17

Page 18

Intel® 82854 Graphics Memory Controller Hub (GMCH)

Intel 82801DBM ICH4-M The component contains the primary PCI interface, LPC interface, USB 2.0,

ATA-100, AC’97, and other I/O functions. It communicates with the Intel

®

82854

GMCH over a proprietary interconnect called the Hub interface. Throughout this

datasheet, the Intel 82801DBM ICH4-M component will be referred to as the

ICH4-M

IPI Inter Processor Interrupt

LCD Liquid Crystal Display

MSI Message Signaled Interrupts. MSI allow a device to request interrupt service via

a standard memory write transaction instead of through a hardware signal

Native Graphic Mode The Intel

®

82854 GMCH can support RGB and Dual Independent Display in this

mode

PWM Pulse Width Modulation

SD Standard definition, typically MP@ML for MPEG2

SSC Spread Spectrum Clocking

STB Set Top Box

System Bus Processor-to-Intel

®

82854 GMCH interface. The Enhanced mode of the

Scalable bus is the P6 Bus plus enhancements, consisting of source

synchronous transfers for address and data, and system bus interrupt delivery.

The Intel Celeron M processor implements a subset of Enhanced mode.

UMA Unified Memory Architecture with graphics memory for the IGD inside system

memory

VDL Video Data Link

18 D15343-003

Page 19

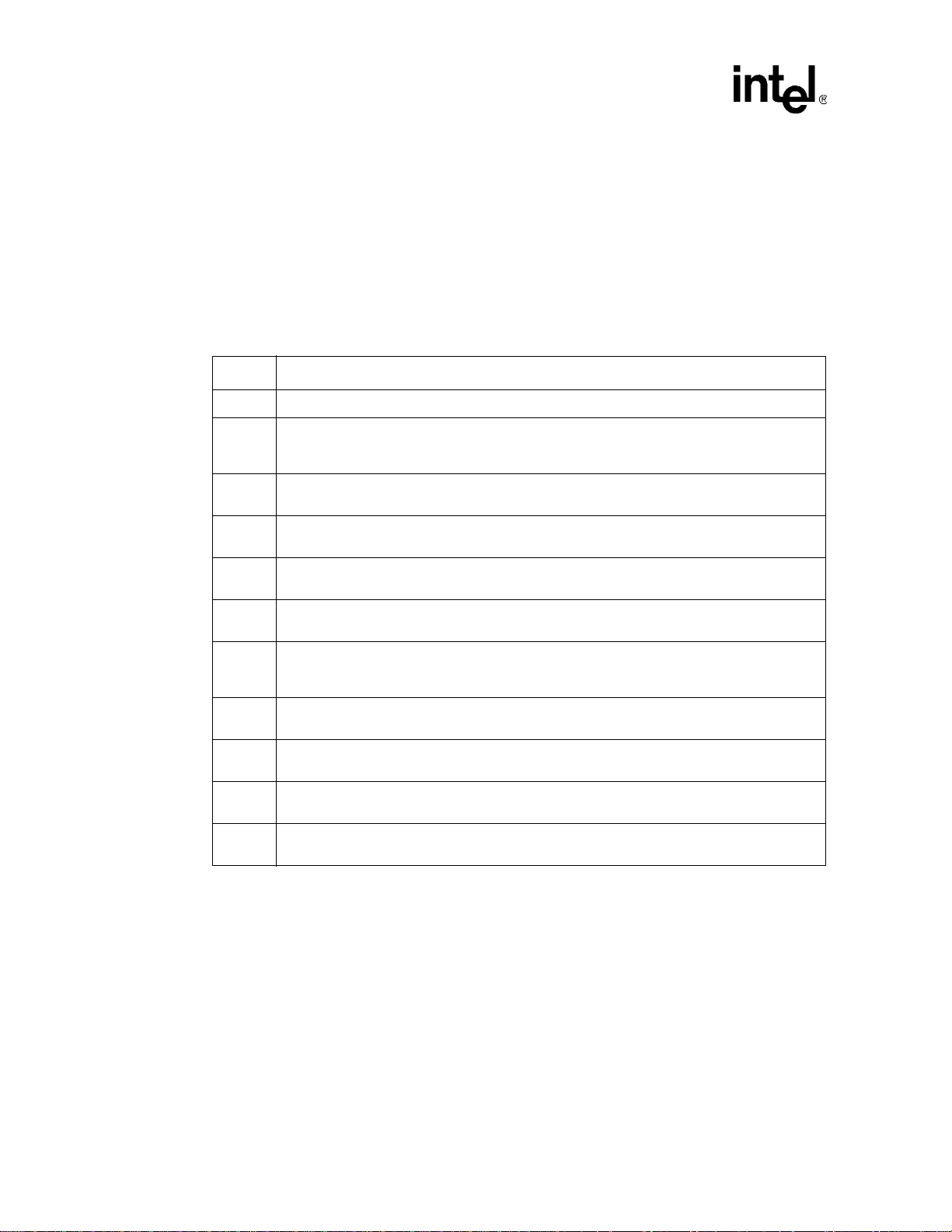

1.3 Reference Documents

Table 2. Reference Documents

Document Location

Intel® Celeron® M Processor Datasheet http://www.intel.com/design/mobile/datashts/300302.htm

Introduction

Ultra Low Voltage Intel(R) Celeron(R) M

Processor at 600 MHz Addendum to the

Intel(R) Celeron(R) M Processor Datasheet

Intel® 854 Chipset Platform Design Guide

for Use with Ultra Low Voltage Intel®

Celeron® M Processor at 600 MHz

PCI Local Bus Specification 2.2 http://www.pcisig.com

Intel® 82801DBM I/O Controller Hub 4

Mobile (ICH4-M) Datasheet

Advanced Configuration and Power

Management (ACPI) Specification 1.0b &

2.0

IA-32 Intel® Architecture Software

Developer Manual Volume 3: System

Programming Guide

INTEL® DIGITAL VIDEO OUT (DVO) PORT

HARDWARE EXTERNAL DESIGN

SPECIFICATION (EDS) VER – 2.X

ARIB TR-B15 Operational Guidelines for

Digital Satellite Broadcasting (detailed

Implementation guideline for receiver)

ATSC Standards http://www.atsc.org/standards.html

http://developer.intel.com/design/intarch/datashts/

301753.htm

Please contact your local Intel representative for this

document.

http://developer.intel.com/design/mobile/datashts/

252337.htm

http://www.acpi.info/

http://developer.intel.com/design/pentium4/manuals/

245472.htm

Please contact your local Intel representative for this

document.

http://www.arib.or.jp/english/html/overview/ov/tr_b15.html

D15343-003 19

Page 20

Intel® 82854 Graphics Memory Controller Hub (GMCH)

20 D15343-003

Page 21

2.0 Intel® 82854 GMCH Overview

2.1 System Architecture

The Intel® 82854 GMCH includes a processor interface, DDR SDRAM interface, display

interface, and Hub interface.

Combined with the ULV Intel® Celeron® M Processor or Genuine Intel® Processor, and an ICH4M, it provides many of the functions required to deliver the features below:

• Overall system software platform

• Graphic overlay function for the GUI and 3-D graphics for gaming.

• Soft CODEC function

• STB middleware execution

• New STB embedded applications requiring IA level of high performance.

2.1.1 Intel® 82854 GMCH

The Intel® 82854 GMCH is in a 732-pin Micro-FCBGA package that contains the following

functionality listed below:

• AGTL+ host bus supporting 32-bit host addressing with Enhanced Intel SpeedStep technology

support

• Supports a single channel of DDR SDRAM memory

• System memory supports DDR 266/333 MHz (SSTL_2) DDR SDRAM

• Integrated graphics capabilities: Graphic Core frequency at 200, 250 MHz

• Supports three display ports: one progressive scan analog monitor and two DVO ports.

• Enhanced Power Management Graphics features

Intel® 82854 GMCH Overview

D15343-003 21

Page 22

Intel® 82854 Graphics Memory Controller Hub (GMCH)

2.2 Processor Host Interface

The Intel® 82854 GMCH supports the Intel Celeron M Processor, and Genuine Intel Processor.

Key features of the front side bus (FSB) are:

• Support for a 400-MHz system bus frequency.

• Source synchronous double pumped address (2X)

• Source synchronous quad pumped data (4X)

• Front side bus interrupt delivery

• Low voltage swing Vtt (1.05 ~ 1.55V)

• Dynamic Power Down (DPWR#) support

• Integrates AGTL+ termination resistors on all of the AGTL+ signals

• Supports 32-bit host bus addressing allowing the CPU to access the entire 4 GB of the GMCH

memory address space.

• An 8-deep, In-Order queue

• Support DPWR# signal

• Supports one outstanding defer cycle at a time to any particular I/O interface

2.3 GMCH System Memory Interface

The GMCH system memory controller directly supports the following:

• One channel of PC2100/2700 DIMM DDR SDRAM memory

• DDR SDRAM devices with densities of 128-Mb, 256-Mb, and 512-Mb technology

• Up to 1 GB (512-Mb technology) with two DDR DIMMs

• Up to 2 GB (512-Mb technology) using high density devices with two DDR DIMMs

Table 3. DDR SDRAM Memory Capacity

Technology Width System Memory Capacity

128 Mb 16 256 MB -

256 Mb 16 512 MB -

512 Mb 16 1 GB -

128 Mb 8 256 MB 512 MB

256 Mb 8 512 MB 1 GB

512 Mb 8 1 GB 2 GB

The GMCH system memory interface supports a thermal throttling scheme to selectively throttle

reads and/or writes. Throttling can be triggered either by the on-die thermal sensor, or by preset

write bandwidth limits. Read throttle can also be triggered by an external input pin. The memory

controller logic supports aggressive Dynamic Row Power Down features to help reduce power and

supports Address and Control line tri-stating when DDR SDRAM is in an active power down or in

self refresh state.

System Memory Capacity

with Stacked Memory

22 D15343-003

Page 23

The GMCH system memory architecture is optimized to maintain open pages (up to 16-KB page

size) across multiple rows. As a result, up to 16 pages across four rows is supported. To

complement this, the GMCH will tend to keep pages open within rows, or will only close a single

bank on a page miss. The GMCH supports only four bank memory technologies.

2.4 Graphics Features

The GMCH IGD provides a highly integrated graphics accelerator delivering high performance

2D, 3D, and video capabilities. With its interfaces to UMA using a DVMT configuration, an analog

display, and two digital display ports, the GMCH can provide a complete graphics solution.

The GMCH also provides 2D hardware acceleration for block transfers of data (BLTs). The BLT

engine provides the ability to copy a source block of data to a destination and perform raster

operations (for example, ROP1, ROP2, and ROP3) on the data using a pattern, and/or another

destination. Performing these common tasks in hardware reduces CPU load, and thus improves

performance.

High bandwidth access to data is provided through the system memory interface. The GMCH uses

Tiling architecture to increase system memory efficiency and thus maximize effective rendering

bandwidth. The Intel

rendering technology. The Intel

Cubic filtering.

®

82854 GMCH improves 3D performance and quality with 3D Zone

Intel® 82854 GMCH Overview

®

82854 GMCH also supports Video Mixer rendering, and Bi-

2.5 Display Features

The Intel® 82854 GMCH has three display ports: one analog and two digital. With these interfaces,

the GMCH can provide support for a progressive scan analog monitor and two DVO ports. The

native graphic mode is able to deliver up to two streams of data via the two DVO ports.

2.5.1 GMCH Analog Display Port

The Intel® 82854 GMCH has an integrated 350-MHz, 24-bit RAMDAC that can directly drive a

progressive scan analog monitor pixel resolution up to 1600x1200 at 85-Hz refresh and up to

2048x1536 at 75-Hz refresh. In the native graphic mode, the Analog display port can be driven by

Pipe A or Pipe B.

2.5.2 GMCH Integrated DVO Ports

The Intel® 82854 GMCH provides a digital display channel that is capable of driving a pixel clock

up to 165 MHz.

The GMCH supports three ARIB planes of graphics: Still Picture Plane, Text and Graphic Plane,

and Superimpose Text Plane at a frame rate of 10 fps. A minimum of two displays are supported.

The ARIB plane resolutions supported can be found in Figure 8.

In native graphics mode, the GMCH supports a single display up to 60 fps real time with maximum

resolution of 720 x 480 pixels.

D15343-003 23

Page 24

Intel® 82854 Graphics Memory Controller Hub (GMCH)

2.6 Hub Interface

A proprietary interconnect connects the GMCH to the ICH4-M. All communication between the

GMCH and the ICH4-M occurs over the Hub interface 1.5. The Hub interface runs at 66 MHz

(266-MB/s).

2.7 Address Decode Policies

Host initiated I/O cycles are positively decoded to the GMCH configuration space and

subtractively decoded to the Hub interface. Host initiated system memory cycles are positively

decoded to DDR SDRAM and are again subtractively decoded to the Hub interface, if less than

4 GB. System memory accesses from the Hub interface to DDR SDRAM will be snooped on

the FSB.

24 D15343-003

Page 25

2.8 GMCH Clocking

The GMCH has the following clock input/output pins:

• 400-MHz, spread spectrum, low voltage differential BCLK, BCLK# for front side bus (FSB)

• 66-MHz, 3.3-V GCLKIN for Hub interface buffers

• Six pairs of differential output clocks (SCK[5:0], SCK[5:0]#), 200/266 MHz, 2.5 V for system

memory interface

• 48-MHz, non-Spread Spectrum, 3.3-V DREFCLK for the Display Frequency Synthesis

• 8-MHz or 66-MHz, Spread Spectrum, 3.3-V DREFSSCLK for the Display Frequency

Synthesis

• Up to 148.5 MHz, 1.5-V DVOBCCLKINT for TV-Out mode

• DPMS clock for S1-M

Clock Synthesizer chips are responsible for generating the system host clocks, GMCH display

clocks, Hub interface clocks, PCI clocks, SIO clocks, and FWH clocks. The host target speed is

400 MHz. The GMCH does not require any relationship between the BCLK Host clock and the

66-MHz clock generated for the Hub interface; they are asynchronous to each other. The Hub

interface runs at a constant 66-MHz base frequency . Table 4 indicates the frequency ratios between

the various interfaces that the GMCH supports.

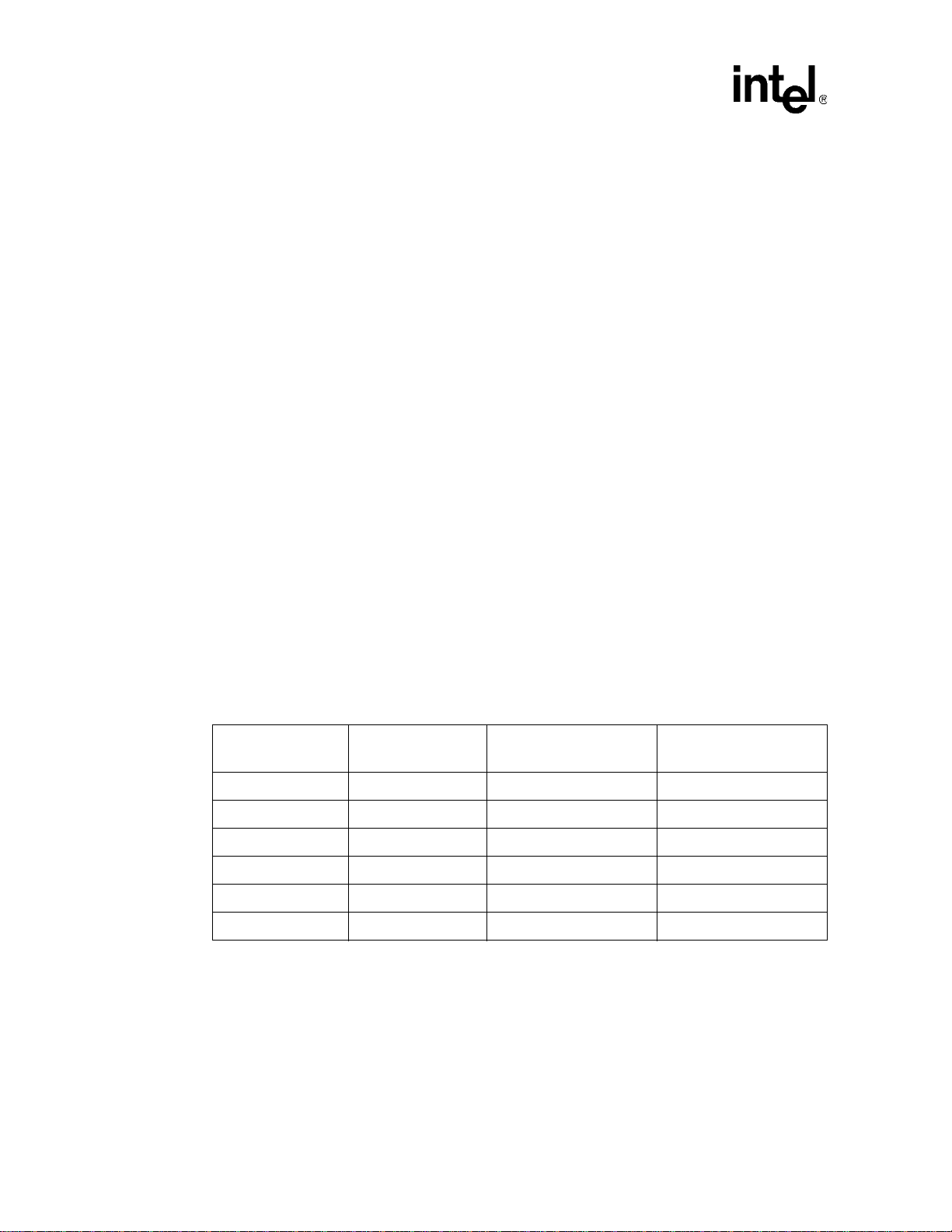

Table 4. Intel® 82854 GMCH Interface Clocks

Intel® 82854 GMCH Overview

Interface Clock Speed

CPU Bus 100 MHz Reference 4 400 8 3200

DDR SDRAM 133 MHz 1:1 Synchronous 2 266 8 2128

166 MHz 1:1 Synchronous 2 333 8 2664

DVO B or DVO C

(Native Graphic

Mode)

DVO B+DVO C

(Native Graphic

Mode)

DAC Interface 350 MHz Asynchronous 1 350 3 1050

Up to 165

MHz

Up to 330

MHz

CPU System

Bus Frequency

Ratio

Asynchronous 2 330 1.5 495

Asynchronous 2 660 3 1980

Samples

Per Clock

Data Rate

(Megasamples/s)

Data

Width

(Bytes)

Peak

Bandwidth

(MB/s)

D15343-003 25

Page 26

Intel® 82854 Graphics Memory Controller Hub (GMCH)

2.9 System Interrupts

The GMCH supports both the legacy Intel 8259 Programmable Interrupt delivery mechanism and

the Intel Celeron M processor FSB interrupt delivery mechanism. The serial APIC Interrupt

mechanism is not supported.

The Intel 8259 Interrupt delivery mechanism support consists of flushing in bound Hub interface

write buffers when an Interrupt Acknowledge cycle is forwarded from the system bus to the Hub

interface.

PCI MSI interrupts are generated as memory writes. The GMCH decodes upstream memory writes

to the range 0FEE0_0000h - 0FEEF_FFFFh from the Hub interface as message based interrupts.

The GMCH forwards the memory writes along with the associated write data to the system bus as

an Interrupt Message transaction. Since this address does not decode as part of main system

memory, the write cycle and the write data do not get forwarded to system memory via the write

buffer . The GMCH provides the response and HTRDY# for all Interrupt Message cycles including

the ones originating from the GMCH. The GMCH also supports interrupt redirection for upstream

interrupt memory writes.

For message based interrupts, system write buffer coherency is maintained by relying on strict

ordering of memory writes. The GMCH ensures that all memory writes received from a given

interface prior to an interrupt message memory write are delivered to the system bus for snooping

in the same order that they occur on the given interface.

26 D15343-003

Page 27

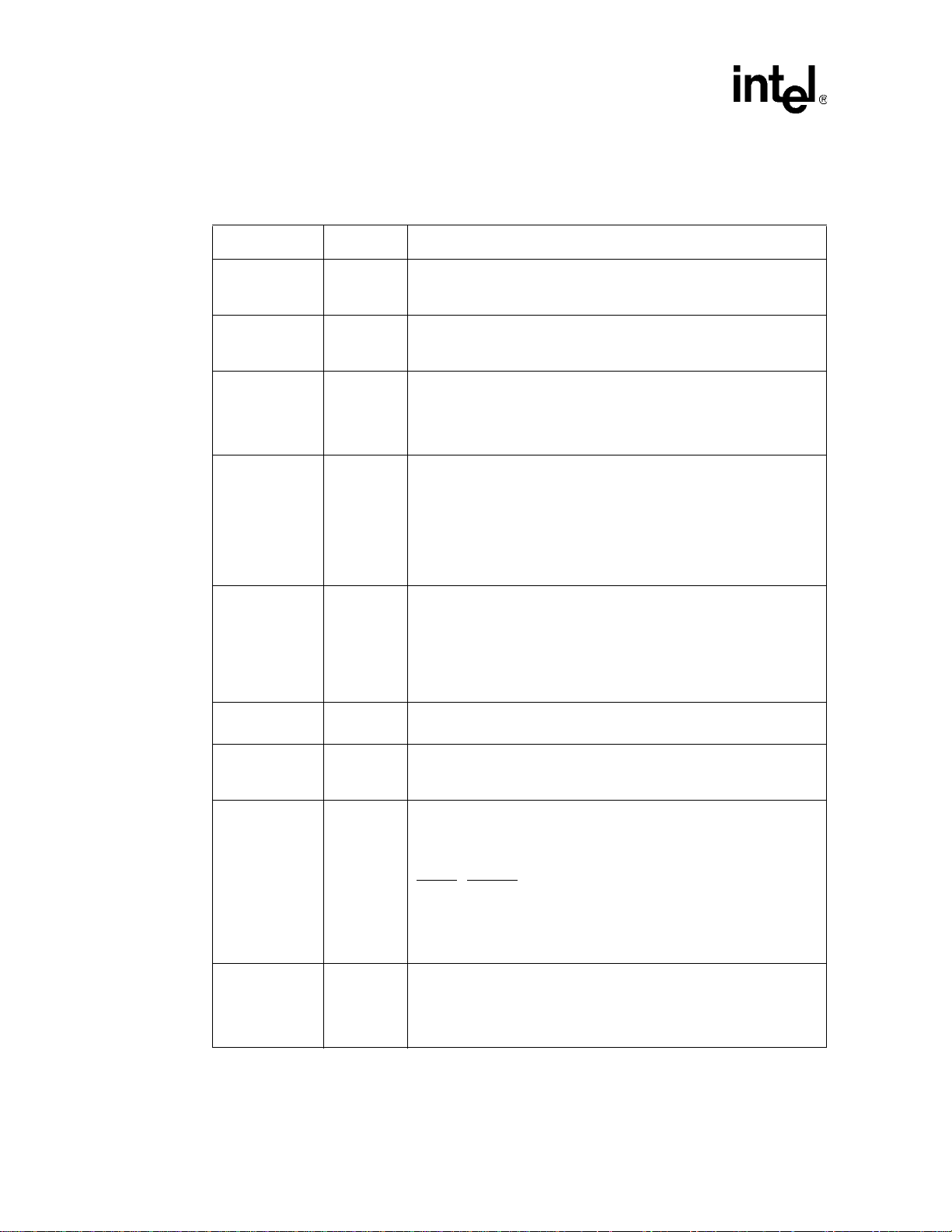

3.0 Signal Description

This section describes the Intel® 82854 GMCH signals. These signals are arranged in functional

groups according to their associated interface. The following notations are used to describe the

signal type.

Notation Description

I Input pin

O Output pin

I/O Bi-directional Input/Output pin

The signal description also includes the type of buffer used for the particular signal:

Buffer Description

AGTL+ Open Drain AGTL+ interface signal. Refer to the AGTL+ I/O

Specification for complete details. The GMCH integrates AGTL+

termination resistors, and supports VTTLF of 1.05 V ± 5%. AGTL+

signals are "inverted bus" style where a low voltage represents a

logical 1.

DVO DVO buffers (1.5-V tolerant)

Hub Compatible to Hub interface 1.5

SSTL_2 Stub Series Termination Logic compatible signals (2.5-V tolerant)

LVTTL Low Voltage TTL compatible signals (3.3-V tolerant)

CMOS CMOS buffers (3.3-V tolerant)

Analog Analog signal interface

Ref Voltage reference signal

Signal Description

Note: System Address and Data Bus signals are logically inverted signals. In other words, the actual

values are inverted from what appears on the system bus. This must be taken into account and the

addresses and data bus signals must be inverted inside the GMCH. All processor control signals

follow normal convention: A 0 indicates an active level (low voltage), and a 1 indicates an active

level (high voltage).

D15343-003 27

Page 28

Intel® 854 Graphics Memory Controller Hub (GMCH)

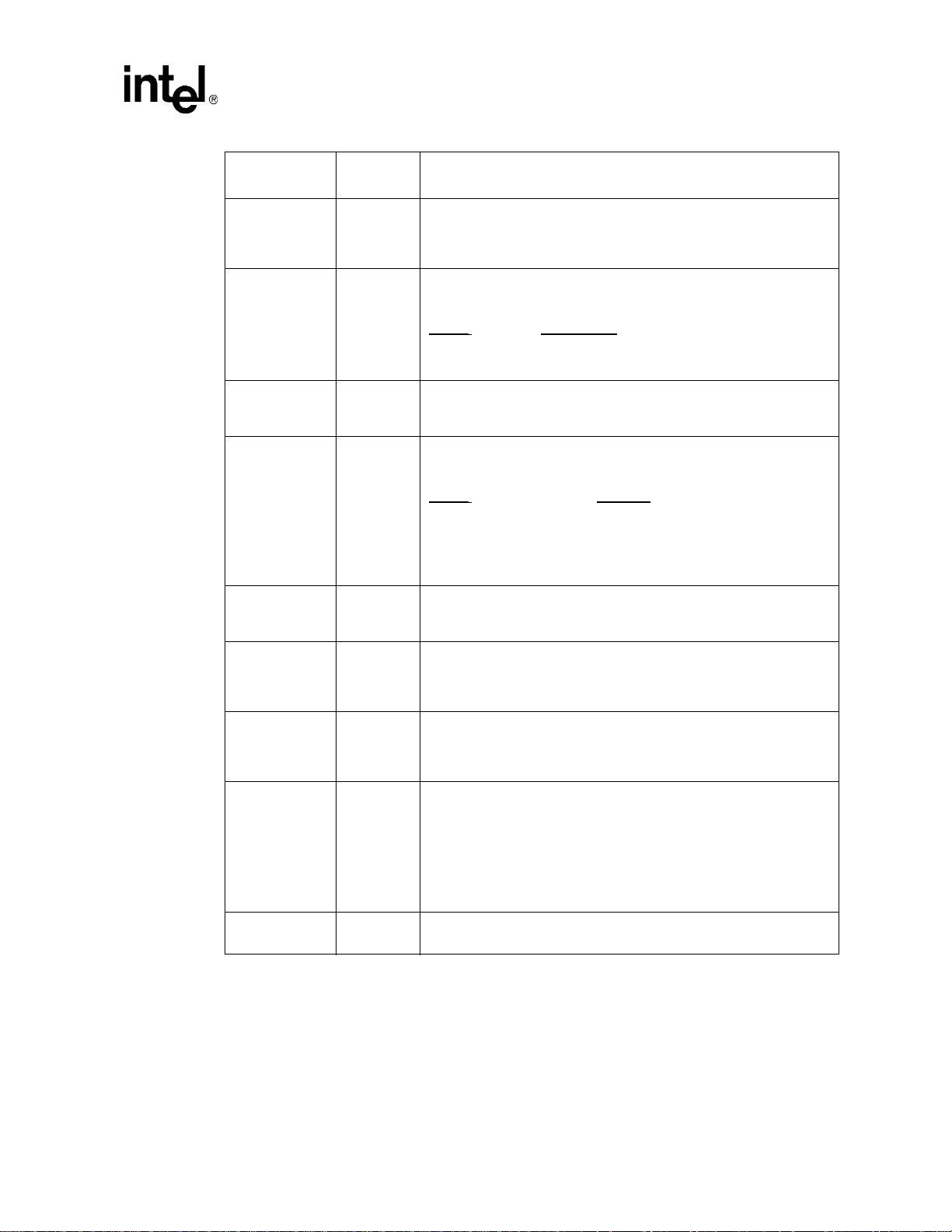

3.1 Host Interface Signals

Table 5. Host Interface Signal Descriptions

Signal Name Type Description

ADS# I/O

AGTL+

BNR# I/O

AGTL+

BPRI# O

AGTL+

BREQ0# I/O

AGTL+

CPURST# O

AGTL+

DBSY# I/O

AGTL+

Address Strobe: The system bus owner asserts ADS# to indicate the

first of two cycles of a request phase. The GMCH can assert this signal

for snoop cycles and interrupt messages.

Block Next Request: Used to block the current request bus owner from

issuing a new request. This signal is used to dynamically control the CPU

bus pipeline depth.

Bus Priority Request: The GMCH is the only Priority Agent on the

system bus. It asserts this signal to obtain the ownership of the address

bus. This signal has priority over symmetric bus requests and will cause

the current symmetric owner to stop issuing new transactions unless the

HLOCK# signal was asserted.

Bus Request 0#: The GMCH pulls the processor bus BREQ0# signal

low during CPURST#. The signal is sampled by the processor on the

active-to-inactive transition of CPURST#. The minimum setup time for

this signal is 4 BCLKs. The minimum hold time is 2 clocks and the

maximum hold time is 20 BCLKs. BREQ0# should be tristated after the

hold time requirement has been satisfied.

During regular operation, the GMCH will use BREQ0# as an early

indication for FSB Address and Ctl input buffer and sense amp activation.

CPU Reset: The CPURST# pin is an output from the GMCH. The

GMCH asserts CPURST# while RESET# (PCIRST# from ICH4-M) is

asserted and for approximately 1 ms after RESET# is deasserted. The

CPURST# allows the processor to begin execution in a known state.

Note that the ICH4-M must provide CPU strap set-up and hold-times

around CPURST#. This requires strict synchronization between GMCH,

CPURST# deassertion and ICH4-M driving the straps.

Data Bus Busy: Used by the data bus owner to hold the data bus for

transfers requiring more than one cycle.

DEFER# O

AGTL+

DINV[3:0]# I/O

AGTL+

DPSLP# I

CMOS

Defer: GMCH will generate a deferred response as defined by the rules

of the GMCH’s Dynamic Defer policy. The GMCH will also use the

DEFER# signal to indicate a CPU retry response.

Dynamic Bus Inversion: Driven along with the HD[63:0]# signals.

Indicates if the associated signals are inverted or not. DINV[3:0]# are

asserted such that the number of data bits driven electrically low (low

voltage) within the corresponding 16-bit group never exceeds 8.

DINV#

Data Bits

DINV[3]# HD[63:48]#

DINV[2]# HD[47:32]#

DINV[1]# HD[31:16]#

DINV[0]# HD[16:0]#

Deep Sleep #: This signal comes from the ICH4-M device, providing an

indication of C3 and C4 state control to the CPU. Deassertion of this

signal is used as an early indication for C3 and C4 wake up (to active

HPLL). Note that this is a low-voltage CMOS buffer operating on the FSB

VTT power plane.

28 D15343-003

Page 29

Signal Description

DRDY# I/O

AGTL+

HA[31:3]# I/O

HADSTB[1:0]# I/O

HD[63:0]# I/O

HDSTBP[3:0]#

HDSTBN[3:0]#

HIT# I/O

AGTL+

AGTL+

AGTL+

I/O

AGTL+

AGTL+

Data Ready: Asserted for each cycle that data is transferred.

Host Address Bus: HA[31:3]# connects to the CPU address bus. During

processor cycles the HA[31:3]# are inputs. The GMCH drives HA[31:3]#

during snoop cycles on behalf of Hub interface. HA[31:3]# are

transferred at 2x rate. Note that the address is inverted on the CPU bus.

Host Address Strobe: HA[31:3]# connects to the CPU address bus.

During CPU cycles, the source synchronous strobes are used to transfer

HA[31:3]# and HREQ[4:0]# at the 2x transfer rate.

Strobe

Address Bits

HADSTB[0]# HA[16:3]#, HREQ[4:0]#

HADSTB[1]# HA[31:17]#

Host Data: These signals are connected to the CPU data bus.

HD[63:0]# are transferred at 4x rate. Note that the data signals are

inverted on the CPU bus.

Differential Host Data Strobes: The differential source synchronous

strobes are used to transfer HD[63:0]# and DINV[3:0]# at the 4x

transfer rate.

Strobe

Data Bits

HDSTBP[3]#, HDSTBN[3]# HD[63:48]#, DINV[3]#

HDSTBP[2]#, HDSTBN[2]# HD[47:32]#, DINV[2]#

HDSTBP[1]#, HDSTBN[1]# HD[31:16]#, DINV[1]#

HDSTBP[0]#, HDSTBN[0]# HD[15:0]#, DINV[0]#

Hit: Indicates that a caching agent holds an unmodified version of the

requested line. Also, driven in conjunction with HITM# by the target to

extend the snoop window.

HITM# I/O

AGTL+

HLOCK# I/O

AGTL+

HREQ[4:0]# I/O

AGTL+

HTRDY# O

AGTL+

Hit Modified: Indicates that a caching agent holds a modified version of

the requested line and that this agent assumes responsibility for

providing the line. Also, driven in conjunction with HIT# to extend the

snoop window.

Host Lock: All CPU bus cycles sampled with the assertion of HLOCK#

and ADS#, until the negation of HLOCK# must be atomic; that is, no Hub

interface snoopable access to system memory is allowed when HLOCK#

is asserted by the CPU.

Host Request Command: Defines the attributes of the request.

HREQ[4:0]# are transferred at 2x rate. Asserted by the requesting agent

during both halves of the Request Phase. In the first half the signals

define the transaction type to a level of detail that is sufficient to begin a

snoop request. In the second half the signals carry additional information

to define the complete transaction type.

The transactions supported by the GMCH Host Bridge are defined in the

Host Interface section of this document.

Host Target Ready: Indicates that the target of the processor

transaction is able to enter the data transfer phase.

D15343-003 29

Page 30

Intel® 854 Graphics Memory Controller Hub (GMCH)

RS[2:0]# O

AGTL+

Response Status: Indicates the type of response according to the

following the table:

RS[2:0]#

000 Idle state

001 Retry response

010 Deferred response

011 Reserved (not driven by GMCH)

100 Hard Failure (not driven by GMCH)

101 No data response

110 Implicit Write back

111 Normal data response

Response type

30 D15343-003

Page 31

3.2 DDR SDRAM Interface

Table 6. DDR SDRAM Interface Descriptions

Signal Name Type Description

Signal Description

SCS[3:0]# O

SSTL_2

SMA[12:0] O

SSTL_2

SBA[1:0] O

SSTL_2

SRAS# O

SSTL_2

SCAS# O

SSTL_2

SWE# O

SSTL_2

SDQ[63:0] I/O

SSTL_2

Chip Select: These pins select the particular DDR SDRAM

components during the active state.

NOTE: There is one SCS# per DDR-SDRAM Physical DDR DIMM

device row. These signals can be toggled on every rising System

Memory Clock edge (SCMDCLK).

Multiplexed Memory Address: These signals are used to provide the

multiplexed row and column address to the DDR SDRAM.

Bank Select (Memory Bank Address): These signals define which

banks are selected within each DDR SDRAM row. The SMA and SBA

signals combine to address every possible location within a DDR

SDRAM device.

DDR Row Address Strobe: SRAS# may be heavily loaded and

requires tw0 DDR SDRAM clock cycles for setup time to the DDR

SDRAMs. Used with SCAS# and SWE# (along with SCS#) to define the

system memory commands.

DDR Column Address Strobe: SCAS# may be heavily loaded and

requires two clock cycles for setup time to the DDR SDRAMs. Used

with SRAS# and SWE# (along with SCS#) to define the system memory

commands.

Write Enable: Used with SCAS# and SRAS# (along with SCS#) to

define the DDR SDRAM commands. SWE# is asserted during writes to

DDR SDRAM. SWE# may be heavily loaded and requires two clock

cycles for setup time to the DDR SDRAMs.

Data Lines: These signals are used to interface to the DDR SDRAM

data bus.

I/O

SDQS[8:0]

SCKE[3:0] O

SSTL_2

SSTL_2

Data Strobes: Data strobes are used for capturing data. During writes,

SDQS is centered on data. During reads, SDQS is edge aligned with

data. The following list matches the data strobe with the data bytes.

There is an associated data strobe (DQS) for each data signal (DQ) and

check bit (CB) group.

SDQS[7] -> SDQ[63:56]

SDQS[6] -> SDQ[55:48]

SDQS[5] -> SDQ[47:40]

SDQS[4] -> SDQ[39:32]

SDQS[3] -> SDQ[31:24]

SDQS[2] -> SDQ[23:16]

SDQS[1] -> SDQ[15:8]

SDQS[0] -> SDQ[7:0]

Clock Enable: These pins are used to signal a self-refresh or power

down command to the DDR SDRAM array when entering system

suspend. SCKE is also used to dynamically power down inactive DDR

SDRAM rows. There is one SCKE per DDR SDRAM row. These

signals can be toggled on every rising SCK edge.

D15343-003 31

Page 32

Intel® 854 Graphics Memory Controller Hub (GMCH)

SMAB[5,4,2,1] O

SSTL_2

SDM[8:0] O

SSTL_2

RCVENOUT# O

SSTL_2

RCVENIN# O

SSTL_2

3.3 Hub Interface Signals

Table 7. Hub Interface Signals

Signal Name Type Description

HL[10:0] I/O Hub Packet Data: Data signals used for HI read and write operations.

HLSTB I/O Hub Packet Strobe: One of two differential strobe signals used to transmit or

receive packet data over HI.

HLSTB# I/O Hub Packet Strobe Complement: One of two differential strobe signals used

to transmit or receive packet data over HI.

Memory Address Copies: These signals are identical to SMA[5,4,2,1]

and are used to reduce loading for selective CPC(clock-per-command).

These copies are not inverted.

Data Mask: When activated during writes, the corresponding data

groups in the DDR SDRAM are masked. There is one SDM for every

eight data lines. SDM can be sampled on both edges of the data

strobes.

Clock Output: Reserved, NC.

Clock Input: Reserved, NC.

32 D15343-003

Page 33

3.4 Clocks

Table 8. Clock Signals

Signal Name Type Description

Host Processor Clocking

Signal Description

BCLK

BCLK#

System Memory Clocking

SCK[5:0] O

SCK[5:0]# O

DVO/Hub Input Clocking

GCLKIN I

DVO Clocking

DVOBCLK

DVOBCLK#

DVOCCLK

DVOCCLK#

CMOS

SSTL_2

SSTL_2

CMOS

DVO

DVO

I

O

O

Differential Host Clock In: These pins receive a buffered host clock

from the external clock synthesizer. This clock is used by all of the

GMCH logic that are in the Host clock domain (Host, Hub and system

memory). The clock is also the reference clock for the graphics core

PLL. This is a low voltage differential input.

Differential DDR SDRAM Clock: SCK and SCK# pairs are differential

clock outputs. The crossing of the positive edge of SCK and the

negative edge of SCK# is used to sample the address and control

signals on the DDR SDRAM. There are 3 pairs to each DDR DIMM.

Complementary Differential DDR SDRAM Clock: These are the

complimentary differential DDR SDRAM clock signals.

Input Clock: 66-MHz, 3.3-V input clock from external buffer DVO/Hub

interface.

Differential DVO Clock Output: These pins provide a differential pair

reference clock that can run up to 165-MHz.

DVOBC LK corresponds to the primary clock out.

DVOBC LK# corresponds to the primary complementary clock out.

DVOBC LK and DVOB CLK # should be left as NC (“Not Connected”) if

the DVO B port is not implemented.

Differential DVO Clock Output: These pins provide a differential pair

reference clock that can run up to 165-MHz.

DVOCCL K corresponds to the primary clock out.

DVOCCL K# corresponds to the primary complementary clock out.

DVOCCL K and DVOCCL K# should be left as NC (“Not Connected”) if

the DVO C port is not implemented.

DVOBCCLKINT I

DVO

DVOBC Pixel Clock Input/Interrupt: This signal may be selected as

the reference input to either dot clock PLL (DPLL) or may be

configured as an interrupt input. A TV-out device can provide the clock

reference. The maximum input frequency for this signal is 148.5 -MHz.

DVOBC Pixel Clock Input: When selected as the dot clock PLL (DPLL)

reference input, this clock reference input supports SSC clocking for

DVO LVDS devices.

DVOBC Interrupt: When configured as an interrupt input, this interrupt

can support either DVOB or DVOC.

DVOBC CLK INT needs to be pulled down if the signal is NOT used.

D15343-003 33

Page 34

Intel® 854 Graphics Memory Controller Hub (GMCH)

DPMS I

DVO

DAC Clocking

DREFCLK I

LVT TL

Display Power Management Signaling: This signal is used only in

mobile systems to act as the DREFCLK in certain power management

states (i.e., Display Power Down Mode); DPMS Clock is used to

refresh video during S1-M. Clock Chip is powered down in S1-M.

DPMS should come from a clock source that runs during S1-M and

needs to be 1.5 V. So, an example would be to use a 1.5-V version of

SUSCLK from ICH4-M.

Display Clock Input: This pin is used to provide a 48-MHz input clock

to the Display PLL that is used for 2D/Video and DAC.

34 D15343-003

Page 35

3.5 Internal Graphics Display Signals

The IGD has support for DVOB/C interfaces, and an Analog CRT port.Digital Video Output B

(DVOB) Port.

3.5.1 Digital Video Output B (DVOB) Port

Table 9. Digital Video Output B (DVOB) Port Signal Descriptions

Name Type Description

Signal Description

DVOBD[11:0] O

DVO

DVOBHSYNC O

DVO

DVOBVSYNC O

DVO

DVOBBLANK# O

DVO

DVOBFLDSTL I

DVO

DVOB Data: This data bus is used to drive 12-bit RGB data on each edge

of the differential clock signals, DVOBC LK and DVOBC LK# . This provides

24-bits of data per clock period. In dual channel mode, this provides the

lower 12-bits of pixel data.

DVOBD[11:0] should be left as NC (“Not Connected”) if not used.

Horizontal Sync: HSYNC signal for the DVOB interface.

DVOBHSYNC should be left as left as NC (“Not Connected”) if not used.

Vertical Sync: VSYNC signal for the DVOB interface.

DVOBVSYNC should be left as left as NC (“Not Connected”) if the signal

is NOT used when using internal graphics device.

Flicker Blank or Border Period Indication: DVOBBLANK# is a

programmable output pin driven by the GMCH.

When programmed as a blank period indication, this pin indicates active

pixels excluding the border. When programmed as a border period

indication, this pin indicates active pixel including the border pixels.

DVOBBLANK# should be left as left as NC (“Not Connected”) if not used.

TV Field and Flat Panel Stall Signal. This input can be programmed to

be either a TV Field input from the TV encoder or Stall input from the flat

panel.

DVOB TV Field Signal: When used as a Field input, it synchronizes the

overlay field with the TV encoder field when the overlay is displaying an

interleaved source.

DVOB Flat Panel Stall Signal: When used as the Stall input, it indicates

that the pixel pipeline should stall one horizontal line. The signal changes

during horizontal blanking. The panel fitting logic, when expanding the

image vertically, uses this.

DVOBF LDS TL needs to be pulled down if not used.

D15343-003 35

Page 36

Intel® 854 Graphics Memory Controller Hub (GMCH)

3.5.2 Digital Video Output C (DVOC) Port

Table 10. Digital Video Output C (DVOC) Port Signal Descriptions

Name Type Description

DVOCD[11:0] O

DVO

DVOCHSYNC O

DVO

DVOCVSYNC O

DVO

DVOCBLANK# O

DVO

DVOCFLDSTL I

DVO

[Native Graphic Mode]

DVOC Data: This data bus is used to drive 12-bit RGB data on each edge

of the differential clock signals, DVOCC LK and DVOCC LK# . This

provides 24-bits of data per clock period. In dual channel mode, this

provides the upper 12-bits of pixel data.

DVOCD[11:0] should be left as left as NC (“Not Connected”) if not used.

Horizontal Sync: HSYNC signal for the DVOC interface.

DVOCHSYNC should be left as left as NC (“Not Connected”) if not used.

Vertical Sync: VSYNC signal for the DVOC interface.

DVOCVSYNC should be left as left as NC (“Not Connected”) if the signal

is NOT used when using internal graphics device.

Flicker Blank or Border Period Indication: DVOCBLANK# is a

programmable output pin driven by the GMCH.

When programmed as a blank period indication, this pin indicates active

pixels excluding the border. When programmed as a border period

indication, this pin indicates active pixel including the border pixels.

DVOCBLANK# should be left as left as NC (“Not Connected”) if not used.

TV Field and Flat Panel Stall Signal. This input can be programmed to

be either a TV Field input from the TV encoder or Stall input from the flat

panel.

DVOC TV Field Signal: When used as a Field input, it synchronizes the

overlay field with the TV encoder field when the overlay is displaying an

interleaved source.

DVOC Flat Panel Stall Signal: When used as the Stall input, it indicates

that the pixel pipeline should stall one horizontal line. The signal changes

during horizontal blanking. The panel fitting logic, when expanding the

image vertically, uses this.

DVOCF LDS TL needs to be pulled down if not used.

36 D15343-003

Page 37

Table 11. DVOB and DVOC Port Common Signal Descriptions

Name Type Description

Signal Description

DVOBCINTR# I

DVO

ADDID[7:0] I

DVO

DVODETECT I

DVO

DVOBC Interrupt: This pin is used to signal an interrupt, typically used to

indicate a hot plug or unplug of a digital display.

ADDID[7:0]: These pins are used to communicate to the Video BIOS

when an external device is interfaced to the DVO port.

Note: Bit[7] needs to be strapped low when an on-board DVO device is

present. The other pins should be left as NC.

ADDID[0] = 0, Reserve

ADDID[0] = 1, the Intel

Native Graphic Mode

For detail of strapping option, please refer to Table 33.

DVODETECT: This strapping signal indicates to the GMCH whether a

DVO device is present or not. When a DVO device is connected, then

DVODETECT = 0.

3.5.3 Analog CRT Display

Table 12. Analog CRT Display Signal Descriptions

Pin Name Type Description

VSYNC O

CMOS

HSYNC O

CMOS

CRT Vertical Synchronization: This signal is used as the vertical sync signal.

CRT Horizontal Synchronization: This signal is used as the horizontal sync

signal.

®

82854 GMCH is strapped to operate under

RED O

Analog

RED# O

Analog

GREEN O

Analog

GREEN# O

Analog

BLUE

Analog

BLUE#

Analog

O

O

Red (Analog Video Output): This signal is a CRT Analog video output from

the internal color palette DAC. The DAC is designed for a 37.5-Ω equivalent

load on each pin (that is, a 75-Ω resistor on the board, in parallel with the 75-Ω

CRT load).

Red# (Analog Output): Tied to ground.

Green (Analog Video Output): This signal is a CRT analog video output from

the internal color palette DAC. The DAC is designed for a 37.5-Ω equivalent

load on each pin (that is, a 75-Ω resistor on the board, in parallel with the 75- Ω

CRT load).

Green# (Analog Output): Tied to ground.

Blue (Analog Video Output) : This signal is a CRT Analog video output from

the internal color palette DAC. The DAC is designed for a 37.5-Ω equivalent

load on each pin (that is, a 75-ohm resistor on the board, in parallel with the 75Ω CRT load).

Blue# (Analog Output): Tied to ground.

D15343-003 37

Page 38

Intel® 854 Graphics Memory Controller Hub (GMCH)

3.5.4 General Purpose Input/Output Signals

Table 13. GPIO Signal Descriptions

GPIO I/F Total Type Comments