Page 1

Intel® Xeon® Processor 5600 Series

Datasheet, Volume 1

June 2011

Reference Number: 323369-002

Page 2

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED,

BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS

PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER,

AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING T O SALE AND/OR USE OF INTEL PRODUCT S INCLUDING

LIABILITY OR WARRANTIES RELA TING T O FITNES S FOR A PARTICULAR PURPOSE, MERCHANT ABILITY, OR INFRINGEMENT OF ANY

PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life savin g, or

life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel

reserves these for future definition and shall have no responsibility whatsoev er for conflicts or incompatibilities arising from future

changes to them.

®

The Intel

deviate from published specifications. Current characterized errata are available on request.

Intel processor numbers are not a measure of performance. Processor numb ers differentia te features withi n each processo r family,

not across different processor families. See http://www.intel.com/products/processor_number for details. Over time processor

numbers will increment based on changes in clock, speed, cache, FSB, or other features, and increments are not intended to

represent proportional or quantitative increases in any particular feature. Current roadmap processor number progression is not

necessarily representative of future roadmaps. See www.intel.com/products/processor_number for details.

Xeon® Processor 5600 Series may contain design defects or errors known as errata which may cause the product to

Hyper-Threading Technology requires a computer system with a processor supporting HT Technology and an HT Technologyenabled chipset, BIOS and operating system. Performance will va ry de pe ndi ng on the specific hardware and software y ou use. For

more information including details on which processors support HT Technology, see

http://www.intel.com/products/ht/hyperthreading_more.htm.

Enabling Execute Disable Bit functionality requires a PC with a processor with Execute Disable Bit capability and a supporting

operating system. Check with your PC manufacturer on whether your system delivers Execute Disable Bit functionality.

64-bit computing on Intel architecture requires a computer system with a processor, chipset, BIOS, operating system, device

drivers and applications enabled for Intel® 64 architecture. Performance will vary depending on your hardware and software

configurations. Consult with your system vendor for more information.

Intel® AES-NI requires a computer system with an AES-NI enabled processor, as well as non-Intel software to execute the

instructions in the correct sequence. AES-NI is available on select Intel® processors. For availability, consult your reseller or

system manufacturer. For more information, see http://software.intel.com/en-us/articles/intel-advanced-encryption-standardinstructions-aes-ni/

Intel® Virtualization Technology requires a computer system with an enabled Intel® processor, BIOS, virtual machine monitor

(VMM) and, for some uses, certain computer system software enabled for it. Functionality, performance or other benefits will vary

depending on hardware and software configur ations and may re quire a BIOS update. S oftware applicatio ns may not be compatible

with all operating systems. Please check with your application vendor.

Intel® Turbo Boost Technology requires a PC with a processor with Intel Turbo Boost Technology capability. Intel Turbo Boost

Technology performance varies depending on hardware, software and overall system configuration. Check with your PC

manufacturer on whether your system delivers Intel Turbo Boost Technology. For more information, see www.intel.com.

Enhanced Intel SpeedStep® Technology. See the http://processorfinder.intel.com or contact your Intel representative for more

information.

Intel, Xeon, Intel 64, Enhanced Intel SpeedStep Technology, and the Intel logo are trademarks of Intel Corporation in the U .S. and

other countries.

*Other brands and names are the property of their respective owners.

Copyright © 2008-2011, Intel Corporation.

2 Intel® Xeon® Processor 5600 Series Datasheet Volume 1

Page 3

Contents

1Introduction............................................................................................................11

1.1 Processor Features............................................................................................12

1.2 Platform Features............................... .. .............................................................12

1.3 Terminology .....................................................................................................13

1.4 References.......................................................................................................15

1.5 Statement of Volatility .......................................................................................15

2 Electrical Specifications...........................................................................................17

2.1 Processor Signaling ...........................................................................................17

2.1.1 Intel® QuickPath Interconnect ...............................................................17

2.1.2 DDR3 Signal Groups..............................................................................17

2.1.3 Platform Environmental Control Interface (PECI).......................................17

2.1.4 Processor Sideband Signals....................................................................18

2.1.5 System Reference Clock ........................................................................18

2.1.6 Test Access Port (TAP) Signals................................................................19

2.1.7 Power / Other Signals............................................................................19

2.1.8 Reserved or Unused Signals...................................................................27

2.2 Signal Group Summary............................. ............................ .............................27

2.3 Mixing Processors..............................................................................................29

2.4 Flexible Motherboard Guidelines (FMB)............................. ... .. ........................... .. ..30

2.5 Absolute Maximum and Minimum Ratings .............................................................30

2.6 Processor DC Specifications ................................................................................31

2.6.1 VCC Overshoot Specifications.................................................................35

2.6.2 Die Voltage Validation ...........................................................................36

2.7 Intel QuickPath Interconnect Specifications...........................................................44

2.8 AC Specifications...............................................................................................47

2.9 Processor AC Timing Waveforms .........................................................................54

3 Signal Quality Specifications....................................................................................65

3.1 Overshoot/Undershoot Tolerance.........................................................................65

4 Package Mechanical Specifications ..........................................................................67

4.1 Package Mechanical Specifications.......................................................................67

4.1.1 Package Mechanical Drawing..................................................................67

4.1.2 Processor Component Keep-Out Zones ....................................................70

4.1.3 Package Loading Specifications...............................................................70

4.1.4 Package Handling Guidelines..................................................................70

4.1.5 Package Insertion Specifications.............................................................70

4.1.6 Processor Mass Specification ......... .. ............................ .. .. .. .....................71

4.1.7 Processor Materials................................... .. .. ............................ ............71

4.1.8 Processor Markings...............................................................................71

5Land Listing.............................................................................................................73

5.1 Listing by Land Name ........................... .. .. .......................... .. .. ...........................73

5.2 Listing by Land Number ............................ .........................................................90

6 Signal Definitions .................................................................................................. 109

6.1 Signal Definitions .................................................. .. ........................................ 109

7 Thermal Specifications .......................................................................................... 113

7.1 Package Thermal Specifications......................... .. .. ........................... ................. 113

7.1.1 Thermal Specifications......................................................................... 113

7.1.2 Thermal Metrology.............................................................................. 128

7.2 Processor Thermal Features.............................................................................. 128

7.2.1 Processor Temperature........................................... .. .. .. ....................... 128

Intel® Xeon® Processor 5600 Series Datasheet Volume 1 3

Page 4

7.2.2 Adaptive Thermal Monitor.....................................................................129

7.2.3 On-Demand Mode ...............................................................................131

7.2.4 PROCHOT# Signal...............................................................................131

7.2.5 THERMTRIP# Signal ............................................................................132

7.3 Platform Environment Control Interface (PECI)....................................................132

7.3.1 PECI Client Capabilities ........................................................................133

7.3.2 Client Command Suite ...... .. .. .................................................. ... .. ........134

7.3.3 Multi-Domain Commands .....................................................................153

7.3.4 Client Responses.................................................................................153

7.3.5 Originator Responses...........................................................................155

7.3.6 Temperature Data...............................................................................155

7.3.7 Client Management............... .. ......................... .. .. .......................... .. .. ..156

7.4 Storage Conditions Specifications.......................................................................158

8Features................................................................................................................161

8.1 Power-On Configuration (POC)...........................................................................161

8.2 Clock Control and Low Power States........................... .. .. ....................................162

8.2.1 Thread and Core Power State Descriptions..............................................163

8.2.2 Package Power State Descriptions .........................................................164

8.2.3 Intel Xeon Processor 5600 Series C-State Power Specifications..................165

8.3 Sleep States ...................................................................................................165

8.4 Intel

®

Turbo Boost Technology............................................. .. ...........................166

8.5 Enhanced Intel SpeedStep® Technology ................... ......................... .. .. .............166

9 Boxed Processor Specifications..............................................................................167

9.1 Introduction....................................................................................................167

9.1.1 Available Boxed Thermal Solution Configurations.....................................167

9.1.2 Intel® Thermal Solution STS100C

(Passive/Active Combination Heat Sink Solution).....................................167

9.1.3 Intel Thermal Solution STS100A (Active Heat Sink Solution) .....................168

9.1.4 Intel Thermal Solution STS100P

(Boxed 25.5 mm Tall Passive Heat Sink Solution)....................................169

9.2 Mechanical Specifications..................................................................................169

9.2.1 Boxed Processor Heat Sink Dimensions and Baseboard Keepout Zones.......170

9.2.2 Boxed Processor Retention Mechanism and Heat Sink

Support (URS)....................... .. .. ................................................... .. .. ..179

9.3 Fan Power Supply [STS100C (Combo) and STS100A (Active) Solutions]....... ...........180

9.3.1 Boxed Processor Cooling Requirements..................................................181

9.4 Boxed Processor Contents.................................................................................183

4 Intel® Xeon® Processor 5600 Series Datasheet Volume 1

Page 5

Figures

2-1 Active ODT for a Differential Link Example............................................................17

2-2 Input Device Hysteresis .....................................................................................18

2-3 VCC Static and Transient Tolerance Loadlines1,2,3,4..............................................35

2-4 VCC Overshoot Example Waveform......................................................................36

2-5 Load Current Versus Time (Frequency Optimized Server/Workstation),2................... 37

2-6 Load Current Versus Time (Advanced Server/Workstation),2................................... 37

2-7 Load Current Versus Time (Standard Server/Workstation),2....................................38

2-8 Load Current Versus Time (Low Power & LV-60W),2...................... .........................38

2-9 Load Current Versus Time (Low Power & LV-40W),2...................... .........................39

2-10 VTT Static and Transient Tolerance Loadlines........................................................40

2-11 Intel QuickPath Interconnect Electrical Test Setup for Validating

Standalone TX Voltage and Timing Parameters......................................................54

2-12 Intel QuickPath Interconnect Electrical Test Setup for Validating

TX + Worst-Case Interconnect Specifications ........................................................55

2-13 Distribution Profile of Common Mode Noise for Either Tx or Rx.................................55

2-14 Distribution Profile of UI-UI Jitter and Accumulated Jitter........................................56

2-15 Eye Mask at the End of Tx + Channel...................................................................56

2-16 Differential Clock Crosspoint Specification.............................................................57

2-17 Differential Clock Measurement Points for Duty Cycle and Period .............................57

2-18 Differential Clock Measurement Points for Rise and Fall time ...................................57

2-19 Single-Ended Clock Measurement Points for Absolute Cross Point and Swing .............58

2-20 Single-Ended Clock Measurement Points for Delta Cross Point ......... ........................ 58

2-21 Differential Clock Measurement Point for Ringback.................................................58

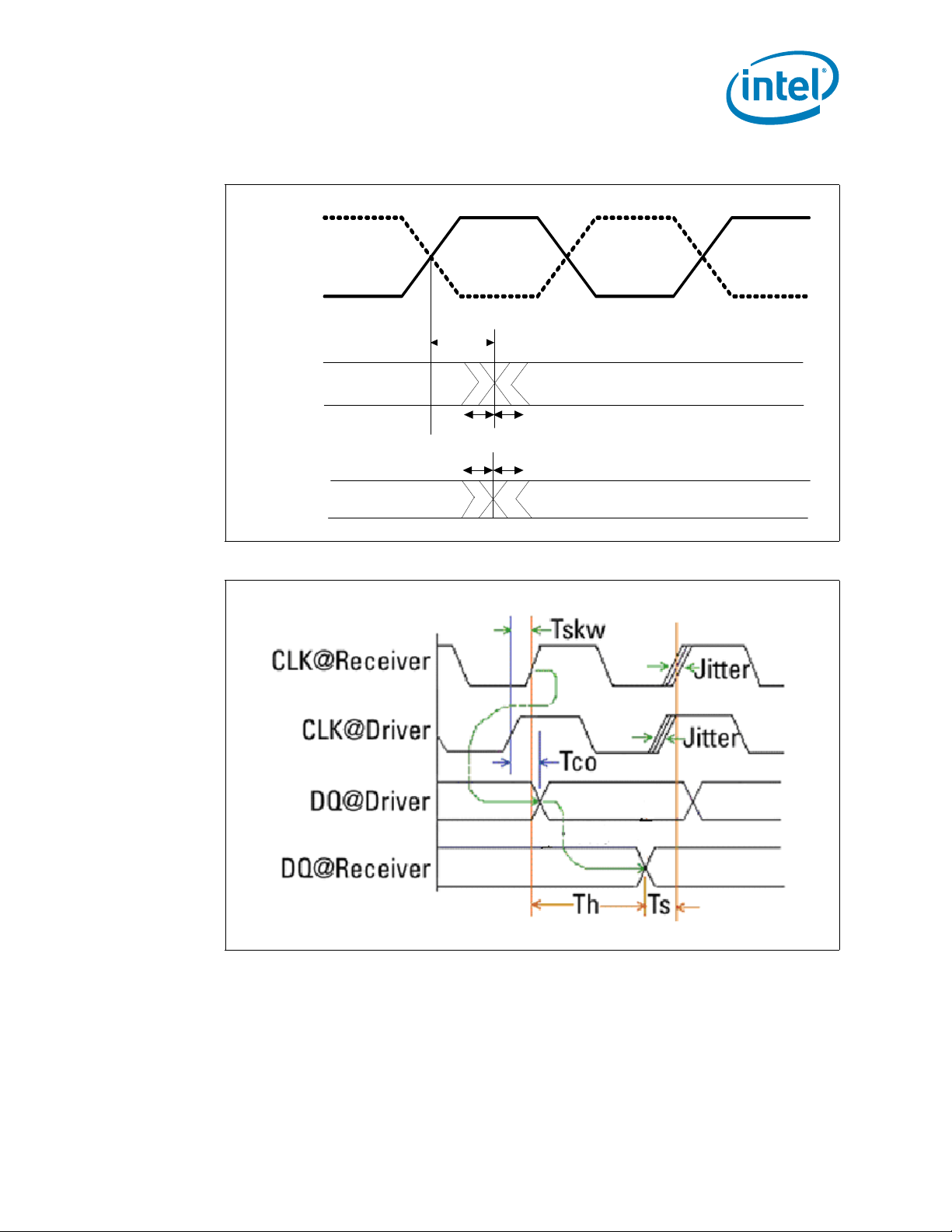

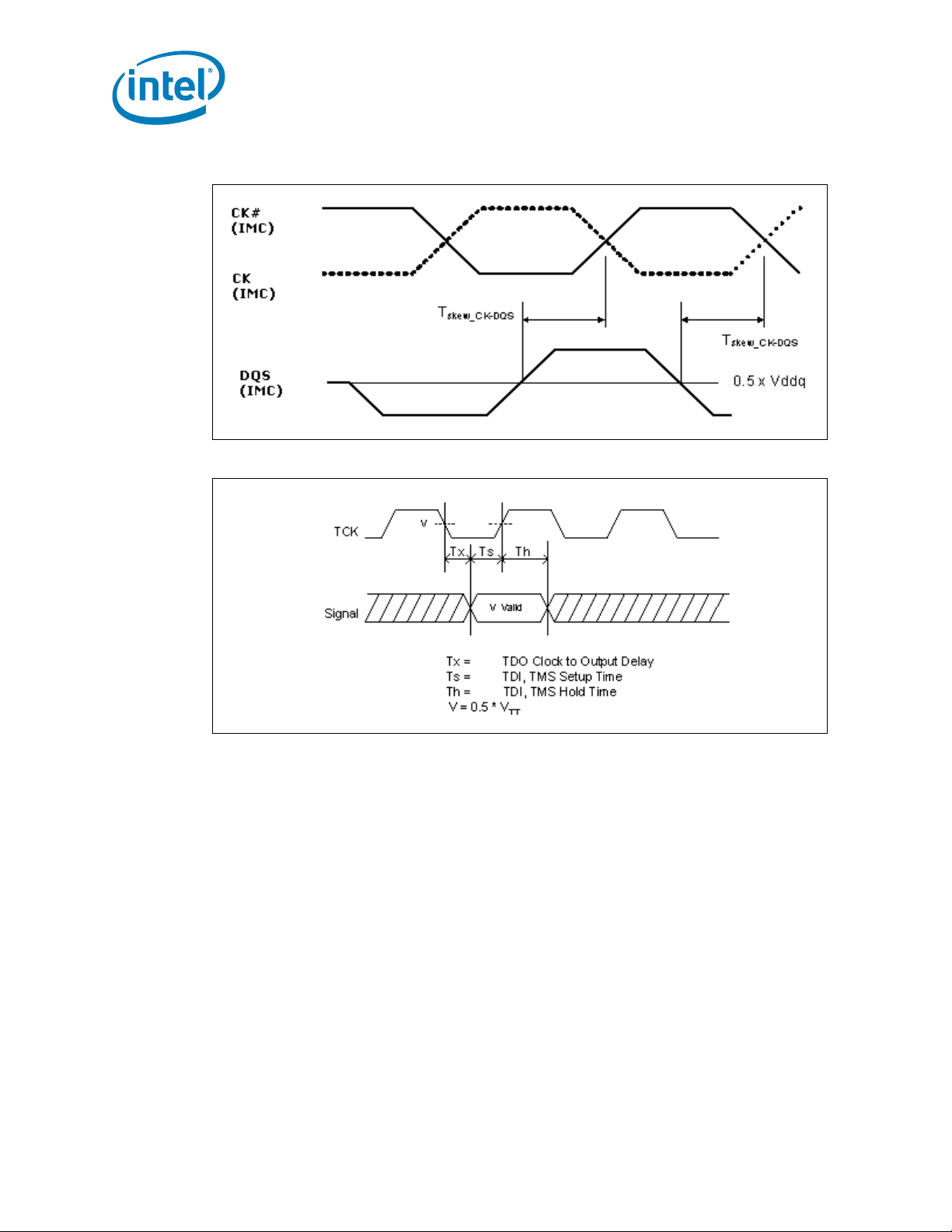

2-22 DDR3 Command / Control and Clock Timing Waveform ..........................................59

2-23 DDR3 Clock to Output Timing Waveform ..............................................................59

2-24 DDR3 Clock to DQS Skew Timing Waveform .........................................................60

2-25 TAP Valid Delay Timing Waveform .......................................................................60

2-26 Test Reset (TRST#), Asynch GTL Input, and PROCHOT# Timing Waveform ............... 61

2-27 THERMTRIP# Power Down Sequence ...................................................................61

2-28 Voltage Sequence Timing Requirements ...............................................................62

2-29 VID Step Times and Vcc Waveforms ....................................................................63

3-1 Maximum Acceptable Overshoot/Undershoot Waveform..........................................66

4-1 Processor Package Assembly Sketch ....................................................................67

4-2 Processor Package Drawing (Sheet 1 of 2)............................................................68

4-3 Processor Package Drawing (Sheet 2 of 2)............................................................69

4-4 Processor Top-Side Markings ..............................................................................71

7-1 Frequency Optimized Server/Workstation Platform Thermal Profile (6 Core) ............ 115

7-2 Frequency Optimized Server/Workstation Platform Thermal Profile (4 Core) ............ 116

7-3 Advanced Server/Workstation Platform Thermal Profile A and B (6 Core) ................ 117

7-4 Advanced Server/Workstation Platform Thermal Profile A and B (4 Core) ................ 119

7-5 Standard Server/Workstation Platform Thermal Profile (6 Core)............................. 121

7-6 Standard Server/Workstation Platform Thermal Profile (4 Core)............................. 122

7-7 Low Power Platform 60W Thermal Profile (6 Core) ............................................... 123

7-8 Low Power Platform 40W Thermal Profile (4 Core) ............................................... 124

7-9 LV-60W Processor Dual Thermal Profile.............................................................. 125

7-10 LV-40W Processor Dual Thermal Profile.............................................................. 127

7-11 Case Temperature (TCASE) Measurement Location............................. .. ............... 128

7-12 Frequency and Voltage Ordering........................................................................ 130

7-13 Ping()............................................................................................................ 134

7-14 Ping() Example............................................................................................... 134

Intel® Xeon® Processor 5600 Series Datasheet Volume 1 5

Page 6

7-15 GetDIB() ........................................................................................................135

7-16 Device Info Field Definition ...............................................................................135

7-17 Revision Number Definition...............................................................................135

7-18 GetTemp()......................................................................................................136

7-19 GetTemp() Example.........................................................................................136

7-20 PCI Configuration Address.................................................................................137

7-21 PCIConfigRd().................................................................................................138

7-22 PCIConfigWr().................................................................................................140

7-23 Thermal Status Word .................... .. ........................... .. ............................ ........142

7-24 Thermal Data Configuration Register ..................................................................143

7-25 Machine Check Read MbxSend() Data Format......................................................143

7-26 ACPI T-State Throttling Control Read / Write Definition.........................................147

7-27 Energy Accumulator Register Definition ..............................................................148

7-28 MbxSend() Command Data Format ............... .. ............................ .. .. .. .................149

7-29 MbxSend()......................................................................................................150

7-30 MbxGet()........................................................................................................151

7-31 Temperature Sensor Data Format ......................................................................155

7-32 PECI Power-Up Timeline ...................................................................................157

8-1 PROCHOT# POC Timing Requirements................................................................161

8-2 Power States........................................................... .. .. .......................... .. .. ......163

9-1 STS100C Passive / Active Combination Heat Sink (with Removable Fan) .................168

9-2 STS100C Passive / Active Combination Heat Sink (with Fan Removed)....................168

9-3 STS100A Active Heat Sink ................................................................................169

9-4 STS100P 25.5 mm Tall Passive Heat Sink............................................................169

9-5 Top Side Baseboard Keep-Out Zones..................................................................171

9-6 Top Side Baseboard Mounting-Hole Keep-Out Zones.............................................172

9-7 Bottom Side Baseboard Keep-Out Zones.............................................................173

9-8 Primary and Secondary Side 3D Height Restriction Zones......................................174

9-9 Volumetric Height Keep-Ins...............................................................................175

9-10 Volumetric Height Keep-Ins...............................................................................176

9-11 4-Pin Fan Cable Connector (For Active Heat Sink) ................................................177

9-12 4-Pin Base Baseboard Fan Header (For Active Heat Sink) ......................................178

9-13 Thermal Solution Installation.............................................................................180

9-14 Fan Cable Connector Pin Out For 4-Pin Ac tive Thermal Solution..............................181

6 Intel® Xeon® Processor 5600 Series Datasheet Volume 1

Page 7

Tables

1-1 Intel® Xeon® Processor 5600 Series Feature Set Overview....................................12

1-2 References.......................................................................................................15

2-1 Processor Power Supply Voltages1.......................................................................19

2-2 Voltage Identification Definition...........................................................................21

2-3 Power-On Configuration (POC[7:0]) Decode..........................................................25

2-4 VTT Voltage Identification Definition ....................................................................26

2-5 Signal Groups....................... .......................... .. .. ......................... .. .. .................27

2-6 Signals With On-Die Termination (ODT).................. .. .. .. .. ............................ .. .. .. ....29

2-7 Processor Absolute Minimum and Maximum Ratings...............................................31

2-8 Voltage and Current Specifications.......................................................................31

2-9 VCC Static and Transient Tolerance.....................................................................34

2-10 VCC Overshoot Specifications..............................................................................35

2-11 VTT Static and Transient Tolerance.....................................................................39

2-12 DDR3 and DDR3L Signal Group DC Specifications ..................................................41

2-13 PECI Signal DC Electrical Limits...........................................................................41

2-14 System Reference Clock DC Specifications............................................................42

2-15 RESET# Signal DC Specifications.........................................................................42

2-16 TAP Signal Group DC Specifications .....................................................................43

2-17 xxxPWRGOOD Signal Group DC Specifications.......................................................43

2-18 Processor Sideband Signal Group DC Specifications................................................43

2-19 Common Intel QuickPath Interconnect Specifications .............................................44

2-20 Parameter Values for Intel QuickPath Interconnect Channels at 4.8 GT/s ..................45

2-21 Parameter Values for Intel QuickPath Interconnect Channel at 5.86 or

6.4 GT/s ..........................................................................................................47

2-22 System Reference Clock AC Specifications .................................................. .. .. .. ....48

2-23 DDR3/DDR3L Electrical Characteristics and AC Specifications at 800 MT/s.................48

2-24 DDR3 Electrical Characteristics and AC Specifications at 1066 MT/s.......................... 49

2-25 DDR3/DDR3L Electrical Characteristics and AC Specifications at 1333 MT/s ............... 51

2-26 Processor Sideband Signal Group AC Specifications................................................52

2-27 TAP Signal Group AC Specifications......................................................................53

2-28 VID Signal Group AC Specifications......................................................................53

3-1 Overshoot/Undershoot Tolerance.........................................................................65

4-1 Processor Loading Specifications .........................................................................70

4-2 Package Handling Guidelines............................. .. ........................... .. .. .................70

4-3 Processor Materials............................................................................................71

5-1 Land Name.......................................................................................................73

5-2 Land Number....................................................................................................90

6-1 Signal Definitions .................................................. .......................................... 109

7-1 Frequency Optimized Server/Workstation Platform Thermal Specifications .............. 114

7-2 Frequency Optimized Server/Workstation Platform Thermal Profile (6 Core) ............ 115

7-3 Frequency Optimized Server/Workstation Platform Thermal Profile (4 Core) ............ 116

7-4 Advanced Server/Workstation Platform Thermal Specifications .............................. 117

7-5 Advanced Server/Workstation Thermal Profile A (6 Core)...................................... 118

7-6 Advanced Server/Workstation Thermal Profile B (6 Core)..................................... 118

7-7 Advanced Server/Workstation Thermal Profile A (4 Core)...................................... 119

7-8 Advanced Server/Workstation Thermal Profile B (4 Core)..................................... 120

7-9 Standard Server/Workstation Platform Thermal Specifications............................... 120

7-10 Standard Server/Workstation Platform Thermal Profile (6 Core)............................. 121

7-11 Standard Server/Workstation Platform Thermal Profile (4 Core)............................. 122

Intel® Xeon® Processor 5600 Series Datasheet Volume 1 7

Page 8

7-12 Low Power Platform 60W Thermal Specifications..................................................123

7-13 Low Power Platform 60W Thermal Profile (6 Core)................................................123

7-14 Low Power Platform 40W Thermal Specifications..................................................124

7-15 Low Power Platform 40W Thermal Profile (4 Core)................................................125

7-16 LV-60W Processor Thermal Specifications............................................................125

7-17 LV-60W Processor Dual Thermal Profile...............................................................126

7-18 LV-40W Processor Thermal Specifications............................................................126

7-19 LV-40W Processor Dual Thermal Profile...............................................................127

7-20 Summary of Processor-Specific PECI Commands..................................................133

7-21 GetTemp() Response Definition ................ ............................ .. .. .. .. .....................137

7-22 PCIConfigRd() Response Definition.....................................................................138

7-23 PCIConfigWr() Device/Function Support..............................................................138

7-24 PCIConfigWr() Response Definition.....................................................................140

7-25 Mailbox Command Summary.............................................................................141

7-26 Counter Definition............................................................................................142

7-27 Machine Check Bank Definitions.........................................................................143

7-28 ACPI T-state Duty Cycle Definition .....................................................................146

7-29 MbxSend() Response Definition ................................................ .. .. .....................150

7-30 MbxGet() Response Definition ...........................................................................151

7-31 Domain ID Definition............................................ .. .. ........................................153

7-32 Multi-Domain Command Code Reference.............................................................153

7-33 Completion Code Pass/Fail Mask........................................................................154

7-34 Device Specific Completion Code (CC) Definition..................................................154

7-35 Originator Response Guidelines.................................................................... .. .. ..155

7-36 Error Codes and Descriptions.............................................................................156

7-37 PECI Client Response During Power-Up (During ‘Data Not Ready’)..........................156

7-38 Storage Condition Ratings.................................................................................158

8-1 Power-On Configuration Signal Options...............................................................161

8-2 Coordination of Thread Power States at the Core Level .........................................163

8-3 Processor C-State Power Specifications...............................................................165

8-4 Processor S-States...........................................................................................166

9-1 PWM Fan Frequency Specifications For 4-Pin Active Thermal Solution......................181

9-2 Fan Specifications For 4-Pin Active Thermal Solution.............................................181

9-3 Fan Cable Connector P in Out for 4-Pin Active Thermal Solution ..............................181

8 Intel® Xeon® Processor 5600 Series Datasheet Volume 1

Page 9

Revision History

Revision

Number

-001 • Initial Release March 2010

-002 • Added Section 1.5: Statement of Volatility June 2011

Description Date

§

Intel® Xeon® Processor 5600 Series Datasheet Volume 1 9

Page 10

10 Intel® Xeon® Processor 5600 Series Datasheet Volume 1

Page 11

Introduction

1 Introduction

The Intel® Xeon® processor 5600 series is a server/workstation multi-core processor

based on 32 nm process technology. The processors feature two Intel® QuickPath

Interconnect point-to-point links capable of up to 6.4 GT/s, up to 12 MB of shared

cache, and an Integrated Memory Controller. The processors are optimized for

performance with the power efficiencies of a low-power microarchitecture to enable

smaller, quieter systems.

This datasheet provides DC and AC electrical specifications, signal integrity, differential

signaling specifications, pinout and signal definitions, package mechanical

specifications and thermal requirements, and additional features pertinent to

implementation and operation of the processor.

The Intel Xeon processor 5600 series features a range of Thermal Design Power (TDP)

envelopes from 40W TDP up to 130W TDP, and is segmented into multiple platforms:

• 2-Socket Frequency Optimized Server/Workstation Platforms support a 130 W

Thermal Design Power (TDP) SKU and up to 6 core support. These platforms

provide optimal overall performance and reliability, in addition to high-end graphics

support.

• 2-Socket Advanced Server/Workstation Platforms support a 95 W Thermal Design

Power (TDP) SKU. These platforms provide optimal overall performance featuring

up to 6 core support.

• 2-Socket Standard Server/Workstation Platforms support 80 W TDP processor

SKUs supporting up to 6 cores. These platforms provide optimal performance per

watt for rack-optimized platforms.

• Low Power Platforms implement 60 W TDP (up to 6 cores) and 40 W TDP (up to 4

cores) processor SKU’s. These processors are intended for dual-processor server

blades and embedded servers.

• 1-Socket Workstation Platforms support Intel® Xeon® Processor W3680. These

platforms enable a wide range of options for either the performance, power, or cost

sensitive customer.

• Platforms supporting Higher Case Temperature Low-Voltage Processors with 60 W

TDP (up to 6 cores) and 40 W TDP (up to 4 cores). The higher case temperatures

are intended to meet the short-term thermal profile requirements of NEBS Level 3.

These 2-socket processors are ideal for thermally-constrained form factors in

embedded servers, communications and storage markets. Specifications denoted

as LV-60W apply to the Intel® Xeon® Processor L5638. Specifications denoted as

LV-40W apply to the Intel® Xeon® Processor L5618.

®

Note: All references to “chipset” in this document pertain to the Intel

Intel® Xeon® Processor 5600 Series Datasheet Volume 1 11

®

5500 chipset.

Intel

Intel is committed to delivering processors for both server and workstation platforms

that maximize performance while meeting all Intel Quality and Reliability goals. The

product’s reliability assessment is based on a datasheet compliant system and

reference use condition. Intel utilizes a broad set of use condition assumptions (that is,

percentage of time in active vs. inactive operation, non-operating conditions, and the

number of power cycles per year) to ensure proper operation over the life of the

5520 chipset and the

Page 12

product. The reference use condition differs between workstation and server processor

SKU’s. Implementing processors outside of reference use conditions may affect

reliability performance.

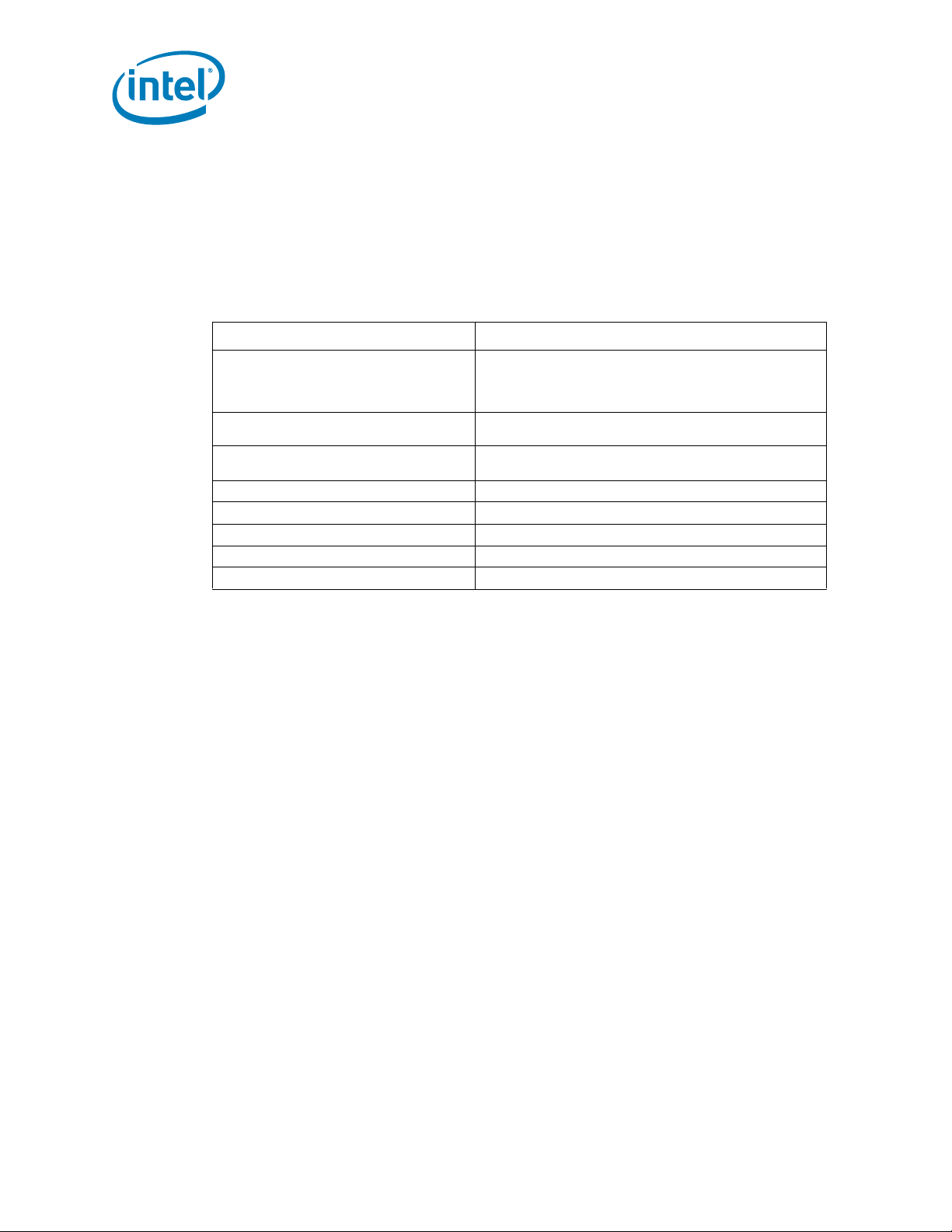

1.1 Processor Features

Introduction

.

Table 1-1 provides an overview the Intel Xeon processor 5600 series feature set.

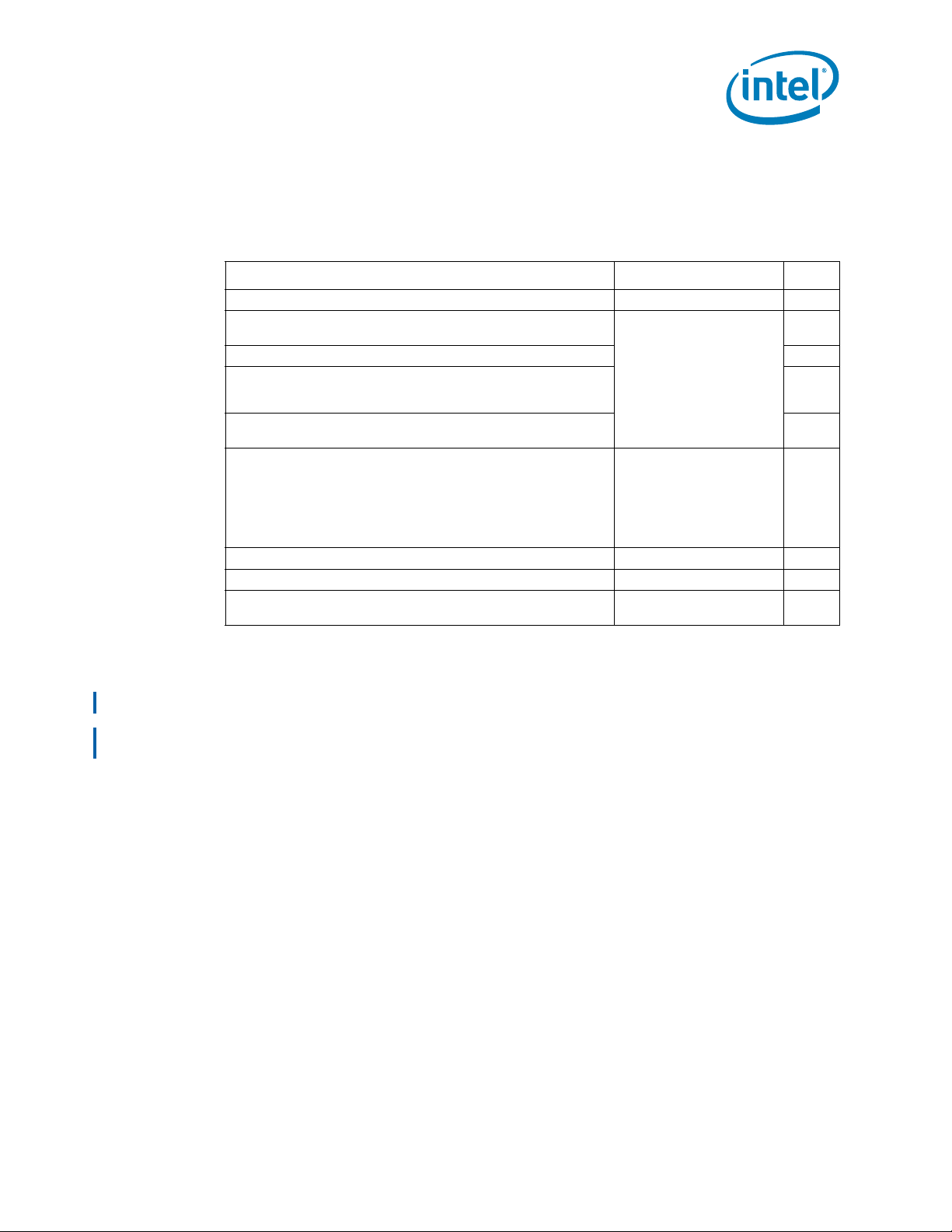

Table 1-1. Intel® Xeon® Processor 5600 Series Feature Set Overview

Feature Intel® Xeon® Processor 5600 Series

Cache Sizes Instruction Cache: 32 kB

12 MB Last-Level Cache shared among all cores

Data Transfer Rate (GT/s) Two full-width Intel® QuickPath Interconnect links;

Memory Support Integrated Memory Controller supports up to 3 channels of

DDR3 Memory Speed (MHz) 800, 1066, 1333

Multi-Core Support Up to 6 cores per processor (package)

®

Intel

Hyper-Threading Technology 2 threads per core

Dual Processor Support Up to 2 processor sockets per platform

Package 1366-land FC-LGA

DDR3 or DDR3L memory, with up to 3 DIMMs per channel

Data Cache: 32 kB

256 kB Mid-Level Cache per core

Up to 6.40 GT/s in each direction

The Intel Xeon processor 5600 series support all the existing Streaming SIMD

Extensions 2 (SSE2), Streaming SIMD Extensions 3 (SSE3) and Streaming SIMD

Extensions 4 (SSE4) instructions. Additionally, Intel Xeon processor 5600 series

support Intel® AES New Instructions (Intel® AES-NI).

The Intel Xeon processor 5600 series support Direct Cache Access (DCA). DCA enables

supported I/O adapter to pre-fetch data from memory to the processor cache, thereby

avoiding cache misses and improving application response times.

These processors support a maximum physical address size of 40 bits. Also supported

is IA-32e paging which adds support for 1 GB (2

4 kB page size support for linear to physical address translation.

Finally, these processors support several advanced technologies including Execute

Disable Bit, Intel

®

64 Technology, Enhanced Intel SpeedStep® Technology, Intel®

Virtualization Technology (Intel® VT), Intel® Hyper-Threading Technology, and Intel®

Turbo Boost Technology.

1.2 Platform Features

Various new component and platform capabilities are available with the implementation

of Intel Xeon processor 5600 series.

New memory subsystem capabilities include Low Voltage DDR3 (DDR3L) DIMM support

for power optimization. The Intel Xeon processor 5600 series also add features to

provide improved manageability of memory channels. The DDR_THERM2# signal has

been added to support high-temperature DIMMs and their 2X refresh requirements.

12 Intel

30

) page size in addition to 2 MB and

®

Xeon® Processor 5600 Series Datasheet Volume 1

Page 13

Introduction

Intel Xeon processor 5600 series are based on a low-power microarchitecture that

supports operation within various C-states. Additionally, six execution cores and power

management coordination logic are optimized to manage C-state support at both the

execution core and package levels. An Intel Turbo Boost Technology optimization

feature is supported on these processors for improved energy efficiency.

®

Trusted Execution Technology (Intel® TXT) is also supported and represents a

Intel

set of enhanced hardware components designed to help protect sensitive information

from software-based attacks. Features include capabilities in the microprocessor,

chipset, I/O subsystems, and other platform components. When coupled with suitably

enabled operating systems and applications, Intel TXT helps protect the confidentiality

and integrity of data in the face of increasingly hostile security environment.

1.3 Terminology

A ‘#’ symbol after a signal name refers to an active low signal, indicating a signal is in

the active state when driven to a low voltage level. For example, when RESET# is low,

a reset has been requested.

A ‘_N’ and ‘_P’ after a signal name refers to a differential pair.

Commonly used terms are explained here for clarification:

• 1366-land FC-LGA package — The Intel Xeon processor 5600 series is available

in a Flip-Chip Land Grid Array (FC-LGA) package, consisting of processor mounted

on a land grid array substrate with an integrated heat spreader (IHS).

• DDR3 — Double Data Rate 3 synchronous dynamic random access memory

(SDRAM) is the DDR memory standard, developed as the successor to DDR2

SDRAM.

• Enhanced Intel SpeedStep

Technology allows the operating system to reduce power consumption when

performance is not needed.

• Execute Disable Bit — Execute Disable allows memory to be marked as

executable or non-executable, when combined with a supporting operating system.

If code attempts to run in non-executable memory the processor raises an error to

the operating system. This feature can prevent some classes of viruses or worms

that exploit buffer over run vulnerabilities and can thus help improve the overall

security of the system. See the Intel

Developer's Manuals for more detailed information.

• Functional Operation — Refers to the normal operating conditions in which all

processor specifications, including DC, AC, signal quality , m echanical, and thermal,

are satisfied.

• Integrated Memory Controller (IMC) — This is a memory controller that is

integrated in the processor die. Intel Xeon processor 5600 series can support up to

3 channels of DDR3, DDR3L memory , with up to 3 DIMMs per channel. Please refer

to Intel Plan of Record for supported DIMM types, densities and configurations.

®

• Intel

faster than the marked frequency if the part is operating under power,

temperature, and current specification limits of the Thermal Design Power (TDP).

This results in increased performance of both single and multi-threaded

applications.

• Intel

extensions to Intel processors and chipsets that, with appropriate software,

enhance the platform security capabilities.

Turbo Boost Technology - A way to automatically run the processor core

®

Trusted Execution Technology - A highly versatile set of hardware

®

Technology — Enhanced Intel SpeedStep®

®

64 and IA-32 Architecture Software

Intel® Xeon® Processor 5600 Series Datasheet Volume 1 13

Page 14

Introduction

• Intel® QuickPath Interconnect (Intel® QPI) — A cache-coherent, links-based

interconnect specification for Intel processors, chipsets, and I/O bridge

components.

• Intel® 64 Architecture — An enhancement to Intel's IA-32 architec ture, allowing

the processor to execute operating systems and applications written to take

advantage of Intel

®

64.

• Intel® Virtualization Technology (Intel® VT) — A set of hardware

enhancements to Intel server and client platforms that can improve virtualization

solutions. VT provides a foundation for widely-deployed virtualization solutions and

enables more robust hardware assisted virtualization solution.

• Integrated Heat Spreader (IHS) — A component of the processor package used

to enhance the thermal performance of the package. Component thermal solutions

interface with the processor at the IHS surface.

• Jitter — Any timing variation of a transition edge or edges from the defined Unit

Interval (UI).

• LGA1366 Socket — The 1366-land FC-LGA package mates with the system board

through this surface mount, 1366-contact socket.

• Network Equipment Building System (NEBS) — The most common set of

environmental design guidelines applied to telecommunications equipment in the

United States.

• Serve r SKU — A processor Stock Keeping Unit (SKU) to be installed in either

server or workstation platforms. Electrical, power and thermal specifications for

these SKU’s are based on specific use condition assumptions. Server processors

may be further categorized as Frequency Optimized, Advanced, Standard and Low

Power SKUs. For further details on use condition assumptions, please refer to the

latest Product Release Qualification (PRQ) Report available via your Customer

Quality Engineer (CQE) contact.

• Storage Conditions — Refers to a non-operational state. The processor may be

installed in a platform, in a tray , or loose. Processors ma y be sealed in packaging or

exposed to free air. Under these conditions, processor lands should not be

connected to any supply voltages, have any I/Os biased, or receive any clocks.

• Unit Interval (UI) — Signaling convention that is binary and unidirectional. In

this binary signaling, one bit is sent for every edge of the forwarded clock, whether

it be a rising edge or a falling edge. If a number of edges are collected at instances

, t2, tn,...., tk then the UI at instance “n” is defined as:

t

1

UI n = t n - t

• Workstation SKU — A processor SKU to be installed in workstation platforms

only. Electrical, power and thermal specifications for these processors have been

developed based on Intel’s reliability goals at a reference use condition. In addition,

the processor validation and production test conditions have been optimized based

on these conditions. Operating “Workstation” processors in a server environment or

other application, could impact reliability performance, which means Intel’s

reliability goals may not be met. For further details on use condition assumptions or

reliability performance, please refer to the latest Product Release Qualification

(PRQ) Report available via your Customer Quality Engineer (CQE) contact.

14 Intel

n - 1

®

Xeon® Processor 5600 Series Datasheet Volume 1

Page 15

Introduction

1.4 References

Platform designers are strongly encouraged to maintain familiarity with the most up-todate revisions of processor and platform collateral.

Table 1-2. References

Advanced Configuration and Power Interface Specification www.acpi.info.

Compact Electronics Bay Specification: A Server System

Infrastructure (SSI) Specification for Value Servers and Workstations

Electronics Bay Specification for 2008 Servers and Workstation

Entry-Level Electronics-Bay Specifications: A Server System

Infrastructure (SSI) Specification for Entry Pedestal Servers and

Workstations

Thin Electronics Bay Specification: A Server System Infrastructure

(SSI) Specification for Rack-Optimized Servers

®

Intel

64 and IA-32 Architecture Software Developer's Manual

• Volume 1: Basic Architecture

• Volume 2A: Instruction Set Reference, A-M

• Volume 2B: Instruction Set Reference, N-Z

• Volume 3A: System Programming Guide, Part 1

• Volume 3B: Systems Programming Guide, Part 2

®

64 and IA-32 Architectures Optimization Reference Manual 248966 1

Intel

®

Intel

Xeon® Processor 5600 Series Datasheet, Volume 2 323370 1

®

Intel

Xeon® Processor 5500/5600 Series Thermal/Mechanical

Design Guide

Document Location / Document#1Notes

www.ssiforum.org

1

253665

253666

253667

253668

253669

321323 1

Notes:

1. Document is available publicly at http://www.intel.com.

1.5 Statement of Volatility

No Intel Xeon processor 5600 series product family processors retain any end user data

when powered down and/or when the parts are physically removed from the socket.

§

Intel® Xeon® Processor 5600 Series Datasheet Volume 1 15

Page 16

Introduction

16 Intel

®

Xeon® Processor 5600 Series Datasheet Volume 1

Page 17

Electrical Specifications

T

X

R

X

R

TT

R

TT

R

TT

R

TT

Signal

Signal

2 Electrical Specifications

2.1 Processor Signaling

The Intel Xeon processor 5600 series include 1366 lands, which utilize various signaling

technologies. Signals are grouped by electrical characteristics and buffer type into

various signal groups. These include Intel QuickPath Interconnect, DDR3 (Reference

Clock, Command, Control, and Data), Platform Environmental Control Interface (PECI),

Processor Sideband, System Reference Clock, Test Access Port (TAP), and Power/Other

signals. Refer to Table 2-5 for details.

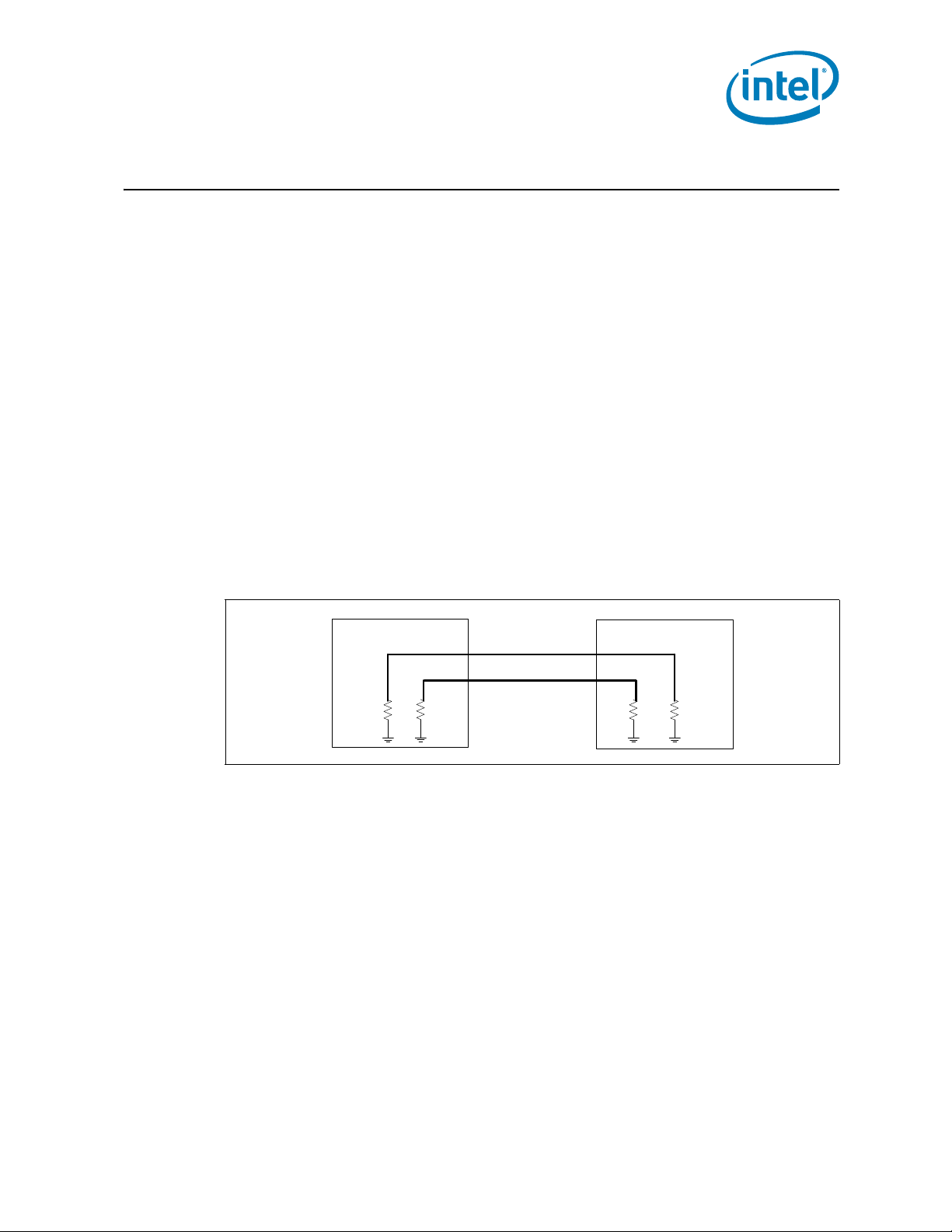

2.1.1 Intel® QuickPath Interconnect

The Intel Xeon processor 5600 series provide two Intel QuickPath Interconnect ports

for high speed serial transfer between other enabled components. Each port consists of

two uni-directional links (for transmit and receive). A differential signaling scheme is

utilized, which consists of opposite-polarity (D_P, D_N) signal pairs.

On-die termination (ODT) is included on the processor silicon and terminated to V

Intel chipsets also provide ODT, thus eliminating the need to terminate on the system

board. Figure 2-1 illustrates the active ODT.

Figure 2-1. Active ODT for a Differential Link Example

2.1.2 DDR3 Signal Groups

The memory interface utilizes DDR3 technology, which consists of numerous signal

groups. These include: Reference Clocks, Command Signals, Control Signals, and Data

Signals. Each group consists of numerous signals, which may utilize various signaling

technologies. Please refer to Table 2-5 for further details.

2.1.3 Platform Environmental Control Interface (PECI)

PECI is an Intel proprietary interface that provides a communication channel between

Intel processors and chipset components to external thermal monitoring devices. The

processor contains a Digital Thermal Sensor (DTS) that reports a relative die

temperature as an offset from Thermal Control Circuit (TCC) activation temperature.

Temperature sensors located throughout the die are implemented as analog-to-digital

converters calibrated at the factory. PECI provides an interface for external devices to

read processor temperature, perform processor manageability functions, and manage

processor interface tuning and diagnostics. Please refer to Section 7.3 for processor

specific implementation details for PECI.

SS

.

Intel® Xeon® Processor 5600 Series Datasheet Volume 1 17

Page 18

Electrical Specifications

Minimum V

P

Maximum V

P

Minimum V

N

Maximum V

N

PECI High Range

PECI Low Range

Valid Input

Signal Range

Minimum

Hysteresis

V

TTD

PECI Ground

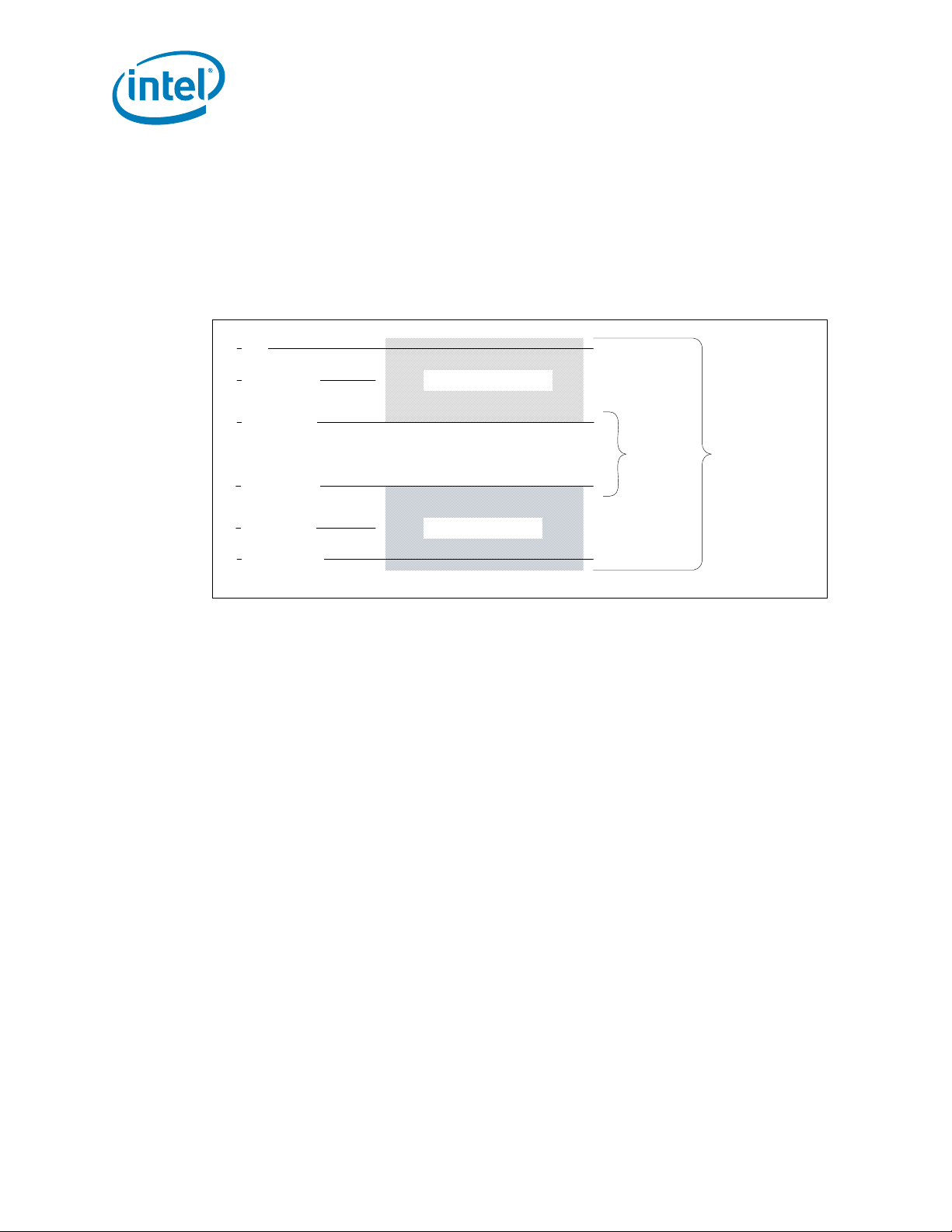

The PECI interface operates at a nominal voltage set by V

specifications shown in Table 2-13 is used with devices normally operating from a V

interface supply.

2.1.3.1 Input Device Hysteresis

The PECI client and host input buffers must use a Schmitt-triggered input design for

improved noise immunity. Pl ease refer to Figure 2-2 and Table 2-13.

Figure 2-2. Input Device Hysteresis

. The set of DC electrical

TTD

TTD

2.1.4 Processor Sideband Signals

Intel Xeon processor 5600 series include sideband signals that provide a variety of

functions. Details can be found in Table 2-5.

All Asynchronous Processor Sideband signals are required to be asserted/deasserted

for at least eight BCLKs in order for the processor to recognize the proper signal state.

See Table 2-18 and Table 2-26 for DC and AC specifications, respectively. Refer to

Section 3 for applicable signal integrity specifications.

2.1.5 System Reference Clock

The processor core, processor uncore, Intel QuickPath Interconnect link, and DDR3

memory interface frequencies are generated from BCLK_DP and BCLK_DN signals.

There is no direct link between core frequency and Intel QuickPath Interconnect link

frequency (for example, no core frequency to Intel QuickPath Interconnect multiplier).

The processor maximum core frequency, Intel QuickPath Interconnect link frequency

and DDR memory frequency are set during manufacturing. It is possible to override the

processor core frequency setting using software. This permits operation at lower core

frequencies than the factory set maximum core frequency.

The processor core frequency is configured during reset by using values stored within

the device during manufacturing. The stored value sets the lowest core multiplier at

which the particular processor can operate. If higher speeds are desired, the

appropriate ratio can be configured via the IA32_PERF_CTL MSR (MSR 199h); Bits

[15:0].

18 Intel

®

Xeon® Processor 5600 Series Datasheet Volume 1

Page 19

Electrical Specifications

Clock multiplying within the processor is provided by the internal phase locked loop

(PLL), which requires a constant frequency BCLK_DP, BCLK_DN input, with exceptions

for spread spectrum clocking. DC specifications for the BCLK_DP, BCLK_DN inputs are

provided in Table 2-14 and AC specifications in Table 2-22. These specifications must

be met while also meeting the associated signal quality specifications outlined in

Section 3.

2.1.6 Test Access Port (TAP) Signals

Due to the voltage levels supported by other components in the Test Access Port (TAP)

logic, it is recommended that the processor(s) be first in the TAP chain and followed by

any other components within the system. A translation buffer should be used to

connect to the rest of the chain unless one of the other components is capable of

accepting an input of the appropriate voltage. Similar considerations must be made for

TCK, TDO, TMS, and TRST#. Two copies of each signal may be required with each

driving a different voltage level.

Processor TAP signal DC specifications can be found in Table 2-18. AC specifications are

located in Table 2-27.

Note: While TDI, TMS and TRST# do not include On-Die Termination (OD T), these signals are

weakly pulled-up via a 1-5 kΩ resistor to V

TT

.

Note: While TCK does not include ODT, this signal is weakly pulled-down via a

1-5 kΩ resistor to V

SS

.

2.1.7 Power / Other Signals

Processors also include various other signals including power/ground, sense points, and

analog inputs. Details can be found in Table 2-5.

Table 2-1 outlines the required voltage supplies necessary to support Intel Xeon

processor 5600 series.

Table 2-1. Processor Power Supply Voltages

Power Rail Nominal Voltage Notes

V

CC

V

CCPLL

V

DDQ

V

, V

TTA

TTD

See Table 2-9;

Figure 2-3

1.80 V

1.50 V

1.35 V

See Table 2-11;

Figure 2-10

1

Each processor includes a dedicated VR11.1 regulator.

Each processor includes dedicated V

Each processor and DDR3 / DDR3L stack shares a dedicated voltage

regulator. It is expected that regulators will support both 1.50 and

1.35 V.

Each processor includes a dedicated VR11.0 regulator.

= V

+ V

V

TT

TTA

VID range is 1.025-1.2000 V; 20 mV offset (see Table 2-4); V

represents a typical voltage. V

31.5 mV offset from V

; P1V1_Vtt is VID[4:2] controlled,

TTD

TT_MIN

(typ).

TT

and PLL circuits.

CCPLL

and V

TT_MAX

loadlines represent a

TT

Note:

1. Refer to Table 2-8 for voltage and current specifications.

2.1.7.1 Power and Ground Lands

For clean on-chip power distribution, processors include lands for all required voltage

supplies. These include:

Intel® Xeon® Processor 5600 Series Datasheet Volume 1 19

Page 20

Electrical Specifications

•210 each VCC (271 ea. VSS) lands must be supplied with the voltage determined by

the VID[7:0] signals. Table 2-2 defines the voltage level associated with each core

VID pattern. Table 2-9 and Figure 2-3 represent V

•3 each V

lands, connected to a 1.8 V supply, power the Phase Lock Loop (PLL)

CCPLL

static and transient limits.

CC

clock generation circuitry. An on-die PLL filter solution is implemented within the

processor.

• 45 eac h V

(17 ea. VSS) lands, connected to a 1.50 / 1.35 V supply, provide

DDQ

power to the processor DDR3 interface. This supply also powers the DDR3 memory

subsystem.

•7 each V

(5 ea. VSS) and 26 ea. V

TTA

(17 ea. VSS) lands must be supplied with

TTD

the voltage determined by the VTT_VID[4:2] signals. Coupled with a 20 mV offset,

this corresponds to a VTT_VID pattern of ‘010xxx10’. Table 2-4 specifies the

voltage levels associated with each VTT

represent V

static and transient limits.

TT

VID pattern. Table 2-11 and Figure 2-10

_

All VCC, V

CCPLL, VDDQ, VTTA

, and V

lands must be connected to their respective

TTD

processor power planes, while all VSS lands must be connected to the system ground

plane.

2.1.7.2 Decoupling Guidelines

Due to its large number of transistors and high internal clock speeds, the processor is

capable of generating large current swings between low and full power states. This may

cause voltages on power planes to sag below their minimum values if bulk decoupling is

not adequate. Larger bulk storage (C

), such as electrolytic capacitors, supply

BULK

current during longer lasting changes in current demand, for example coming out of an

idle condition. Similarly, they act as a storage well for current when entering an idle

condition from a running condition. Care must be taken in the baseboard design to

ensure that the voltages provided to the processor remain within the specifications

listed in Table 2-8. Failure to do so can result in timing violations or reduced lifetime of

the processor.

2.1.7.3 Processor VCC Voltage Identification (VID) Signals

The voltage set by the VID signals is the maximum reference voltage regulator (VR)

output to be delivered to the processor VCC lands. VID signals are CMOS push/pull

outputs. Please refer to Table 2-18 for the DC specifications for these signals.

Individual processor VID values may be calibrated during manufacturing such that two

devices at the same core frequency may have different default VID settings.

The processor uses eight voltage identification signals, VID[7:0], to support automatic

selection of power supply voltages. Table 2-2 specifies the voltage level corresponding

to the state of VID[7:0]. A ‘1’ in this table refers to a high voltage level and a ‘0’ refers

to a low voltage level. If the processor socket is empty (SKTOCC# pulled high), or the

voltage regulation circuit cannot supply the voltage that is requested, the voltage

regulator must disable itself.

The processor provides the ability to operate while transitioning to an adjacent VID and

its associated processor core voltage (V

). This is represented by a DC shift in the

CC

loadline. It should be noted that a low-to-high or high-to-low voltage state change may

result in as many VID transitions as necessary to reach the target core voltage.

T ransitions abov e the maximum specified VID are not permitted. Table 2-8 includes VID

step sizes and DC shift ranges. Minimum and maximum voltages must be maintained

as shown in Table 2-9.

20 Intel

®

Xeon® Processor 5600 Series Datasheet Volume 1

Page 21

Electrical Specifications

The VRM or EVRD utilized must be capable of regulating its output to the value defined

by the new VID. DC specifications for dynamic VID transitions are included in

Table 2-18, while AC specifications are included in Table 2-28.

Power source characteristics must be guaranteed to be stable whenever the supply to

the voltage regulator is stable.

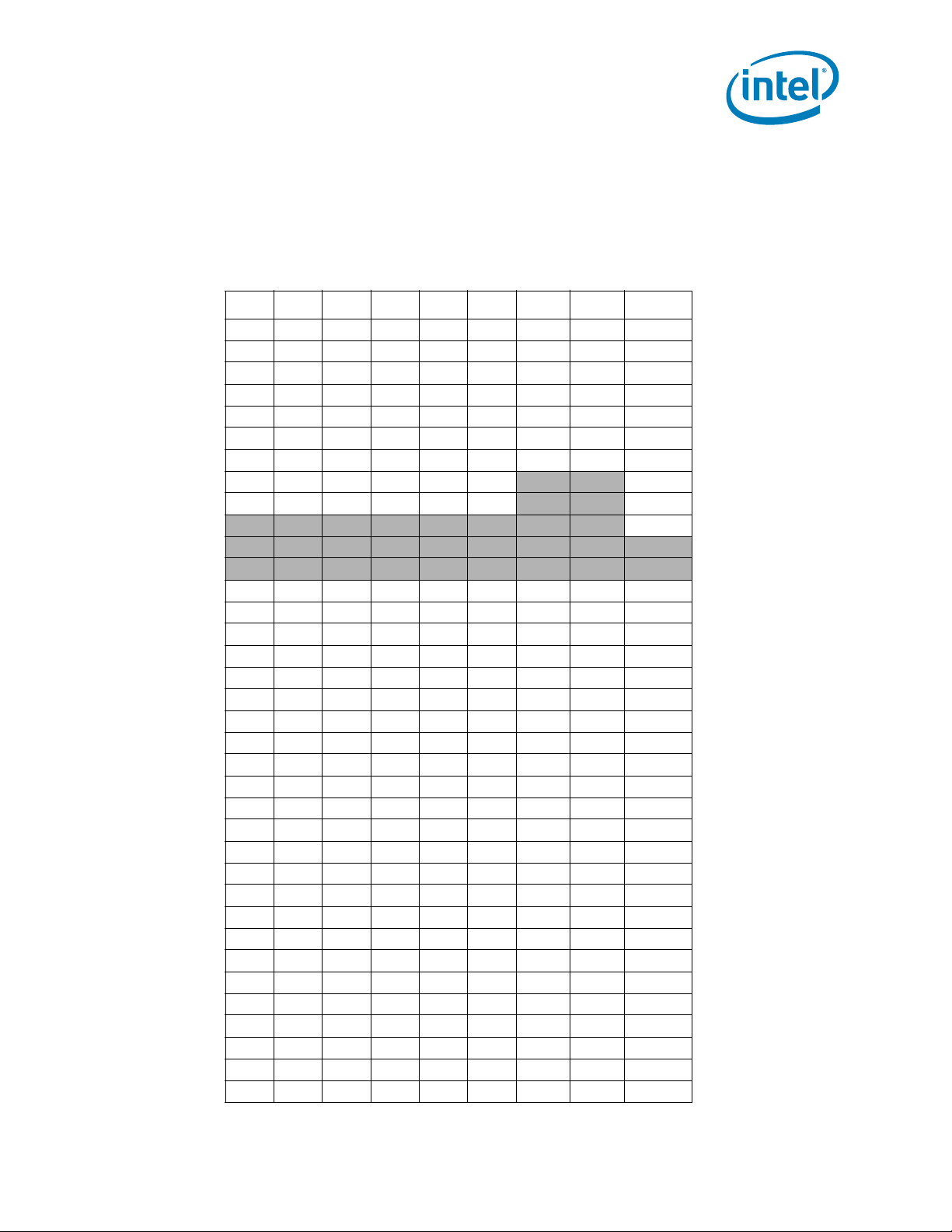

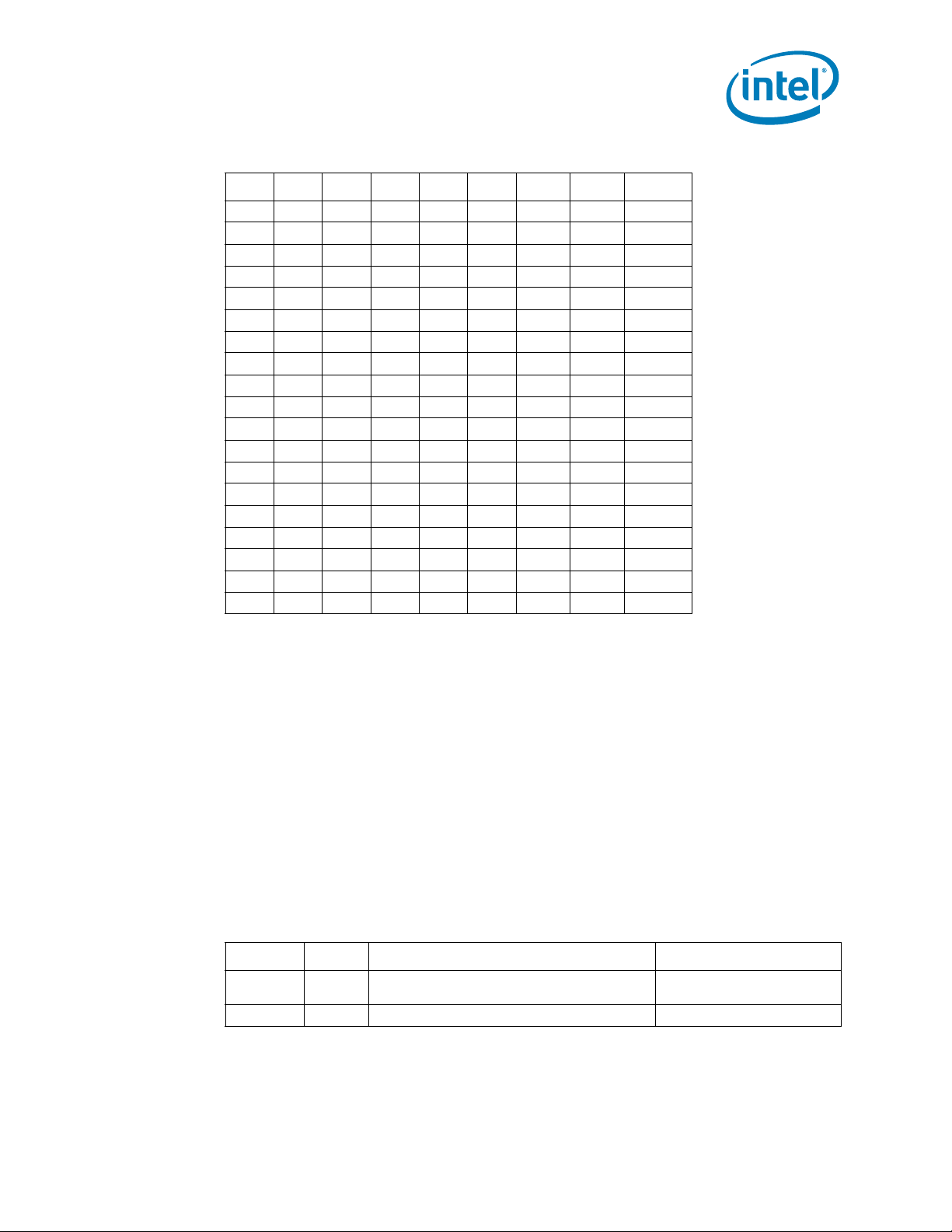

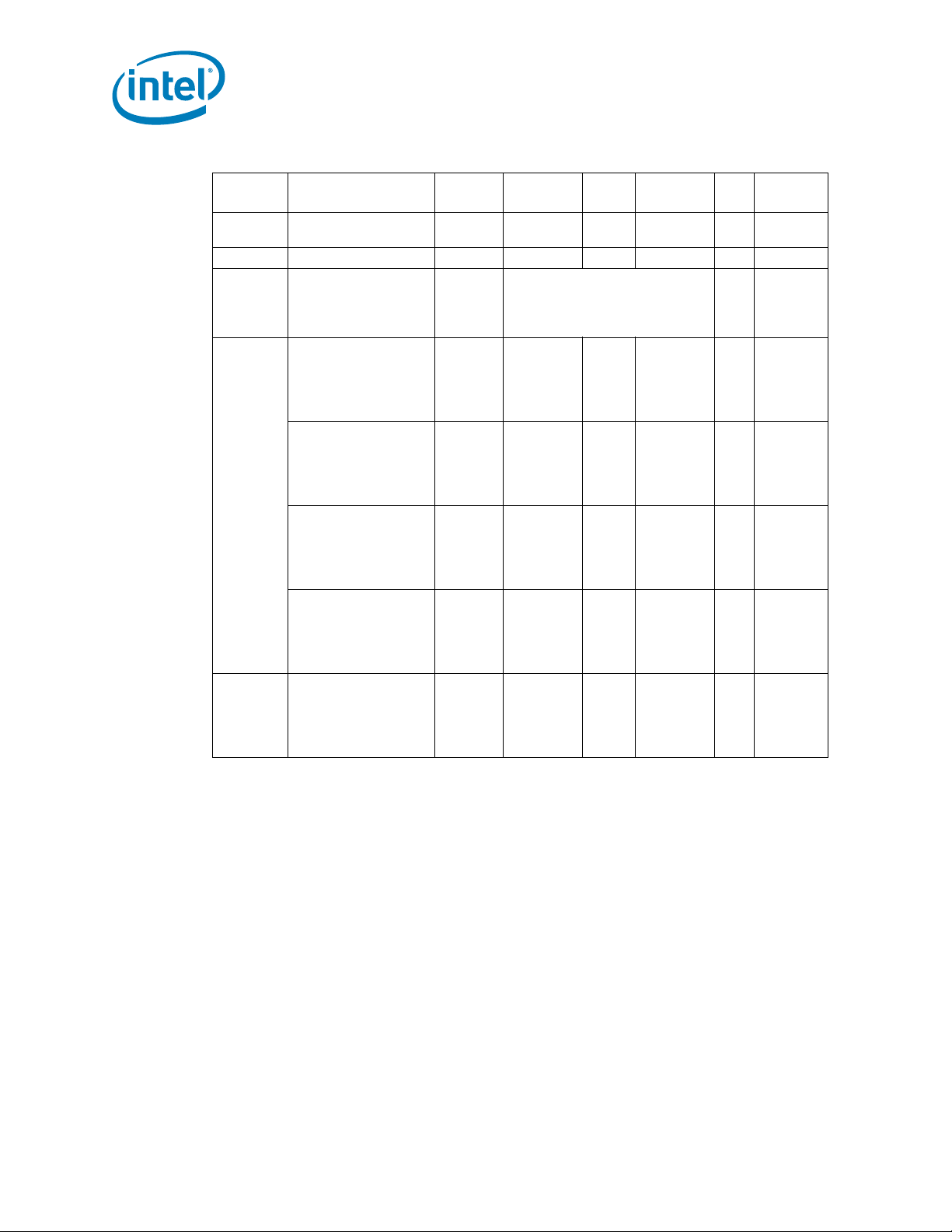

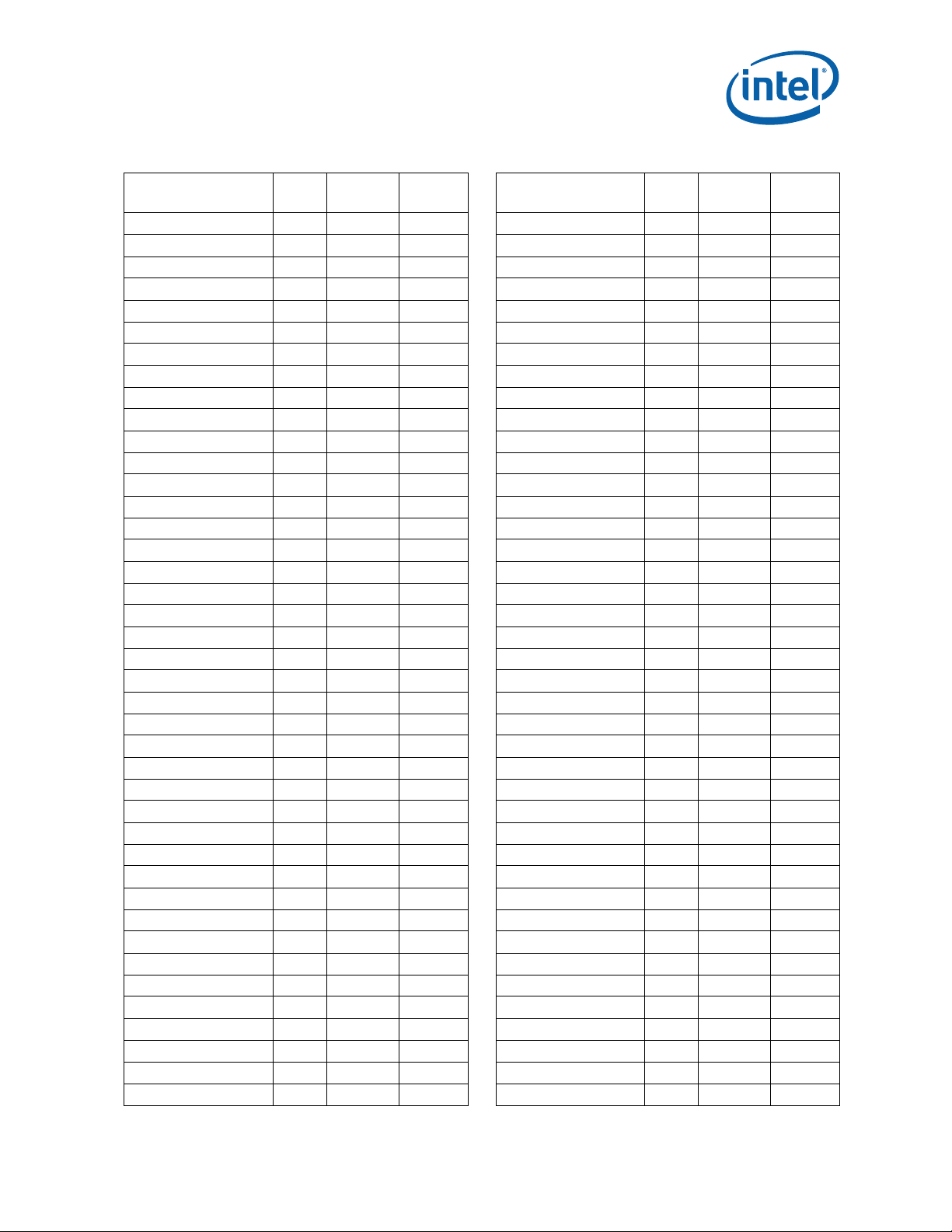

Table 2-2. Voltage Identification Definition (Sheet 1 of 5)

VID7 VID6 VID5 VID4 VID3 VID2 VID1 VID0 V

000000 0 0 OFF

000000 0 1 OFF

000000 1 01.60000

000000 1 11.59375

000001 0 01.58750

000001 0 11.58125

000001 1 01.57500

000001

000010

0 0 0 0 1 0 0 1 1.55625

0 0 0 0 1 0 1 0 1.55000

0 0 0 0 1 0 1 1 1.54375

000011 0 01.53750

000011 0 11.53125

000011 1 01.52500

000011 1 11.51875

000100 0 01.51250

000100 0 11.50625

000100 1 01.50000

000100 1 11.49375

000101 0 01.48750

000101 0 11.48125

000101 1 01.47500

000101 1 11.46875

000110 0 01.46250

000110 0 11.45625

000110 1 01.45000

000110 1 11.44375

000111 0 01.43750

000111 0 11.43125

000111 1 01.42500

000111 1 11.41875

001000 0 01.41250

001000 0 11.40625

001000 1 01.40000

001000 1 11.39375

1 1 1.56875

0 0 1.56250

CC_MAX

Intel® Xeon® Processor 5600 Series Datasheet Volume 1 21

Page 22

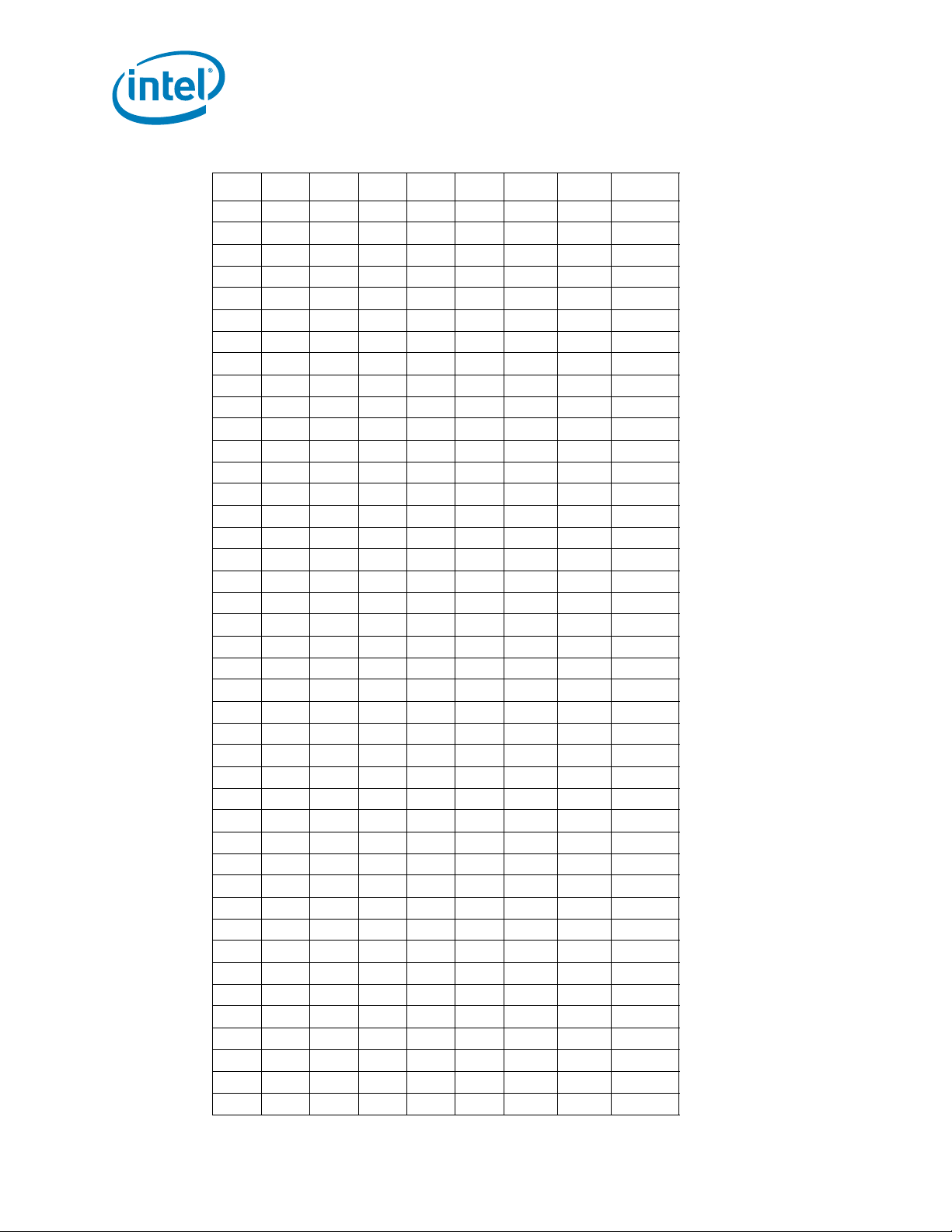

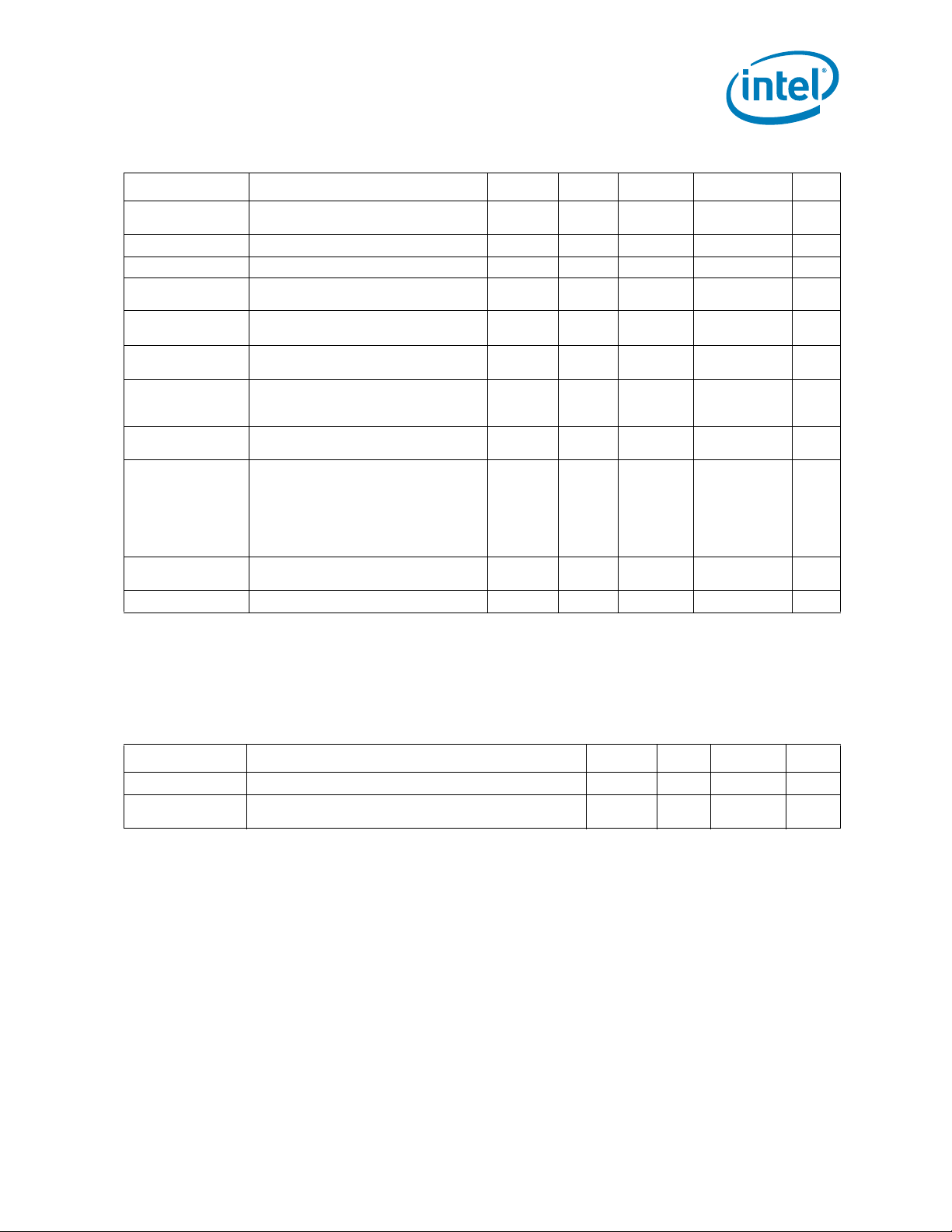

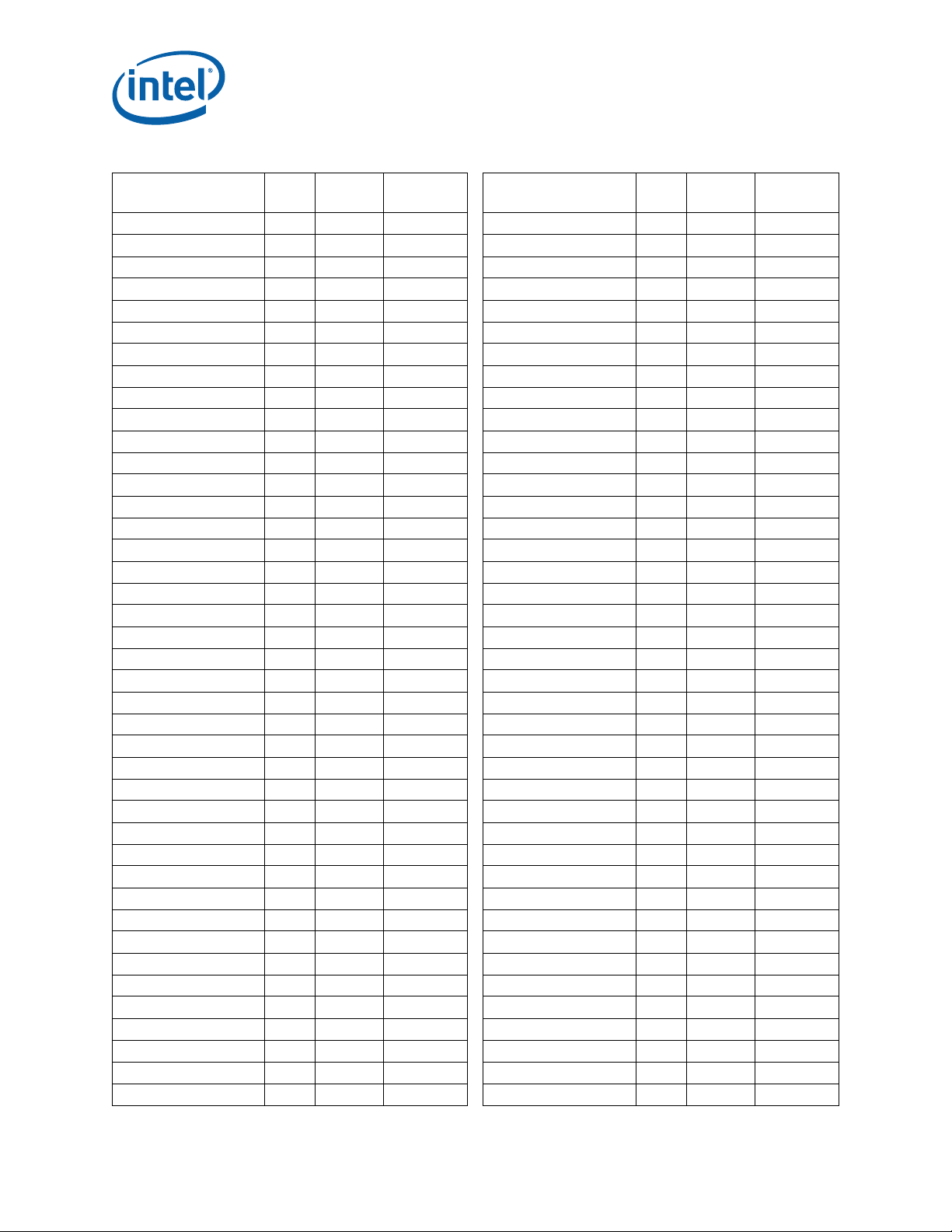

Table 2-2. Voltage Identification Definition (Sheet 2 of 5)

Electrical Specifications

VID7 VID6 VID5 VID4 VID3 VID2 VID1 VID0 V

CC_MAX

001001 0 01.38750

001001 0 11.38125

001001 1 01.37500

001001 1 11.36875

001010 0 01.36250

001010 0 11.35625

001010 1 01.35000

001010 1 11.34375

001011 0 01.33750

001011 0 11.33125

001011 1 01.32500

001011 1 11.31875

001100 0 01.31250

001100 0 11.30625

001100 1 01.30000

001100 1 11.29375

001101 0 01.28750

001101 0 11.28125

001101 1 01.27500

001101 1 11.26875

001110 0 01.26250

001110 0 11.25625

001110 1 01.25000

001110 1 11.24375

001111 0 01.23750

001111 0 11.23125

001111 1 01.22500

001111 1 11.21875

010000 0 01.21250

010000 0 11.20625

010000 1 01.20000

010000 1 11.19375

010001 0 01.18750

010001 0 11.18125

010001 1 01.17500

010001 1 11.16875

010010 0 01.16250

010010 0 11.15625

010010 1 01.15000

010010 1 11.14375

010011 0 01.13750

010011 0 11.13125

22 Intel

®

Xeon® Processor 5600 Series Datasheet Volume 1

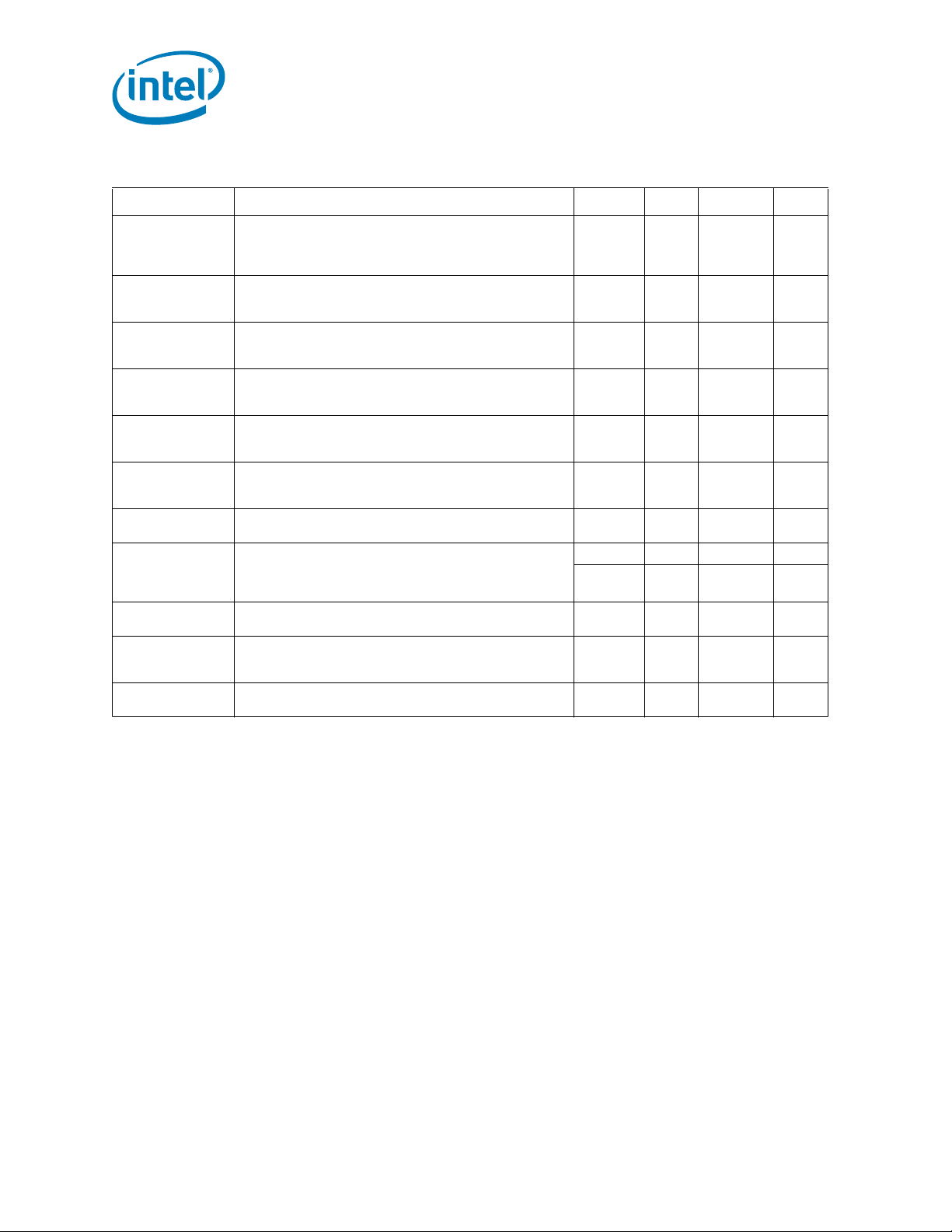

Page 23

Electrical Specifications

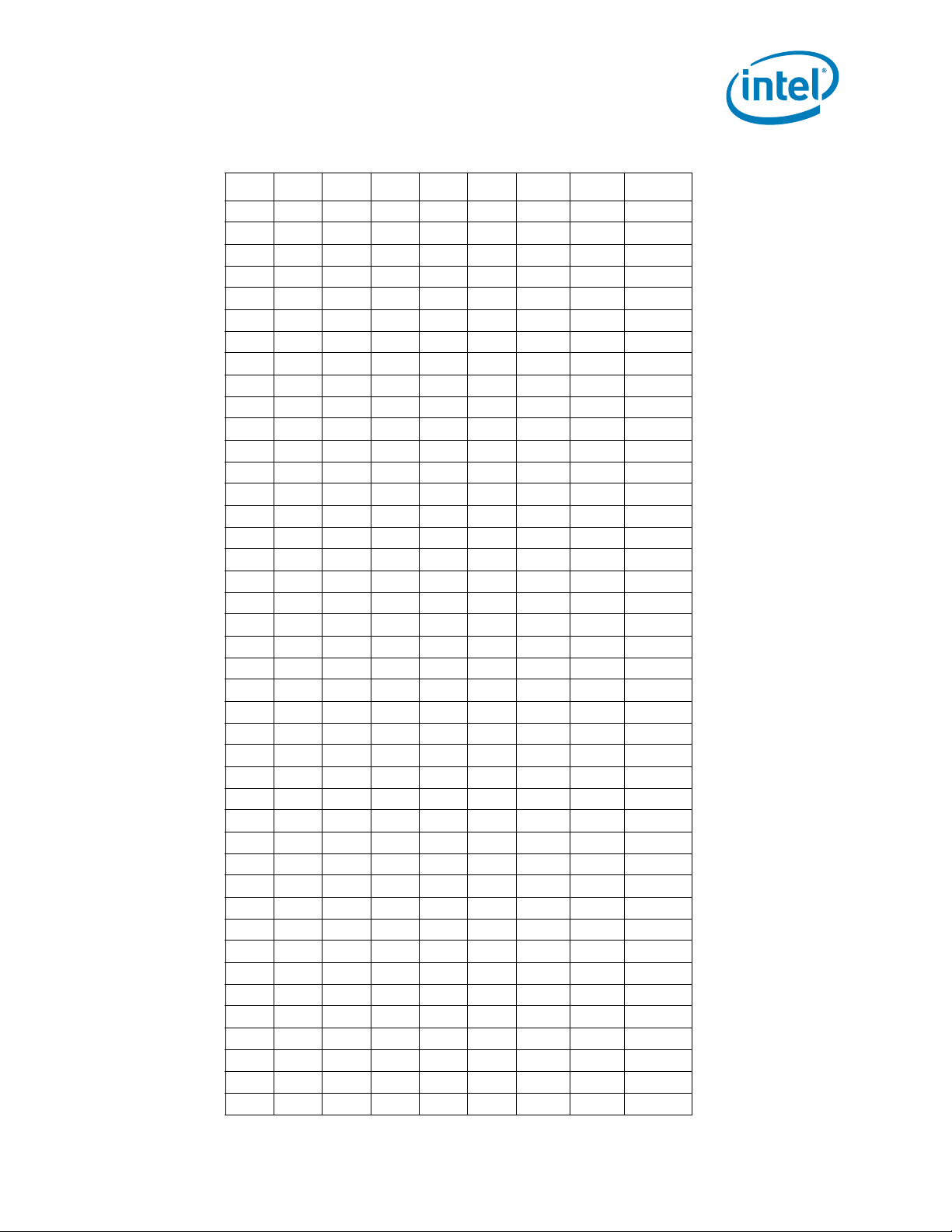

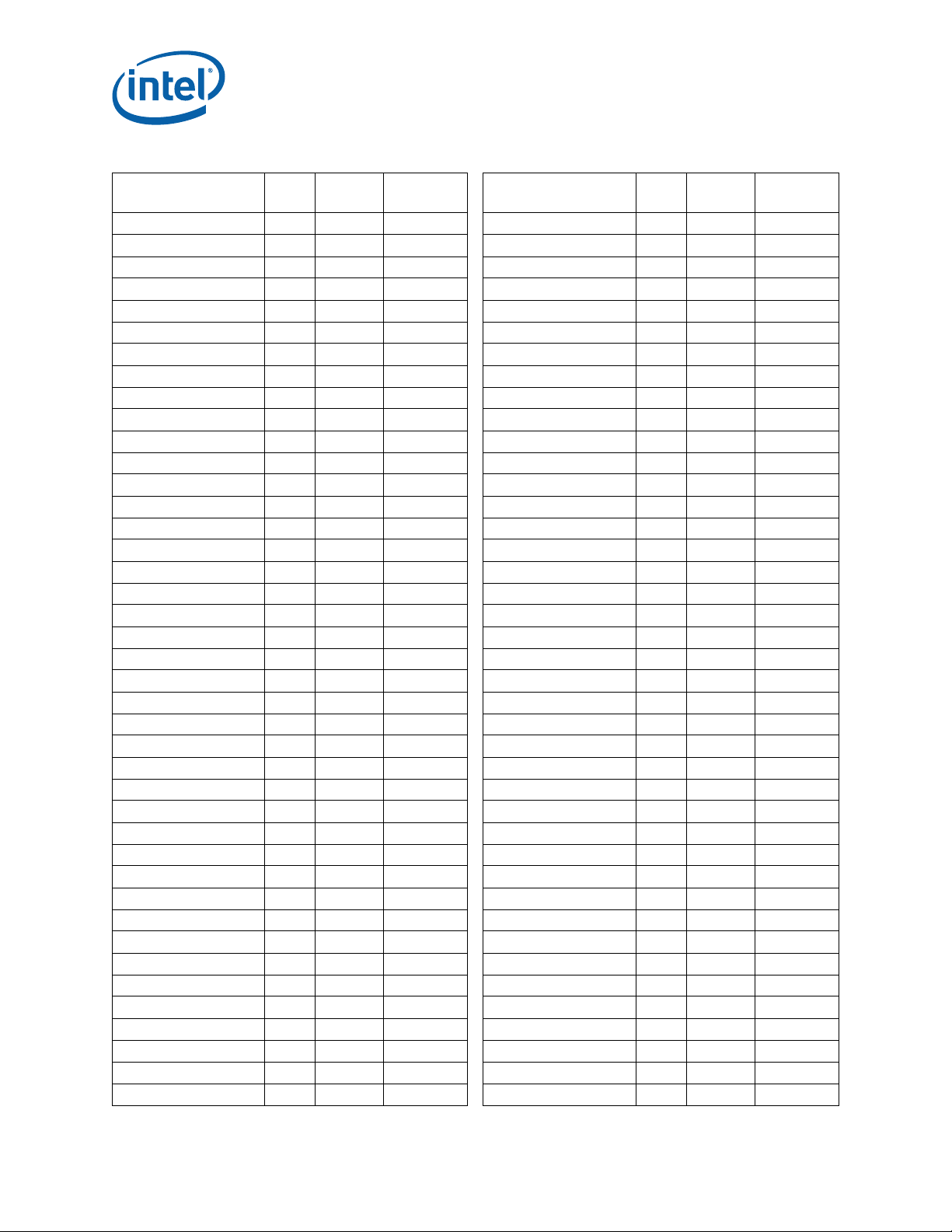

Table 2-2. Voltage Identification Definition (Sheet 3 of 5)

VID7 VID6 VID5 VID4 VID3 VID2 VID1 VID0 V

010011 1 01.12500

010011 1 11.11875

010100 0 01.11250

010100 0 11.10625

010100 1 01.10000

010100 1 11.09375

010101 0 01.08750

010101 0 11.08125

010101 1 01.07500

010101 1 11.06875

010110 0 01.06250

010110 0 11.05625

010110 1 01.05000

010110 1 11.04375

010111 0 01.03750

010111 0 11.03125

010111 1 01.02500

010111 1 11.01875

011000 0 01.01250

011000 0 11.00625

011000 1 01.00000

011000 1 10.99375

011001 0 00.98750

011001 0 10.98125

011001 1 00.97500

011001 1 10.96875

011010 0 00.96250

011010 0 10.95625

011010 1 00.95000

011010 1 10.94375

011011 0 00.93750

011011 0 10.93125

011011 1 00.92500

011011 1 10.91875

011100 0 00.91250

011100 0 10.90625

011100 1 00.90000

011100 1 10.89375

011101 0 00.88750

011101 0 10.88125

011101 1 00.87500

011101 1 10.86875

CC_MAX

Intel® Xeon® Processor 5600 Series Datasheet Volume 1 23

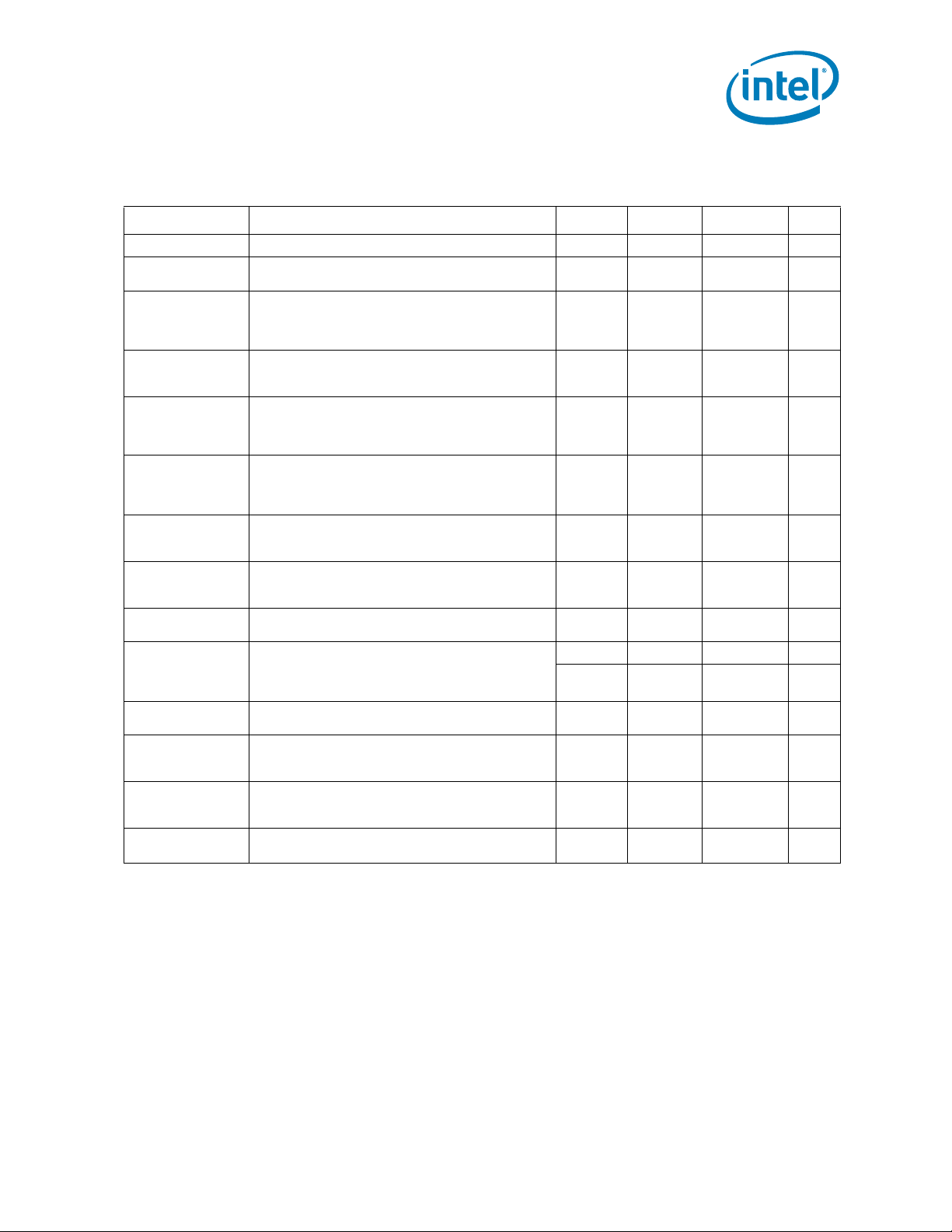

Page 24

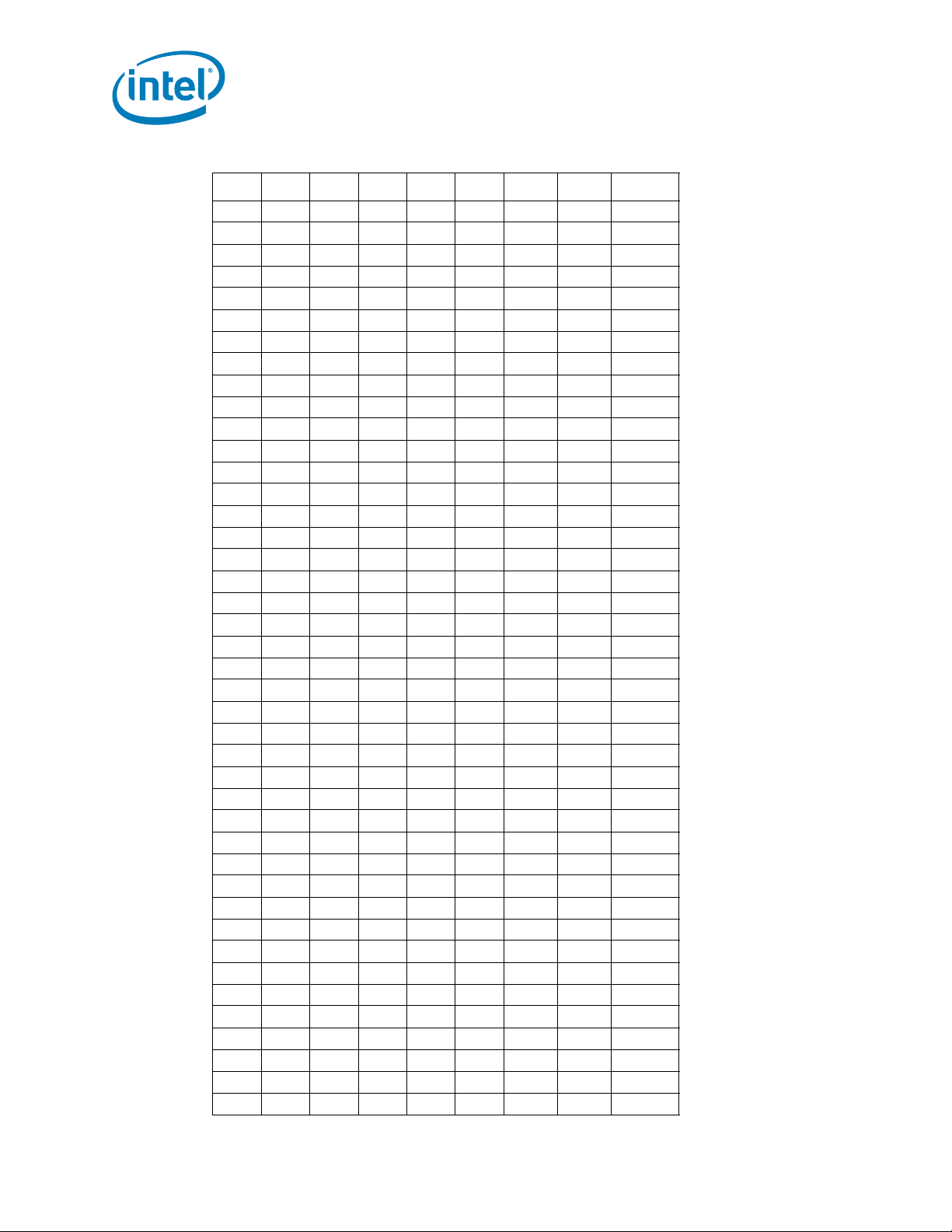

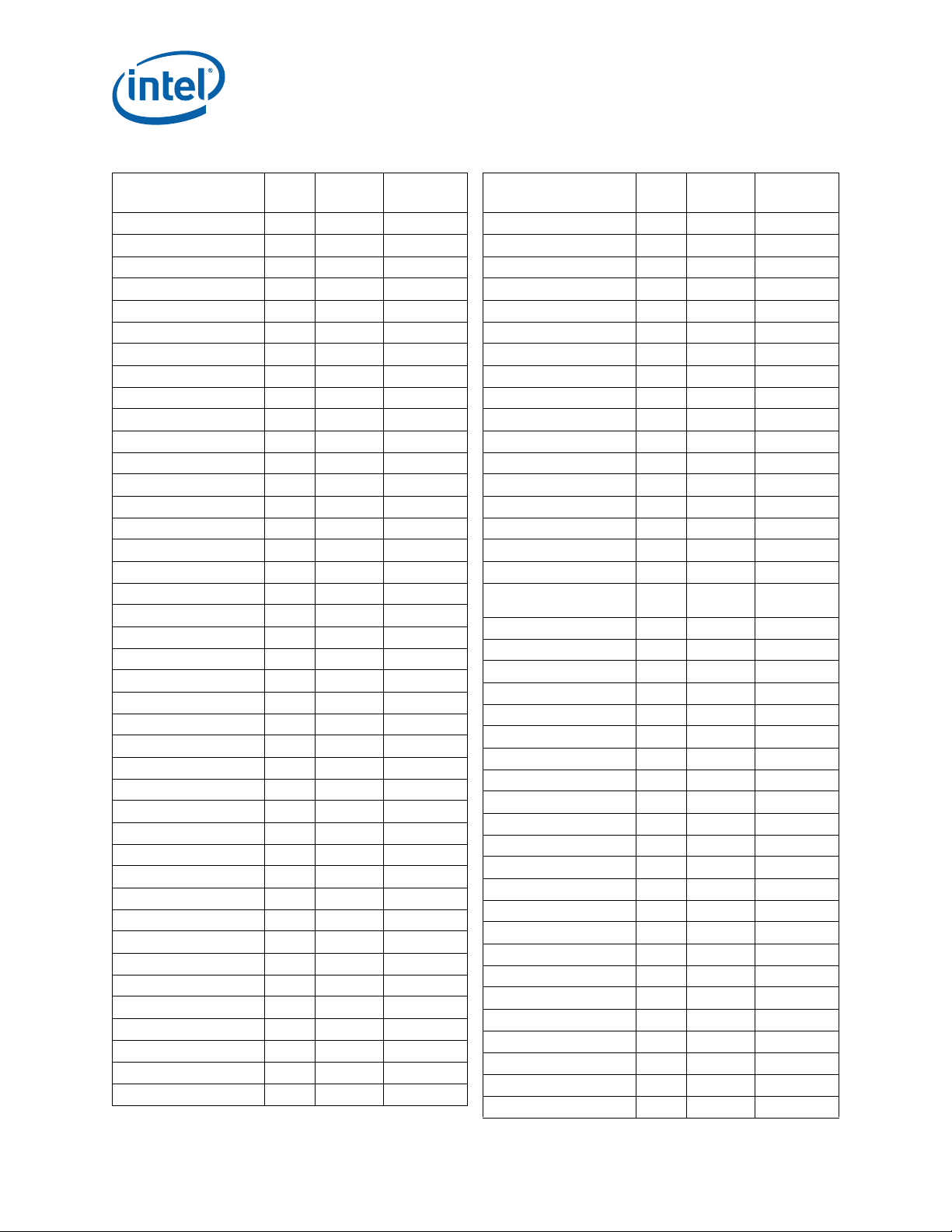

Table 2-2. Voltage Identification Definition (Sheet 4 of 5)

Electrical Specifications

VID7 VID6 VID5 VID4 VID3 VID2 VID1 VID0 V

CC_MAX

011110 0 00.86250

011110 0 10.85625

011110 1 00.85000

011110 1 10.84375

011111 0 00.83750

011111 0 10.83125

011111 1 00.82500

011111 1 10.81875

100000 0 00.81250

100000 0 10.80625

100000 1 00.80000

100000 1 10.79375

100001 0 00.78750

100001 0 10.78125

100001 1 00.77500

100001 1 10.76875

100010 0 00.76250

100010 0 10.75625

100010 1 00.75000

100010 1 10.74375

100011 0 00.73750

100011 0 10.73125

100011 1 00.72500

100011 1 10.71875

100100 0 00.71250

100100 0 10.70625

100100 1 00.70000

100100 1 10.69375

100101 0 00.68750

100101 0 10.68125

100101 1 00.67500

100101 1 10.66875

100110 0 00.66250

100110 0 10.65625

100110 1 00.65000

100110 1 10.64375

100111 0 00.63750

100111 0 10.63125

100111 1 00.62500

100111 1 10.61875

101000 0 00.61250

101000 0 10.60625

24 Intel

®

Xeon® Processor 5600 Series Datasheet Volume 1

Page 25

Electrical Specifications

Table 2-2. Voltage Identification Definition (Sheet 5 of 5)

VID7 VID6 VID5 VID4 VID3 VID2 VID1 VID0 V

101000 1 00.60000

101000 1 10.59375

101001 0 00.58750

101001 0 10.58125

101001 1 00.57500

101001 1 10.56875

101010 0 00.56250

101010 0 10.55625

101010 1 00.55000

101010 1 10.54375

101011 0 00.53750

101011 0 10.53125

101011 1 00.52500

101011 1 10.51875

101100 0 00.51250

101100 0 10.50625

101100 1 00.50000

111111 1 0 OFF

111111 1 1 OFF

Notes:

1. When the “11111111” VID pattern is observed, or when the SKTOCC# pin is pulled high, the voltage

regulator output should be disabled.

2. The VID range includes VID transitions that may be initiated by thermal events, Extended HALT state

transitions (see Section 8.2), higher C-States (see Section 8.2) or Enhanced Intel SpeedStep

transitions (see Section 8.5). The Extended HALT state must be enabled for the processor to

remain within its specifications

3. Once the VRM/EVRD is operating after power-up, if either the Output Enable signal is de-asserted or a

specific VID off code is received, the VRM/EVRD must turn off its output (the output should go to high

impedance) within 500 ms and latch off until power is cycled.

CC_MAX

®

Technology

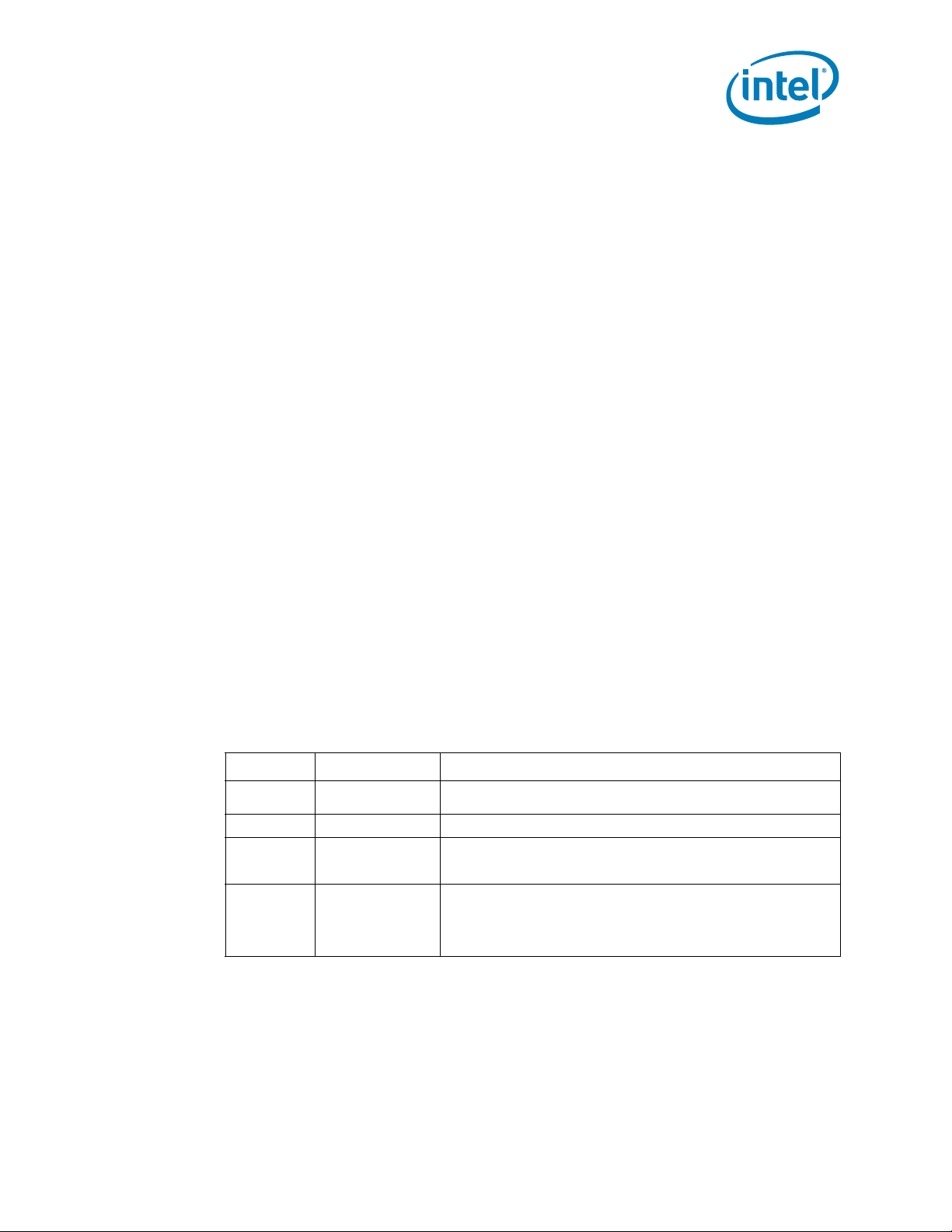

2.1.7.3.1 Power-On Configuration (POC) Logic

VID[7:0] signals also serve a second function. During power-up, Power-On

Configuration POC[7:0] logic levels are MUX’ed onto these signals via 1-5 kΩ pull-up or

pull down resistors located on the baseboard. These values provide voltage regulator

keying (VID[7]), inform the processor of the platforms power delivery capabilities

(MSID[2:0]), and program the gain applied to the ISENSE input (CSC[2:0]). Table 2-3

maps VID signals to the corresponding POC functionality.

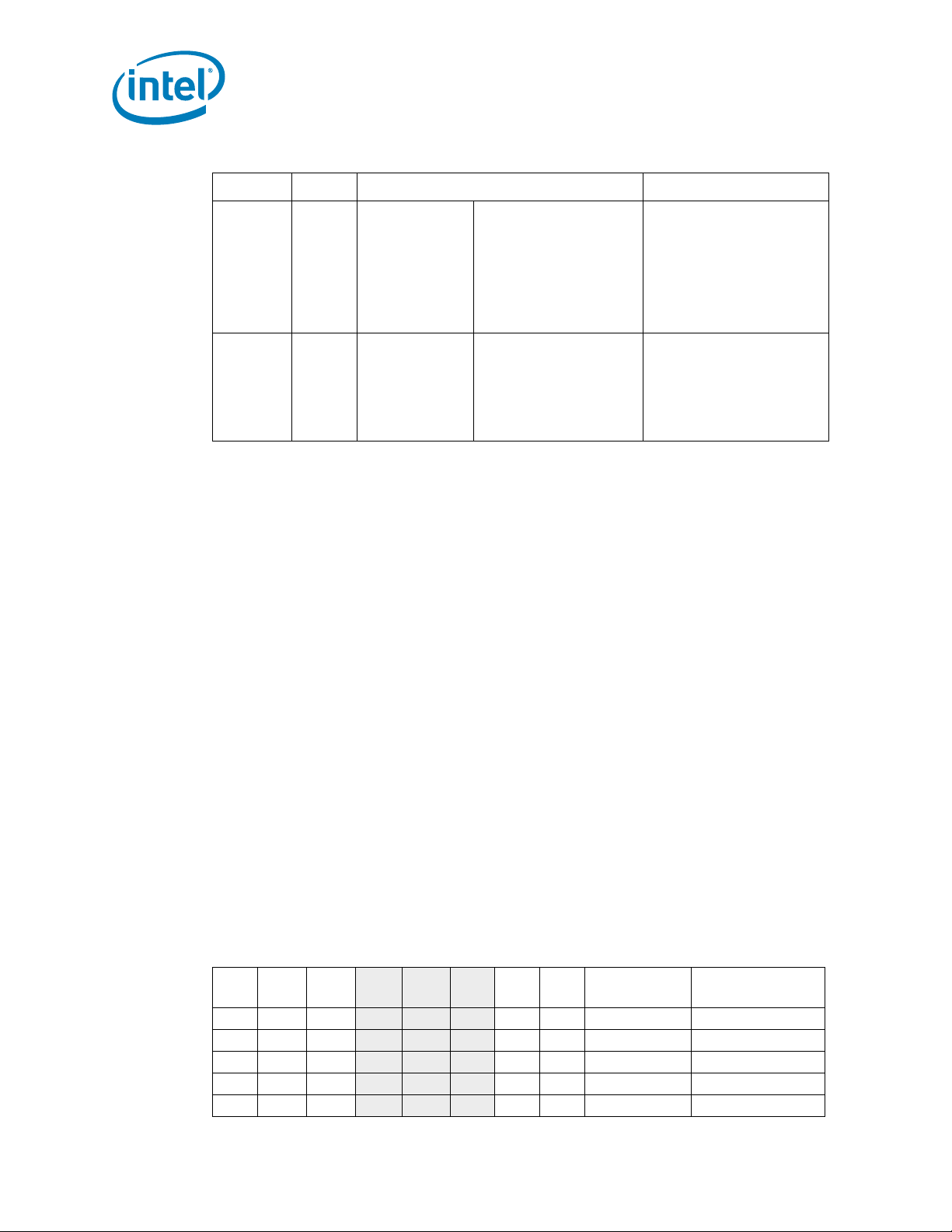

Table 2-3. Power-On Configuration (POC[7:0]) Decode (Sheet 1 of 2)

Function Bits POC Settings Description

VR_Key VID[7] 0b for VR11.1 Electronic safety key

Spare VID[6] 0b (default) Reserved for future use

Intel® Xeon® Processor 5600 Series Datasheet Volume 1 25

distinguishing VR11.1

Page 26

Table 2-3. Power-On Configuration (POC[7:0]) Decode (Sheet 2 of 2)

Function Bits POC Settings Description

CSC[2:0] VID[5:3] -000b

-001b

-010b

-011b

-100b

-101b

-111b

MSID[2:0] VID[2:0] -001b

-011b

-100b

-101b

-110b

Note:

1. This setting is defined for future use; no Intel Xeon processor 5600 series SKU is defined with ICC_MAX=40

A.

2. In general, set PWM IMON slope to 900 mV = IMAX, where IMAX = ICCMAX. For the 130 W SKU, set IMON

slope to 900 mV= 180 A. All other SKUs must match the values shown above. Please consult the PWM

datasheet for the IMON slope setting.

Feature Disabled

ICC_MAX = 40 A

40 W TDP / ICC_MAX = 50 A

60 W TDP / ICC_MAX = 80 A

80W TDP / ICC_MAX = 100 A

95W TDP / ICC_MAX = 120 A

130W TDP / ICC_MAX =

150A

40 W TDP / 50 A ICC_MAX

60 W TDP / 80 A ICC_MAX

80 W TDP / 100 A ICC_MAX

95 W TDP / 120 A ICC_MAX

130 W TDP / 150 A ICC_MAX

1

2

Current Sensor Configuration

(CSC) programs the gain

applied to the ISENSE A/D

output. ISENSE data is then

used to dynamically calculate

current and power.

MSID[2:0] signals are provided

to indicate the Market Segment

for the processor and may be

used for future processor

compatibility or keying. See

Section 8.1 for platform timing

requirements of the MSID[2:0]

signals.

Electrical Specifications

Some POC signals include specific timing requirements. Please refer to Section 8.1 for

further details.

2.1.7.4 Processor VTT Voltage Identification (VTT_VID) Signals

The voltage set by the VTT_VID signals is the typical reference voltage regulator (VR)

output to be delivered to the processor V

regulator will supply all V

TTA

and V

TTD

outputs. Please refer to Table 2-18 for the DC specifications for these signals.

Individual processor VTT_VID values may be calibrated during manufacturing such that

two devices at the same core frequency may have different default VTT_VID settings.

The processor utilizes three voltage identification signals to support automatic selection

of power supply voltages. These correspond to VTT_VID[4:2]. The V

delivered to the processor lands must also encompass a 20 mV offset (See Table 2-4;

V

) above the voltage level corresponding to the state of the VTT_VID[7:0] signals

TT_TYP

(See Table 2-4; VR 11.0 Voltage). Table 2-11 and Figure 2-10 provide the resulting

static and transient tolerances. Please note that the maximum and minimum electrical

loadlines are defined by a 31.5 mV tolerance band above and below V

Power source characteristics must be guaranteed to be stable whenever the supply to

the voltage regulator is stable.

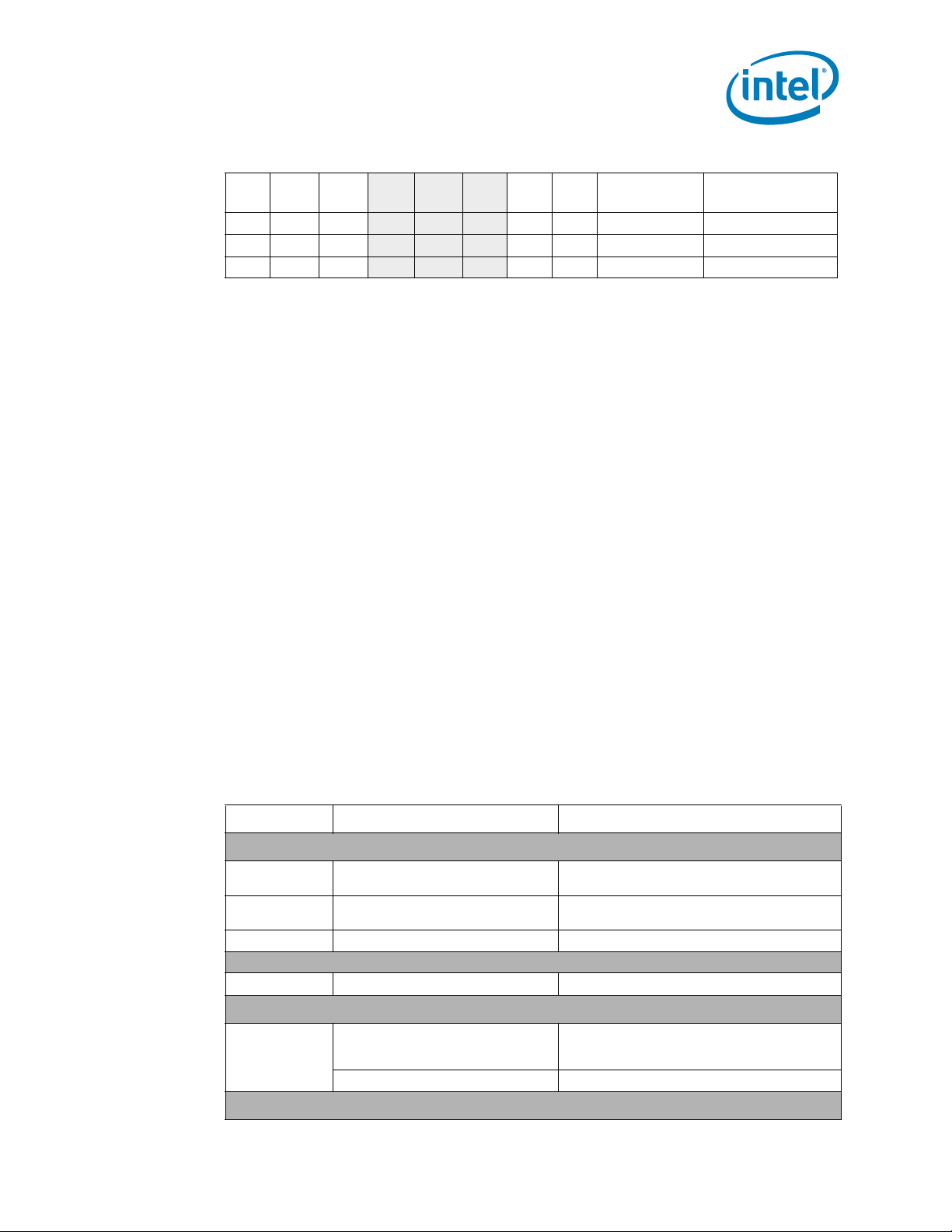

Table 2-4. VTT Voltage Identification Definition (Sheet 1 of 2)

VID7 VID6 VID5 VID4 VID3 VID2 VID1 VID0

010

010

010

010

010

0 0 0 1 0 1.200 V 1.220 V

0 0 1 1 0 1.175 V 1.195 V

0 1 0 1 0 1.150 V 1.170 V

0 1 1 1 0 1.125 V 1.145 V

1 0 0 1 0 1.100 V 1.120 V

TTA

and V

lands. It is expected that one

TTD

lands. VTT_VID signals are CMOS push/pull

VR 11.0

Voltage

voltage level

TT

valu es.

TT_TYP

V

TT_TYP

(Voltage + Offset)

26 Intel

®

Xeon® Processor 5600 Series Datasheet Volume 1

Page 27

Electrical Specifications

Table 2-4. VTT Voltage Identification Definition (Sheet 2 of 2)

VID7 VID6 VID5 VID4 VID3 VID2 VID1 VID0

0101 0 1 1 0 1.075 V 1.095 V

010

010

1 1 0 1 0 1.050 V 1.070 V

1 1 1 1 0 1.025 V 1.045 V

2.1.8 Reserved or Unused Signals

All Reserved (RSVD) signals must remain unconnected. Connection of these signals to

, V

, V

, V

V

CC

TTA

TTD

component malfunction or incompatibility with future processors. See Section 5 for the

land listing and the location of all Reserved signals.

For reliable operation, connect unused inputs or bidirectional signals to an appropriate

signal level. Unused Intel QuickPath Interconnect input and output pins can be left

floating. Unused active high inputs should be connected through a resistor to ground

). Unused outputs can be left unconnected; however, this may interfere with some

(V

SS

TAP functions, complicate debug probing, and prev ent boundary scan testing. A resistor

must be used when tying bidirectional signals to power or ground. When tying any

signal to power or ground, including a resistor will also allow for system testability.

Resistor values should be within ± 20% of the impedance of the baseboard trace,

unless otherwise noted in the appropriate platform design guidelines.

TAP signals do not include on-die termination, however they may include resistors on

package (refer to Section 2.1.6 for details). Inputs and utilized outputs must be

terminated on the baseboard. Unused outputs may be terminated on the baseboard or

left unconnected. Note that leaving unused outputs unterminated may interfere with

some TAP functions, complicate debug probing, and prevent boundary scan testing.

, VSS, or any other signal (including each other) can result in

DDQ

VR 11.0

Voltage

V

TT_TYP

(Voltage + Offset)

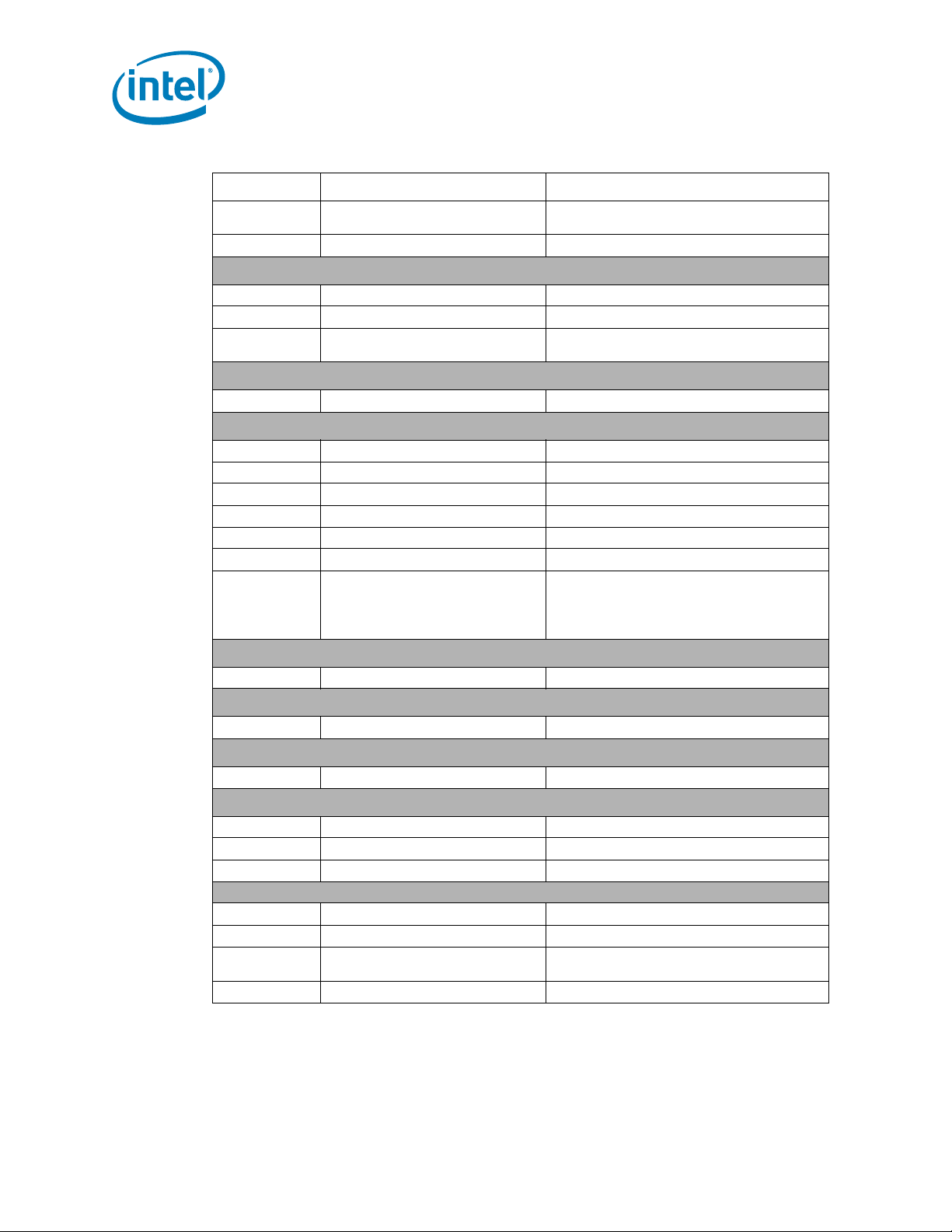

2.2 Signal Group Summary

Signals are aligned in Table 2-5 by buffer type and characteristics. “Buffer Type”

denotes the applicable signaling technology and specifications.

Table 2-5. Signal Groups (Sheet 1 of 2)

Signal Group Buffer Type Signals

Intel® QuickPath Interconnect Signals

Differential Intel®

Differential Intel®

Single ended Analog Input QPI[0/1]_COMP

DDR3 Reference Clocks

Differential Output DDR{0/1/2}_CLK_[P/N][3:0]

DDR3 Command Signals

Single ended CMOS Output DDR{0/1/2}_RAS#, DDR{0/1/2}_CAS#,

DDR3 Control Signals

QuickPath Interconnect Input QPI[0/1]_DRX_D[N/P][19:0],

QuickPath Interconnect Output QPI[0/1]_DTX_D[N/P][19:0],

2

2

Asynchronous Output DDR{0/1/2}_RESET#

2

1

QPI[0/1]_CLKRX_DP, QPI[0/1]_CLKRX_DN

QPI[0/1]_CLKTX_DP, QPI[0/1]_CLKTX_DN

DDR{0/1/2}_WE#, DDR{0/1/2}_MA[15:0],

DDR{0/1/2}_BA[2:0], DDR{0/1/2}_MA_PAR

Intel® Xeon® Processor 5600 Series Datasheet Volume 1 27

Page 28

Notes:

Table 2-5. Signal Groups (Sheet 2 of 2)

Signal Group Buffer Type Signals

Single ended CM OS Output DDR{0/1/2}_CS#[7:0], DDR{0/1/2}_ODT[5:0],

Single ended Analog Input DDR_VREF, DDR_COMP[2:0]

DDR3 Data Signals

Single ended CMOS Input/Output DDR{0/1/2}_DQ[63:0], DDR{0/1/2}_ECC[7:0]

Differential CMOS Input/Output DDR{0/1/2}_DQS_[N/P][17:0]

Single ended Asynchronous Input DDR{0/1/2}_PAR_ERR#[2:0],

Platform Environmental Control Interface (PECI)

Single ended Asynchronous Input/Output PECI

Processor Sideband Signals

Single ended GTL Input/Output BPM#[7:0], CAT_ERR#

Single ended Asynchronous Input PECI_ID#

Single ended Asynchronous GTL Output PRDY#, THERMTRIP#

Single ended Asynchronous GTL Input PREQ#

Single ended Asynchronous GTL Input/Output PROCHOT#

Single ended Asynchronous CMOS Output PSI#, TAPPWRGOOD

Single ended CMOS Output VID[7:6],

PWRGOOD Signal

Single ended Asynchronous Input VCCPWRGOOD, VDDPWRGOOD, VTTPWRGOOD

Reset Signal

Single ended Reset Input RESET#

System Reference Clock

Differential Input BCLK_DP, BCLK_DN

Test Access Port (TAP) Signals

Differential CMOS Output BCLK_ITP_DP, BCLK_ITP_DN

Single ended Input TCK, TDI, TMS, TRST#

Single ended GTL Output TDO

Power/Other Signals

2

Power / Ground V

Analog Input COMP0, ISENSE

Sense Points VCCSENSE, VSSSENSE, VSS_SENSE_VTTD,

Other SKTOCC#, DBR#

Electrical Specifications

1

DDR{0/1/2}_CKE[3:0]

DDR_THERM#, DDR_THERM2#

VID[5:3]/CSC[2:0],

VID[2:0]/MSID[2:0],

VTT_VID[4:2]

, V

CCPLL

, V

DDQ, VTTA

CC

, V

TTD

VTTD_SENSE

, V

SS

1. Refer to Section 5 for land assignments and Section 6 for signal definitions.

2. DDR{0/1/2} refers to DDR3 channel 0, DDR3 channel 1, and DDR3 Channel 2

Signals that include on-die termination (ODT) are listed in Table 2-6.

28 Intel

®

Xeon® Processor 5600 Series Datasheet Volume 1

Page 29

Electrical Specifications

Table 2-6. Signals With On-Die Termination (ODT)

Intel® QuickPath Interconnect Interface Signal Group

QPI[1:0]_DRX_DP[19:0], QPI[1:0]_DRX_DN[19:0], QPI[1:0]_TRX_DP[19:0], QPI[1:0]_TRX_DN[19:0],

QPI[0/1]_CLKRX_D[N/P], QPI[0/1]_CLKTX_D[N/P]

DDR3 Signal Group

DDR{0/1/2}_DQ[63:0], DDR{0/1/2}_DQS_[N/P][17:0], DDR{0/1/2}_ECC[7:0],

DDR{0/1/2}_PAR_ERR#[2:0]

Processor Sideband Signal Group

BPM#[7:0]6, PECI_ID#7, PREQ#

Test Access Port (TAP) Signal Group

4

TCK

, TDI5, TMS5, TRST#

Power/Other Signal Group

TAPPWRGOOD8, VCCPWRGOOD, VDDPWRGOOD, VTTPWRGOOD

1,2

3

1

6,

TAPPWRGOOD

5

9

8

1

Notes:

1. Unless otherwise specified, signals have ODT in the package with a 50 Ω pull-down to V

2. Unless otherwise specified, all DDR3 signals are terminated to V

3. DDR{0/1/2}_PAR_ERR#[2:0] are terminated to V