Page 1

HF/50MHz TRANSCEIVER

S-14407XZ-C1

Feb. 2008

Page 2

INTRODUCTION CAUTION

This service manual describes the latest service information

for the IC-7700 HF/50MHz TRANSCEIVER at the time of

publication.

MODEL VERSION

USA

EUR

FRA

IC-7700

ITR

ESP

UK

KOR

NEVER connect the transceiver to an AC outlet or to a DC

power supply that uses more than specifed. This will ruin

the transceiver.

DO NOT expose the transceiver to rain, snow or any liquids.

DO NOT reverse the polarities of the power supply when

connecting the transceiver.

DO NOT apply an RF signal of more than 20 dBm (100 mW) to

the antenna connector. This could damage the transceiver’s

front-end.

To upgrade quality, any electrical or mechanical parts and

internal circuits are subject to change without notice or

obligation.

ORDERING PARTS

Be sure to include the following four points when ordering

replacement parts:

1. 10-digit Icom parts numbers

2. Component name

3. Equipment model name and unit name

4. Quantity required

<ORDER EXAMPLE>

1110003491 S.IC TA31136FNG IC-7700 MAIN UNIT 5 pieces

8820001210 Screw 2438 screw IC-7700 Top cover 10 pieces

Addresses are provided on the inside back cover for your

convenience.

Icom, Icom Inc. and

Kingdom, Germany, France, Spain, Russia and/or other countries.

logo are registered trademarks of Icom Incorporated (Japan) in the United States, the United

REPAIR NOTES

1. Make sure the problem is internal before disassembling

the transceiver.

2. DO NOT open the transceiver until the transceiver is

disconnected from its power source.

3. DO NOT force any of the variable components. Turn

them slowly and smoothly.

4. DO NOT short any circuits or electronic parts. An

insulated tuning tool MUST be used for all adjustments.

5. DO NOT keep power ON for a long time when the

transceiver is defective.

6. DO NOT transmit power into a Standard Signal

Generator or a Sweep Generator.

7. ALWAYS connect a 50 dB to 60 dB attenuator between

the transceiver and a Deviation Meter or Spectrum

Analyzer when using such test equipment.

8. READ the instructions of test equipment throughly

before connecting a test equipment to the transceiver.

Page 3

CONTENTS

SECTION 1 SPECIFICATIONS

SECTION 2 INSIDE VIEWS

SECTION 3 CIRCUIT DESCRIPITON

3-1 RECEIVER CIRCUITS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3-2 TRANSMITTER CIRCUITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

3-3 FREQUENCY SYNTHESIZER CIRCUITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

3-4 MAIN CPU PORT ALLOCATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

SECTION 4 ADJUSTMENT PROCEDURES

4-1 PREPARATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4-2 ADJUSTMENTS ON THE OSC UNIT AND PLL UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

4-3 ADJUSTMENTS ON THE RF UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

4-4 ADJUSTMENTS ON THE PA200W BOARD. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

4-5 ADJUSTMENTS ON THE MAIN UNIT (including RF UNIT) . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

4-6 ADJUSTMENTS ON THE SCOPE UNIT. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-11

4-7 AUTOMATIC ADJUSTMENTS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-12

SECTION 5 PARTS LIST

SECTION 6 MECHANICAL PARTS

SECTION 7 BOARD LAYOUTS

SECTION 8 GENERAL WIRING

SECTION 9 BLOCK DIAGRAM

SECTION 10 SCHEMATIC DIAGRAM

FRONT UNIT. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-1

LOGIC UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-2

MAIN UNIT. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-8

PLL UNIT. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-12

OSC UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-13

ANT-SW UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-16

DIGISEL UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-16

RF UNIT. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-17

NETWORK BOARD. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-22

CTRL BOARD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-23

FILTER UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-24

PA200W BOARD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-25

SCOPE UNIT. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-26

DC-DC UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-29

Page 4

SECTION 1 SPECIFICATIONS

D

D

General

• Frequency coverage (unit: MHz) :

Receiver 0.030000–60.000000*

Transmitter 1.800000–1.999999*2, 3.500000–3.999999*2,

5.330500*3, 5.346500*3, 5.366500*3, 5.371500*3,

5.403500*3, 7.000000–7.300000*2,

10.100000–10.150000*2, 14.000000–14.350000*2,

• Operating mode : USB, LSB, CW, RTTY, PSK31, AM, FM

• Number of memory channels : 101 (99 regular, 2 scan edges)

• Antenna connector : SO-239×4 (antenna impedance: 50 1)

• Operating temperature range : 0˚C to +50˚C; +32˚F to +122˚F

• Frequency stability : Less than ±0.05 ppm (approx. 5 min. after from turn

• Frequency resolution : 1Hz

• Power supply requirement : 85–265 V AC (universal input)

• Power consumption :

Receive Stand-by 200 VAtypical

Max. audio 210 VA typical

Transmit at 200 W 800 VA

• Dimensions (projections not included) : 425×149×437 mm; 1623⁄32×57⁄8×177⁄32 in

• Weight : Approx. 22.5 kg; 50 lb

• ACC 1 connectors : 8-pin DIN connector

• ACC 2 connectors : 7-pin DIN connector

• Display* : 7-inch (diagonal) TFT color LCD (800×480)

• EXT-DISPLAY connector : D-sub 15S

• CI-V connector : 2-conductor 3.5 (d) mm (1⁄8w)

• RS-232C connector : D-sub 9-pin

• USB connector : USB (Universal Serial Bus)1.1/2.0×2

18.068000–18.168000*2, 21.000000–21.450000*2,

24.890000–24.990000*2, 28.000000–29.700000*2,

50.000000–54.000000*

*1Some frequency ranges are not guaranteed.

2

*

Depending on versions. *3USA version only.

the main power, [I/O], ON, 0–50˚C; 32–122˚F)

1

2

Transmitter

• Transmit output power :

SSB, CW, RTTY, PSK31, FM

AM 5–50 W

• Modulation system :

SSB D.P.S.N. modulation

AM Digital low power modulation

FM Digital phase modulation

• Spurious emission :

Harmonics More than 60 dB (HF bands)

Unwanted emission More than 50 dB (HF bands)

(except Harmonics)

Out of band emission More than 40 dB (HF bands)

• Carrier suppression : More than 63 dB

• Unwanted side-band suppression : More than 80 dB

•∂TX variable range : ±9.999 kHz

• Microphone connector : 8-pin connector (600 1)

• ELEC-KEY connector : 3-conductor 6.35 (d) mm (1⁄4w)

• KEY connector : 3-conductor 6.35 (d) mm (1⁄4w)

• RELAY connector : Phono (RCA)

• ALC connector : Phono (RCA)

5–200 W

More than 70 dB (50 MHz band)

More than 66 dB (50 MHz band)

More than 60 dB (50 MHz band)

1 - 1

Page 5

D

D

D

D

Receiver

• Receive system : Double conversion superheterodyne system

• Intermediate frequencies :

1st 64.455 MHz

2nd 36 kHz

• Sensitivity (typical) :

SSB, CW, RTTY (BW=2.4 kHz, 10 dB S/N)

0.100000– 1.799999 MHz 0.5 µV

1.800000–29.990000 MHz 0.16 µV

50.000000–54.000000 MHz 0.13 µV (pre-amp 2 ON)

AM (BW=6 kHz, 10 dB S/N)

0.100000– 1.799999 MHz 6.3 µV

1.800000–29.990000 MHz 2 µV (pre-amp 1 ON)

50.000000–54.000000 MHz 1 µV

FM (BW=15 kHz, 12 dB SINAD)

28.000000–29.990000 MHz 0.5 µV (pre-amp 1 ON)

50.000000–54.000000 MHz 0.32 µV (pre-amp 2 ON)

• Internal Modulate Distortion (typical) : Dynamic range 109 dB

(at 14.100 MHz, 100 kHz separation, pre-amp OFF,

CW mode; BW=500 Hz)

• Selectivity :

SSB, RTTY (BW=2.4 kHz) More than 2.4 kHz/–3 dB

Less than 3.6 kHz/–60 dB

CW (BW=500 Hz) More than 500 Hz/–3 dB

Less than 700 Hz/–60 dB

AM (BW=6 kHz) More than 6.0 kHz/–3 dB

Less than 15.0 kHz/–60 dB

FM (BW=15 kHz) More than 12.0 kHz/–6 dB

Less than 20.0 kHz/–60 dB

• Spurious and image rejection ratio : More than 70 dB

• Squelch sensitivity (pre-amp OFF) :

SSB, CW, RTTY, PSK31 Less than 5.6 µ V

FM Less than 1 µV

• RIT variable range : ±9.999 kHz

• Audio output power : More than 2.6 W at 10% distortion with an 8 1 load

• PHONES connector : 3-conductor 6.35 (d) mm (1⁄4w)

• EXT-SP connectors : 2-conductor 3.5 (d) mm (1⁄8w)/8 1

(pre-amp 1 ON)

(pre-amp 1 ON)

(pre-amp 1 ON)

(pre-amp 2 ON)

Antenna tuner

• Matching impedance range : 16.7 to 150 1 unbalanced

(HF bands; VSWR better than 3:1)

20 to 125 1 unbalanced

(50 MHz band; VSWR better than 2.5:1)

• Minimum operating input : 8W (HF bands)

15 W (50 MHz band)

• Tuning accuracy : VSWR 1.5:1 or less

• Insertion loss (after tuning) : Less than 1.0 dB

All stated specifications are typical and subject to change without notice or obligation.

1 - 2

Page 6

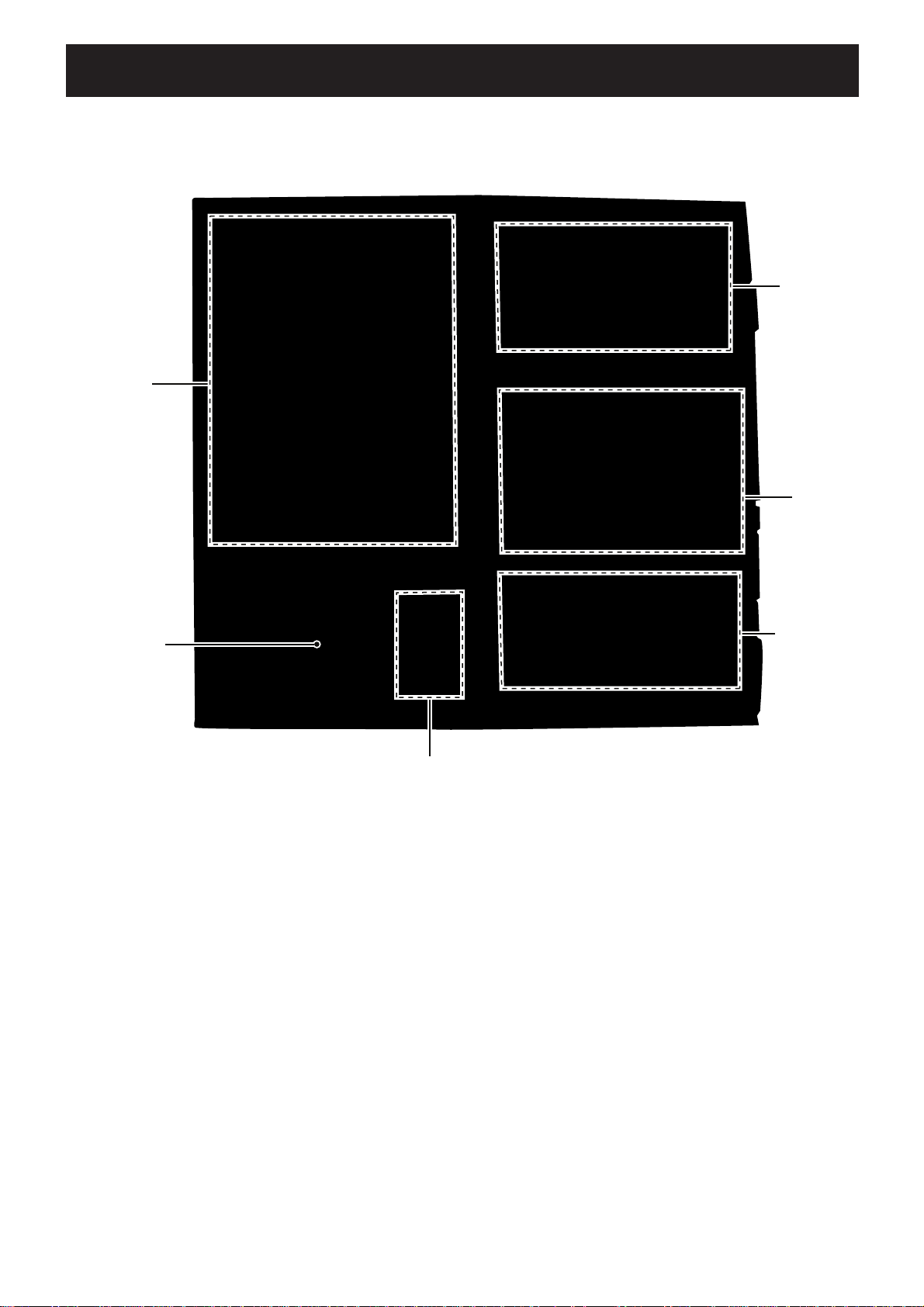

SECTION 2 INSIDE VIEW

(viewing from the bottom)

RF UNIT

MAIN UNIT

PLL UNIT

DIGISEL UNIT

(under the cover)

SCOPE UNIT

OSC UNIT

2 - 1

Page 7

SECTION 3 CIRCUIT DESCRIPTION

3-1 RECEIVER CIRCUITS

ANT-SW UNIT

Antenna switching relays (RL51, 61, 71, 81) select the RX

signals which are from [ANT1]–[ANT4], and the relays are

controlled by relay controller (IC11). RX signals from [ANT1]

–[ANT3] are applied to the CTRL BOARD, RX signals from

[ANT4] are applied to the RF UNIT directly.

CTRL BOARD

The CTRL BOARD has TX/RX switch which toggles the RF

path between in TX and RX.

RX signals from the ANT-SW UNIT are passed through the

TX/RX switches (RL252–254), and applied to the RF UNIT.

RF UNIT

RF UNIT contains receive circuits; from RX BPF to 2nd

RX IF AMP. The RX signals are filtered by BPFs to remove

unwanted signals and amplified, then down-converted twice

into 2nd IF signal.

The received signals from the ANT-SW UNIT and CTRL

BOARD are passed through some relays and attenuators,

then filtered by BPFs which is assigned to filter the RX

signals that desired to receive. The filtered RX signals are

amplified by RF AMPs before being applied to the 1st mixer.

• 0.03–30 MHz SIGNALS

The RX signals from the band SW (RL351) are passed

though one of the BPF or LPF. The filtered signals are

entered to the DIGISEL UNIT, and gone through or

by-passed the DIGISEL (Digital RF Selector Switch) filter.

When the DIGISEL function is activated, the RX signals

are passed through the DIGISEL SW (RL21) and narrow

bandwidth filter (D_SEL) which filters out unwanted signals

with its sharpen frequency response. The filtered signals are

amplified by the RF AMP (Q201) which recovers the insert

loss of the D_SEL filter, then backed to the RF UNIT via

DIGISEL SW (RL2).

• 30–60 MHz SIGNALS

RX signals from the band SW (RL351) are passed though

one of the BPFs (Fc=50–54 MHz or Fc=54–60 MHz) to

remove unwanted signals.

The filtered signals are amplified by one of (or both of)

the Pre-AMPs (or by-passed; according to the setting).

The amplified RX signals are then applied to the 1st mixer

(Q1211, 1212) via the LPF.

The RX signals are mixed with the 1st LO signals from PLL

UNIT (the 1st LO signals are gone through LO AMP (Q1301),

HPF and LPF before being applied.) to be converted into

the 1st RX IF signal.

A portion of 1st IF signal is applied to the SCOPE UNIT via

buffer (Q1352).

The converted 1st RX IF signal is then filtered by one of 1st

IF filters on the MCF BOARDs (FI1401). Selecting of the

filter to pass is carried out by IF SW (IC1402, 1403). The

filtered 1st RX IF signal is amplified by two 1st IF AMPs

(Q1401–1403), then splitted into two before being applied

to the 2nd mixers; as a image rejection mixer (IC501,

1502). Each divided 1st RX IF signal is mixed with 2nd LO

signals from the PLL UNIT (gone through ATT, LO AMP

(Q1651), buffer (IC1651) and another buffer (IC1651)), to be

converted into the 36 kHz 2nd RX IF signal.

One of the LO signal is 90 degrees phase-shifted before

being applied to the 2nd mixer (IC1502), and the converted

2nd RX IF is 90 degrees phase-shifted too.

These converted 2nd RX IF signals are buffer-amplified

by buffer (IC1502/IC1501) and amplified by 2nd IF AMP

(IC1504/IC1503). Then the 2nd RX IF signals whose phase

is different each other are phase-shifted by the phase shifter

(IC1505), then composed by the composer (IC1505).

The composed 2nd RX IF signal is amplified by another 2nd

IF AMP (IC1506), then entered to the MAIN UNIT.

The RX signals from the DIGISEL UNIT are applied to or

by-passed the Pre-AMP.

When the Pre-AMP1/2 is activated, the RX signals are

applied to the Pre-AMP1 (for all HF bands) or Pre-AMP2

(for 24 MHz and above) via P.AMP SW (RL1004), and the

amplified RX signals are applied to the 1st mixer (IC1051)

via the P.AMP SWs (RL1005, 1006) and LPF.

The RX signals are mixed with the 1st LO signals from

the PLL UNIT (1st LO signals are gone through LO AMPs

(Q1105, 1104, 1101) before being applied.) to be converted

into the 1st RX IF signal.

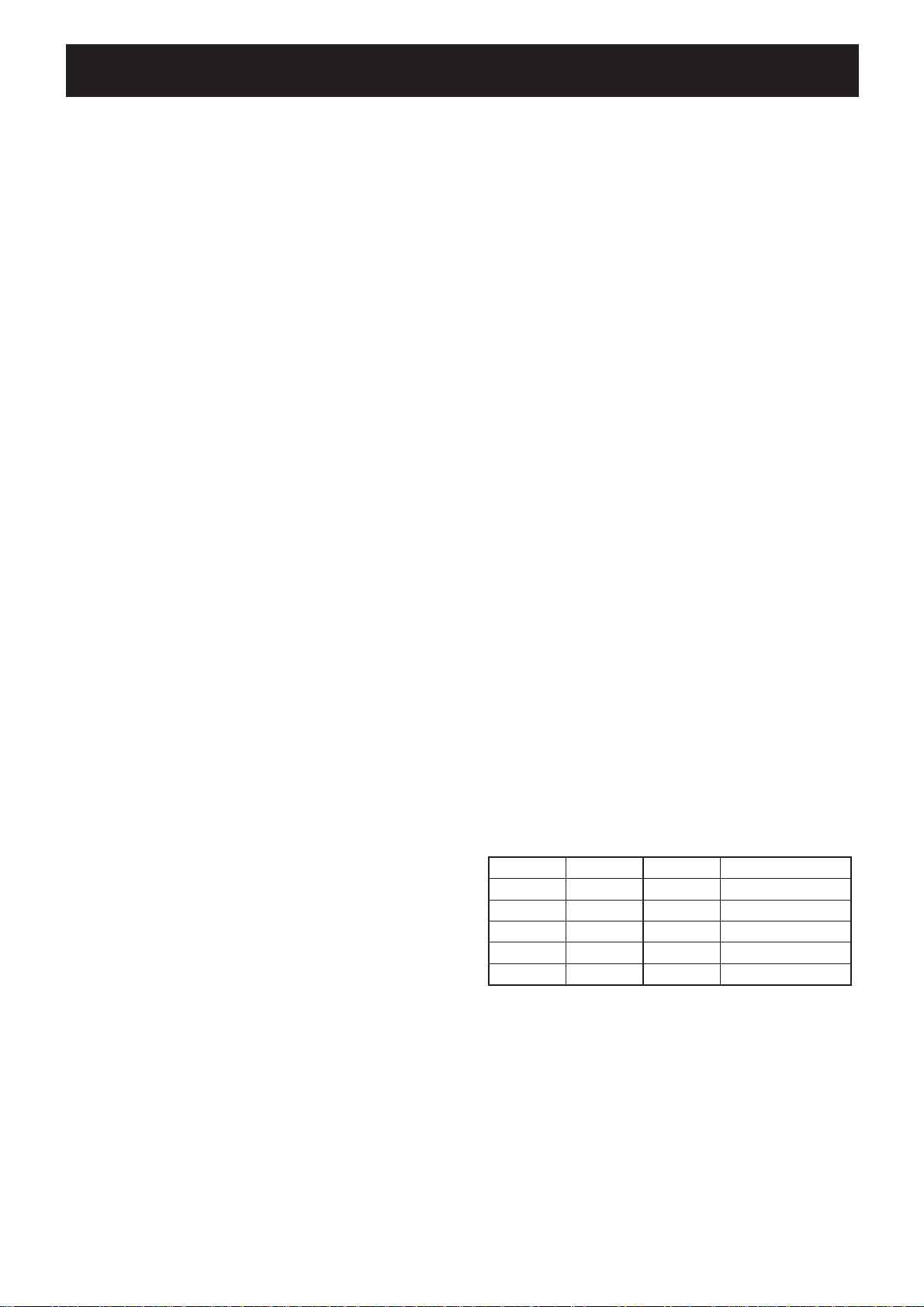

• FREQUENCY CONFIGURATION

Signal Frequency Signal Frequency

1st RX IF 64.455 MHz 1st RX LO 64.485–124.455 MHz

2nd RX IF 36 kHz 2nd RX LO 64.491 MHz

1st TX IF 36 kHz 1st TX LO 64.485–124.455 MHz

2nd TX IF 455 kHz 2nd TX LO 64 MHz

3rd TX IF (*)

*; Refer to "SPECIFICATIONS."

3 - 1

Page 8

MAIN UNIT

MIAN UNIT contains receive circuits; from demodulator

to AF circuits. The 2nd IF signal is demodulated by digital

audio processing circuits.

• DEMODULATOR CIRCUIT

The 36 kHz 2nd RX IF signal from the MAIN UNIT is

applied to the Analog to Digital Converter (ADC; IC1251) via

the IF mute SW (IC1201) and unbalance-balance convert

circuit (IC1211, 1231), to be converted into the 24-bit serial

data. The serial data is applied to the DSP (IC1001) and

processed as digital audio signals. The processed digital

audio signals are then applied to the Digital Audio Converter

(DAC; IC1501) to be converted into the analog audio

signals; as recovered AF signals.

The recovered AF signals are applied to the RX AF circuits

via buffer (IC1751).

• RX AF CIRCUITS

The recovered AF signals are amplified and level-adjusted,

then output from the audio interfaces. (The destination of AF

output signals is depends on the setting)

<OUTPUT FROM Int./Ext. SPEAKER>

The recovered AF signals from the buffer (IC1751) are

passed through the SQL SW (Q351), and applied to the

AF AMP (IC331). The amplified AF signals are splitted into

two AF lines; one is bound for the headphones jack (J2) on

the FRONT UNIT, another is bound for the internal speaker

(SP1)/external speaker via the external SP jack (J751) on

the MAIN UNIT. Both of AF signals on each AF lines are

applied to the 2-channel Voltage Controlled Amplifier (VCA;

IC311) whose gain is determined by applied control voltage

to be adjusted its signal level.

SCOPE UNIT

The 1st RX/TX IF signal from the buffer (Q1352) on the RF

UNIT are passed through the scope IF SW (IC31), scope

ATT, LPF and BPF (dual tuned), and amplified by scope

AMP (Q2) then applied to the 2nd scope mixer (D101).

The 1st IF signal is converted into the 45 MHz 2nd scope IF

signal (S2IF), and filtered to remove unwanted signals, then

amplified by the 2nd scope IF AMPs (Q201 and Q202). The

amplified 2nd scope IF signal is applied to the 3rd scope

mixer (D4) to be converted into the 200 kHz 3rd scope IF

signal. The converted signal is amplified by the 3rd scope IF

AMP (IC401), filtered by the active LPF (IC403), level-limited

by the saturation AMP (IC404). The level-limited signal is

applied to the ADC (IC501) which samples the 200 kHz 3rd

scope IF signal (0–2.5 V) into digital signal, then applied to

the DSP (IC601) as the serial data.

The DSP processes input data, then output to the CPU to

display the frequency and relative signal strength of RX

signals on the spectrum screen.

The level-adjusted AF signals are applied to the AF power

AMP (IC281) which power-amplifies to obtain audio output

power, via LPF (Q291/301).

The power-amplified AF signals are passed through the AF

mute SW (RL261), then applied to the internal speaker (SP1)

via the external SP jack (J751), or an external speaker on

the MAIN UNIT.

When the headphones are connected to the headphones

jack (J2) on the FRONT UNIT, the power-amplified AF

signals from the AF power AMP (IC281) are applied to the

connected headphones.

<TO THE AUDIO STORAGE>

When recording received audio, recovered AF signals from

the buffer (IC1571) are also send to the audio storage

(IC203) on the LOGIC UNIT to be recorded.

<OUTPUT FROM ACC PORT>

The recovered AF signals from the buffer (IC1571) are

amplified by AF AMPs (IC241), the amplified AF signals

are applied to the VCA (IC231) to be adjusted its signal

level. The level-adjusted AF signals are output from [ACC1]

socket.

3 - 2

Page 9

3-2 TRANSMITTER CIRCUITS

MAIN UNIT

The MAIN UNIT contains transmit circuits; from MIC AMP to

modulator cicuit.

CTRL BOARD

The CTRL BOARD mainly contains circuits for parameter

detection of TX signal; Forward Wave, Reflected wave,

Reactance, Resistance, antenna current and voltage.

• TX AF CIRCUITS

The audio signals from the microphone (MIC signals)

are amplified by MIC AMP (IC171) and level-adjusted by

VCA (IC171). The level-adjusted MIC signals are passed

through the MIC mute SW (IC201) and MIC line selector

(IC211) which selects the MIC line; MIC signals from the

microphone jack on the FRONT UNIT, or from [ACC1]

socket on the MAIN UNIT.

The MIC signals are then applied to the limiter AMP (IC221)

which limits the amplitude of MIC signals. The amplitudelimited MIC signals are applied to the ADC (IC1251) via the

unbalance-balance convert circuit (IC1311, 1321, 1331),

to be converted into the 24-bit serial data. The serial data

is applied to the DSP (IC1001) and processed as digital

audio signals. The processed digital audio signals are then

applied to the Digital to Analog Converter (DAC; IC1501) to

be converted into the analog audio signals; as the 36 kHz

1st TX IF signal. The 1st TX IF signal is entered to the RF

UNIT.

RF UNIT

RF UNIT contains transmit circuits; TX mixers and AMPs.

The 36 kHz 1st TX IF signal from the MAIN UNIT is applied

to the 1st TX mixer (IC503) to be mixed with the 491 kHz

3rd LO signal from the PLL UNIT, to be converted into

the 455 kHz 2nd TX IF signal. The converted 2nd TX IF is

amplified by the 2nd IF AMP (Q501), filtered by 2nd TX IF

filter (FI1501 for BW=20 kHz or FI1502 for BW=4 kHz). The

filtered 2nd TX signal is amplified by 2nd IF AMP (Q504),

and applied to the 2nd TX mixer (D505) to be mixed with the

64 MHz 2nd LO signal from the PLL UNIT, to be converted

into the 64.455 MHz 3rd TX IF signal. The converted 3rd

TX IF signal is passed through the BPF (FI503), amplified

by 3rd IF AMP (Q506), and filtered by the LPF. The filtered

3rd TX IF signal is applied to the 3rd TX mixer (D506) to

be mixed with the 3rd LO signal from the PLL UNIT, to

be converted into the 4th TX IF signal (=TX signal). The

converted TX signal is filtered by the LPF, amplified by RF

AMP (Q508), passed through one of BPFs, then applied to

the YGR AMP (Q801).

TX signal from the FILTER UNIT is passed through several

detection circuits in sequence, then applied to the antenna

[ANT1]–[ANT4].

• FOR (Forward Wave) voltage detection circuit

A portion of TX signal is rectified by current trans (L101) and

diode (D102), and the produced DC voltage is composed

by C103, C106 and C116 to detect FOR voltage (Forward

wave components). The detected voltage is amplified by

IC101 and applied to the A/D port of CPU (IC1).

• REF (Reflected Wave) voltage detection circuit

A portion of TX signal is rectified by current trans (L101) and

diode (D101), and the produced DC voltage is composed by

C102, C105, C115, C120 and C121 to detect REF voltage

(Reflected wave components). The detected voltage is

amplified by IC101 and applied to the A/D port of CPU (IC1).

• Reactance components detection circuit

A portion of TX signal which is detected by current trans

(L151) and TX signal which is divided by C153 and C158

are amplified by C-MOS IC. This AMP, as the first stage,

employs a C-MOS type AMP to detect the low TX signal.

The inverter AMP requires input level lower than others

need, and provides high speed operation for stable high

frequency operation with low TX signal.

The amplified signal is adjusted its wavefor m, then applied

to the IC155 and IC156 for phase comparison. The output

signal is rectified by D153 and D154, composed and

amplified by IC201, then applied to the A/D port of the CPU

(IC1).

• Resistance components detection

A portion of TX signal which is detected by current trans

(L201) and TX signal which is divided by C202, C205 and

C206 are adjusted so that two of these are the same on the

voltage. And two of these are rectified composed each other

to detect the resistance components. When the detected

voltage is increased, Q201 is activated to amplify the signal

for high detection sensitivity.

The amplified TX signal is entered to the PA200W BOARD.

PA200W BOARD

• TX AMPLIFIERS

The TX signal from the RF UNIT is amplified by the RF AMP

(Q101), Pre-drive (Q201), drive (Q301) and power (Q401A,

B) amplifiers in sequence, to obtain TX output power. The

power-amplified TX signal is entered to the FILTER UNIT.

FILTER UNIT

• TX FILTERS

The power-amplified TX signal from the PA200W BOARD

is passed through one of BPFs (according to the TX

frequency) to remove unwanted signals including harmonic

components. The filtered TX signal is then entered to the

CTRL BOARD.

3 - 3

Page 10

3-3 FREQUENCY SYNTHESIZER CIRCUITS

PLL UNIT

PLL UNIT provides LO signals; 1st LO for TX/RX IF circuits,

2nd RX LO (64.491 MHz), 2nd TX LO (64 MHz), 3rd TX LO

(491 kHz), marker frequency (100 kHz), reference frequency

for the SCOPE UNIT (40 MHz) and clock signal for the DSP

UNIT (12.888 MHz). These LO signals are generated by the

reference signal from the OSC UNIT as reference.

This transeiver employs the Direct Digital Synthesizer (DDS)

which digitally creates arbitrary waveforms and frequencies

from a fixed source frequency, to provide extremely high

resolution and stability frequency and pure wavefor m.

• Reference frequency signal

The 10 MHz reference frequency signal generated on

the OSC UNIT is applied to the 4th harmonic extractor

(Q702, L702, 703) via buffer (Q30) to produce the 40 MHz

reference signal.

• 1st LO signals

The 40 MHz reference signal from the harmonic extractor

is amplified by Q101, and applied to the DDS (IC101)

as the clock signal. The DDS generates the 10.4122038

–10.4963312 MHz sine waves, and these are passed

through the ceramic filter (FI101; Fc=10.7 MHz) to adjust

the wavefor m, then applied to the PLL IC (IC201) via buffer

(Q151).

<2nd TX LO signal>

The VCO output signal from the hybrid divider is passed

through the ATT, and applied to the 2nd LO AMP (Q591).

The amplified VCO output signal is passed through the BPF,

then entered to the RF UNIT as the 2nd TX LO signal.

<2nd RX LO signal>

The VCO output signal from the hybrid divider is passed

through the ATT, and applied to the 2nd LO AMP (Q801).

The amplified VCO output signal is passed through the ATT

and, applied to the 2nd LO mixer (D821) and mixed with

the 491 kHz 3rd TX LO signal from the 3rd TX LO oscillator

(IC651), to convert into the 64.491 MHz 2nd RX LO signal.

The converted 2nd RX LO signal is passed through the

ATT and BPF, and applied to the 2nd LO AMP (Q831). The

amplified signal is entered to the RF UNIT as the 2nd RX

LO signal.

• 3rd TX LO signal

The 40 MHz reference signal from the harmonic extractor

is amplified by IC652, and applied to the DDS (IC565) as

the clock signal. Using the clock signal, the DDS directly

generates the 491 kHz 3rd TX LO signal.

The output signal of DDS is passed through the LPF and

HPF, and applied to the buffer AMP (Q680). The bufferamplified 2rd TX LO signal is entered to the RF UNIT via

ATT.

The PLL IC (IC201) controls the oscillating frequency

of 6 VCOs (VCO1 to VCO6) using the reference signal

generated by the DDS as reference frequency.

VCO

VCO1 Q220 64.485–72.454999 MHz

VCO2 Q230 72.455–79.454999 MHz

VCO3 Q240 79.455–86.454999 MHz

VCO4 Q250 86.455–94.454999 MHz

VCO5 Q260 94.455–109.454999 MHz

VCO6 Q270 109.455–124.455 MHz

Oscillator

component

Oscillating frequency

The output signals of each VCOs (1st LO signals) are

buffer-amplified by Q301, passed through the HPF and

LPF, then amplified by the 1st LO AMPs (Q302 and Q351).

The amplified 1st LO signals are buffer-amplified by Q352,

passed through the LPF, HPF and ATT, then output to the

RF UNIT as 1st LO signals (64.485–124.455 MHz).

• 2nd LO signals

The 40 MHz reference signal from the harmonic extractor is

amplified by IC503, and applied to the DDS (IC501) as the

clock signal. The DDS generates the reference frequency

which controls the oscillating frequency of 64 MHz VCO

(Q541).

The output signal of 64 MHz VCO (Q541) is buffer-amplified

by Q561, and applied to the hybrid divider.

The hybrid divider divides the VCO output into two; 2nd TX

LO and 2nd RX LO.

• DSP system clock

The 40 MHz reference signal from the harmonic extractor

is amplified by IC1651, and applied to the DDS (IC1652)

as the clock signal. Using the clock signal, the DDS directly

generates 12.288 MHz system clock signal. The system

clock signal is passed through the LPF and HPF, and

applied to the buffer (Q1680). The buffer-amplified system

clock signal is entered to the MAIN UNIT via ATT.

• Scope clock

The 40 MHz reference signal from the harmonic extractor is

amplified by Q1601, and entered to the SCOPE UNIT.

3 - 4

Page 11

3-4 MAIN CPU (IC604) PORT ALLOCATIONS

Pin

No.

Clock signal to 4094/LMX2306 (PLL UNIT).

42

(DDS for 1st LO PLL-IC/DDS, 2nd TX LO DDS, 3rd TX LO)

"Serial data to 4094/LMX2306 (PLL UNIT).

43

(DDS for 1st LO PLL-IC/DDS, 2nd TX LO DDS, 3rd TX LO)

44 N/C O

45 Mode status (1Lo or T2Lo) output. O

46 Chip select siganl to PLL. I/O

47 Strobe to the PLL. O

51 Clock signal to units other than PLL and SCOPE. O

52 Serial data (other than PLL, SCOPE and DSP). O

53 N/C O

54 CI-V format data (UART). O

55 CI-V format data (UART). I

56 Clock to the DSP IC. O

57 Seral data (TXD/RXD) to the DSP. O

58 START signal to the TUNER UNIT (UART, 9600). O

142 Serial data to the DAC (BU9480) for ext. S-meter. O

140 Clock (A-clock) to the DAC (BU9480) for ext. S-meter. O

138 Clock (B-clock) to the DAC (BU9480) for ext. S-meter. O

137 Power line for liner circuit control signal. O "H"=Power ON

113 Forword wave detected voltage (A/D). I

114 Refl ected wave detected voltage (A/D). I

115 ALC fedback voltage (A/D). I

116 Drain current (fi nal amp.). I

117 Drain voltage (fi nal amp.). I

118 PA UNIT temparature. I

119 Cooling fan motor current. I

120 Voltage from key pad (rear panel). I

133 Serial data to the FRONT CPU (UART, 38400). O

134 Serial data from the FRONT CPU (UART, 38400). I

135 CW/RTTY keying signal to the DSP. O "L"=Key pushed

81 Mute control signal. I "H"=Mute

82 TX power line control signal. O "L"=TX

83 Noise pulse. I

105 RX power line control signal. O "L"=RX

3 Serial communication with the scope DDS (AD9857) detect signal. O "H"=detected

33 Serial data to the SCOPE UNIT DDS/PLL/DSP. O

34 Strobe to the scope PLL (LMX2306). O

59 Chip selet signal to the scope DDS (AD9857). O "L"=AD9875 is slected

60 Profi le (0/1) select signal to the scope DDS (AD9857). O "H"=Profi le 1 is selected.

61 Clock signal to the DDS/PLL/DSP. O

121 DSP data (TXD/RXD). I

122 Hand shake signal from SCOPE DSP. I

123 Extra port for SCOPE DSP. I

124 Serial data from SCOPE DSP. I

125 N/C I

126 Through signal from the TUNER UNIT. I "H"=Through

127 Key input from the tUNER UNIT. I "H"=Tuner ON

128 Straight key input (A/D). I "L"=Key pushed

Description

IN/

OUT

O

O

Condtion

3 - 5

Page 12

3-4 MAIN CPU (IC604) PORT ALLOCATIONS (continued)

Pin

No.

23 Clock to the EEPRROM (HN58X2464TI). O

24 Serial data from the EEPRROM (HN58X2464TI). I/O

26 Clock signal to the EEPROM (DIGISEL UNIT; CAT24WC256). O

27 Serial data from/to the EEPROM (DIGISEL UNIT; CAT24WC256). I/O

30 RTTY keying. I "H"="space" is marked

31 Transverter control signal from the [ACC] connector. I

21 PLL unlock signal. I "L"=Unlocked

5–

Address bus lines. O

20

73–

Data bus lines. I/O

71

84 WAIT signal (bus line control). I "L"=Wait.

85 SEND signal. O "L"=TX

86 Dual Port SRAM intrude signal. I

87 "L" indicator control signal (bus control). O "L"= lights.

88 "H" indicator control signal (bus control). O "H"= lights.

89 READ data (bus contol). O

90 Address data (bus contol). O

94 PTT/ACC SEND input. I "H"=TX

107 Squelch signal to the [ACC] connector. O

109 Squelch signal. O

35 External SEND (lead relay) signal output. O "H"=Relay ON

36 External SEND (IC relay) signal output. O "H"=Relay ON

37 Chip select signal to the Dual Port SRAM. O "L"=SRAM is selected.

38 Chip select signal to the expander. O

Description

IN/

OUT

"L"= Transverter is

"H"= Squelch open (RX

"L"= Squelch open (Mute

"L"= Expander is

Condtion

activated.

LED lights)

OFF)

selected.

3 - 6

Page 13

SECTION 4 ADJUSTMENT PROCEDURE

4-1 PREPARATION

¤ REQUIRED EQUIPMENTS

EQUIPMENT SPECIFICATION EQUIPMENT SPECIFICATION

Spectrum analyzer

RF power

(terminated type)

Frequency Counter

Modulation

Analyzer

Audio Generator

Frequency range : At least 90 MHz

Bandwidth : 100 kHz or more

Measuring range : 10–300 W

Frequency range : 1.8–100 MHz

Impedance : 50

SWR : Less than 1.2 : 1

Frequency range : 0.1–100 MHz

Frequency accuracy :

Input level : Less than 1 mW

Frequency range : 30–300 MHz

Measuring range : 0 to ±10 kHz

Frequency range : 300–3000 Hz

Output level : 1–500 mV

Ω

±0.5 ppm or better

Digital multimeter

Standard Signal

Generator (SSG)

AC Millivoltmeter Measuring range : 10 mV to 10 V

External Speaker

Attenuator

CAUTION!: BACK UP originally programmed contents (Memory channels, Common settings, etc.) in the transceiver before

starting adjustment. When all adjustments are completed, these contents in the transceiver will be cleared.

Input impedance : 50 kΩ/DC or more

Measuring range : Voltage: 0.1–10V

Current: 5A/30A

Frequency range : 0.1–100 MHz

Output level : 0.1 µV to 32 mV

(–127 to –17 dBm)

Input impedance : 8

Capacity : More than 5 W

Power attenuation : 50 or 60 dB

Capacity : More than 200 W

Ω

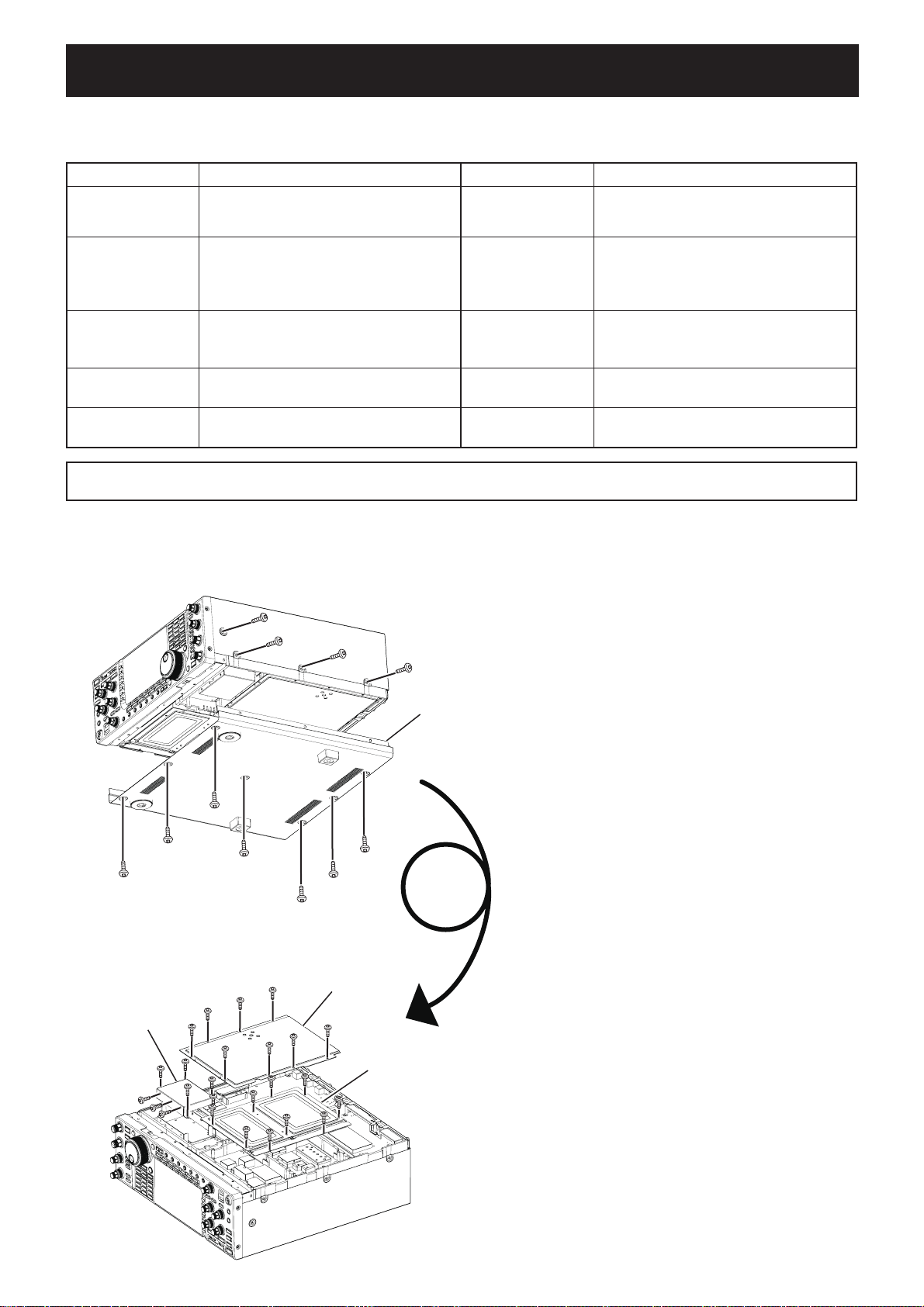

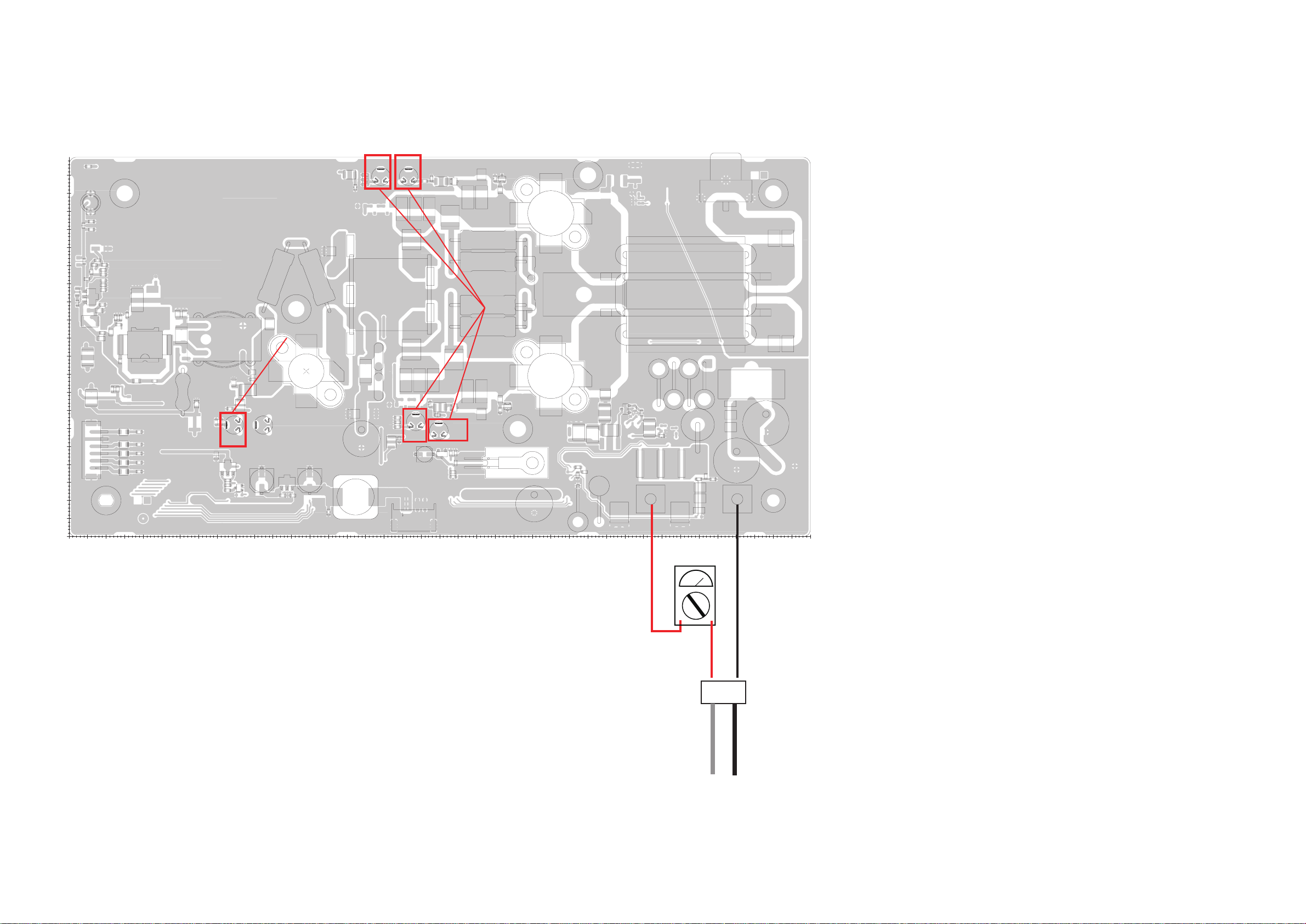

¤ EXPOSING UNITS

CAUTION: The transceiver weighs approx. 22.5 kg (50 lb). Always have two people available to carry, lift or turn over the transceiver.

1) Remove 8 screws from the both sides.

2) Remove 7 screws from the bottom, then remove the

bottom cover.

Bottom cover

OSC UNIT cover

RF UNIT cover

PLL/SCOPE UNITs cover

3) Turn over the transceiver.

4) Remove 8 screws from the RF UNIT cover, 10 screws

from the PLL/SCOPE UNITs cover and 10 screws

from the OSC UNIT cover, then remove those covers.

4 - 1

Page 14

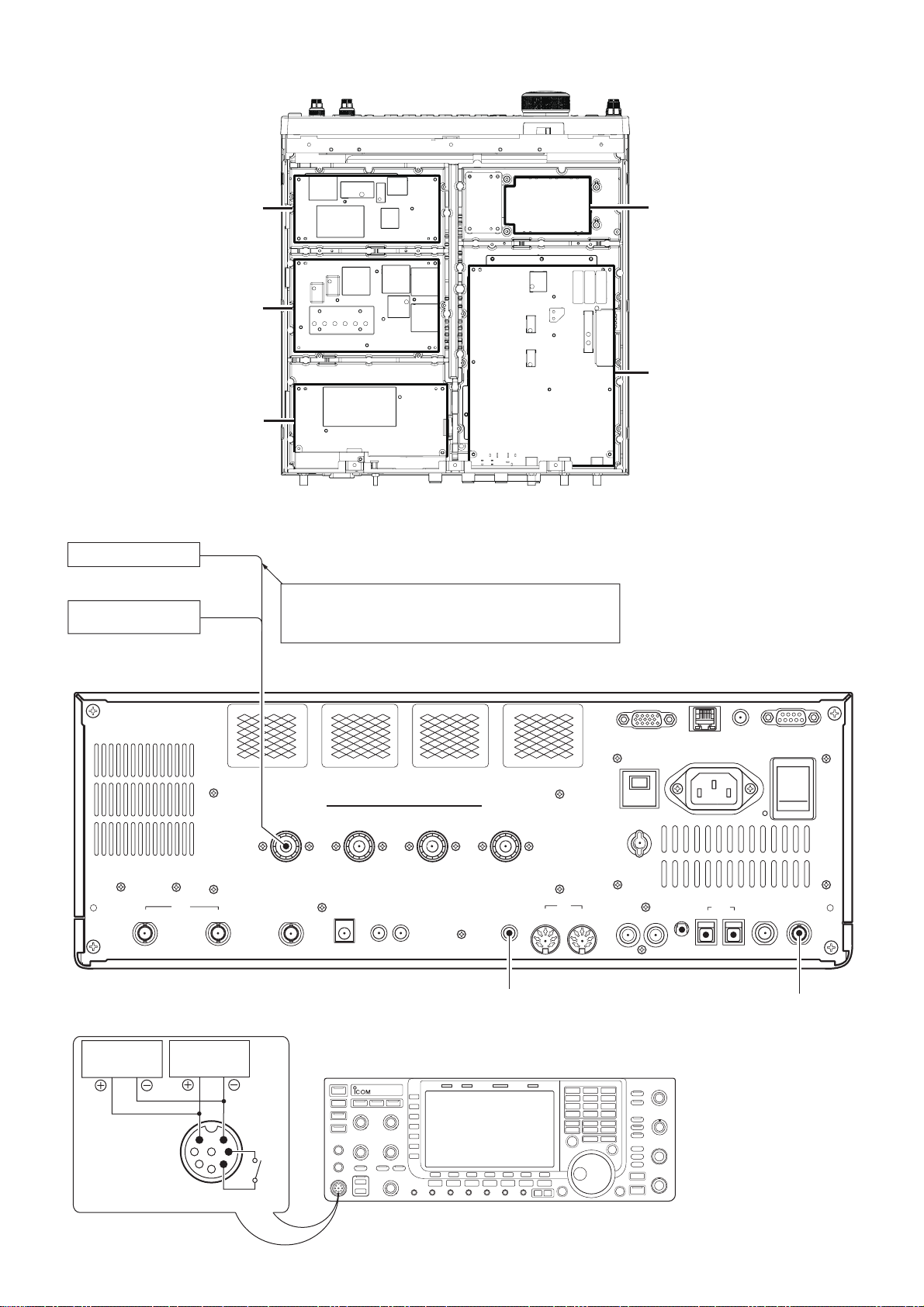

¤ UNITS LOCATION

<Bottom view>

SCOPE UNIT

PLL UNIT

MAIN UNIT

¤ CONNECTIONS

SSG

RF power meter

OSC UNIT

RF UNIT

CAUTION !

DO NOT select an TX adjustment item while an SSG

is connected to the antenna connector.

AC millvolt

meter

RX ANT

Audio

generator

<Rear view>

CW KEY

-

RS

232C

I

REF I/O

10MHz

-

10dBm

SSG

AC

S/P DIF

REMOTE

INOUT

EXT-DISPLAY

15A

ANT 1 AN T 2 ANT 3 ANT 4

DC OUT

INOUT

X-VERTER

15V

MAX1A

METER

EXT

KEYPAD

EXT-SP

ACC

12

GND

ALC

ALCRELAY

ADJ

SINAD METER

(for adjustments on the OSC UNIT)

<Front view>

[MIC]

PTT

4 - 2

Page 15

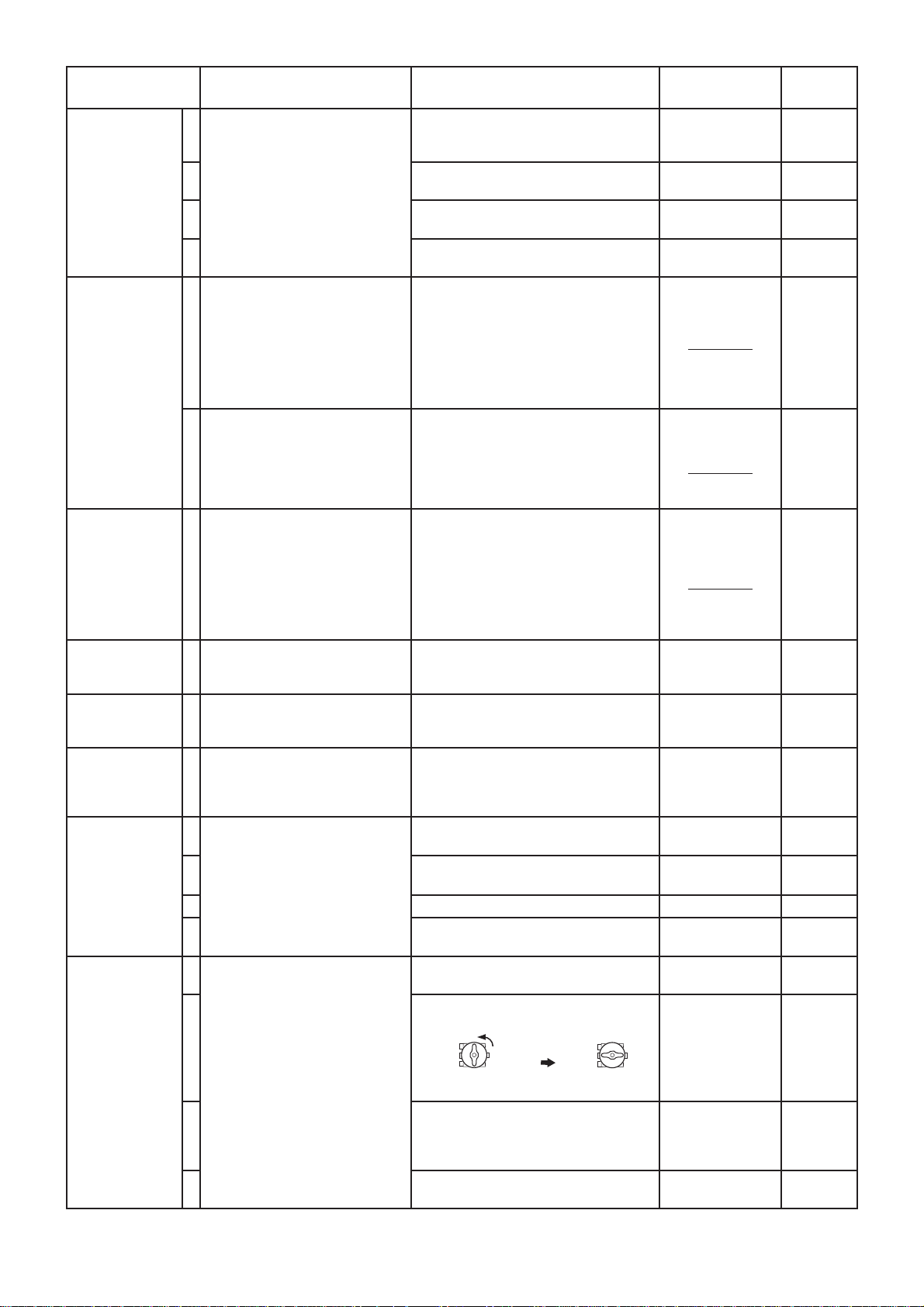

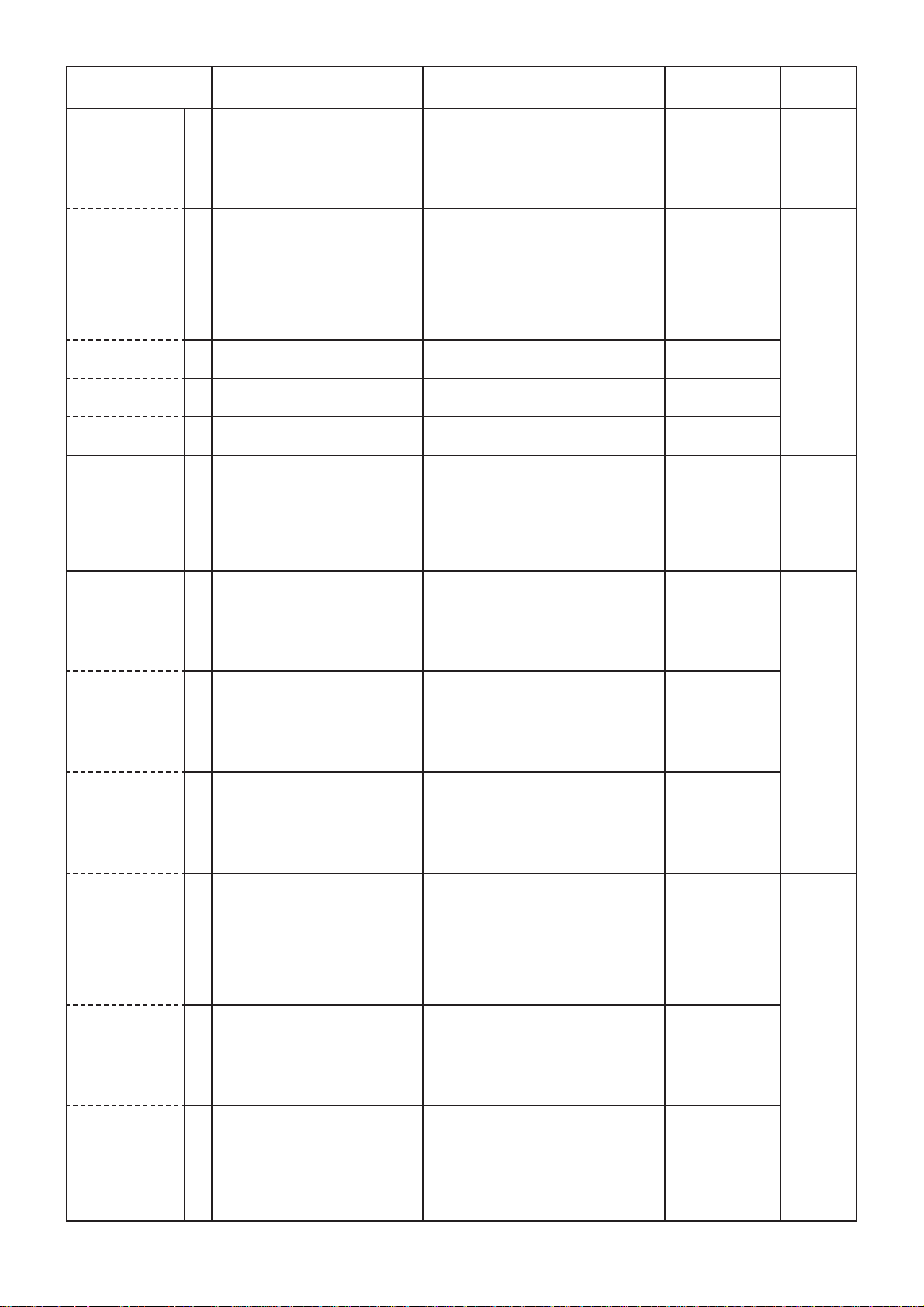

4-2 ADJUSTMENTS ON THE OSC UNIT AND PLL UNIT

ADJUSTMENT ADJUSTMENT CONDITION OPERATION

REFERENCE

SIGNAL LEVEL

REFERENCE

SIGNAL LEVEL

(40MHz)

HPL

LOCK VOL T A GE

(VCO1)

(VCO2) 2 • Frequency : 14.999 MHz

(VCO3) 3 • Frequency : 21.999 MHz

(VCO4) 4 • Frequency : 29.999 MHz

(VCO5) 5

(VCO6) 6 • Frequency : 60.000 MHz

1st LO

OUTPUT LEVEL

2nd LO

LOCK VOL T A GE

RX 2nd LO

LEVEL

TX 2nd LO

LEVEL

1 • Reference signal source :

External

• Receiving

1 • Receiving 1) Connect a Spectrum Analyzer to

1 • Frequency : 7.999 MHz

• Mode : USB

• Receiving

• Mode : USB

• Receiving

• Mode : USB

• Receiving

• Mode : USB

• Receiving

• Frequency : 44.999 MHz

• Mode : USB

• Receiving

• Mode : USB

• Receiving

1 • Frequency : 14.999 MHz

• Mode : USB

• Receiving

1 • Frequency : 14.100 MHz

• Mode : USB

• Receiving

1 • Frequency : 14.100 MHz

• Mode : USB

• Receiving

1 • Frequency : 14.100 MHz

• Mode : USB

• T r ansmitting

1) Connect an Standard Signal

Generator to J1071 ([EXT-REF I/O]

terminal on the rear panel) and set

as;

Frequecy : 10.000 MHz

Level : –10.0 dBm

Modulation : None

2) Connect a Spectrum Analyzer to

J1072.

3) Adjust the REF signal level with

L1061 and L1062.

CP701 (PLL UNIT).

2) Adjust the REF signal (40 MHz)

level with L702 and L703.

1) Connect a Digital multimeter to CP2

"LV2" (PLL UNIT).

2) Adjust the lock voltage with C222.

1) Connect a Digital multimeter to CP2

"LV2" (PLL UNIT).

2) Adjust the lock voltage with C232.

1) Connect a Digital multimeter to CP2

"LV2" (PLL UNIT).

2) Adjust the lock voltage with C242.

1) Connect a Digital multimeter to CP2

"LV2" (PLL UNIT).

2) Adjust the lock voltage with C252.

1) Connect a Digital multimeter to CP2

"LV2" (PLL UNIT).

2) Adjust the lock voltage with C262.

1) Connect a Digital multimeter to CP2

"LV2" (PLL UNIT).

2) Adjust the lock voltage with C272.

1) Connect a Spectrum Analyzer to

J351 "1LO" (PLL UNIT).

2) Adjust the output level with R357.

1) Connect a Digital multimeter to CP3

"LV3" (PLL UNIT).

2) Adjust the lock voltage with C546.

1) Connect a Spectrum Analyzer to

J831 "R2LO" (PLL UNIT).

2) Adjust the output level with L801

and L834.

1) Connect a Dummy Load to [ANT1].

2) Connect a Spectrum Analyzer to

J561 "T2LO" (PLL UNIT).

3) Adjust the output level with L565

and L566.

ADJUSTMENT

POINT

L1061, L1062

(OSC UNIT)

(repeatedly)

L702, L703

(PLL UNIT)

(repeatedly)

C222

(PLL UNIT)

C232

(PLL UNIT)

C242

(PLL UNIT)

C252

(PLL UNIT)

C262

(PLL UNIT)

C272

(PLL UNIT)

R357

(PLL UNIT)

C546

(PLL UNIT)

L801, L834

(PLL UNIT)

(repeatedly)

L565, L566

(PLL UNIT)

(repeatedly)

VALUE

Maximum

level

Maximum

level

3.9–4.1 V

3.9–4.1 V

3.9–4.1 V

3.9–4.1 V

3.9–4.1 V

3.9–4.1 V

2.35–2.85

dBm

1.7–2.3 V

Max. level

(–20.0

dBm ±3.0

dB)

Max.

level

(3.0 dBm

±3.0 dB)

4 - 3

Page 16

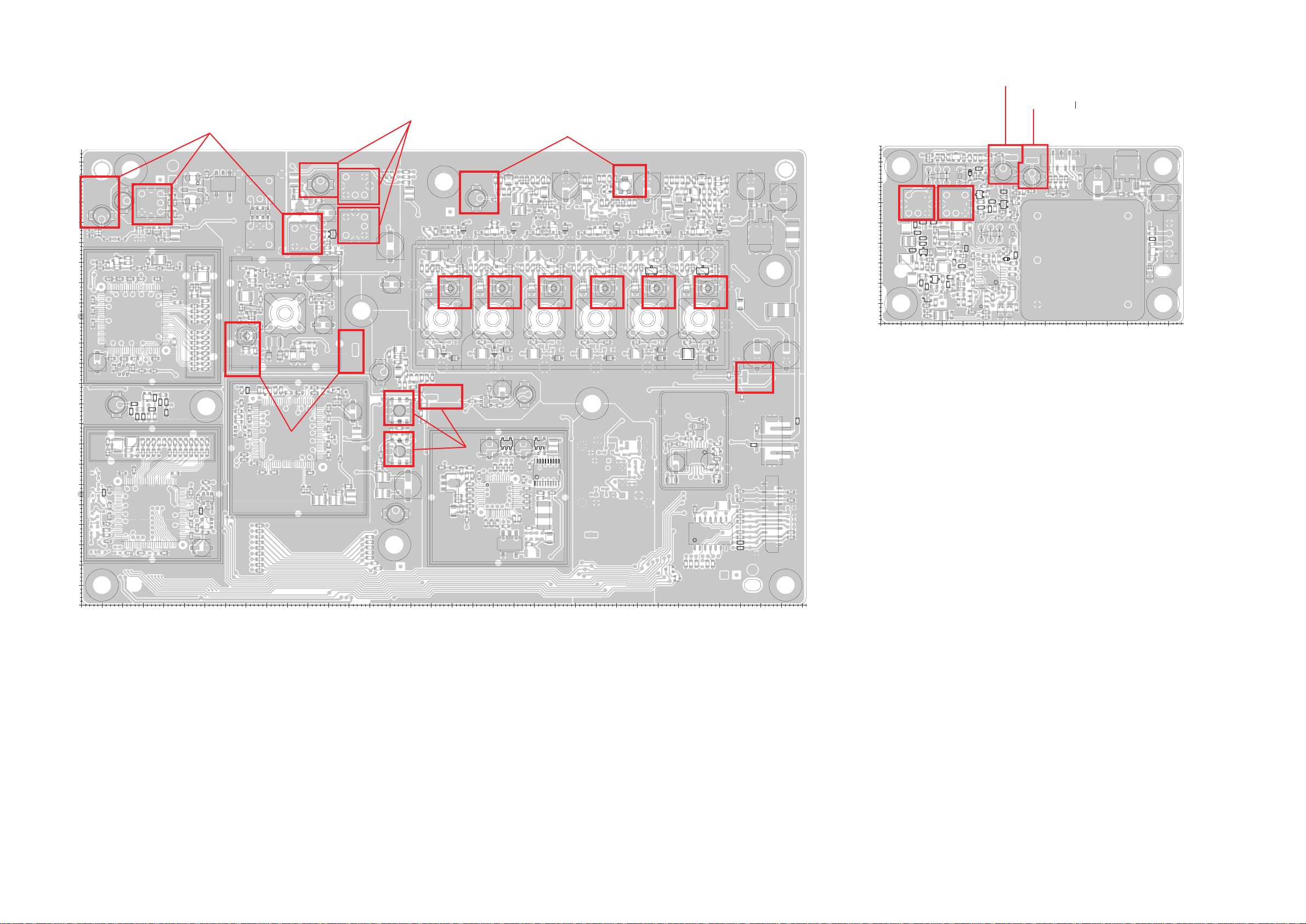

L1061

L1062

J1072

J1071

From SG

To RF voltmeter

CP2

HPL lock voltage check

C232

(VCO2)

C222

(VCO1)

R357

1st LO level adjustment

L703

Reference signal level (40MHz) adjustment

L702

CP701

C272

HPL lock voltage adjustment

(VCO6)

C262

(VCO5)

C252

(VCO4)

C242

(VCO3)

J351

C546

2nd LO lock voltage adjust

CP3

L834

L801

L565

L566

TX 2nd LO level

adjustment

J831

J561

RX 2nd LO level

adjustment

- ADJUSTMENT AND CHECK POINTS -

• PLL UNIT (TOP VIEW)

• PLL UNIT

(TOP VIEW)

RX 2nd LO level

adjustment

1

C831

R2Lo

J831

TO RF J1651

R692

R691

R690

C691

J831

C692

R686 R687

C668 C669 C670 C671 C672

C666

C663 C664

C653

DACK

TOMAINJ801

R1680

C1670

R1707

R1706

C1669

T3Lo

J681

R812

R814

TO RF J501

C811

R689

Q680

R685

R688

C690

C654 C655 C657 C658

C1684C1685

C661

MP1651

L1682

C1671 C1672 C1673

IC652

J1681

C1682

C1683

C1668

C1667

L1681

R1691

R1692

IC651

R656

C1666

C1691

C660

R1690

C1681

R693

Q1680

R1686

R1689

C1692

C1680

R1679

R1676

R1678

IC1652

Q831

C834C835

R834R835

L834

L834

C813

Q811

L812

C812

L683

C687

C686

C688C689

C667

C665

C659

R657

C1689

9

R1687

R1688

R1693

R1685

C1690

MP1653

R1673

R1675

R1677

R1664 R1665

R1666 R1667

R1668 R1669

R1670 R1671

R1672

R1674

C1661

C1664C1665

L831

FI831

C838

C832

MP651

C684C685

L682

C682

C683

L681

C681

C680

R679 R680

R677 R678

R675 R676

R673 R674

R671 R672

R669 R670

R667 R668

R665 R666

R663 R664

R661 R662

R659 R660

R658

R655

2nd LO lock voltage adjust

R1656R1657

R1658 R1659

R1660 R1661

R1662 R1663

R1651

C1651

IC1651

R1652

C1652

R1694

C1659 C1660

IC1701

R1705

C1711

C1655 C1656

C1658

R565

MP653

R546

L543

C549

C546

C550

C546

C545

C546

R580

R711

C526

C525

R506

IC503

R503

R504

D821

L801

Q561

R563

R564

Q541

R544

R545

C543

C580

C517C518C519

C520

EP1708

EP1701

EP1702

EP1703

EP1704

EP1705

EP1706

EP1707

EP1709

4

V0 V5 V10 V15 V20 V25 V30 V35 V40 V45 V50 V55 V60 V65 V70 V75 V80 V85 V90 V95 V100 V105 V110

H0H5H10

H20H25

H15

H30H35

H40H45

C566

R570

R561

C551

C547 C548

D542

Q580

R582

C504 C506

R573

R571

R572

L541

MP541

R581

MP501

L822

L821

C542

C581

TO RF J502

L801

R574 R575

L542

R556

IC501

H50

L562

R839

Q832

C553

R554

C559

C515C516

J561

C837

C554

Q540

R540

C540

R548

R550

C558

R509

C514

C507

C532

R522

L530 L531

H55H60

T2Lo

J561

C836

C802

C803

R803

R802

C541

C521

C552

R555

R537

C509 C510 C511 C512 C513

C533

TX 2nd LO level

adjustment

L566

C20

C21

L566

L565

L565

Q801

C801

6

CP3

CP3

J1601

TO SCOPE J3

LV3

C503

L501

L532

C1751

C1752

C1753

C1754

C1755

H65H70

10M

C1756

C1757

C703

C704

L701

L30

L703

R712

R704

L702

D501

Q502

C501

C502

R534

C535

C534

EP22

C22

EP21

EP20

C565

C593

L1603

C1613

C1612

C1611

L1602

C1609

SAD

L703

C712

C710

C709

L702

H75H80

L20

C1610

C1608

Q1601

C1607

R1608

C711

C705

J31

TO OSC

J1702

7

8

R272

L272

R270

C274

R274

C278

(VCO6)

L270

R1602R1606

R1607

C1601

C713

R709

R708

R710

1st LO level adjustment

J351

1Lo

J351

TO RF J351

C294

D272

R262 R263

R273

C293

C277

C273

C272

C272

D271

D270

CP701

R101 R102 R103

Q101

L102

C291

L262

C275

C263

C264

R260

R264

C262

R271

C276

C268

C272

(VCO5)

C260

L271

L260

CP701

R604

IC602

Reference signal level (40MHz) adjustment

C101

R104

R105

R108

C107

C108

C109

R106

C106

C102

C104

C103

C105

R107

C110

DIP

L451

C453

C441

C442

C444

C445

C446

C448

R364

R366

C447

R441

C451

C452

R365

L442

C361

C292

HPL lock voltage adjustment

C267

C262

C265

R261

C266

L452

D262

R252 R253

R254

D441

L252

C254

R250

C258

C262

(VCO4)

C250

L261

D261

D263

C604

R603

C124

C118

C111

L250

C605

TO RF J1001

C122

C123

C120

R109

R110

R111

R112

C117

C116

IC101

C115

C114

C119

R113

C112

C113

C128

R138

L103

C443

L441

R442

R443

C449

Q441

C290

C289

C257

C253

C252

C252

D250

J601

MKR

IC103IC104

L101

C121

IC102

R131R132

R133

FI101

L123

C255

R251

C256

C353

D252

R242 R243

R244

C252

L251

5

L242

C244

R357

R358

R359

C355

C357

C351

C352

Q351

L351

R352

R356

C356

C288

C287

C247

C245

C243

R240

C242

R241

C246

C248

C242

(VCO3)

C240 C241

L240

D240

LV1

CP1

R357

R357

R353

D242

C242

L241

MP221

R355

R234

C354

R232 R233

L232

C234

C230

L230

C311

R354

C286

C285

C239

C237

C233

R230

C232

C238

C232

(VCO2)

D231

C296

D230

MP101

B6724D

PLL

H90H95H100H105

H85

H110H115

H120

H125H130

H135

C309

C334

C335

C337

C341

C344

C310

L332

R341

C336

D341

L302

R343

L341

Q341

C284

Q280Q281Q282Q283Q284Q285

D232

R222 R223

C283

L222

C235

C223

C224

R220

R224

Q220Q230Q240Q250Q260Q270

C222

R231

C236

C228

C232

(VCO1)

C220 C221

L231

L220

MP201

R210

C219

C201

C203

C208

C206

R206

IC201

C202

L201

C2

R4R5R6

Q41

D201

176x113 t=1.6(2)

H145H150

H140

To RF voltmeter

From SG

• OSC UNIT

(TOP VIEW)

J1072

J1071

C1072

Q1070

C1008

C1048

L1044

Q1042

C1052

R1045

R1046

R1092

R1091

R1043

C1043

C1044

C1092

C1050

Q1043

C1074

R1044

EP1091

C1093

R1075

R1080

C1075

R1074

R1012

D1011

Q1011

C1018

C1017

R1064

R

R1068

Q1062

C1062

R1067

L1061

C1064

C1067

R1065

L1061

C1051

RL1010

EP1092

R1095

C1091

C1042

IC1091

R1099

C1094

R1100

IC1092

R1094

R1093

R1098

R1061

C6110

C1063

R1063

R1062

C1016

C1005

D1010

Q1061

C1004

Q1010

R1096

R1097

R1102

C1019

C1007

R1071

R1073

D1071

D1072

R1011

C1006

R1072

C1071

J1071

C2017

N

R2018

J2016

Q1012Q1013

C2016

R2017

X10

R2016

J2016

C1010

C1011

IC10

C1012

C1013

C1015

EP1010

C1014

EP1070

J2017

C1070

C1069

EP1069

Q1101

R1101

C1101

R1077

J1072

R1078

R1079

C1073

C1077

R305

L331

C302

R306R307

R304

C332C333

C301

C331

R301

R342

C342

C229

C227

C225

R221

C226

C222

D221

D220

R201

Q201

C212

C204

C205

R205

D205

IC2

R3

R19

C54

R303

Q301

C308

R302

D222

C51

C52C53

IC51

R51

L1062

3

C222

L280

R61

L221

C61

C64

C210

C209

C259

R17

R16

L2

R15

R14

R13

R11

R10

EP12

EP11

CP2

CP2

LV2

HPL lock voltage check

J2019

BROWN

TO DC-DC

J2018

J2019

C16

C15

C18

C17

EP10

C19

TO LOGIC

C14

EP13

J2018

2

H155

H160

H165

H170

H175

RL1011

L1062

C1031

C1066

C1030

L1024

C1047

C1028

L1021

R1027

C1026

C1025

Q1022

R1028

C1033

R1025

R1021

C1021

R1020

C1023

C1032

Q1021

R1023

R1026

R1024

C1024

Q1023

C1045

C1020

L1020

C1046

L1041

R1022

L1042

C1022

L1043

R1047

R1013

C1053

B6734B

L1023

C1027

L1022

V0 V5 V10 V15 V20 V25 V30 V35 V40

H0H5H10H15H20H25H30H35H40H45H50H55H60H65H70

4 - 4

Page 17

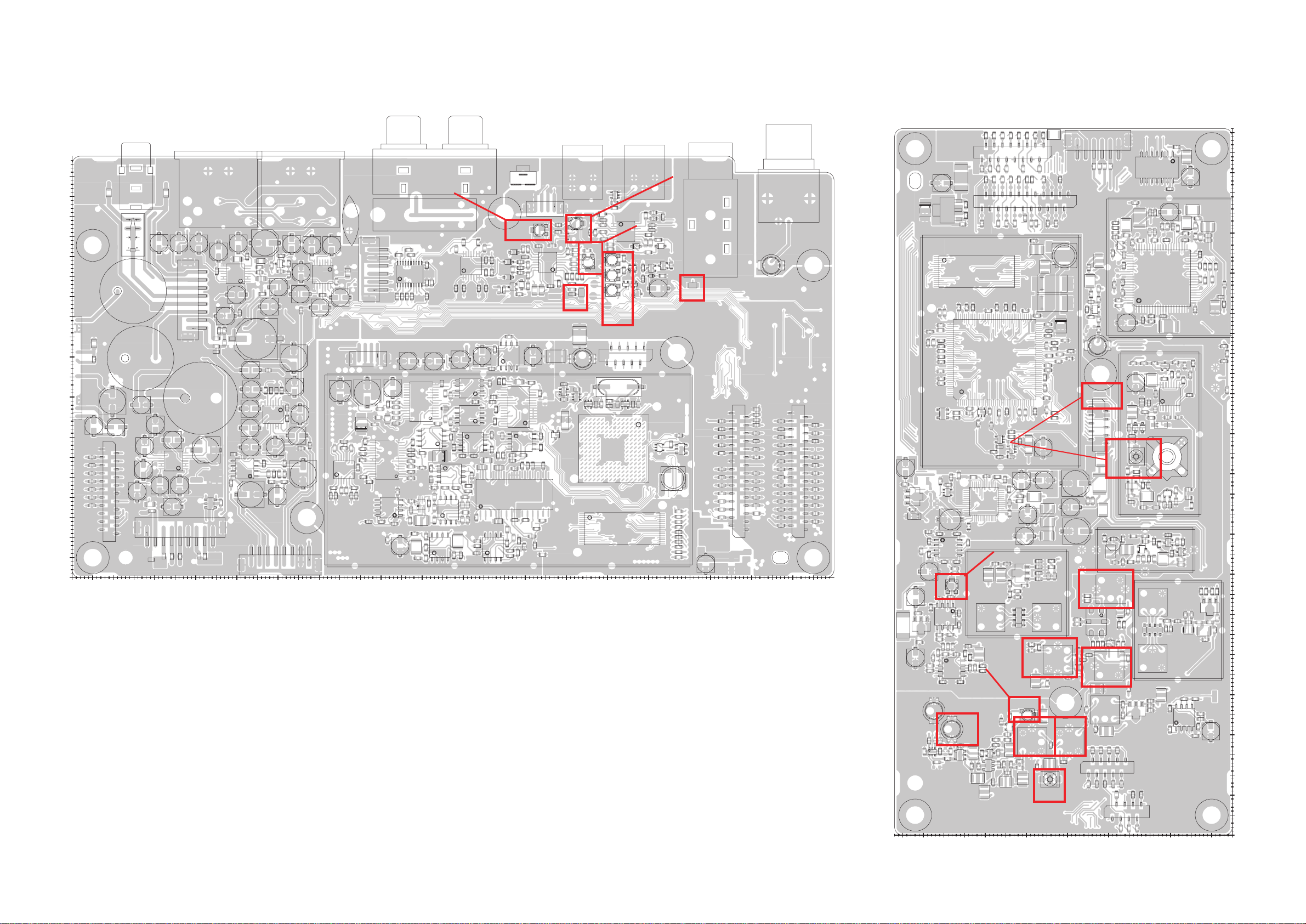

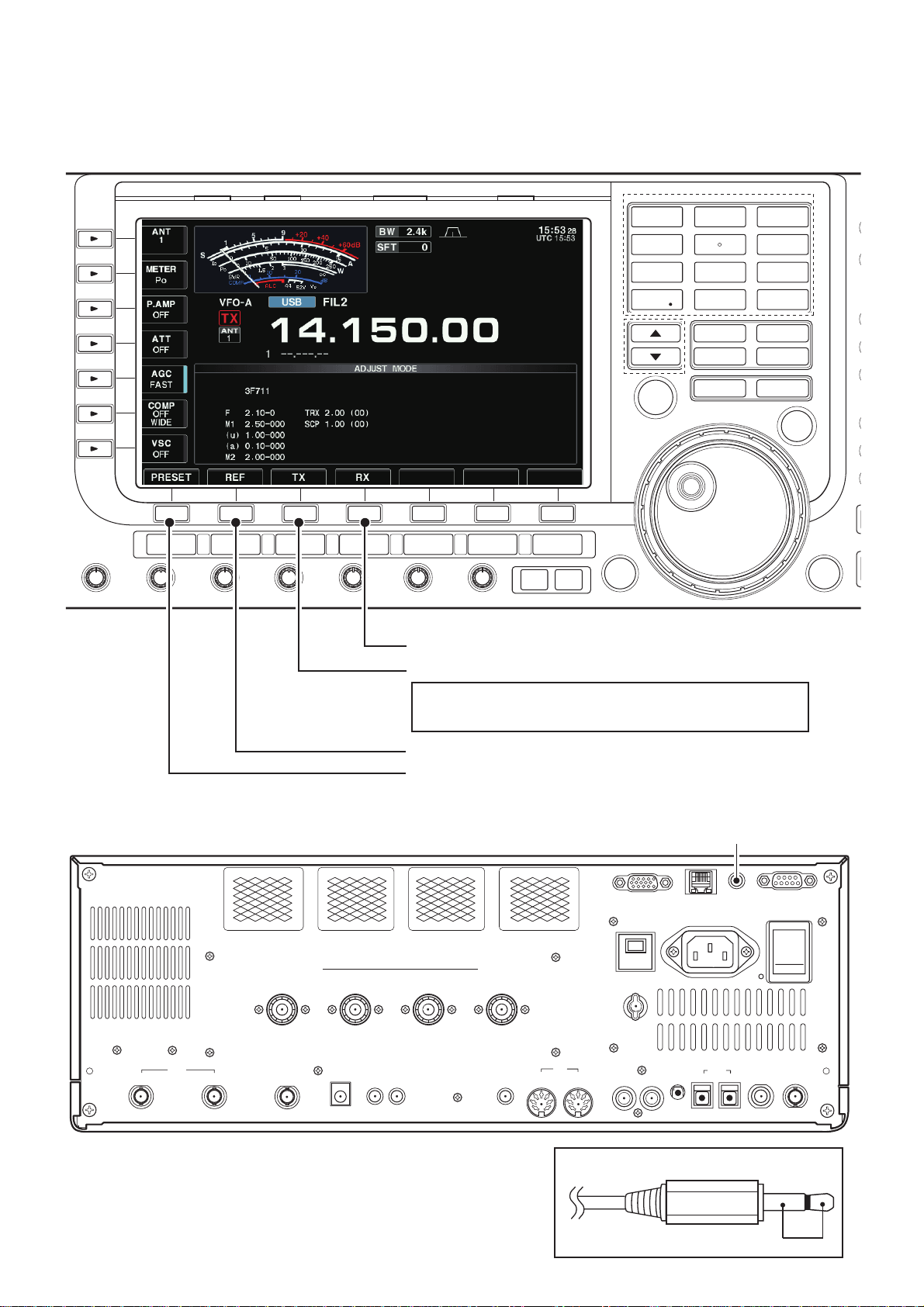

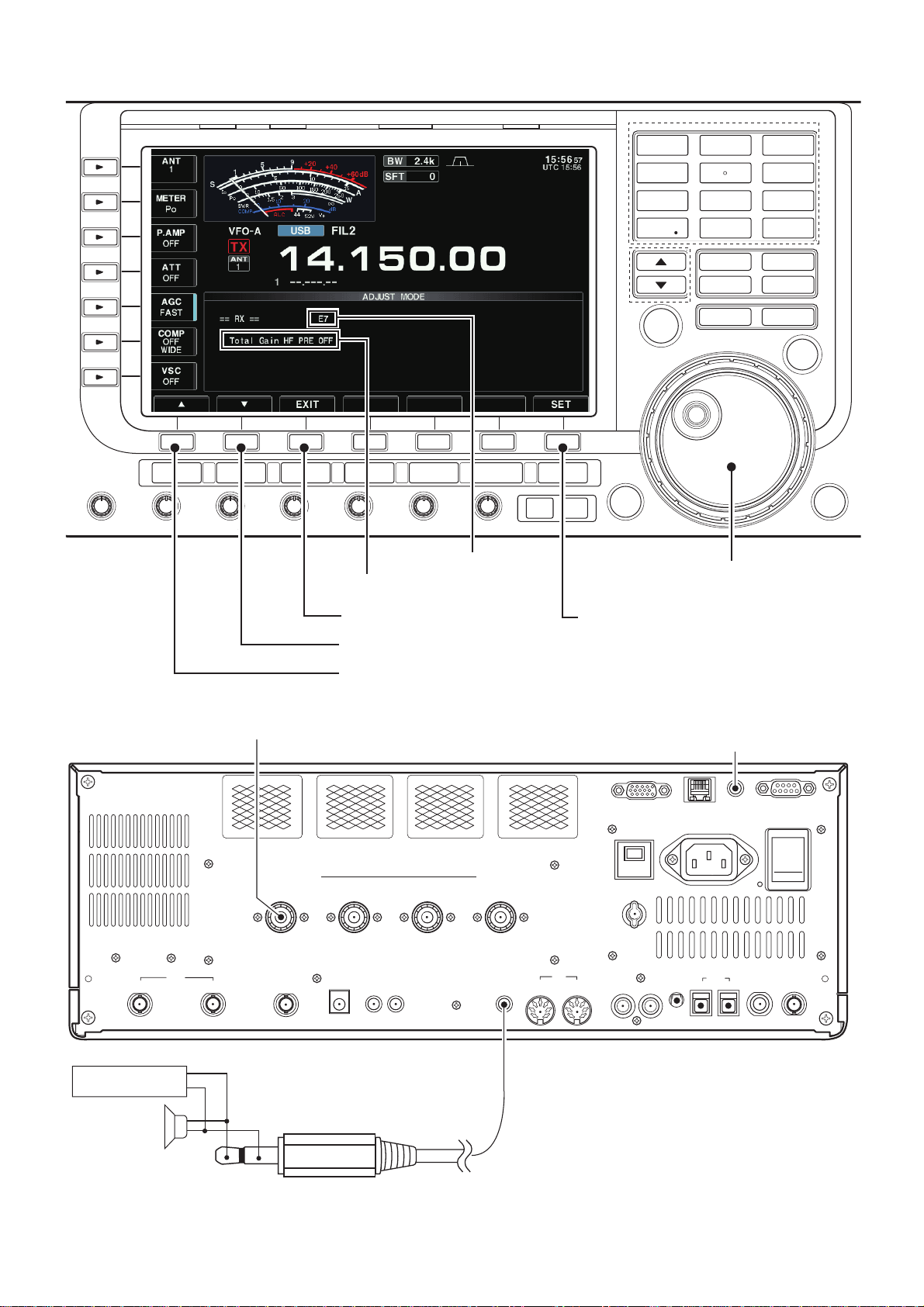

4-3 ADJUSTMENTS ON THE RF UNIT

s

ADJUSTMENT ADJUSTMENT CONDITION OPERATION

PRERARATION

(Preset)

(MCF-M) 4• Set the L1401 and L1402 as below.

(MCF-W) 5• Set the L1401 and L1402 as below.

(MCF-N) 6• Set the L1401 and L1402 as below.

1 • Frequency : 14.150 MHz

• Mode : USB

• ANTENNA : [ANT1]

2• Connect a Digital multimeter to

• [P.AMP1] : "ON"

• Receiving

• Connect a Digital multimeter to

CP1102" (RF UNIT).

CP1103" (RF UNIT).

3• Set R1228 (RF UNIT) to center

position.

Center position

3 rotation

Core

3.5 rotations

Core

ADJUSTMENT

POINT

R1101

(RF UNIT)

R1132

(RF UNIT)

R1228

(RF UNIT)

L1401, L1402

(MCF-M BOARD)

L1401, L1402

(MCF-W BOARD)

VALUE

4.4–4.6 V

4.4–4.6 V

Center

position

–

–

RECEIVE

SENSITIVITY

(HF BAND)

IMAGE

RESPONSE

RECEIVE

SENSITIVITY

(50 MHz BAND)

IF THROUGH

(50 MHz)

1 • Frequency : 14.150 MHz

• Mode : USB

• ANTENNA : [ANT1]

• Receiving

1 • Frequency : 14.150 MHz

• Mode : USB

• ANTENNA : [ANT1]

• Receiving

1 • Frequency : 50.0200 MHz

• Mode : USB

• ANTENNA : [ANT1]

• [PREAMP2] : "ON"

• Receiving

1 • Frequency : 50.0200 MHz

• Mode : USB

• Receiving

4.5 rotations

Core

1) Connect an SSG to the [ANT1] and

set as;

Frequecy : 14.1515 MHz

Level : 0 dBµ

Modulation : None

2) Connect an AC Millivoltmeter to the

[EXP-SP].

3) Adjust the sensitivity with L1408

and L1058.

1) Connect an SSG to the [ANT1] and

set as;

Frequecy : 14.0765 MHz

Level : +94 dBµ

Modulation : None

2) Connect an AC Millivoltmeter to the

[EXP-SP].

3) Adjust the sensitivity with R1516

and C1656.

1) Connect an SSG to the [ANT1] and

set as;

Frequecy : 50.0215 MHz

Level : –10 dBµ

Modulation : None

2) Connect an AC Millivoltmeter to the

[EXP-SP].

3) Adjust the sensitivity with L1222.

1) Connect an SSG to the [ANT1] and

set as;

Frequecy : 64.455 MHz

Level : +94 dBµ

Modulation : None

2) Monitoring the S-METER on the

display, adjust the swing width with

C1265.

L1401, L1402

(MCF-N BOARD)

L1408, L1058

(repeatedly)

(RF UNIT)

R1516, C1656

(RF UNIT)

L1222

(RF UNIT)

C1265

(RF UNIT)

–

Max. audio

output leve

Min. audio

output leve

Max. audio

output leve

Min.

swing

width

l

l

l

4 - 5

Page 18

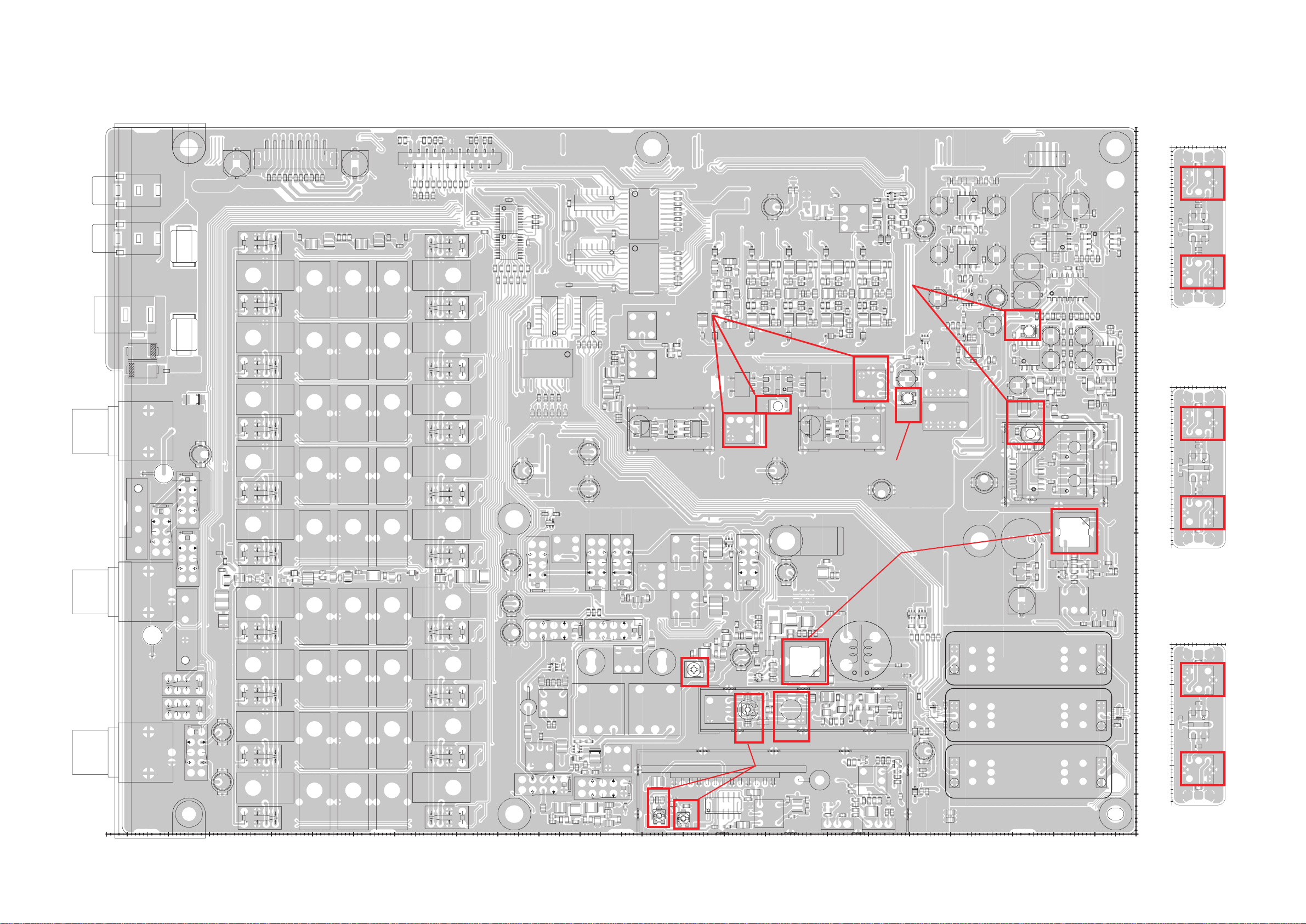

R1101

Preset

R1228

L1058

RX sensitivity adjustment

L1408

Image response adjustment

R1516

C1656

RX sensitivity

(50MHz)

adjustment

L1222

C1265

TX output power adjustment

L505

C576

L512

R538

TX total gain adjustment

R1132

IF through (50MHz)

adjustment

Preset

L1401

L1402

Preset

L1401

L1402

Preset

L1401

L1402

- ADJUSTMENT AND CHECK POINTS -

• RF UNIT (TOP VIEW)

KEYPAD

METER

J2001

D2001

DC-OUT

D2002

XVRT

RL381

RXANT-IN

RL410

RL431

RXANT-OUT

9

J2002J2003

EP2002

J103

RL352

J104

R405

J105

1

2002F1002F

2A

FUSE

C397

V

TO RF J810

R388

RL401

J391

RL351

R264

C287

R262

RL353

L268

R322

L326

E

TO CTRL J351

J106

RL402

J108

F

TO ANT-SW J3

C2010

RL2

L27

RL22

L57

RL52

L87

RL82

L117

RL112

L147

RL142

L177

RL172

L207

RL202

L237

RL232

L267

RL262

H175

• MCF-M BOARD

(TOP VIEW)

C2006

C2012

L25

L55

L85

L145

L294

L205

L235

L265

L3

C7

C297

L293

EP2004

J2006

TO MAIN J941

R1

R3

C272

J2007

C2007

C2013

C2015

C2016

C2017

EP2014

EP2015

EP2016

TO DC-DC J7

C10

6L5L

C2019

EP2017

RED

C8

C9

C11

L4

EP2018

EP2013

J2007

L26

L56

L86

L116

L115

L146

L295

L176

C302

L291

C283

L175

C304

D262

L292

C285

R263

Q260

C286

C303

R260

L296

L206

L236

L266

L24

L54

L84

L114

L144

L174

L204

L234

L264

EP2005

C2009

D260

EP2007

C2004

EP2006

EP2008

C2023

EP2010

EP2009

C2022

R2007

C2021

C276

J2006

R2008

R2009

R2010

L260

R261

C2018

C2020

EP2012

EP2011

R2011

R2012

C398

RL1

L23

R121

R122

R123

R101

R103

R105

R104

R135

201CI101CI

R134

R133

C399

R118

R120

R107

R108

R102

R106

R117

R119

RL21

C1724

L53

RL51

L83

L113

RL81

RL111

I

C1723

J351

TO PLL J351

R1706

C1722

8

L143

RL141

J102

RL902

R320

L320

G

J2004

L173

RL171

TO DIGISEL J1

J101

L203

RL201

IF through (50MHz)

TO DIGISEL J2

L1005

L1004

L233

RL231

L263

RL261

C1014

L1006

RL1006

4

4091C3091C

L1902

EP1901

IC1701

R1712

R1715

IC1703

R1720

R1721

R1722

C1717

C1718

C1720

C1721

C910C914

Q901

L905

RL1003RL1004

Q1005

EP1802

L1008

C1011

C1013

R1006

R1008

C1038

R1024

C1041

C1037

L1013

Q1205

D1001

R1018

R1002

C1001

R1019

L1052

R1056

L1053

C1054

C1053

C1057

C1067

C1055

C1056

7

R1909

C1202

L1015

R1133

R1134

L522

L1208

L1011

L1056

C1125

R1132

C577

D506

R1132

R576

R575

C574

R577

MP511

L1009

C1104

R1105

R1910

R1911

R1912

R1913

R1914

R1915

R1916

R1902

R1903

R1904

R1905

R1906

R1907

R1908

L646

R610

L513

L1213

0

42

1C

L1216

L1210

6

32

1C

C1250

L1228

C1266

C1265

C1265

R1228

CP1102

C1101

R1101

R1101

R1101

L650

L648

D619 D620

L1214

L1211

C1248C1249

R1203

R1135

C759

C756

C761

C755

L649

C751

C750

C749

C760

C745

L512

C1246

L1218

C1247

L1219

J1001

J601

TO PLL

L1220

IC1051

C1123

L651

L647

Q1701

C1241

IC1904

IC1903

IC1702

2091CI1091CI

2091C1091C

TX output power adjustment

L521

R1709

R1710

R1711

R580

C569

R579

C590

R578

L527

C568

C589

C567

L519

C565

L518

C566

C564

R562

L514

J503

W

J352

TO RF J1101

RL903

RL1201

L1201

C1201

R1211

EP1813

EP1814

EP1816

L1007

C1265

L1010

adjustment

EP1810 EP1811

C1034

L1054

R1071

C1032

R1055

C1071

R1132

C1073

L1071

C1072

L1072

EP1815

L1012

CP1103

RL1005

DIP

D

TO PA200W J1

J801

L644

L645

C758

C741

C740

C738

C739

L643

C737

R611

C733

C732

C734

C735

C747

L641

L642

D617 D618

L510

C576

C576

L512

J808

RX sensitivity adjustment

RL1202

R1210

R1209

C1215

C1244C1245

L1217

C1214

R1208

C1268

D1201

R1316

C1083

M

IC1081

C1252

Q1212

R1227

R1228

R1232

R1226

Q1211

C1251

R1228

Preset

R1104

C1124

R1103

C736

R1315

C743 C744

C731

C729

C1256

T

R1054

EP1832

C1084

C1085

EP1831

C742

R609

C730

FI503

C576

U

L1060

CP802

R820

R821

R819

C807

R817

CP801

D616

L639

C722

C723

C718

C719

L637

D615

D614

C726

L640

L634

C725

C727 C728

Image response adjustment

C724

C706

C707

L638

L633

C720

R608

C721

C717

C716

C702

C703

C715

L636

L632

C713

C714

D613

L509

L508

TX total gain adjustment

TO SCOPE J11

MP506

6

C1360

L1353

R1360

TO SCOPE J1

R1151

L1063

C1066

C1070

C1074

L1058

R1314

L1307

L1223

C1312

L1301

RX sensitivity

C1302

C1303

L1222

L1103

R1107

C1122

R1114

Q1101

L1101

C1102

L1062

C1062

C1061

L1222

L1055

L1102

C1103

J1301

C1064

C804

L803

L635

C709

C708

C704

C701

C700

L631

R613

C1357

C1305

C1304

D505

C1306

C710

C711 C712

C705

R607

C699

C698

C697

R614

R612

L505

MP502

L1058

C1153

L1303

L1302

C1314

R1302

R1111

R1113

L1105

R1122

C1126

C1106

L629

C690

C691

L628

C686

C687

L627

D611 D612

MP1058

C1307

Q1301

Q1102

R1118

C1111

R1117

R1119

C1112

J502

R1116

L1304

C1110

L1104

L630

C685

C684

L626

C801

L801

R801

C802

C693

C692

C689

L505

R1304

R1123

D801

C695 C696

C688

C682 C683

J

L1305

C1116

C1109

R1121

R811

Q804

Q805

R810

R816

R815

R814

R813

C814

R812

C813

C816

D802

C694

R606

C681

R534

C539

R537

C540

R538

R538

L507

TO PLL J561

EP1092

EP1093

L1151

C1405

C1093

C1308

R1307

C1309

(50MHz)

MP1301

C1310

C1313

20

1

1D1011

W

R1124

Q1105

R1126

C1117

C1118

D

R1127

C1115

C1113

Q1104

TO RF J391

J810

C507

C513

C520

Q509

Q503

R538

C506

R509

C512

C519

R518

C522

FI502

IC501

R508

C510

C511

IC502

R516

R517

C521

IC503

C518

C525

R519

R585

Q501

C526

C527

R525

R504

R505

C503

C505

V

FI501

RF

TO PLL J831

B6721D

5

Q1702 Q1703

C1091 C1092

EP1091

EP1833

EP1835

EP1837

C1403

C1406C1407

adjustment

IC1402

021

9211

1C

R

J1101

R1130

TO RF J352

C1121

9

8

1

2

11C

11R

R1073

R1072

MP1101

TO MAIN J831

J1501

R501

R502

R503

C501

C502

C508

C509

R506

R507

C515

C514

TO PLL J681

J501

R510

L

C517

R1516

C524

R1516

C523

R523

L504

R524

C528

R526

R527

R1517

C1517

R1529

C1507

C1656

C1508

C1656

C1655

R1657

J1651

K

C1659

IC1704

C1706

MCF-W BOARD

J1405

MCF-M BOARD

J1403

MCF-N BOARD

J1401

IC1506

R1540

C1536

C1530

C1523

R1524

R1533

1351R0351R

C1526 C1527

R1523

C1522

R1522

R1536

IC1505

41

51

R3

15

1R2

C1512 C1513

151

R

3

C1537

C1538

R1541 R1543

R1661

R1539

C1663

R1662

C1535

EP1505

R1519

C1515

C1516

R1515

R1518

C1514

C1511

R1506

C1509

C1521

2051CI1051CI

R1501

J1501

C1540

C1539

C1541

C1531

C1534

C1529

R1532

R1534

R1535

R1516

C1528

4051CI3051CI

C1525

R1527

R1528

R1525

C1524

2051Q1051Q

C1503

C1504

L1501

C1519

C1656

L1652

R1665

R1658

8561C7561C

R1660

IC1651

R1659

MP1652

C1703

L1408

R1409

C1429

W1411

C1441

R1411

R1412

L1408

C1704C1705

Q1402

C1428

R1408

R1402

Q1403

L1407

C1423

J1406

J1404

J1402

2

IC1652

R1675

R1520

R1508

C1520

R1521

R1507

C1506

R1504

C1502

MP1408

C1433

R1413

C1431

C1421

R1544

R1511

R1503

C1505

C1518

C1501

L1405 L1406

R1415

C1420

C1662

R1663

R1677

R1502

IC1403

C1510

R1509 R1510

C1418

H155H160H165H170

H140H145H150

H90H95H100H105H110H115H120H125H130H135

MP1651

H85

H65H70H75H80

H50H55H60

H20H25H30H35H40H45

H15

H0H5H10

V0 V5 V10

H0H5H10H15H20H25H30H35

L1401

MCF-M

C1404 C1405

B6739A

L1402

TUONI

• MCF-N BOARD

(TOP VIEW)

V0 V5 V10

H0H5H10H15H20H25H30H35

L1401

MCF-N

C1404 C1405

B6740A

L1402

TUONI

• MCF-W BOARD

(TOP VIEW)

V0 V5 V10

H0H5H10H15H20H25H30H35

L1401

MCF-W

C1404

B6722A

L1402

TUONI

V0 V5 V10 V15 V20 V25 V30 V35 V40 V45 V50 V55 V60 V65 V70 V75 V80 V85 V90 V95 V100V105V110V115V120V125V130V135V140V145V150V155V160V165V170V175V180V185V190V195V200V205V210V215V220V225V230V235V240V245V250

C1401

C1403

C1402

C1406

C1407

C1408

C1401

C1403

C1402

C1406

C1407

C1408

C1401

C1402

C1406

C1408

FI1401

FI1401

FI1401

MIDDLE

Preset

2041L1041L

NARROW

Preset

2041L1041L

WIDE

Preset

2041L1041L

4 - 6

Page 19

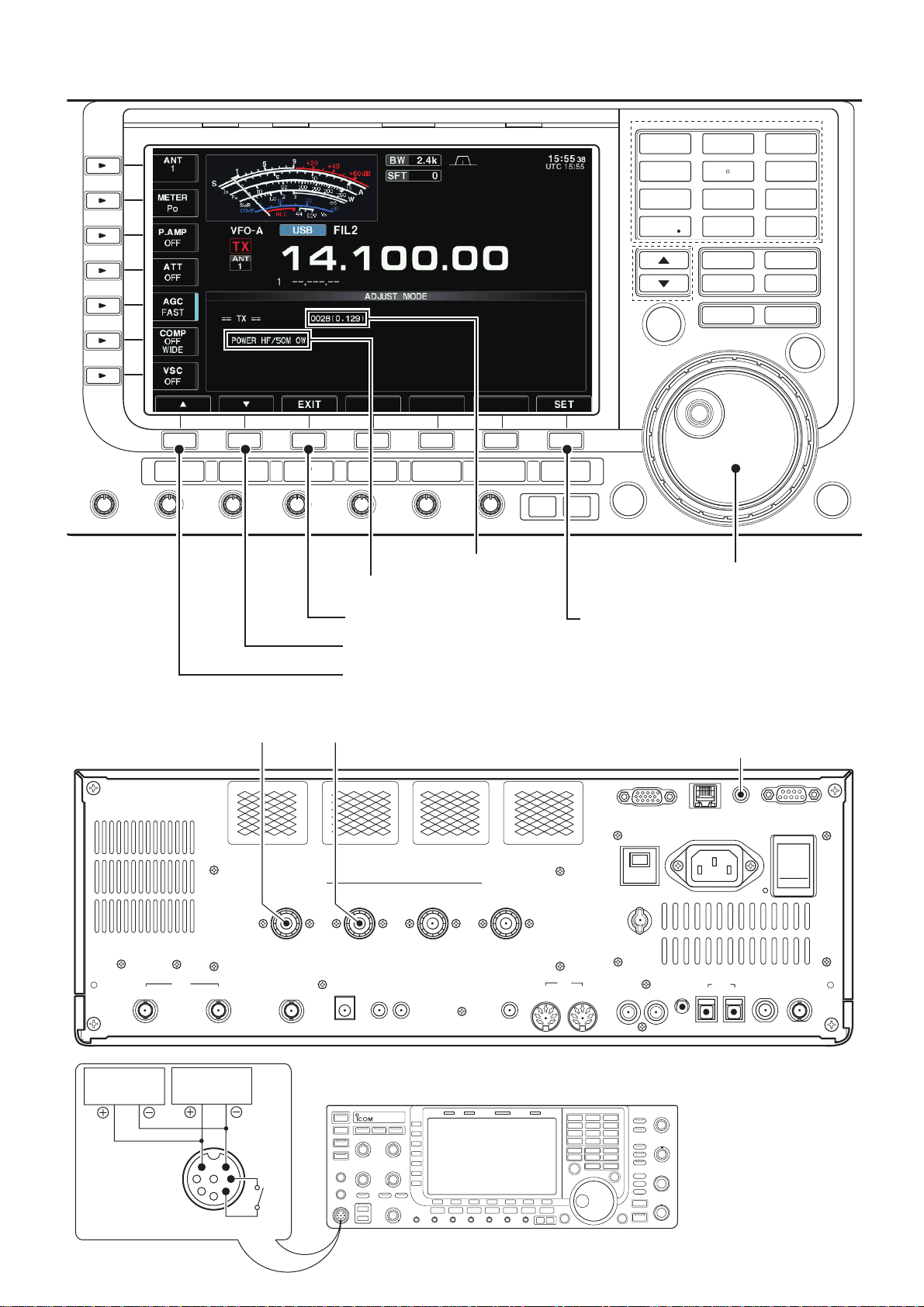

4-4 ADJUSTMENTS ON THE PA200W BOARD

ADJUSTMENT ADJUSTMENT CONDITION OPERATION

IDLING

(Preparation)

IDLING

(DRIVER AMP.)

"IDLING" must be adjusted by cold-started.

1 • Mode : USB

• MIC gain : Minimum

2 1) Set 3 variable resisters to the preset

1 • Frequency : 14.100 MHz

• Mode : USB

• T r ansmitting

• Connect an Audio Generator to the

MIC jack (see the page 4-2) and set

it as;

Frequency : 1.5 kHz

Level : 1 mV

point.

2) Disconnect the W1 from the PA200W

BOARD, and connect an Ammeter

between the PA200W BOARD and

W1.

3) Measure the driving current, and

note it as the initial value.

• Adjust the driving current with R301.

ADJUSTMENT

POINT

––

R301, R407,

R410

R301

VALUE

Max.

counter

clockwise

+1.0 A

more than

initial value

IDLING

(FINAL AMP.)

1 • Frequency : 14.100 MHz

• Mode : USB

• T r ansmitting

2 R410 (for main

3 Apply slight vibration to the PA200W BOARD, and verify that the current is stable against the vibration.

• Adjust the driving current with

variable resisters.

R407 (for main

adjustment)

R425 (for critical

adjustment)

adjustment)

R426 (for critical

adjustment)

+2.0 A

more than

initial value

+3.0 A

more than

initial value

4 - 7

Page 20

Idling adjustment (Driver amp.)

R301

R407

R410

R425

R426

Idling adjustment (Final amp.)

- ADJUSTMENT AND CHECK POINTS -

• PA200W BOARD

(TOP VIEW)

C113

3

J1

DIP

R101

TO RF J801

C106

R107

TO MAIN J851

2

V0 V5 V10 V15 V20 V25 V30 V35 V40 V45 V50 V55 V60 V65 V70 V75 V80 V85 V90 V95 V100

H0H5H10H15

D

R102

R103

B6728A

R117

C102

C104

R113

R106

R105

C103

R104

C107

C108

R108

Q101

C110

C109

L101

C111

C112

R119

L102

J2

R203

C202

C114

R112

R111

R110

Q201

R201

C201

R115

R118

R202

L4

C4

L6

C6

L3

C3

L2

C2

L1

C1

J2

H20

PA200W

C204

C206

Idling adjustment (Driver amp.)

R205

L202

C305

L201

C207

C303

C307

C309

R301

R4

Q1

C8

R2

R1

H25H30H35H40H45

C301

R305

R302

L301

R301

Q2

R310

H50H55

R425

R407

L307

C403

R407

C405

C407

C318

C319

2

1

3

R

7

0

3

R

4

C311

L306

R401

R425

R423

R402

C401C402

C409

D401

C413

L401

D403D404

R403

C415

R416 R418

R420R422

C411

R408R409

R411

R413

Q401A

L403

J402

R427

Idling adjustment (Final amp.)

W401

L304

Q301

Q301

C314

IC2

C10

C12

C11

C9

H60

H65H70H75H80H85

C7

C317

L7

R309

L305

R410

L303

C408

C406

C404

C313

R404

R405

R410

J5

H90H95

R406

C414

L402

R424

D1

C17

GRAY

BLACK

TO DC-DC J8

C416

R412

R426

R426

R5

C16

C15

R7

R6

J5

H100H105H110

Q401B

R414

D402

C412

C410

5

R3

C513

H120H125H130

H115

Q401

Q401

R508

R514

H135

R563

R507

C507

6

C551

R551

R565

R552

R513

H140H145

EP501

C515

D551

H150

C553

R554

R523

GRAY

H155

R502

R564

C554

C

J401

TO FILTER J901

L404

L404

R501

R511

R512

W501

R521

R522

R503

C506

R504

C510

C511

C512

C514

H160H165H170H175

C503

C502

EP503

C501

C505

EP502

BLACK

L501

H180

C417

C419

H185H190

C504

1

7

C418

C420

H195

H200

Ammeter

–

+: Gray

+

W1

(from REG UNIT)

–: Black

4 - 8

Page 21

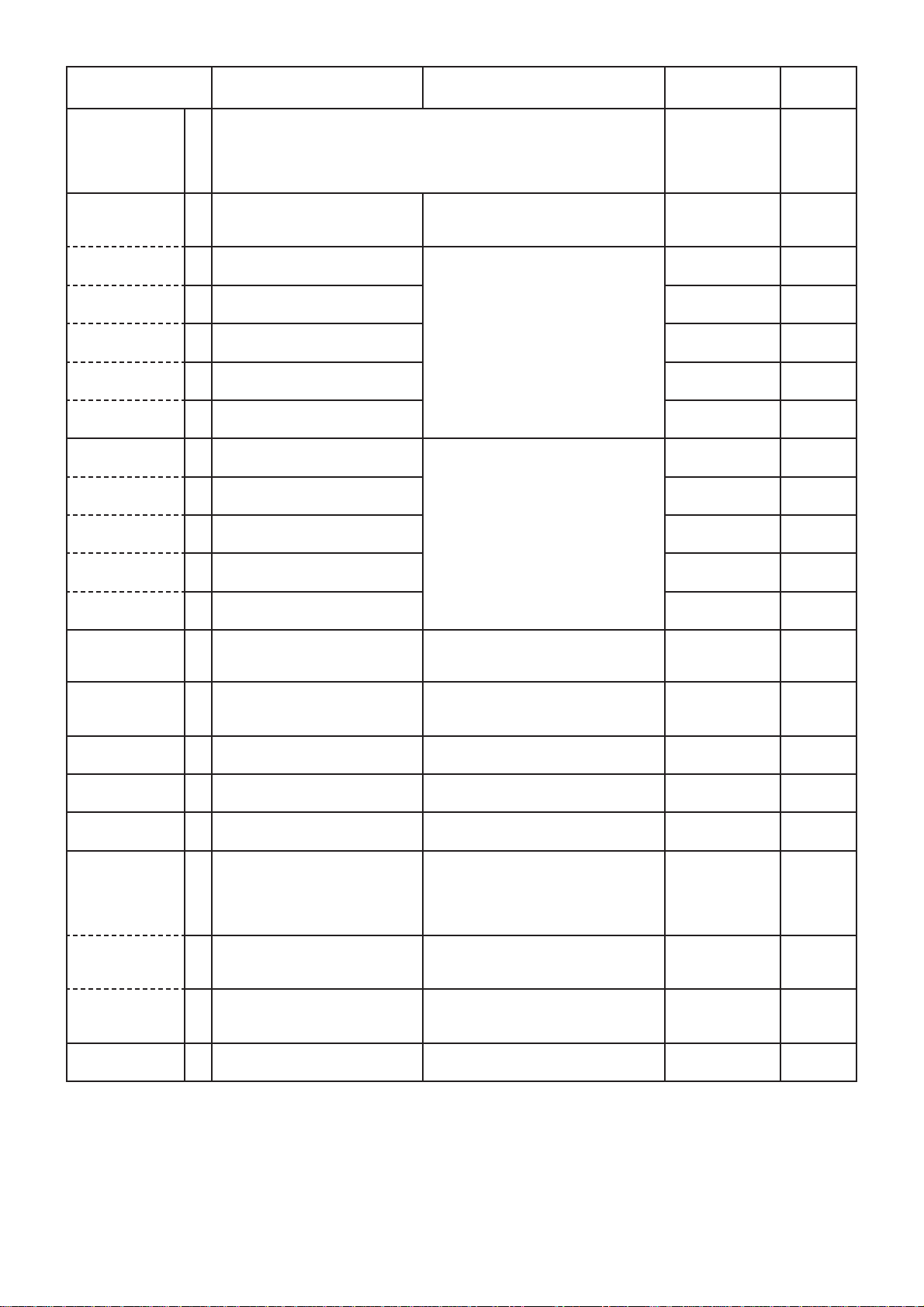

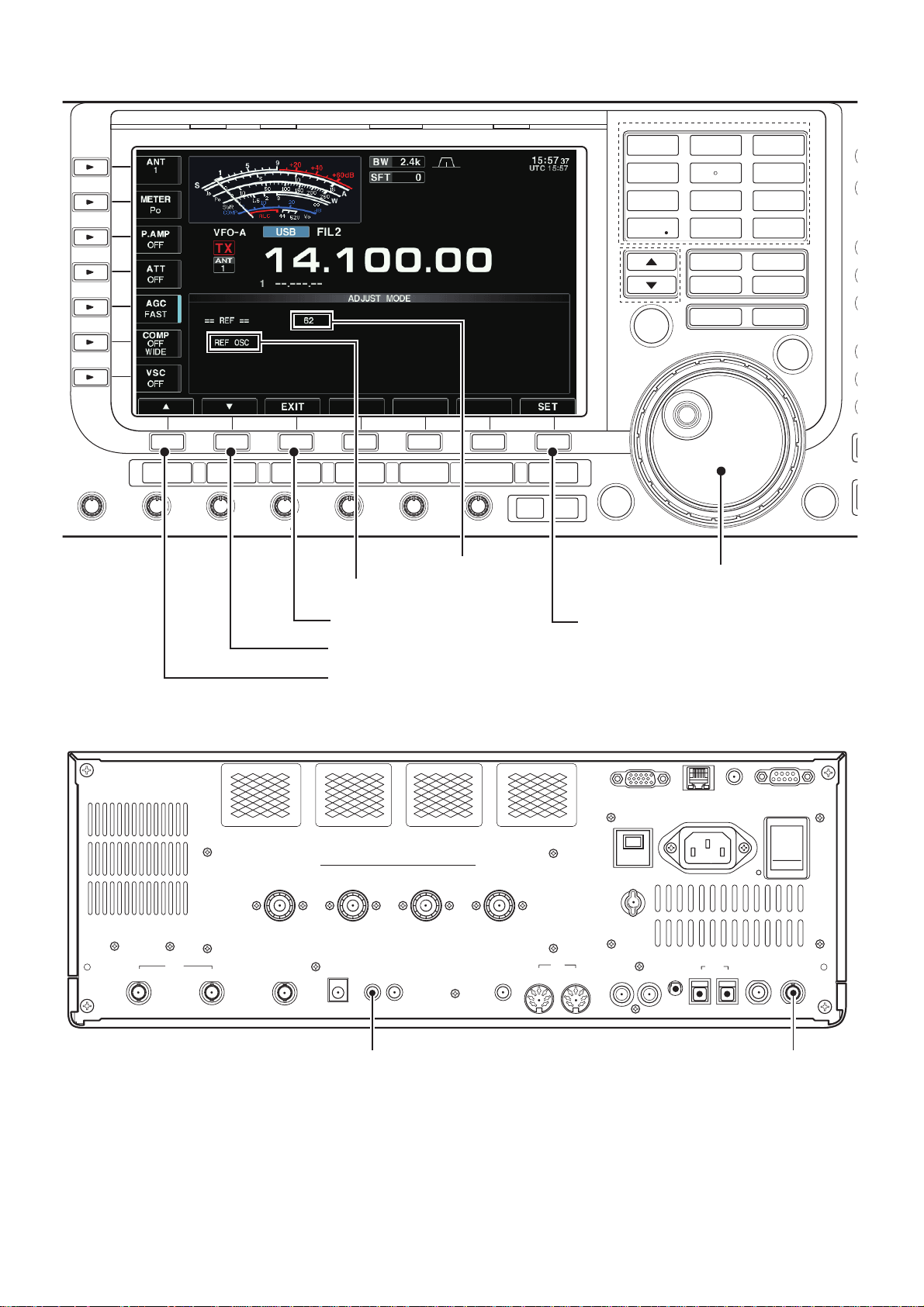

4-5 ADJUSTMENTS ON THE MAIN UNIT (including RF UNIT)

ADJUSTMENT ADJUSTMENT CONDITION OPERATION

PREPARATION

(Preset)

TRANSMIT

OUTPUT

POWER

TRANSMIT

TOTAL GAIN

TRANSMIT

HIGH POWER

(HF)

TRANSMIT

HIGH POWER

(50 MHz)

AM CARRYER

POWER

APC Vd

(Drain-Volatge)

APC Id

(Drain-Current)

1 • Receiving 1) Turn the power OFF.

2• Set the variable resister to the preset

3• Set the variable resister to the preset

3• Connect a Digital multimeter to the

1 • Frequency : 14.100 MHz

• Mode : USB

• T r ansmitting

2 • Frequency : 14.100 MHz

• Mode : FM

• MIC gain : Maximum

• T r ansmitting

1 • Frequency : 14.100 MHz

• Mode : USB

• MIC gain : Center

• T r ansmitting

1 • Frequency : 14.100 MHz

• Mode : RTTY

• T r ansmitting

1 • Frequency : 50.100 MHz

• Mode : RTTY

• T r ansmitting

1 • Frequency : 14.100 MHz

• Mode : AM

• MIC input : OFF

• T r ansmitting

1 • Frequency : 1.900 MHz

• Mode : RTTY

• T r ansmitting

2•

3 • Adjust the RF power with R2042. R2042 220 W

4 • Disconnect the CP2051 from the

1 • Frequency : 24.900 MHz

• Mode : RTTY

• MIC : OFF

2• Set the variable resister to the preset

• T r ansmitting

2) Push and hold [F-INP]+[MW] keys,

and turn the power ON (All clear).

point.

point.

CP2001.

1) Connect an Audio Generator to the

MIC jack (see the page 4-2) and set

it as;

Frequency : 1.5 kHz

Level : 1 mV

2) Connect an RF Power Meter to the

[ANT1].

3) Adjust the RF power.

1) Set the SSG as;

Frequency : 1 kHz

Level : 10 mV

2) Connect an RF Power Meter to the

[ANT1].

3) Adjust the RF power.

1) Connect an Audio Generator to the

MIC jack (see the page 4-2) and set

it as;

Frequency : 1.5 kHz

Level : 1 mV

2) Connect an RF Power Meter to the

[ANT1].

3) Adjust the RF power.

• Connect an RF Power Meter to the

[ANT1]. R2072 200 W

• Connect an RF Power Meter to the

[ANT1]. R2068 200 W

• Connect an RF Power Meter to the

[ANT1].

• Connect the CP2051 to the GND.

Turn the R2042 max. counter

clockwise.

GND.

• Connect the CP2051, CP2041 to the

GND.

point.

90° to CCW

(Center position)

ADJUSTMENT

POINT

––

R2042 Max. CW

R2006

R2028 0.3–0.7 V

L505→C576

L512

(RF UNIT)

(in sequence,

repeatedly)

C576

(RF UNIT)

R538

(RF UNIT)

R2065 50 W

CP2051

R2042

(CCW rotation)

CP2051

CP2051, CP2041

R2006

→

VALUE

3 o'clock

position

Maximum

output

power

Maximum

output

power

130 W

to the

GND

Max.

CCW

Disconnect

from GND

to the

GND

90° to

CCW

3• Disconnect the W1 from the PA200W

BOARD, and connect an Ammeter

between the PA200W BOARD and

W1.

4• Disconnect the CP2051 and CP2041

from the GND.

4 - 9

R2006

(CW rotatioin)

CP2051, CP2041

12.0 A

Disconnect

from GND

Page 22

S3LO LV adjustment

L201

Scope Gain adjustment

Scope Attenuation adjustment

L203

L202

L5L5L6

R11

C41

R416

Preset

TX power adjustment

R2072

R2068

R2065

Preset/APC(Vd) adjustment

CP2041

CP801

C824

Scope adjustment

Preset/APC(Id) adjustment

R2006

R2042

R2028

CP2051

- ADJUSTMENT AND CHECK POINTS -

J1

• MAIN UNIT

(TOP VIEW)

J751

EP752

2

C281

C271

C282

R282

C283

C285

C284

IC281

EP942

EP944

R946

R948

R950

J941

R951

R953

3

H5

H0

V0 V5 V10 V15 V20 V25 V30 V35 V40 V45 V50 V55 V60 V65 V70 V75 V80 V85 V90 V95 V100

RL261

H10

C286

TO RF J2006

J941

C334

J811

ORANGE

EP751

J741

C748

C287

C318

C316

C317

C315

C332

EP816

EP815