HYUNDAI MICRO ELECTRONICS

8-BIT SINGLE-CHIP MICROCONTROLLERS

GMS90X51C

GMS90X52C

GMS90X54C

User’s Manual (Ver. 1.0)

+<81'$,

Semiconductor Group of Hyundai Electronics Industrial Co., Ltd.

MicroElectronics

Version 1.0

Published by

MCU Application Team

HYUNDAI MicroElectronics All right reserved.

2001

2001

20012001

Additional information of this manual may be served by HYUNDAI MicroElectronics offices in Korea or Distributors and Representatives listed at address directory.

HYUNDAI MicroElectronics reserves the right to make changes to any information here in at any time without

notice.

The information, diagrams and other data in this manual are correct and reliable; however, HYUNDAI MicroElectronics is in no way responsible for any violat ion s of patent s or other ri gh ts of the t hird par ty generated by

the use of this manual.

GMS90X5XC Series HYUNDAI MicroElectronics

Device Naming Structure

GMS90X5XC

Mask ROM version

HYUNDAI MicroElectronics MCU

- GCXXX XX XX

ROM size

1:

2:

4:

Operating Voltage

C:L:4.25~5.5V

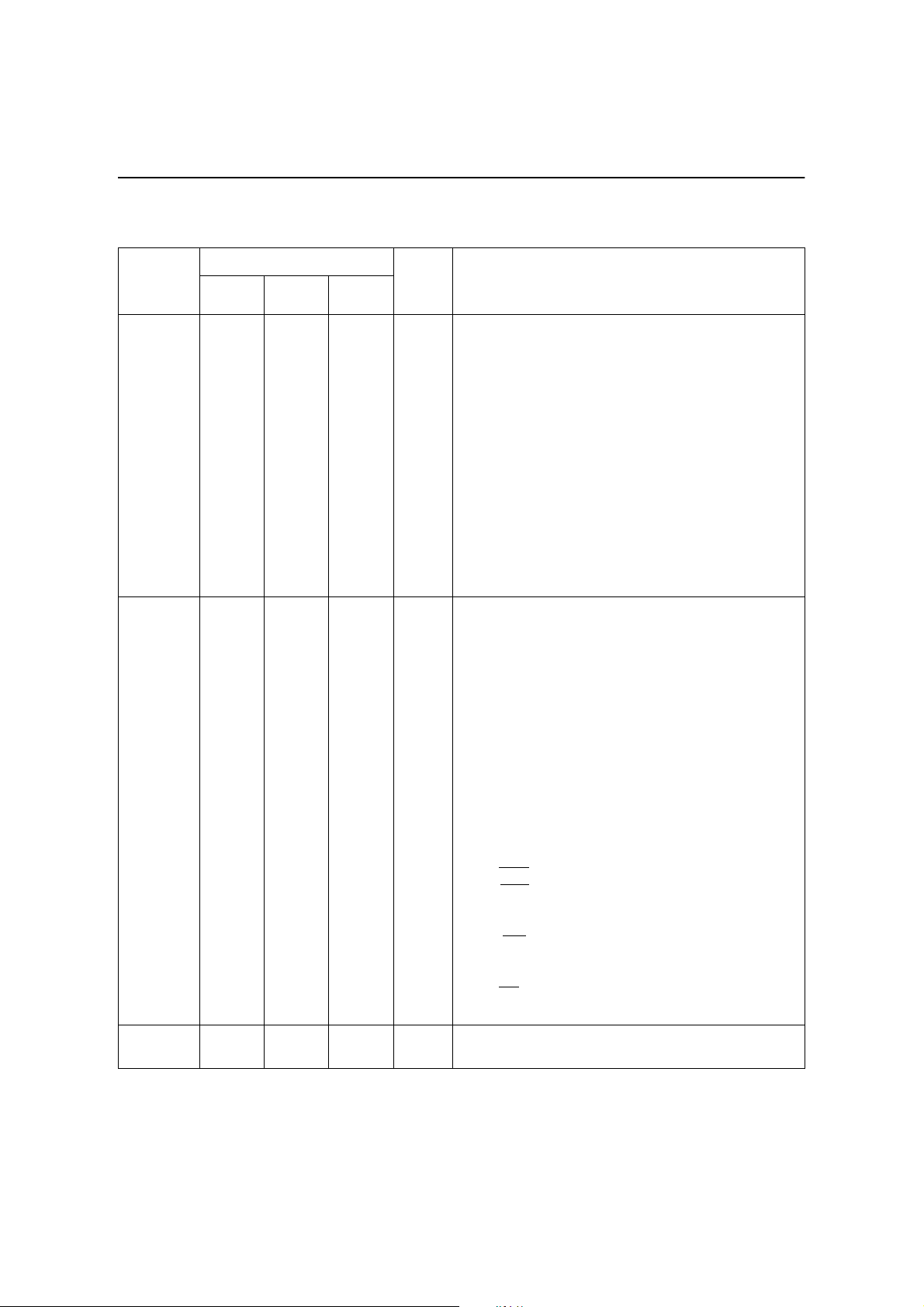

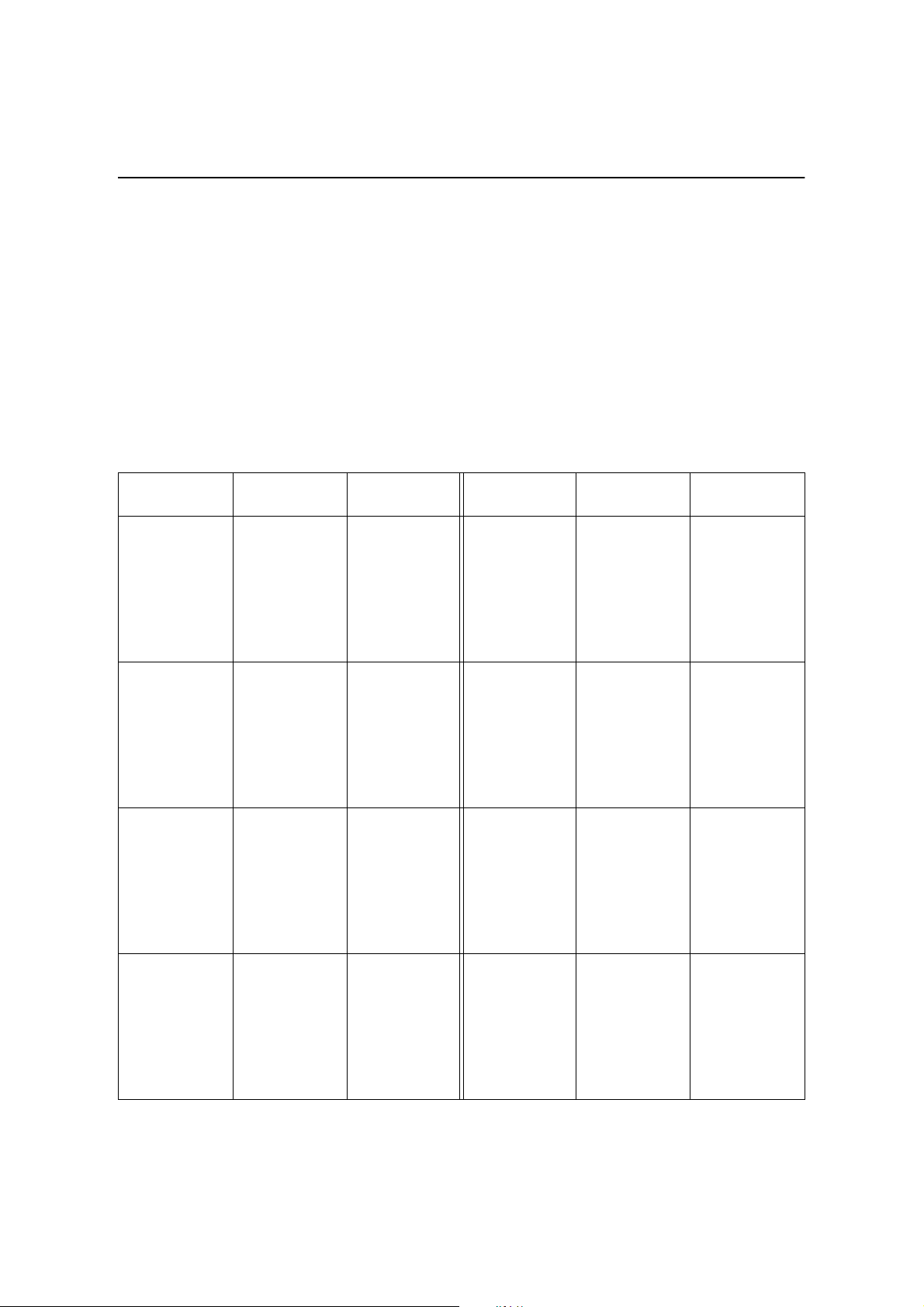

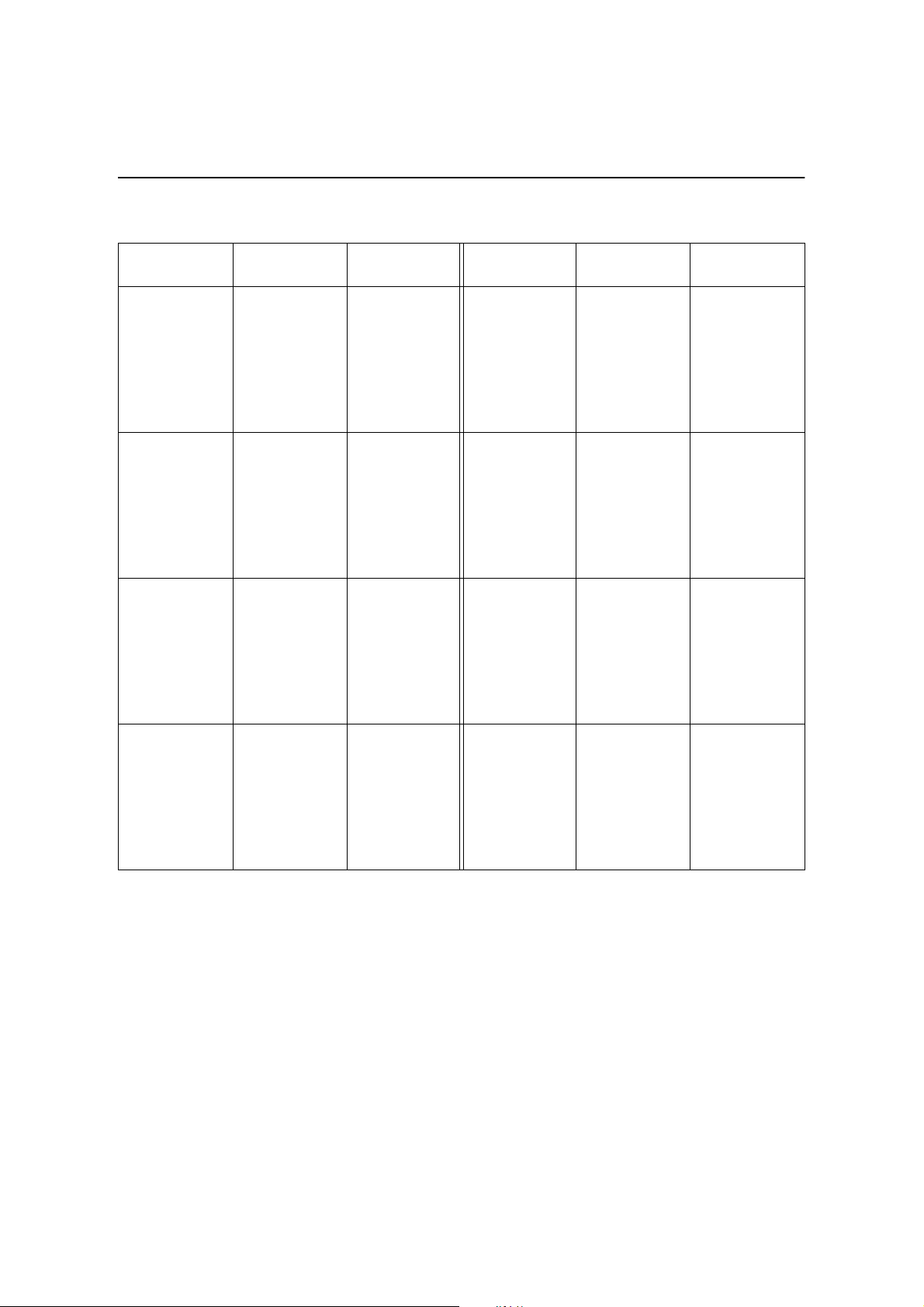

GMS90X5XC Series Selection Guide

Frequency

Blank:

16: 16MHz

24:

40:

Package Type

Blank:

PL:

Q:

ROM Code serial No.

12MHz

24MHz

40MHz

40PDIP

44PLCC

44MQFP

4k bytes

8k bytes

16k bytes

2.7~3.6V

Operating

Voltage

(V)

4.25~5.5 4K

2.7~3.6 4K

Jan. 2001 Ver 1.0

ROM size

MASK

8K

16K

8K

16K

(bytes)

RAM size

(bytes)

128

256

256

128

256

256

Device Name

GMS90C51C

GMS90C52C

GMS90C54C

GMS90L51C

GMS90L52C

GMS90L54C

Operating

Frequency

12/24/40

12/24/40

12/24/40

12/16

12/16

12/16

(MHz)

GMS90X5XC Series HYUNDAI MicroElectronics

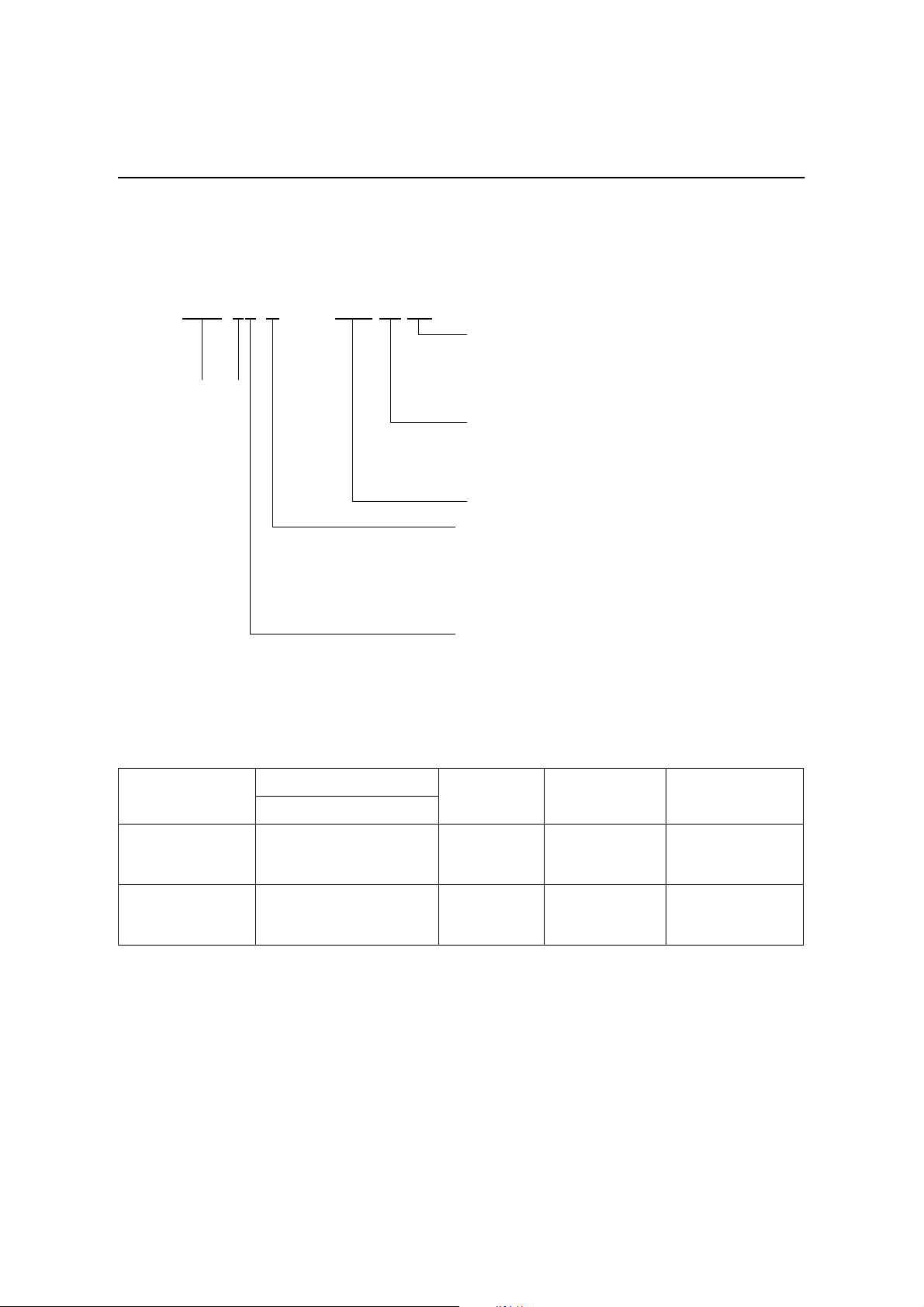

GMS90C51C GMS90L51C(Low voltage versions)

• Fully compatible to standard MCS-51 microcontroller

• Wide operating frequency up to 40MHz

(for more detail, see “GMS90X5XC Series Selection Guide”)

• X2 Speed Improvement capability (

20MHz @5V (Equivalent to 40MHz @5V)

8MHz @3V (Equivalent to 16MHz @3V)

•4K × 8 ROM

• 128 × 8 RAM

• 64K external program memory space

• 64K external data memory space

• Four 8-bit ports

• Two 16-bit Timers / Counters

•USART

• Programmable ALE pin enable / disable (Low

• Five interrupt sources, two priority levels

• Power saving Idle and power down mode

• 2.7Volt low voltage version available

• P-DIP-40, P-LCC-44, P-MQFP-44 package

6 clocks/machine cycle

EMI

)

)

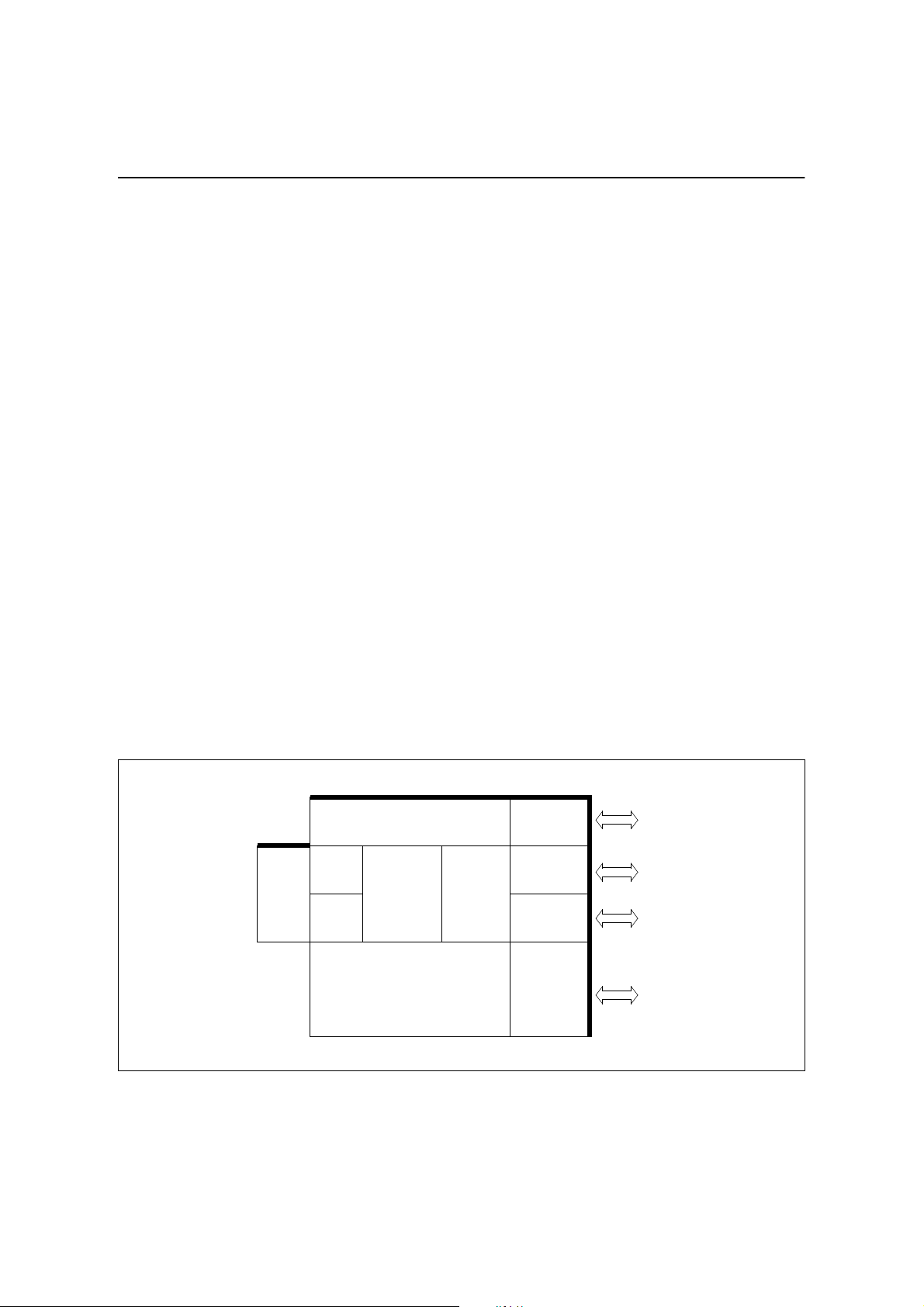

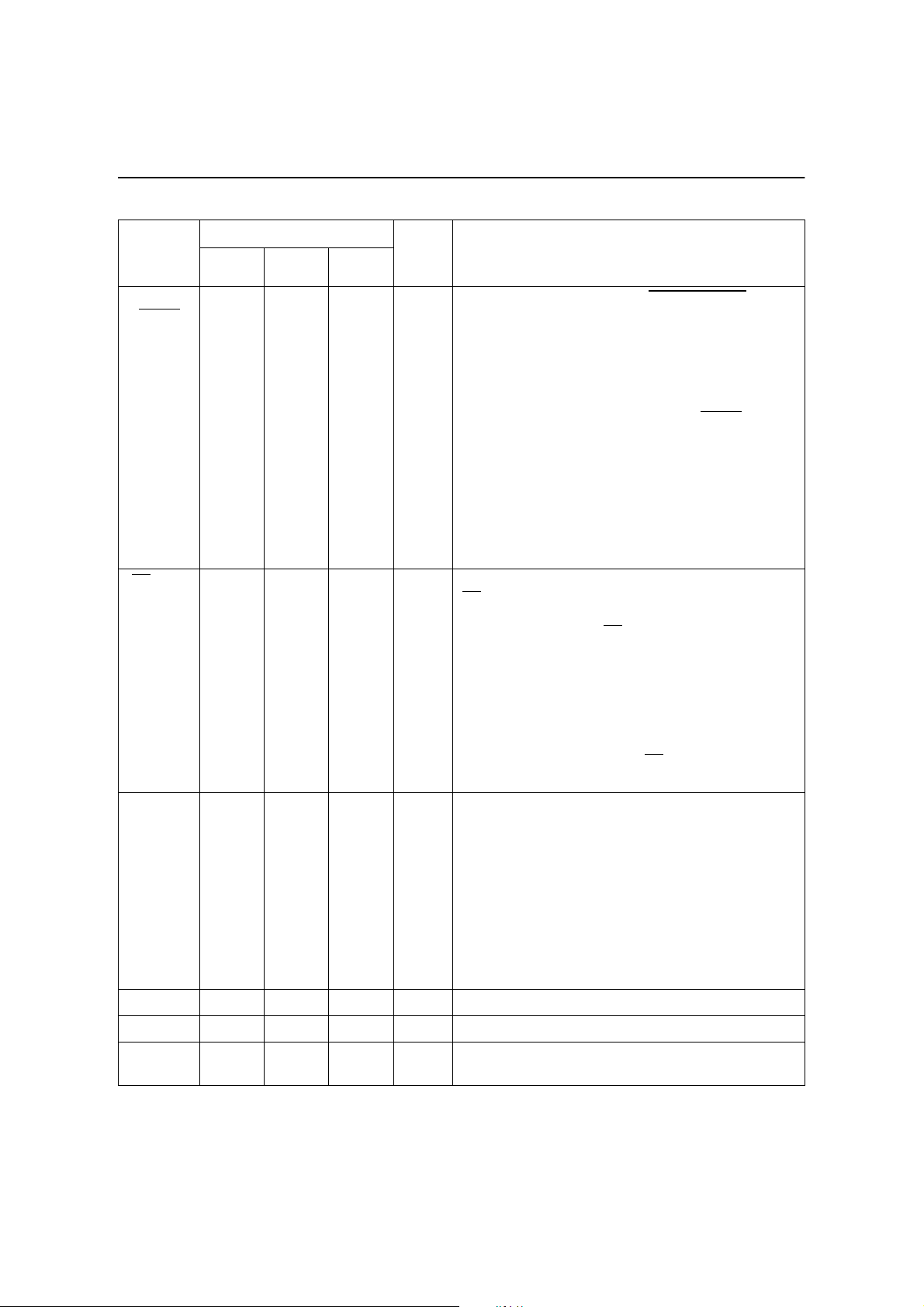

Block Diagram

Jan. 2001 Ver 1.0

T 0

T 1

ROM / EPROM

RAM

128 × 8

CPU

4K × 8

8-BIT

USART

PORT 0

PORT 1

PORT 2

PORT 3

I/O

I/O

I/O

I/O

GMS90X5XC Series HYUNDAI MicroElectronics

GMS90C52C/54C GMS90L52C/54C(Low voltage versions)

• Fully compatible to standard MCS-51 microcontroller

• Wide operating frequency up to 40MHz

(for more detail, see “GMS90X5XC Series Selection Guide”)

• X2 Speed Improvement capability (

20MHz @5V (Equivalent to 40MHz @5V)

8MHz @3V (Equivalent to 16MHz @3V)

•8K/16K bytes ROM

• 256 × 8 RAM

• 64K external program memory space

• 64K external data memory space

• Four 8-bit ports

• Three 16-bit Timers / Counters (Timer2 with up/down counter feature)

•USART

• One clock output port

• Programmable ALE pin enable / disable (Low

• Six interrupt sources, two priority levels

• Power saving Idle and power down mode

• 2.7Volt low voltage version available

• P-DIP-40, P-LCC-44, P-MQFP-44 package

6 clocks/machine cycle

EMI

)

)

Block Diagram

T 2

RAM

256 × 8

T 0

CPU

T 1

ROM / EPROM

GMS90X52C: 8K × 8

GMS90X54C: 16K × 8

8-BIT

USART

PORT 0

PORT 1

PORT 2

PORT 3

I/O

I/O

I/O

I/O

Jan. 2001 Ver 1.0 1

HYUNDAI MicroElectronics GMS90X5XC Series

PIN CONFIGURATION

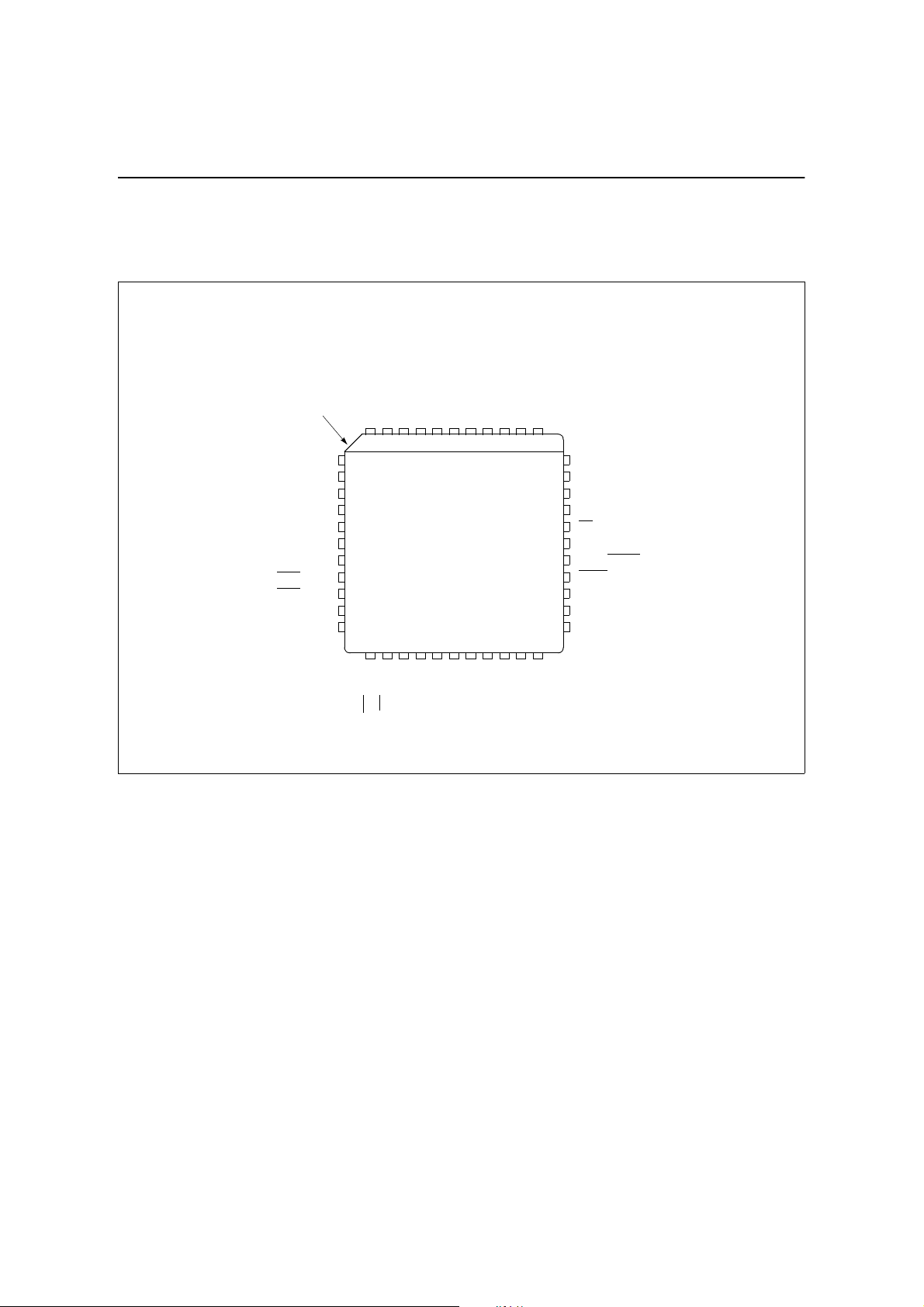

44-PLCC Pin Configuration (top view)

N.C.: Do not connect.

INDEX

CORNER

RESET

RxD / P3.0

N.C.*

TxD / P3.1

/ P3.2

INT0

/ P3.3

INT1

T0 / P3.4

T1 / P3.5

P1.5

P1.6

P1.7

P1.4

P1.3

P1.2

P1.1 / T2EX

65432

7

8

9

10

11

12

13

14

15

16

17

1819202122232425262728

/ P3.7

XTAL2

XTAL1

RD

WR / P3.6

P1.0 / T2

N.C.*

1

SS

V

N.C.*

CC

V

4443424140

P2.0 / A8

P0.0 / AD0

P2.1 / A9

P0.1 / AD1

P0.2 / AD2

P0.3 / AD3

P0.4 / AD4

39

P0.5 / AD5

38

P0.6 / AD6

37

P0.7 / AD7

36

/ V

EA

35

34

33

32

31

30

29

P2.2 / A10

P2.4 / A12

P2.3 / A11

PP

N.C.*

ALE / PROG

PSEN

P2.7 / A15

P2.6 / A14

P2.5 / A13

2 Jan. 2001 Ver 1.0

GMS90X5XC Series HYUNDAI MicroElectronics

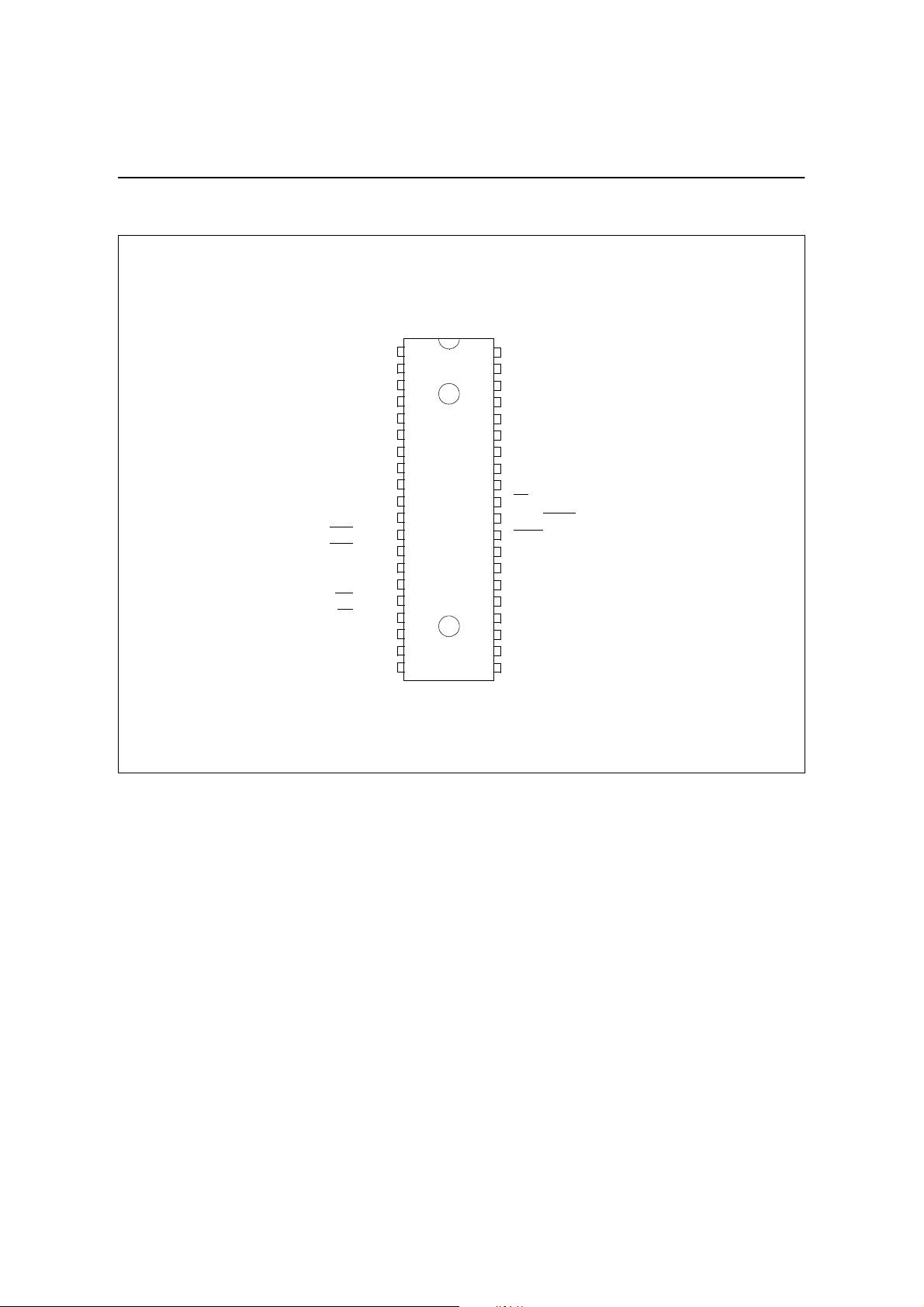

40-PDIP Pin Configuration (top view)

T2 / P1.0

T2EX / P1.1

P1.2

P1.3

P1.4

P1.5

P1.6

P1.7

RESET

RxD / P3.0

TxD / P3.1

INT0

/ P3.2

/ P3.3

INT1

T0 / P3.4

T1 / P3.5

WR

/ P3.6

RD

/ P3.7

XTAL2

XTAL1

V

V

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

SS

20

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

CC

P0.0 / AD0

P0.1 / AD1

P0.2 / AD2

P0.3 / AD3

P0.4 / AD4

P0.5 / AD5

P0.6 / AD6

P0.7 / AD7

EA

/ V

PP

ALE / PROG

PSEN

P2.7 / A15

P2.6 / A14

P2.5 / A13

P2.4 / A12

P2.3 / A11

P2.2 / A10

P2.1 / A9

P2.0 / A8

Jan. 2001 Ver 1.0 3

HYUNDAI MicroElectronics GMS90X5XC Series

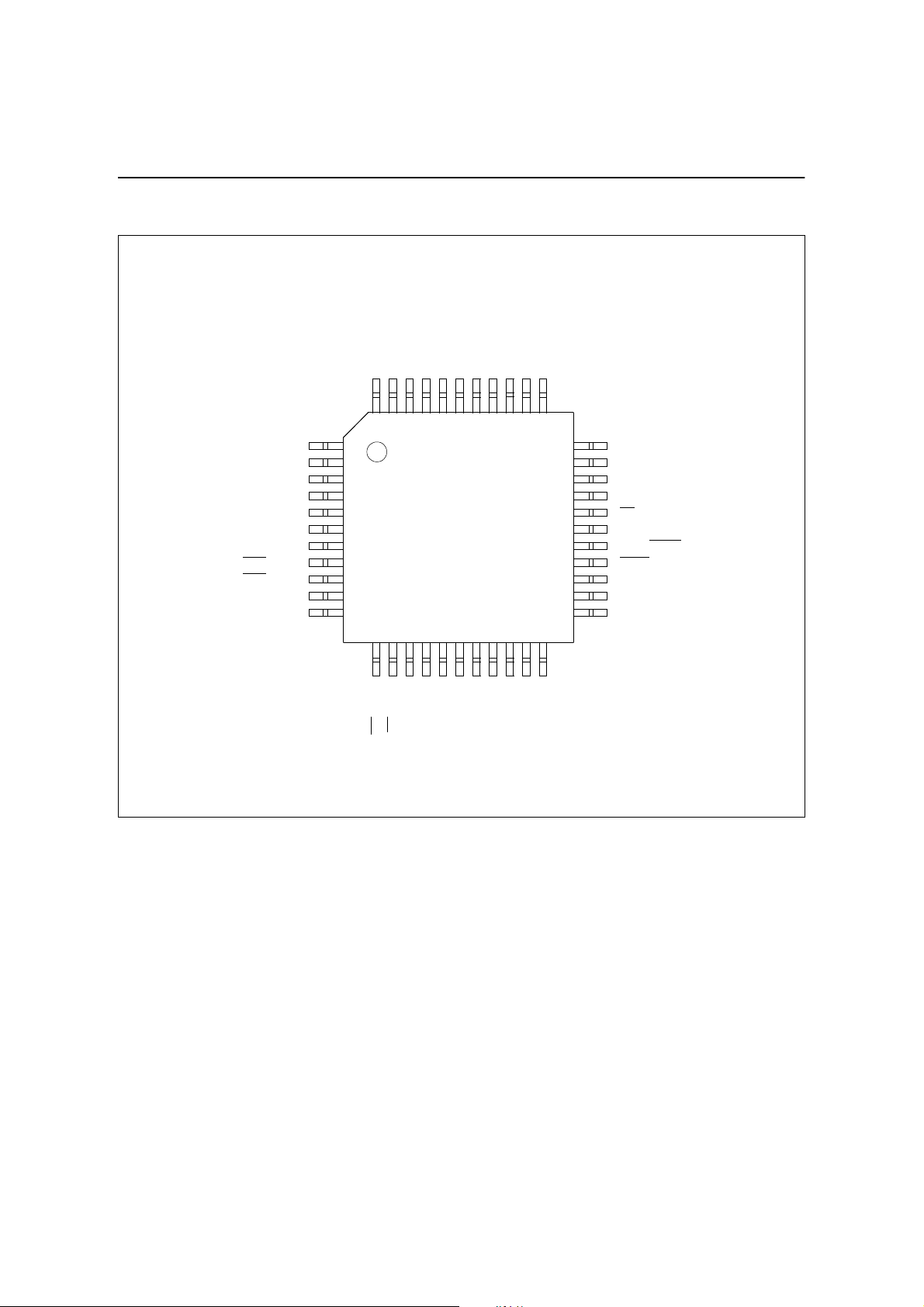

44-MQFP Pin Configuration (top view)

CC

P0.0 / AD0

P0.1 / AD1

P0.2 / AD2

P0.3 / AD3

33

32

31

30

29

28

27

26

25

24

23

P0.4 / AD4

P0.5 / AD5

P0.6 / AD6

P0.7 / AD7

/ V

EA

PP

N.C.*

ALE / PROG

PSEN

P2.7 / A15

P2.6 / A14

P2.5 / A13

P1.5

P1.6

P1.7

RESET

RxD / P3.0

N.C.*

TxD / P3.1

/ P3.2

INT0

/ P3.3

INT1

T0 / P3.4

T1 / P3.5

P1.4

P1.3

P1.2

P1.1 / T2EX

P1.0 / T2

N.C.*

V

4443424140393837363534

1

2

3

4

5

6

7

8

9

10

11

1213141516171819202122

N.C.: Do not connect.

SS

V

/ P3.7

XTAL2

RD

WR / P3.6

N.C.*

XTAL1

P2.0 / A8

P2.1 / A9

P2.2 / A10

P2.4 / A12

P2.3 / A11

4 Jan. 2001 Ver 1.0

GMS90X5XC Series HYUNDAI MicroElectronics

Logic Symbol

V

CCVSS

XTAL1

XTAL2

RESET

EA/V

PP

ALE/PROG

PSEN

Port 0

8-bit Digital I/O

Port 1

8-bit Digital I/O

Port 2

8-bit Digital I/O

Port 3

8-bit Digital I/O

Jan. 2001 Ver 1.0 5

HYUNDAI MicroElectronics GMS90X5XC Series

PIN DEFINITIONS AND FUNCTIONS

Pin Number

Symbol

P1.0-P1.7 2-9

PLCC-44PDIP-40MQFP-

1-8

44

40-44,

1-3

2

3

2

P3.0-P3.7 11,

1

2

1

40

41

40

10-17 5, 7-13 I/O

13-19

11

13

14

15

16

17

18

19

10

11

12

13

14

15

16

17

5

7

8

9

10

11

12

13

XTAL2 20 18 14 O

Input/

Output

I/O

Function

Port1

Port 1 is an 8-bit bidirectional I/O port with internal

pull-ups. Port 1 pins that have 1s written to them are

pulled high by the intern al pu ll-u p res is tors and c an be

used as inputs. As inputs, port 1 pins that are

externally pulled low will source current because of

the pulls-ups (I

, in the DC characteristics). Pins P1.0

IL

and P1.1 also. Port1 also receives the low-order

address byte during program memory verification.

Port1 also serves alternate functions of Timer 2.

P1.0 / T2 :Timer/counter 2 external count input

P1.1 / T2EX :Timer/counter 2 trigger input

In GMS90X52C/54C:

P1.0 / T2, Clock Out : Timer/counter 2 external count

input, Clock Out

Port 3

Port 3 is an 8-bit bidirectional I/O port with internal

pull-ups. Port 3 pins that have 1s written to them are

pulled high by the intern al pu ll-u p res is tors and c an be

used as inputs. As inputs, port 3 pins that are

externally pulled low will source current because of

the pulls-ups (I

, in the DC characteristic s). Port 3 also

IL

serves the special features of the 80C51 family, as

listed below.

P3.0 / RxD

receiver data input (asynchronous) or

data input output(s yn chronous) of serial

interface 0

P3.1 / TxD

transmitter data output (asynchronous)

or clock output (synchronous) of the

serial interface 0

P3.2 /INT0

P3 .3 / IN T 1

P3.4 /T0

P3.5 /T1

P3.6 / WR

interrupt 0 input/timer 0 gate control

interrupt 1 input/timer 1 gate control

counter 0 input

counter 1 input

the write control signal latche s t he data

byte from port 0 into the external data

memory

P3.7 /RD

the read control signal enables the

external data memory to port 0

XTAL2

Output of the inverting oscillator amplifier.

6 Jan. 2001 Ver 1.0

GMS90X5XC Series HYUNDAI MicroElectronics

Symbol

Pin Number

PLCC-44PDIP-40MQFP-

44

Input/

Output

XTAL1 21 19 15 I

P2.0-P2.7 24-31 21-28 18-25 I/O

PSEN

32 29 26 O

RESET 10 9 4 I

Function

XTAL1

Input to the inverting oscillator amplifier and input to

the internal clock generator circuits.To drive the

device from an external clock source, XTAL1 should

be driven, while XTAL2 is left unconnected. There are

no requirements on the duty cycle of the external

clock signal, since the input to the internal clocking

circuitry is divided down by a divide-by-two flip-flop.

Minimum and maximum high and low times as well as

rise fall times specified in the AC characteristics must

be observed.

Port 2

Port 2 is an 8-bit bidirectional I/O port with internal

pull-ups. Port 2 pins that have 1s written to them are

pulled high by the intern al pu ll-u p res is tors and c an be

used as inputs. As inputs, port 2 pins that are

externally pulled low will source current because of

the pulls-ups (I

, in the DC characteristics).Port 2

IL

emits the high-order address byte during fetches from

external program memory and during accesses to

external data memory that use 16-bit addresses

(MOVX @DPTR). In this application it uses strong

internal pull-ups when emitting 1s. During accesses to

external data memory that use 8-bit addresses

(MOVX @Ri), port 2 emits the contents of the P2

special function register.

The Program Store Enable

The read strobe to external program memory when

the device is executing code from the external

program memory. PSEN is activated twice each

machine cycle, except that two PSEN

activati ons are

skipped during each access to external data memory.

PSEN is not activated during fetches from internal

program memory.

RESET

A high level on this pin for two machine cycles while

the oscilla tor is runni ng resets the device. An interna l

diffused resistor to V

only an external capacitor to V

permits power-on reset using

SS

CC

.

Jan. 2001 Ver 1.0 7

HYUNDAI MicroElectronics GMS90X5XC Series

Symbol

ALE /

Pin Number

PLCC-44PDIP-40MQFP-

44

33 30 27 O

Input/

Output

PROG

EA

/ V

PP

35 31 29 I External Access Enable / Program Supply Voltage

P0.0-P0.7 36-43 32-39 30-37 I/O

V

SS

V

CC

N.C. 1,12

22 20 16 44 40 38 -

-6,17

23,34

28,39

Function

The Address Latch Enable / Program pulse

Output pulse for latching the low byte of the address

during an access to external memory. In normal

operation, ALE is emitted at a constant rate of 1/6 the

oscillator frequency, and can be used for external

timing or clocking. Note that one ALE pulse is skipped

during each access to external data memory. This pin

is also the program pulse input (PROG

EPROM programming.

If desired, ALE operation can be disabled by setting

bit 0 of SFR location 8E

. With this bit set, the pin is

H

weakly pulled high. The ALE disable feature will be

terminated by reset. Setting the ALE-disable bit has

no affect if the microcontroller is in external execution

mode.

must be external held low to enable the device to

EA

fetch code from external program memory locations

0000H to FFFFH. If EA is held high, the device

executes from internal program memory unless the

program counter contains an address greater than its

internal memory size. This pin also receives the

12.75V programming supply voltage (V

EPROM programming.

Note; however, that if any of the Lock bits are

programmed, EA

will be internally

latched on reset.

Port 0

Port 0 is an 8-bit open-drain bidirectional I/O port.

Port 0 pins that have 1s written to them float and can

be used as high-impedance inputs.

Port 0 is also the multipl exed low-orde r address and

data bus during accesses to external program and

data memory. In this application it uses strong internal

pull-ups when emitting 1s. Port 0 also outputs the

code bytes during program verification in the

GMS97X5X. External pull-up resistors are required

during program verification.

Circuit ground potential

Supply terminal

No connection

-

for all operating modes

) during

) during

PP

8 Jan. 2001 Ver 1.0

GMS90X5XC Series HYUNDAI MicroElectronics

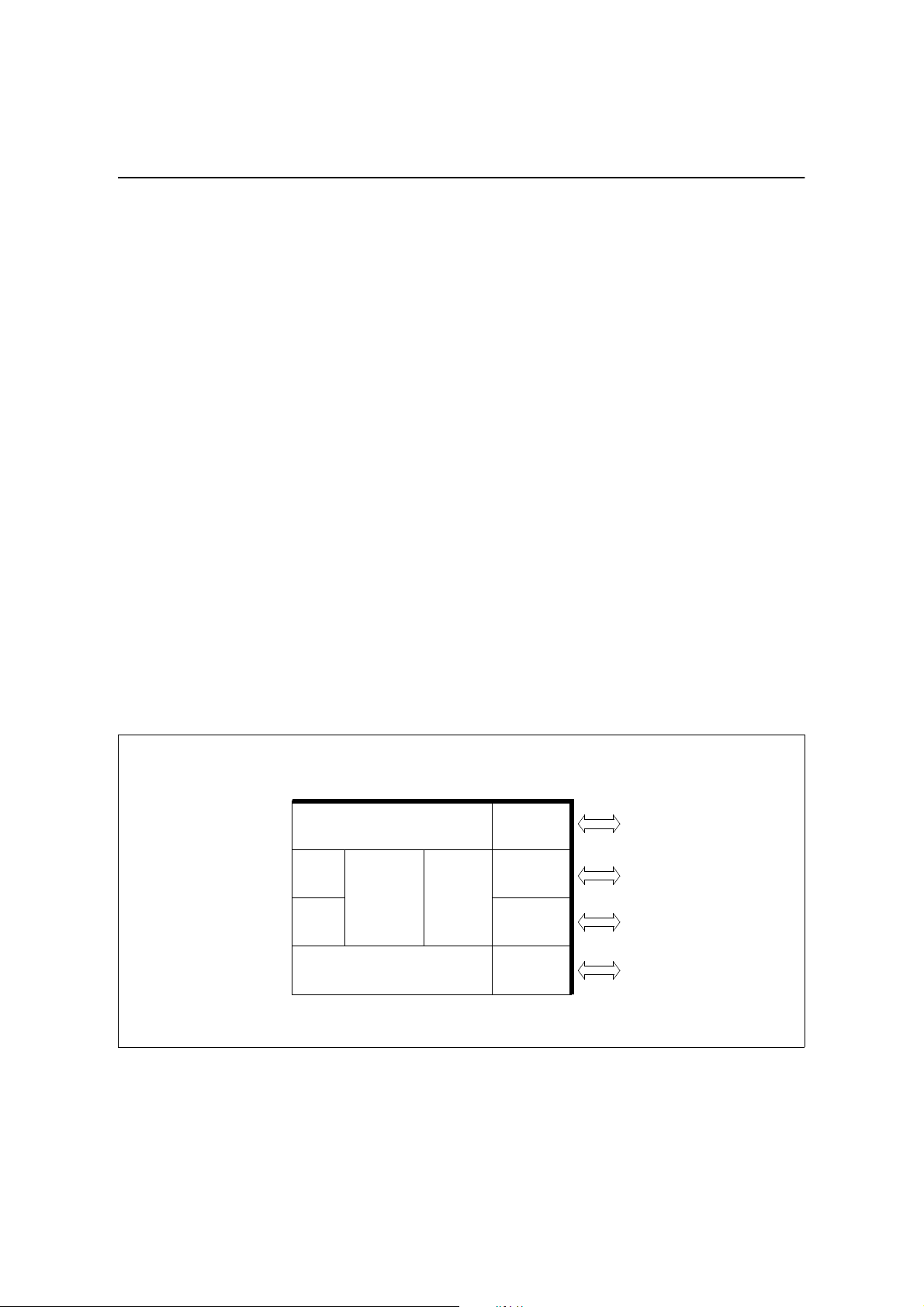

FUNCTIONAL DESCRIPTION

The GMS90X5XC series is fully compatible to the standard 8051 microcontroller family.

It is compatible with the general 8051 family. While maintaining all architectural and operational characteristics

of the general 8051 family.

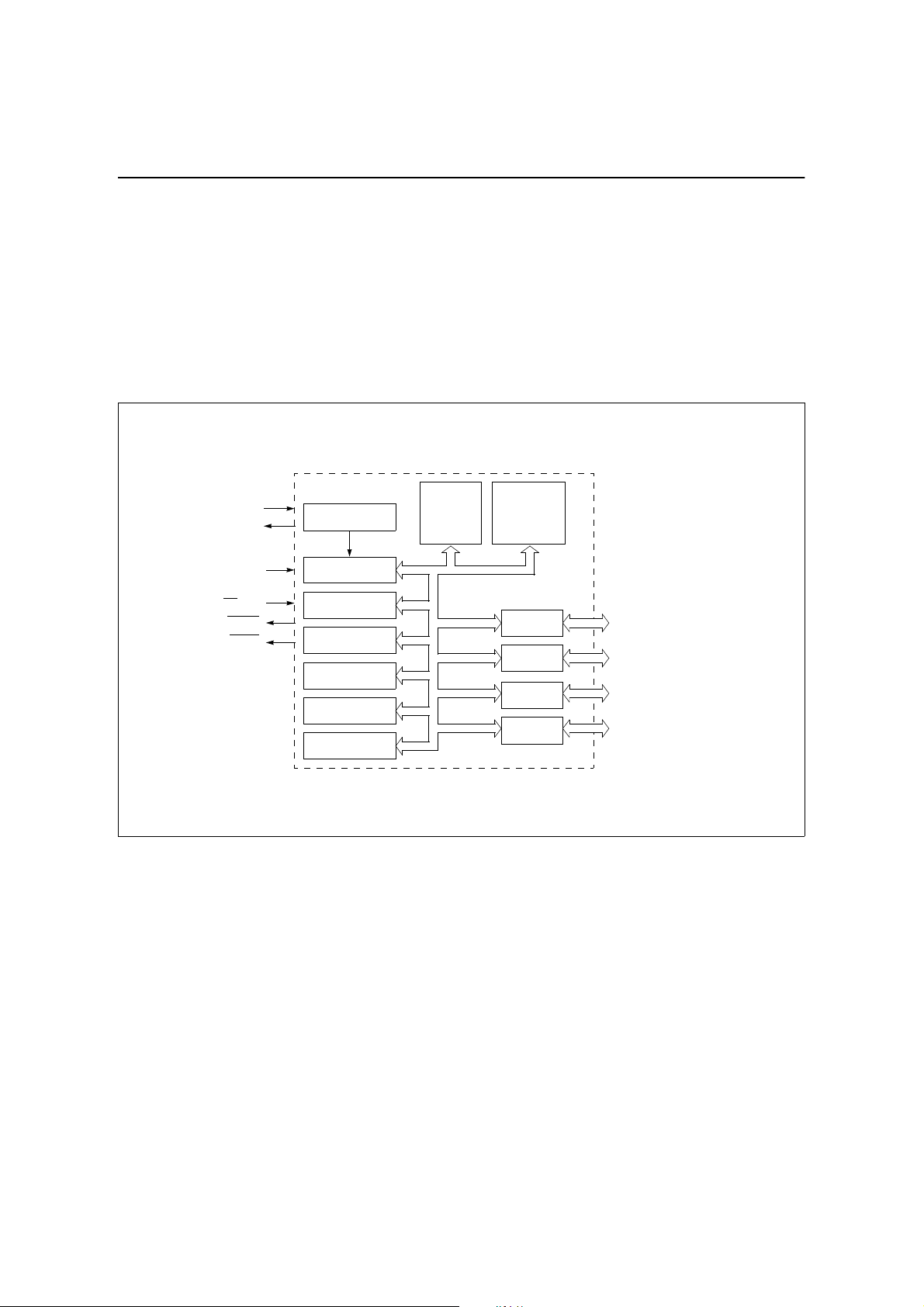

Figure 1 shows a block diagram of the GMS90X5XC series

XTAL1

XTAL2

RESET

EA

/V

ALE/PROG

PSEN

OSC & TIMING

CPU

PP

Timer 0

Timer 1

Timer 2

Interrupt Unit

Serial Channel

RAM

128/256×8

Figure 1. Block Diagram of the GMS90X5XC series

ROM/EPROM

4K/8K/16K

Port 0

Port 1

Port 2

Port 3

Port 0

8-bit Digit. I/O

Port 1

8-bit Digit. I/O

Port 2

8-bit Digit. I/O

Port 3

8-bit Digit. I/O

Jan. 2001 Ver 1.0 9

HYUNDAI MicroElectronics GMS90X5XC Series

CPU

The GMS90X5XC series is efficient both as a controller and as an arithmetic processor. It has exten sive facilities for binary and BCD arithmetic and excels in its bit-handling capabilities. Efficient use of program memory

results from an i nstructio n set consist ing of 44% o ne-byte, 41% two-byte, and 15% three-byt e instruction s. With

a 12 MHz crystal, 58% of the instructions are executed in 1.0µs (40MHz: 300ns).

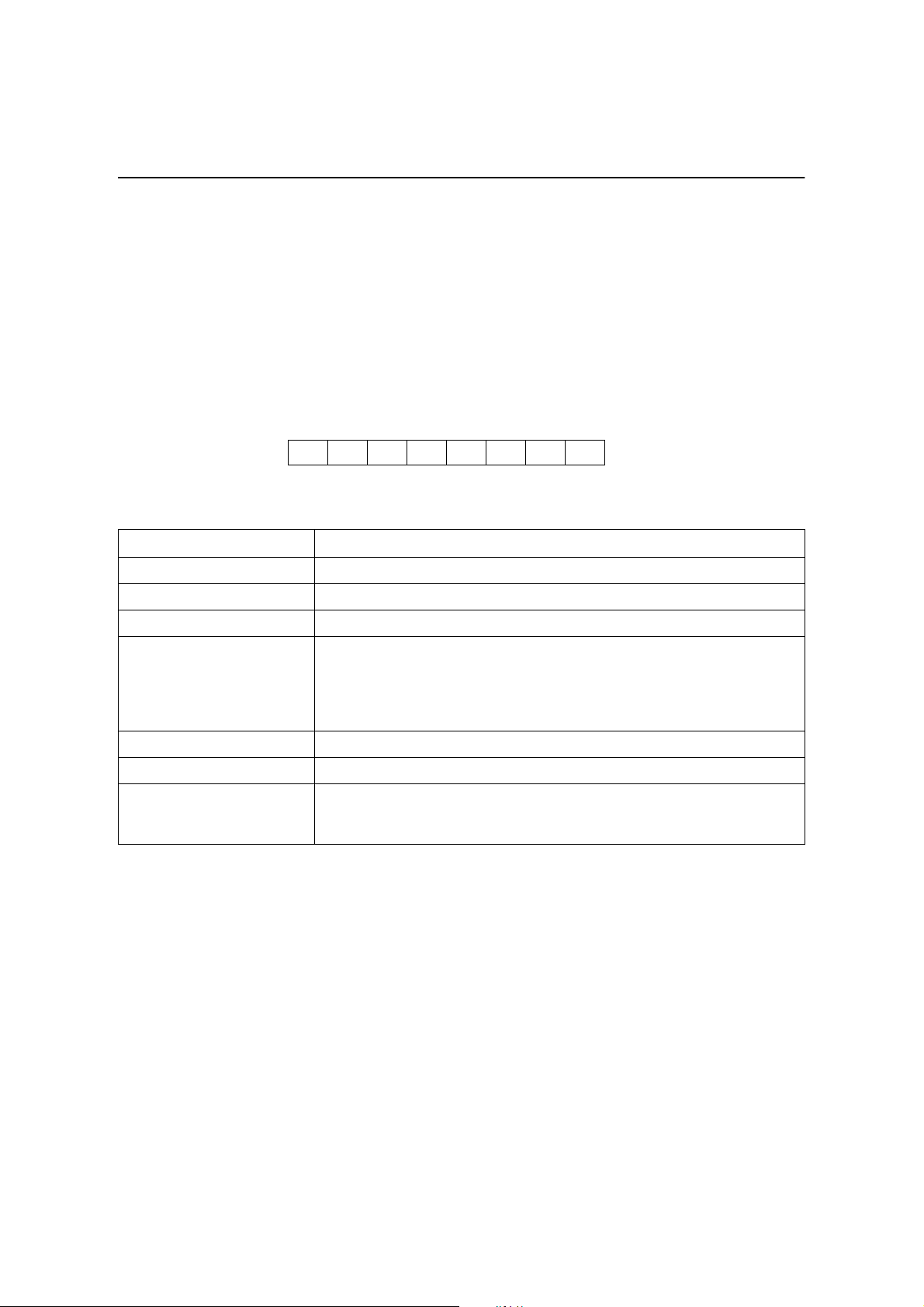

Special Function Register PSW

LSB

PSW

Bit No.

Addr. D0

MSB

76543210

H

CY AC F0 RS1 RS0 OV F1 P

Bit Function

Carry Flag

Auxiliary Carry Flag

(for BCD operations)

General Purpose Flag

Register Bank select control bits

Bank 0 selected, data address 00

Bank 1 selected, data address 08H - 0F

Bank 2 selected, data address 10H - 17

Bank 3 selected, data address 18H - 1F

H

- 07

H

H

H

H

Overflow Flag

General Purpose Flag

Parity Flag

Set/cleared by hardware each instruction cycle to indicate an odd/even

number of "one" bits in the accumulator, i.e. even parity.

RS1

0

0

1

1

CY

AC

F0

RS0

0

1

0

1

OV

F1

P

Reset value of PSW is 00H.

10 Jan. 2001 Ver 1.0

GMS90X5XC Series HYUNDAI MicroElectronics

SPECIAL FUNCTION REGISTERS

All registers, except the program co unter and the four general pu rpose register banks, r eside in the special fu nction register area.

The 28 special function registers (SFR) include pointers and registers that provide an interface b etween the CPU

and the other on-chip peripherals. There are also 128 directly addressable bits within the SFR area.

All SFRs are listed in Table 1, Table 2, and Table 3.

In Table 1 they are organized in numeric order of their addresses. In Table 2 they are organized in groups which

refer to the functional blocks of the GMS90X5XC series. Table 3 illustrates the contents of the SFRs

Table 1. Special Function Registers in Numeric Order of their Addresses

Address Register

80H

81H

82H

83H

84H

85H

86H

87H

90H

91H

92H

93H

94H

95H

96H

97H

A0H

A1H

A2H

A3H

A4H

A5H

A6H

A7H

B0H

B1H

B2H

B3H

B4H

B5H

B6H

B7H

1)

P0

SP

DPL

DPH

reserved

reserved

reserved

PCON

1)

P1

reserved

reserved

reserved

reserved

reserved

reserved

reserved

3)

P2

reserved

reserved

reserved

reserved

reserved

reserved

reserved

1)

P3

reserved

reserved

reserved

reserved

reserved

reserved

reserved

Contents after

0XXX0000

Reset

FFH

07H

00H

00H

XXH

XXH

XXH

FF

00

XXH

XXH

XXH

XXH

XXH

XXH

FFH

XXH

XXH

XXH

XXH

XXH

XXH

XXH

FFH

XXH

XXH

XXH

XXH

XXH

XXH

XXH

Address Register

88H

89H

8AH

8BH

2)

2)

2)

2)

B

H

H

2)

2)

2)

2)

2)

2)

2)

2)

2)

2)

2)

2)

2)

8CH

8DH

8EH

8FH

98H

99H

9AH

9BH

9CH

9DH

9EH

9FH

A8H

A9H

AAH

ABH

ACH

ADH

AEH

AFH

B8H

2)

2)

2)

2)

2)

2)

2)

B9H

BAH

BBH

BCH

BDH

BEH

BFH

(cont’d)

TCON

TMOD

TL0

TL1

TH0

TH1

AUXR0

CKCON

SCON

SBUF

reserved

reserved

reserved

reserved

reserved

reserved

1)

IE

reserved

reserved

reserved

reserved

reserved

reserved

reserved

1)

IP

reserved

reserved

reserved

reserved

reserved

reserved

reserved

1)

1)

Contents after

XXXXXXX0

Reset

00H

00H

00H

00H

00H

00H

2)

XXH

00H

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

0X000000B

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

XX000000B

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

B

2)

2)

Jan. 2001 Ver 1.0 11

HYUNDAI MicroElectronics GMS90X5XC Series

Table 1. Special Function Registers in Numeric Order of their Addresses

Address Register

C0H

C1H

C2H

C3H

C4H

C5H

C6H

C7H

D0H

D1H

D2H

D3H

D4H

D5H

D6H

D7H

E0H

E1H

E2H

E3H

E4H

E5H

E6H

E7H

F0H

F1H

F2H

F3H

F4H

F5H

F6H

F7H

1) Bit-addressable Special Function Register.

2) X means that the value is indeterminate and the location is reserved.

3) Bit-addressable Special Function Register.

4) These Registers are in the GMS90X52C/54C only.

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

1)

PSW

reserved

reserved

reserved

reserved

reserved

reserved

reserved

1)

ACC

reserved

reserved

reserved

reserved

reserved

reserved

reserved

1)

B

reserved

reserved

reserved

reserved

reserved

reserved

reserved

Contents after

Reset

XX

H

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

FFH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

00H

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

00H

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

Address Register

3)

C8H

4)

C9H

3)

CAH

3)

CBH

3)

CCH

3)

CDH

CEH

CFH

D8H

D9H

DAH

DBH

DCH

DDH

DEH

DFH

E8H

E9H

EAH

EBH

ECH

EDH

EEH

EFH

F8H

F9H

FAH

FBH

FCH

FDH

FEH

FFH

(cont’d)

T2CON

T2MOD

RC2L

RC2H

TL2

TH2

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

1)

Contents after

Reset

00H

XXXXXX00

2)

B

00H

00H

00H

00H

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

12 Jan. 2001 Ver 1.0

Loading...

Loading...