Page 1

Honeywell

Component Maintenance Manual

XK516D1 HF Transceiver

Part Number

964-0452-001

964-0452-002

964-0452-011

964-0452-012

964-0452-022

I.B. 1516A Page T-1/T-2

DOCUMENT NO. 012-0693-001

Honeywell CAGE Code 97896

23-12-01

May 5/97

Rev. 3: Oct 25/02

Page 2

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

RECORD OF REVISIONS

REV. INSERTION BY

NO. DATE

1 Mar 30/01 HON

2 Sep 5/01 HON

3 Oct 25/02 HON

REV. INSERTION BY

NO. DATE

REV. INSERTION BY

NO. DATE

Retain this record in the front of the manual or chapter. Upon receipt of revisions, insert revised

pages in the manual, and enter revision number, date inserted, and initials.

I.B. 1516A Page RR-1/RR-2

23-12-01

Oct 25/02

Page 3

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

RECORD OF TEMPORARY REVISIONS

TEMPORARY

REV. NO.

23-01 Jul 15/97 Mar 30/01

23-02 Nov 7/01 Oct 25-02

23-03 Feb 5/02 Oct 25-02

23-04 Mar 26/02 Oct 25-02

23-05 Jul 26/02 Oct 25-02

ISSUE

DATE

INSERTION

DATE / BY

INCORPORATION

DATE

INCORPORATION DATE is the date of the CMM revision that incorporates TR information.

I.B. 1516A Page TR-1/TR-2

23-12-01

Oct 25/02

Page 4

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

SERVICE BULLETIN LIST

SERVICE BULLETIN

NUMBER

964-0452-00X-23-1

(012-0693-101)

964-0452-00X-23-2

(012-0693-102)

964-0452-00X-23-3

(012-0693-103)

964-0452-00X-23-4

(012-0693-104)

964-0452-0XX-23-5

(012-0693-105)

964-0452-0XX-23-6

(012-0693-106)

964-0452-00X-23-7

(012-0693-107)

964-0452-00X-23-8

(012-0693-108)

964-0452-00X-23-9

(012-0693-109)

964-0452-00X-23-10

(012-0693-110)

964-0452-00X-23-11

(012-0693-111)

964-0452-00X-23-12

(012-0693-112)

DATE

INCORPORATED DESCRIPTION

Mar 30/01 Corrects for anomalous behavior observed during

power interrupts between 4 and 250ms duration.

SW Ver. 1.50; HW Mod 10.

Mar 30/01 Corrects for anomalous behavior observed during

testing at Airbus. Refer to EPRs 00001, 00002,

and 00003. SW Ver. 1.60; HW Mod 14.

Mar 30/01 Eliminates problems encountered with the existing

Controller D module, and provides more reliable

XK516D1 Transceiver operation. HW Mod 22.

Mar 30/01 Eliminates problems encountered with the

ON/OFF module, and provides more reliable

XK516D1 Transceiver operation. HW Mod 15.

Mar 30/01 Changes made in the upgraded software: Added

bit with Air/Ground status information to ARINC

429 Word Label 270 broadcast to ACARS MU and

Radio Control Panel. HFDL SW Mod 3.

Mar 30/01 Changes made in the upgraded software: Correct-

ed erroneous LRU Fault indication when Transceiver is in Data mode and on the ground, and the

Radio Control Panel input to the Radio is missing

or not available on both frequency select ports.

HFDL SW Mod 4.

Mar 30/01 Eliminates problems encountered with the existing

Receiver/Exciter module, and provides more reliable XK516D1 Transceiver operation. HW Mod 13.

Mar 30/01 Eliminates problems encountered during vibration

testing, and provides more reliable XK516D1

Transceiver operation. HW Mod 11.

Mar 30/01 Converting the HF Transceivers to the new Part

Numbers will correct potential HF system lockup

conditions, resulting from unreliable HF Transceiver/Coupler control communications in installations

with high EMI conditions.

Mar 30/01 Corrects potential HF system lockup conditions,

resulting from unreliable HF Transceiver/Coupler

control communications in installations with high

EMI conditions. The software upgrade sets the coaxial interface to Coupler, as the default, in the

Transceiver Control software. SW Ver. 1.70; HW

Mod 16.

Mar 30/01 Reduces potential HF Transceiver susceptibility to

false PTT activation caused by keying of other audio components. HW Mod 18.

Mar 30/01 Corrects for spurious signals on SELCAL output

caused by ringing in SELCAL output stage. Corrects for intermodulation distortion in the RF spectrum in the internal HFDL data mode. HW Mod 19.

I.B.1516A Page SB-1

23-12-01

Sep 5/01

Page 5

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

SERVICE BULLETIN

NUMBER

964-0452-0XX-23-13

(012-0693-113)

964-0452-0XX-23-14

(012-0693-114)

964-0452-022-23-15

(012-0693-115)

964-0452-00X-23-16

(012-0693-116)

964-0452-012-23-17

(012-0693-117)

964-0452-00X-23-18

(012-0693-118)

964-0452-012-23-19

(012-0693-119)

964-0452-0XX-23-20

(012-0693-120)

964-0452-022-21

(012-0693-121)

964-0452-012-23-22

(012-0693-122)

DATE

INCORPORATED DESCRIPTION

Mar 30/01 The HFDR Software Mod 6 version contains cus-

tomer requested Red label changes to be used for

flight testing. HFDL SW Mod 6.

Mar 30/01 Converts the Transceivers to the production ver-

sion of PN 964-0452-012, which are HFDL Software Mod 8.

Mar 30/01 Converts HF Transceivers with Honeywell propri-

etary HF Data Link (HFDL) protocol (PN

964-0452-022) to HF Transceivers, using the industry standard ARINC 635 HFDL protocol (PN

964-0452-012). HFDL SW Mod 8.

Mar 30/01 Changes the default date mode of operation of the

-0X2 Transceivers when both TP7G and MP2D

are grounded to Internal HFDL Data Mode instead

of defaulting to External Data Mode. This change

does not affect the voice mode of operation of any

of the radios. HW Mods 21 and 22.

Mar 30/01 Changes the Airborne Datalink Processor (ADP)

software to add the capability to display the ADP

and High Frequency Modem (HFM) software part

numbers on the ACARS/MCDU system and to fix

minor problems identified during testing of HFDL

Software Mod 8. HFDL SW Mod 9.

Mar 30/01 Reverts back to Software Version 1.70. Software

Version 1.80 introduced problems with sidetone

suppression during transmit operation. SW Ver.

1.70; HW Mod 22.

Mar 30/01 Incorporates changes to the Airborne Datalink Pro-

cessor (ADP) software requested by ARINC to

prevent the HFDL System from logging on to a

ground station when the ICAO address input from

the MODE-S transponder is missing, and readjusts

the data rate thresholds. HFDL SW Mod 10.

Mar 30/01 Allows the HF Transceivers and Control Panel to

be powered up in any sequence. Currently, the

"HFDR INSTALLED" discrete output of the HF Data Radio (or DOUT0 Spare Discrete OUT of A2

ADP board) is grounded on power up under software control. The "HFDR INSTALLED" discrete

needs to be grounded on the A2 ADP board even

when power is OFF. HW Mod 23.

Mar 30/01 Incorporates changes to the Airborne Datalink Pro-

cessor (ADP) software to reduce/eliminate nuisance HFDR Faults (Fault Code 39) caused by input power transients. HFDL SW Mod 5.

Mar 30/01 Incorporates minor changes to the Airborne

Datalink Processor (ADP) software requested by

ARINC to ensure that the Maximum Uplink Data

Rate recommended by the avionics to the HFDL

ground stations is a minimum of 300bps. HFDL

SW Mod 11.

1I.B.1516A Page SB-2

23-12-01

Sep 5/01

Page 6

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

SERVICE BULLETIN

NUMBER

964-0452-0XX-23-23

(012-0693-123)

964-0452-00X-23-24

(012-0693-124)

964-0452-00X-23-25

(012-0693-125)

964-0452-00X-23-26

(012-0693-126)

964-0452-0XX-23-27

(012-0693-127)

964-0452-0XX-23-28

(012-0693-128)

964-0452-0XX-23-29

(012-0693-129)

964-0452-0XX-23-30

(012-0693-130)

DATE

INCORPORATED DESCRIPTION

Mar 30/01 Upgrades Transceiver to be capable of operation

in HF Datalink (HFDL) mode per ARINC 753 and

635, as well as the HF Voice Radio (HFVR) capabilities. Control SW Ver. 1.70; HFDL HW Mod 11.

Mar 30/01 Corrects for nuisance CMC input fault reporting.

SW Ver. 2.00; HW Mod 27.

Mar 30/01 Allows the ARINC 429 interface between the HF

Transceiver and a CMU or ATSU to operate reliably at high-speed. Also improves susceptibility of

the Transceiver to short power interrupts of 10 to

40ms when operating in data mode. Mod 28.

Mar 30/01 Incorporates minor changes to Airborne Datalink

Processor (ADP) software to improve data mode

operation during short power interrupts, and to enable high-speed 429 interface to the ATSU. HFDL

SW Mod 12.

Mar 30/01 Converts the Airborne Datalink Processor (ADP)

CCA, A2, from either Part No. 722-4134-006 to

722-4134-008 or from Part No. 722-4134-007 to

722-4134-009. The modification consists of removing IC sockets XU6 and XU23. Mod 31.

Oct 25/02 Replaces the EMC Filter, A7, Part No. 300-1096-

001 (R&S Part No. 6030.2251.02, Mod 4 or lower)

with EMC Filter, A7, Part No. 300-1096-002 (R&S

Part No. 6030.2251.02, Mod 5). HW Mod 33.

Oct 25/02 Replaces EPROM set, Part No. 6030.2151.00 Ver-

sion 2.00 or lower, with Version 2.20 on Controller

D, A8. HW Mod 34.

Oct 25/02 Instructions to upload upgraded HFDL software via

a Portable Data Loader while on the bench. HW

Mod 13.

I.B. 1516A Page SB-3/SB-4

23-12-01

Oct 25/02

Page 7

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

LIST OF EFFECTIVE PAGES

PAGE DATE PAGE DATE PAGE DATE

T-1 Oct 25/02

T-2 Blank

RR-1 Oct 25/02

RR-2 Blank

TR-1 Oct 25/02

TR-2 Blank

SB-1 Sep 5/01

SB-2 Sep 5/01

SB-3 Oct 25/02

SB-4 Blank

LEP-1 Oct 25/02

LEP-2 Oct 25/02

LEP-3 Oct 25/02

LEP-4 Oct 25/02

TC-1 Oct 25/02

TC-2 Mar 30/01

TC-3 Mar 30/01

TC-4 Mar 30/01

TC-5Oct 25/02

TC-6 Oct 25/02

INTRO-1 Mar 30/01

INTRO-2 Mar 30/01

INTRO-3 Mar 30/01

INTRO-4 Mar 30/01

1Mar 30/01

2Mar 30/01

3Mar 30/01

4Mar 30/01

5Mar 30/01

6Mar 30/01

7Mar 30/01

8Mar 30/01

9Mar 30/01

10 Mar 30/01

11 Mar 30/01

12 Mar 30/01

13 Mar 30/01

14 Mar 30/01

15 Mar 30/01

16 Blank

17 Mar 30/01

18 Blank

19 Mar 30/01

20 Blank

21 Mar 30/01

22 Mar 30/01

23 Mar 30/01

24 Mar 30/01

25 Mar 30/01

26 Blank

27 Mar 30/01

28 Blank

29 Mar 30/01

30 Mar 30/01

31 Mar 30/01

32 Mar 30/01

33 Mar 30/01

34 Mar 30/01

35 Mar 30/01

36 Blank

37 Mar 30/01

38 Blank

39 Mar 30/01

40 Mar 30/01

41 Mar 30/01

42 Mar 30/01

43 Mar 30/01

44 Blank

45 Mar 30/01

46 Mar 30/01

47 Mar 30/01

48 Blank

49 Mar 30/01

50 Mar 30/01

51 Mar 30/01

52 Blank

53 Mar 30/01

54 Mar 30/01

55 Mar 30/01

56 Mar 30/01

57 Mar 30/01

58 Blank

59 Mar 30/01

60 Mar 30/01

61 Mar 30/01

62 Mar 30/01

63 Mar 30/01

64 Mar 30/01

65 Mar 30/01

66 Blank

67 Mar 30/01

68 Mar 30/01

69 Mar 30/01

70 Blank

71 Mar 30/01

72 Mar 30/01

73 Mar 30/01

74 Mar 30/01

75 Mar 30/01

76 Mar 30/01

77 Mar 30/01

78 Blank

79 Mar 30/01

80 Mar 30/01

81 Mar 30/01

82 Mar 30/01

83 Mar 30/01

84 Mar 30/01

85 Mar 30/01

86 Mar 30/01

87 Mar 30/01

88 Blank

89 Mar 30/01

90 Mar 30/01

101 Oct 25/02

102 Oct 25/02

103 Oct 25/02

104 Oct 25/02

105 Oct 25/02

106 Blank

107 Oct 25/02

108 Blank

109 Oct 25/02

110 Blank

111 Oct 25/02

112 Blank

113 Oct 25/02

114 Blank

115 Oct 25/02

116 Oct 25/02

117 Oct 25/02

118 Oct 25/02

119 Oct 25/02

120 Oct 25/02

121 Oct 25/02

122 Oct 25/02

122.1 Oct 25/02

122.2 Oct 25/02

122.3 Oct 25/02

122.4 Oct 25/02

122.5 Oct 25/02

122.6 Oct 25/02

I.B. 1516A Page LEP-1

23-12-01

Oct 25/02

Page 8

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

PAGE DATE PAGE DATE PAGE DATE

122.7 Oct 25/02

122.8 Oct 25/02

122.9 Oct 25/02

122.10 Oct 25/02

122.11 Oct 25/02

122.12 Oct 25/02

122.13 Oct 25/02

122.14 Oct 25/02

122.15 Oct 25/02

122.16 Oct 25/02

122.17 Oct 25/02

122.18 Blank

122.19 Oct 25/02

122.20 Blank

123 Oct 25/02

124 Blank

125 Oct 25/02

126 Blank

127 Oct 25/02

128 Blank

129 Oct 25/02

130 Blank

131 Oct 25/02

132 Blank

133 Oct 25/02

134 Blank

135 Oct 25/02

136 Blank

137 Oct 25/02

138 Blank

139 Mar 30/01

140 Blank

141 Mar 30/01

142 Blank

143 Mar 30/01

144 Blank

145 Mar 30/01

146 Blank

147 Mar 30/01

148 Blank

149 Mar 30/01

150 Blank

151 Mar 30/01

152 Blank

153 Mar 30/01

154 Blank

155 Mar 30/01

156 Blank

157 Mar 30/01

158 Blank

159 Mar 30/01

160 Blank

161 Mar 30/01

162 Blank

163 Mar 30/01

164 Blank

165 Mar 30/01

166 Blank

167 Mar 30/01

168 Blank

169 Mar 30/01

170 Blank

171 Mar 30/01

172 Blank

173 Mar 30/01

174 Blank

175 Mar 30/01

176 Blank

177 Mar 30/01

178 Blank

179 Mar 30/01

180 Blank

181 Mar 30/01

182 Blank

183 Mar 30/01

184 Blank

185 Mar 30/01

186 Blank

187 Mar 30/01

188 Blank

189 Mar 30/01

190 Blank

191 Mar 30/01

192 Blank

193 Mar 30/01

194 Blank

195 Mar 30/01

196 Blank

197 Mar 30/01

198 Mar 30/01

198.1 Mar 30/01

198.2 Blank

198.3 Mar 30/01

198.4 Blank

198.5 Mar 30/01

198.6 Blank

198.7 Mar 30/01

198.8 Blank

198.9 Mar 30/01

198.10 Blank

198.11 Mar 30/01

198.12 Blank

198.13 Mar 30/01

198.14 Blank

198.15 Mar 30/01

198.16 Blank

198.17 Mar 30/01

198.18 Blank

198.19 Mar 30/01

198.20 Blank

198.21 Mar 30/01

198.22 Blank

198.23 Mar 30/01

198.24 Blank

198.25 Mar 30/01

198.26 Blank

198.27 Mar 30/01

198.28 Blank

198.29 Mar 30/01

198.30 Blank

198.31 Mar 30/01

198.32 Blank

198.33 Mar 30/01

198.34 Blank

198.35 Mar 30/01

198.36 Blank

198.37 Mar 30/01

198.38 Blank

198.39 Mar 30/01

198.40 Blank

198.41 Mar 30/01

198.42 Blank

198.43 Mar 30/01

198.44 Blank

198.45 Mar 30/01

198.46 Blank

198.47 Mar 30/01

198.48 Blank

198.49 Mar 30/01

198.50 Blank

198.51 Mar 30/01

198.52 Blank

198.53 Mar 30/01

198.54 Blank

198.55 Mar 30/01

198.56 Blank

198.57 Mar 30/01

198.58 Blank

198.59 Mar 30/01

198.60 Blank

198.61 Mar 30/01

198.62 Blank

198.63 Mar 30/01

I.B. 1516A Page LEP-2

23-12-01

Oct 25/02

Page 9

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

PAGE DATE

198.64 Blank

198.65 Mar 30/01

198.66 Blank

198.67 Mar 30/01

198.68 Blank

198.69 Mar 30/01

198.70 Blank

198.71 Mar 30/01

198.72 Blank

198.73 Mar 30/01

198.74 Blank

198.75 Mar 30/01

198.76 Blank

198.77 Mar 30/01

198.78 Blank

198.79 Mar 30/01

198.80 Blank

198.81 Mar 30/01

198.82 Blank

198.83 Mar 30/01

198.84 Blank

198.85 Mar 30/01

198.86 Blank

198.87 Mar 30/01

198.88 Blank

198.89 Mar 30/01

198.90 Blank

198.91 Mar 30/01

198.92 Blank

198.93 Mar 30/01

198.94 Blank

198.95 Mar 30/01

198.96 Blank

198.97 Mar 30/01

198.98 Blank

198.99 Mar 30/01

198.100 Blank

198.101 Mar 30/01

198.102 Mar 30/01

198.103 Mar 30/01

198.104 Blank

198.105 Mar 30/01

198.106 Blank

198.107 Mar 30/01

198.108 Blank

198.109 Mar 30/01

198.110 Blank

198.111 Mar 30/01

198.112 Blank

198.113 Mar 30/01

198.114 Blank

PAGE DATE PAGE DATE

198.115 Mar 30/01

198.116 Blank

198.117 Mar 30/01

198.118 Blank

198.119 Mar 30/01

198.120 Blank

198.121 Mar 30/01

198.122 Blank

198.123 Mar 30/01

198.124 Blank

198.125 Mar 30/01

198.126 Blank

198.127 Mar 30/01

198.128 Blank

198.129 Mar 30/01

198.130 Blank

198.131 Mar 30/01

198.132 Blank

198.133 Mar 30/01

198.134 Blank

198.135 Mar 30/01

198.136 Blank

198.137 Mar 30/01

198.138 Blank

198.139 Mar 30/01

198.140 Blank

198.141 Mar 30/01

198.142 Blank

198.143 Mar 30/01

198.144 Blank

198.145 Mar 30/01

198.146 Blank

198.147 Mar 30/01

198.148 Blank

198.149 Mar 30/01

198.150 Blank

198.151 Mar 30/01

198.152 Blank

198.153 Mar 30/01

198.154 Blank

198.155 Mar 30/01

198.156 Blank

198.157 Mar 30/01

198.158 Blank

198.159 Mar 30/01

198.160 Blank

198.161 Mar 30/01

198.162 Blank

198.163 Mar 30/01

198.164 Blank

198.165 Mar 30/01

198.166 Blank

198.167 Mar 30/01

198.168 Blank

198.169 Mar 30/01

198.170 Blank

198.171 Mar 30/01

198.172 Blank

198.173 Mar 30/01

198.174 Blank

198.175 Mar 30/01

198.176 Blank

198.177 Mar 30/01

198.178 Blank

198.179 Mar 30/01

198.180 Blank

198.181 Mar 30/01

198.182 Blank

198.183 Mar 30/01

198.184 Blank

198.185 Mar 30/01

198.186 Blank

198.187 Mar 30/01

198.188 Blank

198.189 Mar 30/01

198.190 Blank

198.191 Mar 30/01

198.192 Blank

198.193 Mar 30/01

198.194 Blank

198.195 Mar 30/01

198.196 Blank

198.197 Mar 30/01

198.198 Blank

198.199 Mar 30/01

198.200 Blank

198.201 Mar 30/01

198.202 Blank

198.203 Mar 30/01

198.204 Blank

198.205 Mar 30/01

198.206 Blank

301 Mar 30/01

302 Mar 30/01

401 Mar 30/01

402 Mar 30/01

403 Mar 30/01

404 Blank

501 Mar 30/01

I.B. 1516A Page LEP-3

23-12-01

Oct 25/02

Page 10

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

PAGE DATE

502 Mar 30/01

601 Mar 30/01

602 Mar 30/01

603 Mar 30/01

604 Blank

701 Oct 25/02

702 Mar 30/01

703 Mar 30/01

704 Blank

801 Mar 30/01

802 Blank

901 Oct 25/02

902 Oct 25/02

1001 Mar 30/01

1002 Mar 30/01

1003 Mar 30/01

1004 Mar 30/01

1005 Oct 25/02

1006 Blank

1007 Blank

1008 Mar 30/01

1009 Blank

1010 Oct 25/02

1011 Oct 25/02

1012 Oct 25/02

1013 Mar 30/01

1014 Oct 25/02

PAGE DATE PAGE DATE

I.B. 1516A Page LEP-4

23-12-01

Oct 25/02

Page 11

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

TABLE OF CONTENTS

TITLE PAGE

DESCRIPTION AND OPERATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1. General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. Purpose of Equipment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

3. Equipment Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

A. Mechanical . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

B. Electrical . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

C. Equipment Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

D. Operation of HF Data Radio (HFDR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

E. Operation of XK516D1 in Voice Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

4. Theory of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

A. General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

B. Simplified Theory of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

C. Detailed Theory of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

TESTING AND FAULT ISOLATION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

2. Test Equipment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

3. Test Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

4. Power Requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

5. Automated Test Equipment (ATE) Setup. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

A. Software Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

B. ATP Software Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

C. CFDS Software Installation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

6. HF Transceiver Test Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

7. HF Transceiver ATP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

8. Test Complete . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

9. Fault Isolation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .115

A. General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .115

B. Methods of Fault Isolation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .115

C. Fault Isolation Aids . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .115

D. BITE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .116

E. Manually-Initiated Test/Power Up Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122.4

F. Basic Voltage Test Procedure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122.5

G. Transceiver Fault Isolation Chart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122.6

H. Procedure to Verify Failed Frequency with the CFDS Function . . . . . . . . . . . . . . . . . . 122.7

DISASSEMBLY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 301

1. General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 301

I.B.1516A Page TC-1

23-12-01

Oct 25/02

Page 12

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

TITLE PAGE

2. Disassembly Techniques . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .301

3. XK516D1 Transceiver. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .301

CLEANING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 401

1. General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .401

2. Transceiver Procedures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .401

A. Cleaning the Exterior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .401

B. Cleaning the Interior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .402

C. Modules and Circuit Card Assemblies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .402

D. Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .402

E. Machined metal Parts or Assemblies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .403

F. Miscellaneous Metal Parts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .403

G. Nonmetallic Parts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .403

CHECK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 501

1. General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .501

2. General Checks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .501

3. Specific Checks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .501

A. Housing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .501

B. Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .501

C. Covers and Shields . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .501

D. Seals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .501

E. Insulators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .501

F. Modules and CCA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .502

G. Electrical Parts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .502

REPAIR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 601

1. General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .601

2. Circuit Card Assemblies (CCA). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .601

3. Conformal Coating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .602

A. Removal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .602

B. Application . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .602

4. Solder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .602

5. Wire. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .602

6. Painted Surfaces. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .602

7. Transceiver Special Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .603

ASSEMBLY (INCLUDING STORAGE). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 701

1. General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .701

2. Transceiver Assembly. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .701

1I.B.1516A Page TC-2

23-12-01

Mar 30/01

Page 13

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

TITLE PAGE

A. Housing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 701

B. Motherboard, A6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 701

C. EMC Filter, A7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 701

D. Power Supply, A4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 702

E. Power Amplifier, A3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 702

F. Receiver/Exciter Module, A1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 702

G. Airborne Data Link Processor, A2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 702

H. LED Board, A5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 702

I. Interface D, A9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 702

J. Controller D, A8 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 702

K. HF Modem CCA, A10 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 702

L. Chassis Cover . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 702

M. Bottom Cover . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 702

N. Bottom Cover . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 702

3. Storage After Assembly. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 702

A. Temporary Storage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 703

B. Extended Storage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 703

FITS AND CLEARANCES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 801

SPECIAL TOOLS, FIXTURES, AND EQUIPMENT. . . . . . . . . . . . . . . . . . . . . . . . . . . . 901

ILLUSTRATED PARTS LIST . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1001

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1001

2. Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1001

3. Equipment Designator Index. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1002

4. Numerical Index . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1002

5. Manufacturers’ Codes, Names, and Addresses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1002

MANUFACTURERS’ CODES, NAMES, AND ADDRESSES . . . . . . . . . . . . . . . . . . . 1003

EQUIPMENT DESIGNATOR INDEX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1004

NUMERICAL INDEX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1005

I.B.1516A Page TC-3

23-12-01

Mar 30/01

Page 14

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

LIST OF ILLUSTRATIONS

FIGURE DESCRIPTION PAGE

1 XK516D1 HF Transceiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

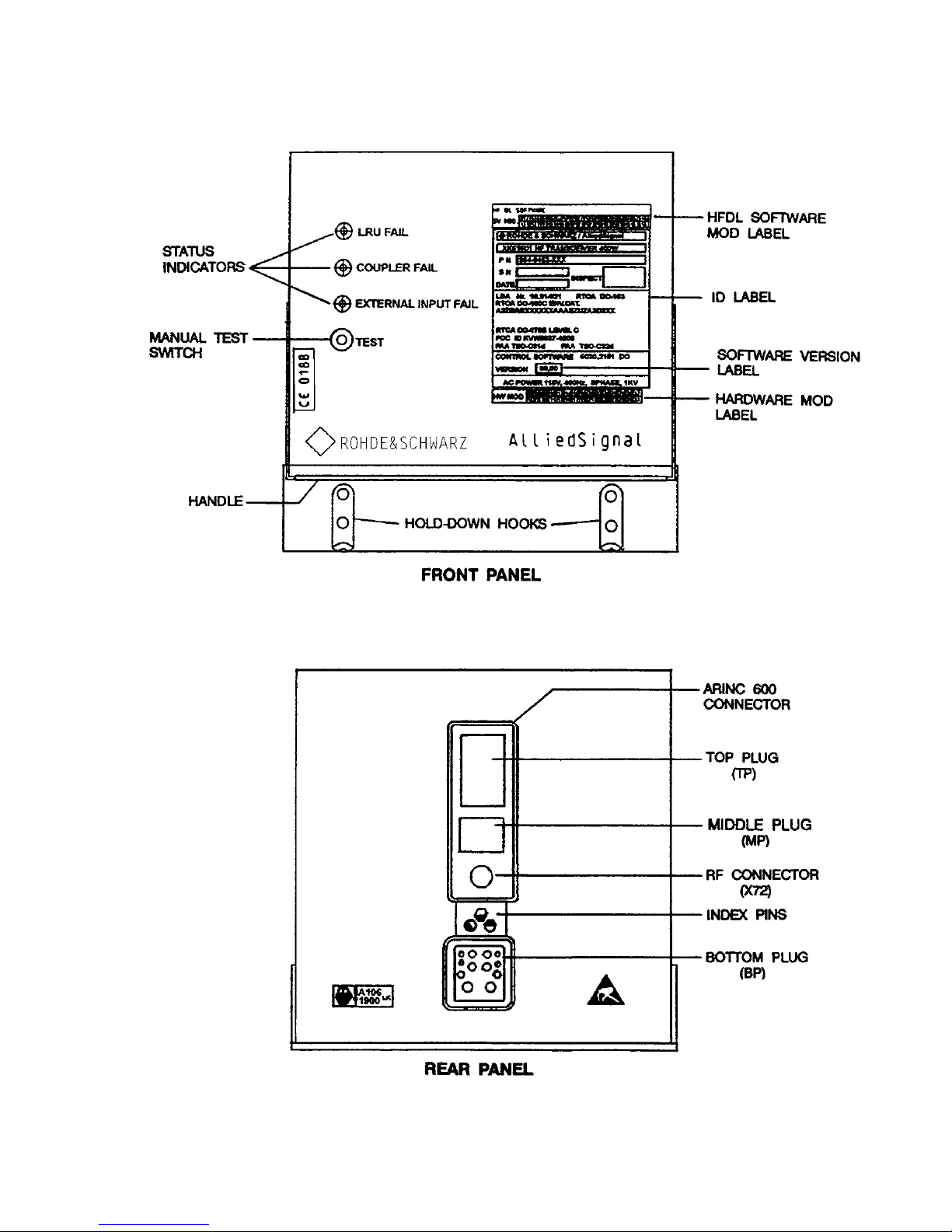

2 Transceiver Front Panel and Rear Connector. . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

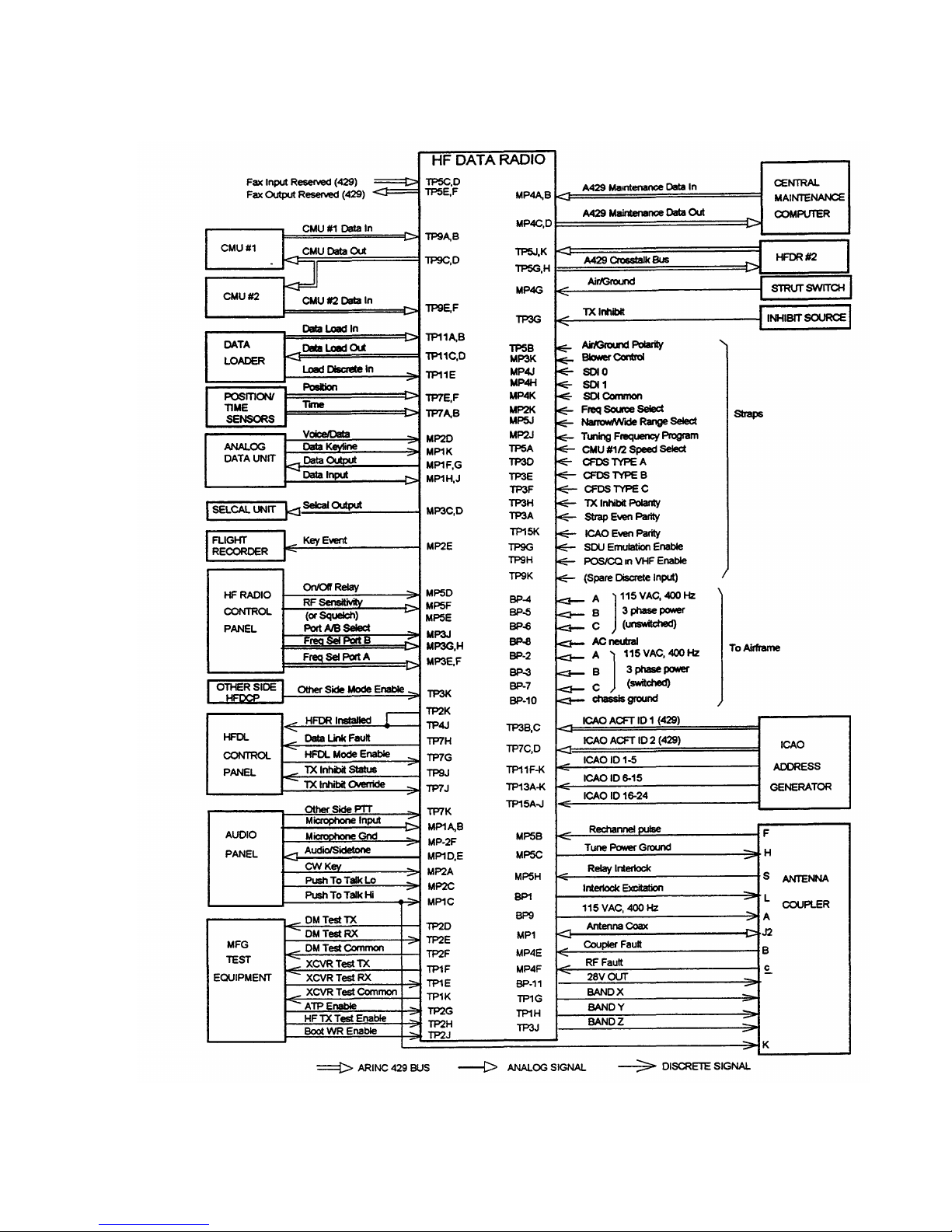

3 Interconnect Diagram, HF Voice/Data Radio System . . . . . . . . . . . . . . . . . . . . . . 5

4 Transceiver Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

5 Interconnect Diagram (Simplified), Transceiver . . . . . . . . . . . . . . . . . . . . . . . . . 13

6 Block Diagram, Transceiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

7 Functional Diagram, Receiver/transmitter, A1. . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

8 Block Diagram, ADP, A2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

9 Connector Pin Assignments, ADP, A2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

10 Block Diagram, HF Modem, A10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

11 Connector Pin Assignments, HF Modem, A10 . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

12 Block Diagram, Synthesizer Loop 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

13 Block Diagram, Synthesizer Loop 2 and 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

14 Frequency Range Corresponding Data Word . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

15 Gate Arrays Register Address. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

16 Synthesizer D6 Divider Position . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

17 Block Diagram, Receiver Analog Front-End . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

18 Block Diagram, Transceiver AF/Digital Section. . . . . . . . . . . . . . . . . . . . . . . . . . . 49

19 Block Diagram, Exciter Analog Section. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

20 Block Diagram, Power Amplifier Board, A3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

21 Block Diagram, Amplifier Board, A31

22 Block Diagram, Amplifier Control, A33 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

23 Block Diagram, Harmonic Filter, A32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

24 Block Diagram, Controller Voice, A8 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

25 Assignment of Chip Select Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

26 Connection of an ASCII Terminal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

27 Format of an ARINC Word . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

28 Minimum Interval between two ARINC Words . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

29 Assignment of ARINC Level to TTL Level. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

30 Linking Diagram of TTL Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

31 Block Diagram, ARINC Input. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

32 Level of Differential Output Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

A3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

33 Block Diagram, ARINC Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

34 Block Diagram, ARINC Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

35 Block Diagram, Regulator Board, A41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

1I.B.1516A Page TC-4

23-12-01

Mar 30/01

Page 15

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

FIGURE DESCRIPTION PAGE

36 Block Diagram, Filter Board, A71 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

101 Test Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

102 Transceiver Main Menu (ABD0048) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

103 Transceiver LRU Identification Menu (ABD0048) . . . . . . . . . . . . . . . . . . . . . . . . 118

104 Transceiver Last Leg Report with No Fault Indicated . . . . . . . . . . . . . . . . . . . . . 118

105 Transceiver Last Leg Report with Failures Detected. . . . . . . . . . . . . . . . . . . . . . 119

106 Previous Leg Report with Failure Detected . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

107 Transceiver Ground Report with No Fault Detected . . . . . . . . . . . . . . . . . . . . . . 120

108 Previous Ground Report with Failure Detected . . . . . . . . . . . . . . . . . . . . . . . . . . 121

109 Transceiver Troubleshooting with No Fault Detected . . . . . . . . . . . . . . . . . . . . . 122

110 Transceiver Troubleshooting Data Menu with Failure Detected

111 Transceiver Ground Scanning Menu with No Fault Detected . . . . . . . . . . . . . .122.1

112 Transceiver Ground Scanning Menu with Failure Detected . . . . . . . . . . . . . . .122.2

113 Table of Fault Messages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .122.3

. . . . . . . . . . . . . 122

114 Table of Test Results . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .122.4

115 Transceiver Test Menu with No Fault Detected . . . . . . . . . . . . . . . . . . . . . . . .122.5

116 Transceiver Test Menu with Failure Detected . . . . . . . . . . . . . . . . . . . . . . . . . .122.5

117 Basic Voltage Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .122.6

117A Sample Test Report . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .122.8

118 Transceiver Fault Isolation Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122.19

119 Schematic, XK516D1 400W HF Transceiver. . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

120 Schematic, Receiver/Exciter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

121 Schematic, RF Board. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

122 Schematic, IF Processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

123 Schematic, Subsynthesizer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

124 Schematic, On Off Board. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 195

125 Schematic, Airborne Datalink Processor, A2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

126 Schematic, HF Modem, A10 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198.19

127 Schematic, Power Amplifier, A3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198.35

128 Schematic, Amplifier Board, A31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198.39

129 Schematic, Harmonic Filter, A32 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198.51

130 Schematic, Amplifier Control, A33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198.65

131 Schematic, Power Supply, A4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198.79

132 Schematic, Regulator Board, A41 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198.83

133 Schematic, Mains Filter, A42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198.95

134 Schematic, LED Board, A5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198.99

135 Schematic, Motherboard, A6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198.101

I.B.1516A Page TC-5

23-12-01

Oct 25/02

Page 16

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

FIGURE DESCRIPTION PAGE

136 Schematic, EMC Filter, A7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198.123

137 Schematic, Controller D, A8 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198.161

138 Schematic, Interface D, A9 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198.177

401 Cleaning Materials . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 401

601 Repair Materials . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 601

701 Assembly Materials. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 701

901 Special Tools, Fixtures, and Equipment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 901

IPL 1 XK516D1 400W HF Transceiver. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1008

1I.B.1516A Page TC-6

23-12-01

Oct 25/02

Page 17

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

INTRODUCTION

This manual was prepared by Honeywell according to ATA Specification No. 100.

The front matter consists of a title page that displays the equipment name and part number, and the

ATA and document numbers assigned to the manual, a Record of Revisions page for recording

revision incorporation, a Record of Temporary Revisions page for recording temporary revision

(yellow page) insertion prior to formal revision, a Service Bulletin List that includes a brief

description of the reason for the bulletin, and the date that Service Bulletin information was

incorporated into the manual, a Table of Contents, and a List of Illustrations.

DESCRIPTION AND OPERATION section contains an equipment illustration, table of leading

particulars, a general description, and a description of operation for electronic assemblies, to assist

in understanding the equipment for fault isolation purposes.

TESTING AND TROUBLESHOOTING section contains tests to enable maintenance personnel to

assess the operational condition of the equipment, a troubleshooting guide to assist in fault

isolation, and schematics.

DISASSEMBLY section contains procedures for disassembling the equipment to the part

replacement level. Complete overhaul procedures are not provided. Specific procedures are

intended to be a supplement to, and are correlated with the Illustrated Parts List (IPL).

CLEANING section contains general cleaning procedures, which should be observed during repair

and part replacement where applicable.

CHECK section contains general areas to visually observe during disassembly and assembly to

assure that equipment operational standards are met.

REPAIR section contains specific instructions for repairing areas of the equipment not specifically

covered in the ASSEMBLY section.

ASSEMBLY section contains all specific instructions necessary for part replacement and to

supplement the IPL.

FITS AND CLEARANCES section contains a list of dimensional values, torques, etc., if required

during assembly. These parameters are also specified in the ASSEMBLY section where applicable.

SPECIAL TOOLS, FIXTURES, AND EQUIPMENT section contains a list of all special equipment

required to perform procedures specified in the other manual sections.

ILLUSTRATED PARTS LIST (IPL) section contains illustrations and parts lists for all equipment

assemblies, subassemblies, and components. The illustrations and parts lists are item-number

keyed for location of parts, and list quantities, part numbers, and part descriptions. An introduction

to the IPL relates how it is used, definitions used, equipment designators, and alphanumerical

indices for parts.

I.B.1516A Page INTRO-1

23-12-01

Mar 30/01

Page 18

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

ABBREVIATIONS AND ACRONYMS

A/D Analog-to-Digital

AC Alternating Current

ACARS Aircraft Communications Addressing and Reporting System

ADP Airborne Datalink Processor

AF Audio Frequency

AGC Automatic Gain Control

AM Amplitude Modulation

AMPL Amplifier

ARINC Aeronautical Radio, Inc.

ATA Air Transport Association

ATE Automatic Test Equipment

ATP Acceptance Test Procedure

BIT Built-In Test

BITE Built-In Test Equipment

BP Bottom Plug

CCelsius

CCA Circuit Card Assembly(ies)

CFDS Central Fault Display System

CMC Central Maintenance Computer

CMU Communications Management Unit

CPLR Coupler

D/A Digital-to-Analog

dB Decibel

dBm Decibel with respect to 1 milliwatt

DC Direct Current

DDS Direct Signal Synthesis

DM Data Module

DMM Digital Multimeter

DOD-HDBK Department of Defense Handbook

DOS Disk Operating System

EMC Electromagnetic Compatibility

EMF Electromotive Force

EEPROM Electrically Erasable Programmable Read Only Memory

EPROM Electrically Programmable Read Only Memory

F Fahrenheit

FAA Federal Aviation Administration

1I.B.1516A Page INTRO-2

23-12-01

Mar 30/01

Page 19

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

Fig. Figure

GND Ground

GSE Ground Support Equipment

HF High Frequency

HFDL High Frequency Data Link

HFDR High Frequency Data Radio

HFM High Frequency Modem

HFVR High Frequency Voice Radio

Hg Mercury

Hz Hertz

IF Intermediate Frequency

kHz kilohertz

kBps kilobits per second

LED Light Emitting Diode

LRU Line Replaceable Unit

MCU Modular Concept Unit

MHz Megahertz

MIL-STD Military Standard

MP Middle Plug

MS Windows Microsoft Windows

mV millivolt

nm Nanometer

PC Personal Computer

PLL Phase-locked Loop

PROM Programmable Read Only Memory

PTT Push-to-Talk

PWB Printed Wiring Board

Ref. Reference

RF Radio Frequency

RTCA Radio Technical Commission for Aeronautics

RX Receive

SSB Single Sideband

TDMA Time Division Multiple Access

TP Test Point or Top Plug

TX Transmit

UTC Universal Time Coordinated

VVolt

VAC Volts Alternating Current

I.B.1516A Page INTRO-3

23-12-01

Mar 30/01

Page 20

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

VCO Voltage-controlled Oscillator

VDC Volts Direct Current

WWatt

XCVR Transceiver

1I.B.1516A Page INTRO-4

23-12-01

Mar 30/01

Page 21

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

TO: HOLDERS OF XK516D1 HF TRANSCEIVER COMPONENT MAINTENANCE MANUAL, PART

NO. 964-0452-0XX, I.B.1516A, REV. 2, DATED SEP 5/01.

REVISION 3 DATED Oct 25/02

HIGHLIGHTS

This manual was revised and only revised pages were printed. Please replace existing pages with the

attached Revision 3 pages, dated Oct 25/02.

Revised pages are outlined below. Changes are marked with a bar in the left-hand column.

PAGE DESCRIPTION

Front Matter Updated to Rev. 3. Added SB28, SB29, and SB30 to the Service Bulletin List.

101 Step 2: Added second sentence.

102 Step 6: Was: Prepare HF ATE for HF Transceiver Test. Renumbered steps (1)

through (4) as A through D.

Step 6B: Was: ". . . Power Meter to the FK516 Coupler, using the appropriate FK516

Coupler Interface Cable.".

103 Added step 7. HF Transceiver ATP. Moved step (4) Task 12: Receive Mode SSB and

AM Tests to step 7F(6).

104 Added step 8. Test Complete.

105-113 Figure 101: Added Note 4 to sheet 1. Added sheets 2 through 5.

115 Renumbered step 6 as 9.

122.7 Moved step H. Transceiver ATP to step 7. Added step H. Procedure to Verify Failed

Frequency with the CFDS Function.

122.8 Added Figure 117A Sample Test Report.

122.19 Added correct sheet 1 to Fig. 118. Renumbered sheets 1 through 8 as 2 through 9.

701 Item 2: Added No. 4.

Item 3: Sealant was 1675D/A and manufacturer was Minnesota Mining and Manufac-

turing Co.

901 Item 1: Added Coupler Test Interface Cable, JcAIR Part No. 55-0958-05.

Item 2: source was: Honeywell. FK517 was FK516.

Item 3: source was: Honeywell.

902 Item 2: Model NAP Z6 was Model NAP 26.

Item 3: (1KW) was (500W). Same source as item 1 was Rohde and Schwarz.

Item 4: Added Agilent Model No.; Agilent Technologies, Inc. was Hewlett-Packard Co.

Added Alternate Test Equipment to CMS 54, items 1 through 6.

1005 6030.1555.02 was 6030.1555.01. 6030.1555.03 was 6030.1555.02.

1010 Added Figure name and number.

1011 Added (VD8286) VS0715705 to items 15, 40, 45, and 55.

1012 Added (VD8286) VS0715705 to item 115.

1014 Item 320 was: 6030.1555.01.

Item 320A was: 6030.1555.02.

I.B.1516A Page 1/2

23-12-01

Oct 25/02

Page 22

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

I.B.1516A Page 3

Transceiver Front Panel and Rear Connector

Figure 2

23-12-01

Mar 30/01

Page 23

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

B. Electrical

The XK516D1 HF Transceiver mode of operation (SSB or AM voice, data, etc.) is controlled

via 2 ARINC 429 serial ports, which are connected on the aircraft to the radio management

panel. The Transceiver is configured for control via ARINC 429 words, both with label 037,

and words with label 205, 206, 207 (installation dependent).

The Transceiver can be connected by means of 2 additional ARINC 429 ports (receive and

transmit) to an on-board central fault display system (CFDS) according to ARINC 604 or to a

central maintenance computer (CMC). There are 3 input discretes (CFDS type programming

pins) that are available in the rear connector to identify the type of aircraft maintenance system. The Transceiver automatically detects which type of aircraft maintenance system (CFDS

or CMC) it is connected to if the CFDS Type input discretes are all open.

Part Number 964-0452-002, 012, and 022 Tranceivers can also be connected to 1 or 2

ACARS Management Units (MU) or Communications Management Units (CMU) by means

of 1 transmit and 2 receive ARINC 429 ports to provide the means to exchange data link

messages with compatible HF Data Link Ground Stations when the Transceiver is operating

in the internal HFDL Data mode. Refer to Fig. 3 for the HF Voice/Data Radio System Interconnect Diagram, showing all the possible connections to other aircraft systems.

The FK 516 Antenna Coupler (part of XK 516D HF Radio system) is connected to the Transceiver by a coaxial cable and a multiwire control cable. The coaxial cable carries the RF signal and control data for the coupler. The coupler control data consists of serial data messages

sent via the inner conductor of the coaxial cable.The multiwire control cable provides the coupler with 115V/400Hz (single phase) power. The control cable also provides the interlock wiring between couplers in dual HF installations. As an option, for single HF installations, the

multiwire control cable may not be used. In this case, the coaxial cable also carries the Coupler power supply (+28V).

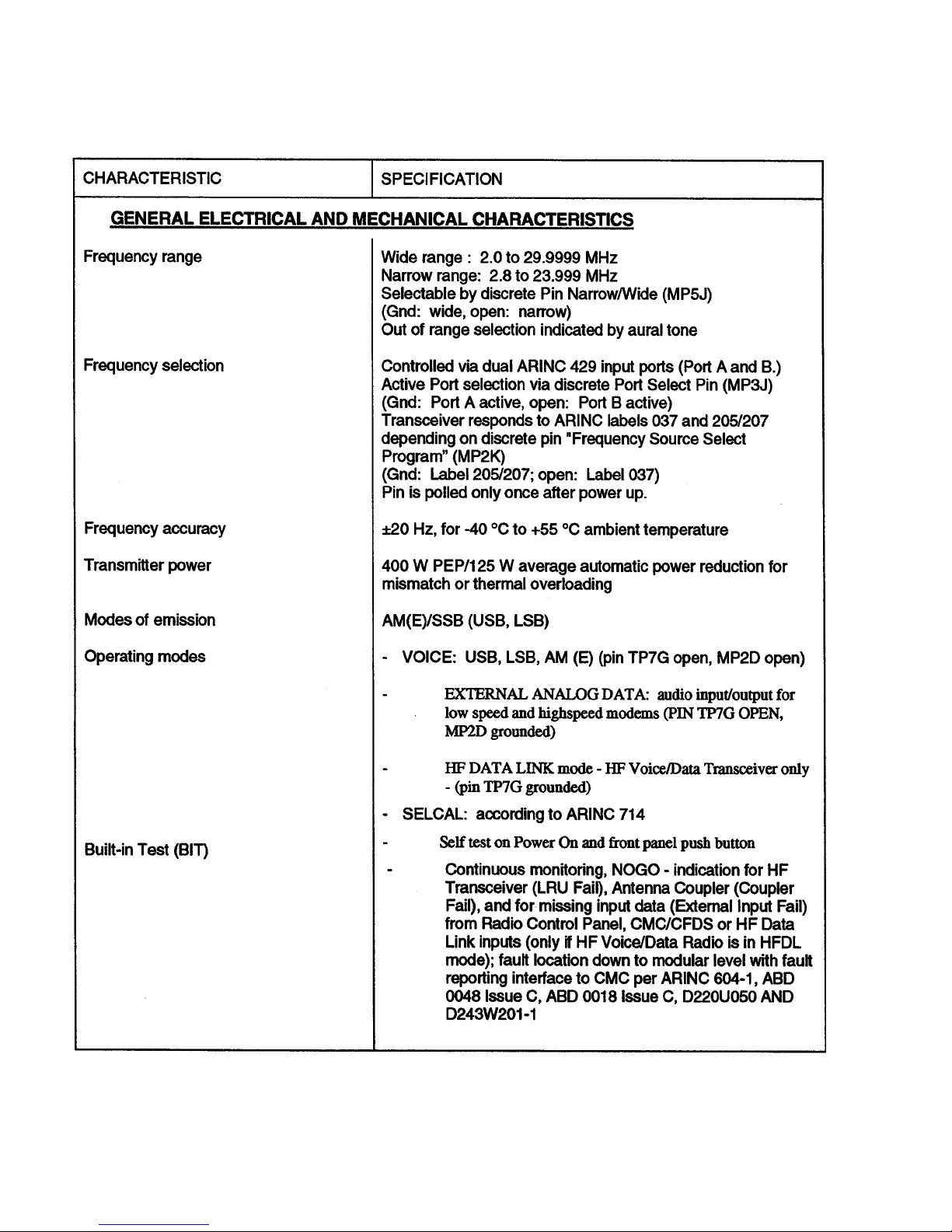

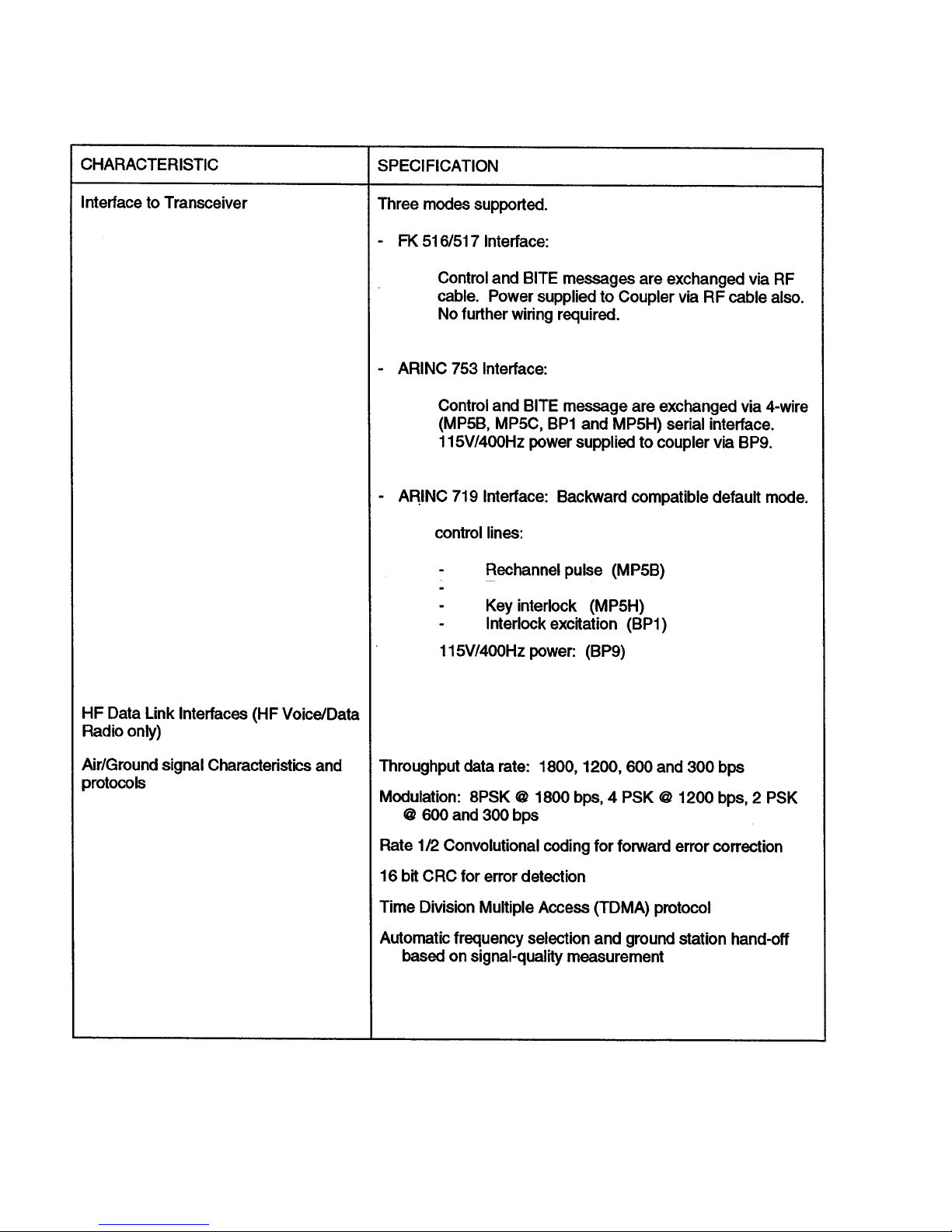

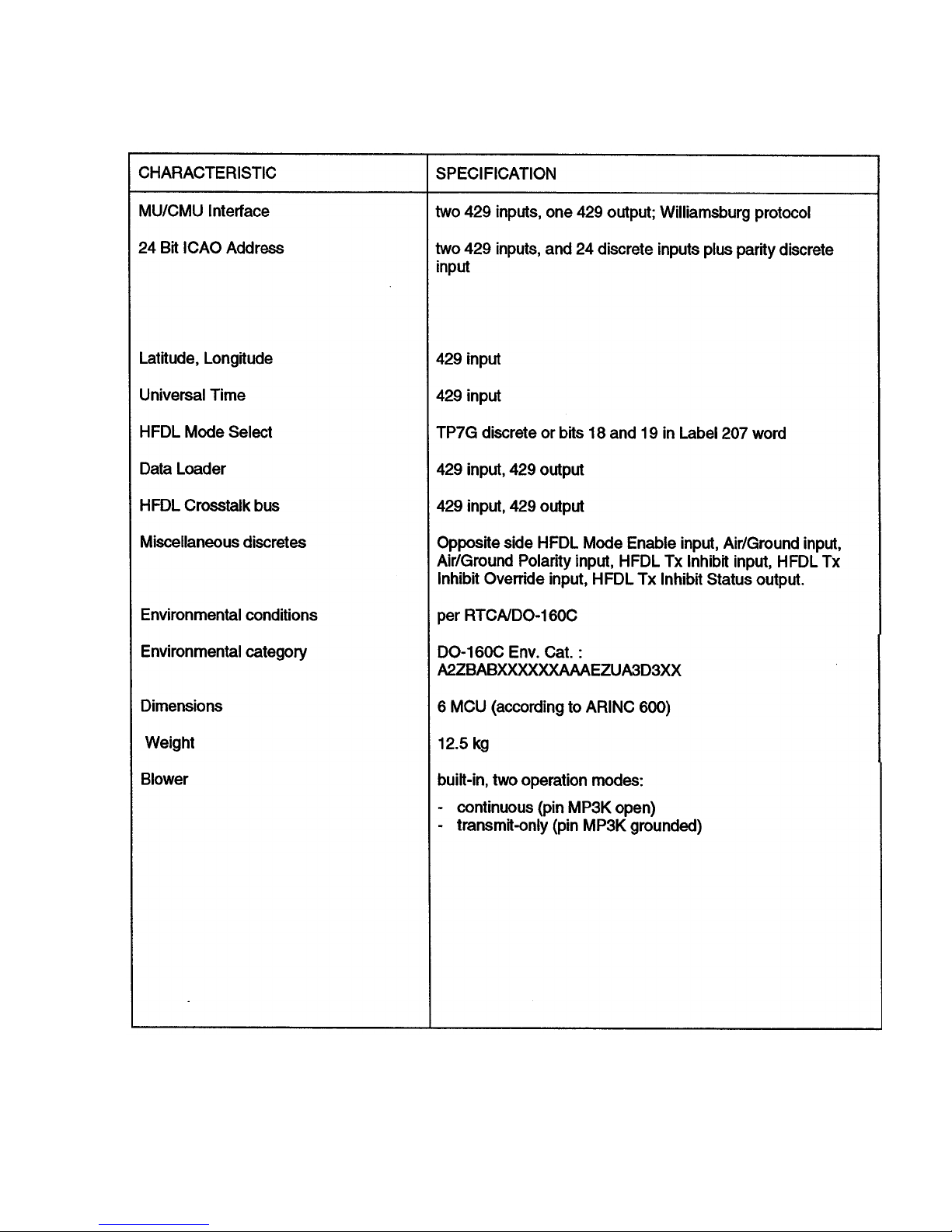

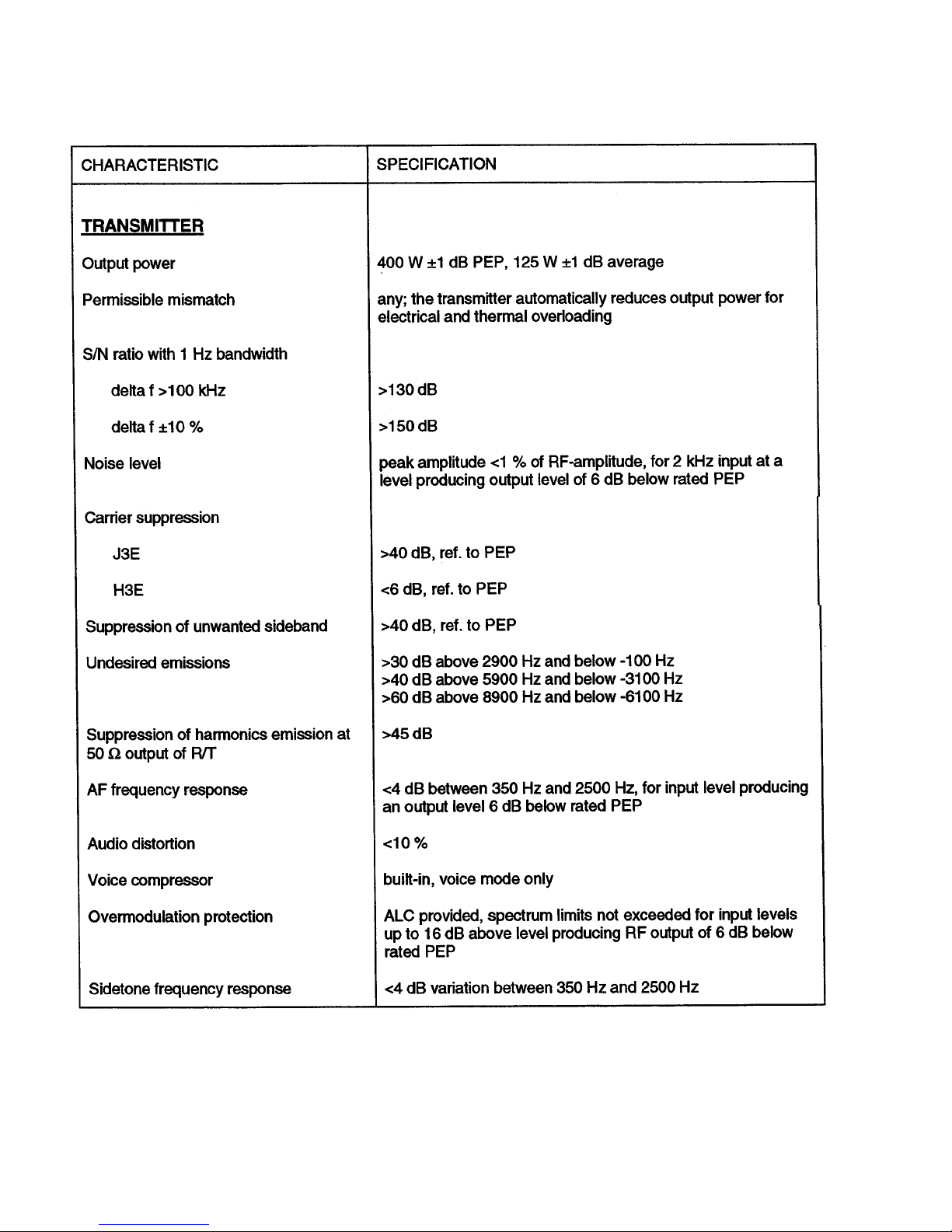

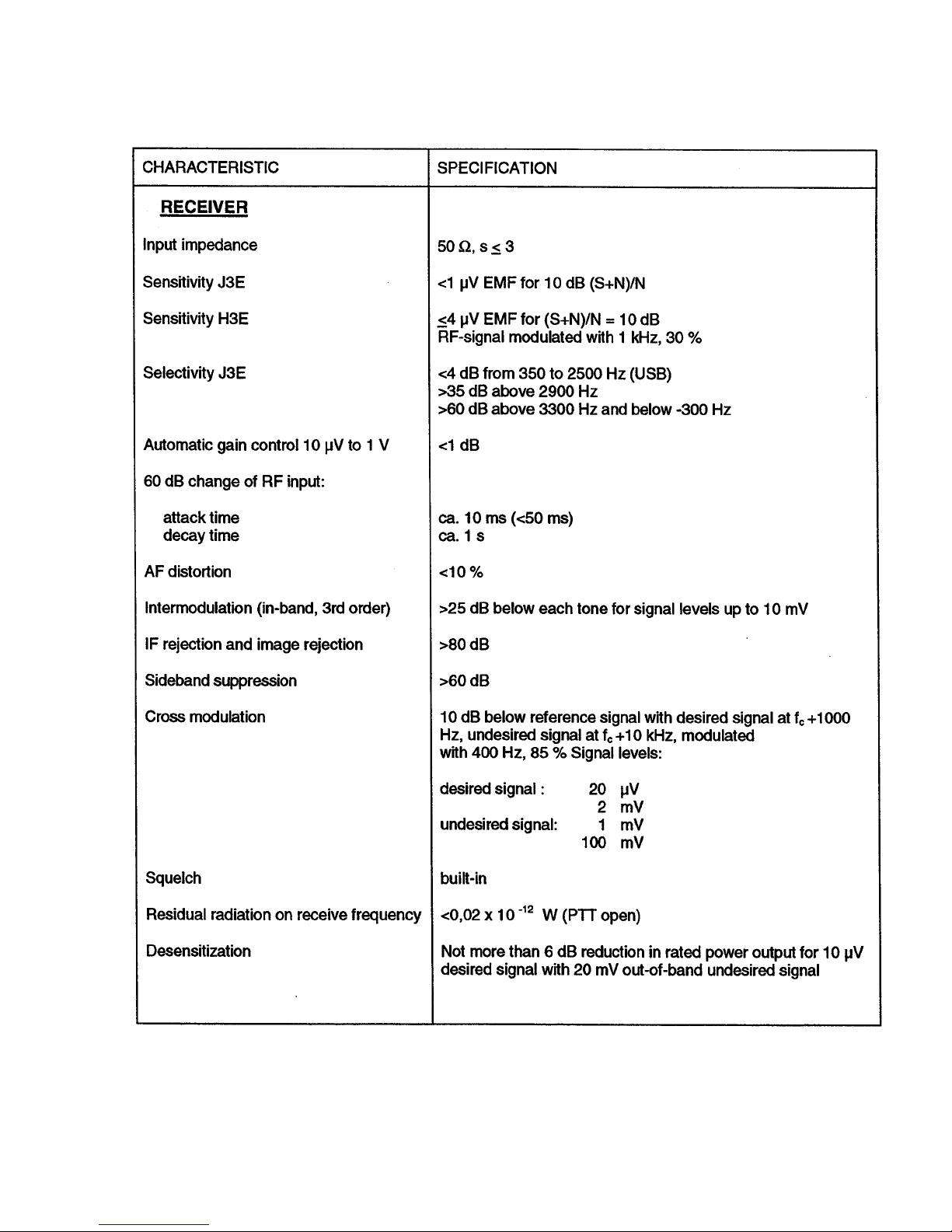

C. Equipment Specifications

The specifications for the XK516D1 HF Transceiver are listed in Fig. 4.

D. Operation of XK516D1 in Voice Mode

(1) To operate the XK516D1 in Voice Mode, the operator selects either SSB Mode or AM

Mode on the Radio Control Panel and selects the frequency.

(2) The radio tunes to the selected frequency, and the received audio can immediately be

heard on the Audio Management System.

(3) To initiate transmission, the microphone keyline (PTT) must be grounded while speaking

into the microphone.

E. Operation of XK516D1 in HF Data Link Mode

(1) To select HF Data Link Mode, the operator must select DATA mode on the Radio Control

Panel.

(2) When the HFDR is placed in data mode, the HFDR performs an automatic frequency

search from a list of frequencies assigned to HF Data Sync operation. Voice communication through this radio is not possible during this mode of operation.

(3) Based on the aircraft’s position and time of day, the HFDR prioritizes its list of possible

frequencies so that frequencies with the highest probability of propagation are tried first.

1I.B.1516A Page 4

23-12-01

Mar 30/01

Page 24

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

Interconnect Diagram, HF Voice/Data Radio System

I.B.1516A Page 5

Figure 3

23-12-01

Mar 30/01

Page 25

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

1I.B.1516A Page 6

Transceiver Specifications

Figure 4 (Sheet 1)

23-12-01

Mar 30/01

Page 26

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

I.B.1516A Page 7

Transceiver Specifications

Figure 4 (Sheet 2)

23-12-01

Mar 30/01

Page 27

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

Backup to 516/517 Interface.

Primary mode.

Tune power (MPSC)

1I.B.1516A Page 8

Transceiver Specifications

Figure 4 (Sheet 3)

23-12-01

Mar 30/01

Page 28

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

I.B.1516A Page 9

Transceiver Specifications

Figure 4 (Sheet 4)

23-12-01

Mar 30/01

Page 29

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

1I.B.1516A Page 10

Transceiver Specifications

Figure 4 (Sheet 5)

23-12-01

Mar 30/01

Page 30

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

I.B.1516A Page 11

Transceiver Specifications

Figure 4 (Sheet 6)

23-12-01

Mar 30/01

Page 31

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

(4) The HFDR then tunes to the first frequency and listens for a periodic uplink (called a

squitter) from the ground station. If no squitter is detected within 32 seconds, the HFDR

tunes to the next frequency on its list.

(5) The HFDR attempts to send a "log-on" downlink when a valid squitter is received. If the

HF Ground Station correctly decodes the downlink, it indicates this in subsequent squitter

uplinks. When this is received by the HFDR, it considers itself logged-on and indicates to

the ACARS MU that data mode is available. The indication on the ACARS display unit

changes from unavailable to available. Transmission of ACARS downlinks and reception

of uplinks is now possible. Note that the HFDR never transmits on an HF frequency

unless the frequency is in its database and a valid squitter is received on that frequency.

(6) If the "log-on" handshake is unsuccessful, the HFDR selects the next frequency from its

list. The HFDR reprioritizes its frequency list when it receives a squitter, since a squitter

contains a list of frequencies that is used by all HF Ground Stations at that moment. The

HFDR indicates that data mode is unavailable after it has exhausted all the frequencies

on its list, but continues to search for a valid connection.

(7) The HFDR begins a search for a new frequency if it fails to detect the periodic squitter or

fails to get a squitter acknowledgement for a downlink.

(8) The existing HF radio system typically shares a common antenna on the aircraft between

the 2 transceivers. If the HFDR detects a Push-To-Talk (PTT) on the other radio operating in voice mode, it delays the transmission of a pending downlink for about 1 minute

(database parameter) to allow the flight crew to complete their voice conversation.

(9) The flight crew may use the HFDR operating in data mode for voice operation at any time

by placing the unit in voice mode via the cockpit control function.

4. Theory of Operation

A. General

The Transceiver performs reception and transmission of voice and data in the frequency

range 2.0MHz to 29.999MHz. The nominal output power of the transmitter is 400W PEP with

a maximum average power of 125W.

A simplified block diagram of the Transceiver is shown in Fig. 5, and a Transceiver interconnect diagram is shown in Fig. 6.

The drive signal for the RF Amplifier, A3, is generated in Receiver/Exciter, A1. The input audio

signal (voice audio from microphone input MP-1A/1B, external audio from AF data input

MP-1H/1J, or internal HFDL data audio from Modem, A10), is digitized in this module and

converted to the necessary modulation signals (SSB or AM(E)) in a signal processor with the

aid of digital signal processing algorithms at a 25kHz IF. This signal undergoes analog conversion again and is up-converted to the final RF level via 2 mixers.

The frequencies of the up-conversion oscillators are generated in a synthesizer according to

the method of digital direct signal synthesis (DDS). This synthesizer also generates the frequencies of the down-conversion oscillators for the receive direction.

1I.B.1516A Page 12

23-12-01

Mar 30/01

Page 32

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

When receiving, the RF signal is down-converted by means of 2 mixer stages to the second

IF of 25kHz. This IF signal is digitized and undergoes further conditioning in the signal processor. The additional functions, such as filtering, demodulation, and control are achieved by

means of software and appropriate algorithms. The processed signal subsequently undergoes analog conversion again, and is output to the appropriate audio interface (voice audio

output to MP-1D/1E, SELCAL audio output to MP-3C/3D, external data output to MP-1F/1G,

internal HFDL data received audio to Modem, A10).

All external interfaces are passed through EMC Filter, A7, to suppress spurious signals.

The internal BITE system of the Transceiver detects a defective LRU by means of continuous

monitoring, and localizes the fault down to functional units on modules (SRUs). In addition,

I.B.1516A

Block Diagram (Simplified), Transceiver

Figure 5

23-12-01

Page 13

Mar 30/01

Page 33

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

built-in tests can be initiated, manually via a front panel test button, or from the aircraft maintenance system, via an ARINC 429 interface.

The results of the continuous monitoring are permanently supplied to the CFDS/CMC in the

normal mode, according to ARINC 604. In the interactive mode, the faults of previous flight

legs, test initiation, and more detailed fault information (troubleshooting data) are displayed.

The BITE system, and modes of operation, are controlled by the Controller Module, A8.

The Transceiver is configured for connection to a 115V, 400Hz, 3-phase, approximately

1000W supply. The internal voltages are generated in the Power Supply, A4.

B. Simplified Theory of Operation

The primary functions of the individual modules in the Transceiver are described here:

(1) Receiver/Exciter, A1

(a) General

The key signal processing functions for transmitting and receiving are executed in

Receiver/Exciter, A1. The signal progression for receive and transmit operation is

outlined in functional diagram of Fig. 7 .

In the transmit mode, these functions are involved:

• Modulation (AM(E)), SSB)

• Automatic level control

• Voice compressor

• Signal synthesis for conversion oscillators

• Conversion of modulated signal to 2nd IF (25kHz), 1st IF (40.025MHz),

and RF frequency.

In the receive mode, these functions are involved:

• Demodulation (SSB, AM(E))

• Automatic gain control

• IF filteringSignal synthesis for conversion oscillators

• Conversion of RF signal to 1st IF (40.025MHz) and 2nd IF (25kHz)

All the signal processing functions performed on the 25kHz frequency are executed

in a signal processor as described here:

The 2nd IF signal (25kHz) is digitized by an A/D converter (100kHz sampling rate)

and further conditioned in the signal processor. After processing, the signal again

undergoes conversion in the D/A converter (12.5kHz sampling rate), and is supplied

to the audio outputs (audio, SELCAL, data) as an audio signal.

In transmission mode, a signal (audio, data) present at the audio inputs is digitized

by means of an A/D converter (100kHz sampling rate), and converted to the 25kHz

2nd IF signal in the signal processor.

The RF signal is supplied to the 1st mixer via a 30MHz, low-pass filter, and convert-

ed to the 1st IF at 40.025MHz with the aid of the conversion oscillator (42.025MHz)

to 7 0.02499MHz). The conversion oscillator is derived from voltage-controlled oscillator (VCO3). VCO3 forms part of a phase-locked loop (PLL), whose reference

frequency is derived from a signal generated by direct digital synthesis (DSS).

I.B.1516A

23-12-01

Page 14

Mar 30/01

Page 34

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

I.B.1516A Page 15/16

Mar 30/01

23-12-01

Interconnect Diagram, Transceiver

Figure 6

KEY INTERLOCK

EMC

FILTER

A7

TP-7B

HFDR #2 IN HI

HFDR #2 IN LO

HFDR #2 OUT HI

HFDR #2 OUT LO

TP-5J

TP-5K

TP-5G

TP-5H

CMU #1 DATA IN HI

TP-9A

TP-9B

CMU #1 DATA IN LO

CMU #2 DATA IN HI

CMU #2 DATA IN LO

TP-9F

TP-9E

CMU DATA OUT HI

TP-9C

CMU DATA OUT LO

TP-9D

TP-5A

CMU BUS SPEED

TP-7A

GMT IN HI

GMT IN LO

TP-7E

TP-7F

POSITION IN HI

POSITION IN LO

ICAO ID#1 IN HI

ICAO ID#1 IN LO

ICAO ID#2 IN HI

ICAO ID#2 IN LO

TP-3B

TP-3C

TP-7C

TP-7D

TP-11A

TP-11B

TP-11C

TP-11D

TP-11E

DATA LOADER IN HI

DATA LOADER IN LO

DATA LOADER OUT HI

DATA LOADER OUT LO

DATA LOAD DISCRETE

TP-5C

TP-5D

TP-5E

TP-5F

FAX REC HI

FAX REC LO

FAX TRANS HI

FAX TRANS LO

TP-9J

TP-7K

TP-3G

TP-3H

TP-7J

TP-15K

*

TP-4J

TP-2K

(24) ICAO DISCRETES

TX INHIBIT STATUS

OTHER SIDE PTT

TX INHIBIT

TX INHIBIT POLARITY

TX INHIBIT OVERRIDE

ICAO EVEN PARITY

HFDR INSTALLED

INTERFACE

A9

AIRBORNE

DATALINK

PROCESSOR

A2

HF

MODEM

A10

CONTROLLER

A8

OTHER SIDE

MODE EN

HFDL MODE ENABLE

FREQ PORT A HI

FREQ PORT A LO

FREQ PORT B HI

FREQ PORT B LO

CFDS TYPE A

CFDS TYPE B

CFDS TYPE C

BITE IN HI

BITE IN LO

BITE OUT HI

BITE OUT LO

PTT HI

PTT OUT

KEY EVENT

VOICE DATA

DATA KEY

PORT SELECT

GROUND/AIR

GROUND/AIR POLARITY

WIDE RANGE SELECT

FREQ SOURCE SELECT

SQUELCH

SENSITIVITY

DATA LINK FAULT

SDI O

SDI 1

STRAP EVEN PARITY

BAND Z

BAND Y

BAND X

KEY INTERLOCK

TUNE POWER

RECHANNEL PULSE

CW KEY

(24) ICAO DISCRETES

HDFR INSTALLED

BITE IN HI

BITE IN LO

BITE OUT HI

BITE OUT LO

ACTIVE FREQ PORT HI

ACTIVE FREQ PORT LO

ADP PRESENT

ADP COMM HI

ADP COMM LO

INT HFDR FAULT

INT SDI0

INT SDI1

TUNE FAIL

TUNE IN PROGRESS

FREQ SRC SEL

GND/AIR

INTFC SPARE 1

INTFC SPARE 2

ICAO EVEN PARITY

TX INHIBIT OVERRIDE

TX INHIBIT POLARITY

TX INHIBIT

OTHER SIDE PTT

HFDR#2 IN HI

HFDR#2 IN LO

HFDR#2 OUT HI

HFDR#2 OUT LO

CMU#1 DATA IN HI

CMU#1 DATA IN LO

CMU#2 DATA IN HI

CMU#2 DATA IN LO

CMU DATA OUT HI

CMU DATA OUT LO

CMU BUS SPEED

GMT IN HI

GMT IN LO

POSITION IN HI

POSITION IN LO

ICAO ID#1 IN HI

ICAO ID#1 IN LO

ICAO ID#2 IN HI

ICAO ID#2 IN LO

DATA LOADER IN HI

DATA LOADER IN LO

DATA LOADER OUT HI

DATA LOADER OUT LO

DATA LOAD DISCRETE

FAX REC HI

FAX REC LO

FAX TRANS LO

FAX TRANS HI

TX INHIBIT STATUS

+15V

-15V

+5V

GND

HFM RESET

HFM PRESENT

HFM FAULT

HFM RX ACTIVE

HFM TX ACTIVE

ADP SPARE 1

ADP SPARE 2

OTHER SIDE MODE EN

DM TEST

DATA ENABLE

PROCESSOR BUS

RECPLS

STRUT

DATA KEY MON

RESET OUT

INT DATA KEY

POWER

SUPPLY

A4

EMC

FILTER

A7

RECEIVER/

EXCITER

A1

POWER

AMPLIFIER

A3

SPARE DISCRETE INPUT 1

SPARE DISCRETE INPUT 2

SPARE DISCRETE INPUT 3

DM TEST TX

RF IN/OUT

AC FAIL

RESET

DM TEST RX

ATP ENABLE

HF TX TEST ENABLE

BOOT WR ENABLE

POS/CQ IN VHF ENABLE

INT DATA KEY

BLOWER

BLOWER

DATA (AF) IN

DATA (AF) IN HI

STRAP EVEN PARITY

BAND Z

BAND Y

BAND X

TUNE POWER

RECHANNEL PULSE

CW KEY

SDI/ICAO COMMON

SDI 1

SDI 0

DATA LINK FAULT

+15v

-15v

+5v

GND

+15v

-15v

+5v

GND

MFG RESERVED CONNECTIONS

RF IN/OUT

+28v

+50v

+5v

GND

+15v

-15v

BP-3

BP-4

BP-5

BP-6

BP-8

BP-9

BP-10

BP-2

BP-7

115V UNSWITCHED A

115V SWITCHED A

115V SWITCHED B

115V SWITCHED C

CHASSIS GND

115V OUT

AC COLD

115V UNSWITCHED B

115V UNSWITCHED C

+15v

-15v

+5v

GND

+15v

-15v

+5v

GND

TX TIM

RTS

TX DATA

CTS

RX DATA

DATA (AF) OUT

TX DATA AF

RX DATA AF

DATA (AF) IN LO

DATA (AF) OUT HI

DATA (AF) OUT LO

MIKE IN LO

MIKE IN HI

MIKE GND

SENSITIVITY

SQUELCH

FREQ SOURCE SELECT

WIDE RANGE SELECT

GROUND/AIR POLARITY

GROUND/AIR

PORT SELECT

DATA KEY

VOICE DATA

KEY EVENT

PTT LO

PTT HI

BITE OUT LO

BITE OUT HI

BITE IN LO

BITE IN HI

CFDS TYPE C

CFDS TYPE B

CFDS TYPE A

FREQ PORT B LO

FREQ PORT B HI

FREQ PORT A LO

FREQ PORT A HI

HFDL MODE ENABLE

OTHER SIDE MODE EN

AUDIO OUT HI

AUDIO OUT LO

SELCAL HI

SELCAL LO

ON/OFF RELAY

COUPLER FAULT

RF FAULT

28V OUT

INTL EXCIT

(7) TEST ID

SPARE DISCRETE INPUT

SDU EMULATION ENABLE

BOOT WR ENABLE

HF TX TEST ENABLE

ATP ENABLE

DM TEST COM

DM TEST RX

DM TEST TX

TP-2D

TP-2E

TP-2F

TP-2G

TP-2H

TP-2J

TP-9G

TP-9H

TP-9K

TP-1F

TP-1E

TP-1K

TEST COM

TEST TX

TEST RX

TEST TX

TEST RX

+28v

+50v

+5v

GND

+15v

-15v

+28v

+5v

GND

+15v

-15v

MIKE IN HI

MIKE IN LO

AUDIO OUT

SELCAL

MP-4D

MP-1C

MP-2C

MP-2E

MP-2D

MP-1K

MP-3J

MP-4G

TP-5B

MP-2K

MP-5J

MP-5E

MP-5F

TP-7H

MP-4H

MP-4J

MP-4K

MP-2A

MP-5B

MP-5C

MP-5H

* *

TP-1G

TP-1H

TP-3K

TP-7G

MP-3E

MP-3F

MP-3G

MP-3H

TP-3D

TP-3E

TP-3F

MP-4A

MP-4B

MP-4C

TP-3J

TP-3A

MP-3K

MP-1H

MP-1J

MP-1F

MP-1G

MP-1A

MP-1B

MP-2F

MP-1D

MP-1E

MP-3C

MP-3D

MP-5D

MP-4E

MP-4F

BP-11

BP-1

ICAO ID 6

ICAO ID 7

ICAO ID 8

ICAO ID 9

ICAO ID 10

TP-13A

TP-13B

TP-13C

TP-13D

TP-13E

ICAO ID 11

ICAO ID 12

ICAO ID 13

ICAO ID 14

ICAO ID 15

TP-13F

TP-13G

TP-13H

TP-13J

TP-13K

ICAO ID 16

ICAO ID 17

ICAO ID 18

ICAO ID 19

ICAO ID 20

TP-15A

TP-15B

TP-15C

TP-15D

TP-15E

ICAO ID 21

ICAO ID 22

ICAO ID 23

ICAO ID 24

TP-15F

TP-15G

TP-15H

TP-15J

**

UNTID0

UNTID1

UNTID2

UNTID3

UNTID4

UNTID5

UNTID6

TP-2C

TP-1A

TP-1B

TP-1C

TP-1D

TP-2A

TP-2B

*

ICAO ID 1

ICAO ID 2

ICAO ID 3

ICAO ID 4

ICAO ID 5

TP-11F

TP-11G

TP-11H

TP-11J

TP-11K

Page 35

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

I.B.1516A Page 17/18

Mar 30/01

23-12-01

Functional Diagram, Receiver/Transmitter, A1

Figure 7

Page 36

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

I.B.1516A Page 19/20

Mar 30/01

23-12-01

Block Diagram, Power Amplifier Board, A3

Figure 8

Page 37

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

Along with the reference signal, the phase comparator of the PLL is also supplied

with the down-converted frequency of VCO3. The mixing frequency for this down

conversion is obtained from a second PLL. The reference frequency of the 2nd PLL

is derived from a crystal oscillator (10Mhz), which is scaled down by a factor of 100.

The 1st IF of 40.025MHz is supplied to the 2nd mixer via a variable amplifier and

converted to the 2nd IF of 25kHz. The mixing frequency for this mixer (40MHz) is

also generated with the aid of a PLL, whose reference frequency (1MHz) is derived

from a crystal oscillator.

The 2nd IF signal (25kHz) is digitized by a 16-bit A/D converter and supplied to the

signal processor. The demodulation and conversion of the signal to an audio frequency (AF) signal is executed in the signal processor.

The principal functions performed in the signal processor are:

• Demodulation (SSB, AM)

• IF filtering for audio, SELCAL, and AM

• Automatic gain control (90dB dynamic range)

• Squelch

• The audio signal is applied via D/A converter (sampling rate 12.5kHz)

to the audio, SELCAL, and data outputs

(b) Transmit Mode

The audio signal (voice or data) is digitized by the 16-bit A/D converter (100kHz

sampling rate) and read into the signal processor.

The functions that are performed in the signal processor by means of software are:

• Filtering of the audio signal

• Voice compression

• Automatic level control

• Conversion to 25kHz IF frequency

• Conversion of SSB or AM(E) signal

• Mixing to 25kHz

The 25kHz IF signal thus created undergoes analog conversion in a D/A converter

(sampling rate 100kHz). The signal is finally converted to the frequency in the 2.0

to 29.9999MHz range.

The conversion oscillators are generated in the same way as for receive operation.

The output signal of Receiver/Exciter, A1, is a –7dBm (nominal) signal, which is

supplied to the Power Amplifier, A3.

The Receiver/Exciter module is connected to the Controller module, A8, via the

module bus, where all settings are made; e.g., frequency, operating mode, transmission mode, BIT functions.

BIT results and the signal level can be determined via the module bus.

(2) Power Amplifier, A3

Power Amplifier, A3, is composed of Amplifier Board, A31, Harmonic Filter, A32, and Amplifier Control, A33. Refer to Fig. 8 for block diagram.

I.B.1516A

23-12-01

Page 21

Mar 30/01

Page 38

Honeywell

COMPONENT MAINTENANCE MANUAL

PART NUMBER 964-0452

(a) Amplifier Board, A31

The Amplifier Board amplifies the RF input from Receiver/Exciter, A1, with a level

of –7dBm ± 3dB Peak Envelope Power (PEP) or Continuous Wave (CW) to a maximum output power of 125W continuous wave (+51dBm) or 400W +0.5dB PEP

(56dBm +0.5dB). It is composed of 4 amplifier stages, the final stage operates in

push-pull mode. A voltage-controlled attenuator is inserted between the 1st amplifier stage and the 2nd amplifier stage with the function of regulating the output power of Amplifier Board, A31, at a constant level, depending upon the ALC voltage

generated by Amplifier Control, A33.

Amplifier board, A31, also contains a number of monitoring and measuring circuits.

(b) Cooling

The preamplifier and final stage transistors are cooled by a heat sink. An internal

blower ensures the airflow through the Transceiver, and maintains proper cooling

of Power Amplifier, A3, during transmit operations.

(c) Harmonic Filter, A32

Harmonic Filter, A32, contains 1 transmit/receive relay, 7 low-pass filters, 1 or 2 of

which are switched on in order to suppress the harmonics in the RF signal path, depending upon the transmission frequency, as well as a directional coupler for measuring the forward and reflected power.

(d) Modem

The Harmonic Filter, A32, also contains a modem with frequency-division multiplex-

ing, permitting simultaneous bidirectional data transfer between transceiver and antenna coupler vial the coaxial line.

(e) Amplifier Control, A33

Amplifier Control, A33, provides the interface between Controller, A8, and Amplifier

Board, A31, and Harmonic Filter, A32. This connection links the information coming

via the module data bus with internal module signals to obtain control signals for the

Amplifier Board and Harmonic Filter. In addition, the ALC control voltage for regulating the transceiver output power is generated here from various analog measured signals from Amplifier board, A31, and Harmonic Filter, A32.

(3) Power Supply, A4

The Power Supply, A4, is composed of a 3-phase transformer, Regulator Board, A41,

and Mains Filter, A42. The transformer is delta-connected at the input end and the 5 secondary windings are all star-connected. The star point for secondary winding 5 is directly