Page 1

查询MB90246供应商

FUJITSU SEMICONDUCTOR

DATA SHEET

16-bit Proprietary Microcontroller

CMOS

F2MC-16F MB90246A Series

MB90246A

DESCRIPTION

■

The MB90246A series is a 16-bit microcontroller optimum to control mechatronics such as a hard disk drive unit.

2

The instruction set of F

instruction sets for high-level languages, extended addressing mode, enhanced multiplication/division

instructions, and enhanced bit manipulation instructions. The microcontroller has a 32-bit accumulator for

processing long word data (32-bit).

MC-16F CPU core inherits AT architecture of F2MC*-16/16H family with additional

DS07-13505-5E

The MB90246A series contains a production addition unit as peripheral resources for enabling easy

implementation of functions supported by IIR and FIR digital filters. It also supports a wealth of peripheral functions

including:

- an 8/10-bit A/D converter having eight channels;

- an 8-bit D/A converter having three channels;

- UART;

- an 8-bit PWM timer having four channels;

- a timer having three plus one channels;

- an input capture (ICU) having two channels; and

- a DTP/external interrupt circuit having four channels.

2

MC stands for FUJITSU Flexible Microcontroller.

* :F

PACKAGE

■

100-pin Plastic LQFP

(FPT-100P-M05)

Page 2

MB90246A Series

FEATURES

■

•Clock

Operating clock can be selected from divided-by-2, 4, 8 or 32 of oscillation (at oscillation of 32 MHz, 1 MHz

to 16 MHz).

Minimum instruction execution time of 62.5 ns (at machine clock of 16 MHz)

• CPU addressing space of 16 Mbytes

Internal addressing of 24-bit

External accessing can be performed by selecting 8/16-bit bus width (external bus mode)

• Instruction set optimized for controller applications

Rich data types (bit, byte, word, long word)

Rich addressing mode (23 types)

High code efficiency

Enhanced precision calculation realized by the 32-bit accumulator

Signed multiplication/division instruction

• Instruction set designed for high level language (C) and multi-task operations

Adoption of system stack pointer

Enhanced pointer indirect instructions

Barrel shift instructions

• Enhanced execution speed

8-byte instruction queue

• Enhanced interrupt function

Priority levels: 8 levels

External interrupt input ports: 4 ports

• Automatic data transmission function independent of CPU operation

Extended intelligent I/O service function (EI

• Low-power consumption (stand-by) mode

Sleep mode (mode in which CPU operating clock is stopped)

Stop mode (mode in which oscillation is stopped)

Hardware stand-by mode

Gear function

•Process

CMOS technology

• I/O port

General-purpose I/O ports (CMOS): 38

General-purpose I/O ports (TTL): 11

General-purpose I/O ports (N-ch open-drain): 8

Total: 57

•Timer

Timebase timer/watchdog timer: 1 channel

8-bit PWM timer: 4 channels

16-bit re-load timer: 3 channels

• 16-bit I/O timer

16-bit free-run timer: 1 channel

Input capture (ICU): 2 channels

• I/O simple serial interface

Clock synchronized transmission can be used.

• UART: 1 channel

Clock asynchronized or clock synchronized serial transmission can be selectively used.

• DTP/external interrupt circuit: 4 channels

A module for starting extended intelligent I/O service (EI

by an external input.

2

OS)

2

OS) and generating an external interrupt triggered

(Continued)

2

Page 3

MB90246A Series

(Continued)

• Delayed interrupt generation module

Generates an interrupt request for switching tasks.

• 8/10-bit A/D converter: 8 channels

8-bit or 10-bit resolution can be selectively used.

Starting by an external trigger input.

• 8-bit D/A converter

Resolution: 8 bits × 3 channels

• DSP interface for the IIR filter

Function dedicated to IIR calculation

Up to eight items of results of signed multiplication of 16 × 16 bits are added.

Execution time of : 0.625 µs (When oscillation is 32 MHz and when N = M =3)

Up to three N and M values can be set at your disposal.

NM

Yk = Σ bn Yk – n + Σ am Xk – m

n = 0 m = 0

3

Page 4

MB90246A Series

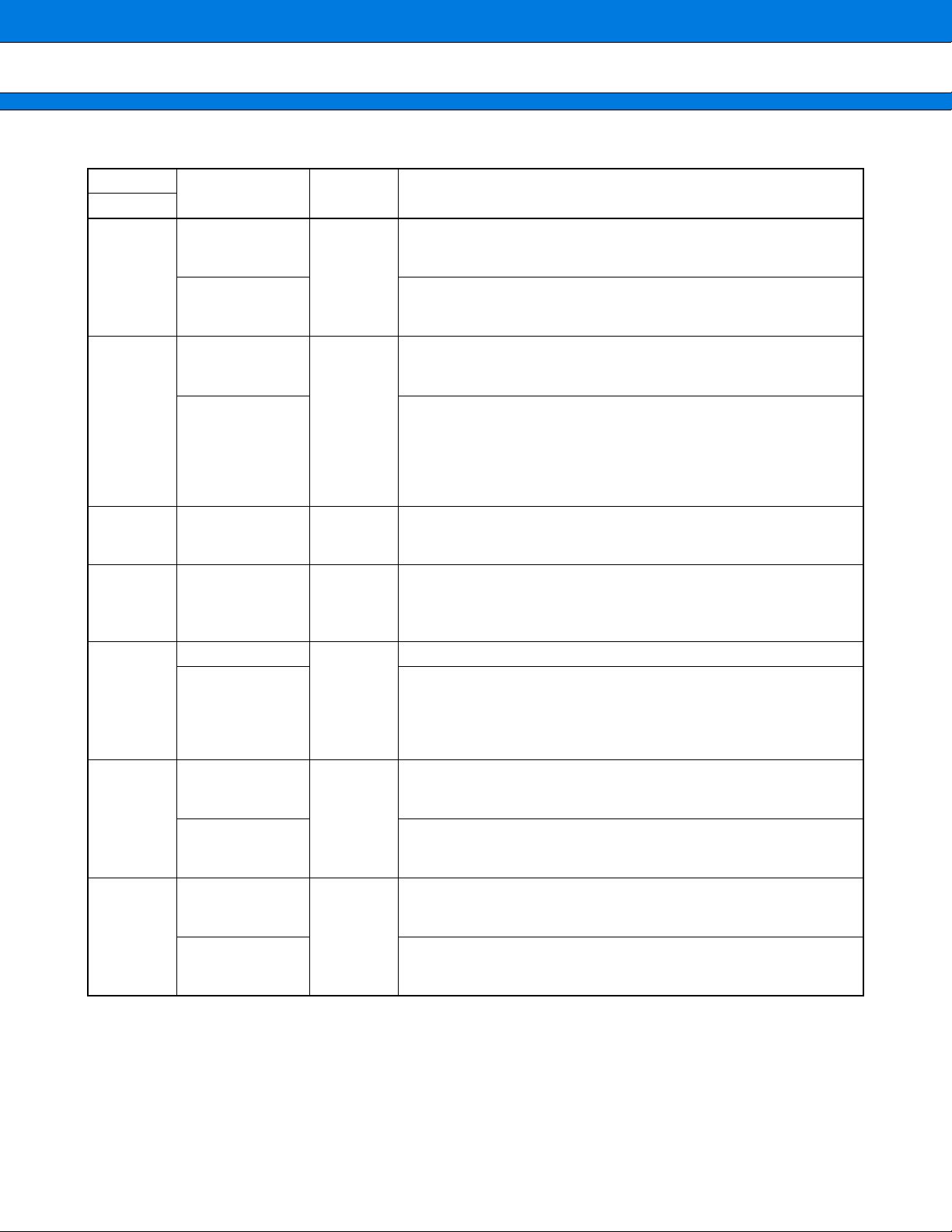

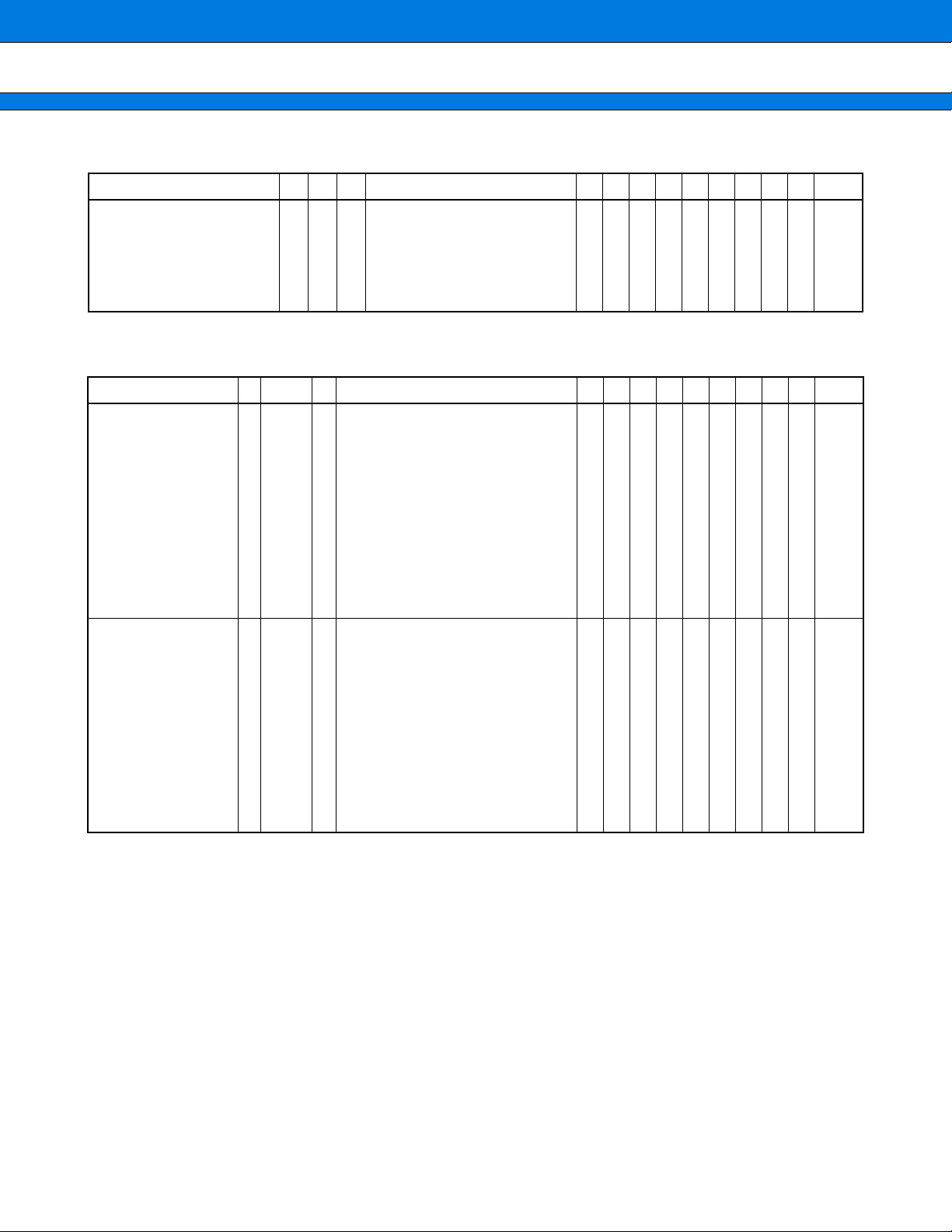

PRODUCT LINEUP

■

Part number

Item

Classification Mass-produced product Evaluation product

ROM size None

RAM size 4 k × 8 bits 6 k × 8 bits

CPU functions

Ports

Timebase timer

Watchdog timer

MB90246A

The number of instructions: 412

Instruction bit length: 8 bits, 16 bits

Instruction length: 1 byte to 7 bytes

Data bit length: 1 bit, 4 bits, 8 bits, 16 bits, 32 bits

Minimum execution time: 62.5 ns (at machine clock of 16 MHz)

Interrupt processing time: 1.0 µs (at machine clock of 16 MHz, minimum

value)

General-purpose I/O ports (CMOS output): 38

General-purpose I/O ports (TTL input): 11

General-purpose I/O ports (N-ch open-drain output): 8

Total: 57

18-bit counter

Interrupt interval: 0.256 ms, 1.024 ms, 4.096 ms, 16.384 ms

(at oscillation of 32 MHz)

Reset generation interval: 3.58 ms, 14.33 ms, 28.67 ms, 57.34 ms

(at oscillation of 32 MHz, minimum value)

MB90V246

8/16-bit PWM timer

16-bit re-load timer

16-bit free-run

16-bit

I/O timer

I/O simple serial interface

UART

DTP/external interrupt circuit

Delayed interrupt generation

module

timer

Input capture

(ICU)

Number of channels: 4

Pulse interval: 0.25 µs to 32.77 ms (at oscillation of 32 MHz)

Number of channels: 3

16-bit re-load timer operation

Interval: 125 ns to 131 ms (at machine clock of 16 MHz)

External event count can be performed.

Number of channel: 1

Overflow interrupts or intermediate bit interrupts may be generated.

Number of channel: 2

Rewriting a register value upon a pin input (rising, falling, or both edges)

Number of channels: 2

Clock synchronized transmission (62.5 kbps to 8 Mbps)

Clock asynchronized transmission (2404 bps to 500 kbps)

Clock synchronized transmission (250 kbps to 2 Mbps)

Transmission can be performed by bi-directional serial transmission or by

master/slave connection.

Number of inputs: 4

Started by a rising edge, a falling edge, an “H” level input, or an “L” level input.

External interrupt circuit or extended intelligent I/O service (EI

An interrupt generation module for switching tasks

used in real-time operating systems.

2

OS) can be used.

(Continued)

4

Page 5

(Continued)

MB90246A Series

Part number

Item

8/10-bit A/D converter

Continuous conversion mode (converts selected channel continuously)

Stop conversion mode (converts selected channel and stop operation repeatedly)

8-bit D/A converter

DSP interface for the IIR

filter

Low-power consumption

(stand-by) mode

Process CMOS

Power supply voltage for

operation*

MB90246A

Conversion precision: 10-bit or 8-bit can be selectively used.

Number of inputs: 8

One-shot conversion mode (converts selected channel only once)

Number of channels: 3

Resolution: 8 bits

Based on the R-2R system

Function dedicated to IIR calculation

Up to 8 items of results of signed

multiplication of 16 × 16 bits are added.

Execution time of : 0.625 µs

(When oscillation is 32 MHz and when N = M = 3)

Up to three N and M values can be set at your disposal.

Sleep/stop/hardware stand-by/gear function

NM

Yk = Σ bn Yk – n + Σ am Xk – m

n = 0 m = 0

4.5 V to 5.5 V

MB90V246

* : Varies with conditions such as the operating frequency. (See section “■ Electrical Characteristics.”) Assurance

for the MB90V246 is given only for operation with a tool at a power voltage of 4.5 V to 5.5 V, an operating

temperature of 0 to 70 degrees centigrade, and an clock frequency of 1.6 MHz to 32 MHz.

Note: A 64-word RAM for product addition is supported in addition to the above RAMs.

PACKAGE AND CORRESPONDING PRODUCTS

■

Package MB90246A MB90V246

FPT-100P-M05 ×

PGA-256C-A02 ×

: Available × : Not available

Note: For more information about each package, see section “■ Package Dimensions.”

DIFFERENCES AMONG PRODUCTS

■

Memory Size

In evaluation with an evaluation chips, note the difference between the evaluation chip and the chip actually used.

The RAM size is 4 Kbytes for the MB90246A, and 6 Kbytes for the MB90V246.

5

Page 6

MB90246A Series

PIN ASSIGNMENT

■

A01

A00

P17/D15

P16/D14

100999897969594939291908988878685848382818079787776

A02

A03

A04

A05

A06

A07

A08

A09

SS

V

A10

A11

A12

A13

A14

A15

P40/A16

P41/A17

P42/A18

P43/A19

P44/A20

CC

V

P45/A21

P46/A22

P47/A23

P70/ASR0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26272829303132333435363738394041424344454647484950

P15/D13

P14/D12

P13/D11

P12/D10

P11/D09

P10/D08

(Top view)

P07

P06

P05

P04

P03

P02

P01

P00

CC

V

X1X0VSSP57

P56/RD

P55/WR/WRL

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

RST

P54/WRH

P53/HRQ

P52/HAK

P51/RDY

P50/CLK

PA5/SCK2

PA4/SOD2

PA3/SID2

PA2/SCK1

PA1/SOD1

PA0/SID1

P96/SCK0

P95/SOD0

P94/SID0

P93/INT3/PWM3

P92/INT2/ATG

P91/INT1

P90/INT0

P87/PWM2

P86/PWM1

P85/PWM0

P84/DAO2

P83/DAO1

P82/DAO0

P71/ASR1

P72

P73

P74/TIN0/TOT0

P75/TIN1/TOT1

P76/TIN2/TOT2

AVCCAVRH

AVRL

AVSSP60/AN0

P61/AN1

P62/AN2

P63/AN3

VSSP64/AN4

P65/AN5

P66/AN6

P67/AN7

DVRH

DVRL

MD0

MD1

MD2

HST

(FPT-100P-M05)

6

Page 7

PIN DESCRIPTION

■

MB90246A Series

Pin no.

LQFP*

80 X0 A This is a crystal oscillator pin.

81 X1

47 to 49 MD0 to MD2 C This is an input pin for selecting operation modes.

75 RST B This is external reset request signal.

50 HST C This is a hardware stand-by input pin.

91 to 98 P10 to P17 D This is a general-purpose I/O port.

16 to 20,

22 to 24

70 P50 E This is a general-purpose I/O port.

71 P51 D This is a general-purpose I/O port.

72 P52 D This is a general-purpose I/O port.

73 P53 D This is a general-purpose I/O port.

74 P54 E This is a general-purpose I/O port.

Pin name

D08 to D15 This is an I/O pin for the upper 8-bit of the external address data

P40 to P44,

P45 to P47

A16 to A20,

A21 to A23

CLK This is a CLK output pin.

RDY This is a ready input pin.

HAK

HRQ This is a hold request input pin.

WRH

Circuit

type

Connect directly to V

This function is valid in the 8-bit mode where the external bus is

valid.

bus.

This function is valid in the 16-bit mode where the external bus is

valid.

E This is a general-purpose I/O port.

This function becomes valid in the bit where the upper address

control register is set to select a port.

This is an output pin for the upper 8-bit of the external address bus.

This function is valid in the mode where the external bus is valid

and the upper address control register is set to select an address.

This function becomes valid when the CLK output is disabled.

This function becomes valid when CLK output is enabled.

This function becomes valid when the external ready function are

disabled.

This function becomes valid when the external ready function is

enabled.

This function becomes valid when the hold function are disabled.

This is a hold acknowledge output pin.

This function becomes valid when the hold function is enabled.

This function becomes valid when the hold function are disabled.

This function becomes valid when the hold function is enabled.

This function becomes valid, in the external bus 8-bit mode, or

WRH

pin output is disabled.

This is a write strobe output pin for the upper 8-bit of the data bus.

This function becomes valid when the external bus 16-bit mode is

selected, and WRH

CC or VSS.

output pin is enabled.

Function

* :FPT-100P-M05

(Continued)

7

Page 8

MB90246A Series

Pin no.

LQFP*

76 P55 E This is a general-purpose I/O port.

77 P56 E This pin cannot be used as a general-purpose port.

78,28,27 P57,P73,P72 E This is a general-purpose I/O port.

36 to 39,

41 to 44

25 P70 E This is a general-purpose I/O port.

26 P71 E This is a general-purpose I/O port.

29 to 31 P74 to P76 E This is a general-purpose I/O port.

51 to 53 P82 to P84 H This is a general-purpose I/O port.

Pin name

WR This is a write strobe output pin for the lower 8-bit of data bus.

WRL

RD

P60 to P63,

P64 to P67

AN0 to AN3,

AN4 to AN7

ASR0 This is a data input pin for input capture 0.

ASR1 This is a data input pin of input capture 1.

TIN0 to TIN 2 This is an input pin of 16-bit timer.

TOT0 to TOT2 These are output pins for 16-bit re-load timer 0 and 1.

DAO0 to DAO2 This is an output pin of 8-bit D/A converter.

Circuit

type

This function becomes valid when WRL

This function becomes valid when WRL

WRL

is used for holding the lower 8-bit for write strobe in 16-bit

access operations, while WR is used for holding 8-bit data for write

strobe in 8-bit access operations.

This is a read strobe output pin for the data bus.

This function is valid in the mode where the external bus is valid.

G This is an I/O port of an N-ch open-drain type.

When the data register is read by a read instruction other than the

modify write instruction with the corresponding bit in ADER set at

“0”, the pin level is acquired. The value set in the data register is

output to the pin as is.

This is an analog input pin of the 8/10-bit A/D converter.

When using this input pin, set the corresponding bit in ADER at “1”.

Also, set the corresponding bit in the data register at “1”.

Because this input is used as required when the input capture 0 is

performing input operations, and it is necessary to stop outputs

from other functions unless such outputs are made intentionally.

Because this input is used as required when input capture 1 is

performing input operations, and it is necessary to stop outputs by

other functions unless such outputs are made intentionally.

This function becomes valid when outputs from 16-bit re-load timer

0 – 2 are disabled.

Because this input is used as required whin 16-bit timer 0 - 2 is

performing input operations,and it is necessary to stop outputs by

other functions unless such outputs are made intentionally.

This function becomes valid when output from 16-bit re-load timer

0 – 2 are enabled.

This function becomes valid when data output from 8-bit D/A

converter 0 – 2 are disabled.

This function becomes valid when data output from 8-bit D/A

converter 0 – 2 are enabled.

Function

/WR pin output is disabled.

/WR pin output is enabled.

* :FPT-100P-M05

8

(Continued)

Page 9

MB90246A Series

Pin no.

LQFP*

54 to 56 P85 to P87 E This is a general-purpose I/O port.

57,

58

59 P92 E This is a general-purpose I/O port.

60 P93 E This is a general-purpose I/O port.

61 P94 E This is a general-purpose I/O port.

Pin name

PWM0 to PWM2 This is an output pin of 8-bit PWM timer.

P90,

P91

INT0,

INT1

INT2 This is an input pin of the DTP/external interrupt circuit ch.2.

ATG

INT3 This is a request input of the DTP/external interrupt circuit

PWM3 This is an output pin of 8-bit PWM timer.

SID0 This is a serial data I/O pin of UART.

Circuit

type

This function becomes valid when output from PWM0 – PWM2 are

disabled.

This function becomes valid when output from PWM0 – PWM2 are

enabled.

F This is a general-purpose I/O port.

This is a request input pin of the DTP/external interrupt circuit ch.0

and 1.

Because this input is used as required when the DTP/external

interrupt circuit is performing input operations, and it is necessary

to stop outputs from other functions unless such outputs are made

intentionally.

Because this input is used as required when the DTP/external

interrupt circuit is performing input operations, and it is necessary

to stop outputs from other functions unless such outputs are made

intentionally.

This is a trigger input pin of the 8/10-bit A/D converter.

Because this input is used as requited when the 8/10-bit A/D

converter is performing input operations, and it is necessary to

stop outputs by other functions unless such outputs are made

intentionally.

This function is always valid.

This function becomes valid when output from PWM3 is disabled.

ch. 3.

Because this input is used as required when the DTP/external

interrupt circuit is performing input operations, and it is necessary

to stop outputs from other functions unless such output are made

intentionally.

This function becomes valid when output from PWM3 is enabled.

This function becomes valid when serial data output from UART is

disabled.

This function becomes valid when serial data output from UART is

enabled.

Because this input is used as required when UART is performing

input operations, and it is necessary to stop outputs by other

functions unless such outputs are made intentionally.

Function

* :FPT-100P-M05

(Continued)

9

Page 10

MB90246A Series

Pin no.

LQFP*

62 P95 E This is a general-purpose I/O port.

63 P96 E This is a general-purpose I/O port.

1 to 6,

100,

99

7,

8,

10 to 15

64 PA0 E This is a general-purpose I/O port.

65 PA1 E This is a general-purpose I/O port.

66 PA2 E This is a general-purpose I/O port.

Pin name

SOD0 This is a data output pin of UART.

SCK0 This is a clock I/O pin of UART.

A02 to A07,

A01,

A00

A08,

A09,

A10 to A15

SID1 This is a data input pin of I/O simple serial interface 1.

SOD1 This is a data output pin of I/O simple serial interface 1.

SCK1 This is a clock output pin of I/O simple serial interface 1.

Circuit

type

This function becomes valid when data output from UART is

disabled.

This function becomes valid when data output from UART is

enabled.

This function becomes valid when clock output from UART is

disabled.

This function becomes valid when clock output from UART is

enabled.

Because this input is used as required when UART is performing

input operations, and it is necessary to stop outputs by other

functions unless such outputs are made intentionally.

E This is an output pin for the lower 8-bit of the external address bus.

E This is an output pin for the middle 8-bit of the external address

bus.

This function is valid in the mode where the external bus is valid

and the middle address control refister is set to select an address.

Because this input is used as required when I/O simple serial

interface 1 is performing input operations, and it is necessarey to

stop outputs by other functions unless such outputs are made

intentionally.

This function becomes valid when data output from I/O simple

serial interface 1 is disabled.

This function becomes valid when data output from I/O simple

serial interface 1 is enabled.

This function becomes valid when clock output from I/O simple

serial interface 1 is disabled.

This function becomes valid when clock output from I/O simple

serial interface 1 is enabled.

Function

* :FPT-100P-M05

10

(Continued)

Page 11

MB90246A Series

(Continued)

Pin no.

LQFP*

Pin name

67 PA3 E This is a general-purpose I/O port.

SID2 This is a data input pin of I/O simple serial interface 2.

68 PA4 E This is a general-purpose I/O port.

SOD2 This is a data output pin of I/O simple serial interface 2.

69 PA5 E This is a general-purpose I/O port.

SCK2 This is clock output pin of I/O simple serial interface 2.

83 to 90 D00 to D07 D This is an I/O pin for the lower 8-bit of the external data bus.

21,

V

CC Power

82

9,

V

SS Power

40,

79

32 AV

CC Power

33 AVRH Power

34 AVRL Power

35 AV

SS Power

45 DVRH Power

46 DVRL Power

Circuit

type

supply

supply

supply

supply

supply

supply

supply

supply

Function

Because this input is used as required when is performing input

operations, and it is I/O simple serial interface 2 necessarey to stop

outputs by other functions unless such outputs are made

intentionally.

This function becomes valid when data output from I/O simple

serial interface 2 is disabled.

This function becomes valid when data output from I/O simple

serial interface 2 is enabled.

This function becomes valid when clock output from I/O simple

serial interface 2 is disabled.

This function becomes valid when clock output from I/O simple

serial interface 2 is enabled.

This is power supply to the digital circuit.

This is a ground level of the digital circuit.

This is power supply to the analog circuit.

Make sure to turn on/turn off this power supply with a voltage

exceeding AV

CC applied to VCC.

This is a reference voltage input to the A/D converter.

Make sure to turn on/turn off this power supply with a voltage

exceeding AVRH applied to AV

CC.

This is a reference voltage input to the A/D converter.

This is a ground level of the analog circuit.

This is an external reference power supply pin for the D/A

converter.

This is an external reference power supply pin for the D/A

converter.

* :FPT-100P-M05

11

Page 12

MB90246A Series

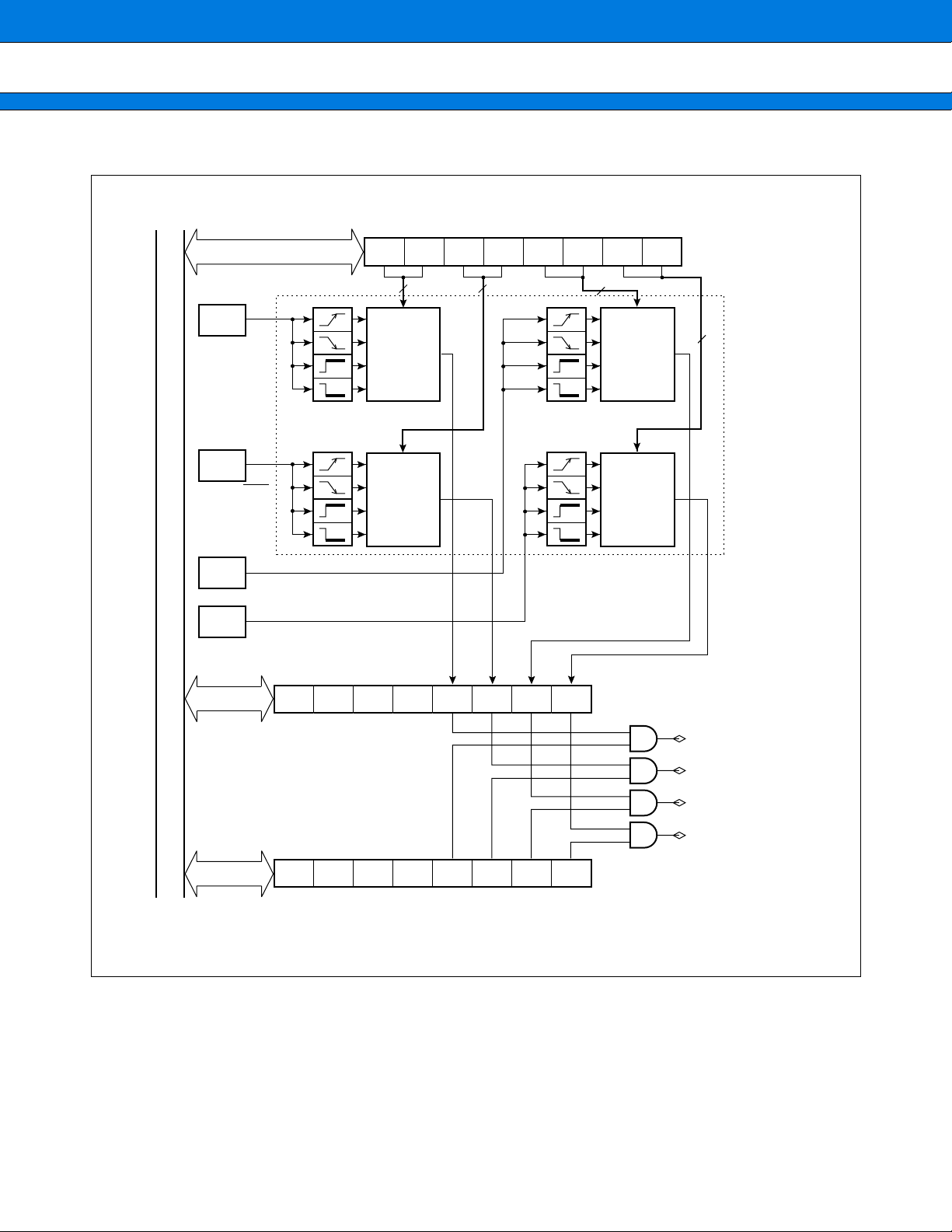

I/O CIRCUIT TYPE

■

Type Circuit Remarks

A • For oscillation of 32 MHz

Clock

suspension

• Oscillation feedback resistor approx.

1 MΩ

X1

X0

N-ch

Clock input

B • CMOS level hysteresis input

CC

V

P-ch type trigger

R

SS

V

CMOS

N-ch type trigger

Digital input

(without stand-by control)

• Pull-up resistor approx. 50 kΩ

C • CMOS level hysteresis input

CC

V

P-ch type trigger

(without stand-by control)

12

R

SS

V

CMOS

N-ch type trigger

Digital input

D • CMOS level output

• TTL level input

(with stand-by control)

R

Standby control signal

P-ch

N-ch

TTL

Digital output

Digital output

Digital input

(Continued)

Page 13

MB90246A Series

(Continued)

Type Circuit Remarks

E • CMOS level output

• CMOS level hysteresis input

(with stand-by control)

R

Standby control signal

CMOS

P-ch

N-ch

Digital output

Digital output

Digital input

F • CMOS level input

• CMOS level hysteresis input

P-ch

Digital output

R Digital output

Standby control signal

(during interrupt disable)

N-ch

Digital input

(with stand-by control (during interrupt

disable))

G • N-ch open-drain

• CMOS level output

• CMOS level hysteresis input

• Analog input

(with analog control)

ADER

R

CMOS

Digital output

Analog input

Digital input

H • CMOS level output

• Analog output

P-ch

Digital output

R

CMOSStandby control signal

N-ch

Digital output

Analog input

Digital input

• CMOS level hysteresis input

(with stand-by control)

13

Page 14

MB90246A Series

HANDLING DEVICES

■

1. Make Sure that the Voltage not Exceed the Maximum Rating (to Avoid a Latch-up)

In CMOS ICs, a latch-up phenomenon is caused when an voltage exceeding VCC or an voltage below VSS is

applied to input or output pins or a voltage exceeding the rating is applied across VCC and VSS.

When a latch-up is caused, the power supply current may be dramatically increased causing resultant thermal

break-down of devices. To avoid the latch-up, make sure that the voltage not exceed the maximum rating.

In turning on/turning off the analog power supply, make sure the analog power voltage (AV

input voltages not exceed the digital voltage (V

CC).

CC, AVRH) and analog

2. Connection of Unused Pins

Leaving unused pins open may result in abnormal operations. Clamp the pin level by connecting it to a pull-up

or a pull-down resistor.

3. Notes on Using External Clock

In using the external clock, drive X0 pin only and leave X1 pin unconnected.

Using external clock

•

X0

Open

X1

MB90246A series

4. Power Supply Pins

In products with multiple VCC or VSS pins, the pins of a same potential are internally connected in the device to

avoid abnormal operations including latch-up. However, connect the pins external power and ground lines to

lower the electro-magnetic emission level and abnormal operation of strobe signals caused by the rise in the

ground level, and to conform to the total current rating.

Make sure to connect V

It is recommended to provide a bypass capacitor of around 0.1 µF between V

CC and VSS pins via lowest impedance to power lines.

CC and VSS pin near the device.

5. Crystal Oscillator Circuit

Noises around X0 or X1 pins may be possible causes of abnormal operations. Make sure to provide bypass

capacitors via shortest distance from X0, X1 pins, crystal oscillator (or ceramic resonator) and ground lines, and

make sure, to the utmost effort, that lines of oscillation circuit not cross the lines of other circuits.

It is highly recommended to provide a printed circuit board art work surrounding X0 and X1 pins with an grand

area for stabilizing the operation.

14

Page 15

MB90246A Series

6. Turning-on Sequence of Power Supply to A/D Converter, D/A Converter and Analog Inputs

Make sure to turn on the A/D converter power supply (AVCC, AVRH, AVRL), D/A converter power supply and

analog inputs (AN0 to AN7) after turning-on the digital power supply (V

Turn-off the digital power after turning off the A/D converter supply and analog inputs. In this case, make sure

that the voltage not exceed AVRH or AV

CC (turning on/off the analog and digital supplies simultaneously is

acceptable).

7. Connection of Unused Pins of A/D Converter

Connect unused pins of A/D converter to AVCC = VCC, AVSS = AVRH = AVRL = VSS.

8. “MOV @AL, AH”, “MOVW @AL, AH” Instructions

When the above instruction is performed to I/O space, an unnecessary writing operation may be performed

(#FF, #FFFF) in the internal bus.

Use the compiler function for inserting an NOP instruction before the above instructions to avoid the writing

operation.

Accessing RAM space with the above instruction does not cause any problem.

CC).

9. Initialization

In the device, there are internal registers which is initialized only by a power-on reset. To initialize these registers

turning on the power again.

10.External Reset Input

To reset the internal securely, “L” level input to the RST pin must be at least 5 machine cycle.

11.HST Pin

Make sure HST pin is set to “H” level when turn on the power supply. Also make sure HST pin is never set to

“L” level, when RST

pin is set to “L” level.

12.CLK Pin

a case 32 MHz

P50/CLK*

X1

X0

2 deviding circuit

STOP

P50 output

P50 input

To the inside

CLK output

*: At P50/CLK pin in the external bus mode, CLK output is selected as an initial value.

15

Page 16

MB90246A Series

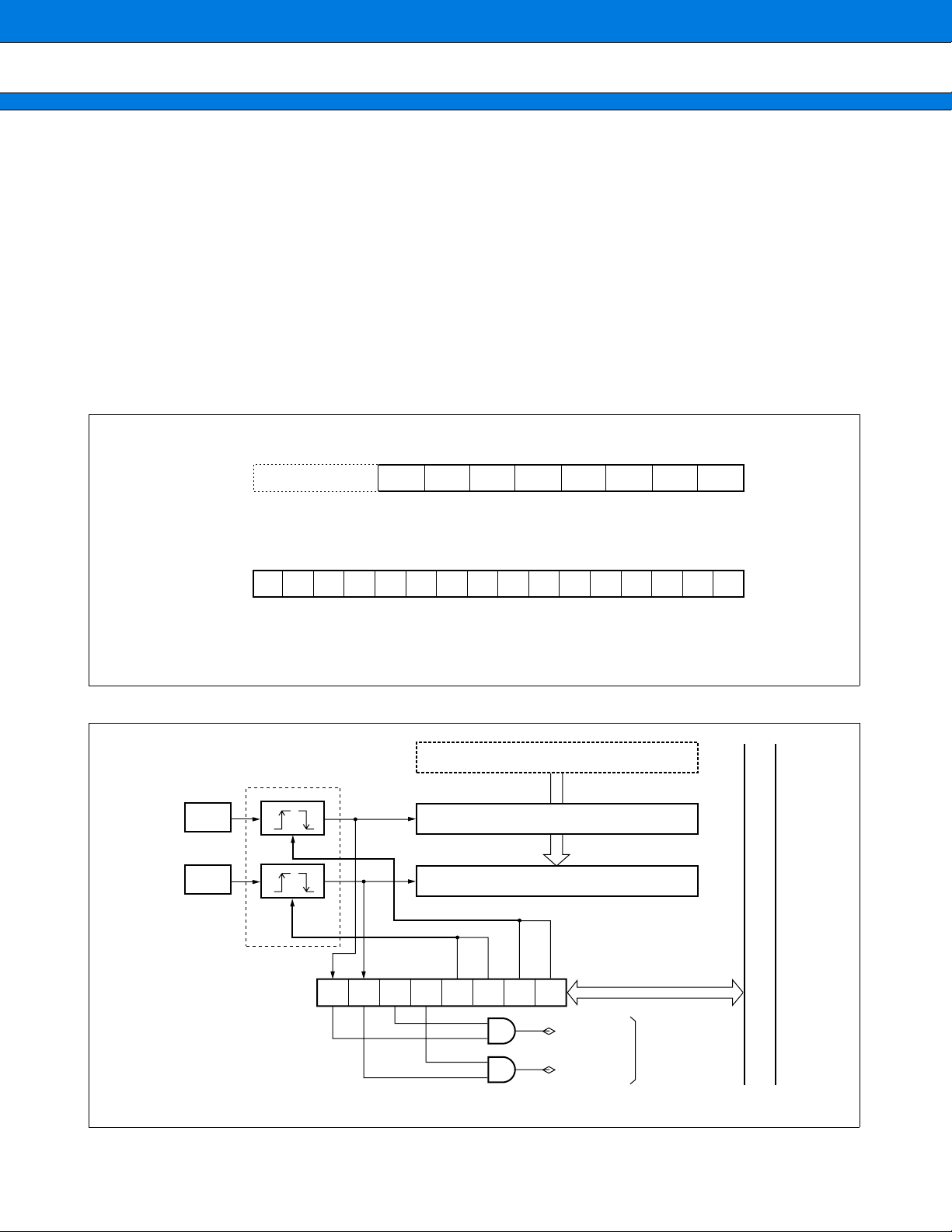

BLOCK DIAGRAM

■

X0

X1

RST

HST

P10/D08 to

P17/D15

A00 to A15

D00 to D07

P40/A16 to

P47/A23

P50/CLK

P51/RDY

P52/HAK

P53/HRQ

P54/WRH

P55/WR/WRL

P56/RD

P57

P72

P73

P74/TIN0/TOT0 to

P76/TIN2/TOT2

P70/ASR0

P71/ASR1

(including timebase timer)

8

16

8

8

3

2

F

MC–16F.

CPU

Clock control block

Port 1

8

External bus

interface

2

13

Port 4, 5

Port 7

3

16-bit

re-load timer

16-bit I/O timer

3

Input compare

2

(ICU)

Interrupt controller

8-bit

D/A converter

Port 8

8-bit

PWM timer

× 4 channels

DTP/external

interrupt

circuit 3

Port 9

Internal data bus

UATR

I/O

simple serial

interface

DVRH

DVRL

3

3

2

4

2

3

P82/DAO0 to

P84/DAO2

3

P85/PWM0 to

P87/PWM2

P93/INT3/PWM3

P94/SID0

P95/SOD0

P96/SCK0

PA0/SID1

PA1/SOD1

PA2/SCK1

PA3/SID2

PA4/SOD2

PA5/SCK2

16

P90/INT0

P91/INT1

P92/INT2/ATG

AVRH

AVRL

CC

AV

SS

AV

P60/AN0 to

P67/AN7

Other pins

MD0 to MD2,

CC,VSS

V

16-bit

free-run timer

DTP/external

interrupt circuit

3

0, 1, 2

Port 9

8/10-bit

A/D converter

8

8

Port 6

Port A

DSP interface for

the IIR filter

RAM

Page 17

MEMORY MAP

FFFFFF

001980

001900

001100

000100

0000C0

000000

H

H

H

H

H

H

External ROM

external bus mode

H

area

External

I/O

External area

RAM

Register

External

area

I/O

MB90246A Series

: Internal access memory

: Enternal access memory

The ROM data of bank FF is reflected in the upper address of bank 00, realizing effective use of the C compiler

small model. The lower 16-bit of bank FF and the lower 16-bit of bank 00 is assigned to the same address,

enabling reference of the table on the ROM without stating “far”.

17

Page 18

MB90246A Series

2

F

MC-16F CPU PROGRAMMING MODEL

■

(1) Dedicated Registers

AH AL

USP

SSP

PS

PC

USPCU

SSCPU

USPCL

SSPCL

: Accumlator (A)

Dual 16-bit register used for storing results of calculation etc. The two 16-bit

registers can be combined to be used as a 32-bit register.

: User stack pointer (USP)

The 16-bit pointer for containing a user stack address.

: System stack pointer (SSP)

The 16-bit pointer for displaying the status of the system stack address.

: Processor status (PS)

The 16-bit register for displaying the system status.

: Program counter (PC)

The 16-bit register for displaying storing location of the current instruction code.

: User stack upper limit register (USPCU)

The 16-bit register for specifying the upper limit of the user stack.

: System stack upper limit register (SSPCU)

The 16-bit register for specifying the upper limit of the system stack.

: User stack lower limit register (USPCL)

The 16-bit register for specifying the lower limit of the user stack.

: System stack lower limit register (SSPCL)

The 16-bit register for specifying the lower limit of the system stack.

32-bit

16-bit

DPR

PCB

DTB

USB

SSB

ADB

8-bit

: Direct page register (DPR)

The 8-bit register for specifying bit 8 through 15 of the operand address in the

short direct addressing mode.

: Program bank register (PCB)

The 8-bit register for displaying the program space.

: Data bank register (DTB)

The 8-bit register for displaying the data space.

: User stack bank register (USB)

The 8-bit register for displaying the user stack space.

: System stack bank register (SSB)

The 8-bit register for displaying the system stack space.

: Additional data bank register (ADB)

The 8-bit register for displaying the additional data.

18

Page 19

(2) General-purpose Registers

MB90246A Series

Maximum of 32 banks

H

000180

+ (RP × 10 H )

(3) Processor Status (PS)

ILM RP CCR

bit 15 bit 14 bit 13 bit 12 bit 11 bit 10 bit 9 bit 8 bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0

PS

ILM2 B4ILM1 ILM0 B3 B2 B1 B0

R7

R5

R3

R1

RW3

RW2

RW1

RW0

16-bit

R6

R4

R2

R0

—

RW7

RL3

RW6

RW5

RL2

RW4

RL1

RL0

ISTNZVC

Initial value

— : Unused

X : Indeterminate

00 000000 10XXXXX

—

19

Page 20

MB90246A Series

I/O MAP

■

Address

000000

Abbreviated

register name

H

Register name

(System reservation area)*

Read/

write

Resource

name

1

Initial value

000001H PDR1 Port 1 data register R/W! Port 1 XXXXXXXXB

000002H

(System reservation area)*

1

000003H

000004H PDR4 Port 4 data register R/W! Port 4 XXXXXXXXB

000005H PDR5 Port 5 data register R/W! Port 5 XXXXXXXXB

000006H PDR6 Port 6 data register R/W! Port 6 1 1 1 1 1 1 1 1 B

000007H PDR7 Port 7 data register R/W! Port 7 – XXXXXXX B

000008H PDR8 Port 8 data register R/W! Port 8 XXXXXX – – B

000009H PDR9 Port 9 data register R/W! Port 9 – XXXXXXX B

00000AH PDRA Port A data register R/W! Port A – – XXXXXXB

00000BH

to

00000F

000010

H

H

(System reservation area)*

(Vacancy)

1

000011H DDR1 Port 1 direction register R/W Port 1 0 0 0 0 0 0 0 0 B

000012H

(System reservation area)*

1

000013H

000014H DDR4 Port 4 direction register R/W Port 4 0 0 0 0 0 0 0 0 B

000015H DDR5 Port 5 direction register R/W Port 5 0 0 0 0 0 0 0 0 B

Port 6,

000016H ADER Analog input enable register R/W

8/10-bit A/D

11111111B

converter

000017H DDR7 Port 7 direction register R/W Port 7 – 0 0 0 0 0 0 0 B

000018H DDR8 Port 8 direction register R/W Port 8 0 0 0 0 0 0 – – B

000019H DDR9 Port 9 direction register R/W Port 9 – X X X X X X X B

00001AH DDRA Port A direction register R/W Port A – – 0 0 0 0 0 0 B

00001BH

to

00001F

000020

H

H SCR1 Serial control status register 1 R/W

000021H SSR1 Serial status register 1 R – – – – – – – 1 B

000022H SDR1L Serial data register 1 (L) R/W XXXXXXXXB

(Vacancy)

10000000B

I/O simple serial

interface 1

000023H SDR1H Serial data register 1 (H) R/W XXXXXXXXB

(Continued)

20

Page 21

MB90246A Series

Address

000024

Abbreviated

register name

H SCR2 Serial control status register 2 R/W

Register name

000025H SSR2 Serial status register 2 R – – – – – – – 1 B

000026H SDR2L Serial data register 2 (L) R/W XXXXXXXXB

Read/

write

Resource

name

I/O simple serial

interface 2

Initial value

10000000B

000027H SDR2H Serial data register 2 (H) R/W XXXXXXXXB

000028H UMC Mode control register R/W

00000100B

000029H USR Status register R/W 00010000B

00002AH

UIDR/

UODR

Input data register/

output data register

R/W XXXXXXXX

UART

00002BH URD Rate and data register R/W 0 0 0 0 0 0 0 0 B

00002CH PWMC3

PWM3 operating mode control

register

R/W

8-bit PWM

timer 3

00000XX1

00002DH (Vacancy)

00002E

00002FH PRLH3 PWM3 re-road register (H) R/W XXXXXXXX B

000030H ENIR DTP/interrupt enable register R/W

000031H EIRR DTP/interrupt factor register R/W – – – – 0 0 0 0 B

H PRLL3 PWM3 re-road register (L) R/W

8-bit PWM

timer 3

DTP/external

interrupt circuit

XXXXXXXXB

––––0000B

000032H ELVR Request level setting register R/W 0 0 0 0 0 0 0 0 B

B

B

000033H (Vacancy)

000034

H PWMC0

PWM0 operating mode control

register

R/W

8-bit PWM

timer 0

00000XX1B

000035H (Vacancy)

000036H PRLL0 PWM0 re-road register (L) R/W

000037H PRLH0 PWM0 re-road register (H) R/W XXXXXXXX B

000038H PWMC1

PWM1 operating mode control

register

R/W

8-bit PWM

timer 0

8-bit PWM

timer 1

XXXXXXXXB

00000XX1

000039H (Vacancy)

00003A

00003BH PRLH1 PWM1 re-road register (H) R/W XXXXXXXX B

00003CH PWMC2

H PRLL1 PWM1 re-road register (L) R/W

PWM2 operating mode control

register

R/W

8-bit PWM

timer 1

8-bit PWM

timer 2

XXXXXXXXB

00000XX1B

00003DH (Vacancy)

00003EH PRLL2 PWM2 re-road register (L) R/W

00003FH PRLH2 PWM2 re-road register (H) R/W XXXXXXXX B

000040H

Timer control status register 0

lower digits

R/W

TMCSR0

000041H

Timer control status register 0

upper digits

R/W ––––0000

8-bit PWM

timer 2

16-bit re-load

timer 0

XXXXXXXXB

00000000

(Continued)

B

B

B

21

Page 22

MB90246A Series

Address

000042

Abbreviated

register name

H

Register name

Read/

write

Resource

name

Initial value

XXXXXXXX

TMR0 16-bit timer register 0 R

000043H XXXXXXXXB

000044H

16-bit re-load

timer 0

XXXXXXXX

TMRLR0 16-bit re-load register 0 R/W

000045H XXXXXXXXB

000046H

(Vacancy)

000047

000048H

H

Timer control status register 1

lower digits

R/W

00000000

TMCSR1

000049H

Timer control status register 1

upper digits

R/W ––––0000

16-bit re-load

00004AH

TMR1 16-bit timer register 1 R

timer 1

XXXXXXXX

00004BH XXXXXXXXB

00004CH

XXXXXXXX

TMRLR1 16-bit re-load register 1 R/W

00004DH XXXXXXXXB

00004EH

(Vacancy)

00004F

000050H

H

Timer control status register 2

lower digits

R/W

00000000

TMCSR2

000051H

Timer control status register 2

upper digits

R/W ––––1111

16-bit re-load

000052H

TMR2 16-bit timer register 2 R

timer 2

XXXXXXXX

000053H XXXXXXXXB

B

B

B

B

B

B

B

B

B

000054H

XXXXXXXX

TMRLR2 16-bit re-load register 2 R/W

000055H XXXXXXXXB

000056H

to

000059

00005A

H

H DADR0 D/A data register 0 R/W

00005BH DACR0 D/A control register 0 R/W – – – – – – – 0 B

00005CH DADR1 D/A data register 1 R/W

00005DH DACR1 D/A control register 1 R/W – – – – – – – 0 B

00005EH DADR2 D/A data register 2 R/W

00005FH DACR2 D/A control register 2 R/W – – – – – – – 0 B

000060H

(Vacancy)

8-bit D/A

converter 0

8-bit D/A

converter 1

8-bit D/A

converter 2

XXXXXXXXB

XXXXXXXXB

XXXXXXXXB

XXXXXXXX

IPCP0 Input capture register 0 R

000061H XXXXXXXXB

000062H

IPCP1 Input capture register 1 R

000063H XXXXXXXXB

16-bit I/O timer

(input

capture 0, 1)

XXXXXXXX

000064H ICS0 Input capture control register R/W 0 0 0 0 0 0 0 0 B

22

B

B

B

(Continued)

Page 23

MB90246A Series

Address

000065

to

00006B

00006C

Abbreviated

register name

H

H

H

Register name

(Vacancy)

TCDT Timer data register R/W

00006DH 00000000B

00006EH TCCS Timer control status register R/W 0 0 0 0 0 0 0 0 B

Read/

write

Resource

name

16-bit I/O timer

(16-bit free-run

timer)

Initial value

00000000

00006FH (Vacancy)

000070

H ADCSL

000071H ADCSH

000072H

A/D control status register lower

digits

A/D control status register upper

digits

R/W

000–0000

R/W –000––00B

XXXXXXXX

ADCT Conversion time setting register R/W

000073H XXXXXXXXB

000074H ADTL0

A/D data register 0

000075H ADTH0 R ––––––**B

000076H ADTL1

R XXXXXXXXB

8/10-bit A/D

converter

R XXXXXXXXB

A/D data register 1

000077H ADTH1 R ––––––**B

000078H ADTL2

R XXXXXXXXB

A/D data register 2

000079H ADTH2 R ––––––**B

B

B

B

00007AH ADTL3

R XXXXXXXXB

A/D data register 3

00007BH ADTH3 R ––––––**B

00007CH

to

00007F

000080

H

H

Product addition control status

register lower digits

(Vacancy)

R/W

XXX0XXX0B

MCSR

000081H

000082H MCCRL

000083H MCCRH

000084H

MDORL

Product addition control status

register digits

Product addition continuation

control register lower digits

Product addition continuation

control register upper digits

R/W –XXXXXXX

R/W 00000000B

R/W ––––––00B

DSP interface

for the IIR filter

XXXXXXXX

R

000085H XXXXXXXXB

000086H MDORM R XXXXXXXXB

000087H

Production addition output

register

XXXXXXXX

MDORH R

000088H XXXXXXXXB

(Continued)

B

B

B

23

Page 24

MB90246A Series

(Continued)

Address

000089

to

Abbreviated

register name

H

Register name

(Vacancy)

Read/

write

Resource

name

Initial value

00008FH

000090

to

H

(System reservation area)*

1

00009EH

Delayed

interrupt

generation

module

–––––––0B

00009FH DIRR

Delayed interrupt factor

generation/

cancellation register

R/W

Low-power

0000A0H STBYC Standby control register R/W

consumption

0001XXXXB

(stand-by) mode

0000A1H

to

(System reservation area)*

1

0000A3H

0000A4H HACR Upper address control register W

*2

External bus pin

0000A5

H EPCR External pin control register W *2

0000A8H WDTC Watchdog timer control register R/W Watchdog timer XXXXXXXXB

0000A9H TBTC Timebase timer control register R/W Timebase timer – X X 0 0 1 0 0 B

0000B0H ICR00 Interrupt control register 00 R/W

00000111B

0000B1H ICR01 Interrupt control register 01 R/W 0 0 0 0 0 1 1 1 B

0000B2H ICR02 Interrupt control register 02 R/W 0 0 0 0 0 1 1 1 B

0000B3H ICR03 Interrupt control register 03 R/W 0 0 0 0 0 1 1 1 B

0000B4H ICR04 Interrupt control register 04 R/W 0 0 0 0 0 1 1 1 B

0000B5H ICR05 Interrupt control register 05 R/W 0 0 0 0 0 1 1 1 B

0000B6H ICR06 Interrupt control register 06 R/W 0 0 0 0 0 1 1 1 B

0000B7H ICR07 Interrupt control register 07 R/W 0 0 0 0 0 1 1 1 B

0000B8H ICR08 Interrupt control register 08 R/W 0 0 0 0 0 1 1 1 B

Interrupt

controller

0000B9H ICR09 Interrupt control register 09 R/W 0 0 0 0 0 1 1 1 B

0000BAH ICR10 Interrupt control register 10 R/W 0 0 0 0 0 1 1 1 B

0000BBH ICR11 Interrupt control register 11 R/W 0 0 0 0 0 1 1 1 B

0000BCH ICR12 Interrupt control register 12 R/W 0 0 0 0 0 1 1 1 B

0000BDH ICR13 Interrupt control register 13 R/W 0 0 0 0 0 1 1 1 B

0000BEH ICR14 Interrupt control register 14 R/W 0 0 0 0 0 1 1 1 B

0000BFH ICR15 Interrupt control register 15 R/W 0 0 0 0 0 1 1 1 B

0000C0H

to

0000FF

(External area)*

H

3

24

Page 25

MB90246A Series

Descriptions for read/write

R/W: Readable and writable

R: Read only

W: Write only

R/W!: Bits for reading operation only or writing operation only are included. Refer to the register lists for specific

resource for detailed information.

Descriptions for initial value

0 : The initial value of this bit is “0”.

1 : The initial value of this bit is “1”.

X : The initial value of this bit is indeterminate.

– : This bit is not used. The initial value is indeterminate.

* : The storage type varies with the value of the ADCSH CREG bit.

*1: Access prohibited.

*2: The initial value varies with bus mode.

*3: This area is the only external access area having an address of 0000FF

specified as reserved areas in the table is handled as if an internal area were accessed. A signal for accessing

an external bus is not generated.

*4: When a register described as R/W! or W in the read/write column is accessed by a bit setting instruction or

other read modify write instructions, the bit pointed to by the instruction becomes a set value. If a bit is writable

by other bits, however, malfunction occurs. You must not, therefore, access that register using these instructions.

H or lower. Access to any of the addresses

Note: For bits that is initialized by an reset operation, the initial value set by the reset operation is listed as an initial

value. Note that the values are different from reading results.

25

Page 26

MB90246A Series

INTERRUPT FACTORS, INTERRUPT VECTORS, INTERRUPT CONTROL REGISTER

■

2

OS

Interrupt source

EI

support

Reset × # 08 08

INT9 instruction × # 09 09

Exception × # 10 0A

DTP/external interrupt circuit

Channel 0

DTP/external interrupt circuit

Channel 1

Interrupt vector Interrupt control register

Number Address ICR Address

H FFFFDCH ——High

H FFFFD8H ——

H FFFFD4H ——

# 11 0B

# 13 0D

H FFFFD0H ICR00 0000B0H

H FFFFC8H ICR01 0000B1H

Input capture (ICU) Channel 0 # 15 0FH FFFFC0H ICR02 0000B2H

Input capture (ICU) Channel 1 # 17 11H FFFFB8H

I/O simple serial interface

Channel 2

DTP/external interrupt circuit

Channel 2

DTP/external interrupt circuit

Channel 3

# 18 12

# 19 13

# 21 15

H FFFFB4H

H FFFFB0H ICR04 0000B4H

H FFFFA8H ICR05 0000B5H

ICR03 0000B3H

16-bit free-run timer Overflow # 23 17H FFFFA0H ICR06 0000B6H

Timebase timer Interval interrupt # 25 19H FFFF98H ICR07 0000B7H

Priority*

2

16-bit re-load timer Channel 0 # 27 1BH FFFF90H

ICR08*

1

0000B8H

8-bit PWM timer Channel 0 × # 28 1CH FFFF8CH

16-bit re-load timer Channel 1 # 29 1DH FFFF88H

ICR09*

1

0000B9H

8-bit PWM timer Channel 1 × # 30 1EH FFFF84H

16-bit re-load timer Channel 2 # 31 1FH FFFF80H

ICR10*

1

0000BAH

8-bit PWM timer Channel 2 × # 32 20H FFFF7CH

8/10-bit A/D converter

measurement complete

# 33 21

H FFFF78H

ICR11*

1

0000BBH

8-bit PWM timer Channel 3 × # 34 22H FFFF74H

I/O simple serial interface

Channel 1

# 35 23

H FFFF70H ICR12 0000BCH

UART transmission complete # 37 25H FFFF68H ICR13 0000BDH

UART reception complete # 39 27H FFFF60H ICR14 0000BEH

Delayed interrupt generation

module

× # 42 2A

H FFFF54H ICR15 0000BFH

Stack fault × # 255 FFH FFFC00H ——Low

: Can be used

×

: Can not be used

: Can be used. With Extended intelligent I/O service (EI

2

OS) stop function at abnormal operation.

: Can be used if interrupt request using ICR are not commonly used.

26

Page 27

MB90246A Series

*1: • Interrupt levels for peripherals that commonly use the ICR register are in the same level.

• When the extended intelligent I/O service (EI

register, only one of the functions can be used.

• When the extended intelligent I/O service (EI

can not be used on the other function.

*2: The level shows priority of same level of interrupt invoked simultaneously.

2

OS) is specified in a peripheral device commonly using the ICR

2

OS) is specified for one of the peripheral functions, interrupts

27

Page 28

MB90246A Series

PERIPHERALS

■

1. I/O Port

(1) Input/output Port

Ports 1, 4, 5, 7 to 9, A are general-purpose I/O ports having a combined function as an external bus pin and a

resource input. The input output ports function as general-purpose I/O port only in the single-chip mode. In the

external bus mode, the ports are configured as external bus pins, and part of pins for port 4 can be configured

as general-purpose I/O port by setting the bus control signal select register (ECSR).

• Operation as output port

The pin is configured as an output port by setting the corresponding bit of the DDR register to “1”.

Writing data to PDR register when the port is configured as output, the data is retained in the output latch in

the PDR and directly output to the pin.

The value of the pin (the same value retained in the output latch of PDR) can be read out by reading the PDR

register.

Note: When a read-modify-write type instruction (e.g. bit set instruction) is performed to the port data register,

the destination bit of the operation is set to the specified value, not affecting the bits configured by the

DDR register for output, however, values of bits configured by the DDR register as inputs are changed

because input values to the pins are written into the output latch. To avoid this situation, configure the

pins by the DDR register as output after writing output data to the PDR register when configuring the bit

used as input as outputs.

• Operation as input port

The pin is configured as an input by setting the corresponding bit of the DDR register to “0”.

When the pin is configured as an input, the output buffer is turned-off and the pin is put into a high-impedance

status.

When a data is written into the PDR register, the data is retained in the output latch of the PDR, but pin outputs

are unaffected.

Reading the PDR register reads out the pin level (“0” or “1”).

• Block diagram

Standby control: Stop, timebase timer mode and SPL=1, or hardware standby mode

PDR (port data register)

PDR read

PDR write

DDR (port direction register)

Internal data bus

Direction latch

DDR write

DDR read

Output latch

P-ch

Pin

N-ch

Standby control (SPL=1)

28

Page 29

MB90246A Series

(2) N-ch Open-drain Port

Port 6 is general-purpose I/O port having a combined function as resource input/output. Each pin can be switched

between resource and port bitwise.

• Operation as output port

When a data is written into the PDR register, the data is latched to the output latch of PDR. When the output

latch value is set to “0”, the output transistor is turned on and the pin status is put into an “L” level output, while

writing “1” turns off the transistor and put the pin in a high-impedance status.

If the output pin is pulled-up, setting output latch value to “1” puts the pin in the pull-up status.

Reading the PDR register returns the pin value (same as the output latch value in the PDR).

Note: Execution of a read-modify-write instruction (e.g. bit set instruction) reads out the output latch value rather

than the pin value, leaving output latch that is not manipulated unchanged.

• Operation as input port

Setting corresponding bit of the PDR register to “1” turns off the output transistor and the pin is put into a high-

impedance status.

Reading the PDR register returns the pin value (“0” or “1”).

• Block diagram

ADER (analog input enable register)

ADER read

ADER latch

ADER write

PDR (port data register)

RMW

(read-modify-write

Internal data bus

Standby control: Stop, timebase timer mode and SPL=1, or hardware standby mode

PDR read

PDR write

Output latch

Standby control (SPL=1)

type instruction)

Output trigger

To analog input

Pin

29

Page 30

MB90246A Series

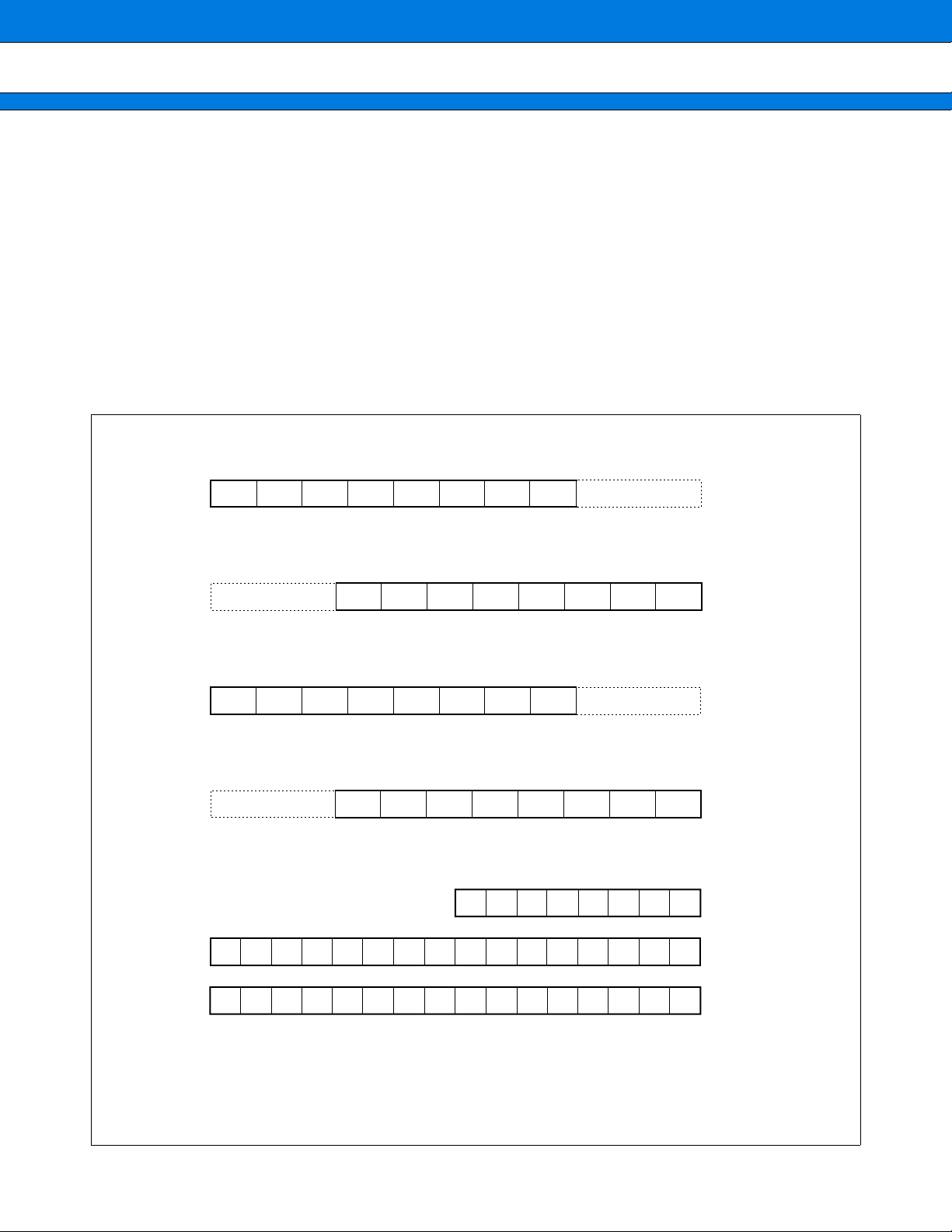

(3) Register Configuration

Address

000001

Address

000004

Address

000005

Address

000006

Address

000007

Address

000008

Address

000009

Address

00000A

Address

000011

Address

000014

Address

000015

Address

000016

bit 15 bit 14 bit 13 bit 12 bit 11 bit 10 bit 9 bit 8

H

P17 P16 P15 P14 P13 P12 P11 P10

R/W R/W R/W R/W R/W R/W R/W R/W

............

bit 15 bit 8

H

(PDR5)

bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0

P47 P46 P45 P44 P43 P42 P41 P40

R/W R/W R/W R/W R/W R/W R/W R/W

bit 15 bit 14 bit 13 bit 12 bit 11 bit 10 bit 9 bit 8

H

P57 P56 P55 P54 P53 P52 P51 P50

R/W R/W R/W R/W R/W R/W R/W R/W

............

bit 15 bit 8

H

(PDR7)

bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0

P67 P66 P65 P64 P63 P62 P61 P60

R/W R/W R/W R/W R/W R/W R/W R/W

bit 15 bit 14 bit 13 bit 12 bit 11 bit 10 bit 9 bit 8

H

— P76 P75 P74 P73 P72 P71 P70

— R/W R/W R/W R/W R/W R/W R/W

............

bit 15 bit 8

H

(PDR9)

bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0

P87 P86 P85 P84 P83 P82 — —

R/W R/W R/W R/W R/W R/W — —

bit 15 bit 14 bit 13 bit 12 bit 11 bit 10 bit 9 bit 8

— P96 P95 P94 P93 P92 P91 P90

H

R/W R/W R/W R/W R/W R/W R/W R/W

............

bit 15 bit 8

H

(Vacancy)

bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0

— — PA5 PA4 PA3 PA2 PA1 PA0

— — R/W R/W R/W R/W R/W R/W

bit 15 bit 14 bit 13 bit 12 bit 11 bit 10 bit 9 bit 8

H

P17 P16 P15 P14 P13 P12 P11 P10

R/W R/W R/W R/W R/W R/W R/W R/W

............

bit 15 bit 8

H

(DDR5)

bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0

P47 P46 P45 P44 P43 P42 P41 P40

R/W R/W R/W R/W R/W R/W R/W R/W

bit 15 bit 14 bit 13 bit 12 bit 11 bit 10 bit 9 bit 8

H

P57 P56 P55 P54 P53 P52 P51 P50

R/W R/W R/W R/W R/W R/W R/W R/W

............

bit 15 bit 8

H

(DDR7)

bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0

P67 P66 P65 P64 P63 P62 P61 P60

R/W R/W R/W R/W R/W R/W R/W R/W

.............

bit 7 bit 0

(System reservation area)

.............

bit 7 bit 0

(PDR4)

.............

bit 7 bit 0

(PDR6)

.............

bit 7 bit 0

(PDR8)

.............

bit 7 bit 0

(System reservation area)

.............

bit 7 bit 0

(DDR4)

Port 1 data register

(PDR1)

Port 4 data register

(PDR4)

Port 5 data register

(PDR5)

Port 6 data register

(PDR6)

Port 7 data register

(PDR7)

Port 8 data register

(PDR8)

Port 9 data register

(PDR9)

Port A data register

(PDRA)

Port 1 direction register

(DDR1)

Port 4 direction register

Port 5 direction register

Analog input enable register

(DDR4)

(DDR5)

(ADER)

30

(Continued)

Page 31

(Continued)

MB90246A Series

Address

000017

Address

000018

Address

000019

Address

00001A

R/W—: Readble and writable

bit 15 bit 14 bit 13 bit 12 bit 11 bit 10 bit 9 bit 8

H

— P76 P75 P74 P73 P72 P71 P70

— R/W R/W R/W R/W R/W R/W R/W

............

bit 15 bit 8

H

H

H

: Unused

(DDR9)

bit 15 bit 14 bit 13 bit 12 bit 11 bit 10 bit 9 bit 8

— P96 P95 P94 P93 P92 P91 P90

R/W R/W R/W R/W R/W R/W R/W R/W

............

bit 15 bit 8

(Vacancy)

bit 7 bit 0

bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0

P87 P86 P85 P84 P83 P82 — —

R/W R/W R/W R/W R/W R/W — —

bit 7 bit 0

............

bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0

— — PA5 PA4 PA3 PA2 PA1 PA0

— — R/W R/W R/W R/W R/W R/W

.............

(ADER)

.............

(DDR8)

Port 7 direction register

(DDR7)

Port 8 direction register

(DDR8)

Port 9 direction register

(DDR9)

Port A direction register

(DDRA)

31

Page 32

MB90246A Series

2. Timebase Timer

The timebase timer is a 18-bit free-run counter (timebase counter) for counting up in synchronization to the

internal count clock (divided-by-2 of oscillation) with an interval timer function for selecting an interval time from

four types of 2

The timebase timer also has a function for supplying operating clocks for the timer output for the oscillation

stabilization time or the watchdog timer etc.

(1) Register Configuration

• Timebase timer control register (TBTC)

Address

0000A9

R/W

W

—

X

RESV

13

/HCLK, 215/HCLK, 217/HCLK, and 219/HCLK.

bit 15 bit 14 bit 13 bit 12 bit 11 bit 10 bit 9 bit 8

H

RESV

R/W — — R/W R/W W R/W R/W

: Readable and writable

: Read onlyR

: Write only

: Unused

: Indeterminate

: Reserved bit

—

—

TBIE TBOF TBR TBC1 TBC0

.............

bit 7 bit 0

(WDTC)

Initial value

0XX00000

B

(2) Block Diagram

To 8-bit

PWM timer

Timebase timer

counter

Divided-by-2

of HCLK

Power-on reset

Start stop mode

CKSCR : MCS = 1→0*

Timebase timer control register

(TBTC)

1

× 2

× 22× 2

Timebase timer

interrupt signal

#25(19

To watchdog timer

3

. . . . . .

Counter

)*

clear circuit

2

1

H

× 28× 29× 210× 211× 212× 213× 214× 215× 216× 217× 2

OF

To oscillation stabilization

time selector of clock control block

Set TBOF

RESV

timer selector

Clear TBOF

——

OF OF

Interval

TBIE TBRTBOF TBC1 TBC0

18

OF

32

OF

: Overflow

HCLK

: Oscillation clock

*1

: Switch machine clock from oscillation clock to PLL clock

*2

: Interrupt signal

Page 33

MB90246A Series

3. Watchdog Timer

The watchdog timer is a 2-bit counter operating with an output of the timebase timer and resets the CPU when

the counter is not cleared for a preset period of time.

(1) Register Configuration

• Watchdog timer control register (WDTC)

Address

0000A8

bit 15 bit 8

H

R: Read only

W: Write only

X : Indeterminate

(2) Block Diagram

Watchdog timer

Start sleep mode

Start hold status

Start stop mode

............

Watchdog timer control register (WDTC)

PONR STBR WRST ERST SRST WTE WT1 WT0

Counter clear

control circuit

bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0

PONR STBR WRST ERST SRST WTE WT1 WT0(TBTC)

RRRRRWWW

2

CLR and start

Count clock

selector

CLR

counter

2-bit

Overflow

CLR

Watchdog reset

generation circuit

Initial value

XXXXXXXX

To internal reset

generation circuit

B

Clear

(Timebase timer counter)

Divided-by-2

of HCLK

HCLK: Oscillation clock

× 2

4

1

× 2

2

...

8

× 29× 210× 211× 212× 213× 214× 215× 216× 217× 2

× 2

18

33

Page 34

MB90246A Series

4. 8-bit PWM Timer

The 8-bit PWM timer is a re-load timer module that can generate a pulse wave with any period/duty ratio. It uses

pulse output control according to timer operation for PWM (Pulse Width Modulation) output.

An appropriate external circuit allows the 8-bit PWM timer to operate as a D/A converter.

The 8-bit PWM timer module consists of two 8-bit re-load registers used to specify “H” width and “L” width and

of a down counter that is loaded alternately with those values and counts down.

• A pulse waveform with any period and duty ratio is generated.

• An output pulse’s duty ratio of 0.4 to 99.6 percent can be set.

• An appropriate external circuit allows this PWM timer to operate as a D/A converter.

• An interrupt request can be generated by counter underflow.

• The count clock can be selected from two types of timebase timer output.

(1) Register Configuration

• PWM0 to 3 operating mode control register (PWM)

Address

PWMC0 : 000034

PWMC1 : 000038

PWMC2 : 00003C

PWMC3 : 00002C

H

H

H

H

............

bit 15 bit 8

(Vacancy)

bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0

PEN PCKS POE PIE PUF — — RESV

R/W R/W R/W R/W R/W R/W R/W R/W

Initial value

00000XX1

00000XX1

00000XX1

00000XX1

B

B

B

B

• PWM0 to 3 re-load register (PRLL, PRLH)

PRLH0 : 000037

Address

PRLH1 : 00003B

PRLH2 : 00003F

PRLH3 : 00002F

PRLL0 : 000036

PRLL1 : 00003A

PRLL2 : 00003E

PRLL3 : 00002E

R/W

RESV

bit 15

H

H

H

H

H

H

H

H

bit 14 bit 13 bit 12 bit 11 bit 10 bit 9 bit 8 bit 7 bit 0bit 1bit 2bit 3bit 4bit 5bit 6

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/WR/WR/WR/WR/WR/WR/W

: Readable and writable

: Unused

—

: Indeterminate

X

: Reserved bit

Initial value

XXXXXXX1

XXXXXXX1

XXXXXXX1

XXXXXXX1

XXXXXXX1

XXXXXXX1

XXXXXXX1

XXXXXXX1

B

B

B

B

B

B

B

B

34

Page 35

(2) Block Diagram

Timerbase timer output (22/HCLK)

Timerbase timer output (2

11

/HCLK)

MB90246A Series

Pin

Count clock

selector

Down counter clear

Re-load

Re-load register

L/H selector

PWM re-load register

(PRLL)

PWM re-load register

Clear

PWM

output latch

Temporary buffer

(PRLH)

Internal data bus

Reverse

PEN

Output enable

PCKS

POE PIE PUF — —

P85/PWM0

P86/PWM1

P87/PWM2

P93/INT3/PWM3

Interrupt request

#28(1C

#30(1E

#32(20

#34(22H)

RESV

PWM operationg mode

control register

(PWMC)

H

)

H

)

H

)

HCLK : Oscillation clock

35

Page 36

MB90246A Series

5. 16-bit Re-load Timer

The 16-bit re-load timer has an internal clock mode for counting down in synchronization to three types of internal

clocks and an event count mode for counting down detecting a given edge of the pulse input to the external bus

pin, and either of the two functions can be selectively used.

For this timer, an “underflow” is defined as the timing of transition from the counter value of “0000

H” to “FFFFH”.

According to this definition, an underflow occurs after [re-load register setting value + 1] counts.

In operating the counter, the re-load mode for repeating counting operation after re-loading a counter value after

an underflow or the one-shot mode for stopping the counting operation after an underflow can be selectively used.

Because the timer can generate an interrupt upon an underflow, the timer conforms to the extended intelligent

2

I/O service (EI

OS).

The MB90246A series has 3 channels of 16-bit re-load timers.

(1) Register Configuration

• Timer control status register 0, 1, 2 upper digits (TMCSR0, TMCSR1, TMCSR2: H)

Address

TMCSR0 : 000041

TMCSR1 : 000049

TMCSR2 : 000051

bit 15 bit 14 bit 13 bit 12 bit 11 bit 10 bit 9 bit 8

H

H

H

— — — — CSL1 CSL0 MOD2 MOD1

————R/WR/WR/WR/W

.............

bit 7 bit 0

(TMCSR : L)

Initial value

----0000

B

• Timer control status register 0, 1, 2 lower digits (TMCSR0, TMCSR1, TMCSR2: L)

Address

TMCSR0 : 000040

TMCSR1 : 000048

TMCSR2 : 000050

.............

bit 15 bit 8

H

H

H

(TMCSR : H)

bit 7 bit 6 bit 5 bit 4 Initial value

OUTEMOD0

RELDOUTL UFINTE TRGCNTE

bit 3 bit 2 bit 1 bit 0

00000000

R/W R/W R/W R/W R/W R/W R/W R/W

B

• 16-bit timer register 0, 1 (TMR0, TMR1, TMR2)

bit 15 Initial value

Address

TMR0 : 000042

TMR1 : 00004A

TMR2 : 000052

H

H

H

bit 14bit 13bit 12bit 11bit 10 bit 9 bit 8 bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

RRRRRRRRRRRRRRRR

• 16-bit re-load register 0, 1 (TMRL0,TMRL1)

TMRLR0 : 000044

Address

TMRLR1 : 00004C

TMRLR2 : 000054

R/W:Readable and writable

R : Read only

W : Write only

— :Unused

X : Indeterminate

bit 15bit 14bit 13bit 12bit 11bit 10 bit 9 bit 8 bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0

H

H

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

H

WWWWWWWWWWWWWWWW

XXXXXXXX

XXXXXXXX

XXXXXXXX

Initial value

XXXXXXXX

XXXXXXXX

XXXXXXXX

B

B

B

B

B

B

36

Page 37

(2) Block Diagram

16-bit timer register (down counter) UF

TMRLR0*

<TMRLR1>

<<TMRLR2>>

1

TMR0*

<TMR1>

<<TMR2>>

Internal data bus

1

16-bit re-load register

Re-load signal

MB90246A Series

Re-load

control circuit

Count clock generation circuit

φ

Prescaler

Clear

Pin

Input

control

circuit

CLK

Gate input

3

Internal

clock

External

Valid clock

decision

circuit

CLK

Clock

selecter

Wait signal

Output control circuit

Output

generation circuit

Revers EN

clock

P74/TIN0/TOT0

<P75/TIN1/TOT1>

<<P76/TIN2/TOT2>>

3

Function select

————CSL1CSL0

Timer control status register (TMCSR0)*

2

Select

signal

MOD2MOD1MOD0 OUTE OUTL

1

<TMCSR1>

<<TMCSR2>>

RELD

INTE UF

Operation

control circuit

CNTE

*1: The timer has ch.0, ch.1 and ch.2, and listed in the parenthesis <> are for ch.1 and << >> for ch.2.

*2: Interrupt number

φ: Machine clock frequency

To UART (ch.1)*

To 8/10-bit A/D converter

(ch. 2)

1

Pin

P74/TIN0/TOT0

<P75/TIN1/TOT1>

<<P76/TIN2/TOT2>>

TRG

Interrupt request signal

H

#27 (1B

<#29 (1D

)

2

H

)>*

<<#31 (1FH)>>

37

Page 38

MB90246A Series

6. 16-bit I/O Timer

The 16-bit I/O timer module consists of one 16-bit free-run timer, two input capture (ICU) circuits, and four output

comparators.

This complex module allows two independent waveforms to be output on the basis of the 16-bit free-run timer.

Input pulse width and external clock periods can, therfore, be measured.

The 16-bit I/O timer consists of:

• a 16-bit free-run timer; and

• two input captures (ICU).

• Block diagram

Internal data bus

16-bit

free-run timer

Dedicated bus

Input capture

(ICU)

38

Page 39

MB90246A Series

(1) 16-bit Free-run Timer

The 16-bit free-run timer consists of a 16-bit up counter, a prescaler, and a control register. The value output

from the timer counter is used as basic timer (base timer) for input capture (ICU).

• A counter operation clock can be selected from four internal clocks.

• An interrupt request can be issued to the CPU by counter overflow.

• The extended intelligent I/O service (EI

• The 16-bit free-run timer counter is cleared to “0000

• Register configuration

• Timer control status register (TCCS)

Address

00006E

H

.............

bit 15 bit 8

(Vacancy)

• Timer data register (TCDT)

Address

00006D

00006C

bit 15

bit 14bit 13bit 12bit 11bit 10 bit 9 bit 8 bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0

H

T15 T14 T13 T12 T11 T10 T09 T08 T07 T06 T05 T04 T03 T02 T01 T00

H

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

2

OS) can be activated.

H” by a reset or by clearing the timer (TCCS: CLK = 0).

bit 7 bit 6 bit 5 bit 4

IVFRESV

R/W R/W R/W R/W R/W R/W R/W R/W

STOPIVFE CLRRESV CLK0CLK1

bit 3 bit 2 bit 1 bit 0

Initial value

00000000

Initial value

00000000

00000000

B

B

B

: Readable and writableR/W

: Reserved bitRESV

• Block diagram

φ

Timer control

status register

Timer data register (TCDT)

OF

CLK CLR

Prescaler

2

(TCCS)

RESV IVF IVFE STOP RESV CLR CLK1 CLK0

16-bit free-run timer

STOP

Count value output

to input capture

(ICU)

Free-run timer

interrupt request

H

#23 (17

)*

Internal data bus

: Machine clock frequency

φ

: Overflow

OF

*

: Interrupt number

39

Page 40

MB90246A Series

(2) Input Capture (ICU)

The input capture (ICU) consists of a capture register corresponding to two 16-bit external input pins, a control

register, and an edge detector. Upon input of a trigger edge through an external input pin, the counter value of

the 16-bit free-run timer is stored into the input capture register, and an interrupt request can be generated

concurrently.

• A capture interrupt can be generated independently for each capture unit.

• The extended intelligent I/O service (EI

• A trigger edge direction can be selected from rising/falling/both edges.

• Since two input capture units can be operated independent of each other, up to two events can be measured

independently.

• The input capture function is suited for measurements of intervals (frequencies) and pulse-widths.

• Register configuration

• Input capture control status register (ICS)

Address

ICS0 : 000064

H

.............

bit 15 bit 8

(Vacancy)

2

OS) can be activated.

bit 7 bit 6 bit 5 bit 4

ICP0ICP1

R/W R/W R/W R/W R/W R/W R/W R/W

ICE0ICE1 EG10EG11 EG00EG01

bit 3 bit 2 bit 1 bit 0

Initial value

00000000

B

• Input capture register (IPCP0, IPCP1)

bit 15

bit 14bit 13bit 12bit 11bit 10 bit 9 bit 8 bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0

H

CP15 CP14 CP13 CP12 CP11 CP10 CP09 CP08 CP07 CP06 CP05 CP04 CP03 CP02 CP01 CP00

H

H

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

H

ICP1 ICP0 ICE1

IPCP0 : 000061

IPCP1 : 000063

IPCP0 : 000060

IPCP1 : 000062

R/W:Readable and writable

R : Read only

X : Indeterminate

•

Block diagram

P71/ASR1

P70/ASR0

Address

Edge detection circuit

Pin

Pin

Input capture

control status

register(ICS)

Input capture register 1 (IPCP1)

Input capture register 0 (IPCP0)

EG11 EG10 EG01 EG00

ICE0

16-bit free-run timer

Initial value

XXXXXXXX

XXXXXXXX

Internal data bus

B

B

40

*: Interrupt number

#17 (11H)

#15 (OF

Input capture

interrupt request

(ICU)

H

)

Page 41

MB90246A Series

7. Simple I/O Serial Interface

The 8/16-bit simple I/O serial interface transfers data synchronously with a clock.

• Communications direction: Concurrent processing of transmission (Whether data is to be sent or received

must be judged by the user.)

• Transfer mode: Clock synchronization function (Only data are transferred.)

• Transfer rate:DC to φ/2 (φ: Machine clock. Frequencies of up to 8 MHz are available when the machine clock

is rated at 16 MHz.)

• Shift clock: A machine clock division clock is used as the shift clock. (One of four division ratios can be

selected.). A shift clock is output only during data transfer.

• Data transfer format: MSB first can be selected. 8 or 16 bits can be selected as data length. Only data are

transferred.

• Interrupt request: An interrupt request is issued upon termination of transfer.

• Inter-CPU connection: Only 1:1 (bidirectional communication)

(1) Register Configuration

• Serial control status register 1, 2 (SCR)

Address

SCR0 : 000020

SCR1 : 000024

.............

bit 15 bit 8

H

H

(SSR)

bit 7 bit 6 bit 5 bit 4

OCKESTOP

R/W R/W R/W R/W R/W R/W R/W R/W

bit 3 bit 2 bit 1 bit 0

SIESOE WBSSIR SMD0SMD1

Initial value

10000000

B

• Serial status register 1, 2 (SSR)

Address

SSR1 : 000021

SSR2 : 000025

bit 15 bit 14 bit 13 bit 12 bit 11 bit 10 bit 9 bit 8

H

———————BUSY

H

———————R

• Serial data register 1, 2 (SDR)

Address

SDR1H : 000023

SDR2H : 000027

SDR1L : 000022

SDR2L : 000026

R/W:Readable and writable

R : Read only

— : Unused

X : Indeterminate

bit 15

bit 14bit 13bit 12bit 11bit 10 bit 9 bit 8 bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0

H

D15 D14 D13 D12 D11 D10 D09 D08 D07 D06 D05 D04 D03 D02 D01 D00

H

H

R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W

H

.............

bit 7 bit 0

(SCR)

Initial value

-------1

Initial value

XXXXXXXX

XXXXXXXX

B

B

B

41

Page 42

MB90246A Series

(2) Block Diagram