Page 1

FUJITSU SEMICONDUCTOR

MICROCONTROLLER MANUAL

MICROCONTROLLERS

CM25–10113–1E

F2MC-8L FAMILY

MB89140 SERIES

HARDWARE MANUAL

Page 2

All Rights Reserved.

F2MC-8L FAMILY

MICROCONTROLLERS

MB89140 SERIES

HARDWARE MANUAL

Edition 1.0 February 1995

1995 FUJITSU DEVICES Inc.

Circuit diagrams utilizing Fujitsu products are included as a means of illustrating typical

semiconductor applications. Complete information sufficient for construction purposes

is not necessarily given.

The information contained in this document has been carefully checked and is believed

to be reliable. However, Fujitsu assumes no responsibility for inaccuracies.

The information contained in this document does not convey any license under the

copyrights, patent rights or trademarks claimed and owned by Fujitsu.

Fujitsu reserves the right to change products or specifications without notice.

No part of this publication may be copied or reproduced in any form or by any means, or

transferred to any third party without prior written consent of Fujitsu.

Page 3

PREFACE

The terms in this manual are defined as follows:

(1) A clock cycle is one clock cycle of the oscillation frequency.

(2) A system clock cycle is the clock frequency divided by the gear function (see 2.2). One cycle time of the

system clock varies with the settings of the CS1 and CS0 bits of the SYCC register. With some internal

resources, the gear change will cause changes in operating speed. See 3.4 for details.

iii

Page 4

Table of Contents

1. GENERAL 1-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1 FEA TURES 1-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 PRODUCT SERIES 1-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 BLOCK DIAGRAM 1-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4 PIN ASSIGNMENT 1-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.5 PIN FUNCTION DESCRIPTION 1-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.6 HANDLING DEVICES 1-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2. HARDWARE CONFIGURATION 2-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1 CPU 2-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 MAIN/SUB CLOCK CONTROL BLOCK 2-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3 INTERRUPT CONTROLLER 2-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4 I/O PORTS 2-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5 WATCH PRESCALER 2-34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6 WATCHDOG TIMER RESET 2-36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.7 TIME-BASE TIMER 2-41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.8 8-BIT PWM TIMER (TIMER 1) 2-43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.9 8/16-BIT TIMER (TIMER 2 AND TIMER 3) 2-48. . . . . . . . . . . . . . . . . . . . . . . . . .

2.10 12-BIT MULTIPUL GENERATOR (MPG, TIMER 4) 2-55. . . . . . . . . . . . . . . . . . .

2.11 8-BIT SERIAL I/O 2-70. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.12 A/D CONVERTER 2-76. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.13 BUZZER OUTPUT CIRCUIT 2-83. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.14 EXTERNAL INTERRUPT CIRCUIT 2-85. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3. OPERA TION 3-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1 CLOCK PULSE GENERATOR 3-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 RESET 3-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.1 Reset Operation 3-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.2 Reset Sources 3-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3 INTERRUPT 3-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4 LOW-POWER CONSUMPTION MODES 3-8. . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5 PIN STATES FOR SLEEP, STOP AND RESET 3-9. . . . . . . . . . . . . . . . . . . . . . .

4. INSTRUCTIONS 4-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1 TRANSFER INSTRUCTIONS 4-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2 OPERATION INSTRUCTIONS 4-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3 BRANCH INSTRUCTIONS 4-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4 OTHER INSTRUCTIONS 4-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5 F

2

MC-8L FAMILY INSTRUCTION MAP 4-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5. MASK OPTIONS 5-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

APPENDIX App. 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

APPENDIX A I/O MAP App.- 3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

APPENDIX B EPROM SETTING FOR MB89P147 App.- 5. . . . . . . . . . . . . . . . . . . . .

APPENDIX C LIST OF SYSTEM CLOCK CYCLE TIMES WHEN GEAR

CHANGED (SOURCE CLOCK: 8 MHz, 4 MHz) App.- 7. . . . . . . . . .

iv

Page 5

Tables

Table 1-1 Types and Functions of MB89140 Series of Microcontrollers 1-5. . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 1-1 Types and Functions of MB89140 Series of Microcontrollers (Continued) 1-6. . . . . . . . . . . . . . . .

Table 1-2 Pin Function Description 1-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 1-3 Pin for External-ROM 1-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 2-1 Table of Reset and Interrupt Vectors 2-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 2-2 Operating State of Low-power Consumption Modes 2-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 2-3 Sources of Reset 2-20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 2-4 List of Port Functions 2-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 2-5 Port register 2-26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 2-6 Relationship between value Set at OUTCR and Duty 2-65. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 2-7 Buzzer Output Frequencies

Table 3-1 Interrupt Sources and Interrupt Vectors 3-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 3-2 Low-power Consumption Mode at Each Clock Mode 3-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 3-3 Pin State of MB89140 3-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

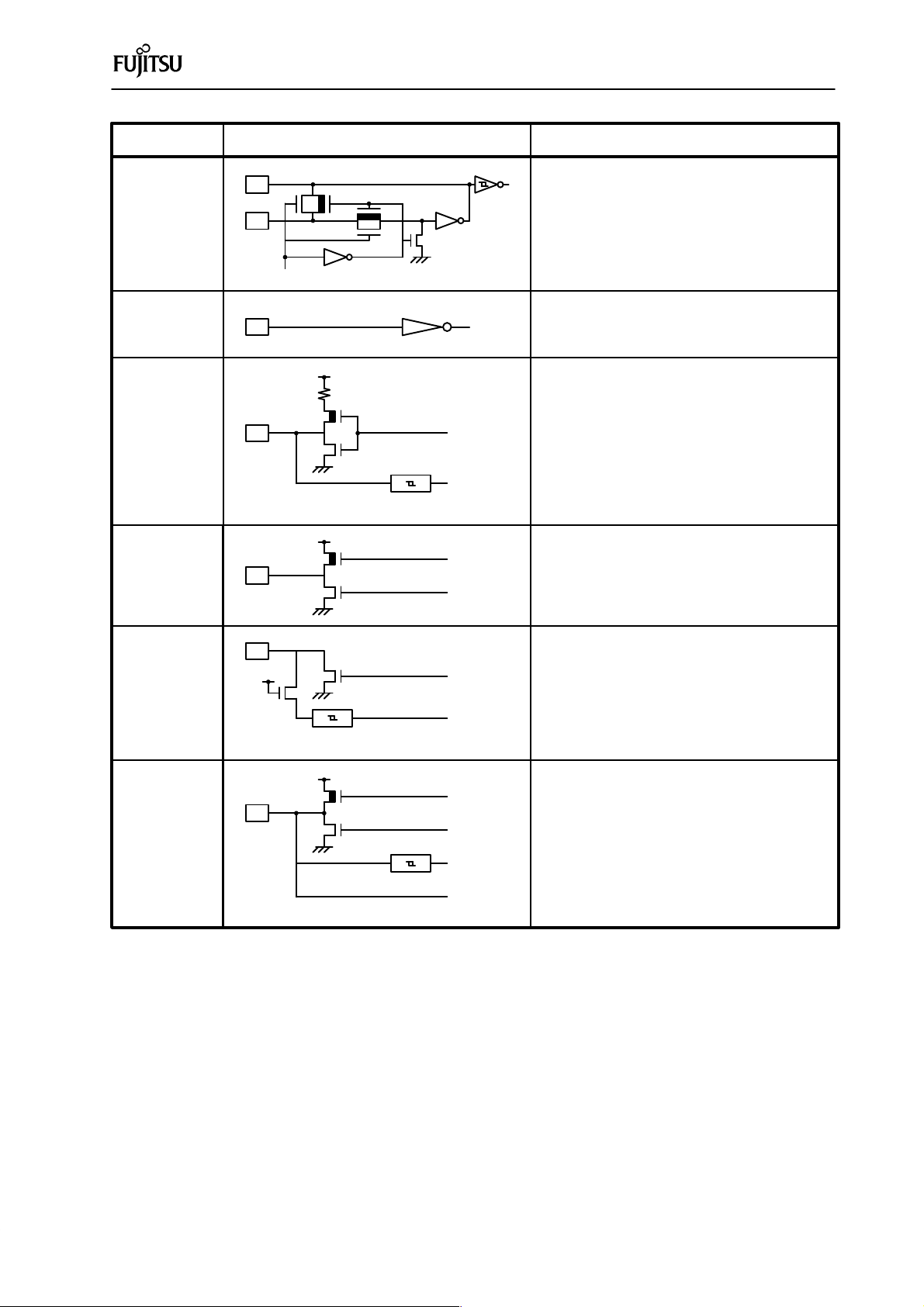

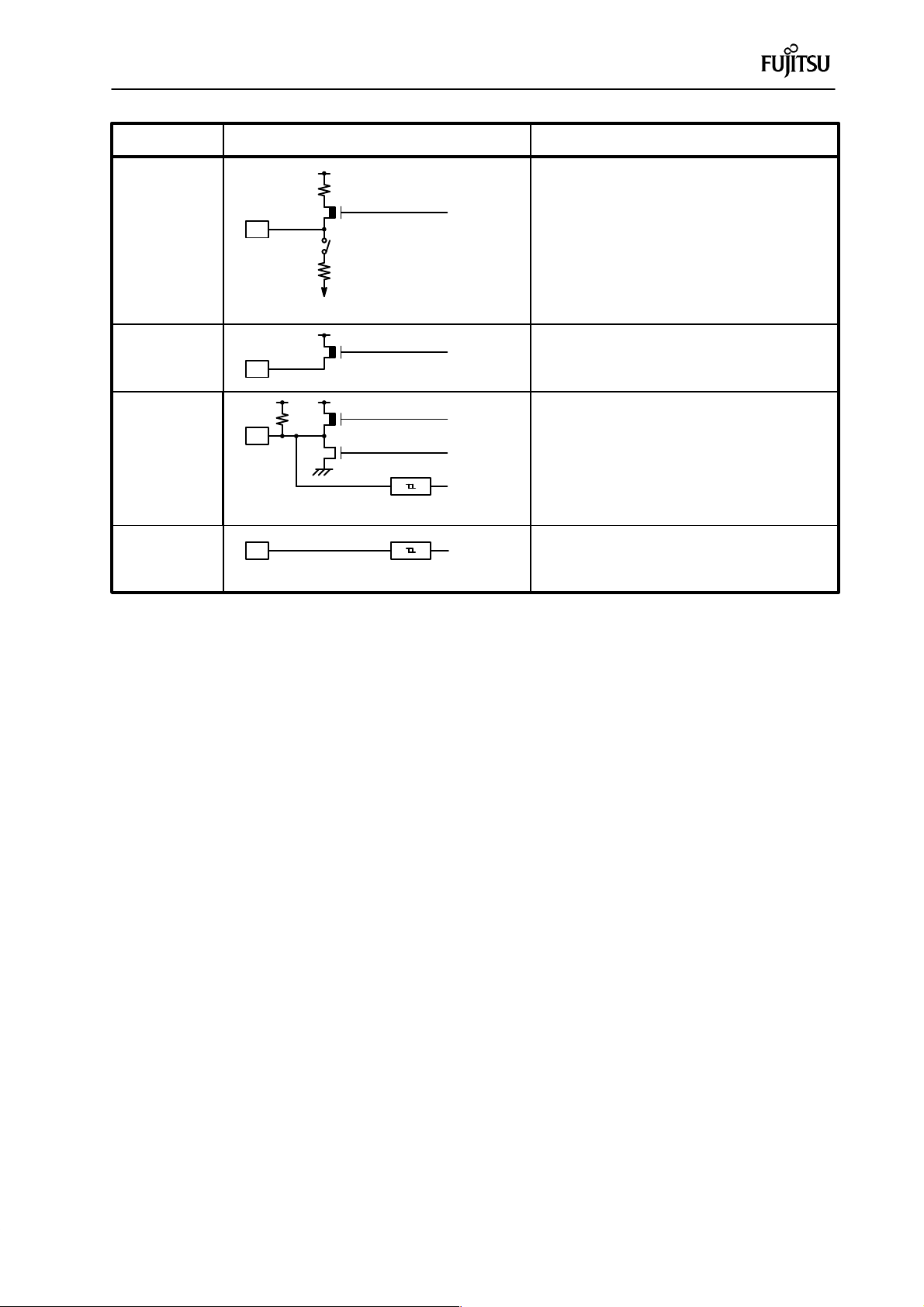

Table 5-1 Mask Options 5-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 5-2 Model Specifications 5-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

(at 8.0 MHz of oscillation frequency) 2-84. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

v

Page 6

Figures

Fig. 1.1 MB89140 series 1-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 1.2 Block Diagram 1-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

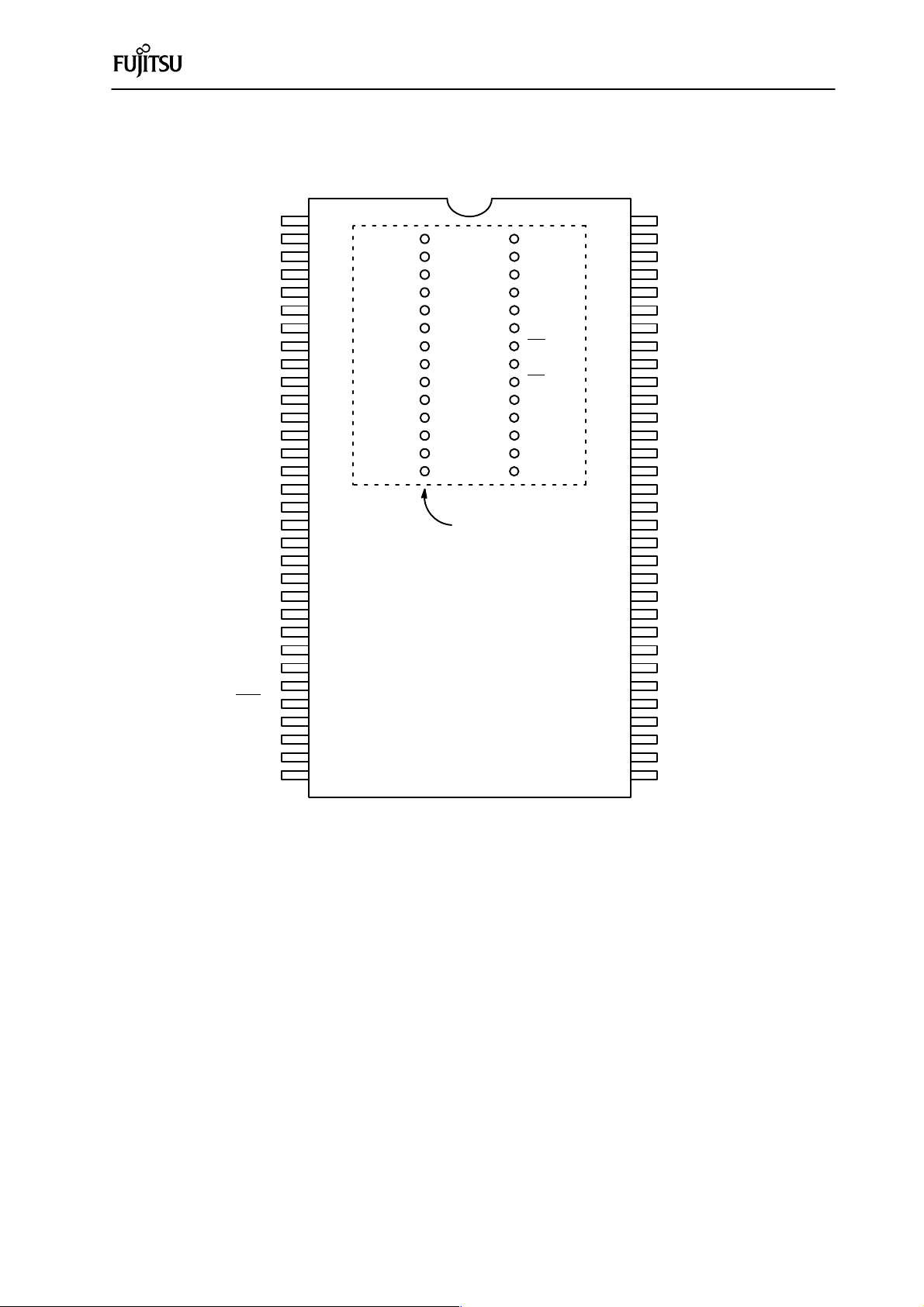

Fig. 1.3 Pin Assignment (DIP-64P-M01, MDP-64C-P02) 1-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

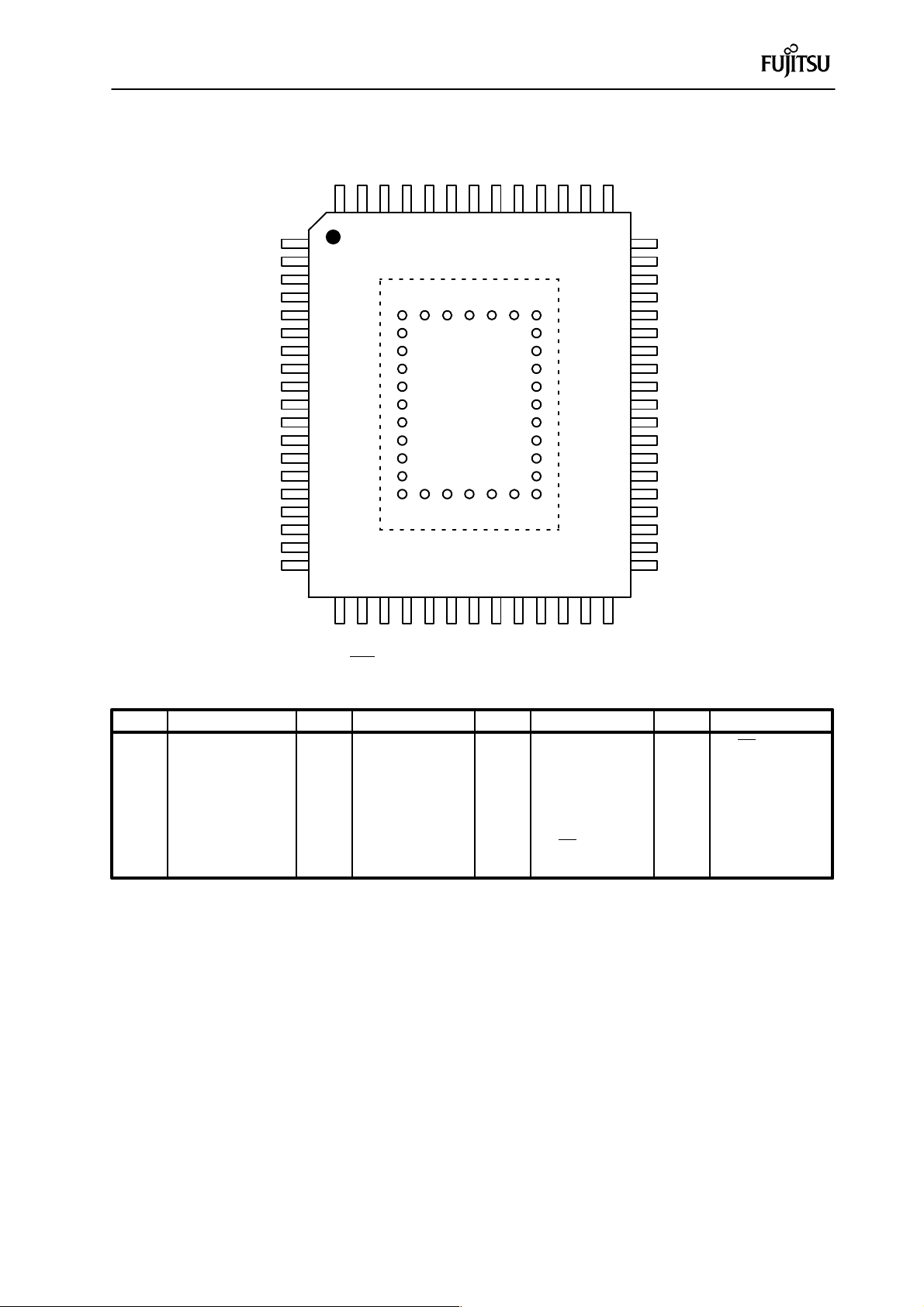

Fig. 1.4 Pin Assignment (FPT-64P-M06, MDP-64C-P01) 1-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 1.5 Input/Output Circuit Configurations 1-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.1 Memory Space of MB89140 Series of Microcontrollers 2-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.2 Arrangement of 16-bit Data in Memory 2-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.3 Arrangement of 16-bit Data during Execution of Instruction 2-5. . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.4 Structure of Processor Status 2-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.5 Rule for Translating Real Addresses at General-purpose Register Area 2-7. . . . . . . . . . . . . . . . .

Fig. 2.6 Register Bank Configuration 2-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.7 Memory Map in Various Modes 2-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.8 Machine Clock Control Block Diagram 2-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.9 Interrupt Controller Block Diagram 2-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.10 Interrupt-processing Flowchart 2-24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.11 Ports 00 to 07 and 10 to 13 2-28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.12 Ports 14 to 16 2-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.13 Ports 20 to 23 2-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.14 Ports 70 and 71 2-30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.15 Ports 35 to 32, 30 and 17 2-31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.16 Port 31 2-32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.17 Ports 40 to 47, 50 to 57 and 60 to 67 2-33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.18 BZ 2-33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.19 Watch Prescaler Block Diagram 2-34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.20 Watchdog Timer Reset Block Diagram 2-36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.21 Time-base Timer Block Diagram 2-41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.22 8-bit PWM Timer (Timer 1) Block Diagram 2-43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.23 Timer Operation 2-46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.24 PWM Pulse Output 2-47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.25 8/16-bit Timer Block Diagram 2-48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.26 Description Diagram for Internal Clock Mode Operation 2-52. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.27 Flow Diagram for Timer Setting 2-52. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.28 External Cock Mode Operation Description Diagram 2-53. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.29 Operation Diagram when Timer Stop Bit is Used 2-53. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.30 MPG Block Diagram 2-56. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.31 Transition of DTTI Input 2-59. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.32 Outline of PWM Output 2-63. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.33 Description of PWM Output Operation 2-63. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.34 Flowchart of PWM Operation 2-64. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.35 Outline of MPG Output 2-67. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.36 Description of PPG Output Operation 2-67. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.37 Flowchart of PPG Operation 2-68. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.38 8-bit Serial I/O Block Diagram 2-70. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.39 Shift Start/Stop Timing 2-74. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.40 Input/Output Shift Timing 2-75. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.41 A/D Comverter Block Diagram 2-76. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.42 Buzzer Output Circuit Block Diagram 2-83. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.43 External Interrupt Circuit Block Diagram 2-85. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 3.1 Clock Pulse Generator 3-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 3.2 Outline of Reset Operation 3-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 3.3 Reset Vector Structure 3-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 3.4 Interrupt-processing Flowchart 3-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

vi

Page 7

1. GENERAL

1.1 FEATURES 1-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 PRODUCT SERIES 1-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 BLOCK DIAGRAM 1-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4 PIN ASSIGNMENT 1-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.5 PIN FUNCTION DESCRIPTION 1-10. . . . . . . . . . . . . . . . .

1.6 HANDLING DEVICES 1-16. . . . . . . . . . . . . . . . . . . . . . . . .

Page 8

GENERAL

The MB89140 series of single-chip microcontrollers use the F2MC-8L CPU core to enable high-speed processing at low voltages, and features a 25 segment VFD (V acuum Fluorescent Display) driver . They contain resources such as timers, a serial interface, an A/D converter and an external interrupt input to provide a wide

variety of applications for commercial and industrial equipment, including portable equipment.

The MB89140 series of single-chip microcontrollers has twenty-five V

which makes it suitable for VFD display application such as microwave oven, fan heater, room air conditioner ,

dashboard controller, and so on.

-40VP-channel high voltage ports

CC

1.1 FEATURES

• Minimum instruction execution time: 0.5 µs (at oscillation frequency of 8 MHz)

• CPU core as commonly used for MB89860 series

Multiplication and division instructions

–Instruction system best for controller

• Operation at low voltage (A/D converter unused)

• 25 segment VFD (Vacuum Fluorescent Display) driver.

• Low current dissipation (applicable to dual-circuit clock)

• Internal high-withstand-voltage ports

• 5 timers

–8-bit PWM timer (available as reload timer)

–12-bit MPG timer (available as PPG output, PWM output and reload timer)

–8/16-bit timer/counter (available as two 8-bit timers)

–21-bit time-base counter

16-bit operation

Instruction test and branch instruction

Bit handling instruction, etc.

• Single serial interface

–Transfer direction selected for communication with various equipment

• A/D converter

–Successive approximation type with 10-bit resolution

• 2-channel external interrupt input

–Two channels can be selected independently to cancel the low-power consumption modes (selectable

from rising edge, falling edge, or both edges).

–The INT1 can be applied from –0.7 V to 7.0 V (N-channel open drain).

• Low-power consumption modes

–Stop mode (The oscillation stops to minimize current consumption.)

–Sleep mode (The CPU stops to cut current consumption to about 30% of normal.)

• Reset output or power-on reset available option can be selected.

• Packages

–SDIP-64 and QFP-64 packages

1-3

Page 9

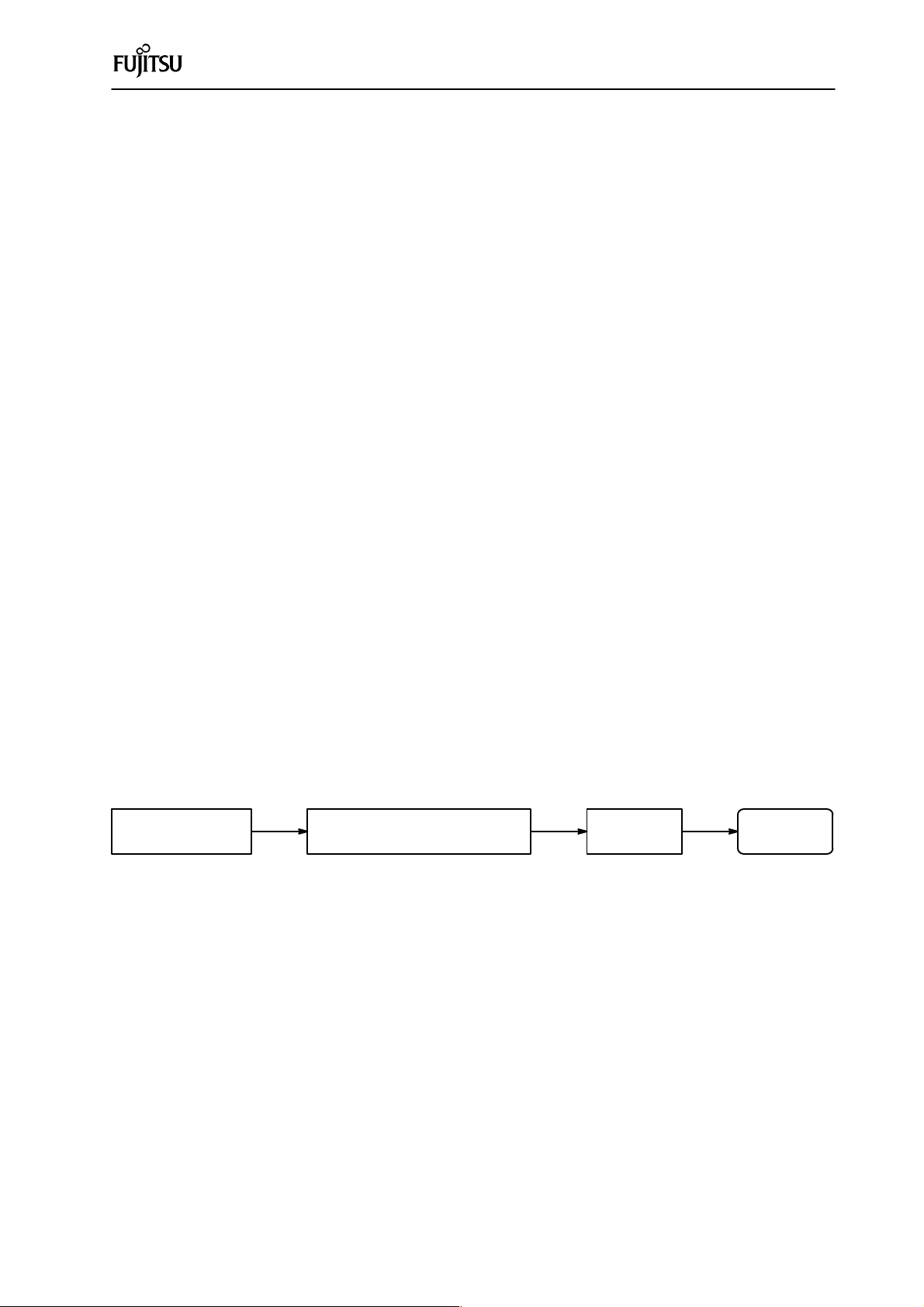

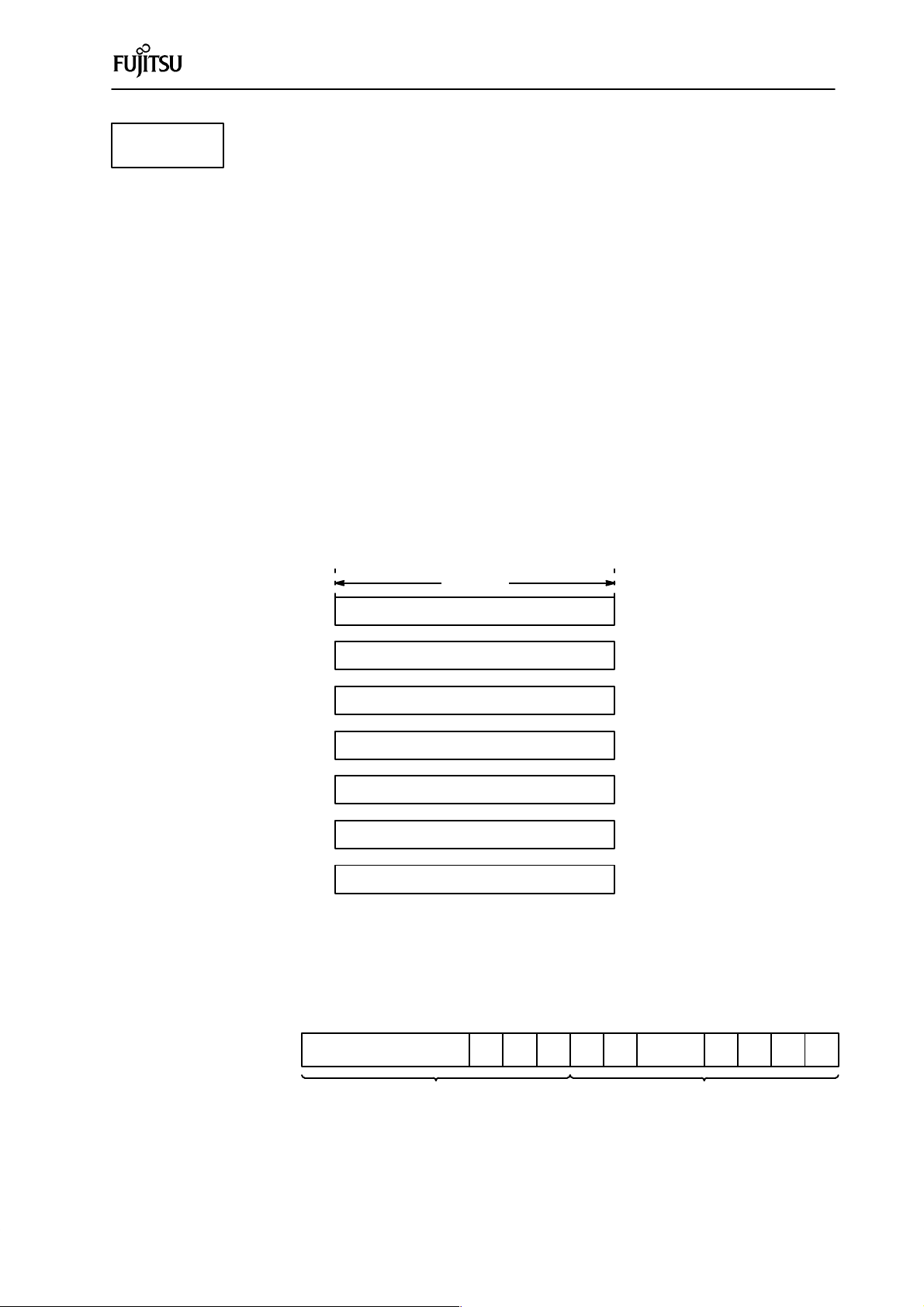

(Planned)

MB89144

ROM 12K

RAM 256

(Under development)

MB89145

ROM 16K

RAM 512

Fig. 1.1 MB89140 series

GENERAL

(Planned)

MB89146

Memory capacity

Small Large

ROM 24K

RAM 768

(Under development)

MB89147

ROM 32K

RAM 1K

1-4

Page 10

GENERAL

1.2 PRODUCT SERIES

Table 1-1 lists the types and functions of the MB89140 series of microcontrollers.

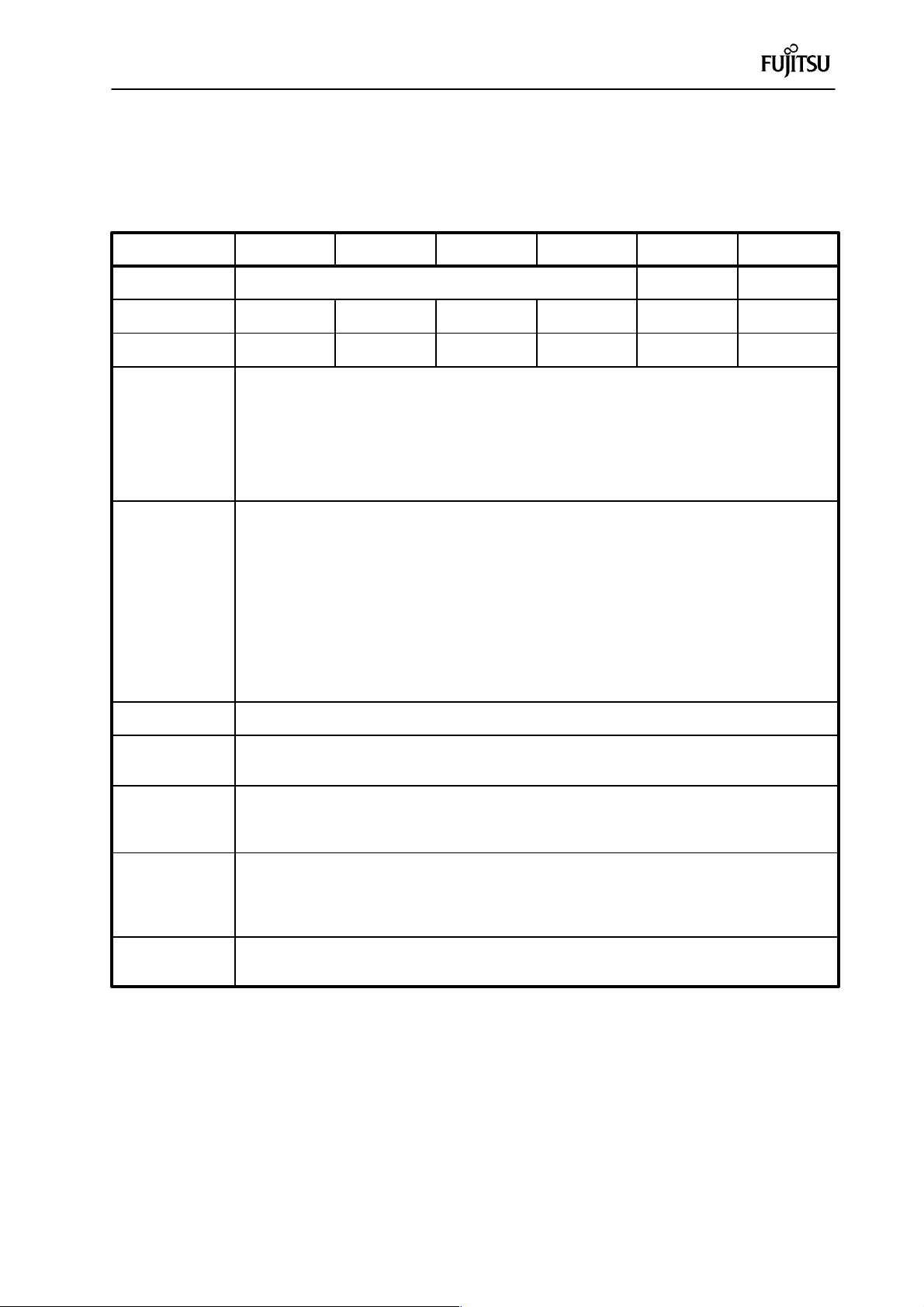

Table 1-1 Types and Functions of MB89140 Series of Microcontrollers

Model Name MB89144 MB89145 MB89146 MB89147

Classification

ROM capacity 12K × 8 bit 16K × 8 bit 24K × 8 bit 32K × 8 bit

RAM capacity 256 × 8 bit 512 × 8 bit 768 × 8 bit 1K × 8 bit

Number of basic instructions 136

Instruction bit length 8 bits

Instruction length 1 to 3 bytes

CPU functions Data bit length 1, 8, 16 bits

Minimum instruction execution time 0.5 µs/8 MHz to 8.0 µs/8 MHz and 61 µs/32.768 kHz

Interrupt processing time 4.5 µs/8 MHz to 72.0 µs/8 MHz and 562.5 µs/32.768 kHz

High-withstand-voltage output port 8 (P60 to P67 for large current)

(P-channel open drain) 16 (P40 to P47, P50 to P57 for small current)

Buzzer output 1 (Large current)

(P-channel open drain, high-withstand-voltage)

Output port (CMOS) 4 (P20 to P23)

Port Input port (CMOS) 2 (P70 to P71; serve as X0A and X1A pins when two

I/O port (CMOS) 23 (P00 to P07, P10 to P17, P30, P32 to P37)

I/O port (N-channel open drain) 1 (P31)

Total 55

Mass-produced product

(Mask ROM product)

Note: The above times vary with gear function.

clocks used)

MB89P147

MB89W147

OTPROM/

EPROM product

Internal

32K × 8 bits

Internal

1K × 8 bits

MB89PV140

Piggyback/evaluation

product for evaluation

and development

External 32K × 8

bits (Piggyback)

Internal

1024 × 8 bits

VFD 25 segment

Time-base timer

8-bit PWM timer

(Timer 1)

12-bit MPB timer 12-bit resolution reload timer operation (toggle output possible)

(Timer 4) 12-bit resolution PPG operation (minimum resolution: 0.5 µs at oscillation frequency of 8.0 MHz and

8/16-bit timer/counter 8/16-bit timer operation (operating clock, internal clock and external trigger). See 2.2 for details.

(Timers 2 and 3) 8/16-bit event counter operation (selectable from rising edge, falling edge, or both edges)

Capable of generating four internal pulses of 0.26 ms, 0.51 ms, 1.02 ms and 0.524 s

(at oscillation frequency of 8.0 MHz)

8-bit timer operation (toggle output possible, 1, 2, 8 or 16 system clock cycles of operating clock)

8-bit resolution PWM operation (conversion cycle: 128 µs to 2.0 ms at oscillation frequency of 8.0 MHz

and maximum gear speed)

12-bit resolution PWM operation (maximum conversion cycle: 2048.4 µs to 16.4 ms

maximum gear speed)

1-5

Page 11

GENERAL

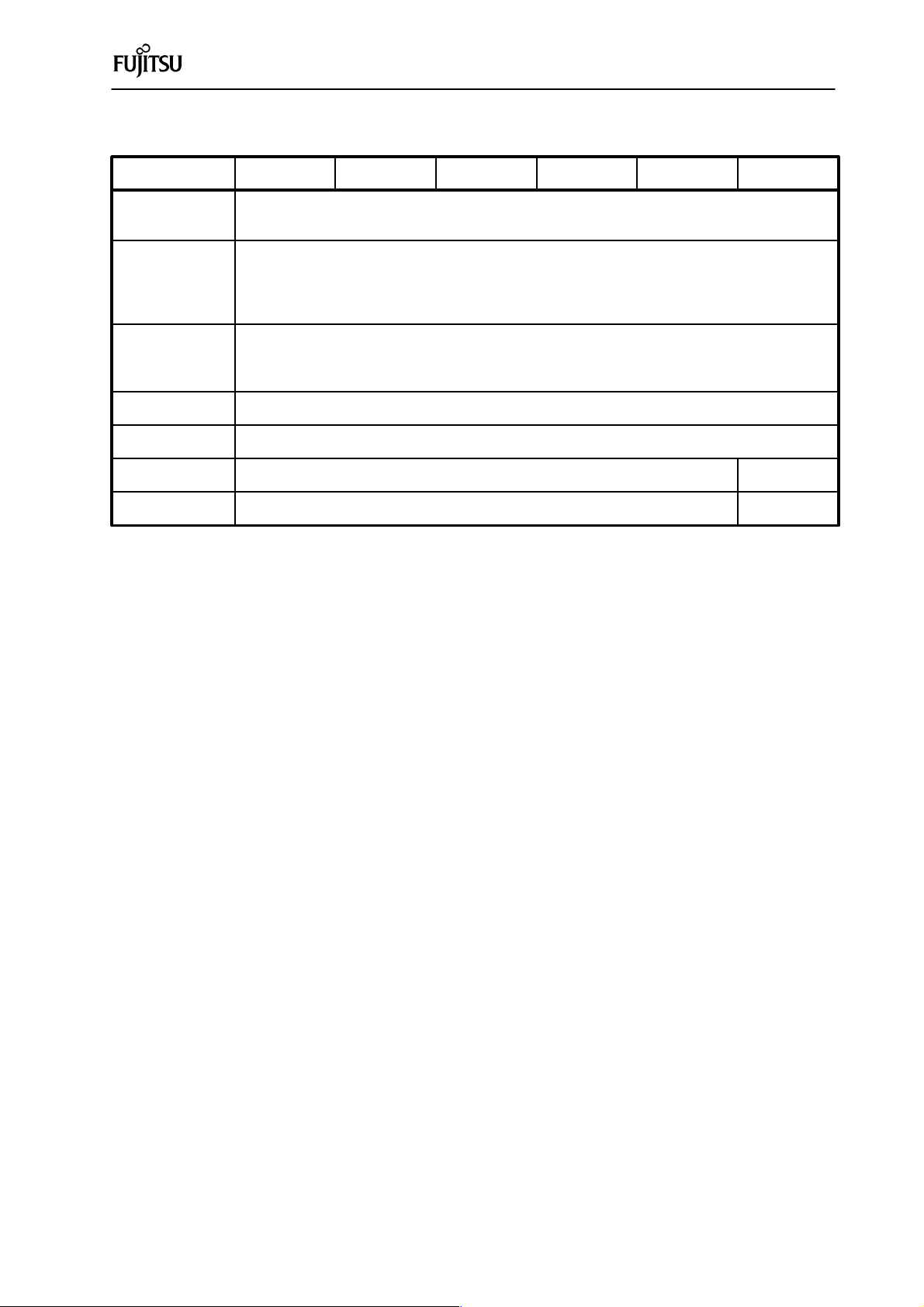

Table 1-1 Types and Functions of MB89140 Series of Microcontrollers (Continued)

Model Name MB89144 MB89145 MB89146 MB89147

Serial I/O

A/D converter

External interrupt Interrupt mode selectable from rising edge, falling edge, or both edge. Analog noise filter built in

Standby mode Sleep, Stop and Watch mode

Process CMOS

Package DIP-64P-M01 (SDIP-64)/FPT-64P-M06 (QFP64)

Operating voltage 2.7 V to 6.0 V* 2.7 V to 6.0 V

8-bit length 1 channel

Transfer clock (external, 4, 8 or 16 system clock cycles)

10-bit resolution, 12 channels

A/D conversion mode (conversion time: 16.5 µs at 8 MHz and maximum gear speed)

Sense mode (conversion time: 9.0 µs at 8 MHz and maximum gear speed)

Continuous start by external activation or internal timer

2 independent channels (edge selection, interrupt vector, interrupt source flag)

For releasing Stop/Sleep modes (edge detection possible in Stop mode)

MB89P147

MB89W147

MB89PV140

MDP-64C-P02/

MQP-64C-P01

* Operating voltage varies depending to the condition such as frequency or others.

1-6

Page 12

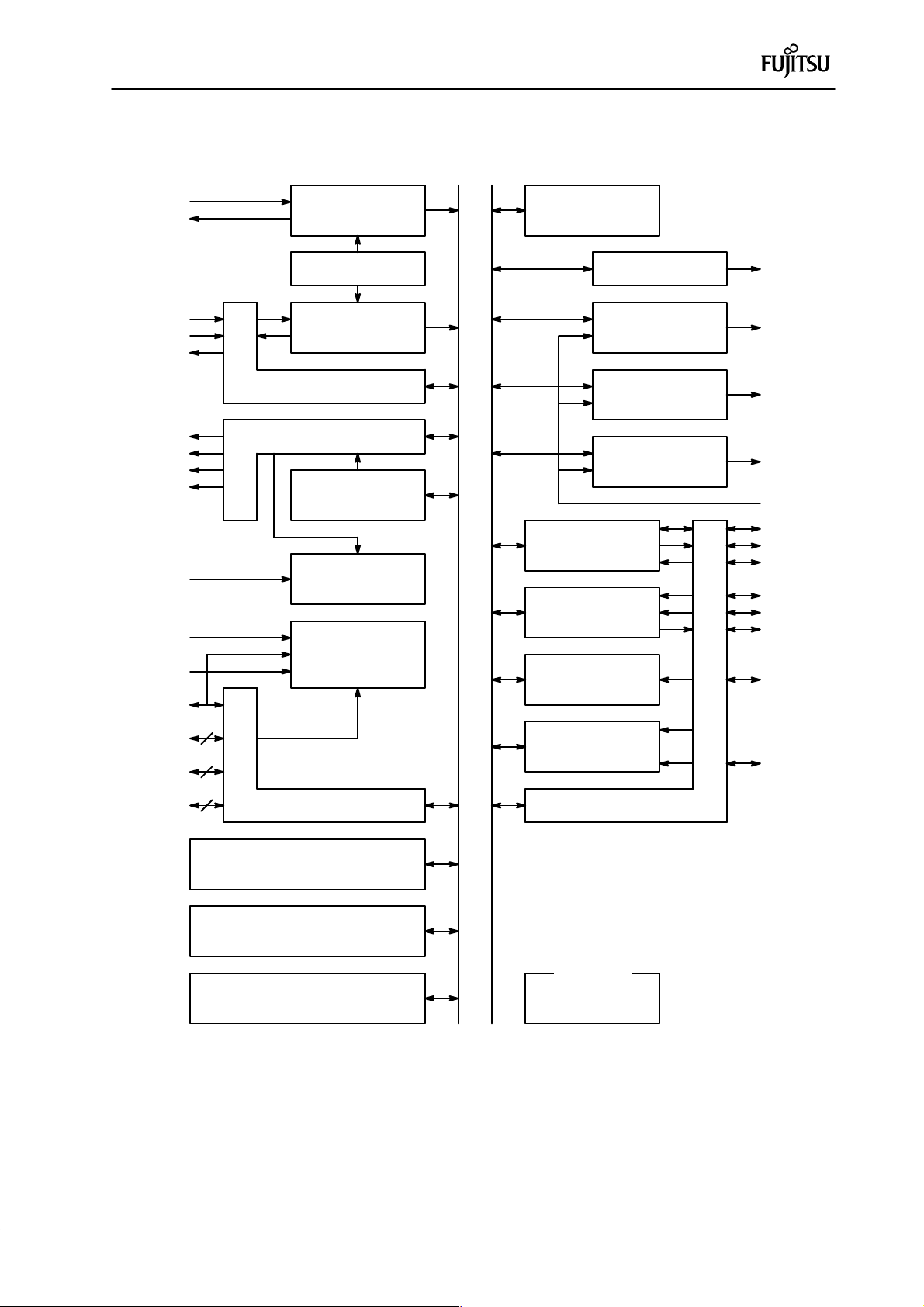

1.3 BLOCK DIAGRAM

GENERAL

Internal bus

X0

X1

P70, P71

X0A

X1A

P23/WDG

P22

P21/PWO0

P20

MODA

AV

CC

AV

SS

Port

7

Port

2

Main clock oscillator

(Max. 8 MHz)

Clock control

Sub clock oscillator

(32.768 kHz)

CMOS input port

CMOS output port

8-bit PWM timer

Mode control

10-bit A/D converter

Time-base timer

High-withstand-voltage

High-withstand-voltage

High-withstand-voltage

8-bit serial

12-bit MPG

8/16-bit timer/counter

Buzzer

port 6

port 5

port 4

Port

3

BZ

P60 to P67

P50 to P57

P40 to P47

VFD

P32/SCK

P33/SO

P34/SI

P30/TRG/INT0

P37/DTTI

P3/PWO1

P35/EC

P17/ADST

P14 to P16

P13/ANB to

P10/AN8

P07/AN7 to

P00/AN0

4

Port

4

0/1

8

CMOS output port

(Max. 512 × 8 bit )

F

(Max. 16 K × 8 bit)

RAM

2

MC-8L

CPU

ROM

External interrupt

Fig. 1.2 Block Diagram

input

CMOS I/O port

Other pins

VCC, V

SS

P31/INT1

1-7

Page 13

1.4 PIN ASSIGNMENT

GENERAL

TOP VIEW

BZ ←

P67 ←

P66 ←

P65 ←

P64 ←

P63 ←

P62 ←

P61 ←

P60 ←

VFD →

P57 ←

P56 ←

P55 ←

P54 ←

P53 ←

P52 ←

P51 ←

P50 ←

P47 ←

P46 ←

P45 ←

P44 ←

P43 ←

P42 ←

P41 ←

P40 ←

P23/WDG ←

RST

↔

MODA →

X0 →

X1 ←

V

←

SS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

A15/VAA

A12

A7

A6

A5

A4

A3

A2

A1

A0

O1

O2

O3

V

SS

65

66

67

68

69

70

71

72

73

74

75

76

77

78

92

91

90

89

88

87

86

85

84

83

82

81

80

79

Items in dotted lines

are only available for

the MB89PV140.

V

CC

A14

A13

A8

A9

A11

OE

A10

CE

O8

O7

O6

O5

O4

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

← V

CC

← AV

CC

← AV

SS

↔ P00/AN0

↔ P01/AN1

↔ P02/AN2

↔ P03/AN3

↔ P04/AN4

↔ P05/AN5

↔ P06/AN6

↔ P07/AN7

↔ P10/AN8

↔ P11/AN9

↔ P12/ANA

↔ P13/ANB

↔ P14

↔ P15

↔ P16

↔ P17/ADST

↔ P30/INT0/TRG

↔ P31/INT1

↔ P32/SCK

↔ P33/SO

↔ P34/SI

↔ P35/EC

↔ P36/PWO1

↔ P37/DTTI

→ P20

→ P21/PWO0

→ P22

← P70/X0A

↔ P71/X1A

The SH-DIP64 cautions are as follows:

• Pins 33 and 34 serve as input-only ports when used as general-purpose ports.

• Pin 28 serves as an output pin when the reset output option is selected.

• P07 to P00 and P13 to P10 serve as analog input ports after reset. When using them as port inputs, registers

PCR0 and PCR1 must be set.

Fig. 1.3 Pin Assignment (DIP-64P-M01, MDP-64C-P02)

1-8

Page 14

GENERAL

P61

P60

VFD

P57

P56

P55

P54

P53

P52

P51

P50

P47

P46

P45

P44

P43

P42

P41

P40

P63 P65 P67 V

CC

AV

SS

P00/ P02/

P62 P64 P66 BZ AV

CC

AN0 AN2

64 63 62 61 60 59 58 57 56 55 54 53 52

1

TOP VIEW

2

3

4

84 83 82 81 80 79 78

5

6

7

8

9

10

11

12

13

14

85

86

87

88

89

90

91

92

93

77

76

75

74

73

72

71

70

69

15

16

17

18

19

94 95 96 65 66 67 68

Items in dotted lines are only

available for the MB89PV140.

20 21 22 23 24 25 26 27 28 29 30 31 32

P01

/AN1

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

P03/AN3

P04/AN4

P05/AN5

P06/AN6

P07/AN7

P10/AN8

P11/AN9

P12/ANA

P13/ANB

P14

P15

P16

P17/ADST

P30/INT0/TRG

P31/INT1

P32/SCK

P33/SO

P34/SI

P35/EC

P23 MODA X1 P71/ P22 P20 P36/

/WDG X1A PWO1

RST

X0 V

P70/ P21/ P37/

SS

X0A PWO0 DTTI

Pin Symbol Pin Symbol Pin Symbol Pin Symbol

65 N.C. 73 A2 81 N.C. 89 OE

66 A15/V

PP

74 A1 82 O4 90 N.C.

67 A12 75 A0 83 O5 91 A11

68 A7 76 N.C. 84 O6 92 A9

69 A6 77 O1 85 O7 93 A8

70 A5 78 O2 86 O8 94 A13

71 A4 79 O3 87 CE

72 A3 80 V

SS

88 A10 96 V

95 A14

CC

Fig. 1.4 Pin Assignment (FPT-64P-M06, MDP-64C-P01)

1-9

Page 15

GENERAL

1.5 PIN FUNCTION DESCRIPTION

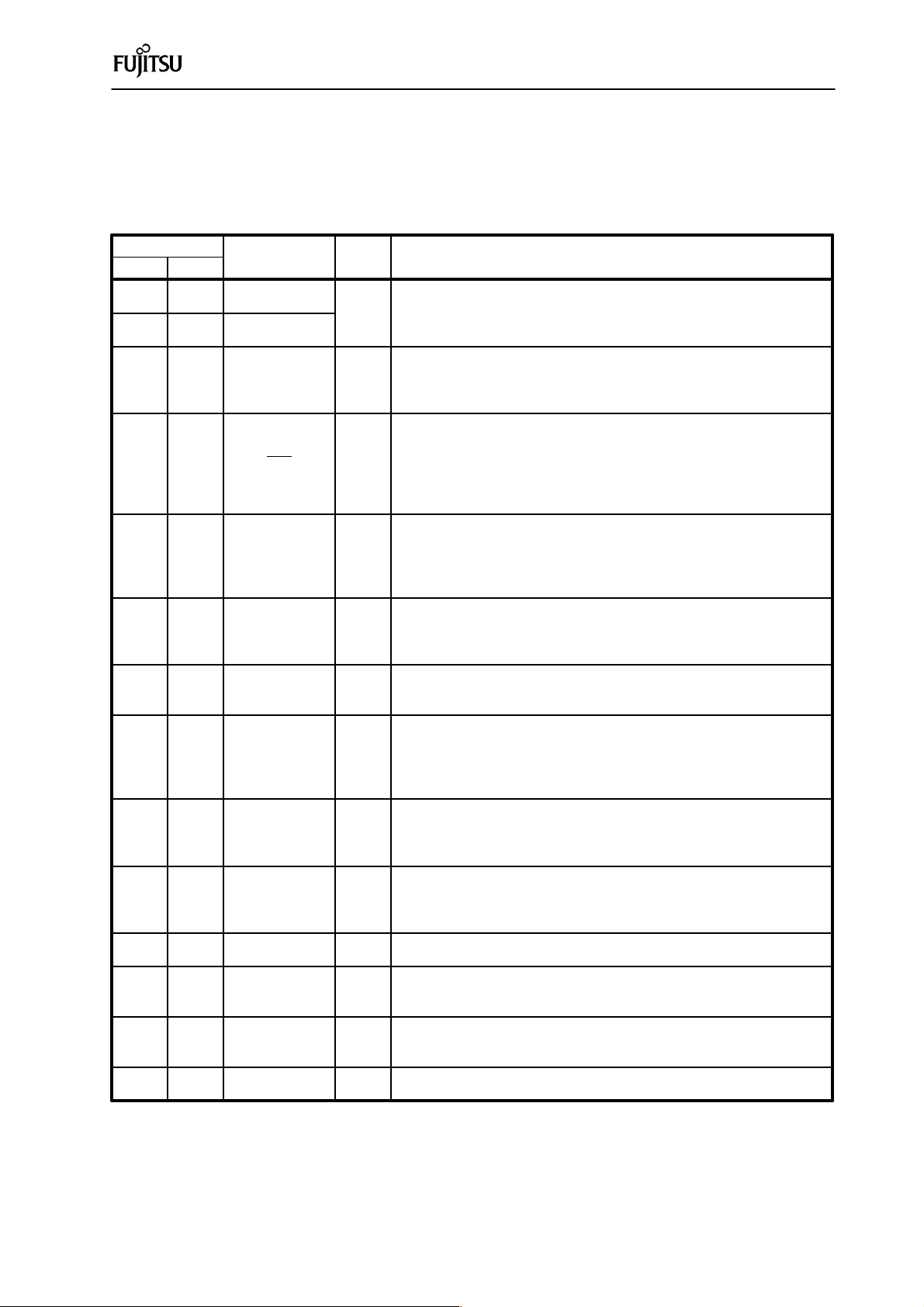

Table 1-2 and NO TAG lists the pin function and Figure 1.3 shows the input/output circuit configurations.

Table 1-2 Pin Function Description

Pin No.

SDIP

30 23 X0 Used for main clock oscillation

31 24 X1

29 22 MODA B Usually connected to V

28 21 RST

54 to 61 47 to 54 to F

46 39 P17/ADST I Input is hysteresis type containing a noise filter. This port also serves as an

47 to 49 40 to 42 P16 to P14 I

QFP

from this pin according to the internal source. The internal circuit is initial-

Pin Name

P07/AN7

P00/AN0

Circuit

type

A A crystal resonator should be used.

Used for input of operation mode select signals

. This pin serves as the VPP pin for EPROM-

mounted models.

Used for input/output of reset signals

Consists of an N-channel open-drain output with a pull-up resistor and

C hysteresis input. When the reset on option is selected, a Low level is output

ized at input of a Low level. A noise canceler is built in.

General-purpose I/O ports

Input is hysteresis type containing a noise filter. Although these ports also

serves as analog input pins, analog input does not pass through the noise

filter for hysteresis input.

General-purpose I/O port

external start pin for the A/D converter.

General-purpose I/O ports

Input is hysteresis type containing a noise filter.

SS

Function

P13/ANB

50 to 53 43 to 46 to F

P10/AN8

34 27 X0A/P70 A/J pin by the mask option. When using as a general-purpose input pin, input

33 26 X1A/P71 A/J pin by the mask option. When using as a general-purpose input pin, input

35 28 P22 D General-purpose output port

27 20 P23/WDG D

36 29 P21/PWO0 D

37 30 P20 D General-purpose output port

General-purpose I/O ports

Input is hysteresis type containing a noise filter. Although these ports serve

as analog input pins, analog input does not pass through the noise filter for

hysteresis input.

Can be selected as a general-purpose input port or sub-clock generating

is hysteresis type containing a noise filter.

Can be selected as a general-purpose input port or sub-clock generating

is hysteresis type containing a noise filter.

General-purpose output port

This port also serves as a watchdog output pin

General-purpose output port

This port also serves as a PWM output pin for the 8-bit PWM timer.

(see 2.2 for watch dog timer).

1-10

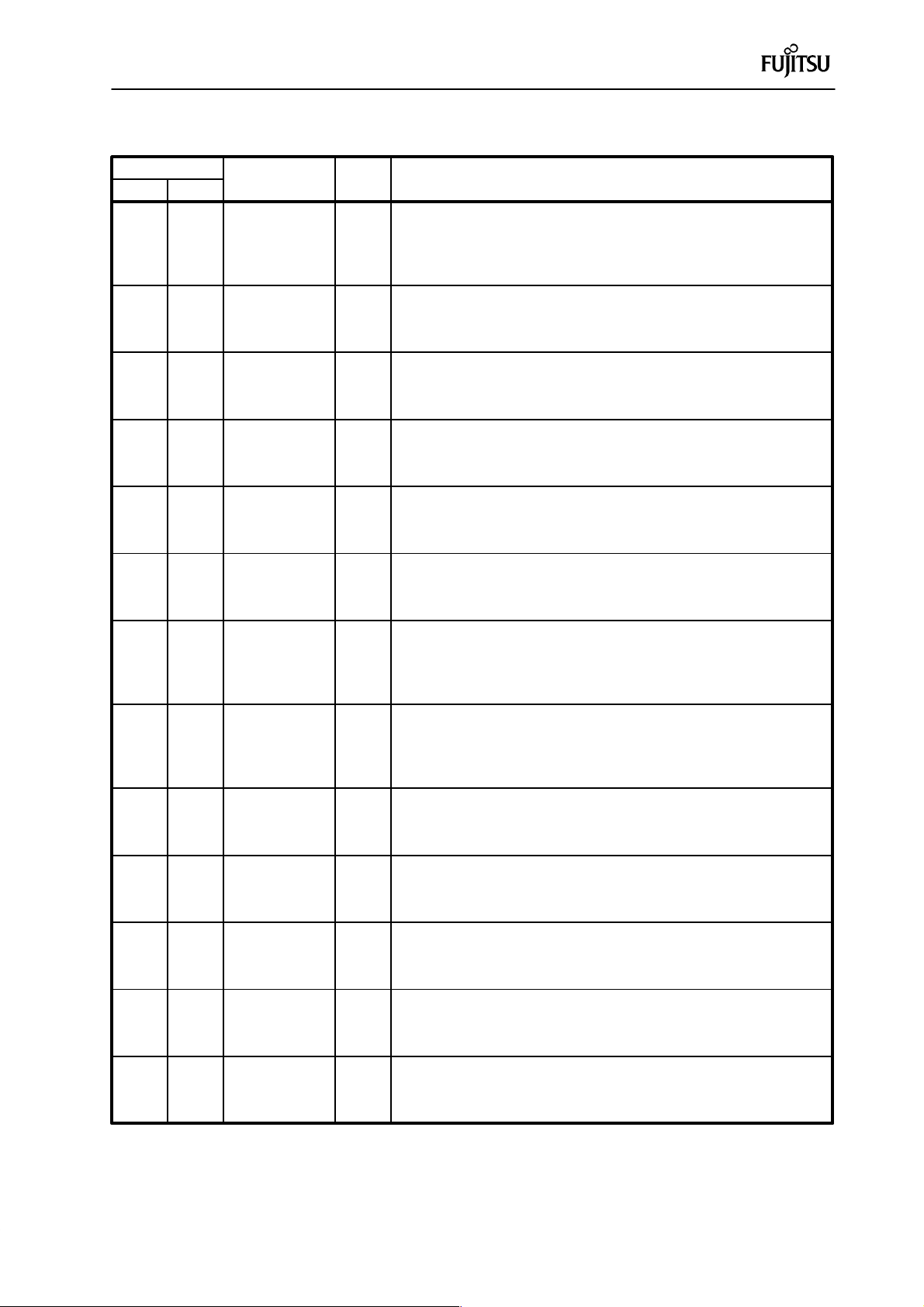

Page 16

GENERAL

Table 1-2 Pin Function Description (Continued)

Pin No.

SDIP

38 31 P37/DTTI I

39 32 P36/PWO1 I Input is hysteresis type containing a noise filter. This port also serves as a

40 33 P35/EC I Input is hysteresis type containing a noise filter . This port also serves as an

41 34 P34/SI I Input is hysteresis type containing a noise filter. This port also serves as an

42 35 P33/SO I Input is hysteresis type containing a noise filter. This port also serves as a

43 36 P32/SCK I Input is hysteresis type containing a noise filter . This port also serves as a

QFP

Pin Name

Circuit

type

Function

General-purpose I/O port

Input is hysteresis type containing a noise filter. When overcurrent is

detected, the external rising or falling edge can be input to inactivate the

12-bit MPG output.

General-purpose I/O port

12-bit MPG output pin.

General-purpose I/O port

external clock input pin for the 8/16-bit timer/counter.

General-purpose I/O port

external clock input pin for the 8-bit timer/counter.

General-purpose I/O port

serial data output pin for the 8-bit serial interface.

General-purpose I/O port

serial transfer clock pin for the 8-bit serial interface.

General-purpose I/O port

44 37 P31/INT1 E

45 38 P30/INT0/TRG I

1 58 BZ H This pin also serves as a P-channel high-withstand-voltage open-drain

19 to 26 12 to 19 P47 to P40 G Two types of microcontrollers are provided: one has a pull-down resistor

11 to 18 4 to 11 P57 to P50 G Two types of microcontrollers are provided: one has a pull-down resistor

2 to 9 59 to 2 P67 to P60 G Two types of microcontrollers are provided: one has a pull-down resistor

10 3 VFD — This pin serves as an NC pin for microcontrollers without a pull-down resistor

Consists of an N-channel open-drain output and hysteresis input containing

a noise filter. This port also serves as an external interrupt pin. Interrupt

input is also hysteresis type containing a noise filter.

General-purpose I/O port

Input is hysteresis type containing a noise filter. This port can also be used

as an external interrupt pin or MPG trigger input pin. Interrupt input is also

hysteresis type containing a noise filter.

Used for buzzer output only

output port.

P-channel high-withstand-voltage open drain output ports for small current

between these ports and the VFD pin, and the other does not.

P-channel high-withstanding-voltage open drain output ports for small current

between these ports and the VFD pin, and the other does not.

P-channel high-withstand-voltage open-drain output ports for large current

between these ports and the VFD pin, and the other does not.

Used for voltage supply connected to pull-down resistors for ports 4, 5 and 6

and the MB89PV140 microcontroller.

1-11

Page 17

GENERAL

Table 1-2 Pin Function Description (Continued)

Pin No.

SDIP

SDIP

64 57 V

32 25 V

63 56 AV

62 55 AV

Pin Name

CC

SS

CC

SS

Circuit

type

Function

— Used for power supply

— Used for power supply (GND)

— Used for power supply for A/D converter

Used for power supply for A/D converter

—

Must be used at same potential as V

SS

pin

1-12

Page 18

GENERAL

Table 1-3 Pin for External-ROM

Pin No.

SDIP QFP

65 66 V

66 67 A12

67 68 A7

68 69 A6

69 70 A5

70 71 A4 Output Address-output pins

71 72 A3

72 73 A2

73 74 A1

74 75 A0

75 77 01

76 78 02 Input Data-input pins

77 79 03

78 80 V

79 82 04

80 83 05

81 84 06 Input Data-input pins

82 85 07

83 86 08

Pin Name

PP

SS

Circuit

type

Output High-level output pin

Output Power (GND) pin

Function

84 87 CE

85 88 A10 Output Address-output pin

86 89 OE

87 91 A11

88 92 A9 Output Address-output pins

89 93 A8

90 94 A13 Output Address-output pin

91 95 A14 Output Address-output pin

92 96 V

CC

Output Chip-enable pin for ROM

A High level is output in the standby mode.

Output Output-enable pin for ROM

A Low level is always output.

Output Power pin for EPROM

1-13

Page 19

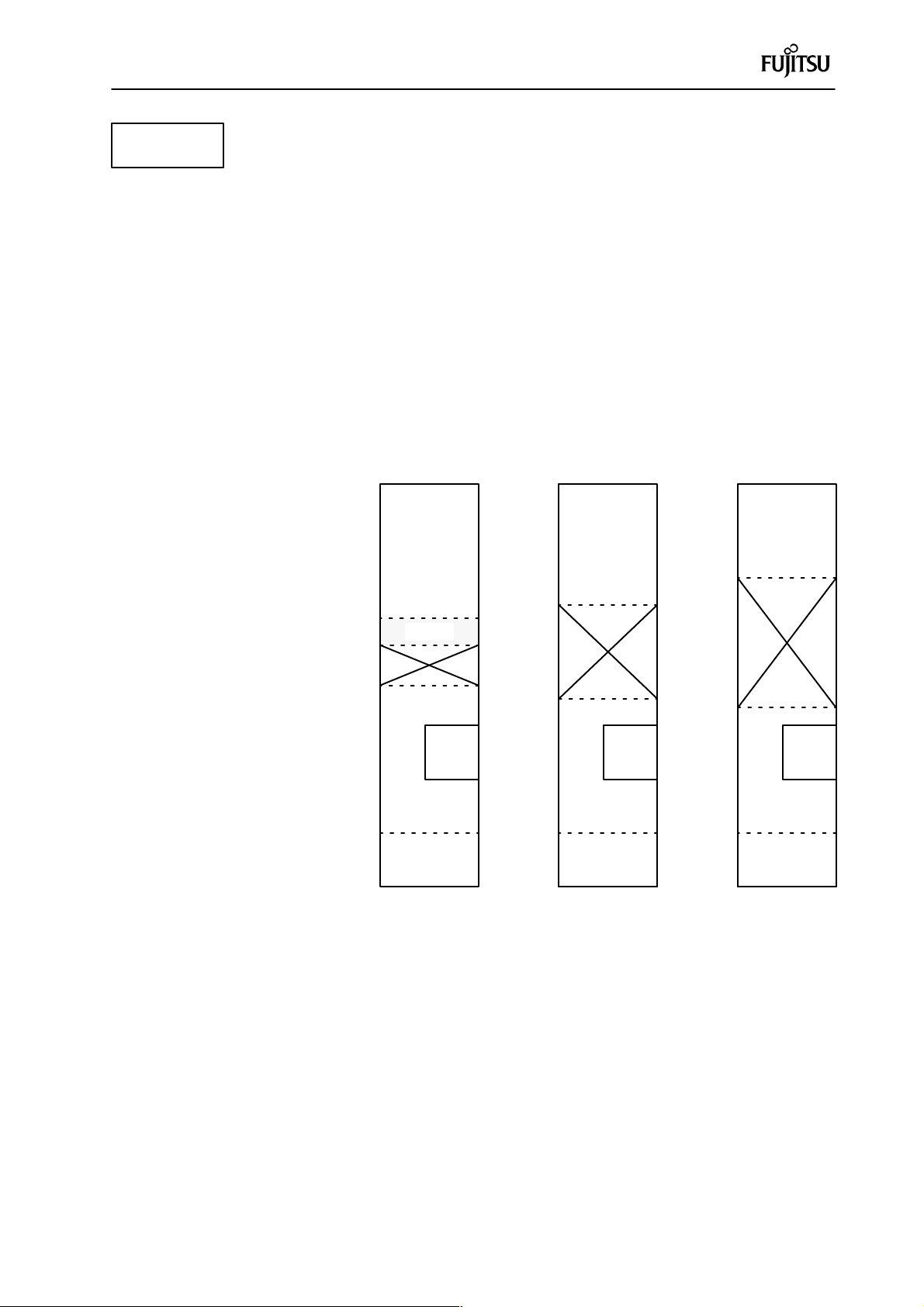

GENERAL

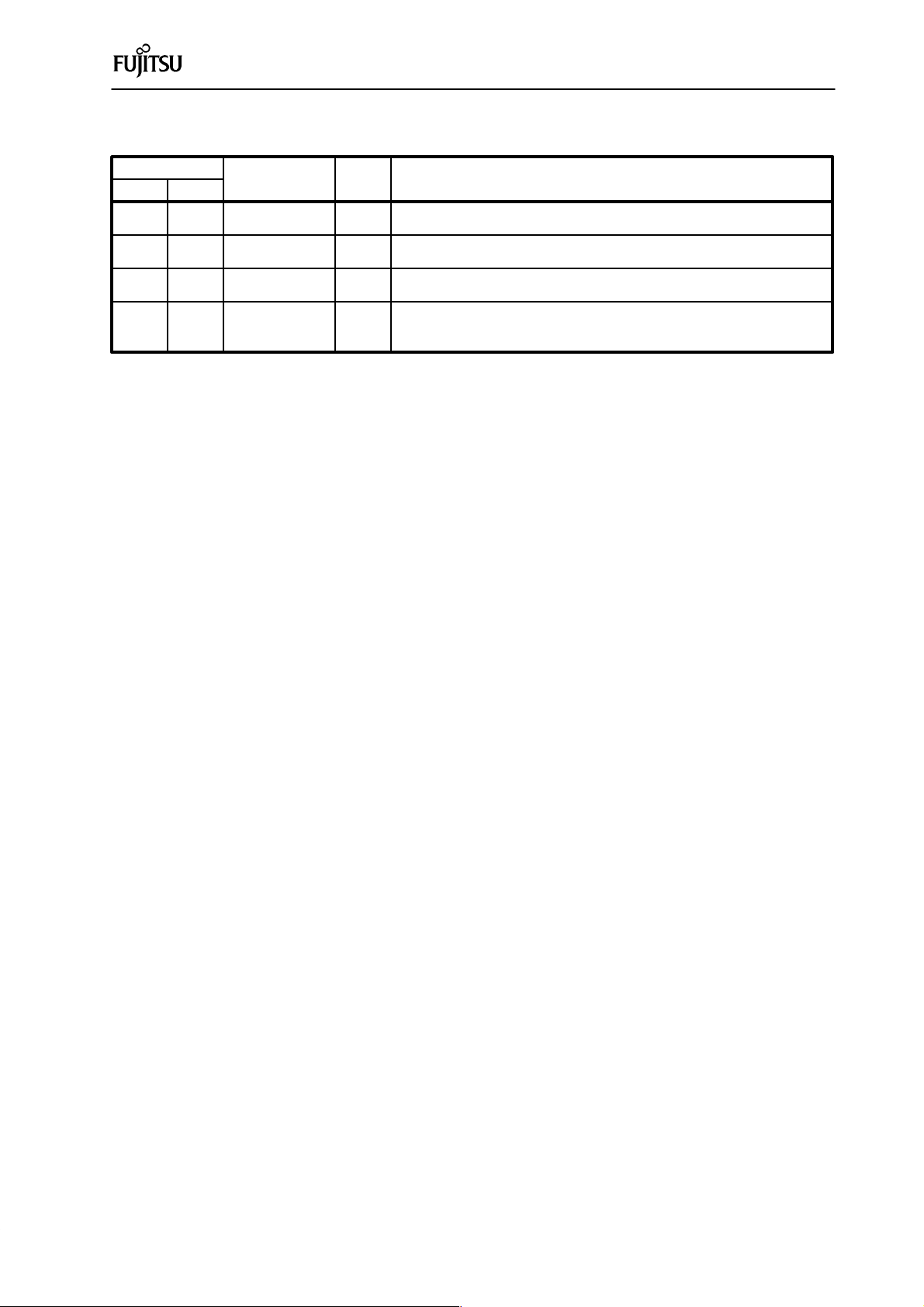

Classification Circuit Remarks

X1

• Feedback resistor: About 2 MΩ

X0

A

Standby control signal

B

R

Pch

• CMOS input

• Output pull-up resistor (Pch): About 50 kΩ (5 V)

• CMOS hysteresis input (with noise filter)

C

Nch

Hysteresis input (with noise filter)

Pch

D

Nch

• CMOS output

• N-ch open drain output

• CMOS hysteresis input (with noise filter)

E

Nch

Hysteresis input (with noise filter)

Pch

Nch

• CMOS output

• CMOS hysteresis input (with noise filter; analog

input excluded)

F

Port

Hysteresis input (with noise filter)

Analog input

Fig. 1.5 Input/Output Circuit Configurations

1-14

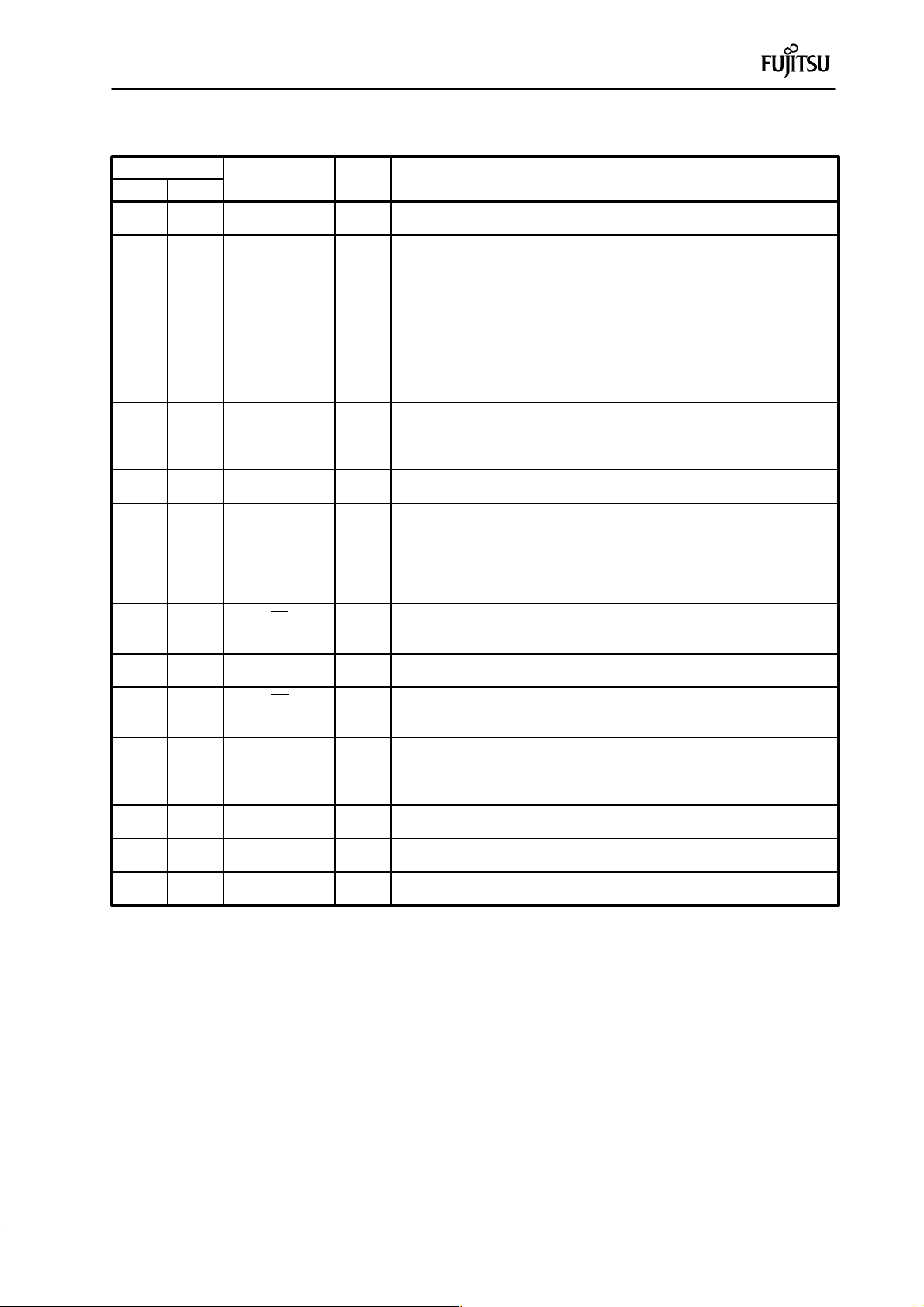

Page 20

GENERAL

Classification Circuit Remarks

R

Pch

G

VFD

Pch

H

Pch

Nch

I

Port

Hysteresis input (with noise filter)

J

Hysteresis input (with noise filter)

Port

• P-channel high-withstand-voltage open-drain

output

• Microcontrollers with and without pull-down resis

tor provided (excluding MB89V140

microcontroller)

• P-channel high-withstand-voltage open-drain

output

• CMOS output

• CMOS hysteresis input (with noise filter)

• The pull-up resistor is optional.

• CMOS hysteresis input (with noise filter)

Fig. 1.5 Input/Output Circuit Configurations (Continued)

1-15

Page 21

1.6 HANDLING DEVICES

(1) Preventing latch-up

GENERAL

Latch-up may occur if a voltage higher than V

than port 40 to 47, or if voltage exceeding the rated value is applied between V

of up to 7 V can be applied to the P31/INT1 pin irrespective of V

or lower than VSS is applied to the input or output pins other

CC

and VSS. However, voltages

CC

.

CC

When latch-up occurs, the supply current increases rapidly , sometimes resulting in overheating and destruction. Therefore, no voltage exceeding the maximum ratings should be used.

(2) Handling unused input pins

Leaving unused input pins open may cause a malfunction. Therefore, these pins should be set to pull-up or

pull-down.

(3) Setting internal connection (IC) pin

Always set IC (internal connections) open.

(4) Variations in supply voltage

Although the specified V

supply voltage operating range is assured, a sudden change in the supply voltage

CC

within the specified range may cause a malfunction. Therefore, the voltage supply to the IC should be kept as

constant as possible. The V

10% of the typical V

value, or the coefficient of excessive variation should be less than 0.1 V/ms. instanta-

CC

ripple (P-P value) at the supply frequency (50 to 60 Hz) should be less than

CC

neous change when the power supply is switched.

(5) Precautions for external clocks

It takes some time for oscillation to stabilize after changing the mode to power-on reset (option selection) and

stop. Consequently, an external clock must be input.

(6) Recommended screening conditions

High-temperature aging is recommended for screening before OPTROM-mounted microcontrollers are

mounted.

Program, verify

High-temperature aging

150C°, 48H

Read Mount

• Writing yield

The test for writing all bits cannot be executed for microcontrollers where the OPTROM microcomputer program is not written. Therefore, the 100% writing yield may not be always assured.

(7) Sequence for application of power and analog inputs to A/D converter

Power supplies (A V

and A VSS) and analog inputs (AN0 to ANB) to the A/D converter should be turned on

CC

after or at the same time the digital power supply (VCC) is turned on.

When the power supplies is turned off, the digital power supply (V

plies (AV

and AVSS) and analog inputs (AN0 to ANB) to the A/D converter are turned off.

CC

) should be turned off and the power sup-

CC

1-16

Page 22

2. HARDWARE CONFIGURATION

2.1 CPU 2-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 MAIN/SUB CLOCK CONTROL BLOCK 2-11. . . . . . . . . .

2.3 INTERRUPT CONTROLLER 2-22. . . . . . . . . . . . . . . . . .

2.4 I/O PORTS 2-25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5 WATCH PRESCALER 2-34. . . . . . . . . . . . . . . . . . . . . . . .

2.6 WATCHDOG TIMER RESET 2-36. . . . . . . . . . . . . . . . . .

2.7 TIME-BASE TIMER 2-41. . . . . . . . . . . . . . . . . . . . . . . . . .

2.8 8-BIT PWM TIMER (TIMER 1) 2-43. . . . . . . . . . . . . . . . .

2.9 8/16-BIT TIMER (TIMER 2 AND TIMER 3) 2-48. . . . . . .

2.10 12-BIT MULTIPUL GENERATOR (MPG, TIMER 4) 2-55

2.11 8-BIT SERIAL I/O 2-70. . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.12 A/D CONVERTER 2-76. . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.13 BUZZER OUTPUT CIRCUIT 2-83. . . . . . . . . . . . . . . . . . .

2.14 EXTERNAL INTERRUPT CIRCUIT 2-85. . . . . . . . . . . . .

Page 23

HARDW ARE CONFIGURATION

CPU

2.1 CPU

This section describes the memory space and register composing CPU

hardware.

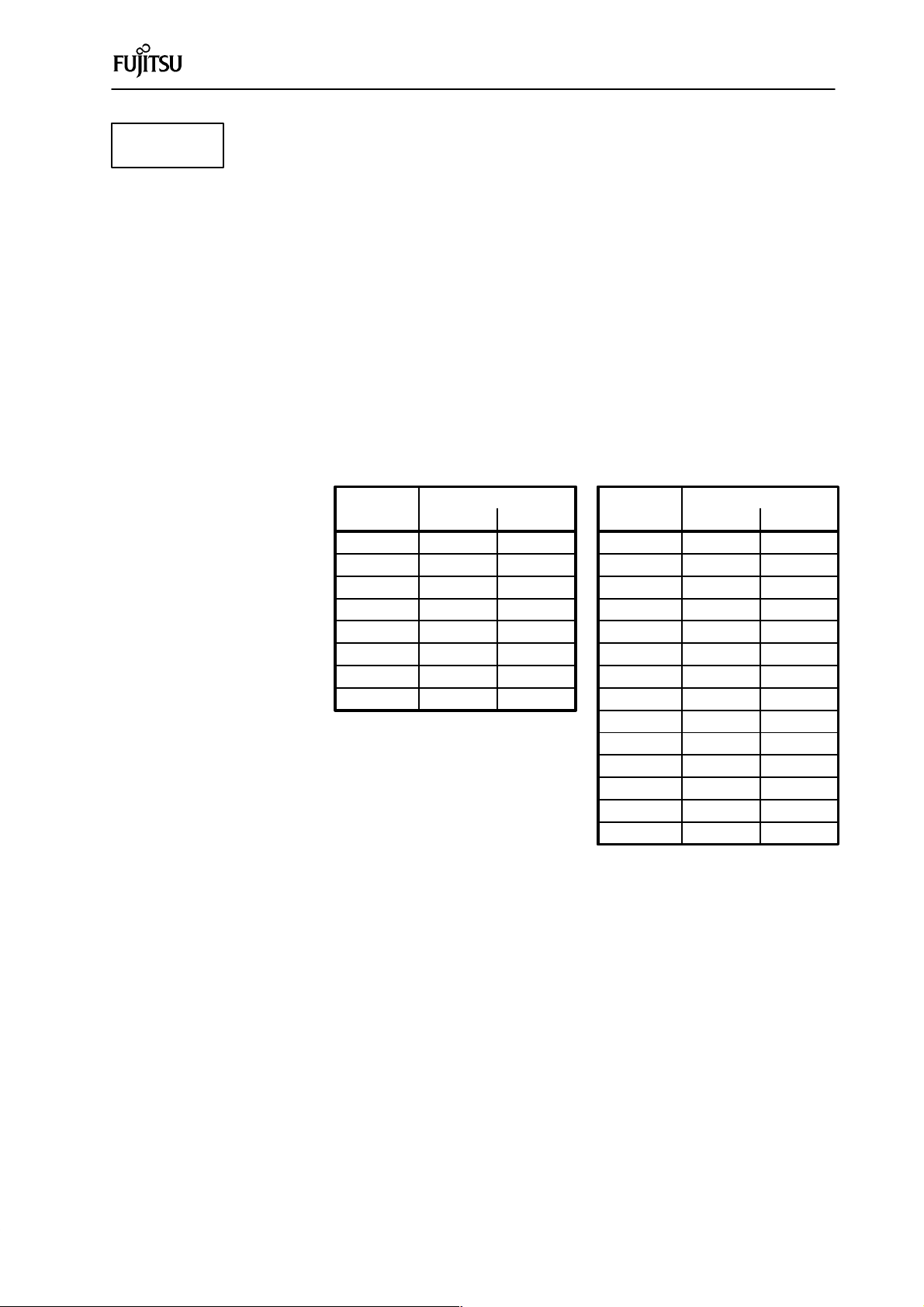

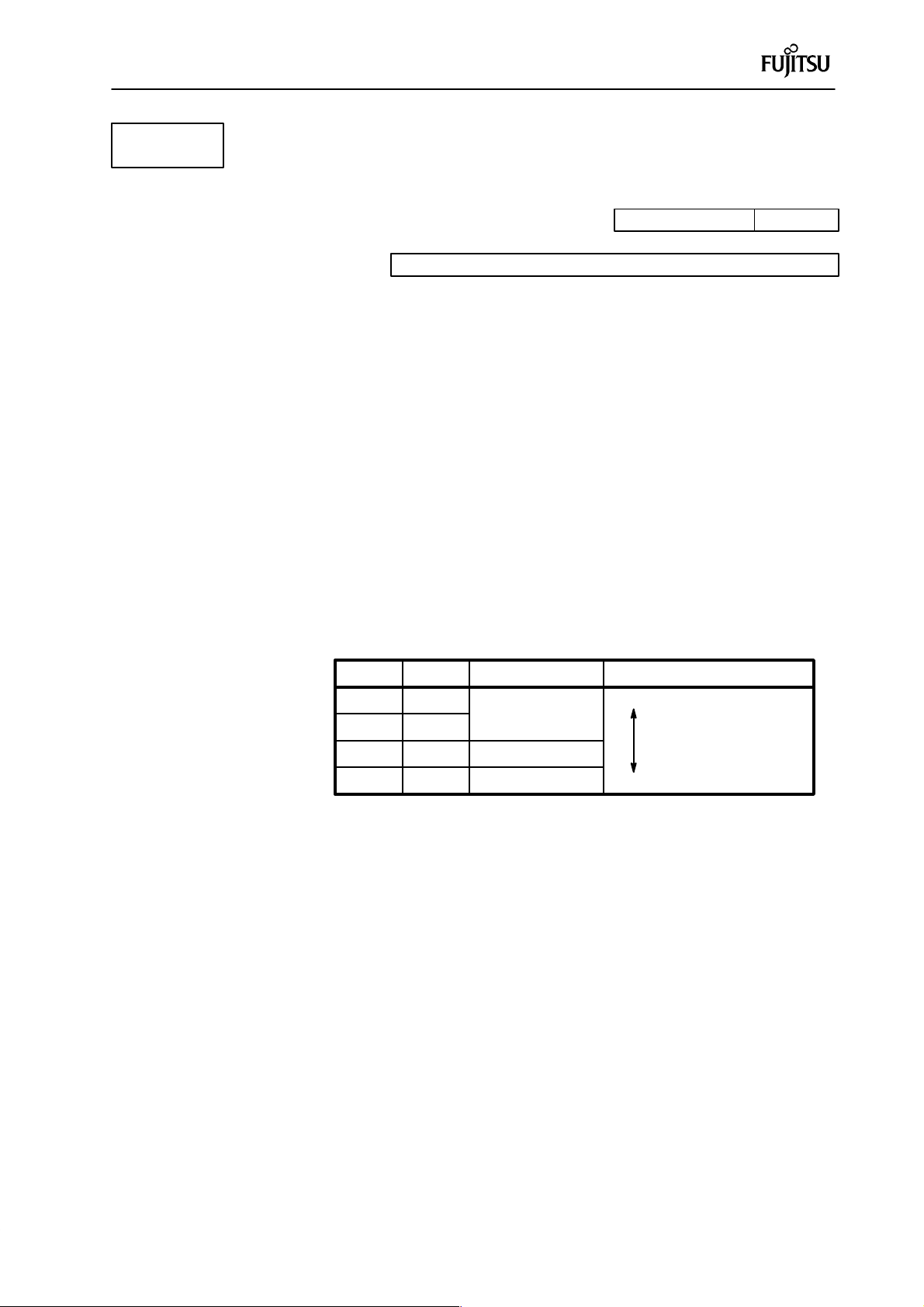

Memory Space

The MB89140 series of microcontrollers have a memory area of 64K bytes.

All I/O, data, and program areas are located in this space. The I/O area is

near the lowest address and the data area is immediately above it. The data

area may be divided into register, stack, and direct-address areas according

to the applications. The program area is located near the highest address

and the tables of interrupt and reset vectors and vector-call instructions are

at the highest address. Figure 2.1 shows the structure of the memory space

for the MB89140 series of microcontrollers.

MB89P147

FFFF

8007

8000

MB89W147

MB89PV140

H

ROM

(External ROM

for MB89PV140

H

H

Note

FFFF

A000

H

H

MB89146

ROM

(24 K)

FFFF

C000

H

H

MB89145

ROM

(16 K)

0480

0200

0100

0080

0000

H

H

Register

H

RAM (1024)

H

I/O

H

0380

0200

0100

0080

0000

H

H

H

H

H

Register

RAM (768)

I/O

0280

0200

0100

0080

0000

H

H

Register

H

RAM (512)

H

I/O

H

Note: To make the user program available between the EPROM-mounted

and mask-ROM-mounted microcontrollers, no user program should

be written at the option EPROM area between 8000

to 8006H (see

H

APPENDIX 2 for details).

Fig. 2.1 Memory Space of MB89140 Series of Microcontrollers

2-3

Page 24

HARDW ARE CONFIGURATION

CPU

• I/O area

This area is where various resources such as control and data registers are

located. The memory map for the I/O area is given in APPENDIX A.

• RAM area

This area is where the static RAM is located. Addresses from 0100

are also used as the general-purpose register area.

01FF

H

to

H

• ROM area

This area is where the internal ROM is located. Addresses from FFC0

are also used for the table of reset and vector-call instructions.

FFFF

H

to

H

T able 2-1 shows the correspondence between each interrupt number or reset and the table addresses to be referenced for the MB89145 series of microcontrollers.

Table 2-1 Table of Reset and Interrupt Vectors

CALLV #0

CALLV #1

CALLV #2

CALLV #3

CALLV #4

CALLV #5

CALLV #6

CALLV #7

Table address

Upper data Lower data

FFC0

FFC2

FFC4

FFC6

FFC8

FFCA

FFCC

FFCE

H

H

H

H

H

FFC1

H

FFC3

H

FFC5

H

FFC7

H

FFC9

H

FFCB

H

H

H

FFCD

FFCF

H

H

H

Interrupt #11

Interrupt #10

Interrupt #9

Interrupt #8

Interrupt #7

Interrupt #6

Interrupt #5

Interrupt #4

Interrupt #3

Interrupt #2

Interrupt #1

Interrupt #0

Reset mode

Reset vector

Note: FFFCH is already reserved.

Table address

Upper data Lower data

FFE4

FFE6

FFE8

FFEA

FFEC

FFEE

FFF0

FFF2

FFF4

FFF6

FFF8

FFFA

–––––

FFFE

H

H

H

H

H

H

H

H

H

H

H

H

H

FFE5

FFE7

FFE9

FFEB

FFED

FFEF

FFF1

FFF3

FFF5

FFF7

FFF9

FFFB

FFFD

FFFF

H

H

H

H

H

H

H

H

H

H

H

H

H

H

2-4

Page 25

HARDW ARE CONFIGURATION

CPU

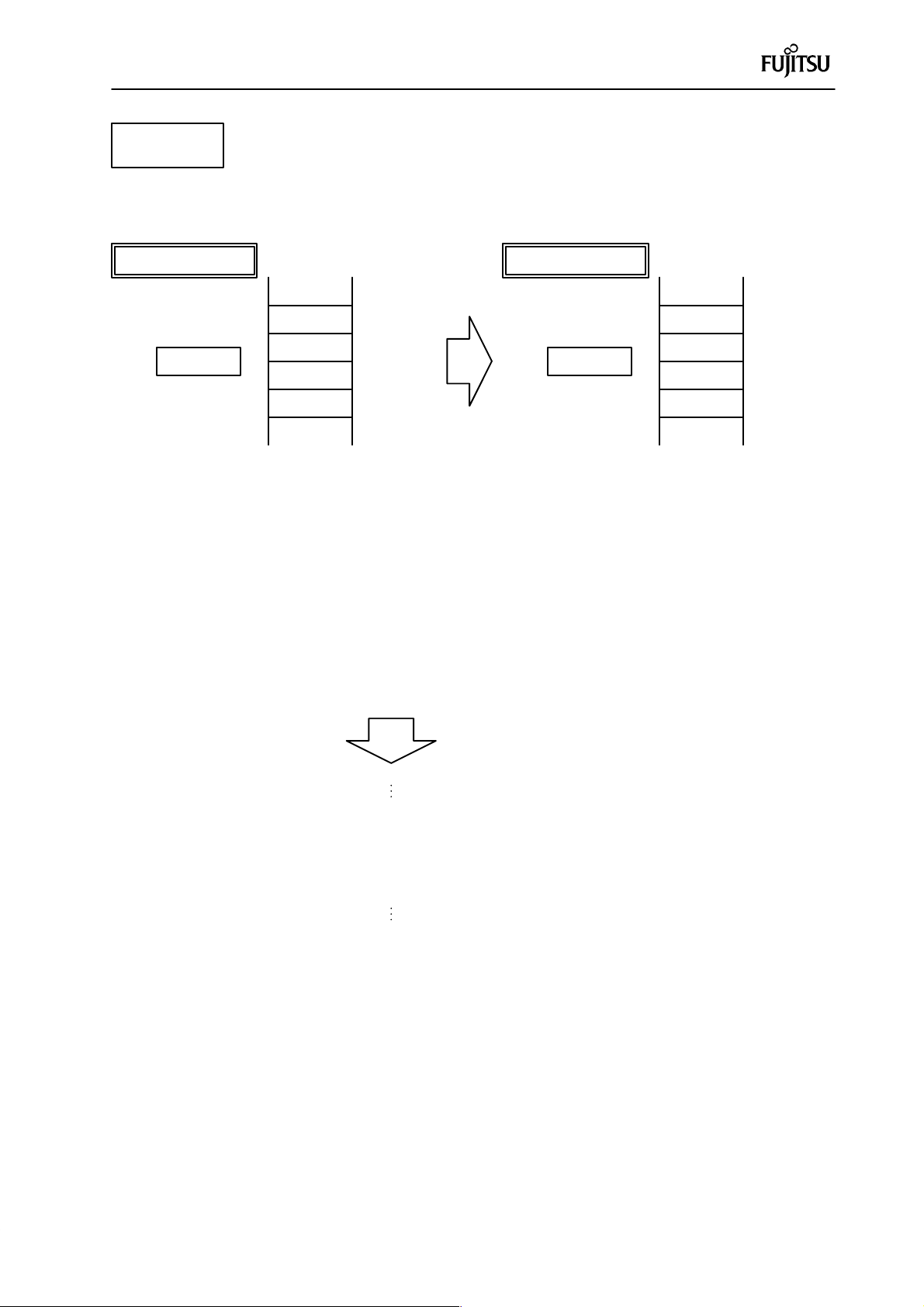

Before execution

A

1234

H

Memory

Arrangement of 16-bit Data in Memory

When the MB89140 series of microcontrollers handle 16-bit data, the data

written at the lower address is treated as the upper data and that written at

the next address is treated as the lower data as shown in Figure 2.2.

After execution

Memory

34

H

12

H

ABCF

ABCE

ABCD

ABCC

H

H

H

H

ABCF

ABCE

ABCD

ABCC

MOVW ABCDH, A

H

H

H

H

1234

A

H

Fig. 2.2 Arrangement of 16-bit Data in Memory

This is the same as when 16-bits are specified by the operand during execution of an instruction. Bits closer to the OP code are treated as the upper

byte and those next to it are treated as the lower byte. This is also the same

when the memory address or 16-bit immediate data is specified by the operand.

[Example]

MOV A, 5678

MOV A, #1234

H

H

; Extended address

; 16-bit immediate data

Assemble

XXXXH XX XX

60 56 78 ; Extended address

XXXX

H

XXXX

E4 12 34 ; 16-bit immediate data

H

XXXXH XX

Fig. 2.3 Arrangement of 16-bit Data during Execution of Instruction

Data saved in the stack by an interrupt is also treated in the same manner.

2-5

Page 26

HARDW ARE CONFIGURATION

CPU

Internal Registers in CPU

The MB89140 series of microcontrollers have dedicated registers in the

CPU and general-purpose registers in memory.

• Program counter (PC) 16-bit long register indicating location

where instructions stored

• Accumulator (A) 16-bit long register where results of opera-

tions stored temporarily; the lower byte is

used to execute 8-bit data processing

instructions.

• T emporary accumulator (T) 16-bit long register; the operations are per-

formed between this register and the accumulator. The lower one byte is used to

execute 8-bit data processing instructions

• Stack pointer (SP) 16-bit long register indicating stack area

• Processor status (PS) 16-bit long register where register pointers

and condition codes stored

• Index register (IX) 16-bit long register for index modification

• Extra pointer (EP) 16-bit long register for memory addressing

16 bits

P C

A

T

IX

EP

SP

PS

Program counter

Accumulator

Temporary accumulator

Index register

Extra pointer

Stack pointer

Processor status

The 16 bits of the processor status (PS) can be divided into 8 upper bits for a

register bank pointer (RP) and 8 lower bits for a condition code register

(CCR). (See Figure 2.4.)

1514131211109876543210

PS RP

Vacant Vacant Vacant H I N Z V C

IL1, 0

RP CCR

Fig. 2.4 Structure of Processor Status

2-6

Page 27

HARDW ARE CONFIGURATION

CPU

The RP indicates the address of the current register bank and the contents

of the RP; the real addresses are translated as shown in Figure 2.5.

Lower bits of OP code

Source

address

R P

’0’ ’0’ ’0’ ’0’ ’0’ ’0’ ’0’ ’1’ R4 R3 R2 R1 R0 b2 b1 b0

↓↓↓↓↓↓↓↓↓↓↓↓↓↓↓↓

A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

Fig. 2.5 Rule for Translating Real Addresses at

General-purpose Register Area

The CCR has bits indicating the results of operations and transfer data contents, and bits controlling the CPU operation when an interrupt occurs.

• H-flag H-flag is set when a carry or a borrow out of bit 3 into bit 4

is generated as a result of operations; it is cleared in other

cases. This flag is used for decimal-correction instructions.

• I-flag An interrupt is enabled when this flag is 1 and is disabled

when it is 0. The I-flag is 0 at reset.

• IL1 and IL0 These bits indicate the level of the currently-enabled inter-

rupt. The CPU executes interrupt processing only when

an interrupt with a value smaller than the value indicated

by this bit is requested.

IL1 IL0 Interrupt level High and low

0

0

High

1

0

1

1

1

0

1

2

3

Low = No interrupt

• N-flag The N-flag is set when the most significant bit is 1 as a

result of operations; it is cleared when the MSB is 0.

• Z-flag Z-flag is set when the bit is 0 as a result of operations; it is

cleared in other cases.

• V-flag V-flag is set when a two’ s complement overflow occurs as

a result of operations; it is reset when an overflow does

not occur.

• C-flag C-flag is set when a carry or a borrow out of bit 7 is gener-

ated as a result of operations; it is cleared in other cases.

When the shift instruction is executed, the value of the

C-flag is shifted out.

2-7

Page 28

HARDW ARE CONFIGURATION

CPU

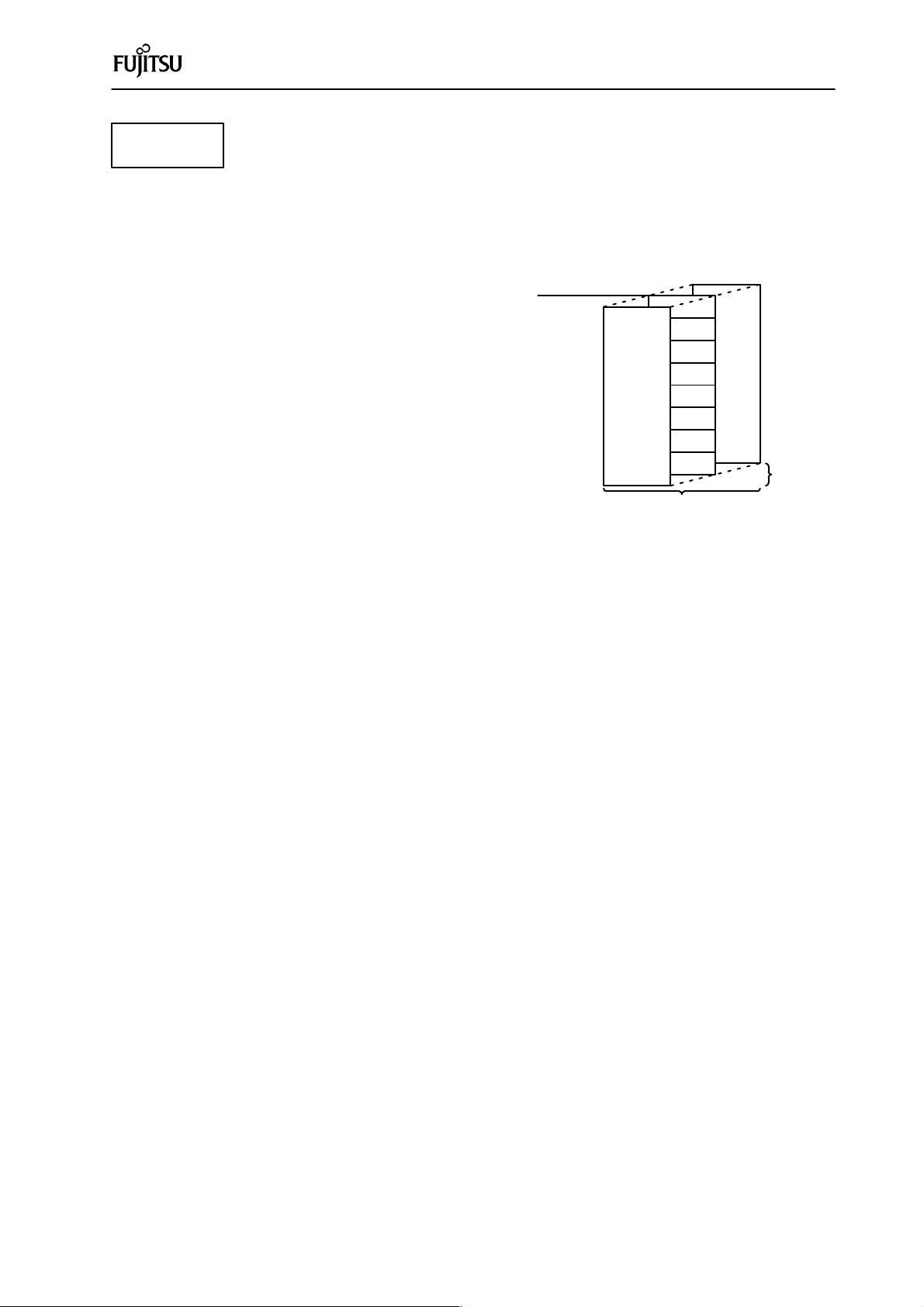

• General-purpose registers

General-purpose registers are 8-bit long registers for storing data.

The 8-bit long general-purpose registers are in the register banks in

memory . One bank has eight registers and up to 32 banks are available for

the MB89140 series of microcontrollers, respectively. The register bank

pointer (RP) indicates the currently-used bank.

Address = 0100H + 8 (RP)

*

Memory area

Fig. 2.6 Register Bank Configuration

R0

R1

R2

R3

R4

R5

R6

R7

32 banks

2-8

Page 29

HARDW ARE CONFIGURATION

CPU

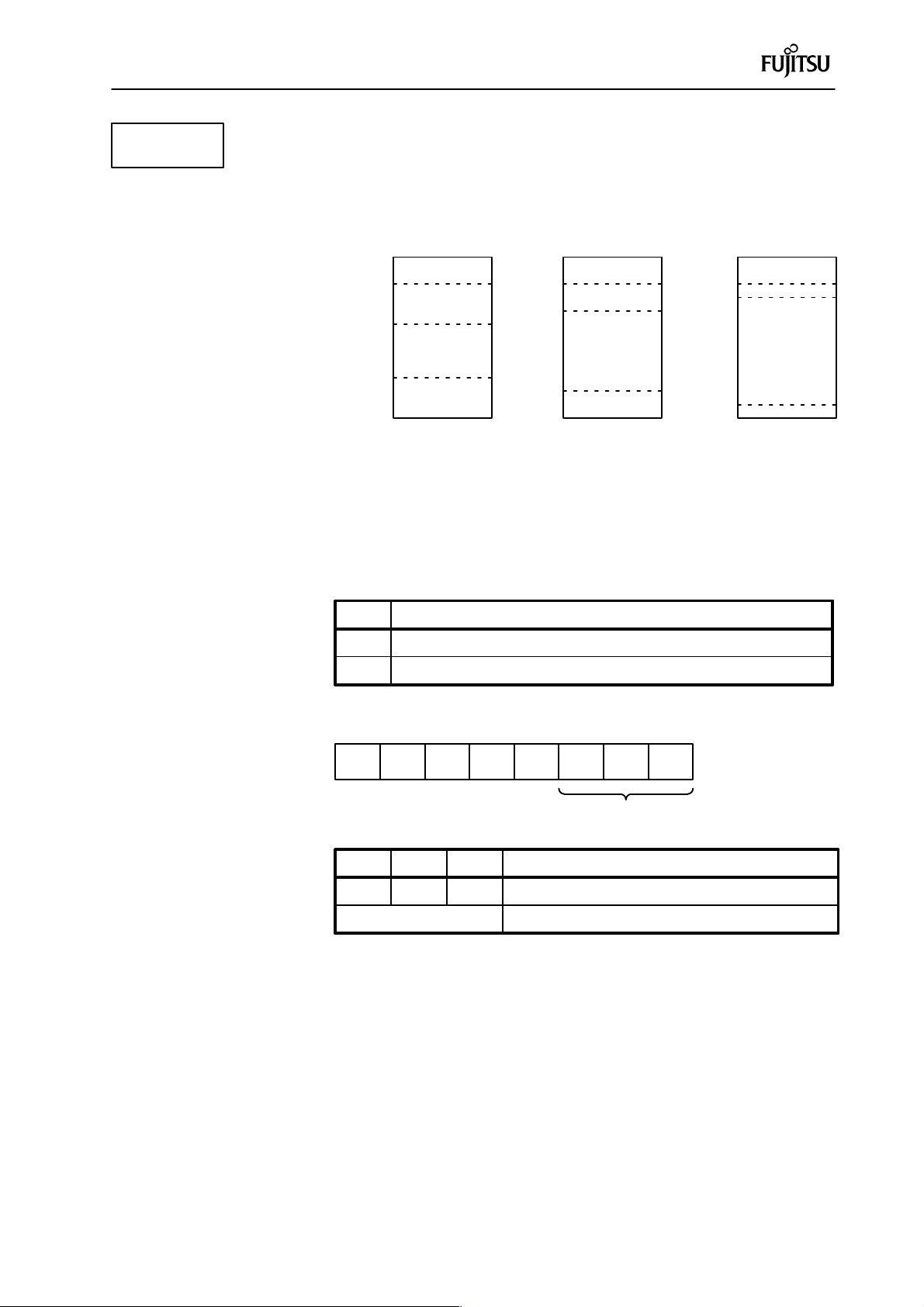

Operation Modes

The MB89140 series of microcontrollers is used in the single-chip mode.

The memory map for each mode is as follows:

→

H

→

H

→

H

→

H

→

H

MB89PV140

Internal I/O

RAM

Inhibited

Internal ROM

Address

0000

H

0080

H

0380

H

A000

H

FFFF

H

→

→

→

→

→

MB89146

Internal I/O

RAM

Inhibited

Internal ROM

Address

0000

H

0080

H

0280

H

C000

H

FFFF

H

→

→

→

→

→

MB89145

Internal I/O

RAM

Inhibited

Internal ROM

Address

0000

0080

0480

8000

FFFF

Fig. 2.7 Memory Map in Various Modes

The mode that the device enters depends on the states of the device-mode

pins and the contents of the mode data fetched during the reset sequence.

The relationship between the states and operations of the device-mode pins

is shown below.

MODA Description

0

1

Reset vectors are read from the internal ROM.

Write mode for products containing EPROM.

The mode data should be set as follows:

T2 T1 T0

Mode bits

T2 T1 Operation

0

0

Other than above

T0

0

Select single-chip mode.

Reserved. Do not set.

: Reserved; Specify 0.

2-9

Page 30

HARDW ARE CONFIGURATION

CPU

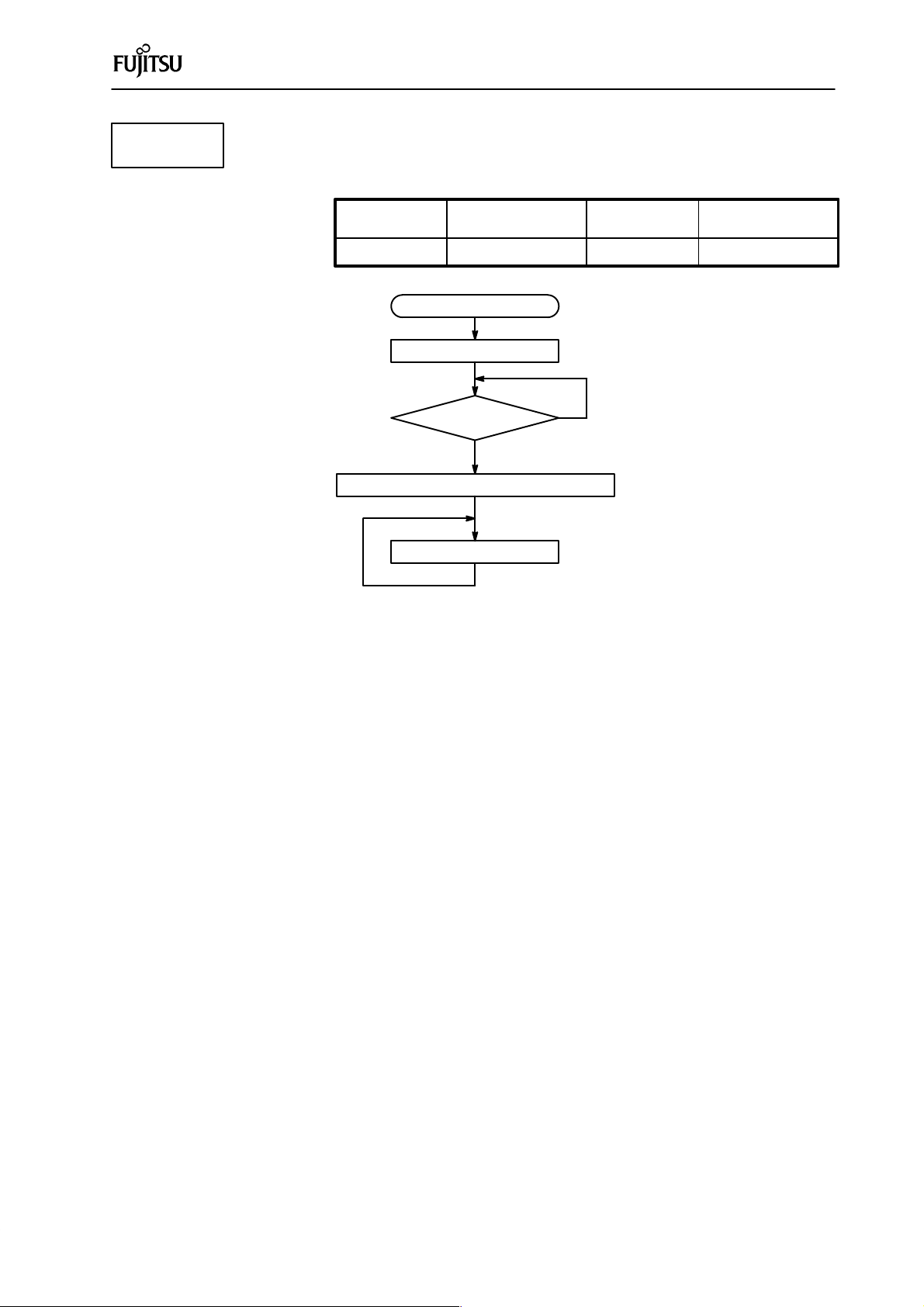

As shown in the flowchart below, the single-chip mode is set according to the

status of the device mode pins and the mode data fetched during the reset

sequence.

Setting

procedure

Fetch programs from internal ROM.

Mode selected Mode pin Mode data

Single-chip mode(1)→(2) 0 XXXXX000

Power-on

Device mode pin

No

Reset cancel?

Ye s

User ROM

(1) Set 0 at the MODA pin.

(2) All pin ports fetch internal

mode data and reset vectors.

2-10

Page 31

HARDW ARE CONFIGURATION

MAIN/SUBCLOCK

CONTROL BLOCK

Main clock

pulse generator

Subclock

pulse generator

WT1

WT0

2.2 MAIN/SUB CLOCK CONTROL BLOCK

This block controls the standby operation, oscillation stabilization time,

software reset, and clock switching.

Block Diagram

CS0 CS1 SCS STP SLP TMD SPLSCM

Prescaler

1/2

1/4

1/8

1/32

Selector

Selector

Clock

control

CPU operation clock

Resource operation clock

Clock for time-base timer

Clock for watch prescaler

Pin state

Clock

specification

Watch

Sleep

Stop

HC1

From timebase timer

HC2

HC3

Selector

HC4

LC from watch

Ready signal

Hold request signal

Hold acknowledge signal

Stop release signal

Fig. 2.8 Machine Clock Control Block Diagram

Register List

Main/sub clock control block consists of standby control register (STBC)

and system clock control register (SYCC).

8 bit

Address: 0007

Address: 0008

H

H

SYCC

STBC

R/W System clock control register

R/W Standby control register

2-1 1

Page 32

HARDW ARE CONFIGURATION

MAIN/SUBCLOCK

CONTROL BLOCK

Address: 0007

Address: 0008

H

H

SYCC

STBC

Description of Registers

The detail of each register is described below.

(1) Standby-control register (STBC)

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Address: 0008

STP SLP SPL RST TMD — — —

H

(W) (W) (R/W) (W) (W)

Initial value

00010XXX

B

[Bit 7] STP: Stop bit

This bit is used to specify switching CPU to the stop mode.

0

1

No operation

Stop mode

This bit is cleared at reset or stop cancellation.

0 is always read when this bit is read.

[Bit 6] SLP: Sleep bit

This bit is used to specify switching the CPU and resources to the sleep

mode.

0

1

No operation

Sleep mode

This bit is cleared at reset, sleep or stop cancellation.

0 is always read when this bit is read.

[Bit 5] SPL: Pin state specifying bit

This bit is used to specify the external pin state in the stop mode.

0

1

Holds state and level immediately before stop mode

High impedance

This bit is cleared at resetting.

[Bit 4] RST: Software reset bit

This bit is used to specify the software reset.

0

1

Generates 16-cycle reset signal

No operation

1 is always read when this bit is read.

Note: If a software reset is performed during operation in a submode, an

oscillation stabilization period is required to switch to the main mode.

Therefore, a reset signal is output during the oscillation stabilization

period.

2-12

Page 33

HARDW ARE CONFIGURATION

MAIN/SUBCLOCK

CONTROL BLOCK

Address: 0007

Address: 0008

H

H

SYCC

STBC

[Bit 3] TMD: Watch bit

This bit is used to specify switching to the watch mode.

0

1

No operation

Watch mode

Writing at this bit is possible only in the submode (SCS = 0). 0 is always read

when this bit is read. This bit is cleared at an interrupt request or reset.

(2) System clock control register (SYCC)

This register controls the clock for operating the CPU and resources.

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Address: 0007

SCM — — WT1 WT0 SCS CS1 CS0

H

(R) (R/W) (R/W) (R/W) (R/W) (R/W)

Initial value

X--MM100

B

[Bit 7] SCM: System clock monitor bit

This bit is used to check whether the current system clock is the main clock

or subclock.

Subclock (Main clock is stopping or oscillation of main clock stablizing)

0

Main clock

1

[Bits 4 and Bit 3] WT1 and WT0: Oscillation stabilization time select bits

These bit are used to select the oscillation stabilization wait time of the main

clock.

WT1 WT0 Oscillation stabilization time

1

1

0

0

1

0

1

0

Approximate 218/f

Approximate 217/f

Approximate 214/f

Approximate 24/f

CH

CH

CH

CH

If the main mode is specified by the system clock select bit (SCS), the mode

switches to main mode after the selected wait time has elapsed.

The oscillation stabilization time after resetting is determined by the initial

value.

This bit should not be rewritten during oscillation stabilization or concurrently with switching of the sub-clock to the main clock.

Oscillation stabilization time

with 8 MHz source clock

32.8 ms

16.4 ms

2.0 ms

0ms

f

: Oscillation frequency of main clock

CH

The oscillation stabilization time for the main clock is generated by dividing

the frequency of the main clock. Since the oscillation cycle is unstable immediately after oscillation starts, the above times should be used as the

standard.

2-13

Page 34

HARDW ARE CONFIGURATION

MAIN/SUBCLOCK

CONTROL BLOCK

[Bit 2] SCS: System clock select bit

This bit is used to select the system clock mode.

Selects subclock (32.768 kHz) mode

0

Selects main clock (8 MHz) mode

1

[Bits 1 and 0] CS1 and CS0: System clock select bits (Gear function)

If the main mode is specified by the system clock select bit (SCS), the system clock is as given in the table below.

CS1 CS0 Instruction cycle

0

0

1

1

0

1

0

1

64/f

16/f

8/f

4/f

CH

CH

CH

CH

Instruction execution time

at 8 MHz source clock

8.0 µs

2.0 µs

1.0 µs

0.5 µs

f

: frequency of main clock

CH

2-14

Page 35

HARDW ARE CONFIGURATION

MAIN/SUBCLOCK

CONTROL BLOCK

Clock

mode of

CPU

Main mode

(CS1,

CS0)

(1, 1) SLEEP Oscillates 32.768 kHz

(1, 0) SLEEP Oscillates 32.768 kHz

(0, 1) SLEEP Oscillates 32.768 kHz

Description of Operation

Main/sub clock block has normal and low-power consumption mode. The

low-power consumption mode are described below.

(1) Low-power consumption mode

This chip has three operation modes. The sleep mode, and stop mode in the

table below reduce the power consumption. In the main mode, four system

clocks can be selected according to the system condition to minimize power

consumption.

Table 2-2 Operating State of Low-power Consumption Modes

State

Clock pulse

mode

Main Sub

RUN 4 MHz

Oscillates 4 MHz 4 MHz

STOP Stops Stops Stops External interrupt

RUN 2.0 MHz

Oscillates 4 MHz 2.0 MHz

STOP Stops Stops Stops External interrupt

RUN 1.0 MHz

Oscillates 4 MHz 1.0 MHz

STOP Stops Stops Stops External interrupt

Each operating clock pulse

(3 MHz main clock)

CPU

Stops

Stops

Stops

Time-base

timer

Each

resource

Wake-up source

in each mode

Clock

Various interrupt

requests

Various interrupt

requests

Various interrupt

requests

RUN 250 kHz

Oscillates 4 MHz 250 kHz

(0, 0) SLEEP Oscillates 32.768 kHz

Stops

STOP Stops Stops Stops External interrupt

RUN 32.768 kHz

Oscillates 32.768 kHz 32.768 kHz

Submode — SLEEP Stops Stops

Stops

STOP Stops Stops Stops External interrupt

Watch Stops Oscillates Stops Stops Stops 32.768 kHz Watch external

mode interrupt

Various interrupt

requests

Various interrupt

requests

• The submode stops oscillation of the main clock.

• The SLEEP mode stops only the operating clock pulse of the CPU; other

operations are continued.

• The W ATCH mode stops the functions of all chips other than the special

resources.

• The STOP state stops the oscillation. Data can be held with the lowest

power consumption in this mode.

2-15

Page 36

HARDW ARE CONFIGURATION

MAIN/SUBCLOCK

CONTROL BLOCK

(a) WATCH mode

• Switching to WATCH mode

– Writing 1 at the TMD bit of the STBC register switches the mode to

WATCH mode. Writing is invalid if 1 is set at the SCS bit (bit 2) of the

SYCC register.

– The WA TCH mode stops all chip functions except the watch prescaler ,

external interrupt, and wake-up functions. Therefore, data can be held

with the lowest power consumption.

– The input/output pins and output pins during the WATCH mode can be

controlled by the SPL bit of the STBC register so that they are held in

the state immediately before entering the WA TCH mode or so that they

enter the high-impedance state.

– If an interrupt is requested when 1 is written at the TMD bit , instruction

execution continues without switching to the WATCH mode.

– In the WA TCH mode, the values of registers and RAM immediately be-

fore entering the WATCH mode are held.

• Canceling WATCH mode

– The WATCH mode is canceled by inputting the reset signal and re-

questing an interrupt.

– When the reset signal is input during the WATCH mode, the CPU is

switched to the reset state and the WATCH mode is canceled.

– When an interrupt higher than level 11 is requested from a resource

during the WATCH mode, the WATCH mode is canceled.

– When the I flag and IL bit are enabled like an ordinary interrupt after

canceling, the CPU executes the interrupt processing. When they are

disabled, the CPU executes the interrupt processing from the instruction next to the one before entering the WATCH mode.

– If the WATCH mode is canceled by inputting the reset signal, the CPU

is switched to the oscillation stabilization wait state. Therefore, the reset sequence is not executed unless the oscillation stabilization time is

elapsed. The oscillation stabilization time will be that of the main clock

selected by the WT1 and WT0 bits. However, when Power-on Reset is

not specified by the mask option, the CPU is not switched to the oscillation stabilization wait state, even if the WATCH mode is canceled by

inputting the reset signal.

(b) SLEEP mode

• Switching to Sleep mode

– Writing 1 at the SLP bit (bit 6) of the STBC register switches the mode to

SLEEP mode.

– The SLEEP mode is the mode to stop clock pulse operating the CPU;

only the CPU stops and the resources continue to operate.

– If an interrupt is requested when 1 is written at the SLP bit (bit 6),

instruction execution continues without switching to the SLEEP mode.

– In the SLEEP mode, the values of registers and RAM immediately be-

fore entering the SLEEP mode are held.

2-16

Page 37

HARDW ARE CONFIGURATION

MAIN/SUBCLOCK

CONTROL BLOCK

• Canceling SLEEP mode

– The SLEEP mode is canceled by inputting the reset signal and re-

questing an interrupt.

– When the reset signal is input during the SLEEP mode, the CPU is

switched to the reset state and the SLEEP mode is canceled.

– When an interrupt level higher than 11 is requested from a resource

during the SLEEP mode, the SLEEP mode is canceled.

– When the I flag and IL bit are enabled like an ordinary interrupt after

canceling, the CPU executes the interrupt processing. When they are

disabled, the CPU executes the interrupt processing from the instruction next to the one before entering the SLEEP mode.

(c) STOP mode

• Switching to STOP mode

– Writing 1 at the STP bit (bit 7) of the STBC register switches the mode

to STOP mode.

– The STOP mode varies when the main clock is operating and when the

subclock is operating.

When the main clock is operating: The main clock stops but the sub-

clock does not stop. All chip functions except the watch function stop.

However, no watch interrupt can be accepted.

When subclock is operating: Both the main clock and subclock stop. All

chip functions stop.

– The input/output pins and output pins during the STOP mode can be

controlled by the SPL bit (bit 5) of the STBC register so that they are

held in the mode immediately before entering the STOP mode, or so

that they enter in the high-impedance state.

– If an interrupt is requested when 1 is written at the STP bit (bit 7),

instruction execution continues without switching to the STOP mode.

– In the STOP mode, the values of registers and RAM immediately be-

fore entering the STOP mode are held.

• Canceling STOP mode

– The STOP mode is canceled either by inputting the reset signal or by

requesting an interrupt.

– When the reset signal is input during the STOP mode, the CPU is

switched to the reset state and the STOP mode is canceled.

– When an interrupt higher than level 11 is requested from the external

interrupt circuit during the STOP mode, the STOP mode is canceled.

– When the I flag and IL bit are enabled like an ordinary interrupt after

canceling, the CPU executes the interrupt processing. When they are

disabled, the CPU executes the interrupt processing from the instruction next to the one before entering the STOP mode.

– Four oscillation stabilization times of the main clock can be selected by

the WT1 and WT0 bits. The oscillation stabilization time of the subclock is fixed (at 215/fCH — fCH: frequency of subclock).

2-17

Page 38

HARDW ARE CONFIGURATION

MAIN/SUBCLOCK

CONTROL BLOCK

– If the STOP mode is canceled by inputting the reset signal, the CPU is

switched to the oscillation stabilization wait state. Therefore, the reset

sequence is not executed unless the oscillation stabilization time is

elapsed. The oscillation stabilization time corresponds to the oscillation

stabilization time of the main clock selected by the WT1 and WT0 bits.

However, when Power-on Reset is not specified by the mask option, the

CPU is not switched to the oscillation stabilization wait state even if the

STOP mode is canceled by inputting the reset signal.

(2) Setting low power consumption mode

STBC Register

STP (Bit 7)

0 0 0 Normal

001 WATCH

0 1 0 SLEEP

1 0 0 STOP

1 ×× Disable

Note: When the mode is switched from the subclock mode to the main clock

mode, do not set the Stop, Sleep, and Watch modes. If the SCS bit of

the SYCC register is rewritten from 0 to 1, set the above modes after

the SCM bit of the SYCC register has been set to 1.

SLP (Bit 6) TMD (Bit 3)

Mode

2-18

Page 39

HARDW ARE CONFIGURATION

MAIN/SUBCLOCK

CONTROL BLOCK

Main STOP

Main stop

Sub oscillate

(8)

Oscillation stabilization

waiting of main clock

(1) (2)

(3)

(3) State transition diagram at low power consumption mode

(27)

(7)

(18)

Main SLEEP

Main oscillate

Sub oscillate

(5)

(4)

Main RUN

Main oscillate

Sub oscillate

(17)

Sub RUN

Oscillation stabilization

waiting of main clock

(9)

(6)

(10)

Sub SLEEP

Main stop

Sub oscillate

(28)

(29)

(16)

(15)

Sub RUN

Main stop

Sub oscillate

(11)

(12)

(19)

Oscillation stabilization

waiting of subclock

(20)

(14)

(24)

WATCH

Main stop

Sub oscillate

(25)

Sub STOP

Main stop

Sub stop

(21)

(13)

(26)

(23)

(22)

Power-on

(1) When power-on reset option is selected

(2) When power-on reset option is not selected

(3) After oscillation stabilized

(4) Set STP bit to 1.

(5) Set SLP bit to 1.

(6) Set SCS bit to 0.

(7) External reset when power-on reset option not selected

(8) External reset or interrupt when power-on reset option se-

lected

(9) External reset or interrupt

(10) External reset when power-on reset option not selected

(11) External reset or other reset when power-on reset option

selected

(12) Set SCS bit to 1.

(13) After oscillation stabilized

(14) Set STP bit to 1.

(15) Set TMD bit to 1.

(16) Set SLP bit to 1.

(17) External reset after oscillation stabilized or when power-on

reset option not selected

(18) External reset or other reset when power-on reset option

selected

(19) External reset after oscillation is stabilized or when power-on

reset option not selected

(20) External reset when power-on reset option selected

(21) External reset when power-on reset

option not selected

(22) Interrupt

(23) External reset

when power-on reset

option selected

(24) External reset

when power-on reset

option selected

(25) External reset

when power-on reset

option not selected

(26) Interrupt

(27) External reset

when power-on reset

option selected

(28) External reset

when power-on reset

option not selected

(29) Interrupt

2-19

Page 40

HARDW ARE CONFIGURATION

MAIN/SUBCLOCK

CONTROL BLOCK

Power-on reset

Watchdog timer reset

External reset

Software reset

Reset Control Section

Reset control Internal reset signal

• Reset

There are four types of resets as shown in Table 2-3.

Table 2-3 Sources of Reset

Reset name Description

Power-on reset Turns power on

Watchdog reset Overflows watchdog timer

External-pin reset Sets external-reset pin to Low

Software reset Writes 0 at RST (bit 4) of STBC

When the power-on reset and reset during the stop state are used, the oscillation stabilization time is needed after the oscillator operates. The timebase timer or watch prescaler controls this stabilization time. Consequently ,

the operation does not start immediately even after canceling the reset.

However if Power-on Reset Disabled is selected by the mask option, no oscillation stabilization time is required in any state after external pins have

been released from the reset.

Note: If the Power-on Reset unavailable option is selected, keep the RST

pin Low until the oscillation stabilization time selected in the option

has elapsed after power-on.

2-20

Page 41

HARDW ARE CONFIGURATION

MAIN/SUBCLOCK

CONTROL BLOCK

Single Clock

The single clock can be selected by the mask option. In the single clock operation, the functions are the same as those of the double clock module except that the subclock mode cannot be set. In the single-circuit clock operation, the P71/X1A and P70/X0A function as input ports.

• State transition diagram

Main SLEEP

Main oscillate

(8)

Main STOP

Main stop

(7)

(6)

(5)

(4)

Main RUN

Main oscillate

(3)

Oscillation stabilization

waiting of main clock

(1) (2)

Power-on

(1) When power-on reset

option selected

(2) When power-on reset

option not selected

(3) After oscillation stabilized

(4) Set STP bit to 1.

(5) Set SLP bit to 1.

(6) External reset when power-on reset option not selected

(7) External reset or interrupt when power-on reset option selected

(8) External reset or interrupt

2-21

Page 42

HARDW ARE CONFIGURATION

INTERRUPT

CONTROLLER

Resource #2

•

•

•

Resource #n

F2MC-8L bus

Test

register

G L

G

•

•

•

•

•

•

G

2.3 INTERRUPT CONTROLLER

The interrupt controller for the F2MC-8L family is located between the

2

MC-8L CPU and each resource. This controller receives interrupt re-

F

quests from the resources, assigns priority to them, and transfers the

priority to the CPU; it also decides the priority of same-level interrupts.

Block Diagram

CPU

2

Address decorder

LevelResource #1

L

•

•

•

L

Level

•

•

•

Level

Level

deciding

block

•

•

•

G

•

•

•

Interrupt

vector

generation

block

G

•

•

•

Same level

priority order

deciding

block

G

Fig. 2.9 Interrupt Controller Block Diagram

Register List

Interrupt controller consists of interrupt-level registers (ILR1, 2, and 3).

8 bit

Address: 007C

Address: 007D

Address: 007E

H

H

H

ILR1

ILR2

ILR3

W Interrupt level register #1

W Interrupt level register #2

W Interrupt level register #3

2-22

Page 43

HARDW ARE CONFIGURATION

INTERRUPT

CONTROLLER

Address: 007C

Address: 007D

Address: 007E

[Example]

Interrupt requests

from resources

Description of Registers

The detail of each register is described below.

ILR1

H

ILR2

H

ILR3

H

• Interrupt level register (ILRX: Interrupt Level Register X)

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Address: 007C

Address: 007D

Address: 007E

L31 L30 L21 L20 L11 L10 L01 L00

H

L71 L70 L61 L60 L51 L50 L41 L40

H

LB1 LB0 LA1 LA0 L91 L90 L81 L80

H

(W) (W) (W) (W) (W) (W) (W) (W)

Initial value

11111111

B

The ILRX sets the interrupt level of each resource. The digits in the center of

each bit correspond to the interrupt numbers.

MB89140 hardware manual

L3X

Interrupt control module

IR0

IR1

IR2

IR3

IRB

Interrupt

number

#0

#1

#2

#3

#11

Table address

Upper Lower

FFFB

FFFA

FFF9

FFF8

FFF7

FFF6

FFF5

FFF4

FFE5

FFE4

When an interrupt is requested from a resource, the interrupt controller

transfers the interrupt level based on the value set at the 2-bits of the ILRX

corresponding to the interrupt to the CPU. The relationship between the 2

bits of the ILRX and the required interrupt levels is as follows:

Lx1 Lx0 Required interrupt level

0 × 1

10 2

1 1 3 (None)

2-23

Page 44

HARDW ARE CONFIGURATION

INTERRUPT

CONTROLLER

Description of Operation

The functions of interrupt controllers are described below.

• Interrupt functions

The MB89140 series of microcontrollers have 12 inputs for interrupt re-

quests from each resource. The interrupt level is set by 2-bit registers corresponding to each input. When an interrupt is requested from a resource, the

interrupt controller receives it and transfers the contents of the corresponding level register to the CPU. The interrupt to the device is processed as

follows: