Page 1

FUJITSU SEMICONDUCTOR

CONTROLLER MANUAL

MICROCONTROLLERS

CM25-10130-1E

F2MC-8L FAMILY

MB89950 SERIES

HARDWARE MANUAL

Page 2

PREFACE

The MB89950 series of microcontrollers are mid-range of microcontroller. They are

general-purpose and high-speed products in the F2MC-8L Family series of 8-bit single-

chip microcontr ollers operating at lo w voltages . It has UA RT, PWM, LCD cont roller and etc.

This manual covers the functions and operations of the MB89950 series of microcontrollers.

Refer to the

F2MC-8L Family Software Manual

for instructions.

iii

Page 3

Table of Contents

1. GENERAL ......................................................................................................................1-1

1.1 Features ...................................................................................................................1-3

1.2 Product Series .........................................................................................................1-4

1.3 Block Diagram ..........................................................................................................1-5

1.4 Pin Assignment ........................................................................................................1-6

1.5 Pin Description .........................................................................................................1-8

1.6 Handling Devices ...................................................................................................1-12

2. HARDWARE CONFIGURATION .................................................................................... 2-1

2.1 CPU .........................................................................................................................2-3

2.1.1 Memory Space ...............................................................................................2-3

2.1.3 Internal Registers in CPU ...............................................................................2-6

2.1.4 Clock Control Block ........................................................................................2-9

2.1

2.2 Peripherals .............................................................................................................2-18

2.2.2 8-bit PWM Timer (Timer 1) ...........................................................................2-25

2.2.3 Pulse-width Count Timer (Timer 2) ..............................................................2-30

2.2.4 UART ...........................................................................................................2-37

2.2.5 8-bit Serial I/O ..............................................................................................2-50

2.2.6 External Interrupt ..........................................................................................2-56

2.2.7 LCD Controller/driver ....................................................................................2-59

2.2.8 Time-base Timer ..........................................................................................2-69

2.2.9 Watchdog Timer Reset .................................................................................2-71

3. OPERATION ..................................................................................................................3-1

4. INSTRUCTIONS ............................................................................................................. 4-1

5. MASK OPTIONS ............................................................................................................. 5-1

APPENDIX ..................................................................................................................... App-1

2.1.2 Arrangement of 16-bit Data in Memory Space ...............................................2-5

.

5 Interrupt Controller ....................... ............................................. ....... ............ 2- 15

2.2.1 I/O Ports .......................................................................................................2-18

3.1 Clock Pulse Generator .............................................................................................3-3

3.2 Reset .......................................................................................................................3-4

3.2.1 Reset Operation ..............................................................................................3-4

3.2.2 Reset Sources ................................................................................................3-5

3.3 Interrupt ...................................................................................................................3-6

3.4 Low-power Consumption Modes .............................................................................3-8

3.5 Pin States for Sleep, Stop and Reset ......................................................................3-9

4.1 Legend .....................................................................................................................4-3

4.2 Transfer Instructions ................................................................................................4-4

4.3 Operation Instructions ..............................................................................................4-5

4.4 Branch Instructions .......................... ...... ............................................. ....... ..............4-6

4.5 Other Instructions .....................................................................................................4-7

2

4.6 F

MC-8L Family Instruction Map .............................................................................4-8

Appendix A I/O Map ................................................................................................. App-3

Appendix B Writing EPROM .................................................................................... App-5

iv

Page 4

Tables

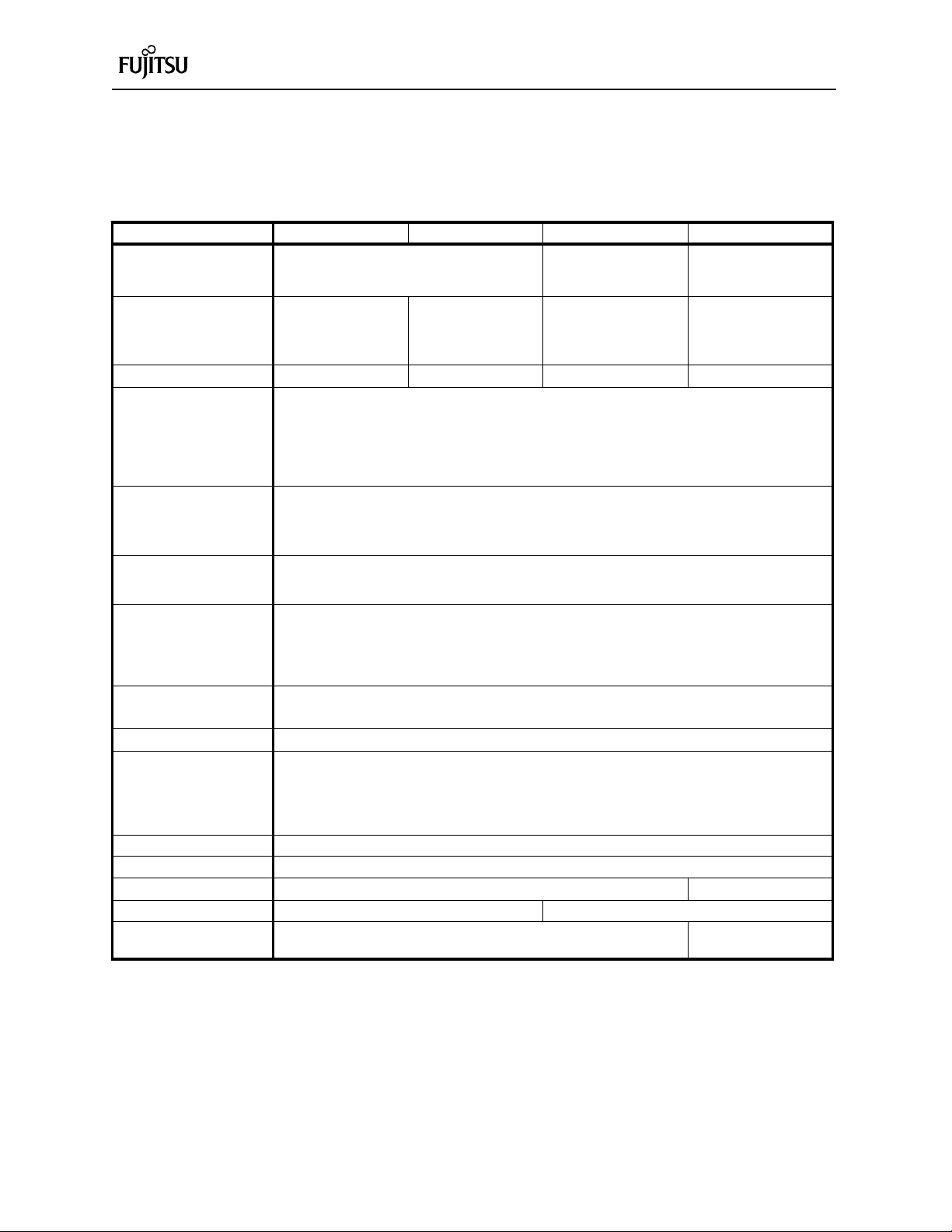

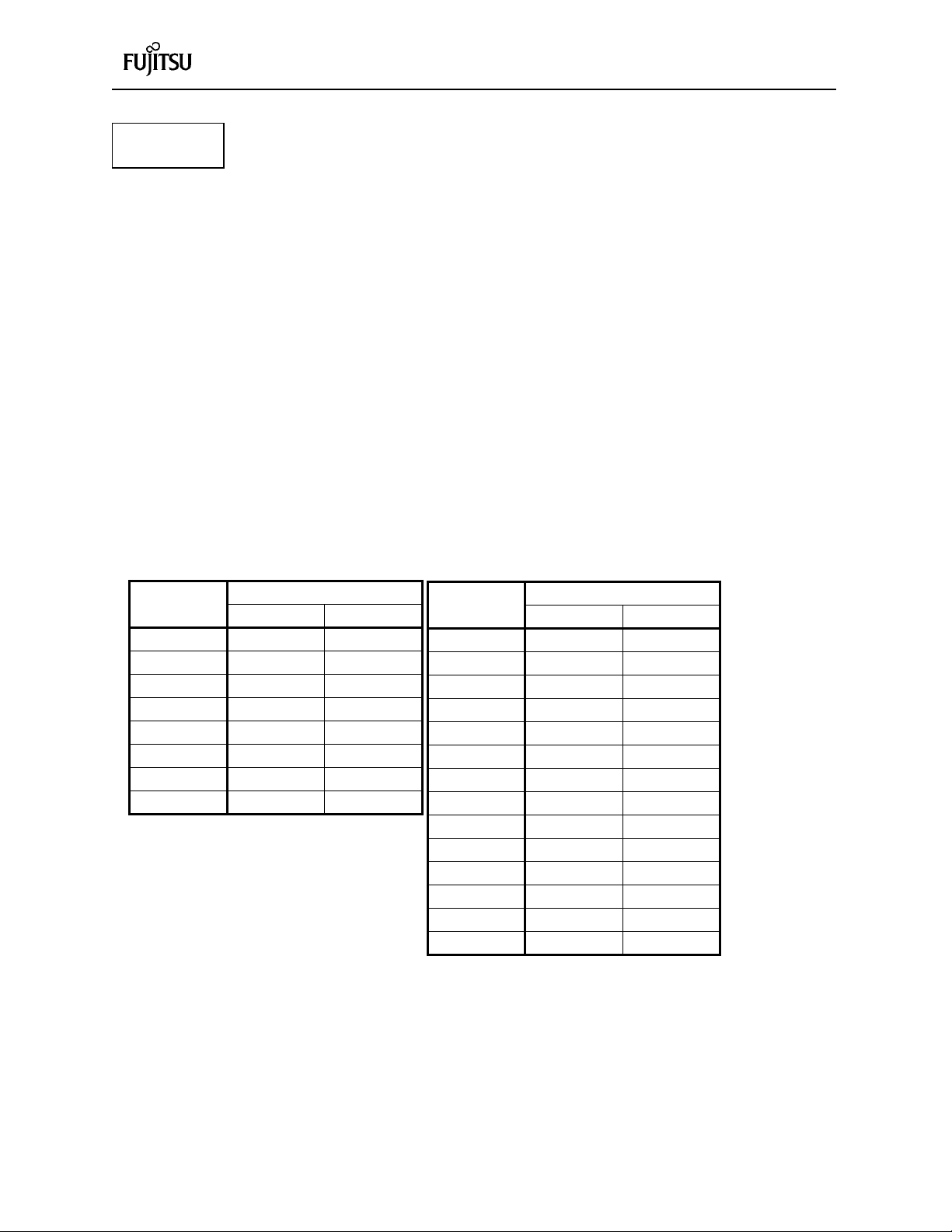

Table 1–1 Types and Functions of MB89950 Series of Microcontrollers ...........................1-4

Table 1–2 Pin Description ..................................................................................................1-8

Table 1–3 Pin Description for External ROM ......................................................................1-9

Table 2–1 Table of Reset and Interrupt Vectors .................................................................2-4

Table 2–2 Operating Mode of Low-power Consumption Modes ......................................2-11

Table 2–3 Selection of Oscillation Stabilization Time .......................................................2-12

Table 2–4 Sources of Reset .............................................................................................2-14

Table 2–5 List of Port Functions .......................................................................................2-18

Table 2–6 Operation Modes of UART ..............................................................................2-46

Table 2–7 Clock Division Ratio..........................................................................................2-48

Table 2–8 Input Clock of Baud Rate Generator ...............................................................2-48

Table 2–9 Selection of Baud Rate (When Dedicated Baud Rate Generate Used) ..........2-49

Table 3–1 Interrupt Sources and Interrupt Vectors ............................................................3-7

Table 3–2 Low-power Consumption Mode at Each Clock Mode ........................................3-8

Table 3–3 Pin State of MB89950 ........................................................................................3-9

Table 5–1 Mask Options .....................................................................................................5-3

Table 5–2 Recommended Port/Segment Mask Option Combinations ...............................5-3

v

Page 5

Figures

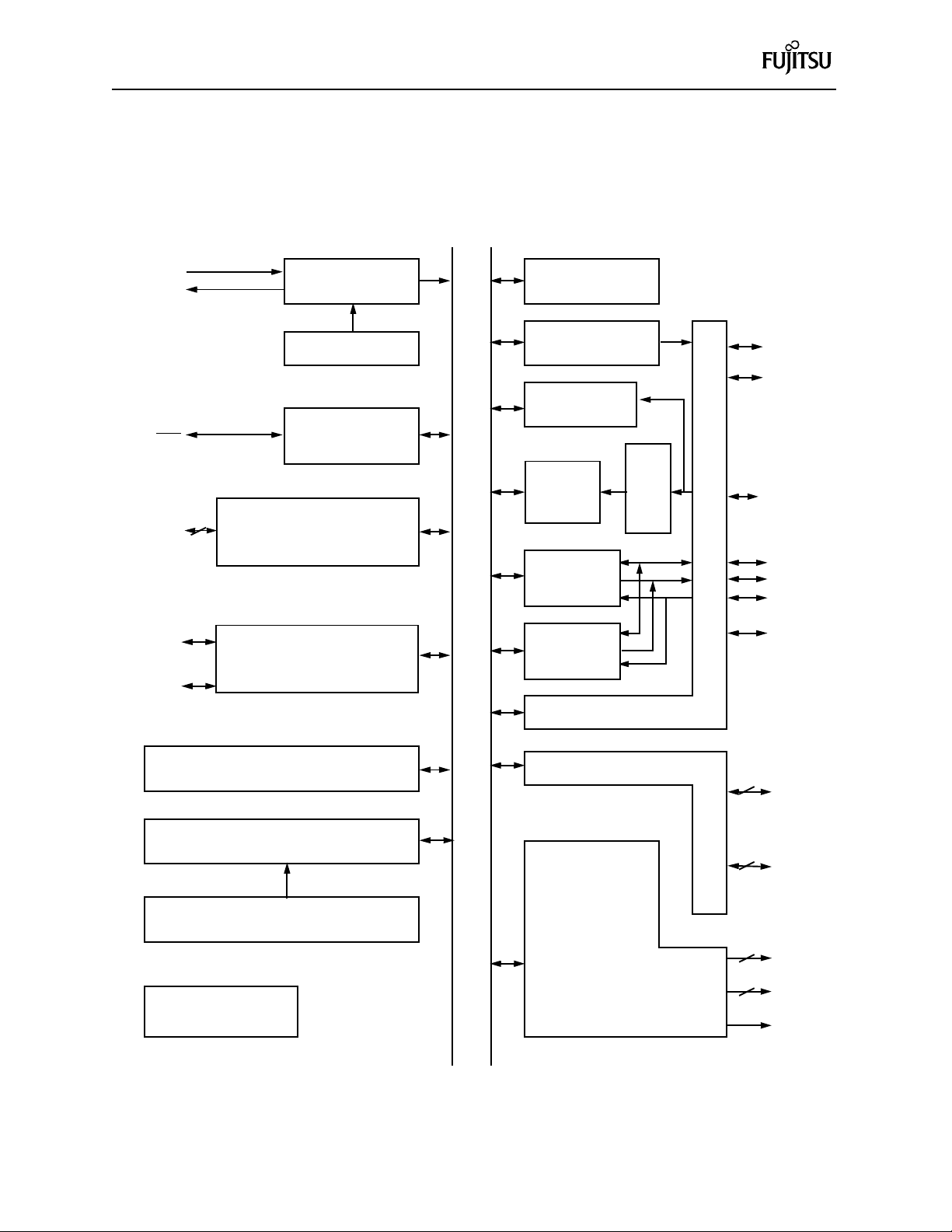

Fig. 1.1 Block Diagram (MB89953) .............................................................................................1-5

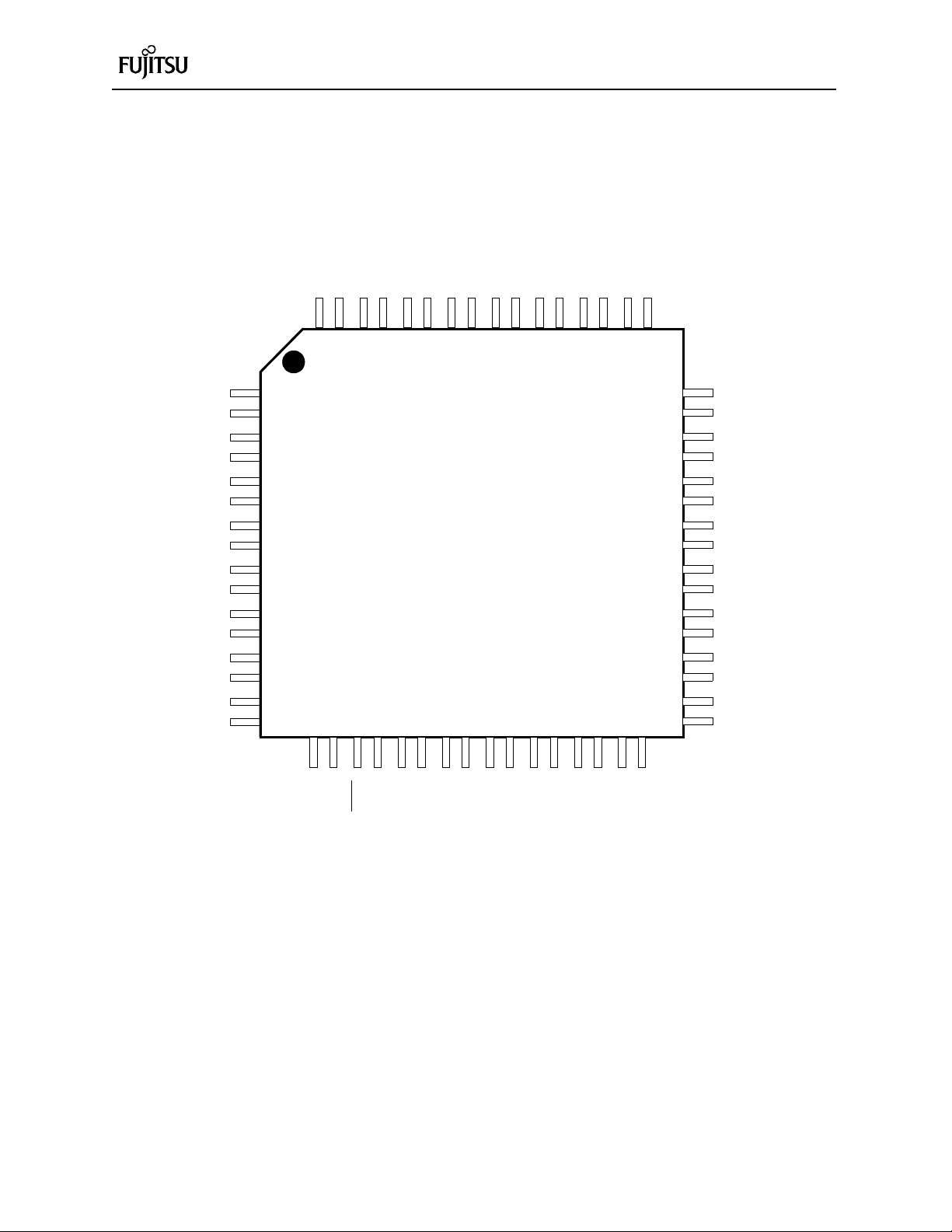

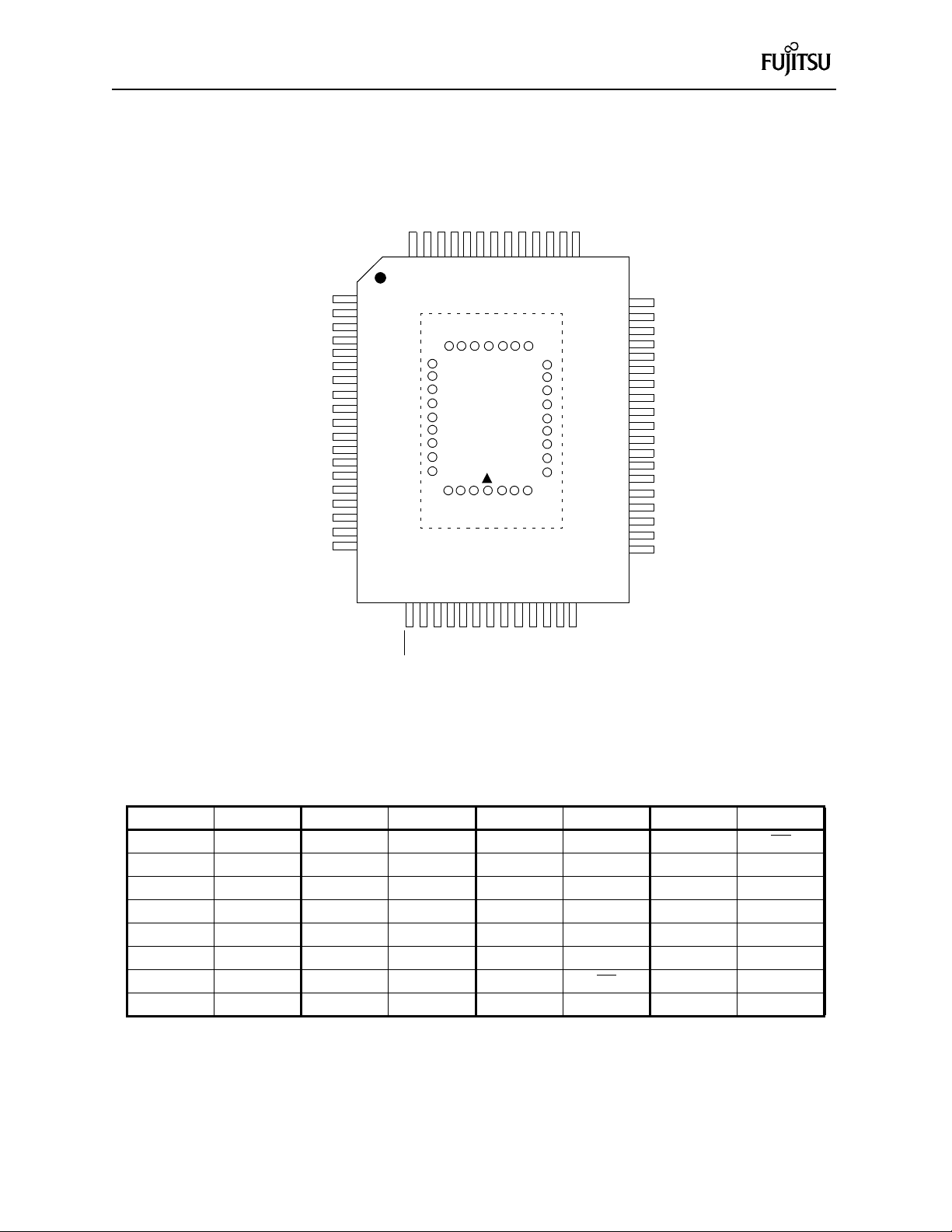

Fig. 1.2 Pin Assignment of MB89953 and MB89P955 (QFP-64, pitch: 0.65 mm) .......................1-6

Fig. 1.3 Pin Assignment of MB89PV950 (MQFP-64, pitch: 0.8 mm) ...........................................1-7

Fig. 1.4 I/O Circuits ....................................................................................................................1-10

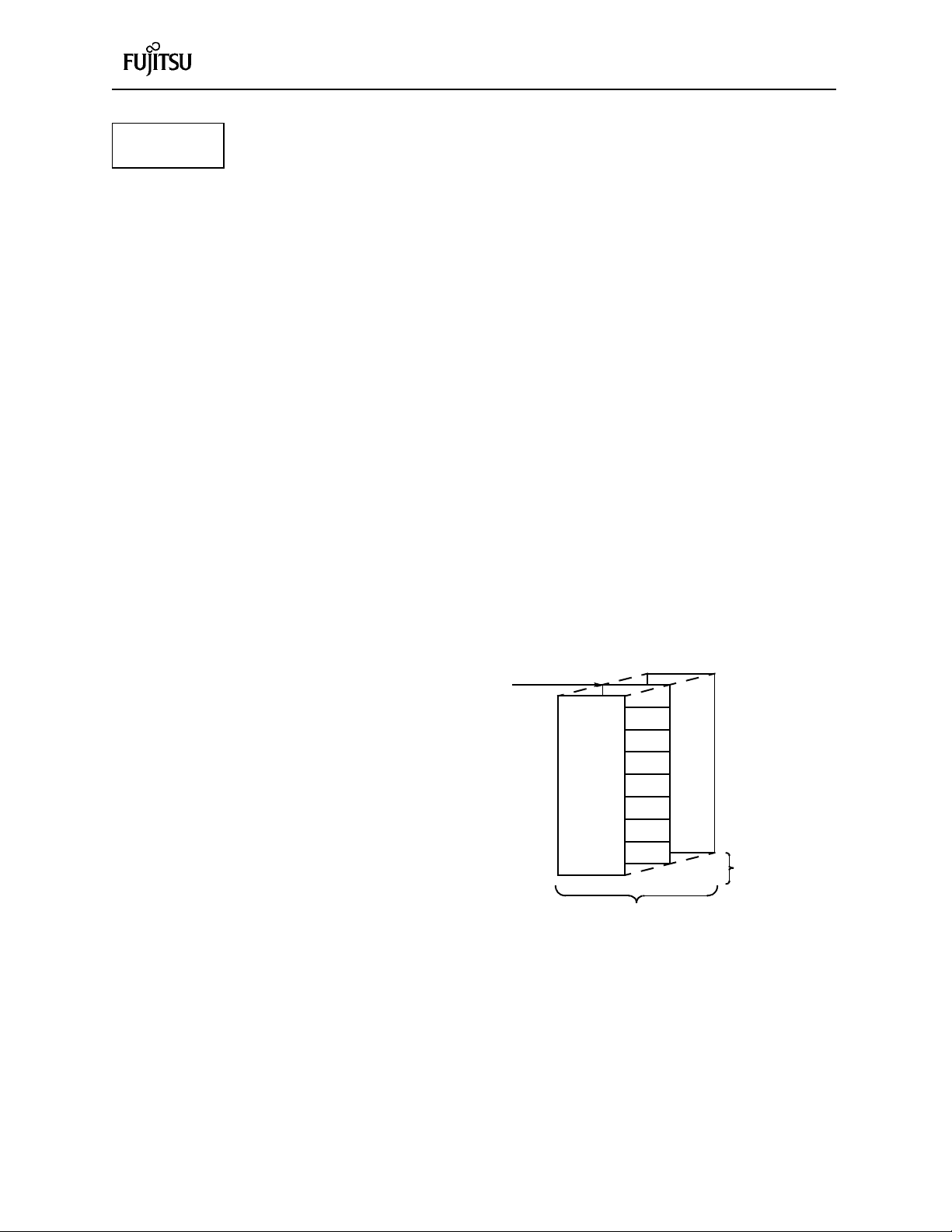

Fig. 2.1 Memory Space of MB89950 Series Microcontrollers .....................................................2-3

Fig. 2.2 Arrangement of 16 bit Data in Memory Space ...............................................................2-5

Fig. 2.3 Arrangement of 16 bit Data during Execution of Instruction ...........................................2-5

Fig. 2.4 Structure of Processor Status .........................................................................................2-7

Fig. 2.5 Rule for Translating Real Addresses at General-purpose Register Area .......................2-7

Fig. 2.6 Register Bank Configuration ...........................................................................................2-8

Fig. 2.7 Interrupt-processing Flowchart .....................................................................................2-17

Fig. 2.8 Ports 0, 1 and 2 ............................................................................................................2-20

Fig. 2.9 Port 3 ............................................................................................................................2-22

Fig. 2.10 Port 4 ..........................................................................................................................2-24

Fig. 2.11 Timer Operation ..........................................................................................................2-28

Fig. 2.12 PWM Pulse Output .....................................................................................................2-29

Fig. 2.13 Measurement of High Pulse Width .............................................................................2-35

Fig. 2.14 Operation of Noise Clearing Circuit ............................................................................2-36

Fig. 2.15 RDRF Flag Set Timing ...............................................................................................2-46

Fig. 2.16 ORFE Flag Set Timing ...............................................................................................2-47

Fig. 2.17 TDRE Flag Set Timing ................................................................................................2-47

Fig. 2.18 Transfer Data Format (Synchronous Transfer) ..........................................................2-47

Fig. 2.19 Shift Start/Stop Timing ................................................................................................2-55

Fig. 2.20 Input/Output Shift Timing ............................................................................................2-55

Fig. 2.21 LCD Controller /Driver Block Diagram ........................................................................2-59

Fig. 2.22 Example of Waveform at Pin Corresponding to the RAM Data for Display ................2-64

Fig. 2.23 Example of Waveform at Pin Corresponding to the RAM Data for Display ................2-65

Fig. 2.24 Example of Waveform at Pin Corresponding to the RAM Data for Display ................2-66

Fig. 2.25 Connection Examples for Supply Power for Driving LCD ...........................................2-67

Fig. 2.26 Built-in Voltage Dividing resistors ...............................................................................2-68

Fig. 3.1 Clock Pulse Generator ...................................................................................................3-3

Fig. 3.2 Outline of Reset Operation .............................................................................................3-4

Fig. 3.3 Reset Vector Structure ...................................................................................................3-4

Fig. 3.4 Interrupt-processing Flowchart .......................................................................................3-6

vi

Page 6

1. GENERAL

1.1 Features ................................................................................ 1-3

1.2 Product Series ........................................................ ............... 1-4

1.3 Block Diagram .................................................... .... ..... .......... 1-5

1.4 Pin Assignment ....................................................... ..... ..... ..... 1-6

1.5 Pin Description ..................................... .... ..... ..... ................... 1-8

1.6 Handling Devices ........................ ..... ....................................1-12

Page 7

GENERAL

2

The MB89950 series of single-chip compact microcontroller using the F

MC-8L core for which can operate

at high-speeds and low voltages. They contain peripheral such as timers, UART, serial interfaces, and

external interrupts, including a 168-pixel LCD controller/driver; they are best suited for use in LCD panels.

1.1 Features

•

High-speed processing even at low voltages

Minimum instruction execution time: 0.8 µs/5 MHz (V

2

•

F

MC-8L family CPU core

Instruction system most suited to controller

- Multiplication and division instructions

- 16-bit arithmetic operation

- Instruction test and branch instruction

- Bit manipulation instruction, etc.

•

LCD controller/driver

- Maximum 42 segment outputs × 4 common outputs

- Built-in LCD driver split resistor

CC

= 5 V)

•

Three-channel timer unit

- 8-bit PWM timer: (usable as both reload timer and PWM timer)

- 8-bit pulse width count timer: (usable as both reload timer)

- 20-bit time-based counter

•

Two serial interfaces

- 8-bit synchronous serial interface (The transfer direction can be selected to communicate with various

equipment.)

- UART (5, 7, and 8-bit transfers possible)

•

External-interrupt input: 2 channels

- 2 channels can be used to clear the low-power consumption modes.

(An edge-detection function is provided)

•

Low-power consumption modes

- Stop mode (Oscillation stops to minimize the current consumption.)

- Sleep mode (The CPU stops to reduce current consumption to about 30% of normal.)

1– 3

Page 8

GENERAL

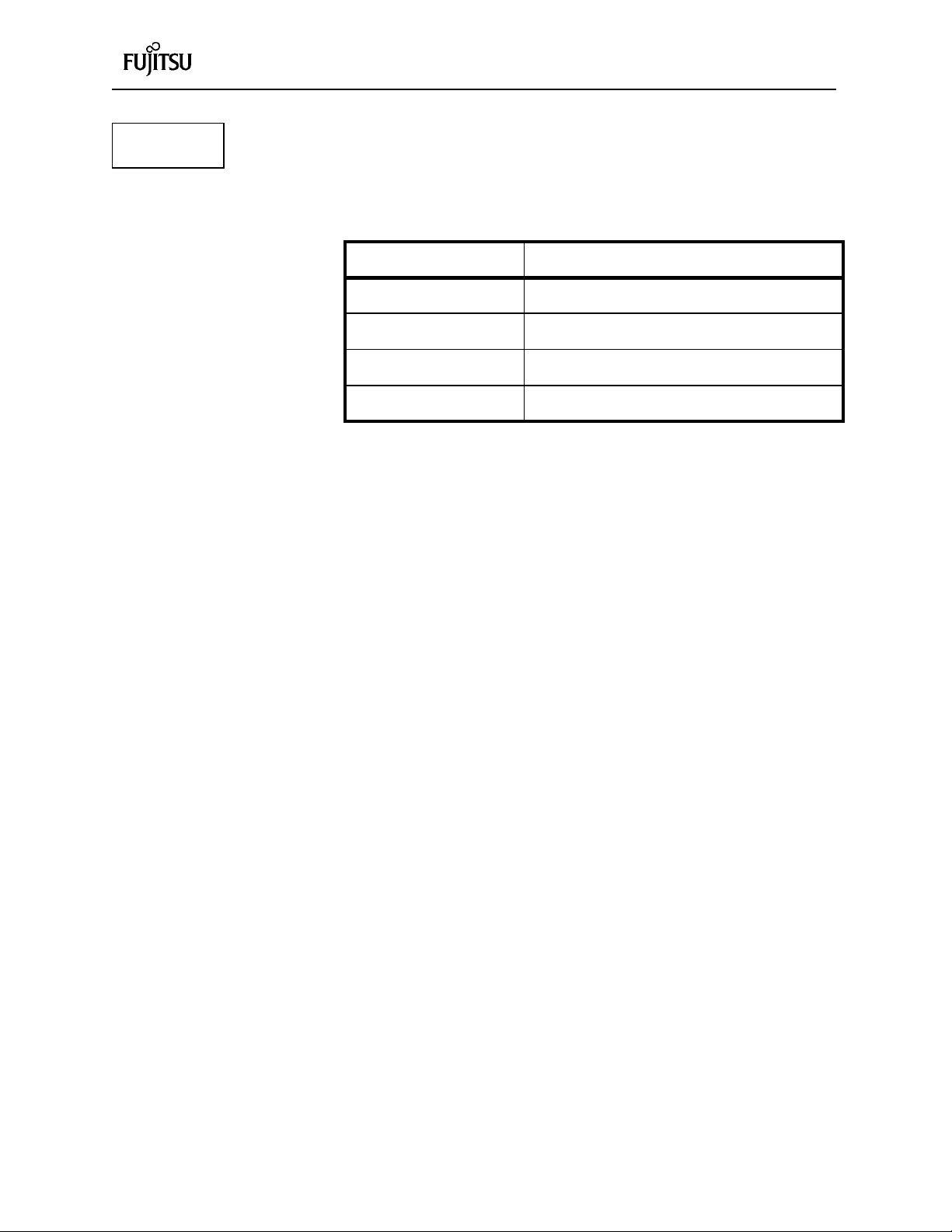

1.2 Product Series

Table 1–1 lists the types and functions of the MB89950 series of microcontrollers.

Table 1–1 Types and Functions of MB89950 Series of Microcontrollers

Model name MB89951 MB89953 M B89P 955 MB89PV950

Classification

ROM capacity

RAM capacity

CPU function

Port

PWM Timer

Pulse-width Counter

Timer

Serial I/O

UART

LCD controller/driver

External Interrupt

Standby Mode

Package

Operation Voltage

EPROM

*2

Mass-produced product

(Mask ROM product)

4K × 8 bits

(internal ROM)

128 × 8 bits 256 × 8 bits 512 × 8 bits 1024 × 8 bits

Number of basic instructions:136

Instruction bit length:8 bits

Instruction length:1 to 3 bytes

Data bit length:1, 8, 16 bits

Minimum instruction execution time:0.8 µs at 5 MHz (V

Interrupt processing time:7.2 µs at 5 MHz (V

I/O port (N-ch open drain): 22 (also used as segment pin)

I/O port (N-ch open drain): 4 (two of them are also used as LCD bias pins)

I/O port (CMOS): 7 (6 used as peripheral)

Total: 33 (Maximum)

8-bit reload timer operation (toggle output possible)

8-bit resolution PWM operation

Operation clock (pulse-width count timer output: 0.8

8-bit reload timer operation

8-bit pulse width measurement (continuous measurement, High- and Low-width measurement, and

one-cycle measurement)

Operation clock (0.8

8-bit length, selectable from least significant bit (LSB) first or most significant bit (MSB) first, transfer

clock (external, 1.6

5-, 7-, 8-bit transfers possible, internal baud-rate generator (Max. 78125 bps/5 MHz)

Common output: 4

Segment output: 42 (max.)

Operation mode: 1/2 bias and 1/2 duty, 1/3 bias and 1/3 duty, 1/3 bias and 1/4 duty

LCD controller display RAM capacity: 42 × 4 bits

LCD driver split resistor: built-in (external resistor selectable)

2 (edge selectable: one serving as pulse-width count timer input)

Sleep mode, stop mode

µ

µ

s, 6.4 µs, 25.6 µs/5 MHz)

2.2 V to 6.0 V 2.7 V to 6.0 V

8K × 8 bits

(internal ROM)

s, 3.2 µs, 25.6 µs/5 MHz)

FPT-64-M09 MQP-64C-P01

not applicable

*1 Mask Option.

*2 Varies according to conditions such as frequency.

One-time programmable Piggyback/Evaluation

16K × 8 bits

(Internal PROM; writable

by general-purpose

writers)

= 5 V)

CC

= 5 V)

CC

*1

µ

s, 12.8 µs, 51.2 µs/5 MHz)

and development

product

32K × 8 bits

(External ROM)

MBM27C256A-25

(LCC package)

1– 4

Page 9

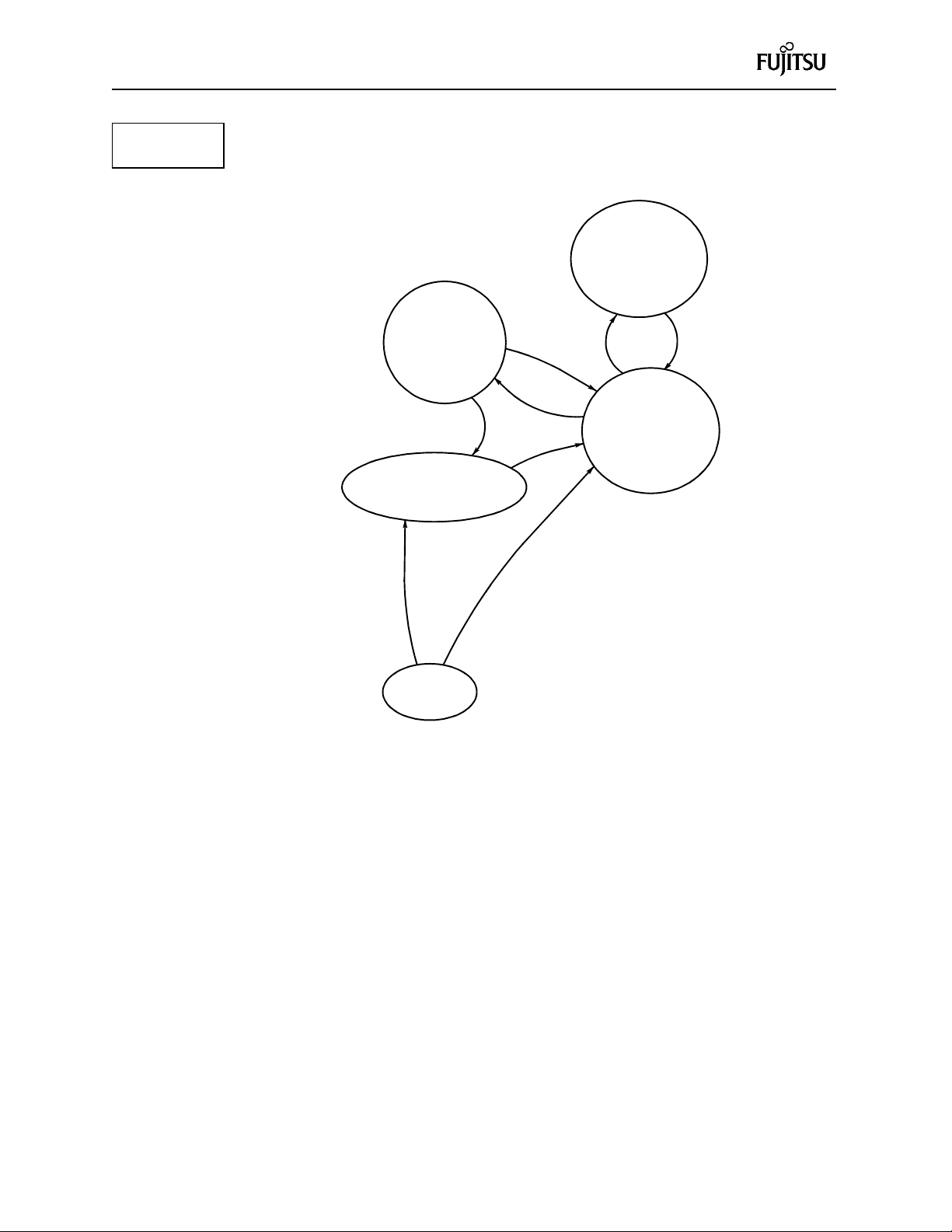

1.3 Block Diagram

GENERAL

Internal bus

RST

P20 to P25/

SEG36 to

SEG41

P30, P31

P33/V2

P32/V1

X0

X1

Main oscillator

circuit

Clock control

Reset circuit

(WDT)

Port 2

6

N-ch open-drain I/O port

Port 3

N-ch open-drain I/O port

Time-base timer

8-bit PWM timer

External interrupt

8-bit

pulse width

count timer

8-bit serial

UART

CMOS I/O port

Noise

clear

Port

4

P41/PWM

P40

P42/PWC/

INT1

P45/SCK

P44/SO

P43/SI

P46/INT0

R A M (256 × 8 bits)

F

CPU

R O M (8 K × 8 bits)

Other pins

MODA

V

, VSS

CC

2

MC-8L

N-ch open-drain I/O port

LCD controller driver

Fig. 1.1 Block Diagram (MB89953)

1– 5

Port

0/1

8

P00/SEG20 to

P07/SEG27

8

P10/SEG28 to

P17/SEG35

20

SEG0 to

SEG19

4

COM0 to

COM3

V3

Page 10

1.4 Pin Assignment

SEG5

SEG6

SEG7

SEG8

GENERAL

SEG9

SEG10

SEG11

SEG12

VCCSEG13

SEG14

SEG15

SEG16

SEG17

SEG18

SEG19

SEG4

SEG3

SEG2

SEG1

SEG0

COM3

COM2

COM1

COM0

V3

P33/V2

P32/V1

P31

P30

P40

P41/PWM

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

646362616059585756555453525150

Top view

QFP-64

171819202122232425262728293031

X1

V

SS

P45/SCK

P46/INT0

P25/SEG41

P24/SEG40

P23/SEG39

P22/SEG38

P21/SEG37

RST

P43/SI

P42/INT1/PWC

X0

MODA

P44/SO

32

P20/SEG36

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

P00/SEG20

P01/SEG21

P02/SEG22

P03/SEG23

P04/SEG24

P05/SEG25

P06/SEG26

P07/SEG27

P10/SEG28

P11/SEG29

P12/SEG30

P13/SEG31

P14/SEG32

P15/SEG33

P16/SEG34

P17/SEG35

Fig. 1.2 Pin Assignment of MB89953 and MB89P955 (QFP-64, pitch: 0.65 mm)

1– 6

Page 11

GENERAL

SEG6

SEG7

SEG8

SEG9

SEG10

SEG11

SEG12

Vcc

SEG13

SEG14

SEG15

SEG16

SEG17

64636261605958575655545352

SEG5

SEG4

SEG3

SEG2

SEG1

SEG0

COM3

COM2

COM1

COM0

V3

V2/P33

V1/P32

P31

P30

P40

PWM/P41

INT1/PWC/P42

SI/P43

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

84838281807978

85

86

87

88

89

90

91

92

93

94959665666768

(Top View)

20212223242526272829303132

X0

X1

RST

SO/P44

Vss

MODA

SCK/P45

51

50

49

48

SEG38/P22

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

SEG37/P21

77

76

75

74

73

72

71

70

69

INT0/P46

SEG41/P25

SEG40/P24

SEG39/P23

SEG18

SEG19

SEG20/P00

SEG21/P01

SEG22/P02

SEG23/P03

SEG24/P04

SEG25/P05

SEG26/P06

SEG27/P07

SEG28/P10

SEG29/P11

SEG30/P12

SEG31/P13

SEG32/P14

SEG33/P15

SEG34/P16

SEG35/P17

SEG36/P20

Fig. 1.3 Pin Assignment of MB89PV950 (MQFP-64, pitch: 0.8 mm)

Pin assignment on package top (MB89PV950 only

)

Pin No. Pin Name Pin No. Pin Name Pin No. Pin Name Pin No. Pin Name

65 N.C. 73 A2 81 N.C. 89 OE

66 Vpp 74 A1 82 O4 90 N.C.

67 A12 75 A0 83 O5 91 A11

68 A7 76 N.C. 84 O6 92 A9

69 A6 77 O1 85 O7 93 A8

70 A5 78 O2 86 O8 94 A13

71 A4 79 O3 87 CE

95 A14

72 A3 80 Vss 88 A10 96 Vcc

N.C.: Non connection pin. Keep open.

1– 7

Page 12

GENERAL

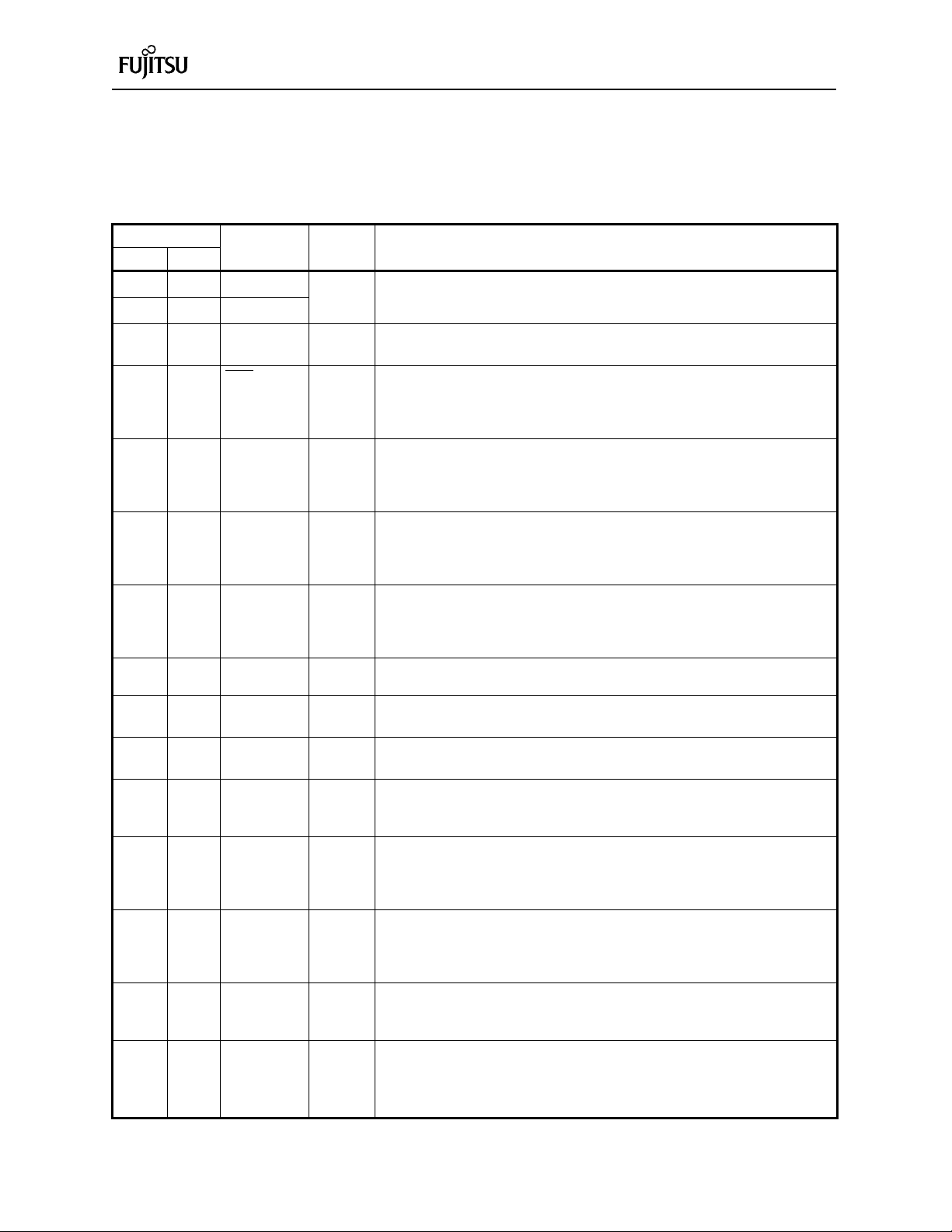

1.5 Pin Description

Table 1–2 lists the pin functions and shows the Fig. 1.4 input/output circuits.

T able 1–2 Pin Description

Pin No

0.65 0.8

22 23

23 24

21 22

19 20

48 to 41 49 to

42

40 to 33 41 to

34

32 to 27 33 to

28

14 to 11 15 to

12

12 to 11 13 to

12

15 16

16 17

17 18

18 19

20 21

25 26

Pin Name Circuit Function

X0 A Clock oscillator pins

X1

MODA B Operation-mode select pins

RST

P00/SEG20

to

P07/SEG27

P10/SEG28

to

P17/SEG35

P20/SEG36

to

P25/SEG41

P30 to P31 F N-channel open-drain type general-purpose I/O ports

P32/V1 to

P33/V2

P40 E General-purpose I/O ports

P41/PWM E General-purpose I/O port

P42/PWC/

INT1

P43/SI E General-purpose I/O port

P44/SO E General-purpose I/O port

P45/SCK E General-purpose I/O port

C Reset I/O pin

D N-channel open-drain type general-purpose I/O ports

D N-channel open-drain type general-purpose I/O ports

D N-channel open-drain type general-purpose I/O ports

D N-channel open-drain type general-purpose I/O ports

E General-purpose I/O port

This pin is connected directly to V

This pin consists of an N-ch open-drain output with a pull-up resistor and

hysteresis input. A Low l evel is pu t out from this pin. A “LOW” vo ltage o n

this port generates a RESET condition.

Also serve as LCDC controller segment outputs.

Switching between port output and segment output is performed by the

mask option every 8 bits.

Also serve as LCDC controller segment outputs.

Switching between port output and segment output is performed by the

mask option.

Also serve as LCDC controller segment outputs.

Switching between port output and segment output is performed by the

mask option.

Also serve as LCDC controller power supply.

A pull-up resistor option is provided.

Serves as PWM timer toggle output (PWM).

A pull-up resistor option is provided.

Also serves as pul se-width coun t tim er input (PWC) a nd exter nal interr upt

input (INT1). The PWC and INT1 inputs are hysteresis type. A pull-up

resistor option is provided.

Also serves as serial I/O and UART data input (SI). The SI input is

hysteresis type.

A pull-up resistor option is provided.

Also serves as serial I/O and UART data output (SO).

A pull-up resistor option is provided.

Also serves as serial I/O and UART clock input/output (SCK). The SCK

input is hysteresis type.

A pull-up resistor option is provided.

SS

with pull down resistor.

1– 8

Page 13

GENERAL

Pin No

0.65 0.8

26 27

5 to 1

64 to 57

55 to 49

9 to 6 7 to 10

10 11

56 57

24 25

6 to 1

64 to

58

56 to

50

Table 1–2 Pin Description

Pin Name Circuit Function

P46/INT0 E General-purpose input port

Also serves as external-interrupt input (INT0).

The input is hysteresis type.

A pull-up resistor option is provided.

SEG0 to

G For LCDC controller segment ouput

SEG19

COM0 TO

COM3

V3 - For LCD driver power supply

Vcc - Power Pin

Vss - Power (GND) Pin

G For LCDC controller common output

(Continued)

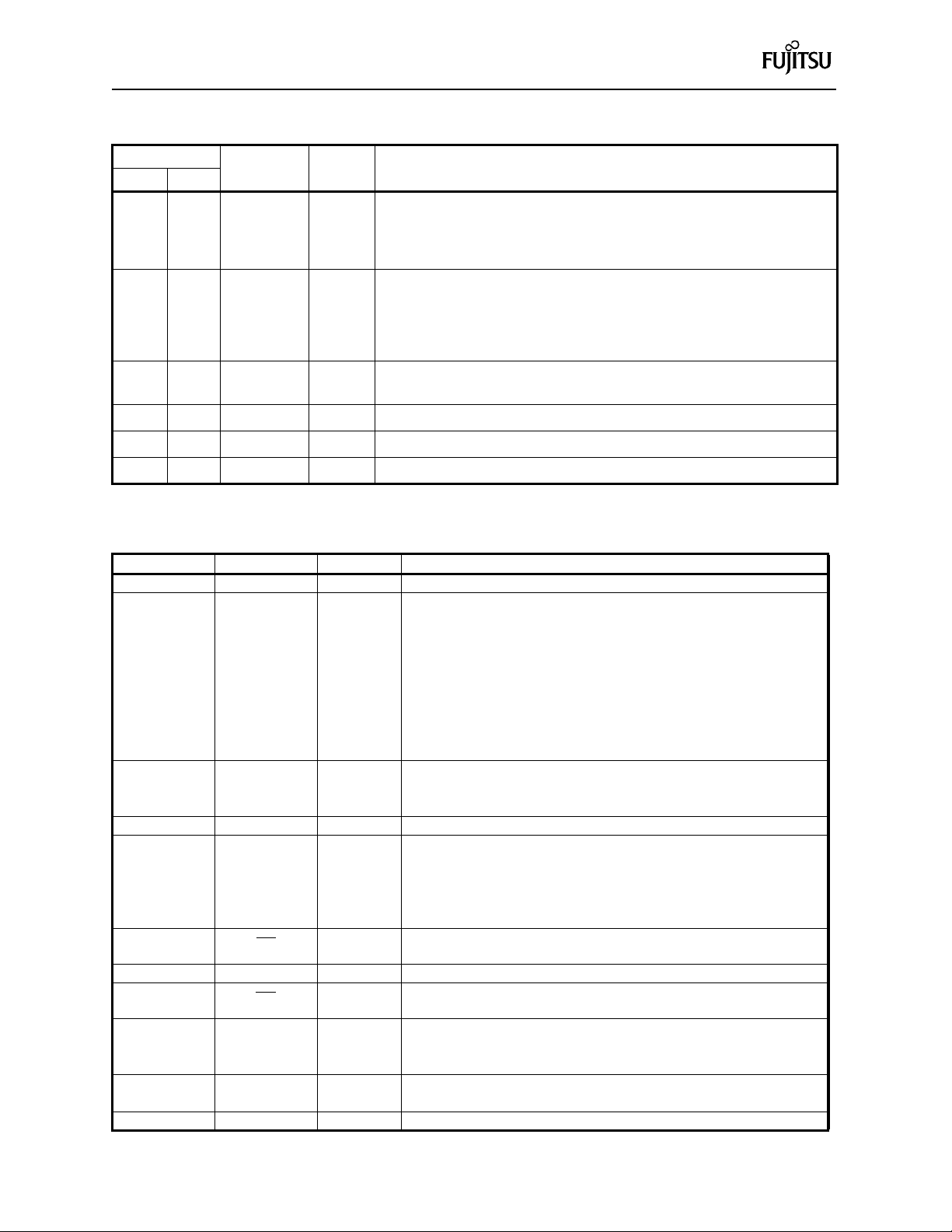

T able 1–3 Pin Description for External ROM

• External EPROM pins (for MB89PV950)

Pins No. Pin Name I/O Function

66 Vpp O For High-level output

67 A12

68 A7

69 A6

70 A5

71 A4

72 A3

73 A2

74 A1

75 A0

77 O1

79 O3

80 Vss O For power supply (GND)

82 04

83 O5

84 O6

85 O7

86 O8

87 CE

88 A10 O For address output

89 OE O

91 A11

93 A8

94 A13

95 A14

96 Vcc O For EPROM power supply

O For address output

I For data input78 O2

I For data input

O

O For address output92 A9

O For address output

For ROM out put enable

The High level is output in standby mode .

For ROM output enable.

The Low level is always output.

1– 9

Page 14

GENERAL

Table 1–3 Pin Description for External ROM

(Continued)

• External EPROM pins (for MB89PV950)

Pins No. Pin Name I/O Function

65

76

81

90

N.C. —

For internal connection

Keep open.

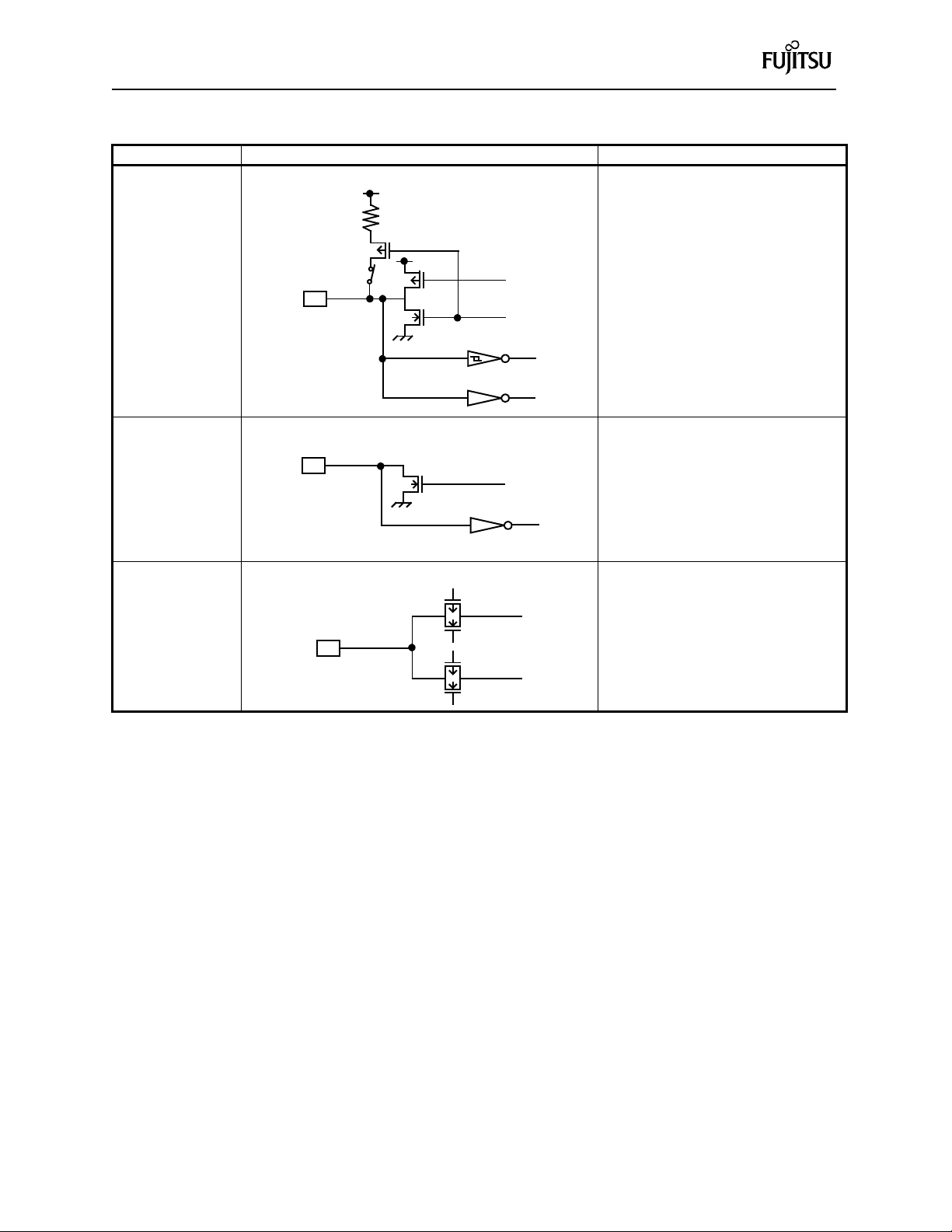

Fig. 1.4 I/O Circuits

Classification Circuit Remarks

A • Crystal oscillator

X1

• Feedback resistor: About 1 M

5 V (1 to 5 MHz)

X0

Standby control signal

B • CMOS input

• Pull down resistor (N-ch)

Ω

/

R

C • Output pull-up resistor (P-ch):

Ω

• About 50 M

R

P-ch

N-ch

• Hysteresis input

(5 V)

D • N-ch open-drain output

• CMOS input

N-ch

• The segment output is optional.

1– 10

Page 15

GENERAL

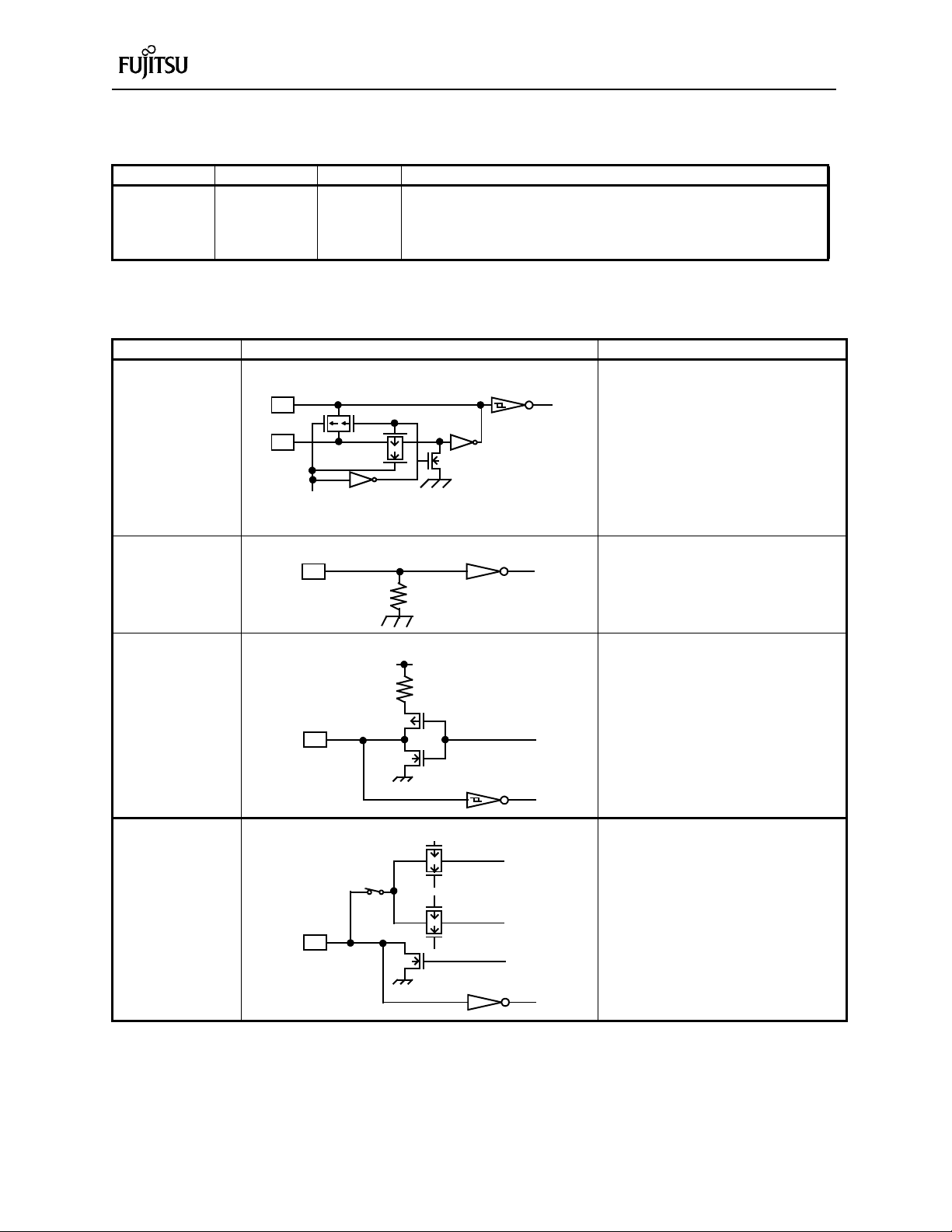

Fig. 1.4 I/O Circuits

(Continued)

Classification Circuit Remarks

E • CMOS output

• CMOS input

R

P-ch

P-ch

N-ch

• Hysteresis input

(peripheral input)

• The pull-up resistor is optional.

F • N-ch open-drain output

• CMOS input

N-ch

G • LCDC output

1– 11

Page 16

1.6 Handling Devices

(1) Preventing latch-up

GENERAL

Latchup may occur on CMOS ICs if voltage higher than V

or lower than VSS is applied to input and output

CC

pins other than medium to high-voltage pins or if higher than the voltage which shows on Absolute Maximum

Ratings is applied between V

and VSS.

CC

When latch-up occurs, supply current increases rapidly and might thermally damage elements. When using,

take great care not to exceed the absolute maximum ratings.

(2) Treatment of Unused Input Pins

Leaving unused input pins open could cause malfunctions. They should be connected to pull-up or pulldown resistor.

(3) Power Supply Voltage Fluctuations

Although V

power supply voltage is assured to operate within the rated, a rapid change to the IC is therefore

CC

cause malfunctions, ev en if it occurs within the rated range. Stabilizing voltage supplied of the IC is therefore

important. As stabilization guidelines, it is recommended to control power so that V

(P-P. value) will be less that 10% of the standard V

value at the commercial frequency (50 to 60 Hz) and

CC

ripple fluctuations

CC

the transient fluctuation rate will be less than 0.1 V/ms at the time of a momentary fluctuation such as when

power is switched.

(4) Precaution When Using an External Clock

Even when an external clock is used, oscillation stabilization time is required for power-on reset (option

selection) and release from stop mode.

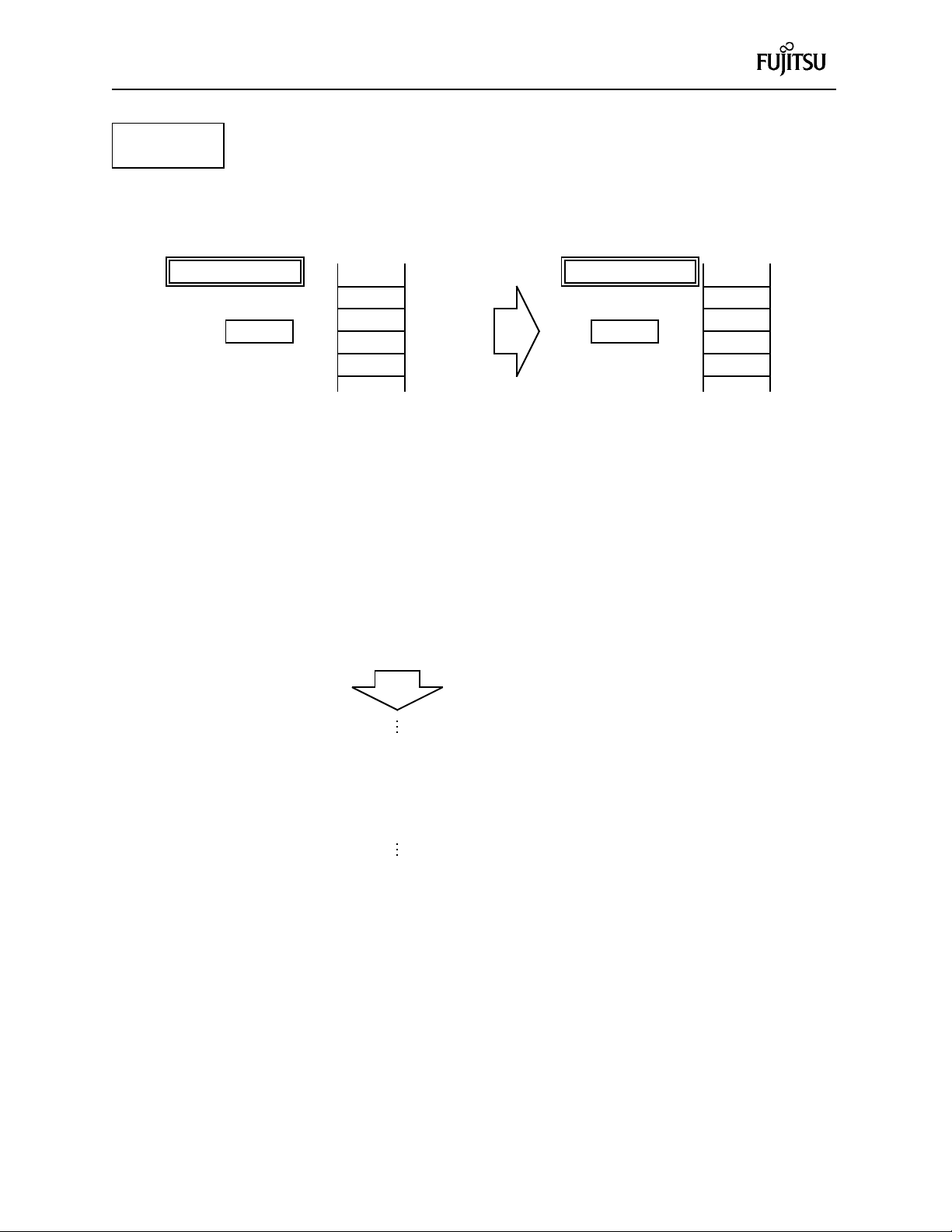

(5) Recommended Screening Conditions

The OTPROM product should be screened by high-temperature aging before mounting.

Verify program

High-temperature aging (150°C, 48H)

Read

Mount

The programming test cannot be performed for all bits of the preprogrammed OTPROM product due to its

characteristics. Consequently, 100% programming yielding cannot be ensured.

1– 12

Page 17

2. HARDWARE CONFIGURATION

2.1 CPU ... ...................................................................................2-3

2.2 Peripherals .......................................................................... 2-18

Page 18

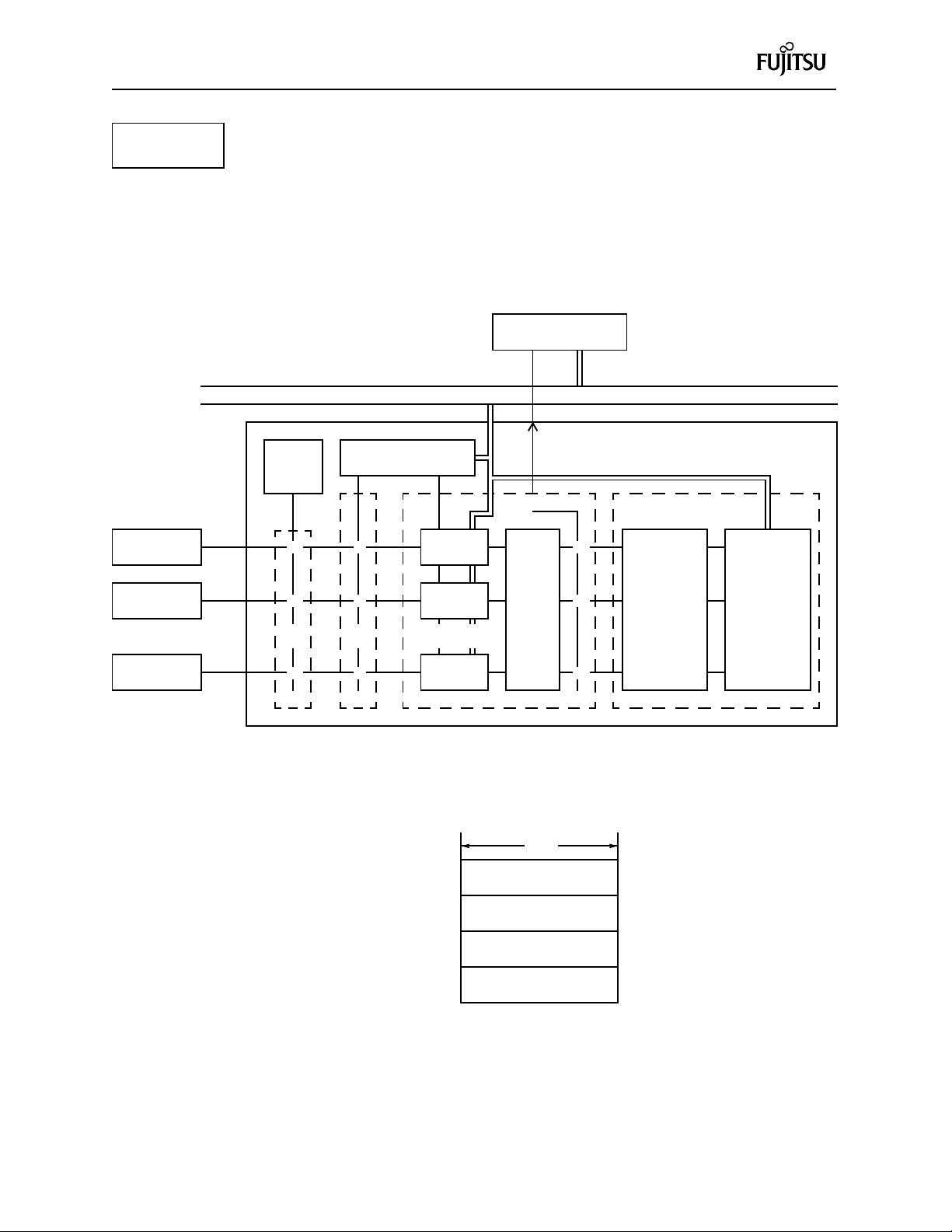

HARDWARE CONFIGURATION

This chapter describes each block of the CPU hardware.

CPU

0000

0080

00C0

0100

0140

H

H

H

H

Register

H

MB89951

I/O

Reserved

RAM

2.1 CPU

This section describes the memory space and register composing CPU

hardware.

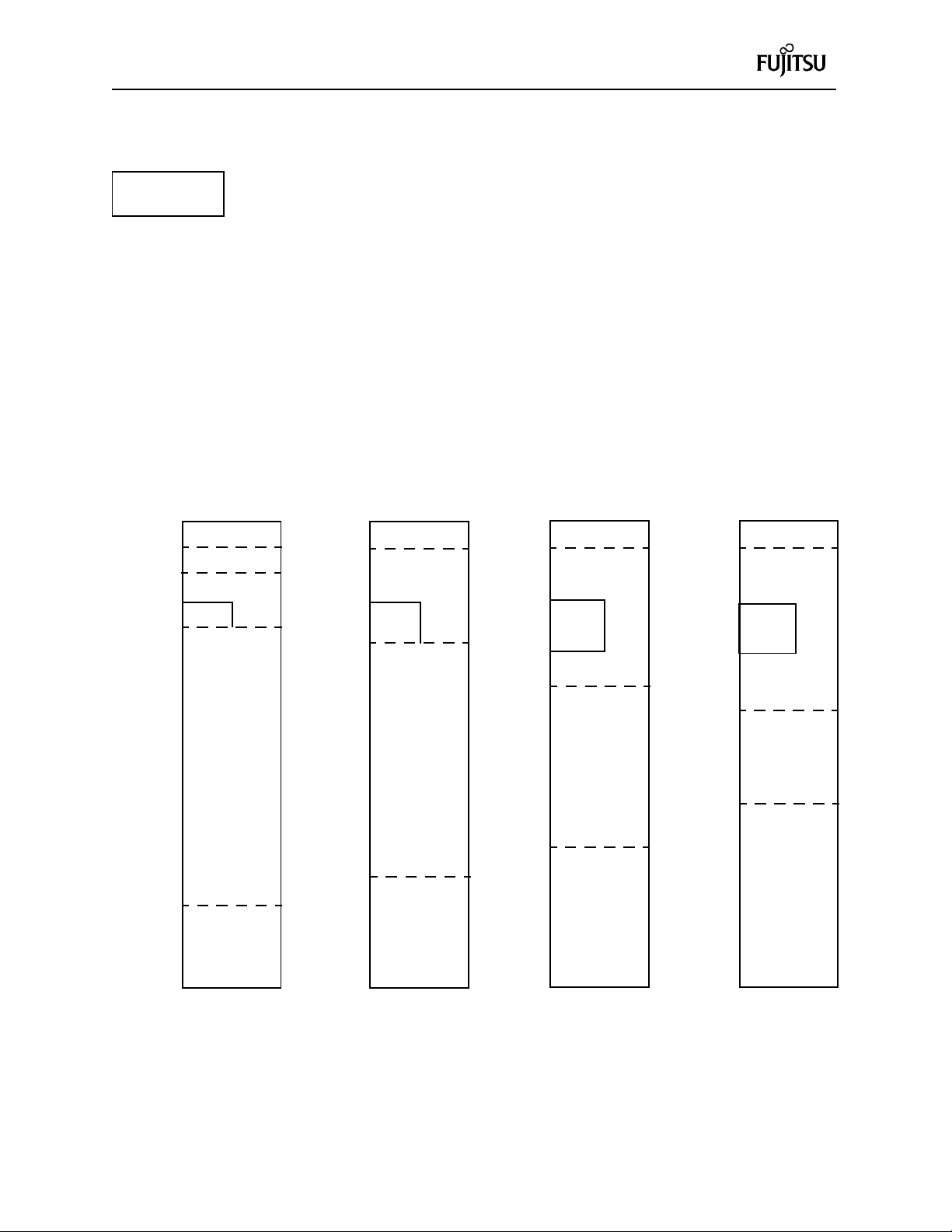

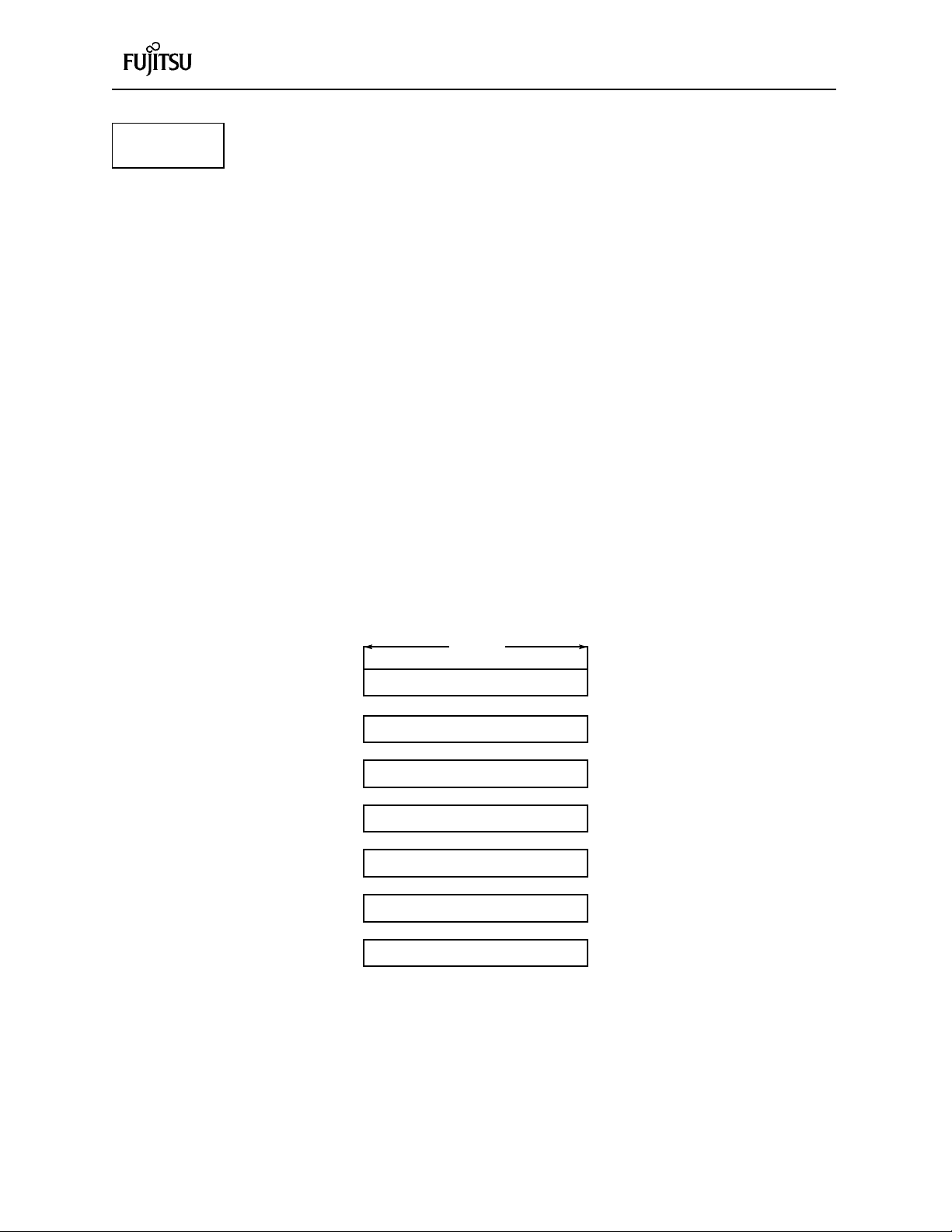

2.1.1 Memory Space

F2MC-8L CPU has a memory space of 64 Kilobytes. All I/O, data, and

program areas are located in this space. The I/O area is near the lowest

address and the data area is immediately above it. The data area can be

divided into register, stack, and direct-address areas according to the

applications. The program area is located near the highest address, and

the tables of interrupt and reset vectors and vector-call instructions are at

the highest address in this area. Fig.2.1 shows the structure of the

memory space for the MB89950 series of microcontrollers.

MB89PV950

H

H

H

Register

H

I/O

RAM

0000

0080

0100

0180

H

H

H

Register

H

MB89953

I/O

RAM

0000

0080

0100

0200

0280

H

H

H

Register

H

H

MB89P955

I/O

RAM

0000

0080

0100

0200

F000

0480

H

Vacant

E000

H

ROM

Vacant

C000

H

ROM

Vacant

8000

H

ROM

Vacant

H

ROM

Fig. 2.1 Memory Space of MB89950 Series Microcontrollers

2– 3

Page 19

HARDWARE CONFIGURATION

CPU

(1) I/O area

This area is where various peripherals such as control and data registers

are located. The memory map for the I/O area is given in APPENDIX A.

(2) RAM area

This area is where the static RAM is located. Addresses from

017F

(

H

0100

H

to

013F

in MB89951,

H

0100

to

H

01FF0

in MB89P955 and

H

0100

H

to

MB89PV950) are also used as the general-purpose register area. One can

access these registers through register-related instructions or just treat

them as ordinary RAM.

(3) ROM area

This area is wh ere the in ternal ROM is locate d. Addres ses from

are also used for the table of interrupt, reset and vector-call

FFFF

H

FFC0

H

to

instructions. T able 2–1 shows the correspondence between each interrupt

number or reset and the table addresses to be referenced for the MB89950

series of microcontrollers.

Table 2–1 Table of Reset and Interrupt Vectors

CALLV #0

CALLV #1

CALLV #2

CALLV #3

CALLV #4

CALLV #5

CALLV #6

CALLV #7

Table address

Upper data Lower data

FFC0

FFC2

FFC4

FFC6

FFC8

FFCA

FFCC

FFCE

H

H

H

H

H

H

H

H

FFC1

FFC3

FFC5

FFC7

FFC9

FFCB

FFCD

FFCF

H

H

H

H

H

H

H

H

Interrupt #B

Interrupt #A

Interrupt #9

Interrupt #8

Interrupt #7

Interrupt #6

Interrupt #5

Interrupt #4

Interrupt #3

Interrupt #2

Interrupt #1

Interrupt #0

Reset mode

Reset vector

FFFC

Note:

FFFD

is already reserved . W hen using

H

in the reset mode, write

H

Table address

Upper data Lower data

00

FFE5

FFE7

FFE9

FFEB

FFED

FFEF

FFF1

FFF3

FFF5

FFF7

FFF9

FFFB

FFFF

.

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

FFE4

H

FFE6

H

FFE8

H

FFEA

H

FFEC

H

FFEE

H

FFF0

H

FFF2

H

FFF4

H

FFF6

H

FFF8

H

FFFA

H

----- FFFD

FFFE

H

2– 4

Page 20

HARDWARE CONFIGURATION

CPU

Before execution

A

1234

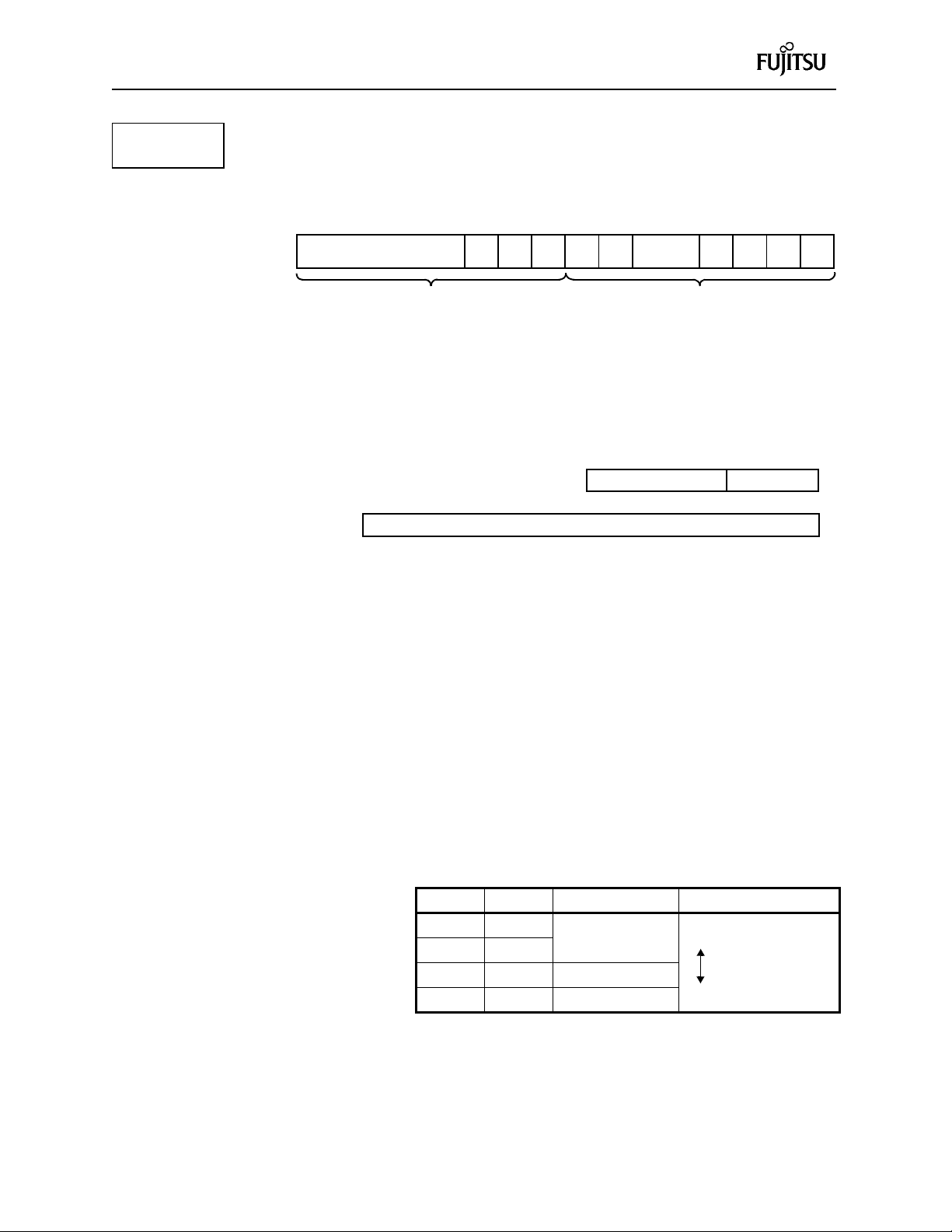

2.1.2 Arrangement of 16-bit Data in Memory Space

When the MB89950 series of microcontrollers handle 16-bit data, the data

written at the lower address is treated as the upper 8-bit data and that written

at the next address is treated as the lower 8-bit data as shown in Fig. 2.2.

Memory

MOVW ABCDH , A

ABCF

H

ABCE

H

ABCD

ABCC

H

H

H

Fig. 2.2 Arrangement of 16 bit Data in Memory Space

This is the same when 16 bits are specified by the operand during execution

of an instruction. Bits closer to the OP code are treated as the upper byte

and those next to it are treated as the lower byte. This is also the same

when the memory address or 16-bit immediate data is specified by the

operand.

After execution

1234

A

Memory

ABCF

H

34

H

ABCE

H

12

H

ABCD

ABCC

H

H

H

[Example]

MOV A, 5678

MOV A, #1234

; Extended address

H

; 16-bit immediate data

H

Assemble

XXXXH XX XX

60 56 78

XXXX

XXXX

XXXX

H

H

H

E4 12 34

XX

; Extended address

; 16-bit immediate data

Fig. 2.3 Arrangement of 16 bit Data during Execution of Instruction

Data saved in the stack by an interrupt is also treated in the same manner.

2– 5

Page 21

HARDWARE CONFIGURATION

CPU

2.1.3 Internal Registers in CPU

The MB89950 series of microcontrollers have dedicated registers in the

CPU and general-purpose registers in memory. The types of dedicated

registers are as follows.

•

Program counter (PC) 16-bit length register indicating the location

where instruction s ar e stored .

•

Accumulator (A) 16-bit length register storing results of

operations temporarily. The lower one byte

is used to execute 8-bit data processing

instructions.

•

Temporary accumulator (T) 16-bit length register where the operations

are performed between this register and the

accumulator. The lower one byte is used to

execute 8-bit data processing instructions.

•

Index register (IX) 16-bit length register for index modification.

•

Extra pointer (EP) 16-bit length register for indicating memory

address.

•

Stack pointer (SP) 16-bit length register indicating stack area.

•

Processor status (PS) 16-bit length register where register

pointers and condition codes are stored.

16 bits

P C

A

T

IX

EP

SP

PS

Program counter

Accumulator

Temporary accumulator

Index register

Extra pointer

Stack pointer

Processor status

2– 6

Page 22

HARDWARE CONFIGURATION

CPU

for a register bank pointer (RP) and 8 lower bits for a condition code register

(CCR). (See Fig. 2.4.)

The 16 bits of the processor status (PS) can be divided into 8 upper bits

1514131211109876543210

PS

RP

Vacant Vacant Vacant

RP

HI NZVC

IL1, 0

CCR

Fig. 2.4 Structure of Processor Status

The RP indicates the address of the current register bank. The relationship

between the contents of the RP and the real addresses is as shown in

Figure 2.5.

Source address

R P

‘0’ ‘0’ ‘0’ ‘0’ ‘0’ ‘0’ ‘0’ ‘1’ R4 R3 R2 R1 R0 b2 b1 b0

↓↓↓↓↓↓↓↓↓↓↓↓↓↓↓↓

A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

Lower bits of OP code

Fig. 2.5 Rule for Translating Real Addresses at General-purpose Register Area

The CCR has bits indicating the results of operations and transfer data

contents, and bits controlling the CPU operation when an interrupt occurs.

- H-flag H-flag is set when a carry or a borrow out of bit 3 into bit 4

is generated as a result of operations; it is cleared in other

cases. This flag is used for decimal-correction instructions.

- I-flag An interrupt is enabled when this flag is 1 and is disabled

when it is 0. The I-flag is 0 at reset.

- IL1 and IL0 These bits indicate the level of the currently-enabled

interrupt. The CPU executes interrupt processing only when

an interrupt with a value smaller than the value indicated by

this bit is requested.

IL1 IL0 Interrupt level High and low

00

1

High

01

10 2

11 3

low = No interrupt

- N-flag The N-flag is set when the most significant bit is 1 as a result

of operations; it is cleared when the MSB is 0.

2– 7

Page 23

HARDWARE CONFIGURATION

CPU

- Z-flag Z-flag is set when zero is the result of operations; it is

cleared in other cases.

- V-flag V -flag is set when a two’s complement overflow occurs as a

result of operations; it is reset when an overflow does not

occur.

- C-flag C-flag is set when a carry or a borrow out of bit 7 is generated

as a result of operations; it is cleared in other cases. When

the shift instruction is executed, the value of the C- flag is

shifted out.

•

General-purpose register..... 8-bit length register where data are stored.

8-bit general-purpose registers are provided in the register banks in the

memory for storing data. Eight registers are provided per bank for and up

to 16 banks can be used for MB89953 (8 banks are provided in MB89951,

32 banks are provided in MB89P955 and MB89PV950).

The register bank pointer (RP) indicates the currently-used bank.

Note: The register banks are as follows depend on RAM area.

MB89951

MB89953

MB89P955

MB89PV950

0100

0100

0100

0100

H

H

H

H

to

to

to

to

013F

017F

01FF

01FF

8 banks

H

16 banks

H

32 banks

H

32 banks

H

Address =

0100

+ 8*(RP)

H

Memory area

Fig. 2.6 Register Bank Configuration

R0

R1

R2

R3

R4

R5

R6

R7

16 banks

2– 8

Page 24

HARDWARE CONFIGURATION

CPU

Clock

oscillator

2.1.4 Clock Control Block

This block controls the standby operation and software reset.

(1) Machine clock control block diagram

(a) Machine clock control section

STP SLP SPL

Pin state

Stop

CPU operation clock

Clock control

Peripheral operation clock

From time-base timer

Power-on reset

Watchdog timer reset

External reset

Software reset

HC1

HC3

Stop release signal

Selector

Option

(b) Reset control section

Reset control

(2) Register list

Address:

0008

H

8 bits

STBC

Internal reset signal

Standby control register

2– 9

Page 25

HARDWARE CONFIGURATION

CPU

0008

(3) Description of registers

The detail of each register is described below.

STBCAddress:

H

(a) Standby control register (STBC)

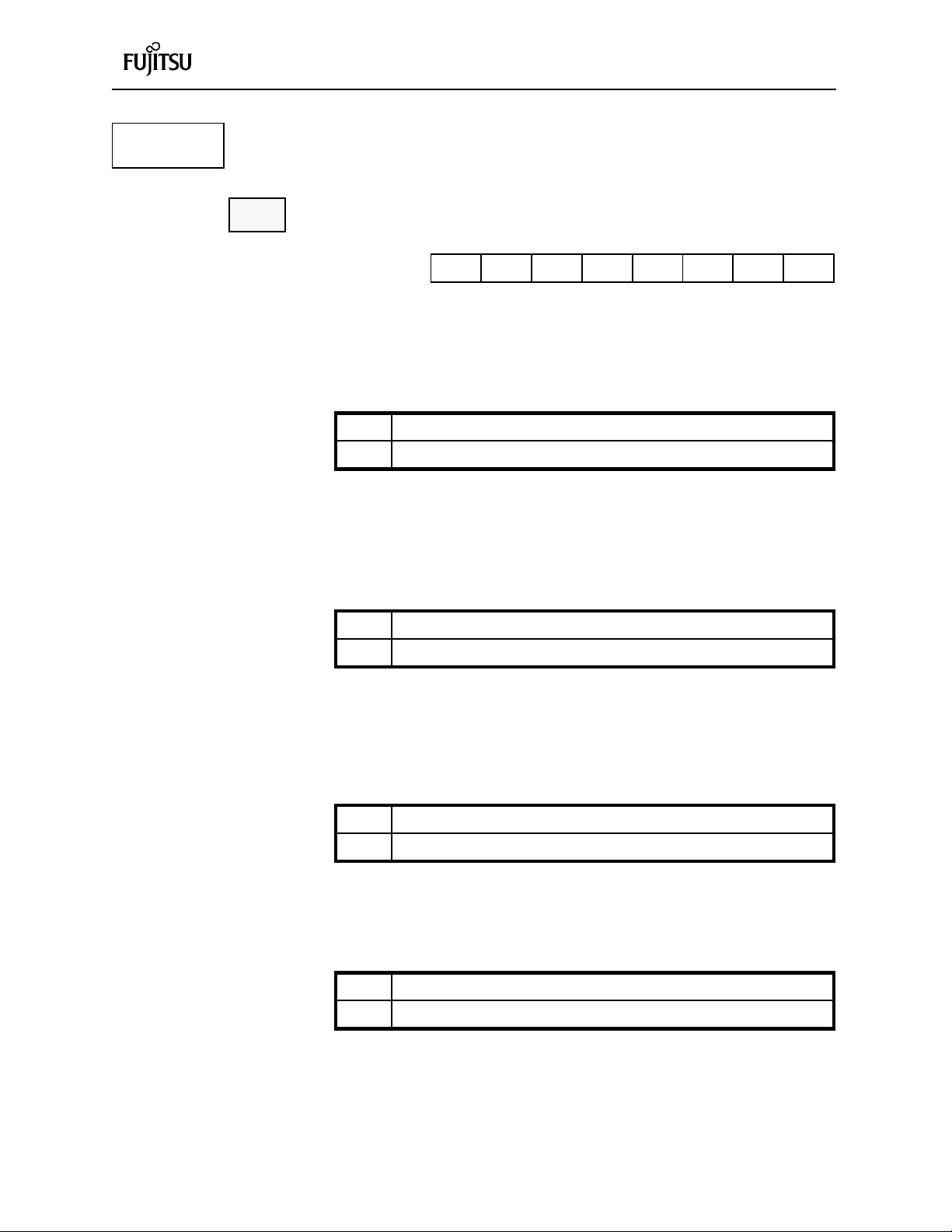

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Address:

0008

STPSLPSPLRST————

H

(W) (W) (R/W) (W )

(Initial value)

0001XXXX

[Bit 7] STP: Stop bit

This bit is used to specify switching CPU to the stop mode.

0

1

No operation

Stop mode

This bit is cleared at reset or stop cancellation.

0 is always read when this bit is read.

[Bit 6] SLP: Sleep bit

This bit is used to specify switching the CPU to the sleep mode.

0

1

No operation

Sleep mode

This bit is cleared at reset, sleep cancellation or stop cancellation.

0 is always read when this bit is read.

[Bit 5] SPL: Pin state specifying bit

This bit is used to specify the external pin state in the stop mode.

0

1

Holds pin state and level immediately before stop mode

High impedance

This bit is cleared at reset.

[Bit 4] RST: Software reset bit

This bit is used to specify the software reset.

0

1

Generates 4-cycle reset signal

No operation

1 is always read when this bit is read.

2– 10

Page 26

HARDWARE CONFIGURATION

CPU

(4) Description of operation

(a) Low-power consumption mode

This chip has three operation modes shown in the table below. The sleep

mode and stop mode reduce the power consumption. The system clock

can be selected out of three according to the system condition to minimize

power consumption.

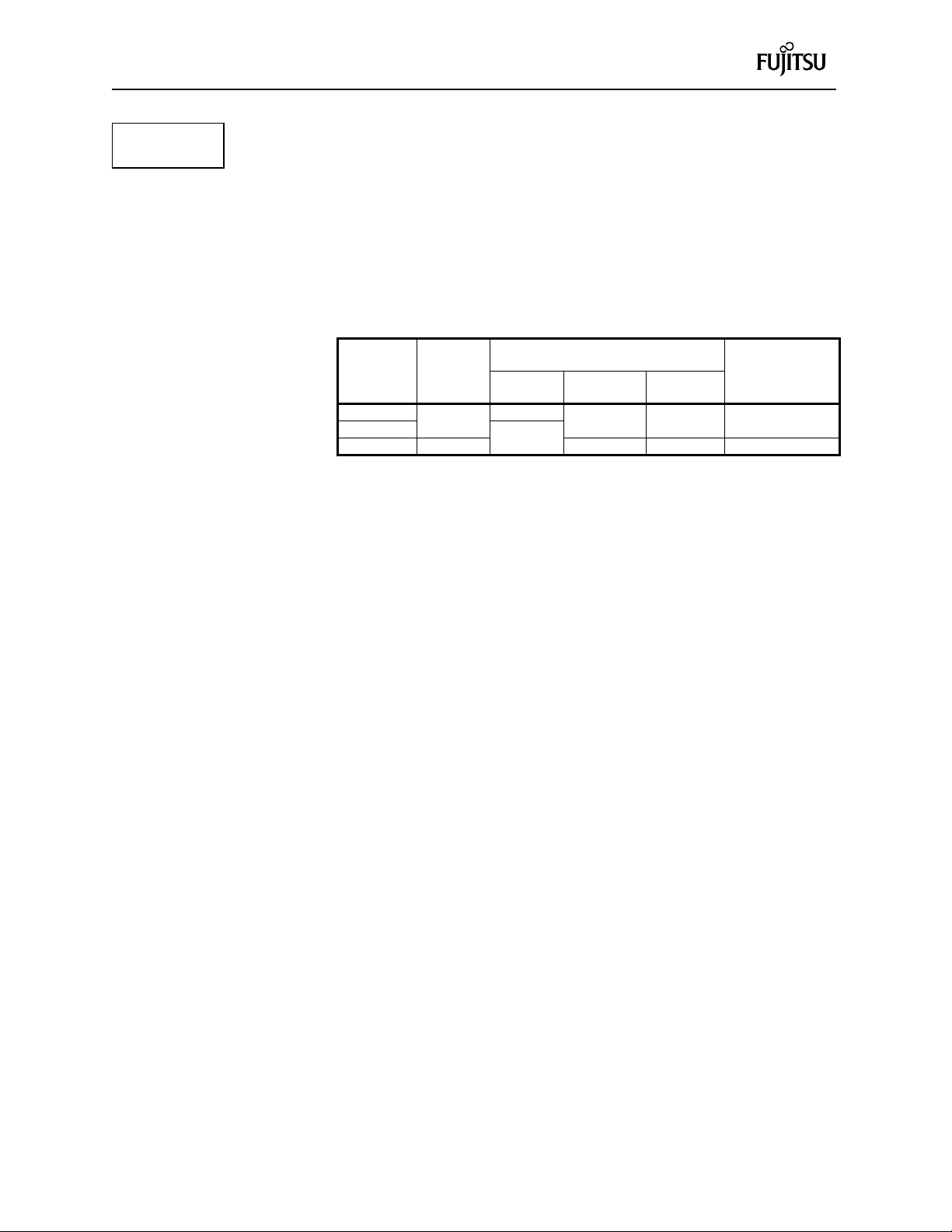

Table 2–2 Operating Mode of Low-power Consumption Modes

Each operating clock pulse

Oscillation

mode

RUN

SLEEP

STOP Stop Stops Stops External interrupt

Clock

pulse

Oscillates

CPU

2.5 MHz

Stops

(5 MHz clock)

Time-base

timer

2.5 MHz 2.5 MHz

peripheral

Each

Wake-up source

in each mode

Various interrupt

requests

• The SLEEP mode stops only the operating clock pulse of the CPU; other

operations are continued.

• The STOP mode stops the oscillation. Data can be held with the lowest

power consumption in this mode.

a. SLEEP mode

• Switching to Sleep mode

- Writing 1 at the SLP (bit 6) of the STBC register switches the mode to

SLEEP mode.

- The SLEEP mode is the mode to stop clock pulse operating the CPU;

only the CPU stops and the peripherals continue to operate.

- If an interrupt is requested when 1 is written at the SLP (bit 6),

instruction ex ecution continues without switching to the SLEEP mode.

- In the SLEEP mode, the contents of registers and RAM immediately

before entering the SLEEP mode are held.

• Canceling SLEEP mode

- The SLEEP mode is canceled by inputting the reset signal or

requesting an interrupt.

- When the reset signal is input during the SLEEP mode, the CPU is

switched to the reset state and the SLEEP mode is canceled.

- When an interrupt level higher than 11 is requested from a peripheral

during the SLEEP mode, the SLEEP mode is canceled.

- When the I flag and IL bit are enable after canceling, the CPU executes

the interrupt processing like an ordinary interrupt. When they are

disabled, the CPU starts processing the next instruction given before

entering the SLEEP mode.

2– 11

Page 27

HARDWARE CONFIGURATION

CPU

b. STOP mode

• Switching to STOP mode

- Writing 1 at the STP (bit 7) of the STBC register switches the mode to

STOP mode.

- The STOP mode stops clock oscillation and the CPU and all

peripherals stop.

- The input/output pins and output pins in the STOP mode can be

controlled by the SPL (bit 5) of the STBC register so that they are held

in the state immediately before entering the STOP mode, or so that

they enter in the high-impedance state.

- If an interrupt is requested when 1 is written at the STP (bit 7),

instruction execution continues without switching to the STOP mode.

- In the STOP mode, the contents of registers and RAM immediately

before entering the STOP mode are held.

• Canceling STOP mode

- The STOP mode is canceled either by inputting the reset signal or by

requesting an interrupt.

- When the reset signal is input during the STOP mode, the CPU is

switched to the reset state and the STOP mode is canceled.

- When an interrupt higher than level 11 is requested from the external

interrupt circuit during the STOP mode, the STOP mode is canceled.

- When the I flag and IL bit are enabled after canceling, the CPU

executes the interrupt processing like an ordinary interrupt. When they

are disabled, the CPU starts processing the next instruction given

before entering the STOP mode.

- The oscillation stabilization time can be selected from the two types

in Table 2–3 as options.

- If the STOP mode is canceled by inputting the reset signal, the CPU

is switched to the oscillation stabilization state. Therefore, the reset

sequence is not executed unless the oscillation stabilization time is

elapsed. The oscillation stabilization time corresponds to the

optionally selected oscillation stabilization time of the main clock.

However, when Power-on reset unavailable is selected by the mask

option, the CPU is not switched to the oscillation stabilization state

even if the STOP mode is canceled by inputting the reset signal.

Table 2–3 Selection of Oscillation Stabilization Time

Oscillation

stabilization time

18

14

/f

CH

/f

CH

About 2

About 2

Oscillation stabilization

Remarks

time at 5 MHz

About 52.4 ms For crystal oscillator

About 3.28 ms For crystal oscillator

2– 12

Page 28

HARDWARE CONFIGURATION

CPU

(b) State transition diagram

STOP

Clock stops.

(8)

(3)

Oscillation stabilization

waiting

(7)

SLEEP

Clock oscillates.

(5)

(4)

Clock oscillates.

(9)

RUN

(1) (2)

Power-on

(1) When power-on reset available selected

(2) When power-on reset unavailable selected

(3) After oscillation stabilizing

(4) Set STP bit to 1.

(5) Set SLP bit to 1.

(7) External reset when power-on reset unavailable selected

(8) External reset or interrupt when power-on reset available selected

(9) External reset or interrupt

2– 13

Page 29

HARDWARE CONFIGURATION

CPU

(c) Reset

There are four types of reset depending on the source shown in Table 2–4.

Table 2–4 Sources of Reset

Reset name Description

External-pin reset

Software reset

Watchdog reset

Power-on reset

When the power-on reset or reset during the stop state is used, the

oscillation stabilization time is needed after the oscillator starts operating.

The time-base timer controls this stabilization time. Consequently, the

operation does not start immediately even after canceling the reset.

Howev er, if P ower-on reset is not selected by the mask option, no oscillation

stabilization time is required in any state after external pins have been

released from the reset.

When setting external-reset pin to Low

When writing 0 at RST (bit 4) of STBC

When watchdog timer overflows

When turning power on

Note: A longer time than the optionally-specified oscillation stabilization

time should be allowed for reset at power-on of P ower-on reset

unavailable products. In other cases, the time is based on theorist

timing given in the

characteristics.”

MB89950 SERIES DATA SHEET

“AC

2– 14

Page 30

HARDWARE CONFIGURATION

CPU

Peripheral #1

F2MC-8L bus

Test

register

G L

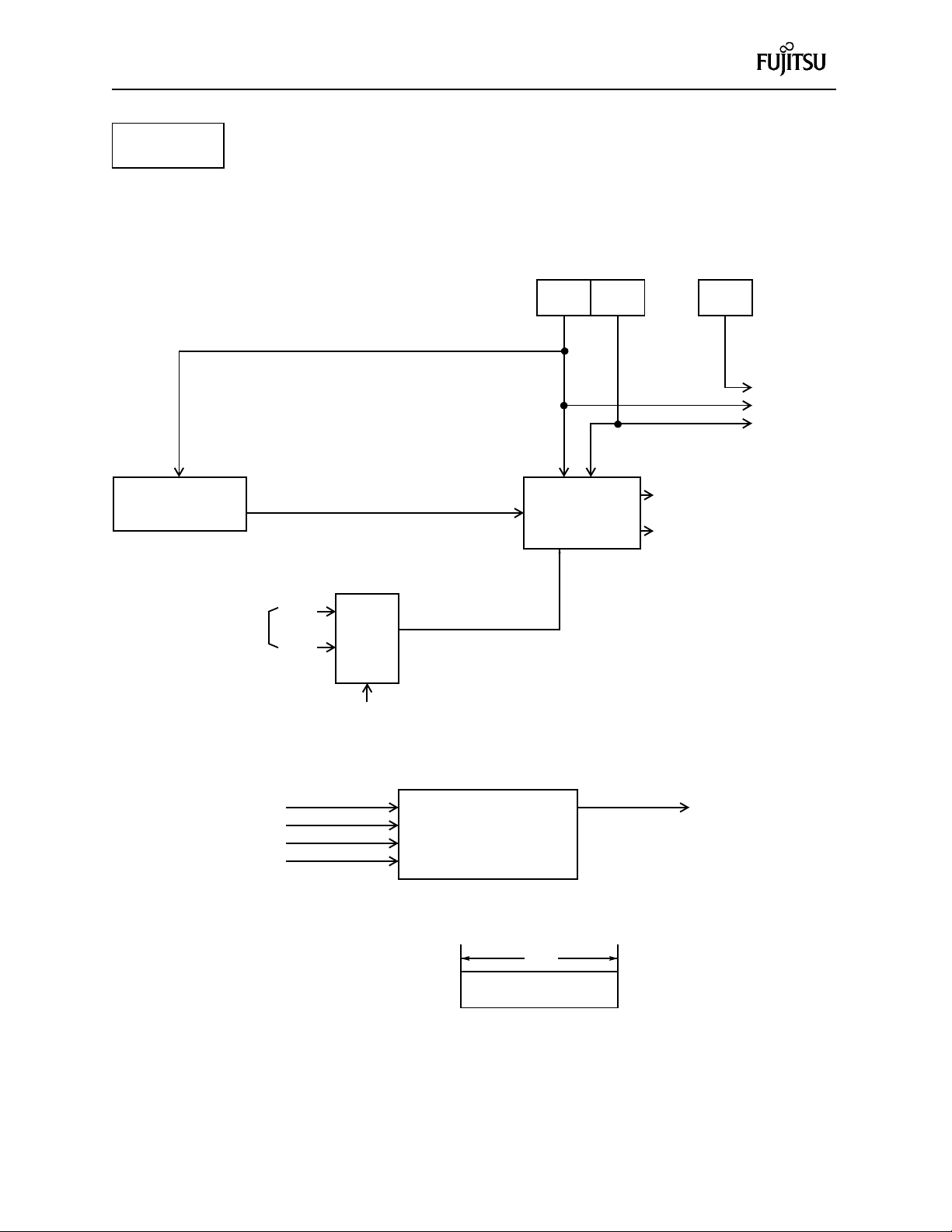

2.1.5 Interrupt Controller

The interrupt controller for the F2MC-8L family is located between the CPU

and each peripheral. This controller receives interrupt requests from the

peripherals, assigns priority to them. When the interrupt controller transfers

the priority to the CPU, it also decides the priority of same-level interrupts.

(1) Block diagram

CPU

2

Address decoder

Level

G

Peripheral #2

•

•

Peripheral #n

G

•

•

•

G

L

•

•

•

L

Level

•

•

•

Level

•

•

•

Level

deciding

block

G

G

Same level

priority

deciding

block

Interrupt

vector

generation

•

block

•

•

(2) Register list

Interrupt controller consists of interrupt-level registers (ILR1, 2, and 3) and

interrupt-test register (ITR).

8 bits

Address:

Address:

Address:

Address:

007C

007D

007E

007F

H

H

H

H

ILR1

ILR2

ILR3

ITR

W Interrupt level register #1

W Interrupt level register #2

W Interrupt level register #3

— Interrupt test register

2– 15

Page 31

HARDWARE CONFIGURATION

CPU

Address:

Address:

Address:

Address:

[Example]

007C

007D

007E

007F

Interrupt requests

from peripherals

ILR1

H

ILR2

H

ILR3

H

ITR

H

(3) Description of registers

The details of each register is described below.

(a) Interrupt level register 1 to 3 (ILRx: Interrupt Level Register x)

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Address:

Address:

Address:

007C

007D

007E

L31 L30 L21 L20 L11 L10 L01 L00

H

L71 L70 L61 L60 L51 L50 L41 L40

H

LB1 LB0 LA1 LA0 L91 L90 L81 L80

H

(W) (W) (W) (W) (W ) (W) (W) (W)

(Initial value)

11111111

B

The ILRx sets the interrupt level of each peripheral. The digits in the center

of each bit correspond to the interrupt numbers.

MB89820 hardware manual

L3X

Interrupt control module

IR0

IR1

IR2

IR3

IRB

Interrupt

number

#0

#1

#2

#3

#11

Table address

Upper Lower

FFFA

FFF8

FFF6

FFF4

FFE4

FFFB

FFF9

FFF7

FFF5

FFE5

007C

007D

007E

007F

[Bits 7 and 6][Bits 5 and 4][Bits 3 and 2][Bits 1 and 0]Lx1, Lx0: Interrupt

level setting bit

Lx1 Lx0 Required interrupt level

0

1

1

X

0

1

1

2

3 (None)

When an interrupt is requested from a peripheral, the interrupt controller

transfers the interrupt level based on the value set at the 2 bits of the ILRx

corresponding to the interrupt to the CPU.

(b) Interrupt test register (ITR)

ILR1Address:

H

ILR2Address:

H

ILR3Address:

H

ITRAddress:

H

Address:

007F

The ITR is used for testing. Do not access it.

Bit 7 Bit 6 Bit 5 Bit 4 B it 3 Bit 2 Bit 1 Bit 0

——————

H

(Initial value)

XXXXXX00

B

**

(—) (—)

2– 16

Page 32

HARDWARE CONFIGURATION

CPU

(4) Description of operation

The functions of interrupt controllers are described below.

(a) Interrupt functions

The MB89950 series of microcontrollers have 7 inputs for interrupt requests

from the peripherals. The interrupt level is set by 2-bit registers

corresponding to each input. When an interrupt is requested from a

peripheral, the interrupt controller receives it and transfers the contents of

the correspo ndi ng level register to the C PU. The interrupt to the de vice is

processed as follows:

(1) An interrupt source is generated inside a peripheral.

(2) If an interrupt is enabled after referring to the interrupt-enable bit

inside the peripheral, an interrupt request is output from the

peripheral to the interrupt controller.

(3) After receiving this interrupt request, the interrupt controller

determines the priority of simultaneously-requested interrupts and

then transfers the interrupt level for the applicable interrupt to the

CPU.

(4) The CPU compares the interrupt level requested from the interrupt

controller with the IL bi t in the processor status register.

(5) As a result of the comparison, if the interrupt level has priority over

the current interrupt processing level, the contents of the I-flag in the

same processor status register are checked.

(6) As a result of the check in step (5), if the I-flag is enabled for an

interrupt, the contents of the IL bit are set to the required level. As

soon as the currently-executing instruction is terminated, the CPU

performs the interrupt processing and transfers control to the

interrupt-processing routine.

(7) When an interrupt source is cleared by software in the user’s interrupt

processing routine, the CPU terminates the interrupt processing.

Fig. 2.7 outlines the interrupt operation for the MB89950 series of

microcontrollers.

Internal bus

Register file

IPLA IR

(6)

CPU

Peripheral

Enable FF

AND

(7)

Source FF

(1)

Peripheral

(2)

Fig. 2.7 Interrupt-processing Flowchart

2– 17

PS I IL

Check Comparator

(5) (4)

(3)

Level

comparator

Interrupt controller

Page 33

Peripherals

Pin Input Type Output

Type

P00 to

P07

P10 to

P17

P20 to

P25

P30 to

P33

P40 to

P45

CMOS N-ch

open drain

CMOS N-ch

open drain

CMOS N-ch

open drain

CMOS N-ch

open drain

CMOS CMOS

Hysteresis Timer serial/external

push-pull

HARDWARE CONFIGURATION

2.2 Peripherals

2.2.1 I/O Ports

• The MB89950 series of microcontrollers have fiv e par alle l ports (33 pins).

Ports 0 and 1 serve as 8-bit I/O ports; port 2 serves 6-bit I/O port; port

3 serves as 4-bit I/O ports; port 4 serves as 7-bit I/O port.

• Ports 0, 1, 2, 3 and 4 are also used as peripherals.

(1) List of port functions

Table 2–5 List of Port Functions

Function bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 b it 1 bit 0

Parallel port 0 P07 P06 P05 P04 P03 P02 P01 P00

Segment output SEG 27

—————————————

Parallel port 1 P17 P16 P15 P14 P13 P12 P11 P10

Segment port 1 SEG 35

Parallel port 2

Parallel port 3

LCD voltage

Parallel port 4

interrupt

—————————————

——

——

————

————

—

INT0 SCK SO SI PWC

—

P25 P24 P23 P22 P21 P20

SEG41

————————

P33 P32 P31 P30

V2 V1

P46 P45 P44 P43 P42 P41 P40

/INT1

SEG20

SEG28

SEG36

——

PWM

—

Address:

Address:

Address:

Address:

Address:

Address:

0000

0002

0004

000C

000E

000F

(2) Register list

I/O port consists of the following registers.

8 bits

H

H

H

H

H

H

PDR0

PDR1

PDR2

PDR3

PDR4

DDR4

R/W Port 0 data register

R/W Port 1 data register

R/W Port 2 data register

R/W Port 3 data register

R/W Port 4 data register

W Port 4 data direction register

Initi al value = 11111111

Initi al value = 11111111

Initi al value = 11111111

Initi al value = 11111111

Initial value = XXXXXXXX

Initial value = X0000000

B

B

B

B

B

B

2– 18

Page 34

HARDWARE CONFIGURATION

Peripherals

(3) Description of functions

The function of each port is described below.

P00 to P07: N-ch open-drain type input/output ports

(also used as segment output)

P10 to P17: N-ch open-drain type input/output ports

(also used as segment output)

P20 to P25: N-ch open-drain type input/output ports

(also used as segment output)

• Operation for output port

The value written at the PDR is output to the pin. When the PDR is read,

usually, the value of the pin is read instead of the contents of the output

latch. However , when the Read Modify Write instruction is executed, the

contents of the output latch are read. Therefore, the bit-processing

instruction can be used even if input and output are mixed with each other.

• Operation for input port

When using these ports as input ports, set 1 at the PDR and turn the

output transistor off. The value of the pin can always be read when the

PDR is read. When the segment output is selected by the LCD controller

port/segment select bit, the input data is always read as 0.

• Operation for segment output

When using these ports as segment outputs, the segment output must

be selected by the mask option. When segment output is selected using

the LCD controller port/segment select bit, these ports can be used as

segment outputs.

• State at reset

At reset, these ports serve as port inputs. The PDR is initialized to 1 and

the output transistor is turned off at all bits.

• State in stop mode

For segment output, the output state when the CPU enters the stop mode

is held. For port output, the pins states in stop mode are controlled by

SPL bit in standby control register (STBC).

When SPL=0, pin states before entering stop mode are held.

When SPL=1, port pins go high impedance in stop mode.

2– 19

Page 35

Peripherals

HARDWARE CONFIGURATION

Internal-data bus

PDR

PDR read

PDR read

(when Read Modify Write instruction

executed)

Output latch

PDR write

Stop, SPL = 1

Fig. 2.8 Ports 0, 1 and 2

Note: Selection of segment output using the mask option is available only

for mass-produced products. The mask option must be consistent

with LCD segment output select register (SEGR).

Segment output select register

Stop, SPL = 1

Segment output

Mask option

(Note)

Pin

N-ch

2– 20

Page 36

HARDWARE CONFIGURATION

Peripherals

P30, P31: N-ch open-drain output, CMOS input

P32, P33: N-ch open-drain type input/output ports

(also used as LCD controller power supply V1,V2)

• Operation for output port

The value written at the PDR is output to the pin. When the PDR is read,

usually, the value of the pin is read instead of the contents of the output

latch. However , when the Read Modify Write instruction is executed, the

contents of the output latch are read. Therefore, the bit-processing

instruction can be used even if input and output are mixed with each other.

• Operation for input port

When using these ports as input ports, set 1 at the PDR and turn the

output transistor off. The value of the pin can always be read when the

PDR is read. When V1/V2 is selected by PSEL bit of LCDR, the input

data is always read as 0.

• Operation for V1 and V2

The PSEL bit in LCDR (see page 2-60) must be cleared in order to choose

P32/P33 as LCD controller power supply.

• State at reset

At reset, these ports serve as LCD controller power supply . The PDR is

initialized to 1 and the output transistor is turned off at all bits. Since PSEL

bit of LCDR will be reset to zero (see page 2-60), therefore P32/P33 will

be configured to V1/V2 right after reset.

• State in stop mode

If P32/P33 is chosen as V1/V2 and stop mode is triggered, the voltage

at those pins before stop mode will be held. For port output, the pins

states in stop mode are controlled by SPL bit in standby control register

(STBC).

When SPL=0, pin states before entering stop mode are held.

When SPL=1, port pins go high impedance in stop mode.

2– 21

Page 37

HARDWARE CONFIGURATION

Internal-data bus

PDR

PDR read

PDR read

(when Read Modify Write instruction

executed)

Output latch

PDR write

Stop, SPL = 1

Fig. 2.9 Port 3

Only for P32 and P33

PSEL of LCDR

V1/ V2

Stop

Pin

N-ch

2– 22

Page 38

HARDWARE CONFIGURATION

Peripherals

P40 to P46: CMOS type I/O ports

(also used as peripheral input and output)

• Switching input and output

This port has a data-direction register (DDR) and a port-data register

(PDR) for each bit. Input and output can be set independently for each

bit. The pin with the DDR set to 1 is set to output, and the pin with the

DDR set to 0 is set to input. When the peripheral output bit is enabled,

these ports are set to output irrespective of the DDR setting conditions.

• Operation for output port (DDR = 1)

The value written at the PDR is output to the pin where the DDR is set

to 1. When the PDR is read, usually, the value of the pin is read instead

of the contents of the output latch. However , when the Read Modify Write

instruction is executed, the contents of the output latch are read

irrespective of the DDR setting conditions. Therefore, the bit-processing

instruction can be used even if input and output are mixed with each

other. When data is written to the PDR, the written data is held in the

output latch irrespective of the DDR setting conditions.

• Operation for input port (DDR = 0)

When used as the input port, the output impedance goes High.

Therefore, when the PDR is read, the value of the pin is read.

• Peripheral output operation

When using as the peripheral output, setting is performed by the

peripheral output enable bit (See the description of each peripheral). The

peripheral output enable bit has priority in switching input and output.

Even if the output from each peripheral is enabled, the read value of the

port is effective, so the peripheral output value can be checked.

• Peripheral input operation

The pin value at a port with the peripheral input function is always input

for the peripheral input irrespective of the setting of the DDR and

peripheral. Set the DDR to input when using an external signal for the

peripheral input.

• State when reset

When reset, the DDR is initialized to 0 and the output impedance goes

High at all bits. When reset, the PDR is not initialized. Therefore, set

the value of the PDR before setting the DDR to output.

• State in stop mode

With the SPL bit of the standby-control register set to 1, the output

impedance goes High in stop mode irrespective of the value of the DDR.

2– 23

Page 39

Peripherals

HARDWARE CONFIGURATION

External interrupt enable

Stop, SPL = 1

To external interrupt

Stop, SPL = 1

Peripheral input

Internal-data bus

PDR

PDR read

PDR read

(when Read Modify Write instruction executed)

Output latch

PDR write

DDR

DDR write

Stop, SPL = 1

Fig. 2.10 Port 4

Peripheral

output

Peripheral

output enable

Pull-up resistor

(option)

P-ch

P-ch

Pin

N-ch

2– 24

Page 40

HARDWARE CONFIGURATION

Peripherals

IRQ2

2.2.2 8-bit PWM Timer (Timer 1)

• This timer can be used as an 8-bit timer or PWM control circuit with

8-bit resolution.

• Four kinds of clock frequency can be selected.

(1) Block diagram

Internal-data bus

P/T

CNTR

P/T — P1 P0 TRE TIR 0E TIE

COMR

Start

CLK

CLEAR

OVER FLOW

Compare register

8-bit

counter

8

CPU clock pulse*

Timer-2 output

(PWC timer)

Selector

1/2

1/32

1/128

* CPU clock pulse is 1/2 oscillation.

(2) Register list

Address:

Address:

Timer/

PWM

0012

0013

8

Comparator

PWM generator and

output control

Output

enable

Output

P41/PWM

8 bits

H

H

CNTR

COMR

R/W Control register

W Compare register

signal

2– 25

Page 41

HARDWARE CONFIGURATION

Peripherals

Address:

Address:

0012H

0013H

CNTR

COMR

(3) Description of registers

(a) Control register (CNTR)

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Address:

0012

P/T — P1 P0 TPE TIR OE TIE

H

(R/W) (R/W) (R/W) (R/W) (R/W) (R/W) (R/W)

(Initial value)

0X000000

B

[Bit 7] P/T: Timer/PWM operation mode switching bit

The operation is performed as the ti mer whe n bit 7 i s set to 0, and as the

0

Timer

1

PWM control circuit

When switching, set channel to stop counting (TPE = 0), interrupt disabled

(TIE = 0) and interrupt request flag cleared (TIR = 0).

[Bits 5 and 4] P1 and P0: Clock-pulse select bits

Clock pulses from the prescaler or WT0 output of timer 2 (pulse-width count

timer) can be selected using P1 and P0.

P1 P0 Clock cycle

0

0

1

1

Internal clock pulse 1 instruction cycle

0

Internal clock pulse 16 instruction cycles

1

Internal clock pulse 64 instruction cycles

0

Timer 2 cycle

1

Note that these bits must not be rewritten when the counter is operating

(TPE = 1).

[Bit 3] TPE: Counting enable bit

When these bits are set to 1, the timer or PWM control circuit starts

operation.

0

Stops counting

1

Starts counting

[Bit 2] TIR1: PWM channel interrupt request flag bit

Bit 2 goes to 1 when an interrupt source occurs. To clear the generated

interrupt source, write 0 at this bit. The meaning of bit to be read is as

follows:

2– 26

Page 42

HARDWARE CONFIGURATION

Values of counter and COMR do not match.

0

Values of counter and COMR match.

1

Peripherals

Note that 1 is always read when the Read Modify Write instruction is

executed.

The meaning of each bit to be written is as follows:

0

Clears this bit

1

Does not change this bit nor affect other bits

Note: In the PWM operation mode, neither the read nor write values of

these bits have any meaning.

[Bit 1] OE: Output signal control bit

When bit 1 is 1, the port serves as the PWM timer output. In the timer

operation mode, a signal that is reversed each time the values of the counter

and the compare register match is output. In the PWM operation mode, a

PWM signal is output.

0

General-purpose ports (P41)

1

Counter/PWM output pins (PWM)

Even if the DDR of P41 is set for input (bit 1 of DDR4 is set to 1), when this

bit is 1, it serves as the counter/PWM output pin.

Address:

Address:

0012H

0013H

CNTR

COMR

[Bit 0] TIE: Interrupt enable bit (Timer mode)

If bit 0 is set to 1, an interrupt occurs when the values of the counter and

the compare register match.

0

Disables counter interrupt output

1

Enables counter interrupt output

However, in the PWM operation mode, an interrupt does not occur

irrespective of the value of this bits.

(b) Compare register (COMR)

This register holds the value to be compared with the counter value in the

timer operation mode, and also clears the counter when the value agrees

with the counter value. In the PWM operation mode, the High pulse width

can be specified by this register value.

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Address:

0013

H

(W) (W) (W) (W) (W ) (W) (W) (W)

(Initial value)

XXXXXXXX

B

2– 27

Page 43

HARDWARE CONFIGURATION

Peripherals

Count-clock pulse

TPE

P41/PWM

TIR bit setting

(4) Description of operation

(a) Timer function

Setting the P/TX bit of the CNTR to 0 gives the timer-operation mode. When

the TPE bit of the CNTR is set to 1, the counter starts incrementing from

. When the value of the counter agrees with that of the COMR, the

00

H

counter is cleared on the next count clock pulse and incrementing restarts.

Therefore, the TIR bits are set and the output pin is reversed (but, when

the TPE bit is 0, the output pin is fixed at Low level) in cycles of the count

clock pulses when

than those of the count clock pulses when

is written at the COMR, or in cycles 256 times longer

00

H

is written.

FF

H

If the value of the COMR is rewritten in the timer-operation mode, it becomes

effective from the next cycle (when the value of the counter is

, the value

00

H

of the COMR is transferred to the comparator latch).

00 00 00 00 00 01 FF 00

Value of COMR

00 FF

Fig. 2.11 Timer Operation

If the TIE bit of the CNTR is set to 1, an interrupt occurs when the values

of the counter and COMR match. During interrupt processing, the TIR bit

is used as the interrupt flag. The TIR bit is set irrespective of the value of

the TIE bit. However, if the values of the counter and COMR match, the

TIR bit is set to 1 even after an interrupt is disabled.

Writing 0 at the TIR bit permits clearing of the interrupt source or the TIR

bit. When the Read Modify Write instruction is read, the TIR bit is set so

that 1 can always be read to prevent erroneous clearing.

By using P0 and P1 bit in CNTR, 1 out of 4 clock sources can be selected

for the counter.

2– 28

Page 44

HARDWARE CONFIGURATION

Wh

COMR i

Peripherals

•

en

Counter value

PWM pulse output

•

When COMR is

Counter value

PWM pulse output

(b) PWM operation

Setting the P/TX bit of the CNTR to 1 gives the PWM operation mode. The

COMR specifies the duty of the output pulse. Pulses can be output with

1/256 resolution and a duty of 0% to 99.6%.

When 0 (

0%; when 128 (

) is written at the COMR, the duty of the PWM output pulse is

00

H

) is written, the duty is 50%, and when 255 (

80

H

FF

written, it is 99.6%.

The value of COMR is transferred to the comparator latch when the value

of the counter is

. If the value of the COMR is rewritten in the PWM

00

H

operation mode, it becomes effective from the next cycle.

At starting (counter = 00), output is high. When the counter matches the

compare register, output goes low.

00

s

H

80

••••••••• •••••••

00

H

H

••••• •••••

00

H

80

••••• •••••

H

FF

00

H

H

••••• •••••

00

FF

H

H

H

80

) is

H

•

When COMR is

Counter value

comparison match

FF

H

••••••••• •••••••••

00

H

FF

H

00

H

Fig. 2.12 PWM Pulse Output

In the PWM operation mode, the values at the TIR bit of the CNTR have

no meaning. No interruption occurs even if the TIE bit are 1.

The cycle of the PWM pulse can be changed by switching the count clock

pulse.

The count clock pulse can be selected from three clock pulses of the

prescaler and the clock pulse of the internal timer by the clock pulse select

bits P1 and P0 of the CNTR.

2– 29

Page 45

Peripherals

Internal-data bus

HARDWARE CONFIGURATION

2.2.3 Pulse-width Count Timer (Timer 2)

• This timer has timer and pulse-width measurement functions.

• The timer function has two modes: reload timer and one-shot.

• In the reload timer mode, the set values are counted down repeatedly.

• In the one-shot mode, counting down is started from the set values and

stops at the first underflow.

• The pulse-width measurement function enables measurement of High,

Low, or one-cycle widths of pulses input from pins.

• For inputting from pins, the 5-bit noise-clearing circuit is selectable.

(1) Block diagram

PCR2

NCCR

PCR1

Function switching circuit

Timing generator

8-bit down counter

RLBR

Selector

Input-pulse edge

detector

1/2

1/8

1/64

Noise clear

CPU clock pulse*

Selector

To PWM timer

IRQ3

From time-base

timer

P42/PWC/

INT1

* The CPU clock pulse is an oscillation-divided pulse.

2– 30

Page 46

HARDWARE CONFIGURATION

[

Peripherals

0014

0015

0016

0017

(2) Register list

8 bits

Address:

Address:

Address:

Address:

0014

0015

0016

0017

H

H

H

H

PCR1

PCR2

RLBR

NCCR

R/W Pulse-width control register 1

R/W Pulse-width control register 2

R/W Reload buffer register

R/W Noise-clear control register

(3) Description of registers

PCR1Address:

H

PCR2Address:

H

RLBRAddress:

H

NCCRAddress:

H

(a) Pulse-width control register 1 (PCR1)

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Address:

0014

EN — IE — — UF IR BF

H

(R/W) (R/W) (R/W) (R/W) (R/W) (R)

Bit 7] EN: Count enable bit

(Initial value)

000XX000

B

At the timer function, when 1 is written at this bit, the value of the data

register is loaded to start counting down. When 0 is written, counting down

stops. At the pulse-width measurement function, when 1 is written at this

bit, the measurement-enable state is set. Under this condition, counting

down is started when the edge of the measured pulse is detected. When

0 is written at this bit during measurement, counting down stops; the count

is not transferred to the reload buffer register (RLBR).

Timer function

0

Count disable

1

Count enable/start

Pulse-width measurement function

Pulse-width measureme nt stop/disable

Pulse-width measurem ent ena ble/start

[Bit 5] IE: Interrupt request enable bit

When bit 5 is 1, an interrupt request is output when the interrupt request

flags (UF, IR, and BF) are set.

0

Interrupt disabled

1

Interrupt enabled

[Bit 2] UF: Underflow interrupt request bit

Bit 2 indicates whether the timer underflowed. The meaning of each bit to

be read is as follows:

0

No underflow

1

Underflow occurred

2– 31

Page 47

HARDWARE CONFIGURATION

[

Peripherals

1 is always read when the Read Modify Write instruction is executed.

The meaning of each bit to be written is as follows:

0

Clears this bit

1