Page 1

FUJITSU SEMICONDUCTOR

CONTROLLER MANUAL

MB89950/950A Series

HARDWARE MANUAL

CM25-10146-1E

F2MC-8L

8-BIT MICROCONTROLLER

Page 2

Page 3

F2MC-8L

8-BIT MICROCONTROLLER

MB89950/950A Series

HARDWARE MANUAL

FUJITSU LIMITED

Page 4

Page 5

PREFACE

■ Objectives and Intended Reader

The MB89950/950A series has been developed as a general-purpose version of the F2MC-8L family

consisting of proprietary 8-bit, single-chip microcontrollers. The MB89950/950A series is applicable to a

wide range of applications from consumer products to industrial equipment, including portable devices.

This manual describes the functions and operation of the MB89950/950A series and is aimed at engineers

using the MB89950/950A series of microcontrollers to develop actual products. See the F

Series Programming Manual for details on the MB89950/950A instruction set.

■ Trademarks

F2MC is the abbreviation of FUJITSU Flexible Microcontroller.

Other system and product names in this manual are trademarks of respective companies or organizations.

TM

The symbols

■ Structure of This Manual

This manual contains the following 12 chapters:

CHAPTER 1 "OVERVIEW"

and ® are sometimes omitted in this manual.

2

MC-8L MB89600

This chapter describes the main features and basic specifications of the MB89950/950A series.

CHAPTER 2 "HANDLING DEVICE"

This chapter describes points to note when using the general-purpose single-chip microcontroller.

CHAPTER 3 "CPU"

This chapter describes the functions and operation of the CPU.

CHAPTER 4 "I/O PORTS"

This chapter describes the functions and operation of the I/O ports.

CHAPTER 5 "TIMEBASE TIMER"

This chapter describes the functions and operation of the timebase timer.

CHAPTER 6 "WATCHDOG TIMER"

This chapter describes the functions and operation of the watchdog timer.

CHAPTER 7 "8-BIT PWM TIMER"

This chapter describes the functions and operation of the 8-bit PWM timer.

CHAPTER 8 "PULSE WIDTH COUNT TIMER (PWC)"

This chapter describes the functions and operation of the pulse width count timer (PWC).

CHAPTER 9 "8-BIT SERIAL I/O"

This chapter describes the functions and operation of the 8-bit serial I/O.

CHAPTER 10 "UART"

This chapter describes the functions and operation of the UART.

CHAPTER 11 "EXTERNAL INTERRUPT CIRCUIT (EDGE)"

This chapter describes the functions and operation of the external interrupt circuit.

i

Page 6

CHAPTER 12 "LCD CONTROLLER/DRIVER"

This chapter describes the functions and operation of the LCD controller/driver.

APPENDIX

This appendix includes I/O maps, instruction lists, and other information.

• The contents of this document are subject to change without notice. Customers are advised to consult with

FUJITSU sales representatives before ordering.

• The information and circuit diagrams in this document are presented as examples of semiconductor device

applications, and are not intended to be incorporated in devices for actual use. Also, FUJITSU is unable to assume

responsibility for infringement of any patent rights or other rights of third parties arising from the use of this

information or circuit diagrams.

• The products described in this document are designed, developed and manufactured as contemplated for general

use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but

are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers

that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to

death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility,

aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control

in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial

satellite).

Please note that Fujitsu will not be liable against you and/or any third party for any claims or damages arising in

connection with above-mentioned uses of the products.

• Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss

from such failures by incorporating safety design measures into your facility and equipment such as redundancy,

fire protection, and prevention of over-current levels and other abnormal operating conditions.

• If any products described in this document represent goods or technologies subject to certain restrictions on export

under the Foreign Exchange and Foreign Trade Law of Japan, the prior authorization by Japanese government will

be required for export of those products from Japan.

©2002 FUJITSU LIMITED Printed in Japan

ii

Page 7

READING THIS MANUAL

■ Notations of the Register Name and Pin Name

Example for description of register name and bit name

●

Notations of a double-purpose pin

●

P22/SCK pin

Some pins can be used by switching their functions using, for example, settings by a program. Each

double-purpose pin is represented by separating the name of each function using "/".

iii

Page 8

■

Documents and Development Tools Required for Development

Items necessary for the development of this product are as follows.

To obtain the necessary documents and development tools, contact a company sales

representative.

Manuals required for development

●

[Check field]

2

MC-8L MB89950/950A series data sheet (provides a table of electrical characteristics and vari-

F

ous examples of this product)

2

MC-8L Programming Manual (manual including instructions for the F2MC-8L family)

F

*

2

MC Family Softune C Compiler Manual (required only if C language is used for develop-

FR/F

ment) (manual describing how to develop and activate programs in the C language)

*

2

FR/F

MC Family Softune Assembler Manual for V3 (manual describing program development

using the assembler language)

*

2

FR/F

MC Family Softune Linkage Kit Manual for V3 (manual describing functions and opera-

tions of the assembler, linker, and library manager

Manuals with the * mark are attached to each product.

Other manuals, such as those for development, are attached to respective products.

Software required for development

[Check field]

Softune V3 Workbench

Softune V3 for personal ICE (required only if the evaluation is performed for the personal-ICE)

Softune V3 for compact ICE (required only if the evaluation is performed for the compact-ICE)

The type of software product is dependent on the OS to be used.

For details, see the F

2

MC Development Tool Catalog or Product Guide.

iv

Page 9

❍

What is needed for evaluation on the one-time PROM microcomputer (if the programming

operation is performed at your side)

[Check field]

Development tools

●

[Check field]

MB89P955

EPROM programmer

(Programmer available for the MBM27C1001)

Package conversion adapter

ROM-64QF2-28DP-8L3

MB89PV950 (piggyback/evaluation device)

Development tool

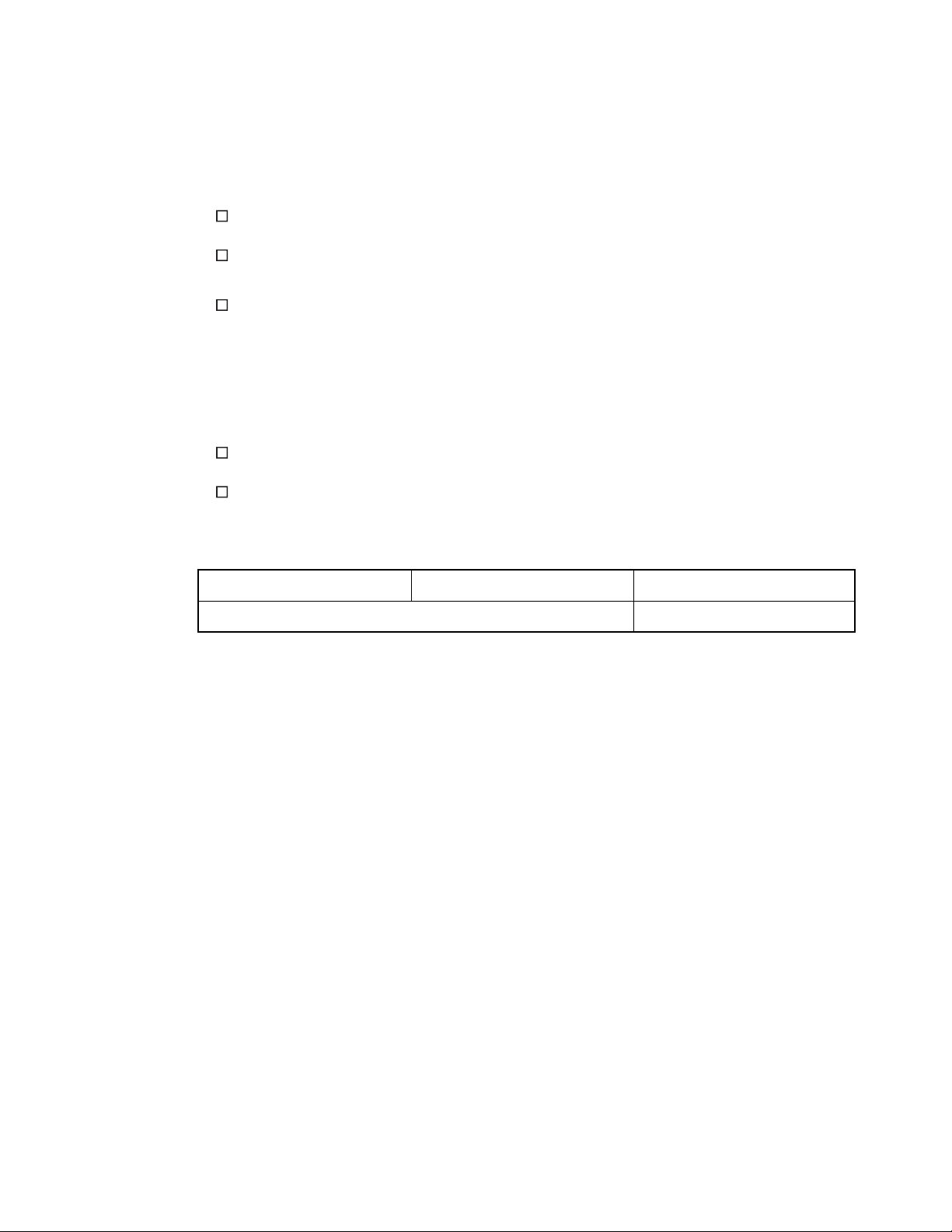

References

●

Main unit Pod Probe

MB2141A + MB2144-505 MB2144-203

To use a the other development environment, contact respective makers.

2

•"F

MC Development Tool Catalog"

• "Microcomputer Product Guide"

v

Page 10

vi

Page 11

CONTENTS

CHAPTER 1 OVERVIEW ................................................................................................... 1

1.1 MB89950/950A Series Features ........................................................................................................... 2

1.2 MB89950/950A Series Product Range ................................................................................................. 4

1.3 Differences among Products ................................................................................................................ 6

1.4 Block Diagram of MB89950/950A Series ............................................................................................ 7

1.5 Pin Assignment ..................................................................................................................................... 8

1.6 Package Dimensions .......................................................................................................................... 10

1.7 I/O Pins and Pin Functions ................................................................................................................. 12

CHAPTER 2 HANDLING DEVICES ................................................................................ 17

2.1 Notes on Handling Devices ................................................................................................................ 18

CHAPTER 3 CPU ............................................................................................................ 21

3.1 Memory Space .................................................................................................................................... 22

3.1.1 Special Areas ................................................................................................................................. 24

3.1.2 Storing 16-bit Data in Memory ....................................................................................................... 26

3.2 Dedicated Registers ........................................................................................................................... 27

3.2.1 Condition Code Register (CCR) .................................................................................................... 29

3.2.2 Register Bank Pointer (RP) ........................................................................................................... 32

3.3 General-purpose Registers ................................................................................................................. 33

3.4 Interrupts ............................................................................................................................................. 35

3.4.1 Interrupt Level Setting Registers (ILR1, ILR2, ILR3) ..................................................................... 36

3.4.2 Interrupt Processing ....................................................................................................................... 37

3.4.3 Multiple Interrupts .......................................................................................................................... 39

3.4.4 Interrupt Processing Time .............................................................................................................. 40

3.4.5 Stack Operation during Interrupt Processing ................................................................................. 41

3.4.6 Stack Area for Interrupt Processing ............................................................................................... 42

3.5 Resets ................................................................................................................................................. 43

3.5.1 External Reset Pin ......................................................................................................................... 45

3.5.2 Reset Operation ............................................................................................................................. 46

3.5.3 Pin States during Reset ................................................................................................................. 48

3.6 Clocks ................................................................................................................................................. 49

3.6.1 Clock Generator ............................................................................................................................. 51

3.6.2 Clock Controller ............................................................................................................................. 53

3.6.3 Oscillation Stabilization Delay Time ............................................................................................... 55

3.7 Standby Mode (Low-power Consumption) ......................................................................................... 57

3.7.1 Operating States in Standby Mode ................................................................................................ 58

3.7.2 Sleep Mode ................................................................................................................................... 59

3.7.3 Stop Mode ..................................................................................................................................... 60

3.7.4 Standby Control Register (STBC) .................................................................................................. 61

3.7.5 State Transition Diagram ............................................................................................................... 63

3.7.6 Notes on Using Standby Mode ...................................................................................................... 65

3.8 Memory Access Mode ........................................................................................................................ 67

vii

Page 12

CHAPTER 4 I/O PORTS .................................................................................................. 69

4.1 Overview of I/O Ports .......................................................................................................................... 70

4.2 Port 0 ................................................................................................................................................. 72

4.2.1 Port 0 Data Register (PDR0) ......................................................................................................... 74

4.2.2 Operation of Port 0 ........................................................................................................................ 75

4.3 Port 1 ................................................................................................................................................. 77

4.3.1 Port 1 Data Register (PDR1) ......................................................................................................... 79

4.3.2 Operation of Port 1 ........................................................................................................................ 80

4.4 Port 2 ................................................................................................................................................. 82

4.4.1 Port 2 Data Register (PDR2) ......................................................................................................... 84

4.4.2 Operation of Port 2 ........................................................................................................................ 85

4.5 Port 3 ................................................................................................................................................. 86

4.5.1 Port 3 Data Register (PDR3) ......................................................................................................... 89

4.5.2 Operation of Port 3 ........................................................................................................................ 90

4.6 Port 4 .................................................................................................................................................. 92

4.6.1 Port 4 Registers (PDR4, DDR4) .................................................................................................... 94

4.6.2 Operation of Port 4 ....................................................................................................................... 96

4.7 Program Example for I/O Ports ........................................................................................................... 98

CHAPTER 5 TIMEBASE TIMER ..................................................................................... 99

5.1 Overview of Timebase Timer ........................................................................................................... 100

5.2 Block Diagram of Timebase Timer ................................................................................................... 102

5.3 Timebase Timer Control Register (TBTC) ........................................................................................ 104

5.4 Timebase Timer Interrupt ................................................................................................................. 106

5.5 Operation of Timebase Timer ........................................................................................................... 107

5.6 Notes on Using Timebase Timer ...................................................................................................... 109

5.7 Program Example for Timebase Timer ............................................................................................. 110

CHAPTER 6 WATCHDOG TIMER ................................................................................ 111

6.1 Overview of Watchdog Timer ........................................................................................................... 112

6.2 Block Diagram of Watchdog Timer ................................................................................................... 113

6.3 Watchdog Timer Control Register (WDTC) ...................................................................................... 115

6.4 Operation of Watchdog Timer ........................................................................................................... 116

6.5 Notes on Using Watchdog Timer ...................................................................................................... 118

6.6 Program Example for Watchdog Timer ............................................................................................ 119

CHAPTER 7 8-BIT PWM TIMER ................................................................................... 121

7.1 Overview of 8-bit PWM Timer ........................................................................................................... 122

7.2 Block Diagram of 8-bit PWM Timer .................................................................................................. 124

7.3 Structure of 8-bit PWM Timer .......................................................................................................... 126

7.3.1 PWM Control Register (CNTR) .................................................................................................... 128

7.3.2 PWM Compare Register (COMR) ............................................................................................... 130

7.4 8-bit PWM Timer Interrupts ............................................................................................................... 131

7.5 Operation of Interval Timer Function ................................................................................................ 132

7.6 Operation of PWM Timer Function ................................................................................................... 134

7.7 States in Each Mode during 8-bit PWM Timer Operation ................................................................. 135

7.8 Notes on Using 8-bit PWM Timer ..................................................................................................... 137

viii

Page 13

7.9 Program Example for 8-bit PWM Timer ............................................................................................ 138

CHAPTER 8 PULSE WIDTH COUNT TIMER (PWC) ................................................... 141

8.1 Overview of Pulse Width Count Timer .............................................................................................. 142

8.2 Block Diagram of Pulse Width Count Timer ..................................................................................... 144

8.3 Structure of Pulse Width Count Timer .............................................................................................. 146

8.3.1 PWC Pulse Width Control Register 1 (PCR1) ............................................................................. 148

8.3.2 PWC Pulse Width Control Register 2 (PCR2) ............................................................................. 150

8.3.3 PWC Reload Buffer Register (RLBR) .......................................................................................... 152

8.3.4 PWC Noise Filter Control Register (NCCR) ................................................................................ 154

8.4 Pulse Width Count Timer Interrupts .................................................................................................. 155

8.5 Operation of Interval Timer Function ................................................................................................ 156

8.6 Operation of Pulse Width Measurement Function ............................................................................ 159

8.7 Operation of Noise Filter Circuit ........................................................................................................ 162

8.8 States in Each Mode during Pulse Width Count Timer Operation .................................................... 163

8.9 Notes on Using Pulse Width Count Timer ........................................................................................ 164

8.10 Program Example for Timer Function of Pulse Width Count Timer .................................................. 165

CHAPTER 9 8-BIT SERIAL I/O ..................................................................................... 169

9.1 Overview of 8-bit Serial I/O ............................................................................................................... 170

9.2 Block Diagram of 8-bit Serial I/O ...................................................................................................... 171

9.3 Structure of 8-bit Serial I/O ............................................................................................................... 173

9.3.1 Serial Mode Register (SMR) ........................................................................................................ 176

9.3.2 Serial Data Register (SDR) .......................................................................................................... 179

9.4 8-bit Serial I/O Interrupts ................................................................................................................... 180

9.5 Operation of Serial Output ............................................................................................................... 181

9.6 Operation of Serial Input ................................................................................................................... 183

9.7 States in Each Mode during 8-bit Serial I/O Operation ..................................................................... 185

9.8 Notes on Using 8-bit Serial I/O ......................................................................................................... 188

9.9 Connection Example for 8-bit Serial I/O ........................................................................................... 189

9.10 Program Example for 8-bit Serial I/O ................................................................................................ 190

CHAPTER 10 UART ........................................................................................................ 193

10.1 Overview of UART ............................................................................................................................ 194

10.2 Structure of UART ............................................................................................................................ 199

10.3 UART Pins ........................................................................................................................................ 202

10.4 UART Registers ................................................................................................................................ 204

10.4.1 Serial Mode Control Register 1 (SMC1) ...................................................................................... 205

10.4.2 Serial Rate Control Register (SRC) ............................................................................................. 207

10.4.3 Serial Status and Data Register (SSD) ........................................................................................ 209

10.4.4 Serial Input Data Register (SIDR) ................................................................................................ 211

10.4.5 Serial Output Data Register (SODR) ........................................................................................... 212

10.4.6 Serial Mode Control Register 2 (SMC2) ...................................................................................... 213

10.5 UART Interrupts ................................................................................................................................ 215

10.6 Operation of UART ........................................................................................................................... 216

10.7 Operation of Mode 0, 1, 3 ................................................................................................................ 217

10.8 Program Example for UART ............................................................................................................. 220

ix

Page 14

CHAPTER 11 EXTERNAL INTERRUPT CIRCUIT (EDGE) ............................................ 223

11.1 Overview of the External Interrupt Circuit ........................................................................................ 224

11.2 Block Diagram of the External Interrupt Circuit ................................................................................. 225

11.3 Structure of the External Interrupt Circuit ......................................................................................... 226

11.3.1 External Interrupt Control Register (EIC) ..................................................................................... 228

11.4 External Interrupt Circuit Interrupts ................................................................................................... 230

11.5 Operation of the External Interrupt Circuit ........................................................................................ 231

11.6 Program Example for the External Interrupt Circuit .......................................................................... 232

CHAPTER 12 LCD CONTROLLER/DRIVER .................................................................. 233

12.1 Overview of LCD Controller/Driver .................................................................................................. 234

12.2 Block Diagram of LCD Controller/Driver .......................................................................................... 235

12.2.1 LCD Controller/Driver Internal Voltage Divider ............................................................................ 237

12.2.2 LCD Controller/Driver External Voltage Divider ........................................................................... 239

12.3 Structure of LCD Controller/Driver .................................................................................................... 241

12.3.1 LCD Control Register (LCDR) ..................................................................................................... 244

12.3.2 Segment Output Select Register (SEGR) .................................................................................... 246

12.3.3 Display RAM ................................................................................................................................ 248

12.4 Operation of LCD Controller/Driver .................................................................................................. 250

12.4.1 Output Waveforms during LCD Controller/Driver Operation (1/2 Duty Ratio) ............................. 251

12.4.2 Output Waveforms during LCD Controller/Driver Operation (1/3 Duty Ratio) ............................. 254

12.4.3 Output Waveforms during LCD Controller/Driver Operation (1/4 Duty Ratio) ............................. 257

12.5 Program Example for LCD Controller/Driver .................................................................................... 260

APPENDIX ......................................................................................................................... 263

APPENDIX A I/O Map ................................................................................................................................ 264

APPENDIX B Overview of Instructions ....................................................................................................... 266

B.1 Overview of F

B.2 Addressing ..................................................................................................................................... 269

B.3 Special Instructions ........................................................................................................................ 274

B.4 Bit Manipulation Instructions (SETB, CLRB) .................................................................................. 278

B.5 F

B.6 Instruction map ............................................................................................................................... 286

APPENDIX C Mask Options ....................................................................................................................... 287

APPENDIX D Programming Specifications for One-Time PROM And EPROM Microcontroller ................ 289

D.1 Programming Specifications for One-time PROM and EPROM Microcontrollers .......................... 290

D.2 Programming Yield and Erasure .................................................................................................... 293

D.3 Programming to the EPROM with Piggyback/Evaluation Device ................................................... 294

APPENDIX E MB89950/950A Series Pin States ........................................................................................ 295

2

MC-8L Instructions ..................................................................................................................... 279

2

MC-8L Instructions ................................................................................................. 267

INDEX................................................................................................................................... 297

x

Page 15

CHAPTER 1

OVERVIEW

This chapter describes the main features and basic

specifications of the MB89950/950A series.

1.1 "MB89950/950A Series Features"

1.2 "MB89950/950A Series Product Range"

1.3 "Differences among Products"

1.4 "Block Diagram of MB89950/950A Series"

1.5 "Pin Assignment"

1.6 "Package Dimensions"

1.7 "I/O Pins and Pin Functions"

1

Page 16

CHAPTER 1 OVERVIEW

1.1 MB89950/950A Series Features

The MB89950/950A series is a line of the general-purpose, single-chip microcontrollers.

In addition to a compact instruction set, the microcontrollers contain a variety of

peripheral functions such as an LCD controller/driver, UART, a serial I/O, PWC timer,

PWM timer and external interrupts.

■ MB89950/950A series features

Various package options

●

• QFP packages (0.65 mm lead pitch) for MB89951A/MB89953A/MB89P955 only

High speed processing at low voltage

●

Minimum execution time: 0.8 µs/5 MHz

F2MC-8L family CPU core

●

Instruction set optimized for controllers

• Multiplication and division instructions

• 16-bit arithmetic operations

• Test and branch instructions

• Bit manipulation instructions, etc.

Single-clock control system

●

• Main clock: max. 5 MHz

Four types of timer

●

• 21-bit timebase timer

• Watchdog timer

• 8-bit PWM timer (also can be used as an interval timer)

• 8-bit PWC timer

Two types of serial interface

●

• UART

- 5, 7, 8 bits transfer data length

• Serial I/O

LCD controller/driver

●

• 42 segments x 4 commons (max. 168 pixels)

• Built-in LCD voltage divider

2

Page 17

External interrupts (2 channels)

●

• Two channels are independent and capable of wake-up from low-power consumption mode (with an

edge detection function).

Standby mode (low-power mode)

●

• Stop mode (oscillation stops so as to minimize the current consumption).

• Sleep mode (CPU stops so as to reduce the current consumption to approx. 1/3 of normal).

I/O ports: max. 33 channels

●

• General-purpose I/O ports (N-ch open-drain): 22 (Also serve as segment pins)

• General-purpose I/O ports (N-ch open-drain): 4 (2 also serve as LCD bias pins)

• General-purpose I/O ports (CMOS): 7 (6 also serve as peripheral pins)

CHAPTER 1 OVERVIEW

3

Page 18

CHAPTER 1 OVERVIEW

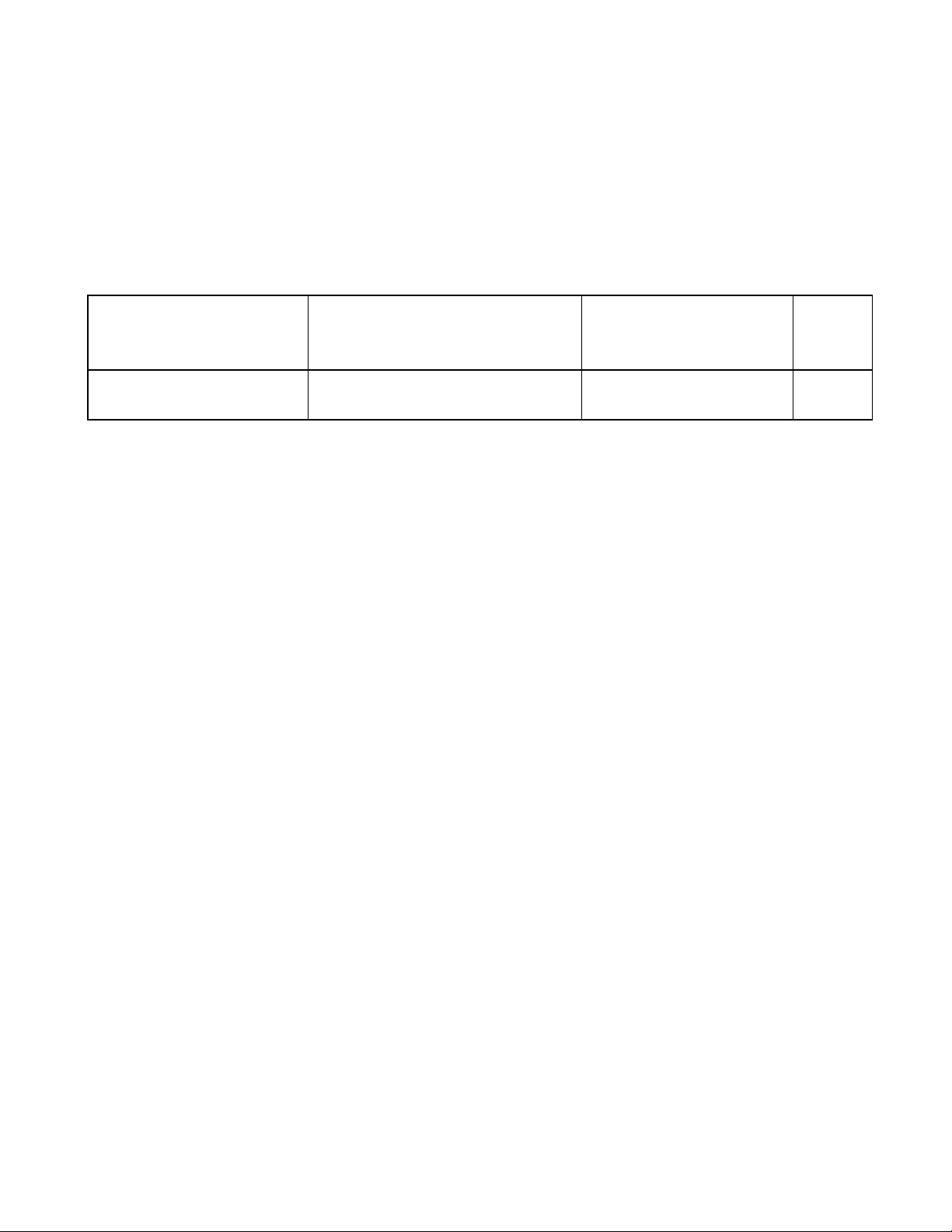

1.2 MB89950/950A Series Product Range

The MB89950/950A series contains 4 different models. Table 1.2-1 "MB89950/950A

series product line-up" lists the product range and Table 1.2-2 "Common specifications

for the MB89950/950A series" lists the common specifications.

■ MB89950/950A series product range

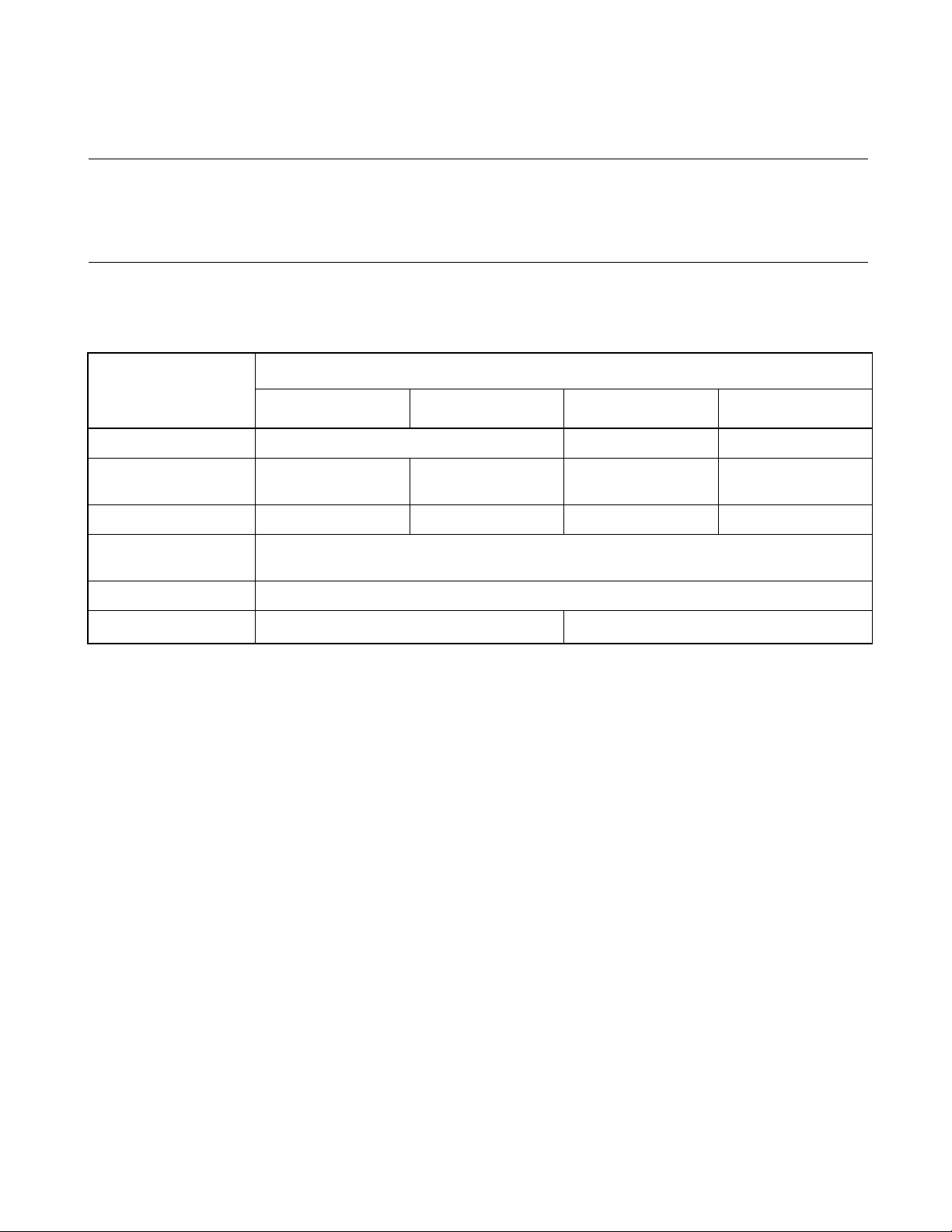

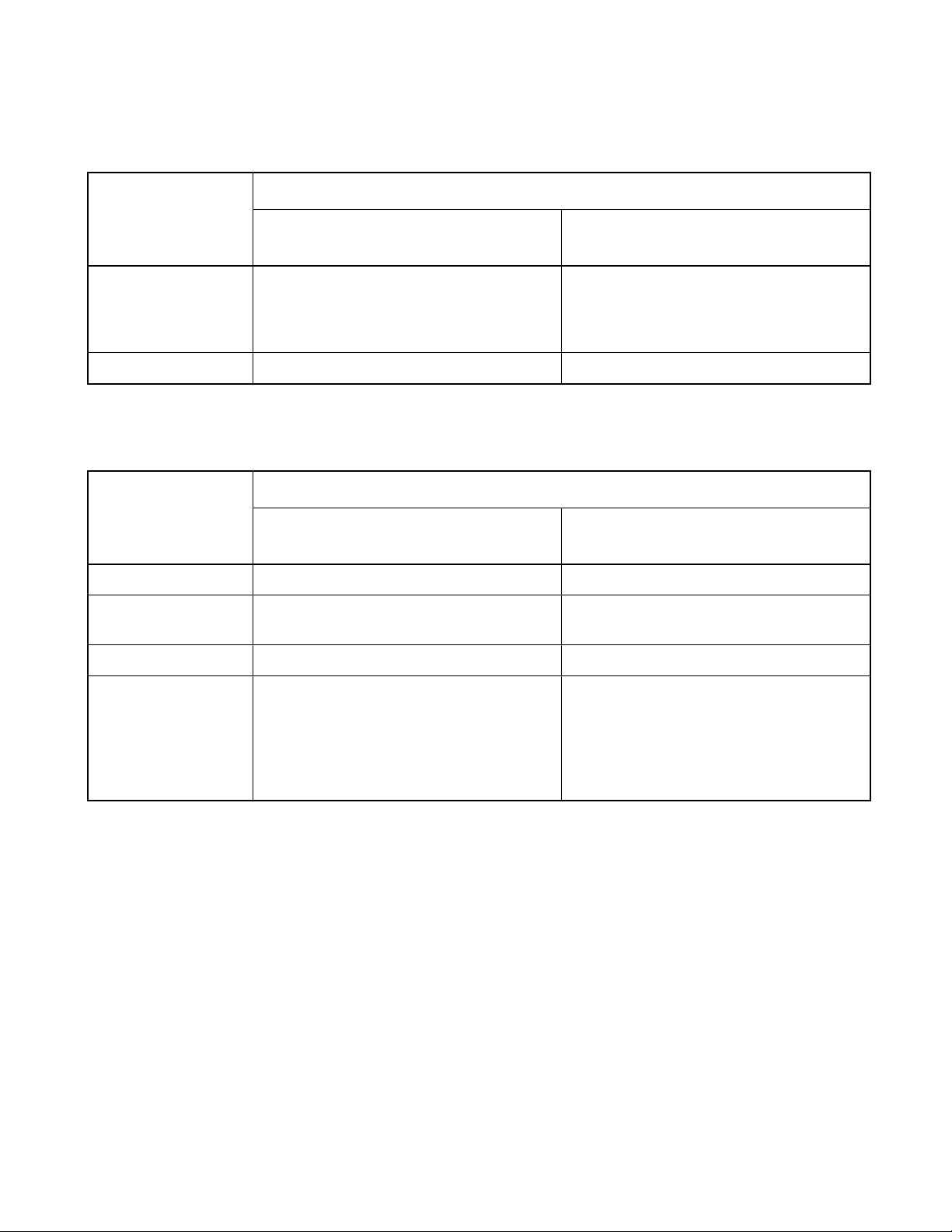

Table 1.2-1 MB89950/950A series product line-up

Part number

MB89951A MB89953A MB89P955

Classification Mask ROM OTP Piggy-back

ROM size 4K x 8 bits

(internal mask ROM)

RAM size 128 x 8 bits 256 x 8 bits 512 x 8 bits 1024 x 8 bits

Low-power consumption

(Standby mode)

Process CMOS

Operating voltage

*1: Varies with conditions such as operating frequencies.

*2: Use MBM27C256A as the external ROM

*1

2.7 V to 5.5 V 2.7 V to 6.0 V

8K x 8 bits

(internal mask ROM)

Sleep mode and stop mode

16K x 8 bits

(internal OTP)

MB89PV950

32K x 8 bits

(external ROM)

*2

4

Page 19

Table 1.2-2 Common specifications for the MB89950/950A series

Parameter Specification

CPU functions Number of instructions: 136

Instruction bit length: 8 bits

Instruction length: 1 to 3 bytes

Data bit length: 1, 8, 16 bits

Minimum execution time: 0.80 µs to 12.8 µs at 5 MHz

Interrupt processing time: 7.26 µs to 115.2 µs at 5 MHz

CHAPTER 1 OVERVIEW

Peripheral

functions

Ports

20-bit timebase

timer

Watchdog timer Reset generate cycle: min. 419.4 ms at 5 MHz

8-bit PWM

timer

PWC timer 8-bit interval timer operation

UART Transfer data length: 5, 7, 8 bits

8-bit serial I/O 8 bits

General-purpose I/O ports (N-ch open-drain): 22 (also serve as LCD segment pins)

General-purpose I/O ports (N-ch open-drain): 4 (two also serve as LCD bias pins)

General-purpose I/O ports (CMOS): 7 (6 ports serve as peripherals)

Total: 33 (max.)

20 bits

Interrupt cycle: 6.55 ms, 26.21 ms, 104.86 ms, 419.43 ms at 5 MHz

8-bit reload timer operation (square wave output; operating frequency: 0.8 µs, 12.8 µs,

51.2 µs at 5 MHz)

8-bit resolution PWM operation (conversion frequency: 204.8 µs - 3.36 s)

Event count function

8-bit pulse width measurement (continuous measurement, High-width, Low-width measurement and

One-cycle measurement)

Operation clock (0.8 µs, 3.2 µs, 25.6 µs at 5 MHz)

Internal baud rate generator (Max. 78125 bps at 5 MHz)

LSB first/MSB first selectability

One clock selectable from four transfer clocks (one external shift clock, three internal shift clocks: 1.6

µs, 6.4 µs, 25.6 µs at 5 MHz)

*1

LCD controller/

driver

External

interrupt

Note:

Unless otherwise specified, values given for clock cycle, conversion times, etc. are for 5 MHz operation.

*1: Segment pins can be selected by mask option.

Common output: 4 (max.)

Segment output: 42 (max.)

Operation mode: 1/2 bias and 1/2 duty, 1/3 bias and 1/3 duty, 1/3 bias and 1/4 duty

LCD display RAM size: 21 bytes (42 x 4 bits, max. 168 pixels)

Dividing voltage for LCD driving: built-in/external voltage divider selectable

2 independent channels (interrupt vector, request flag, request output enable)

Edge selectability (rising/falling)

5

Page 20

CHAPTER 1 OVERVIEW

1.3 Differences among Products

This section describes the differences among the 4 products in the MB89950/950A

series and lists points to note in product selection.

■ Differences among products and points to note for product selection

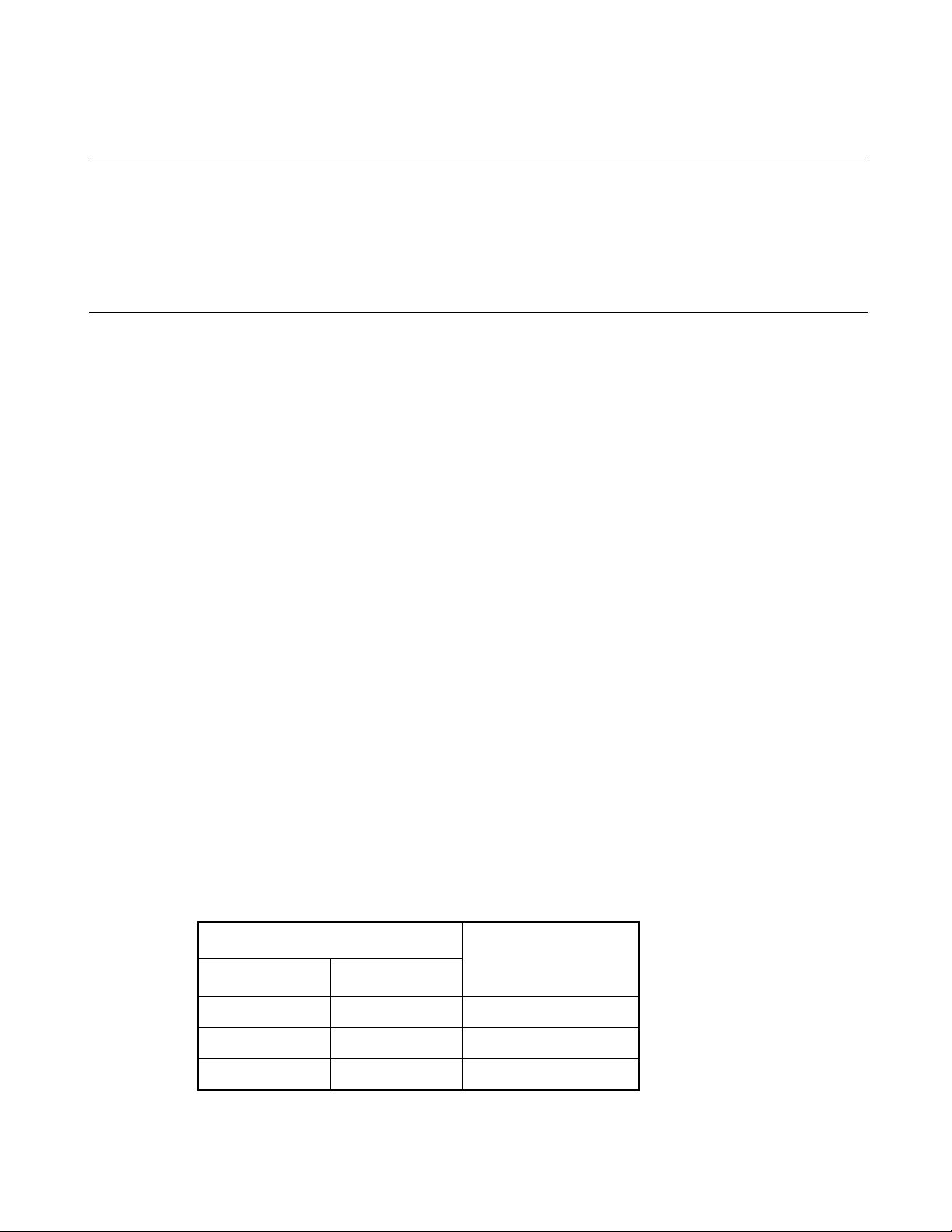

Table 1.3-1 Package and corresponding products

Package Part number

MB89951A MB89953A MB89P955 MB89PV950

FPT-64P-M09

(LQFP-64, 0.65 mm pitch)

MQP-64C-P01

(MQFP-64, 1 mm pitch)

: Available

X: Not available

Current consumption

●

• In the case of the MB89PV950, add the current consumed by the EPROM, which is connected to the top

socket.

• When operated at low speed, the product with a one-time PROM (OTPROM) or an EPROM will

consume more current than the product with mask ROM. However the current consumption in sleep/

stop mode, is the same.

For more information about the package, see Section 1.6 "Package Dimensions".

• For more information about the current consumption, see the electrical characteristics in the Data Sheet.

Mask options

●

X

XXX

Functions that can be selected as options and how to designate these options vary from product to product.

Before using, check Appendix C, "Mask Options".

Take particular care on the following points:

• In the MB89951A and MB89953A, the number of common and segment outputs is specified by Data

Release Form.

• Options are fixed on the MB89PV950. (See Appendix C, "Mask Options")

6

Page 21

CHAPTER 1 OVERVIEW

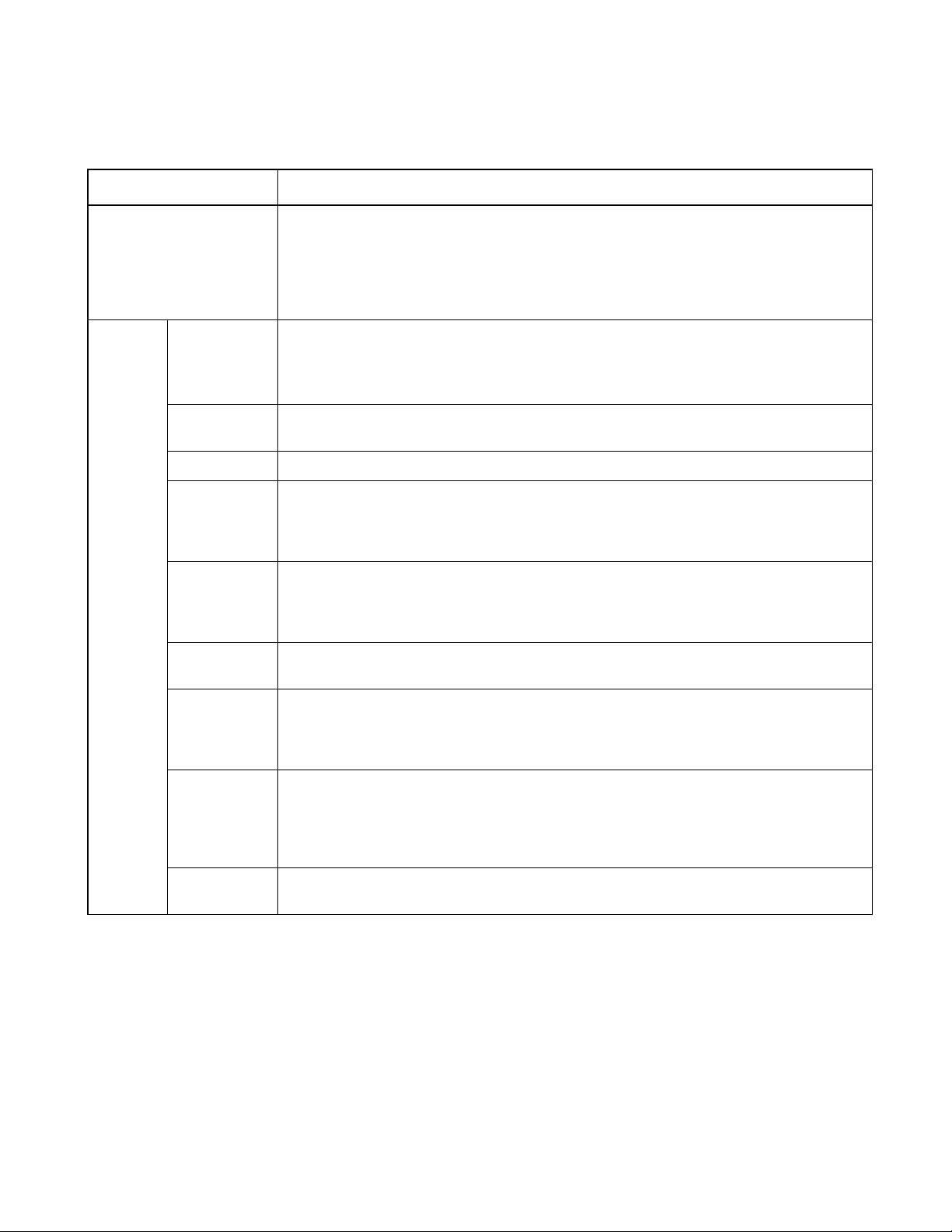

1.4 Block Diagram of MB89950/950A Series

Figure 1.4-1 "MB89950/950A series overall block diagram" shows the block diagram of

the MB89950/950A series.

■ MB89950/950A series block diagram

Figure 1.4-1 MB89950/950A series overall block diagram

X0

X1

RST

Other pins

MODA

V

, VSS

CC

Clock control circuit

(Watchdog timer)

Timebase timer

R A M

2

MC-8L

F

CPU

R O M

Main oscillator

circuit

Reset circuit

Internal bus

8-bit PWM timer

External interrupt

8-bit

pulse width

count timer

8-bit serial I/O

UART

CMOS I/O port

N-ch open-drain I/O port

LCD controller/driver

N-ch open-drain I/O port

Noise

filter

Port 4

Port 0/1/2

Port 3

P41/PWM

P40

P42/PWC/

INT1

P45/SCK

P44/SO

P43/SI

P46/INT0

8

P00/SEG20 to

P07/SEG27

8

P10/SEG28 to

P17/SEG35

6

P20/SEG36 to

P25/SEG41

20

SEG0 to

SEG19

4

COM0 to

COM3

V3

P33/V2

2

P32/V1

2

P30, P31

7

Page 22

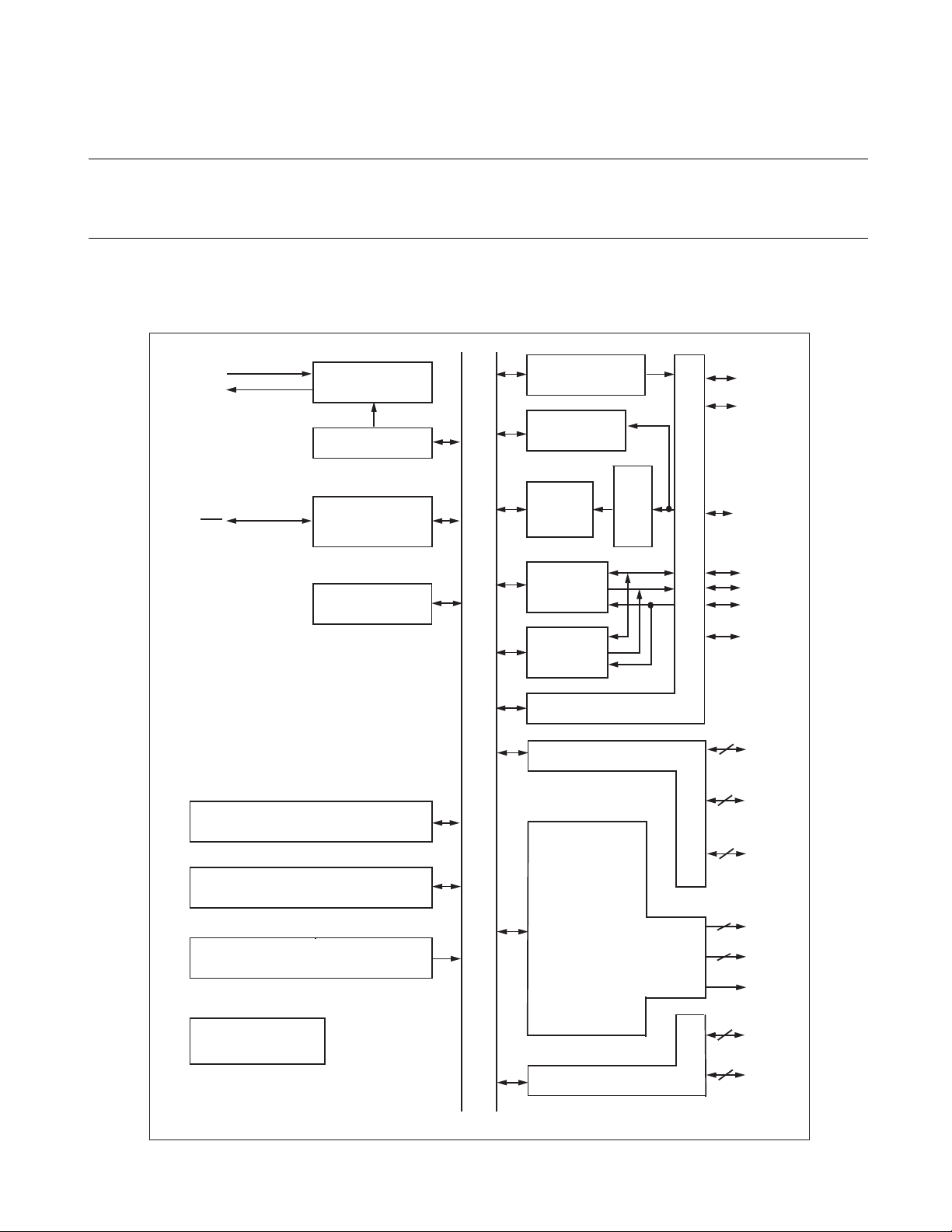

CHAPTER 1 OVERVIEW

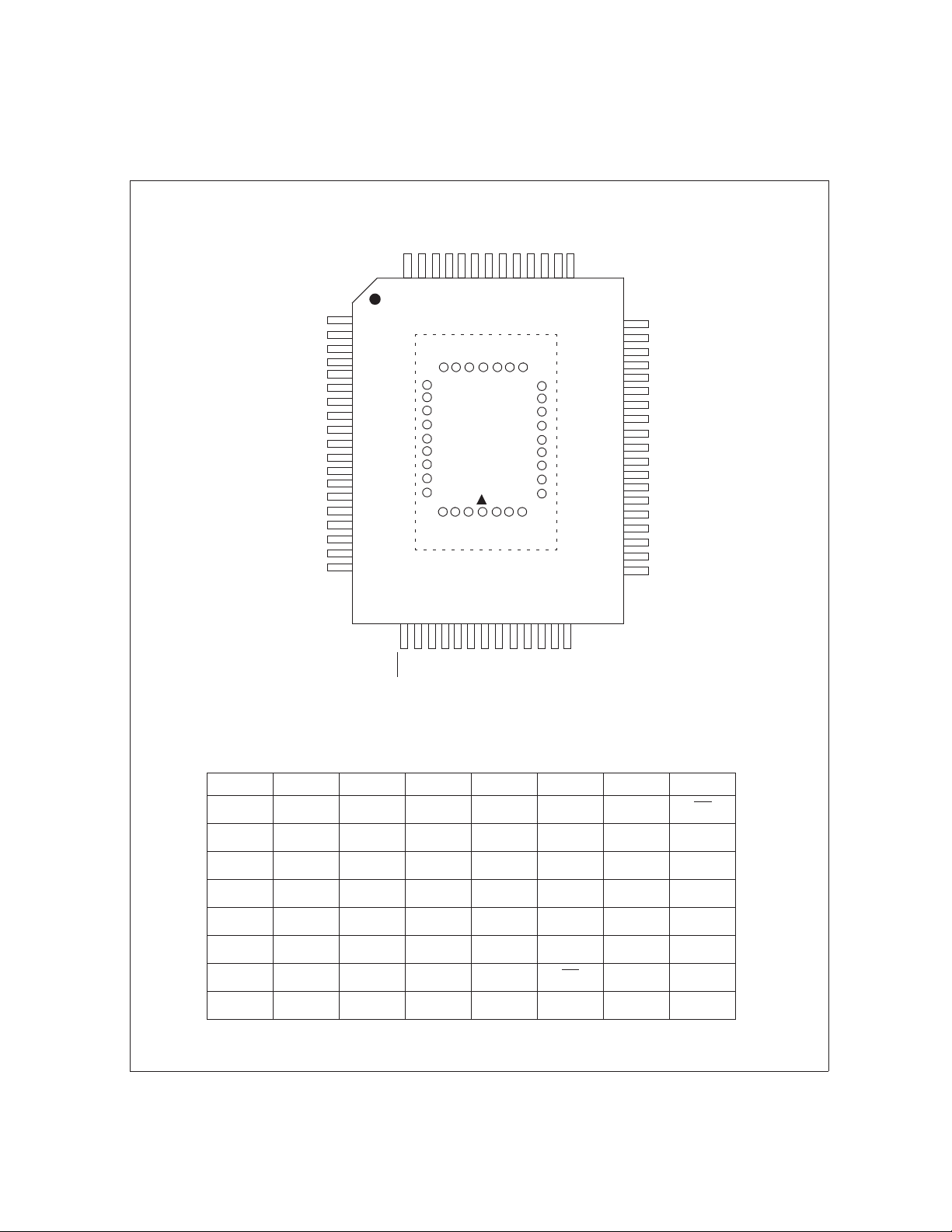

1.5 Pin Assignment

Figure 1.5-1 "FPT-64P-M09 pin assignment" and Figure 1.5-2 "MQP-64C-P01 pin

assignment" show the pin assignment diagrams for the MB89950/950A series.

■ FPT-64P-M09 pin assignment

Figure 1.5-1 FPT-64P-M09 pin assignment

SEG5

SEG6

SEG7

SEG8

SEG9

SEG10

SEG11

SEG12

VCCSEG13

SEG14

SEG15

SEG16

SEG17

SEG18

SEG19

SEG4

SEG3

SEG2

SEG1

SEG0

COM3

COM2

COM1

COM0

V3

P33/V2

P32/V1

P31

P30

P40

P41/PWM

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

646362616059585756555453525150

TOP VIEW

QFP-64

171819202122232425262728293031

X1

SS

V

P45/SCK

P46/INT0

P25/SEG41

P24/SEG40

P23/SEG39

P22/SEG38

P21/SEG37

MODA

P44/SO

X0

RST

P43/SI

P42/INT1/PWC

32

P20/SEG36

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

P00/SEG20

P01/SEG21

P02/SEG22

P03/SEG23

P04/SEG24

P05/SEG25

P06/SEG26

P07/SEG27

P10/SEG28

P11/SEG29

P12/SEG30

P13/SEG31

P14/SEG32

P15/SEG33

P16/SEG34

P17/SEG35

8

Page 23

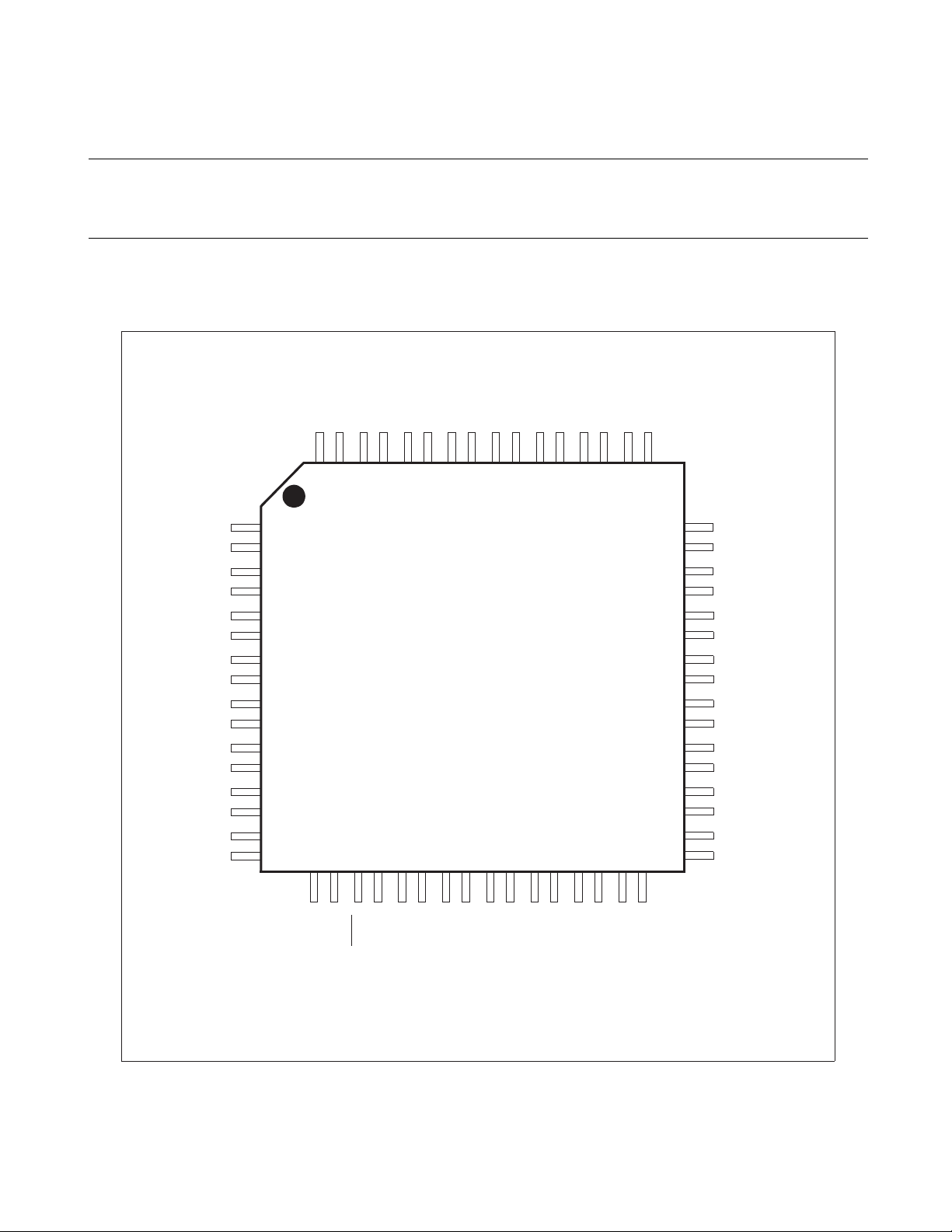

■ MQP-64C-P01 pin assignment

Figure 1.5-2 MQP-64C-P01 pin assignment

SEG6

SEG7

SEG8

SEG9

SEG10

SEG11

SEG12

Vcc

SEG13

SEG14

SEG15

SEG16

64636261605958575655545352

CHAPTER 1 OVERVIEW

SEG17

SEG5

SEG4

SEG3

SEG2

SEG1

SEG0

COM3

COM2

COM1

COM0

V3

V2/P33

V1/P32

P31

P30

P40

P41/PWM

P42/PWC/INT1

P43/SI

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

84838281807978

85

86

87

88

89

90

91

92

93

94959665666768

(TOP VIEW)

20212223242526272829303132

X0

X1

RST

P44/SO

Vss

MODA

Pin assignment on package top (MB89PV950 only)

51

50

49

48

77

76

75

74

73

72

71

70

69

P45/SCK

P46/INT0

P25/SEG41

P24/SEG40

P23/SEG39

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

P22/SEG38

P21/SEG37

SEG18

SEG19

P00/SEG20

P01/SEG21

P02/SEG22

P03/SEG23

P04/SEG24

P05/SEG25

P06/SEG26

P07/SEG27

P10/SEG28

P11/SEG29

P12/SEG30

P13/SEG31

P14/SEG32

P15/SEG33

P16/SEG34

P17/SEG35

P20/SEG36

Pin no. Pin name Pin no. Pin nam e Pi n no. Pin nam e Pin no. Pi n name

65 N.C. 73 A2 81 N.C. 89 OE

66 Vpp 74 A1 82 O4 90 N.C.

67 A127 5 A0 83 O5 91A 11

68 A7 76 N.C. 84 O6 92 A9

69 A6 77 O1 85 O7 93 A8

70 A5 78 O2 86 O8 94 A13

71 A4 79 O3 87 CE

95 A14

72 A3 80 Vss 88 A10 96 Vcc

N.C.: Internally connected. Do not use.

9

Page 24

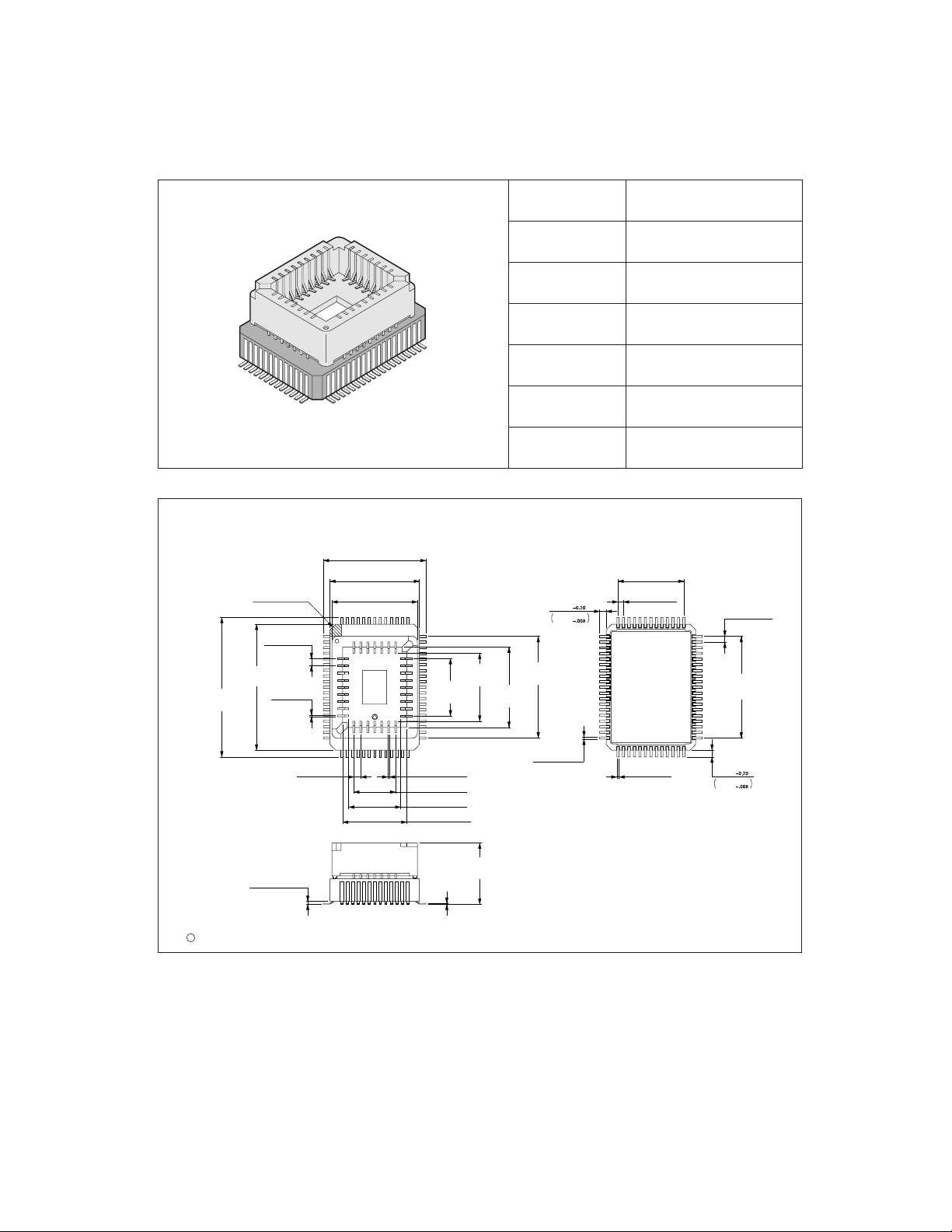

CHAPTER 1 OVERVIEW

1.6 Package Dimensions

Two types of packages are available for MB89950/950A series. Figure 1.6-1 "FPT-64PM09 package dimensions" and Figure 1.6-2 "MQP-64C-P01 package dimensions" show

the package dimensions.

■ FPT-64P-M09 package dimensions

Figure 1.6-1 FPT-64P-M09 package dimensions

64-pin plastic LQFP Lead pitch 0.65 mm

64-pin plastic LQFP

(FPT-64P-M09)

49

(FPT-64P-M09)

14.00±0.20(.551±.008)SQ

12.00±0.10(.472±.004)SQ

INDEX

Package width

package length

12

12 mm

Lead shape Gullwing

Sealing method Plastic mold

Mounting height 1.70 mm MAX

Note: Pins width and pins thickness include plating thickness.

0.145±0.055

3348

32

(.0057±.0022)

0.10(.004)

0.10(.004)

Details of "A" part

+0.20

1.50

+.008

.059

0.25(.010)

(Mounting height)

10

64

116

0.65(.026)

C

2001 FUJITSU LIMITED F64018S-c-2-4

0.32±0.05

(.013±.002)

17

0.13(.005)

0.50±0.20

"A"

M

(.020±.008)

0.60±0.15

(.024±.006)

Dimensions in mm (inches).

0.10±0.10

(.004±.004)

(Stand off)

Page 25

■ MQP-64C-P01 package dimensions

Figure 1.6-2 MQP-64C-P01 package dimensions

64-pin ceramic MQFP Lead pitch 1.00 mm

CHAPTER 1 OVERVIEW

Lead shape Straight

(MQP-64C-P01)

64-pin ceramic MQFP

(MQP-64C-P01)

INDEX AREA

1.27±0.13

(.050±.005)

22.30±0.33

(.878±.013)

24.70(.972)

TYP

0.30(.012)

TYP

18.70(.736)TYP

16.30±0.33

(.642±.013)

15.58±0.20

(.613±.008)

12.02(.473)

10.16(.400)

TYP

Mounted package

18.12±0.20

(.713±.008)

TYP

14.22(.560)

TYP

Motherboard

material

material

+0.40

1.20

+.016

.047

12.00(.472)TYP

1.00±0.25

(.039±.010)

Ceramic

Plastic

18.00(.709)

1.00±0.25

(.039±.010)

TYP

1.27±0.13

(.050±.005)

0.50(.020)TYP

C

1994 FUJITSU LIMITED M64004SC-1-3

0.30(.012)TYP

7.62(.300)TYP

9.48(.373)TYP

11.68(.460)TYP

10.82(.426)

0.15±0.05

(.006±.002)

MAX

0.40±0.10

(.016±.004)

0.40±0.10

(.016±.004)

Dimensions in mm (inches).

1.20

.047

+0.40

+.016

11

Page 26

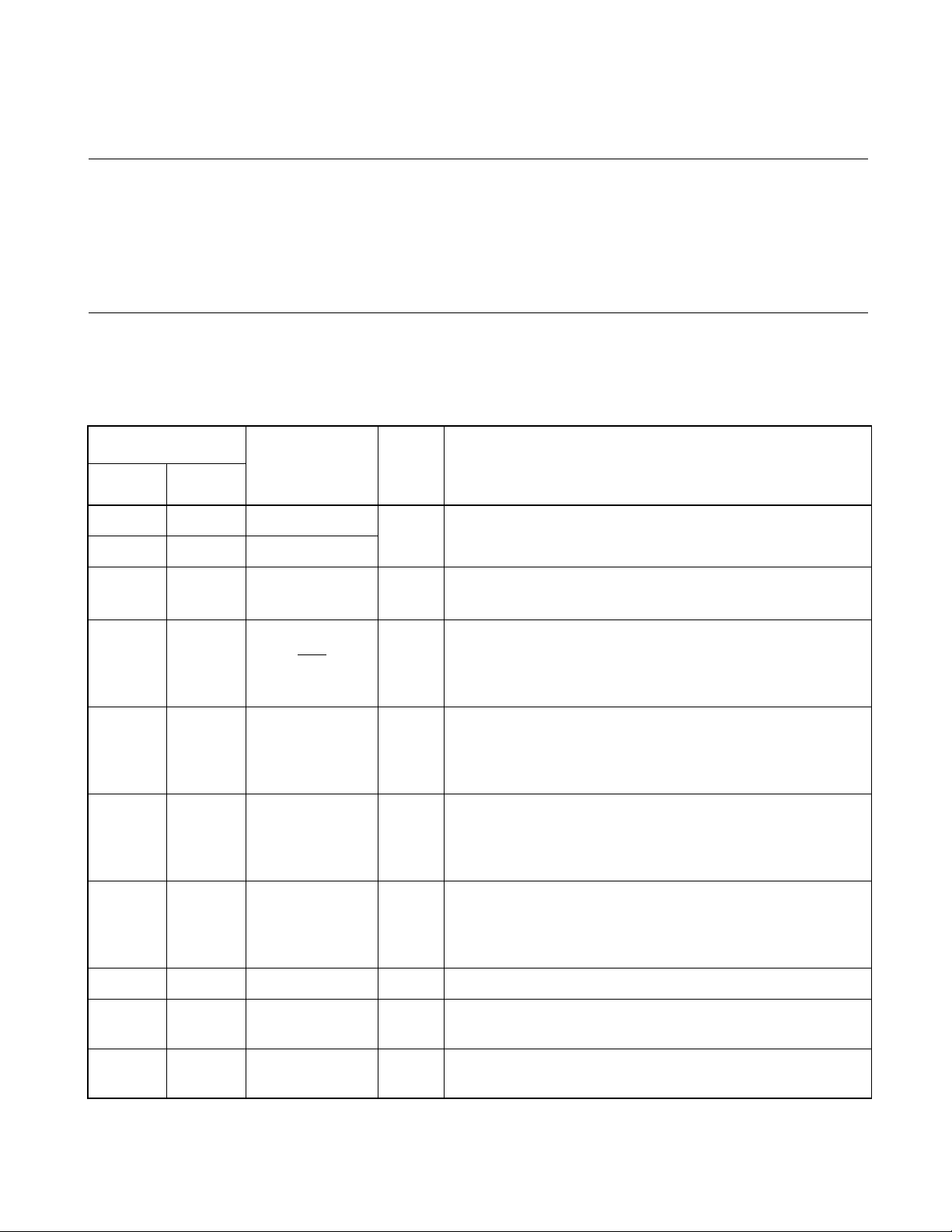

CHAPTER 1 OVERVIEW

1.7 I/O Pins and Pin Functions

Table 1.7-1 "Pin description" and Table 1.7-2 "Pin description for external ROM (for

MB89PV950 only)" list the MB89950/950A series I/O pins and their functions. Table 1.7-3

"I/O circuit type" lists the I/O circuit types.

The letter in the "I/O circuit type" column in Table 1.7-1 "Pin description" refer to the

letter in the "Type" column Table 1.7-3 "I/O circuit type".

■ I/O pins and pin functions

Table 1.7-1 Pin description (1/2)

Pin no.

*1

LQFP

22 23 X0

23 24 X1

21 22 MODA B

19 20 RST C

48 to 41 49 to 42

40 to 33 41 to 34

MQFP

*2

Pin name

P00/SEG20

to

P07/SEG27

P10/SEG28

to

P17/SEG35

I/O

circuit

type

A Clock oscillator pins.

Operation mode selection pin.

This pin is connected directly to V

Reset I/O pin.

This pin consists of an N-ch open-drain output with a pull-up

resistor and hysteresis input. A "LOW" level is output from this

pin. A "LOW" voltage on this port generates a RESET condition.

N-channel open-drain type general-purpose I/O ports.

D

D

Also serve as LCD controller/driver segment outputs.

Switching between port output and segment driver output is

performed by the mask option.

N-channel open-drain type general-purpose I/O ports.

Also serve as LCD controller/driver segment outputs.

Switching between port output and segment driver output is

performed by the mask option.

Function

SS

with pull-down resistor.

P20/SEG36

32 to 27 33 to 28

14 to 13 15 to 14 P30 to P31 F N-channel open-drain type general-purpose I/O ports.

12 to 11 13 to 12

15 16 P40 E

12

to

P25/SEG41

P32/V1 to

P33/V2

D

H

N-channel open-drain type general-purpose I/O ports.

Also serve as LCD controller/driver segment outputs.

Switching between port output and segment driver output is

performed by the mask option.

N-channel open-drain type general-purpose I/O ports.

Also serve as LCD controller/driver power supply.

General-purpose I/O port.

A pull-up resistor option is provided.

Page 27

Table 1.7-1 Pin description (2/2)

CHAPTER 1 OVERVIEW

Pin no.

Pin name

LQFP

*1

MQFP

*2

16 17 P41/PWM E

17 18 P42/PWC/INT1 E

18 19 P43/SI E

20 21 P44/SO E

25 26 P45/SCK E

I/O

circuit

type

Function

General-purpose I/O port.

Also serves as PWM timer toggle output (PWM).

A pull-up resistor option is provided.

General-purpose I/O port.

Also serves as pulse-width count timer input (PWC) and external

interrupt input (INT1).

The PWC and INT1 inputs are hysteresis type.

A pull-up resistor option is provided.

General-purpose I/O port.

Also serves as serial I/O and UART data input (SI).

The SI input is hysteresis type.

A pull-up resistor option is provided.

General-purpose I/O port.

Also serves as serial I/O and UART data output (SO).

A pull-up resistor option is provided.

General-purpose I/O port.

Also serves as serial I/O and UART clock input/output (SCK).

The SCK input is hysteresis type.

A pull-up resistor option is provided.

General-purpose input port.

26 27 P46/INT0 E

Also serves as external interrupt input (INT0).

The input is hysteresis type.

A pull-up resistor option is provided.

5 to 1

64 to 57

55 to 49

6 to 1

64 to 58

56 to 50

For LCD segment driver outputs.

SEG0 to SEG19 G

9 to 6 10 to 7 COM0 to COM3 G For LCD common driver outputs.

10 11 V3 - For LCD driver power supply.

56 57

24 25

V

CC

V

SS

Power pin.

-

Power (GND) pin.

-

*1: FPT-64P-M09

*2: MQP-64C-P01

13

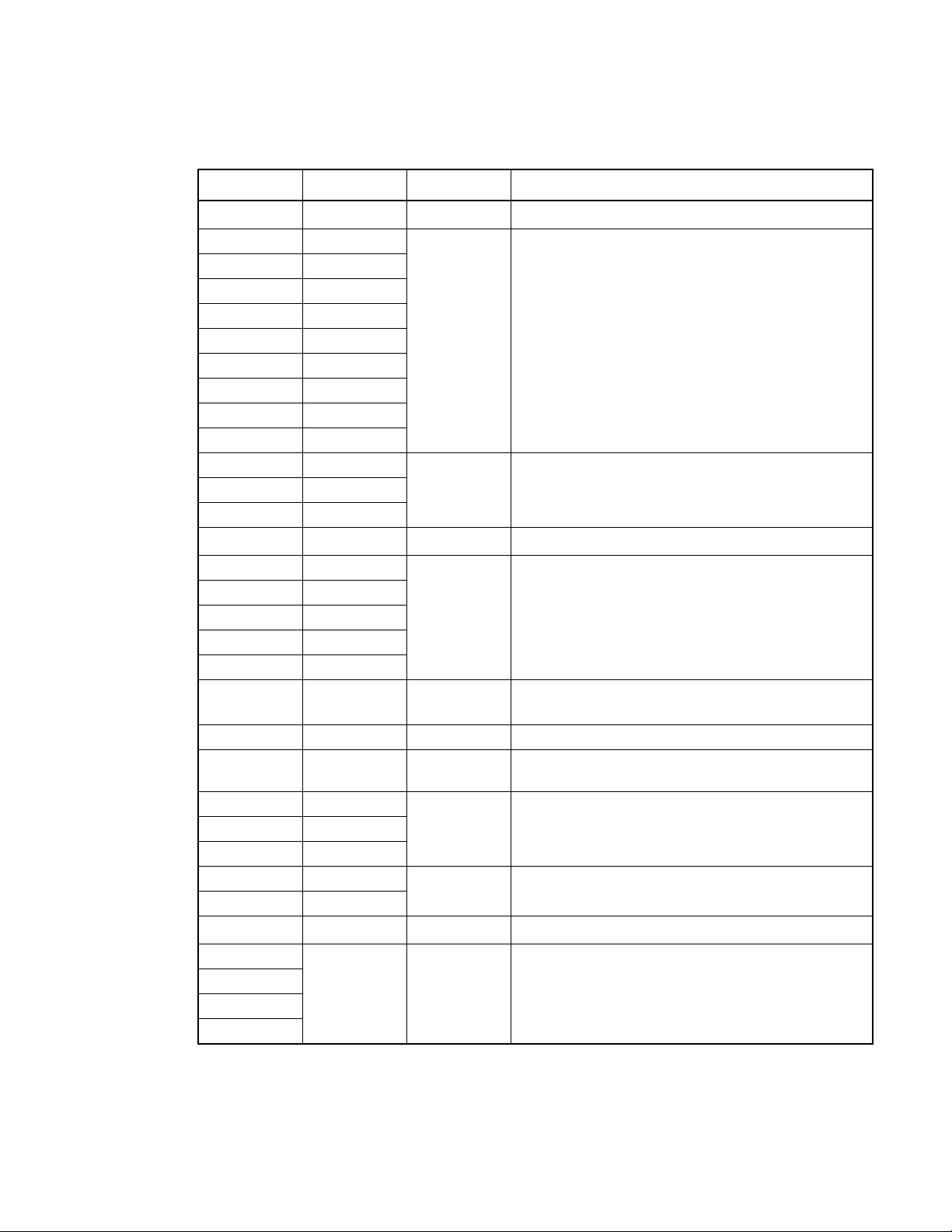

Page 28

CHAPTER 1 OVERVIEW

Table 1.7-2 Pin description for external ROM (for MB89PV950 only)

Pin no. Pin name I/O Function

66

67 A12

68 A7

69 A6

70 A5

71 A4

72 A3

73 A2

74 A1

75 A0

77 O1

79 O3

80

82 O4

83 O5

84 O6

85 O7

86 O8

87 CE O

88 A10 O For address output.

89 OE O

91 A11

93 A8

94 A13

95 A14

96

65

76

81

90

V

PP

V

SS

V

CC

N.C. --

O For high-level output.

O For address output.

I For data input.78 O2

O For power supply (GND).

I For data input.

For ROM chip enable.

The High level is output in standby mode.

For ROM output enable.

The Low level is always output.

O For address output.92 A9

O For address output.

O For EPROM power supply.

For internal connection.

Keep open.

14

Page 29

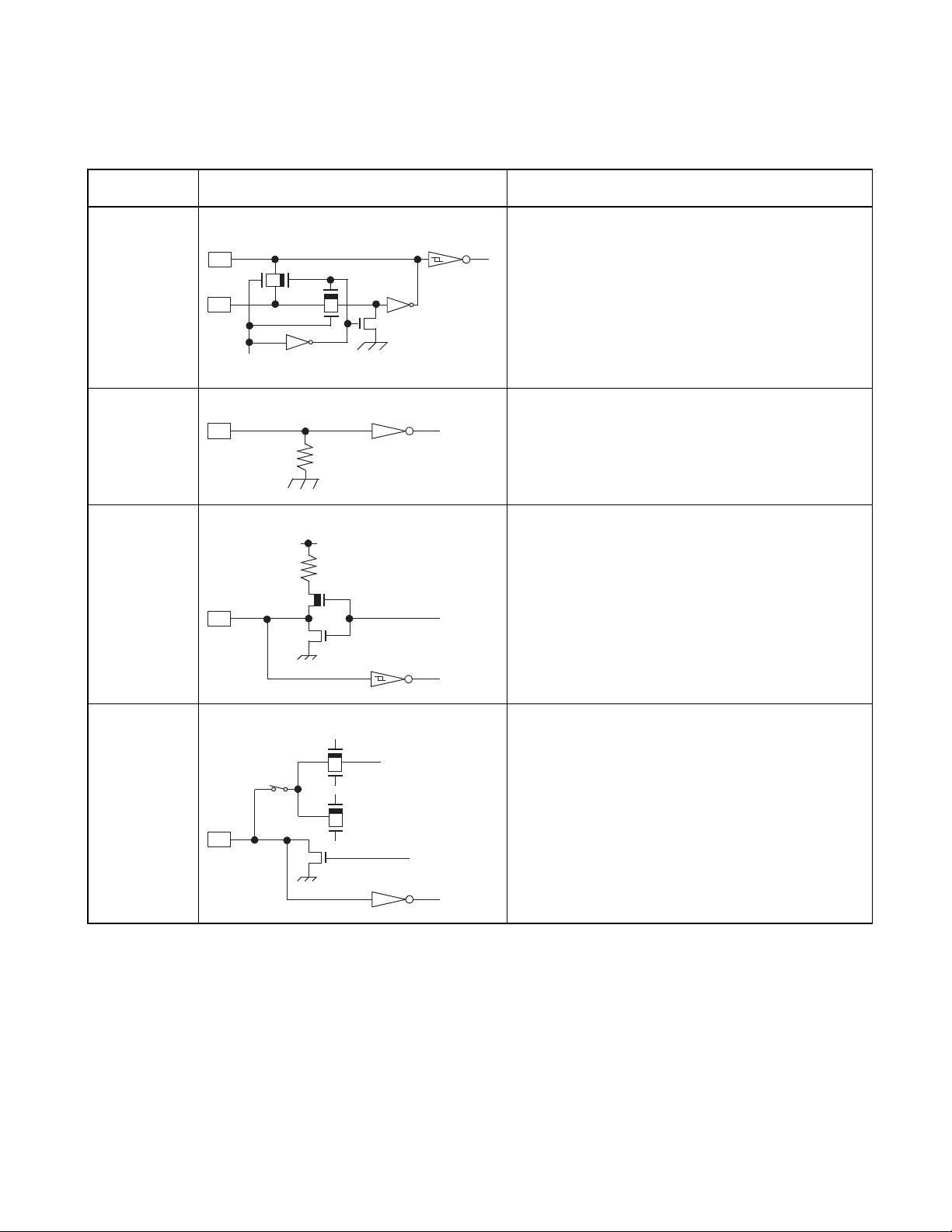

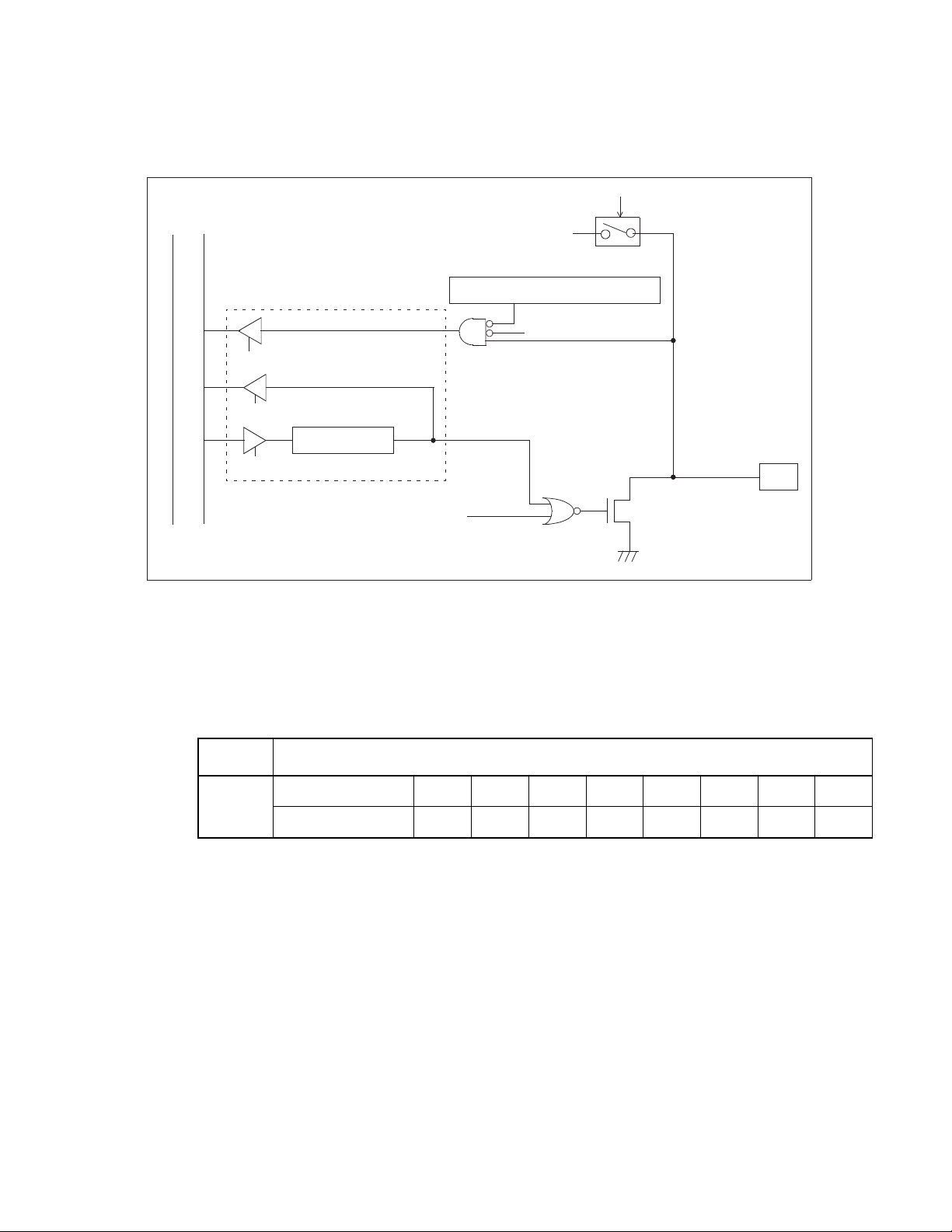

Table 1.7-3 I/O circuit type (1/2)

Type Circuit Remarks

A • Crystal oscillator

X1

N-ch

X0

S

tandby control signal

P-ch

P-ch

N-ch

N-ch

• Feedback resistor: About 1 MΩ (5 V)

B • CMOS input

• Pull-down resistor (N-ch): About 50 kΩ (5 V)

R

CHAPTER 1 OVERVIEW

C • Output pull-up resistor (P-ch): About 50 kΩ (5 V)

• Hysteresis input

R

P-ch

N-ch

D • N-ch open-drain output

• CMOS input

P-ch

N-ch

P-ch

N-ch

N-ch

• The segment driver output is optional.

15

Page 30

CHAPTER 1 OVERVIEW

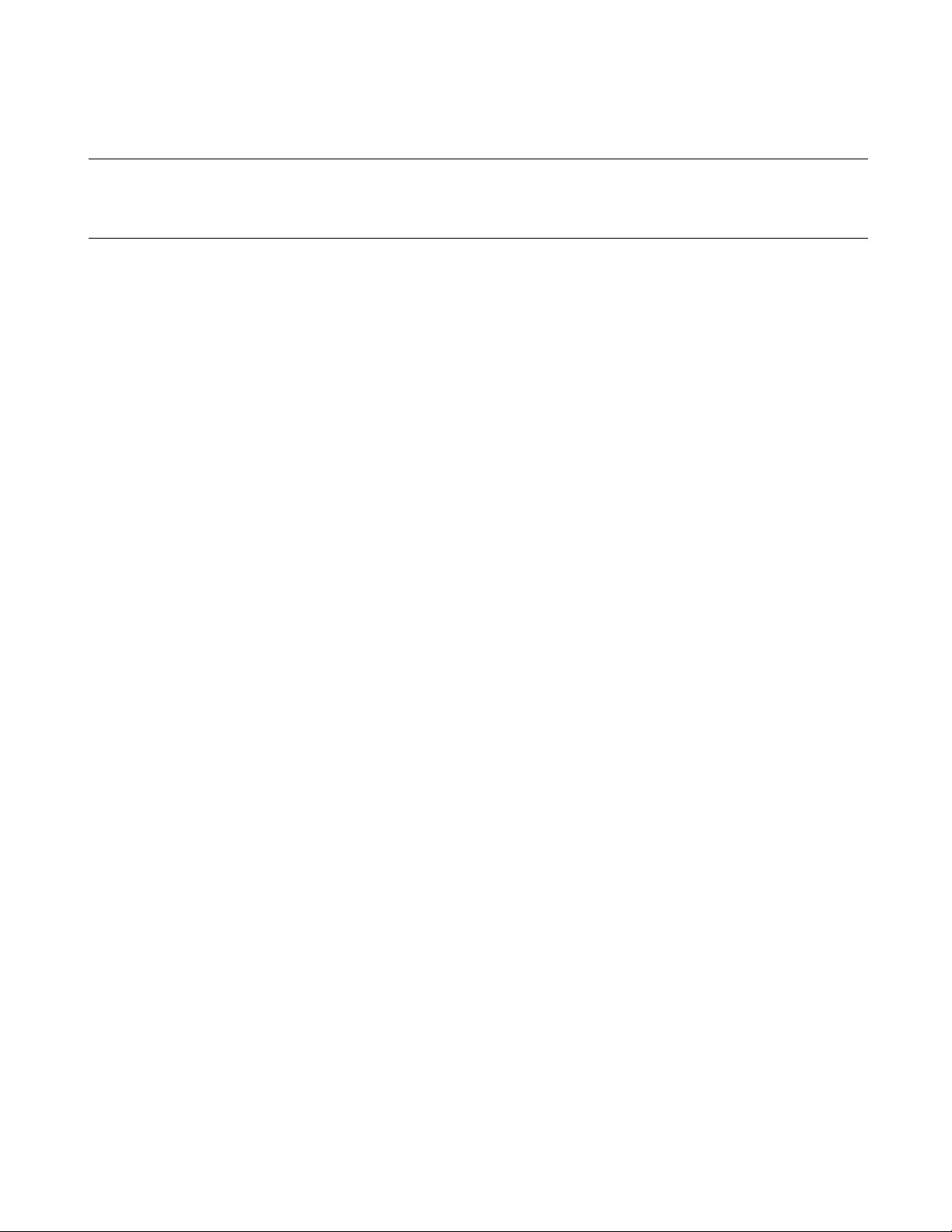

Table 1.7-3 I/O circuit type (2/2)

Type Circuit Remarks

E • CMOS output

• CMOS input

R

P-ch

P-ch

N-ch

• Hysteresis input (peripheral input)

• The pull-up resistor is optional: About 50 kΩ (5 V)

F • N-ch open-drain output

• CMOS input

N-ch

G • LCD controller/driver common/segment driver

output

P-ch

N-ch

P-ch

N-ch

H • N-ch open-drain output

• CMOS input

P-ch

N-ch

N-ch

16

Page 31

CHAPTER 2

HANDLING DEVICES

This chapter describes points to note when using the

general-purpose single-chip microcontroller.

2.1 "Notes on Handling Devices"

17

Page 32

CHAPTER 2 HANDLING DEVICES

2.1 Notes on Handling Devices

This section lists points to note regarding the power supply voltage, pins, and other

device handling aspects.

■ Notes on handling devices

Preventing latch-up

●

Latch-up may occur on CMOS ICs if voltage higher than V

output pins other than medium to high-voltage pins or if higher than the voltage which shows on Absolute

Maximum Ratings is applied between V

When latch-up occurs, supply current increases rapidly and might thermally damage elements. Take great

care not to exceed the absolute maximum ratings in circuit operation.

Treatment of unused input pins

●

Leaving unused input pins open could cause malfunctions. They should be connected to pull-up or pull-

down resistor.

Power supply voltage fluctuations

●

Although V

therefore cause malfunctions, even if it occurs within the rated range. Stabilizing voltage supplied of the IC

is therefore important. As stabilization guidelines, it is recommended to control power so that V

fluctuations (P-P. value) will be less that 10% of the standard V

to 60 Hz) and the transient fluctuation rate will be less than 0.1 V/ms at the time of a momentary

fluctuation such as when power is switched.

Precaution when using an external clock

●

power supply voltage is assured to operate within the rated, a rapid change to the IC is

CC

and VSS.

CC

or lower than VSS is applied to input and

CC

CC

value at the commercial frequency (50

CC

ripple

18

Even when an external clock is used, oscillation stabilization time is required for power-on reset (option

selection) and release from stop mode.

Page 33

Recommended screening conditions

●

The OTPROM product should be screened by high-temperature aging before mounting.

High-temperature aging (150 C, 48Hrs)

The programming test cannot be performed for all bits of the preprogrammed OTPROM product due to its

characteristics. Consequently, 100% programming yielding cannot be ensured.

Treatment of N.C. pins

●

Be sure to leave (internally connected) N.C. pins open.

CHAPTER 2 HANDLING DEVICES

Verify program

Read

Mount

Unused LCD controller/driver dedicated pins

●

When LCD controller/driver dedicated pins are not in use, keep it open.

Port shared with SEG pin

●

When using port shared with SEG pin, be sure that the input voltage to port does not exceed the voltage of

V3 (SEG driving voltage). When power-on or reset, SEG pin will output an initial value of "L".

LCD controller/driver not in use

●

When LCD controller/driver is not in use, connect the V3 pin to V

dedicated pins open.

and keep other LCD controller/driver

CC

19

Page 34

CHAPTER 2 HANDLING DEVICES

20

Page 35

CHAPTER 3

CPU

This chapter describes the functions and operation of

the CPU.

3.1 "Memory Space"

3.2 "Dedicated Registers"

3.3 "General-purpose Registers"

3.4 "Interrupts"

3.5 "Resets"

3.6 "Clocks"

3.7 "Standby Modes (Low-power Consumption)"

3.8 "Memory Access Mode"

21

Page 36

CHAPTER 3 CPU

3.1 Memory Space

The microcontrollers of the MB89950/950A series offer a memory space of 64 Kbytes.

The memory space contains the I/O area, RAM area, ROM area, and external area. The

memory space contains areas used for special purposes such as the general-purpose

registers and vector table.

■ Memory space structure

I/O area (addresses: 0000H to 007FH)

●

• Control registers and data registers for the internal peripheral functions are located in this area.

• As the I/O area is allocated within the memory space, I/O can be accessed in the same way as memory.

High-speed access using direct addressing is available.

RAM area

●

ROM area

●

• Internal static RAM is provided as an internal data area.

• The internal RAM size differs from product to product.

• Addresses between 0080

• Addresses between 0100

apply for some products).

• The contents of RAM is indeterminate after a reset.

• Internal ROM is provided as an internal program area.

• The internal ROM size differs from product to product.

• Addresses between FFC0

and 00FFH support high-speed access using direct addressing.

H

and 01FFH can be used as the general-purpose register area (restrictions

H

and FFFFH are used for the vector table, etc.

H

22

Page 37

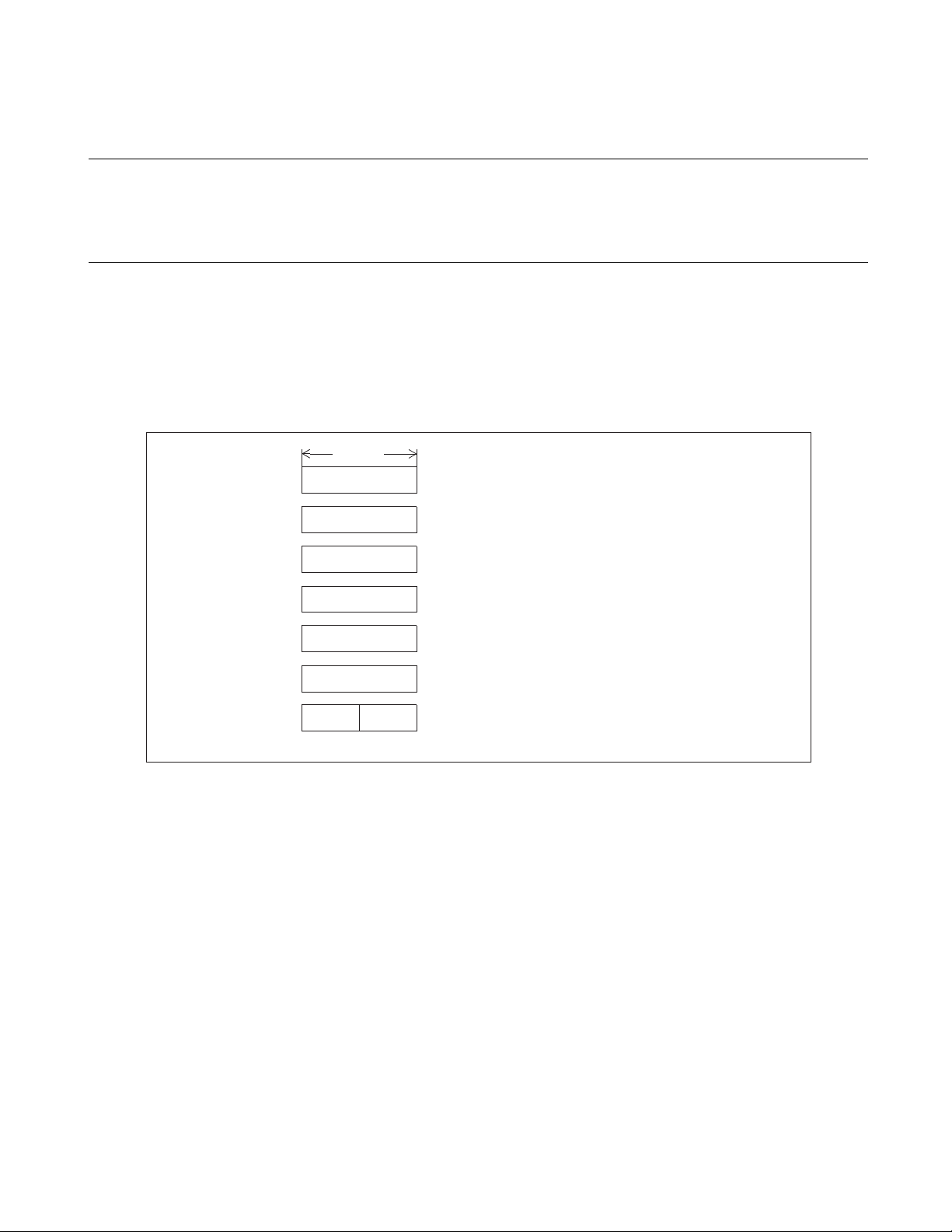

■ Memory map

CHAPTER 3 CPU

Figure 3.1-1 Memory map

0000

0080

00C0

0100

0140

F000

FFC0

FFFF

MB89951A

H

H

Reserved

H

RAM

H

Registers

H

Access

prohibited

H

ROM

H

H

I/O

0000

0080

0100

0180H

E000

FFC0

FFFF

MB89953A

H

I/O

H

RAM

H

Registers

Access

prohibited

H

ROM

H

H

Vector table

0000

0080

0100

0200H

0280

MB89P955

H

H

RAM

H

Registers

H

I/O

0000

0080

0100

0200H

MB89PV950

H

I/O

H

RAM

H

Registers

0480H

C000

FFC0

FFFF

H

H

H

Access

prohibited

ROM

8000

FFC0

FFFF

H

H

H

Access

prohibited

ROM

(reset, interrupt, vector call instruction)

23

Page 38

CHAPTER 3 CPU

3.1.1 Special Areas

In addition to the I/O area, the special purpose areas in the memory space include the

general-purpose register area and the vector table area.

■ General-purpose register areas (addresses: 0100H to 01FFH)

• Provides auxiliary registers for 8-bit arithmetic operation and transfer instructions.

• Allocated to a region of the RAM area. Can also be used as normal RAM.

• Using the area as general-purpose registers enables high-speed access by general-purpose register

addressing using short instructions.

Table 3.1-1 "General-purpose register areas" lists the areas in each device that can be used for general-

purpose registers.

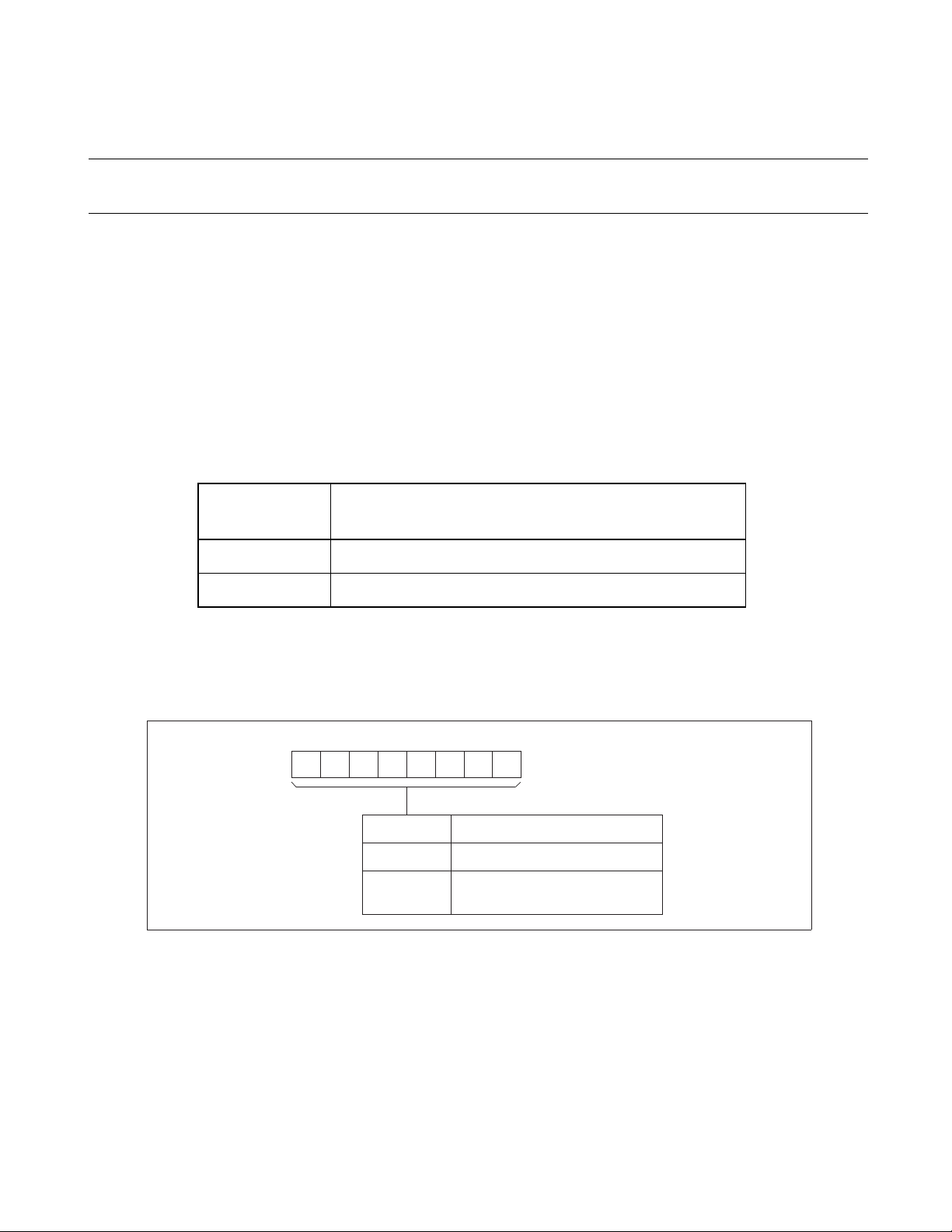

Table 3.1-1 General-purpose register areas

Part number MB89951A MB89953A MB89P955/PV950

Number of banks 8 16 32

Address range 0100

See section 3.2.2 "Register Bank Pointer (RP)" and section 3.3 "General-purpose Registers" for details.

to 013F

H

H

0100H to 017F

H

0100H to 01FF

H

24

Page 39

■ Vector table area (addresses: FFC0H to FFFFH)

• Used as the vector table for the vector call instruction, interrupts, and resets.

• The vector table is allocated at the top of the ROM area. The start address of the corresponding

processing routine is set as data at each vector table address.

Table 3.1-2 "Vector table" lists the vector table addresses referenced by the vector call instruction,

interrupts, and resets.

See Section 3.4 "Interrupts", Section 3.5 "Resets", and "(6) CALLV #vct" in Appendix B.2, "Special

Instructions" for details.

Table 3.1-2 Vector table

CHAPTER 3 CPU

Vector call

instruction

Vector table address

Upper Lower Upper Lower

CALLV #0 FFC0

CALLV #1 FFC2

CALLV #2 FFC4

CALLV #3 FFC6

CALLV #4 FFC8

CALLV #5 FFCA

CALLV #6 FFCC

CALLV #7 FFCE

Vector table address

Interrupts

H

H

H

H

H

H

H

H

FFC1

FFC3

FFC5

FFC7

FFC9

FFCB

FFCD

FFCF

H

H

H

H

H

H

H

H

IRQB FFE4

IRQA FFE6

IRQ9 FFE8

IRQ8 FFEA

IRQ7 FFEC

IRQ6 FFEE

IRQ5 FFF0

IRQ4 FFF2

IRQ3 FFF4

IRQ2 FFF6

IRQ1 FFF8

IRQ0 FFFA

H

H

H

H

H

H

H

H

H

H

H

H

FFE5

FFE7

FFE9

FFEB

FFED

FFEF

FFF1

FFF3H

FFF5

FFF7

FFF9

FFFB

H

H

H

H

H

H

H

H

H

H

H

Mode data

Reset vector FFFE

--

(*1)

H

*1: FFFCH is not available. (Set FFH.)

FFFD

FFFF

H

H

25

Page 40

CHAPTER 3 CPU

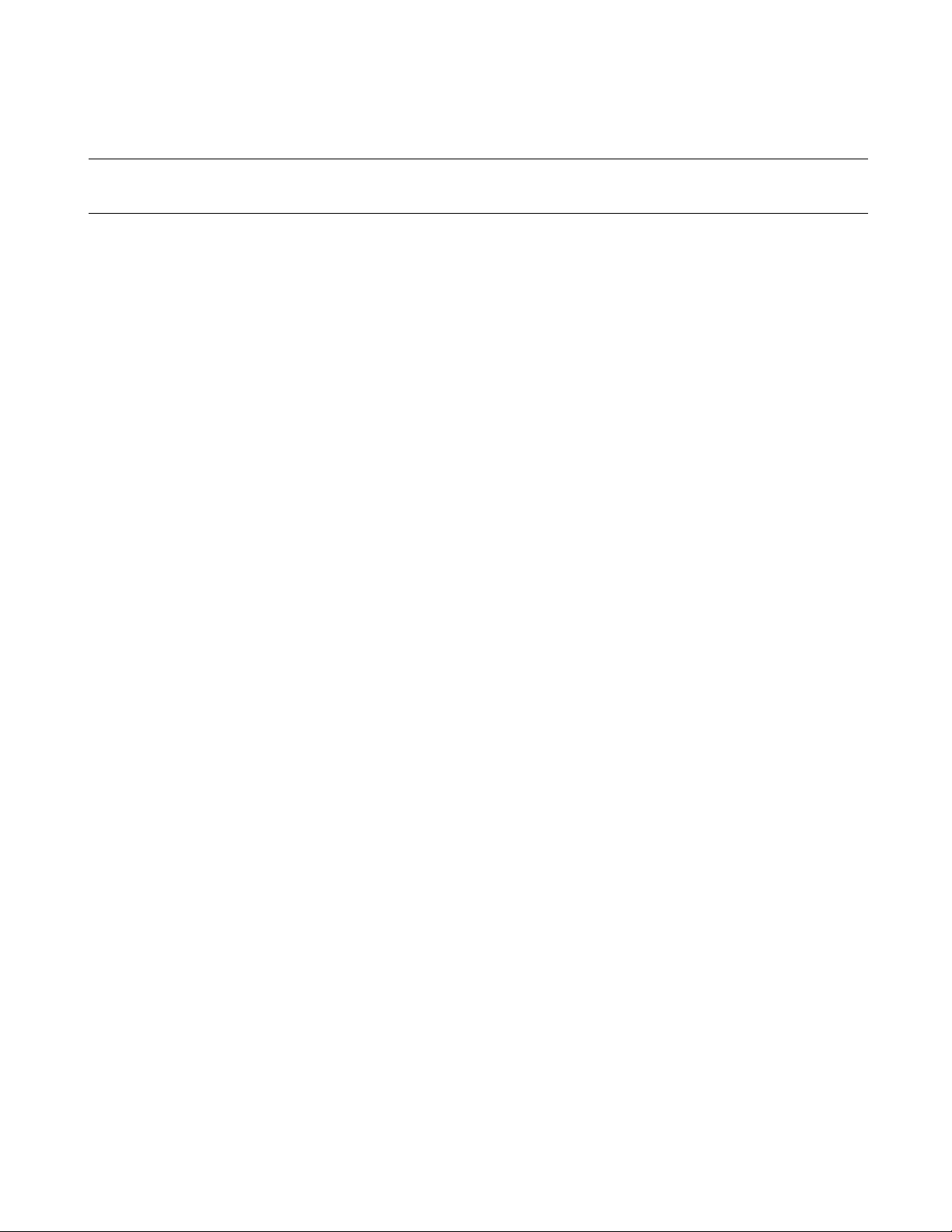

3.1.2 Storing 16-bit Data in Memory

For 16-bit data and the stack, store the upper data in the lower memory address value.

■ Storing 16-bit data in RAM

When writing 16-bit data to memory, store the upper byte at the lower address and the lower byte at the

next address. Handle reading of 16-bit data in the same way.

Figure 3.1-2 "Storing 16-bit data in memory" shows how 16-bit data is stored in memory.

Figure 3.1-2 Storing 16-bit data in memory

Memory Memory

Before execution

Before execution

1 2 3 4 H

1 2 3 4 H

A

A

Memory Memory

MOVW 0081H,A

MOVW 0081H,A

0080

0080

H

H

0081

0081

H

H

0082

0082

H

H

0083H

0083H

After execution

After execution

1 2 3 4 H

1 2 3 4 H

A

A

12H

12H

34H

34H

0080

0080

0081

0081

0082

0082

0083H

0083H

H

H

H

H

H

H

■ Storing 16-bit operands

The same byte order applies when specifying a 16-bit operand in an instruction. Store the upper byte at the

address following the operation code (instruction) and the lower byte at the next address.

The byte ordering applies to both 16-bit immediate data and operands that specify a memory address.

Figure 3.1-3 "Byte order of 16-bit data in an instruction" shows how 16-bit data is stored in an instruction.

Figure 3.1-3 Byte order of 16-bit data in an instruction

[Example] MOV A,5678H ; Extended address

MOVW A,#1234H ; 16-bit immediate data

X X X 0 H XX XX

X X X 2

X X X 5

X X X 8

■ Storing 16-bit data on stack

The same byte order applies when saving 16-bit register data on the stack during an interrupt or similar.

The upper byte is stored in the lower address.

After assembly

.

.

.

H 60 56 78 ; Extended address

H E4 12 34 ; 16-bit immediate data

H XX

.

.

.

26

Page 41

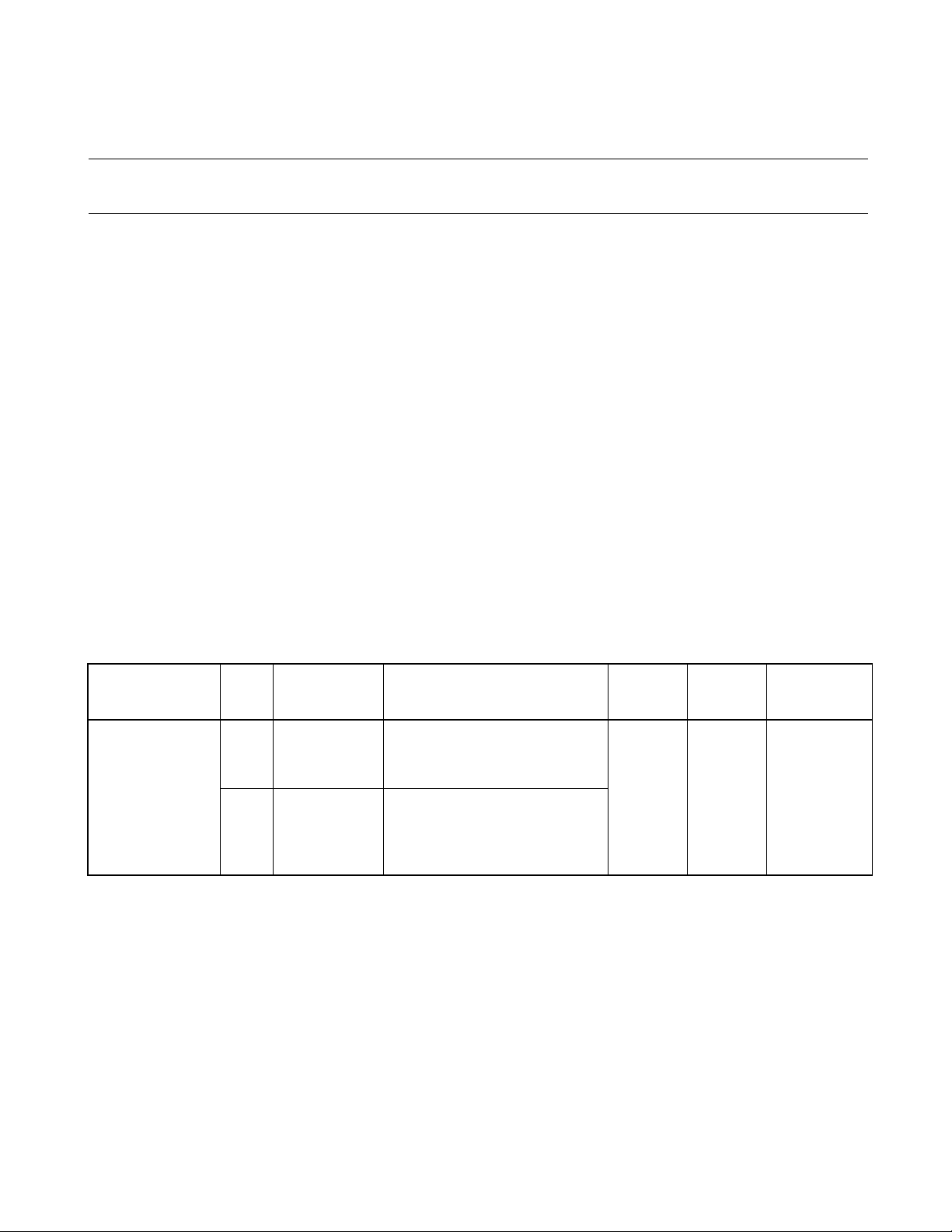

CHAPTER 3 CPU

3.2 Dedicated Registers

The dedicated registers in the CPU consist of the program counter (PC), two arithmetic

operation registers (A and T), three address pointers (IX, EP, and SP), and the program

status (PS). All registers are 16 bits.

■ Dedicated register configuration

The dedicated registers in the CPU consist of seven 16-bit registers. Some of these registers are also able to

be used as 8-bit register, using the lower 8 bits only.

Figure 3.2-1 "Dedicated register configuration" shows the structure of the dedicated registers.

Figure 3.2-1 Dedicated register configuration

Initial value

FFFD

H

Indeterminate

Indeterminate

Indeterminate

Indeterminate

Indeterminate

I-flag = "0"

IL0, IL1 = "11"

Otherbits are indeterminate

16 bits

RP CCR

■ Dedicated register functions

Program counter (PC)

●

The program counter is a 16-bit counter that indicates the memory address of the instruction currently

being executed by the CPU. Instruction execution, interrupts, resets, and similar update the contents of the

program counter. The initial value during a reset is the read address of the mode data (FFFD

PC

A

T

IX

EP

SP

PS

: Program counter

A register for indicating the current instruction

storage positions

: Accumulator

A temporary register for storing arithmetic operations or

transfer instructions

: Temporary accumulator

A register for performing arithmetic operations with

the accumulator

: Index register

A register for indicating an index address

: Extra pointer

A pointer for indicating a memory address

: Stack pointer

A register for indicating the current stack location

: Program status

A register for storing a register bank pointer and

condition code

).

H

Accumulator (A)

●

The accumulator is a 16-bit arithmetic operation register. The accumulator is used to perform arithmetic

operations and data transfers with data in memory or in other registers such as the temporary accumulator

(T). The content of the accumulator can be treated as either word (16-bit) or byte (8-bit) data. Only the

lower 8 bits (AL) of the accumulator are used for byte arithmetic operations or transfers. In this case, the

upper 8 bits (AH) remain unchanged. The content of the accumulator after a reset is indeterminate.

27

Page 42

CHAPTER 3 CPU

Temporary accumulator (T)

●

The temporary accumulator is an auxiliary 16-bit arithmetic operation register used to perform arithmetic

operations with the data in the accumulator (A). The content of the temporary accumulator is treated as

word data (16-bit) for word-length arithmetic operations with the accumulator and as byte data (8-bit) for

byte-length arithmetic operations. For byte-length arithmetic operations, only the lower 8 bits of the

temporary accumulator (TL) are used and the upper 8 bits (TH) are not used.

Executing a transfer instruction to transfer data to the accumulator (A) automatically transfer the previous

content of the accumulator to the temporary accumulator. In this case also, a byte transfer leaves the upper

8 bits of the temporary accumulator (TH) unchanged. The content of the temporary accumulator after a

reset is indeterminate.

Index register (IX)

●

The index register is a 16-bit register used to hold the index address. The index register is used in

conjunction with a single byte offset value (-128 to +127). Adding the sign-extended offset value to the

index address generates the memory address for data access. The content of the index register after a reset

is indeterminate.

Extra pointer (EP)

●

The extra pointer is a 16-bit register used to hold a memory address for data access. The content of the

extra pointer after a reset is indeterminate.

Stack pointer (SP)

●

The stack pointer is a 16-bit register used to hold the address referenced during operations such as

interrupts, subroutine calls, and the stack save and restore instructions. The value of the stack pointer

during program execution is the address of the most recently saved data on the stack. The content of the

stack pointer after a reset is indeterminate.

Program status (PS)

●

The program status is a 16-bit control register. The upper 8 bits contain the register bank pointer (RP)

which points to the address of the current general-purpose register bank.

The lower 8 bits contain the condition code register (CCR) which contains flags indicating the current CPU

status. The two 8-bit registers which form the program status cannot be accessed independently (the

program status can only be accessed by the MOVW A,PS and MOVW PS,A instructions).

Refer to the F

2

MC-8L MB89600 series Programming Manual for details on using the dedicated registers.

28

Page 43

CHAPTER 3 CPU

3.2.1 Condition Code Register (CCR)

The condition code register (CCR) located in the lower 8 bits of the program status (PS)

consists of the C, V, Z, N, and H bits indicating the results of arithmetic operations and

the contents of transfer data, and the I, IL1, and IL0 bits for control whether or not the

CPU accepts interrupt requests.

■ Structure of condition code register (CCR)

Figure 3.2-2 Structure of condition code register

RP CCR

Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

R4 R3 R2 R1 R0 ——— HIIL1IL0NZVC

PS

Half-carry flag

Interrupt enable flag

Interrupt level bits

Negative flag

Zero flag

X: Indeterminate

- : Unused

Overflow flag

Carry flag

CCR initial value

X011XXXX

B

■ Arithmetic operation result bits

Half-carry flag (H)

●

Set to "1" when a carry from bit 3 to bit 4 or a borrow from bit 4 to bit 3 occurs as a result of an arithmetic

operation. Clear to "0" otherwise. As this flag is for the decimal adjustment instructions, do not use this flag

in cases other than addition or subtraction.

Negative flag (N)

●

Set to "1" if the most significant bit (MSB) is set to "1" as a result of an arithmetic operation. Clear to "0"

when the bit is set to "0".

Zero flag (Z)

●

Set to "1" when an arithmetic operation results in "0". Clear to "0" otherwise.

Overflow flag (V)

●

Set to "1" if a signed numeric value overflows because of an arithmetic calculation. Clear to "0" if the

overflow does not occur.

29

Page 44

CHAPTER 3 CPU

Carry flag (C)

●

Set to "1" when a carry from bit 7 or borrow to bit 7 occurs as a result of an arithmetic operation. Clear to

"0" otherwise. Set to the shift-out value in case of a shift instruction.

Figure 3.2-3 "Change of carry flag by shift instruction" shows the change of the carry flag by a shift

instruction.

Left shift (ROLC) Right shift (RORC)

C

Note:

Reference:

Figure 3.2-3 Change of carry flag by shift instruction

Bit 7 Bit 0

Bit 7 Bit 0

C

The condition code register is part of the program status (PS) and cannot be accessed independently.

In practice, the flag bits are rarely fetched and used directly. Instead, the bits are used indirectly by

instructions such as branch instructions (such as BNZ) or the decimal adjustment instructions (DAA,

DAS). The content of the flags after a reset is indeterminate.

■ Interrupt acceptance control bit

Interrupt enable flag (I)

●

Interrupt is enabled when this flag is set to "1" and the CPU accepts interrupt. Interrupt is prohibited when

this flag is set to "0" and the CPU does not accept interrupt.

The initial value after a reset is "0".

Normal practice is to set the flag to "1" by the SETI instruction and clear to "0" by the CLRI instruction.

Interrupt level bits (IL1, IL0)

●

These bits indicate the level of the interrupt currently being accepted by the CPU. The value is compared

with the interrupt level setting registers (ILR1 to ILR3) which have a setting for each peripheral function

interrupt request (IRQ0 to IRQB).

Given that the interrupt enable flag is enabled (I = "1"), the CPU only performs interrupt processing for

interrupt requests with an interrupt level value that is less than the value of these bits. Table 3.2-1 "Interrupt

level" lists the interrupt level priorities. The initial value after a reset is "11

Table 3.2-1 Interrupt level

IL1 IL0 Interrupt level Priority

00

01

".

B

1

High

30

10 2

11 3

Low (no interrupt)

Page 45

Reference:

CHAPTER 3 CPU

The interrupt level bits (IL1, IL0) are normally "11

(during main program execution).

See Section 3.4 "Interrupts" for details on interrupts.

" when the CPU is not processing an interrupt

B

31

Page 46

CHAPTER 3 CPU

3.2.2 Register Bank Pointer (RP)

The register bank pointer (RP) located in the upper 8 bits of the program status (PS)

indicates the address of the general-purpose register bank currently in use. The RP is

converted to form the actual address in general-purpose register addressing.

■ Structure of register bank pointer (RP)

Figure 3.2-4 "Structure of register bank pointer" shows the structure of the register bank pointer.

Figure 3.2-4 Structure of register bank pointer

RP CCR

Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

R4 R3 R2 R1 R0 ——— HIIL1IL0NZVC

PS

X: Indeterminate

- : Unused

RP initial value

XXXXXXXX

B

The register bank pointer indicates the address of the register bank currently in use. Figure 3.2-5 "Rule for

conversion of actual addresses of general-purpose register area" shows the relationship between the pointer

contents and the actual address is based on the conversion rule.

Figure 3.2-5 Rule for conversion of actual addresses of general-purpose register area

Upper bits of RP Lower operation codes

"0" "0" "0" "0" "0" "0" "0" "1" R4 R3 R2 R1 R0 b2 b1 b0

Generated addresses

A15 A14 A13 A12 A10 A11 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

The register bank pointer points to the memory block (register bank) in the RAM area that is used for

general-purpose registers. A total of 32 register banks are available. A register bank is specified by setting a

value between 0 and 31 in the upper 5 bits of the register bank pointer. Each register bank contains eight 8-

bit general-purpose registers. Registers are specified by the lower 3 bits of the operation codes.

Using the register bank pointer, the addresses 0100

to 01FFH can be used as the general-purpose register

H

area. However, the available area is limited on some products if internal RAM only is used. The initial

value after a reset is indeterminate.

Note:

32

The register bank pointer is part of the program status (PS) and cannot be accessed independently.

Page 47

CHAPTER 3 CPU

3.3 General-purpose Registers

The general-purpose registers are a memory block made up of banks, with 8 x 8-bit

registers per bank.

The register bank pointer (RP) is used to specify the register bank.

The function permits the use of up to 32 banks, but the number of banks that can

actually be used depends on how much RAM the device has.

Register banks are valid for interrupt processing, vector call processing, and

subroutine calls.

■ Structure of general-purpose registers

• The general-purpose registers are 8 bits and located in the register banks of the general-purpose register

area (in RAM).

• One bank contains eight registers (R0 to R7) and up to a total of 32 banks. However, the number of

banks available for general-purpose registers is limited on some products if internal RAM only is used.

• The register bank currently in use is specified by the register bank pointer (RP). The lower three bits of

the operation code specify general-purpose register 0 (R0) to general-purpose register 7 (R7).

Figure 3.3-1 "Register bank structure" shows the register bank structure.

Figure 3.3-1 Register bank structure

Lower 3 bits of

the operation code

R0

R1

R2

R3

R4

R5

R6

R7

R0

R7

000

001

010

011

100

101

110

111

000

:

:

111

:

:

:

:

:

:

Bank 0

(RP="00000---

Bank 1

(RP="00001---

Bank 2

to

Bank 30

B")

B")

32 banks

(RAM area)

The number of banks is limited

on available RAM size.

100

108

H*

H*

1F8H*

1FFH

*: The top address of a register bank = 0100

000

R0

:

:

111