Freescale Semiconductor, Inc.

MCF5249

ColdFire® Integrated Microprocessor

User’s Manual

nc...

I

cale Semiconductor,

Frees

MCF5249UM/D

Rev. 4.0, 10/2003

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

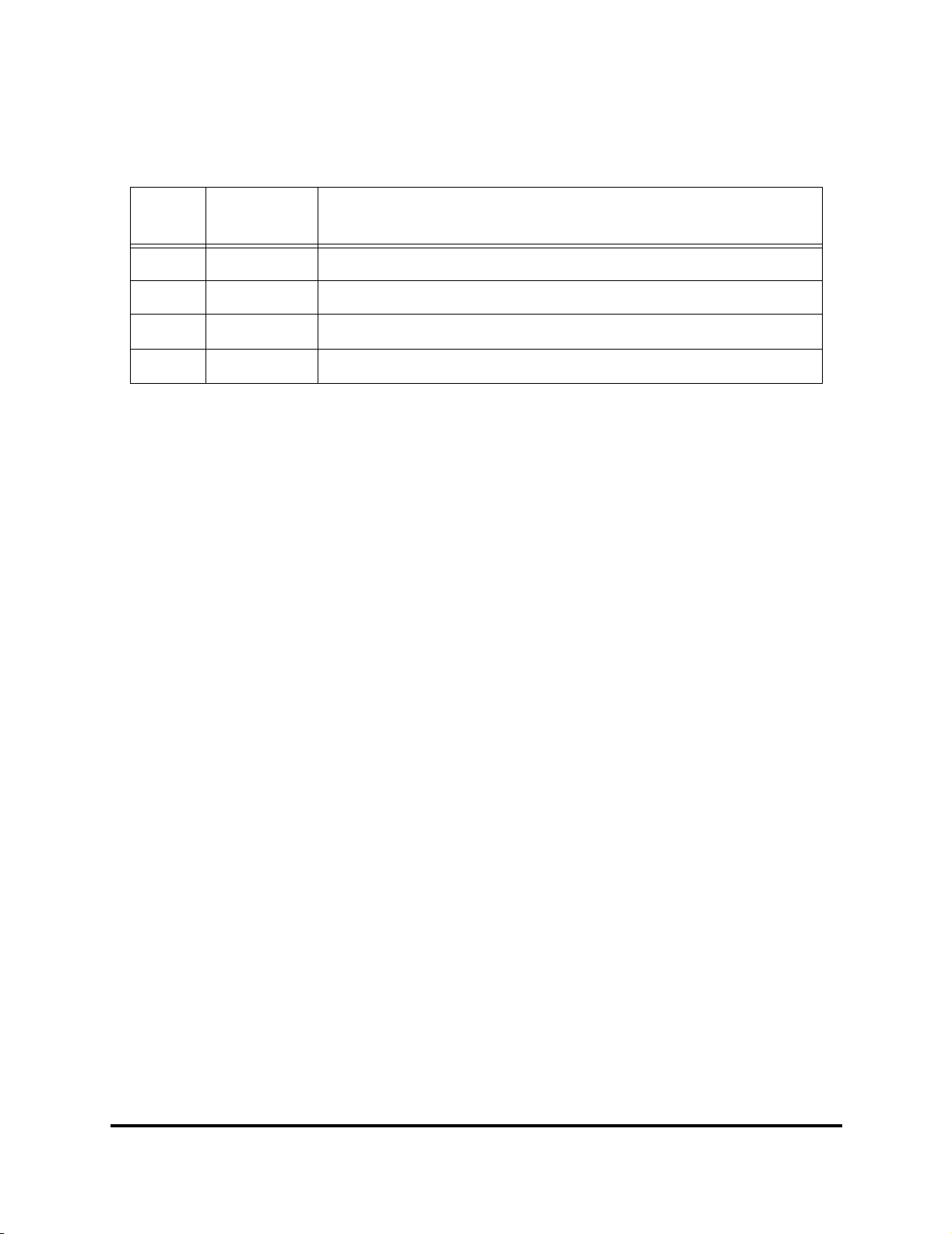

Document Revision History

Document Revision History

Rev.

No.

1.0 10/2002 Chapter 21, Electrical Specifications

2.0 05/2003 Chapter 21, Electrical Specifications

3.0 08/2003 Chapter 4, QSPISEL bit

4.0 10/29/03 Chapter 21, Electrical Specifications

nc...

I

cale Semiconductor,

Date Substantive Change(s)

Frees

2 MCF5249UM MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

TABLE OF CONTENTS

Paragraph Page

Number Number

SECTION 1

INTRODUCTION 1

1.1 MCF5249 Overview .............................................................................................................1-1

1.2 MCF5249 Feature Introduction ............................................................................................1-1

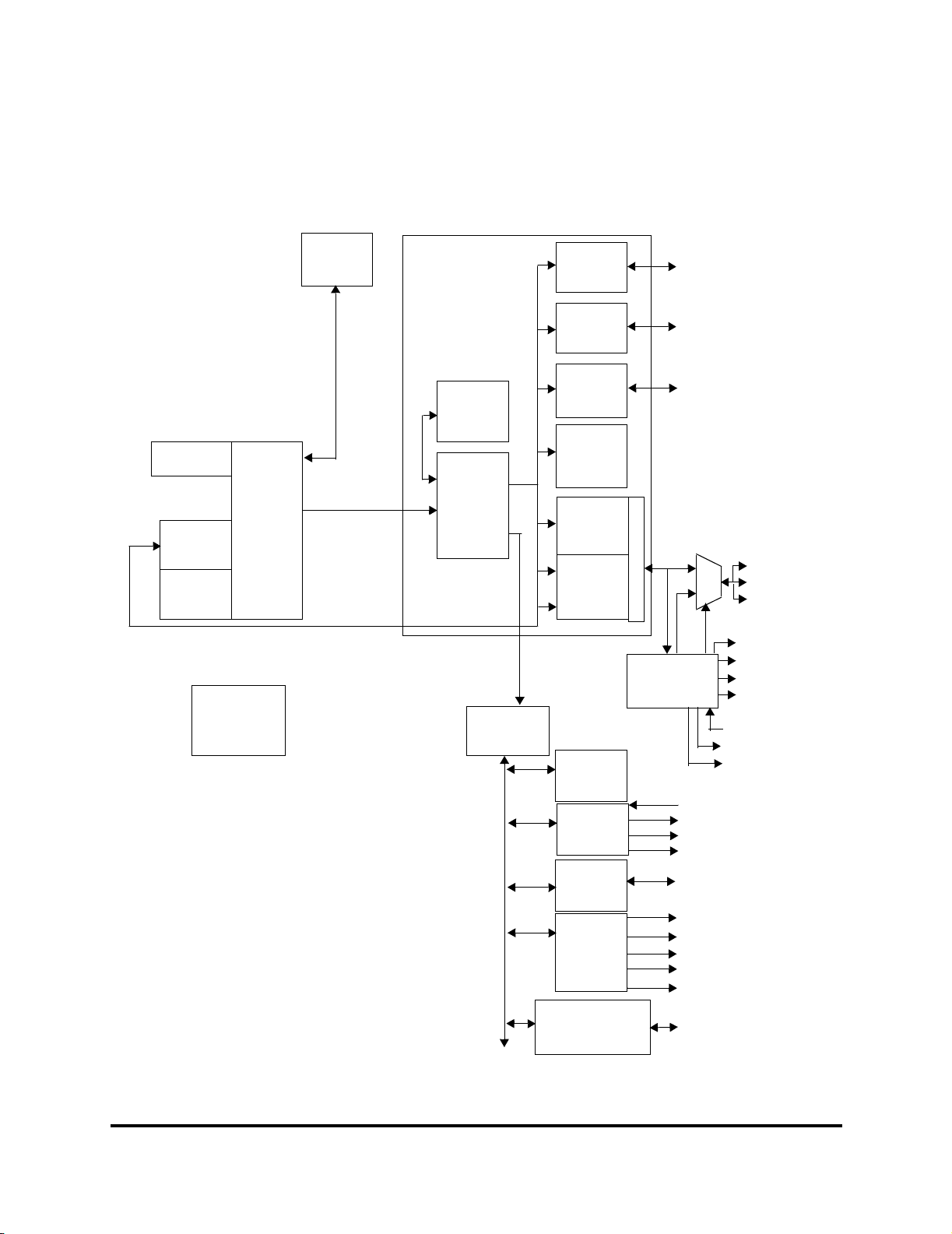

1.3 MCF5249 Block Diagram .....................................................................................................1-2

1.4 MCF5249 Feature Details ....................................................................................................1-3

1.5 160 MAPBGA Ball Assignments ..........................................................................................1-5

1.6 MCF5249 Functional Overview ...........................................................................................1-6

1.6.1 ColdFire V2 Core ............................................................................................................1-6

1.6.2 DMA Controller ...............................................................................................................1-6

1.6.3 Enhanced Multiply and Accumulate Module (EMAC) .....................................................1-6

1.6.4 Instruction Cache ............................................................................................................1-6

1.6.5 Internal 96-KByte SRAM ................................................................................................1-6

1.6.6 DRAM Controller ............................................................................................................1-7

1.6.7 System Interface .............................................................................................................1-7

1.6.8 External Bus Interface ....................................................................................................1-7

1.6.9 Serial Audio Interfaces ...................................................................................................1-7

1.6.10 IEC958 Digital Audio Interfaces ......................................................................................1-7

1.6.11 Audio Bus .......................................................................................................................1-7

1.6.12 CD-ROM Encoder/Decoder ............................................................................................1-8

1.6.13 Dual UART Module .........................................................................................................1-8

1.6.14 Queued Serial Peripheral Interface QSPI .......................................................................1-8

1.6.15 Timer Module ..................................................................................................................1-8

1.6.16 IDE and SmartMedia Interfaces .....................................................................................1-9

1.6.17 Analog/Digital Converter (ADC) ......................................................................................1-9

1.6.18 Flash Memory Card Interface .........................................................................................1-9

1.6.19 I

1.6.20 Chip-Selects ...................................................................................................................1-9

1.6.21 GPIO Interface ................................................................................................................1-9

1.6.22 Interrupt Controller ..........................................................................................................1-9

1.6.23 JTAG ............................................................................................................................1-10

1.6.24 System Debug Interface ...............................................................................................1-10

1.6.25 Crystal and On-chip PLL ..............................................................................................1-10

2.1 Introduction ..........................................................................................................................2-1

2.2 GPIO ....................................................................................................................................2-4

2.3 MCF5249 BUS SIGNALS ....................................................................................................2-4

2.3.1 ADDRESS BUS ..............................................................................................................2-4

2.3.2 READ-WRITE CONTROL ..............................................................................................2-4

2.3.3 OUTPUT ENABLE ..........................................................................................................2-5

2.3.4 Data Bus .........................................................................................................................2-5

2.3.5 Transfer Acknowledge ....................................................................................................2-5

2.4 SDRAM Controller Signals ..................................................................................................2-5

2.5 CHIP SELECTS ...................................................................................................................2-5

2.6 ISA bus ................................................................................................................................2-6

2.7 bus buffer signals .................................................................................................................2-6

2

C Module ......................................................................................................................1-9

SECTION 2

SIGNAL DESCRIPTION

MOTOROLA Table of Contents TOC-1

For More Information On This Product,

Go to: www.freescale.com

nc...

I

cale Semiconductor,

Frees

Table of Contents

Paragraph Page

Number Number

2.8 I2C Module Signals ..............................................................................................................2-6

2.9 Serial Module Signals ..........................................................................................................2-6

2.10 Timer Module Signals ..........................................................................................................2-7

2.11 Serial Audio Interface Signals ..............................................................................................2-7

2.12 Digital Audio Interface Signals .............................................................................................2-9

2.13 Subcode interface ................................................................................................................2-9

2.14 Analog to Digital Converter (ADC) .......................................................................................2-9

2.15 Secure Digital/ MemoryStick card Interface .......................................................................2-10

2.16 Queued Serial Peripheral Interface (QSPI) .......................................................................2-10

2.17 Crystal Trim .......................................................................................................................2-11

2.18 Clock Out ...........................................................................................................................2-11

2.19 Debug and Test Signals ....................................................................................................2-11

2.19.1 Test Mode .....................................................................................................................2-11

2.19.2 High Impedance ...........................................................................................................2-11

2.19.3 Processor Clock Output ................................................................................................2-11

2.19.4 Debug Data ..................................................................................................................2-11

2.19.5 Processor Status ..........................................................................................................2-11

2.20 BDM/JTAG Signals ............................................................................................................2-12

2.20.1 Test Clock .....................................................................................................................2-12

2.20.2 Test Reset/Development Serial Clock ..........................................................................2-12

2.20.3 Test Mode Select/Break Point ......................................................................................2-13

2.20.4 Test Data Input/Development Serial Input ....................................................................2-13

2.20.5 Test Data Output/Development Serial Output ..............................................................2-13

2.21 Clock and Reset signals ....................................................................................................2-14

2.21.1 Reset In ........................................................................................................................2-14

2.21.2 System Bus input ..........................................................................................................2-14

Freescale Semiconductor, Inc.

SECTION 3

COLDFIRE CORE

3.1 Processor Pipelines .............................................................................................................3-1

3.2 Processor Register Description ...........................................................................................3-2

3.2.1 User Programming Model ...............................................................................................3-2

3.2.1.1 Data Registers (D0–D7) ............................................................................................3-2

3.2.1.2 Address Registers (A0–A6) .......................................................................................3-2

3.2.1.3 Stack Pointer (A7,SP) ................................................................................................3-2

3.2.1.4 Program Counter (PC) ...............................................................................................3-3

3.2.1.5 Condition Code Register (CCR) ................................................................................3-3

3.2.2 Enhanced Multiply Accumulate Module (EMAC) User Programming Model ..................3-4

3.2.2.1 EMAC Instruction Set Summary ................................................................................3-4

3.2.3 Supervisor Programming Model .....................................................................................3-5

3.2.3.1 Status Register (SR) ..................................................................................................3-6

3.2.3.2 Vector Base Register (VBR) ......................................................................................3-6

3.3 Exception Processing Overview ..........................................................................................3-7

3.4 Exception Stack Frame Definition ........................................................................................3-8

3.5 Processor Exceptions ........................................................................................................3-10

3.5.1 Access Error Exception ................................................................................................3-10

3.5.2 Address Error Exception ...............................................................................................3-10

3.5.3 Illegal Instruction Exception ..........................................................................................3-10

3.5.4 Divide By Zero ..............................................................................................................3-10

3.5.5 Privilege Violation .........................................................................................................3-11

3.5.6 Trace Exception ............................................................................................................3-11

TOC-2 MCF5249UM MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

Paragraph Page

Number Number

3.5.7 Debug Interrupt .............................................................................................................3-11

3.5.8 RTE and Format Error Exceptions ................................................................................3-11

3.5.9 TRAP Instruction Exceptions ........................................................................................3-12

3.5.10 Interrupt Exception .......................................................................................................3-12

3.5.11 Fault-on-Fault Halt ........................................................................................................3-12

3.5.12 Reset Exception ...........................................................................................................3-12

3.6 Instruction Execution Timing ..............................................................................................3-12

3.6.1 Timing Assumptions .....................................................................................................3-13

3.6.2 MOVE Instruction Execution Times ..............................................................................3-13

3.7 Standard One Operand Instruction Execution Times ........................................................3-15

3.8 Standard Two Operand Instruction Execution Times ........................................................3-16

3.9 Miscellaneous Instruction Execution Times .......................................................................3-18

3.10 Branch Instruction Execution Times ..................................................................................3-19

Table of Contents

SECTION 4

PHASE-LOCKED LOOP AND CLOCK DIVIDERS

4.1 PLL Features .......................................................................................................................4-1

4.2 PLL Programming ................................................................................................................4-2

4.2.1 PLL Operation ................................................................................................................4-4

4.2.2 PLL Lock-in Time ............................................................................................................4-4

4..2.3 PLL Electrical Limits .......................................................................................................4-4

4.3 Audio Clock Generation .......................................................................................................4-5

4.4 Reduced Power Mode .........................................................................................................4-6

4.5 Recommended Settings ......................................................................................................4-6

SECTION 5

INSTRUCTION CACHE

5.1 Instruction Cache Features ..................................................................................................5-1

5.2 Instruction Cache Physical Organization .............................................................................5-1

5.3 Instruction Cache Operation ................................................................................................5-2

5.3.1 Interaction with Other Modules .......................................................................................5-2

5.3.2 Memory Reference Attributes .........................................................................................5-3

5.3.3 Cache Coherency and Invalidation .................................................................................5-3

5.3.4 Reset ..............................................................................................................................5-3

5.3.5 Cache Miss Fetch Algorithm/Line Fills ............................................................................5-3

5.4 Instruction Cache Programming Model ...............................................................................5-5

5.4.1 Instruction Cache Registers Memory Map ......................................................................5-5

5.4.2 Instruction Cache Register .............................................................................................5-6

5.4.2.1 Cache Control Register .............................................................................................5-6

5.4.2.2 Access Control Registers ..........................................................................................5-8

MOTOROLA Table of Contents TOC-3

For More Information On This Product,

Go to: www.freescale.com

nc...

I

cale Semiconductor,

Frees

Table of Contents

Paragraph Page

Number Number

Freescale Semiconductor, Inc.

SECTION 6

STATIC RAM (SRAM)

6.1 SRAM Features ...................................................................................................................6-1

6.2 SRAM Operation ..................................................................................................................6-1

6.3 SRAM Programming Model .................................................................................................6-1

6.3.1 SRAM Base Address Register .......................................................................................6-1

6.3.2 SRAM Initialization .........................................................................................................6-4

6.3.3 SRAM Initialization Code ................................................................................................6-4

6.3.4 Power Management .......................................................................................................6-4

SECTION 7

SYNCHRONOUS DRAM CONTROLLER MODULE

7.1 DRAM Features ...................................................................................................................7-1

7.1.1 Definitions .......................................................................................................................7-1

7.1.2 Block Diagram and Major Components ..........................................................................7-1

7.2 DRAM Controller Operation .................................................................................................7-2

7.2.1 DRAM Controller Registers ............................................................................................7-2

7.3 Synchronous Operation .......................................................................................................7-3

7.3.1 DRAM Controller Signals in Synchronous Mode ............................................................7-4

7.3.2 Synchronous Register Set ..............................................................................................7-5

7.3.2.1 DRAM Control Register (DCR) (Synchronous Mode) ...............................................7-5

7.3.2.2 DRAM Address and Control (DACR0/DACR1) (Synchronous Mode) .......................7-7

7.3.2.3 DRAM Controller Mask Registers (DMR0/DMR1) .....................................................7-9

7.3.3 General Synchronous Operation Guidelines ................................................................7-10

7.3.3.1 Address Multiplexing ...............................................................................................7-10

7.3.3.2 Interfacing Example .................................................................................................7-11

7.3.3.3 Burst Page Mode .....................................................................................................7-11

7.3.3.4 Continuous Page Mode ...........................................................................................7-13

7.3.3.5 Auto-Refresh Operation ...........................................................................................7-15

7.3.3.6 Self-Refresh Operation ............................................................................................7-16

7.3.4 Initialization Sequence ..................................................................................................7-17

7.3.4.1 Mode Register Settings ...........................................................................................7-17

7.4 SDRAM Example ...............................................................................................................7-18

7.4.1 SDRAM Interface Configuration ...................................................................................7-18

7.4.2 DCR Initialization ..........................................................................................................7-19

7.4.3 DACR Initialization ........................................................................................................7-19

7.4.4 DMR Initialization ..........................................................................................................7-21

7.4.5 Mode Register Initialization ..........................................................................................7-22

7.4.6 Initialization Code .........................................................................................................7-23

SECTION 8

BUS OPERATION

8.1 Bus Features .......................................................................................................................8-1

8.2 Bus And Control Signals ......................................................................................................8-1

8.2.1 Address Bus ...................................................................................................................8-1

8.2.2 Read/Write control ..........................................................................................................8-2

8.2.3 Transfer Acknowledge (TA) ............................................................................................8-2

8.2.4 Data Bus .........................................................................................................................8-2

8.2.5 Chip Selects ...................................................................................................................8-3

8.2.6 Output Enable .................................................................................................................8-3

TOC-4 MCF5249UM MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Paragraph Page

Number Number

8.3 Clock and Reset Signals ......................................................................................................8-3

8.3.1 Reset In ..........................................................................................................................8-4

8.3.2 System Bus Clock Output ...............................................................................................8-4

8.4 Bus Characteristics ..............................................................................................................8-4

8.5 Data Transfer Operation ......................................................................................................8-5

8.5.1 Bus Cycle Execution .......................................................................................................8-6

8.5.2 Read Cycle .....................................................................................................................8-7

8.5.3 Write Cycle .....................................................................................................................8-8

8.5.4 Back-to-Back Bus Cycles .............................................................................................8-10

8.5.5 Burst Cycles .................................................................................................................8-11

8.5.5.1 Line Transfers ..........................................................................................................8-11

8.5.5.2 Line Read Bus Cycles .............................................................................................8-11

8.5.5.3 Line Write Bus Cycles .............................................................................................8-12

8.6 Misaligned Operands .........................................................................................................8-14

8.7 Reset Operation .................................................................................................................8-15

8.7.1 Software Watchdog Reset ............................................................................................8-16

nc...

I

Table of Contents

SECTION 9

SYSTEM INTEGRATION MODULE

cale Semiconductor,

Frees

9.1 SIM Introduction ...................................................................................................................9-1

9.1.1 SIM Features ..................................................................................................................9-1

9.2 Programming Model ............................................................................................................9-1

9.2.1 SIM Register Memory Map .............................................................................................9-1

9.3 SIM Programming and Configuration ..................................................................................9-3

9.3.1 Module Base Address Registers ....................................................................................9-3

9.3.2 Device ID ........................................................................................................................9-5

9.3.3 Interrupt Controller ..........................................................................................................9-6

9.4 Interrupt Interface ................................................................................................................9-6

9.4.1 Primary controller Interrupt Registers .............................................................................9-6

9.4.1.1 Interrupt Mask Register .............................................................................................9-9

9.4.1.2 Interrupt Pending Register .......................................................................................9-10

9.4.2 Secondary Interrupt Controller Registers .....................................................................9-11

9.4.2.1 Interrupt Level Selection ..........................................................................................9-11

9.4.2.2 Interrupt Vector Generation .....................................................................................9-12

9.4.2.3 Spurious Vector Register .........................................................................................9-12

9.4.2.4 Secondary Interrupt Sources ...................................................................................9-12

9.4.3 Software interrupts .......................................................................................................9-15

9.5 System Protection And Reset Status .................................................................................9-15

9.5.1 Reset Status Register ...................................................................................................9-15

9.5.2 Software Watchdog Timer ............................................................................................9-16

9.5.2.1 System Protection Control Register ........................................................................9-18

9.5.2.2 Software Watchdog Interrupt Vector Register .........................................................9-19

9.5.2.3 Software Watchdog Service Register ......................................................................9-20

9.6 CPU STOP Instruction .......................................................................................................9-20

9.7 MCF5249 Bus Arbitration Control ......................................................................................9-20

9.7.1 Default Bus Master Park Register ................................................................................9-20

9.7.1.1 Internal Arbitration Operation ..................................................................................9-20

9.7.1.2 PARK Register Bit Configuration .............................................................................9-21

9.8 General Purpose I/Os ........................................................................................................9-23

9.8.1 General Purpose Inputs ................................................................................................9-23

9.8.1.1 General Purpose Input Interrupts ............................................................................9-25

9.8.2 General Purpose Outputs .............................................................................................9-26

MOTOROLA Table of Contents TOC-5

For More Information On This Product,

Go to: www.freescale.com

nc...

I

cale Semiconductor,

Frees

Table of Contents

Paragraph Page

Number Number

Freescale Semiconductor, Inc.

SECTION 10

CHIP-SELECT MODULE

10.1 Introduction ........................................................................................................................10-1

10.1.1 Chip Select Features ....................................................................................................10-1

10.2 Chip-Select Signals ...........................................................................................................10-1

10.2.1 Chip Selects .................................................................................................................10-1

10.2.1.1 CS0 .........................................................................................................................10-1

10.2.1.2 CS1/GPIO1 .............................................................................................................10-1

10.2.1.3 CS2/IDE-DIOR/GPIO13 and IDE-DIOW/GPIO14 ...................................................10-1

10.2.1.4 CS3/SRE/GPIO11 and SWE/GPIO12 .....................................................................10-2

10.2.2 Output Enable OE/gpio9 ...............................................................................................10-2

10.2.3 buffer enable signals - bufenb1 and bufenb2 ...............................................................10-2

10.2.4 IORDY - bus termination signal ....................................................................................10-2

10.3 MCF5249Chip-Select Operation ........................................................................................10-2

10.3.1 Chip-Select Module ......................................................................................................10-2

10.3.1.1 General Chip Select Operation ................................................................................10-3

10.3.1.1.1 Port Sizing ..........................................................................................................10-4

10.3.2 Global Chip-Select Operation .......................................................................................10-4

10.4 Programming Model ..........................................................................................................10-4

10.4.1 Chip-Select Registers Memory Map .............................................................................10-4

10.4.2 Chip Select Module Registers ......................................................................................10-6

10.4.2.1 Chip Select Address Register ..................................................................................10-6

10.4.2.2 Chip Select Mask Register ......................................................................................10-6

10.4.2.3 Chip Select Control Register ...................................................................................10-8

10.4.2.4 Code example .......................................................................................................10-10

SECTION 11

TIMER MODULE

11.1 Timer Module Overview .....................................................................................................11-1

11.2 Timer Features ..................................................................................................................11-1

11.3 Timer Signals .....................................................................................................................11-1

11.3.1 Timer Inputs ..................................................................................................................11-1

11.3.2 Timer Outputs ...............................................................................................................11-1

11.4 General-Purpose Timer Units ............................................................................................11-2

11.4.1 Selecting the Prescaler .................................................................................................11-3

11.4.2 Capture Mode ...............................................................................................................11-3

11.4.3 Configuring the Timer for Reference Compare .............................................................11-3

11.4.4 Configuring the Timer for Output Mode ........................................................................11-3

11.5 General-Purpose Timer Registers .....................................................................................11-3

11.5.1 Timer Mode Registers (TMR0, TMR1) .........................................................................11-4

11.5.2 Timer Reference Registers (TRR0, TRR1) ...................................................................11-5

11.5.3 Timer Capture Registers (TCR0, TCR1) ......................................................................11-5

11.5.4 Timer Counters (TCN0, TCN1) .....................................................................................11-6

11.5.5 Timer Event Registers (TER0, TER1) ..........................................................................11-6

11.5.6 Timer Initialization Example Code ................................................................................11-7

11.5.6.1 Timer 0 (Timer Mode Register) ...............................................................................11-7

11.5.6.2 Timer 0 (Timer Reference Register 0) .....................................................................11-8

11.5.6.3 Timer 1 (Timer Mode Register 1) ............................................................................11-8

TOC-6 MCF5249UM MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Paragraph Page

Number Number

Table of Contents

SECTION 12

ANALOG TO DIGITAL CONVERTER (ADC)

12.1 ADC Overview ...................................................................................................................12-1

12.2 ADC Functionality ..............................................................................................................12-2

SECTION 13

IDE AND FLASHMEDIA INTERFACE

13.1 IDE and SmartMedia Overview .........................................................................................13-1

13.1.1 Buffer enables bufenb1, bufenB2, and associated logic. .............................................13-2

13.1.2 Generation of IDE-DIOR, IDE-DIOW, SRE, SWE ........................................................13-4

13.1.3 Cycle termination on CS2, CS3 (DIOR, DIOW, SRE, SWE) ........................................13-5

13.2 SmartMedia Interface Setup ..............................................................................................13-6

13.2.1 SmartMedia timing ........................................................................................................13-7

13.3 Setting Up The IDE Interface .............................................................................................13-8

nc...

I

cale Semiconductor,

13.3.1 IDE timing diagram .......................................................................................................13-8

13.4 FlashMedia Interface .......................................................................................................13-10

13.4.1 FlashMedia Interface Registers ..................................................................................13-10

13.4.1.1 FlashMedia Clock Generation and Configuration ..................................................13-11

13.4.2 FlashMedia Interface Operation .................................................................................13-12

13.4.2.1 FlashMedia Command Registers in MemoryStick Mode .......................................13-13

13.4.2.2 FlashMedia Command Register 1 in Secure Digital Mode ....................................13-13

13.4.2.3 FLASHMEDIA COMMAND REGISTER 2 in Secure Digital Mode ........................13-14

13.4.3 FlashMedia Data Register ..........................................................................................13-15

13.4.3.1 FlashMedia Status Register ..................................................................................13-15

13.4.4 FlashMedia Interrupt Interface ....................................................................................13-15

13.4.5 FlashMedia Interface Operation in MemoryStick Mode ..............................................13-16

13.4.5.1 Reading Data From the MemoryStick ...................................................................13-17

13.4.5.2 Writing Data to the MemoryStick ...........................................................................13-18

13.4.5.3 Interrupt From MemoryStick ..................................................................................13-19

13.4.6 FlashMedia interface Operation in Secure Digital (SD) mode ....................................13-20

13.4.6.1 Sent Command To Card ........................................................................................13-20

13.4.6.2 Write Data To Card ................................................................................................13-21

13.4.7 Commonly used commands in SD mode ...................................................................13-23

13.4.7.1 Send Command To Card (No Data) ......................................................................13-23

13.4.7.2 Send Command To Card (Receive Multiple Data Blocks and Status) ..................13-24

13.4.7.3 Send Command To Card (Write Multiple Data Blocks) .........................................13-25

Frees

SECTION 14

DMA CONTROLLER MODULE

14.1 DMA Features ....................................................................................................................14-2

14.2 DMA Signal Description .....................................................................................................14-2

14.2.1 DMA Request ...............................................................................................................14-2

14.3 DMA Module Overview ......................................................................................................14-2

14.4 DMA Programming Model .................................................................................................14-3

14.4.1 REQUEST source selection .........................................................................................14-5

14.4.2 Source Address Register ..............................................................................................14-8

14.4.3 FLASHmEDIA DATA RegisterS ...................................................................................14-9

14.4.4 Byte Count Register .....................................................................................................14-9

14.4.5 DMA Control Register .................................................................................................14-10

MOTOROLA Table of Contents TOC-7

For More Information On This Product,

Go to: www.freescale.com

Table of Contents

Paragraph Page

Number Number

14.4.6 DMA Status Register ..................................................................................................14-13

14.4.7 DMA Interrupt Vector Register ...................................................................................14-15

14.5 Transfer Request Generation ..........................................................................................14-15

14.5.1 Cycle-Steal Mode .......................................................................................................14-15

14.5.2 Continuous Mode .......................................................................................................14-15

14.6 Data Transfer Modes .......................................................................................................14-16

14.6.1 Dual-Address Transaction ..........................................................................................14-16

14.6.1.1 Dual-Address Read ...............................................................................................14-16

14.6.1.2 Dual-Address Write ...............................................................................................14-16

14.7 DMA Transfer Functional Description .............................................................................14-16

14.7.1 Channel Initialization and Startup ...............................................................................14-17

14.7.1.1 Channel Prioritization ............................................................................................14-17

14.7.1.2 Programming the DMA ..........................................................................................14-17

14.7.2 Data Transfer ..............................................................................................................14-18

14.7.2.1 Periphery Request Operation ................................................................................14-18

14.7.2.2 Auto Alignment ......................................................................................................14-18

nc...

I

14.7.2.3 Bandwidth Control .................................................................................................14-19

14.7.3 Channel Termination ..................................................................................................14-19

14.7.3.1 Error Conditions .....................................................................................................14-19

14.7.3.2 Interrupts ...............................................................................................................14-19

Freescale Semiconductor, Inc.

cale Semiconductor,

Frees

SECTION 15

UART MODULES

15.1 Module Overview ...............................................................................................................15-1

15.1.1 Serial Communication Channel ....................................................................................15-2

15.1.2 Baud-Rate Generator/Timer .........................................................................................15-2

15.1.3 Interrupt Control Logic ..................................................................................................15-2

15.2 UART Module Signal Definitions .......................................................................................15-3

15.2.1 Transmitter Serial Data Output .....................................................................................15-3

15.2.2 Receiver Serial Data Input ............................................................................................15-3

15.2.3 Request-To-Send .........................................................................................................15-4

15.2.4 Clear-To-Send ..............................................................................................................15-4

15.3 Operation ...........................................................................................................................15-4

15.3.1 Baud-Rate Generator/Timer .........................................................................................15-4

15.3.2 Transmitter and Receiver Operating Modes .................................................................15-5

15.3.2.1 Transmitter ..............................................................................................................15-5

15.3.2.2 Receiver ..................................................................................................................15-7

15.3.2.3 Receiver FIFO .........................................................................................................15-8

15.3.3 Looping Modes .............................................................................................................15-9

15.3.3.1 Automatic Echo Mode .............................................................................................15-9

15.3.3.2 Local Loopback Mode .............................................................................................15-9

15.3.3.3 Remote Loopback Mode .......................................................................................15-10

15.3.4 Multidrop Mode ...........................................................................................................15-10

15.3.5 Bus Operation .............................................................................................................15-12

15.3.5.1 Read Cycles ..........................................................................................................15-12

15.3.5.2 Write Cycles ..........................................................................................................15-12

15.3.5.3 Interrupt Acknowledge Cycles ...............................................................................15-12

15.4 Register Description and Programming ...........................................................................15-12

15.4.1 Register Description ...................................................................................................15-12

15.4.1.1 Mode Register 1 (UMR1n) .....................................................................................15-13

15.4.1.2 Mode Register 2 (UMR2n) .....................................................................................15-15

TOC-8 MCF5249UM MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

Paragraph Page

Number Number

15.4.1.3 Status Registers (USRn) .......................................................................................15-18

15.4.1.4 Clock-Select Registers (USCRn) ...........................................................................15-19

15.4.1.5 Command Registers (UCRn) .................................................................................15-20

15.4.1.6 Miscellaneous Commands ....................................................................................15-20

15.4.1.6.1 Reset Mode Register Pointer ...........................................................................15-21

15.4.1.6.2 Reset Receiver .................................................................................................15-21

15.4.1.6.3 Reset Transmitter .............................................................................................15-21

15.4.1.6.4 Reset Error Status ............................................................................................15-21

15.4.1.6.5 Reset Break-Change Interrupt .........................................................................15-21

15.4.1.6.6 Start Break .......................................................................................................15-21

15.4.1.6.7 Stop Break ........................................................................................................15-21

15.4.1.7 Transmitter Commands .........................................................................................15-21

15.4.1.7.1 No Action Taken ...............................................................................................15-22

15.4.1.7.2 Transmitter Enable ...........................................................................................15-22

15.4.1.7.3 Transmitter Disable ..........................................................................................15-22

15.4.1.7.4 Do Not Use .......................................................................................................15-22

15.4.1.8 Receiver Commands .............................................................................................15-22

15.4.1.8.1 No Action Taken ...............................................................................................15-22

15.4.1.8.2 Receiver Enable ...............................................................................................15-22

15.4.1.8.3 Receiver Disable ..............................................................................................15-23

15.4.1.8.4 Do Not Use .......................................................................................................15-23

15.4.1.9 Receiver Buffer Registers (UBRn) .........................................................................15-23

15.4.1.10 Transmitter Buffer Registers (UTBn) .....................................................................15-23

15.4.1.11 Input Port Change Registers UIPCRn) ..................................................................15-24

15.4.1.12 Auxiliary Control Registers (UACRn) .....................................................................15-24

15.4.1.13 Interrupt Status Registers (UISRn) ........................................................................15-25

15.4.1.14 Interrupt Mask Registers UIMRn) ..........................................................................15-26

15.4.1.15 Timer Upper Preload Register (UBG1n) ................................................................15-27

15.4.1.16 Timer Upper Preload Register 2 (UBG2n) .............................................................15-27

15.4.1.17 Interrupt Vector Registers (UIVRn) ........................................................................15-27

15.4.1.18 Input Port Registers (UIPn) ...................................................................................15-28

15.4.1.19 Output Port Data Registers (UOP1n) ....................................................................15-28

15.4.2 Programming ..............................................................................................................15-29

15.4.2.1 UART Module Initialization ....................................................................................15-29

15.4.2.2 I/O Driver Example ................................................................................................15-29

15.4.1.3 Interrupt Handling ..................................................................................................15-29

15.5 UART Module Initialization Sequence .............................................................................15-30

Table of Contents

SECTION 16

QUEUED SERIAL PERIPHERAL INTERFACE (QSPI) MODULE

16.1 Overview ............................................................................................................................16-1

16.2 Features .............................................................................................................................16-1

16.3 Module Description ............................................................................................................16-1

16.3.1 Interface and Pins .........................................................................................................16-1

16.3.2 Internal Bus Interface ...................................................................................................16-2

16.4 Operation ...........................................................................................................................16-3

16.4.1 QSPI RAM ....................................................................................................................16-3

16.4.1.1 Transmit RAM ..........................................................................................................16-5

16.4.1.2 Receive RAM ...........................................................................................................16-5

16.4.1.3 Command RAM .......................................................................................................16-5

16.4.2 Baud Rate Selection .....................................................................................................16-6

MOTOROLA Table of Contents TOC-9

For More Information On This Product,

Go to: www.freescale.com

Table of Contents

Paragraph Page

Number Number

16.4.3 Transfer Delays ............................................................................................................16-6

16.4.4 Transfer Length ............................................................................................................16-7

16.4.5 Data Transfer ................................................................................................................16-7

16.5 Programming Model ..........................................................................................................16-8

16.5.1 QSPI Mode Register (QMR) .........................................................................................16-8

16.5.2 QSPI Delay Register (QDLYR) ...................................................................................16-10

16.5.3 QSPI Wrap Register (QWR) .......................................................................................16-10

16.5.4 QSPI Interrupt Register (QIR) ....................................................................................16-11

16.5.5 QSPI Address Register (QAR) ...................................................................................16-12

16.5.6 QSPI Data Register (QDR) .........................................................................................16-13

16.5.7 Command RAM Registers (QCR0–QCR15) ...............................................................16-13

16.5.8 Programming Example ...............................................................................................16-15

Freescale Semiconductor, Inc.

SECTION 17

AUDIO FUNCTIONS

nc...

I

cale Semiconductor,

Frees

17.1 Audio Interface Overview ...................................................................................................17-1

17.1.1 Audio Interface Structure ..............................................................................................17-2

17.1.1.1 Audio Interrupt Mask and Interrupt Status Registers ...............................................17-3

17.2 Serial Audio Interface (IIS/EIAJ) ........................................................................................17-5

17.2.1 IIS/EIAJ Transmitter Descriptions .................................................................................17-9

17.2.2 IIS/EIAJ Transmitter Interrupts .....................................................................................17-9

17.2.3 IIS/EIAJ Receiver Descriptions .....................................................................................17-9

17.3 Digital Audio Interface (EBU) ...........................................................................................17-10

17.3.1 IEC958 Receive Interface ...........................................................................................17-13

17.3.1.1 Audio Data Reception ............................................................................................17-13

17.3.1.2 Control Channel Reception ...................................................................................17-13

17.3.1.3 Control Channel Interrupt (IEC958 “C” Channel New Frame) ...............................17-13

17.3.1.4 Validity Flag Reception ..........................................................................................17-13

17.3.1.5 IEC958 Exception Definition ..................................................................................17-14

17.3.1.6 EBU Extracted Clock .............................................................................................17-14

17.3.1.7 Reception of User Channel and CD-subcode Over IEC958 Receiver ..................17-14

17.3.1.8 U and Q Receive Register Interrupts .....................................................................17-16

17.3.1.9 Behavior of User Channel Receive Interface (CD Data) .......................................17-16

17.3.1.10 Behavior of User Channel Receive Interface (non-CD data) .................................17-18

17.3.2 IEC958 Transmit Interface ..........................................................................................17-18

17.3.2.1 Transmit “C” Channel ............................................................................................17-18

17.3.2.2 IEC958 Transmitter Exception Conditions .............................................................17-19

17.3.2.3 IEC958-3 Ed2 and Tech 3250-E Standards Compliance ......................................17-19

17.3.2.4 Transmission of U-Channel and CD Subcode Data ..............................................17-20

17.3.3 CD Subcode Interrupts ...............................................................................................17-21

17.3.3.1 Free Running Counter Synchronization ................................................................17-22

17.3.3.2 Controlling the SFSY Sync Position ......................................................................17-22

17.3.4 Inserting CD User Channel Data Into IEC958 Transmit Data .....................................17-22

17.4 Processor Interface Overview ..........................................................................................17-23

17.4.1 Data Exchange Register Descriptions ........................................................................17-23

17.4.2 Data Exchange Register Overview .............................................................................17-24

17.4.2.1 Data In Selection ...................................................................................................17-25

17.4.3 PDIR and PDOR Field Formatting ..............................................................................17-27

17.4.4 Overrun and Underrun with PDIR and PDOR Registers ............................................17-27

17.4.5 Automatic Resynchronization of FIFOs ......................................................................17-28

17.4.6 Audio Interrupts ..........................................................................................................17-30

TOC-10 MCF5249UM MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

Paragraph Page

Number Number

17.4.6.1 AudioTick Interrupts ...............................................................................................17-30

17.4.6.2 PDIR1, PDIR2, and PDIR3, Exceptions ................................................................17-30

17.4.6.3 PDOR1, PDOR2, and PDOR3 Exceptions ............................................................17-30

17.4.6.4 Audio Interrupt Routines and Timing .....................................................................17-32

17.4.7 CD-ROM Block Encoder and Decoder .......................................................................17-33

17.4.7.1 CD-ROM Decoder Interrupts .................................................................................17-35

17.4.7.2 CD-ROM Encoder Interrupts .................................................................................17-36

17.5 DMA Channel Interaction .................................................................................................17-36

17.6 Phase/Frequency Determination and Xtrim Function ......................................................17-37

17.6.1 Incoming Source Frequency Measurement ................................................................17-37

17.6.1.1 Filtering for the Discrete Time Oscillator ...............................................................17-40

17.6.2 XTRIM Option - Locking Xtal Clock to Incoming Signal ..............................................17-40

17.6.3 XTRIM Internal Logic ..................................................................................................17-40

17.7 Audio Interface Memory Map ...........................................................................................17-41

Table of Contents

SECTION 18

I2C MODULES

18.1 I2C Overview ......................................................................................................................18-1

18.2 I

18.3 I

18.4 I

18.4.1 START Signal ...............................................................................................................18-3

18.4.2 Slave Address Transmission ........................................................................................18-3

18.4.3 Data Transfer ................................................................................................................18-4

18.4.4 Repeated START Signal ..............................................................................................18-4

18.4.5 STOP Signal .................................................................................................................18-4

18.4.6 Arbitration Procedure ....................................................................................................18-4

18.4.7 Clock Synchronization ..................................................................................................18-4

18.4.8 Handshaking .................................................................................................................18-5

18.4.9 Clock Stretching ...........................................................................................................18-5

18.5 Programming Model ..........................................................................................................18-5

18.5.1 I

18.5.2 I

18.5.3 I

18.5.4 I

18.5.5 I

18.6 I

18.6.1 Initialization Sequence ................................................................................................18-12

18.6.2 Generation of START .................................................................................................18-12

18.6.3 Post-Transfer Software Response .............................................................................18-13

18.6.4 Slave Mode .................................................................................................................18-14

18.6.5 Arbitration Lost ...........................................................................................................18-15

2

C Interface Features .......................................................................................................18-1

2

C System Configuration ..................................................................................................18-2

2

C Protocol .......................................................................................................................18-3

2

C Address Registers (MADR) ....................................................................................18-6

2

C Frequency Divider Registers (MFDR) ....................................................................18-6

2

C Control Registers (MBCR) ......................................................................................18-8

2

C Status Registers (MBSR) .....................................................................................18-10

2

C Data I/O Registers (MBDR) ..................................................................................18-11

2

C Programming Examples ............................................................................................18-12

SECTION 19

DEBUG SUPPORT

19.1 Breakpoint (BKPT) .............................................................................................................19-1

19.1.1 Debug Support Signals ................................................................................................19-1

19.1.2 Debug Data (DDATA[3:0]) ............................................................................................19-1

19.1.3 Development Serial Clock (DSCLK) .............................................................................19-2

19.1.4 Development Serial Input (DSI) ....................................................................................19-2

MOTOROLA Table of Contents TOC-11

For More Information On This Product,

Go to: www.freescale.com

nc...

I

cale Semiconductor,

Frees

Table of Contents

Paragraph Page

Number Number

19.1.5 Development Serial Output (DSO) ...............................................................................19-2

19.1.6 Processor Status (PST[3:0]) .........................................................................................19-2

19.1.7 Processor Status Clock (PSTCLK) ...............................................................................19-3

19.2 Real-Time Trace Support ..................................................................................................19-4

19.2.1 Processor Status Signal Encoding ...............................................................................19-4

19.2.1.1 Continue Execution (PST = $0) ...............................................................................19-4

19.2.1.2 Begin Execution of an Instruction (PST = $1) .........................................................19-4

19.2.1.3 Entry into User Mode (PST = $3) ............................................................................19-4

19.2.1.4 Begin Execution of PULSE or WDDATA instructions (PST = $4) ...........................19-4

19.2.1.5 Begin Execution of Taken Branch (PST = $5) .........................................................19-5

19.2.1.6 Begin Execution of RTE Instruction (PST = $7) ......................................................19-6

19.2.1.7 Begin Data Transfer (PST = $8–$B) .......................................................................19-6

19.2.1.8 Exception Processing (PST = $C) ...........................................................................19-6

19.2.1.9 Emulator Mode Exception Processing (PST = $D) .................................................19-6

19.2.1.10 Processor Stopped (PST = $E) ...............................................................................19-6

19.2.1.11 Processor Halted (PST = $F) ..................................................................................19-6

19.3 Background-Debug Mode (BDM) ......................................................................................19-6

19.3.1 CPU Halt .......................................................................................................................19-7

19.3.2 BDM Serial Interface ....................................................................................................19-7

19.3.2.1 Receive Packet Format ...........................................................................................19-8

19.3.2.2 Transmit Packet Format ..........................................................................................19-9

19.3.3 BDM Command Set ......................................................................................................19-9

19.3.3.1 BDM Command Set Summary ................................................................................19-9

19.3.3.2 ColdFire BDM Commands .......................................................................................19-9

19.3.3.3 Command Sequence Diagram ..............................................................................19-11

19.3.3.4 Command Set Descriptions ...................................................................................19-13

19.3.3.4.1 Read Address/Data Register (RAREG/RDREG) .............................................19-13

19.3.3.4.2 Write Address/Data Register (WAREG and WDREG) .....................................19-13

19.3.3.4.3 Read Memory Location (READ) .......................................................................19-14

19.3.3.4.4 Write Memory Location (WRITE) .....................................................................19-16

19.3.3.4.5 Dump Memory Block (DUMP) ..........................................................................19-17

19.3.3.4.6 Fill Memory Block (FILL) ..................................................................................19-18

19.3.3.4.7 Resume Execution (GO) ..................................................................................19-20

19.3.3.4.8 No Operation (NOP) .........................................................................................19-20

19.3.3.4.9 Read Control Register (RCREG) .....................................................................19-21

19.3.3.4.10 Write Control Register (WCREG) .....................................................................19-22

19.3.3.4.11 Read Debug Module Register (RDMREG) .......................................................19-22

19.3.3.4.12 Write Debug Module Register (WDMREG) ......................................................19-23

19.3.3.4.13 Unassigned Opcodes .......................................................................................19-24

19.3.3.5 BDM Accesses of the EMAC Registers .................................................................19-24

19.4 Real-Time Debug Support ...............................................................................................19-25

19.4.1 Theory of Operation ....................................................................................................19-26

19.4.1.1 Emulator Mode ......................................................................................................19-27

19.4.1.2 Debug Module Hardware .......................................................................................19-27

19.4.1.2.1 Reuse of Debug Module Hardware (Rev. A) ....................................................19-27

19.4.2 Programming Model ...................................................................................................19-28

19.4.2.1 Address Breakpoint Registers ...............................................................................19-28

19.4.2.2 Address Attribute Trigger Register ........................................................................19-29

19.4.2.3 Program Counter Breakpoint Register (PBR, PBMR) ...........................................19-31

19.4.2.4 Data Breakpoint Registers (DBR, DBMR) .............................................................19-32

19.4.2.5 Trigger Definition Register (TDR) ..........................................................................19-34

19.4.2.6 Configuration/Status Register (CSR) .....................................................................19-36

Freescale Semiconductor, Inc.

TOC-12 MCF5249UM MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

Paragraph Page

Number Number

19.4.2.7 BDM Address Attribute (BAAR) .............................................................................19-39

19.4.3 Concurrent BDM and Processor Operation ................................................................19-40

19.4.4 Motorola-Recommended BDM Pinout ........................................................................19-41

Table of Contents

SECTION 20

IEEE 1149.1 TEST ACCESS PORT (JTAG)

20.1 JTAG Overview ..................................................................................................................20-1

20.2 JTAG Signal Descriptions .................................................................................................20-2

20.2.1 Test Clock - (TCK) ........................................................................................................20-3

20.2.2 Test Reset/Development Serial Clock - (TRST/DSCLK) ..............................................20-3

20.2.3 Test Mode Select/ Breakpoint (TMS/BKPT) .................................................................20-3

20.2.4 Test Data Input/Development Serial Input - (TDI/DSI) .................................................20-4

20.2.5 Test Data Output/Development Serial Output - (TDO/DSO) ........................................20-4

20.3 TAP Controller ...................................................................................................................20-4

20.4 JTAG Registers .................................................................................................................20-6

20.4.1 JTAG Instruction Shift Register ...................................................................................20-6

20.4.1.1 EXTEST Instruction .................................................................................................20-6

20.4.1.2 IDCODE ...................................................................................................................20-6

20.4.1.3 SAMPLE/PRELOAD Instruction ..............................................................................20-7

20.4.1.4 CLAMP Instruction ...................................................................................................20-7

20.4.1.5 HIGHZ Instruction ....................................................................................................20-7

20.4.1.6 BYPASS Instruction .................................................................................................20-7

20.4.2 IDcode Register ............................................................................................................20-8