Fairchild Semiconductor MM74HC574WMX, MM74HC574SJ, MM74HC574MTC, MM74HC574MTCX, MM74HC574WM Datasheet

...

September 1983

Revised February 1999

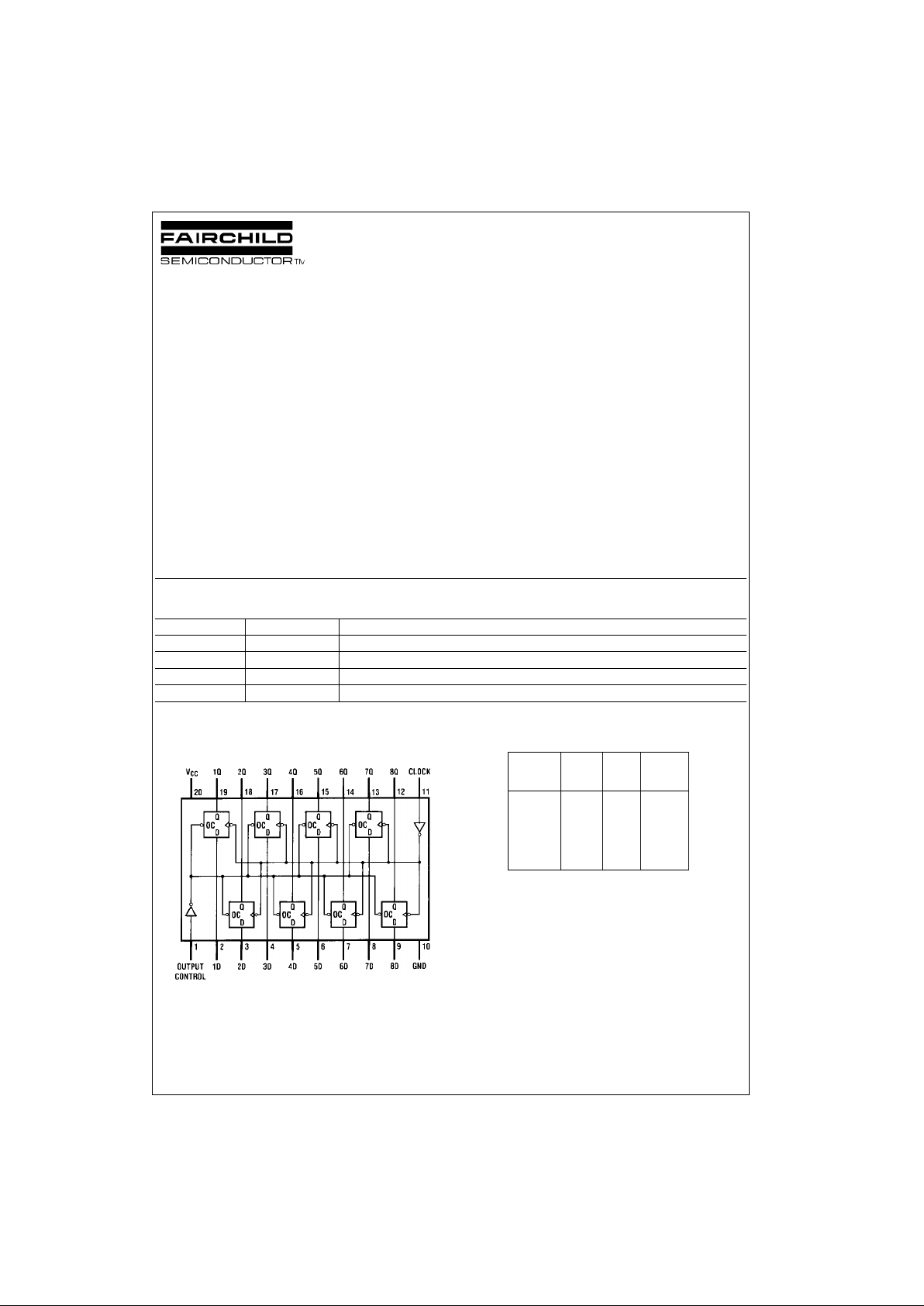

MM74HC574 3-STATE Octal D-Type Edge-Triggered Flip-Flop

© 1999 Fairchild Semiconductor Corporation DS005213.prf www.fairchildsemi.com

MM74HC574

3-STATE Octal D-Type Edge-Triggered Flip-Flop

General Description

The MM74HC574 high speed octal D-type flip-flops utilize

advanced silicon-gate P-well CMOS technology. They possess the high noise immun ity and low powe r consumption

of standard CMOS integrated circuits , a s well as th e a bility

to drive 15 LS-TTL loads. Due to the large output drive

capability and the 3-STATE feature, these devices are ideally suited for interfacing with bus lines in a bus organized

system.

These devices are positive e dge triggered flip-flops. Da ta

at the D inputs, meeting the set-up and hold time req uirements, are transferred to th e Q outputs on positive going

transitions of the CLOC K (CK) input. When a high logic

level is applied to the OUTPUT CONTROL (OC) input, all

outputs go to a high im pedance state, regar dless of what

signals are present at the oth er inputs and the state of the

storage elements.

The 74HC logic fam ily is spee d, function , and pi nout compatible with the sta ndard 74LS logic fami ly. All inputs are

protected from damage due to static discharge by inte rnal

diode clamps to V

CC

and ground.

Features

■ Typical propagation delay: 18 ns

■ Wide operating voltage range: 2V–6V

■ Low input current: 1 µA maximum

■ Low quiescent current: 80 µA maximum

■ Compatible with bus-oriented systems

■ Output drive capability: 15 LS-TTL loads

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering cod e.

Connection Diagram

Pin Assignments f or DIP, SOIC, SOP and TSSOP

Top View

Truth Table

H = HIGH Level

L = LOW Level

X = Don't Care

↑ = Transition from LOW-to-HIGH

Z = High Impedance St at e

Q

0

= The le vel of the output before ste ady state input conditions w ere

established

Order Number Package Number Package Description

MM74C574WM M20B 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300”

MM74C574SJ M20D 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

MM74C574MTC MTC20 20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4m Wide

MM74C574N N20A 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide

Output Clock Data Output

Control

L ↑ HH

L ↑ LL

LLXQ

0

HXXZ

www.fairchildsemi.com 2

MM74HC574

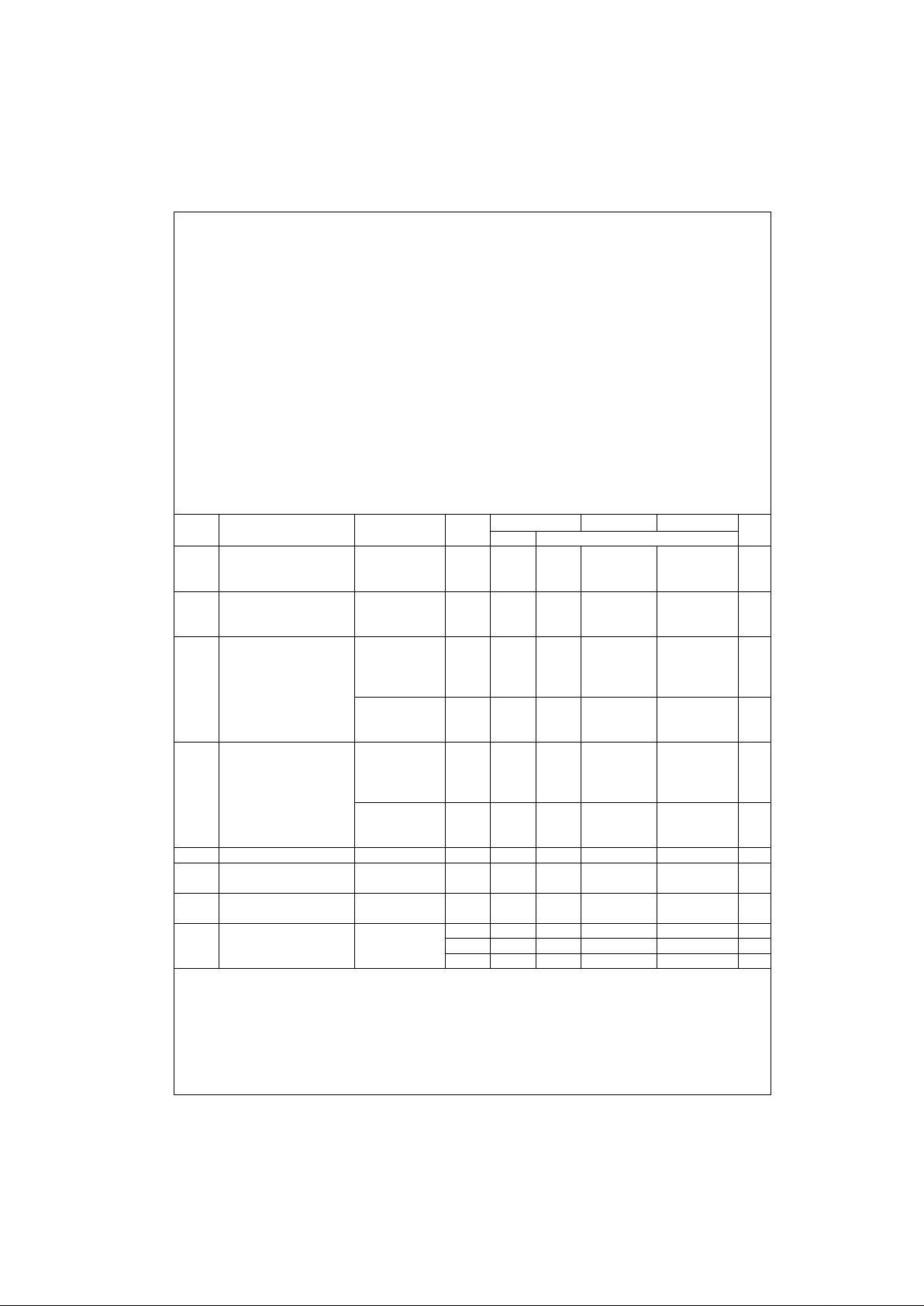

Absolute Maximum Ratings(Note 1)

(Note 2)

Recommended Operating

Conditions

Note 1: Maximum Ratings are those values beyond which damage to the

device may occur.

Note 2: Unless otherwise specified all voltages are referenced to ground.

Note 3: Power Dissipation temper ature dera ting — plas tic “N” packa ge: −

12 mW/°C from 65 °C to 85°C.

DC Electrical Characteristics (Note 4)

Note 4: For a power supply of 5V ±1 0% the w orst-c ase ou tput vol tages (VOH, and VOL) occur for HC at 4.5V. Thus the 4. 5V valu es shoul d be use d when

designing with this supply. Worst-case V

IH

and VIL occur at V

CC

= 5.5V and 4.5V respectively. (The VIH value at 5.5V is 3.85V.) The worst-case leakage cur-

rent (I

IN

, ICC, and IOZ) occur for CMOS at the higher voltage and so th e 6. 0V values should be used.

Supply Voltage (VCC) −0.5 to +7.0V

DC Input Voltage (V

IN

) −1.5 to V

CC

+1.5V

DC Output Voltage (V

OUT

) −0.5 to V

CC

+0.5V

Clamp Diode Current (I

IK

, IOK) ±20 mA

DC Output Current, per pin (I

OUT

) ±35 mA

DC V

CC

or GND Current, per pin (ICC) ±70 mA

Storage Temperature Range (T

STG

) −65°C to +150°C

Power Dissipation (P

D

)

(Note 3) 600 mW

S.O. Package only 500 mW

Lead Temperature (T

L

)

(Soldering 10 seconds) 260°C

Min Max Units

Supply Voltage (V

CC

)26V

DC Input or Output Voltage 0 V

CC

V

(V

IN,VOUT

)

Operating Temperature Range (T

A

) −40 +85 °C

Input Rise or Fall Times

(t

r

, tf) V

CC

= 2.0V 1000 ns

V

CC

= 4.5V 500 ns

V

CC

= 6.0V 400 ns

Symbol Parameter Conditions

V

CC

TA = 25°CTA = −40 to 85°CTA = −55 to 125°C

Units

Typ Guaranteed Limits

V

IH

Minimum HIGH Level Input 2.0V 1.5 1.5 1.5 V

Voltage 4.5V 3.15 3.15 3.15 V

6.0V 4.2 4.2 4.2 V

V

IL

Maximum LOW Level Input 2.0V 0.5 0.5 0.5 V

Voltage 4.5V 1.35 1.35 1.35 V

6.0V 1.8 1.8 1.8 V

V

OH

Minimum HIGH Level Output V

IN

= VIH or V

IL

Voltage |I

OUT

| ≤ 20 µA 2.0V 2.0 1.9 1.9 1.9 V

4.5V 4.5 4.4 4.4 4.4 V

6.0V 6.0 5.9 5.9 5.9 V

V

IN

= VIH or V

IL

|I

OUT

| ≤ 6.0 mA 4.5V 4.2 3.98 3.84 3.7 V

|I

OUT

| ≤ 7.8 mA 6.0V 5.7 5.48 5.34 5.2 V

V

OL

Maximum LOW Level Output V

IN

= VIH or V

IL

Voltage |I

OUT

| ≤ 20 µA 2.0V 0 0.1 0.1 0.1 V

4.5V 0 0.1 0.1 0.1 V

6.0V 0 0.1 0.1 0.1 V

V

IN

= VIH or V

IL

|I

OUT

| ≤ 6.0 mA 4.5V 0.2 0.26 0.33 0.4 V

|I

OUT

| ≤ 7.8 mA 6.0V 0.2 0.26 0.33 0.4 V

I

IN

Maximum Input Current V

IN

= VCC or GND 6.0V ±0.1 ±1.0 ±1.0 µA

I

OZ

Maximum 3-STATE V

OUT

= VCC or GND

Output Leakage Current OC = V

IH

6.0V ±0.5 ±5.0 ±10 µA

I

CC

Maximum Quiescent Supply V

IN

= VCC or GND

Current I

OUT

= 0 µA6.0V 8.080 160µA

∆I

CC

Quiescent Supply Current VCC = 5.5V OE 1.0 1.5 1.8 2.0 mA

per Input Pin VIN = 2.4V CLK 0.6 0.8 1.0 1.1 mA

or 0.4V (Note 4) DATA 0.4 0.5 0.6 0.7 mA

3 www.fairchildsemi.com

MM74HC574

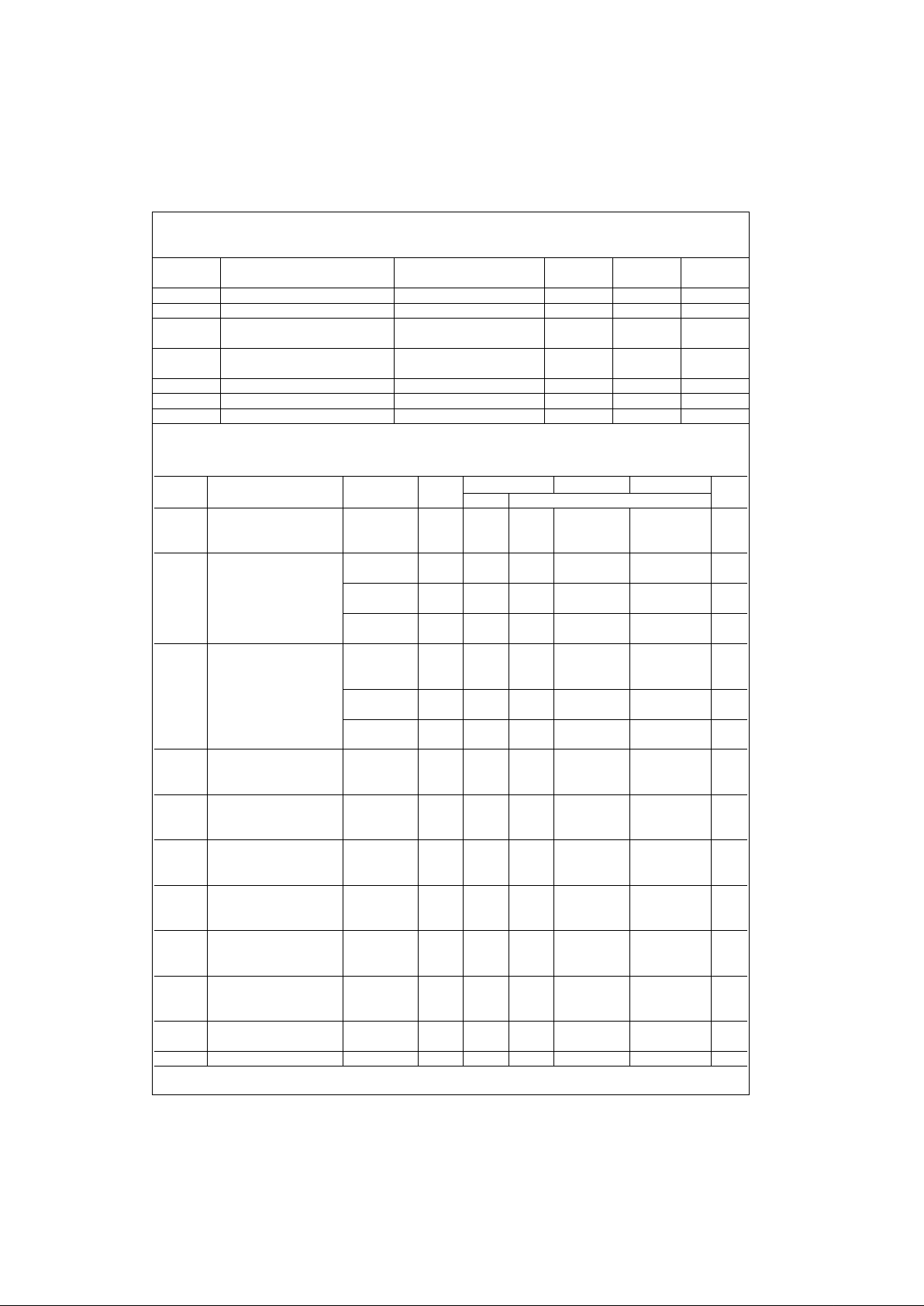

AC Electrical Characteristics

V

CC

= 5V, T

A

= 25°C, t

r

= t

f

= 6 ns

AC Electrical Characteristics

V

CC

= 2.0 − 6.0V, CL = 50 pF, tr = t

f

= 6 ns (unless otherwise specified)

Symbol Parameter Conditions Typ

Guaranteed

Units

Limit

f

MAX

Maximum Operating Frequency 60 33 MHz

t

PHL

, t

PLH

Maximum Propagation Delay, Clock to Q CL = 45 pF 17 27 ns

t

PZH

, t

PZL

Maximum Output Enable Time RL = 1 kΩ 19 28 ns

CL = 45 pF

t

PHZ

, t

PLZ

Maximum Output Disable Time RL = 1 kΩ 14 25 ns

CL = 5 pF

t

S

Minimum Setup Time, Data to Clock 10 12 ns

t

H

Minimum Hold Time, Clock to Data −35ns

t

W

Minimum Pulse Clock Width 8 15 ns

Symbol Parameter Conditions

V

CC

TA = 25°CTA = −40 to 85°CTA = −55 to 125°C

Units

Typ Guaranteed Limits

f

MAX

Maximum Operating Frequency CL = 50 pF 2.0V 33 28 23 MHz

4.5V 30 24 20 MHz

6.0V 35 28 23 MHz

t

PHL

, t

PLH

Maximum Propagation CL = 50 pF 2.0V 18 30 38 45 ns

Delay, Clock to Q CL = 150 pF 2.0V 51 155 194 233 ns

CL = 50 pF 4.5V 13 23 29 35 ns

CL = 150 pF 4.5V 19 31 47 47 ns

CL = 50 pF 6.0V 12 20 25 30 ns

CL = 150 pF 6.0V 18 27 34 41 ns

t

PZH

, t

PZL

Maximum Output Enable RL = 1 kΩ

Time CL = 50 pF 2.0V 22 30 38 45 ns

CL = 150 pF 2.0V 59 180 225 270 ns

CL = 50 pF 4.5V 14 28 35 42 ns

CL = 150 pF 4.5V 20 36 45 54 ns

CL = 50 pF 6.0V 12 24 30 36 ns

CL = 150 pF 6.0V 18 31 39 47 ns

t

PHZ

, t

PLZ

Maximum Output Disable Time RL = 1 kΩ 2.0V 15 30 38 45 ns

CL = 50 pF 4.5V 12 25 31 38 ns

6.0V 10 21 27 32 ns

t

S

Minimum Setup Time 2.0V 6 12 15 18 ns

Data to Clock 4.5V 20 25 30 ns

6.0V 17 21 25 ns

t

H

Minimum Hold Time 2.0V −15 6 8 ns

Clock to Data 4.5V 0 0 0 ns

6.0V 0 0 0 ns

t

THL

, t

TLH

Maximum Output Rise CL = 50 pF 2.0V 6 12 15 18 ns

and Fall Time 4.5V 7 12 15 18 ns

6.0V 6 10 13 15 ns

t

W

Minimum Clock Pulse Width 2.0V 30 15 20 24 ns

4.5V 9 16 20 24 ns

6.0V 8 14 18 20 ns

tr,t

f

Maximum Clock Input Rise 2.0V 1000 1000 1000 ns

and Fall Time 4.5V 500 500 500 ns

6.0V 400 400 400 ns

C

PD

Power Dissipation Capacitance OC = VCC 5 pF

(Note 5) (per latch) OC = GND 58 pF

C

IN

Maximum Input Capacitance 5 10 10 10 pF

Loading...

Loading...