Fairchild Semiconductor DM74LS90N, DM74LS90MX, DM74LS90M, DM74LS90CW Datasheet

© 2000 Fairchild Semiconductor Corporation DS006381 www.fairchildsemi.com

August 1986

Revised March 2000

DM74LS90 Decade and Binary Counters

DM74LS90

Decade and Binary Counters

General Description

Each of these monolithic counters contains four masterslave flip-flops and additio nal ga ting to pr ovid e a di vid e-b ytwo counter and a three-stage binary counter for which the

count cycle length is divide-by-five for the DM74LS90.

All of these counters have a gated zero reset and the

DM74LS90 also has gated set-to-nine inputs for use in

BCD nine’s complement applications.

To use their maximum count length (decade or four bit

binary), the B input is connected to the Q

A

output. The

input count pulses are applied to input A and the outputs

are as described in the appropriate truth table. A symmetrical divide-by-ten count can be obtained from the

DM74LS90 counters by conne cting the Q

D

output to the A

input and applying the input count to the B input which

gives a divide-by-ten square wave at output Q

A

.

Features

■ Typical power dissipation 45 mW

■ Count frequency 42 MHz

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering code.

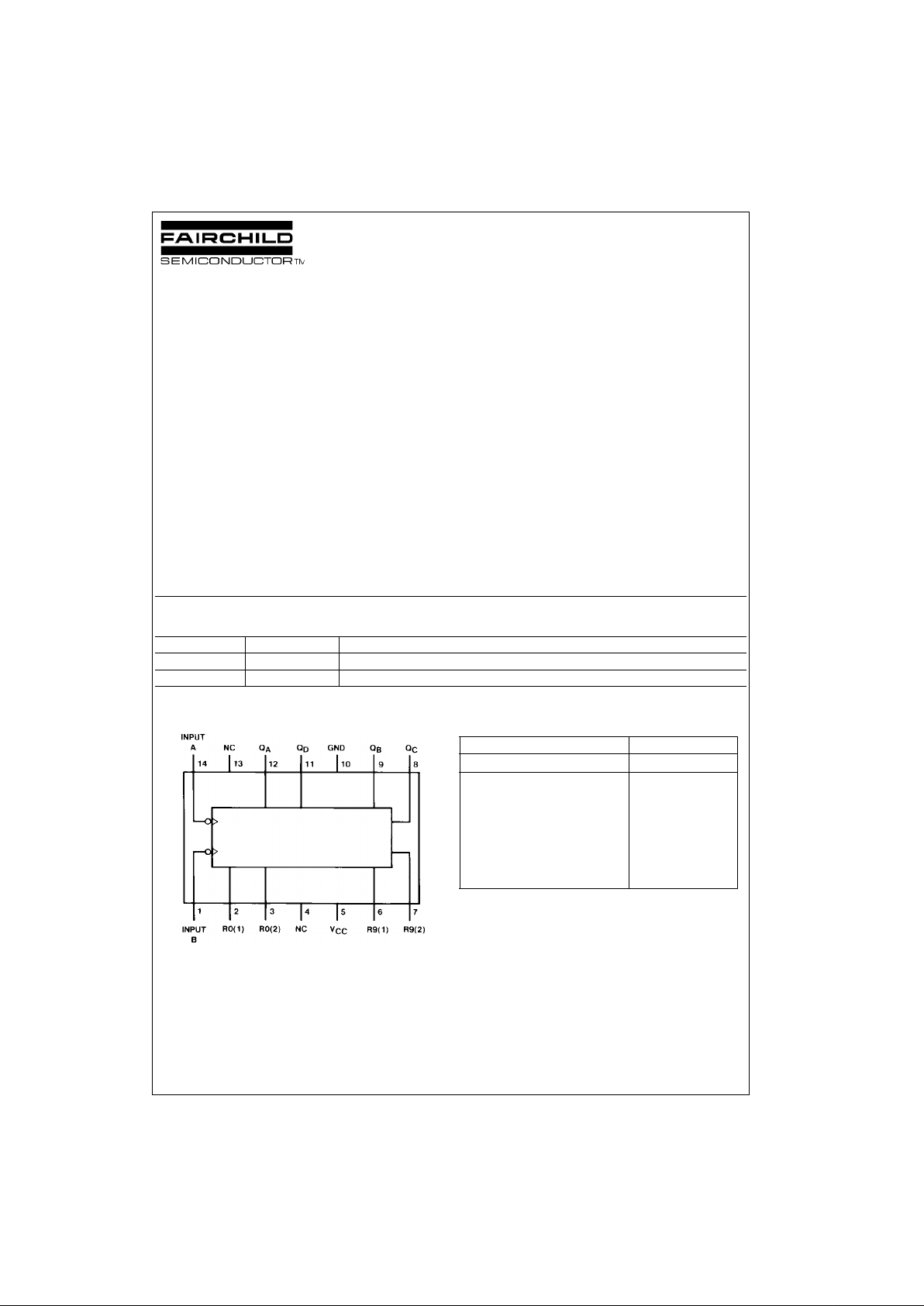

Connection Diagram Reset/Count Truth Table

Order Number Package Number Package Description

DM74LS90M M14A 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow

DM74LS90N N14A 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Reset Inputs Output

R0(1) R0(2) R9(1) R9(2) Q

DQCQBQA

H H L X LLLL

H H X L LLLL

XXHHHLLH

X L X L COUNT

L X L X COUNT

L X X L COUNT

X L L X COUNT

www.fairchildsemi.com 2

DM74LS90

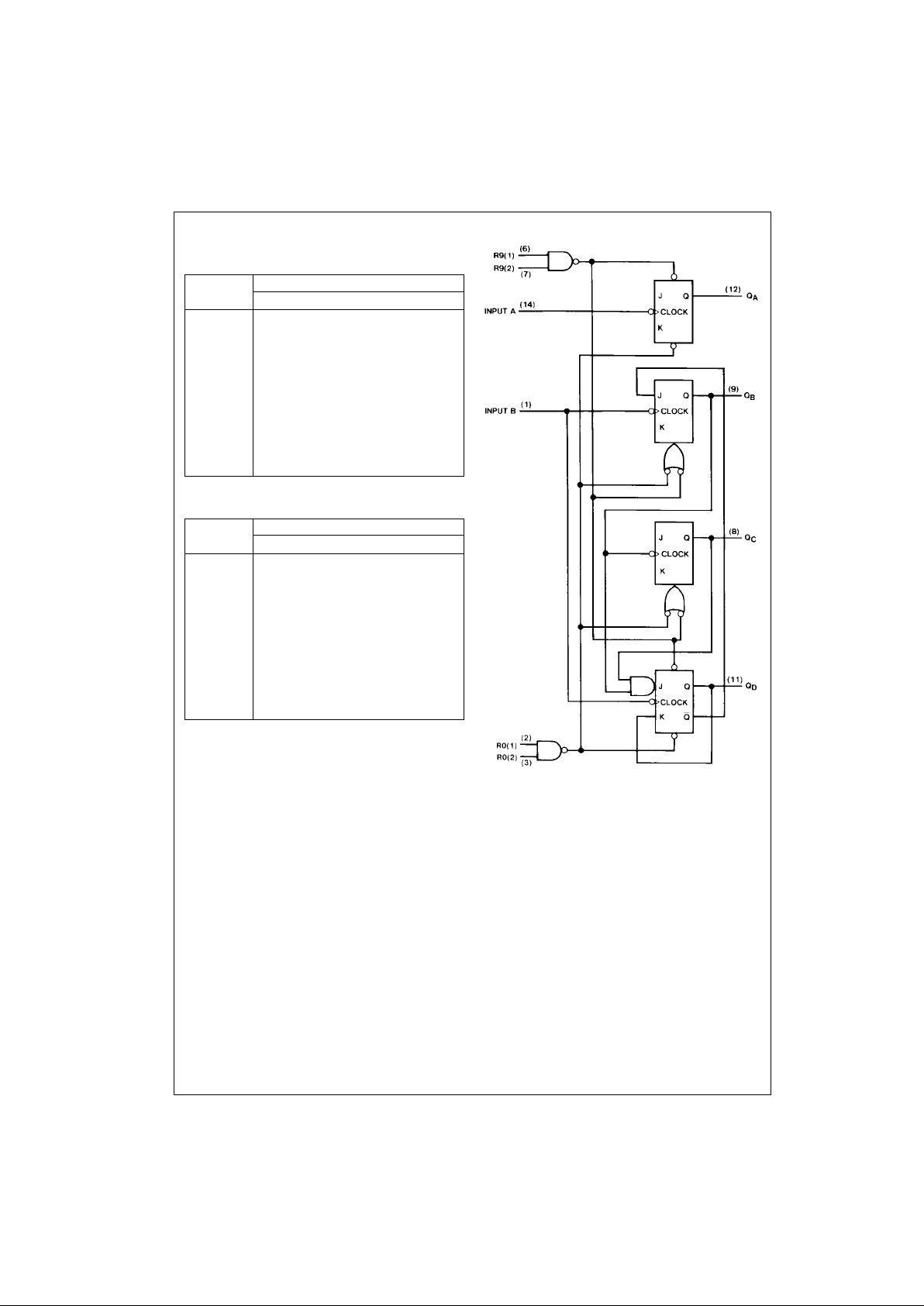

Function Tables

BCD Count Sequence (Note 1)

Bi-Quinary (5-2) (Note 2)

H = HIGH Level

L = LOW Level

X = Don’t Care

Note 1: Output Q

A

is connected to input B for BCD count.

Note 2: Output Q

D

is connected to input A for bi-quinary count.

Note 3: Output Q

A

is connected to input B.

Logic Diagram

The J and K inputs sho wn without connec tion are for refere nce only and

are functionally at a high level.

Count Output

Q

D

Q

C

Q

B

Q

A

0 LLLL

1LLLH

2LLHL

3LLHH

4LHLL

5LHLH

6LHHL

7 LHHH

8 HLLL

9HLLH

Count Output

Q

A

Q

D

Q

C

Q

B

0 LLLL

1LLLH

2LLHL

3LLHH

4LHLL

5 HLLL

6HLLH

7HLHL

8HLHH

9HHLL

Loading...

Loading...