Fairchild Semiconductor DM74LS574WMX, DM74LS574WM, DM74LS574N Datasheet

© 2000 Fairchild Semiconductor Corporation DS009815 www.fairchildsemi.com

March 1988

Revised March 2000

DM74LS574 Octal D-Type Flip-Flop with 3-STATE Outputs

DM74LS574

Octal D-Type Flip-Flop with 3-STATE Outputs

General Description

The DM74LS574 is a high spee d low power o ctal flip-flop

with a buffered common Cl ock (CP) and a buffered common Output Enable (OE

). The information presented to the

D inputs is stored in the flip-flops on the LOW-to-HIGH

Clock (CP) transition.

This device is functionally identical to the DM74LS374

except for the pinouts.

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering code.

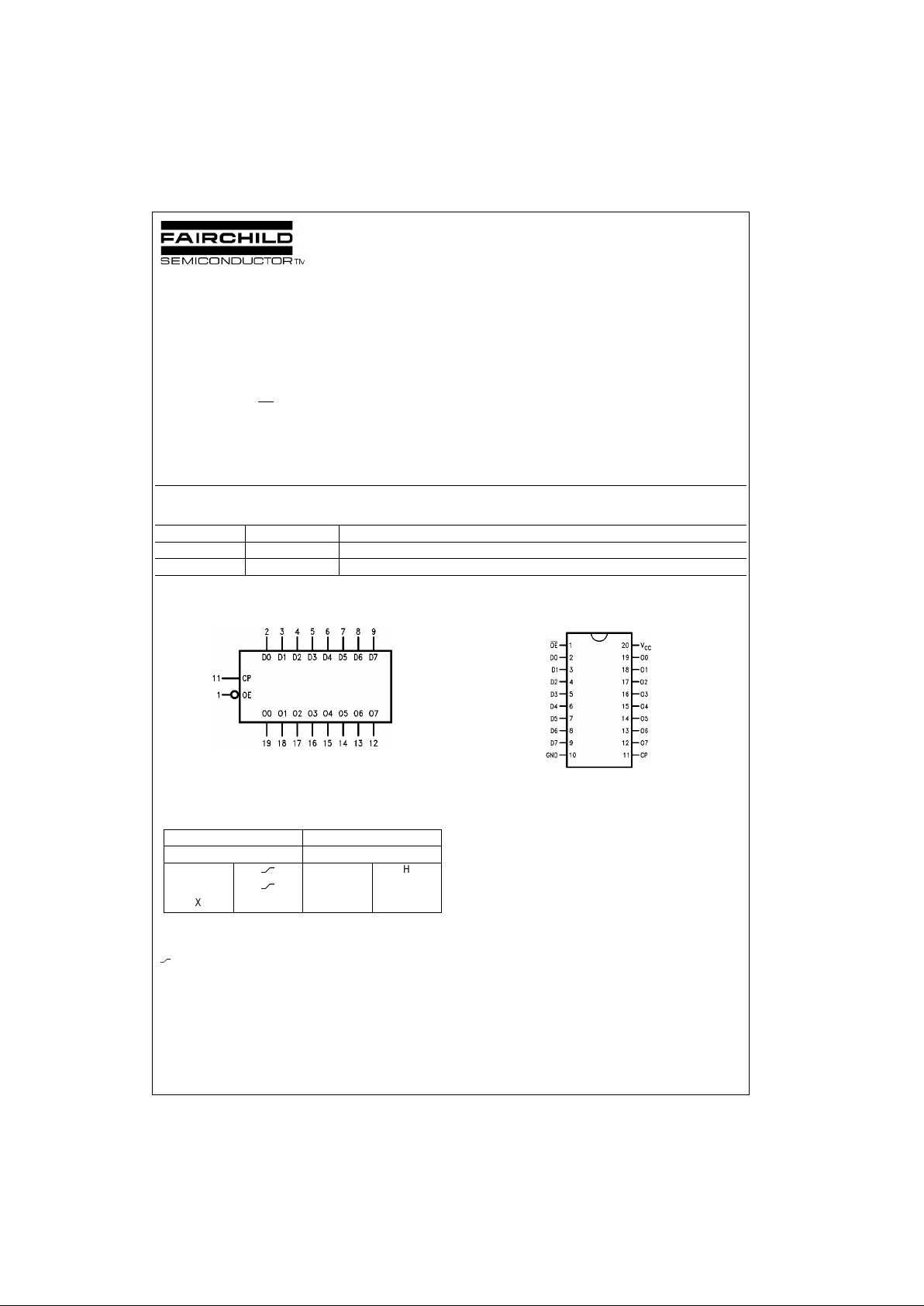

Logic Symbol

VCC = Pin 20

GND = Pin 10

Connection Diagram

Truth Table

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

Z = High Impedance

= HIGH-to-LOW Clock (CP) transition

Order Number Package Number Package Description

DM74LS574WM M20B 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide

DM74LS574N N20A 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Inputs Outputs

Dn CP OE On

H

LH

L

LL

XXHZ

www.fairchildsemi.com 2

DM74LS574

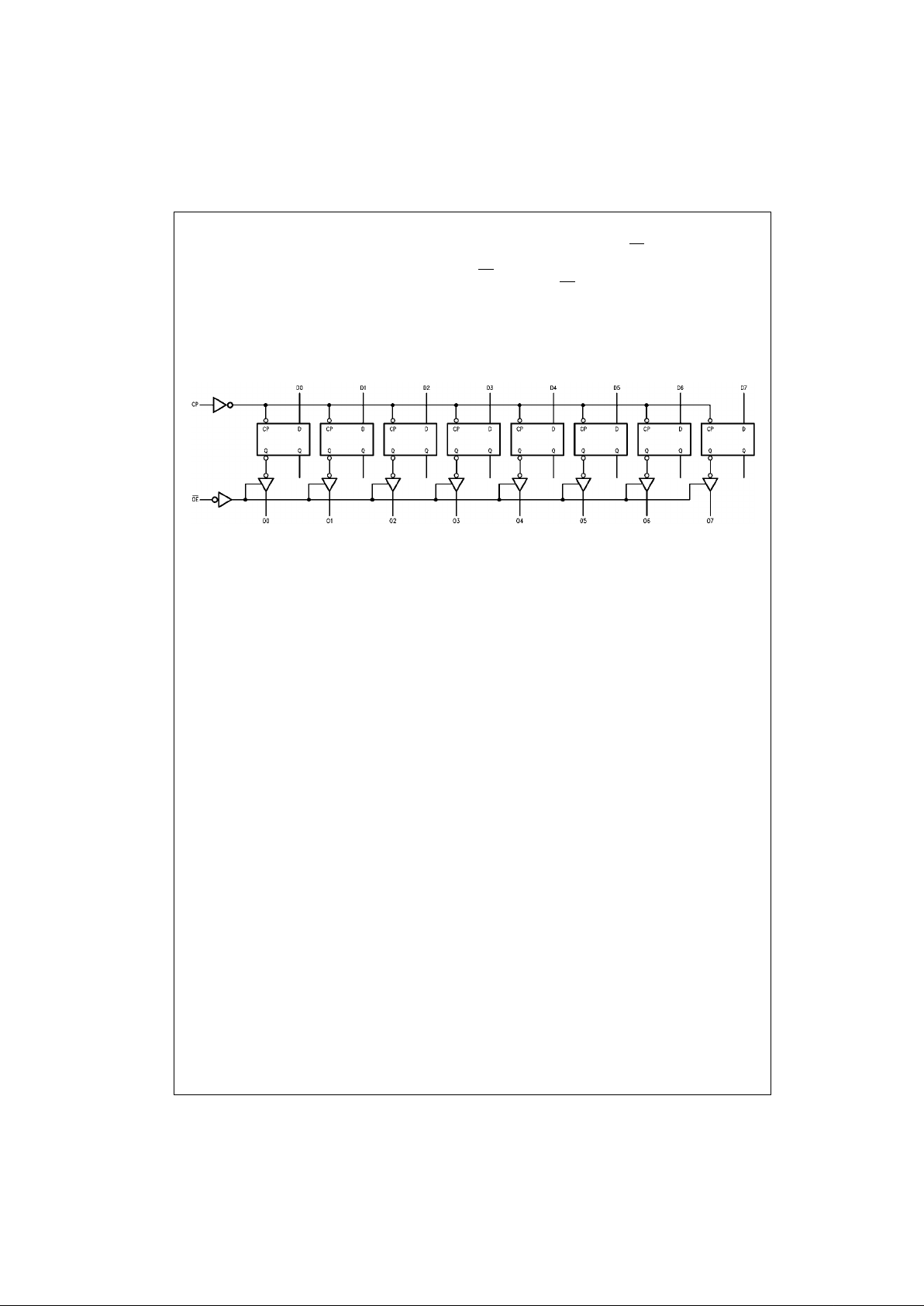

Functional Description

The DM74LS574 consists of ei ght edge-tri ggered flip-flops

with individual D-type inputs and 3-STATE true outputs.

The buffered clock an d buffered Outputs Enable are common to all flip-flops. The eight flip-flops will store the sta te

of their individual D inp uts that meet the setup and hold

times requirement s on the LOW-to-H IGH Clock ( CP) tran-

sition. With the Output Enable (OE

) LOW, the contents of

the eight flip-flops are available at the outpu ts. When the

OE

is HIGH, the outputs go to the high impedance state.

Operation of the O E

input does not affect the state of the

flip-flops.

Logic Diagram

Loading...

Loading...