Fairchild Semiconductor DM74LS47N, DM74LS47MX, DM74LS47M Datasheet

© 2000 Fairchild Semiconductor Corporation DS009817 www.fairchildsemi.com

October 1988

Revised March 2000

DM74LS47 BCD to 7-Segment Decoder/Driver with Open-Collector Outputs

DM74LS47

BCD to 7-Segment Decoder/Driver with

Open-Collector Outputs

General Description

The DM74LS47 accepts four lines of BCD (8421) input

data, generates their com plements interna lly and decodes

the data with seven AND/OR gates havin g open-collector

outputs to drive indica tor segm ents dir ectly. Each segment

output is guaranteed to sink 24 mA in the ON (LOW) state

and withstand 15V in the OFF (H IGH) state with a maximum leakage current of 250 µA. Auxiliary in puts provided

blanking, lamp test and cascadable zero-suppression functions.

Features

■ Open-collector outputs

■ Drive indicator segments directly

■ Cascadable zero-suppression capability

■ Lamp test input

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering code.

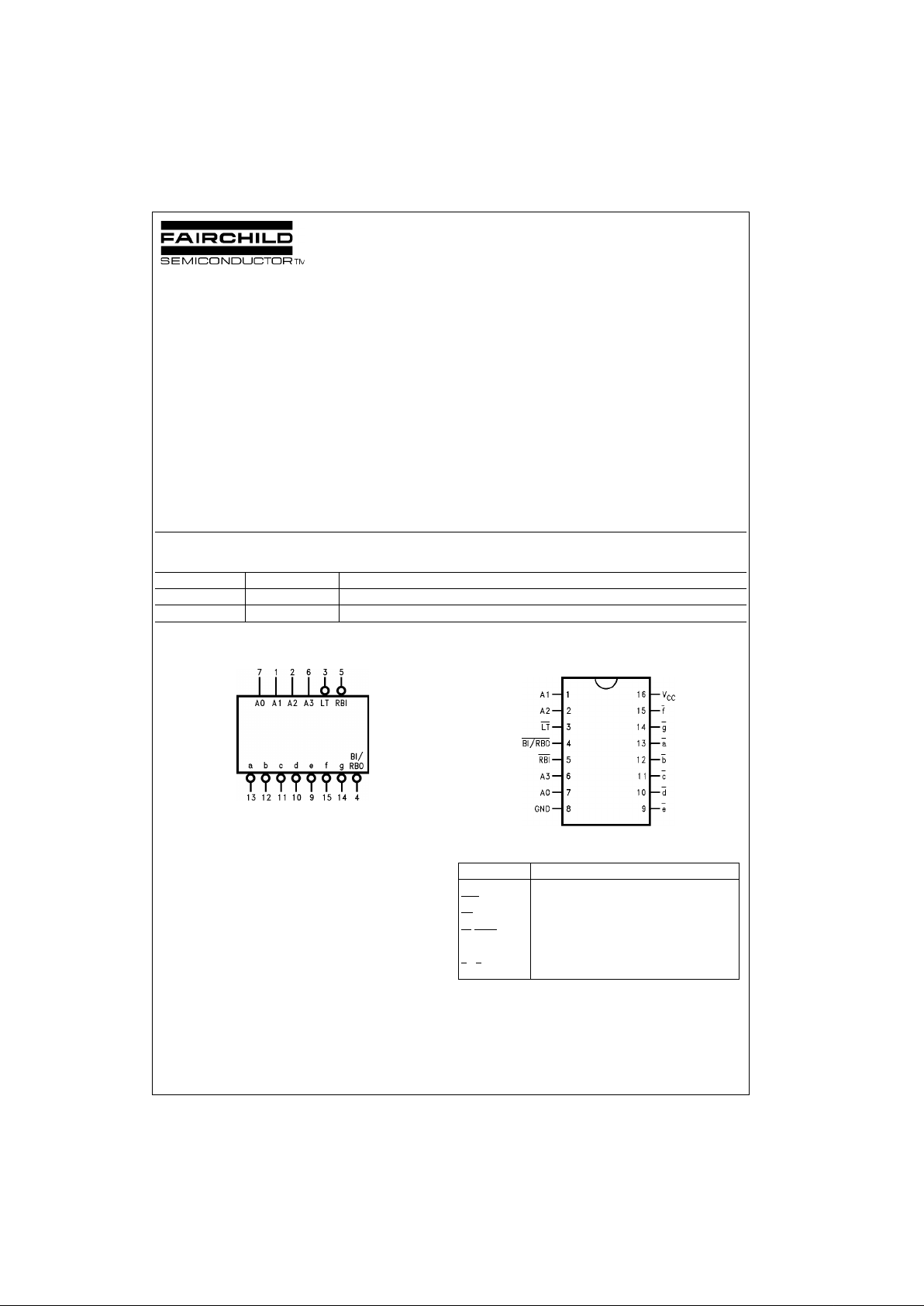

Logic Symbol

VCC = Pin 16

GND = Pin 8

Connection Diagram

Pin Descriptions

Note 1: OC—Open Collector

Order Number Package Number Package Description

DM74LS47M M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

DM74LS47N N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Pin Names Description

A0–A3 BCD Inputs

RBI

Ripple Blanking Input (Active LOW)

LT

Lamp Test Input (Active LOW)

BI

/RBO Blanking Input (Active LOW) or

Ripple Blanking Output (Active LOW)

a

–g Segment Outputs (Active LOW) (Note 1)

www.fairchildsemi.com 2

DM74LS47

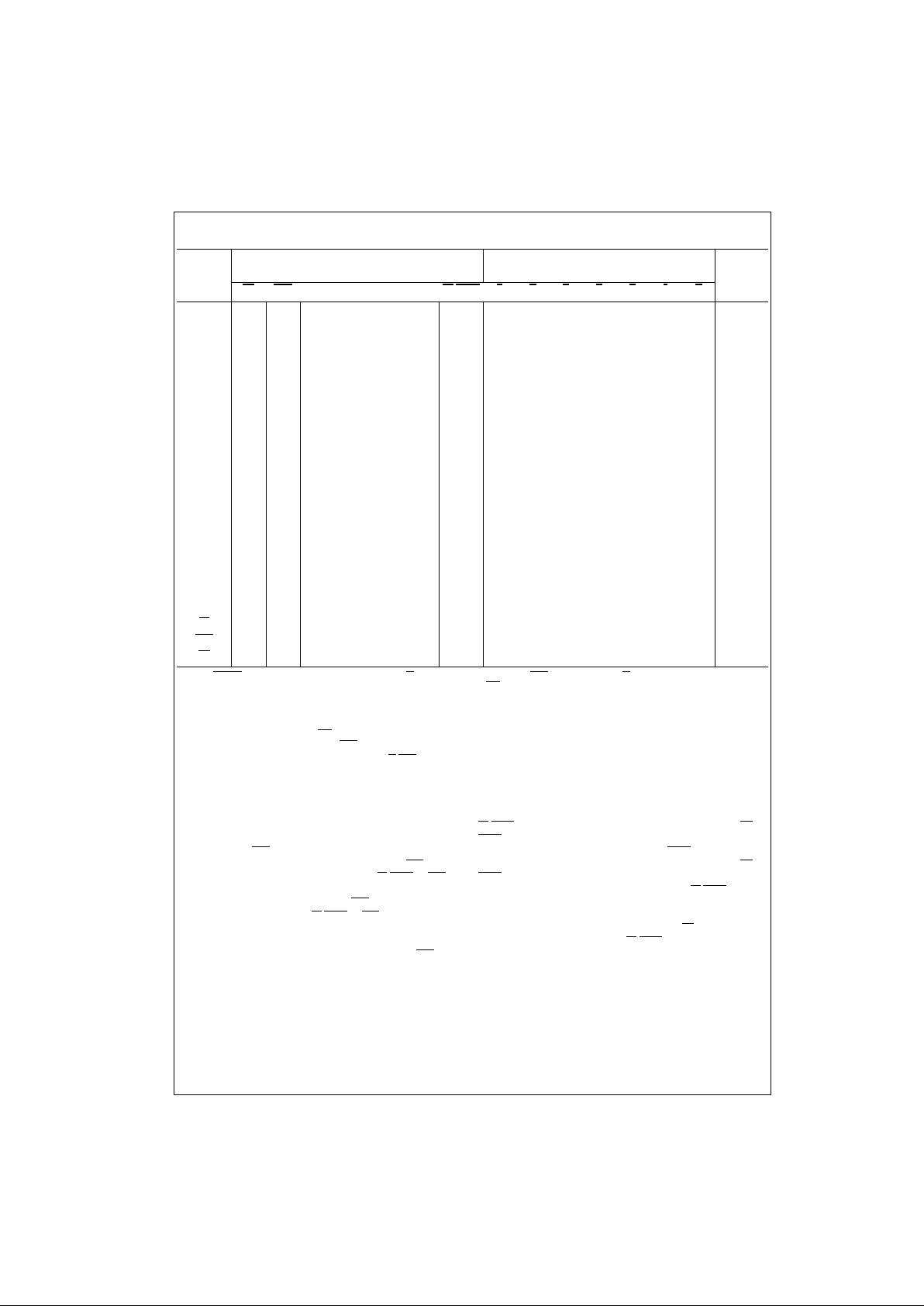

Truth Table

Note 2: BI/RBO is wire-AN D logic serving as blanking input (B I) and/or ripple-bla nk ing output (RBO). The blanking out (BI) must be open or held at a HIGH

level when output fun ctions 0 through 15 ar e desired, and ripple-bl anking input (RBI

) must be open or at a HIGH lev el if blanking or a decima l 0 is not

desired. X = input may be HIGH or LOW.

Note 3: When a LOW level is applied to the blanking input (forced condition) all segment outputs go to a HIGH level regardless of the state of any other input

condition.

Note 4: When ripple-b lanking input (RB I

) and inputs A0, A1, A2 a nd A3 are LOW le vel, w ith th e l amp test inpu t a t H IGH leve l, a ll se gme nt o utpu ts go t o a

HIGH level and the ripple-blanking output (RBO

) goes to a LOW level (re sp onse condition).

Note 5: When the blanking input/ripple-blanking output (BI

/RBO) is OPEN or hel d at a HIG H lev el, and a LOW level is applied to lamp test input , all seg m ent

outputs go to a LOW level.

Functional Description

The DM74LS47 decodes the input data in the pattern indicated in the Truth Table and the segment identification

illustration. If the input data is decimal zero, a LOW signal

applied to the RBI

blanks the display and causes a multi-

digit display. For example, by grounding the RBI

of the

highest order decoder and connecting its BI

/RBO to RBI of

the next lowest order decoder, etc., leading zeros will be

suppressed. Similarly, by grounding RBI

of the lowest order

decoder and connecting its BI

/RBO to RBI of the next highest order decoder, etc., trailing zeros will be suppressed.

Leading and trailing zeros can be suppressed simultaneously by using external gates, i.e.: by driving RBI

of a

intermediate decoder fro m an OR gate whose inputs are

BI

/RBO of the next highest and lowest order decoders. BI/

RBO also serves as an unconditio nal blanking input. The

internal NAND gate that gen erates the RBO

signal has a

resistive pull-up, as oppose d to a totem pole, and thu s BI/

RBO can be forced LOW by exte rnal means, usin g wiredcollector logic. A LOW signal thus app lied to BI

/RBO turns

off all segment outputs. This b lanking f eature can be used

to control display inten sity by vary ing the d uty cycle of the

blanking signal. A LOW signal applied to LT

turns on all

segment outputs, provided that BI

/RBO is not forced LOW.

Decimal

Inputs Outputs

or Note

Function

LT

RBI A3 A2 A1 A0 BI/RBO a b c d e f g

0 HHLLLL H LLLLLLH(Note 2)

1 H X L L L H H H L L H H H H (Note 2)

2HXLLHLHLLHLLHL

3 HXLLHHHLLLLHHL

4HXLHLLHHLLHHLL

5 HXLHLHHLHLLHLL

6 HXLHHL H HHLLLLL

7 HXLHHHHLLLHHHH

8 HXHL LL H LLLLLLL

9 HXHL LH H LLLHHLL

10 H X H L H L H H H H L L H L

11 HXH LHH H HHLLHHL

12 H X H H L L H H L H H H L L

13 HXHHLHHLHHLHLL

14 HXHHHL H HHHLLLL

15 H XH HH H H HHHHHHH

BI

XXXXXX L HHHHHHH(Note 3)

RBI

H L L L L L L HHHHHHH(Note 4)

LT

LXXXXX H LLLLLLL(Note 5)

Loading...

Loading...