Fairchild Semiconductor DM74AS646WM, DM74AS646NT, DM74AS646WMX Datasheet

© 2000 Fairchild Semiconductor Corporation DS006324 www.fairchildsemi.com

October 1986

Revised March 2000

DM74AS646 • DM74AS648 Octal Bus Transceiver and Register

DM74AS646 • DM74AS648

Octal Bus Transceiver and Register

General Description

This device incorpor ates an octal bus transceiver and an

octal D-type register configured to enable multiplexed

transmission of data from bus to bus or internal reg ister to

bus.

This bus transceiver features totem-p ole 3-STATE outputs

designed specifically fo r driving highly-capacitive or relatively low-impedance loads. The high-impedance third

state and increased high-logic-level drive provide this

device with the capability of being connected directly to and

driving the bus lines in a bus-organized system without

need for interface or pull-up comp onents. It is pa rticularly

attractive for imple menting buffer registers, I/O ports, bidirectional bus drivers, and working registers.

The registers in the DM74AS646, D M74AS648 are e dgetriggered D-type flip-flops. On the positive transition of the

clock (CAB or CBA), the input bus data is stored.

The SAB and SBA control pins are provided to select

whether real-time data or stored data is transferred. A LOW

input level selects real-time data, and a HIGH level selects

stored data. The select controls have a “make before

break” configuration to eliminate a glitch which wo uld normally occur in a typical multiplexer during the transition

between stored and real-time data.

The enable G

and direction control pins provide four modes

of operation; real-tim e data trans fer from bus A to B, realtime data transfer from bus B to A, real-time bus A and/or B

data transfer to internal storage, or internal store data

transfer to bus A or B.

When the enable G

pin is LOW, the direction pin selects

which bus receives da ta. When th e enable G

pin is HIGH,

both buses become disabled yet their input function is still

enabled.

Features

■ Switching specifications at 50 pF

■ Switching specifications guaranteed over full tempera-

ture and V

CC

range

■ Advanced oxide-isolated, ion-implanted Schottky TTL

process

■ Functionally and pin-for-pin compatible with LS TTL

counterpart

■ 3-STATE buffer-type outputs drive bus lines directly

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering code.

Order Number Package Number Package Description

DM74AS646WM M24B 24-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide

DM74AS646NT N24C 24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-100, 0.300 Wide

DM74AS648WM M24B 24-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide

DM74AS648NT N24C 24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-100, 0.300 Wide

www.fairchildsemi.com 2

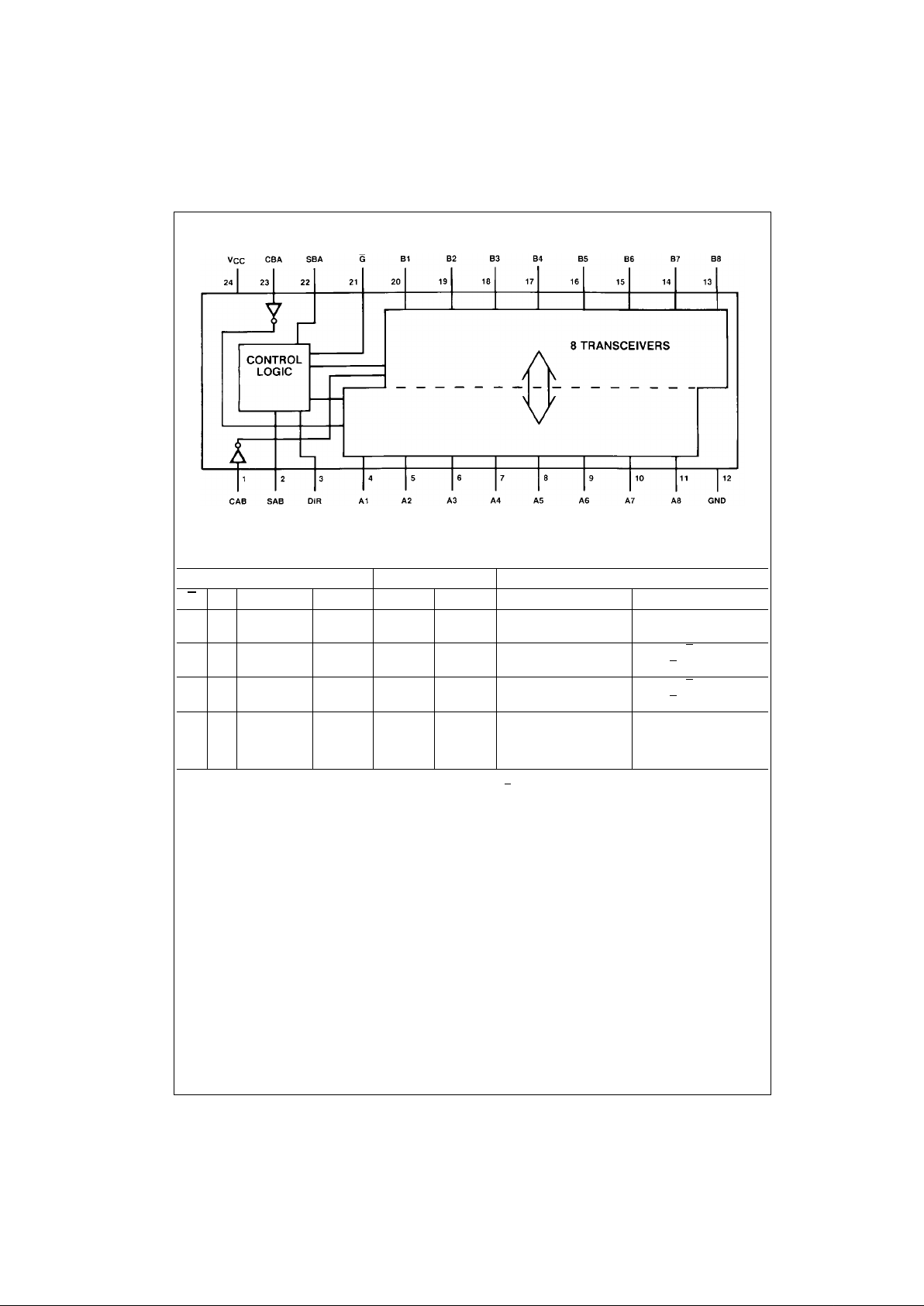

DM74AS646 • DM74AS648

Connection Diagram

Function Table

H—HIGH level; L—LOW level; X—irrelevant; ↑—LOW-to-HIGH level tran s it ion

Note 1: The data output functions may be enabled or disabled by various signals at the G

and DIR inputs. Data input functions are always enabled,

i.e., data at the bus pins will be stored on eve ry LOW -t o-HIGH transition on th e c lock inputs.

Inputs Data I/O (Note 1) Operation or Function

G

DIR CAB CBA SAB SBA A1 thru A8 B1 thru B8 DM74AS646 DM74AS648

H X H or L H or L X X Input Input Isolation, Hold Storage Isolation, Hold Storage

X ↑↑X X Store A and B Data Store A and B Data

L L X X X L Output Input Real Time B Data to A Bus Real Time B

Data to A Bus

L X H or L X H Stored B Data to A Bus Stored B

Data to A Bus

L H X X L X Input Output Real Time A Data to B Bus Real Time A

Data to B Bus

H H or L X H X Stored A Data to B Bus Stored A

Data to B Bus

XX ↑ X X X Input

Unspecified

(Note 1)

Store A, B Unspecified

(Note 1)

Store A, B Unspecified

(Note 1)

XX X ↑ XX

Unspecified

(Note 1)

Input

Store B, A Unspecified

(Note 1)

Store B, A Unspecified

(Note 1)

3 www.fairchildsemi.com

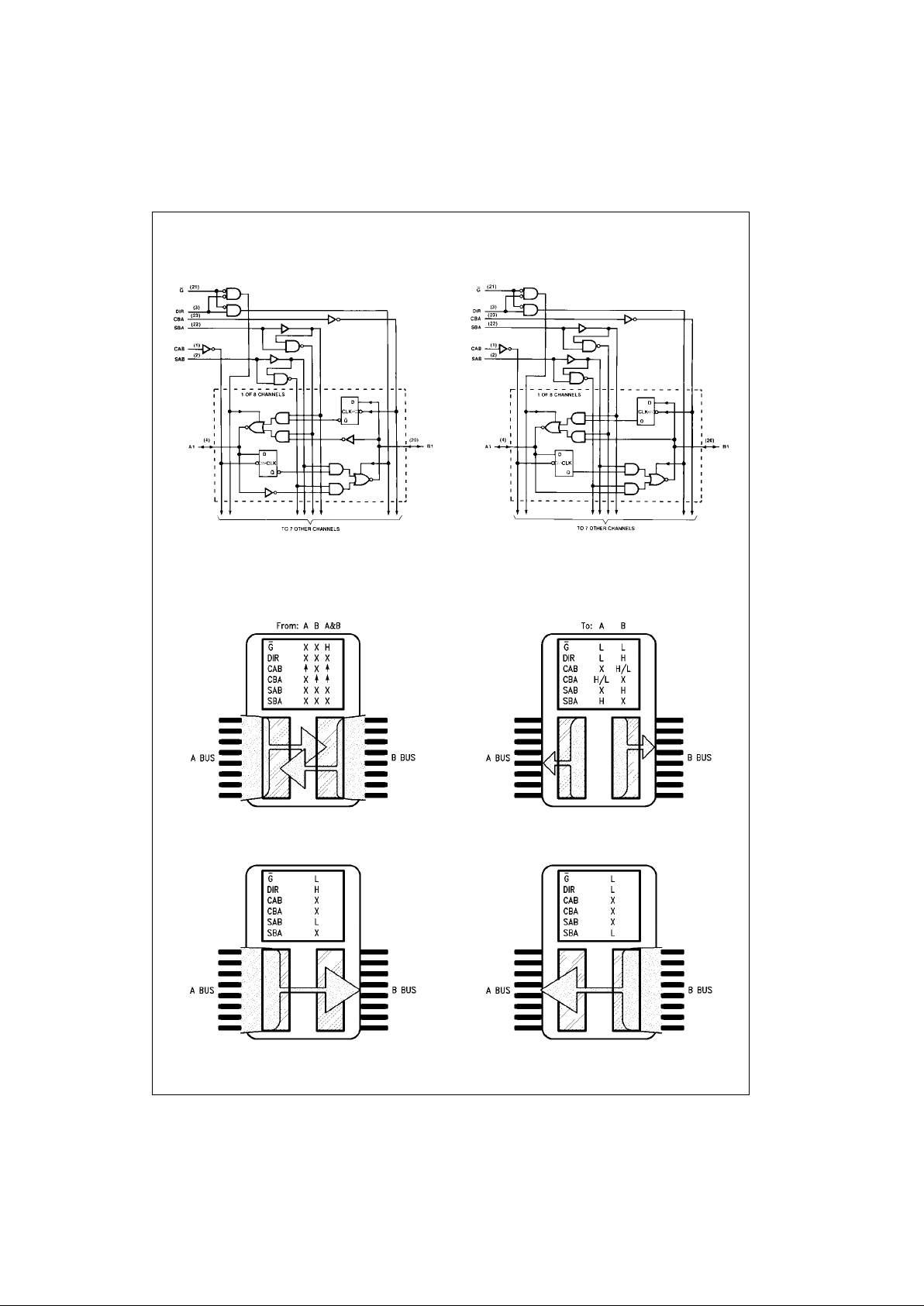

DM74AS646 • DM74AS648

Logic Diagrams

(positive logic)

DM74AS646 DM74AS648

Different Modes of Control for DM74AS646, DM74AS648

Storage From A, B or A and B Transfer Stored Data to A or B

(Note 2)

Real-Time Transfer Bus A to Bus B

(Note 2)

Real-Time Transfer Bus B to Bus A

(Note 2)

Note 2: The complement of A and B data are stored and transferred for DM74AS648

Loading...

Loading...