Fairchild Semiconductor DM74AS640WMX, DM74AS640WM, DM74AS640N Datasheet

© 2000 Fairchild Semiconductor Corporation DS006708 www.fairchildsemi.com

October 1986

Revised March 2000

DM74AS640 3-STATE Octal Bus Transceiver

DM74AS640

3-STATE Octal Bus Transceiver

General Description

This advanced Schottky device contains 8 pairs of 3STATE logic elements confi gured as octa l bus transce iver.

This circuit is designed for us e in memory, microprocessor

systems and in asynchronous bidirectional data buses.

This device transmits data from the A bus to the B b us, or

vice versa, depending upon the l ogic level of th e direction

control input (DIR). T he enable input (G

) can be used to

disable the devices, effecting isolation of buses A and B.

The 3-STATE circuitry also contains a prote ction feature

that prevents these transceivers from glitching the bus during power-up or power-down.

Features

■ Switching specifications at 50 pF

■ Switching specifications guaranteed over full tempera-

ture and V

CC

range

■ Advanced oxide-isolated, ion-implanted Schottky TTL

process

■ Functionally and pin for pin compatible with Schottky,

low power Schottky, and advanced low power Schottky

TTL counterpart

■ Improved AC performance over Schottky, low power

Schottky, and advanced low power Schottky counterparts

■ 3-STATE outputs independent ly controlled on A and B

buses

■ Low output impedance driv e to drive terminated transmission lines to 133Ω

■ Specified to interface with CMOS at V

OH

= VCC − 2V

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering code.

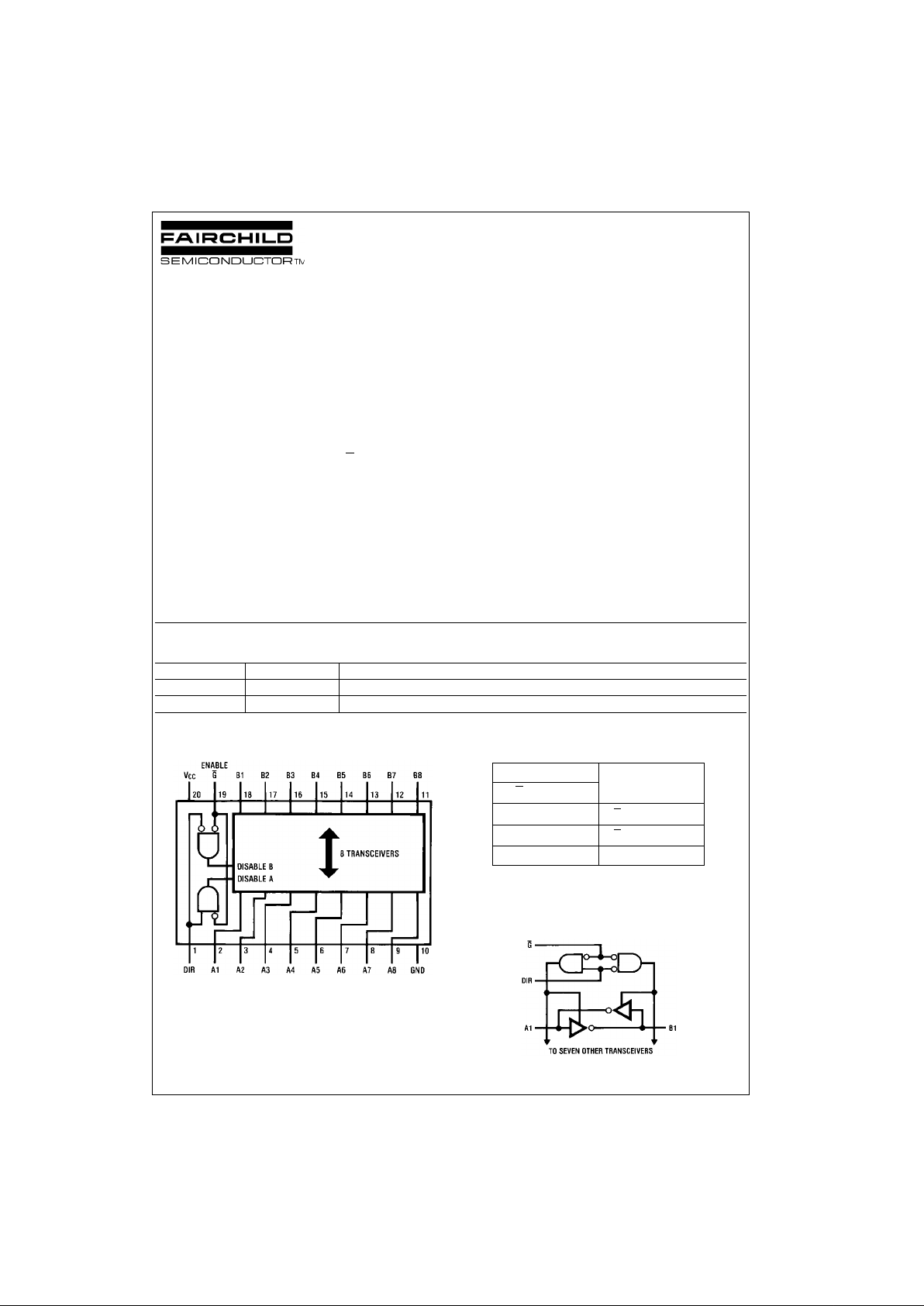

Connection Diagram

Top View

Function Table

H = HIGH Logic Level

L = LOW Logic Level

X = Immaterial

Logic Diagram

Order Number Package Number Package Description

DM74AS640WM M20B 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide

DM74AS640N N20A 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Control Inputs

Operation

G

DIR

LLB

Data to A Bus

LHA

Data to B Bus

HX Isolation

www.fairchildsemi.com 2

DM74AS640

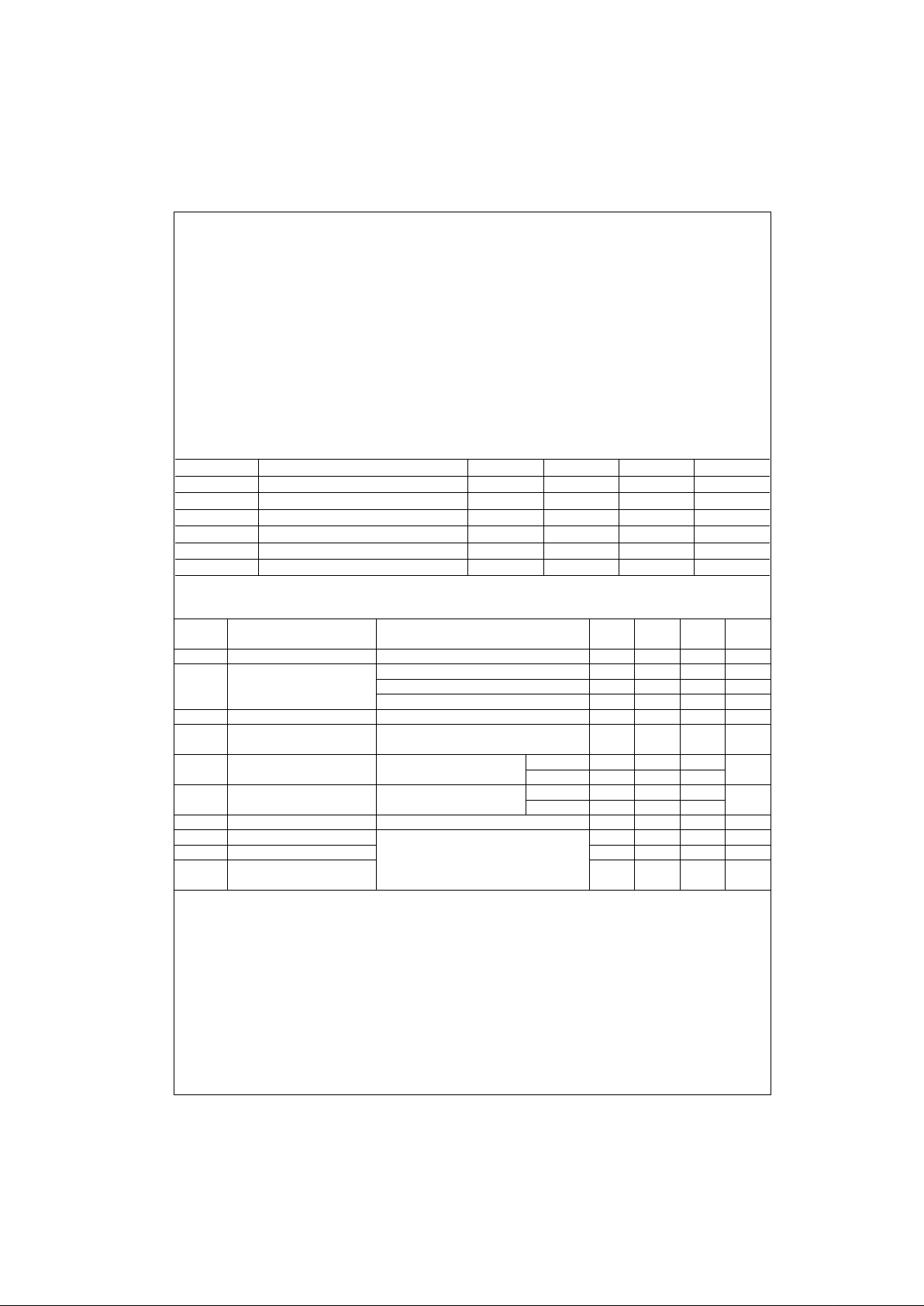

Absolute Maximum Ratings(Note 1)

Note 1: The “Absolute Maximum Ratings” are those values beyond which

the safety of the dev ice cannot be guaranteed. T he device sh ould not be

operated at these limits. The parametric values defined in the Electrical

Characteristics tables are not guaranteed at the absolute maximum ratings.

The “Recommend ed O peratin g Cond itions” t able w ill defin e the co ndition s

for actual device operation.

Recommended Operating Conditions

Electrical Characteristics

over recommended operating free air temperature range (unless otherwise noted)

Note 2: All typicals are at VCC = 5.0V, TA = 25°C.

Note 3: For I/O ports, the parameters I

IH

and IIL include the OFF-Stat e output current, I

OZH

and I

OZL

.

Supply Voltage 7V

Input Voltage

Control Inputs 7V

I/O Ports 5.5V

Operating Free Air Temperature Range 0°C to +70°C

Storage Temperature Range −65°C to +150°C

Typical θ

JA

N Package 51.5°C

M Package 69.0°C

Symbol Parameter Min Typ Max Units

V

CC

Supply Voltage 4.5 5 5.5 V

V

IH

HIGH Level Input Voltage 2 V

V

IL

LOW Level Input Voltage 0.8 V

I

OH

HIGH Level Output Current −15 mA

I

OL

LOW Level Output Current 64 mA

T

A

Free Air Operating Temperature 0 70 °C

Symbol Parameter Conditions

Min Typ Max

Units

(Note 2)

V

I

Input Clamp Voltage VCC = Min, II = −18 mA −1.2 V

V

OH

HIGH Level VCC = 4.5V to 5.5V, IOH = −2 mA VCC − 2V

Output Voltage VCC = 4.5V, IOH = −3 mA 2.4 V

VCC = 4.5V, IOH = Max 2.4 V

V

OL

LOW Level Output Voltage VCC = Min, IOL = Max 0.35 0.55 V

I

I

Input Current at Max VCC = Max, VI = 7V,

0.1 mA

Input Voltage (VI = 5.5V for A or B Ports)

I

IH

HIGH Level VCC = Max Control Inputs 20

µA

Input Current VI = 2.7V (Note 3) A or B Ports 70

I

IL

LOW Level VCC = Max, Control Inputs −0.5

mA

Input Current VI = 0.4V (Note 3) A or B Ports −0.75

I

O

Output Drive Current VCC = Max, VO = 2.25V −50 −150 mA

I

CCH

Supply Current with Outputs HIGH VCC = Max 37 58 mA

I

CCL

Supply Current with Outputs LOW 78 123 mA

I

CCZ

Supply Current with Outputs

51 80 mA

in 3-STATE

Loading...

Loading...