Fairchild Semiconductor 100398QIX, 100398QI, 100398QCX, 100398QC, 100398PC Datasheet

© 2000 Fairchild Semiconductor Corporation DS010970 www.fairchildsemi.com

February 1992

Revised August 2000

100398 Quad Differential ECL/TTL Translating Transceiver with Latch

100398

Quad Differential ECL/TTL Translating Transceiver

with Latch

General Description

The 100398 is a quad latched transceiver designed to convert TTL logic levels to differential F100K ECL logic levels

and vice versa. This device was desig ned wit h the capa bi lity of driving a differential 25

Ω ECL load with cutoff capabil-

ity, and will sink a 64 mA TTL load. The 100398 is ideal for

mixed technology applications utilizing either an ECL or

TTL backplane.

The direction of translat ion is set by the direction control

pin (DIR). The DIR pin on the 100398 accept s TTL logic

levels. A TTL LOW on DIR sets up the ECL pi ns as inputs

and TTL pins as ou tputs. A TTL HIG H on DIR sets up the

TTL pins as inputs and ECL pins as outputs.

A LOW on the outp ut en able inp ut pi n (OE) hol ds the ECL

output in a cut-off state and the TTL outputs at a high

impedance level. A HIGH on the latch enable input (LE)

latches the data at both inputs even though only one output

is enabled at the time. A LOW on LE makes the latch transparent.

The cut-off state is designe d to be more negative than a

normal ECL LOW l evel. This allows the output emi tter-followers to turn off when the termination supply is

−2.0V, pre-

senting a high impedance to the data bus. This high

impedance reduces termination power and prevents loss of

low state noise margin when several loads share the bus.

The 100398 is designe d with FAST

TTL output buffers,

featuring optimal DC drive an d capabl e of quickly cha rging

and discharging highly capacitive loads. All Inputs have

50 k

Ω pull-down resistors.

Features

■ Differential ECL input/output structure

■ 64 mA FAST TTL outputs

■ 25

Ω differential ECL outputs with cut-off

■ Bi-directional translation

■ 2000V ESD protection

■ Latched outputs

■ 3-STATE outputs

■ Voltage compensated operating range

= −4.2V to −5.7V

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering code.

FAST is a registered trademark of Fairc hild Semiconductor.

Order Number Package Number Package Description

100398PC N24E 24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-010, 0.400 Wide

100398QC V28A 28-Lead Plastic Lead Chip Carrier (PLCC), JEDEC MO-047, 0.450 Square

100398QI V28A 28-Lead Plastic Lead Chip Carrier (PLCC), JEDEC MO-047, 0.450 Square

Industrial Temperature Range (

−40°C to +85°C)

www.fairchildsemi.com 2

100398

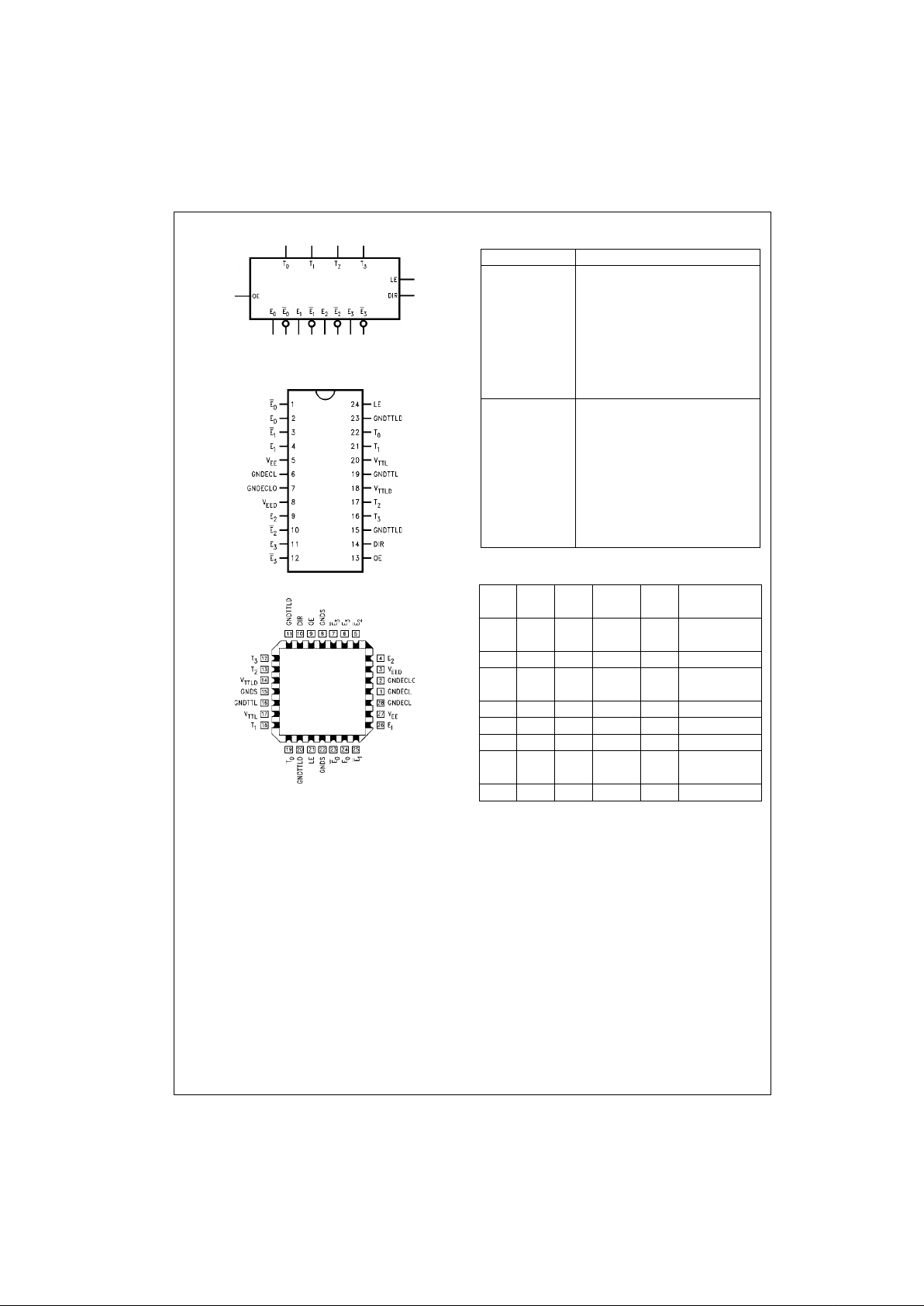

Logic Symbol

Connection Diagrams

24-Pin DIP

28-Pin PLCC

Pin Descriptions

Tr uth Table

H = HIGH Voltage Level

L = LOW Voltage Level

X = Don’t Care

Z = High Impedance

Note 1: ECL input to TTL out put mode.

Note 2: TTL input to ECL output mode.

Note 3: Retains data present before LE set HIGH.

Note 4: Latch is transparent.

Pin Names Description

E

0–E3

ECL Data I/O

E

0–E3

Complementary ECL

Data I/O

T

0–T3

TTL Data I/O

OE Output Enable Input Levels

LE Latch Enable Input Levels

DIR Direction Control

Input (TTL levels)

GNDECL ECL Ground

GNDECLO ECL Output Ground

GNDS ECL Ground-to-Substrate

V

EE

ECL Quiescent Power Supply

V

EED

ECL Dynamic Power Supply

GNDTTL TTL Quiescent Ground

GNDTTLD TTL Dynamic Ground

V

TTL

TTL Quiescent Power Supply

V

TTLD

TTL Dynamic Power Supply

LE DIR OE ECL TTL

Notes

Port Port

000LOWZ

(Cut-Off)

0 0 1 Input Output (Note 1)(Note 4)

010LOWZ

(Cut-Off)

0 1 1 Output Input (Note 2)(Note 4)

1 0 0 Input Z (Note 1)(Note 3)

1 0 1 Latched X (Note 1)(Note 3)

1 1 0 Low Input (Note 2)(Note 3)

(Cut-Off)

1 1 1 Latched X (Note 2)(Note 3)

3 www.fairchildsemi.com

100398

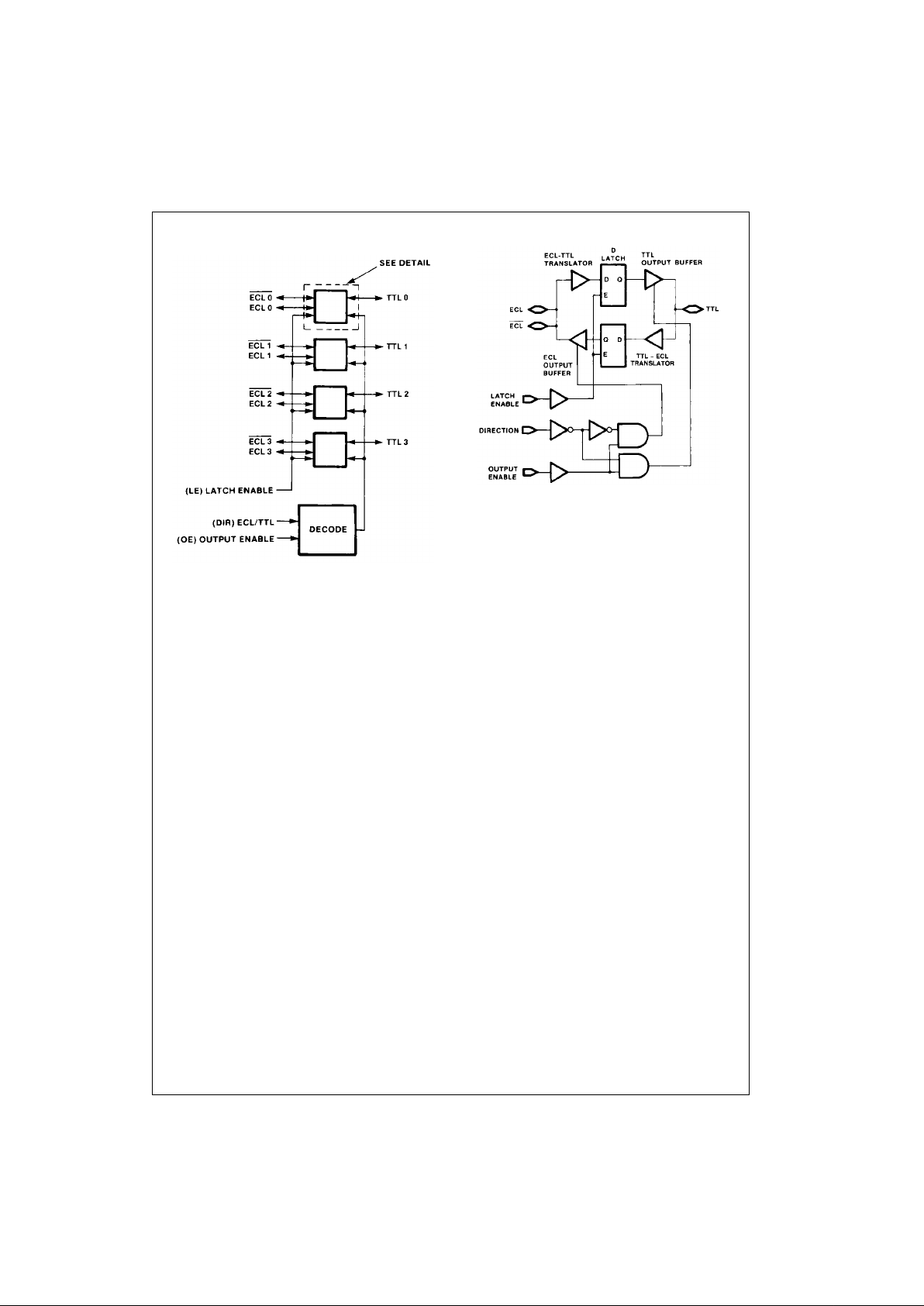

Functional Diagram

Note: LE, and OE use TTL logic levels

Detail

www.fairchildsemi.com 4

100398

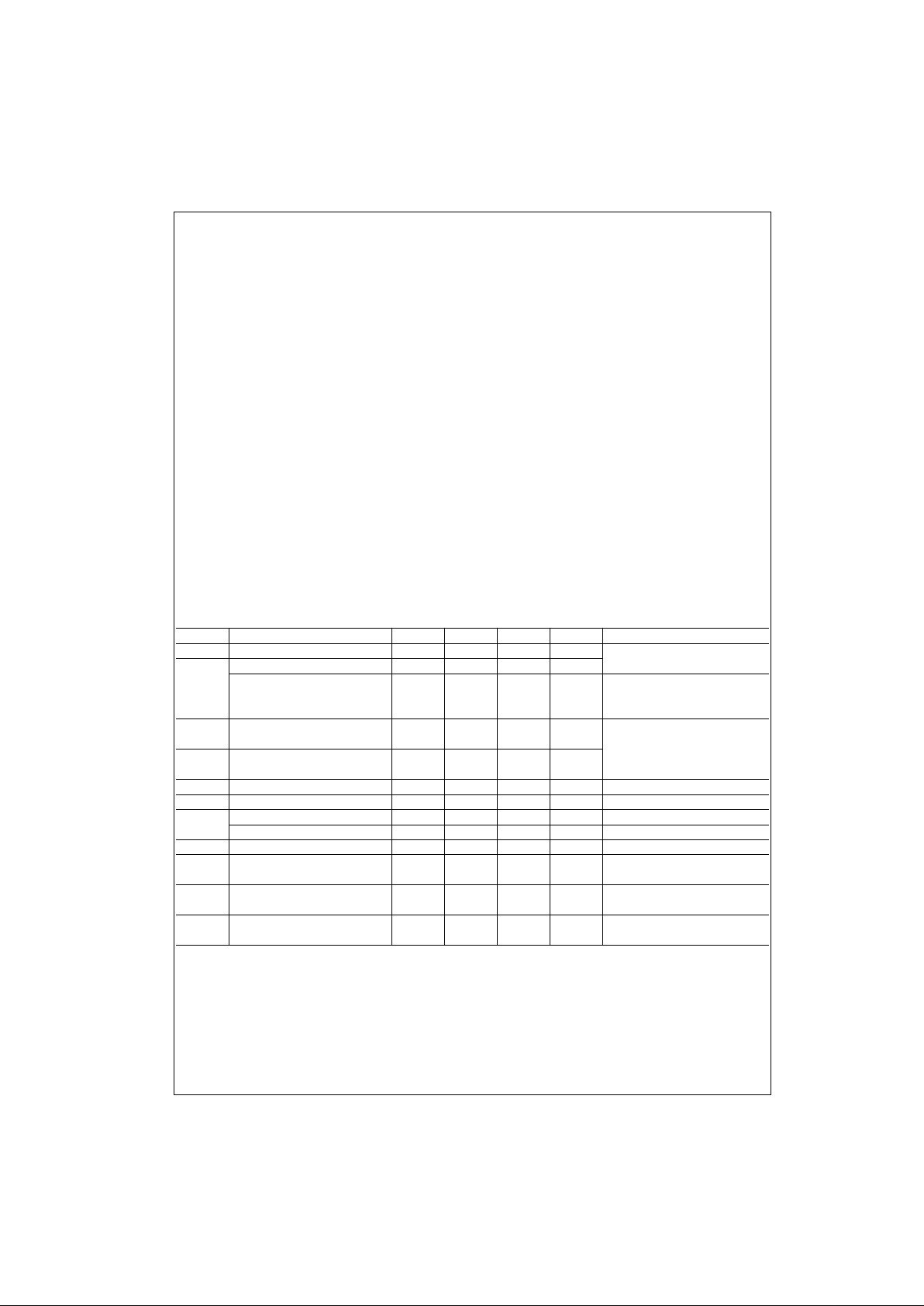

Absolute Maximum Ratings(Note 5) Recommended Operating

Conditions

Note 5: The “Absolute Maximum Ratings” are those values beyon d which

the safety of the dev ice cannot be guaranteed. T he device sh ould not be

operated at these limit s. The parametric values defin ed in the Electrical

Characteristics tables are not guaranteed at the absolute maximum rating.

The “Recomme nded O peratin g Cond itions ” table will defin e the condition s

for actual device operation.

Note 6: The specified limits represent t he “worst case” value for the param-

eter. Since these value s normally occur at th e temperature extrem es, additional noise immunity and guardbanding can be achieved by decreasing the

allowable system operating ranges. Conditions for testing shown in the

tables are chosen to guarantee operation under “worst case” conditions.

Note 7: ESD testing conf orm s t o M I L-STD-883, Method 3015.

Commercial Version

TTL-to-ECL DC Electrical Characteristics

(Note 9)

V

EE

= −4.2V to −5.7V, GND = 0V, TC = 0°C to +85°C, V

TTL

= +4.5V to +5.5V

Note 8: Either voltage limit or cu rrent limit is sufficient to protec t inputs.

Note 9: The specified limits represent the “worst case” value for the parameter. Since these values normally occur at the temperature extremes, additional

noise immunity and guardbanding can be achieved by decreasing the all owable syste m opera ti ng r ange s. Co ndi ti ons fo r t est ing shown in the ta ble s are chosen to guarantee operation under “worst case” conditions.

Storage Temperature (T

STG

) −65°C to +150°C

Maximum Junction Temperature

(T

J

) +150°C

V

EE

Pin Potential to Ground Pin −7.0V to +0.5V

V

TTL

Pin Potential to Ground Pin −0.5V to +6.0V

ECL Input Voltage (DC) V

EE

to +0.5V

ECL Output Current

(DC Output HIGH)

−50 mA

TTL Input Voltage (Note 6)

−0.5V to +7.0V

TTL Input Current (Note 6)

−30 mA to +5.0 mA

Voltage Applied to Output in

HIGH State 3-STATE Output

−0.5V to +5.5V

Current Applied to TTL

Output in LOW State (Max) twice the Rated I

OL

(mA)

ESD (Note 7)

≥ 2000V

Case Temperature (T

C

)

Commercial 0

°C to +85°C

Industrial

−40°C to +85°C

ECL Supply Voltage (V

EE

) −5.7V to −4.2V

TTL Supply Voltage (V

TTL

) +4.5V to +5.5V

Symbol Parameter Min Typ Max Units Conditions

V

OH

Output HIGH Voltage −1025 −955 −870 mV VIN = V

IH(Max)

or V

IL(Min)

V

OL

Output LOW Voltage −1830 −1705 −1620 mV Loading with 50Ω to − 2V

Cutoff Voltage −2000 −1950 mV OE and LE LOW, DIR HIGH

V

IN

= V

IH(Max)

or VIL(Min),

Loading with 50Ω to −2V

V

OHC

Output HIGH Voltage

−1035 mV

Corner Point High VIN = V

IH(Min)

or V

IL(Max)

V

OLC

Output LOW Voltage

−1610 mV

Loading with 50Ω to −2V

Corner Point Low

V

IH

Input HIGH Voltage 2.0 5.0 V Over V

TTL

, VEE, TC Range

V

IL

Input LOW Voltage 0 0.8 V Over V

TTL

, VEE, TC Range

I

IH

Input HIGH Current 5.0 µAVIN = +2.7V

Breakdown Test 0.5 mA VIN = +5.5V

I

IL

Input LOW Current −700 µAVIN = +0.5V

V

FCD

Input Clamp

−1.2 V IIN = −18 mA

Diode Voltage

I

EE

VEE Supply Current −99 −50 mA LE LOW, OE and DIR HIGH

Inputs Open

I

EEZ

VEE Supply Current −159 −90 mA LE and OE LOW, DIR HIGH

Inputs Open

Loading...

Loading...