Page 1

ARM720T Revision 4

(AMBA AHB Bus Interface Version)

CORE CPU MANUAL

Page 2

NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko

Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due

to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that

anything made in accordance with this material will be free from any patent or copyright infringement of a third

party. This material or portions thereof may contain technology or the subject relating to strategic products under

the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the

Ministry of International Trade and Industry or other approval from another government agency.

* is the registered trademark of ARM Limited.

* CompactFlash is a registered trademark of Sandisk Corporation.

Names mentioned herein are trademarks and/or registered trademarks of their respective companies.

Copyright ©2001, 2003 ARM Limited. All rights reserved.

Page 3

Preface

1 Introduction

2 Programmer’s Model

3 Configuration

4 Instruction and Data Cache

5Write Buffer

6 The Bus Interface

7 Memory Management Unit

8 Coprocessor Interface

9 Debugging Your System

10 ETM Interface

11 Test Support

A Signal Descriptions

Glossary

Index

Page 4

Page 5

Preface

About this document................................................................................................xi

1 Introduction

1.1 About the ARM720T processor.................................................................1-1

1.2 Coprocessors ............................................................................................1-5

1.3 About the instruction set............................................................................1-5

1.4 Silicon revisions.......................................................................................1-18

2 Programmer’s Model

2.1 Processor operating states........................................................................2-1

2.2 Memory formats.........................................................................................2-2

2.3 Instruction length.......................................................................................2-3

2.4 Data types .................................................................................................2-3

2.5 Operating modes.......................................................................................2-4

2.6 Registers ...................................................................................................2-4

2.7 Program status registers ...........................................................................2-8

2.8 Exceptions...............................................................................................2-10

2.9 Relocation of low virtual addresses by the FCSE PID.............................2-15

2.10 Reset.......................................................................................................2-16

2.11 Implementation-defined behavior of instructions.....................................2-17

CONTENTS

Contents

3 Configuration

3.1 About configuration....................................................................................3-1

3.2 Internal coprocessor instructions...............................................................3-2

3.3 Registers ...................................................................................................3-3

4 Instruction and Data Cache

4.1 About the instruction and data cache ........................................................4-1

4.2 IDC validity ................................................................................................4-2

4.3 IDC enable, disable, and reset ..................................................................4-2

5 Write Buffer

5.1 About the write buffer ................................................................................5-1

5.2 Write buffer operation................................................................................5-2

6 The Bus Interface

6.1 About the bus interface..............................................................................6-1

6.2 Bus interface signals .................................................................................6-3

6.3 Transfer types............................................................................................6-5

6.4 Address and control signals ......................................................................6-7

6.5 Slave transfer response signals ................................................................6-9

6.6 Data buses ..............................................................................................6-10

6.7 Arbitration................................................................................................6-12

6.8 Bus clocking ............................................................................................6-13

ARM720T CORE CPU MANUAL EPSON i

Page 6

CONTENTS

6.9 Reset .......................................................................................................6-13

7 Memory Management Unit

7.1 About the MMU..........................................................................................7-1

7.2 MMU program-accessible registers...........................................................7-3

7.3 Address translation....................................................................................7-4

7.4 MMU faults and CPU aborts....................................................................7-15

7.5 Fault address and fault status registers...................................................7-16

7.6 Domain access control ............................................................................7-17

7.7 Fault checking sequence.........................................................................7-19

7.8 External aborts.........................................................................................7-21

7.9 Interaction of the MMU and cache...........................................................7-21

8 Coprocessor Interface

8.1 About coprocessors...................................................................................8-1

8.2 Coprocessor interface signals ...................................................................8-3

8.3 Pipeline-following signals...........................................................................8-4

8.4 Coprocessor interface handshaking..........................................................8-5

8.5 Connecting coprocessors..........................................................................8-9

8.6 Not using an external coprocessor..........................................................8-10

8.7 STC operations........................................................................................8-10

8.8 Undefined instructions.............................................................................8-10

8.9 Privileged instructions..............................................................................8-10

9 Debugging Your System

9.1 About debugging your system...................................................................9-2

9.2 Controlling debugging................................................................................9-3

9.3 Entry into debug state................................................................................9-5

9.4 Debug interface .........................................................................................9-9

9.5 ARM720T core clock domains...................................................................9-9

9.6 The EmbeddedICE-RT macrocell............................................................9-10

9.7 Disabling EmbeddedICE-RT....................................................................9-11

9.8 EmbeddedICE-RT register map ..............................................................9-12

9.9 Monitor mode debugging.........................................................................9-12

9.10 The debug communications channel.......................................................9-14

9.11 Scan chains and the JTAG interface.......................................................9-17

9.12 The TAP controller...................................................................................9-19

9.13 Public JTAG instructions..........................................................................9-20

9.14 Test data registers...................................................................................9-22

9.15 Scan timing..............................................................................................9-25

9.16 Examining the core and the system in debug state.................................9-26

9.17 Exit from debug state...............................................................................9-29

9.18 The program counter during debug.........................................................9-30

9.19 Priorities and exceptions..........................................................................9-32

9.20 Watchpoint unit registers.........................................................................9-33

9.21 Programming breakpoints........................................................................9-36

9.22 Programming watchpoints.......................................................................9-38

9.23 Abort status register.................................................................................9-38

9.24 Debug control register .............................................................................9-39

9.25 Debug status register...............................................................................9-41

9.26 Coupling breakpoints and watchpoints....................................................9-43

9.27 EmbeddedICE-RT timing.........................................................................9-44

ii EPSON ARM720T CORE CPU MANUAL

Page 7

10 ETM Interface

10.1 About the ETM interface..........................................................................10-1

10.2 Enabling and disabling the ETM7 interface.............................................10-1

10.3 Connections between the ETM7 macrocell and the

ARM720T processor................................................................................10-2

10.4 Clocks and resets....................................................................................10-3

10.5 Debug request wiring...............................................................................10-3

10.6 TAP interface wiring ................................................................................10-3

11 Test Support

11.1 About the ARM720T test registers ..........................................................11-1

11.2 Automatic Test Pattern Generation (ATPG)............................................11-2

11.3 Test State Register..................................................................................11-3

11.4 Cache test registers and operations........................................................11-3

11.5 MMU test registers and operations..........................................................11-8

A Signal Descriptions

A.1 AMBA interface signals .............................................................................A-1

A.2 Coprocessor interface signals ...................................................................A-2

A.3 JTAG and test signals ...............................................................................A-3

A.4 Debugger signals.......................................................................................A-4

A.5 Embedded trace macrocell interface signals.............................................A-5

A.6 ATPG test signals......................................................................................A-7

A.7 Miscellaneous signals................................................................................A-7

CONTENTS

Glossary

Index

ARM720T CORE CPU MANUAL EPSON iii

Page 8

CONTENTS

List of Figures

Figure 1-1 720T Block diagram....................................................................................1-2

Figure 1-2 ARM720T processor functional signals.......................................................1-3

Figure 1-3 ARM instruction set formats........................................................................1-7

Figure 1-4 Thumb instruction set formats...................................................................1-14

Figure 2-1 Big-endian addresses of bytes with words..................................................2-2

Figure 2-2 Little-endian addresses of bytes with words ...............................................2-3

Figure 2-3 Register organization in ARM state.............................................................2-5

Figure 2-4 Register organization in Thumb state .........................................................2-6

Figure 2-5 Mapping of Thumb state registers onto ARM state registers......................2-7

Figure 2-6 Program status register format....................................................................2-8

Figure 3-1 MRC and MCR bit pattern...........................................................................3-2

Figure 3-2 ID Register read format...............................................................................3-3

Figure 3-3 ID Register write format ..............................................................................3-3

Figure 3-4 Control Register read format.......................................................................3-4

Figure 3-5 Control Register write format ......................................................................3-4

Figure 3-6 Translation Table Base Register format......................................................3-5

Figure 3-7 Domain Access Control Register format.....................................................3-6

Figure 3-8 Fault Status Register format .......................................................................3-6

Figure 3-9 Fault Address Register format ....................................................................3-7

Figure 3-10 FCSCE PID Register format .......................................................................3-8

Figure 3-11 PROCID Register format.............................................................................3-8

Figure 6-1 Simple AHB transfer....................................................................................6-2

Figure 6-2 AHB bus master interface...........................................................................6-4

Figure 6-3 Simple memory cycle..................................................................................6-5

Figure 6-4 Transfer type examples...............................................................................6-6

Figure 7-1 Translation Table Base Register.................................................................7-4

Figure 7-2 Translating page tables...............................................................................7-5

Figure 7-3 Accessing translation table level one descriptors .......................................7-6

Figure 7-4 Level one descriptor....................................................................................7-6

Figure 7-5 Section descriptor .......................................................................................7-8

Figure 7-6 Coarse page table descriptor......................................................................7-8

Figure 7-7 Fine page table descriptor...........................................................................7-9

Figure 7-8 Section translation.....................................................................................7-10

Figure 7-9 Level two descriptor..................................................................................7-10

Figure 7-10 Large page translation from a coarse page table......................................7-12

Figure 7-11 Small page translation from a coarse page table......................................7-13

Figure 7-12 Tiny page translation from a fine page table.............................................7-14

Figure 7-13 Domain Access Control Register format...................................................7-17

Figure 7-14 Sequence for checking faults....................................................................7-19

Figure 8-1 Coprocessor busy-wait sequence...............................................................8-6

Figure 8-2 Coprocessor register transfer sequence.....................................................8-7

Figure 8-3 Coprocessor data operation sequence.......................................................8-7

Figure 8-4 Coprocessor load sequence .......................................................................8-8

Figure 8-5 Example coprocessor connections .............................................................8-9

Figure 9-1 Typical debug system .................................................................................9-2

Figure 9-2 ARM720T processor block diagram............................................................9-3

Figure 9-3 Debug state entry........................................................................................9-5

iv EPSON ARM720T CORE CPU MANUAL

Page 9

CONTENTS

Figure 9-4 Clock synchronization.................................................................................9-8

Figure 9-5 The ARM720T core, TAP controller, and EmbeddedICE-RT macrocell...9-10

Figure 9-6 Domain Access Control Register..............................................................9-14

Figure 9-7 ARM720T processor scan chain arrangements........................................9-17

Figure 9-8 Test access port controller state transitions..............................................9-19

Figure 9-9 ID code register format..............................................................................9-22

Figure 9-10 Scan timing ...............................................................................................9-25

Figure 9-11 Debug exit sequence ................................................................................9-29

Figure 9-12 EmbeddedICE-RT block diagram .............................................................9-34

Figure 9-13 Watchpoint control value, and mask format..............................................9-35

Figure 9-14 Debug abort status register.......................................................................9-38

Figure 9-15 Debug control register format....................................................................9-39

Figure 9-16 Debug status register format.....................................................................9-41

Figure 9-17 Debug control and status register structure..............................................9-42

Figure 11-1 CP15 MRC and MCR bit pattern...............................................................11-1

Figure 11-2 Rd format, CAM read................................................................................11-4

Figure 11-3 Rd format, CAM write................................................................................11-4

Figure 11-4 Rd format, RAM read................................................................................11-5

Figure 11-5 Rd format, RAM write................................................................................11-5

Figure 11-6 Rd format, CAM match RAM read ............................................................11-5

Figure 11-7 Data format, CAM read.............................................................................11-5

Figure 11-8 Data format, RAM read.............................................................................11-5

Figure 11-9 Data format, CAM match RAM read .........................................................11-6

Figure 11-10 Rd format, write cache victim and lockdown base....................................11-6

Figure 11-11 Rd format, write cache victim....................................................................11-6

Figure 11-12 Rd format, CAM write and data format, CAM read .................................11-10

Figure 11-13 Rd format, RAM1 write............................................................................11-10

Figure 11-14 Data format, RAM1 read.........................................................................11-11

Figure 11-15 Rd format, RAM2 write and data format, RAM2 read .............................11-11

Figure 11-16 Rd format, write TLB lockdown...............................................................11-12

ARM720T CORE CPU MANUAL EPSON v

Page 10

CONTENTS

List of Tables

Table 1-1 Key to tables ...............................................................................................1-6

Table 1-2 ARM instruction summary...........................................................................1-8

Table 1-3 Addressing mode 2...................................................................................1-10

Table 1-4 Addressing mode 2 (privileged) ................................................................1-11

Table 1-5 Addressing mode 3...................................................................................1-11

Table 1-6 Addressing mode 4 (load).........................................................................1-11

Table 1-7 Addressing mode 4 (store)........................................................................1-12

Table 1-8 Addressing mode 5...................................................................................1-12

Table 1-9 Operand 2.................................................................................................1-12

Table 1-10 Fields.........................................................................................................1-12

Table 1-11 Condition fields..........................................................................................1-13

Table 1-12 Thumb instruction summary......................................................................1-15

Table 2-1 ARM720T modes of operation ....................................................................2-4

Table 2-2 PSR mode bit values...................................................................................2-9

Table 2-3 Exception entry and exit............................................................................2-11

Table 2-4 Exception vector addresses......................................................................2-13

Table 3-1 Cache and MMU Control Register ..............................................................3-3

Table 3-2 Cache operation..........................................................................................3-7

Table 3-3 TLB operations............................................................................................3-7

Table 6-1 Transfer type encoding ...............................................................................6-5

Table 6-2 Transfer size encodings..............................................................................6-7

Table 6-3 Burst type encodings...................................................................................6-8

Table 6-4 Protection control encodings.......................................................................6-8

Table 6-5 Response encodings.................................................................................6-10

Table 6-6 Active byte lanes for a 32-bit little-endian data bus...................................6-11

Table 6-7 Active byte lanes for a 32-bit big-endian data bus ....................................6-12

Table 7-1 CP15 register functions...............................................................................7-3

Table 7-2 Level one descriptor bits.............................................................................7-7

Table 7-3 Interpreting level one descriptor bits [1:0] ...................................................7-7

Table 7-4 Section descriptor bits.................................................................................7-8

Table 7-5 Coarse page table descriptor bits ...............................................................7-9

Table 7-6 Fine page table descriptor bits....................................................................7-9

Table 7-7 Level two descriptor bits............................................................................7-11

Table 7-8 Interpreting page table entry bits [1:0].......................................................7-11

Table 7-9 Priority encoding of fault status.................................................................7-16

Table 7-10 Interpreting access control bits in Domain Access Control Register.........7-17

Table 7-11 Interpreting access permission (AP) bits...................................................7-18

Table 8-1 Coprocessor availability ..............................................................................8-2

Table 8-2 Handshaking signals...................................................................................8-5

Table 8-3 Handshake signal connections ...................................................................8-9

Table 8-4 CPnTRANS signal meanings....................................................................8-10

Table 9-1 Function and mapping of EmbeddedICE-RT registers .............................9-12

Table 9-2 Domain Access Control Register bit assignments ....................................9-15

Table 9-3 Instruction encodings for scan chain 15....................................................9-18

Table 9-4 Public instructions.....................................................................................9-20

Table 9-5 Scan chain number allocation...................................................................9-23

Table 9-6 Scan chain 1 cells.....................................................................................9-25

vi EPSON ARM720T CORE CPU MANUAL

Page 11

CONTENTS

Table 9-7 Determining the cause of entry to debug state .........................................9-32

Table 9-8 SIZE[1:0] signal encoding.........................................................................9-35

Table 9-9 Debug control register bit assignments.....................................................9-39

Table 9-10 Interrupt signal control...............................................................................9-40

Table 9-11 Debug status register bit assignments......................................................9-41

Table 10-1 Connections between the ETM7 macrocell and

the ARM720T processor...........................................................................10-2

Table 11-1 Summary of ATPG test signals.................................................................11-2

Table 11-2 Test State Register operations..................................................................11-3

Table 11-3 Summary of CP15 register c7, c9, and c15 operations.............................11-4

Table 11-4 Write cache victim and lockdown operations............................................11-6

Table 11-5 CAM, RAM1, and RAM2 register c15 operations......................................11-9

Table 11-6 Register c2, c3, c5, c6, c8, c10, and c15 operations ................................11-9

Table 11-7 CAM memory region size........................................................................11-10

Table 11-8 Access permission bit setting..................................................................11-11

Table 11-9 Miss and fault encoding ..........................................................................11-11

Table 11-10 RAM2 memory region size......................................................................11-12

Table A-1 AMBA interface signals...............................................................................A-1

Table A-2 Coprocessor interface signal descriptions ..................................................A-2

Table A-3 JTAG and test signal descriptions...............................................................A-3

Table A-4 Debugger signal descriptions......................................................................A-4

Table A-5 ETM interface signal descriptions...............................................................A-5

Table A-6 ATPG test signal descriptions....................................................................A-7

Table A-7 Miscellaneous signal descriptions...............................................................A-7

ARM720T CORE CPU MANUAL EPSON vii

Page 12

CONTENTS

THIS PAGE IS BLANK.

viii EPSON ARM DDI 0229B

Page 13

Preface

Page 14

Page 15

Preface

Preface

This preface introduces the

CPU Manual

. It contains the following sections:

About this document ................................................................................................. xi

ARM720T Revision 4 (AMBA AHB Bus Interface Version) CORE

About this document

This document is a technical reference manual for the ARM720T r4p2 processor.

Intended audience

This document has been written for experienced hardware and software engineers who might

or might not have experience of the architecture, configuration, integration, and instruction

sets with reference to the ARM product range. it provides information to enable designers to

integrate the processor into a target system as quickly as possible.

Using this manual

This document is organized into the following chapters:

Chapter 1

Chapter 2

Introduction

Programmer’s Model

Read this chapter for an introduction to the ARM720T processor.

Chapter 3

Chapter 4

Chapter 5

Chapter 6

Chapter 7

Read this chapter for a description of the 32-bit ARM and 16-bit

Thumb instruction sets.

Configuration

Read this chapter for a description of the ARM1156F-S control

coprocessor CP15 register configurations and programming

details.

Instruction and Data Cache

Read this chapter for a description of the mixed instruction and

data cache.

Write Buffer

The Bus Interface

Memory Management Unit

Read this chapter for a description on how to enhance the system

performance of the ARM720T processor by using the write buffer.

Read this chapter for a description of the ARM720T processor bus

interface.

Read this chapter for a description of the functions and how to use

of the

Memory Management Unit

(MMU).

ARM720T CORE CPU MANUAL EPSON xi

Page 16

Preface

Chapter 8

Chapter 9

Chapter 10

Chapter 11

Chapter

Coprocessor Interface

Read this chapter for a description on how to connect coprocessors

to the ARM1156F-S coprocessor interface.

Debugging Your System

Read this chapter for a description of the hardware extensions and

integrated on-chip debug support for the ARM720T processor.

ETM Interface

Test Support

Signal Descriptions

Read this chapter for a description of the Embedded Trace

Macrocell support for the ARM720T processor.

Read this chapter for a description of how to perform device-specific

test operations.

Read this appendix for a list of all ARM720T processor interface

signals.

Typographical conventions

The following typographical conventions are used in this document:

bold Highlights ARM processor signal names, and interface elements

such as menu names. Also used for terms in descriptive lists, where

appropriate.

italic

monospace Denotes text that can be entered at the keyboard, such as

space Denotes a permitted abbreviation for a command or option. The

mono

monospace italic Denotes arguments to commands or functions where the argument

monospace bold Denotes language keywords when used outside example code.

Highlights special terminology, cross-references, and citations.

commands, file names and program names, and source code.

underlined text can be entered instead of the full command or

option name.

is to be replaced by a specific value.

Product revision status

The rnpn identifier indicates the revision status of the product described in this document,

where:

n

r

n

p

Identifies the major revision of the product.

Identifies the minor revision or modification status of the product.

xii EPSON ARM720T CORE CPU MANUAL

Page 17

Preface

Timing diagram conventions

This manual contains one or more timing diagrams. The following key explains the

components used in these diagrams. Any variations are clearly labeled when they occur.

Therefore, no additional meaning must be attached unless specifically stated.

Clock

HIGH to LOW

Transient

HIGH/LOW to HIGH

Bus stable

Bus to high impedance

Bus change

High impedance to stable bus

Key to timing diagram conventions

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within

the shaded area at that time. The actual level is unimportant and does not affect normal

operation.

Further reading

This section lists publications by ARM Limited, and by third parties.

ARM periodically provides updates and corrections to its documentation. See

http://www.arm.com for current errata sheets, addenda, and ARM Frequently Asked Questions.

ARM publications

This document contains information that is specific to the ARM720T processor. Refer to the

following documents for other relevant information:

ARM Architecture Reference Manual

•

AMBA Specification (Rev 2.0)

•

•

ETM7 (Rev 1) Technical Reference Manual

ARM7TDMI-S (Rev 4) Technical Reference Manual

•

(ARM IHI 0011)

(ARM DDI 0100)

(ARM DDI 0158)

(ARM DDI 0234).

Other publications

This section lists relevant documents published by third parties.

Standard Test Access Port and Boundary Scan Architecture

•

(IEEE Std.

1149.1.1990).

Figure 9-8 on page 9-19 is printed with permission IEEE Std. 1149.1-1990, IEEE Standard

Test Access Port and Boundary-Scan Architecture Copyright 2001, by IEEE. The IEEE

disclaims any responsibility or liability resulting from the placement and use in the described

manner.

ARM720T CORE CPU MANUAL EPSON xiii

Page 18

Preface

THIS PAGE IS BLANK.

xiv EPSON ARM720T CORE CPU MANUAL

Page 19

1

Introduction

Page 20

Page 21

1: Introduction

1 Introduction

This chapter provides an introduction to the ARM720T processor. It contains the following

sections:

1.1 About the ARM720T processor.................................................................. 1-1

1.2 Coprocessors............................................................................................... 1-5

1.3 About the instruction set ........................................................................... 1-5

1.4 Silicon revisions........................................................................................ 1-18

1.1 About the ARM720T processor

The ARM720T processor is a general-purpose 32-bit microprocessor with 8KB cache, enlarged

write buffer , and

processor uses the ARM7TDMI-S CPU, and is software-compatible with the ARM processor

family.

Memory Management Unit

(MMU) combined in a single chip. The ARM720T

The on-chip mixed data and instruction cache, together with the write buffer, substantially

raise the average execution speed and reduce the average amount of memory bandwidth

required by the processor . This enables the external memory to support additional processors

or

Direct Memory Access

The MMU supports a conventional two-level page table structure and several extensions that

make it ideal for running high-end embedded applications and sophisticated operating

systems.

The allocation of virtual addresses with different task IDs improves performance in task

switching operations with the cache enabled. These relocated virtual addresses are monitored

by the EmbeddedICE-RT block.

The memory interface enables the performance potential to be realized without incurring high

costs in the memory system. Speed-critical control signals are pipelined to allow system

control functions to be implemented in standard low-power logic. These control signals permit

the exploitation of paged mode access offered by industry-standard DRAMs.

The ARM720T processor is provided with an

brings out the required signals from the ARM core to the periphery of the ARM720T processor .

This enables you to connect a standard ETM7 macrocell.

The ARM720T processor is a fully static part and has been designed to minimize power

requirements. This makes it ideal for portable applications where low power consumption is

essential.

The ARM720T processor architecture is based on

principles. The instruction set and related decode mechanism are greatly simplified compared

with microprogrammed

(DMA) channels with minimal performance loss.

Embedded T race Macrocell

Reduced Instruction Set Computer

Complex Instruction Set Computers

(CISCs).

(ETM) interface that

(RISC)

ARM720T CORE CPU MANUAL EPSON 1-1

Page 22

1: Introduction

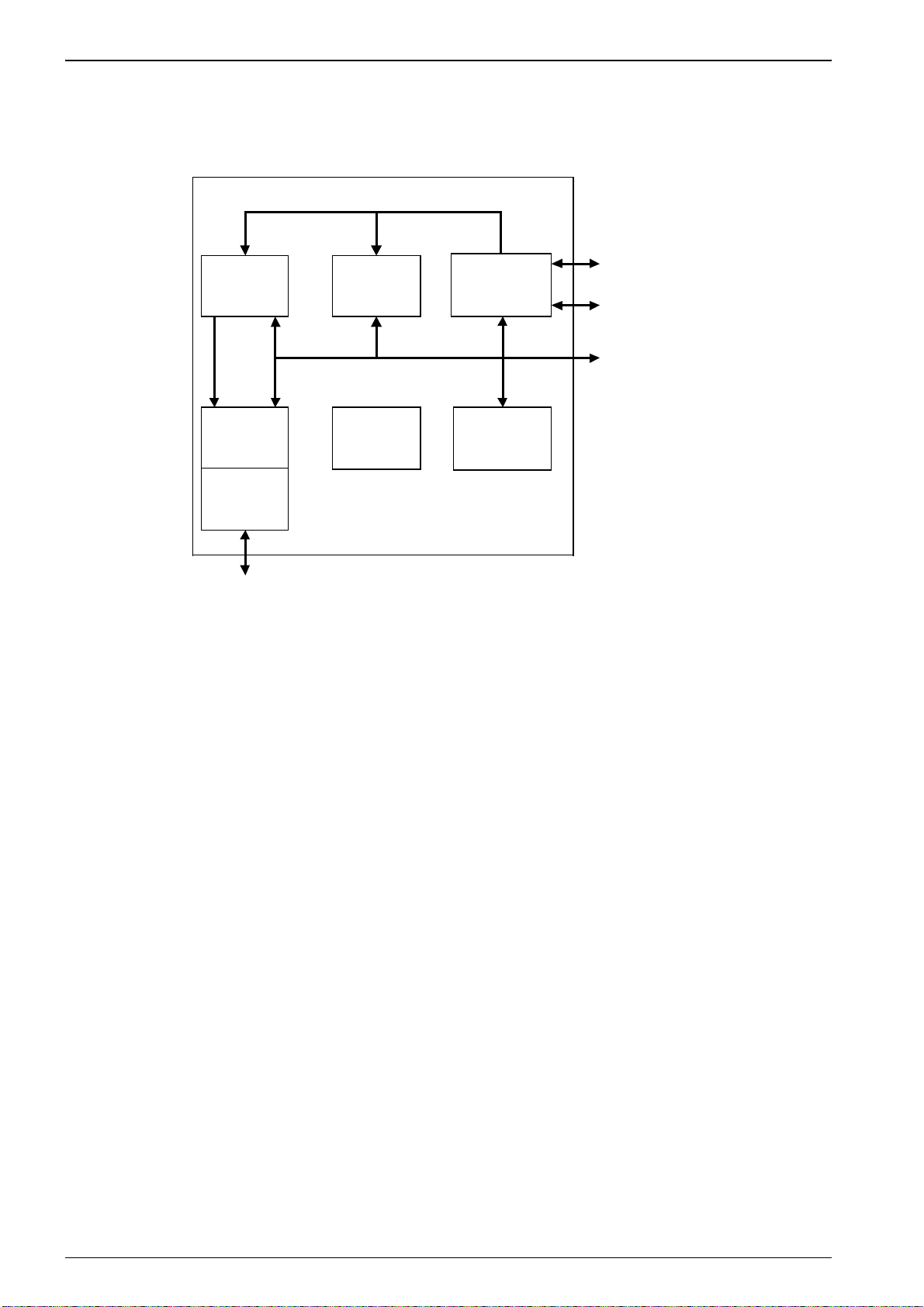

A block diagram of the ARM720T processor is shown in Figure 1-1.

Virtual addres s bus

MMU

8KB cache

Internal data bus

ARM720T core

JTAG debug

inter f ace

ETM interfac e

Coprocess or

inter f ace

Data and

address

buffers

AMBA

inter f ace

AMBA AHB

bus interfac e

Control and

clocking logic

System c ontrol

coproc essor

ARM720T

Figure 1-1 720T Block diagram

1-2 EPSON ARM720T CORE CPU MANUAL

Page 23

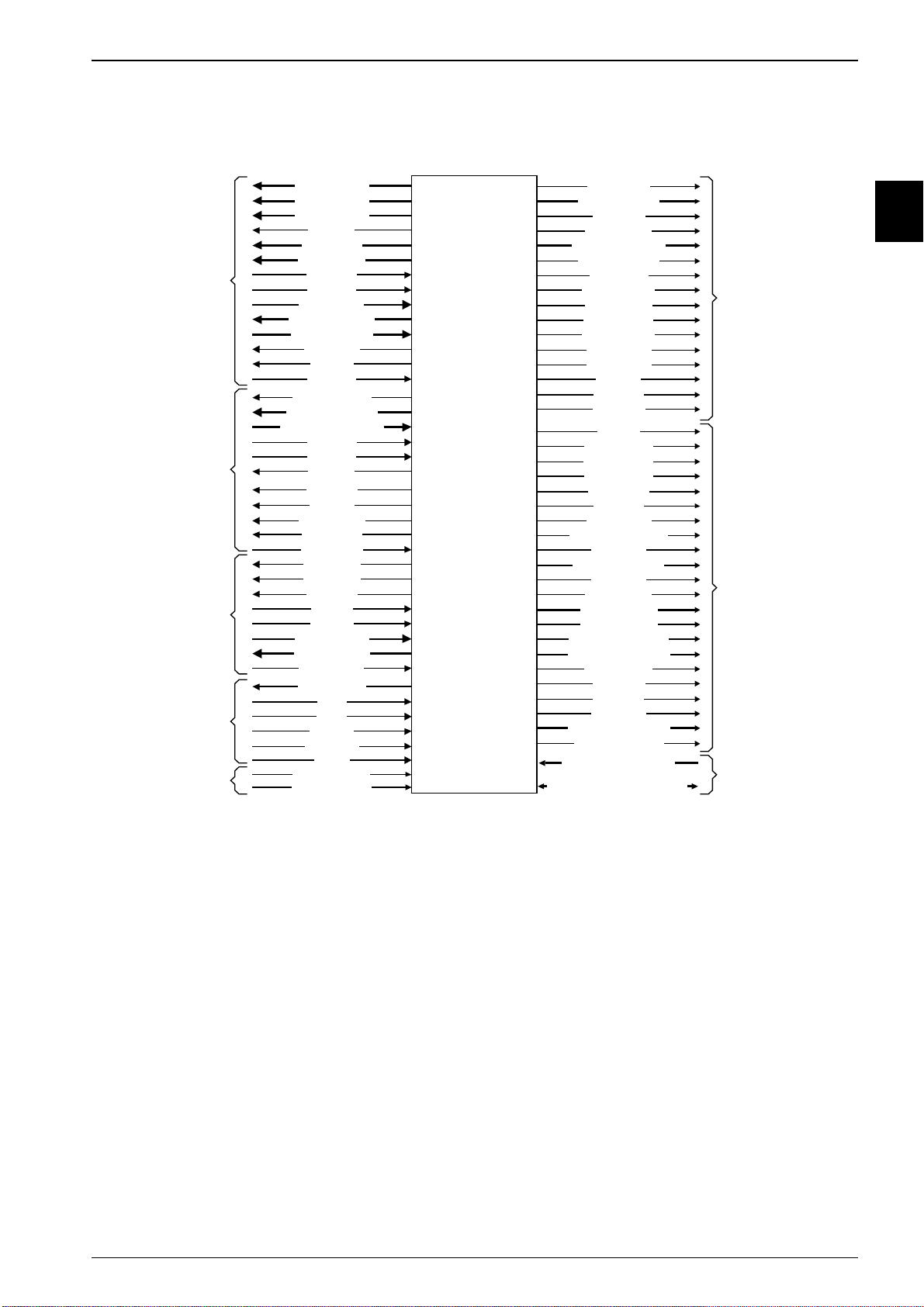

The functional signals on the ARM720T processor are shown in Figure 1-2.

1: Introduction

AMBA

inte r f ace

Coprocess or

inte r f ace

Deb ug

inte r f ace

Mis cellaneous

signals

ATPG

Signals

HADDR[ 31:0 ]

HTRANS[ 1:0]

HBURST [2:0]

HWRI T E

HSIZE[2 :0]

HPROT [3 :0]

HGRA NT

HREADY

HRESP[1:0]

HWDA TA [31 :0]

HRDAT A[ 31:0 ]

HBUSREQ

HLOC K

HCL KEN

EXTCPCLKEN

EXT C P DIN[ 3 1: 0]

EXTCPDOUT[31:0]

EXT C P A

EXT C P B

CPnCPI

CPnOPC

CPTBIT

CPnTRANS

CPnMREQ

EXT CPDBE

COMMRX

COMMTX

DBGA CK

DBGEN

DBGRQ

DBGEXT [1:0]

DBGRNG[ 1:0]

DBGBREAK

BIGENDOUT

nFIQ

nIRQ

VINITHI

HRESETn

HCL K

TESTENABLE

SCANENABLE

ARM720T processor

DBGIR[ 3:0]

DBGSREG[ 3:0]

DBGSDI N

DBGSDO UT

DBGT APS M [3 :0]

DBGC APT URE

DBGSHI FT

DBGUPDA TE

DBGINTEST

DBGEXT EST

DBGn TDOEN

DBGn TRST

DBGT CKEN

DBGT DI

DBGT DO

DBGT MS

ET M EN

ET M BI GEND

ET M HI V ECS

ET M n M REQ

ET M n OP C

ET M SEQ

ET M n EXEC

ETM INSTRVALID

ET M n CP I

ETM ADDR[31 :0]

ET M n RW

ET M C LK EN

ET M SI Z E[1 :0 ]

ETM DBGA CK

ETM RDATA[31 :0]

ET M W DAT A [ 31 :0 ]

ETM ABORT

ET M C PA

ET M C PB

ET M T BIT

ETM PROCID[ 31:0]

ETM PROCIDW R

SCANIN0 - SCANIN6

SCANOUT0 - SCANOUT6

JTAG

inte r f ace

ETM interfac e

ATPG

Signals

Figure 1-2 ARM720T processor functional signals

1.1.1 EmbeddedICE-RT logic

The EmbeddedICE-RT logic provides integrated on-chip debug support for the ARM720T core.

It enables you to program the conditions under which a breakpoint or watchpoint can occur.

The EmbeddedICE-RT logic is an enhanced implementation of EmbeddedICE, and enables

you to perform debugging in monitor mode. In monitor mode, the core takes an exception on a

breakpoint or watchpoint, rather than entering debug state as it does in halt mode.

If the core does not enter debug state when it encounters a watchpoint or breakpoint, it can

continue to service hardware interrupt requests as normal. Debugging in monitor mode is

useful if the core forms part of the feedback loop of a mechanical system, where stopping the

core can potentially lead to system failure.

The EmbeddedICE-RT logic contains a

used to pass information between the target and the host debugger. The EmbeddedICE-RT

logic is controlled through the

ARM720T CORE CPU MANUAL EPSON 1-3

Joint Test Action Group

Debug Communications Channel

(DCC). The DCC is

(JTAG) test access port.

Page 24

1: Introduction

Changes to the programmer’s model

T o provide support for the EmbeddedICE-RT macrocell, the following changes have been made

to the programmer’s model for the ARM720T processor:

Debug Control Register

There are two new bits in the Debug Control Register:

Bit 4 Monitor mode enable. Use this to control how the device reacts on

a breakpoint or watchpoint:

• When set, the core takes the instruction or data abort

exception.

• When clear, the core enters debug state.

Bit 5 EmbeddedICE-RT disable. Use this when changing watchpoints

and breakpoints:

• When set, this bit disables breakpoints and watchpoints,

enabling the breakpoint or watchpoint registers to be

programmed with new values.

• When clear , the new breakpoint or watchpoint values become

operational.

For more information, see

Debug control register

on page 9-39.

Coprocessor register map

A new register, r2, in the coprocessor CP14 register map indicates if the processor

entered the Prefetch or Data Abort exception because of a real abort, or because of a

breakpoint or watchpoint. For more details, see

For more details, see Chapter 9

Debugging Your System

Abort status register

.

on page 9-38.

1-4 EPSON ARM720T CORE CPU MANUAL

Page 25

1: Introduction

1.2 Coprocessors

The ARM720T processor has an internal coprocessor designated CP15 for internal control of

the device (see Chapter 3

The ARM720T processor also includes a port for the connection of on-chip external

coprocessors. This enables extension of the ARM720T functionality in an

architecturally-consistent manner.

Configuration

).

1.3 About the instruction set

The instruction set comprises ten basic instruction types:

• Two types use the on-chip arithmetic logic unit, barrel shifter, and multiplier to

perform high-speed operations on the data in a bank of 31 registers, each 32 bits

wide.

• Three types of instruction control the data transfer between memory and the

registers:

– one optimized for flexibility of addressing

– one for rapid context switching

– one for swapping data.

• Two instructions control the flow and privilege level of execution.

• Three types are dedicated to the control of external coprocessors. These enable you

to extend the functionality of the instruction set off-chip in an open and uniform

way.

The ARM instruction set is a good target for compilers of many different high-level languages.

Where required for critical code segments, assembly code programming is also

straightforward.

ARM720T CORE CPU MANUAL EPSON 1-5

Page 26

1: Introduction

1.3.1 Format summary

This section provides a summary of the ARM and Thumb instruction sets:

•

ARM instruction set

on page 1-7

Thumb instruction set

•

on page 1-14

A key to the instruction set tables is shown in Table 1-1.

The ARM7TDMI-S core on the ARM720T processor is an implementation of the ARM

architecture v4T. For a complete description of both instruction sets, see the

Architecture Reference Manual

.

ARM

Table 1-1 Key to tables

Entry Description

{cond} Refer to Table 1-11 on page 1-13.

<Oprnd2> Refer to Table 1-9 on page 1-12.

{field} Refer to Table 1-10 on page 1-12.

S Sets condition codes (optional).

B Byte operation (optional).

H Halfword operation (optional).

T Forces address translation. Cannot be

used with pre-indexed addresses.

<a_mode2> Refer to Table 1-3 on page 1-10 .

<a_mode2P> Refer to Table 1-4 on page 1-11.

<a_mode3> Refer to Table 1-5 on page 1-11 .

<a_mode4L> Refer to Table 1-6 on page 1-11.

<a_mode4S> Refer to Table 1-7 on page 1-12.

<a_mode5> Refer to Table 1-8 on page 1-12 .

#<32bit_Imm> A 32-bit constant, formed by

right-rotating an 8-bit value by an even

number of bits.

<reglist> A comma-separated list of registers,

enclosed in braces ( { and } ).

1-6 EPSON ARM720T CORE CPU MANUAL

Page 27

1: Introduction

1.3.2 ARM instruction set

This section gives an overview of the ARM instructions available. For full details of these

instructions, see the

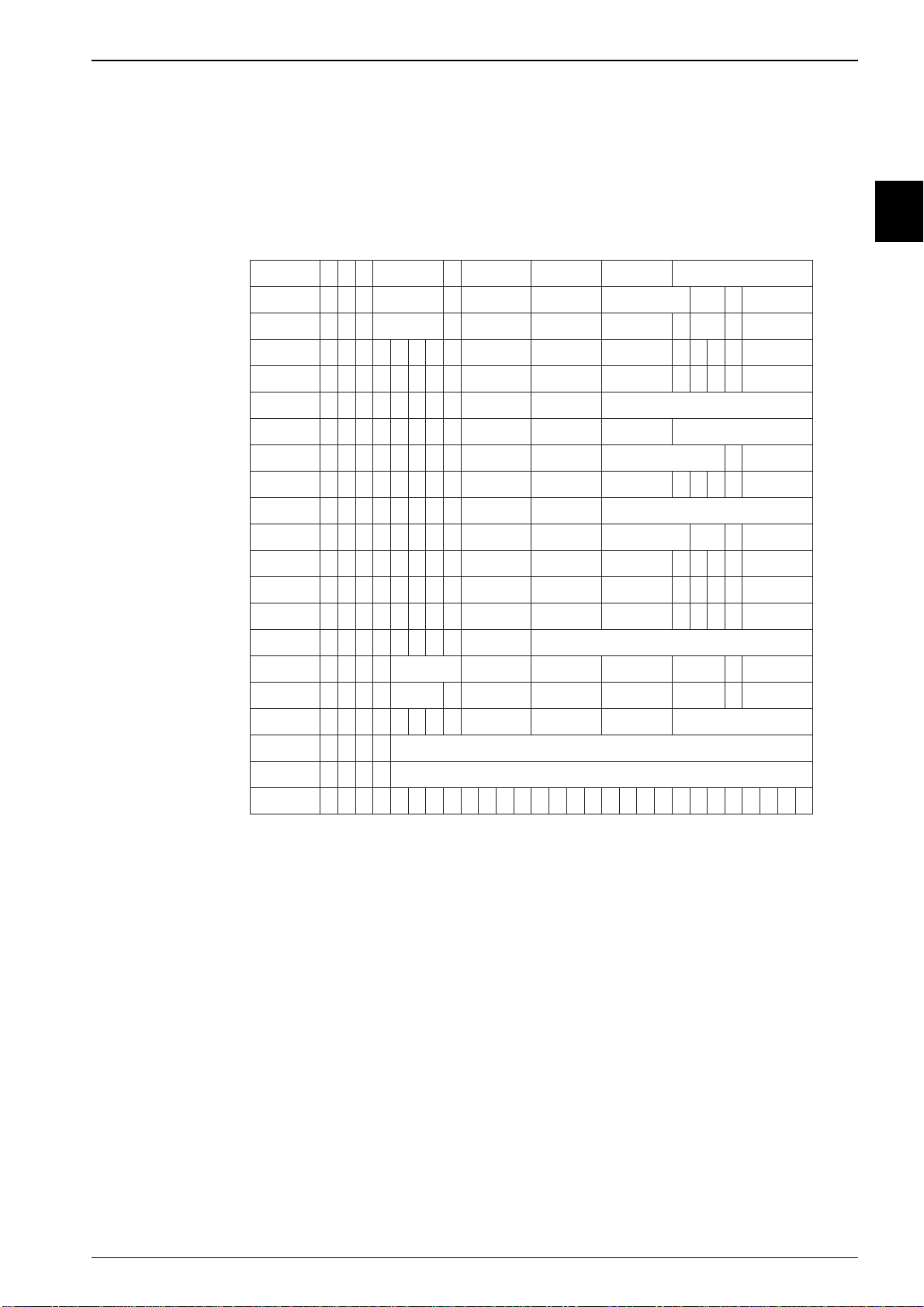

The ARM instruction set formats are shown in Figure 1-3.

Data processing

immediate

Data processing

immediate shift

Data processing register

Multiply

Multiply long

Move from status register

Move immediate to status

Move register to status

Load/store immediate

Load/store register offset

Load/store halfword/

Load/store halfword/

Load/store multiple

Coprocessor register

Coprocessor load and

Branch and branch with

register

register

Branch/exchange

instruction set

signed byte

signed byte

Swap/swap byte

Coprocessor data

processing

transfers

Software interrupt

Undefined

ARM Architecture Reference Manual

.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

0 0 1 op S Rn Rd rotate immediatecond

0 0 0 opcode S Rn Rd shift immediate shift 0 Rm

0 0 0 opcode S Rn Rd Rs shift 1 Rm0

0 0 0 0 0 0 A S

0

0

0

0

1

U

A

Rd

S

RdHi

Rn

RdLo

Rs

Rn

1 0 0 1

1 0 0 1

0 0 0 1 0 R 0 0 SBO Rd SBZ

0 0 1 1 0 R 1 0 Mask SBO rotate immediate

0 0 0 1 0 R 1 0 Mask SBO SBZ Rm0

0 0 0 1 0 0 1 0 SBO SBO SBO Rm10 0 0

0 1 0 P U B W L Rn Rd immediate

0 1 1 P U B W L Rn Rd shift immediate shift 0

0

0

0

P

U

1

W

L

Rn

0

0

0

P

U

0

W

L

Rn

Rd

Rd

High offset 1 S H 1

SBZ 1 S H 1

000 1 0 B 0 0 Rn Rd 1 0 0 1SBZ Rm

1

0

0

P U S W L

1

1

1

0

op1

1

1

1

0

op1

1

1

0

P

U N W L Rn

1

0

1

L 24_bit_offset

1

1

1

1

Rn

CRn

L

CRn

CRd

Rd

CRd

Register list

cp_num

cp_num

cp_num

op2

op201

8_bit_offset

swi_number

shift

offset

store

link

cond

cond

cond

cond

cond

cond

cond

cond

cond

cond

cond

cond

cond

cond

cond

cond

cond

cond

cond

0 1 1 x 1x x x x x x x x x x x x x x x x x x x x x x xcond

Rm

Rm

Rm

Low offset

Rm

CRm

CRm

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

Figure 1-3 ARM instruction set formats

Note: Some instruction codes are not defined but do not cause the Undefined instruction

trap to be taken, for example, a multiply instruction with bit 6 set. You must not

use these instructions, because their action might change in future ARM

implementations.

ARM720T CORE CPU MANUAL EPSON 1-7

Page 28

1: Introduction

The ARM instruction set summary is shown in Table 1-2.

Table 1-2 ARM instructio n su mm ary

Operation Assembler

Move Move MOV{cond}{S} <Rd>, <Oprnd2>

Move NOT MVN{cond}{S} <Rd>, <Oprnd2>

Move SPSR to register MRS{cond} <Rd>, SPSR

Move CPSR to register MRS{cond} <Rd>, CPSR

Move register to SPSR MSR{cond} SPSR{field}, <Rm>

Move register to CPSR MSR{cond} CPSR{field}, <Rm>

Move immediate to SPSR flags MSR{cond} SPSR_f, #<32bit_Imm>

Move immediate to CPSR flags MSR{cond} CPSR_f, #<32bit_Imm>

Arithmetic Add ADD{cond}{S} <Rd>, <Rn>, <Oprnd2>

Add with carry ADC{cond}{S} <Rd>, <Rn>, <Oprnd2>

Subtract SUB{cond}{S} <Rd>, <Rn>, <Oprnd2>

Subtract with carry SBC{cond}{S} <Rd>, <Rn>, <Oprnd2>

Subtract reverse subtract RSB{cond}{S} <Rd>, <Rn>, <Oprnd2>

Subtract reverse subtract with carry RSC{cond}{S} <Rd>, <Rn>, <Oprnd2>

Multiply MUL{cond}{S} <Rd>, <Rm>, <Rs>

Multiply accumulate MLA{cond}{S} <Rd>, <Rm>, <Rs>, <Rn>

Multiply unsigned long UM UL L { c o n d } { S } <R d L o > , < R d H i>, <Rm>, < R s >

Multiply unsigned accumulate long UMLAL{cond}{S} <RdLo>, <RdHi>, <Rm>, <Rs>

Multiply signed long SMULL{cond}{S} <RdLo>, <RdHi>, <Rm>, <Rs>

Multiply signed accumulate long SMLAL{cond}{S} <RdLo>, <RdHi>, <Rm>, <Rs>

Compare CMP{cond} <Rd>, <Oprnd2>

Compare negative CMN{cond} <Rd>, <Oprnd2>

Logical Test TST{cond} <Rn>, <Oprnd2>

Test equivalence TEQ{cond} <Rn>, <Oprnd2>

AND AND{cond}{S} <Rd>, <Rn>, <Oprnd2>

EOR EOR{cond}{S} <Rd>, <Rn>, <Oprnd2>

ORR ORR{cond}{S} <Rd>, <Rn>, <Oprnd2>

Bit clear BIC{cond}{S} <Rd>, <Rn>, <Oprnd2>

Branch Branch B{cond} <label>

Branch with link BL{cond} <label>

Branch, and exchange instruction

set

1-8 EPSON ARM720T CORE CPU MANUAL

BX{cond} <Rn>

Page 29

Table 1-2 ARM instructio n su mm ary (continue d)

Operation Assembler

Load Word LDR{cond} <Rd>, <a_mode2>

Word with User Mode privilege LDR{cond}T <Rd>, <a_mode2P>

Byte LDR{cond}B <Rd>, <a_mode2>

Byte with User Mode privilege LDR{cond}BT <Rd>, <a_mode2P>

Byte signed LDR{cond}SB <Rd>, <a_mode3>

Halfword LDR{cond}H <Rd>, <a_mode3>

Halfword signed LDR{cond}SH <Rd>, <a_mode3>

1: Introduction

Multiple block

Increment before LDM{cond }IB <Rd>{!}, <reglist>{^}

data

operations

Increment after LDM{cond}IA <Rd>{!}, <reglist>{^}

Decrement before LDM{cond}DB <Rd>{!}, <reglist>{^}

Decrement after LDM{cond}DA <Rd>{!}, <reglist>{^}

Stack operations LDM{cond}<a_mode4L> <Rd>{!}, <reglist>

Stack operations, and restore

LDM{cond}<a_mode4L> <Rd>{!}, <reglist+pc>^

CPSR

User registers LDM{cond}<a_mode4L> <Rd>{!}, <reglist>^

Store Word STR{cond} <Rd>, <a_mode2>

Word with User Mode privilege STR{cond}T <Rd>, <a_mode2P>

Byte STR{cond}B <Rd>, <a_mode2>

Byte with User Mode privilege STR{cond}BT <Rd>, <a_mode2P>

Halfword STR{cond}H <Rd>, <a_mode3>

Multiple block

Increment before STM{cond }IB <Rd>{!}, <reglist>{^}

data

operations

Increment after STM{cond}IA <Rd>{!}, <reg lis t>{^}

Decrement before STM{cond}DB <Rd>{!}, <reglist>{^}

Decrement after STM{cond}DA <Rd>{!}, <reglist>{^}

Stack operations STM{cond}<a_mode4S> <Rd>{!}, <reglist>

User registers STM{cond}<a_mode4S> <Rd>{!}, <reglist>^

Swap Word SWP{cond} <Rd>, <Rm>, [<Rn>]

Byte SWP{cond}B <Rd>, <Rm>, [<Rn>]

ARM720T CORE CPU MANUAL EPSON 1-9

Page 30

1: Introduction

Table 1-2 ARM instruction summary (continued)

Operation Assembler

Coprocessors Data operations CDP{cond} p<cpnum>, <op1>, <CRd>, <CRn>,

<CRm>, <op2>

Move to ARM reg from coproc MRC{cond} p<cpnum>, <op1>, <Rd>, <CRn>,

<CRm>, <op2>

Move to coproc from ARM reg MCR{cond} p<cpnum>, <op1>, <Rd>, <CRn>,

<CRm>, <op2>

Load LDC{cond} p<cpnum>, <CRd>, <a_mode5>

Store STC{cond} p<cpn um>, <C Rd>, <a_mode5>

Software

Interrupt

SWI <24bit_Imm>

Addressing mode 2, <a_mode2>, is shown in Table 1-3.

Table 1-3 Addressing mode 2

Operation Assembler

Immediate offset [<Rn>, #+/-<12bit_Offset>]

Register offset [<Rn>, +/-<Rm>]

Scaled register offset [<Rn>, +/-<Rm>, LSL #<5bit_shift_imm>]

[<Rn>, +/-<Rm>, LSR #<5bit_shift_imm>]

[<Rn>, +/-<Rm>, ASR #<5bit_shift_imm>]

[<Rn>, +/-<Rm>, ROR #<5bit_shift_imm>]

[<Rn>, +/-<Rm>, RRX]

Pre-indexed immediate offset [<Rn>, #+/-<12bit_Offset>]!

Pre-indexed register offset [<Rn>, +/-<Rm>]!

Pre-indexed scaled register offset [<Rn>, +/-<Rm>, LSL #<5bit_shift_imm>]!

[<Rn>, +/-<Rm>, LSR #<5bit_shift_imm>]!

[<Rn>, +/-<Rm>, ASR #<5bit_shift_imm>]!

[<Rn>, +/-<Rm>, ROR #<5bit_shift_imm>]!

[<Rn>, +/-<Rm>, RRX]!

Post-indexed immediate offset [<Rn>], #+/-<12bit_Offset>

Post-indexed register offset [<Rn>], +/-<Rm>

Post-indexed scaled register offset [<Rn>], +/-<Rm>, LSL #<5bit_shift_imm>

[<Rn>], +/-<Rm>, LSR #<5bit_shift_imm>

[<Rn>], +/-<Rm>, ASR #<5bit_shift_imm>

[<Rn>], +/-<Rm>, ROR #<5bit_shift_imm>

[<Rn>, +/-<Rm>, RRX]

1-10 EPSON ARM720T CORE CPU MANUAL

Page 31

Addressing mode 2 (privileged), <a_mode2P>, is shown in Table 1-4.

Table 1-4 Addressing mode 2 (privileged)

Operation Assembler

Immediate offset [<Rn>, #+/-<12bit_Offset>]

Register offset [<Rn>, +/-<Rm>]

Scaled register offset [<Rn>, +/-<Rm>, LSL #<5bit_shift_imm>]

[<Rn>, +/-<Rm>, LSR #<5bit_shift_imm>]

[<Rn>, +/-<Rm>, ASR #<5bit_shift_imm>]

[<Rn>, +/-<Rm>, ROR #<5bit_shift_imm>]

[<Rn>, +/-<Rm>, RRX]

Post-indexed immediate offset [<Rn>], #+/-<12bit_Offset>

Post-indexed register offset [<Rn>], +/-<Rm>

Post-indexed scaled register offset [<Rn>], +/-<Rm>, LSL #<5bit_shift_imm>

1: Introduction

[<Rn>], +/-<Rm>, LSR #<5bit_shift_imm>

[<Rn>], +/-<Rm>, ASR #<5bit_shift_imm>

[<Rn>], +/-<Rm>, ROR #<5bit_shift_imm>

[<Rn>, +/-<Rm>, RRX]

Addressing mode 3 (signed byte, and halfword data transfer), <a_mode3>, is shown in

Table 1-5.

Table 1-5 Addressing mode 3

Operation Assembler

Immediate offset [<Rn>, #+/-<8bit_Offset>]

Pre-indexed [<Rn>, #+/-<8bit_Offset>]!

Post-indexed [<Rn>], #+/-<8bit_Offset>

Register [<Rn>, +/-<Rm>]

Pre-indexed [<Rn>, +/-<Rm>]!

Post-indexed [<Rn>], +/-<Rm>

Addressing mode 4 (load), <a_mode4L>, is shown in Table 1-6.

Table 1-6 Addressing mode 4 (load)

Addressing mode Stack type

IA Increment afte r FD Full descending

IB Increment before ED Empty descending

DA Decrement after FA Full ascending

DB Decrement before EA Empty ascending

ARM720T CORE CPU MANUAL EPSON 1-11

Page 32

1: Introduction

Addressing mode 4 (store), <a_mode4S>, is shown in Table 1-7.

Table 1-7 Addressing mode 4 (store)

Addressing mode Stack type

IA Increment after EA Empty ascending

IB Increment before FA Full ascending

DA Decrement after ED Empty descending

DB Decrement before FD Full descending

Addressing mode 5 (coprocessor data transfer), <a_mode5>, is shown in Table 1-8.

Table 1-8 Addressing mode 5

Operation Assembler

Immediate offset [<Rn>, #+/-<8bit_Offset*4>]

Pre-indexed [<Rn>, #+/-<8bit_Offset*4>]!

Post-indexed [<Rn>], #+/-<8bit_Offset*4>

Operand 2, <Oprnd2>, is shown in Table 1-9.

Table 1-9 Operand 2

Operation Assembler

Immediate value #<32bit_Imm>

Logical shift left <Rm> LSL #<5bit_Imm>

Logical shift right <Rm> LSR #<5bit_Imm>

Arithmetic shift right <Rm> ASR #<5bit_Imm>

Rotate right <Rm> ROR #<5bit_Imm>

Register <Rm>

Logical shift left <Rm> LSL <Rs>

Logical shift right <Rm> LSR <Rs>

Arithmetic shift right <Rm> ASR <Rs>

Rotate right <Rm> ROR <Rs>

Rotate right extended <Rm> RRX

Fields, {field}, are shown in Table 1-10.

Table 1-10 Fields

Suffix Sets

_c Control field mask bit (bit 3)

_f Flags field mask bit (bit 0)

_s Status field mask bit (bit 1)

_x Extension field mask bit (bit 2)

1-12 EPSON ARM720T CORE CPU MANUAL

Page 33

Condition fields, {cond}, are shown in Table 1-11.

Table 1-11 Condition fields

Suffix Description Condition(s)

EQ Equal Z set

NE Not equal Z clear

CS Unsigned higher, or same C set

CC Unsig ned lower C clear

MI Negative N set

PL Positive, or zero N clear

VS Overflow V set

VC No overflow V clear

HI Unsigned higher C set, Z clear

LS Unsigned lower, or same C clear, Z set

1: Introduction

GE Greater, or equal N=V (N and V set or N and V clear)

LT Less than N<>V (N set and V clear) or (N clear and V set)

GT Greater than Z clear, N=V (N and V set or N and V clear)

LE Less than, or equal Z set or N<>V (N set and V clear) or (N clear and V set)

AL Always Always

ARM720T CORE CPU MANUAL EPSON 1-13

Page 34

1: Introduction

1.3.3 Thumb instruction set

This section gives an overview of the Thumb instructions available. For full details of these

instructions, see the

The Thumb instruction set formats are shown in Figure 1-4.

ARM Architecture Reference Manual

15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

.

Move shifted register

Add and subtract

Move, compare, add, and subtract

immediate

ALU operation

High register operations and branch

exchange

PC-relative load

Load and store with relative offset

Load and store sign-extended byte and

halfword

Load and store with immediate offset

Load and store halfword

SP-relative load and store

Load address

Add offset to stack pointer

02

0 0 1

03

0 1 0 0 0 0

04

05

0 1 0 0 1

06

0 1 0

07

08

09

10

11

12

13

RdOp

Rd

Rd Word81 L1 0 0

Rd Word80 SP1 0 1

Offset5 RdRsOp00001

Op

Offset5B L0 1 1

Rn/

offset3

Op

H1 H2

Ro1 L B 0

Offset8

Word8

Rb

Rb RdOffset50 L1 0 0

SWord70 0 0 S1 1 01 0

RdRsOp000 111

RdRs

RdHdRs/Hs0 1 0 0 0 1

RdRb

RdRbRo1 H S 10 1 0

Rd

Push and pop registers

Multiple load and store

Conditional branch

Software interrupt

Unconditional branch

Long branch with link OffsetH1 1 11

14

15

16

17

18

19

15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

Figure 1-4 Thumb instruction set formats

Rlist1 0 R1 1 L1 0

RlistRb0 0 L1 1

Softset8Cond0 11 1

Value81 1 1 11 0 11

Offset1101 1 01

1-14 EPSON ARM720T CORE CPU MANUAL

Page 35

The Thumb instruction set summary is shown in Table 1-12.

Table 1-12 Thumb instruction summary

Operation Assembler

Move Immediate MOV <Rd>, #<8bit_Imm>

High to Low MOV <Rd>, <Hs>

Low to High MOV <Hd>, <Rs>

High to High MOV <Hd>, <Hs>

Arithmetic Add ADD <Rd>, <Rs>, #<3bit_Imm>

Add Low, and Low ADD <Rd>, <Rs>, <Rn>

Add High to Low ADD <Rd>, <Hs>

Add Low to High ADD <Hd>, <Rs>

Add High to High ADD <Hd>, <Hs>

Add Immediate ADD <Rd>, #<8bit_Imm>

1: Introduction

Add Value to SP ADD SP, #<7bit_Imm>

ADD SP, #-<7bit_Imm>

Add with carry ADC <Rd>, <Rs>

Subtract SUB <Rd>, <Rs>, <Rn>

SUB <Rd>, <Rs>, #<3bit_Imm>

Subtract Immediate SUB <Rd>, #<8bit_Imm>

Subtract with carry SBC <Rd>, <Rs>

Negate NEG <Rd>, <Rs>

Multiply MUL <Rd>, <Rs>

Compare Low, and Low CMP <Rd>, <Rs>

Compare Low, and High CMP <Rd>, <Hs>

Compare High, and Low CMP <Hd>, <Rs>

Compare High, and High CMP <Hd>, <Hs>

Compare Negative CMN <Rd>, <Rs>

Compare Immediate CMP <Rd>, #<8bit_Imm>

Logical AND AND <Rd>, <Rs>

EOR EOR <Rd>, <Rs>

OR ORR <Rd>, <Rs>

Bit clear BIC <Rd>, <Rs>

Move NOT MVN <Rd>, <Rs>

Test bits TST <Rd>, <Rs>

ARM720T CORE CPU MANUAL EPSON 1-15

Page 36

1: Introduction

Table 1-12 Thumb instruction summary (continued)

Operation Assembler

Shift/Rotate Logical shift left LSL <Rd>, <Rs>, #<5bit_shift_imm> LSL

<Rd>, <Rs>

Logical shift right LSR <Rd>, <Rs>, #<5bit_shift_imm> LSR

<Rd>, <Rs>

Arithmetic shift right ASR <Rd>, <Rs>, #<5bit_shift_i mm> ASR

<Rd>, <Rs>

Rotate right ROR <Rd>, <Rs>

Branch Conditional

if Z set BEQ <label>

if Z clear BNE <label>

if C set BCS <label>

if C clear BCC <label>

if N set BMI <label>

if N clear BPL <label>

if V set BVS <label>

if V clear BVC <label>

if C set, and Z clear BHI <label>

if C clear, and Z set BLS <label>

if N set, and V set, or if N

BGE <label>

clear, and V clear

if N set, and V clear, or if

BLT <label>

N clear, and V set

if Z clear, and N, or V set,

BGT <label>

or if Z clear, and N, or V

clear

if Z set, or N set, and V

BLE <label>

clear, or N clear, and V

set

Unconditional B <label>

Long branch with link BL <label>

Optional state change

to address held in Lo reg BX <Rs>

to address held in Hi reg BX <Hs>

Load With immediate offset

word LDR <Rd>, [<Rb>, #<7bit_offset>]

halfword LDRH <Rd>, [<Rb>, #<6bit_offset>]

byte LDRB <Rd>, [<Rb>, #<5bit_offset>]

1-16 EPSON ARM720T CORE CPU MANUAL

Page 37

Table 1-12 Thumb instruction summary (continued)

Operation Assembler

Load With register offset

word LDR <Rd>, [<Rb>, <Ro>]

halfword LDRH <Rd>, [<Rb>, <Ro>]

signed halfword LDRSH <Rd>, [<Rb>, <Ro>]

byte LDRB <Rd>, [<Rb>, <Ro>]

signed byte LDRSB <Rd>, [<Rb>, <Ro>]

PC-relative LDR <Rd>, [PC, #<10bit_offset>]

SP-relative LDR <Rd> , [SP, #<10bit_offset>]

Address

using PC ADD <Rd>, PC, #<10bit_ offset>

using SP ADD <Rd>, SP, #<10bit_offset>

1: Introduction

Multiple LDMIA Rb!, <reglist>

Store With immediate offset

word STR <Rd>, [<Rb>, #<7bit_offset>]

halfword STRH <Rd>, [<Rb>, #<6bit_offset>]

byte STRB <Rd>, [<Rb>, #<5bit_offset>]

With register offset

word STR <Rd>, [<Rb>, <Ro>]

halfword STRH <Rd>, [<Rb>, <Ro>]

byte STRB <Rd>, [<Rb>, <Ro>]

SP-relative STR <Rd>, [SP, #<10bit_offset>]

Multiple STMIA <Rb>!, <reglist>

Push/Pop Push registers onto stack PUSH <re glist>

Push LR, and registers

onto stack

Pop registers from stack POP <reglist>

PUSH <reglist, LR>

Pop registers, and PC

from stack

Software

Interrupt

Note: All thumb fetches are done as 32-bit bus transactions using the 32-bit thumb

POP <reglist, PC>

SWI <8bit_Imm>

prefetch buffer.

ARM720T CORE CPU MANUAL EPSON 1-17

Page 38

1: Introduction

1.4 Silicon revisions

This manual is for revision r4p2 of the ARM720T macrocell. See

page xii for details of revision numbering. There are no functional differences from previous

revisions.

Product revision status

on

1-18 EPSON ARM720T CORE CPU MANUAL

Page 39

2

Programmer’s Model

Page 40

Page 41

2: Programmer’s Model

2 Programmer’ s Model

This chapter describes the programmer’s model for the ARM720T processor. It contains the

following sections:

2.1 Processor operating states......................................................................... 2-1

2.2 Memory formats......................................................................................... 2-2

2.3 Instruction length ........................... ..... .... .... .... .... ..... .... .... .... .... ..... .... .... .... 2-3

2.4 Data types................................................................................................... 2-3

2.5 Operating modes .................................................. ..... .... .... .... .... ..... .... .... .... 2-4

2.6 Registers..................................................................................................... 2-4

2.7 Program status registers ........................................................................... 2-8

2.8 Exceptions................................................................................................. 2-10

2.9 Relocation of low virtual addresses by the FCSE PID........................... 2-15

2.10 Reset.......................................................................................................... 2-16

2.11 Implementation-defined behavior of instructions.................................. 2-17

2.1 Processor operating states

From the point of view of the programmer , the ARM720T processor can be in one of two states:

ARM state This executes 32-bit, word-aligned ARM instructions.

Thumb state This operates with 16-bit, halfword-aligned Thumb instructions. In

this state, the PC uses bit 1 to select between alternate halfwords.

2.1.1 Switching between processor states

Transition between processor states does not affect the processor mode or the contents of the

registers.

Entering Thumb state

Entry into Thumb state can be achieved by executing a BX instruction with the state bit (bit

0) set in the operand register.

T ransition to Thumb state also occurs automatically on return from an exception, for example,

Interrupt ReQuest

Interrupt

Entering ARM state

Entry into ARM state happens:

(SWI) if the exception was entered with the processor in Thumb state.

(IRQ),

Fast Interrupt reQuest

(FIQ), UNDEF, ABORT, and

SoftWare

• On execution of the BX instruction with the state bit clear in the operand register.

• On the processor taking an exception, for example, IRQ, FIQ, RESET, UNDEF,

ABORT, and SWI. In this case, the PC is placed in the link register of the exception

mode, and execution starts at the vector address of the exception.

ARM720T CORE CPU MANUAL EPSON 2-1

Page 42

2: Programmer’s Model

2.2 Memory formats

The ARM720T processor views memory as a linear collection of bytes numbered upwards from

zero, as follows:

Bytes 0 to 3 Hold the first stored word.

Bytes 4 to 7 Hold the second stored word.

Bytes 8 to 11 Hold the third stored word.

Words are stored in memory as big or little-endian, as described in the following sections:

Big-endian format

•

•

Little-endian format

The endianness used depends on the status of the B bit in the Control Register of the system

control coprocessor. See

Control Register

2.2.1 Big-endian format

In big-endian format, the most significant byte of a word is store d at the lowest numbered byte

and the least significant byte at the highest numbered byte. Byte 0 of the memory system is

therefore connected to data lines 31 to 24.

on page 2-3.

on page 3-4 for more information.

Big-endian format is shown in Figure 2-1.

Higher address

Lower address

31 24 23

8

4

0 1 2 3

16 15 8 7 0

9

5

10

6

11

7

Figure 2-1 Big-endian addresses of bytes with words

Note:

• Most significant byte is at lowest address

• Word is addressed by byte address of most significant byte.

Word

address

8

4

0

2-2 EPSON ARM720T CORE CPU MANUAL

Page 43

2: Programmer’s Model

2.2.2 Little-endian format

In little-endian format, the lowest numbered byte in a word is considered the least significant

byte of the word, and the highest numbered byte the most significant. Byte 0 of the memory

system is therefore connected to data lines 7 to 0.

Little-endian format is shown in Figure 2-2.

Higher address

Lower address

31 24 23

11

7

3 2 1 0

16 15 8 7 0

10

6

9

5

8

4

Figure 2-2 Little-endian addresses of bytes with words

Note:

• Least significant byte is at lowest address

• Word is addressed by byte address of least significant byte.

2.3 Instruction length

Instructions are:

• 32 bits long in ARM state

• 16 bits long in Thumb state.

2.4 Data types

Word

address

8

4

0

The ARM720T processor supports the following data types:

•byte (8-bit)

• halfword (16-bit)

• word (32-bit).

You must align these as follows:

• word quantities to 4-byte boundaries

• halfwords quantities to 2-byte boundaries

• byte quantities can be placed on any byte boundary.

ARM720T CORE CPU MANUAL EPSON 2-3

Page 44

2: Programmer’s Model

2.5 Operating modes

The ARM720T processor supports seven modes of operation, as shown in Table 2-1.

Table 2-1 ARM720T modes of operation

Mode Type Description

User usr The normal ARM program execution mode

FIQ fiq Used for most performance-critical interrupts in a system

IRQ irq Used for general-purpose interrupt handling

Supervisor svc Protected mode for the operating system

Abort mode abt Entered after a Data Abort or instruction Prefetch Abort

System sys A privileged User mode for the operating system

Undefined und Entered when an Undefined Instruction is executed

2.5.1 Changing operating modes

Mode changes can be made under software control, by external interrupts or during exception

processing. Most application programs execute in User mode. The non-User modes, known as

privileged modes, are entered in order to service interrupts or exceptions, or to access

protected resources.

2.6 Registers

The ARM720T processor has a total of 37 registers:

• 31 general-purpose 32-bit registers

• six program status registers.

These registers cannot all be seen at once. The processor state and operating mode dictate

which registers are available to the programmer at any one time.

2.6.1 The ARM state register set

In ARM state, 16 general registers and one or two status registers are visible at any one time.

In privileged (non-User) modes, mode-specific banked registers are switched in. Figure 2-3 on

page 2-5 shows which registers are available in each mode. The banked registers are marked

with a shaded triangle.

The ARM state register set contains 16 directly accessible registers, r0 to r15. All of these,

except r15, are general-purpose, and can be used to hold either data or address values.

Registers r14 and r15 also have special roles, as follows:

Register r14 This register is used as the subroutine Link Register . This receives

a copy of r15 when a

executed. At all other times it can be treated as a general-purpose

register. The corresponding banked registers r14_svc, r14_irq,

r14_fiq, r14_abt, and r14_und are similarly used to hold the return

values of r15 when interrupts and exceptions arise, or when BL

instructions are executed within interrupt or exception routines.

Register r15 This register holds the

[1:0] of r15 are zero and bits [31:2] contain the PC. In Thumb state,

bit 0 is zero and bits [31:1] contain the PC.

In addition to these, the

information. It contains condition code flags and the current mode bits.

2-4 EPSON ARM720T CORE CPU MANUAL

Current Program Status Register

Branch and Link

Program Counter

(CPSR) is used to store status

(BL) code instruction is

(PC). In ARM state, bits

Page 45

2: Programmer’s Model

Interrupt modes

FIQ mode has seven banked registers mapped to r8-14 (r8_fiq-r14_fiq). In ARM state, many

FIQ handlers can use these banked registers to avoid having to save any registers onto a stack.

User , IRQ, Supe rvisor, Abort, and Undefined modes each have two banked registers, mapped

to r13 and r14, enabling each of these modes to have a private stack pointer and link registers.

ARM state general registers and program counter

System and User

r0

r1

r2

r3

r4

r5

r6

r7

r8

r9

r10

r11

r12

r13

r14

r15 (PC)

FIQ

r0

r1

r2

r3

r4

r5

r6

r7

r8_fiq

r9_fiq

r10_fiq

r11_fiq

r12_fiq

r13_fiq

r14_fiq

r15 (PC)

Supervisor

r0

r1

r2

r3

r4

r5

r6

r7

r8

r9

r10

r11

r12

r13_svc

r14_svc

r15 (PC)

Abort

r0

r1

r2

r3

r4

r5

r6

r7

r8

r9

r10

r11

r12

r13_abt

r14_abt

r15 (PC)

ARM state program status registers

IRQ

r0

r1

r2

r3

r4

r5

r6

r7

r8

r9

r10

r11

r12

r13_irq

r14_irq

r15 (PC)

Undefined

r0

r1

r2

r3

r4

r5

r6

r7

r8

r9

r10

r11

r12

r13_und

r14_und

r15 (PC)

CPSR CPSR

SPSR_fiq

= banked register

CPSR

SPSR_svc

CPSR

SPSR_abt

Figure 2-3 Register organization in ARM state

CPSR

SPSR_irq

CPSR

SPSR_und

ARM720T CORE CPU MANUAL EPSON 2-5

Page 46

2: Programmer’s Model

2.6.2 The Thumb state register set

The Thumb state register set is a subset of the ARM state set. You have direct access to:

• eight general registers, (r0–r7)

•the PC

•a

•a

Stack Pointer

Link Register

(SP)

(LR)

register

•the CPSR.

There are banked SPs, LRs, and

Saved Program Status Registers

mode. This is shown in Figure 2-4.

Thumb state general registers and program counter

System and User

r0

r1

r2

r3

r4

r5

r6

r7

SP

LR

PC

FIQ

r0

r1

r2

r3

r4

r5

r6

r7

SP_fiq

LR_fiq

PC

Supervisor

r0

r1

r2

r3

r4

r5

r6

r7

SP_svc

LR_svc

PC

Abort

r0

r1

r2

r3

r4

r5

r6

r7

SP_abt

LR_abt

PC

(SPSRs) for each privileged

IRQ

r0

r1

r2

r3

r4

r5

r6

r7

SP_irq

LR_irq

PC

Undefined

r0

r1

r2

r3

r4

r5

r6

r7

SP_und

LR_und

PC

CPSR CPSR

SPSR_fiq

= banked register

Figure 2-4 Register organization in Thumb state

Thumb state program status registers

CPSR

SPSR_svc

CPSR

SPSR_abt

CPSR

SPSR_irq

CPSR

SPSR_und