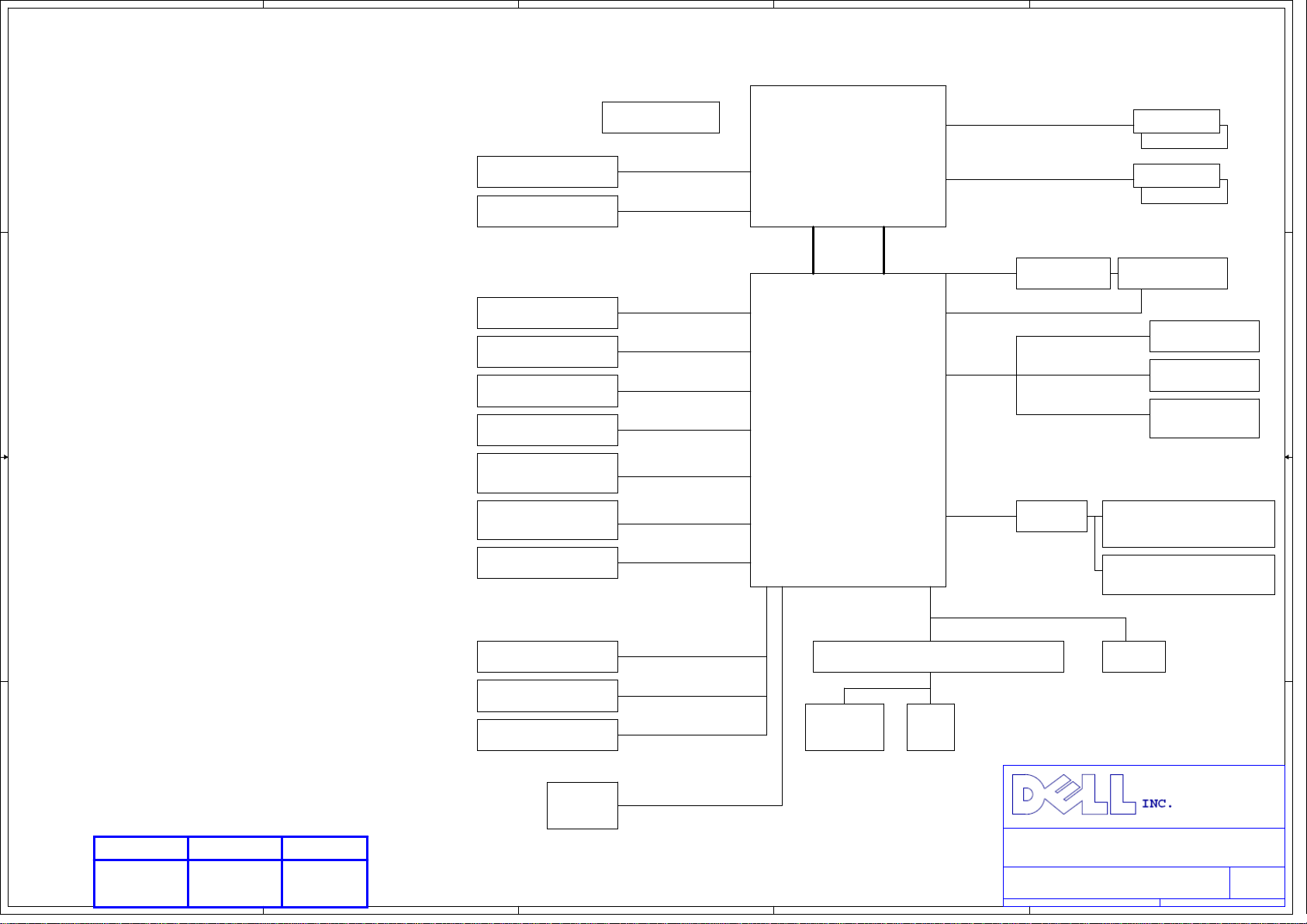

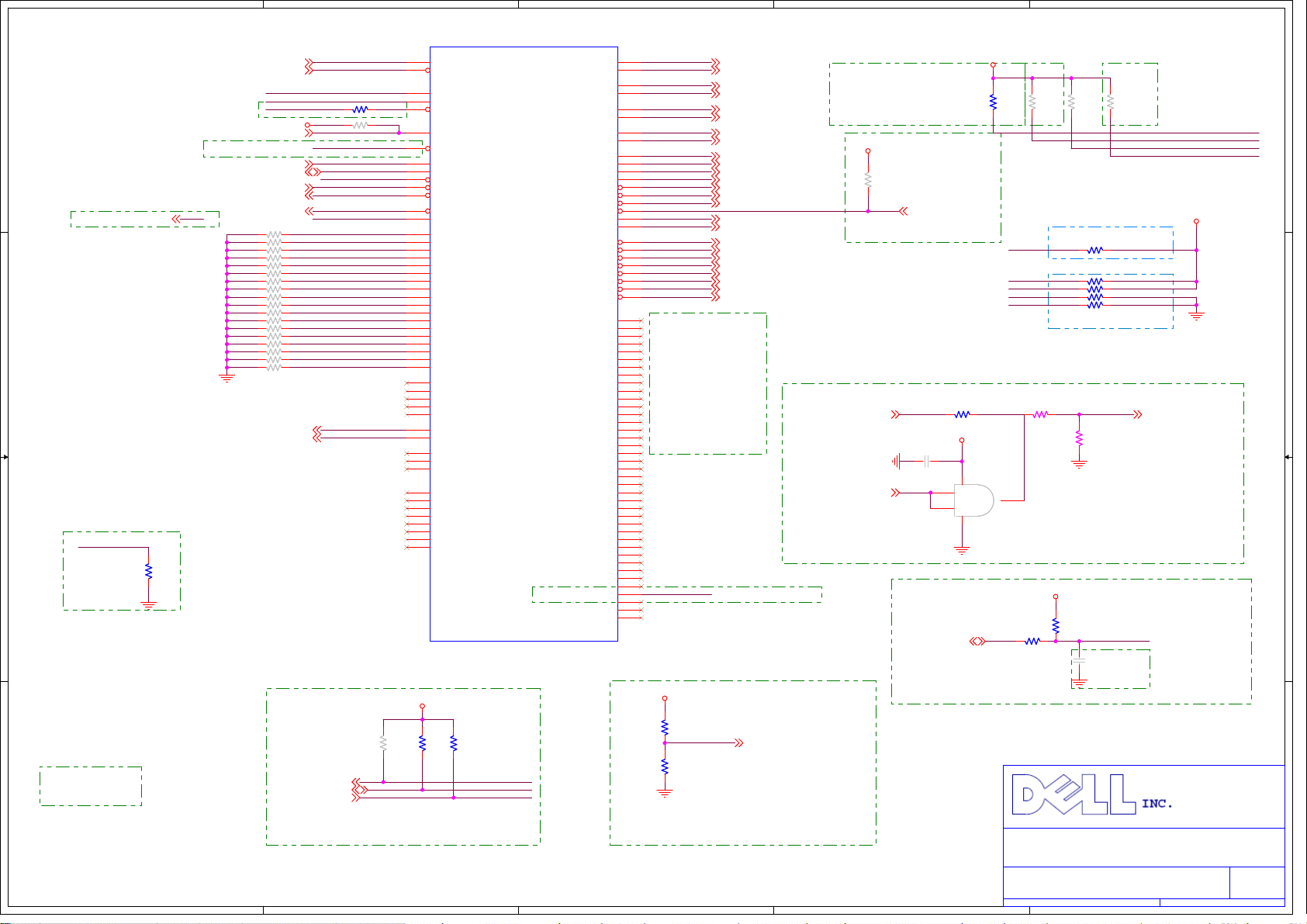

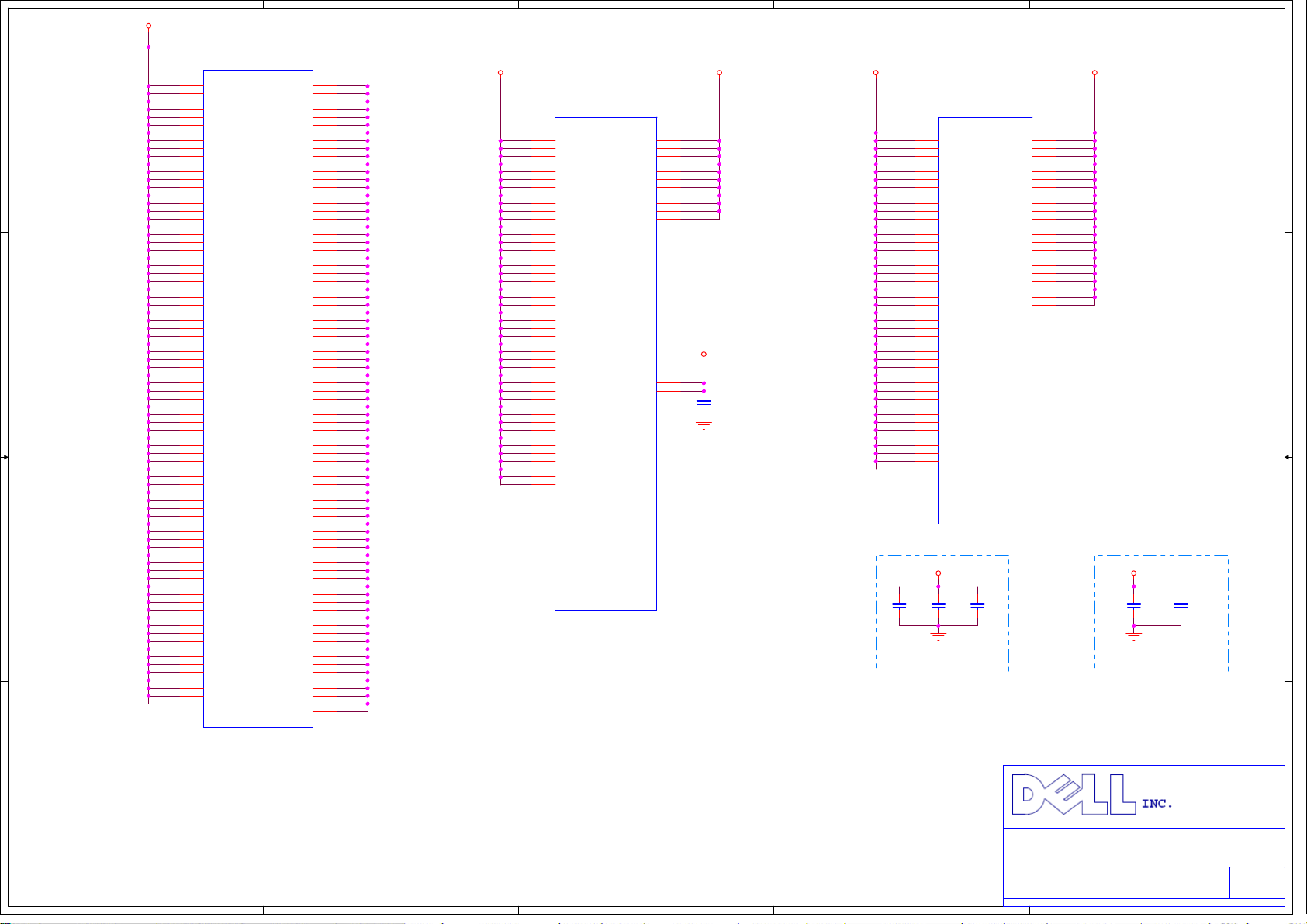

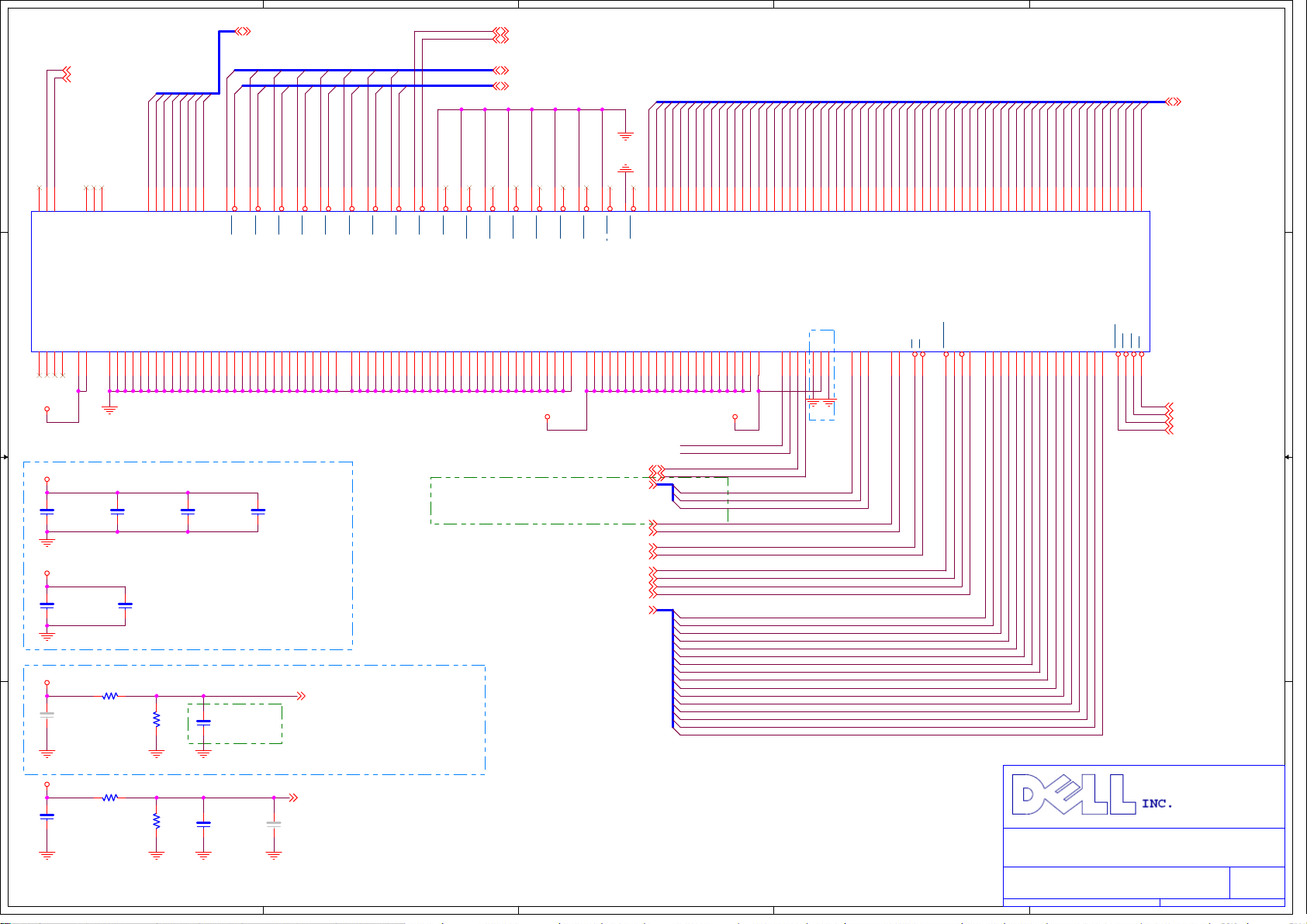

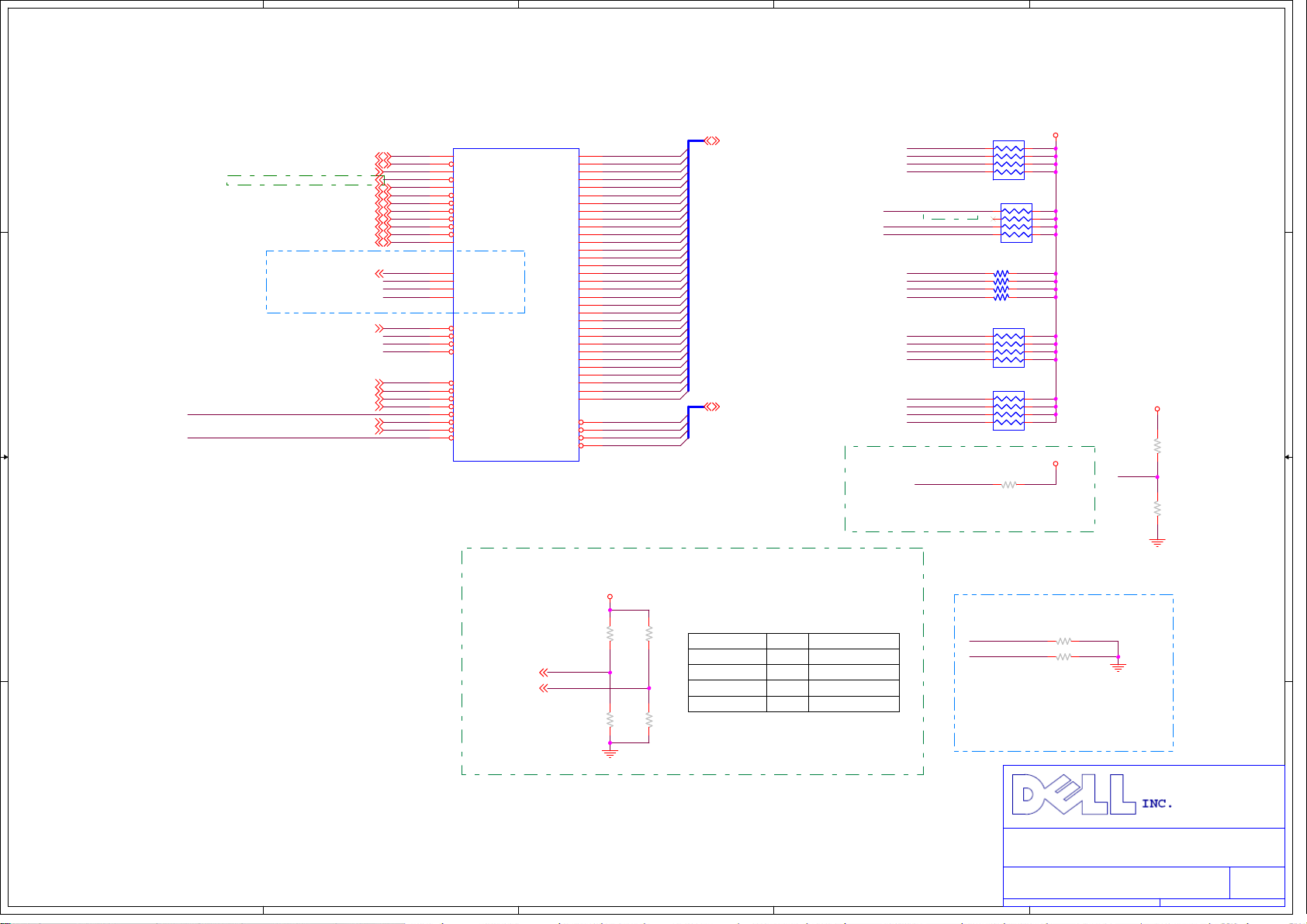

Dell OPTIPLEX 7010 Schematics

5

4

3

2

1

Lainikai - MT / DT

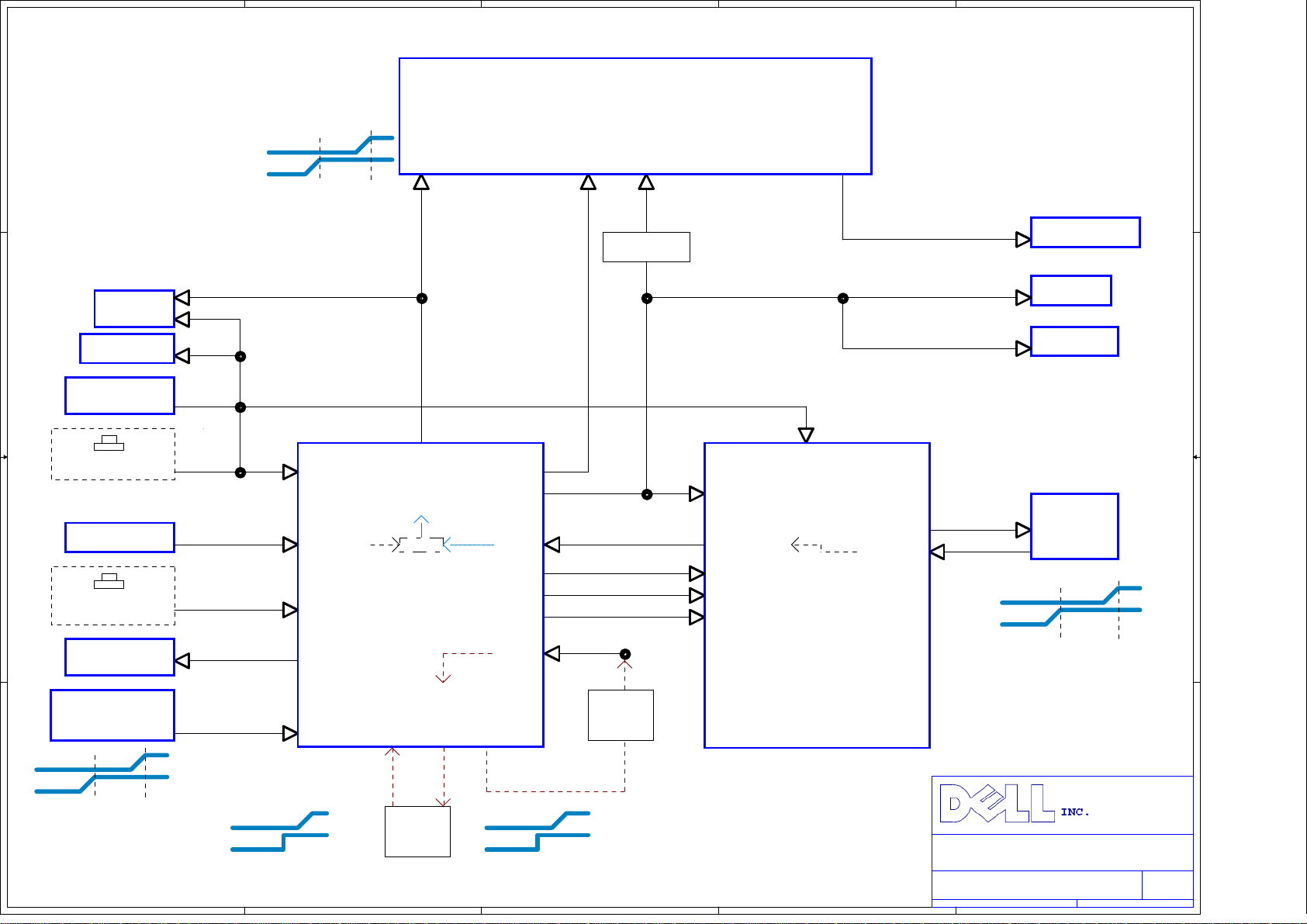

1. Index / Block diagram

2. SMBus MAP

3. Clock Distribution

D D

4. Power Delivery Map

5. Power On Sequence

6. Reset / Power Good Map

7. Strap/IRQ/IDSel Table

8. GPIO Table

XDP

9-14. CPU

15-16. DDR3 Conn: CHA

PCIe 16x slot X1

17-18. DDR3 Conn: CHB

19. TBD

20. TBD

21-30. PCH

31. PCH MISC Conn/BUZ/ID

32-33. SIO:SMSC5544

34-35. LAN: INTEL LEWISVILLE

DISPLAY PORT

36-37 AUDIO:ALC269Q

C C

38. Slot1: PCIe 16x

DISPLAY PORT

39. Slot4: PCIe 4x

40. Display Port 1

41. Display Port 2

VGA CONN

42. VGA Conn

43. SATA Conn

PCI Slot X1

44. TBD

45. Rear USB

46. TPM & TCM

47. Thermal Sensor Conn

48. FAN

49. PS2 Conn

PCIe 16x Slot X1

(wired as 4x signal)

PCIe 1x Slot X1

50. COM1

51. SPI

B B

52. XDP

53. Pilot Run Conn

XDP

54. EMI

55. COM2 HDR

56. Front_Panel

57. Front USB 3.0

58. Slot3: PCI

SATA 3.0 CONN X2

59. Slot2: PCIe 1x

60. SATA_MT

SATA 2.0 CONN X1

61. Flexbay USB

62. TBD

63. Power Conn

SATA 2.0 CONN X1

64. Power Sequence

65-66. Power: Linear Power

A A

67-68. Power: Vcore PWM

69-70. Power: VCCIO/VCCSA

71. Power: DDR3/5Vdual/5VUSB

DESIGN APPROVECHECK

Hiko

5

IvanHiko

4

(MT)

SPI ROM

2M+8M

Page 65 ~ 70

VRD12 / VRM / Linear

Page 52

PCIe Gen3 16x

Page 38

DP Link

Page 40

DP Link

Page 41

VGA

Page 42

PCI

Page 58

PCIe Gen2 4x

Page 39

PCIe Gen2 1x

Page 59

Page 52

SATA Port 0/1

Page 43

SATA Port 2

Page 43

SATA Port 3

Page 60

SPI

Page 51

3

Intel PROCESSOR

IVY BRIDGE

LGA1155

Page 9-14

FDI

DMI

Intel

PANTHER Point

Page 21-30

SMSC5545

2

PS2

KB/MS

SERIAL

Port

Page 50 Page 49

CHANNEL A DDR3 SDRAM (1333/1600)

Page 15, 16

CHANNEL B DDR3 SDRAM (1333/1600)

Page 17, 18

PCIe 1x

Page 34

USB

HDA

Page 36

LPC

Page 32

Intel

Lewisville

Port 8/9

Port 2 ~ 5

Page 45

Port 0/1/10/11

Page 56

Port 12/13

Page 61

ALC269Q

(TCM is just reserved because

MRD has removed TCM requirement)

Title

Title

Title

Index / Block diagram

Index / Block diagram

DWG NO Rev

DWG NO Rev

DWG NO Rev

Date: Sheet

Date: Sheet of

Date: Sheet of

Index / Block diagram

Lanikai _MT/DT

Lanikai _MT/DT

Lanikai _MT/DT

DDR3 DIMM 1

DDR3 DIMM 3

DDR3 DIMM 2

DDR3 DIMM 4

Page 35

NIC + USB

Ports X 2

Rear USB Ports

2.0x2 3.0x2

Front USB Ports

2.0x2 3.0x2

Internal USB

Header X1

Page 37

Rear Audio CONN

Line In (MIC In)/Line Out

Front Audio CONN

HP Out/ MIC In

Page 56

TPM/TCM

Page 46

of

171Wednesday, June 13, 2012

171Wednesday, June 13, 2012

171Wednesday, June 13, 2012

1

A00

A00

A00

5

4

3

2

1

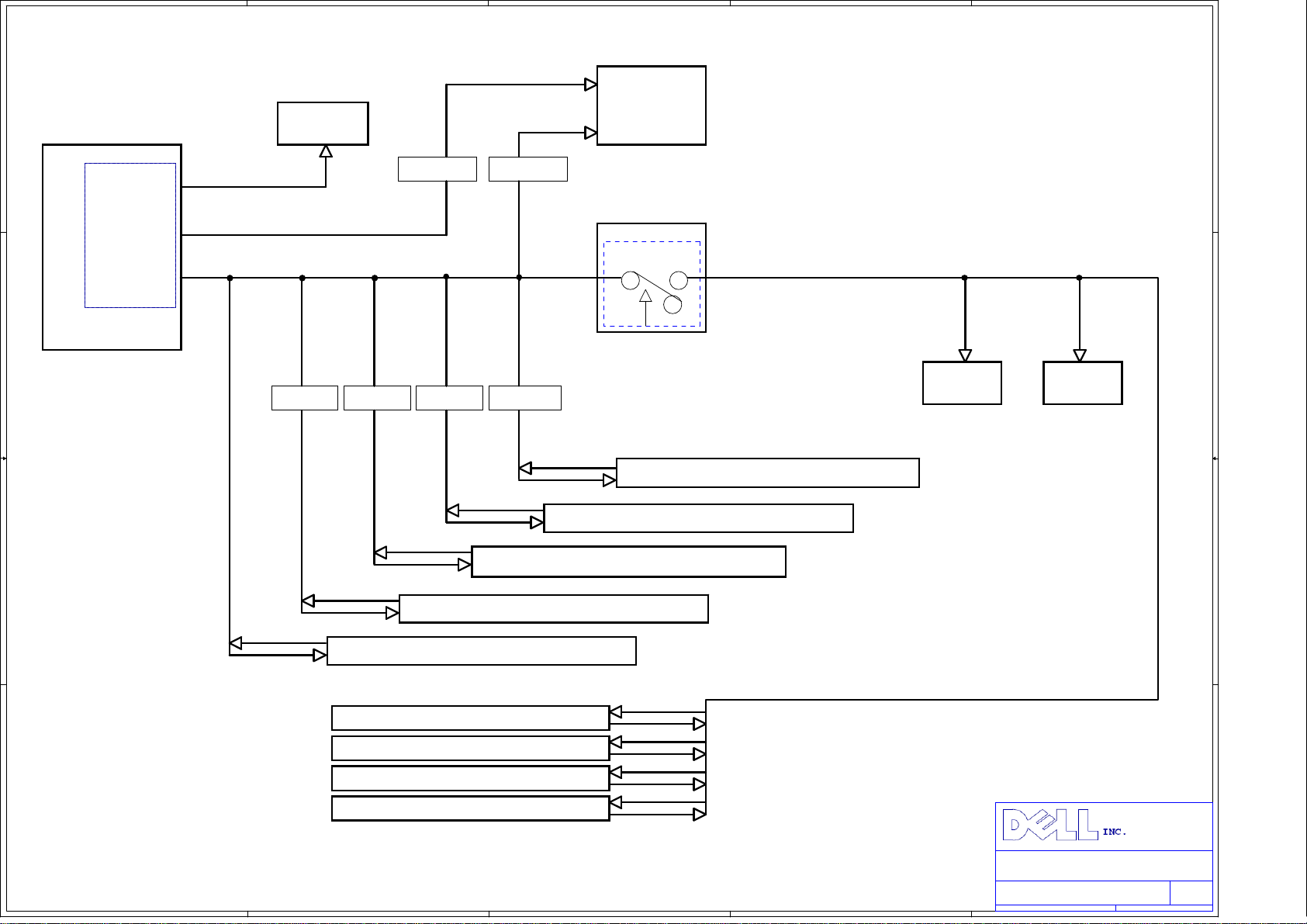

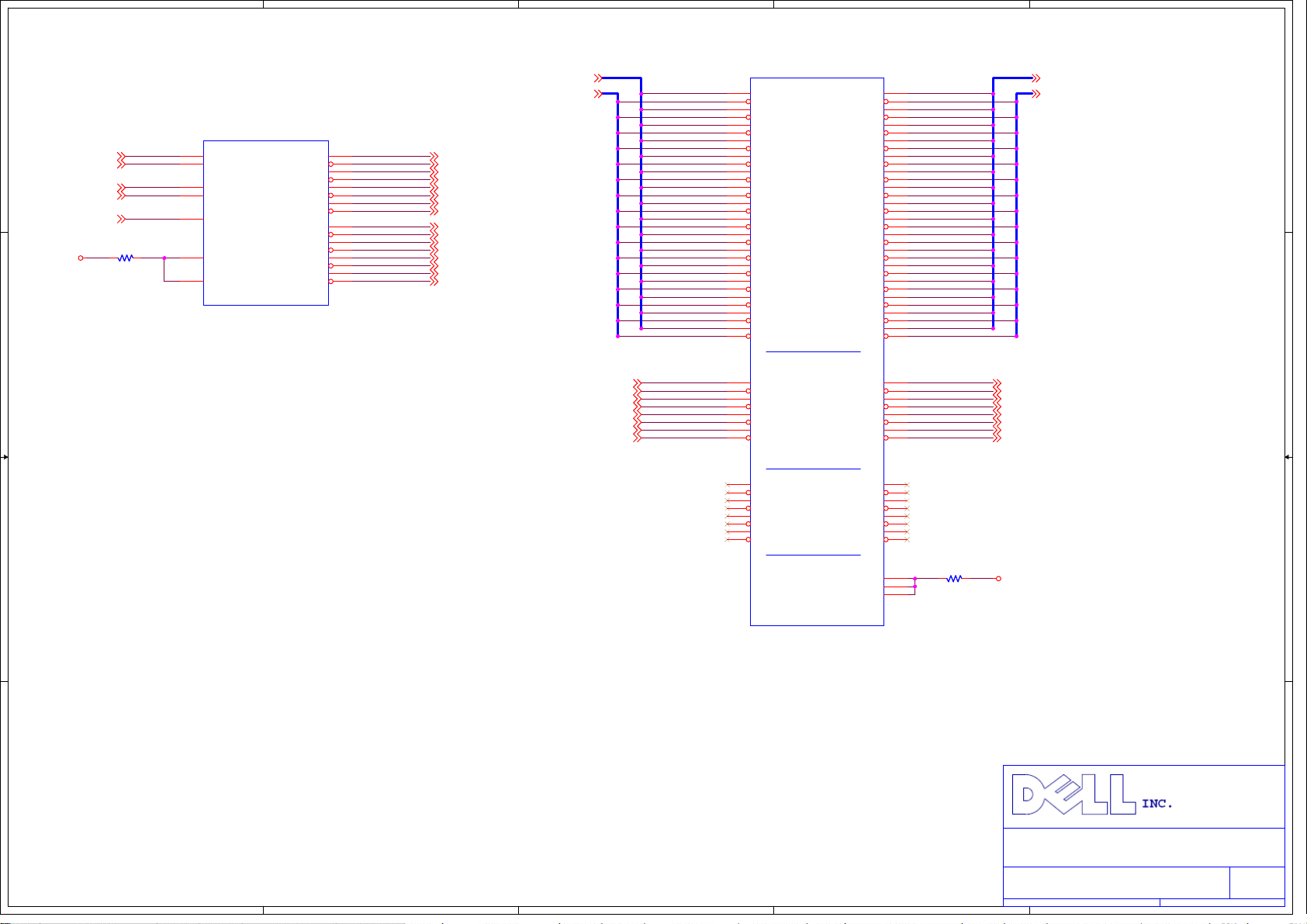

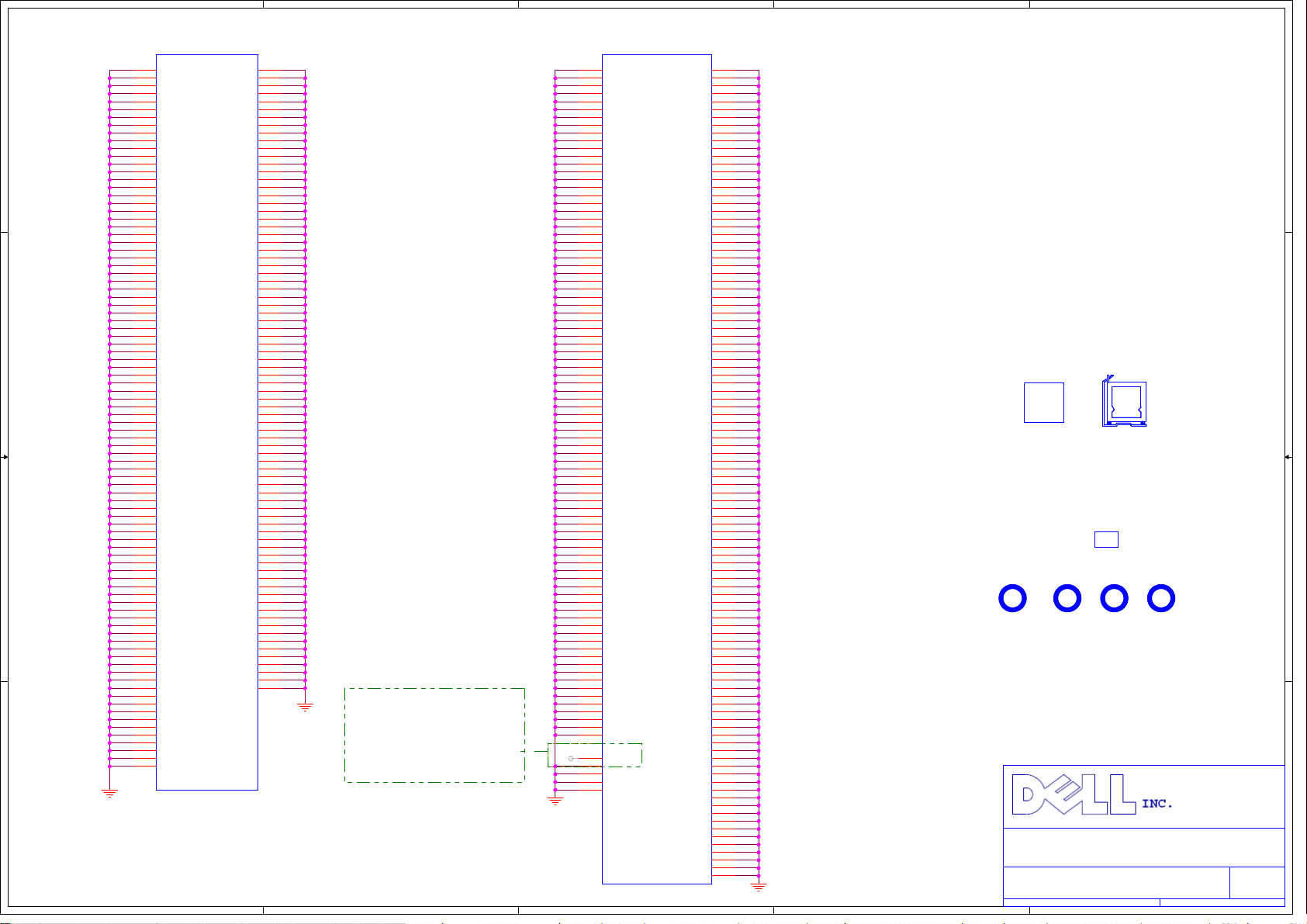

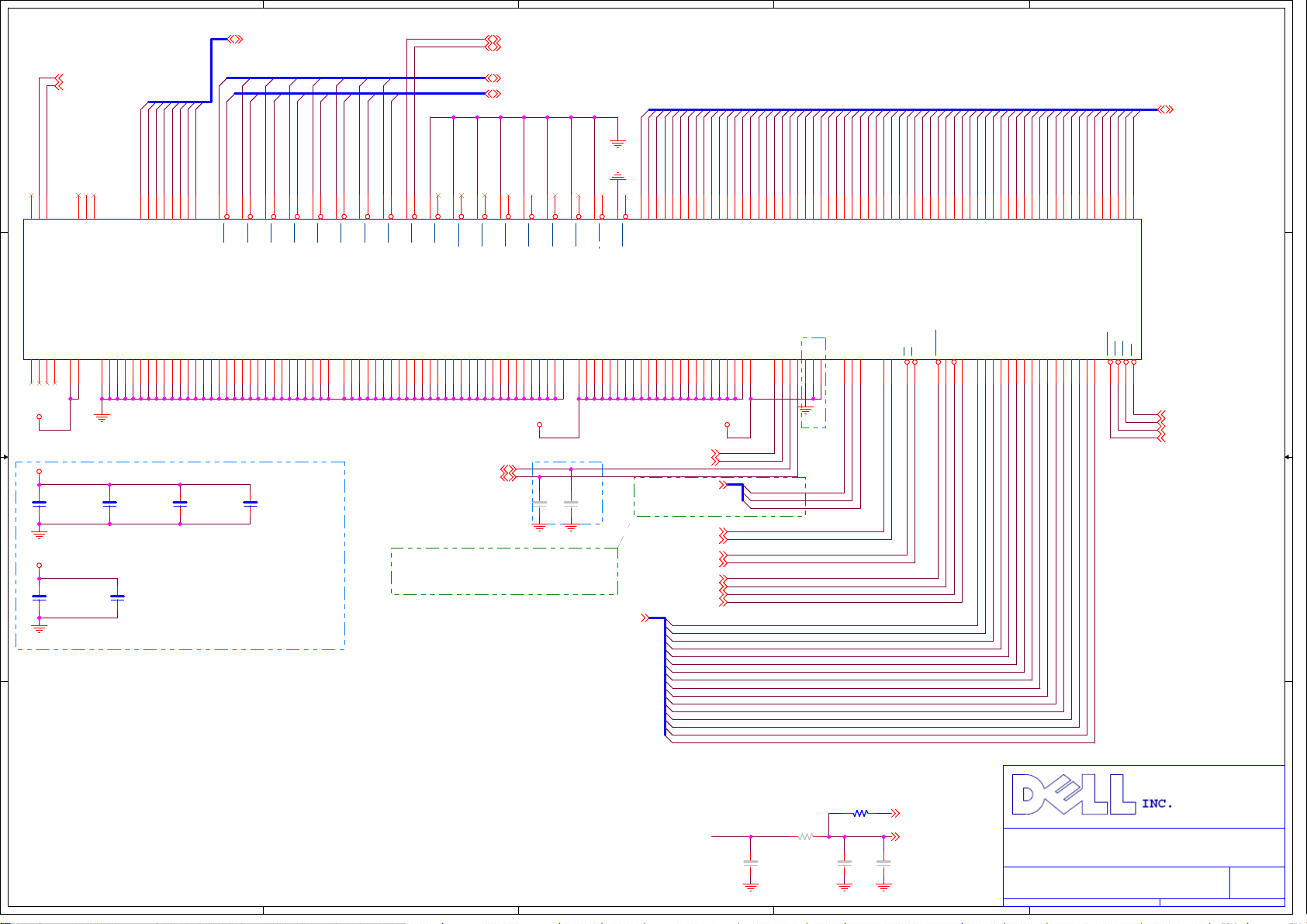

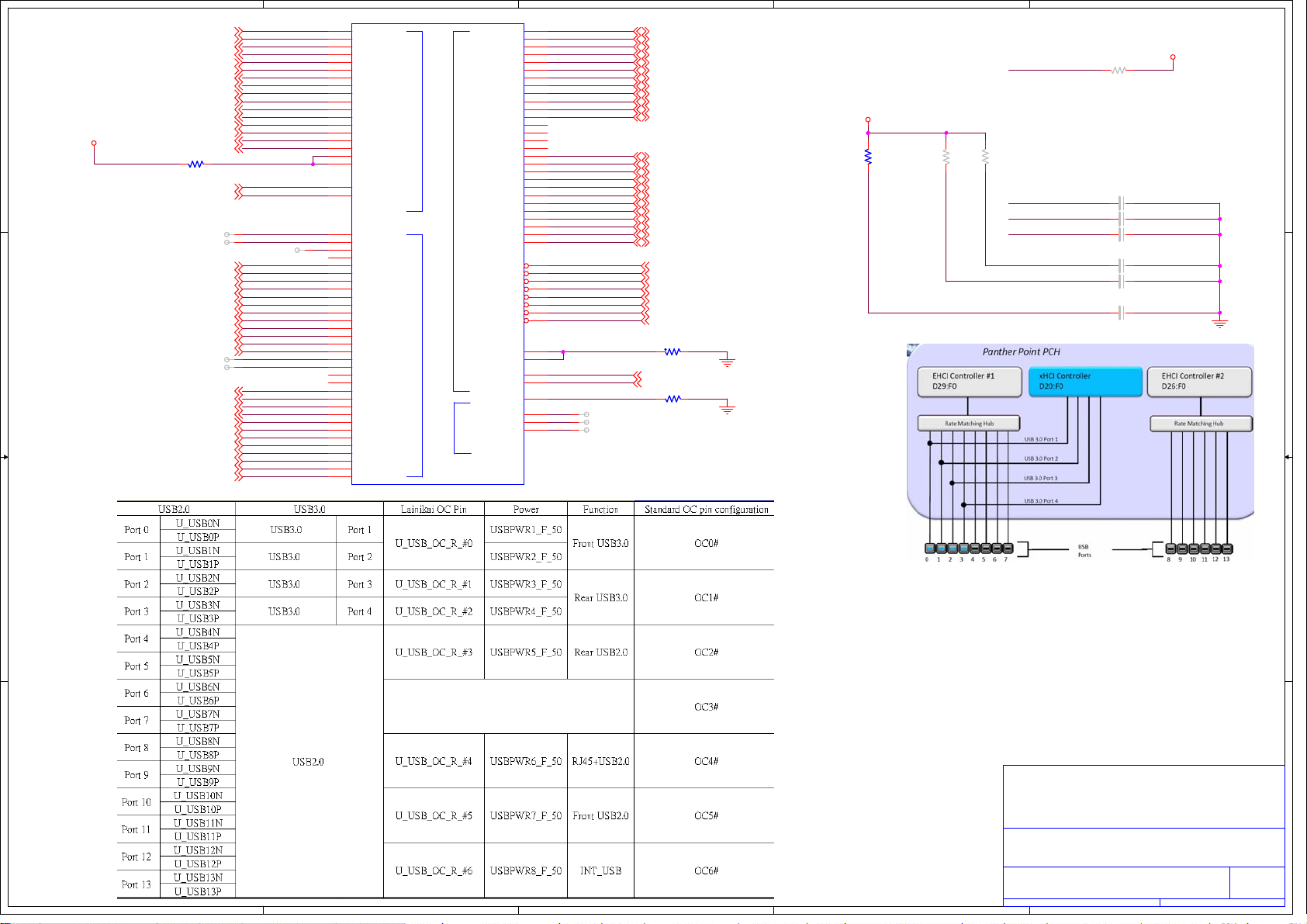

SMBUS DIAGRAM

SMdata2

SMdclk2

D D

Intel Lewisvillies

LOM

5545 SIO

SMdata1

SMdclk1

R015/RO16RO31/RO32

QO4/QO5

SMBus

Controller

SMLINK0

SMLINK1

BUS Switch

RESUME SMBUS

C C

PCH

RX5/RX6

RX3/RX4

RX1/RX2

RX9/RX10

Main SMBUS

CPU-XDP

PCH-XDP

Mini-PCIe 1x

PCIE 16x SMBUS

B B

PCIE 1x SMBUS

PCIE 4x SMBUS

PCI EXPRESS 1x

PCI EXPRESS 16x (wired as 4x signal)

PCI EXPRESS 16x

SLOT 4

SLOT 2

SLOT 1

3

SLOT 3

Title

Title

Title

DWG NO Rev

DWG NO Rev

DWG NO Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Lanikai _MT/DT

Lanikai _MT/DT

Lanikai _MT/DT

1

A00

A00

A00

of

271Wednesday, June 13, 2012

of

271Wednesday, June 13, 2012

of

271Wednesday, June 13, 2012

PCI SMBUS

A A

5

PCI SLOT

DIMM SLOTS

4

DDR3 DIMM1 CHA

DDR3 DIMM3 CHA

DDR3 DIMM2 CHB

DDR3 DIMM4 CHB

Address : 0 X00

Address : 0 X02

Address : 0 X04

Address : 0 X06

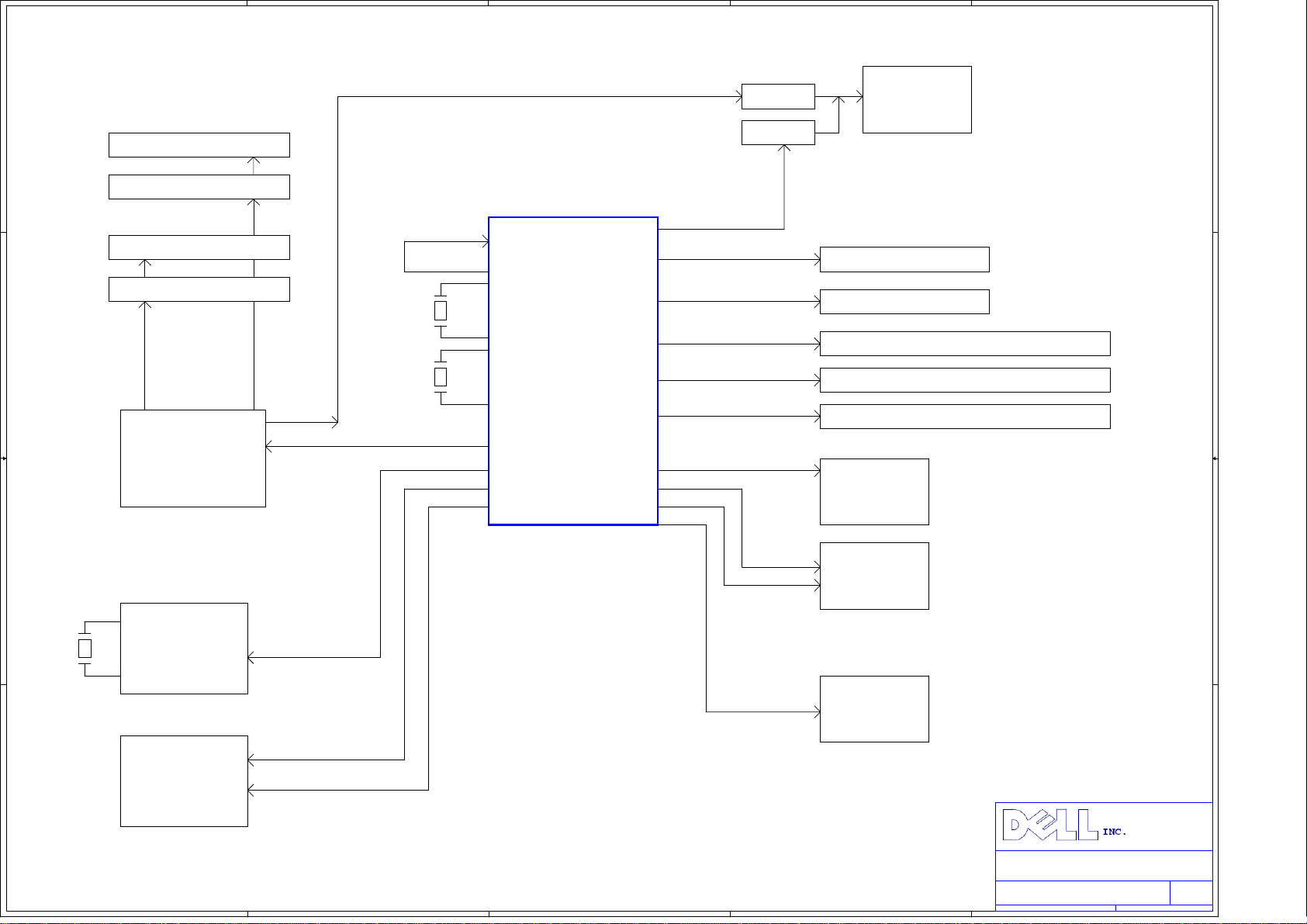

5

4

3

2

1

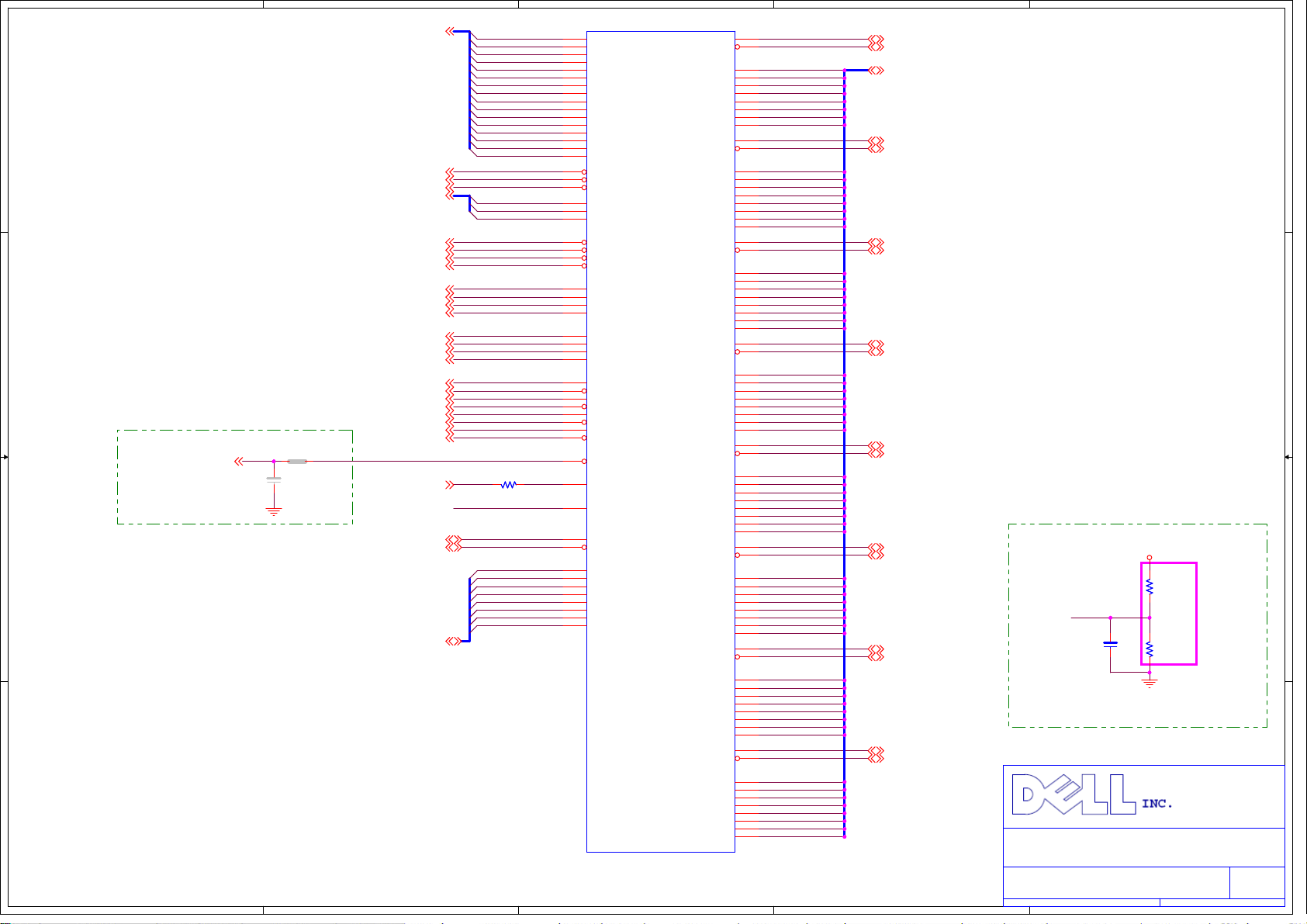

H_ITPCLK/H_ITPCLK#

D D

RS204/RS205

RS204/RS205

CPU XDP

DIMM 2

Channel B

DIMM 4

C_PCH_ITP/C_PCH_ITP#

DIMM 1

Channel A

C_PCI_SB

DIMM 3

25 MHZ

C C

PCH

D3_MA_CLK/CLK#[0:3]

D3_MB_CLK/CLK#[0:3]

32.768 KHZ

Buffer Through Mode

C_PE_100M_MCP/MCP#

CPU

C_PCIEX1_1/C_PCIEX1#_1

C_PCI_SL1

C_PCIEX16_1/C_PCIEX16#_1

C_PCIEX1_2/C_PCIEX1#_2

C_PCIEX4_1/C_PCIEX4#_1

C_SRC1_PCH/C_SRC1_PCH#

MINI PCIe

PCI SLOT

PCI EXPRESS X16

PCI EXPRESS X1

PCI EXPRESS X4

SLOT 3

SLOT 1

SLOT 2

SLOT 4

PCH XDP

B B

25 MHZ

LAN 82579

SUPER IO

A A

5

C_PCIE_L1/L1#

C_LPC_SIO

C_14M_SIO

4

3

C_14M_TPM

C_TPM

C_LPC_TPM

TPM/TCM

LPC HEADER

2

Title

Title

Title

DWG NO Rev

DWG NO Rev

DWG NO Rev

Date: Sheet

Date: Sheet

Date: Sheet

Clock Distribution

Clock Distribution

Clock Distribution

Lanikai _MT/DT

Lanikai _MT/DT

Lanikai _MT/DT

1

371Wednesday, June 13, 2012

371Wednesday, June 13, 2012

371Wednesday, June 13, 2012

A00

A00

A00

of

of

of

5

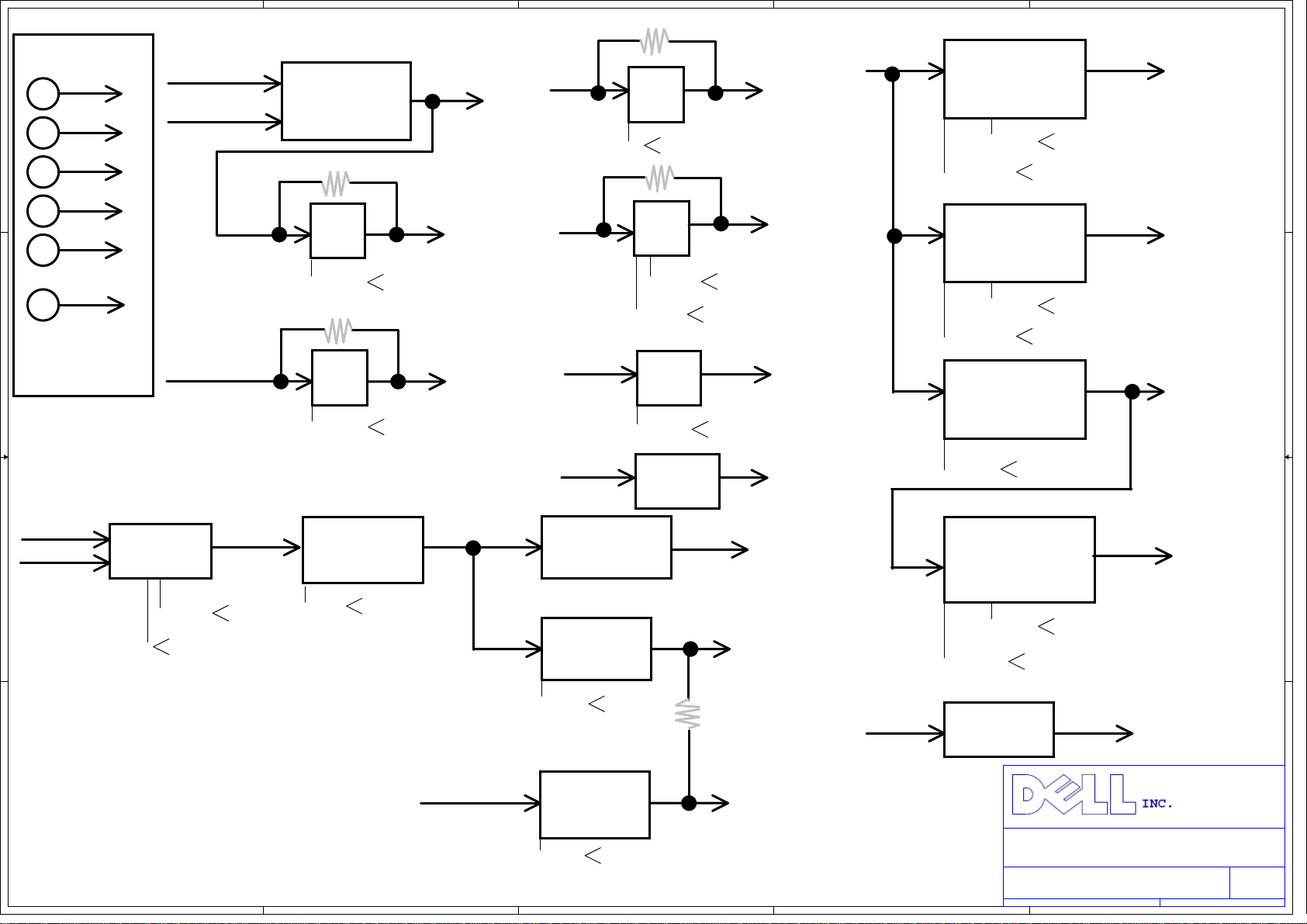

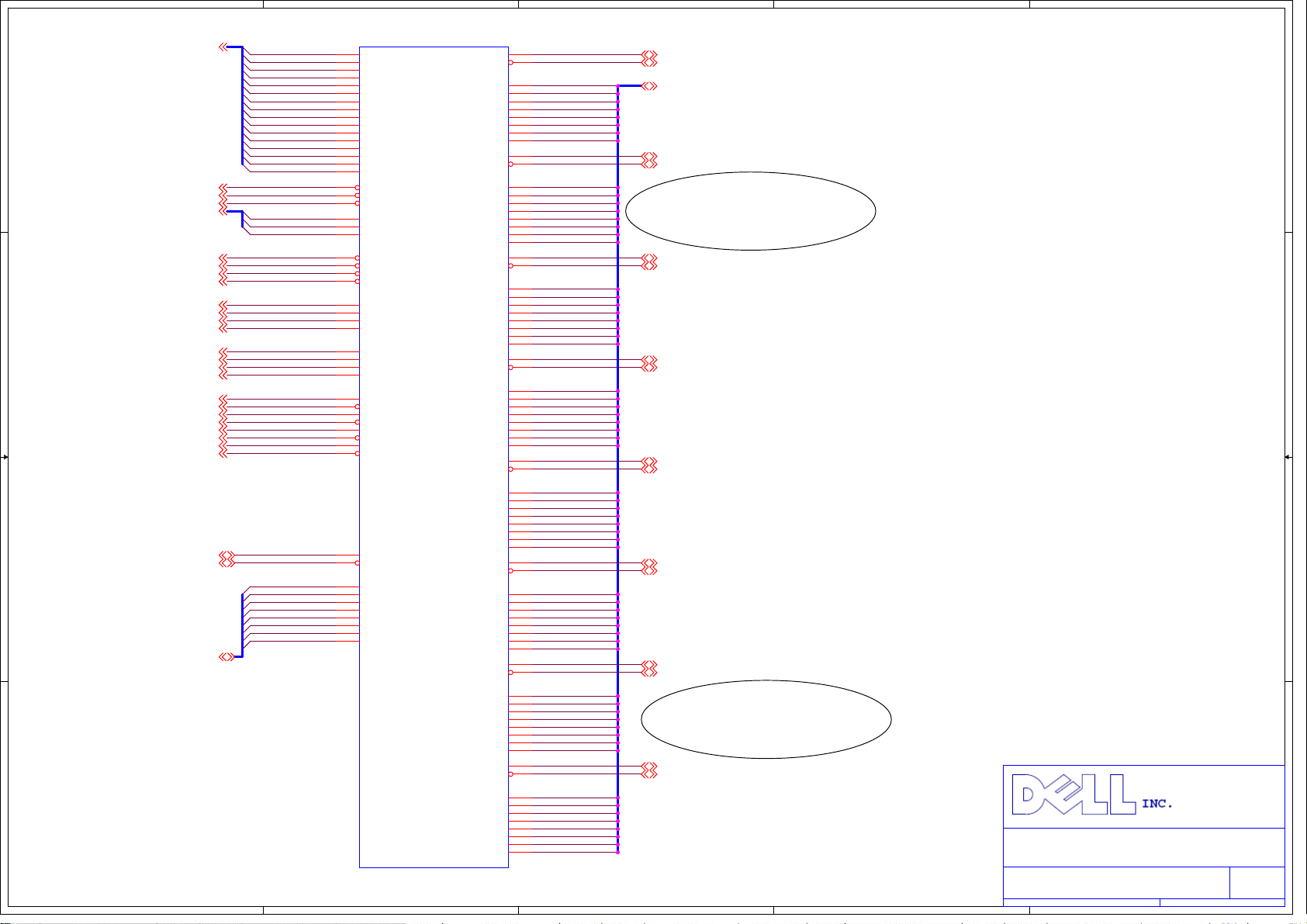

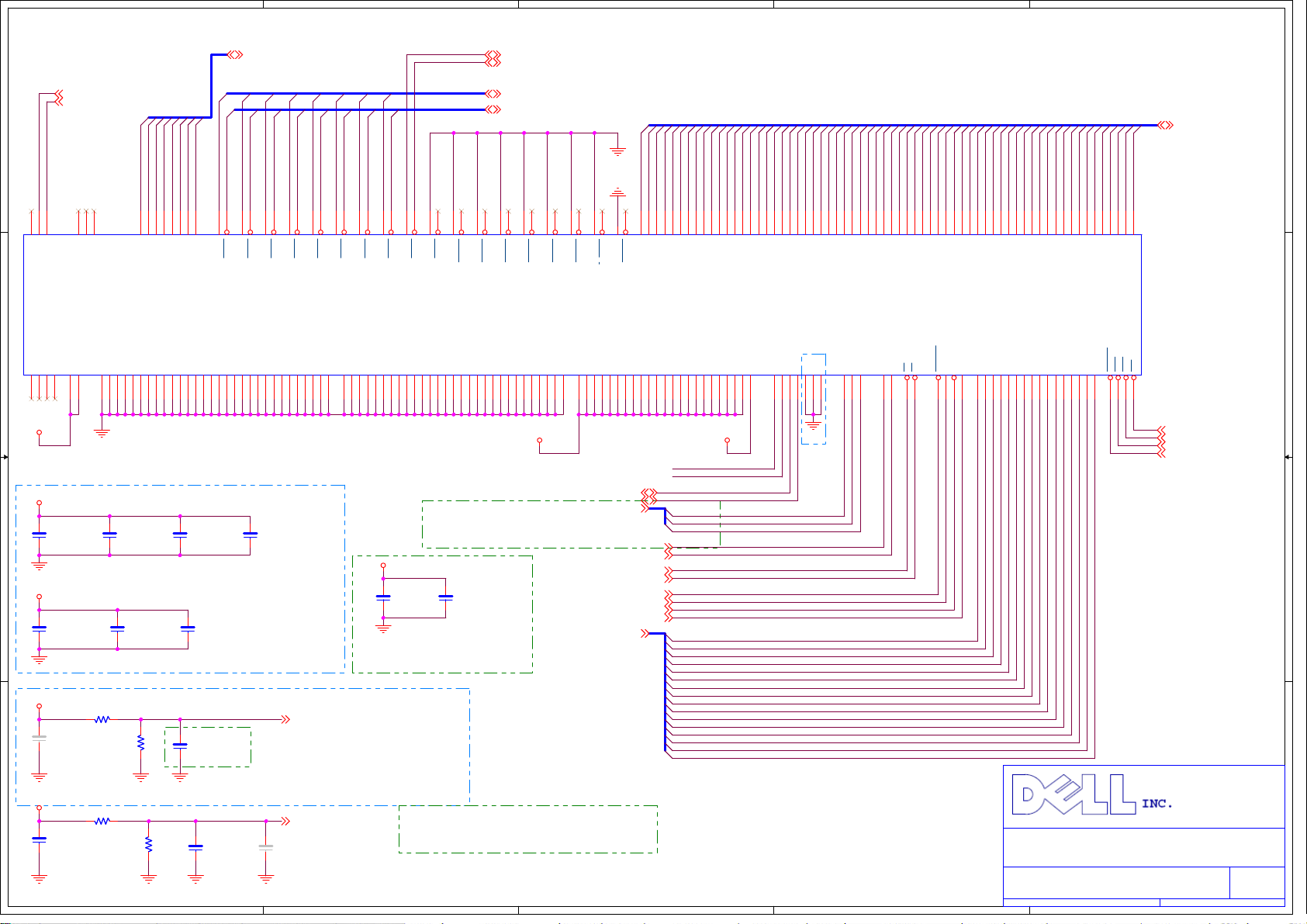

POWER DELIVERY MAP

PSU

2X12

S0

+5V

5V

10A

D D

-12V

Deep Sleep : Off

5VSB

3V

12V

+3V

2.4A

+12V

7A

-12V

+5VSB

S0

S0

S0

S5,S0,S3,S4

2X2

+12V_CPU

12V

10.6A

Current listed are for

a typical 265W PSU

C C

S0

+5VSB

+3V

+5VSB

S0

S5,S0,S3,S4

+3V_Dual

S5,S0,S3,S4

+3V_Dual Linear

Fairchild

FAN5078D3 /N AOD452

+/-5% DC + AC

P-FET

FDN340P

Switch

SLP_SUS_FET#

P-FET

FDN340P

Switch

SLP_SUS_FET#

4

resistor, empty

H=Power on

L=Power off

resistor, empty

H=Power on

L=Power off

+3V_Dual

Deep Sleep : Off

Default S5,S0,S3,S4

+3V_S5

Default S5,S0,S3,S4

+5V_S5

+3V_S5

S5,S0,S3,S4

+3V_S5

+3V_S5

+3V

S0

3

P-FET

FDN340P

Switch

S_SLP_M#

P-FET

FDN340P

Switch

S_SLP_S4#

S_PCIAUX_GATE

P-FET

SI4835DDY

Switch

S_SLP_LAN#

LDO

NCP1117STAT3G

resistor, empty

0.016A

H=Power on

L=Power off

resistor, empty

S0=1.5A,

S3~5=0.45A

H=Power on

L=Power off

0.218A

H=Power on

L=Power off

resistor, empty

H=Power on

L=Power off

0.375A

Deep Sleep : Off

Default : S0

ME : Mx/Moff

+3V_EPW

Deep Sleep : Off

Default S5,S0,S3,S4

+3V_PCIAUX

Deep Sleep : Off

Default : S0

ME : Mx/Moff

+3V_LAN

+V_1.5V_PCIE

+12V_CPU

S0

2

VCC_CORE

ON NCP6153+NCP5901

S0

VRD12 switcher, 4ph

SVID

85A TDC; 112A ICCMAX

LL = 1.7m ohms

+1P05V_VCCIO

VCC_AXG

ON NCP6153+NCP5901

VRD12 switcher, 1ph

SVID

25A TDC; 35A ICCMAX

LL = 4.1m ohms

+1P05V_VCCIO

VCCIO

ON NCP5230

Switcher, 1ph

17A Imax

+/-0.5% DC, +/-4.5% AC

1-bit VID(1.05V/1.0V)

+1P05V_PCH

S_SLP_S3#

S_SLP_S3#

H=Power on

L=Power off

H=Power on

L=Power off

H=Power on

L=Power off

H=Power on

L=Power off

H=Power on

L=Power off

1

+VCORE

+1P1V_AXG

+1P05V_VCCIO

S0

S0

S0

DDR3

H = +5V

L = +5VSB

S0,S3

Fairchild FAN5078D3

Switcher, 1ph

1.5V, 25A Imax

+/- 5% DC+ AC

S0

S_SLP_S4#

S3

H=Power on

L=Power off

4

+1P5V_SM

Deep Sleep : Off

Default S5,S0,S3,S4

S0,S3,

+5V_S5

+5VSB

S5,S0,S3,S4

S0

+5V

B B

A A

P SI3457CDV-T1-E3

N AOD452

Switch

B_ATX_PWROK

S_SLP_S3#

5

+5V_DUAL

H=Power on

L=Power off

DDR3 Vtt

Fairchild FAN5078D3

Linear

0.75V, 1A TDC

+/- 5% DC+ AC

PCH Core

Linear OP LM358

1.05V,7.5A Imax

+/- 5% DC+ AC

S_SLP_S3#

PCH ME (AMT only)

Richtek RT8068

Switcher, 1ph

1.05V, 1.8A Imax

+/- 5% DC+ AC

S_SLP_M#

H=Power on

L=Power off

H=Power on

L=Power off

VCCSA Linear

ON NCP102

+1P5V_SM_VTT

+1P05V_PCH

Non-AMT

stuff resistor,

empty for ME

Default S0

ME : Mx/Moff

+1P05V_ME

3

S0,S3,

S0

+3V

8.8A Imax

+/-5% DC + AC

1-bit VID(0.925V/0.85V)

VCCIO_PWRGD

SFR

S0

2

Linear OP LM358

1.8V, 1.6A Imax

+/-5% DC + AC

+V_VCCSA

S_SLP_S3#

H=Power on

L=Power off

H=Power on

L=Power off

+1P8V_SFR

Title

Title

Title

Power Delivery Map

Power Delivery Map

DWG NO Rev

DWG NO Rev

DWG NO Rev

Date: Sheet

Date: Sheet of

Date: Sheet of

Power Delivery Map

Lanikai _MT/DT

Lanikai _MT/DT

Lanikai _MT/DT

1

S0

S0

A00

A00

A00

of

471Wednesday, June 13, 2012

471Wednesday, June 13, 2012

471Wednesday, June 13, 2012

5

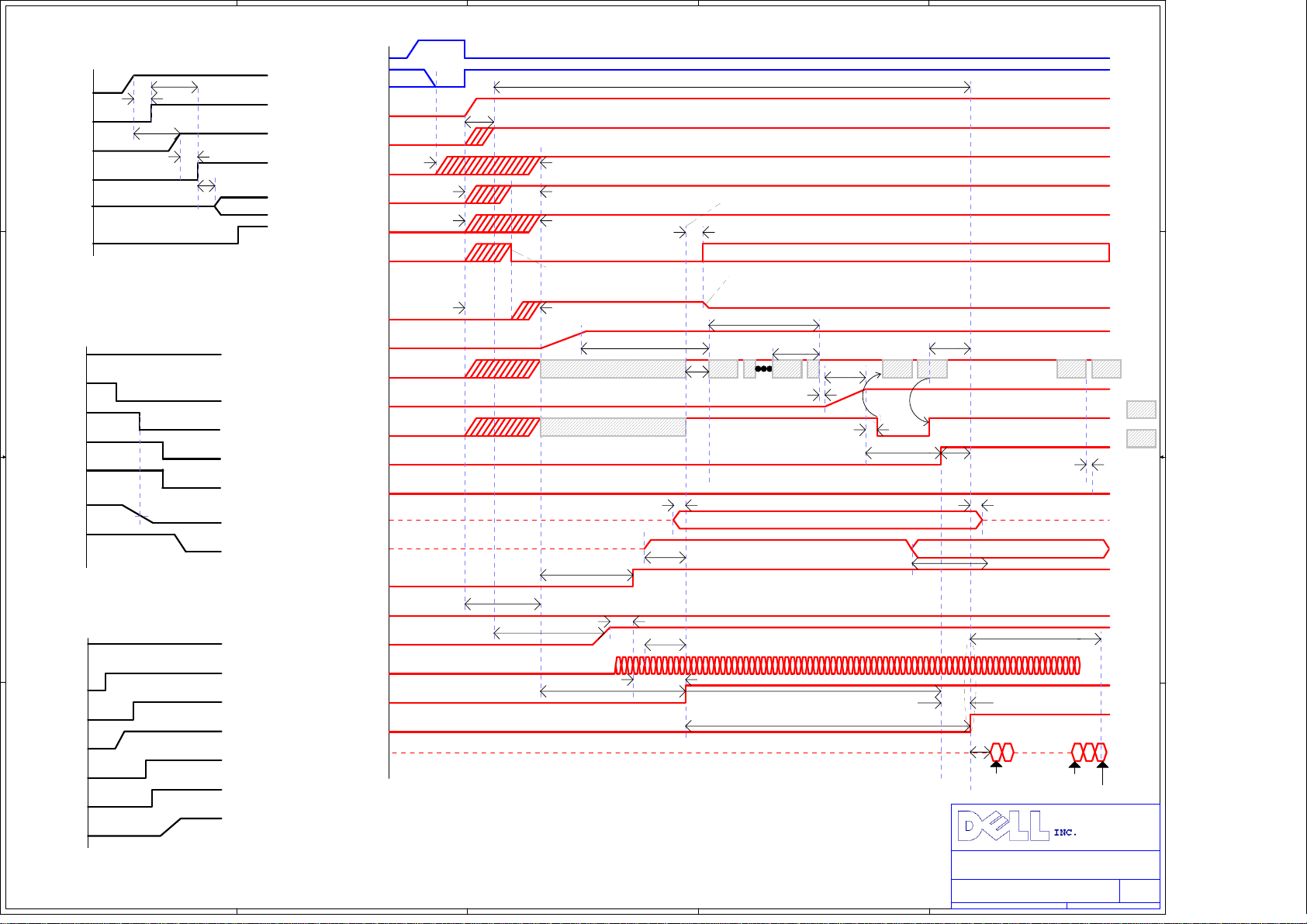

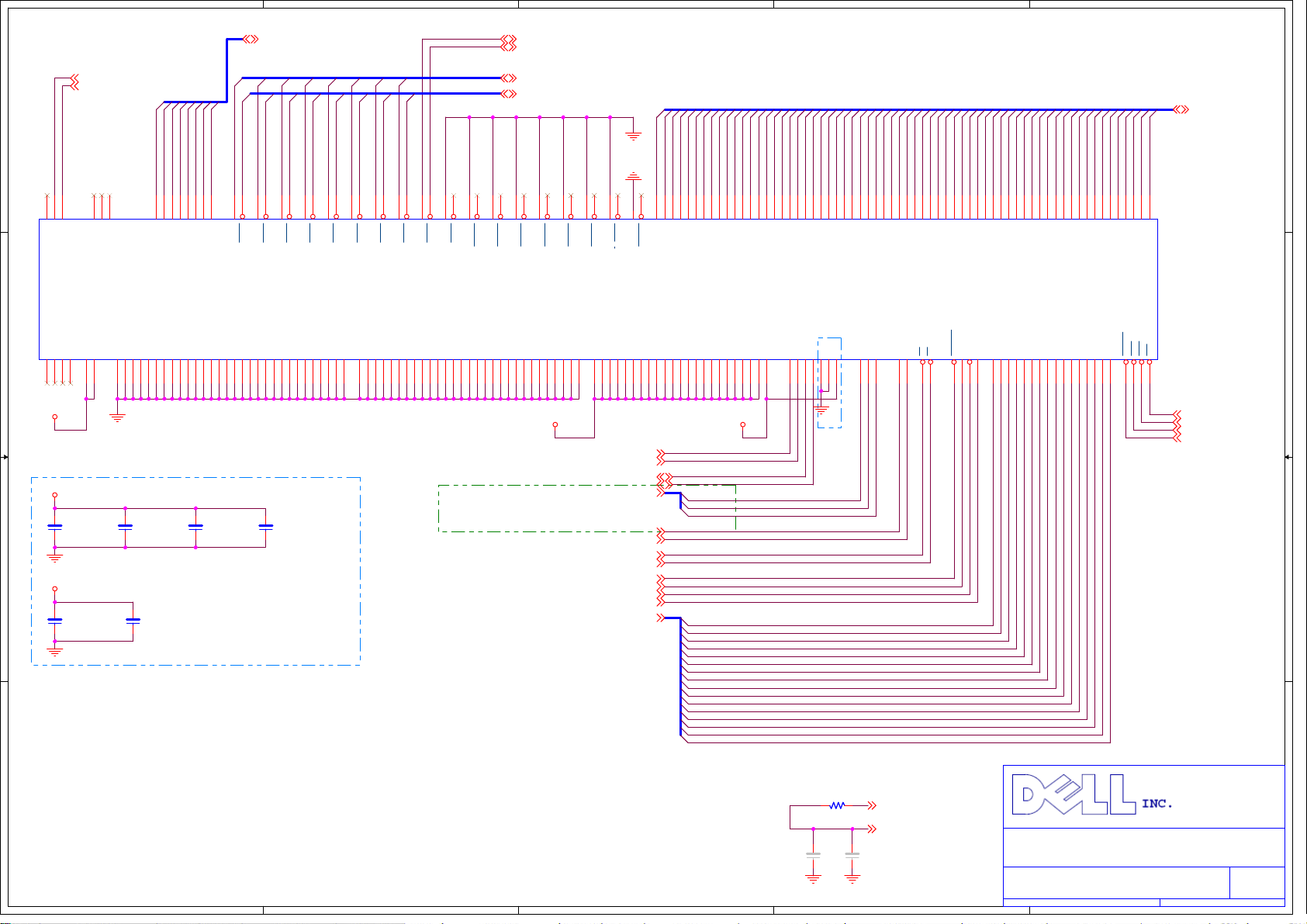

POWER ON Timing Diagram

4

3

2

1

G3 to S4/S5 Timing Diagram

VccRTC

D D

RTCRST#

t200

VCCSUS

RSMRST#

SUSCLK

SLP_S5#

C C

Deep Sleep Entry

DPWROK

SUSWARN#

SUS_PWR_ACK

SLP_SUS#

RSMRST#

+5VDUAL

+5V_S5/+3V_S5

B B

t226

t225

t201

t202

1.05V

Deep Sleep Exit

DPWROK

SLP_SUS#

RSMRST#

+5V_S5/+3V_S5

SUSWARN#

A A

SUS_PWR_ACK

O_PS_ON#

S_SLP_S3#

+12V/+5V

+1P5V_SM

+1P05V_VCCIO

+1P8V_SFR

H_VCCSA_VID

+V_VCCSA

SVIDs

(VIDSOUT/VIDCLK)

+VCORE

SAlert#I

VIDALERT#

VR_Ready

Feed into PCH

SYS_PWROK

+1P1V_AXG

Srtaps=CFG[x}

S_Thermtrip#

H_SM_DRAMPWRGD

(xxDRAM_PWROK)

D3_RESET#

PWRGD_3V

Feeds into PCH_PWROK

BCLK, PCIe

CLKs

UNCOREPWRGOOD

(PROCPWRGD)

S_RLTRST#

DMI

Power rails rise

0.2 – 20ms

Power rails rise

+3V

0.2 – 20ms

=50ms

=50ms

=50ms

EN

Note4:Uncorepwergood must be at

a valid level during all power states

PCI/PCIe:100ms min

PSU: <=20ms

=500ms

T

VCCSA VID[0] Buffers Output is

stable after VccIO Ramp

Uncorepwrgd must be stable (low) at this time

Recommended that VccSA ramp after VCCIO has

remped to ensure VCCSA_VID[0] is stable

VSABOOT=SNB Vmax

V

RC

Note5: Core and GT power supplies should not source current during this time.

Note5: Core and GT power supplies should not source current during this time.

Note:DDR spec reuqires that DDR_RESET# be

asserted during power ramp cycle

IH

T

A

VR:5ms max

CPU SVID buffers are Hi-Z once VCCIO is

stable and Uncorepowergood=0

CPU SVID buffers are Hi-Z once VCCIO is

stable and Uncorepowergood=0

Min 10 PCIe bclks

T

10

CPU:1ms min

PSU

100ms~500ms

T

2

CPU:5ms min, 650ms max

17

T

11

CPU:[x]ms min

PCH t34

(1ms)

Min 10 PCIe bclks

PCH t573

(1, 5, 50, or 100ms)

T

1

CPU:

500us max

T

Uncorepwrgood assertion

MAX TBDns

VCCUSA VID[0] FINAL

Ramp not to exceed 50mV/us

VSAFINAL

Typ 60us

Depends on exact SVID

transactions between CPU

and VR

MISC

13

Inactive / Disable

Note: PCH THERMAL WATCHDOG TIMER WILL BE DISABLED WITH SNB.

SNB WILL NOT EXCEED VR IMAX UNTIL THERMTRIP# IS ENABLED

T

A

C

K

0

B

A

Set VID

A

SLOW

Packet

VR:5us max

A

C

C

K

K

T

D

0

1

VR:2ms max

T

C

T

VR:1us max

C

K

1

GT Ramp will occur after PLTRST#

Strapping option

T

6

CPU:1ms min, 100ms max

E

GETReg

status

Packet

T

F

VR:min=Te,5ms max

T

12

CPUPWRGOOD

SYS_PWROK(VR_READY)

T

8

CPU:

400us min

A

A

C

C

Pay

K

K

load

0

1

=5ms

PCH(t1001)

T

14

Min 10 PCIe bclks

Set VID

Packet

T

VR:5us max

Satus

Packet

CPU

Packet

GT

Packet

C

Enable

CPU:[x]ms min

BIOS will deassert DDR_RESET#

PCH: No min/max requirement

AND

PCH t1001

30us, 1, 2or 5ms

=PCH_PWROK & SYS_PWROK &

t1001 Timer expired & internal_ready

T

?

DMI training CPU_RESET_DONE

CPU_RESET_DONE_ACK

+5VDUAL

Title

Title

Title

DWG NO Rev

DWG NO Rev

DWG NO Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

Power On Sequence

Power On Sequence

Power On Sequence

Lanikai _MT/DT

Lanikai _MT/DT

Lanikai _MT/DT

1

A00

A00

A00

of

571Wednesday, June 13, 2012

of

571Wednesday, June 13, 2012

of

571Wednesday, June 13, 2012

5

4

3

2

1

RESET / Power Good MAP

Sequence Signal Name:

O_PWRBTN#IN

(1)

S_SLP_S4# S_SLP_S3#

(2)

D D

O_PSON#

(3)

B_ATX_PWROK

(4)

PCH_MEPWRGD

(5)

S_PCH_SYSPWROK P_VR_READY

(6)

PWRGD_3V

(7)

H_DRAMPWRGD

(8)

H_PWRGD

(9)

S_PLTRST#

(10)

X_PLTRST_PCIE_SLOT# K_PCIRST#_SLOT

(11)

A_Z_RST#

(12)

D3_RESET#

H_RESET#_R S_PLTRST#_R

CPU-XDP

C C

PCH-XDP

F_TP_XDP_RST

Front Panel

O_PWRBTN#IN

S_SLP_M#

(9)

(1)

(1)

PROCPWRGD

PWROK

> 1ms

UNCOREPWRGOOD

(9)

CPU-Ivy Bridge

SM_DRAMPWROK

RESET*

(10)

Buffer (UH2)

SM_DRAMRST*

Deep Sleep Exit MAP

Sequence Signal Name:

O_PWRBTN#IN

(D1)

S_SLP_SUS#

(D2)

S_RSMRST#

(D3)

S_SUSWARN#

(D4)

S_SUS_PWR_ACK#

(D5)

(8)

(10)

(10)

DDRIII Slots

D3_RESET#

LAN

PE_RST_N

TPM/TCM

LRESET#

(1)

Power On Botton

O_PWRBTN#IN

(1) (1)

(D1)

PWRBTN#

DRAMPWROK

PLTRST# LRESET#

PROCPWRGD

VRD 12

VR_RDY

B B

RESET BUTTON

FP_RST#

HD Audio

RESET#

(12)

(6)

SYS_PWROK

SYS_RESET#

HDA_RST#

AND

PCH

PWROK

SLP_S4# SLP_S4_S5#

SLP_A# IO_SMI#

RSMRST#

(8)

(10)

(2)

(2)

(2)

(7)

PWR_GOOD_3V

SLP_S3#SLP_S3#

PCI_RST_SYS#

PWRBTN#

SIO-5545

PS_ON#

PWRGD_PS

(4)

(3)

PWR_GOOD_3V

PWRGD_PS

ATX Power

PSON

PWROK

100~120ms

(D3)

ME POWER-GOOD

CIRCUIT

PCH_MEPWRGD

PCH_MEPWRGD

+1P05V_ME

A A

> 1ms

5

+5VDUAL

SUSACK#

(5)

APWROK

4

SUSACK#

Sequence

Logic

Circuit

Page.64

SUSWARN#

(D4)(D5)

SLP_SUS#

(D2)

+5V_S5/+3V_S5

SLP_SUS#

Sequence

Logic

Circuit

Page.64

3

Title

Title

Title

Reset / Power Good Map

Reset / Power Good Map

Reset / Power Good Map

DWG NO Rev

DWG NO Rev

DWG NO Rev

Lanikai _MT/DT

Lanikai _MT/DT

Date: Sheet

Date: Sheet of

2

Date: Sheet of

Lanikai _MT/DT

1

671Wednesday, June 13, 2012

671Wednesday, June 13, 2012

671Wednesday, June 13, 2012

A00

A00

A00

of

5

4

3

2

1

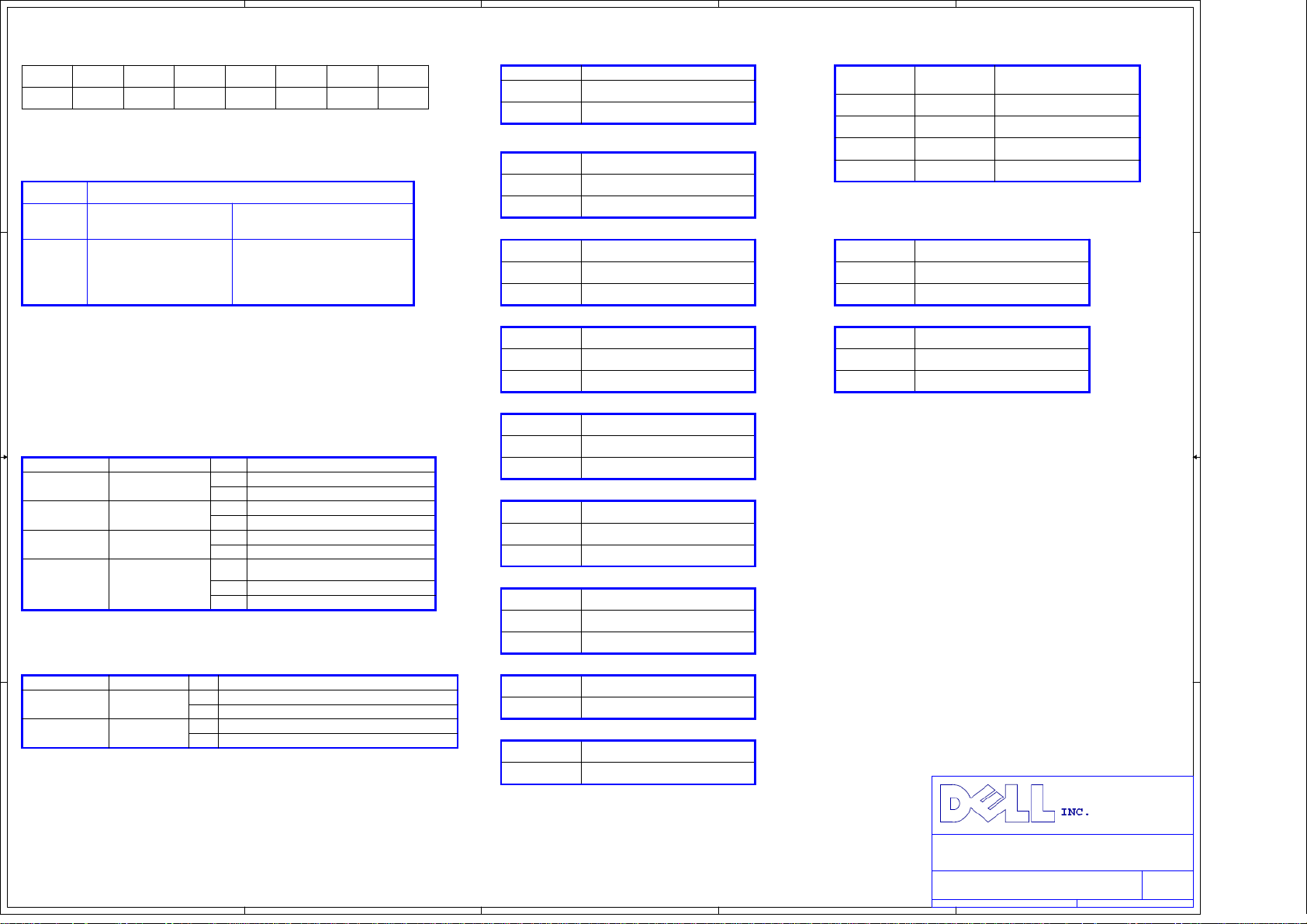

IRQ Routing Table

INTA# INTB# INTC# INTD# IDSEL REQn# GNTn#

Slot3 A BCD 1800

D D

STRAPPING Table

CPU side

CFG[17:0] Description

[2]

[6:5]

C C

PIN NAME

PCI2/TME

(PIN4)

PCI4/SRC5_EN

(PIN6)

PCIF5/ITP_EN

(PIN7)

B B

PCI3/CFGP

(PIN5)

PCI Express static x16

lane numbering reversal

PCI Express Bifurcation

NET

C_CK505_33M_PCI2

C_CK505_33M_PCI4

C_CK505_33M_PCI5

C_CK505_33M_PCI3

1: normal

0: lane numbers reversed

00: 1x8, 2x4 PCI Express

01: reserved

10: 2x8 PCI Express

11: 1x16 PCI Express

Strapping description

Overclocking DISABLED

1

Overclocking ENABLED

0

SRC5

1

CPU_STOP# and PCI_STOP#

0

CPU_ITP

1

SRC8

0

See CFG Table

(Set SATA and SRC come from PLL4)

Low

See CFG Table

Mid

See CFG Table

High

Default

Default

DEFAULT

DEFAULT

DEFAULT

DEFAULT

SIO SMSC5545

PIN NAME

GP070 / PWM4

(PIN127)

DTR1# [TEST_EN]

/GP051

(PIN104)

A A

NET

O_SPEAKER

O_DTR1#_R

Strapping description

Disable

Diag_En

1

0

1

0

Enable

Diag_En

PE BOOT Loader Strap (DTR1#)= Load from SPI

PE BOOT Loader Strap (DTR1#)= No Load from SPI

DEFAULT

DEFAULT

PCH

On-Die PLL Voltage Regulator Voltage Select

HDA_SYNC

High

Low

On-Die PLL Voltage Regulator

GPIO28

(IN-PU)

High

Low

Topblock Swap Mode

GNT3#/GPIO55

(IN-PU)

High

Low

No Reboot Mode

SPKR

(IN-PD)

High

Low

Integrated 1.05V VRM

INTVRMEN

High

Low

TLS Confidentiality

GPIO15

(IN-PD)

High

Low

Flash Descriptor Override Strap

HDA_SDO

High

Low

DMI Rx Termination Voltage

SPI_MOSI

(IN-PD)

Low

DMI Termination Voltage

NV_CLE

(IN-PU)

High

Description

1.5V

1.8V

Description

Regulator is enabled.

Regulator is disabled.

Description

Topblock swap mode: Disable

Topblock swap mode: Enable

Description

No reboot mode: Enable

No reboot mode: Disable

Description

Integrated 1.05V VRM: Enable

Integrated 1.05V VRM: Disable

Description

ME Crypto TLS cipher suite

with confidentiality

ME Crypto TLS cipher suite

with no confidentiality

Description

Flash descriptor security

will be override

Disable ME in Manufacturing Mode

Description

DMI Rx Termination Voltage

Description

DMI and FDI Tx/Rx

Termination Voltage

DEFAULT

DEFAULT

DEFAULT

DEFAULT

DEFAULT

DEFAULT

DEFAULT

DEFAULT

DEFAULT

Boot BIOS Destination Selection

GNT1#

(IN-PU)

Low

High

Low

High

Deep S4/S5 Well on-die Voltage Regulator Enable

DSWVRMEN

High

Low

Digital Port C Strap

DDPC_CTRLDATA

High

Low

SATA1GP/GP19

(IN-PU)

Low

Low

High

High

Description

Enable

Disable

Description

Configure Port C

Disable

Description

Flash cycle routed to LPC

Flash cycle routed to PCI

Flash cycle routed to NAND

Flash cycle routed to SPI

DEFAULT

DEFAULT

DEFAULT

Title

Title

Title

DWG NO Rev

DWG NO Rev

DWG NO Rev

Date: Sheet

Date: Sheet of

5

4

3

2

Date: Sheet of

GPIO/IRQ/IDSEL Table

GPIO/IRQ/IDSEL Table

GPIO/IRQ/IDSEL Table

Lanikai _MT/DT

Lanikai _MT/DT

Lanikai _MT/DT

771Wednesday, June 13, 2012

771Wednesday, June 13, 2012

771Wednesday, June 13, 2012

1

A00

A00

A00

of

5

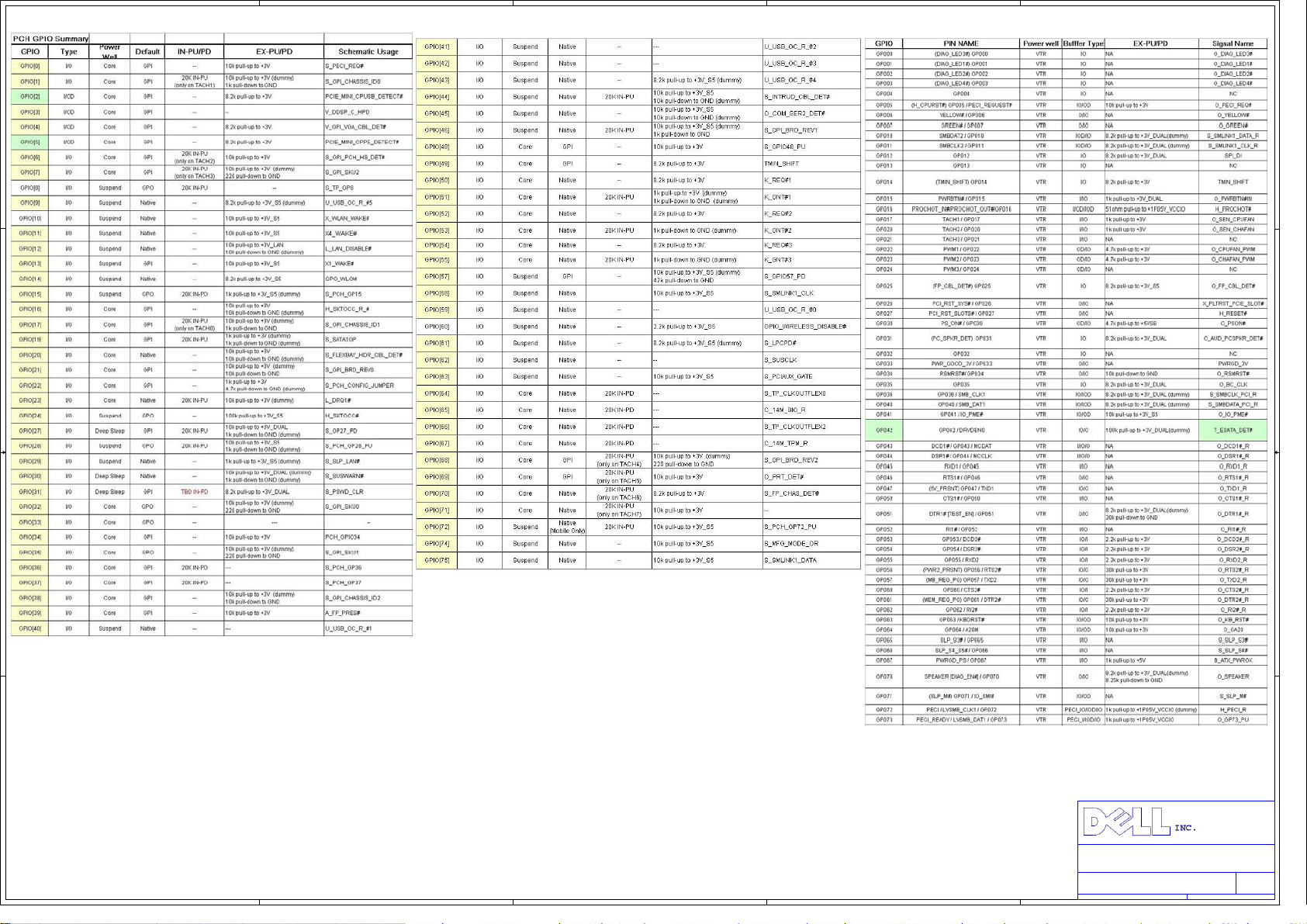

D D

C C

4

3

2

1

B B

A A

Title

Title

Title

DWG NO Rev

DWG NO Rev

DWG NO Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

GPIO Table

GPIO Table

GPIO Table

Lanikai _MT/DT

Lanikai _MT/DT

Lanikai _MT/DT

1

A00

A00

A00

of

871Wednesday, June 13, 2012

of

871Wednesday, June 13, 2012

of

871Wednesday, June 13, 2012

5

C_PE_100M_MCP27

C_PE_100M_MCP#27

H_VIDSCLK

RH2 change to 44.2 ;

D D

Change net name to

H_RESET#-12/28/09

Add off-page toXDP; CRB 0.7

12/27/09

C C

H_PWRGD

B B

CRB0.7 12/07/09

H_CFG052

*

*

RH58

RH58

1K

1K

H_VIDSOUT

H_VIDALERT#

+1P05V_VCCIO

H_PWRGD24,52,64

H_PM_SYNC23

H_PECI23,32

H_PROCHOT#32,67

H_THERMTRIP#23

H_SKTOCC#23,24

RH10 1.5KDummy

RH10 1.5KDummy

RH11 1.5KDummy

RH11 1.5KDummy

RH12 1.5KDummy

RH12 1.5KDummy

RH13 1.5KDummy

RH13 1.5KDummy

RH14 1.5KDummy

RH14 1.5KDummy

RH15 1.5KDummy

RH15 1.5KDummy

RH16 1.5KDummy

RH16 1.5KDummy

RH19 1.5KDummy

RH19 1.5KDummy

RH20 1.5KDummy

RH20 1.5KDummy

RH22 1.5KDummy

RH22 1.5KDummy

RH24 1.5KDummy

RH24 1.5KDummy

RH26 1.5KDummy

RH26 1.5KDummy

RH28 1.5KDummy

RH28 1.5KDummy

RH29 1.5KDummy

RH29 1.5KDummy

RH30 1.5KDummy

RH30 1.5KDummy

RH31 1.5KDummy

RH31 1.5KDummy

RH32 1.5KDummy

RH32 1.5KDummy

RH33 1.5KDummy

RH33 1.5KDummy

H_CPU_DIMM_VREF_B18

H_CPU_DIMM_VREF_A16

RH2 44.2Ohm

RH2 44.2Ohm

RH1 49.9

RH1 49.9

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

20100709: Reserve RH58 connect H_PWRGD to GND

H_VIDSCLK67

A A

H_VIDSOUT67

H_VIDALERT#67

Remove CH1,CH2-12/29/09

RH39 change to 110 ohm; CRB 0.7-11/30/09

5

*

*

+/-1%

+/-1%

*

*

+/-1%Dummy

+/-1%Dummy

H_RESET#_R

H_CATERR

H_PROC_SEL

H_CFG0

H_CFG1

H_CFG2

H_CFG3

H_CFG4

H_CFG5

H_CFG6

H_CFG7

H_CFG8

H_CFG9

H_CFG10

H_CFG11

H_CFG12

H_CFG13

H_CFG14

H_CFG15

H_CFG16

H_CFG17

RH38

RH38

91 Ohm

91 Ohm

+/-1%

+/-1%

Dummy

Dummy

4

*

*

110Ohm

110Ohm

4

RH39

RH39

UH1E

UH1E

W2

BCLK0

W1

BCLK0*

C37

VIDSCLK

B37

VIDSOUT

A37

VIDALERT*

J40

UNCOREPWRGOOD

F36

RESET*

E38

PM_SYNC

J35

PECI

E37

CATERR*

H34

PROCHOT*

G35

THERMTRIP*

AJ33

SKTOCC*

K32

PROC_SEL

H36

CFG0

J36

CFG1

J37

CFG2

K36

CFG3

L36

CFG4

N35

CFG5

L37

CFG6

M36

CFG7

J38

CFG8

L35

CFG9

M38

CFG10

N36

CFG11

N38

CFG12

N39

CFG13

N37

CFG14

N40

CFG15

G37

CFG16

G36

CFG17

A38

NCTF0

AU40

NCTF1

AW38

NCTF2

C2

NCTF3

D1

NCTF4

AH1

FC_AH1

AH4

FC_AH4

AV1

RSVD_NCTF0

AW2

RSVD_NCTF1

AY3

RSVD_NCTF2

R34

RSVD40

R36

RSVD41

R38

RSVD42

R40

RSVD43

J31

RSVD44

AD34

RSVD45

AD35

RSVD46

K31

RSVD47

PE115527-4041-0DF

PE115527-4041-0DF

+1P05V_VCCIO

*

*

RH40

RH40

75

75

+/-1%

+/-1%

+/-1%

+/-1%

3

TDO

TCK

TMS

TRST*

PRDY*

PREQ*

DBR*

RSVD36

RSVD0

BPM0*

BPM1*

BPM2*

BPM3*

BPM4*

BPM5*

BPM6*

BPM7*

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD37

RSVD38

RSVD39

P34

T2

A36

B36

AB4

AB3

L32

M32

L39

L40

TDI

M40

L38

J39

K38

K40

E39

C40

D40

H40

H38

G38

G40

G39

F38

E40

F40

AB6

AB7

AD37

AE6

AF4

AG4

AJ11

AJ29

AJ30

AJ31

AN20

AP20

AT11

AT14

AU10

AV34

AW34

AY10

C38

C39

D38

H7

H8

J33

J34

J9

K34

K9

L31

L33

L34

L9

M34

N33

N34

P33

P35

P37

P39

20100107:

Remove test points

H_VCCIO_SEL

+5V

*

*

RH37

RH37

10K

10K

*

*

RH34

RH34

4.7K

4.7K

VCCSA_VID

VCCSA_SENSE

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

VSSIO_SENSE

VCCAXG_SENSE

VSSAXG_SENSE

MISC

MISC

VCCP_SELECT

5/10

5/10

*

*

H_VCCSA_VID 70

H_VCCSA_SENSE 70

H_VCC_SENSE 67

H_VSS_SENSE 67

H_VCCTT_SENSE 69

H_VSSTT_SENSE 69

H_VCCAGX_SENSE 67

H_VSSAGX_SENSE 67

H_TDO 52

H_TDI 52

H_TCK 52

H_TMS 52

H_TRST# 52

H_PRDY# 52

H_PREQ# 52

H_ITPCLK 52

H_ITPCLK# 52

H_BPM#0 52

H_BPM#1 52

H_BPM#2 52

H_BPM#3 52

H_BPM#4 52

H_BPM#5 52

H_BPM#6 52

H_BPM#7 52

H_VCCIO_SEL 69

RO40change reference to

RH7 and move from SIO to

CPU side ; CRB

0.7-12/29/09

+3V_S5

Add RH66 pull-up to +3V_DUAL;

CRB 0.7-12/10/09

H_RESET#32

S_PLTRST#24,32,34,46,52,53

*

*

RH66

RH66

220

220

+/-5%

+/-5%

Dummy

Dummy

2

RH4 usage 1kOhm ; CRB 0.7-12/10/09

Removed RH3; CRB 0.7-12/29/09

Dummy RH6 ; CRB 0.7-12/28/09

+1P05V_VCCIO

FP_RST# 24,52,53

RH35 0

RH35 0

*

*

+3V_DUAL

CH2 0.1uF

CH2 0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

53

UH2

UH2

1

2

74AHCT1G08GW

74AHCT1G08GW

M_NVR_CLE25

RH17 change to 4.7k; CRB 0.7-11/30/09

20100709: Reserve CH11 connect H_PROC_SEL to GND

Removed RH7; CRB 0.7-12/10/09

*

*

*

RH7

RH7

51 Ohm

51 Ohm

H_TDO

H_TDI

H_TMS

H_TCK

H_TRST#

RH61 750

RH61 750

4

Dummy

Dummy

RH17

RH17

4.7K

4.7K

*

*

*

+1P8V_SFR

*

*

RH5

RH5

RH4

RH4

51 Ohm

51 Ohm

1K

1K

Dummy

Dummy

Dummy

Dummy

Close to

XDP Conn

RH18 51 Ohm

RH18 51 Ohm

RH21 51 Ohm

RH21 51 Ohm

RH23 51 Ohm

RH23 51 Ohm

RH25 51 Ohm

RH25 51 Ohm

RH27 51 Ohm

RH27 51 Ohm

Close to

CPU

*

*

+/-1%

+/-1%

RH62

RH62

*

*

316

316

+/-1%

+/-1%

Change H_RESET# source from SIO

directly-12/28/09

20100104: add UH2 to prevent SIO

can't use

*

*

RH60

RH60

2.2K

2.2K

CH11

CH11

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

Dummy

Dummy

*

*

*

*

*

*

*

*

*

*

*

*

H_PROC_SEL

RH6

RH6

51 Ohm

51 Ohm

Dummy

Dummy

1

+1P05V_VCCIO

H_RESET#_R 52

H_PROCHOT#

H_PECI

H_THERMTRIP#

H_CATERR

Add H_VCCIO_SEL circuit; CRB 0.7-12/03/09

Title

Title

Title

CPU-1: MISC

CPU-1: MISC

DWG NO Rev

DWG NO Rev

DWG NO Rev

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet

CPU-1: MISC

Lanikai _MT/DT

Lanikai _MT/DT

Lanikai _MT/DT

1

A00

A00

A00

of

971Wednesday, June 13, 2012

971Wednesday, June 13, 2012

971Wednesday, June 13, 2012

5

D D

H_FDI_FSYNC025

H_FDI_LSYNC025

H_FDI_FSYNC125

H_FDI_LSYNC125

H_FDI_INT25

RH41 24.9

RH41 24.9

*

+1P05V_VCCIO

C C

*

+/-1%

+/-1%

UH1D

UH1D

AC5

FDI_FSYNC0

AC4

FDI_LSYNC0

AE5

FDI_FSYNC1

AE4

FDI_LSYNC1

AG3

FDI_INT

AE2

FDI_COMPIO

AE1

FDI_ICOMPO

PE115527-4041-0DF

PE115527-4041-0DF

FDI

FDI

4/10

4/10

FDI_TX0

FDI_TX0*

FDI_TX1

FDI_TX1*

FDI_TX2

FDI_TX2*

FDI_TX3

FDI_TX3*

FDI_TX4

FDI_TX4*

FDI_TX5

FDI_TX5*

FDI_TX6

FDI_TX6*

FDI_TX7

FDI_TX7*

AC8

AC7

AC2

AC3

AD2

AD1

AD4

AD3

AD7

AD6

AE7

AE8

AF3

AF2

AG2

AG1

4

X_1X16_RXP[15..0]38

X_1X16_RXN[15..0]38

H_FDI_TXP0 25

H_FDI_TXN0 25

H_FDI_TXP1 25

H_FDI_TXN1 25

H_FDI_TXP2 25

H_FDI_TXN2 25

H_FDI_TXP3 25

H_FDI_TXN3 25

H_FDI_TXP4 25

H_FDI_TXN4 25

H_FDI_TXP5 25

H_FDI_TXN5 25

H_FDI_TXP6 25

H_FDI_TXN6 25

H_FDI_TXP7 25

H_FDI_TXN7 25

3

X_1X16_RXP0

X_1X16_RXN0

X_1X16_RXP1

X_1X16_RXN1

X_1X16_RXP2

X_1X16_RXN2

X_1X16_RXP3

X_1X16_RXN3

X_1X16_RXP4

X_1X16_RXN4

X_1X16_RXP5

X_1X16_RXN5

X_1X16_RXP6

X_1X16_RXN6

X_1X16_RXP7

X_1X16_RXN7

X_1X16_RXP8

X_1X16_RXN8

X_1X16_RXP9

X_1X16_RXN9

X_1X16_RXP10

X_1X16_RXN10

X_1X16_RXP11

X_1X16_RXN11

X_1X16_RXP12

X_1X16_RXN12

X_1X16_RXP13

X_1X16_RXN13

X_1X16_RXP14

X_1X16_RXN14

X_1X16_RXP15

X_1X16_RXN15

B11

B12

D12

D11

C10

E10

C9

E9

B8

B7

C6

C5

A5

A6

E2

E1

G2

G1

H3

H4

K3

K4

M3

M4

N1

N2

F4

F3

J1

J2

L1

L2

UH1C

UH1C

PEG_RX0

PEG_RX0*

PEG_RX1

PEG_RX1*

PEG_RX2

PEG_RX2*

PEG_RX3

PEG_RX3*

PEG_RX4

PEG_RX4*

PEG_RX5

PEG_RX5*

PEG_RX6

PEG_RX6*

PEG_RX7

PEG_RX7*

PEG_RX8

PEG_RX8*

PEG_RX9

PEG_RX9*

PEG_RX10

PEG_RX10*

PEG_RX11

PEG_RX11*

PEG_RX12

PEG_RX12*

PEG_RX13

PEG_RX13*

PEG_RX14

PEG_RX14*

PEG_RX15

PEG_RX15*

PEG

PEG

PEG_TX0

PEG_TX0*

PEG_TX1

PEG_TX1*

PEG_TX2

PEG_TX2*

PEG_TX3

PEG_TX3*

PEG_TX4

PEG_TX4*

PEG_TX5

PEG_TX5*

PEG_TX6

PEG_TX6*

PEG_TX7

PEG_TX7*

PEG_TX8

PEG_TX8*

PEG_TX9

PEG_TX9*

PEG_TX10

PEG_TX10*

PEG_TX11

PEG_TX011

PEG_TX12

PEG_TX12*

PEG_TX13

PEG_TX13*

PEG_TX14

PEG_TX14*

PEG_TX15

PEG_TX15*

C13

C14

E14

E13

G14

G13

F12

F11

J14

J13

D8

D7

D3

C3

E6

E5

F8

F7

G10

G9

G5

G6

K7

K8

J5

J6

M8

M7

L6

L5

N5

N6

2

X_1X16_TXP0

X_1X16_TXN0

X_1X16_TXP1

X_1X16_TXN1

X_1X16_TXP2

X_1X16_TXN2

X_1X16_TXP3

X_1X16_TXN3

X_1X16_TXP4

X_1X16_TXN4

X_1X16_TXP5

X_1X16_TXN5

X_1X16_TXP6

X_1X16_TXN6

X_1X16_TXP7

X_1X16_TXN7

X_1X16_TXP8

X_1X16_TXN8

X_1X16_TXP9

X_1X16_TXN9

X_1X16_TXP10

X_1X16_TXN10

X_1X16_TXP11

X_1X16_TXN11

X_1X16_TXP12

X_1X16_TXN12

X_1X16_TXP13

X_1X16_TXN13

X_1X16_TXP14

X_1X16_TXN14

X_1X16_TXP15

X_1X16_TXN15

1

X_1X16_TXP[15..0] 38

X_1X16_TXN[15..0] 38

H_DMI_RXP022

H_DMI_RXN022

H_DMI_RXP122

H_DMI_RXN122

H_DMI_RXP222

H_DMI_RXN222

H_DMI_RXP322

H_DMI_RXN322

B B

A A

W5

DMI_RX0

W4

DMI_RX0*

V3

DMI_RX1

V4

DMI_RX1*

Y3

DMI_RX2

Y4

DMI_RX2*

AA4

DMI_RX3

AA5

DMI_RX3*

P3

PE_RX0

P4

PE_RX0*

R2

PE_RX1

R1

PE_RX1*

T4

PE_RX2

T3

PE_RX2*

U2

PE_RX3

U1

PE_RX3*

PE115527-4041-0DF

PE115527-4041-0DF

3/10

3/10

DMI

DMI

GEN

GEN

PEG_COMPI

PEG_ICOMPO

PEG_RCOMPO

DMI_TX0

DMI_TX0*

DMI_TX1

DMI_TX1*

DMI_TX2

DMI_TX2*

DMI_TX3

DMI_TX3*

PE_TX0

PE_TX0*

PE_TX1

PE_TX1*

PE_TX2

PE_TX2*

PE_TX3

PE_TX3*

V7

V6

W7

W8

Y6

Y7

AA7

AA8

P8

P7

T7

T8

R6

R5

U5

U6

B4

B5

C4

RH42 24.9

RH42 24.9

*

*

+/-1%

+/-1%

H_DMI_TXP0 22

H_DMI_TXN0 22

H_DMI_TXP1 22

H_DMI_TXN1 22

H_DMI_TXP2 22

H_DMI_TXN2 22

H_DMI_TXP3 22

H_DMI_TXN3 22

+1P05V_VCCIO

Title

Title

Title

CPU-2: FDI/PCIe/DMI

CPU-2: FDI/PCIe/DMI

DWG NO Rev

DWG NO Rev

DWG NO Rev

Date: Sheet

Date: Sheet of

5

4

3

2

Date: Sheet of

CPU-2: FDI/PCIe/DMI

Lanikai _MT/DT

Lanikai _MT/DT

Lanikai _MT/DT

10 71Wednesday, June 13, 2012

10 71Wednesday, June 13, 2012

10 71Wednesday, June 13, 2012

1

A00

A00

A00

of

5

D D

C C

1 2

D3_RESET#15,16,17,18

Add RC

filter;CRB

0.7-11/30/09

B B

A A

5

RH8 DummyRH8 Dummy

CH47

CH47

*

*

0.1uF

0.1uF

Dummy

Dummy

16V, X7R, +/-10%

16V, X7R, +/-10%

4

UH1A

D3_MAA[15..0]15,16

D3_WEA#15,16

D3_CASA#15,16

D3_RASA#15,16

D3_BAA[2..0]15,16

D3_SCS_A#015

D3_SCS_A#115

D3_SCS_A#216

D3_SCS_A#316

D3_CKE_A015

D3_CKE_A115

D3_CKE_A216

D3_CKE_A316

D3_ODT_A015

D3_ODT_A115

D3_ODT_A216

D3_ODT_A316

D3_MA_CLK015

D3_MA_CLK#015

D3_MA_CLK115

D3_MA_CLK#115

D3_MA_CLK216

D3_MA_CLK#216

D3_MA_CLK316

D3_MA_CLK#316

H_DRAMPWRGD24

D3_DQS_A815,16

D3_DQS_A#815,16

D3_ECC_CB_A[7..0]15,16

4

D3_MAA0

D3_MAA1

D3_MAA2

D3_MAA3

D3_MAA4

D3_MAA5

D3_MAA6

D3_MAA7

D3_MAA8

D3_MAA9

D3_MAA10

D3_MAA11

D3_MAA12

D3_MAA13

D3_MAA14

D3_MAA15

D3_BAA0

D3_BAA1

D3_BAA2

RH51 120Ohm

RH51 120Ohm

*

*

+/-5%

+/-5%

H_SM_VREF

D3_ECC_CB_A0

D3_ECC_CB_A1

D3_ECC_CB_A2

D3_ECC_CB_A3

D3_ECC_CB_A4

D3_ECC_CB_A5

D3_ECC_CB_A6

D3_ECC_CB_A7

UH1A

AV27

SA_MA0

AY24

SA_MA1

AW24

SA_MA2

AW23

SA_MA3

AV23

SA_MA4

AT24

SA_MA5

AT23

SA_MA6

AU22

SA_MA7

AV22

SA_MA8

AT22

SA_MA9

AV28

SA_MA10

AU21

SA_MA11

AT21

SA_MA12

AW32

SA_MA13

AU20

SA_MA14

AT20

SA_MA15

AW29

SA_WE*

AV30

SA_CAS*

AU28

SA_RAS*

AY29

SA_BS0

AW28

SA_BS1

AV20

SA_BS2

AU29

SA_CS0*

AV32

SA_CS1*

AW30

SA_CS2*

AU33

SA_CS3*

AV19

SA_CKE0

AT19

SA_CKE1

AU18

SA_CKE2

AV18

SA_CKE3

AV31

SA_ODT0

AU32

SA_ODT1

AU30

SA_ODT2

AW33

SA_ODT3

AY25

SA_CK0

AW25

SA_CK0*

AU24

SA_CK1

AU25

SA_CK1*

AW27

SA_CK2

AY27

SA_CK2*

AV26

SA_CK3

AW26

SA_CK3*

AW18

SM_DRAMRST*

AJ19

SM_DRAMPWROK

AJ22

SM_VREF

AV13

SA_DQS8

AV12

SA_DQS8*

AU12

SA_ECC_CB0

AU14

SA_ECC_CB1

AW13

SA_ECC_CB2

AY13

SA_ECC_CB3

AU13

SA_ECC_CB4

AU11

SA_ECC_CB5

AY12

SA_ECC_CB6

AW12

SA_ECC_CB7

PE115527-4041-0DF

PE115527-4041-0DF

3

DDR_A

DDR_A

1/10

1/10

3

SA_DQS0

SA_DQS0*

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQS1

SA_DQS1*

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQS2

SA_DQS2*

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQS3

SA_DQS3*

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQS4

SA_DQS4*

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQS5

SA_DQS5*

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQS6

SA_DQS6*

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQS7

SA_DQS7*

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

AK3

AK2

AJ3

AJ4

AL3

AL4

AJ2

AJ1

AL2

AL1

AP3

AP2

AN1

AN4

AR3

AR4

AN2

AN3

AR2

AR1

AW4

AV4

AV2

AW3

AV5

AW5

AU2

AU3

AU5

AY5

AV8

AW8

AY7

AU7

AV9

AU9

AV7

AW7

AW9

AY9

AV37

AV36

AU35

AW37

AU39

AU36

AW35

AY36

AU38

AU37

AP38

AP39

AR40

AR37

AN38

AN37

AR39

AR38

AN39

AN40

AK38

AK39

AL40

AL37

AJ38

AJ37

AL39

AL38

AJ39

AJ40

AF38

AF39

AG40

AG37

AE38

AE37

AG39

AG38

AE39

AE40

D3_DQ_A0

D3_DQ_A1

D3_DQ_A2

D3_DQ_A3

D3_DQ_A4

D3_DQ_A5

D3_DQ_A6

D3_DQ_A7

D3_DQ_A8

D3_DQ_A9

D3_DQ_A10

D3_DQ_A11

D3_DQ_A12

D3_DQ_A13

D3_DQ_A14

D3_DQ_A15

D3_DQ_A16

D3_DQ_A17

D3_DQ_A18

D3_DQ_A19

D3_DQ_A20

D3_DQ_A21

D3_DQ_A22

D3_DQ_A23

D3_DQ_A24

D3_DQ_A25

D3_DQ_A26

D3_DQ_A27

D3_DQ_A28

D3_DQ_A29

D3_DQ_A30

D3_DQ_A31

D3_DQ_A32

D3_DQ_A33

D3_DQ_A34

D3_DQ_A35

D3_DQ_A36

D3_DQ_A37

D3_DQ_A38

D3_DQ_A39

D3_DQ_A40

D3_DQ_A41

D3_DQ_A42

D3_DQ_A43

D3_DQ_A44

D3_DQ_A45

D3_DQ_A46

D3_DQ_A47

D3_DQ_A48

D3_DQ_A49

D3_DQ_A50

D3_DQ_A51

D3_DQ_A52

D3_DQ_A53

D3_DQ_A54

D3_DQ_A55

D3_DQ_A56

D3_DQ_A57

D3_DQ_A58

D3_DQ_A59

D3_DQ_A60

D3_DQ_A61

D3_DQ_A62

D3_DQ_A63

2

D3_DQS_A0 15,16

D3_DQS_A#0 15,16

D3_DQ_A[63..0] 15,16

D3_DQS_A1 15,16

D3_DQS_A#1 15,16

D3_DQS_A2 15,16

D3_DQS_A#2 15,16

D3_DQS_A3 15,16

D3_DQS_A#3 15,16

D3_DQS_A4 15,16

D3_DQS_A#4 15,16

D3_DQS_A5 15,16

D3_DQS_A#5 15,16

D3_DQS_A6 15,16

D3_DQS_A#6 15,16

D3_DQS_A7 15,16

D3_DQS_A#7 15,16

2

1

+1P5V_SM

RH43

RH43

*

*

100 Ohm

100 Ohm

+/-1%

+/-1%

H_SM_VREF

CH3

CH3

RH44

0.1uF

0.1uF

RH44

*

*

100 Ohm

100 Ohm

+/-1%

+/-1%

RH43,RH44 is 1k

in PDG; 100 in

CRB

11 71Wednesday, June 13, 2012

11 71Wednesday, June 13, 2012

11 71Wednesday, June 13, 2012

1

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

RH43,RH44 usage 100 Ohm follow CRB;

CRB 0.7-12/10/09

Title

Title

Title

CPU-3: DDR3_CHA

CPU-3: DDR3_CHA

DWG NO Rev

DWG NO Rev

DWG NO Rev

Date: Sheet

Date: Sheet of

Date: Sheet of

CPU-3: DDR3_CHA

Lanikai _MT/DT

Lanikai _MT/DT

Lanikai _MT/DT

A00

A00

A00

of

5

D3_MAB[15..0]17,18

D D

D3_WEB#17,18

D3_CASB#17,18

D3_RASB#17,18

D3_BAB[2..0]17,18

D3_SCS_B#017

D3_SCS_B#117

D3_SCS_B#218

D3_SCS_B#318

D3_CKE_B017

D3_CKE_B117

D3_CKE_B218

D3_CKE_B318

C C

B B

A A

D3_ODT_B017

D3_ODT_B117

D3_ODT_B218

D3_ODT_B318

D3_MB_CLK017

D3_MB_CLK#017

D3_MB_CLK117

D3_MB_CLK#117

D3_MB_CLK218

D3_MB_CLK#218

D3_MB_CLK318

D3_MB_CLK#318

D3_DQS_B817,18

D3_DQS_B#817,18

D3_ECC_CB_B[7..0]17,18

5

D3_MAB0

D3_MAB1

D3_MAB2

D3_MAB3

D3_MAB4

D3_MAB5

D3_MAB6

D3_MAB7

D3_MAB8

D3_MAB9

D3_MAB10

D3_MAB11

D3_MAB12

D3_MAB13

D3_MAB14

D3_MAB15

D3_BAB0

D3_BAB1

D3_BAB2

D3_ECC_CB_B0

D3_ECC_CB_B1

D3_ECC_CB_B2

D3_ECC_CB_B3

D3_ECC_CB_B4

D3_ECC_CB_B5

D3_ECC_CB_B6

D3_ECC_CB_B7

AK24

AM20

AM19

AK18

AP19

AP18

AM18

AL18

AN18

AY17

AN23

AU17

AT18

AR26

AY16

AV16

AR25

AK25

AP24

AP23

AM24

AW17

AN25

AN26

AL25

AT26

AU16

AY15

AW15

AV15

AL26

AP26

AM26

AK26

AL21

AL22

AL20

AK20

AL23

AM22

AP21

AN21

AN16

AN15

AL16

AM16

AP16

AR16

AL15

AM15

AR15

AP15

4

UH1B

UH1B

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_WE*

SB_CAS*

SB_RAS*

SB_BS0

SB_BS1

SB_BS2

SB_CS0*

SB_CS1*

SB_CS2*

SB_CS3*

SB_CKE0

SB_CKE1

SB_CKE2

SB_CKE3

SB_ODT0

SB_ODT1

SB_ODT2

SB_ODT3

SB_CK0

SB_CK0*

SB_CK1

SB_CK1*

SB_CK2

SB_CK2*

SB_CK3

SB_CK3*

SB_DQS8

SB_DQS8*

SB_ECC_CB0

SB_ECC_CB1

SB_ECC_CB2

SB_ECC_CB3

SB_ECC_CB4

SB_ECC_CB5

SB_ECC_CB6

SB_ECC_CB7

PE115527-4041-0DF

PE115527-4041-0DF

4

DDR_B

DDR_B

2/10

2/10

SB_DQS0

SB_DQS0*

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQS1

SB_DQS1*

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQS2

SB_DQS2*

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQS3

SB_DQS3*

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQS4

SB_DQS4*

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQS5

SB_DQS5*

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQS6

SB_DQS6*

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQS7

SB_DQS7*

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

AH7

AH6

AG7

AG8

AJ9

AJ8

AG5

AG6

AJ6

AJ7

AM8

AL8

AL7

AM7

AM10

AL10

AL6

AM6

AL9

AM9

AR8

AP8

AP7

AR7

AP10

AR10

AP6

AR6

AP9

AR9

AN13

AN12

AM12

AM13

AR13

AP13

AL12

AL13

AR12

AP12

AN29

AN28

AR28

AR29

AL28

AL29

AP28

AP29

AM28

AM29

AP33

AR33

AP32

AP31

AP35

AP34

AR32

AR31

AR35

AR34

AL33

AM33

AM32

AM31

AL35

AL32

AM34

AL31

AM35

AL34

AG35

AG34

AH35

AH34

AE34

AE35

AJ35

AJ34

AF33

AF35

D3_DQ_B0

D3_DQ_B1

D3_DQ_B2

D3_DQ_B3

D3_DQ_B4

D3_DQ_B5

D3_DQ_B6

D3_DQ_B7

D3_DQ_B13

D3_DQ_B9

D3_DQ_B11

D3_DQ_B15

D3_DQ_B12

D3_DQ_B8

D3_DQ_B14

D3_DQ_B10

D3_DQ_B16

D3_DQ_B17

D3_DQ_B18

D3_DQ_B19

D3_DQ_B20

D3_DQ_B21

D3_DQ_B22

D3_DQ_B23

D3_DQ_B24

D3_DQ_B25

D3_DQ_B26

D3_DQ_B27

D3_DQ_B28

D3_DQ_B29

D3_DQ_B30

D3_DQ_B31

D3_DQ_B32

D3_DQ_B33

D3_DQ_B34

D3_DQ_B35

D3_DQ_B36

D3_DQ_B37

D3_DQ_B38

D3_DQ_B39

D3_DQ_B40

D3_DQ_B41

D3_DQ_B42

D3_DQ_B43

D3_DQ_B44

D3_DQ_B45

D3_DQ_B46

D3_DQ_B47

D3_DQ_B48

D3_DQ_B52

D3_DQ_B55

D3_DQ_B51

D3_DQ_B54

D3_DQ_B49

D3_DQ_B53

D3_DQ_B50

D3_DQ_B56

D3_DQ_B57

D3_DQ_B58

D3_DQ_B59

D3_DQ_B60

D3_DQ_B61

D3_DQ_B62

D3_DQ_B63

3

D3_DQS_B0 17,18

D3_DQS_B#0 17,18

D3_DQ_B[63..0] 17,18

D3_DQS_B1 17,18

D3_DQS_B#1 17,18

DQ REMAPPING IMPLEMENTED

TO IMPROVE BREAKOUT AND

MINIMIZE CH-2-CH COUPLING

D3_DQS_B2 17,18

D3_DQS_B#2 17,18

D3_DQS_B3 17,18

D3_DQS_B#3 17,18

D3_DQS_B4 17,18

D3_DQS_B#4 17,18

D3_DQS_B5 17,18

D3_DQS_B#5 17,18

D3_DQS_B6 17,18

D3_DQS_B#6 17,18

DQ REMAPPING IMPLEMENTED

TO IMPROVE BREAKOUT AND

MINIMIZE CH-2-CH COUPLING

D3_DQS_B7 17,18

D3_DQS_B#7 17,18

3

2

Title

Title

Title

CPU-4: DDR3_CHB

CPU-4: DDR3_CHB

DWG NO Rev

DWG NO Rev

DWG NO Rev

Date: Sheet

Date: Sheet of

2

Date: Sheet of

CPU-4: DDR3_CHB

Lanikai _MT/DT

Lanikai _MT/DT

Lanikai _MT/DT

1

A00

A00

A00

of

12 71Wednesday, June 13, 2012

12 71Wednesday, June 13, 2012

12 71Wednesday, June 13, 2012

1

5

+VCORE

UH1F

UH1F

A12

VCC_1

A13

VCC_2

A14

VCC_3

A15

VCC_4

A16

VCC_5

D D

C C

B B

A18

VCC_6

A24

VCC_7

A25

VCC_8

A27

VCC_9

A28

VCC_10

B15

VCC_11

B16

VCC_12

B18

VCC_13

B24

VCC_14

B25

VCC_15

B27

VCC_16

B28

VCC_17

B30

VCC_18

B31

VCC_19

B33

VCC_20

B34

VCC_21

C15

VCC_22

C16

VCC_23

C18

VCC_24

C19

VCC_25

C21

VCC_26

C22

VCC_27

C24

VCC_28

C25

VCC_29

C27

VCC_30

C28

VCC_31

C30

VCC_32

C31

VCC_33

C33

VCC_34

C34

VCC_35

C36

VCC_36

D13

VCC_37

D14

VCC_38

D15

VCC_39

D16

VCC_40

D18

VCC_41

D19

VCC_42

D21

VCC_43

D22

VCC_44

D24

VCC_45

D25

VCC_46

D27

VCC_47

D28

VCC_48

D30

VCC_49

D31

VCC_50

D33

VCC_51

D34

VCC_52

D35

VCC_53

D36

VCC_54

E15

VCC_55

E16

VCC_56

E18

VCC_57

E19

VCC_58

E21

VCC_59

E22

VCC_60

E24

VCC_61

E25

VCC_62

E27

VCC_63

E28

VCC_64

E30

VCC_65

E31

VCC_66

E33

VCC_67

E34

VCC_68

E35

VCC_69

F15

VCC_70

F16

VCC_71

F18

VCC_72

F19

VCC_73

F21

VCC_74

F22

VCC_75

F24

VCC_76

F25

VCC_77

F27

VCC_78

F28

VCC_79

F30

VCC_80

PE115527-4041-0DF

PE115527-4041-0DF

CPU POWER

CPU POWER

6/10

6/10

VCC_81

VCC_82

VCC_83

VCC_84

VCC_85

VCC_86

VCC_87

VCC_88

VCC_89

VCC_90

VCC_91

VCC_92

VCC_93

VCC_94

VCC_95

VCC_96

VCC_97

VCC_98

VCC_99

VCC_100

VCC_101

VCC_102

VCC_103

VCC_104

VCC_105

VCC_106

VCC_107

VCC_108

VCC_109

VCC_110

VCC_111

VCC_112

VCC_113

VCC_114

VCC_115

VCC_116

VCC_117

VCC_118

VCC_119

VCC_120

VCC_121

VCC_122

VCC_123

VCC_124

VCC_125

VCC_126

VCC_127

VCC_128

VCC_129

VCC_130

VCC_131

VCC_132

VCC_133

VCC_134

VCC_135

VCC_136

VCC_137

VCC_138

VCC_139

VCC_140

VCC_141

VCC_142

VCC_143

VCC_144

VCC_145

VCC_146

VCC_147

VCC_148

VCC_149

VCC_150

VCC_151

VCC_152

VCC_153

VCC_154

VCC_155

VCC_156

VCC_157

VCC_158

VCC_159

VCC_160

VCC_161

F31

F32

F33

F34

G15

G16

G18

G19

G21

G22

G24

G25

G27

G28

G30

G31

G32

G33

H13

H14

H15

H16

H18

H19

H21

H22

H24

H25

H27

H28

H30

H31

H32

J12

J15

J16

J18

J19

J21

J22

J24

J25

J27

J28

J30

K15

K16

K18

K19

K21

K22

K24

K25

K27

K28

K30

L13

L14

L15

L16

L18

L19

L21

L22

L24

L25

L27

L28

L30

M14

M15

M16

M18

M19

M21

M22

M24

M25

M27

M28

M30

4

+1P05V_VCCIO +1P5V_SM

UH1G

UH1G

A11

VCCIO_1

A7

VCCIO_2

AA3

VCCIO_3

AB8

VCCIO_4

AF8

VCCIO_5

AG33

VCCIO_6

AJ16

VCCIO_7

AJ17

VCCIO_8

AJ26

VCCIO_9

AJ28

VCCIO_10

AJ32

VCCIO_11

AK15

VCCIO_12

AK17

VCCIO_13

AK19

VCCIO_14

AK21

VCCIO_15

AK23

VCCIO_16

AK27

VCCIO_17

AK29

VCCIO_18

AK30

VCCIO_19

B9

VCCIO_20

D10

VCCIO_21

D6

VCCIO_22

E3

VCCIO_23

E4

VCCIO_24

G3

VCCIO_25

G4

VCCIO_26

J3

VCCIO_27

J4

VCCIO_28

J7

VCCIO_29

J8

VCCIO_30

L3

VCCIO_31

L4

VCCIO_32

L7

VCCIO_33

M13

VCCIO_34

N3

VCCIO_35

N4

VCCIO_36

N7

VCCIO_37

R3

VCCIO_38

R4

VCCIO_39

R7

VCCIO_40

U3

VCCIO_41

U4

VCCIO_42

U7

VCCIO_43

V8

VCCIO_44

W3

VCCIO_45

7/10

7/10

PE115527-4041-0DF

PE115527-4041-0DF

3

H10

VCCSA_1

H11

VCCSA_2

H12

VCCSA_3

J10

VCCSA_4

K10

VCCSA_5

K11

VCCSA_6

L11

VCCSA_7

L12

VCCSA_8

M10

VCCSA_9

M11

VCCSA_10

M12

VCCSA_11

CPU POWER

CPU POWER

AK11

VCCPLL_1

AK12

VCCPLL_2

+V_VCCSA

+1P8V_SFR

CH4

CH4

*

*

1uF

1uF

16V, X5R, +/-10%

16V, X5R, +/-10%

+1P1V_AXG

2

UH1H

UH1H

AB33

VAXG_1

AB34

VAXG_2

AB35

VAXG_3

AB36

VAXG_4

AB37

VAXG_5

AB38

VAXG_6

AB39

VAXG_7

AB40

VAXG_8

AC33

VAXG_9

AC34

VAXG_10

AC35

VAXG_11

AC36

VAXG_12

AC37

VAXG_13

AC38

VAXG_14

AC39

VAXG_15

AC40

VAXG_16

T33

VAXG_17

T34

VAXG_18

T35

VAXG_19

T36

VAXG_20

T37

VAXG_21

T38

VAXG_22

T39

VAXG_23

T40

VAXG_24

U33

VAXG_25

U34

VAXG_26

U35

VAXG_27

U36

VAXG_28

U37

VAXG_29

U38

VAXG_30

U39

VAXG_31

U40

VAXG_32

W33

VAXG_33

W34

VAXG_34

W35

VAXG_35

W36

VAXG_36

W37

VAXG_37

W38

VAXG_38

Y33

VAXG_39

Y34

VAXG_40

Y35

VAXG_41

Y36

VAXG_42

Y37

VAXG_43

Y38

VAXG_44

CH5

CH5

*

*

*

*

4.7uF

4.7uF

6.3V, X5R, +/-10%

6.3V, X5R, +/-10%

MCH POWER

MCH POWER

8/10

8/10

PE115527-4041-0DF

PE115527-4041-0DF

CH6

CH6

CH7

CH7

*

*

0.1uF

0.1uF

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

16V, X7R, +/-10%

16V, X7R, +/-10%

VDDQ_1

VDDQ_2

VDDQ_3

VDDQ_6

VDDQ_4

VDDQ_5

VDDQ_7

VDDQ_8

VDDQ_9

VDDQ_10

VDDQ_11

VDDQ_12

VDDQ_13

VDDQ_14

VDDQ_15

VDDQ_16

VDDQ_17

VDDQ_18

VDDQ_19

VDDQ_20

VDDQ_21

VDDQ_22

VDDQ_23

AJ13

AJ14

AJ20

AJ23

AJ24

AR20

AR21

AR22

AR23

AR24

AU19

AU23

AU27

AU31

AV21

AV24

AV25

AV29

AV33

AW31

AY23

AY26

AY28

1

+1P5V_SM+1P05V_VCCIO

CH9

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

CH9

*

*

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

CH8

CH8

*

*

22uF

22uF

CLOSE TO CPU CLOSE TO CPU

A A

Title

Title

Title

CPU-5: Power

CPU-5: Power

DWG NO Rev

DWG NO Rev

DWG NO Rev

Date: Sheet

Date: Sheet of

5

4

3

2

Date: Sheet of

CPU-5: Power

Lanikai _MT/DT

Lanikai _MT/DT

Lanikai _MT/DT

1

A00

A00

A00

of

13 71Wednesday, June 13, 2012

13 71Wednesday, June 13, 2012

13 71Wednesday, June 13, 2012

5

UH1I

UH1I

A17

VSS_1

A23

VSS_2

A26

VSS_3

A29

VSS_4

A35

VSS_5

AA33

VSS_6

AA34

VSS_7

D D

C C

B B

A A

AA35

AA36

AA37

AA38

AA6

AB5

AC1

AC6

AD33

AD36

AD38

AD39

AD40

AD5

AD8

AE3

AE33

AE36

AF1

AF34

AF36

AF37

AF40

AF5

AF6

AF7

AG36

AH2

AH3

AH33

AH36

AH37

AH38

AH39

AH40

AH5

AH8

AJ12

AJ15

AJ18

AJ21

AJ25

AJ27

AJ36

AJ5

AK1

AK10

AK13

AK14

AK16

AK22

AK28

AK31

AK32

AK33

AK34

AK35

AK36

AK37

AK4

AK40

AK5

AK6

AK7

AK8

AK9

AL11

AL14

AL17

AL19

AL24

AL27

AL30

AL36

AL5

AM1

AM11

AM14

AM17

AM2

AM21

AM23

AM25

5

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

9/10

9/10

PE115527-4041-0DF

PE115527-4041-0DF

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

GND

GND

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

AM27

AM3

AM30

AM36

AM37

AM38

AM39

AM4

AM40

AM5

AN10

AN11

AN14

AN17

AN19

AN22

AN24

AN27

AN30

AN31

AN32

AN33

AN34

AN35

AN36

AN5

AN6

AN7

AN8

AN9

AP1

AP11

AP14

AP17

AP22

AP25

AP27

AP30

AP36

AP37

AP4

AP40

AP5

AR11

AR14

AR17

AR18

AR19

AR27

AR30

AR36

AR5

AT1

AT10

AT12

AT13

AT15

AT16

AT17

AT2

AT25

AT27

AT28

AT29

AT3

AT30

AT31

AT32

AT33

AT34

AT35

AT36

AT37

AT38

AT39

AT4

AT40

AT5

AT6

AT7

4

B39 update to RSVD48;

PDG 0.7-12/07/09

EDS: B39 defined "VSS_NCTF"

CRB: B39 defined "RSVD"

Pin_B39 follow CRB pin define;

CRB 0.7-12/10/09

4

TPH99TPH99

AT8

AT9

AU1

AU15

AU26

AU34

AU4

AU6

AU8

AV10

AV11

AV14

AV17

AV3

AV35

AV38

AV6

AW10

AW11

AW14

AW16

AW36

AW6

AY11

AY14

AY18

AY35

AY4

AY6

AY8

C11

C12

C17

C20

C23

C26

C29

C32

C35

D17

D20

D23

D26

D29

D32

D37

D39

AV39

AY37

B10

B13

B14

B17

B23

B26

B29

B32

B35

B38

E11

E12

E17

E20

E23

E26

E29

E32

E36

F10

F13

F14

F17

F20

F23

F26

F29

F35

B39

B6

C7

C8

D2

D4

D5

D9

E7

E8

F1

F2

A4

B3

3

UH1J

UH1J

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

VSS_180

VSS_181

VSS_182

VSS_183

VSS_184

VSS_185

VSS_186

VSS_187

VSS_188

VSS_189

VSS_190

VSS_191

VSS_192

VSS_193

VSS_194

VSS_195

VSS_196

VSS_197

VSS_198

VSS_199

VSS_200

VSS_201

VSS_202

VSS_203

VSS_204

VSS_205

VSS_206

VSS_207

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

VSS_213

VSS_214

VSS_215

VSS_216

VSS_217

VSS_218

VSS_219

VSS_220

VSS_221

VSS_222

VSS_223

VSS_224

VSS_225

VSS_226

VSS_227

VSS_228

VSS_229

VSS_230

VSS_231

VSS_232

VSS_233

VSS_234

VSS_235

VSS_236

VSS_237

VSS_238

VSS_239

VSS_240

VSS_241

VSS_242

VSS_243

VSS_244

VSS_245

VSS_246

VSS_247

VSS_248

VSS_249

VSS_250

VSS_251

VSS_252

VSS_253

VSS_254

VSS_255

VSS_256

RSVD48

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

10/10

10/10

PE115527-4041-0DF

PE115527-4041-0DF

3

VSS_257

VSS_258

VSS_259

VSS_260

VSS_261

VSS_262

VSS_263

VSS_264

VSS_265

VSS_266

VSS_267

VSS_268

VSS_269

VSS_270

VSS_271

VSS_272

VSS_273

VSS_274

VSS_275

VSS_276

VSS_277

VSS_278

VSS_279

VSS_280

VSS_281

VSS_282

VSS_283

VSS_284

VSS_285

VSS_286

VSS_287

VSS_288

VSS_289

VSS_290

VSS_291

VSS_292

VSS_293

VSS_294

VSS_295

VSS_296

VSS_297

VSS_298

VSS_299

VSS_300

VSS_301

VSS_302

VSS_303

VSS_304

GND

GND

VSS_305

VSS_306

VSS_307

VSS_308

VSS_309

VSS_310

VSS_311

VSS_312

VSS_313

VSS_314

VSS_315

VSS_316

VSS_317

VSS_318

VSS_319

VSS_320

VSS_321

VSS_322

VSS_323

VSS_324

VSS_325

VSS_326

VSS_327

VSS_328

VSS_329

VSS_330

VSS_331

VSS_332

VSS_333

VSS_334

VSS_335

VSS_336

VSS_337

VSS_338

VSS_339

VSS_340

VSS_341

VSS_342

VSS_343

VSS_344

VSS_345

VSS_346

VSS_347

VSS_348

VSS_349

VSS_350

VSS_351

VSS_352

VSS_353

VSS_354

VSS_355

VSS_356

VSS_357

VSS_358

VSS_359

VSS_360

F37

F39

F5

F6

F9

G11

G12

G17

G20

G23

G26

G29

G34

G7

G8

H1

H17

H2

H20

H23

H26

H29

H33

H35

H37

H39

H5

H6

H9

J11

J17

J20

J23

J26

J29

J32

K1

K12

K13

K14

K17

K2

K20

K23

K26

K29

K33

K35

K37

K39

K5

K6

L10

L17

L20

L23

L26

L29

L8

M1

M17

M2

M20

M23

M26

M29

M33

M35

M37

M39

M5

M6

M9

N8

P1

P2

P36

P38

P40

P5

P6

R33

R35

R37

R39

R8

T1

T5

T6

U8

V1

V2

V33

V34

V35

V36

V37

V38

V39

V40

V5

W6

Y5

Y8

2

UH1_1

UH1_1

Retention Module

Retention Module

MLH1MLH1

Title

Title

Title

DWG NO Rev

DWG NO Rev

DWG NO Rev

Date: Sheet

Date: Sheet of

2

Date: Sheet of

ACA-ZIF-078-P05_A

ACA-ZIF-078-P05_A

2D lable

2D lable

MLH2MLH2 MLH3MLH3 MLH4MLH4

CPU-6: GND

CPU-6: GND

CPU-6: GND

Lanikai _MT/DT

Lanikai _MT/DT

Lanikai _MT/DT

UH1_B

UH1_B

<LBL>

<LBL>

1

A00

A00

A00

of

14 71Wednesday, June 13, 2012

14 71Wednesday, June 13, 2012

14 71Wednesday, June 13, 2012

1

5

CHANNEL A BANK 1

SMB ADDRESS:000

D3_ECC_CB_A[7..0] 11,16

4

D3_DQS_A8 11,16

D3_DQS_A#8 11,16

3

2

1

143

144

DQS11

DQS10

DM2/DQS11

D3_DQS_A[7..0] 11,16

D3_DQS_A#[7..0] 11,16

212

203

152

153

DM3/DQS12

DQS12

204

DQS13

DM4/DQS13

+1P5V_SM

213

DQS14

DM5/DQS14

D3_DQ_A[63..0] 11,16

D3_DQ_A63

D3_DQ_A62

D3_DQ_A61

D3_DQ_A60

D3_DQ_A59

D3_DQ_A58

D3_DQ_A57

D3_DQ_A56

D3_DQ_A55

D3_DQ_A54

D3_DQ_A53

D3_DQ_A52

D3_DQ_A51

D3_DQ_A50

D3_DQ_A49

D3_DQ_A48

D3_DQ_A47

D3_DQ_A46

D3_DQ_A45

D3_DQ_A44

D3_DQ_A43

D3_DQ_A42

D3_DQ_A41

D3_DQ_A40

D3_DQ_A39

D3_DQ_A38

D3_DQ_A37

D3_DQ_A36

D3_DQ_A35

D3_DQ_A34

D3_DQ_A33

D3_DQ_A32

D3_DQ_A31

D3_DQ_A30

D3_DQ_A29

D3_DQ_A28

D3_DQ_A27

D3_DQ_A26

D3_DQ_A25

D3_DQ_A24

D3_DQ_A23

D3_DQ_A22

D3_DQ_A21

D3_DQ_A20

D3_DQ_A19

D3_DQ_A18

D3_DQ_A17

D3_DQ_A16

D3_DQ_A15

D3_DQ_A14

D3_DQ_A13

D3_DQ_A12

D3_DQ_A11

D3_DQ_A10

D3_DQ_A9

D3_DQ_A8

D3_DQ_A7

D3_DQ_A6

D3_DQ_A5

D3_DQ_A4

D3_DQ_A3

D3_DQ_A2

D3_DQ_A1

D3_DQ_A0

122

123

128

129

13

131

132

137

138

140

141

146

147

149

150

155

156

200

201

206

207

209

210

215

216

100

105

106

218

219

224

225

108

109

114

115

227

228

233

DQ57

A14

171

DQ58

A15

DQ59

168

DQ60

RESET

DQ61

CAS74RAS

192

234

DQ62

73

DQ63

WE

DIMM3

DIMM3

DDRIII

DDRIII

D3_WEA# 11,16

D3_RASA# 11,16

D3_CASA# 11,16

D3_RESET# 11,16,17,18

161

230

221

DM6/DQS15

S_SMBCLK_MAIN16,17,18,32,52

S_SMBDATA_MAIN16,17,18,32,52

162

231

222

DQ03DQ14DQ29DQ310DQ4

DQ5

DQ6

DQ7

DQ812DQ9

DQ1018DQ1119DQ12

DQ13

DQ14

DQ15

DQ1621DQ1722DQ1827DQ1928DQ20

DQ21

DQ22

DQ23

DQ2430DQ2531DQ2636DQ2737DQ28

DQ29

DQ30

DQ31

DQ3281DQ3382DQ3487DQ3588DQ36

DQ37

DQ38

DQ39

DQ4090DQ4191DQ4296DQ4397DQ44

DQ45

DQ46

DQ47

DQ4899DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQS17

DQS15

NC/DQS16

DM8/DQS17

DM7/DQS16

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

197

194

191

189

186

183

182

179

D3_BAA[2..0]11,16

D3_CKE_A111

D3_CKE_A011

D3_SCS_A#111

D3_SCS_A#011

D3_MA_CLK#111

D3_MA_CLK111

D3_MA_CLK#011

D3_MA_CLK011

D3_MAA[15..0]11,16

DDRIII

DDRIII

VDDQ

VDDQ

VDDQ

VDD78VDD75VDD72VDD69VDD66VDD65VDD62VDD60VDD57VDD54VDD51VDDSPD

176

173

170

+3V

D3_CA_VREF_A

D3_DQ_VREF_A

D3_BAA2

D3_BAA1

D3_BAA0

D3_MAA0

D3_MAA1

D3_MAA2

D3_MAA3

D3_MAA4

D3_MAA5

D3_MAA6

D3_MAA7

D3_MAA8

D3_MAA9

D3_MAA10

D3_MAA11

D3_MAA12

D3_MAA13

D3_MAA14

D3_MAA15

SA2

VREFDQ1SCL

SDA

SA1

SA0

BA071BA1

CKE050CKE1

S0

169

S176CK1/NU64CK1/NU63CK0*

193

VREFCA

67

236

118

238

BA2

52

119

237

117

190

CK0

185

184A0188A1181

A261A3

180

A459A558A6

178

A756A9

000

DQ56

A10/AP70A1155A12

A13

A8

175

174

196

177

172

D3_ODT_A1 11

D3_ODT_A0 11

D D

D3_DQS_A#7

D3_DQS_A#6

D3_DQS_A#5

D3_DQS_A#4

D3_DQS_A#3

D3_DQS_A#2

D3_DQS_A#1

D3_DQS_A#0

D3_DQS_A2

D3_DQS_A1

VSS

D3_DQS_A0

D3_ECC_CB_A5

D3_ECC_CB_A6

D3_ECC_CB_A7

24

15

6

159

164

165

DQS225DQS2

DQS116DQS1

DQS07DQS0

CB<5>

CB<6>

CB<7>

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

208

205

202

199

166

163

160

157

154

151

148

145

142

139

D3_ECC_CB_A2

D3_ECC_CB_A3

D3_ECC_CB_A4

D3_ECC_CB_A1

D3_ECC_CB_A0

79

RSVD

C C

FREE1

198

187

+1P5V_SM_VTT

195

ODT177ODT0

FREE2

FREE349FREE4

48

53

167

68

NC/TEST4

NC/PAR_IN

NC/ERR_OUT

VSS

VSS

VSS

VTT

VTT

239

235

232

120

240

229

VSS

VSS

226

223

158

CB<0>39CB<1>40CB<2>45CB<3>46CB<4>

VSS

VSS

VSS

VSS

220

217

214

211

D3_DQS_A3

136

DQS334DQS3

VSS

D3_DQS_A5

D3_DQS_A4

84

33

DQS485DQS4

VSS

VSS

VSS

VSS

VSS

133

130

127

124

121

D3_DQS_A7

D3_DQS_A6

112

103

102

93

DQS6

DQS6

DQS594DQS5

VSS

VSS

VSS

VSS

VSS

116

113

110

107

104

101

125

134

135

126

42

111

DQS9

DQS843DQS8

DQS7

DQS7

DM0/DQS9

DM1/DQS10

VSS

VSS98VSS95VSS92VSS89VSS86VSS83VSS80VSS47VSS44VSS41VSS38VSS35VSS32VSS29VSS26VSS23VSS20VSS17VSS14VSS11VSS8VSS5VSS2VDDQ

CLOSE TO DIMM POWER PIN

+1P5V_SM

CD1

CD1

*

*

1uF

1uF

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

B B

+1P5V_SM_VTT

CD8

CD8

*

*

4.7uF

4.7uF

6.3V, X5R, +/-10%

6.3V, X5R, +/-10%

CD2

CD2

*