Dell Latitude E5450 Schematics

A

COMPAL CONFIDENTIAL

B

C

D

E

1 1

PCB NO :

BOM P/N :

DAA0007U000

4319R031L01 (SMT MB AA901 ZAM70 U W/DOCK I5 1.9G R1)

MODEL NAME :

ZAM70

4319R031L02 (SMT MB AA901 ZAM70 U W/DOCK I3 1.9G R1)

GPIO MAP: 3.6C

2 2

Huston 14" UMA

Broadwell U

2014-03-07

REV : 0.3 (X01)

@ : Nopop Component

EMC@ : EMI, ESD and RF Component

@EMC@ : EMI, ESD and RF Nopop Component

3 3

CXDP@ : XDP Component

VPRO@ : Support VPRO

CONN@ : Connector Component

CPU_QG5M

A

UC1CPU3@

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

B

C

D

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Cover Sheet

Cover Sheet

Cover Sheet

LA-A901P

LA-A901P

LA-A901P

1 53Thursday, March 06, 2014

1 53Thursday, March 06, 2014

1 53Thursday, March 06, 2014

E

0.3

0.3

0.3

UC1CPU1@

CPU_QG22

MB PCB

Part Number

DAA0007U000

Layout Dell logo

4 4

COPYRIGHT 2014

ALL RIGHT RESERVED

REV: X01

PWB: DKNFC

DATE: 1410-06

UC1CPU2@

CPU_QG21

Description

PCB 13D LA-A901P REV0 MB/UMA DOCK 1

A

B

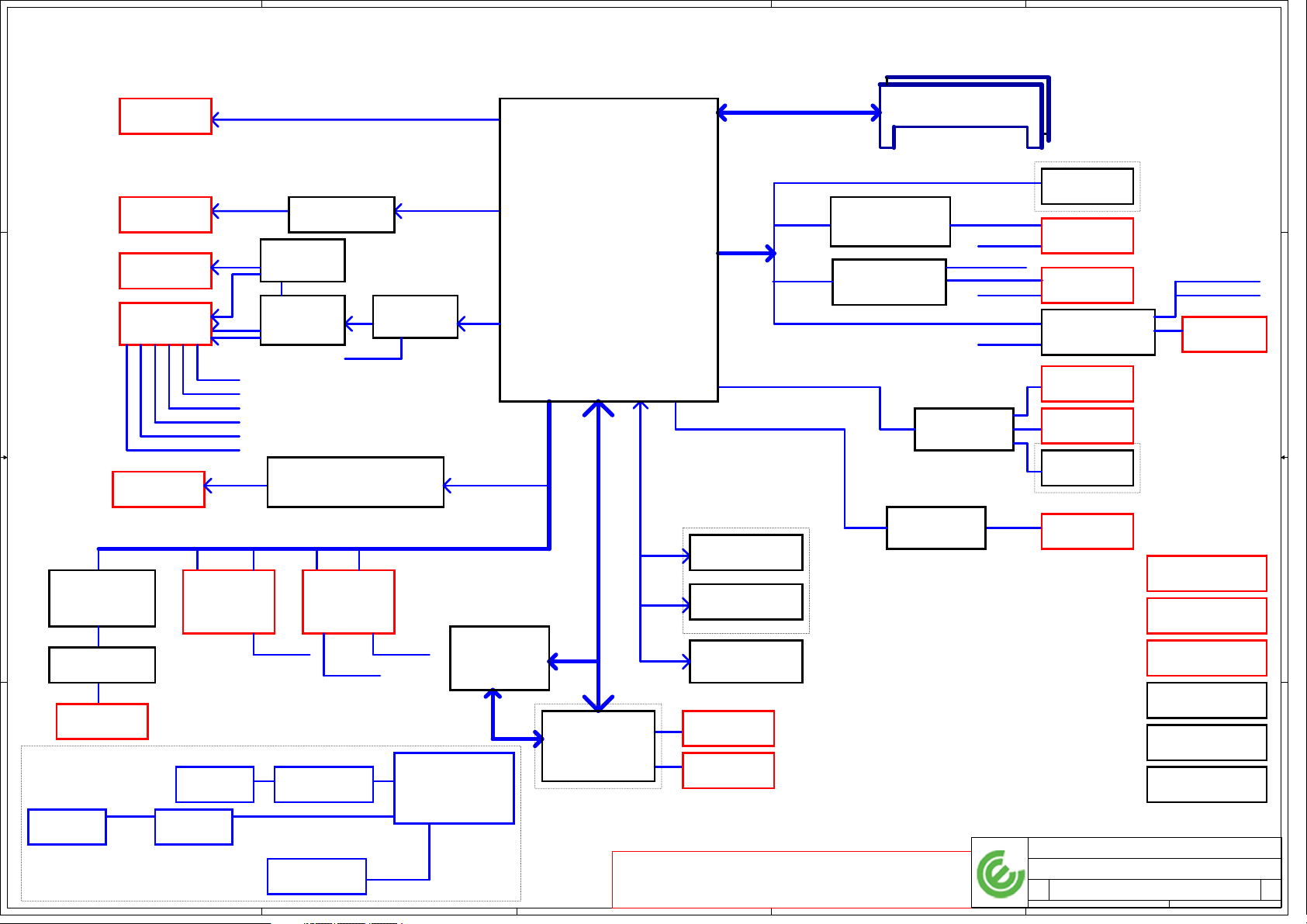

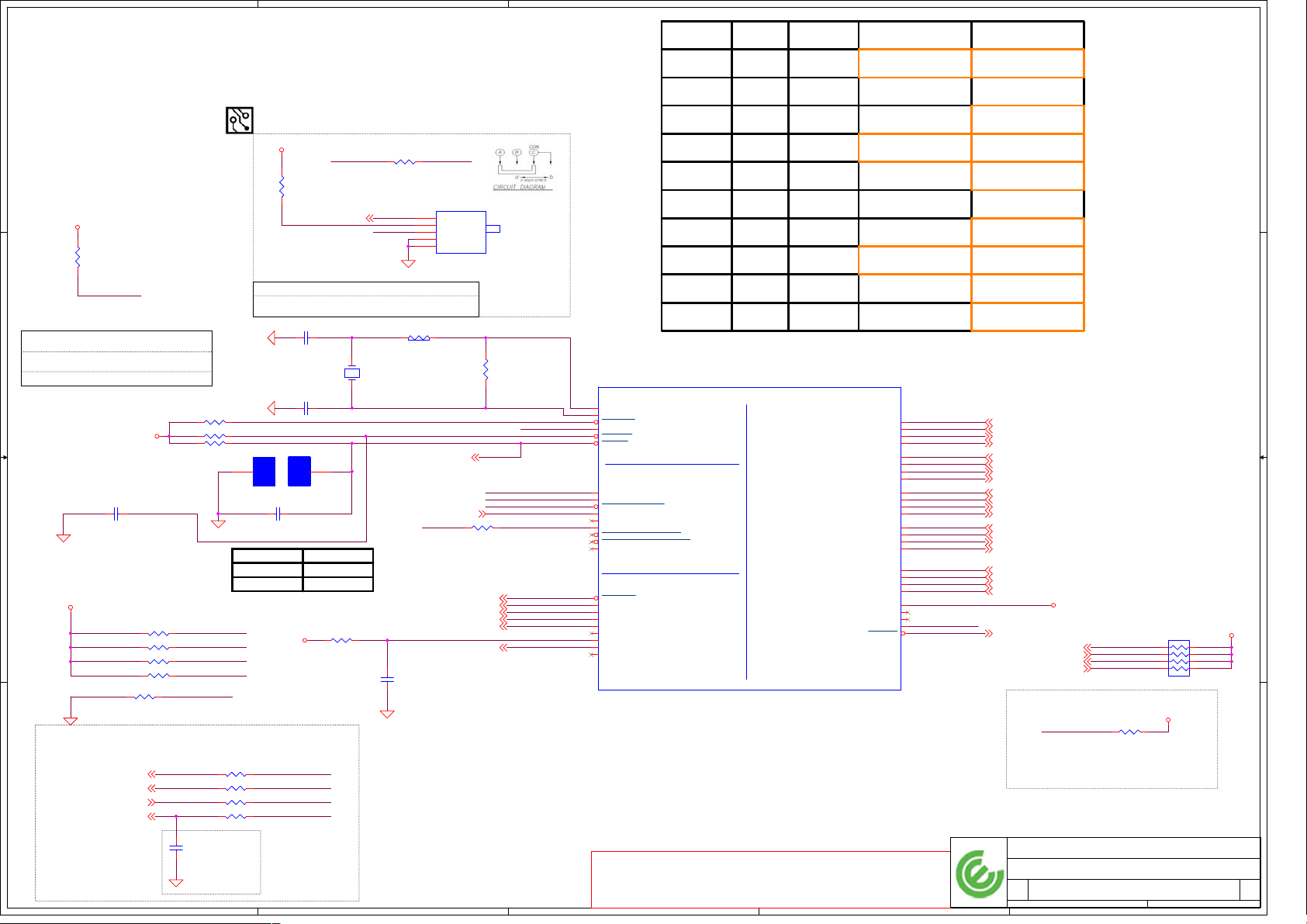

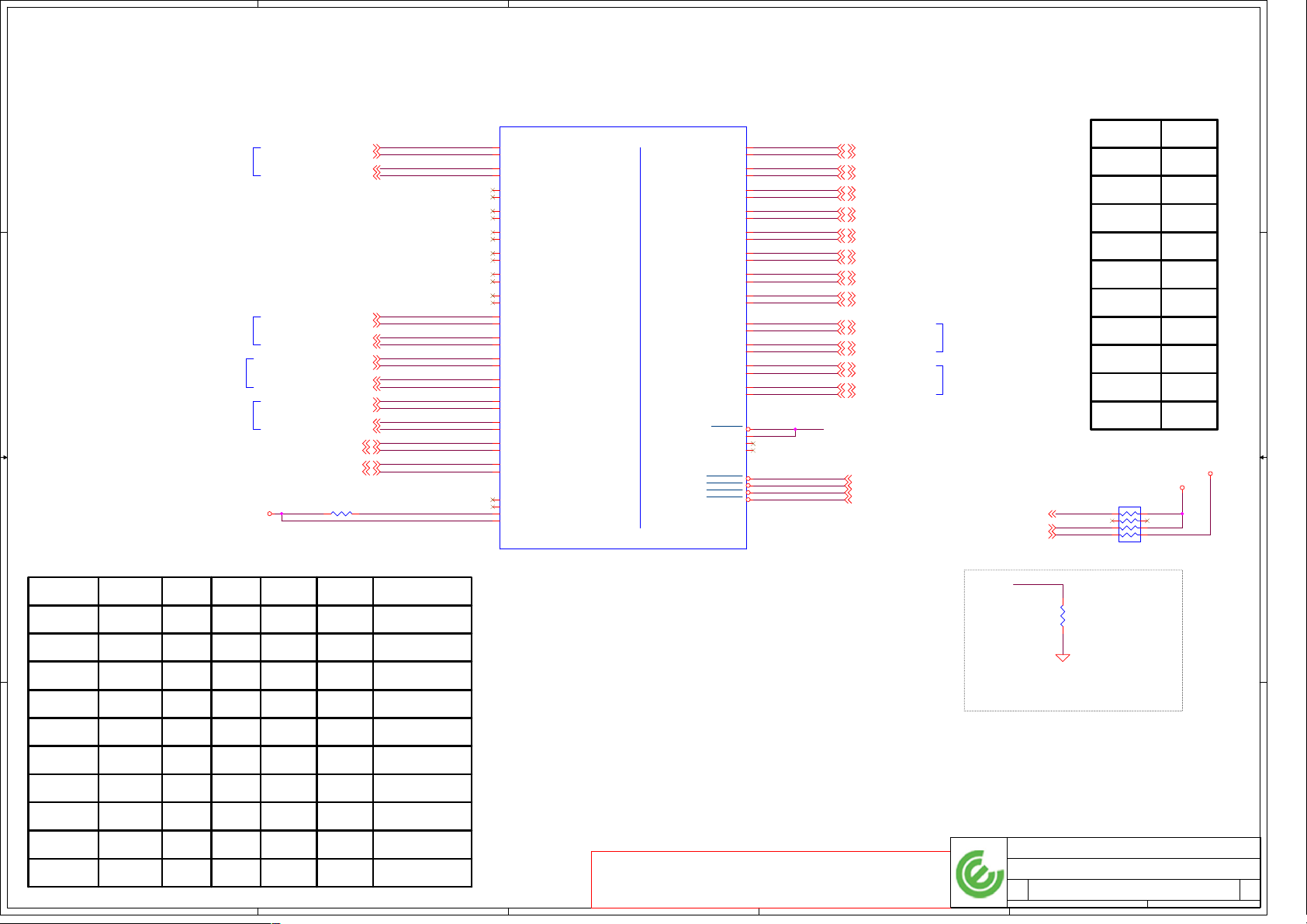

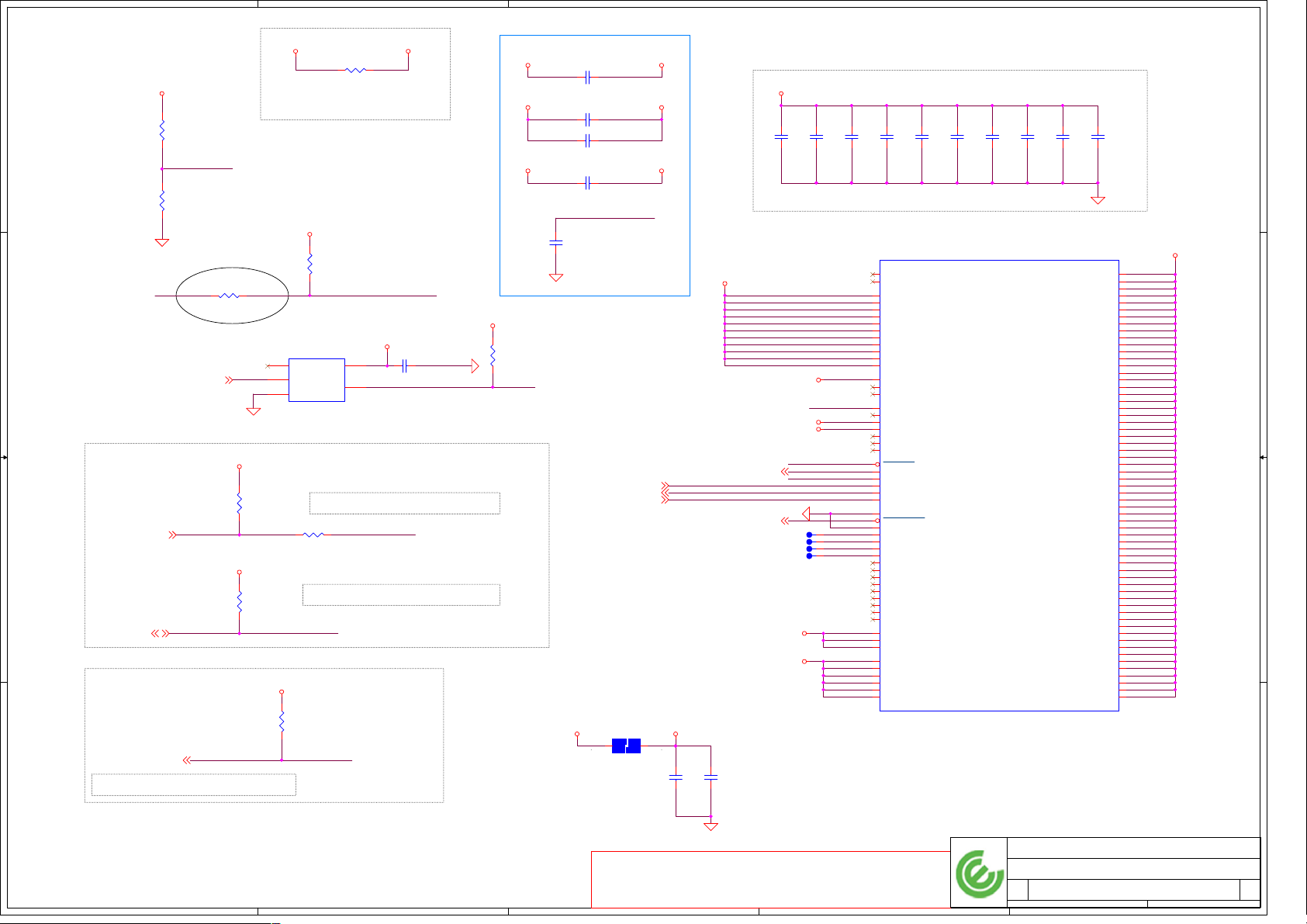

Houston 14 UMA Dock Block Diagram

C

D

E

Reverse Type

Memory BUS (DDR3L)

1 1

eDP CONN

PAGE 23

eDP

1333/1600MHz

INTEL

HDMI CONN

PAGE 24

HDMI

Reduce Level

Shifter

PAGE 24

PI3V713

DP 1.2

PAGE 30

VGA SW

PAGE 26

IDT

VMM3320

PAGE 22

DP

WIGIG_DP

Card reader

O2 Micro OZ777FJ2LN-B

PCIE6_L1

USB2.0[7]

Fingerprint

PCI Express BUS

PCIE4

WLAN/BT/

WIGIG

WIGIG_DP

TDA8034HN

SPI

PCIE5_L0

PAGE 30

USB2.0[2]

FP_USB

PS8338B

DP Sw

VGA CONN

PAGE 26

VGA

E-Dock

PAGE 34

2 2

DAI

LAN

SATA1

DOCK_USB2.0[0]

DOCK_USB2.0[3]

DOCK_USB3.0[1]

SD4.0

PAGE 29 PAGE 29

3 3

PCIE3

Intel Clarkville

I218LM

PAGE 28

Transformer

PAGE 28

RJ45

PAGE 28

PCIE6_L0

SATA

WWAN/LTE

Caching Card

Smart Card

4 4

RFID/NFC

BCM20793

CONN

A

B

DDI1

PAGE 25

USH

TPM1.2

BCM5882

USH board

BROADWELL ULT

DDI2

PCIE1

SMSC SIO

ECE5048

PAGE 35

BC BUS

PAGE 29

LPC

SMSC KBC

MEC5085

PAGE 36

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

PAGE 6~17

SPI

C

USB

HD Audio I/F

SATA1

W25Q64CVSSIQ

64M 4K sector

W25Q32BVSSIQ

32M 4K sector

Discrete TPM

AT97SC3205

KB/TP CONN

PAGE 37

FAN CONN

PAGE 36

USB2.0[1]

USB2.0[3]

PAGE 7

PAGE 27

USB POWER SHARE

USB SW

NX3DV221GM

DDR3L-DIMM X2

BANK 0, 1, 2, 3

TPS2544

PAGE 32

PAGE 31

SATA Repeater

D

PAGE 18 19

USB2.0[1]_PS

DOCK_USB2.0[3]

HDA Codec

ALC3235

PAGE 21

PAGE 20

USB2.0[5]

USB3.0[2]

USB2.0[3]

USB3.0[4]

USB2.0[0]

USB3.0[1]

Camera

PAGE 23

USB3.0/2.0

PS

PAGE 32

USB3.0/2.0

PAGE 31

USB SW

PI3USB3102ZLEX

INT.Speaker

Combo Jack

Dig. MIC

PAGE 31

PAGE 21

PAGE 21

PAGE 23

Trough eDP Cable

DOCK_USB3.0[1]

DOCK_USB2.0[0]

USB3.0/2.0

Trough eDP Cable

SATA3 Conn

PAGE 20

USH CONN

CPU XDP Port

Automatic Power

Switch (APS)

Free Fall sensor

DC/DC Interface

Power On/Off

SW & LED

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Block diagram

Block diagram

Block diagram

LA-A901P

LA-A901P

LA-A901P

2 53Thursday, March 06, 2014

2 53Thursday, March 06, 2014

2 53Thursday, March 06, 2014

E

PAGE 31

PAGE 27

PAGE 9

PAGE 9

PAGE 20

PAGE 38

PAGE 39

0.3

0.3

0.3

5

4

3

2

1

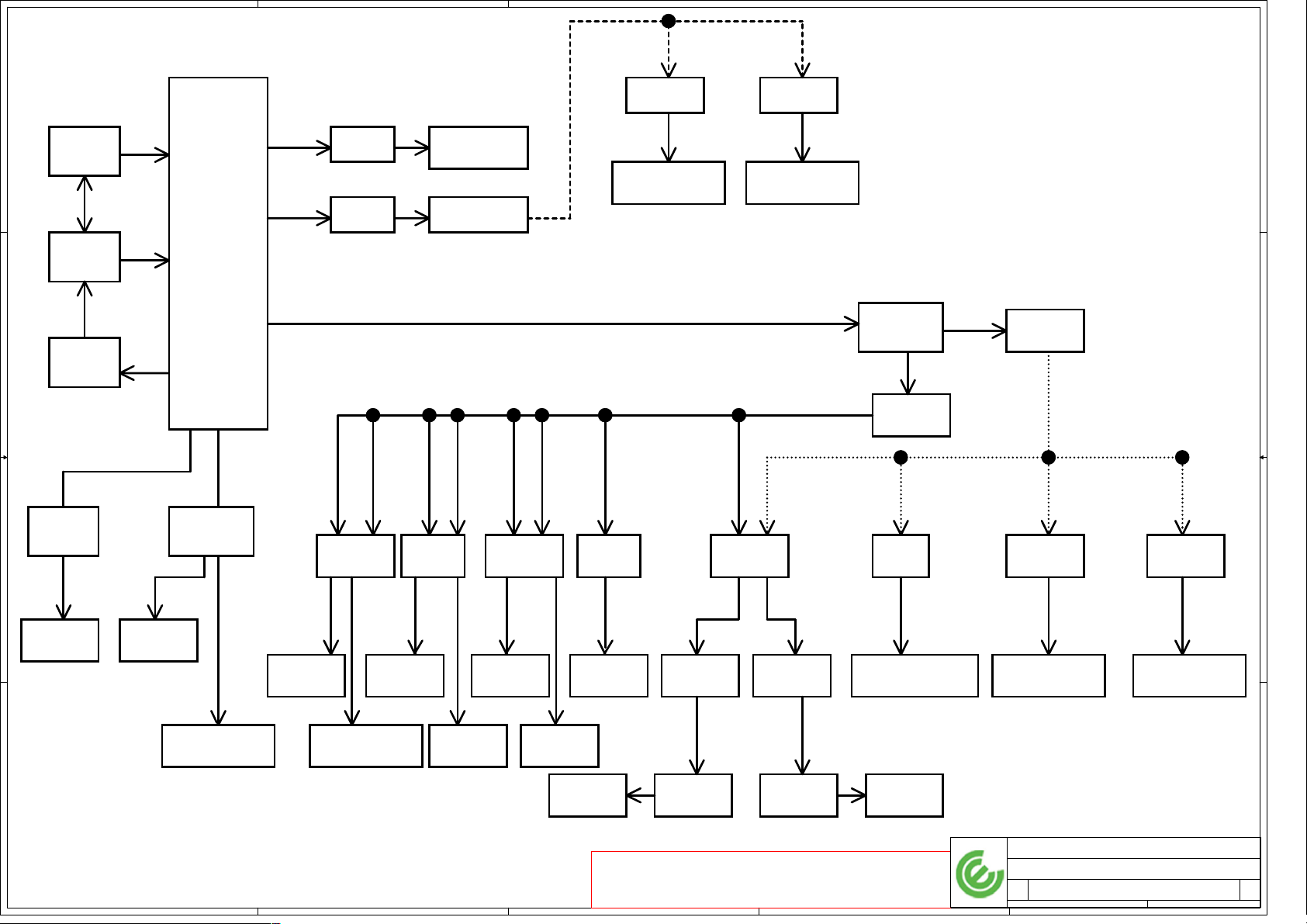

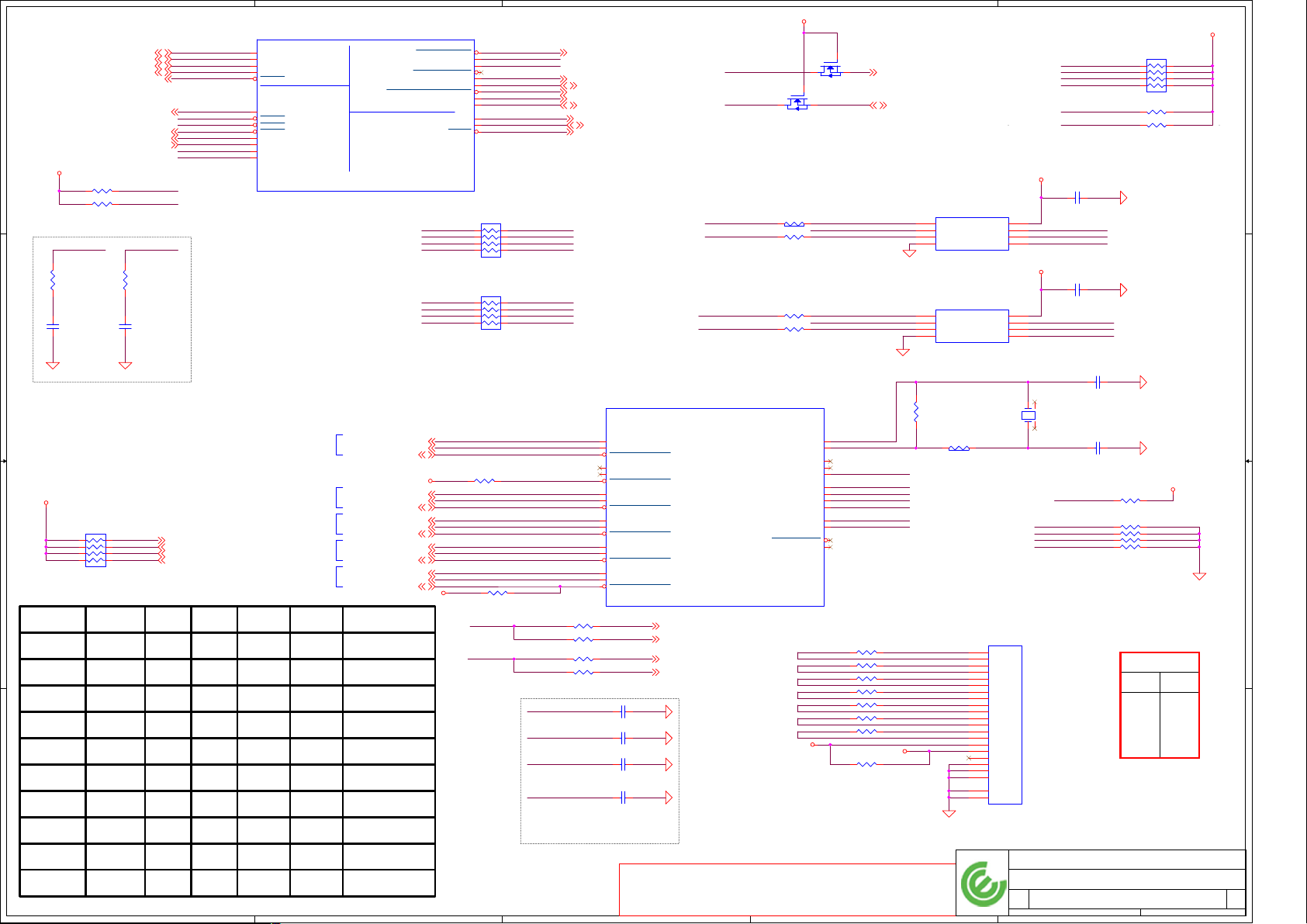

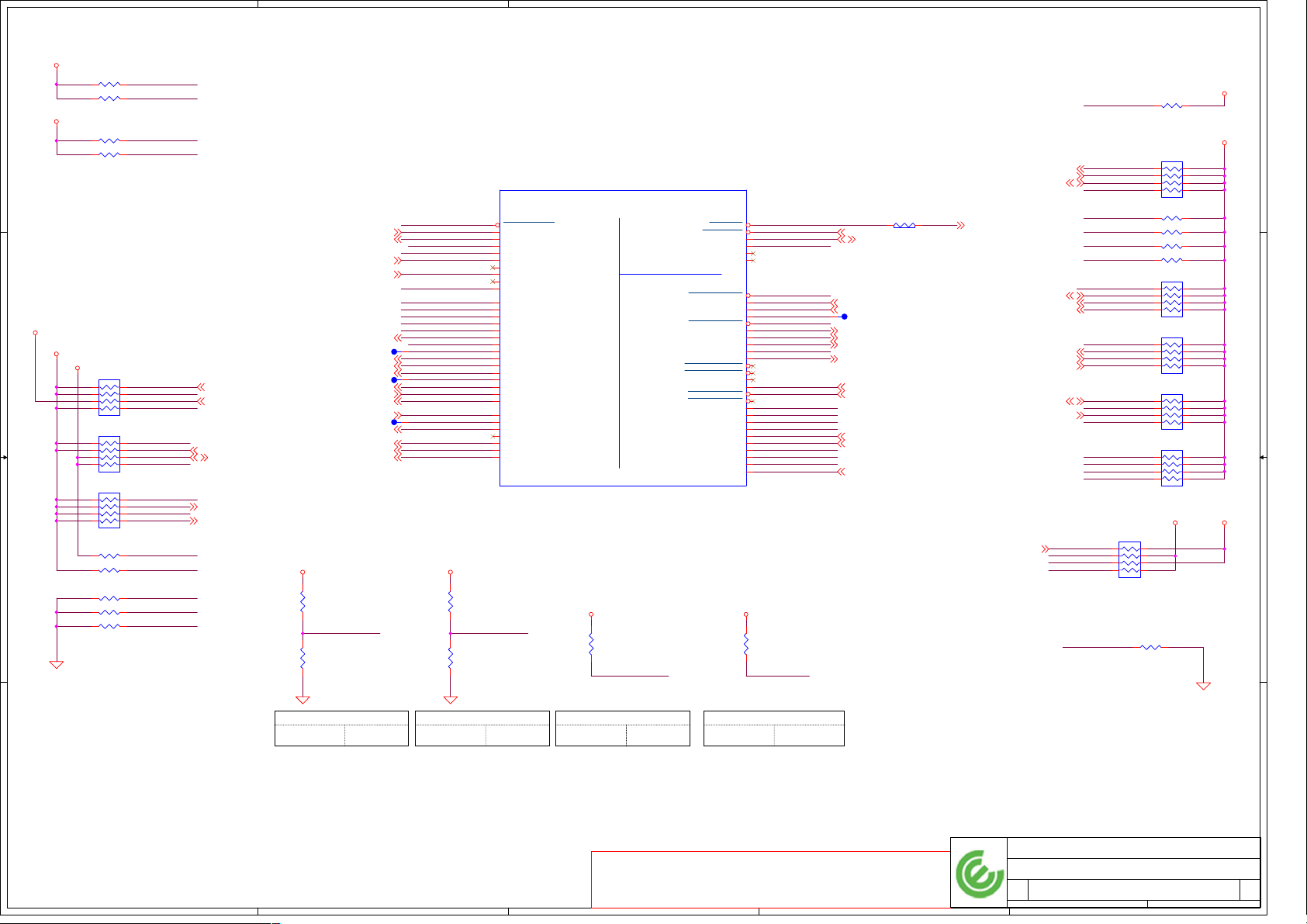

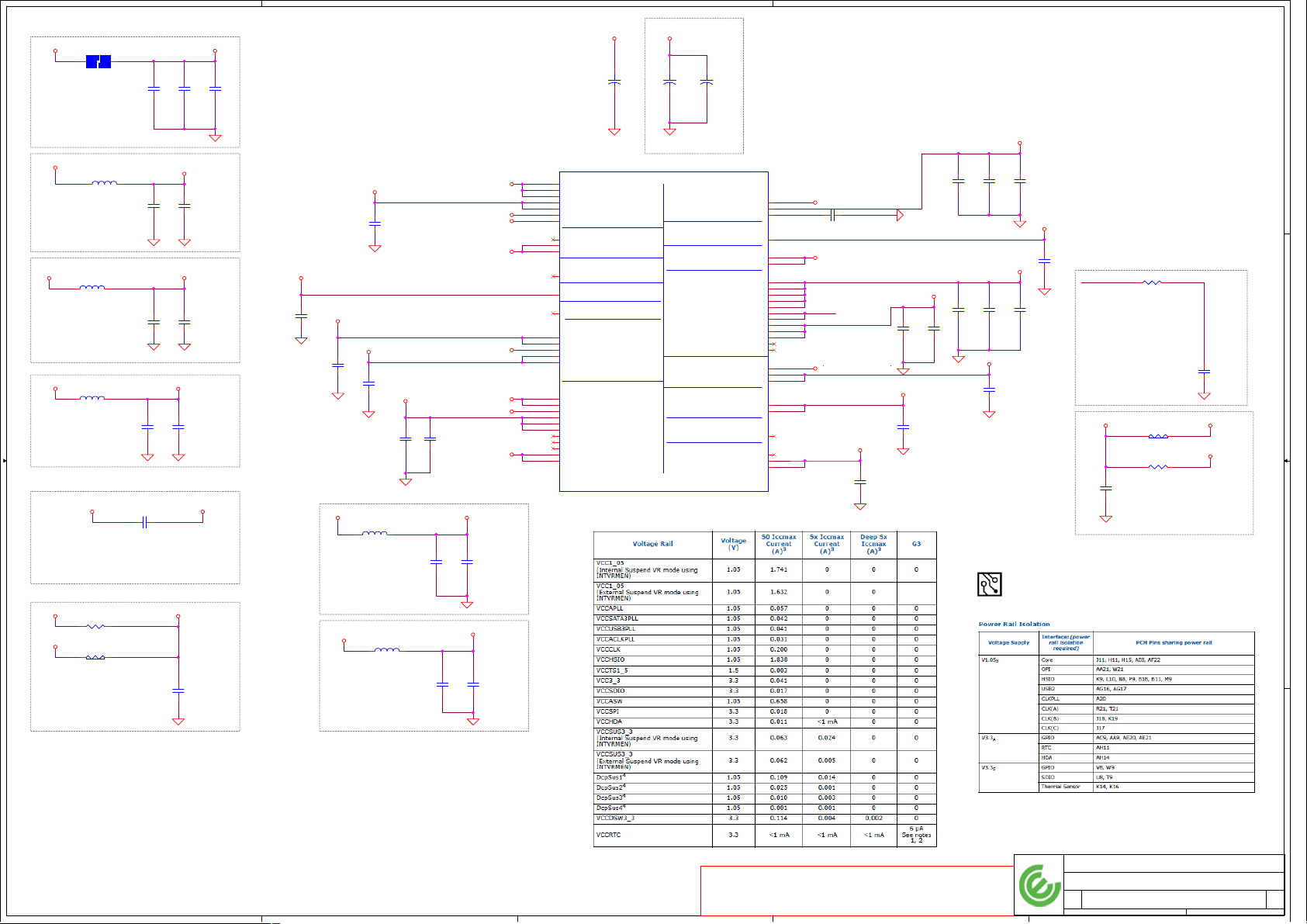

POWER STATES

S

LP

SLP

S3#

S4#

HIGH

HIGH HIGH

LOW HIGH HIGH

LOW

LOW

OW HIGHLOW

LOW HIGH HIGH LOW ON ONOFF OFF OFF

LOW LOW LOW ON OFF OFF OFF OFF

LOW LOW LOW LOW ON OFF OFF OFF OFF

+3.3V_ALW

+3.3V_ALW_PCH

+3.3V_RTC_LDO

power

plane

Signal

State

D D

C C

S0 (Full ON) / M0

S3 (Suspend to RAM) / M3 LOW HIGH HIGH ON ON ON OFF

S4 (Suspend to DISK) / M3 ON ON OFF

S5 (SOFT OFF) / M3 ON ON OFFL

S3 (Suspend to RAM) / M-OFF

S4 (Suspend to DISK) / M-OFF HIGH

S5 (SOFT OFF) / M-OFF

PM TABLE

SLP

SLP

S5#

+3.3V_SUS+5V_ALW +5V_RUN

+1.35V_MEM

ALWAYS

A

PLANE

#

HIGH

HIGH

+0.675V_DDR_VTT

+1.05V_RUN

+VCC_CORE

+1.5V_RUN

ON

M

PLANE

ON

SUS

RUN

PLANE

PLANE

ON ON ON

OFF

OFF

+3.3V_M +3.3V_M

+1.05V_M+3.3V_RUN

+

1.05V_M

(M-OFF)

CLOCKS

OFF

OFF

OFF

PCIE

PCIE 1

PCIE 2

PCIE 3

PCIE 4

PCIE 5

PCIE 6

USB3.0

USB3.0 1

USB3.0 2

USB3.0 3

USB3.0 4

L3

L2

L1

L0

USB PORT#

SATA

SATA 0

SATA 1

SATA 2

SATA 3

DESTINATION

JUSB1-->Rear left

JUSB3-->Right

MMI (CARD READER)

JUSB2-->Rear Right

LOM

WLAN

WIGIG

JDOCK1 (DOCK)

JSATA1 (HDD)

SSD Cache (PCIE)

SSD Cache (SATA/PCIE)/HCA

DESTINATION

State

0

1

S0

B B

S3

S5 S4/AC

S5 S4/AC doesn't exist

ON

ON

ON ON

ON

OFF

OFFOFF

OFFON

OFF

O

FF

need to update Power Status and

PM Table

ON

ON

ON

ON

OFF

OFF

OFFOFF

BDW

ULT

2

3

4

5

6

7

0

JUSB1

JUSB3

WLAN + BT

JUSB2

Touch Screen

CAMERA

USH

WWAN

BIO

USH

A A

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

1

NA

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

Port assignment

Port assignment

Port assignment

LA-A901P

LA-A901P

LA-A901P

3 53Thursday, March 06, 2014

3 53Thursday, March 06, 2014

3 53Thursday, March 06, 2014

1

0.3

0.3

0.3

5

www.vinafix.vn

4

3

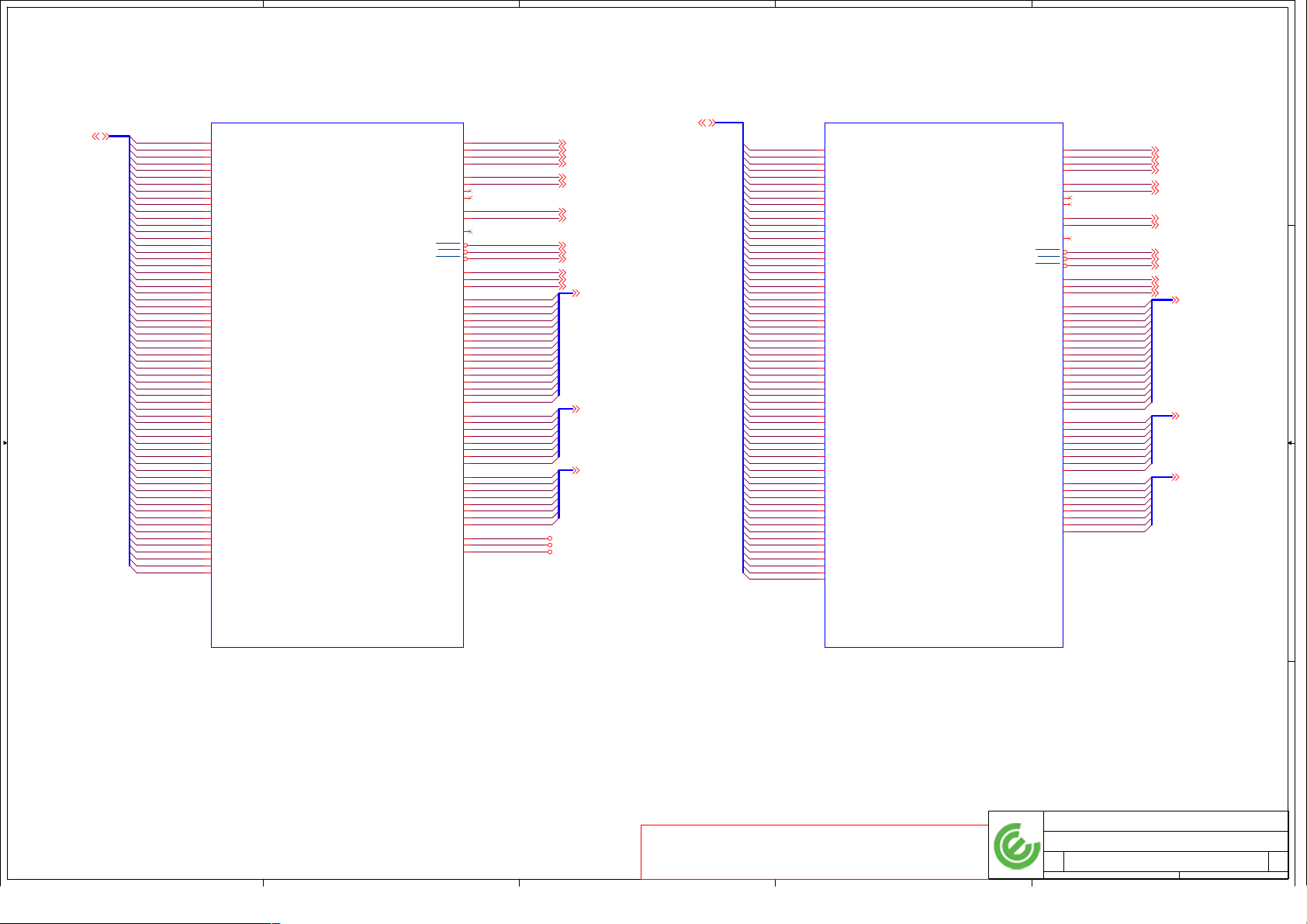

2

1

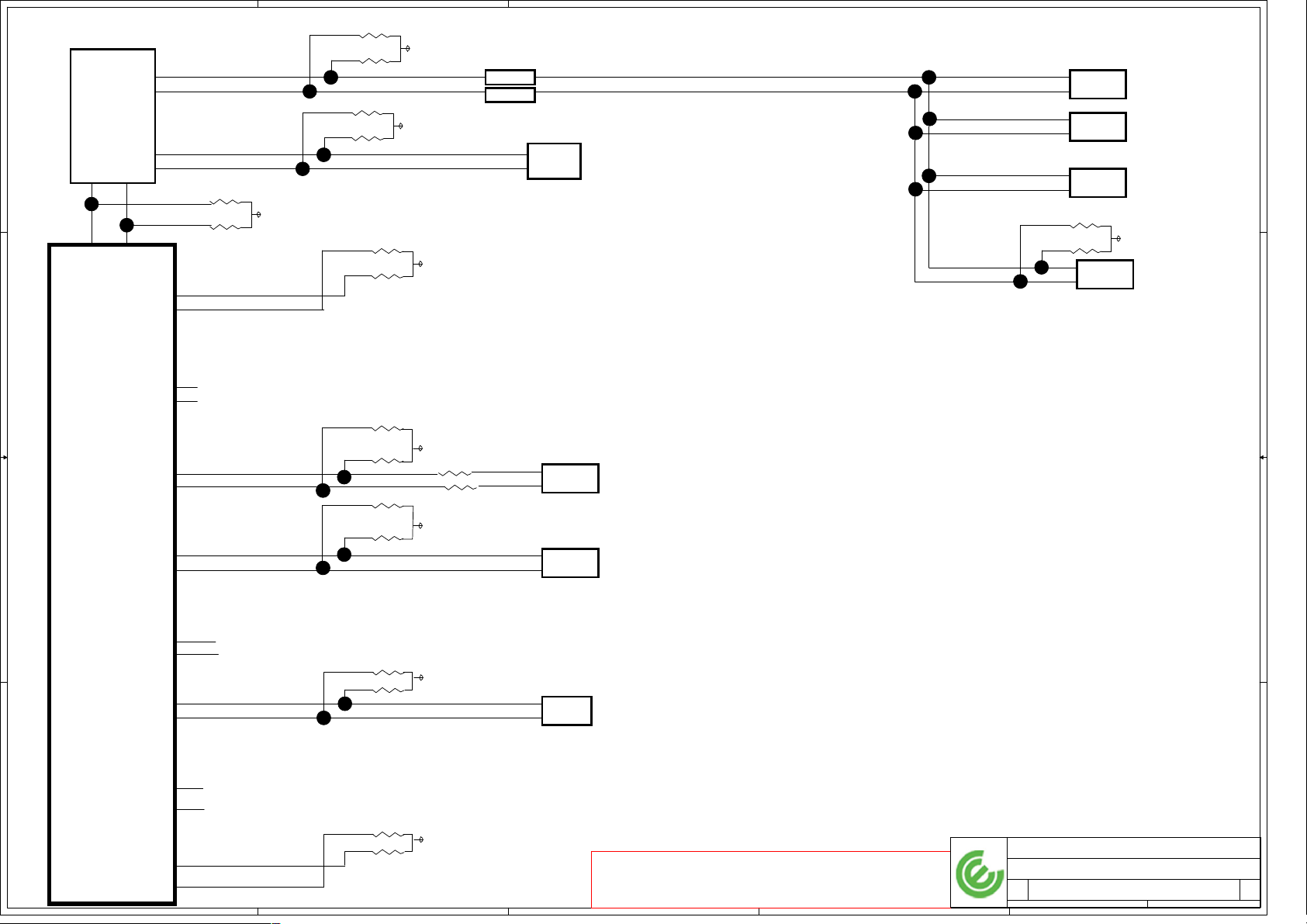

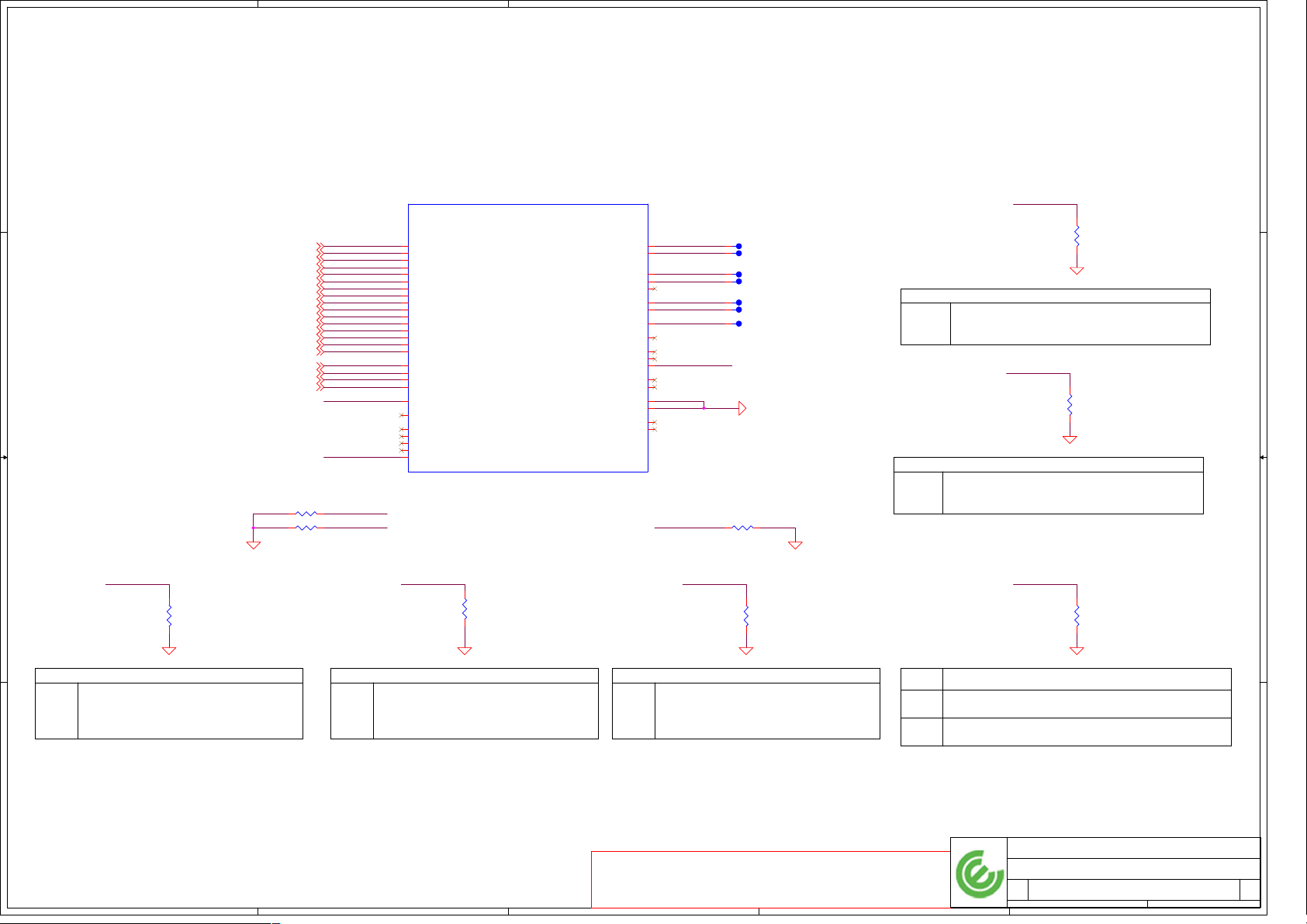

RUN_ON

PS22965

T

(UZ7)

D D

ADAPTER

EN_INVPWR

FDC654P

(QV1)

+BL_PWR_SRC

+1.05V_RUN

A_ON

+

PWR_SRCBATTERY

C C

SY8208

(PU300)

+1.05V_M

MPHYP_PWR_EN

SI3456

(QZ6)

+1.05V_MODPHY

ALWON

TPS51285

(PU100)

+5V_ALW

CHARGER

+3.3V_ALW

A_ON

ISL95813

(PU501)

B B

H_VR_EN

SUS_ON

RT8207

(PU200)

PCH_ALW_ON

TPS22966

(UZ8)

3.3V_WWAN_EN

TPS22966

(UZ2)

SIO_SLP_LAN#

SUS_ON

AUX_EN_WOWL

TPS22966

(UZ3)

EN_LCDPWR

APL3512

(UV24)

RUN_ON

RUN_ON

TPS22966

(UZ9)

USB_PWR_SHR_E N#

TPS2544

(UI3)

USB_PWR_EN1#

G547I2P81U

(

UI1)

USB_PWR_EN2#

G547I2P81U

(UI2)

+VCC_CORE +1.35V_MEM

0.675V_DDR_VTT_ON

0.675V_DDR_VTT

+

A A

+3.3V_WWAN

+3.3V_ALW_PCH

+3.3V_SUS

+3.3V_LAN

+LCDVDD

+3.3V_WLAN

+3.3V_CAM

+3.3V_RUN

3.3V_CAM_EN#

LP2301ALT1G

(QZ1)

+5V_RUN

3.3V_TS_EN

L

P2301ALT1G

(QZ8)

+5V_USB_CHG_PWR +USB_LEFT_PWR

+5V_TSP

+USB_RIGHT_PWR+3.3V_M

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Power rails

Power rails

Power rails

LA-A901P

LA-A901P

LA-A901P

4 53Thursday, March 06, 2014

4 53Thursday, March 06, 2014

4 53Thursday, March 06, 2014

1

0.3

0.3

0.3

5

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

4

3

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

5

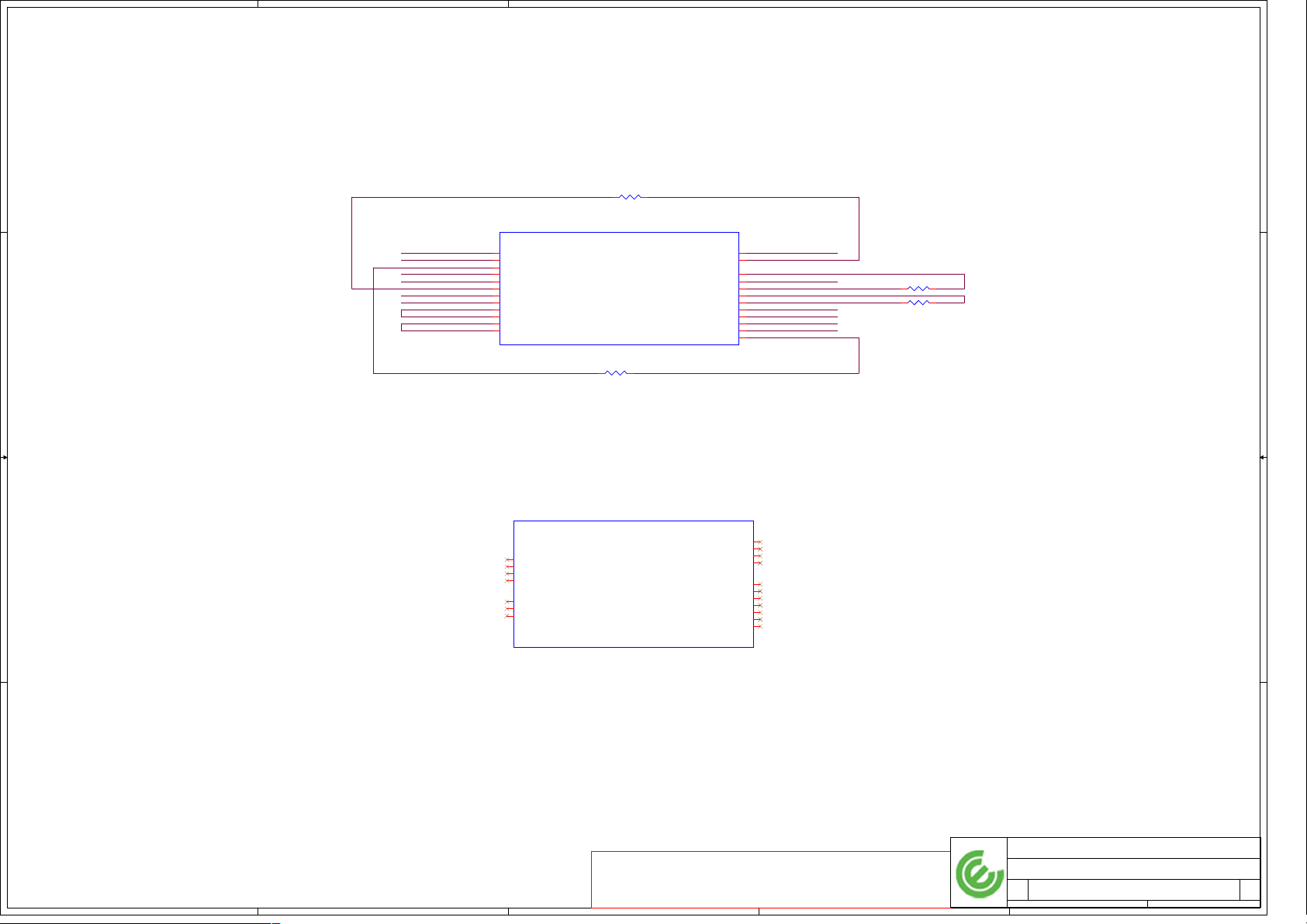

SMBUS Address [0x9a]

B4

A3

B5

A4

MEM_SMBCL K

MEM_SMBDA TA

SML0CLK

SML0DATA

2.2K

2.2K

DOCK_SMB_CLK

DOCK_SMB_DAT

+3.3V_ALW_PCH

AP2

AH1

D D

BDW

AN1

AK1

AU3AH3

SML1_SMBDATA

SML1_SMBCLK

B6A5

3A

3A

1A

1A

C C

1B

1B

499

499

2.2K

2.2K

4

+3.3V_ALW_PCH

2.2K

2.2K

+3.3V_ALW_PCH

+3.3V_ALW

2N7002

2N7002

3

28

31

LOM

2

202

200

202

200

53

51

DIMMA

DIMMB

XDP

1

2.2K

2.2K

4

6

+3.3V_RUN

G Sensor

2.2K

KBC

A56

1C1CB59

PBAT_SMBCLK

2.2K

PBAT_SMBDAT

+3.3V_ALW

100 ohm

100 ohm

7

6

BATTERY

CONN

2.2K

A50

B53

A49

B52

USH_SMBCLK

USH_SMBDAT

B B

MEC 5085

1E

1E

2B

2B

10K

2.2K

B50

A47

B7

A7

CHARGER_SMBCLK

CHARGER_SMBDAT

1G

1G

A A

2D

2D

10K

2.2K

2.2K

B48

B49

GPU_SMBDAT

GPU_SMBCLK

4

2A

2A

5

+3.3V_SUS

+3.3V_ALW

+3.3V_ALW

M9

L9

USH

9

8

Charger

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

SMbus Block diagram

SMbus Block diagram

SMbus Block diagram

LA-A901P

LA-A901P

LA-A901P

5 53Thursday, March 06, 2014

5 53Thursday, March 06, 2014

5 53Thursday, March 06, 2014

1

0.3

0.3

0.3

5

4

3

2

1

SATA0

SATA1

PCB

UMA SATA port

DD

H12 UMA

H12 Entry

H14 DSC

H14 UMA

H14D_En

H14U_En

H15 DSC

H15 UMA

H15D_En

H15U_En

E-Dock

NA

Service Mode Switch:

D D

+RTC_CELL

330K_0402_5%

12

RC1

PCH_INTVRMEN

INTVRMEN - INTEGRATED SUS 1.05V VRM

ENABLE

C C

High - Enable Internal VRs

Low - Enable External VRs

1 2

RC9 1M_0402_5%

+RTC_CELL

1 2

CC3

B B

+1.05V_M

1U_0402_6.3V6K

RC14 51_0402_5%

RC15 51_0402_5%

RC16 51_0402_5%

RC18@ 1K_0402_1%

RC21@ 51_0402_5%

1 2

1 2

RC10 20K_0402_5%

RC8 20K_0402_5%

PCH_JTAG_TDI

12

PCH_JTAG_TDO

12

PCH_JTAG_TMS

12

PCH_JTAG_JTAGX

12

PCH_JTAG_TCK

12

Add a switch to ME_FWP signal to unlock the ME region and

allow the entire region of the SPI flash to be updated using FPT.

+3.3V_ALW_PCH

12

RC2

1K_0402_5%

ME_FWP_EC<36>

ME_FWP PCH has internal 20K PD.

(suspend power rail)

FLASH DESCRIPTOR SECURITY OVERRIDE

LOW = ENABLE (DEFAULT) -->Pin1 & Pin3 short

HIGH = DISABLE (ME can update) -->Pin2 & Pin3 short

CC1

1 2

12P_0402_50V8J

CC2

1 2

12P_0402_50V8J

1

1

CMOS1@SHORT PADS~D

1 2

CC4

CMOS place near DIMM

CMOS_CLR1

2

2

1U_0402_6.3V6K

CMOS setting

RC301@ 0_0402_5%

PT,ST pop RC2 and SW1; MP pop RC301

ME_FWP

12

YC1

32.768KHZ_12.5PF_9H03220008

ME_FWPME_FWP_EC

12

SW1

1

A

2

B

3

C

4

G1

5

G2

SS3-CMFTQR9_3P

1 2

RC4@ 0_0402_5%

PCH_RTCRST#<9>

PCH_AZ_CODEC_SDIN0<21>

ME_FWP

Shunt Clear CMOS

Open

+1.05V_M

Keep CMOS

RC300@

1 2

10K_0402_5%

CC100@

1U_0402_6.3V6K

1 2

PCH_JTAG_TRST#<9>

PCH_JTAG_TCK<9>

PCH_JTAG_TDI<9>

PCH_JTAG_TDO<9>

PCH_JTAG_TMS<9>

PCH_JTAG_JTAGX<9>

PCH_RTCX1PCH_RTCX1_R

10M_0402_5%

12

RC7

PCH_RTCX2

INTRUDER #

PCH_INTVRMEN

SRTCRST#

PCH_RTCRST#

PCH_AZ_BITCLK

PCH_AZ_SYNC

PCH_AZ_RST#

PCH_AZ_CODEC_SDIN0

PCH_AZ_SDOUT

1 2

RC11 1K_0402_5%

PCH_JTAG_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PM_TEST_RST

UC1E

@

AW5

RTCX1

AY5

RTCX2

AU6

INTRUDER

AV7

INTVRMEN

AV6

SRTCRST

AU7

RTCRST

AW8

HDA_BCLK/I2S0_SCLK

AV11

HDA_SYNC/I2S0_SFRM

AU8

HDA_RST/I2S_MCLK

AY10

HDA_SDI0/I2S0_RXD

AU12

HDA_SDI1/I2S1_RXD

AU11

HDA_SDO/I2S0_TXD

AW10

HDA_DOCK_EN/I2S1_TXD

AV10

HDA_DOCK_RST/I2S1_SFRM

AY8

I2S1_SCLK

AU62

PCH_TRST

AE62

PCH_TCK

AD61

PCH_TDI

AE61

PCH_TDO

AD62

PCH_TMS

AL11

RSVD

AC4

RSVD

AE63

JTAGX

AV2

RSVD

BDW-ULT-DDR3L_BGA1168

5 OF 19

E-Dock

-Dock

E

NA

N

E-Dock

E-Dock

NA

NA

RTC

AUDIO SATA

JTAG

A

BDW_ULT_DDR3L

HDD

HDD

HDD

HDD

HDD

HDD

H

HDD

HDD

HDD

HDA for Codec

PCH_AZ_CODEC_SDOUT<21>

A A

PCH_AZ_CODEC_SYNC<21>

PCH_AZ_CODEC_RST#<21>

PCH_AZ_CODEC_BITCLK<21>

1 2

RC19 33_0402_5%

1 2

RC20 33_0402_5%

1 2

RC22 33_0402_5%

1 2

EMC@

RC23 33_0402_5%

27P_0402_50V8J

@EMC@

12

CC5

Reserve for EMI

5

PCH_AZ_SDOUT

PCH_AZ_SYNC

PCH_AZ_RST#

PCH_AZ_BITCLK

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

4

3

SATA2/PCIE6 L1

M2 3042

2nd PCIe Lane for PCIe Cache

M2 3042

SATA-Cache(no HCA)

M2 3042

2nd PCIe Lane for PCIe Cache

M2 3042

SATA-Cache(no HCA)

M2 3042

2nd PCIe Lane for PCIe Cache

SATA_RN0/PERN6_L3

SATA_RP0/PERP6_L3

SATA_TN0/PETN6_L3

SATA_TP0/PETP6_L3

SATA_RN1/PERN6_L2

SATA_RP1/PERP6_L2

SATA_TN1/PETN6_L2

SATA_TP1/PETP6_L2

SATA_RN2/PERN6_L1

SATA_RP2/PERP6_L1

SATA_TN2/PETN6_L1

SATA_TP2/PETP6_L1

SATA_RN3/PERN6_L0

SATA_RP3/PERP6_L0

SATA_TN3/PETN6_L0

SATA_TP3/PETP6_L0

SATA0GP/GPIO34

SATA1GP/GPIO35

SATA2GP/GPIO36

SATA3GP/GPIO37

SATA_IREF

RSVD

RSVD

SATA_RCOMP

SATALED

2

SATA3/PCIE6 L0

M2 3042

(HCA & SATA-Cache)

NA NA

M2 3030 WIGIG

M2 3042

(HCA & SATA-Cache)

N

NA

A

M2 3030 WIGIG

NA

M2 3030 WIGIG

M2 3042

(HCA & SATA-Cache)

NA

NA

J5

H5

B15

A15

J8

H8

A17

B17

J6

H6

B14

C15

F5

E5

C17

D17

V1

U1

V6

AC1

A12

L11

K10

C12

U3

SATA_COMP

SATA_ACT#

M2 3030 WIGIG

Express card

SATA_PRX_DKTX_N0_C <34>

SATA_PRX_DKTX_P0_C <34>

SATA_PTX_DKRX_N0_C <34>

SATA_PTX_DKRX_P0_C <34>

SATA_PRX_DTX_N1 <20>

SATA_PRX_DTX_P1 <20>

SATA_PTX_DRX_N1 <20>

SATA_PTX_DRX_P1 <20>

PCIE_PRX_SATATX_N6_L1 <30>

PCIE_PRX_SATATX_P6_L1 <30>

PCIE_PTX_SATARX_N6_L1 <30>

PCIE_PTX_SATARX_P6_L1 <30>

PCIE_PRX_SATATX_N6_L0 <30>

PCIE_PRX_SATATX_P6_L0 <30>

PCIE_PTX_SATARX_N6_L0 <30>

PCIE_PTX_SATARX_P6_L0 <30>

MPCIE_RST# <12>

HDD_DET# <12,20>

SATA2_PCIE6_L1 <12,35>

mCARD _PCIE #_SAT A < 12,36>

SATA_ACT# <39>

SATA Impedance Compensation

CAD note:

Place the resistor within 500 mils of the PCH. Avoid

routing next to clock pins.

DELL CONFIDENTIAL/PROPRIETARY

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

contact to WWAN

SATA2/PCIE6_L1 contact to WWAN

SATA3/PCIE6 L0 contact to WLAN

contact to WWAN

contact to WLAN

SATA2/PCIE6_L1 contact to WWAN

SATA3/PCIE6 L0 contact to WLAN

contact to WWAN

contact to WLAN

contact to Express card

+PCH_ASATA3PLL

DGPU_PWROK<10>

HDD_FALL_INT<10,20>

PCH_GPIO85<12>

3.3V_TS_EN<12,23>

SATA_COMP

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

CPU (1/12)

CPU (1/12)

CPU (1/12)

LA-A901P

LA-A901P

LA-A901P

for DOCK

SATA HDD

SSD Cache (PCIE)

SSD Cache/HCA (SATA/PCIE)

+3.3V_RUN

RPC18

45

3

6

2

7

1

8

10K_8P4R_5%

+PCH_ASATA3PLL

1 2

RC173.01K_0402_1%

6 53Thursday, March 06, 2014

6 53Thursday, March 06, 2014

6 53Thursday, March 06, 2014

1

0.3

0.3

0.3

5

UC1G

@

AU14

LAD0

AW12

LAD1

AY12

LAD2

AW11

LAD3

AV12

LFRAME

AA3

SPI_CLK

Y7

SPI_CS0

Y4

SPI_CS1

AC2

SPI_CS2

AA2

SPI_MOSI

AA4

SPI_MISO

Y6

SPI_IO2

AF1

SPI_IO3

BDW-ULT-DDR3L_BGA1168

7 OF 19

SOFTWARE TAA

SPI_CLK64

@EMC@

CC10

@EMC@

LPC_LAD0

LPC_LAD1

LPC_LAD2

LPC_LAD3

LPC_LFRAME#

PCH_SPI_CLK

PCH_SPI_CS0#

PCH_SPI_CS1#

PCH_SPI_CS2#

PCH_SPI_DO

PCH_SPI_DIN

PCH_SPI_DO2

PCH_SPI_DO3

LPC_LAD0<35,36>

LPC_LAD1<35,36>

LPC_LAD2<35,36>

LPC_LAD3<35,36>

LPC_LFRAME#<35,36>

1 2

1 2

PCH_SPI_CLK<27>

PCH_SPI_CS2#<27>

PCH_SPI_DO<27>

PCH_SPI_DIN<27>

SPI_PCH_DO2

SPI_PCH_DO3

33_0402_5%

RC62

1 2

33P_0402_50V8J

1 2

D D

+3.3V_SPI

RC29 1K_0402_5%

RC31 1K_0402_5%

SPI_CLK32

33_0402_5%

RC61

@EMC@

1 2

33P_0402_50V8J

CC9

@EMC@

C C

1 2

BDW_ULT_DDR3L

LPC

MMI --->

+3.3V_RUN

RPC6

4 5

3

6

2

7

1

8

PCB

10K_8P4R_5%

PCIE1

SD card

B B

H12 UMA

H12 Entry

H14 DSC

H14 UMA

H14D_En

H14U_En

A A

H15 DSC

H15 UMA

H15D_En

H15U_En

SD card

SD card

SD card

SD card

SD card

SD card

SD card

SD card

5

PCH_GPIO69 <12>

USH_DET# <12,27>

CPUSB# <12>

LCD_CBL_DET# <12,23>

PCIE3PCIE2

NA LOM

NA

LOM

NA

LOM

NA

LOM

NA

LOM

NA

LOM

NA

LOM

NA

LOM

NA

LOM

NA

LOM

10/100/1G LAN --->

WLAN (NGFF1)--->

WGIG (NGFF1)--->

HCA/PCIe cache (NGFF2)--->

PCIE4

WLAN

WLAN

WLAN

WLAN

WLAN

WLAN

WLAN

WLAN

WLAN

WLAN

PCIE5

WIGIG

WIGIGSD card

GPU

WIGIG

GPU

WIGIG

GPU

WIGIG

GPU

WIGIG

4

SMBALERT/GPIO11

SMBCLK

SMBUS

SML1ALERT/PCHHOT/GPIO7 3

C-LINKSPI

SMBDATA

SML0ALERT/GPIO60

SML0CLK

SML0DATA

SML1CLK/GPIO75

SML1DATA/GPIO74

CL_CLK

CL_DATA

CL_RST

SPI_PCH_DIN

SPI_PCH_DO

SPI_PCH_CLK

SPI_PCH_DO3

SPI_PCH_DO3

SPI_PCH_CLK

SPI_PCH_DO

SPI_PCH_DIN

PCIECLK for UMA

CLK_PCIE_MMI#<29>

CLK_PCIE_MMI<29>

MMICLK_RE Q#<12,29>

+3.3V_RUN

CLK_PCIE_LAN#<28>

CLK_PCIE_LAN<28>

LANCLK_REQ#<12,28>

CLK_PCIE_W LAN#<30>

CLK_PCIE_W LAN<30>

WLANCLK_REQ#<12,30>

CLK_PCIE_W IGIG#<30>

CLK_PCIE_W IGIG<30>

WIGIGCLK_REQ#<12,30>

CLK_PCIE_SAT A#<30>

CLK_PCIE_SAT A<30>

SATACLK_REQ#<30>

+3.3V_RUN

PCIE6

M2 3042

(HCA & SATA-Cache)

NA

WIGIG

M2 3042

(HCA & SATA-Cache)

WIGIG

NA

WIGIG

M2 3042

(HCA & SATA-Cache)

WIGIG

NA

4

RC66 10K_0402_5%

RC68 10K_0402_5%

AN2

AP2

AH1

AL2

AN1

AK1

AU4

AU3

AH3

AF2

AD2

AF4

RPC11

1 8

2 7

3 6

4 5

33_0804_8P4R_5%

VPRO@

RPC12

1 8

2 7

3 6

4 5

33_0804_8P4R_5%

1 2

1 2

PCI_CLK_LPC_0

PCI_CLK_LPC_1

MEM_SMBCLK

MEM_SMBDA TA

SML0_SMBCLK

SML0_SMBDATA

SML1_SMBCLK

SML1_SMBDATA

PCH_CL_CLK1

PCH_CL_DATA1

PCH_CL_RST1#

SPI_DIN64

SPI_DO64

SPI_CLK64

SPI_PCH_DO3_64

SPI_PCH_DO3_32

SPI_CLK32

SPI_DO32

SPI_DIN32

PCH_SMB_ALERT# <11>

SML0_SMBCLK <28>

SML0_SMBDATA <28>

PCH_GPIO73 <9>

SML1_SMBCLK <36>

SML1_SMBDATA <36>

PCH_CL_CLK1 <30>

PCH_CL_DATA1 <30>

PCH_CL_RST1# <30>

UC1F

@

C43

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

U2

PCIECLKRQ0/GPIO18

B41

CLKOUT_PCIE_N1

A41

1 2

1 2

1 2

1 2

CLKOUT_PCIE_P1

Y5

PCIECLKRQ1/GPIO19

C41

CLKOUT_PCIE_N2

B42

CLKOUT_PCIE_P2

AD1

PCIECLKRQ2/GPIO20

B38

CLKOUT_PCIE_N3

C37

CLKOUT_PCIE_P3

N1

PCIECLKRQ3/GPIO21

A39

CLKOUT_PCIE_N4

B39

CLKOUT_PCIE_P4

U5

PCIECLKRQ4/GPIO22

B37

CLKOUT_PCIE_N5

A37

CLKOUT_PCIE_P5

T2

PCIECLKRQ5/GPIO23

BDW-ULT-DDR3L_BGA1168

6 OF 19

PCH_GPIO19

RC72EMC@ 22_0402_5%

RC74EMC@ 22_0402_5%

RC67EMC@ 22_0402_5%

RC70EMC@ 22_0402_5%

CLK_PCI_SIO

CLK_PCI_MEC

CLK_PCI_LPDEBUG

CLK_PCI_DOCK

Reserve for EMI

3

MEM_SMBCLK

MEM_SMBDA TA

SPI_PCH_CS0#

SPI_PCH_DO2

SPI_PCH_CS1#

SPI_PCH_DO2

BDW_ULT_DDR3L

CLOCK

SIGNALS

CLK_PCI_SIO <35>

CLK_PCI_MEC <36>

CLK_PCI_LPDEB UG <36>

CLK_PCI_DOCK <3 4>

12

@EMC@12P_0402_50V8J

CC12

12

@EMC@12P_0402_50V8J

CC13

12

@EMC@12P_0402_50V8J

CC14

12

@EMC@12P_0402_50V8J

CC15

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

+3.3V_RUN

6

5

DMN66D0LDW-7_SOT 363-6

3 4

QC1B

DMN66D0LDW-7_SOT 363-6

1 2

RC35 0_0402_5%@

1 2

RC38 33_0402_5%

VPRO@

RC50 0_0402_5%

1 2

VPRO@

RC55 33_0402_5%

1 2

XTAL24_IN

XTAL24_OUT

RSVD

RSVD

DIFFCLK_BIASREF

TESTLOW_C3 5

TESTLOW_C3 4

TESTLOW_AK8

TESTLOW_AL 8

CLKOUT_LPC_0

CLKOUT_LPC_1

CLKOUT_ITPXDP

CLKOUT_ITPXDP_P

+3.3V_SPI

2

2

1

DDR_XDP_WAN_ SMBCLK <9,18,19, 20>

QC1A

SPI_PCH_CS0#_R

SPI_DIN64

SPI_PCH_DO2_64

SPI_PCH_CS1#_R

SPI_DIN32

SPI_PCH_DO2_32

XTAL24_IN

A25

XTAL24_OUT

B25

K21

M21

CLK_BIASREF

C26

MCP_TEST LOW1

C35

MCP_TEST LOW2

C34

MCP_TEST LOW3

AK8

MCP_TEST LOW4

AL8

PCI_CLK_LPC_0

AN15

PCI_CLK_LPC_1

AP15

B35

A35

2

12

12

12

12

12

12

12

+3.3V_M

12

RC224 0_0402_5%

RC225 0_0402_5%

RC226 0_0402_5%

RC227 0_0402_5%

RC228 0_0402_5%

RC229 0_0402_5%

RC230 0_0402_5%

RC231 0_0402_5%

DDR_XDP_WAN_ SMBDAT <9,18,19,20>

64Mb Flash ROM

UC2

1

2

3

4

W25Q64FVSSIQ_SO8

32Mb Flash ROM

UC3

1

2

3

4

W25Q32FVSSIQ_SO8

1M_0402_5%

RC63

1 2

RC65@ 0_0402_5%

SPI_PCH_CS1#

PCH_SPI_CS1#

SPI_PCH_DO

PCH_SPI_DO

SPI_PCH_DIN

PCH_SPI_DIN

SPI_PCH_CLK

PCH_SPI_CLK

SPI_PCH_CS0#

PCH_SPI_CS0#

SPI_PCH_DO2

PCH_SPI_DO2

SPI_PCH_DO3

PCH_SPI_DO3

MEM_SMBCLK

MEM_SMBDA TA

SML1_SMBCLK

SML1_SMBDATA

SML0_SMBCLK

SML0_SMBDATA

+3.3V_SPI

CC6

1 2

0.1U_0402_25V6

/CS

DO(IO1)

/WP(IO2)

GND

VPRO@

/CS

DO/IO1

/WP/IO2

GND

1 2

VCC

/HOLD(IO3)

CLK

DI(IO0)

VCC

/HOLD/IO3

CLK

DI/IO0

XTAL24_OUT_R

JSPI1

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

GND1

22

GND2

TYCO_2-2041070-0

CONN@

8

SPI_PCH_DO3_64

7

SPI_CLK64

6

SPI_DO64

5

+3.3V_SPI

0.1U_0402_25V6

8

SPI_PCH_DO3_32

7

SPI_CLK32

6

SPI_DO32

5

3

4

24MHZ_12PF_X3G024000DC1H

1

2

CLK_BIASREF

MCP_TEST LOW1

MCP_TEST LOW2

MCP_TEST LOW3

MCP_TEST LOW4

VPRO@

CC7

1 2

CC8

12

15P_0402_50V8J

YC2

CC11

12

15P_0402_50V8J

1 2

RC240 10K_0402_5%

1 2

1 2

RC241 10K_0402_5%

1 2

RC242 10K_0402_5%

RC243 10K_0402_5%

1 2

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

ize Document Number Rev

Size Document Number Rev

Size Document Number Rev

S

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

CPU (2/12)

CPU (2/12)

CPU (2/12)

LA-A901P

LA-A901P

LA-A901P

1

RPC14

1

8

2

7

3

6

4 5

2.2K_0804_8P4R_5%

12

12

+PCH_VCCACLKPLL

RC693.01K_0402_1%

support SPI TPM

LPC_0 LPC_1

SIO

DOCK

MEC

DEBUG

7 53Thursday, March 06, 2014

7 53Thursday, March 06, 2014

1

7 53Thursday, March 06, 2014

+3.3V_ALW_PCH

RC33499_0402_1%

RC34499_0402_1%

0.3

0.3

0.3

5

4

3

2

1

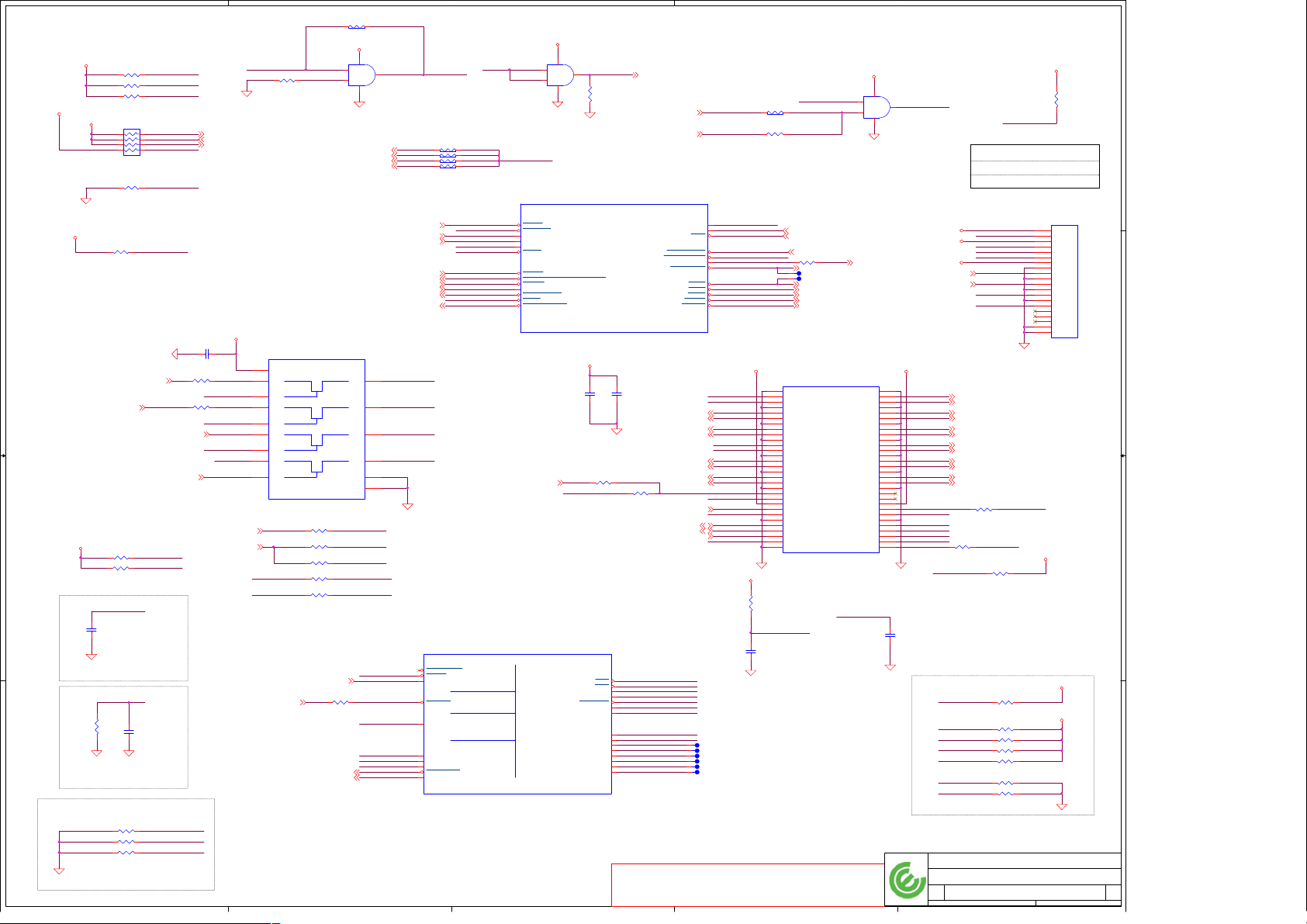

D D

DDR_A_D[0..63]<18>

C C

B B

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

AH63

AH62

AK63

AK62

AH61

AH60

AK61

AK60

AM63

AM62

AP63

AP62

AM61

AM60

AP61

AP60

AP58

AR58

AM57

AK57

AL58

AK58

AR57

AN57

AP55

AR55

AM54

AK54

AL55

AK55

AR54

AN54

AY58

AW58

AY56

AW56

AV58

AU58

AV56

AU56

AY54

AW54

AY52

AW52

AV54

AU54

AV52

AU52

AK40

AK42

AM43

AM45

AK45

AK43

AM40

AM42

AM46

AK46

AM49

AK49

AM48

AK48

AM51

AK51

UC1C

@

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

BDW_ULT_DDR3L

DDR CHANNEL A

SA_CLK#0

SA_CLK0

SA_CLK#1

SA_CLK1

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_CS#0

SA_CS#1

SA_ODT0

SA_RAS

SA_WE

SA_CAS

SA_BA0

SA_BA1

SA_BA2

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

SA_DQSN0

SA_DQSN1

SA_DQSN2

SA_DQSN3

SA_DQSN4

SA_DQSN5

SA_DQSN6

SA_DQSN7

SA_DQSP0

SA_DQSP1

SA_DQSP2

SA_DQSP3

SA_DQSP4

SA_DQSP5

SA_DQSP6

SA_DQSP7

SM_VREF_CA

SM_VREF_DQ0

SM_VREF_DQ1

UC1D

AY31

AW31

AY29

AW29

AV31

AU31

AV29

AU29

AY27

AW27

AY25

AW25

AV27

AU27

AV25

AU25

AM29

AK29

AL28

AK28

AR29

AN29

AR28

AP28

AN26

AR26

AR25

AP25

AK26

AM26

AK25

AL25

AY23

AW23

AY21

AW21

AV23

AU23

AV21

AU21

AY19

AW19

AY17

AW17

AV19

AU19

AV17

AU17

AR21

AR22

AL21

AM22

AN22

AP21

AK21

AK22

AN20

AR20

AK18

AL18

AK20

AM20

AR18

AP18

@

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

DDR_B_D[0..63]<19>

M_CLK_DDR#0

AU37

M_CLK_DDR0

AV37

M_CLK_DDR#1

AW36

M_CLK_DDR1

AY36

DDR_CKE0_DIMMA

AU43

DDR_CKE1_DIMMA DDR_CKE2_DIMMB

AW43

AY42

AY43

DDR_CS0_DIMMA#

AP33

DDR_CS1_DIMMA# DDR_CS2_DIMMB#

AR32

AP32

DDR_A_RAS#

AY34

DDR_A_WE#

AW34

DDR_A_CAS#

AU34

DDR_A_BS0

AU35

DDR_A_BS1

AV35

DDR_A_BS2

AY41

DDR_A_MA0

AU36

DDR_A_MA1

AY37

DDR_A_MA2

AR38

DDR_A_MA3

AP36

DDR_A_MA4

AU39

DDR_A_MA5

AR36

DDR_A_MA6

AV40

DDR_A_MA7

AW39

DDR_A_MA8

AY39

DDR_A_MA9

AU40

DDR_A_MA10

AP35

DDR_A_MA11

AW41

DDR_A_MA12

AU41

DDR_A_MA13

AR35

DDR_A_MA14

AV42

DDR_A_MA15

AU42

DDR_A_DQS#0

AJ61

DDR_A_DQS#1

AN62

DDR_A_DQS#2

AM58

DDR_A_DQS#3

AM55

DDR_A_DQS#4

AV57

DDR_A_DQS#5

AV53

DDR_A_DQS#6

AL43

DDR_A_DQS#7

AL48

DDR_A_DQS0

AJ62

DDR_A_DQS1

AN61

DDR_A_DQS2

AN58

DDR_A_DQS3

AN55

DDR_A_DQS4

AW57

DDR_A_DQS5

AW53

DDR_A_DQS6

AL42

DDR_A_DQS7

AL49

AP49

AR51

AP51

M_CLK_DDR#0 <18>

M_CLK_DDR0 <18>

M_CLK_DDR#1 <18>

M_CLK_DDR1 <18>

DDR_CKE0_DIMMA < 18>

DDR_CKE1_DIMMA < 18>

DDR_CS0_DIMMA# <18>

DDR_CS1_DIMMA# <18>

DDR_A_RAS# <18>

DDR_A_WE# <18>

DDR_A_CAS# <18>

DDR_A_BS0 <18>

DDR_A_BS1 <18>

DDR_A_BS2 <18>

DDR_A_MA[0..15] <18>

DDR_A_DQS#[0..7] <18>

DDR_A_DQS[0..7] <18>

+SM_VREF_CA

+SM_VREF_DQ0

+SM_VREF_DQ1

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

BDW_ULT_DDR3L

DDR CHANNEL B

SB_CK#0

SB_CK0

SB_CK#1

SB_CK1

SB_CKE0

SB_CKE1

SB_CKE2

SB_CKE3

SB_CS#0

SB_CS#1

SB_ODT0

SB_RAS

SB_WE

SB_CAS

SB_BA0

SB_BA1

SB_BA2

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_DQSN0

SB_DQSN1

SB_DQSN2

SB_DQSN3

SB_DQSN4

SB_DQSN5

SB_DQSN6

SB_DQSN7

SB_DQSP0

SB_DQSP1

SB_DQSP2

SB_DQSP3

SB_DQSP4

SB_DQSP5

SB_DQSP6

SB_DQSP7

AM38

AN38

AK38

AL38

AY49

AU50

AW49

AV50

AM32

AK32

AL32

AM35

AK35

AM33

AL35

AM36

AU49

AP40

AR40

AP42

AR42

AR45

AP45

AW46

AY46

AY47

AU46

AK36

AV47

AU47

AK33

AR46

AP46

AW30

AV26

AN28

AN25

AW22

AV18

AN21

AN18

AV30

AW26

AM28

AM25

AV22

AW18

AM21

AM18

M_CLK_DDR#2

M_CLK_DDR2

M_CLK_DDR#3

M_CLK_DDR3

DDR_CKE3_DIMMB

DDR_CS3_DIMMB#

DDR_B_RAS#

DDR_B_WE#

DDR_B_CAS#

DDR_B_BS0

DDR_B_BS1

DDR_B_BS2

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

M_CLK_DDR#2 <19>

M_CLK_DDR2 <19>

M_CLK_DDR#3 <19>

M_CLK_DDR3 <19>

DDR_CKE2_DIMMB <19>

DDR_CKE3_DIMMB <19>

DDR_CS2_DIMMB# <1 9>

DDR_CS3_DIMMB# <1 9>

DDR_B_RAS# <19>

DDR_B_WE# <19>

DDR_B_CAS# <19>

DDR_B_BS0 <19>

DDR_B_BS1 <19>

DDR_B_BS2 <19>

DDR_B_MA[0..15] <19>

DDR_B_DQS#[0..7] <19>

DDR_B_DQS[0..7] <19>

BDW-ULT-DDR3L_BGA1168

3 OF 19

A A

BDW-ULT-DDR3L_BGA1168

4 OF 19

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

CPU (3/12)

CPU (3/12)

CPU (3/12)

LA-A901P

LA-A901P

LA-A901P

1

8 53Thursday, March 06, 2014

8 53Thursday, March 06, 2014

8 53Thursday, March 06, 2014

0.3

0.3

0.3

5

+3.3V_ALW_PCH

RC79 10K_0402_5%

RC81 10K_0402_5%

+PCH_VCCDSW3_3

D D

C C

B B

RC82@ 10K_0402_5%

+3.3V_ALW_PCH

RC91 47K_0402_5%

+3.3V_RUN

RC95@ 8.2K_0402_5%

PCH_JTAG_TDI<6>

+1.05V_VCCST

RC114@ 49.9_0402_1%

RC116 62_0402_5%

1

CC20

22P_0402_50V8J

2

EMI request add

10K_0402_5%

12

RC123

1 2

1 2

1 2

RPC1

4 5

3

2

1

10K_8P4R_5%

1 2

1 2

1 2

1 2

H_PROCHOT#

@EMC@

H_CPUPWRGD

PCH_JTAG_TDO<6>

1

ME_SUS_PWR_ACK

SUSACK#

SUS_STAT#/LPCPD#

6

7

PCH_PCIE_WAKE#

8

PCH_RSMRST#_Q

ME_RESET#

PCH_JTAG_TDI

H_CATERR#

H_PROCHOT#

100P_0402_50V8J

@EMC@

CC83

0.1U_0402_25V6

1 2

RC98 0_0402_5%

CXDP@

1 2

RC99 0_0402_5%

CXDP@

PCH_JTAG_TMS<6>

RUNPWROK<35,36>

CC17

RUNPWROK

RUNPWROK

RUNPWROK

RUNPWROK

XDP_DBRESET#

RC80@ 8.2K_0402_5%

PCH_GPIO73 <7>

SIO_EXT_WAKE# <12,36>

PCH_GPIO46 <12>

+3.3V_RUN

CXDP@

12

TDO_XD P

TDI_XD P_R

PCH_JTAG_TMS

TRST#_ XDP

PCH_JTAG_TRST#<6>

PCH_JTAG_JTAGX<6>

UC7

CXDP@

14

VCC

2

1A

1

1OE

5

2A

4

2OE

9

3A

10

3OE

12

4A

13

4OE

74CBTLV3126BQ_DHVQFN14_2P5X3

reference Shark Bay ULT Validation Customer Debug Port

Implementation Requirement Rev 1.0

PCH_JTAG_TDO

PCH_JTAG_TCK

H_PROCHOT#<36,45,46>

2

CAD Note:

Avoid stub in the PWRGD path

A A

while placing resistors RC123

4

1 2

RC77@ 0_0402_5%

+3.3V_RUN

1

ME_RESET#

12

2

PLTRST_VMM2320#<22>

GND PAD

CPU_XDP_TRST#

12

RC1090_0402_5% CXDP@

CPU_XDP_TCLK

12

RC1120_0402_5% CXDP@

TDO_XD P

12

RC115 @0_0402_5%

TDI_XD P_R

12

RC118 @0_0402_5%

CPU_XDP_TCLK

12

RC119 @0_0402_5%

PECI_EC<36>

1 2

RC121 56_0402_5%

DDR3_DRAMRST#<18,19>

DDR_PG_CTRL<18>

5

P

B

4

O

A

G

74AHC1G09GW_TSSOP5

3

PLTRST_USH#<27>

PLTRST_MMI#<29>

PLTRST_LAN#<28>

3

1B

6

2B

8

3B

11

4B

7

GND

15

H_CATERR#

PECI_EC

H_PROCHOT#_R

H_CPUPWRGD

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

UC4@

SYS_PWROK<36>

RESET_OUT#<15,36>

PCH_RSMRST#_Q<37>

ME_SUS_PWR_ACK<36>

SIO_PWRBTN#<36>

AC_PRESENT<12,36>

PCH_BATLOW#<11>

SIO_SLP_WLAN#<35>

CPU_XDP_TDO

CPU_XDP_TDI

CPU_XDP_TMS

CPU_XDP_TRST#

D61

N62

C61

AU60

AV60

AU61

AV15

AV61

K61

K63

3

+3.3V_RUN

Fix Intel 7260 can no t detect issue .

5

SYS_RESET#

1 2

RC219@ 0_0402_5%

1 2

RC87@ 0_0402_5%

1 2

RC88@ 0_0402_5%

1 2

RC89@ 0_0402_5%

SUSACK#<36>

UC1B

@

PROC_DETECT

CATERR

PECI

PROCHOT

PROCPWRGD

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

SM_DRAMRST

SM_PG_CNTL1

BDW-ULT-DDR3L_BGA1168

2 OF 19

PCH_PLTRST#

UC5

TC7SH08FU_SSOP5~D

PCH_PLTRST#

UC1H

@

AK2

SUSACK#

SYS_RESET#

SYS_PWROK

PM_APWROK_R

PCH_PLTRST#

PCH_RSMRST#_Q PCH_RTCRST#

ME_SUS_PWR_ACK

SIO_PWRBTN#

AC_PRESENT

SIO_SLP_S0#

SIO_SLP_WLAN#

THERMAL

BDW_ULT_DDR3L

MISC

PWR

DDR3L

SUSACK

AC3

SYS_RESET

AG2

SYS_PWROK

AY7

PCH_PWROK

AB5

APWROK

AG7

PLTRST

AW6

RSMRST

AV4

SUSWARN/SUSPW RDNACK/GPIO30

AL7

PWRBTN

AJ8

ACPRESENT/GPIO31

AN4

BATLOW/GPIO72

AF3

SLP_S0

AM5

SLP_WLAN/GPIO29

BDW-ULT-DDR3L_BGA1168

8 OF 19

H_VCCST_PWRGD<15>

It wil l ca use “f loati ng” si tuati on bef ore 3V _RUN c omin g of A ND gat e

1

P

B

PCH_PLTRST#_EC

4

O

2

A

G

3

12

RC304

@

100K_0402_5%

BDW_ULT_DDR3L

SYSTEM POWER MANAGEMENT

+1.05V_RUN

0.1U_0402_25V6

@

12

12

CC18

0.1U_0402_25V6

@

CC19

Place near JXDP1

RC5 need to close to JCPU1

1 2

RC102 1K_0402_5%

CXDP@

JTAG

H_CPUPWRGD

PROC_TRST

1 2

RC103@ 1K_0402_5%

J62

PRDY

K62

PREQ

E60

PROC_TCK

E61

PROC_TMS

E59

F63

PROC_TDI

F62

PROC_TDO

J60

BPM#0

H60

BPM#1

H61

BPM#2

H62

BPM#3

K59

BPM#4

H63

BPM#5

K60

BPM#6

J61

BPM#7

CPU_XDP_PRDY#

CPU_XDP_PREQ#

CPU_XDP_TCLK

CPU_XDP_TMS

CPU_XDP_TRST#

CPU_XDP_TDI

CPU_XDP_TDO

XDP_OBS0_R

XDP_OBS1_R

XDP_OBS2_R

XDP_OBS3_R

XDP_OBS4_R

XDP_OBS5_R

XDP_OBS6_R

XDP_OBS7_R

PCH_PLTRST#_EC <27,30,35,36>

PM_APWROK<36>

1.05V_M_PWRGD<43>

DSWVRMEN

DPWROK

WAKE

CLKRUN/GPIO32

SUS_STAT/GPIO61

SUSCLK/GPIO62

SLP_S5/GPIO63

SLP_S4

SLP_S3

SLP_A

SLP_SUS

SLP_LAN

CFG0<13>

CFG1<13>

CFG2<13>

CFG3<13>

CFG4<13>

CFG5<13>

CFG6<13>

CFG7<13>

CPU_PWR_DEBUG#<15>

DDR_XDP_WAN_SMBDAT<7,18,19,20>

DDR_XDP_WAN_SMBCLK<7,18,19,20>

PCH_JTAG_TCK<6>

AW7

DSWODVREN

PCH_DPWROK

AV5

PCH_PCIE_WAKE#

AJ5

V5

SUS_STAT#/LPCPD#

AG4

SUSCLK_R

AE6

SIO_SLP_S5#

AP5

SIO_SLP_S4#

AJ6

SIO_SLP_S3#

AT4

SIO_SLP_A#

AL5

SIO_SLP_SUS#

AP4

SIO_SLP_LAN#

AJ7

CPU_XDP_PREQ#

CPU_XDP_PRDY#

CFG0

CFG1

CFG2

CFG3

XDP_OBS0_R

XDP_OBS1_R

CFG4

CFG5

CFG6

CFG7

H_VCCST_PWRGD_XDP

SIO_PWRBTN#

SYS_PWROK

CPU_XDP_TCLK

+3.3V_ALW_PCH

0.1U_0402_25V6

CC22@

T10 @PAD~D

T11 @PAD~D

T12 @PAD~D

T13 @PAD~D

T14 @PAD~D

T15 @PAD~D

2

1 2

RC26@ 0_0402_5%

1 2

RC27 0_0402_5%@

PCH_DPWROK <36>

PCH_PCIE_WAKE# <35,36>

CLKRUN# <12,35,36>

1 2

RC136 0_0402_5%@

+1.05V_RUN

JXDP1

1

GND0

3

OBSFN_A0

5

OBSFN_A1

7

GND2

OBSDATA_A09OBSDATA_C0

OBSDATA_A111OBSDATA_C1

13

GND4

OBSDATA_A215OBSDATA_C2

OBSDATA_A317OBSDATA_C3

19

GND6

21

OBSFN_B0

23

OBSFN_B1

25

GND8

OBSDATA_B027OBSDATA_D0

OBSDATA_B129OBSDATA_D1

31

GND10

OBSDATA_B233OBSDATA_D2

OBSDATA_B335OBSDATA_D3

37

GND12

PWRGOOD/HOOK039ITPCLK/ HOOK4

41

HOOK1

VCC_OBS_AB43VCC_OBS_CD

45

HOOK2

47

HOOK3

49

GND14

51

SDA

53

SCL

55

TCK1

57

TCK0

59

GND16

1K_0402_5%

RC120

CXDP@

1 2

SYS_PWROK

12

Place near JXDP1.47

SIO_SLP_A#

PM_APWROK_LPM_APWROK

SIO_SLP_S5# <36>

T8 @PAD~D

T9@PAD~D

SIO_SLP_S4# <36>

SIO_SLP_S3# <36>

SIO_SLP_A# <36>

SIO_SLP_SUS# <36>

SIO_SLP_LAN# <28,36>

ITPCLK# /HOOK5

RESET#/HOOK6

DBR#/HOOK7

Place near JXDP1.48

XDP_DBRESET#

+3.3V_ALW2

1

B

2

A

SUSCLK <30>

GND1

OBSFN_C0

OBSFN_C1

GND3

GND5

GND7

OBSFN_D0

OBSFN_D1

GND9

GND11

GND13

GND15

TD0

TRST#

TDI

TMS

GND17

CONN@SAMTE_BSH-030-01-L-D-A

5

P

PM_APWROK_R

4

O

G

UC6

TC7SH08FU_SSOP5~D

3

+1.05V_RUN

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

0.1U_0402_25V6

CC21

12

CXDP@

+3.3V_ALW_PCH

+PCH_VCCDSW3_3

+PCH_VCCDSW3_3

POWER_SW#_MB<36,39>

CFG17

CFG16

CFG8

CFG9

CFG10

CFG11

CFG19

CFG18

CFG12

CFG13

CFG14

CFG15

XDP_RST#_R

XDP_DBRESET#

TDO_XD P

TRST#_ XDP

PCH_JTAG_TDI

PCH_JTAG_TMS

CFG3_R

DSWODVREN - ON DIE DSW VR ENABLE

HIGH = ENABLED (DEFAULT)

LOW = DISABLED

SIO_SLP_S3#

SIO_SLP_S5#

SIO_SLP_S4#

SIO_SLP_A#

PCH_RTCRST#<6>

SYS_RESET#

SIO_SLP_S0#

CFG17 <13>

CFG16 <13>

CFG8 <13>

CFG9 <13>

CFG10 <13>

CFG11 <13>

CFG19 <13>

CFG18 <13>

CFG12 <13>

CFG13 <13>

CFG14 <13>

CFG15 <13>

RC106 1K_0402_5%

CXDP@

1 2

XDP_DBRESET#

1K_0402_5%

CPU_XDP_TMS

51_0402_5%

CPU_XDP_TDI

51_0402_5%

CPU_XDP_PREQ#

51_0402_5%

CPU_XDP_TDO

51_0402_5%

CPU_XDP_TCLK

51_0402_5%

CPU_XDP_TRST#

51_0402_5%

CFG3

RC113 1K_0402_5%

CXDP@

TDO_XD P

1

DSWODVREN

PCH_PLTRST#_EC

12

12

12

12

12

12

12

12

12

+1.05V_RUN

RC117@51_0402_5%

RC122

RC124@

RC125@

RC126@

RC127

RC128

RC129@

+RTC_CELL

330K_0402_5%

RC78

1 2

JAPS1

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

GND

20

GND

CONN@

ACES_50506-01841-P01

+3.3V_RUN

+1.05V_RUN

DDR3 COMPENSATION SIGNALS

SM_RCOMP0

12

RC130200_0402_1%

SM_RCOMP1

12

RC131121_0402_1%

SM_RCOMP2

12

RC132100_0402_1%

CAD Note:

Trace width=12~15 mil, Spcing=20 mils

Max trace length= 500 mil

5

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

4

3

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

2

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

CPU (4/12)

CPU (4/12)

CPU (4/12)

LA-A901P

LA-A901P

LA-A901P

1

9 53Thursd ay, Marc h 06 , 201 4

9 53Thursd ay, Marc h 06 , 201 4

9 53Thursd ay, Marc h 06 , 201 4

0.3

0.3

0.3

5

D D

4

3

2

1

PCIE

BDW_ULT_DDR3L

BDW_ULT_DDR3L

EDPDDI

DISPLAY

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

EDP_TXN2

EDP_TXP2

EDP_TXN3

EDP_TXP3

EDP_AUXN

EDP_AUXP

EDP_RCOMP

EDP_DISP_UTIL

DDPB_CTRLCLK

DDPB_CTRLDATA

DDPC_CTRLCLK

DDPC_CTRLDATA

DDPB_AUXN

DDPC_AUXN

DDPB_AUXP

DDPC_AUXP

DDPB_HPD

DDPC_HPD

EDP_HPD

C45

B46

A47

B47

C47

C46

A49

B49

A45

B45

D20

A43

B9

C9

D9

D11

C5

B6

B5

A6

C8

A8

D6

EDP_CPU_LANE_N0

EDP_CPU_LANE_P0

EDP_CPU_LANE_N1

EDP_CPU_LANE_P1

EDP_CPU_AUX#

EDP_CPU_AUX

EDP_COMP

CPU_DPB_CTRLCLK

CPU_DPB_CTRLDAT

CPU_DPC_CTRLCLK

CPU_DPC_CTRLDAT

CPU_DPB_AUX#

CPU_DPC_AUX#

CPU_DPB_AUX

CPU_DPC_AUX

DPB_HPD

DPC_HPD

EDP_CPU_HPD

EDP_CPU_LANE_N0 <23>

EDP_CPU_LANE_P0 <23>

EDP_CPU_LANE_N1 <23>

EDP_CPU_LANE_P1 <23>

EDP_CPU_AUX# <23>

EDP_CPU_AUX <23>

CPU_DPB_CTRLCLK <24>

CPU_DPB_CTRLDAT <24>

CPU_DPC_AUX# <25>

CPU_DPC_AUX <25>

DPB_HPD <24>

DPC_HPD <25>

EDP_CPU_HPD <23>

COMPENSATION PU FOR eDP

RPC2

1

2

3

4 5

RPC20

1

2

3

4 5

+VCCIOA_OUT

12

RC13324.9_0402_1%

8

7

6

8

7

6

12

RC141100K_0402_5%

12

RC142100K_0402_5%

EDP_COMP

CAD Note:Trace width=20 mils ,Spacing=25mil,

Max length=100 mils.

CPU_DPB_CTRLDAT

CPU_DPB_CTRLCLK

CPU_DPC_CTRLCLK

CPU_DPC_CTRLDAT

CPU_DPB_AUX#

CPU_DPB_AUX

CPU_DPC_AUX

CPU_DPC_AUX#

EDP_CPU_HPD

DPC_HPD

2.2K_0804_8P4R_5%

100K_0804_8P4R_5%

+3.3V_RUN

UC1A

@

C54

DDI1_LANE_N0<24>

DDI1_LANE_P0<24>

DDI1_LANE_N1<24>

DDI1_LANE_P1<24>

DDI1_LANE_N2<24>

DDI1_LANE_P2<24>

DDI1_LANE_N3<24>

DDI1_LANE_P3<24>

DDI2_LANE_N0<25>

DDI2_LANE_P0<25>

DDI2_LANE_N1<25>

DDI2_LANE_P1<25>

DDI2_LANE_N2<25>

DDI2_LANE_P2<25>

DDI2_LANE_N3<25>

C C

+3.3V_RUN

B B

RPC15

45

3

6

2

7

1

8

10K_8P4R_5%

12

ENVDD_PCH

PCH_GPIO53

1 2

RC139@ 100K_0402_5%

RC140@ 1K_0402_5%

CAM_MIC_CBL_DET# <12,23>

GPU_GC6_FB _EN <12>

3.3V_TP_EN <12>

DDI2_LANE_P3<25>

EDP_BIA_PWM

PANEL_BKLEN

ENVDD_PCH

PCH_GPIO53

CONTACTLESS_DET#<12,27>

HDD_FALL_INT<6,20>

TOUCHPAD_INTR#<12>

EDP_BIA_PWM<23>

PANEL_BKLEN<23>

ENVDD_PCH<23,36>

DGPU_PWROK<6>

PCH_GPIO80<12>

T16@ PAD~D

PCH_GPIO52<12>

DDI1_TXN0

C55

DDI1_TXP0

B58

DDI1_TXN1

C58

DDI1_TXP1

B55

DDI1_TXN2

A55

DDI1_TXP2

A57

DDI1_TXN3

B57

DDI1_TXP3

C51

DDI2_TXN0

C50

DDI2_TXP0

C53

DDI2_TXN1

B54

DDI2_TXP1

C49

DDI2_TXN2

B50

DDI2_TXP2

A53

DDI2_TXN3

B53

DDI2_TXP3

BDW-ULT-DDR3L_BGA1168

1 OF 19

UC1I

@

B8

EDP_BKLCTL

A9

EDP_BKLEN

C6

EDP_VDDEN

U6

PIRQA/GPIO77

P4

PIRQB/GPIO78

N4

PIRQC/GPIO79

N2

PIRQD/GPIO80

AD4

PME

U7

GPIO55

L1

GPIO52

L3

GPIO54

R5

GPIO51

L4

GPIO53

BDW-ULT-DDR3L_BGA1168

9 OF 19

eDP SIDEBAND

A A

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

CPU (5/12)

CPU (5/12)

CPU (5/12)

LA-A901P

LA-A901P

LA-A901P

10 53Thursday, March 06, 2014

10 53Thursday, March 06, 2014

10 53Thursday, March 06, 2014

1

0.3

0.3

0.3

5

4

3

2

1

PCIE for UMA

D D

PCIE_PRX_WIGIGTX_N5<30>

WIGIG --->

10/100/1G LAN --->

C C

WLAN (Mini Card 2)--->

MMI -->

+PCH_AUSB3PLL

B B

PCB

H12 UMA

H12 Entry

H14 DSC

H14 UMA

H14D_En

PCIE1

SD card

SD card

SD card

SD card

PCIE3PCIE2

NA LOM

NA

LOM

NA

LOM

NA

LOM

NA

LOM

PCIE_PRX_WIGIGTX_P5<30>

PCIE_PTX_WIGIGRX_N5<30>

PCIE_PTX_WIGIGRX_P5<30>

PCIE_PRX_GLANTX_N3<28>

PCIE_PRX_GLANTX_P3<28>

PCIE_PTX_GLANRX_N3<28>

PCIE_PTX_GLANRX_P3<28>

PCIE_PRX_WLANTX_N4<30>

PCIE_PRX_WLANTX_P4<30>

PCIE_PTX_WLANRX_N4<30>

PCIE_PTX_WLANRX_P4<30>

PCIE_PRX_MMITX_N1<29>

PCIE_PRX_MMITX_P1<29>

PCIE_PTX_MMIRX_N1<29>

PCIE_PTX_MMIRX_P1<29>

USB3RN4<31>

USB3RP4<31>

USB3TN4<31>

USB3TP4<31>

1 2

RC149 3.01K_0402_1%

PCIE4

WLAN

WLAN

WLAN

WLAN

WLAN

PCIE5

WIGIG

WIGIGSD card

GPU

WIGIG

GPU

PCIE_PRX_WIGIGTX_N5

PCIE_PRX_WIGIGTX_P5

PCIE_PTX_WIGIGRX_N5

PCIE_PTX_WIGIGRX_P5

PCIE_PRX_GLANTX_N3

PCIE_PRX_GLANTX_P3

PCIE_PTX_GLANRX_N3

PCIE_PTX_GLANRX_P3

PCIE_PRX_WLANTX_N4

PCIE_PRX_WLANTX_P4

PCIE_PTX_WLANRX_N4

PCIE_PTX_WLANRX_P4

PCIE_PRX_MMITX_N1

PCIE_PRX_MMITX_P1

PCIE_PTX_MMIRX_N1

PCIE_PTX_MMIRX_P1

PCH_PCIE_RCOMP

PCIE6

M2 3042

(HCA & SATA-Cache)

NA

WIGIG

M2 3042

(HCA & SATA-Cache)

WIGIG

UC1K

@

F10

PERN5_L0

E10

PERP5_L0

C23

PETN5_L0

C22

PETP5_L0

F8

PERN5_L1

E8

PERP5_L1

B23

PETN5_L1

A23

PETP5_L1

H10

PERN5_L2

G10

PERP5_L2

B21

PETN5_L2

C21

PETP5_L2

E6

PERN5_L3

F6

PERP5_L3

B22

PETN5_L3

A21

PETP5_L3

G11

PERN3

F11

PERP3

C29

PETN3

B30

PETP3

F13

PERN4

G13

PERP4

B29

PETN4

A29

PETP4

G17

PERN1/USB3RN3

F17

PERP1/USB3RP3

C30

PETN1/USB3TN3

C31

PETP1/USB3TP3

F15

PERN2/USB3RN4

G15

PERP2/USB3RP4

B31

PETN2/USB3TN4

A31

PETP2/USB3TP4

E15

RSVD

E13

RSVD

A27

PCIE_RCOMP

B27

PCIE_IREF

BDW-ULT-DDR3L_BGA1168

11 OF 19

BDW_ULT_DDR3L

PCIE USB

USB2N0

USB2P0

USB2N1

USB2P1

USB2N2

USB2P2

USB2N3

USB2P3

USB2N4

USB2P4

USB2N5

USB2P5

USB2N6

USB2P6

USB2N7

USB2P7

USB3RN1

USB3RP1

USB3TN1

USB3TP1

USB3RN2

USB3RP2

USB3TN2

USB3TP2

USBRBIAS

USBRBIAS

RSVD

RSVD

OC0/GPIO40

OC1/GPIO41

OC2/GPIO42

OC3/GPIO43

AN8

AM8

AR7

AT7

AR8

AP8

AR10

AT10

AM15

AL15

AM13

AN13

AP11

AN11

AR13

AP13

G20

H20

C33

B34

E18

F18

B33

A33

AJ10

AJ11

AN10

AM10

AL3

AT1

AH2

AV3

USBP0USBP0+

USBP1USBP1+

USBP2USBP2+

USBP3USBP3+

USBP4USBP4+

USBP5USBP5+

USBP6USBP6+

USBP7USBP7+

USBRBIAS

USBP0- <31>

USBP0+ <31>

USBP1- <32>

USBP1+ <32>

USBP2- <30>

USBP2+ <30>

USBP3- <31>

USBP3+ <31>

USBP4- <23>

USBP4+ <23>

USBP5- <23>

USBP5+ <23>

USBP6- <27>

USBP6+ <27>

USBP7- <30>

USBP7+ <30>

USB3RN1 <31>

USB3RP1 <31>

USB3TN1 <31>

USB3TP1 <31>

USB3RN2 <32>

USB3RP2 <32>

USB3TN2 <32>

USB3TP2 <32>

USB_OC0# <12,31>

USB_OC1# <12,32>

USB_OC2# <12,31>

USB_OC3# <12>

-----> Ext Port 1

-----> Ext Port 2 charge

-----> WLAN/BT

-----> Ext Port 3

-----> Touch

-----> Camera

-----> USH

-----> WWAN

-----> Ext USB3 Port 1

-----> Ext USB3 Port 2 charge

-----> USB Port0 (JUSB1)

-----> USB Port1 (JUSB3)

-----> USB Port3 (JUSB2)

PCH_GPIO9<12>

PCH_SMB_ALERT#<7>

PCH_BATLOW#<9>

USBRBIAS

CAD NOTE:

Route single-end 50-ohms and max 500-mils length.

Avoid routing next to clock pins or under stitching capacitors.

Recommended minimum spacing to other signal traces is 15

mils.

PCB

H12 UMA W WAN

H12 Entry

H14 DSC

H14 UMA

H14D_En

H14U_En

H15 DSC

H15 UMA

H15D_En

H15U_En

RPC19

4 5

3

2

1

10K_8P4R_5%

22.6_0402_1%

12

RC152

USB2 7

WWAN

WWAN

WWAN

WWAN

+3.3V_ALW_PCH

6

7

8

NA

N

A

NA

NA

NA

+PCH_VCCDSW3_3

H14U_En

H15 DSC

A A

H15 UMA

H15D_En

H15U_En

SD card

SD card

SD card

SD card

SD card

5

NA

NA

NA

NA

NA

LOM

LOM

LOM

LOM

LOM

WLAN

WLAN

WLAN

WLAN

WLAN

WIGIG

GPU

WIGIG

GPU

WIGIG

NA

WIGIG

M2 3042

(HCA & SATA-Cache)

WIGIG

NA

4

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

2

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

CPU (6/12)

CPU (6/12)

CPU (6/12)

LA-A901P

LA-A901P

LA-A901P

11 53Thursday, March 06, 2014

11 53Thursday, March 06, 2014

11 53Thursday, March 06, 2014

1

0.3

0.3

0.3

5

+PCH_VCCDSW3_3

LAN_WAKE#

RPC10

4 5

3

2

1

10K_8P4R_5%

RPC5

4 5

3

2

1

10K_8P4R_5%

RPC7

4 5

3

2

1

10K_8P4R_5%

12

PM_LANPHY_ENABLE

12

MPHYP_PWR_EN

12

SIO_EXT_SCI#

12

SLATE_MODE

6

7

MEDIACARD_RST#

8

PCH_GPIO44

6

7

PCH_GPIO16

8

PCH_GPIO57

6

KB_DET#

7

8

TPM_PIRQ#

12

PCH_GPIO59

12

3.3V_CAM_EN#

12

NFC_IRQ

12

MPHYP_PWR_EN

12

10K_0402_5%

USB_OC0# <11,31>

AC_PRESENT <9,36>

USB_OC2# <11,31>

LANCLK_REQ# <7,28>

USB_OC3# <11>

USB_OC1# <11,32>

PM_LANPHY_ENABLE<28>

PCH_NFC_RST for Goliad

TOUCH_PANEL_INTR#<23>

+3.3V_RUN

1K_0402_5%

12

RC176@

1K_0402_5%

12

RC181@

MEDIACARD_IRQ#<29>

MPHYP_PWR_EN<38>

KB_DET#<37>

PCH_GPIO66

RC153 10K_0402_5%

RC92 10K_0402_5%

@

+3.3V_RUN

D D

RC155 100K_0402_5%

RC156 100K_0402_5%

+PCH_VCCDSW3_3

C C

+3.3V_ALW_PCH

+3.3V_RUN

B B

RC247 10K_0402_5%

RC245 100K_0402_5%

RC174 100K_0402_5%

RC175 100K_0402_5%

@

RC171

SIO_EXT_WAKE#<9,36>

TPM_PIRQ#<27>

LAN_WAKE#<28,36>

T22

@ PAD~D

T21@ PAD~D

3.3V_CAM_EN#<23>

SIO_EXT_SMI#<36>

PCH_GPIO46<9>

PCH_GPIO9<11>

T27@ PAD~D

mSATA _DEVS LP<30>

HDD_DEVSLP<20>

SIO_EXT_SCI#<36>

SPKR<21>

4

@

UC1J

PCH_GPIO76

SIO_EXT_WAKE# SIO_RCIN#

HOST_ALERT1_R_N

PCH_GPIO16

TPM_PIRQ#

LAN_WAKE#

NFC_IRQ

MEDIACARD_RST#

PCH_GPIO57

SLATE_MODE

PCH_GPIO59

PCH_GPIO44

MEDIACARD_IRQ#

DIMM_DET

PCH_GPIO49

TOUCH_PANEL_INTR#

MPHYP_PWR_EN

KB_DET#

PCH_GPIO14

3.3V_CAM_EN#

SIO_EXT_SMI#

PCH_GPIO10

SIO_EXT_SCI#

SPKR

+3.3V_RUN

10K_0402_5%

12

RC302@

10K_0402_5%

12

RC303

P1

BMBUSY/GPIO76

AU2

GPIO8

AM7

LAN_PHY_PWR_CTRL/GPIO12

AD6

GPIO15

Y1

GPIO16

T3

GPIO17

AD5

GPIO24

AN5

GPIO27

AD7

GPIO28

AN3

GPIO26

AG6

GPIO56

AP1

GPIO57

AL4

GPIO58

AT5

GPIO59

AK4

GPIO44

AB6

GPIO47

U4

GPIO48

Y3

GPIO49

P3

GPIO50

Y2

HSIOPC/GPIO71

AT3

GPIO13

AH4

GPIO14

AM4

GPIO25

AG5

GPIO45

AG3

GPIO46

AM3

GPIO9

AM2

GPIO10

P2

DEVSLP0/GPIO33

C4

SDIO_POWER_EN/GPIO70

L2

DEVSLP1/GPIO38

N5

DEVSLP2/GPIO39

V2

SPKR/GPIO81

BDW-ULT-DDR3L_BGA1168

10 OF 19

DIMM_DET

BDW_ULT_DDR3L

GPIO

+3.3V_ALW_PCH

1K_0402_5%

12

RC179

HOST_ALERT1_R_N

3

CPU/

MISC

SERIAL IO

THRMTRIP

RCIN/GPIO82

SERIRQ

PCH_OPI_RCOMP

RSVD

RSVD

GSPI0_CS/GPIO8 3

GSPI0_CLK/GP IO84

GSPI0_MISO/GPI O85

GSPI0_MOSI/GPI O86

GSPI1_CS/GPIO8 7

GSPI1_CLK/GP IO88

GSPI1_MISO/GPI O89

GSPI_MOSI/GPIO9 0

UART0_RXD/GPIO91

UART0_TXD/GPIO92

UART0_RTS/GPIO93

UART0_CTS/GPIO94

UART1_RXD/GPIO0

UART1_TXD/GPIO1

UART1_RST/GPIO2

UART1_CTS/GPIO3

I2C0_SDA/GP IO4

I2C0_SCL/GPIO5

I2C1_SDA/GP IO6

I2C1_SCL/GPIO7

SDIO_CLK/GPIO64

SDIO_CMD/GPIO65

SDIO_D0/GPIO66

SDIO_D1/GPIO67

SDIO_D2/GPIO68

SDIO_D3/GPIO69

+3.3V_RUN

D60

V4

T4

AW15

AF20

AB21

R6

L6

N6

L8

R7

L5

N7

K2

J1

K3

J2

G1

K4

G2

J3

J4

F2

F3

G4

F1

E3

F4

D3

E4

C3

E2

1K_0402_5%

12

RC180@

H_THERMTRIP#_R

IRQ_SERIRQ

PCH_OPI_COMP

GC6_EVENT #_Q

BBS_BIT

PCH_GPIO87

3.3V_TP_EN

CPPE#

FFS_INT2

LCD_CBL_DET#

PCH_GPIO4

PCH_GPIO5

PCH_GPIO6

PCH_GPIO7

PCH_GPIO66

PCH_GPIO67

PCH_GPIO68

SPKR

2

SIO_RCIN# <36>

IRQ_SERIRQ <35,36>

GPU_GC6_FB _EN <10>

PCH_GPIO85 <6>

T109@PAD~D

3.3V_TP_EN <10>

3.3V_TS_EN <6,23>

3.3V_HDD_EN <20>

CPUSB# <7>

FFS_INT2 <20>

LCD_CBL_DET# <7,23>

USH_DET# <7,27>

CAM_MIC_CBL_DET# <10,23>

PCH_GPIO69 <7>

12

RC161@0_0402_5%

H_THERMTRIP# <36>

WLANCLK_REQ#<7,30>

SATA2_PCIE6_L1<6,35>

TOUCHPAD_INTR#<10>

WIGIGCLK_REQ#<7,30>

CONTACTLESS_DET#<10,27>

mCARD _PCIE #_SAT A<6,36>

MPCIE_RST#<6>

HDD_DET#<6,20>

MMICLK_REQ#<7,29>

PCH_GPIO80<10>

PCH_GPIO52<10>

CLKRUN#<9,35,36>

H_THERMTRIP#

PCH_GPIO76

CPPE#

FFS_INT2

PCH_GPIO67

PCH_GPIO68

TOUCH_PANEL_INTR#

SIO_RCIN#

IRQ_SERIRQ

GC6_EVENT #_Q

PCH_GPIO6

PCH_GPIO7

PCH_GPIO4

PCH_GPIO5

SIO_EXT_SMI#

PCH_GPIO87

MEDIACARD_IRQ#

PCH_OPI_COMP

1

RPC9

6

7

8

10K_8P4R_5%

1 2

RPC17

6

7

8

10K_8P4R_5%

RPC16

6

7

8

10K_8P4R_5%

RPC3

6

7

8

10K_8P4R_5%

RPC4

6

7

8

10K_8P4R_5%

RPC8

1

2

3

4 5

10K_8P4R_5%

+3.3V_ALW_PCH

45

3

2

1

RC17849.9_0402_1%

+1.05V_VCCST

12

RC251K_0402_5%

45

3

2

1

12

RC160100K_0402_5%

12

RC158100K_0402_5%

12

RC16310K_0402_5%

12

RC16410K_0402_5%

45

3

2

1

45

3

2

1

45

3

2

1

8

7

6

+3.3V_RUN

+3.3V_RUN

DIMM Detect

HIGH

LOW(DEFAULT)

A A

ENABLE

DISABLE

HIGH

LOW

1 DIMM

2 DIMM

TLS CONFIDENTIALITYTOP-BLOCK SWAP OVERRIDE

HIGH

LOW(DEFAULT)

ENABLE

DISABLE

No Reboot on TCO Timer expiration

HIGH

LOW(DEFAULT)

ENABLE

DISABLE

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

CPU (7/12)

CPU (7/12)

CPU (7/12)

LA-A901P

LA-A901P

LA-A901P

12 53Thursday, March 06, 2014

12 53Thursday, March 06, 2014

12 53Thursday, March 06, 2014

1

0.3

0.3

0.3

5

D D

4

3

2

1

CFG STRAPS for CPU

@

UC1S

AC60

CFG_RCOMP

12

TDI_IREF

CFG0

CFG1

CFG4

CFG8

CFG9

CFG10

CFG_RCOMP

TDI_IREF

CFG0

AC62

CFG1

AC63

CFG2

AA63

CFG3

AA60

CFG4

Y62

CFG5

Y61

CFG6

Y60

CFG7

V62

CFG8

V61

CFG9

V60

CFG10

U60

CFG11

T63

CFG12

T62

CFG13

T61

CFG14

T60

CFG15

AA62

CFG16

U63

CFG18

AA61

CFG17

U62

CFG19

V63

CFG_RCOMP

A5

RSVD

E1

RSVD

D1

RSVD

J20

RSVD

H18

RSVD

B12

TD_IREF

BDW-ULT-DDR3L_BGA1168

19 OF 19

CFG0<9>

CFG1<9>

CFG2<9>

CFG3<9>

CFG4<9>

CFG5<9>

CFG6<9>

CFG7<9>

CFG8<9>

CFG9<9>

CFG10<9>

CFG11<9>

CFG12<9>

CFG13<9>

C C

CFG14<9>

CFG15<9>

CFG16<9>

CFG18<9>

CFG17<9>

CFG19<9>

RC185 49.9_0402_1%

1 2

RC186 8.2K_0402_1%

BDW_ULT_DDR3L

RESERVED

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

PROC_OPI_RCOMP

RSVD

RSVD

VSS

VSS

RSVD

RSVD

AV63

AU63

C63