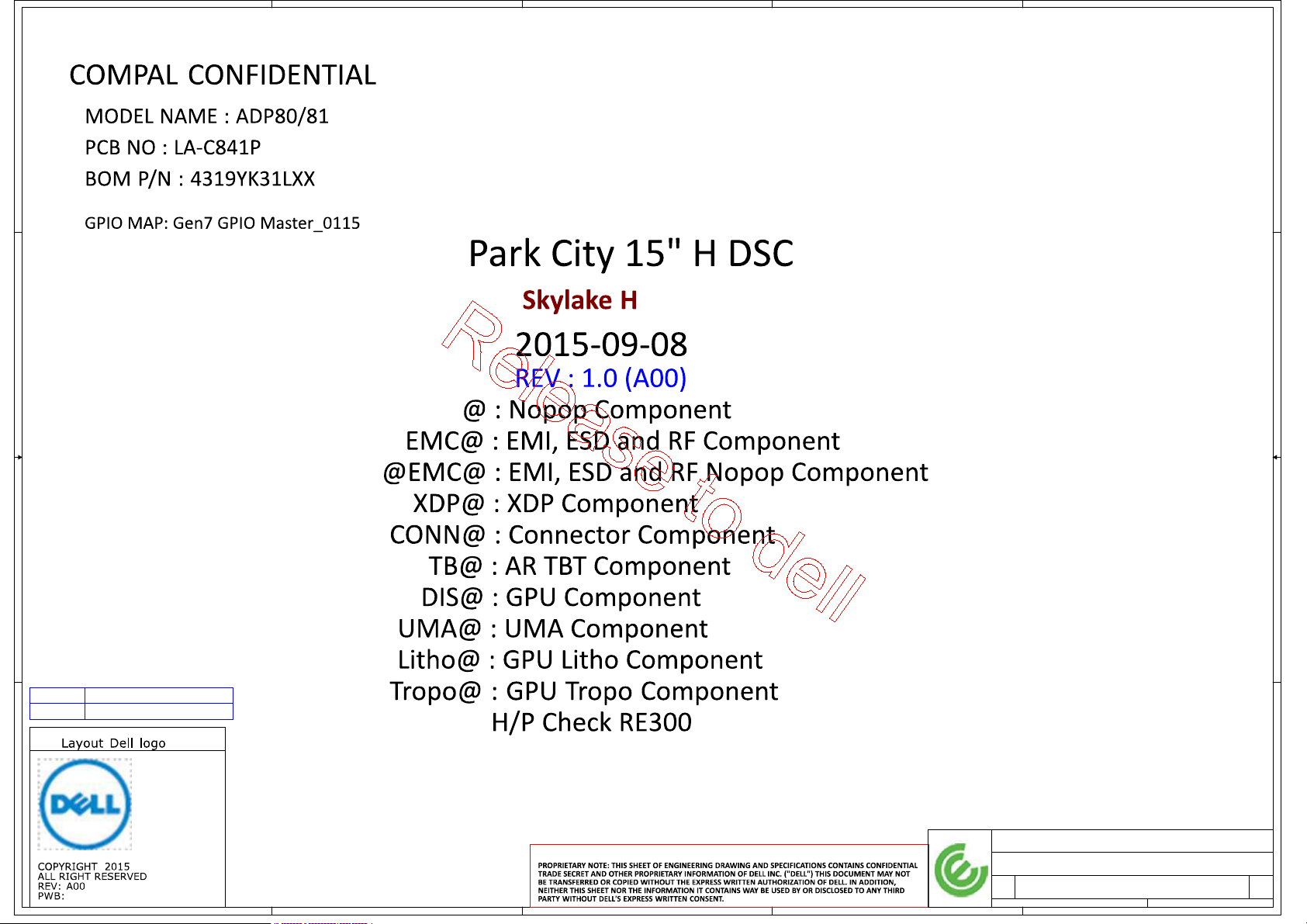

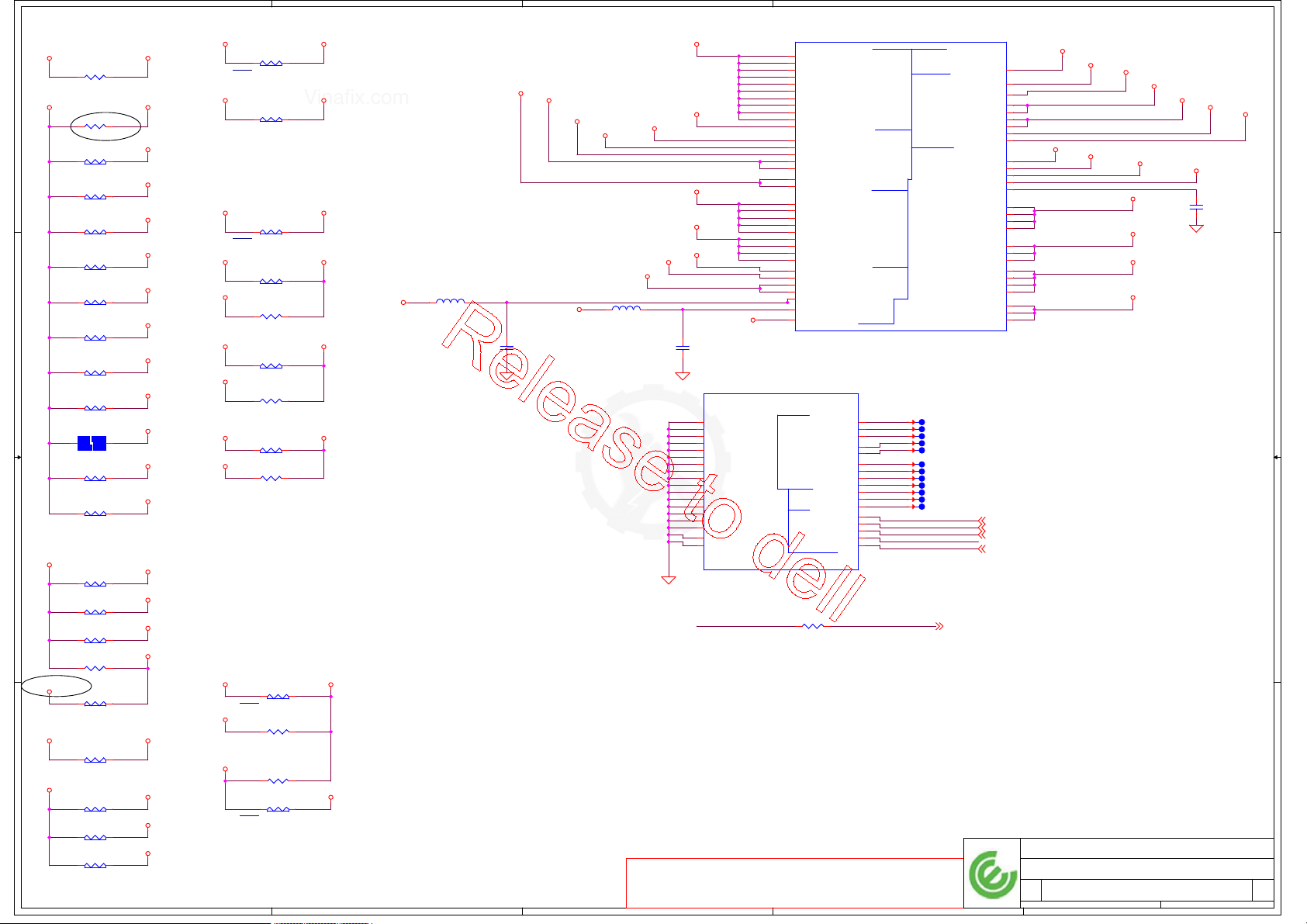

Dell Latitude E5270, Latitude E5470, Latitude E5570, Precision 3510 Schematics

Vinafix.com

A

1 1

2 2

B

C

D

E

3 3

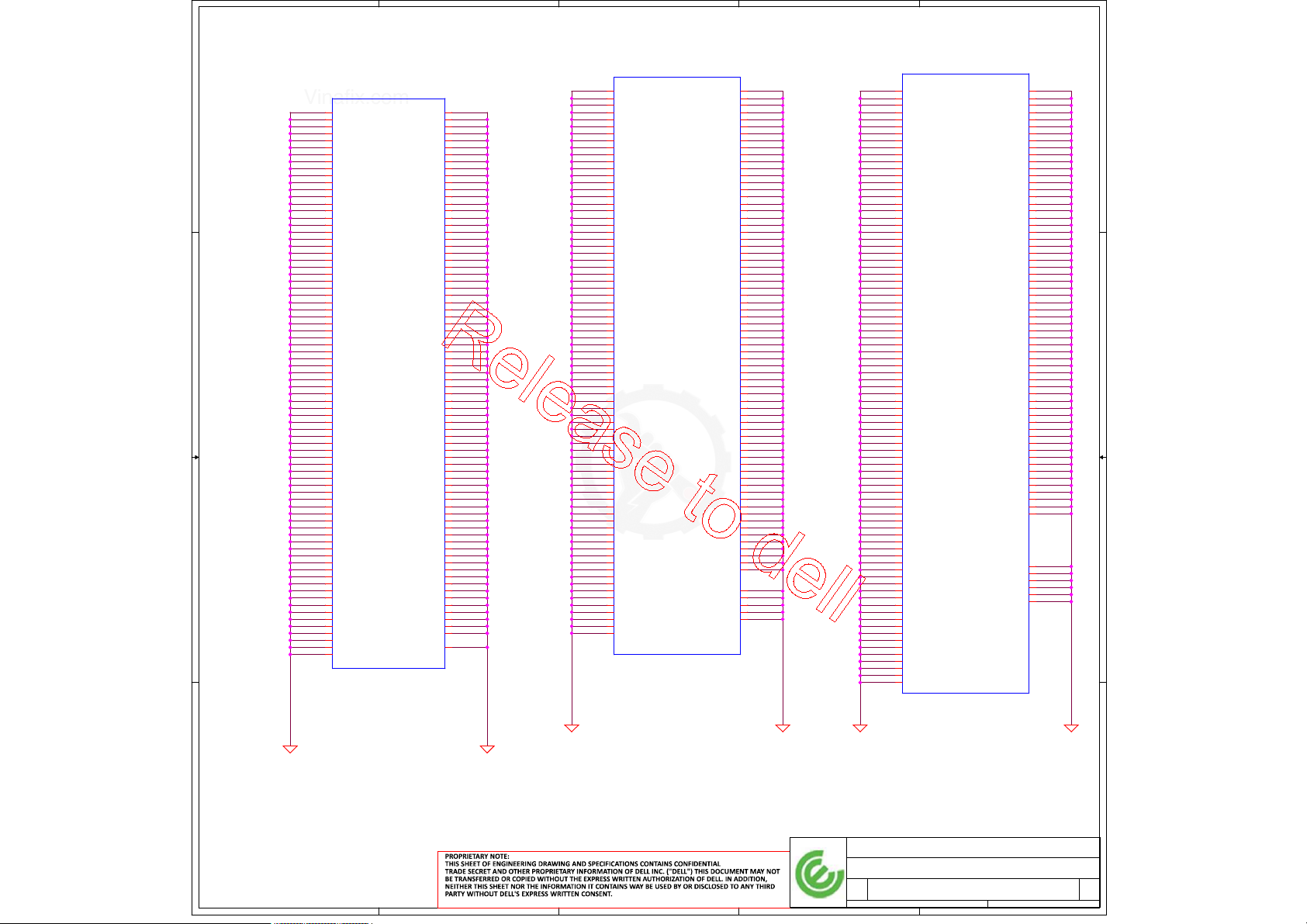

MB PCB

Part Number

DAZ1EO00101 PCB ADP80 LA-C841P LS-C641P

4 4

Description

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size

Size

Size

Date : Sheet o f

Date : Sheet o f

A

B

C

D

Date : Sheet o f

Compal Electronics, Inc.

Cover Sheet

Cover Sheet

Document Number Re v

Document Number Re v

Document Number Re v

Cover Sheet

LA-C841P

LA-C841P

LA-C841P

E

1 74Tuesday, September 08, 2015

1 74Tuesday, September 08, 2015

1 74Tuesday, September 08, 2015

0.1

0.1

0.1

Vinafix.com

A

1 1

2 2

B

C

D

E

3 3

4 4

DELL CONFIDENTIAL/PROPRIETARY

A

B

C

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size

Size

Size

Date: Sheet of

Date: Sheet of

Date: Sheet of

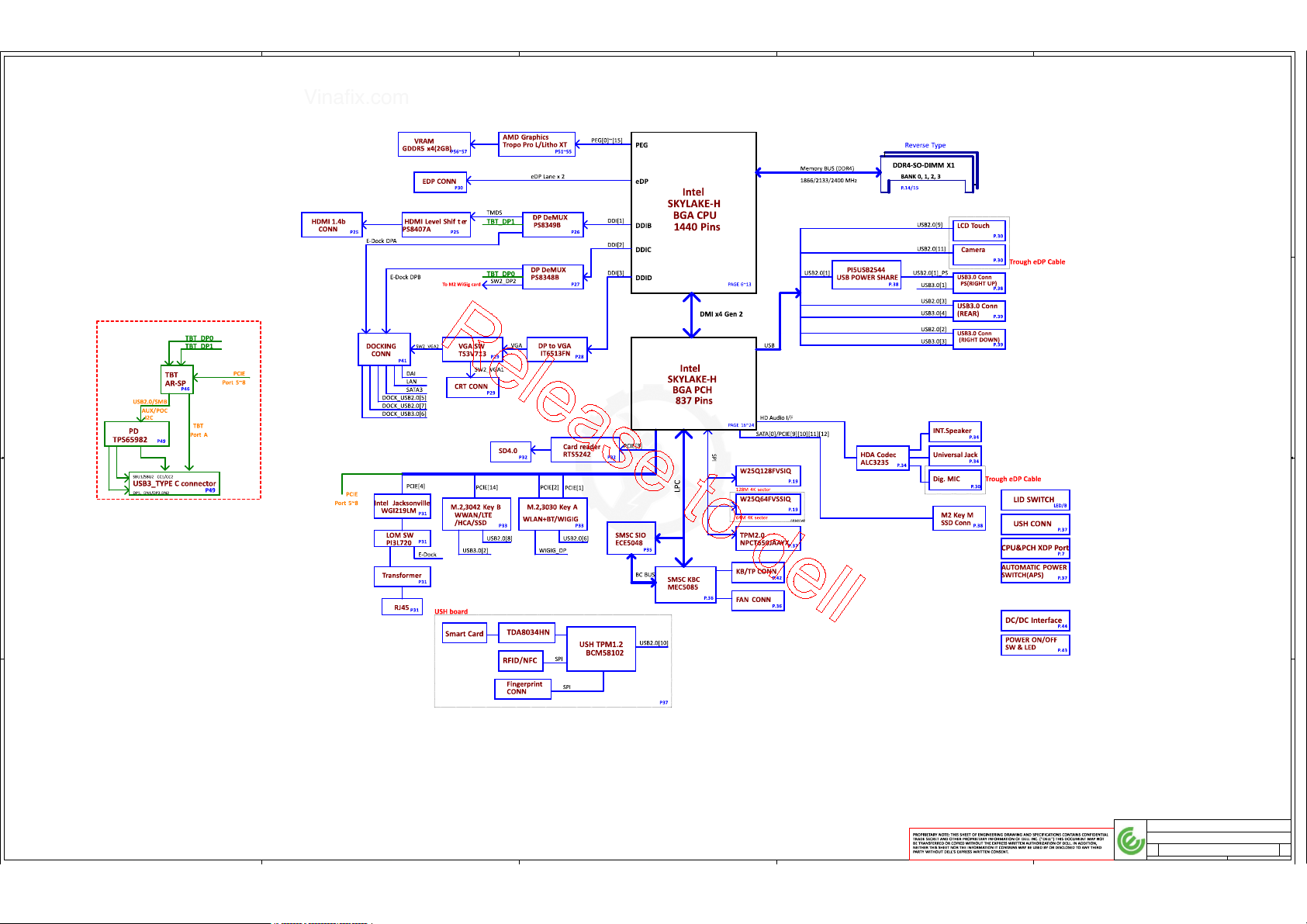

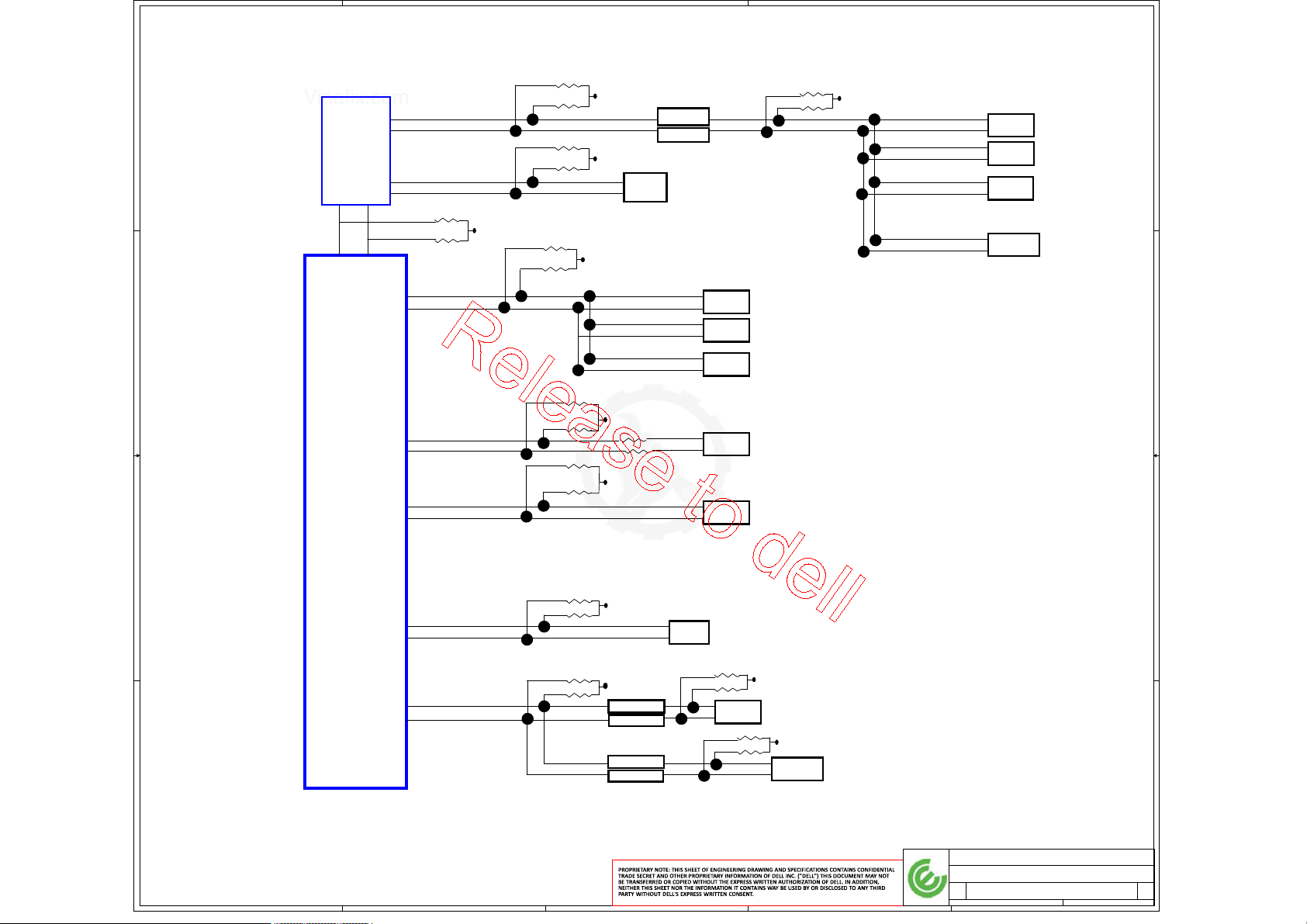

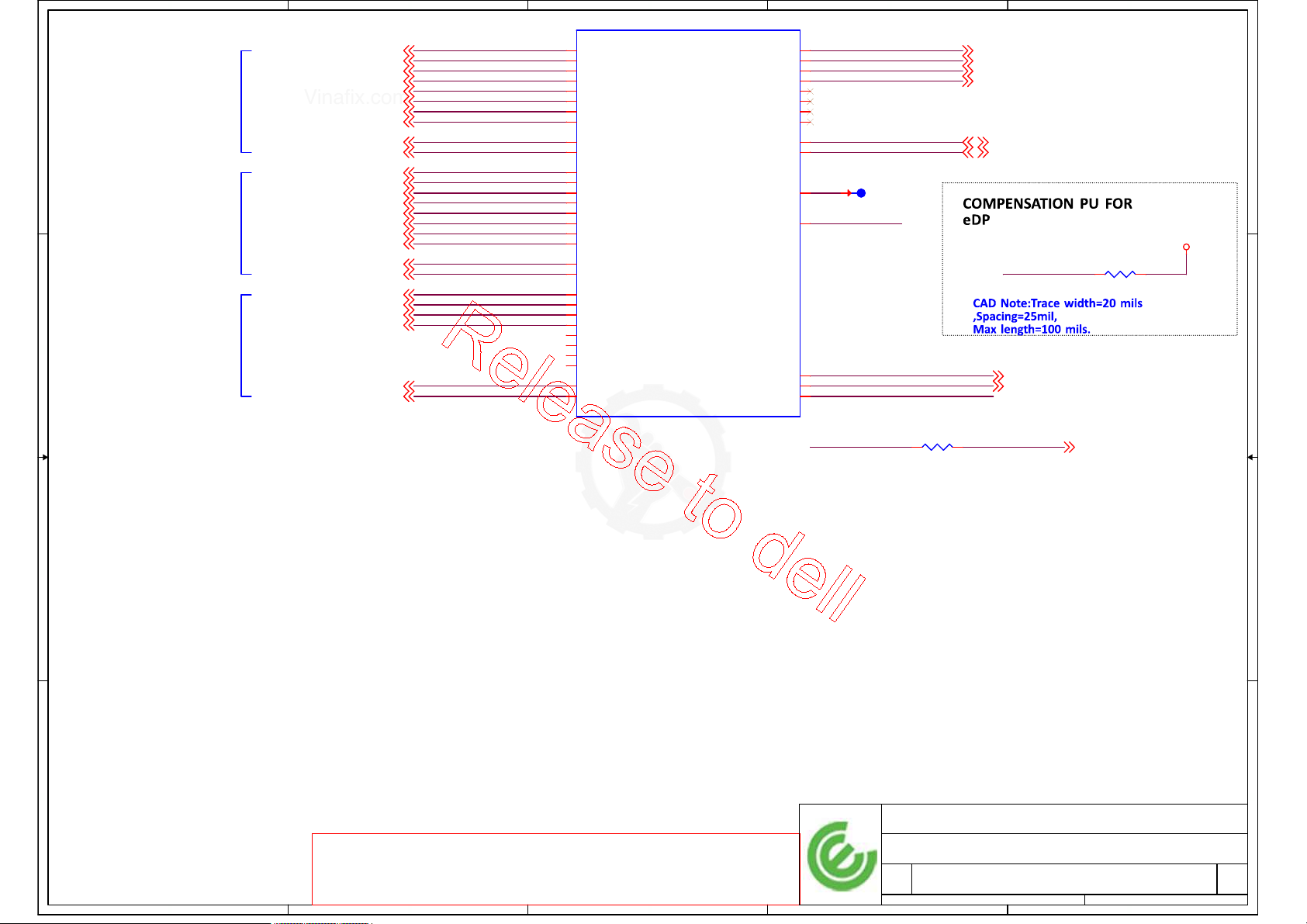

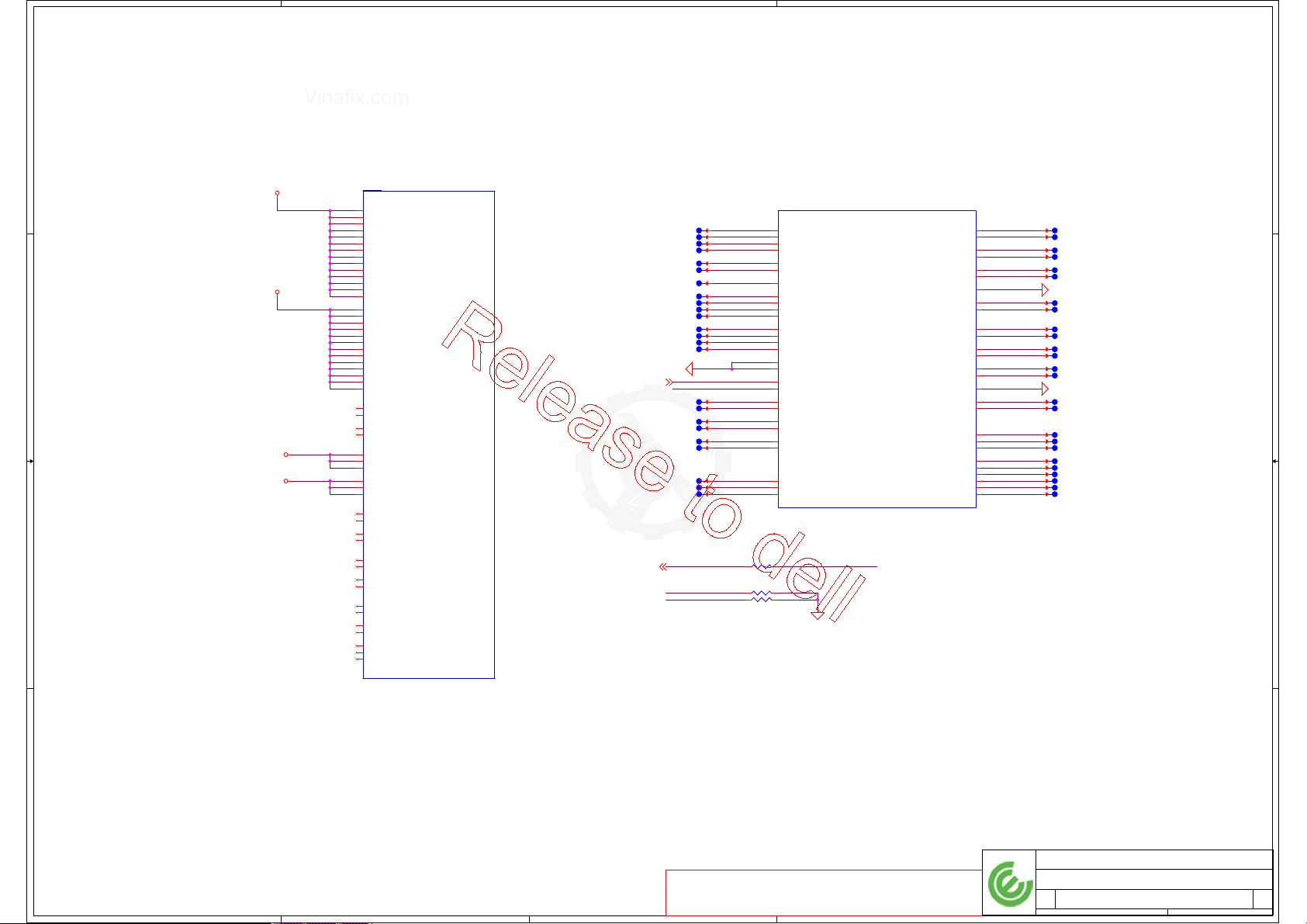

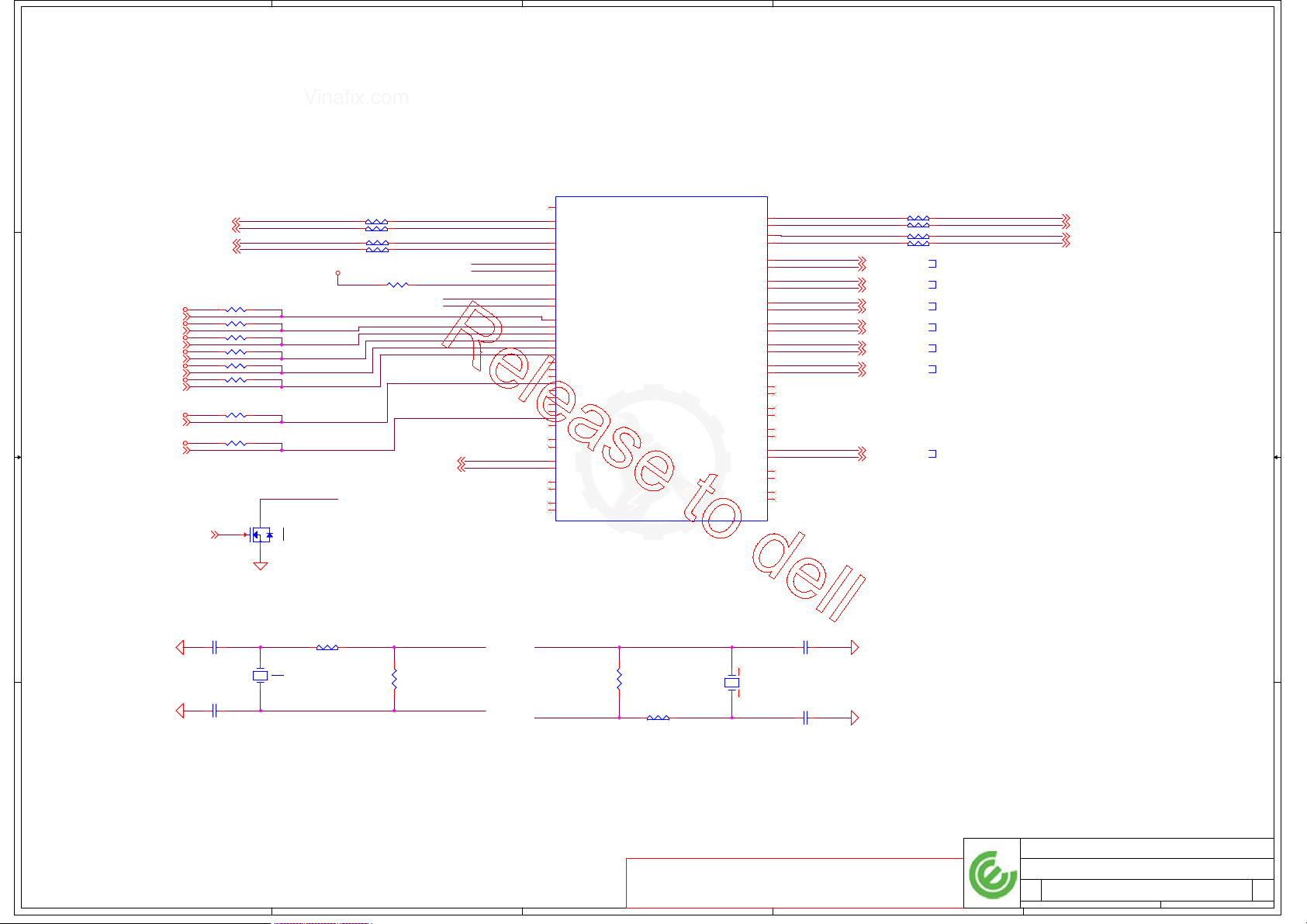

Block diagram

Block diagram

Block diagram

Document Number Rev

Document Number Rev

Document Number Rev

LA-C841P

LA-C841P

LA-C841P

2 74Tuesday, September 08, 2015

2 74Tuesday, September 08, 2015

E

2 74Tuesday, September 08, 2015

0.1

0.1

0.1

Vinafix.com

5

4

3

2

1

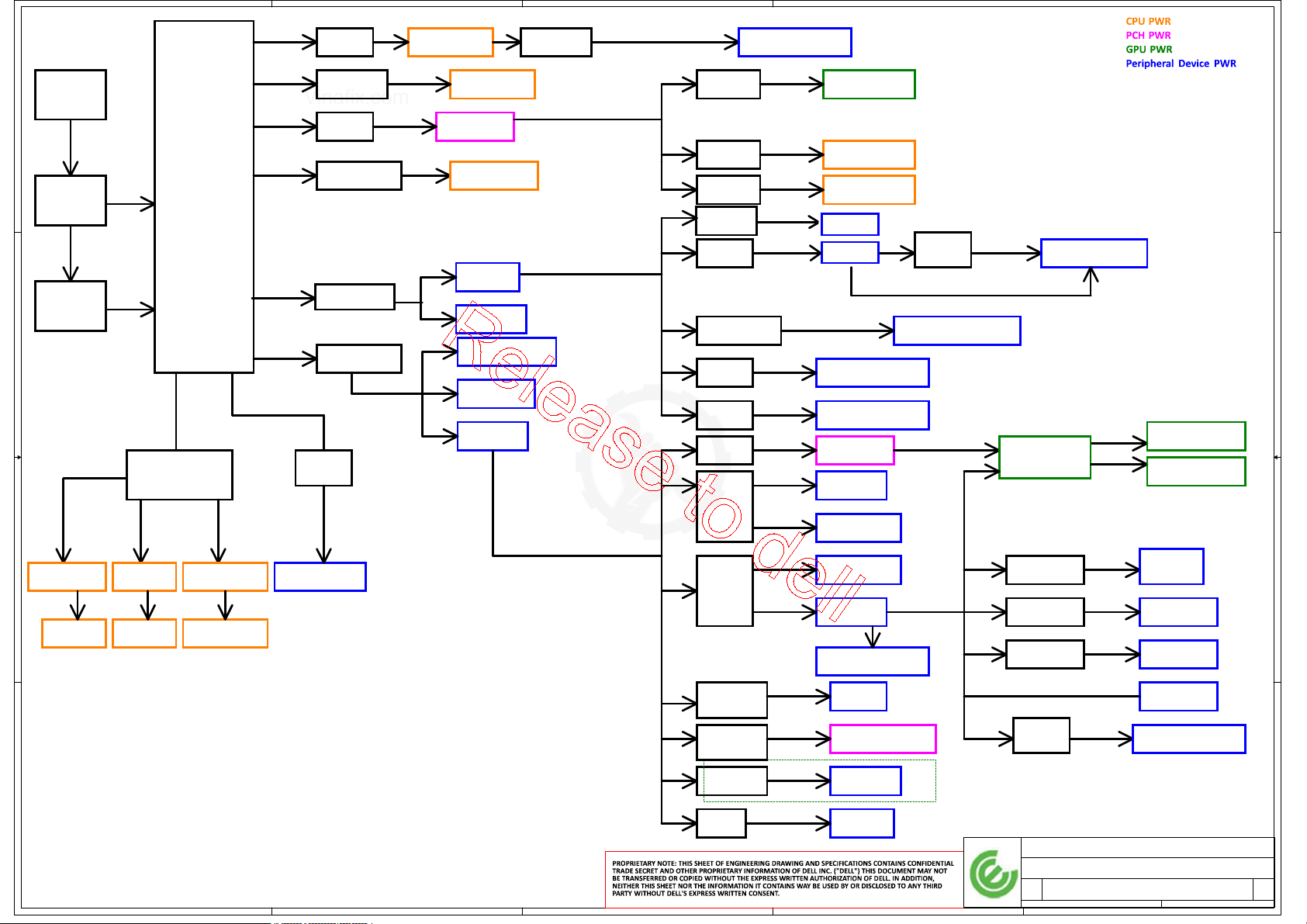

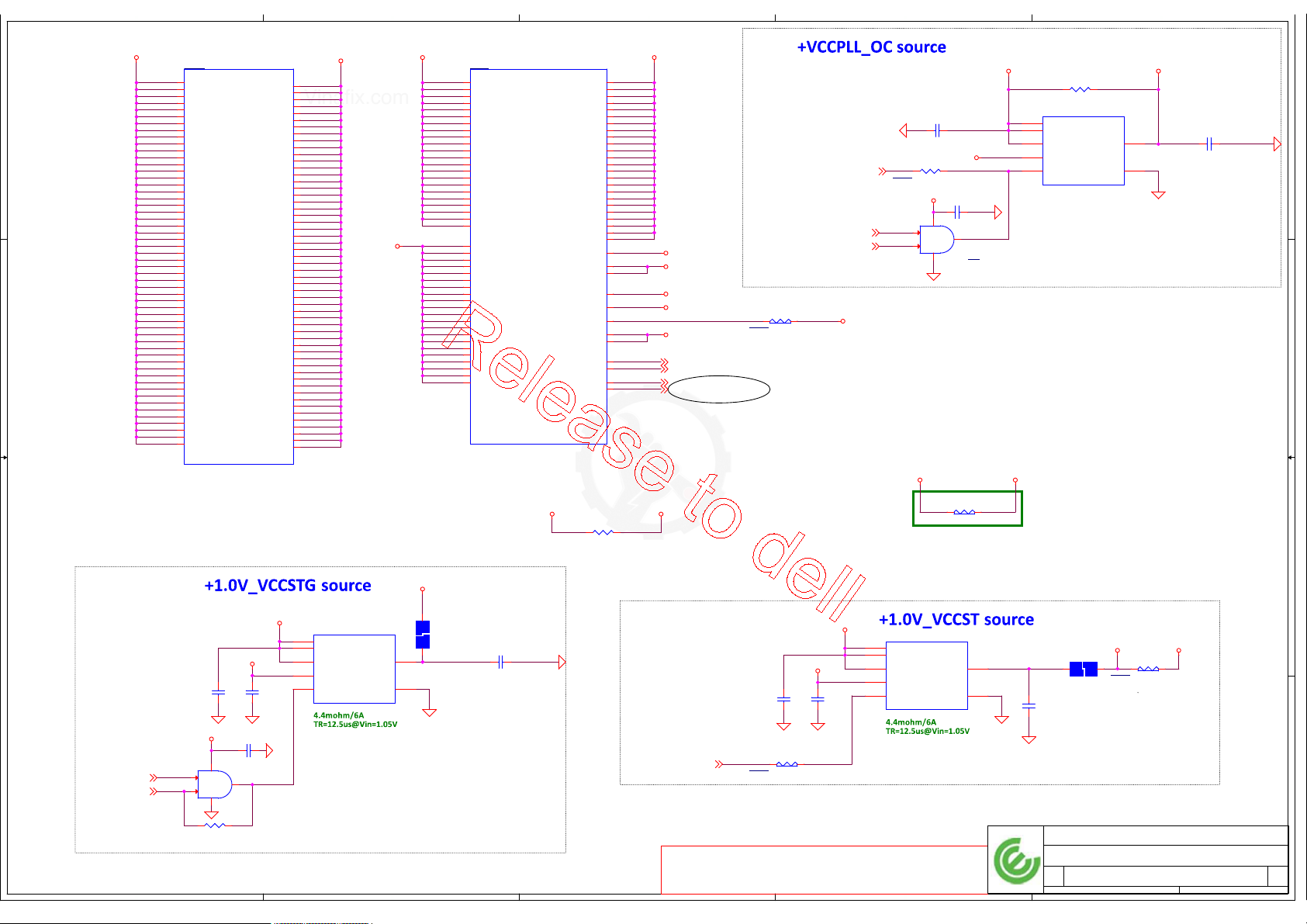

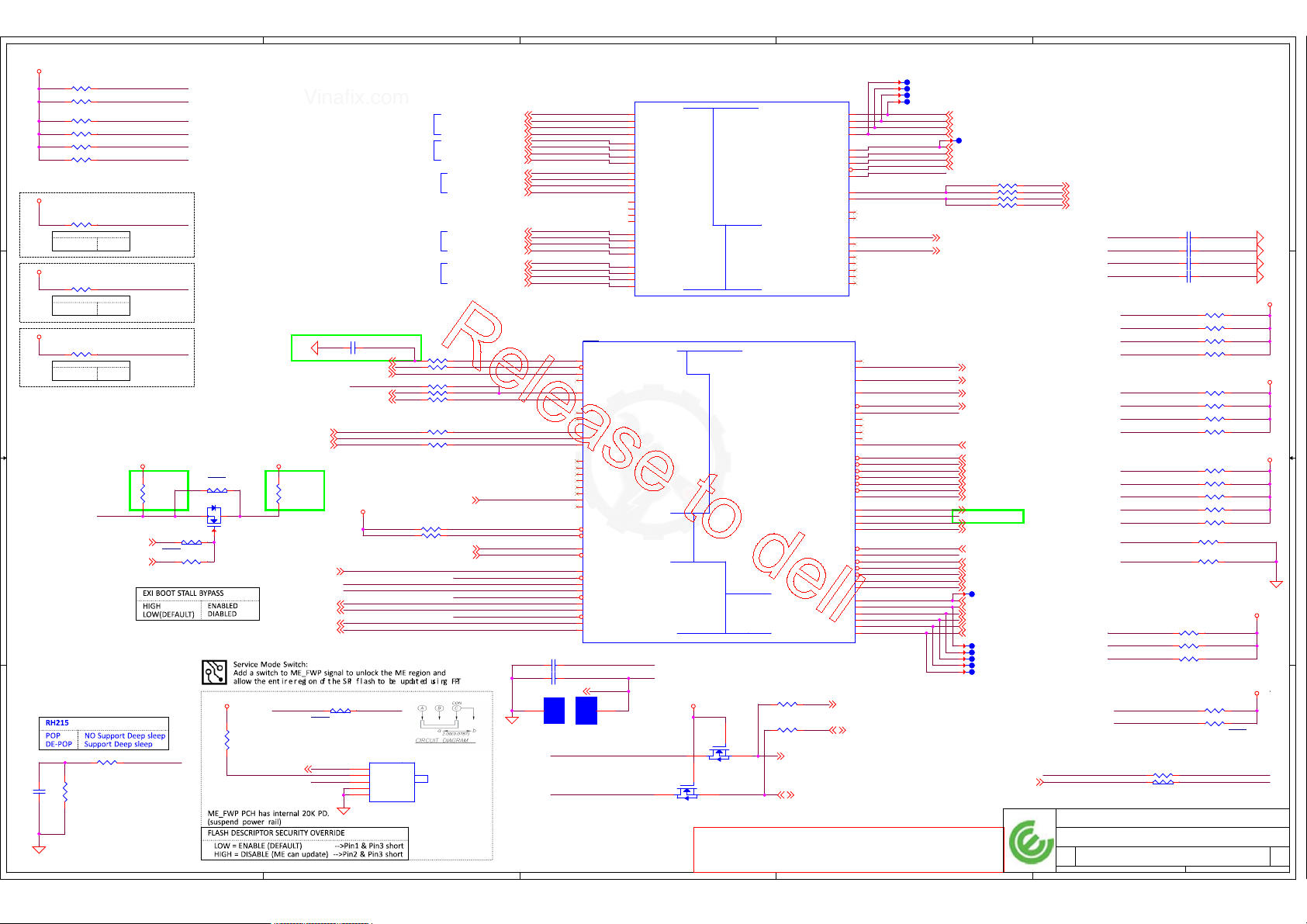

POWER STATES

RUN

State

Signal

S0 (Full ON) / M0

D D

S3 (Suspend to RAM) / M3 LOW

SLP

S3#

HIGH

SLP

SLP

S5#

S4#

HIGH HIGH

HIGH HIGH

ALWAYS

SLP

PLANE

A#

HIGH

ON

ON ON ON

HIGH

M

PLANE

ON

SUS

PLANE

ON ON ON

PLA NE

OFF

CLOCKS

OFF

S4 (Suspend to DISK) / M3

S5 (SOFT OFF) / M3

S3 (Suspend to RAM) / M-OFF

S4 (Suspend to DISK) / M-OFF

S5 (SOFT OFF) / M-OFF

HIGH HIGH

LOW

LOW

LOW

LOW

HIGH HIGH

LOW

LOW LOW LOW

HIGH

LOW LOW LOW LOW

ON ON

HIGH

ON ON

ON ON

LOW

ON

ON

OFF

OFFLOW

OFF

OFF

OFF

OFF

OFF OFF OFF

OFF OFF OFF OFF

OFF OFF OFF OFF

PM TABLE

C C

power

plane

State

S0

B B

S3

S5 S4/AC

+5V_ALW

+3.3V _ALW

+3.3V_ALW_DSW

+3.3V_SUS

+3.3V_A LW_PCH +1.2V_MEM

+RTC_CELL

+1.8V_PRIM

+1.0V_VCCST

+2.5V_ME M

+1.0V_PRIM

+1.0V_PRIM_CORE

+5V_A LW2

+3.3V_ALW2

+3.3V_RTC_LDO

+1.0V_MPHYGT

ON

ON

ON

ON ON

ON

OFF

+5V_RUN

+3.3V_RUN

+0.6V_DDR_VTT

+1.5V_RUN

OFF

OFF

(M-OFF)

+3.3V_M +3.3V_M

+VCC_CORE

+VCC_GT

+1.0VS_VCCIO

+VCC_SA

ON

ON

ON

ON

OFF

OFF

S5 S4/AC doe sn't ex ist

A A

OFFOFF

OFF

OFFOFF

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size

Size

Size

Date : Sheet o f

Date: Sheet o f

5

4

3

2

Date: Sheet o f

Compal Electronics, Inc.

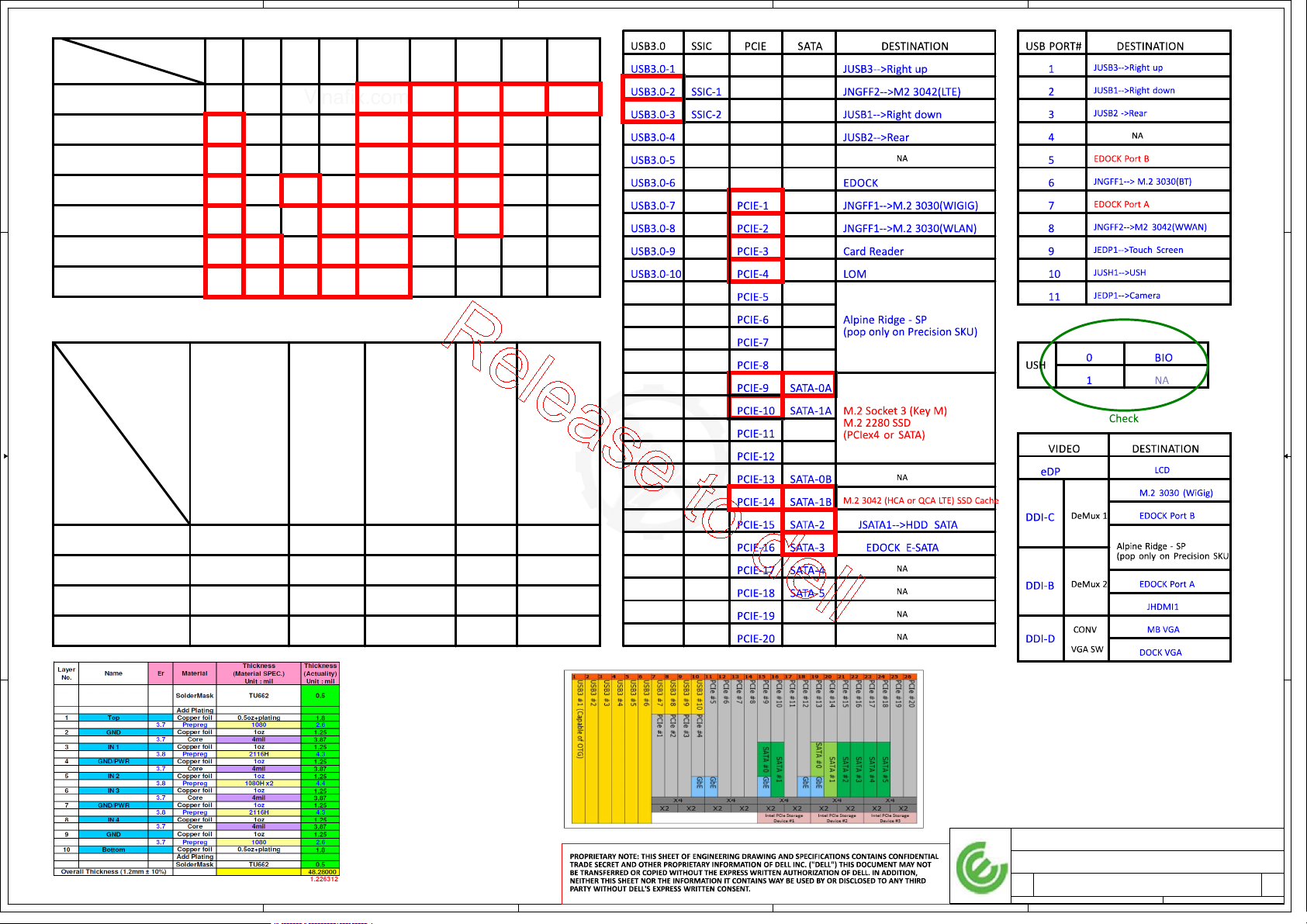

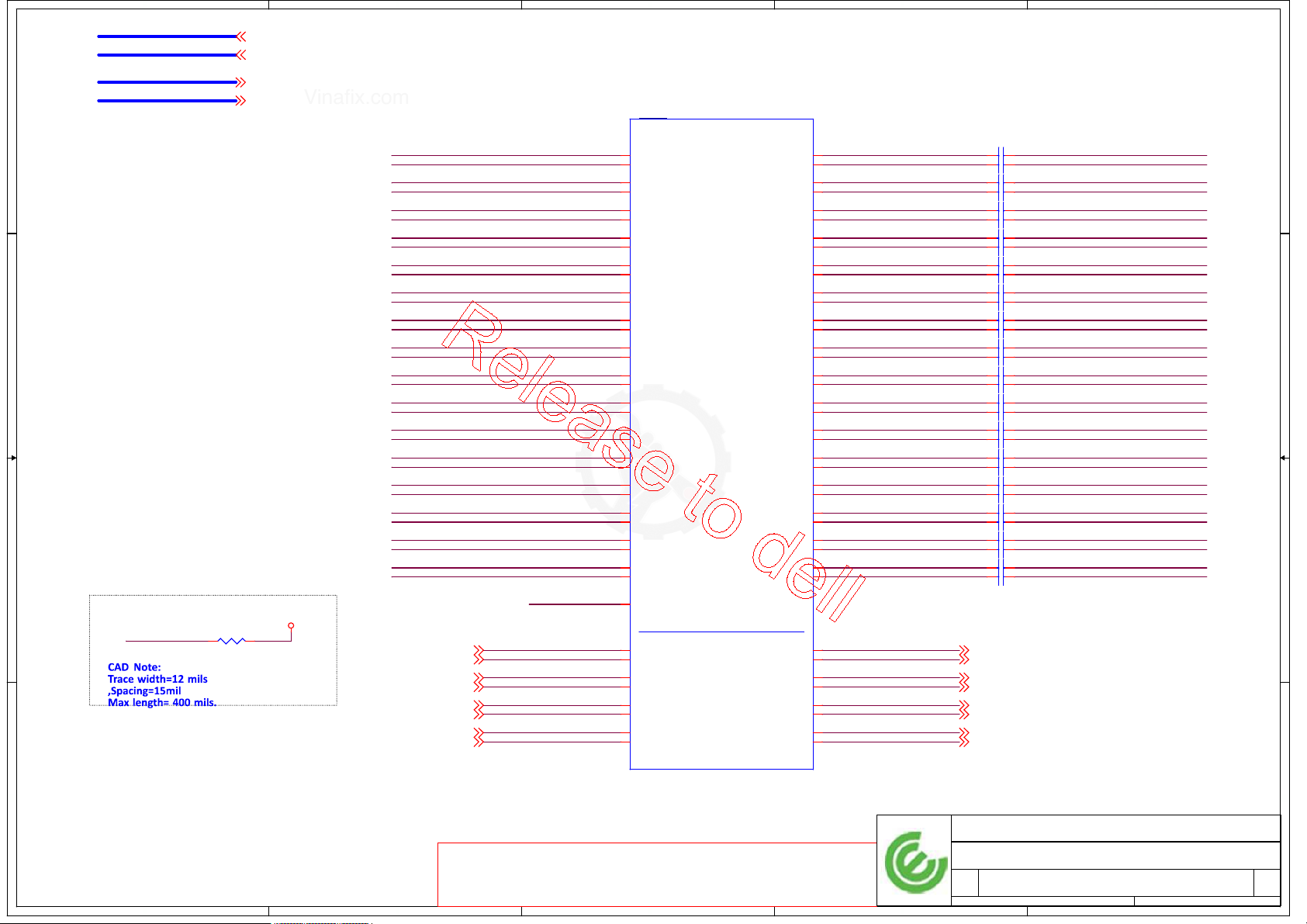

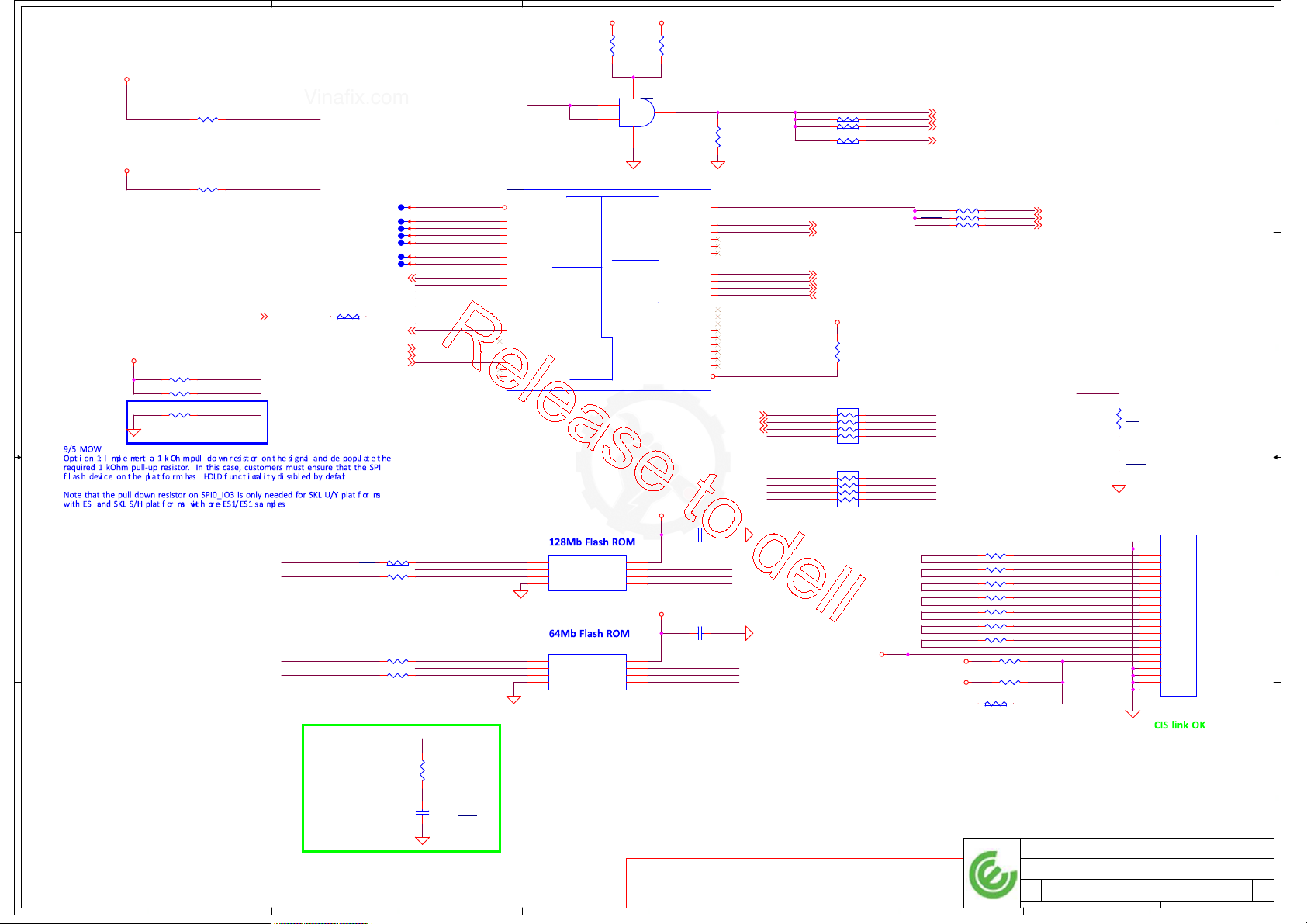

Port assignment

Port assignment

Document Number Re v

Document Number Rev

Document Number Rev

Port assignment

LA-C841P

LA-C841P

LA-C841P

1

3 74Tuesday, September 08, 2015

3 74Tuesday, September 08, 2015

3 74Tuesday, September 08, 2015

0.1

0.1

0.1

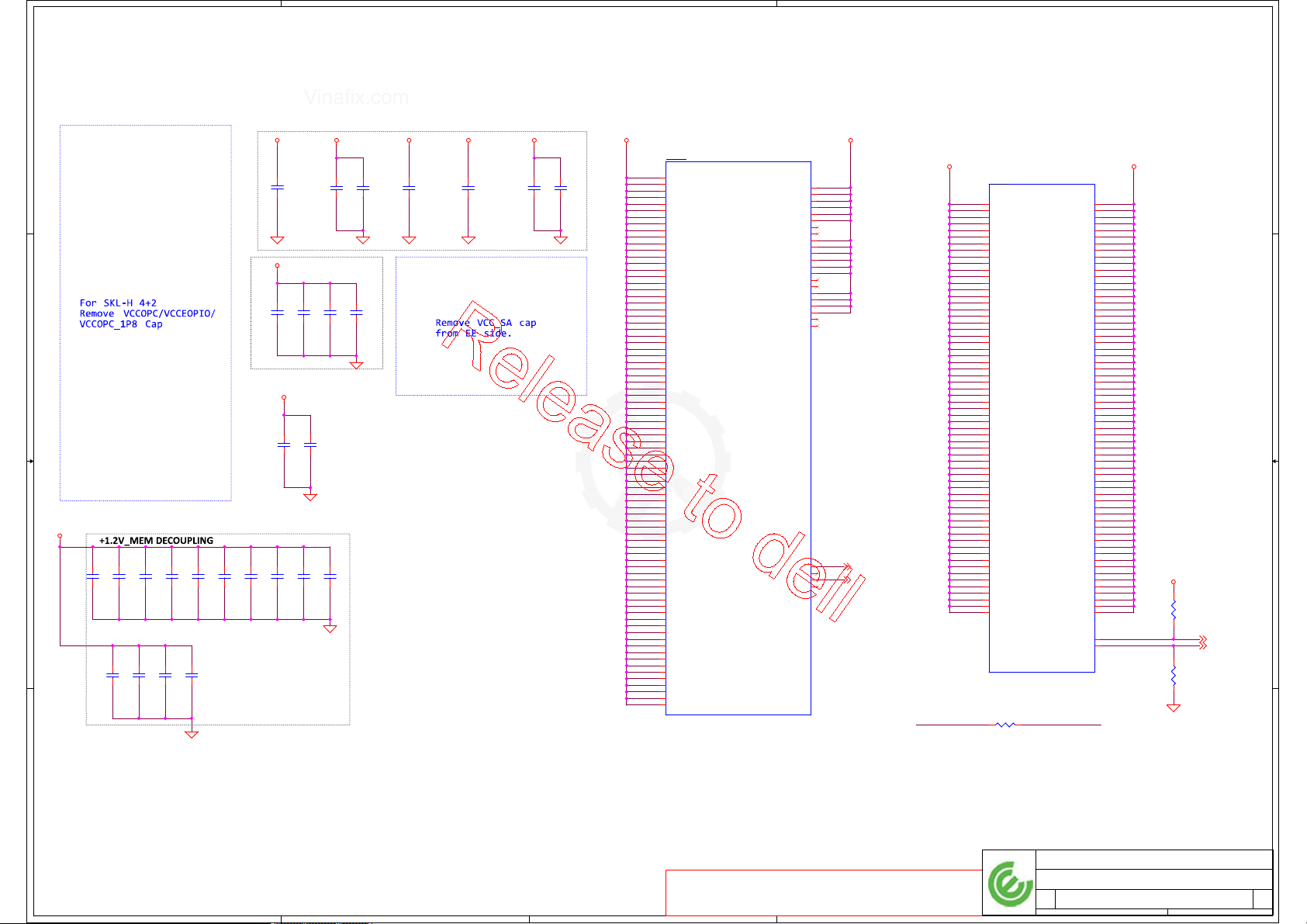

Vinafix.com

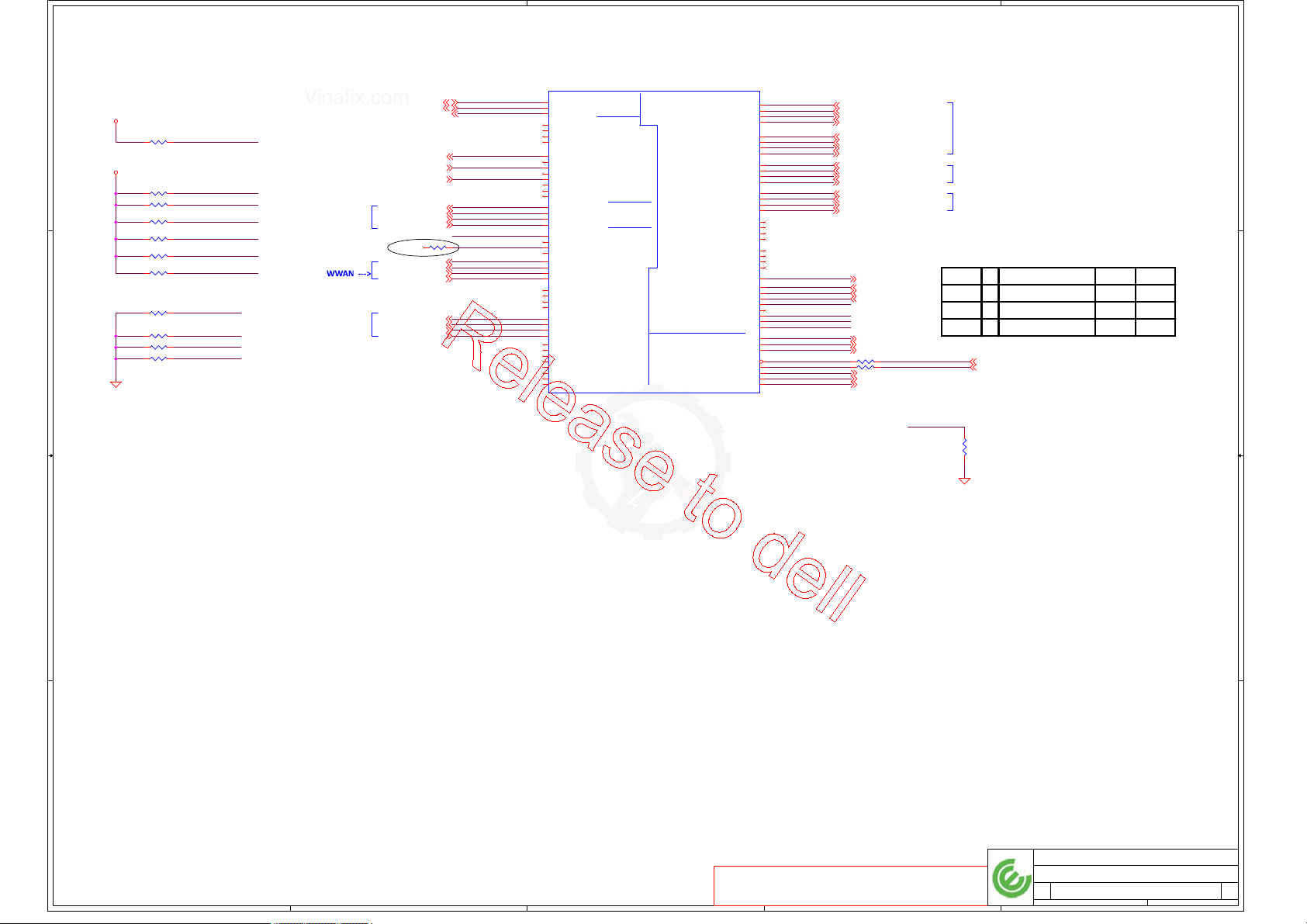

5

RT8207M

(PU201)

AP7175SP

ADAPTER

D D

CHARGER

BQ24777

(PU801)

+PWR_SRC

BATTERY

C C

SIC531CDT1GE

(PU602)

IMVP_V R_ON

B B

+VCC_SA

A A

IMVP_V R_ON

+VCC_GT

5

IMVP_V R_ON

+CPU_B++GPU_B++VCCSA_B+

+VCC_CORE

(PU1500)

SYX198D

(PU301)

SYX196DQNC

(PU401)

SY8286BRAC

(PU102)

SY8286CRAC

(PU100)

AO6405

(QV1)

EN_IN VPWR

+BL_PWR_SRC

SIO_SLP_S4#

SIO_SLP_S4#

SIO_SLP_SUS#

ALWON

ALWON

4

+1.2V_MEM

RUN_ ON

4

+2.5V_MEM

+1.0V_PRIM

+1.0VS_VCCIO

+5V_ALW

+5V_ALW2

+3.3V_RTC_LDO

+3.3V_ALW2

+3.3V_ALW

LDOI N

RT8207

(PU201)

3

0.6V_DDR_VTT_ ON

3

+0.6V_DDR_VTT

TPS22961

(UV27)

TPS22961

(UZ19)

TPS22961

(UZ18)

TPS22967

(UZ23)

EM5209

(UZ4)

PI5USB2544

(UI3)

SY6288

(UI1)

SY6288

(UI2)

SY8032A

(PU501)

EM5209

(UZ3)

3.3V_WWA N_EN

EM5209

(UZ2)

AOZ1336

(UZ8)

EM5209

(UZ4)

TPS22967

(UZ18)

AP2821

(UV24)

+3.3V_RUN_GFX

SIO_SLP_S3#

SIO_SLP_S4#

HDD_ EN

RUN_ ON

USB_PWR_S HR_LFT_EN#

USB_PWR_E N1#

USB_PWR_E N2#

SIO_SLP_SUS#

SIO_SLP_LAN#

AUX_EN_WOWL

@SIO_SLP_WLAN#

@SIO_SLP_WLAN#

RUN_ ON

A_ON

SIO_SLP_SUS#

@PCH_A LW_ON

SUS_ON

ENVDD _PCH

2

+VGA_PCIE

+1.0V_VCCSTG

+1.0V_VCCST

+5V_HDD

+5V_RUN

+5V_USB_CHG_PWR

+USB_LEFT_PWR

+USB_REAR_PWR

+1.8V_PRIM

+3.3V_LAN

+3.3V_WLAN

+3.3V_WWAN

+3.3V_RUN

PJP10

+3.3V_RUN_AUDIO

+3.3V_M

+3.3V_ALW_PCH

+3.3V_CV2

USH/ B

+LCDVDD

2

EM5209

(UZ5)@

1

AUD_P WR_EN

PJP9

+5V_RUN_AUDIO

EM5209

(UV25)

LP2301

(QV8)

AP7175SP

(PU502)

LP2301A

(QZ1)

PJP36

EM5209

(UZ5)@

DGPU_PW R_EN

DGPU_PW R_EN

TS_EN

+3.3V_ RUN

3.3V_CAM_EN#

AUD_P WR_EN

+1.8V_RUN_GFX

+3.3V_RUN_GFX

+5V_TSP

+1.5V_RUN

+3.3V_CAM

+3.3V_HDD

+3.3V_RUN_AUDIO

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size

Size

Size

Date: Sheet of

Date: Sheet o f

Date: Sheet o f

Compal Electronics, Inc.

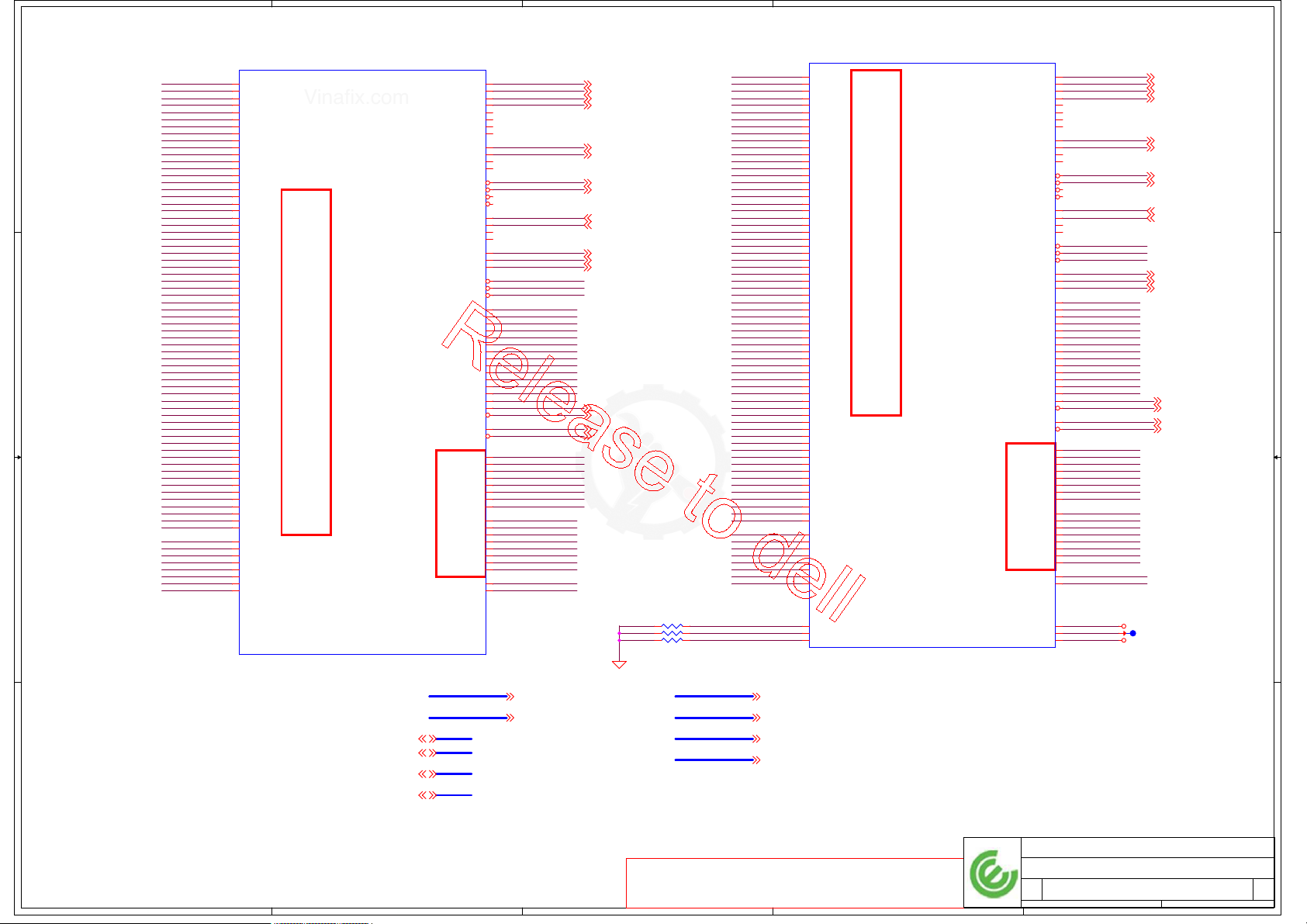

Power rails

Power rails

Document Number Re v

Document Number Rev

Document Number Rev

Power rails

LA-C841P

LA-C841P

LA-C841P

1

0.1

0.1

4 74Tuesday, September 08, 2015

4 74Tuesday, September 08, 2015

4 74Tuesday, September 08, 2015

0.1

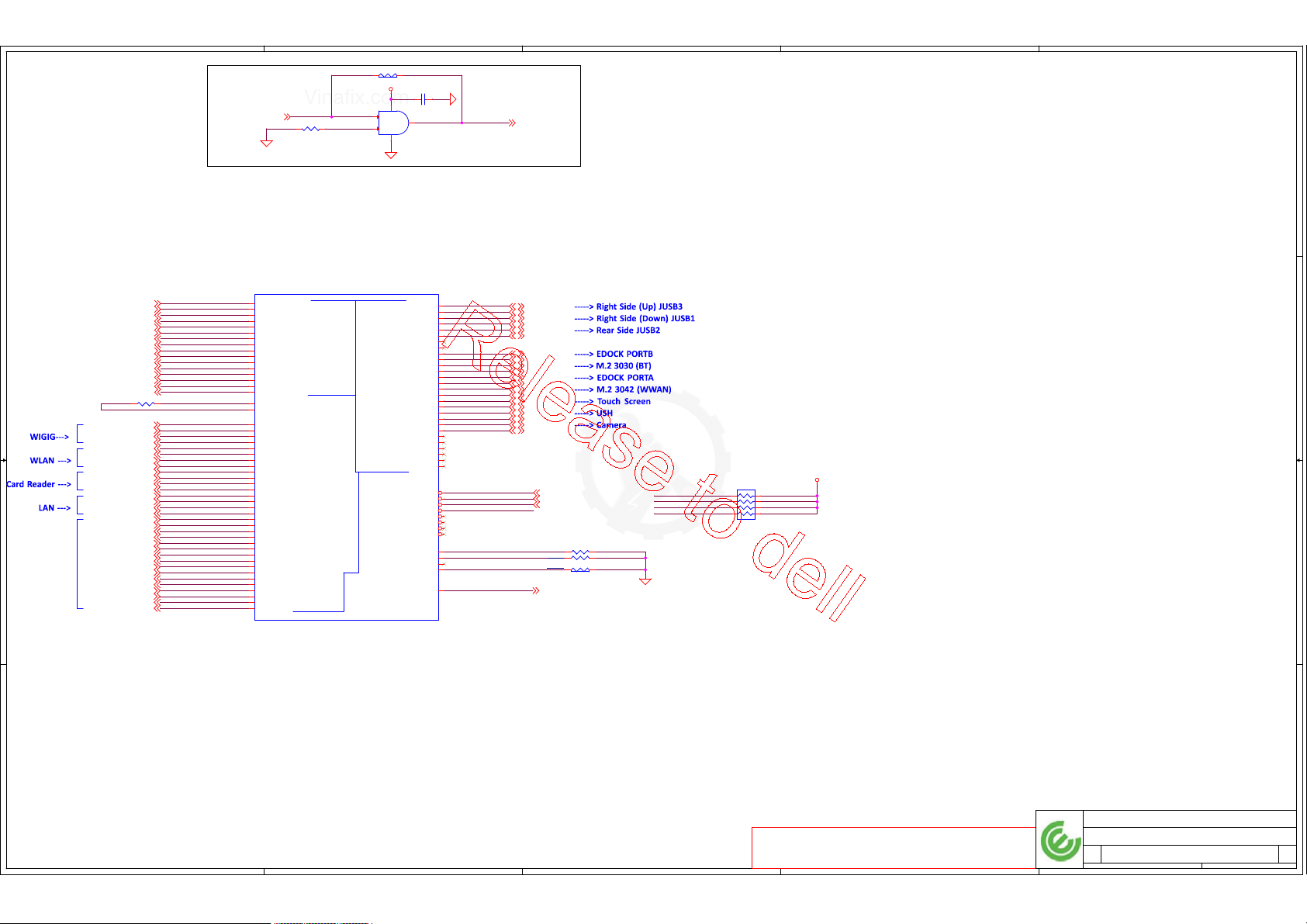

Vinafix.com

5

4

3

2

1

2.2K

2.2K

1K

1K

499

499

+3.3V _ALW_PCH

+3.3V_LAN

28

31

+3.3V_ALW

LOM

DMN66D0LDW

DMN66D0LDW

127

129

DOCKING

2.2K

2.2K

+3.3V_RUN

253

254

253

254

53

51

1

4

DIMM1

DIMM2

XDP1

LNG2DMTR

SMBUS Address [0x9a]

MEM_SMBCLK

D D

AW44

BB43

MEM_SMBDATA

PCH

LAN_SMBCLK

AY44

LAN_SMBDATA

BB39

AW42AW45

SML1_SMBDATA

SML1_SMBCLK

B6A5

1D

1D

B4

1A

A3

1A

1K

1K

DOCK_TNY_SMB_CLK

DOCK_TNY_SMB_DAT

+3.3V _ALW_PCH

AR PD

C C

19

JTHB1

18

2.2K

+3.3V_ALW

KBC

1C1CB59

1E

1E

A56

A50

B53

PBAT_SMBCLK

PBAT_SMBDAT

USH_SMBCLK

USH_SMBDAT

2.2K

2.2K

2.2K

100 ohm

100 ohm

+3.3V_SUS

7

6

5

6

BATTERY

CONN

LYNX(CV2)

MEC 5085

B B

2.2K

+3.3V _ALW

B50

A47

B49

B48

CHARGER_SMBCLK

CHARGER_SMBDAT

UPD_GPU_SMBCLK

UPD_GPU_SMBDAT

1G

1G

1H

1H

A A

2.2K

2.2K

2.2K

+3.3V _ALW

DMN66D0LDW

DMN66D0LDW

DMN66D0LDW

DMN66D0LDW

9

8

Charger

100K

+3.3V _RUN_GFX

100K

AJ23

GPU

AH23

4.7K

+3.3V_VDD _PIC

4.7K

AR PD

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

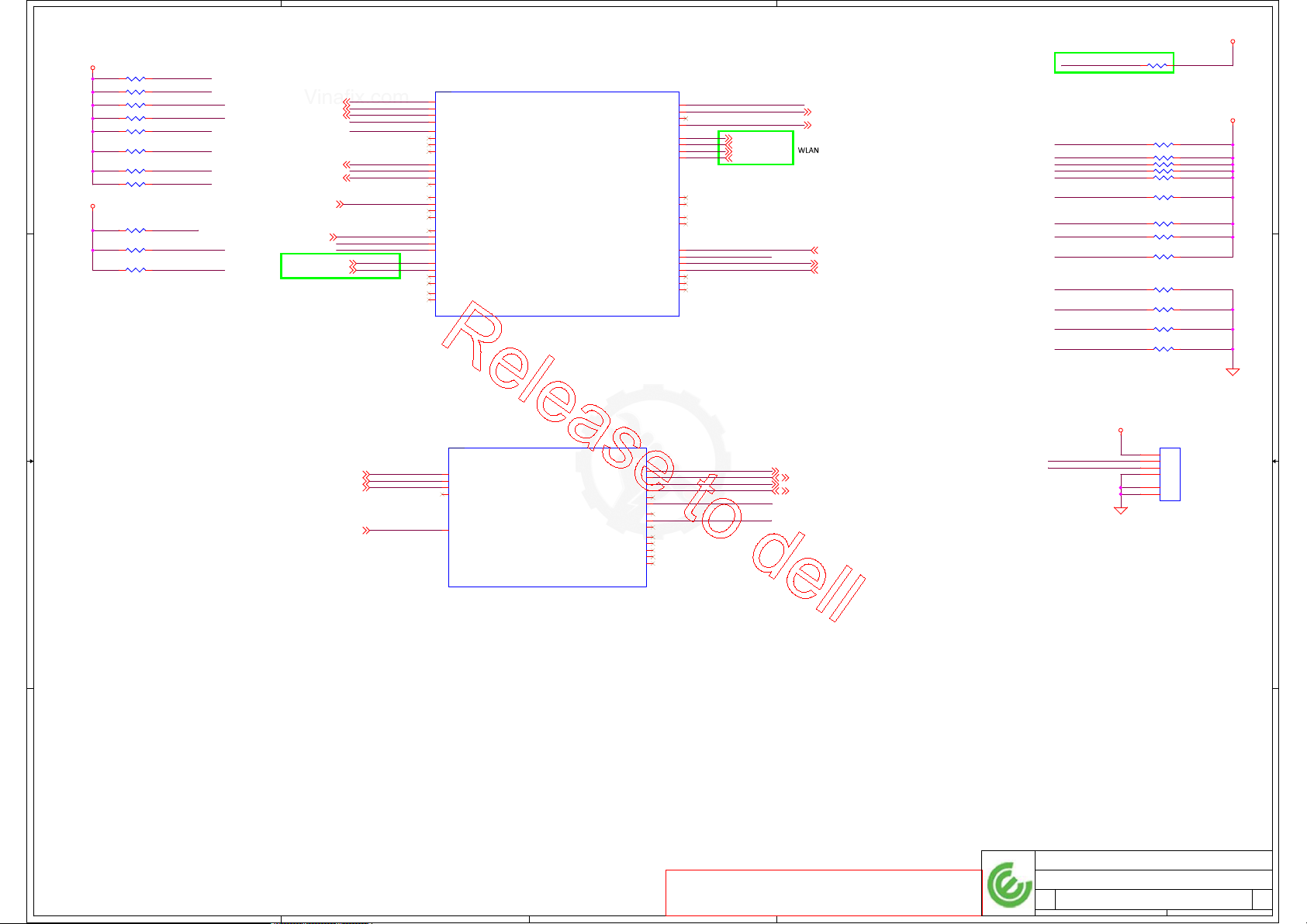

SMbus Block diagram

SMbus Block diagram

SMbus Block diagram

Document Number Re v

Document Number Rev

Document Number Rev

LA-C841P

LA-C841P

LA-C841P

1

5 74Tuesday, September 08, 2015

5 74Tuesday, September 08, 2015

5 74Tuesday, September 08, 2015

0.1

0.1

0.1

5

Title

Title

Title

Size

Size

Size

Date: Sheet of

Date: Sheet o f

4

3

2

Date: Sheet o f

Vinafix.com

5

4

3

2

1

PEG_CRX_GTX_P[0..15]

PEG_CRX_GTX_N[0..15]

PEG_CTX_C_GRX_P[0..15]

PEG_CTX_C_GRX_N[0..15]

D D

C C

B B

PEG_COMP

A A

5

PEG_CRX_GTX_P[0..15] <50>

PEG_CRX_GTX_N[0..15] <50>

PEG_CTX_C_GRX_P[0..15] <50>

PEG_CTX_C_GRX_N[0..15] <50>

+1.0VS_VCCIO

12

RC224.9_0402_1%

CPU1C

PEG_CRX_GTX_P15

PEG_CRX_GTX_N15

PEG_CRX_GTX_P14

PEG_CRX_GTX_N14

PEG_CRX_GTX_P13

PEG_CRX_GTX_N13

PEG_CRX_GTX_P12

PEG_CRX_GTX_N12

PEG_CRX_GTX_P11

PEG_CRX_GTX_N11

PEG_CRX_GTX_P10

PEG_CRX_GTX_N10

PEG_CRX_GTX_P9

PEG_CRX_GTX_N9

PEG_CRX_GTX_P8

PEG_CRX_GTX_N8

PEG_CRX_GTX_P7

PEG_CRX_GTX_N7

PEG_CRX_GTX_P6

PEG_CRX_GTX_N6

PEG_CRX_GTX_P5

PEG_CRX_GTX_N5

PEG_CRX_GTX_P4

PEG_CRX_GTX_N4

PEG_CRX_GTX_P3

PEG_CRX_GTX_N3

PEG_CRX_GTX_P2

PEG_CRX_GTX_N2

PEG_CRX_GTX_P1

PEG_CRX_GTX_N1

PEG_CRX_GTX_P0

PEG_CRX_GTX_N0

PEG_COMP

DMI_CRX_PTX_P0<17>

DMI_CRX_PTX_N0<17>

DMI_CRX_PTX_P1<17>

DMI_CRX_PTX_N1<17>

DMI_CRX_PTX_P2<17>

DMI_CRX_PTX_N2<17>

DMI_CRX_PTX_P3<17>

DMI_CRX_PTX_N3<17>

DMI_CRX_PTX_P0

DMI_CRX_PTX_N0

DMI_CRX_PTX_P1

DMI_CRX_PTX_P2

DMI_CRX_PTX_N2

DMI_CRX_PTX_P3 DMI_CTX_PRX_P3

DMI_CRX_PTX_N3 DMI_CTX_PRX_N3

E25

PEG_RXP[0]

D25

PEG_RXN[0]

E24

PEG_RXP[1]

F24

PEG_RXN[1]

E23

PEG_RXP[2]

D23

PEG_RXN[2]

E22

PEG_RXP[3]

F22

PEG_RXN[3]

E21

PEG_RXP[4]

D21

PEG_RXN[4]

E20

PEG_RXP[5]

F20

PEG_RXN[5]

E19

PEG_RXP[6]

D19

PEG_RXN[6]

E18

PEG_RXP[7]

F18

PEG_RXN[7]

D17

PEG_RXP[8]

E17

PEG_RXN[8]

F16

PEG_RXP[9]

E16

PEG_RXN[9]

D15

PEG_RXP[10]

E15

PEG_RXN[10]

F14

PEG_RXP[11]

E14

PEG_RXN[11]

D13

PEG_RXP[12]

E13

PEG_RXN[12]

F12

PEG_RXP[13]

E12

PEG_RXN[13]

D11

PEG_RXP[14]

E11

PEG_RXN[14]

F10

PEG_RXP[15]

E10

PEG_RXN[15]

G2

PEG_RCOMP

D8

DMI_RXP[0]

E8

DMI_RXN[0]

E6

DMI_RXP[1]

F6

DMI_RXN[1]

D5

DMI_RXP[2]

E5

DMI_RXN[2]

J8

DMI_RXP[3]

J9

DMI_RXN[3]

REV = 1

SKL-H_BGA1440

BGA1440

3 OF 14

PEG_TXP[0]

PEG_TXN[0]

PEG_TXP[1]

PEG_TXN[1]

PEG_TXP[2]

PEG_TXN[2]

PEG_TXP[3]

PEG_TXN[3]

PEG_TXP[4]

PEG_TXN[4]

PEG_TXP[5]

PEG_TXN[5]

PEG_TXP[6]

PEG_TXN[6]

PEG_TXP[7]

PEG_TXN[7]

PEG_TXP[8]

PEG_TXN[8]

PEG_TXP[9]

PEG_TXN[9]

PEG_TXP[10]

PEG_TXN[10]

PEG_TXP[11]

PEG_TXN[11]

PEG_TXP[12]

PEG_TXN[12]

PEG_TXP[13]

PEG_TXN[13]

PEG_TXP[14]

PEG_TXN[14]

PEG_TXP[15]

PEG_TXN[15]

DMI_TXP[0]

DMI_TXN[0]

DMI_TXP[1]

DMI_TXN[1]

DMI_TXP[2]

DMI_TXN[2]

DMI_TXP[3]

DMI_TXN[3]

PEG_CTX_GRX_P15

B25

PEG_CTX_GRX_N15

A25

PEG_CTX_GRX_P14

B24

PEG_CTX_GRX_N14

C24

PEG_CTX_GRX_P13

B23

PEG_CTX_GRX_N13

A23

PEG_CTX_GRX_P12 PEG_CTX_C_GRX_P12

B22

PEG_CTX_GRX_N12 PEG_CTX_C_GRX_N12

C22

PEG_CTX_GRX_P11

B21

PEG_CTX_GRX_N11

A21

PEG_CTX_GRX_P10 PEG_CTX_C_GRX_P10

B20

C20

PEG_CTX_GRX_P9

B19

PEG_CTX_GRX_N9

A19

PEG_CTX_GRX_P8

B18

PEG_CTX_GRX_N8

C18

PEG_CTX_GRX_P7

A17

PEG_CTX_GRX_N7

B17

PEG_CTX_GRX_P6 PEG_CTX_C_GRX_P6

C16

B16

PEG_CTX_GRX_P5

A15

PEG_CTX_GRX_N5

B15

PEG_CTX_GRX_P4

C14

PEG_CTX_GRX_N4

B14

PEG_CTX_GRX_P3

A13

PEG_CTX_GRX_N3

B13

PEG_CTX_GRX_P2

C12

PEG_CTX_GRX_N2

B12

PEG_CTX_GRX_P1

A11

PEG_CTX_GRX_N1

B11

PEG_CTX_GRX_P0

C10

PEG_CTX_GRX_N0

B10

B8

A8

C6

B6

B5

A5

D4

B4

?

DMI_CTX_PRX_P0

DMI_CTX_PRX_N0

DMI_CTX_PRX_P1

DMI_CTX_PRX_N1DMI_CRX_PTX_N1

DMI_CTX_PRX_P2

DMI_CTX_PRX_N2

Tropo@

CC67 0.22U_0402_10V6K

Tropo@

CC44 0.22U_0402_10V6K

Tropo@

CC68 0.22U_0402_10V6K

Tropo@

CC45 0.22U_0402_10V6K

Tropo@

CC51 0.22U_0402_10V6K

Tropo@

CC53 0.22U_0402_10V6K

Tropo@

CC52 0.22U_0402_10V6K

Tropo@

CC73 0.22U_0402_10V6K

Tropo@

CC69 0.22U_0402_10V6K

Tropo@

CC46 0.22U_0402_10V6K

Tropo@

CC54 0.22U_0402_10V6K

Tropo@

CC74 0.22U_0402_10V6K

Tropo@

CC55 0.22U_0402_10V6K

Tropo@

CC47 0.22U_0402_10V6K

Tropo@

CC70 0.22U_0402_10V6K

Tropo@

CC56 0.22U_0402_10V6K

DIS@

CC57 0.22U_0402_10V6K

DIS@

CC75 0.22U_0402_10V6K

DIS@

CC58 0.22U_0402_10V6K

DIS@

CC48 0.22U_0402_10V6K

DIS@

CC71 0.22U_0402_10V6K

DIS@

CC59 0.22U_0402_10V6K

DIS@

CC60 0.22U_0402_10V6K

DIS@

CC76 0.22U_0402_10V6K

DIS@

CC61 0.22U_0402_10V6K

DIS@

CC49 0.22U_0402_10V6K

DIS@

CC72 0.22U_0402_10V6K

DIS@

CC62 0.22U_0402_10V6K

DIS@

CC63 0.22U_0402_10V6K

DIS@

CC77 0.22U_0402_10V6K

DIS@

CC64 0.22U_0402_10V6K

DIS@

CC50 0.22U_0402_10V6K

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

DMI_CTX_PRX_P0 <17>

DMI_CTX_PRX_N0 <17>

DMI_CTX_PRX_P1 <17>

DMI_CTX_PRX_N1 <17>

DMI_CTX_PRX_P2 <17>

DMI_CTX_PRX_N2 <17>

DMI_CTX_PRX_P3 <17>

DMI_CTX_PRX_N3 <17>

PEG_CTX_C_GRX_P15

PEG_CTX_C_GRX_N15

PEG_CTX_C_GRX_P14

PEG_CTX_C_GRX_N14

PEG_CTX_C_GRX_P13

PEG_CTX_C_GRX_N13

PEG_CTX_C_GRX_P11

PEG_CTX_C_GRX_N11

PEG_CTX_C_GRX_N10PEG_CTX_GRX_N10

PEG_CTX_C_GRX_P9

PEG_CTX_C_GRX_N9

PEG_CTX_C_GRX_P8

PEG_CTX_C_GRX_N8

PEG_CTX_C_GRX_P7

PEG_CTX_C_GRX_N7

PEG_CTX_C_GRX_N6PEG_CTX_GRX_N6

PEG_CTX_C_GRX_P5

PEG_CTX_C_GRX_N5

PEG_CTX_C_GRX_P4

PEG_CTX_C_GRX_N4

PEG_CTX_C_GRX_P3

PEG_CTX_C_GRX_N3

PEG_CTX_C_GRX_P2

PEG_CTX_C_GRX_N2

PEG_CTX_C_GRX_P1

PEG_CTX_C_GRX_N1

PEG_CTX_C_GRX_P0

PEG_CTX_C_GRX_N0

?

SKYLAKE_HALO

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

4

3

2

Title

Size

Size

Size

Date : Sheet o f

Date : Sheet o f

Date : Sheet o f

Compal Electronics, Inc.

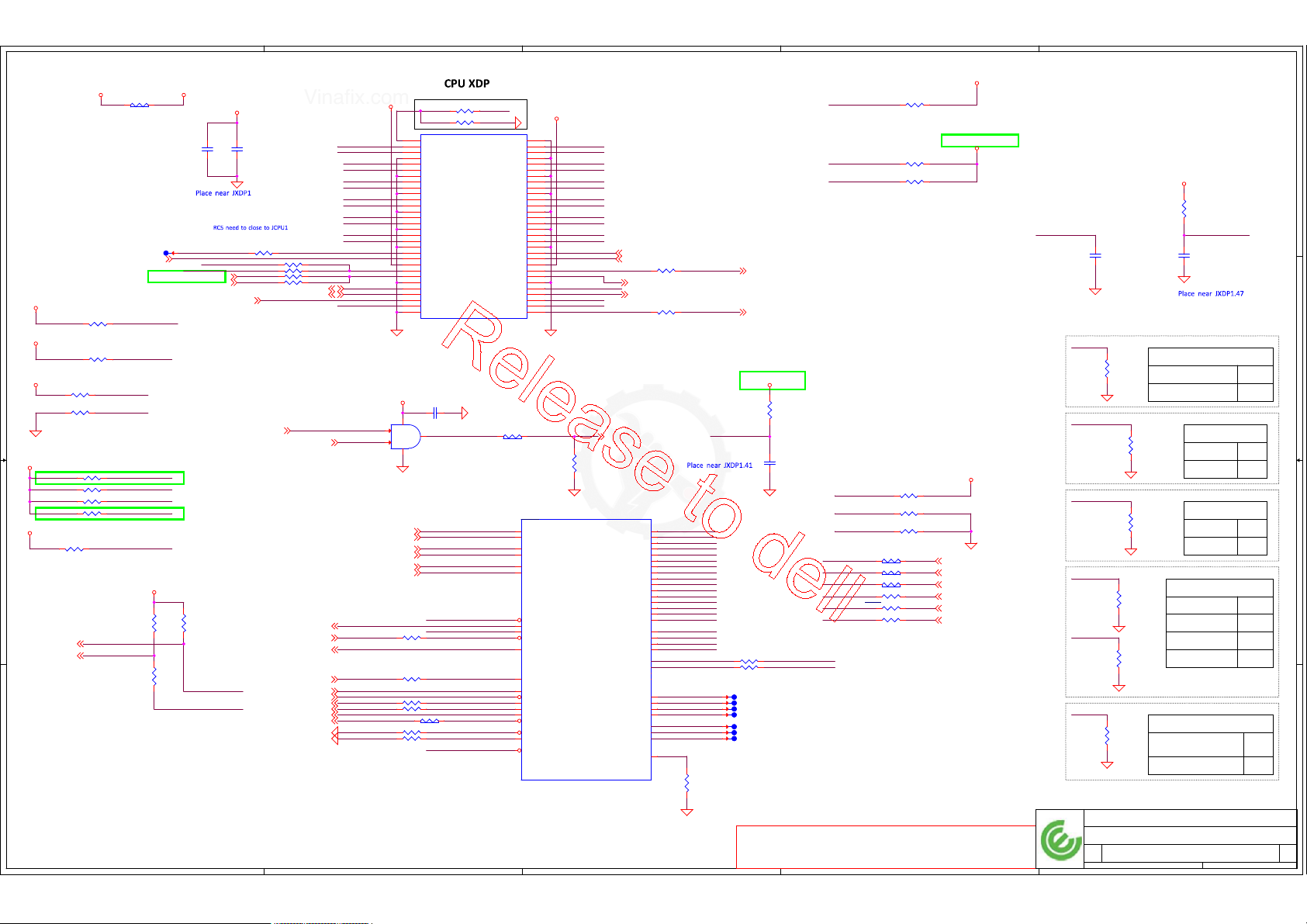

SKL-H (1/8)

SKL-H (1/8)

Document Number Re v

Document Number Re v

Document Number Re v

SKL-H (1/8)

LA-C841P

LA-C841P

LA-C841P

6 74Tuesday, September 08, 2015

6 74Tuesday, September 08, 2015

6 74Tuesday, September 08, 2015

1

0.1

0.1

0.1

Vinafix.com

5

4

3

2

1

12

RC13551_0402_5%

12

RC33551_0402_5%

12

RC30651_0402_5%

PCH_JTAG_TMS <20>

PCH_JTAG_TDI <20>

PCH_JTAG_TDO <20>

PCH_JTAGX <20>

PCH_XDP_PREQ# <22>

PCH_XDP_PRDY# <22>

+1.0V_PRIM_XDP

+3.3V_ALW_PCH

+1.0V_VCCSTG

XDP_DBRESET#

CFG0

CFG2

CFG4

CFG5

CFG6

CFG7

+3.3V_SPI

12

RC5

2.2K_0402_5%

0.1U_0402_25V6

CC35

12

XDP@

12

RC321

@

1K_0402_5%

12

RC181

1K_0402_5%

12

RC322

1K_0402_5%

12

Litho@

RC323

1K_0402_5%

12

RC324

@

1K_0402_5%

12

RC325

@

1K_0402_5%

SYS_PWROK_R

0.1U_0402_25V6

12

CC36@

Stall reset sequence after PCU

PLL lock until de-asserted

No Stall

Stall

1

0

PEG LANE REVERSAL

*

NORMAL

LANE

REVERSE D

1

0

eDP enable

Disable d

Enabled

PCI Express* Bifurcation

1x8, 2x4

Reserved

2x8

1x16

PEG Training

(default) PEG Train

immediately following

RESET# de-assertion

PEG Wait for BIOS for

trai ning

1

0

[6:5 ]

00

01

10

11

1

0

+1.0V_PRIM

RC216 0_0603_1%@

D D

T191

10/23 Intel review

+1.0V_PRIM_XDP

12

+1.0VS_VCCIO

C C

+1.0V_VCCST

1 2

RC329 150_0402_5%@

1 2

RC328 10K_0402_5%@

+1.0V_VCCST

+1.0V_VCCSTG

1 2

RC180 1K_0402_5%

B B

VR_SVID_DATA<63>

VR_SVID_ALERT#<63>

A A

RC13851_0402_5% @

12

RC132150_0402_5%

FIVR_EN

FIVR_EN

12

RC3261K_0402_5%

12

RC1661K_0402_5% @

12

RC1641K_0402_5%

12

RC17249.9_0402_1% @

VR_SVID_DATA

VR_SVID_ALERT#

1 2

@

PAD~D

SIO_PWRBTN#<20,36>

CPU_XDP_PREQ#

FIVR_EN_R

H_THERMTRIP#

PCH_JTAGX

VCCST_PWRGD

H_CATERR#

H_PROCHOT#

+1.0V_VCCST

12

12

+1.0V_PRIM_XDP

+1.0V_PRIM_XDP

0.1U_0402_25V6

0.1U_0402_25V6

@

@

12

12

CC37

CC33

PCH_RSMRST#_R H_VCCST_PWRGD_XDP

CFG0

PCH_SPI_D0<19>

RESET_OUT#<20,36>

1 2

RC124

XDP@ 1K_0402_5%

FIVR_EN

PCH_JTAG_TCK<20>

PCH_RSMRST#<36>

RC217 0_0402_5%@ 1 2

RC126 1K_0402_5%XDP@ 1 2

RC128 0_0402_5%XDP@ 1 2

1 2

RC129 0_0402_5%@

DDR_XDP_WAN_SMBDAT<14,15,20,45>

DDR_XDP_WAN_SMBCLK<14,15,20,45>

PCH_RSMRST#

ALW_PWRGD_3V_5V<58>

CPU_XDP_PREQ#

CPU_XDP_PRDY#

10/23 Intel review

10/23 Intel review

PCH_CPU_PCIBCLK_R_D<18>

PCH_CPU_PCIBCLK_R_D#<18>

56.2_0402_1%

100_0402_5%

12

RC155

220_0402_5%

RC157

RC156

VR_SVID_DATA

CPU_VIDALERT#

VR_SVID_CLK<63>

H_PROCHOT#<36,51,63,66,67>

DDR_VTT_CTRL<14>

VCCST_PWRGD<36>

H_PWRGD<20>

PLTRST_CPU#<16>

H_PM_SYNC_R<16>

H_PM_DOWN<16>

H_PECI<16,36>

H_THERMTRIP#< 14,15,16,36>

+1.0V_PRIM_XDP

CFG0

CFG1

CFG2

CFG3

XDP_OBS0_R

XDP_OBS1_R

CFG4

CFG5

CFG6

CFG7

SIO_PWRBTN#

FIVR_EN_R

SYS_PWROK_R

PCH_JTAG_TCK

CPU_XDP_TCLK

1

2

PCH_CPU_BCLK_R_D<18>

PCH_CPU_BCLK_R_D#<18>

CPU_24MHZ_R_D<18>

CPU_24MHZ_R_D#<18>

VR_SVID_CLK

H_PROCHOT#

RC158 499_0402_1%

DDR_VTT_CTRL

RC159 60.4_0402_1%

H_PWRGD

PLTRST_CPU#

H_PM_SYNC_R

RC167 30_0402_5%

H_PECI

RC168 20_0402_5%

RC319 0_0402_5%

RC171 0_0402_5%@

XDP_PRSNT_PIN1

JXDP1

1

GND0

3

OBSFN_A0

5

OBSFN_A1

7

GND2

OBSDATA_A09OBSDATA_C0

OBSDATA_A111OBSDATA_C1

13

GND4

OBSDATA_A215OBSDATA_C2

OBSDATA_A317OBSDATA_C3

19

GND6

21

OBSFN_B0

23

OBSFN_B1

25

GND8

OBSDATA_B027OBSDATA_D0

OBSDATA_B129OBSDATA_D1

31

GND10

OBSDATA_B233OBSDATA_D2

OBSDATA_B335OBSDATA_D3

37

GND12

PWRGOOD/HOOK039ITPCLK/HOOK4

41

HOOK1

VCC_OBS_AB43VCC_OBS_CD

45

HOOK2

47

HOOK3

49

GND14

51

SDA

53

SCL

55

TCK1

57

TCK0

59

GND16

+3.3V_ALW

CH17

1 2

5

0.1U_0402_25V6

P

B

PM_RSMRST#_AND

4

O

A

G

UC4

3

TC7SH08FU_SSOP5~D

PCH_CPU_BCLK_R_D

PCH_CPU_BCLK_R_D#

PCH_CPU_PCIBCLK_R_D

PCH_CPU_PCIBCLK_R_D#

CPU_24MHZ_R_D

CPU_24MHZ_R_D#

1 2

1 2

1 2

1 2

1 2

RC169 0_0402_5%@

1 2

1 2

XDP@

CFG3

1 2

RC121 1K_0402_5%

1 2

RC122 0_0402_5%@

ITPCLK#/HOOK5

RESET#/HOOK6

RC154 0_0402_5%@

CPU_VIDALERT#

VR_SVID_DATA

H_PROCHOT#_R

VCCST_PWRGD_CPUVCCST_PWRGD

H_PM_SYNC

H_PM_DOWN_RH_PM_DOWN

H_THERMTRIP#_RH_THERMTRIP#

H_SKTOCC# CPU_XDP_PREQ#

SKL_CNL#

H_CATERR#

GND1

OBSFN_C0

OBSFN_C1

GND3

GND5

GND7

OBSFN_D0

OBSFN_D1

GND9

GND11

GND13

DBR#/HOOK7

GND15

TRST#

GND17

CONN@SAMTE_BSH-030-01-L-D-A

1 2

B31

A32

D35

C36

E31

D31

BH31

BH32

BH29

BR30

BT13

H13

BT31

BP35

BM34

BP31

BT34

J31

BR33

BN1

BM30

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

TD0

54

56

TDI

58

TMS

60

CPU1E

BCLKP

BCLKN

PCI_BCLKP

PCI_BCLKN

CLK24P

CLK24N

VIDALERT#

VIDSCK

VIDSOUT

PROCHOT#

DDR_VTT_CNTL

VCCST_PWRGD

PROCPWRGD

RESET#

PM_SYNC

PM_DOWN

PECI

THERMTRIP#

SKTOCC#

PROC_SELECT#

CATERR#

SKL-H_BGA1440

+1.0V_PRIM_XDP

PCH_XDP_CLK_DP

PCH_XDP_CLK_DN

CPU_XDP_HOOK6

XDP_DBRESET#

CPU_XDP_TDO

CPU_XDP_TRST#

CPU_XDP_TDI

CPU_XDP_TMS

CPU_XDP_PRS

PCH_RSMRST#_R

SKYLAKE_HALO

BGA1440

CFG17

CFG16

CFG8

CFG9

CFG10

CFG11

CFG19

CFG18

CFG12

CFG13

CFG14

CFG15

12

PCH_RSMRST#_R <20>

RC318

47K_0402_5%

PROC_TRST#

PROC_PREQ#

PROC_PRDY#

CFG_RCOMP

PCH_XDP_CLK_DP <18>

PCH_XDP_CLK_DN <18>

1 2

RC144 0_0402_5%XDP@

XDP_DBRESET# <17>

CPU_XDP_TRST# <22>

1 2

RC127 1K_0402_5%XDP@

BN25

CFG[0]

BN27

CFG[1]

BN26

CFG[2]

BN28

CFG[3]

BR20

CFG[4]

BM20

CFG[5]

BT20

CFG[6]

BP20

CFG[7]

BR23

CFG[8]

BR22

CFG[9]

BT23

CFG[10]

BT22

CFG[11]

BM19

CFG[12]

BR19

CFG[13]

BP19

CFG[14]

BT19

CFG[15]

BN23

CFG[17]

BP23

CFG[16]

BP22

CFG[19]

BN22

CFG[18]

BR27

BPM#[0]

BT27

BPM#[1]

BM31

BPM#[2]

BT30

BPM#[3]

BT28

PROC_TDO

BL32

PROC_TDI

BP28

PROC_TMS

BR28

PROC_TCK

BP30

BL30

BP27

BT25

ITP_PMODE_CPU

PCH_SPI_D2_XDP

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG17

CFG16

CFG19

CFG18

XDP_OBS0

XDP_OBS1

CPU_XDP_TDO

CPU_XDP_TDI

CPU_XDP_TMS

CPU_XDP_TCLK

CPU_XDP_TRST#

CPU_XDP_PRDY#

12

RC222

49.9_0402_1%

SIO_PWRBTN#

1 2

1 2

RC312 0_0402_5%@

RC313 0_0402_5%@

PAD~D

PAD~D

PAD~D

PAD~D

PAD~D

PAD~D

PAD~D

ITP_PMODE_CPU <20>

PCH_SPI_D2_XDP <19>

+3.3V_ALW

1.5K_0402_5%

XDP@

12

RC241

0.1U_0402_25V6

XDP@

12

CC269

XDP_OBS0_R

XDP_OBS1_R

@

T184

@

T185

@

T180

@

T181

@

T179

@

T190

@

T189

CPU_XDP_HOOK6

10/23 I ntel review

XDP_DBRESET#

PCH_SPI_D0

EDS0.7

CPU_XDP_TDO

CPU_XDP_TRST#

CPU_XDP_TCLK

CPU_XDP_TMS

CPU_XDP_TDI

CPU_XDP_TDO

CPU_XDP_TCLK

CPU_XDP_PREQ#

CPU_XDP_PRDY#

RC307 0_0402_5%@

RC308 0_0402_5%@

RC309 0_0402_5%@

RC143 0_0402_5%@

RC315 0_0402_5%@

RC314 0_0402_5%@

RC6 2.2K_0402_5%XDP@

RC316 1.5K_0402_5%XDP@

RC133 1.5K_0402_5%XDP@

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size

Size

Size

Date: Sheet o f

Date: Sheet o f

Date: Sheet o f

Compal Electronics, Inc.

SKL-H (2/8)

SKL-H (2/8)

SKL-H (2/8)

Document Number Rev

Document Number Rev

Document Number Rev

LA-C841P

LA-C841P

LA-C841P

1

7 74Tuesday, September 08, 2015

7 74Tuesday, September 08, 2015

7 74Tuesday, September 08, 2015

0.1

0.1

0.1

Vinafix.com

5

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

D D

C C

B B

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_A_CB0

DDR_A_CB1

DDR_A_CB2

DDR_A_CB3

DDR_A_CB4

DDR_A_CB5

DDR_A_CB6

DDR_A_CB7

CPU1A

BR6

DDR0_DQ[0]

BT6

DDR0_DQ[1]

BP3

DDR0_DQ[2]

BR3

DDR0_DQ[3]

BN5

DDR0_DQ[4]

BP6

DDR0_DQ[5]

BP2

DDR0_DQ[6]

BN3

DDR0_DQ[7]

BL4

DDR0_DQ[8]

BL5

DDR0_DQ[9]

BL2

DDR0_DQ[10]

BM1

DDR0_DQ[11]

BK4

DDR0_DQ[12]

BK5

DDR0_DQ[13]

BK1

DDR0_DQ[14]

BK2

DDR0_DQ[15]

BG4

DDR0_DQ[16]/DDR0_DQ[32]

BG5

DDR0_DQ[17]/DDR0_DQ[33]

BF4

DDR0_DQ[18]/DDR0_DQ[34]

BF5

DDR0_DQ[19]/DDR0_DQ[35]

BG2

DDR0_DQ[20]/DDR0_DQ[36]

BG1

DDR0_DQ[21]/DDR0_DQ[37]

BF1

DDR0_DQ[22]/DDR0_DQ[38]

BF2

DDR0_DQ[23]/DDR0_DQ[39]

BD2

DDR0_DQ[24]/DDR0_DQ[40]

BD1

DDR0_DQ[25]/DDR0_DQ[41]

BC4

DDR0_DQ[26]/DDR0_DQ[42]

BC5

DDR0_DQ[27]/DDR0_DQ[43]

BD5

DDR0_DQ[28]/DDR0_DQ[44]

BD4

DDR0_DQ[29]/DDR0_DQ[45]

BC1

DDR0_DQ[30]/DDR0_DQ[46]

BC2

DDR0_DQ[31]/DDR0_DQ[47]

AB1

DDR0_DQ[32]/DDR1_DQ[0]

AB2

DDR0_DQ[33]/DDR1_DQ[1]

AA4

DDR0_DQ[34]/DDR1_DQ[2]

AA5

DDR0_DQ[35]/DDR1_DQ[3]

AB5

DDR0_DQ[36]/DDR1_DQ[4]

AB4

DDR0_DQ[37]/DDR1_DQ[5]

AA2

DDR0_DQ[38]/DDR1_DQ[6]

AA1

DDR0_DQ[39]/DDR1_DQ[7]

V5

DDR0_DQ[40]/DDR1_DQ[8]

V2

DDR0_DQ[41]/DDR1_DQ[9]

U1

DDR0_DQ[42]/DDR1_DQ[10]

U2

DDR0_DQ[43]/DDR1_DQ[11]

V1

DDR0_DQ[44]/DDR1_DQ[12]

V4

DDR0_DQ[45]/DDR1_DQ[13]

U5

DDR0_DQ[46]/DDR1_DQ[14]

U4

DDR0_DQ[47]/DDR1_DQ[15]

R2

DDR0_DQ[48]/DDR1_DQ[32]

P5

DDR0_DQ[49]/DDR1_DQ[33]

R4

DDR0_DQ[50]/DDR1_DQ[34]

P4

DDR0_DQ[51]/DDR1_DQ[35]

R5

DDR0_DQ[52]/DDR1_DQ[36]

P2

DDR0_DQ[53]/DDR1_DQ[37]

R1

DDR0_DQ[54]/DDR1_DQ[38]

P1

DDR0_DQ[55]/DDR1_DQ[39]

M4

DDR0_DQ[56]/DDR1_DQ[40]

M1

DDR0_DQ[57]/DDR1_DQ[41]

L4

DDR0_DQ[58]/DDR1_DQ[42]

L2

DDR0_DQ[59]/DDR1_DQ[43]

M5

DDR0_DQ[60]/DDR1_DQ[44]

M2

DDR0_DQ[61]/DDR1_DQ[45]

L5

DDR0_DQ[62]/DDR1_DQ[46]

L1

DDR0_DQ[63]/DDR1_DQ[47]

BA2

DDR0_ECC[0]

BA1

DDR0_ECC[1]

AY4

DDR0_ECC[2]

AY5

DDR0_ECC[3]

BA5

DDR0_ECC[4]

BA4

DDR0_ECC[5]

AY1

DDR0_ECC[6]

AY2

DDR0_ECC[7]

DDR CHANNEL A

SKL-H_BGA1440

SKYLAKE_HALO

BGA1440

4

?

DDR0_CKP[0]

DDR0_CKN[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CLKP[2]

DDR0_CLKN[2]

DDR0_CLKP[3]

DDR0_CLKN[3]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_CS#[2]

DDR0_CS#[3]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_ODT[2]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

1 OF 14

DDR0_ODT[3]

DDR0_MA[3]

DDR0_MA[4]

DDR0_PAR

DDR0_ALERT#

DDR0_DQSN[0]

DDR0_DQSN[1]

DDR0_DQSP[0]

DDR0_DQSP[1]

DDR0_DQSP[8]

DDR0_DQSN[8]

?REV = 1

3

DDR_A_D16

DDR_A_CLK0 DDR_B_CLK#0

AG1

DDR_A_CLK#0

AG2

DDR_A_CLK#1 DDR_B_CLK1

AK1

DDR_A_CLK1

AK2

AL3

AK3

AL2

AL1

DDR_A_CKE0

AT1

DDR_A_CKE1

AT2

AT3

AT5

DDR_A_CS#0

AD5

DDR_A_CS#1

AE2

AD2

AE5

DDR_A_ODT0

AD3

DDR_A_ODT1

AE4

AE1

AD4

DDR_A_BA0

AH5

DDR_A_BA1

AH1

DDR_A_BG0

AU1

DDR_A_MA16

AH4

DDR_A_MA14

AG4

DDR_A_MA15

AD1

DDR_A_MA0

AH3

DDR_A_MA1

AP4

DDR_A_MA2

AN4

DDR_A_MA3

AP5

DDR_A_MA4

AP2

DDR_A_MA5

AP1

DDR_A_MA6

AP3

DDR_A_MA7

AN1

DDR_A_MA8

AN3

DDR_A_MA9

AT4

DDR_A_MA10

AH2

DDR_A_MA11

AN2

DDR_A_MA12

AU4

DDR_A_MA13

AE3

DDR_A_BG1

AU2

DDR_A_ACT#

AU3

DDR_A_PARITY

AG3

DDR_A_ALERT#

AU5

DDR_A_DQS#0

BR5

DDR_A_DQS#1

BL3

DDR_A_DQS#4

BG3

DDR_A_DQS#5

BD3

DDR_B_DQS0

AB3

DDR_B_DQS1

V3

DDR_B_DQS4

R3

DDR_B_DQS5

M3

DDR_A_DQS0

BP5

DDR_A_DQS1

BK3

DDR_A_DQS4

BF3

DDR_A_DQS5

BC3

DDR_B_DQS#0

AA3

DDR_B_DQS#1

U3

DDR_B_DQS#4

P3

DDR_B_DQS#5

L3

DDR_A_DQS8

AY3

DDR_A_DQS#8

BA3

DDR_A_CLK0 <14>

DDR_A_CLK#0 <14>

DDR_A_CLK#1 <14>

DDR_A_CLK1 <14>

DDR_A_CKE0 <14>

DDR_A_CKE1 <14>

DDR_A_CS#0 <14>

DDR_A_CS#1 <14>

DDR_A_ODT0 <14>

DDR_A_ODT1 <14>

DDR_A_BA0 <14>

DDR_A_BA1 <14>

DDR_A_BG0 <14>

DDR_A_BG1 <14>

DDR_A_ACT# <14>

DDR_A_PARITY <14>

DDR_A_ALERT# <14>

1 2

RD18 121_0402_1%

RD21 75_0402_1%

1 2

RD22 100_0402_1%

1 2

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

DDR_B_CB0

DDR_B_CB1

DDR_B_CB2

DDR_B_CB3

DDR_B_CB4

DDR_B_CB5

DDR_B_CB6

DDR_B_CB7

DDR_RCOMP0

DDR_RCOMP1

DDR_RCOMP2

CPU1B

BT11

DDR1_DQ[0]/DDR0_DQ[16]

BR11

DDR1_DQ[1]/DDR0_DQ[17]

BT8

DDR1_DQ[2]/DDR0_DQ[18]

BR8

DDR1_DQ[3]/DDR0_DQ[19]

BP11

DDR1_DQ[4]/DDR0_DQ[20]

BN11

DDR1_DQ[5]/DDR0_DQ[21]

BP8

DDR1_DQ[6]/DDR0_DQ[22]

BN8

DDR1_DQ[7]/DDR0_DQ[23]

BL12

DDR1_DQ[8]/DDR0_DQ[24]

BL11

DDR1_DQ[9]/DDR0_DQ[25]

BL8

DDR1_DQ[10]/DDR0_DQ[26]

BJ8

DDR1_DQ[11]/DDR0_DQ[27]

BJ11

DDR1_DQ[12]/DDR0_DQ[28]

BJ10

DDR1_DQ[13]/DDR0_DQ[29]

BL7

DDR1_DQ[14]/DDR0_DQ[30]

BJ7

DDR1_DQ[15]/DDR0_DQ[31]

BG11

DDR1_DQ[16]/DDR0_DQ[48]

BG10

DDR1_DQ[17]/DDR0_DQ[49]

BG8

DDR1_DQ[18]/DDR0_DQ[50]

BF8

DDR1_DQ[19]/DDR0_DQ[51]

BF11

DDR1_DQ[20]/DDR0_DQ[52]

BF10

DDR1_DQ[21]/DDR0_DQ[53]

BG7

DDR1_DQ[22]/DDR0_DQ[54]

BF7

DDR1_DQ[23]/DDR0_DQ[55]

BB11

DDR1_DQ[24]/DDR0_DQ[56]

BC11

DDR1_DQ[25]/DDR0_DQ[57]

BB8

DDR1_DQ[26]/DDR0_DQ[58]

BC8

DDR1_DQ[27]/DDR0_DQ[59]

BC10

DDR1_DQ[28]/DDR0_DQ[60]

BB10

DDR1_DQ[29]/DDR0_DQ[61]

BC7

DDR1_DQ[30]/DDR0_DQ[62]

BB7

DDR1_DQ[31]/DDR0_DQ[63]

AA11

DDR1_DQ[32]/DDR1_DQ[16]

AA10

DDR1_DQ[33]/DDR1_DQ[17]

AC11

DDR1_DQ[34]/DDR1_DQ[18]

AC10

DDR1_DQ[35]/DDR1_DQ[19]

AA7

DDR1_DQ[36]/DDR1_DQ[20]

AA8

DDR1_DQ[37]/DDR1_DQ[21]

AC8

DDR1_DQ[38]/DDR1_DQ[22]

AC7

DDR1_DQ[39]/DDR1_DQ[23]

W8

DDR1_DQ[40]/DDR1_DQ[24]

W7

DDR1_DQ[41]/DDR1_DQ[25]

V10

DDR1_DQ[42]/DDR1_DQ[26]

V11

DDR1_DQ[43]/DDR1_DQ[27]

W11

DDR1_DQ[44]/DDR1_DQ[28]

W10

DDR1_DQ[45]/DDR1_DQ[29]

V7

DDR1_DQ[46]/DDR1_DQ[30]

V8

DDR1_DQ[47]/DDR1_DQ[31]

R11

DDR1_DQ[48]

P11

DDR1_DQ[49]

P7

DDR1_DQ[50]

R8

DDR1_DQ[51]

R10

DDR1_DQ[52]

P10

DDR1_DQ[53]

R7

DDR1_DQ[54]

P8

DDR1_DQ[55]

L11

DDR1_DQ[56]

M11

DDR1_DQ[57]

L7

DDR1_DQ[58]

M8

DDR1_DQ[59]

L10

DDR1_DQ[60]

M10

DDR1_DQ[61]

M7

DDR1_DQ[62]

L8

DDR1_DQ[63]

AW11

DDR1_ECC[0]

AY11

DDR1_ECC[1]

AY8

DDR1_ECC[2]

AW8

DDR1_ECC[3]

AY10

DDR1_ECC[4]

AW10

DDR1_ECC[5]

AY7

DDR1_ECC[6]

AW7

DDR1_ECC[7]

G1

DDR_RCOMP[0]

H1

DDR_RCOMP[1]

J2

DDR_RCOMP[2]

SKL-H_BGA1440

DDR CHANNEL B

REV = 1

2

?

SKYLAKE_HALO

BGA1440

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSP[5]/DDR1_DQSP[3]

2 OF 14

DDR1_CKP[0]

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[1]

DDR1_CLKP[2]

DDR1_CLKN[2]

DDR1_CLKP[3]

DDR1_CLKN[3]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_CS#[2]

DDR1_CS#[3]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_ODT[2]

DDR1_ODT[3]

DDR1_MA[3]

DDR1_MA[4]

DDR1_PAR

DDR1_ALERT#

DDR1_DQSN[6]

DDR1_DQSN[7]

DDR1_DQSP[6]

DDR1_DQSP[7]

DDR1_DQSP[8]

DDR1_DQSN[8]

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

?

AM9

AN9

AM8

AM7

AM11

AM10

AJ10

AJ11

AT8

AT10

AT7

AT11

AF11

AE7

AF10

AE10

AF7

AE8

AE9

AE11

AH10

AH11

AF8

AH8

AH9

AR9

AJ9

AK6

AK5

AL5

AL6

AM6

AN7

AN10

AN8

AR11

AH7

AN11

AR10

AF9

AR7

AT9

AJ7

AR8

BP9

BL9

BG9

BC9

AC9

W9

R9

M9

BR9

BJ9

BF9

BB9

AA9

V9

P9

L9

AW9

AY9

BN13

BP13

BR13

DDR_B_CLK0

DDR_B_CLK#1

DDR_B_CKE0

DDR_B_CKE1

DDR_B_CS#0

DDR_B_CS#1

DDR_B_ODT0

DDR_B_ODT1

DDR_B_MA16

DDR_B_MA14

DDR_B_MA15

DDR_B_BA0

DDR_B_BA1

DDR_B_BG0

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_BG1

DDR_B_ACT#

DDR_B_PARITY

DDR_B_ALERT#

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#6

DDR_A_DQS#7

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#6

DDR_B_DQS#7

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS6

DDR_A_DQS7

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS6

DDR_B_DQS7

DDR_B_DQS8

DDR_B_DQS#8

1

DDR_B_CLK0 <15>

DDR_B_CLK#0 <15>

DDR_B_CLK#1 <15>

DDR_B_CLK1 <15>

DDR_B_CKE0 <15>

DDR_B_CKE1 <15>

DDR_B_CS#0 <15>

DDR_B_CS#1 <15>

DDR_B_ODT0 <15>

DDR_B_ODT1 <15>

DDR_B_BA0 <15>

DDR_B_BA1 <15>

DDR_B_BG0 <15>

DDR_B_BG1 <15>

DDR_B_ACT# <15>

DDR_B_PARITY <15>

DDR_B_ALERT# <15>

+DDR_VREF_CA

@

T199

PAD~D

+DDR_VREF_B_DQ

DDR_A_MA[0..16] <14>

DDR_B_MA[0..16] <15>

DDR_A_D[0..63]<14>

DDR_B_D[0..63]<15>

DDR_A_CB[0..7]<14>

A A

DDR_B_CB[0..7]<15>

DDR_A_DQS[0..8] <14>

DDR_B_DQS[0..8] <15>

DDR_A_DQS#[0..8] <14>

DDR_B_DQS#[0..8] <15>

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size

Size

Size

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

SKL-H (3/8)

SKL-H (3/8)

Document Number Re v

Document Number Re v

Document Number Re v

SKL-H (3/8)

LA-C841P

LA-C841P

LA-C841P

1

8 74Tuesday, September 08, 2015

8 74Tuesday, September 08, 2015

8 74Tuesday, September 08, 2015

0.1

0.1

0.1

Vinafix.com

5

CPU_DP1_P0<26>

CPU_DP1_N0<26>

CPU_DP1_P1<26>

DOCK, AR, HDMI

D D

DOCK, AR, WIGIG

C C

CPU_DP1_P2<26>

CPU_DP1_N2<26>

CPU_DP1_P3<26>

CPU_DP1_N3<26>

CPU_DP1_AUXP<26>

CPU_DP1_AUXN<26>

CPU_DP2_P0<27>

CPU_DP2_N0<27>

CPU_DP2_P1<27>

CPU_DP2_N1<27>

CPU_DP2_P2<27>

CPU_DP2_N2<27>

CPU_DP2_P3<27>

CPU_DP2_N3<27>

CPU_DP2_AUXP<27>

CPU_DP2_AUXN<27>

CPU_DP3_P0<28>

CPU_DP3_N0<28>

CPU_DP3_P1<28>

CPU_DP3_N1<28>

VGA

CPU_DP3_AUXP<28>

CPU_DP3_AUXN<28>

4

CPU_DP1_P0

CPU_DP1_N0

CPU_DP1_P1

CPU_DP1_P2

CPU_DP1_N2

CPU_DP1_P3

CPU_DP1_N3

CPU_DP1_AUXP

CPU_DP1_AUXN

CPU_DP2_P0

CPU_DP2_N0

CPU_DP2_P1

CPU_DP2_N1

CPU_DP2_P2

CPU_DP2_N2

CPU_DP2_P3

CPU_DP2_N3

CPU_DP2_AUXP

CPU_DP2_AUXN

CPU_DP3_P0

CPU_DP3_N0

CPU_DP3_P1

CPU_DP3_N1

CPU_DP3_AUXP

CPU_DP3_AUXN

CPU1D

K36

DDI1_TXP[0]

K37

DDI1_TXN[0]

J35

DDI1_TXP[1]

J34

DDI1_TXN[1]

H37

DDI1_TXP[2]

H36

DDI1_TXN[2]

J37

DDI1_TXP[3]

J38

DDI1_TXN[3]

D27

DDI1_AUXP

E27

DDI1_AUXN

H34

DDI2_TXP[0]

H33

DDI2_TXN[0]

F37

DDI2_TXP[1]

G38

DDI2_TXN[1]

F34

DDI2_TXP[2]

F35

DDI2_TXN[2]

E37

DDI2_TXP[3]

E36

DDI2_TXN[3]

F26

DDI2_AUXP

E26

DDI2_AUXN

C34

DDI3_TXP[0]

D34

DDI3_TXN[0]

B36

DDI3_TXP[1]

B34

DDI3_TXN[1]

F33

DDI3_TXP[2]

E33

DDI3_TXN[2]

C33

DDI3_TXP[3]

B33

DDI3_TXN[3]

A27

DDI3_AUXP

B27

DDI3_AUXN

SKL-H_BGA1440

3

SKYLAKE_HALO

BGA1440

4 OF 14

REV = 1

?

EDP_TXP[0]

EDP_TXN[0]

EDP_TXP[1]

EDP_TXN[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXP

EDP_AUXN

EDP_DISP_UTIL

EDP_RCOMP

PROC_AUDIO_CLK

PROC_AUDIO_SDI

PROC_AUDIO_SDO

2

EDP_TXP0

D29

EDP_TXN0

E29

EDP_TXP1

F28

EDP_TXN1CPU_DP1_N1

E28

B29

A29

B28

C28

EDP_AUXP

C26

EDP_AUXN

B26

A33

EDP_COMP

D37

G27

G25

G29

?

AUD_AZACPU_SDI AUD_AZACPU_SDI_R

@

PAD~D

AUD_AZACPU_SCLK

AUD_AZACPU_SDO

AUD_AZACPU_SDI

T194

1 2

RC66 20_0402_5%

EDP_TXP0 <30>

EDP_TXN0 <30>

EDP_TXP1 <30>

EDP_TXN1 <30>CPU_DP1_N1<26>

EDP_AUXP <30>

EDP_AUXN <30>

EDP_COMP

AUD_AZACPU_SCLK <20>

AUD_AZACPU_SDO <20>

1

+1.0VS_VCCIO

12

RC124.9_0402_1%

AUD_AZACPU_SDI_R <20>

B B

A A

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

Date : Sheet o f

Date : Sheet o f

Date : Sheet o f

2

Compal Electronics, Inc.

SKL-H (4/8)

SKL-H (4/8)

SKL-H (4/8)

LA-C841P

LA-C841P

LA-C841P

9 74Tuesday, September 08, 2015

9 74Tuesday, September 08, 2015

9 74Tuesday, September 08, 2015

1

0.1

0.1

0.1

Vinafix.com

5

D D

4

3

2

1

+VCC_EDRAM

3.3A

+VCC_EDRAM_ED2

C C

+VCC_EOPIO

+VCC_EOPIO_ED2

B B

3.2A

BJ17

BJ19

BJ20

BK17

BK19

BK20

BL16

BL17

BL18

BL19

BL20

BL21

BM17

BN17

BJ23

BJ26

BJ27

BK23

BK26

BK27

BL23

BL24

BL25

BL26

BL27

BL28

BM24

BL15

BM16

BL22

BM22

BP15

BR15

BT15

BP16

BR16

BT16

BN15

BM15

BP17

BN16

BM14

BL14

BJ35

BJ36

AT13

AW13

AU13

AY13

BT29

BR25

BP25

CPU1J

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

VCCOPC_SENSE

VSSOPC_SENSE

RSVD

RSVD

VCCEOPIO

VCCEOPIO

VCCEOPIO

RSVD

RSVD

RSVD

VCCEOPIO_SENSE

VSSEOPIO_SENSE

RSVD

RSVD

VCC_OPC_1P8

VCC_OPC_1P8

RSVD

RSVD

ZVM#

MSM#

ZVM2#

MSM2#

OPC_RCOMP

OPCE_RCOMP

OPCE_RCOMP2

SKL-H_BGA1440

SKYLAKE_HALO

BGA1440

CPU1K

T1PAD~D @

T2PAD~D @

T3PAD~D @

T4PAD~D @

T5PAD~D @

T6PAD~D @

T7PAD~D @

T9PAD~D @

T10PAD~D @

T11PAD~D @

T8PAD~D @

T14PAD~D @

T13PAD~D @

T15PAD~D @

T12PAD~D @

PCH_2_CPU_TRIGGER<22>

CPU_2_PCH_TRIGGER<22>

PCH_2_CPU_TRIGGER

CPU_2_PCH_TRIGGER_R

TP_SKL_F30

T16PAD~D @

TP_SKL_E30

T17PAD~D @

T18PAD~D @

T19PAD~D @

T21PAD~D @

T20PAD~D @

T23PAD~D @ T47 PAD~D@

T24PAD~D @

T22PAD~D @

TP_SKL_F30

TP_SKL_E30

D1

RSVD_TP

E1

RSVD_TP

E3

RSVD_TP

E2

RSVD_TP

BR1

RSVD_TP

BT2

RSVD_TP

BN35

RSVD

J24

RSVD

H24

RSVD

BN33

RSVD

BL34

RSVD

N29

RSVD

R14

RSVD

AE29

RSVD

AA14

RSVD

A36

RSVD

A37

RSVD

H23

PROC_TRIGIN

J23

PROC_TRIGOUT

F30

RSVD

E30

RSVD

B30

RSVD

C30

RSVD

G3

RSVD

J3

RSVD

BR35

RSVD

BR31

RSVD

BH30

RSVD

SKL-H_BGA1440

1 2

RC177 30_0402_5%

1 2

RC178 0_0402_5%@

1 2

RC179 0_0402_5%@

CPU_2_PCH_TRIGGER_RCPU_2_PCH_TRIGGER

SKYLAKE_HALO

BGA1440

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

NCTF

NCTF

NCTF

NCTF

NCTF

NCTF

BM33

BL33

BJ14

BJ13

BK28

BJ28

BJ18

VSS

BJ16

BK16

BK24

BJ24

BK21

BJ21

BT17

BR17

BK18

VSS

BJ34

BJ33

G13

AJ8

BL31

B2

B38

BP1

BR2

C1

C38

T26 PAD~D@

T25 PAD~D@

T28 PAD~D@

T27 PAD~D@

T29 PAD~D@

T30 PAD~D@

T31 PAD~D@

T32 PAD~D@

T34 PAD~D@

T33 PAD~D@

T36 PAD~D@

T35 PAD~D@

T37 PAD~D@

T38 PAD~D@

T39 PAD~D@

T40 PAD~D@

T42 PAD~D@

T41 PAD~D@

T44 PAD~D@

T43 PAD~D@

T45 PAD~D@

T46 PAD~D@

T48 PAD~D@

T49 PAD~D@

A A

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size

Size

Size

Date : Sheet o f

Date : Sheet o f

Date : Sheet o f

Compal Electronics, Inc.

SKL-H (5/8)

SKL-H (5/8)

Document Number Re v

Document Number Re v

Document Number Re v

SKL-H (5/8)

LA-C841P

LA-C841P

LA-C841P

1

10 74Tuesday, September 08, 2015

10 74Tuesday, September 08, 2015

10 74Tuesday, September 08, 2015

0.1

0.1

0.1

Vinafix.com

5

4

3

2

1

+VCC_GT +VCC_SA

D D

C C

BG34

BG35

BG36

BH33

BH34

BH35

BH36

BH37

BH38

BJ37

BJ38

BL36

BL37

BM36

BM37

BN36

BN37

BN38

BP37

BP38

BR37

BT37

BE38

BF13

BF14

BF29

BF30

BF31

BF32

BF35

BF36

BF37

BF38

BG29

BG30

BG31

BG32

BG33

BC36

BC37

BC38

BD13

BD14

BD29

BD30

BD31

BD32

BD33

BD34

BD35

BD36

BE31

BE32

BE37

SKYLAKE_HALO

CPU1H

BGA1440

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

SKL-H_BGA1440

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

AV29

AV30

AV31

AV32

AV33

AV34

AV35

AV36

AW14

AW31

AW32

AW33

AW34

AW35

AW36

AW37

AW38

AY29

AY30

AY31

AY32

AY35

AY36

AY37

AY38

BA13

BA14

BA29

BA30

BA31

BA32

BA33

BA34

BA35

BA36

BB13

BB14

BB31

BB32

BB33

BB34

BB35

BB36

BB37

BB38

BC29

BC30

BC31

BC32

BC35

BE33

BE34

BE35

BE36

+VCC_GT

+1.0VS_VCCIO

AG12

J30

K29

K30

K31

K32

K33

K34

K35

L31

L32

L35

L36

L37

L38

M29

M30

M31

M32

M33

M34

M35

M36

G15

G17

G19

G21

H15

H16

H17

H19

H20

H21

H26

H27

J15

J16

J17

J19

J20

J21

J26

J27

CPU1I

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

SKL-H_BGA1440

SKYLAKE_HALO

BGA1440

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQC

VCCPLL_OC

VCCPLL_OC

VCCST

VCCSTG

VCCSTG

VCCPLL

VCCPLL

VCCSA_SENSE

VSSSA_SENSE

VCCIO_SENSE

VSSIO_SENSE

AA6

AE12

AF5

AF6

AG5

AG9

AJ12

AL11

AP6

AP7

AR12

AR6

AT12

AW6

AY6

J5

J6

K12

K6

L12

L6

R6

T6

W6

Y12

BH13

G11

H30

H29

G30

H28

J28

M38

M37

H14

J14

+1.2V_MEM

12A

+VCC_FUSEPRG

+VCC_VDDQ_CLK

+VCC_SFR_OC

+1.0V_VCCST

+1.0V_VCCSTG

+1.0V_VCCSFR

VCC_SA_SENSE <63>

VSS_SA_SENSE <63>

VCC_IO_SENSE <61>

VSS_IO_SENSE <61>

RC218 0_0603_1%@

1 2

SIO_SLP_S3#<11,20,36,37,46,61,62>

SIO_SLP_SUS#<20,36,44,60,62>

SIO_SLP_S4#<1 1,20,36,37,59,71>

+1.0V_VCCSTG

+1.2V_MEM

12

CZ114 1U_0402_6.3V6K

+5V_ALW

1 2

RC305 0_0402_5%@

+3.3V_ALW

CZ115

@

1 2

5

0.1U_0402_10V7K

1

P

B

4

O

2

A

G

UC9

3

TC7SH08FU_SSOP5~D

+VCC_VDDQ_CLK +1.2V_MEM

PDDG page19, if don`t support DS3, contact to VDDQ directly

+VCC_SFR_OC

1 2

@

RC302 0_0402_5%

UZ26

1

VIN1

2

VIN2

7

VIN thermal

3

VBIAS

4

ON

TPS22961DNYR_WSON8

VOUT

GND

6

5

@

CZ113 0.1U_0201_10V6K

1 2

+1.0V_VCCSTG +1.0V_VCCST

1 2

RC317 0_0402_5%@

B B

+1.0V_PRIM

+5V_ALW

0.1U_0402_25V6

1U_0402_6.3V6K

1

12

CZ88

2

+3.3V_ALW

C1421

@

1 2

0.1U_0402_25V6

5

1

RC320 0_0402_5%@

IN1

2

IN2

1 2

P

VCCSTG_ON

4

O

G

3

A A

SIO_SLP_S0#<20,37>

SIO_SLP_S3#<11,20,36,37,46,61,62>

SN74AHC1G08DCKR_SC70-5

UC1

5

@

CZ86

UZ19

1

VIN1

2

VIN2

7

VIN thermal

3

VBIAS

4

ON

TPS22961DNYR_WSON8

VOUT

GND

+1.0V_VCCSTG

6

5

4

12

PJP1602

@

PAD-OPEN1x1m

+1.0V_VCCSTG_C

+1.0V_PRIM

1 2

CZ82 0.1U_0402_25V6@

SIO_SLP_S4#<11,20,36,37,59,71>

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

RC303 0_0402_5%@

1U_0402_6.3V6K

1

2

1 2

+5V_ALW

CZ107

0.1U_0402_25V6

12

VCCST_ON

@

CZ108

UZ18

1

VIN1

2

VIN2

7

VIN thermal

3

VBIAS

4

ON

TPS22961DNYR_WSON8

1 2

RC220 0_0402_5%@

+1.0V_VCCST +1.0V_VCCSFR

VOUT

GND

6

5

+1.0V_VCCST_UZ18

12

@

PAD-OPEN1x1m

CZ63

0.1U_0402_25V6

PJP17

1 2

12

RC304 0_0402_5%@

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size

Size

Size

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

SKL-H (6/8)

SKL-H (6/8)

Document Number Re v

Document Number Re v

Document Number Re v

SKL-H (6/8)

LA-C841P

LA-C841P

LA-C841P

1

11 74Tuesday, September 08, 2015

11 74Tuesday, September 08, 2015

11 74Tuesday, September 08, 2015

0.1

0.1

0.1

Vinafix.com

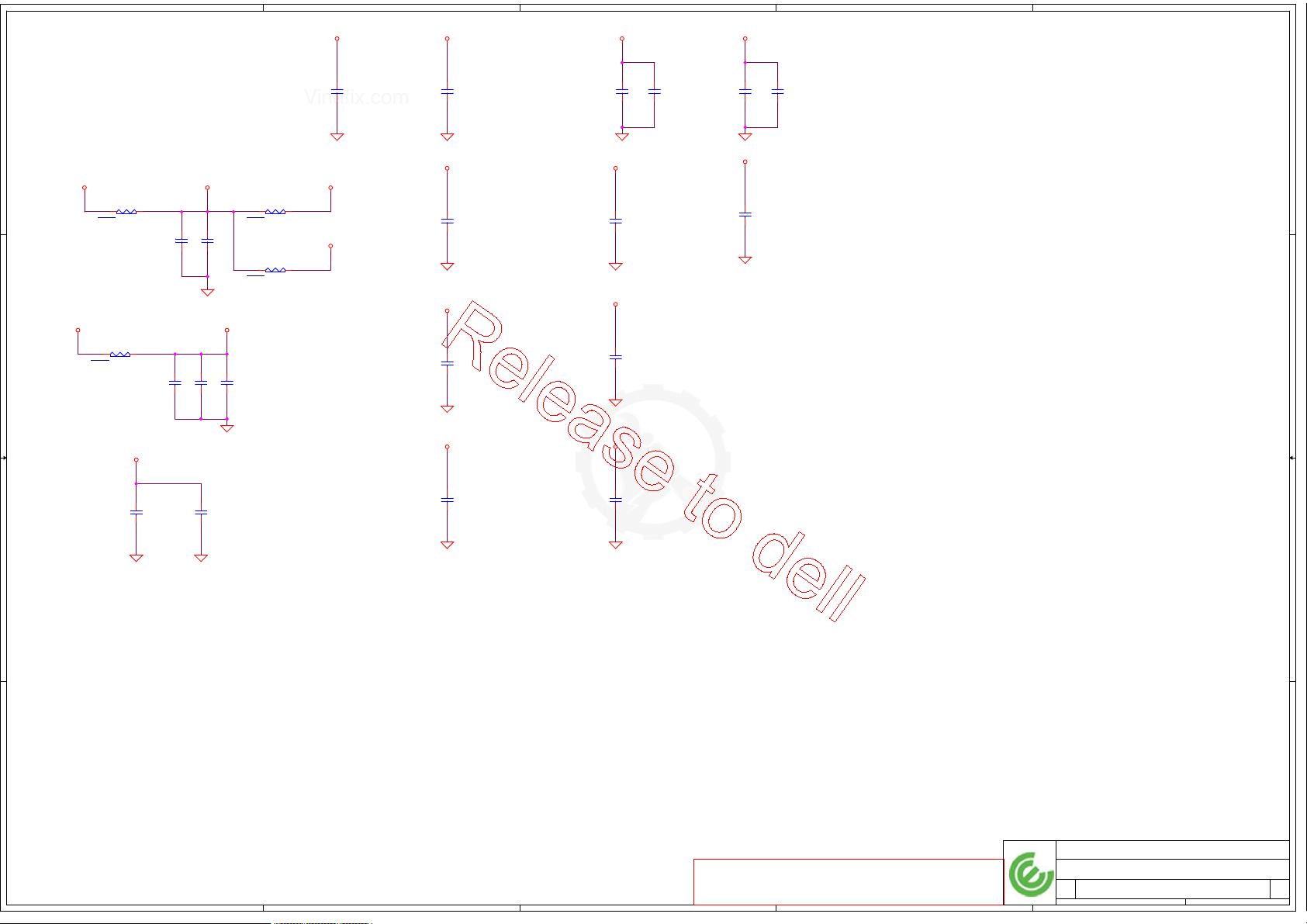

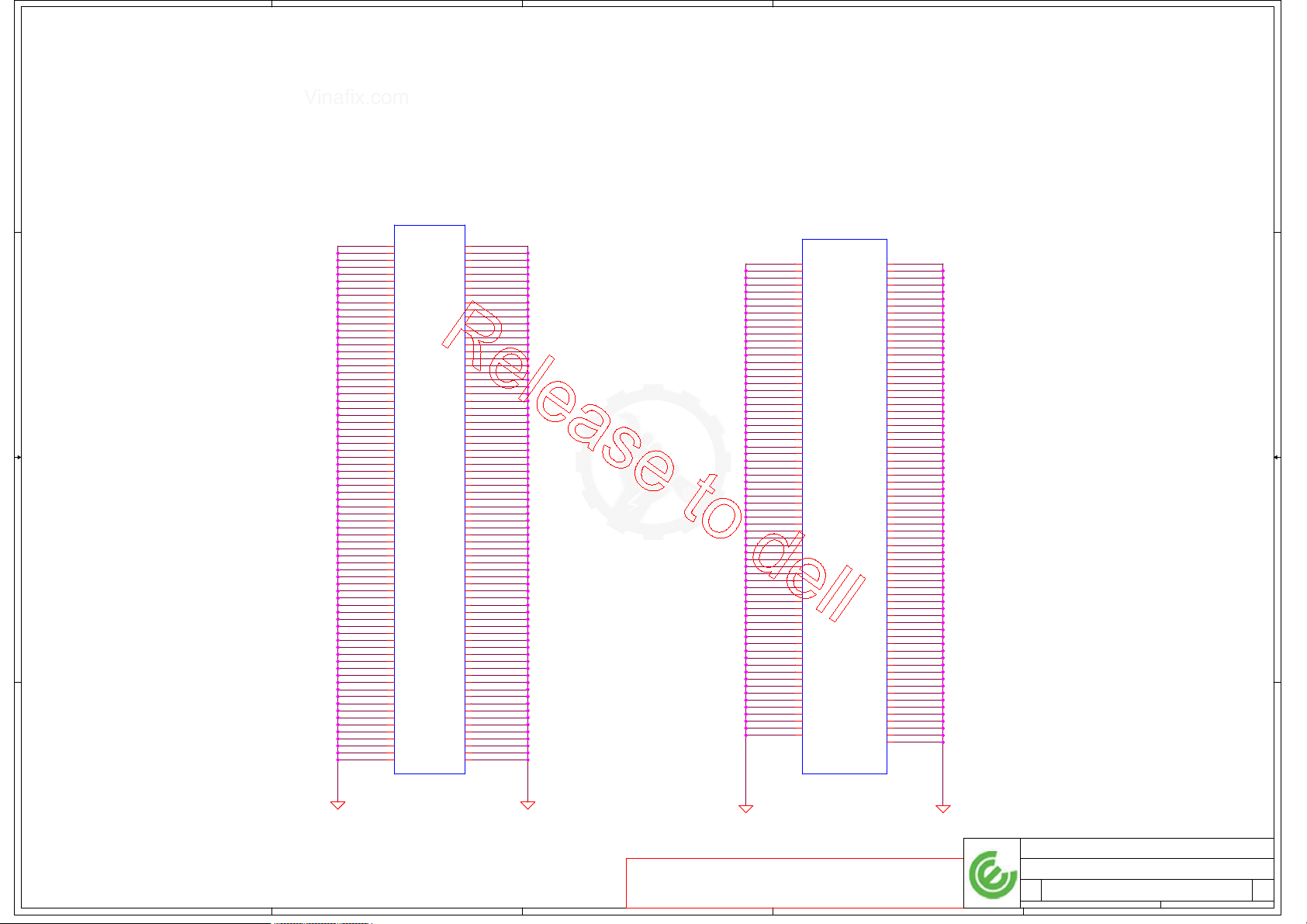

5

4

3

2

1

D D

C C

+1.2V_MEM

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

1

1

B B

CC161

2

2

22U_0603_6.3V6M

12

CC81

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

1

CC170

2

22U_0603_6.3V6M

12

CC82

10U_0603_6.3V6M~D

1

1

CC168

CC164

2

2

22U_0603_6.3V6M

22U_0603_6.3V6M

12

12

CC84

CC83

+VCC_VDDQ_CLK +1.0V_VCCSTG

+1.0VS_VCCIO

PLACE CAP BACKSIDE

10U_0603_6.3V6M~D

1

1

CC166

CC163

2

2

1

2

12

+1.0V_VCCST

10U_0603_6.3V6M~D

1

CC171

2

10U_0603_6.3V6M~D

CC185

PLACE CAP BACKSIDE

22U_0603_6.3V6M

22U_0603_6.3V6M

CC188

CC189

12

12

1U_0402_6.3V6K

1U_0402_6.3V6K

2

2

CC194

CC193

1

1

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

1

CC165

CC172

2

1

2

1U_0402_6.3V6K

2

1

22U_0603_6.3V6M

CC187

10U_0603_6.3V6M~D

CC167

PLACE CAP BACKSIDE

+1.0V_VCCSFR +1.0V_VCCST

1U_0402_6.3V6K

2

CC195

CC186

1

22U_0603_6.3V6M

CC272

12

+VCC_SFR_OC +VCC_GT +VCC_GTU

SKYLAKE_HALO

1U_0402_6.3V6K

1U_0402_6.3V6K

2

CC192

1

1U_0402_6.3V6K

2

CC191

1

1U_0402_6.3V6K

2

2

CC209

CC210

1

1

AJ29

AJ30

AJ31

AJ32

AJ33

AJ34

AJ35

AJ36

AK31

AK32

AK33

AK34

AK35

AK36

AK37

AK38

AL13

AL29

AL30

AL31

AL32

AL35

AL36

AL37

AL38

AM13

AM14

AM29

AM30

AM31

AM32

AM33

AM34

AM35

AM36

AN13

AN14

AN31

AN32

AN33

AN34

AN35

AN36

AN37

AN38

AP13

AP14

AP29

AP30

AP31

AP32

AP35

AP36

AP37

AP38

AR29

AR30

AR31

AR32

AR33

AR34

AR35

AR36

AT14

AT31

AT32

AT33

AT34

AT35

AT36

AT37

AT38

AU14

AU29

AU30

AU31

AU32

AU35

AU36

AU37

AU38

CPU1N

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

SKL-H_BGA1440

BGA1440

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGT_SENSE

VSSGTX_SENSE

VSSGT_SENSE

VCCGTX_SENSE

AF29

AF30

AF31

AF32

AF33

AF34

AG13

AG14

AG31

AG32

AG33

AG34

AG35

AG36

AH13

AH14

AH29

AH30

AH31

AH32

AJ13

AJ14

AH38

AH35

AH37

AH36

VCC_GT_SENSE <63>

VSS_GT_SENSE <63>

+VCC_CORE +VCC_CORE

SKYLAKE_HALO

CPU1G

AA13

AA31

AA32

AA33

AA34

AA35

AA36

AA37

AA38

AB29

AB30

AB31

AB32

AB35

AB36

AB37

AB38

AC13

AC14

AC29

AC30

AC31

AC32

AC33

AC34

AC35

AC36

AD13

AD14

AD31

AD32

AD33

AD34

AD35

AD36

AD37

AD38

AE13

AE14

AE30

AE31

AE32

AE35

AE36

AE37

AE38

AF35

AF36

AF37

AF38

RC221 49.9_0402_1%@

K13

K14

L13

N13

N14

N30

N31

N32

N35

N36

N37

N38

P13

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

SKL-H_BGA1440

1 2

BGA1440

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC_SENSE

VSS_SENSE

VCC_SENSEVSS_SENSE

V32

V33

V34

V35

V36

V37

V38

W13

W14

W29

W30

W31

W32

W35

W36

W37

W38

Y29

Y30

Y31

Y32

Y33

Y34

Y35

Y36

L14

P29

P30

P31

P32

P33

P34

P35

P36

R13

R31

R32

R33

R34

R35

R36

R37

R38

T29

T30

T31

T32

T35

T36

T37

T38

U29

U30

U31

U32

U33

U34

U35

U36

V13

V14

V31

P14

AG37

AG38

VCC_SENSE

VSS_SENSE

+VCC_CORE

12

12

RC140

100_0402_1%

RC141

100_0402_1%

VCC_SENSE <63>

VSS_SENSE <63>

A A

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size

Size

Size

Date : Sheet o f

Date : Sheet o f

Date : Sheet o f

Compal Electronics, Inc.

SKL-H (7/8)

SKL-H (7/8)

Document Number Re v

Document Number Re v

Document Number Re v

SKL-H (7/8)

LA-C841P

LA-C841P

LA-C841P

1

12 74Tuesday, September 08, 2015

12 74Tuesday, September 08, 2015

12 74Tuesday, September 08, 2015

0.1

0.1

0.1

Vinafix.com

5

SKYLAKE_HALO

CPU1F

BGA1440

Y38

VSS

Y37

W34

W33

W12

Y14

Y13

Y11

Y10

Y9

Y8

Y7

W5

W4

W3

W2

W1

V30

V29

V12

V6

U38

U37

U6

T34

T33

T14

T13

T12

T11

T10

T9

T8

T7

T5

T4

T3

T2

T1

R30

R29

R12

P38

P37

P12

P6

N34

N33

N12

N11

N10

N9

N8

N7

N6

N5

N4

N3

N2

N1

M14

M13

M12

M6

L34

L33

L30

L29

K38

K11

K10

K9

K8

K7

K5

K4

K3

K2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SKL-H_BGA1440

NCTFVSS

REV = 1

D D

C C

B B

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

4

?

K1

J36

J33

J32

J25

J22

J18

J10

J7

J4

H35

H32

H25

H22

H18

H12

H11

G28

G26

G24

G23

G22

G20

G18

G16

G14

G12

G10

G9

G8

G6

G5

G4

F36

F31

F29

F27

F25

F23

F21

F19

F17

F15

F13

F11

F9

F8

F5

F4

F3

F2

E38

E35

E34

E9

E4

D33

D30

D28

D26

D24

D22

D20

D18

D16

D14

D12

D10

D9

D6

D3

C37

C31

C29

C27

D38

6 OF 14

BB4

BB3

BB2

BB1

BA38

BA37

BA12

BA11

BA10

BA9

BA8

BA7

BA6

B9

AY34

AY33

AY14

AY12

AW30

AW29

AW12

AW5

AW4

AW3

AW2

AW1

AV38

AV37

AU34

AU33

AU12

AU11

AU10

AU9

AU8

AU7

AU6

AT30

AT29

AT6

AR38

AR37

AR14

AR13

AR5

AR4

AR3

AR2

AR1

AP34

AP33

AP12

AP11

AP10

AP9

AP8

AN30

AN29

AN12

AN6

AN5

AM38

AM37

AM12

AM5

AM4

AM3

AM2

AM1

AL34

AL33

AL14

AL12

AL10

AL9

AL8

AL7

AL4

?

3

SKYLAKE_HALO

CPU1M

BGA1440

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SKL-H_BGA1440

REV = 1

?

13 OF 14

NCTFVSS

NCTFVSS

NCTFVSS

NCTFVSS

NCTFVSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

2

?

SKYLAKE_HALO

CPU1L

VSS

VSS

VSS