Page 1

A

B

COMPAL CONFIDENTIAL

C

D

E

1 1

PCB NO :

LA-2791

COMPAL P/N :

2 2

MODEL NAME :

HAL00

45135631L01

Travis (UMA) Schematics Document

uFCPGA Mobile Yonah

Intel Calistoga + ICH7M

2006-01-20

3 3

4 4

REV : 1.0 (DELL: A00)

DELL CONFIDENTIAL/PROPRIETARY

MB PCB

Part Number Description

DAA0000040L

PCB ZJX LA-2791

REV0 M/B UMA

BOM NO. 45135631L01

PCB P/N: DA800002L1L

A

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

B

C

D

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Cover Sheet

LA-2791

163Tuesday, Feb ru ar y 07, 2006

E

0.6

of

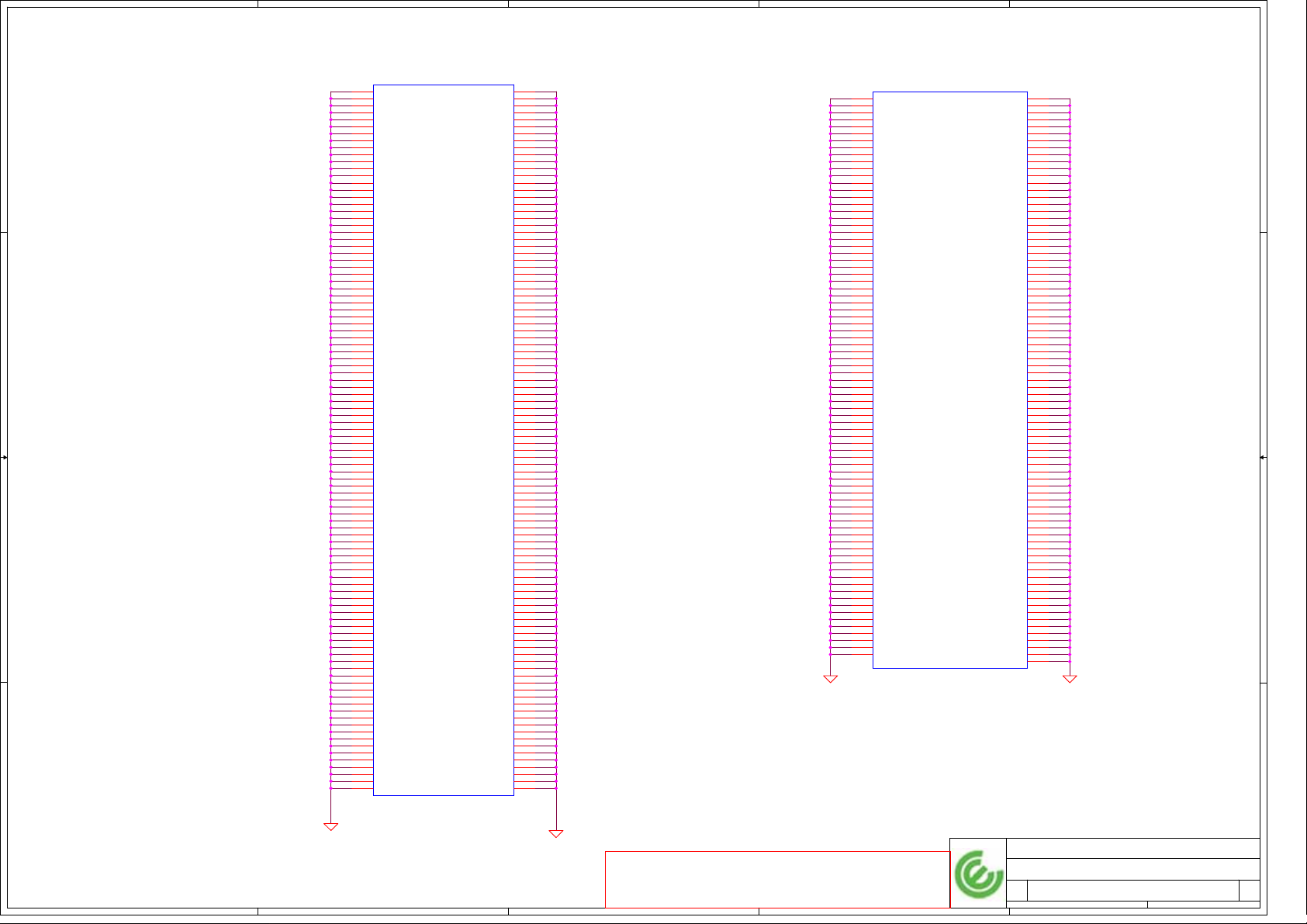

Page 2

A

Compal confidential

Model : HAL00

B

C

D

E

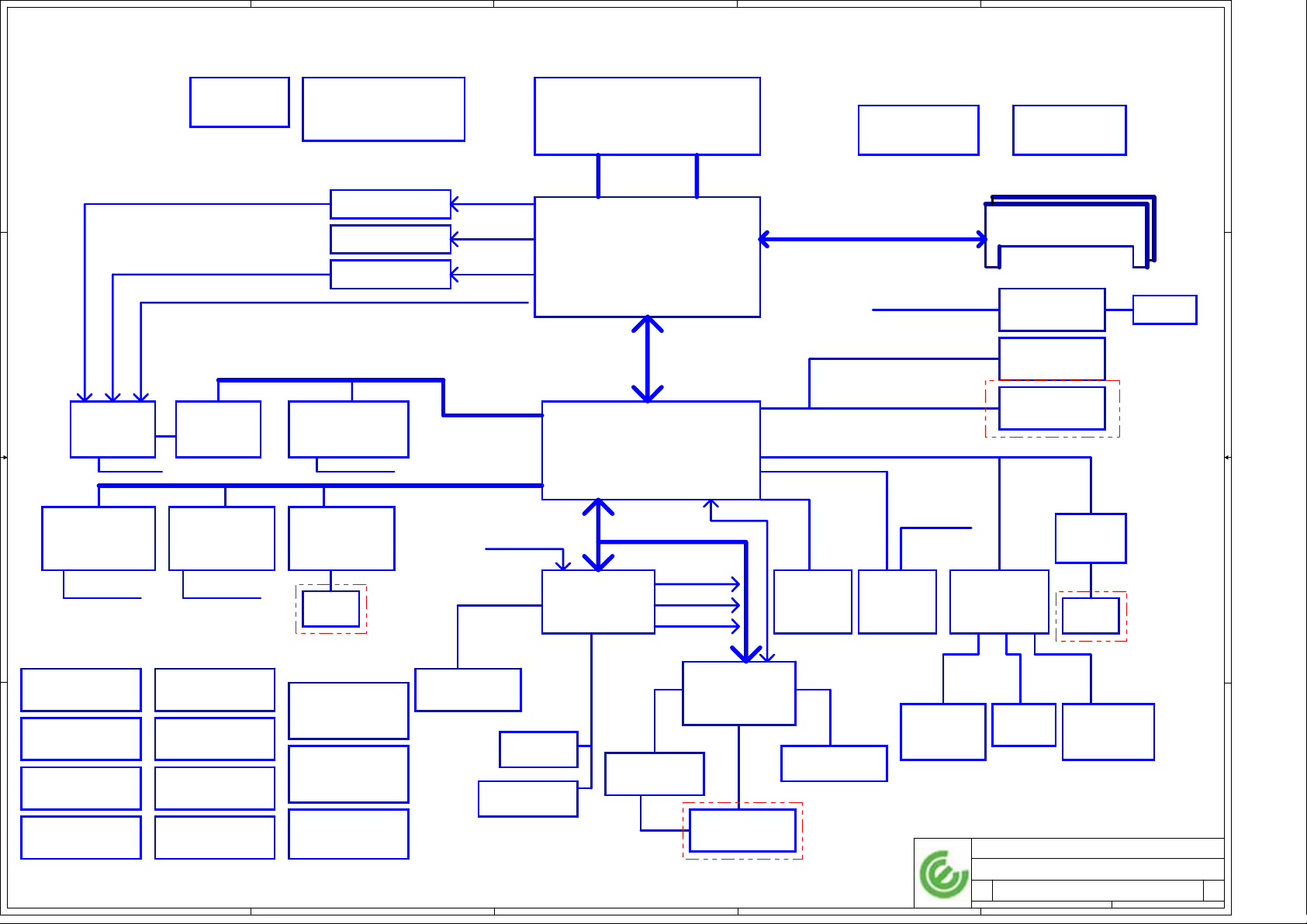

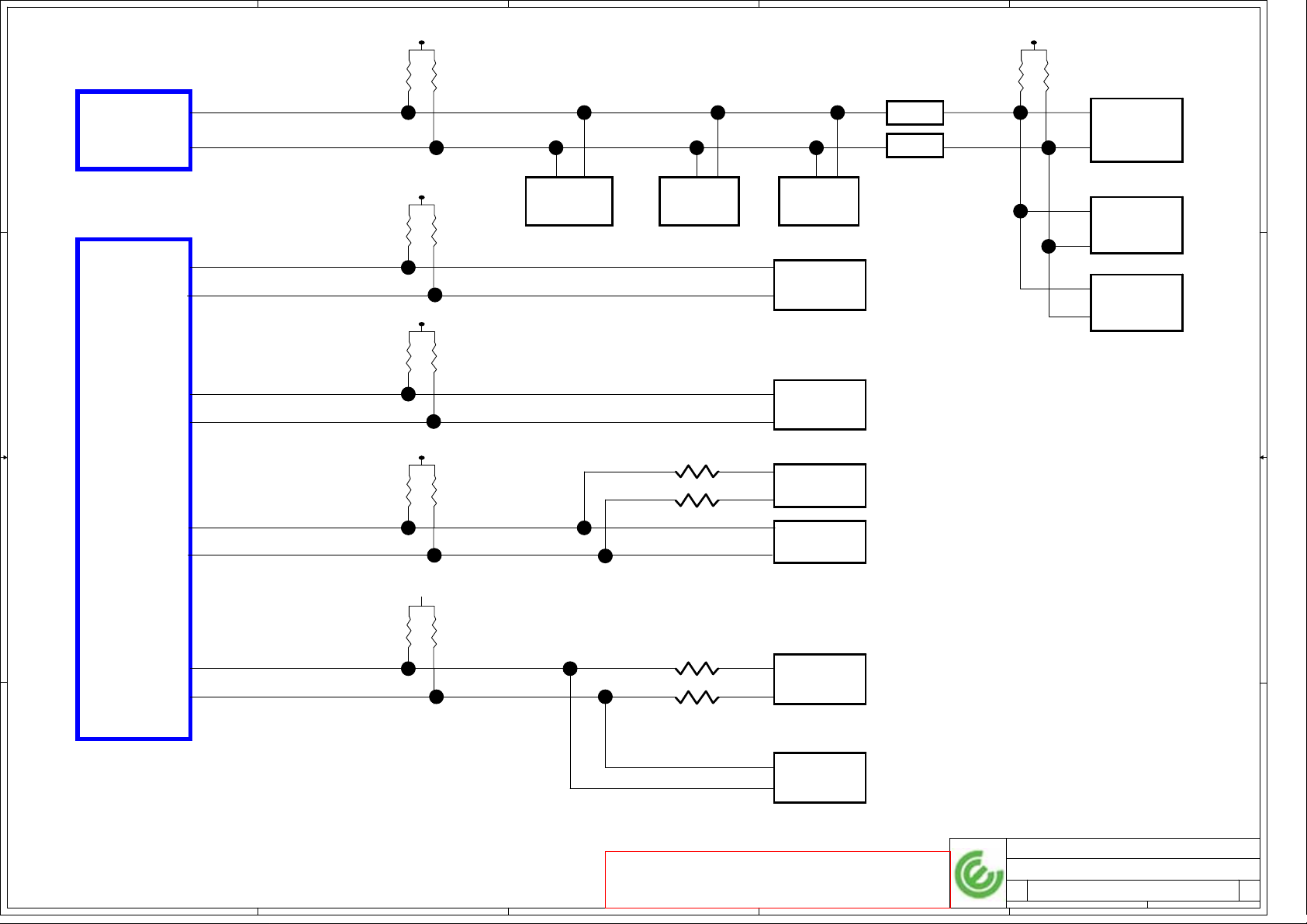

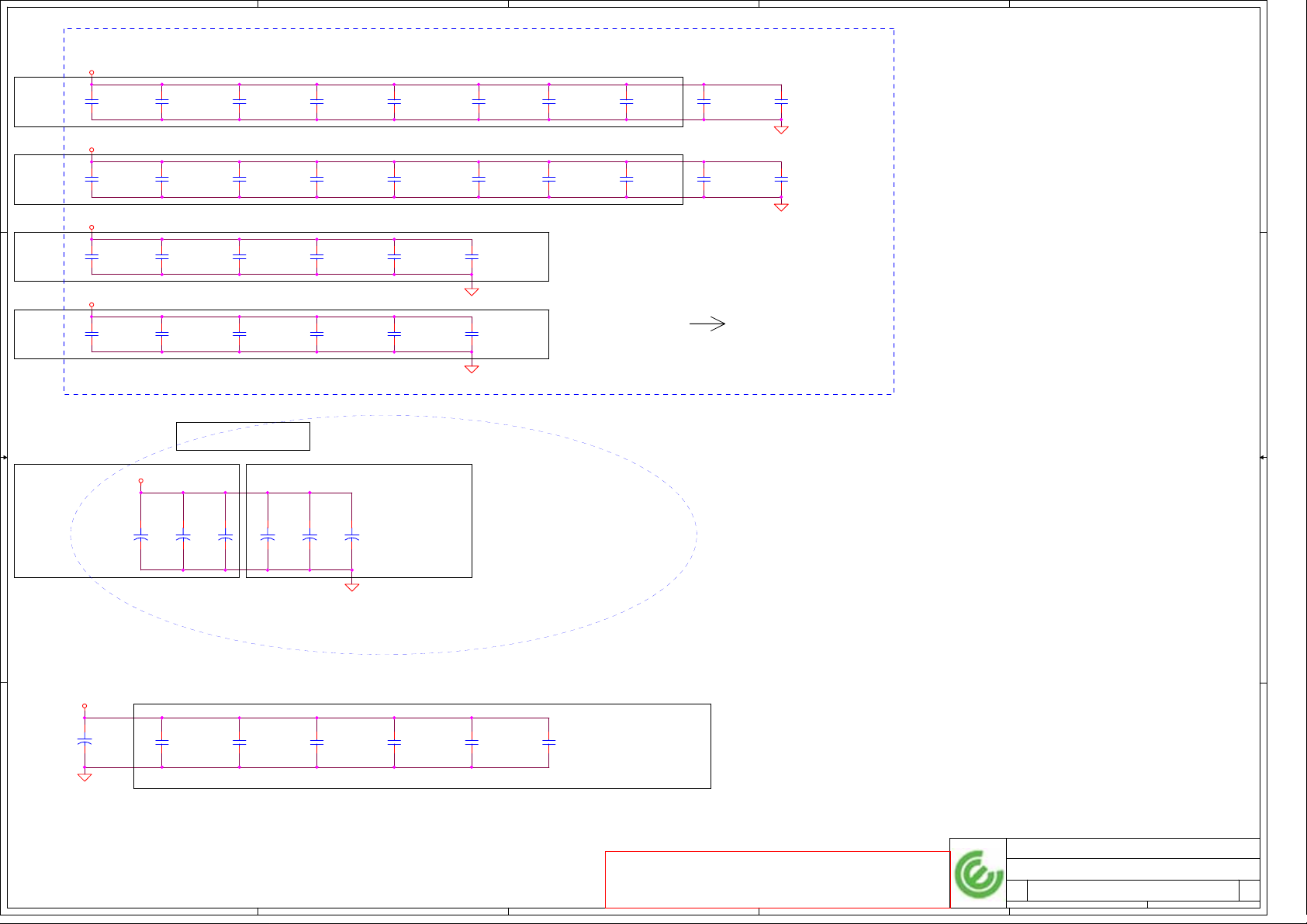

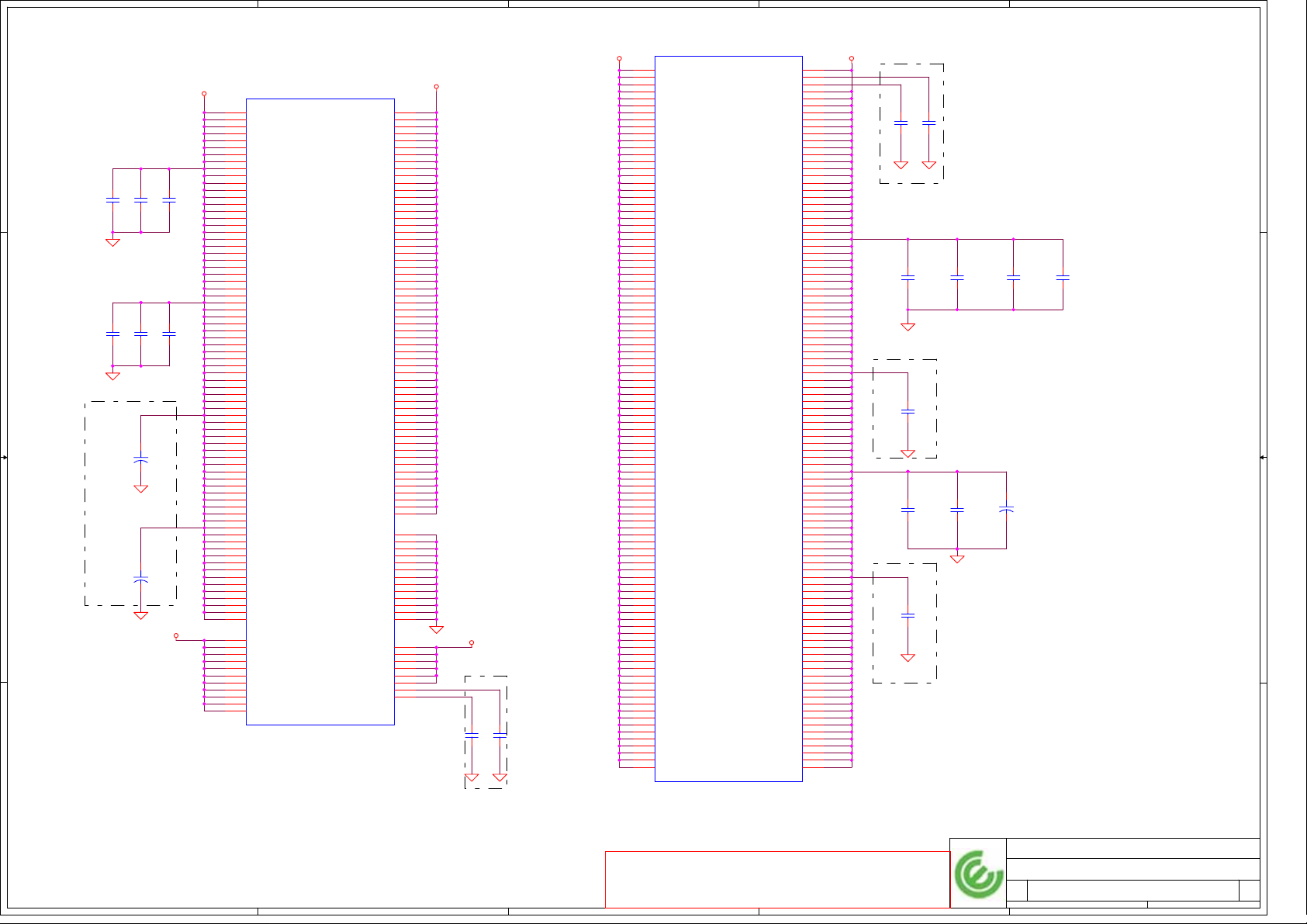

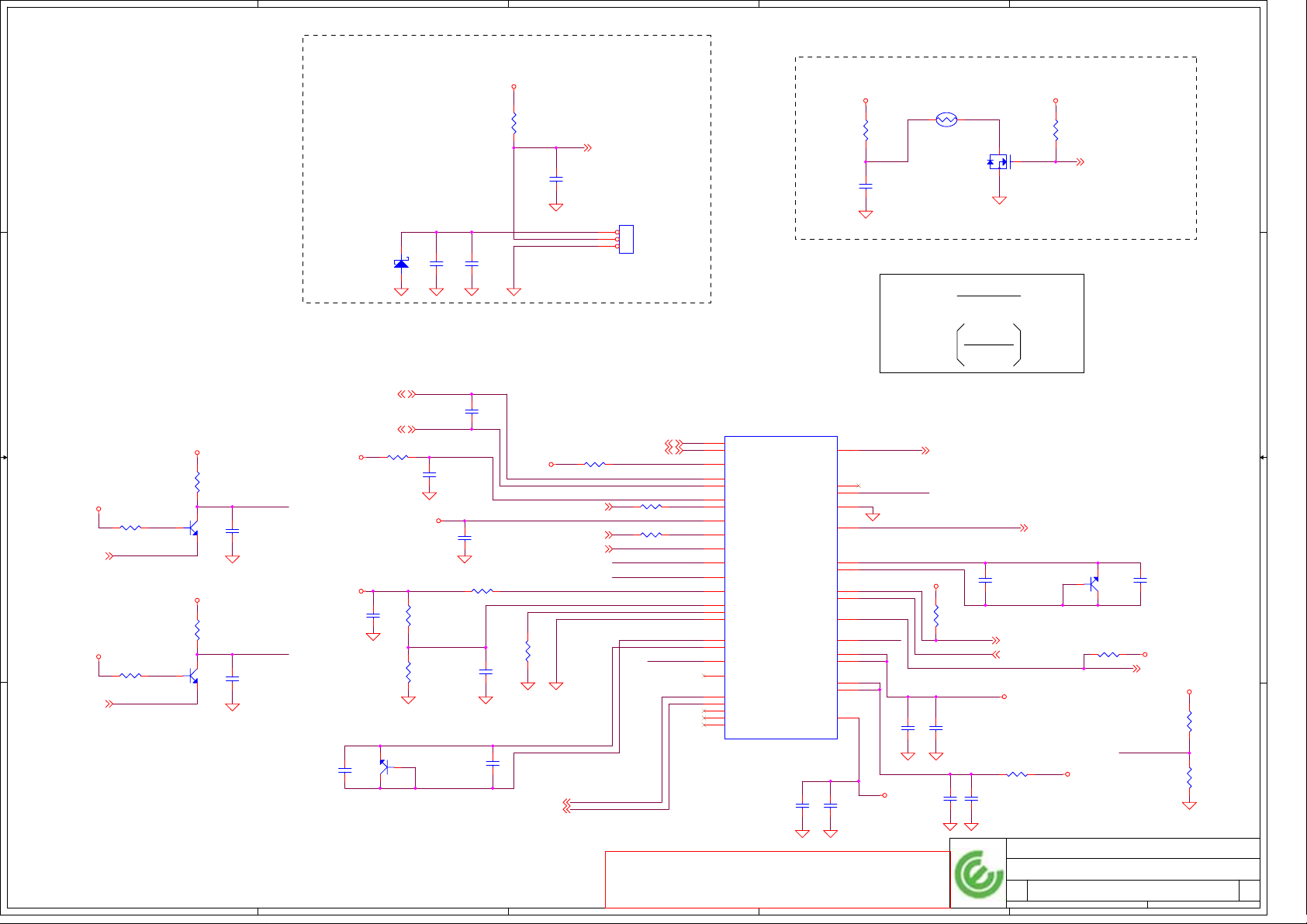

Block Diagram

FAN

1 1

2 2

DOCKING

PORT

PAGE 36

Mini Card2

WLAN

+3.3V_RUN

3 3

FAN1_VOUT

DOCKING

BUFFER

+5VRUN

+3.3V_RUN/ +1.5V_RUN 100MHz

Mini Card 1

WWAN

+3.3V_RUN

+1.5VRUN+1.5VRUN

HUB USB[2]USB[0]

PAGE 35

page 34page 34

page 18

RGB

DVI

TV

+3VRUN

GIGA Enthernet

+3VLAN

Thermal

GUARDIAN II

EMC4000

+3.3V_SUS

CRT CONN

+5V_RUN

LVDS CONN

on M/B Board

DVI Bridge

SI1362

PCI BUS

+3.3V_RUN 33MHz

CardBus

OZ601 TQFP

page 30

HUB USB[1]USB[7]

BCM5752

page 28,29

RJ45

IO/B

page 18

page 20

page 19

page 19

RGB

LVDS

DVO

IDSEL:AD17

(PIRQC,D#,GNT#1,REQ#1)

PCI Express BUS

HUB USB[4]

USB[1]

Pentium-M

Yonah-2M

+1.05V_VCCP (1.05V)

+VCC_CORE

478pin

System Bus

FSB 533/667 MHz

INTEL

+1.5V_RUN

+1.8V_SUS

+1.05V_VCCP (1.05V)

+3.3V_RUN

+2.5V_RUN

Calistoga

1466pin BGA

DMI

+1.5V_RUN

100MHz

+3.3V_RUN

+3.3V_SUS

+1.5V_RUN

+1.05V_VCCP

ICH7-M

652pin BGA

+3VRUN

33MHz

SMSC SIO

ECE5018

+3VALW

page 38

page 7,8,9

H_D#(0..63)H_A#(3..31)

page 10,11,12,13,14,15

INTEL

page 21,22,23,24

SPI

LPC BUS

HUB USB[1]

HUB USB[2]

HUB USB[3]

CPU ITP Port

+1.05V_VCCP

Memory BUS

(DDR2)

48MHz

SATA

S-HDD

+5VHDD

+1.8V_SUS 533 / 667MHz

HUB USB[3]

USB[5,6]

REAR

USB[3,4] SIDE

Azalia I/F

ATA100

USB[2]

D Moudle

page 25 page 25 page 26

+5VMOD

Azalia Codec

Clock GeneratoruFCPGA CPU

SLG84450VTR

+3.3V_RUN

DDRII-DIMM X2

BANK 0, 1, 2, 3, 4 ,5 ,6 ,7 ,8

+0.9V_DDR_VTT

+1.8V_SUS

Smart Card

OZ77C6

+3.3V_RUN

USB Ports X2

+5V_SUS

USB Ports X2

+5V_SUS

STAC9200

+3.3V_RUN

+VDDA

page 16,17

page 31

page 32

IO/B

MDC

+3.3V_SUS

page 33

RJ11

page6page 7

SLOT

USB4 on right side of

connector, USB6 on left side

USB0 on the top of connector,

USB2 on the bottom

Cable

IO/B

1.8V/0.9V

page 48

VCORE (IMVP-6)

page 49

1.5V/1.05V

DC IN

page 47

page 44

Power Sequence

page 42

Power On/Off

CHARGER

4 4

page 50

BATT SELECT

page 51

BATT IN

page 45

3V/5V/15V

page 46

A

SW & LED

page 43

DC/DC Interface

page 41

B

Bluetooth

+3.3V_RUN

page 33

COM

FIR

+3.3V_RUN

page 37

page 37

Int.KBD &

page 40

Stick

Stick

C

MEC5004

+RTC_CELL

+3.3V_ALW

Touch Pad

+5V_RUN

page 39

page 33

SPI

ST M25P80

+3.3V_ALW

page 39

AMP & INT.

Speaker

+5V_SUS +3.3V_RUN

page 27 page 27

INT MIC

+5V_SUS

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

D

Date: Sheet

HeadPhone &

MIC Jack

Compal Electronics, Inc.

Block Diagram

LA-2791

263Tuesday, Feb ru ar y 07, 2006

E

0.6

of

Page 3

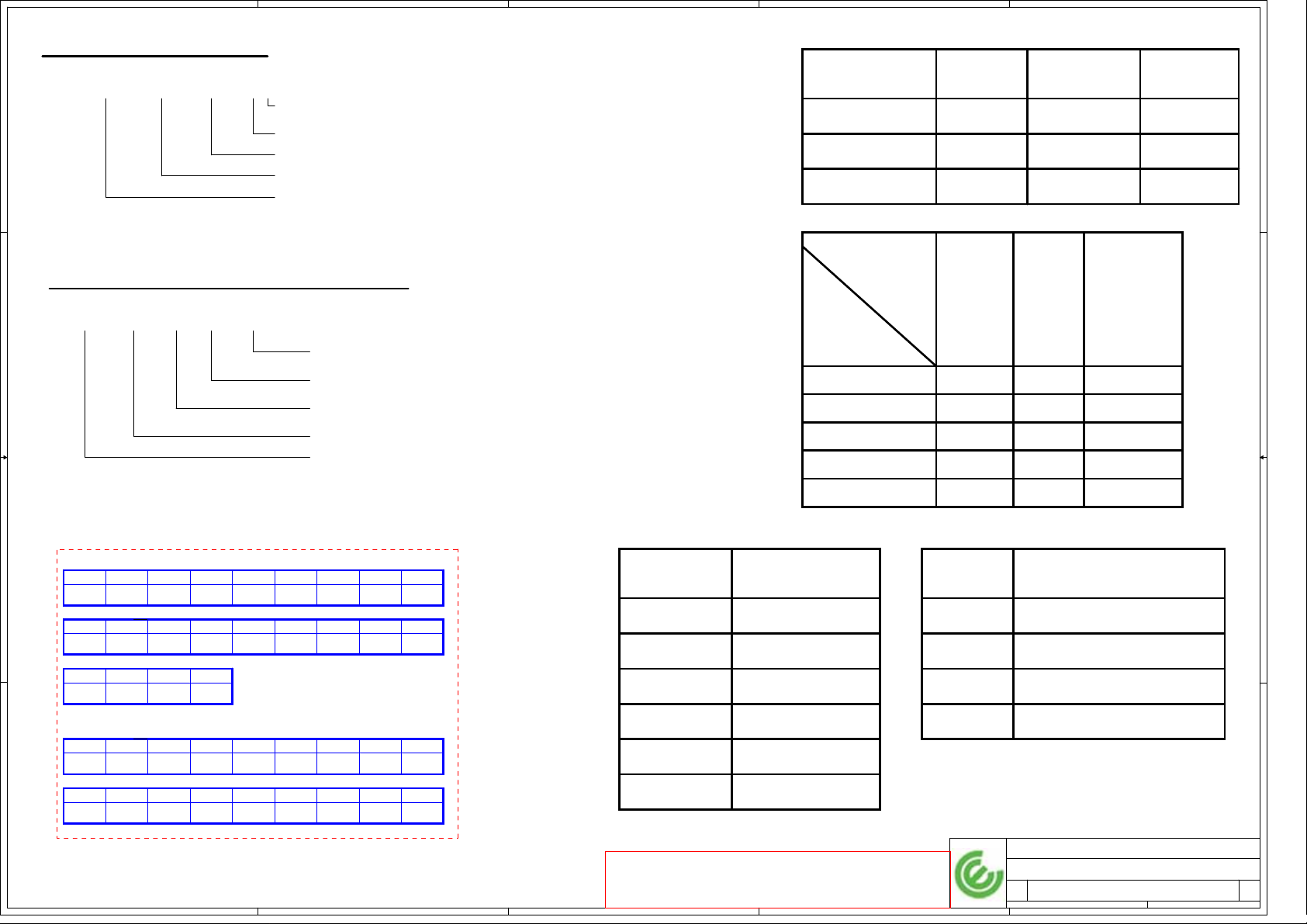

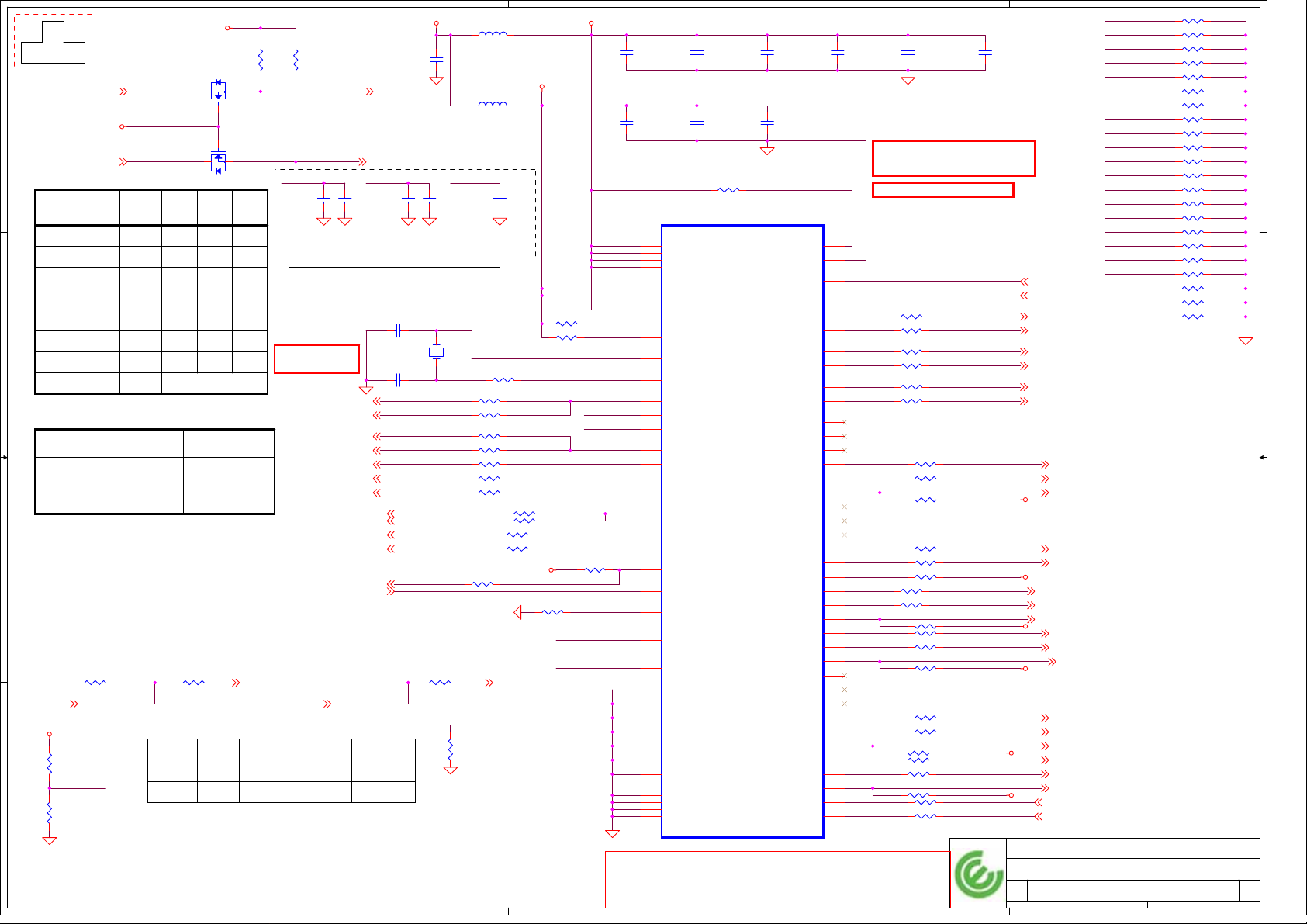

5

Ceramic Capacitors :

4

3

PCI

TABLE

2

1

PCI DEVICE

IDSEL

REQ#/GNT#

PIRQ

0.1U_0402_6.3VXX

D D

Tolerance

Temperatur e Characteristics

CARD BUS

AD17

1

Rated Voltage

Package Size

Value

PM TABLE

+3.3V_SRC

Tantalum or Polymer Capacitors :

power

plane

+3.3V_ALW

10U_D2_10VX_R45

C C

Low ESR Mark : 45 m ohm

Tolerance

Rated Voltage

Package Size

Value

State

S0

S1

S3

S5 S4/AC

S5 S4/AC don't exist

ON

ON

ON

ON

+15V_SUS

+5V_SUS+5V_ALW +1.8V_RUN

+3.3V_SUS

+1.8V_SUS

ON

ON

ON

OFF

OFF

+5V_RUN

+3.3V_RUN

+3.3V_RUN_R

+0.9V_DDR_VTT

+1.5V_RUN

+VCC_CORE

+1.05V_VCCP

+2.5V_RUN

ON

ON

OFF

OFF

OFFOFF

C

Capacitor Spec Guide:

Temperature Characteristics:

B B

A A

Symbol

CODE

Tolerance:

Symbol

CODE

Z5U

8

9

COG SJ

HI J

UK

UJ

A

+-0.05PF

+-0.1PF

M

K

+-20%

+-10%

+-30%

Z5V

X6SNPO

SL

N

A

1

B

2

Z5P

B

BJ

K

X5S

C

+-0.25PF

P

+100,-0%

4

5

G

X

6

X5R

SH

H

+-3%

Z

+80,-20%

30

Y5V

Y5U X7R

C

CH

D

+-0.5PF +-1PF

Q

+20,-10%

+30,-10%

Y5P

DEFG

CJ

CK

F

+-2%

V

+40,-20%

7

J

+-5%

NOTE1:

@XX : Depop component

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

TABLEUSB

USB PORT#

0

1

2

3,4

5,6

7

3

DESTINATION

Mini 2(WLAN)

USB Hub (5018)

D Moudle

SIDE Blue tooth

USB H U B DESTINATION

1

2

3

PC Card Bay

Mini 1(WWAN)

Smart Card --> BIO

4

REAR

Docking

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

2

Date: Sheet

Compal Electronics, Inc.

Index and Config.

LA-2791

363Tuesday, Feb ru ar y 07, 2006

1

0.6

of

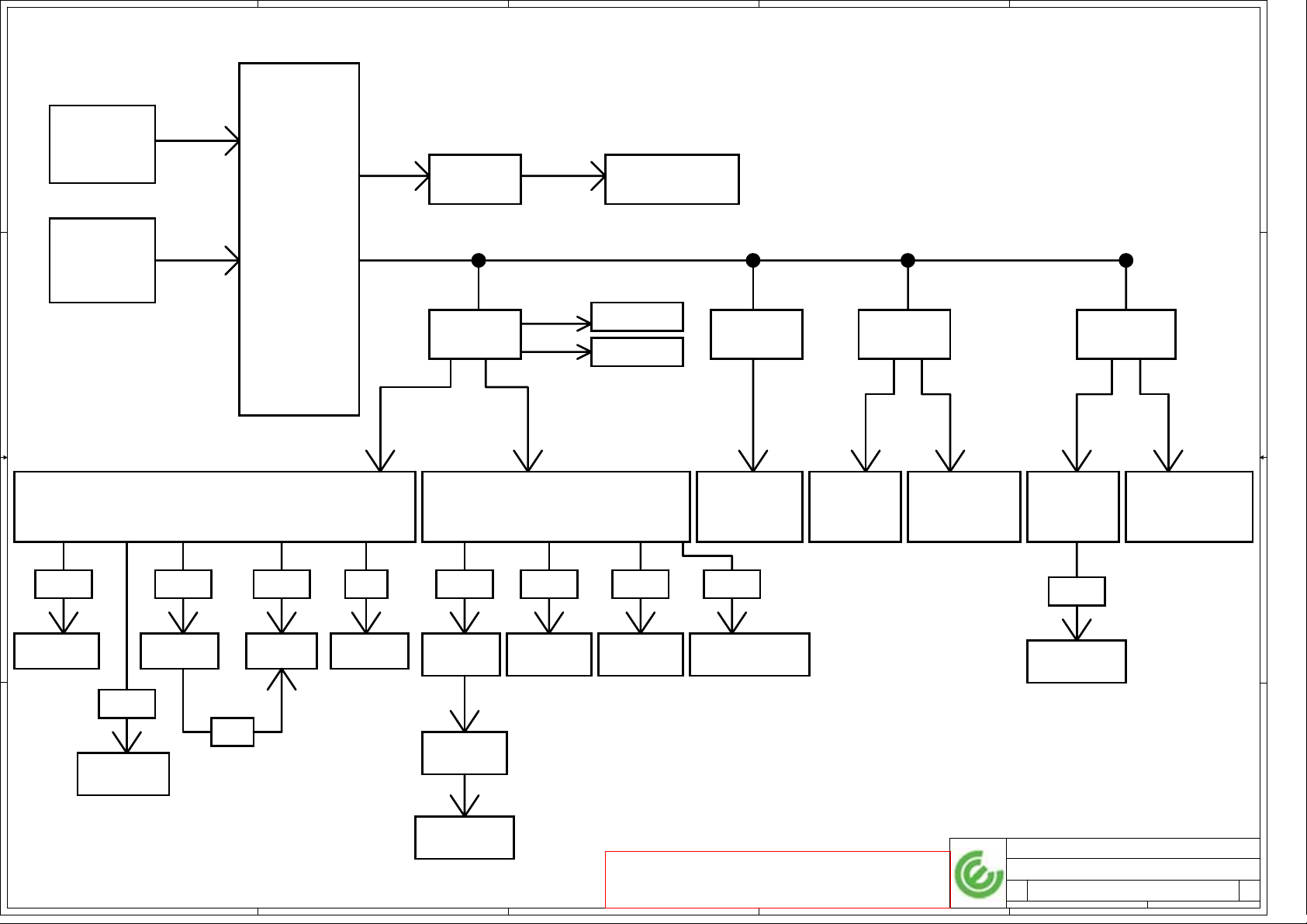

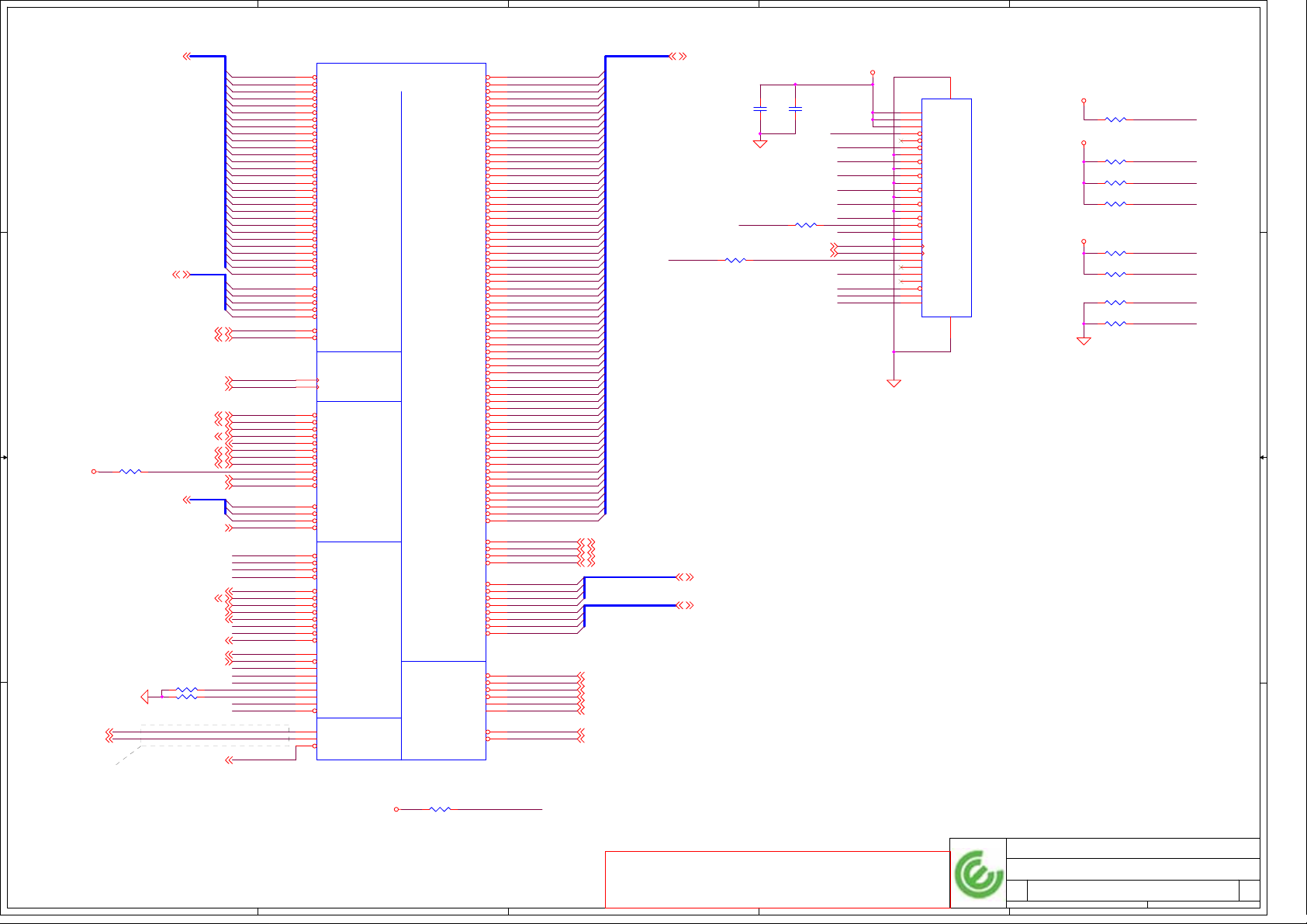

Page 4

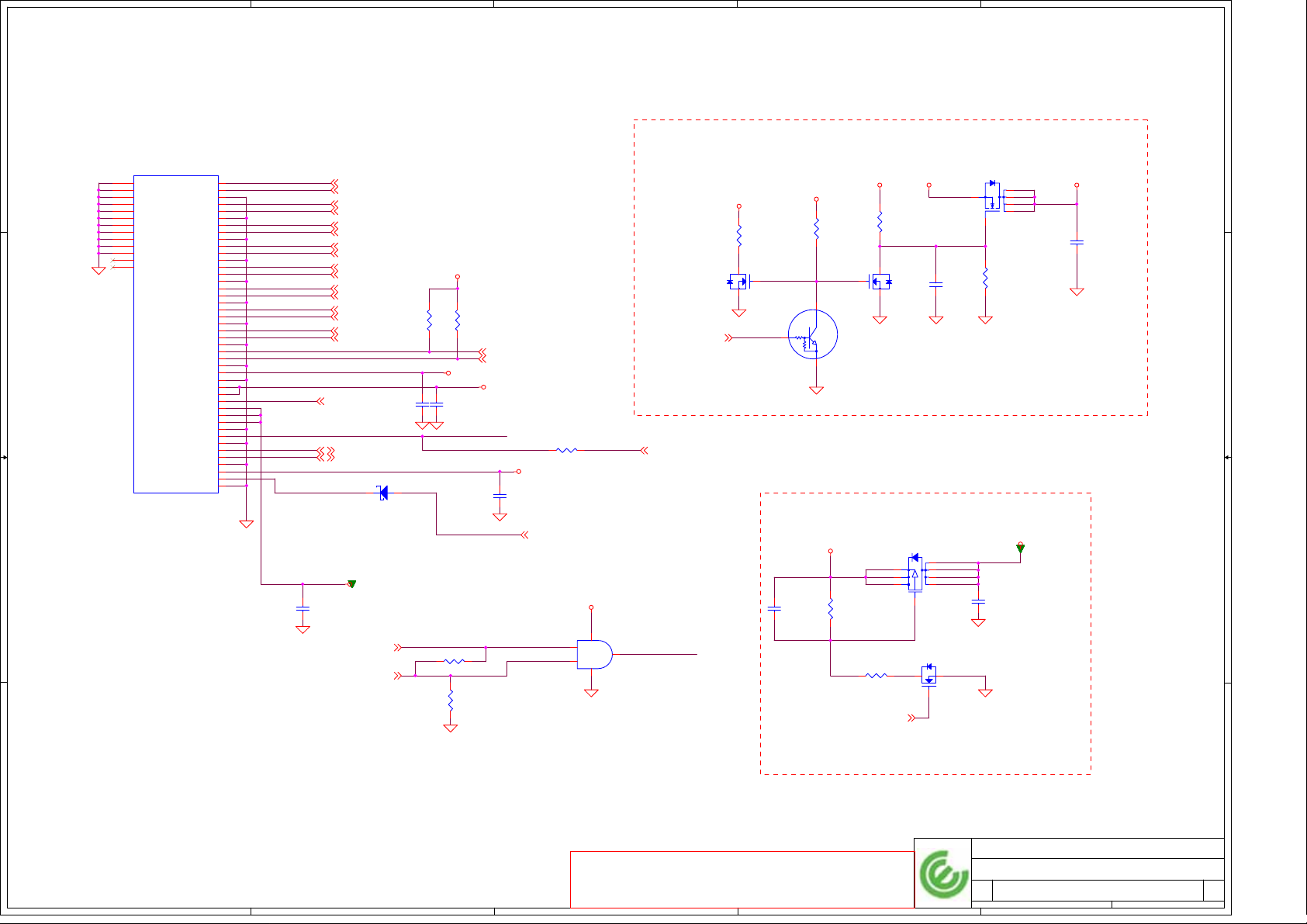

5

D D

4

3

2

1

ADAPTER

+PWR_SRC

FDS4435 +INV_PWR_SRC

RUN_ON

BATTERY

ALWON

C C

SUS_ON

MAX8734

ALWON

SUS_ON

+3.3V_SRC+5V_SUS

B B

SI3456

HDDC_EN#

SI3456

RUN_ON

793475

PL8 SI4800

AUDIO_AVDD_ON

(Option)

SI4800

RUN_ON

SI3456

ENAB_3VLAN

+5V_ALW

+3.3V_ALW

ISL6260 MAX88550

RUNPWROK

+VCC_CORE

SI4800

RUN_ON

ISL6227

RUNPWROK

RUNPWROK

SUSPWROK_5V

+1.8V_SUS

SI3456

RUN_ON

RUN_ON

+0.9V_DDR_VTT+1.05V_VCCP+1.5V_RUN

+VDDA

MODC_EN#

+15V_SUS

+3VLAN

+3.3V_SUS+3.3V_RUN+5V_SATA +5V_RUN

+3.3V_RUN_R

+1.8V_RUN

SI3456

L47

EMC4000

MOD

(+5VRUN)

A A

+2.5V_RUN

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Power Rail

LA-2791

463Tuesday, Feb ru ar y 07, 2006

1

of

0.6

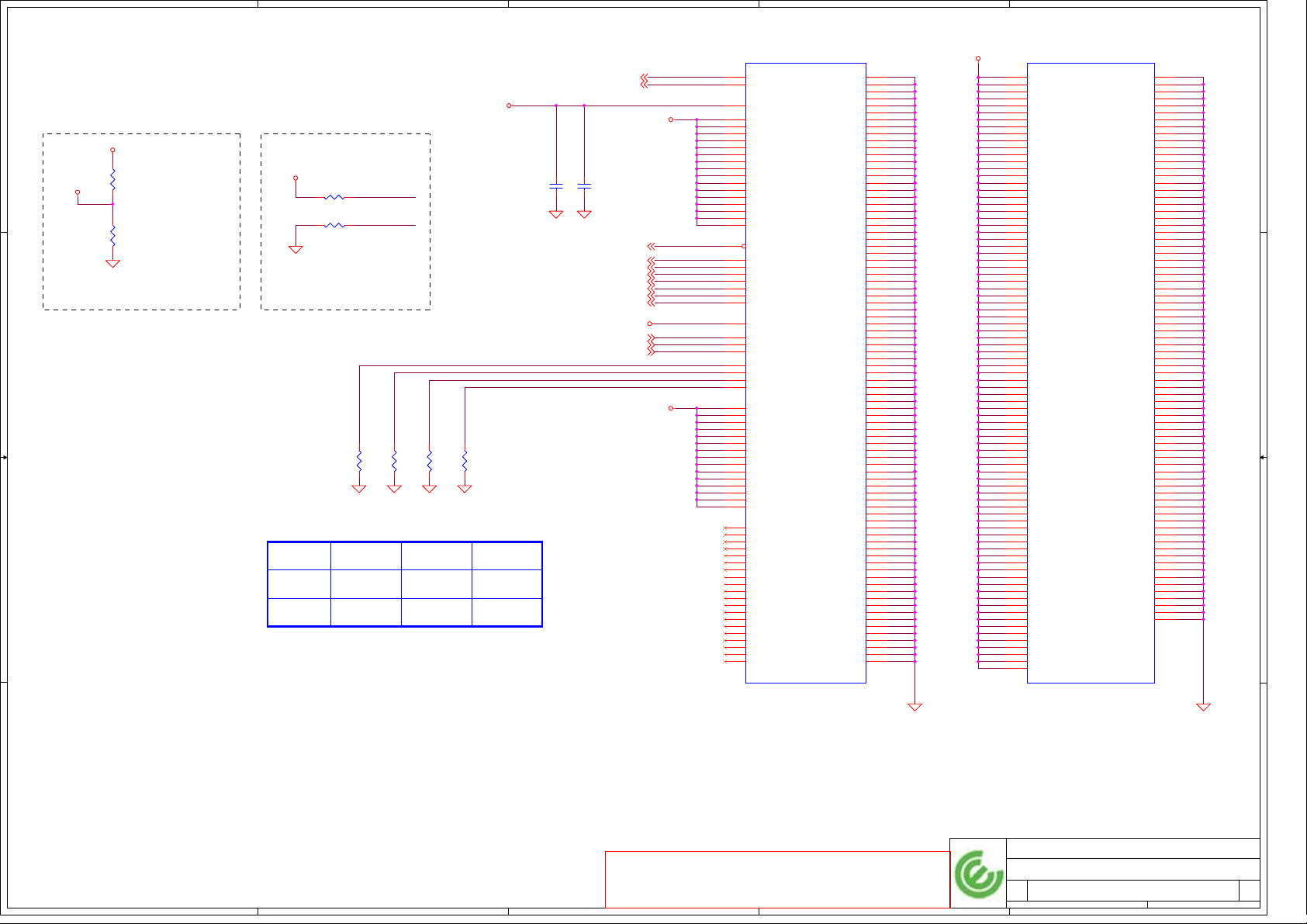

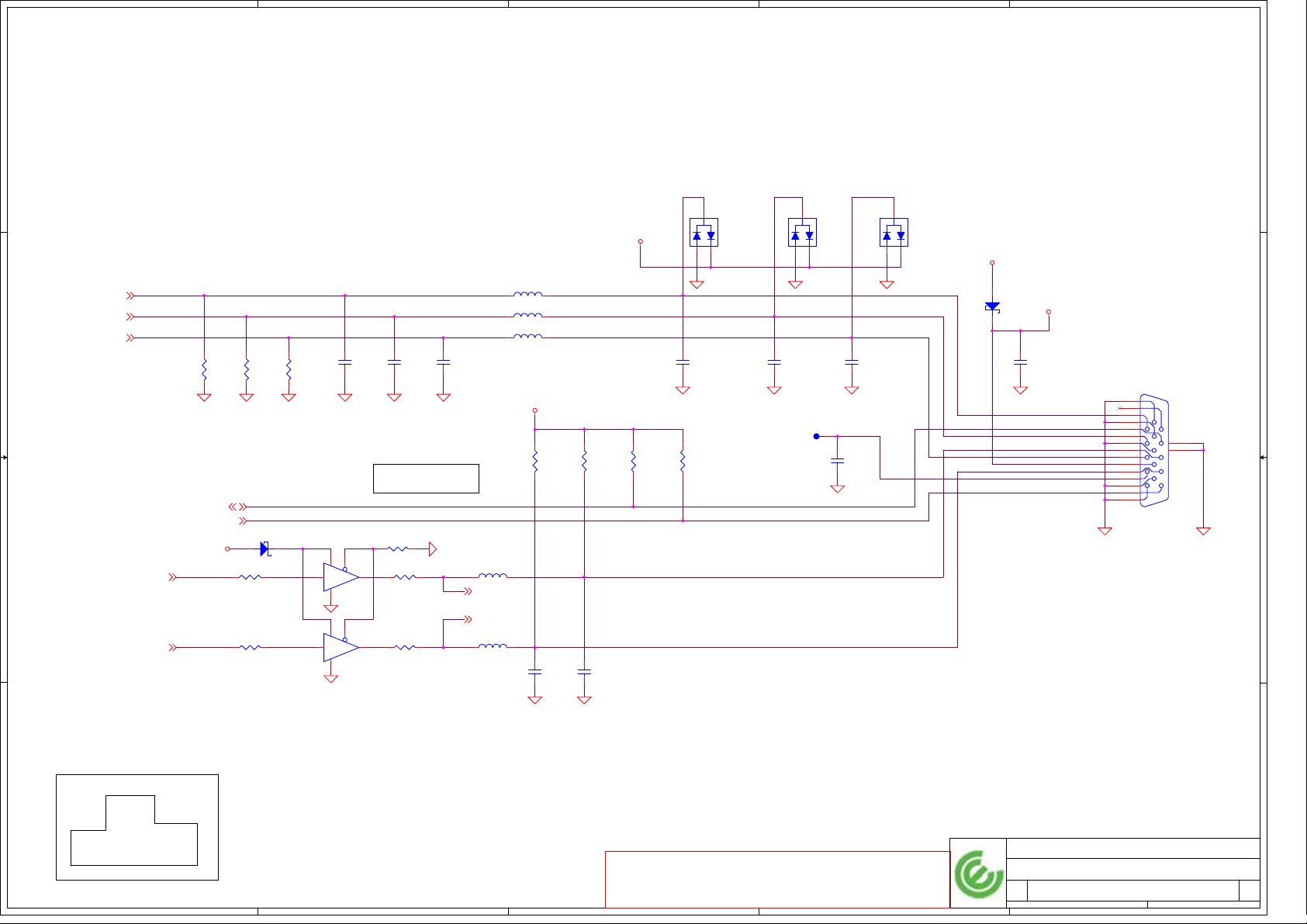

Page 5

5

4

3

2

1

+3.3V_SUS

2.2K 2.2K 2.2K 2.2K

ICH_SMBCLK

C22

D D

C C

B B

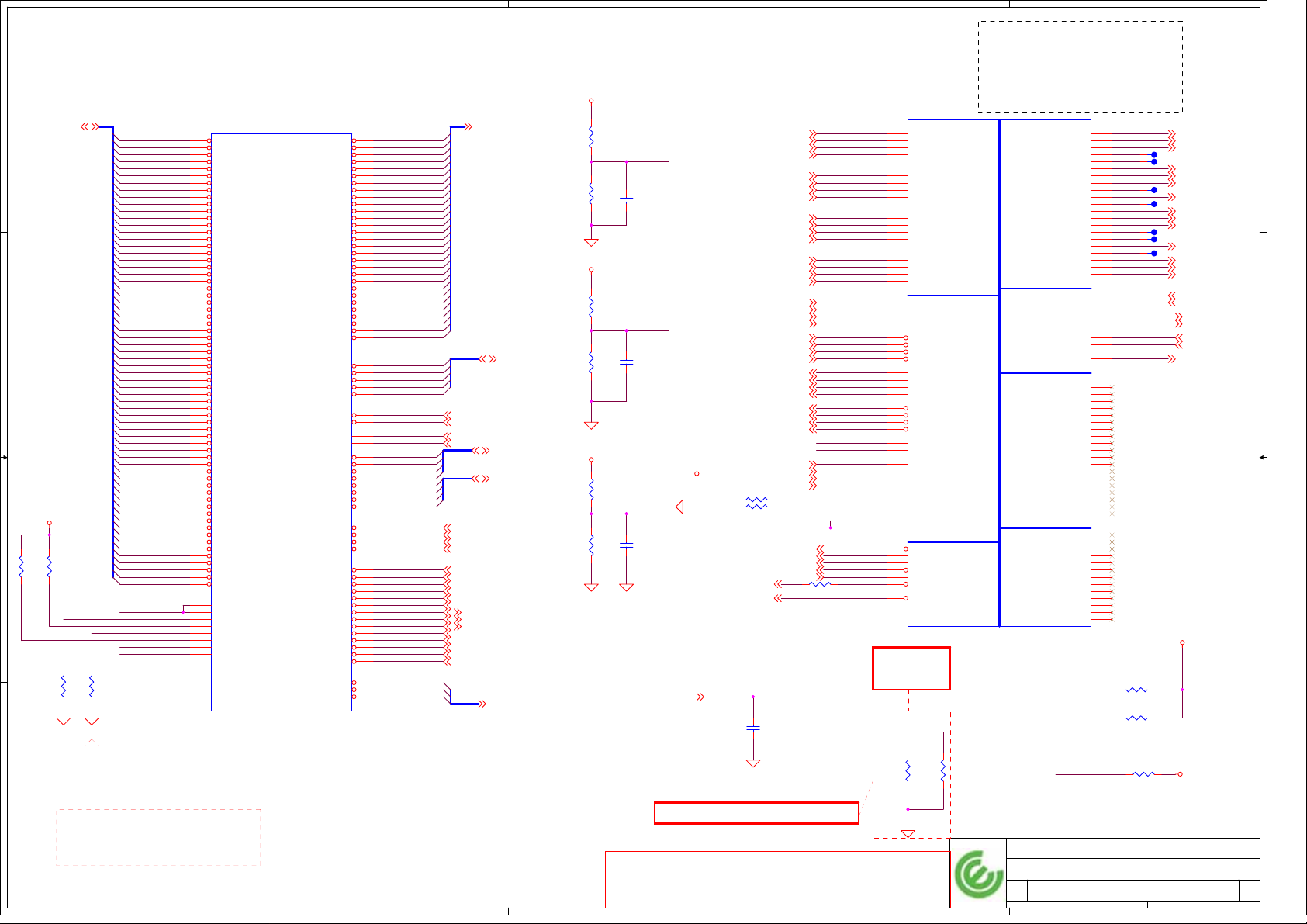

ICH7-M

SIO

Macallan IV

ICH_SMBDATA

B22

+3.3V_ALW

10K 10K

CLK_SMB

6

DAT_SMB +3.3V_ALW

5

+3.3V_ALW

8.2K 8.2K

DOCK_SMB_CLK

10

DOCK_SMB_DAT

9

+3.3V_ALW

4.7K 4.7K

112

111

SBAT_SMBCLK

SBAT_SMBDAT

+3.3V_ALW

+3.3V_SUS

WWAN

SMBUS Address [TBD]

+3.3V_ALW

+3.3V_ALW

2N7002

2N7002

3032

5752M

LOM

SMBUS Address [C8]

100

C8C7

WLAN

SMBUS Address [TBD]

8

GUARDIAN

7

39

DOCKING

40

3

2'nd

4

BATTERY

100

6

INV

5

3032

SMBUS Address [2F]

SMBUS Address [C4, 72, 70, 48]

SMBUS Address [16]

Inverter

SMBUS Address [58]

CLK_SCLK

CLK_SDATA

+3.3V_RUN

197

195

197

195

16

CLK GEN.

17

SMBUS Address [D2]

DIMM0

SMBUS Address [A0]

DIMM1

SMBUS Address [A2]

8.2K8.2K

8

7

A A

PBAT_SMBCLK

PBAT_SMBDAT +3.3V_ALW

100

100

3

BATTERY

4

CONN

9

CHARGER

10

SMBUS Address [16]

SMBUS Address [12]

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

SMBUS TOPOLOGY

LA-2791

563Tuesday, Feb ru ar y 07, 2006

1

0.6

of

Page 6

5

D

1

3

G S

2

2N7002

ICH_SMBDATA23,28,34 CLK_SDATA 16,17

D D

+3.3V_RUN

ICH_SMBCLK23,28,34

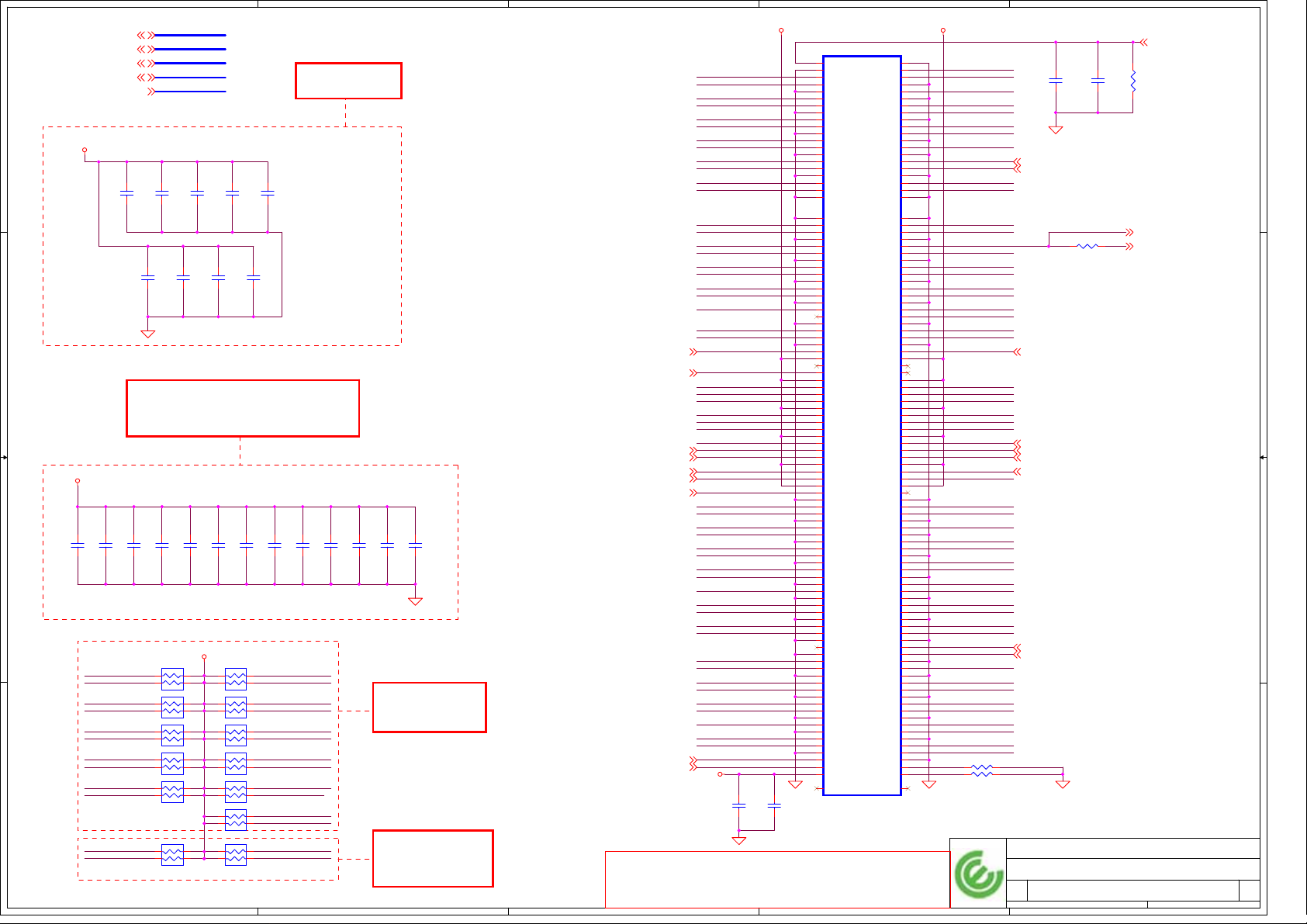

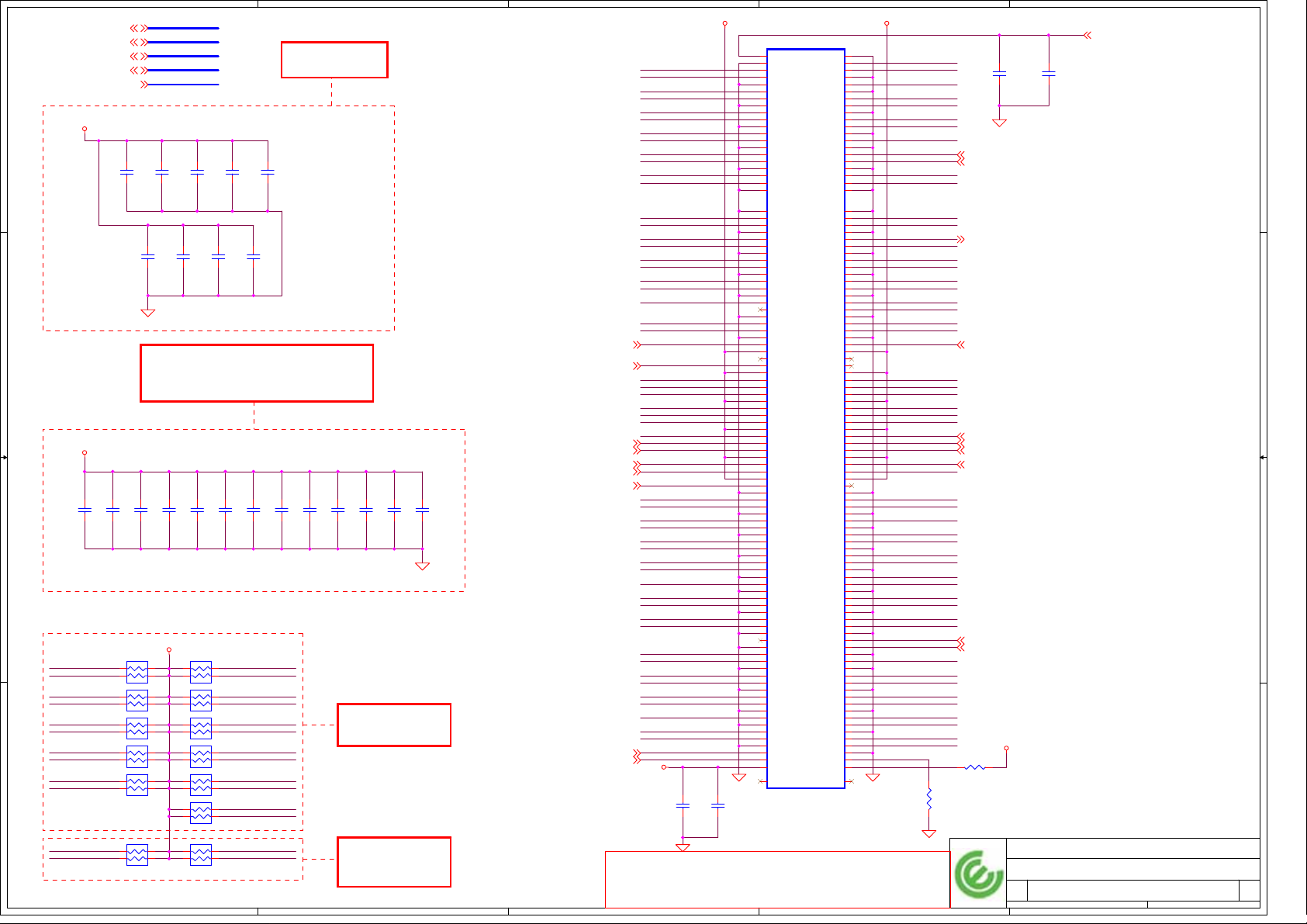

FSC FSB FSA CPU

CLKSEL2 CLKSEL0CLKSEL1

ICH_SMBDATA

ICH_SMBCLK

000

1

*

C C

00

1

0

11

0

1

1

0

1

1

11

0

00

1

0

1

CPU_BSEL CPU_BSEL2(FSC) CPU_BSEL1(FSB)

133

166

B B

R531

8.2K_0402_5%~D

FSC

CPU_BSEL28 CPU_BSEL18

+3.3V_RUN

A A

R271

10K_0402_5%~D

1 2

FSA

12

R278

@

10K_0402_5%~D

0

0

12

*

5

+3.3V_RUN

D

1 3

1 3

D

2N7002W-7-F_SOT323~D

SRC

MHz

MHz

100

266

100

133

100

200

100

166

100

333

100

100

100

400

12

R270

2.2K_0402_5%~D

S

Q36

2N7002W-7-F_SOT323~D

G

2

2

G

S

Q38

PCI

MHz

33.3

33.3

33.3

33.3

33.3

33.3

33.3

12

R275

2.2K_0402_5%~D

CLK_SDATA

CLK_SCLK

1

2

C68

4.7U_0603_6.3V4Z~D

NOTE: Place Decoupling as close as

physically possilble to the VDD pins

Place crystal within

500 mils of CK410

Reserve

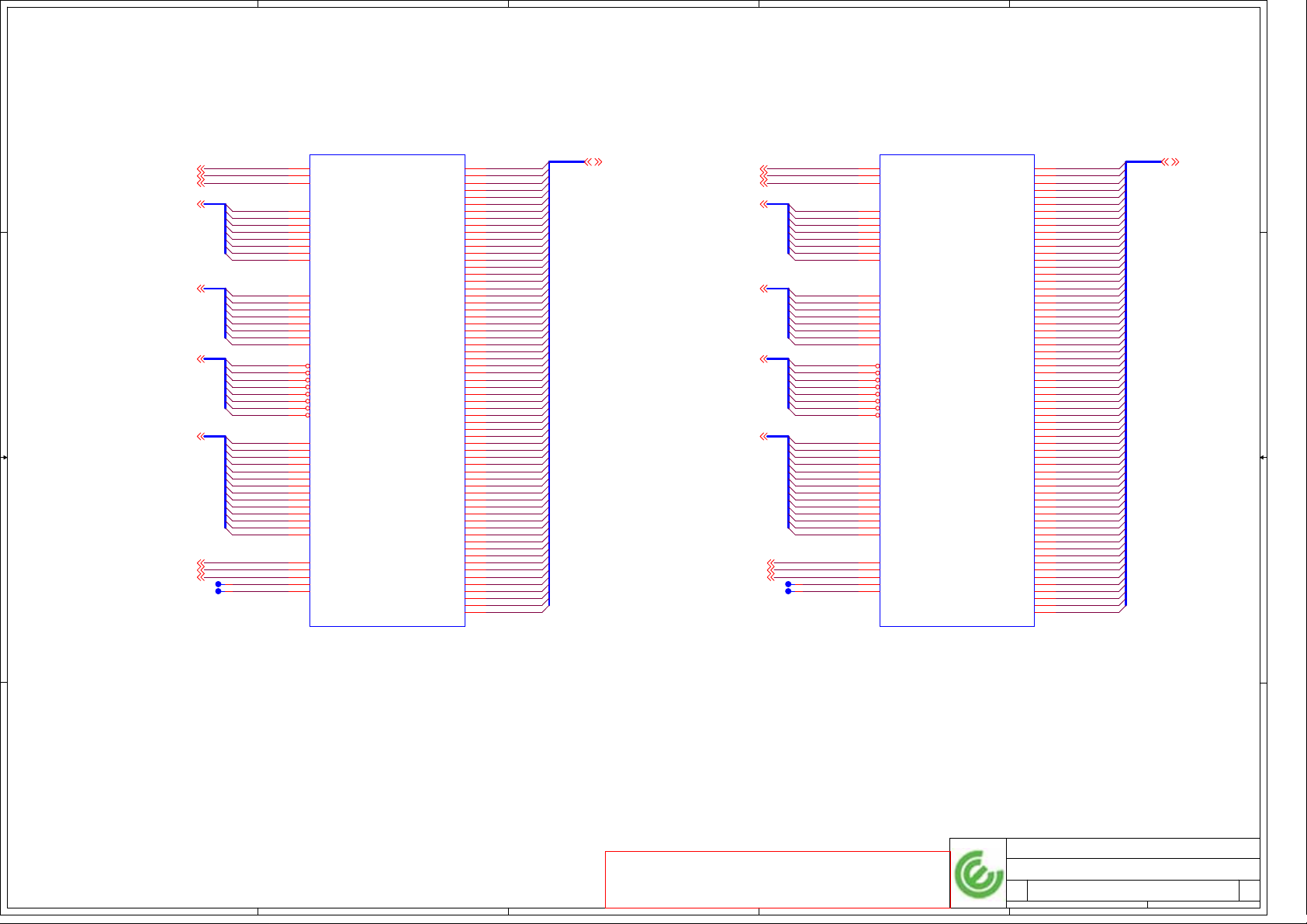

Table : ICS954305AK

0

1

1 2

R330

0_0402_5%~D

MCH_CLKSEL2 10 MCH_CLKSEL1 10

CLK_ICH_48M23

CLK_SMC_48M31

CLK_PCI_500439

CLK_PCI_501838

CLK_PCI_LOM28

CLK_PCI_PCM30

CLK_DOCKPCI_33M36

CLK_ICH_14M23

CLK_SIO_14M38

DREFCLK10

DREFCLK#10

CLK_PCI_ICH21

CLK_ENABLE#49

FCTSEL1 PIN43 PIN44 PIN47 PIN48

01DOT96T DOT96C 96/100M_T 96/100M_C

27M_out 27M SSout SRCT0 SRCC0

4

+3.3V_RUN

1 2

L40

BLM21PG600SN1D_0805~D

1

C326

0.1U_0402_16V4Z~D

CLK_SCLK 16,17

+CK_VDD_48+CK_VDD_A +CK_VDD_REF

1

2

C61

0.047U_0402_16V4Z~D

C329

27P_0402_50V8J~D

C333

27P_0402_50V8J~D

CLK_ICH_48M FSA

CLK_SMC_48M

CLK_PCI_5004

CLK_PCI_5018

CLK_PCI_LOM PCI_LOM

CLK_PCI_PCM PCI_PCM

FSB

2

1

1

2

2

C50

4.7U_0603_6.3V4Z~D

X2

14.31818MHz_20P_1BX14318CC1A~D

12

12

12

DREFCLK# DOT96#

CLK_PCI_ICH PCI_ICH

CLK_ENABLE#

1 2

R354

0_0402_5%~D

BLM21PG600SN1D_0805~D

C51

0.047U_0402_16V4Z~D

R298 12.1_0402_1%~D

R1589 12.1_0402_1%~D

R1619 12.1_0402_1%~D

R1438 12.1_0402_1%~D

R331 33_0402_5%~D

R302 33_0402_5%~D

R294 33_0402_5%~D

CLK_SIO_14M

FCTSEL1

12

10K_0402_5%~D

+CK_VDD_MAIN2

1 2

L32

1

2

C52

0.047U_0402_16V4Z~D

R32

470_0402_5%~D

1 2

12

1 2

12

12

12

12

12

1 2

R266 12.1_0402_1%~D

1 2

R250 12.1_0402_1%~D

1 2

R345 33_0402_5%~D

1 2

R356 33_0402_5%~D

R1582

+3.3V_RUN

33_0402_5%~D

12

R291

1 2

R362 475_0402_1%~D

R274

1_0603_5%~D

1 2

1 2

R273

2.2_0603_5%~D

CLK_XTAL_IN

CLK_XTAL_OUT

10K_0402_5%~D

Solder Thermal Pad to GND. Add min. 4 vias.

4

+CK_VDD_MAIN

FCTSEL1

DOCKPCI_33MCLK_DOCKPCI_33M

CLKREFCLK_ICH_14M

DOT96DREFCLK

R316

1 2

CLKIREF

CLK_SCLK

CLK_SDATA

3

+CK_VDD_MAIN

1

C402

10U_0805_10V4Z~D

2

1

C308

10U_0805_10V4Z~D

2

49

54

65

30

36

+CK_VDD_REF

+CK_VDD_48

FSB

FSC

12

18

40

20

19

41

45

23

34

33

32

27

22

43

44

37

39

16

17

15

21

31

35

42

68

73

74

75

76

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

1

2

1

2

U16

1

VDDSRC

VDDSRC

VDDSRC

VDDSRC

VDDPCI

VDDPCI

VDDCPU

VDDREF

VDD48

X1

X2

USB_48MHz/FSLA

FSLB/TEST_MODE

REF0/FSLC/TEST_SEL

PCICLK4/FCTSEL1

PCICLK3

PCICLK2

PCICLK1

REF1

DOTT_96MHz/27MHz

DOTC_96MHz/27MHz(SS)

ITP_EN/PCICLK_F0

Vtt_PwrGd#/PD

9

IREF

SMBCLK

SMBDAT

4

GNDSRC

GNDCPU

GNDREF

GNDPCI

GNDPCI

GND48

GNDSRC

THRM_PAD

THRM_PAD

THRM_PAD

THRM_PAD

SLG84450VTR_QFN72~D

C384

0.1U_0402_16V4Z~D

C344

0.1U_0402_16V4Z~D

R401

2.2_0603_5%~D

1 2

LCD100/96/SRC0_C

1

C58

0.1U_0402_16V4Z~D

2

1

C330

0.1U_0402_16V4Z~D

2

+CK_VDD_A

PCI_SRC_STOP#

CPU_STOP#

CPUT_ITP/SRCT10

CPUC_ITP/SRCC10

CLKREQ9#

CLKREQ8#

CLKREQ7#

CLKREQ6#

CLKREQ5#

CLKREQ4#

CLKREQ3#

CLKREQ2#

CLKREQ1#

LCD100/96/SRC0_T

VDDA

GNDA

CPUT1

CPUC1

CPUT0

CPUC0

SRCT9

SRCC9

SRCT8

SRCC8

SRCT7

SRCC7

SRCT6

SRCC6

SRCT5

SRCC5

SRCT4

SRCC4

SRCT3

SRCC3

SRCT2

SRCC2

SRCT1

SRCC1

1

C64

0.1U_0402_16V4Z~D

2

7

8

H_STP_PCI#

25

H_STP_CPU#

24

11

10

CPU_BCLK

14

13

CPU_ITP

6

CPU_ITP#

5

3

2

72

PCIE_SATA

70

PCIE_SATA#

69

71

66

67

38

PCIE_ICH

63

PCIE_ICH#

64

62

MCH_3GPLL

60

MCH_3GPLL#

61

29

58

59

57

55

56

28

PCIE_MINI2

52

PCIE_MINI2#

53

26

PCIE_MINI1

50

PCIE_MINI1#

51

46

DOT96_SSC

47

DOT96_SSC#

48

2

1

C389

0.1U_0402_16V4Z~D

2

1

C70

0.1U_0402_16V4Z~D

2

Place near each pin

W>40 mil

Place near CK410+

CLK_MCH_BCLKMCH_BCLK

CLK_MCH_BCLK#MCH_BCLK#

CLK_CPU_BCLK

CLK_CPU_BCLK#CPU_BCLK#

CLK_CPU_ITP

CLK_CPU_ITP#

CLK_MCH_3GPLL

CLK_MCH_3GPLL#

CLK_PCIE_SATA

CLK_PCIE_SATA#

CLK_PCIE_ICH

CLK_PCIE_ICH#

CLK_PCIE_LOMPCIE_LOM

CLK_PCIE_LOM#PCIE_LOM#

CLK_PCIE_MINI2

CLK_PCIE_MINI2#

CLK_PCIE_MINI1

CLK_PCIE_MINI1#

1 2

R348 33_0402_5%~D

1 2

R359 33_0402_5%~D

1 2

R321 33_0402_5%~D

1 2

R337 33_0402_5%~D

1 2

R368 33_0402_5%~D

1 2

R376 33_0402_5%~D

1 2

R394 33_0402_5%~D

1 2

R400 33_0402_5%~D

R292 10K_0402_5%~D

1 2

1 2

R366 33_0402_5%~D

1 2

R375 33_0402_5%~D

1 2

R1761 10K_0402_5%~D@

1 2

R397 33_0402_5%~D

1 2

R402 33_0402_5%~D

R299 10K_0402_5%~D

1 2

1 2

R1435 33_0402_5%~D

1 2

R1436 33_0402_5%~D

1 2

R1762 10K_0402_5%~D

1 2

R1393 33_0402_5%~D

1 2

R1394 33_0402_5%~D

R1395 10K_0402_5%~D

1 2

1 2

R1638 33_0402_5%~D

1 2

R1639 33_0402_5%~D

1 2

R1640 10K_0402_5%~D

1 2

R524 33_0402_5%~D

1 2

R525 33_0402_5%~D

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

2

Date: Sheet

H_STP_PCI# 23

H_STP_CPU# 23

CLK_MCH_BCLK 10

CLK_MCH_BCLK# 10

CLK_CPU_BCLK 7

CLK_CPU_BCLK# 7

CLK_CPU_ITP 7

CLK_CPU_ITP# 7

CLK_PCIE_SATA 22

CLK_PCIE_SATA# 22

SATA_CLKREQ# 23

+3.3V_RUN

CLK_PCIE_ICH 23

CLK_PCIE_ICH# 23

+3.3V_RUN

CLK_MCH_3GPLL 10

CLK_MCH_3GPLL# 10

CLK_3GPLLREQ# 10

+3.3V_RUN

CLK_PCIE_LOM 28

CLK_PCIE_LOM# 28

LOM_CLKREQ# 28

+3.3V_RUN

CLK_PCIE_MINI2 34

CLK_PCIE_MINI2# 34

MINI2CLK_REQ# 34

+3.3V_RUN

CLK_PCIE_MINI1 34

CLK_PCIE_MINI1# 34

MINI1CLK_REQ# 34

+3.3V_RUN

DREF_SSCLK 10

DREF_SSCLK# 10

1

CLK_CPU_ITP

CLK_CPU_ITP#

CLK_MCH_BCLK

CLK_MCH_BCLK#

CLK_CPU_BCLK

CLK_CPU_BCLK#

CLK_MCH_3GPLL

CLK_MCH_3GPLL#

CLK_PCIE_SATA

CLK_PCIE_SATA#

CLK_PCIE_ICH

CLK_PCIE_ICH#

CLK_PCIE_LOM

CLK_PCIE_LOM#

DREFCLK

DREFCLK#

DREF_SSCLK

DREF_SSCLK#

CLK_PCIE_MINI2

CLK_PCIE_MINI2#

CLK_PCIE_MINI1

CLK_PCIE_MINI1#

R369 49.9_0402_1%~D

R377 49.9_0402_1%~D

R349 49.9_0402_1%~D

R360 49.9_0402_1%~D

R322 49.9_0402_1%~D

R338 49.9_0402_1%~D

1 2

R392 49.9_0402_1%~D

1 2

R403 49.9_0402_1%~D

1 2

R381 49.9_0402_1%~D

1 2

R385 49.9_0402_1%~D

1 2

R365 49.9_0402_1%~D

1 2

R374 49.9_0402_1%~D

1 2

R393 49.9_0402_1%~D

1 2

R399 49.9_0402_1%~D

1 2

R344 49.9_0402_1%~D

1 2

R355 49.9_0402_1%~D

1 2

R522 49.9_0402_1%~D

1 2

R523 49.9_0402_1%~D

1 2

R544 49.9_0402_1%~D

1 2

R545 49.9_0402_1%~D

1 2

R1641 49.9_0402_1%~D

1 2

R1642 49.9_0402_1%~D

Compal Electronics, Inc.

Clock Generator

LA-2791

663Tuesday, Feb ru ar y 07, 2006

1

12

12

12

12

12

12

0.6

of

Page 7

5

4

3

2

1

H_A#[3..31]10

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

D D

H_REQ#[0..4]10

H_ADSTB#010

H_RS#[0..2]10

H_ADSTB#110

CLK_CPU_BCLK6

CLK_CPU_BCLK#6

H_ADS#10

H_BNR#10

H_BPRI#10

H_BR0#10

H_DEFER#10

H_DRDY#10

H_HIT#10

H_HITM#10

H_LOCK#10

H_RESET#10

H_TRDY#10

ITP_DBRESET#23,39

H_DBSY#10

H_DPSLP#22

H_DPRSTP#22,49

H_DPWR#10

CPU_PROCHOT#38

H_PWRGOOD22

H_CPUSLP#10,22

R1387

@

1K_0603_1%~D

R1378

51_0603_1%~D

H_THERMTRIP#18

12

12

C C

R422

56_0402_5%~D

+1.05V_VCCP

B B

Pop R1378 required by

Intel for B0 Yonah.

Backward compatible for

A0 and A1 Yonah

H_THERMDA18

H_THERMDC18

H_THERMDA, H_THERMDC routing together.

Trace width / Spacing = 10 / 10 mil

A A

1 2

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_ADSTB#1

CLK_CPU_BCLK

CLK_CPU_BCLK#

H_ADS#

H_BNR#

H_BPRI#

H_BR0#

H_DEFER#

H_DRDY#

H_HIT#

H_HITM#

H_IERR#

H_LOCK#

H_RESET#

H_RS#0

H_RS#1

H_RS#2

H_TRDY#

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_DBRESET#

H_DBSY#

H_DPSLP#

H_DPRSTP#

H_DPWR#

ITP_BPM#4

ITP_BPM#5

H_CPUSLP#

ITP_TCK

ITP_TDI

ITP_TDO

TEST1

TEST2

ITP_TMS

ITP_TRST#

H_THERMDA

H_THERMDC

H_THERMTRIP#

JCPUA

J4

A3#

L4

A4#

M3

A5#

K5

A6#

M1

A7#

N2

A8#

J1

A9#

N3

A10#

P5

A11#

P2

A12#

L1

A13#

P4

A14#

P1

A15#

R1

A16#

Y2

A17#

U5

A18#

R3

A19#

W6

A20#

U4

A21#

Y5

A22#

U2

A23#

R4

A24#

T5

ADDR GROUP

A25#

T3

A26#

W3

A27#

W5

A28#

Y4

A29#

W2

A30#

Y1

A31#

K3

REQ0#

H2

REQ1#

K2

REQ2#

J3

REQ3#

L5

REQ4#

L2

ADSTB0#

V4

ADSTB1#

A22

BCLK0

A21

H1

E2

G5

F1

H5

F21

G6

E4

D20

H4

B1

F3

F4

G3

G2

AD4

AD3

AD1

AC4

C20

E1

B5

E5

D24

AC2

AC1

D21

D6

D7

AC5

AA6

AB3

C26

D25

AB5

AB6

A24

A25

C7

HOST CLK

BCLK1

ADS#

BNR#

BPRI#

BR0#

DEFER#

DRDY#

HIT#

CONTROL

HITM#

IERR#

LOCK#

RESET#

RS0#

RS1#

RS2#

TRDY#

BPM0#

BPM1#

BPM2#

BPM3#

DBR#

DBSY#

DPSLP#

DPRSTP#

DPWR#

PRDY#

PREQ#

PROCHOT#

PWRGOOD

SLP#

TCK

TDI

TDO

TEST1

TEST2

TMS

TRST#

THERMAL

THERMDA

DIODE

THERMDC

THERMTRIP#

TYCO_1-1674770-2_Yonah~D

+1.05V_VCCP

YONAH

MISC

DATA GROUP

LEGACY CPU

R398

56_0402_5%~D

1 2

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DINV0#

DINV1#

DINV2#

DINV3#

DSTBN0#

DSTBN1#

DSTBN2#

DSTBN3#

DSTBP0#

DSTBP1#

DSTBP2#

DSTBP3#

A20M#

FERR#

IGNNE#

INIT#

LINT0

LINT1

STPCLK#

SMI#

H_THERMTRIP#

E22

F24

E26

H22

F23

G25

E25

E23

K24

G24

J24

J23

H26

F26

K22

H25

N22

K25

P26

R23

L25

L22

L23

M23

P25

P22

P23

T24

R24

L26

T25

N24

AA23

AB24

V24

V26

W25

U23

U25

U22

AB25

W22

Y23

AA26

Y26

Y22

AC26

AA24

AC22

AC23

AB22

AA21

AB21

AC25

AD20

AE22

AF23

AD24

AE21

AD21

AE25

AF25

AF22

AF26

J26

M26

V23

AC20

H23

M24

W24

AD23

G22

N25

Y25

AE24

A6

A5

C4

B3

C6

B4

D5

A3

H_D#0H_A#3

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20H_A#23

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_A20M#

H_FERR#

H_IGNNE#

H_INIT#

H_INTR

H_NMI

H_STPCLK#

H_SMI#

H_DINV#0 10

H_DINV#1 10

H_DINV#2 10

H_DINV#3 10

H_A20M# 22

H_FERR# 22

H_IGNNE# 22

H_INIT# 22

H_INTR 22

H_NMI 22

H_STPCLK# 22

H_SMI# 22

H_D#[0..63] 10

ITP_TDO

H_DSTBN#[0..3] 10

H_DSTBP#[0..3] 10

H_RESET#

R434

22.6_0402_1%~D

1 2

1

C71

2

@

1

C72

2

@

0.01U_0402_16V7K~D

0.01U_0402_16V7K~D

R424

22.6_0402_1%~D

1 2

CLK_CPU_ITP6

CLK_CPU_ITP#6

+1.05V_VCCP

ITP_DBRESET#

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_BPM#4

ITP_BPM#5

ITP_TCK

CLK_CPU_ITP

CLK_CPU_ITP#

ITP_TCK

ITP_TRST#

ITP_TMS

ITP_TDI

29

JITP

29

28

VTT1

27

VTT0

26

VTAP

25

DBR#

24

DBA#

23

BPM0#

22

GND5

21

BPM1#

20

GND4

19

BPM2#

18

GND3

17

BPM3#

16

GND2

15

BPM4#

14

GND1

13

BPM5#

12

RESET#

11

FBO

10

GND0

9

BCLKP

8

BCLKN

7

TDO

6

NC2

5

TCK

4

NC1

3

TRST#

2

TMS

1

TDI

30

MOLEX_52435-2891_28P~D@

30

+3.3V_SUS

+1.05V_VCCP

+1.05V_VCCP

R367

150_0402_1%~D

1 2

R415

51_0402_5%~D

1 2

R416

51_0402_5%~D

1 2

R33

54.9_0402_1%~D

1 2

R387

39.2_0402_1%~D

1 2

R417

150_0402_5%~D

1 2

This shall place near CPU

R391

680_0402_5%~D

1 2

R436

27.4_0402_1%~D

1 2

ITP_DBRESET#

ITP_TDO

H_RESET#

ITP_BPM#5

ITP_TMS

ITP_TDI

ITP_TRST#

ITP_TCK

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Yonah in mFCPGA479

LA-2791

763Tuesday, Feb ru ar y 07, 2006

1

0.6

of

Page 8

5

4

3

2

1

Length match within 25 mils

+VCC_CORE

W21

AD26

AB20

AA20

AF20

AE20

AB18

AB17

AA18

AA17

AD18

AD17

AC18

AC17

AF18

AF17

AF7

AE7

B26

K21

J21

M21

N21

T21

R21

V21

G21

AE6

AD6

AF5

AE5

AF4

AE3

AF2

AE2

B22

B23

C21

R26

U26

AF1

D22

C23

C24

AA1

AA4

AB2

AA3

T22

B25

K6

J6

M6

N6

T6

R6

V6

U1

V1

E7

D2

F6

D3

C1

M4

N5

T2

V3

B2

C3

JCPUB

VCCSENSE

VSSSENSE

VCCA

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

PSI#

VID0

VID1

VID2

VID3

VID4

VID5

VID6

GTLREF

BSEL0

BSEL1

BSEL2

COMP0

COMP1

COMP2

COMP3

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

YONAH

TYCO_1-1674770-2_Yonah~D

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

POWER, GROUNG, RESERVED SIGNALS AND NC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AB26

AA25

AD25

AE26

AB23

AC24

AF24

AE23

AA22

AD22

AC21

AF21

AB19

AA19

AD19

AC19

AF19

AE19

AB16

AA16

AD16

AC16

AF16

AE16

AB13

AA14

AD13

AC14

AF13

AE14

AB11

AA11

AD11

AC11

AF11

AE11

AB8

AA8

AD8

AC8

AF8

AE8

AA5

AD5

AC6

AF6

AB4

AC3

AF3

AE4

AB1

AA2

AD2

AE1

B6

C5

F5

E6

H6

J5

M5

L6

P6

R5

V5

U6

Y6

A4

D4

E3

H3

G4

K4

L3

P3

N4

T4

U3

Y3

W4

D1

C2

F2

G1

+1.05V_VCCP

+VCC_CORE

VCCSENSE

VSSSENSE

H_PSI#

CPU_BSEL0

CPU_BSEL1

CPU_BSEL2

VID0

VID1

VID2

VID3

VID4

VID5

VID6

COMP0

COMP1

COMP2

COMP3

VCCSENSE49

VSSSENSE49

+1.5V_RUN

D D

+1.05V_VCCP

R_A

12

V_CPU_GTLREF

R140

1K_0402_1%~D

R_B

12

R147

2K_0402_1%~D

Layout close CPU PIN AD26

0.5 inch (max)

C C

B B

+VCC_CORE

R555

100_0402_1%~D

1 2

R556

100_0402_1%~D

1 2

VCCSENSE

VSSSENSE

Layout close CPU

12

R129

R124

27.4_0402_1%~D

CPU_BSEL CPU_BSEL2 CPU_BSEL1

133

166

00

0

12

12

R465

27.4_0402_1%~D

54.9_0402_1%~D

1

Resistor placed within

0.5" of CPU pin.Trace

should be at least 25

12

mils away from any

other toggling signal.

R457

54.9_0402_1%~D

CPU_BSEL0

1

1

1

1

C87

C88

2

2

10U_0805_4VAM~D

0.01U_0402_16V7K~D

H_PSI#49

VID049

VID149

VID249

VID349

VID449

VID549

VID649

V_CPU_GTLREF

CPU_BSEL010

CPU_BSEL16

CPU_BSEL26

AE18

AE17

AB15

AA15

AD15

AC15

AF15

AE15

AB14

AA13

AD14

AC13

AF14

AE13

AB12

AA12

AD12

AC12

AF12

AE12

AB10

AA10

AD10

AC10

AF10

AE10

JCPUC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AB9

VCC

VCC

AA9

VCC

VCC

AD9

VCC

VCC

AC9

VCC

VCC

AF9

VCC

VCC

AE9

VCC

AB7

VCC

AA7

VCC

AD7

VCC

AC7

VCC

B20

VCC

A20

VCC

F20

VCC

E20

VCC

B18

VCC

B17

VCC

A18

VCC

A17

VCC

D18

VCC

D17

VCC

C18

VCC

C17

VCC

F18

VCC

F17

VCC

E18

VCC

E17

VCC

B15

VCC

A15

VCC

D15

VCC

C15

VCC

F15

VCC

E15

VCC

B14

VCC

A13

VCC

D14

VCC

C13

VCC

F14

VCC

E13

VCC

B12

VCC

A12

VCC

D12

VCC

C12

VCC

F12

VCC

E12

VCC

B10

VCC

B9

VCC

A10

VCC

A9

VCC

D10

VCC

D9

VCC

C10

VCC

C9

VCC

F10

VCC

F9

VCC

E10

VCC

E9

VCC

B7

VCC

A7

VCC

F7

VCC

YONAH

POWER, GROUND

TYCO_1-1674770-2_Yonah~D

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

K1

J2

M2

N1

T1

R2

V2

W1

A26

D26

C25

F25

B24

A23

D23

E24

B21

C22

F22

E21

B19

A19

D19

C19

F19

E19

B16

A16

D16

C16

F16

E16

B13

A14

D13

C14

F13

E14

B11

A11

D11

C11

F11

E11

B8

A8

D8

C8

F8

E8

G26

K26

J25

M25

N26

T26

R25

V25

W26

H24

G23

K23

L24

P24

N23

T23

U24

Y24

W23

H21

J22

M22

L21

P21

R22

V22

U21

Y21

A A

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Yonah in mFCPGA479

LA-2791

1

863Tuesday, Feb ru ar y 07, 2006

0.6

of

Page 9

5

+VCC_CORE

Place these inside

socket cavity on L8

(North side

Secondary)

D D

Place these inside

socket cavity on L8

(Sorth side

Secondary)

Place these inside

socket cavity on L8

(North side

Primary)

Place these inside

socket cavity on L8

(Sorth side

Primary)

C C

1

2

+VCC_CORE

1

2

+VCC_CORE

1

2

+VCC_CORE

1

2

C100

10U_0805_4VAM~D

C428

10U_0805_4VAM~D

C468

10U_0805_4VAM~D

C448

10U_0805_4VAM~D

1

C429

10U_0805_4VAM~D

2

1

C138

10U_0805_4VAM~D

2

1

C140

10U_0805_4VAM~D

2

1

C432

10U_0805_4VAM~D

2

1

C98

10U_0805_4VAM~D

2

1

C447

10U_0805_4VAM~D

2

1

C139

10U_0805_4VAM~D

2

1

C426

10U_0805_4VAM~D

2

1

C430

10U_0805_4VAM~D

2

1

C470

10U_0805_4VAM~D

2

1

C446

10U_0805_4VAM~D

2

1

C427

10U_0805_4VAM~D

2

4

1

2

1

2

1

2

1

2

C99

10U_0805_4VAM~D

C469

10U_0805_4VAM~D

C466

10U_0805_4VAM~D

C431

10U_0805_4VAM~D

1

C472

10U_0805_4VAM~D

2

1

C467

10U_0805_4VAM~D

2

1

C137

10U_0805_4VAM~D

2

1

C120

10U_0805_4VAM~D

2

3

1

C473

10U_0805_4VAM~D

2

1

C471

10U_0805_4VAM~D

2

1

C119

10U_0805_4VAM~D

2

1

C97

10U_0805_4VAM~D

2

22uF 0805 X5R -> 85 degree C

1

C142

10U_0805_4VAM~D

2

1

C102

10U_0805_4VAM~D

2

1

2

1

2

10uF 0805 X5R -> 85 degree C

C141

10U_0805_4VAM~D

C433

10U_0805_4VAM~D

2

1

High Frequence Decoupling

Near VCORE regulator.

+VCC_CORE

South Side Secondary

C352

B B

+1.05V_VCCP

1

C372

@

2

CRB was 270uF

A A

330U_D2E_2.5VM_R9~D

330U_D_2.5VM_R6M~D

7mOhm

PS CAP

+

1

+

2

1

+

C496

2

330U_D_2.5VM_R6M~D

7mOhm

PS CAP

1

C415

0.1U_0402_10V7K~D

2

C354

@

330U_D_2.5VM_R6M~D

7mOhm

PS CAP

1

+

2

1

2

1

+

C618

C497

2

@

330U_D_2.5VM_R6M~D

330U_D_2.5VM_R6M~D

7mOhm

7mOhm

PS CAP

PS CAP

C439

0.1U_0402_10V7K~D

1

+

C365

2

7mOhm

PS CAP

1

C451

0.1U_0402_10V7K~D

2

North Side Secondary

1

+

2

330U_D_2.5VM_R6M~D

1

2

C416

0.1U_0402_10V7K~D

ESR <= 1.5m ohm

Capacitor > 1980uF

1

C462

0.1U_0402_10V7K~D

2

1

C414

0.1U_0402_10V7K~D

2

The caps need change to ESR=6m ohms

Place these inside

socket cavity on L8

(North side

Secondary)

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

CPU Bypass

LA-2791

963Tuesday, Feb ru ar y 07, 2006

1

0.6

of

Page 10

5

4

3

2

1

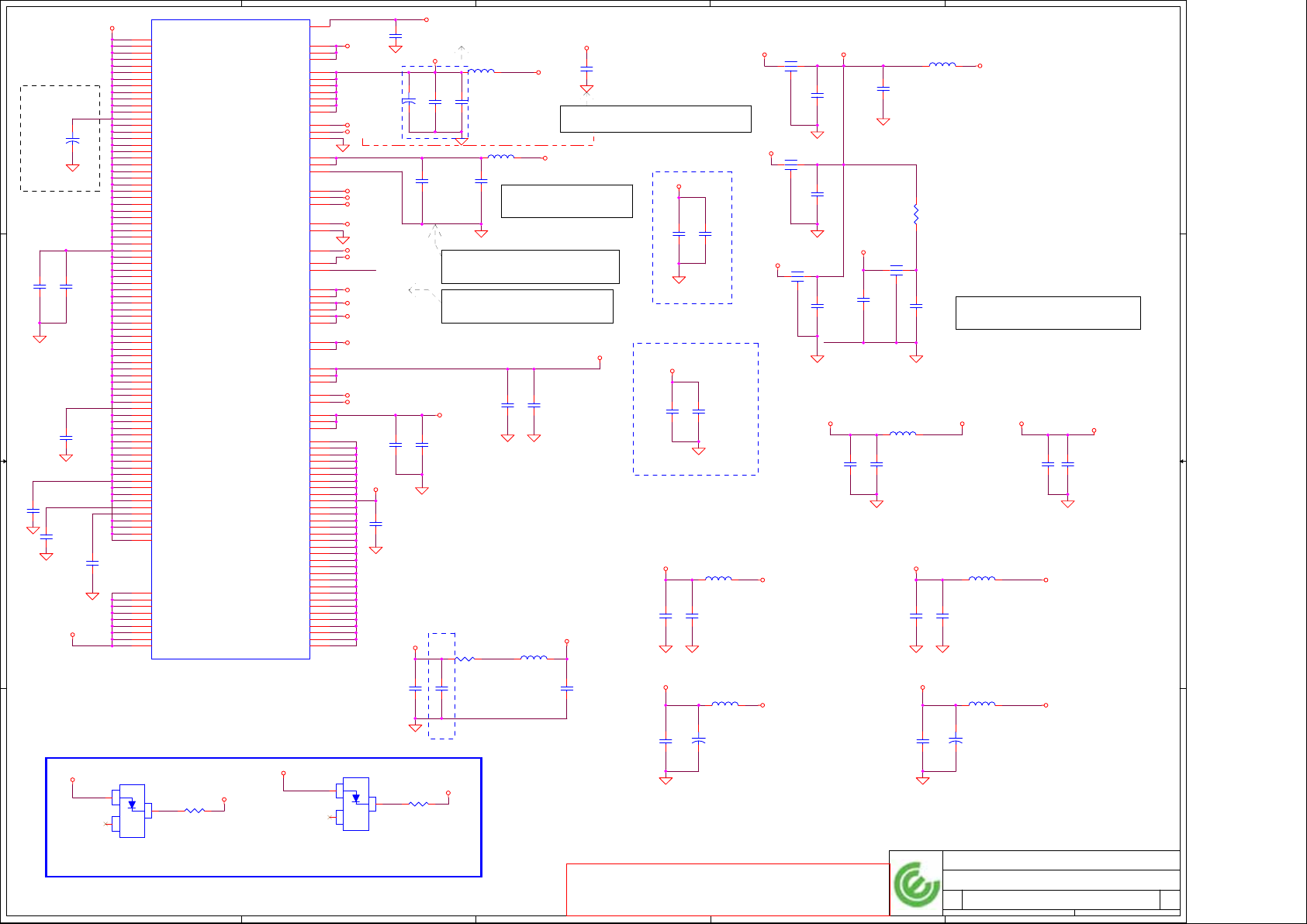

Description at page12

Note :

CFG3:17 has

internal pullup,

+1.05V_VCCP

U40B

AE35

DMIRXN0

AF39

DMIRXN1

AG35

DMIRXN2

AH39

DMIRXN3

AC35

DMIRXP0

AE39

DMIRXP1

AF35

DMIRXP2

AG39

DMIRXP3

AE37

DMITXN0

AF41

DMITXN1

AG37

DMITXN2

AH41

DMITXN3

AC37

DMITXP0

AE41

DMITXP1

AF37

DMITXP2

AG41

DMITXP3

AY35

SM_CK0

AR1

SM_CK1

AW7

SM_CK2

AW40

SM_CK3

AW35

SM_CK0#

AT1

SM_CK1#

AY7

SM_CK2#

AY40

SM_CK3#

AU20

SM_CKE0

AT20

SM_CKE1

BA29

SM_CKE2

AY29

SM_CKE3

AW13

SM_CS0#

AW12

SM_CS1#

AY21

SM_CS2#

AW21

SM_CS3#

AL20

SM_OCDCOMP0

AF10

SM_OCDCOMP1

BA13

SM_ODT0

BA12

SM_ODT1

AY20

SM_ODT2

AU21

SM_ODT3

AV9

SM_RCOMPN

AT9

SM_RCOMPP

AK1

SM_VREF0

AK41

SM_VREF1

G28

PM_BMBUSY#

F25

PM_EXTTS0#

H26

PM_EXTTS1#

G6

PM_THERMTRIP#

AH33

PWROK

AH34

RSTIN#

K28

ICH_SYNC#

CALISTOGA A0 _ FCBGA1466~D

Layout Note:

Route as short

as possible

12

R435

R437

@

@

40.2_0402_1%~D

40.2_0402_1%~D

2

12

+1.05V_VCCP

+1.05V_VCCP

R325

12

R85

H_SWNG1

221_0402_1%~D

12

1

R86

2

C65

100_0402_1%~D

0.1U_0402_16V4Z~D

12

R64

H_SWNG0

221_0402_1%~D

12

1

R65

2

C48

100_0402_1%~D

0.1U_0402_16V4Z~D

12

R326

H_VREF

100_0402_1%~D

12

1

C363

2

200_0402_1%~D

V_DDR_MCH_REF16,17,48

+1.8V_SUS

0.1U_0402_16V4Z~D

DMI_MRX_ITX_N023

DMI_MRX_ITX_N123

DMI_MRX_ITX_N223

DMI_MRX_ITX_N323

DMI_MRX_ITX_P023

DMI_MRX_ITX_P123

DMI_MRX_ITX_P223

DMI_MRX_ITX_P323

DMI_MTX_IRX_N023

DMI_MTX_IRX_N123

DMI_MTX_IRX_N223

DMI_MTX_IRX_N323

DMI_MTX_IRX_P023

DMI_MTX_IRX_P123

DMI_MTX_IRX_P223

DMI_MTX_IRX_P323

M_CLK_DDR016

M_CLK_DDR116

M_CLK_DDR217

M_CLK_DDR317

M_CLK_DDR#016

M_CLK_DDR#116

M_CLK_DDR#217

M_CLK_DDR#317

DDR_CKE0_DIMMA16

DDR_CKE1_DIMMA16

DDR_CKE2_DIMMB17

DDR_CKE3_DIMMB17

DDR_CS0_DIMMA#16

DDR_CS1_DIMMA#16

DDR_CS2_DIMMB#17

DDR_CS3_DIMMB#17

R142 80.6_0402_1%~D

1 2

1 2

R141 80.6_0402_1%~D

MCH_ICH_SYNC#21

V_DDR_MCH_REF

PM_BMBUSY#23

PM_EXTTS#016

PM_EXTTS#123

THERMTRIP_MCH#18

ICH_PWRGD23,42

PLTRST#21,23,28,34,52

V_DDR_MCH_REF

1

C425

2

@

0.1U_0402_16V4Z~D

M_ODT016

M_ODT116

M_ODT217

M_ODT317

DMI_MRX_ITX_N0

DMI_MRX_ITX_N1

DMI_MRX_ITX_N2

DMI_MRX_ITX_N3

DMI_MRX_ITX_P0

DMI_MRX_ITX_P1

DMI_MRX_ITX_P2

DMI_MRX_ITX_P3

DMI_MTX_IRX_N0

DMI_MTX_IRX_N1

DMI_MTX_IRX_N2

DMI_MTX_IRX_N3

DMI_MTX_IRX_P0

DMI_MTX_IRX_P1

DMI_MTX_IRX_P2

DMI_MTX_IRX_P3

M_CLK_DDR0

M_CLK_DDR1

M_CLK_DDR2

M_CLK_DDR3

M_CLK_DDR#0

M_CLK_DDR#1

M_CLK_DDR#2

M_CLK_DDR#3

DDR_CKE0_DIMMA

DDR_CKE1_DIMMA

DDR_CKE2_DIMMB

DDR_CKE3_DIMMB

DDR_CS0_DIMMA#

DDR_CS1_DIMMA#

DDR_CS2_DIMMB#

DDR_CS3_DIMMB#

M_OCDOCMP0

M_OCDOCMP1

M_ODT0

M_ODT1

M_ODT2

M_ODT3

SMRCOMPN

SMRCOMPP

PM_EXTTS#0

PM_EXTTS#1

ICH_PWRGD

PLTRST_R#

12

R441100_0402_1%~D

Stuff R435 & R4 37 for A1 Calistoga

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

D D

H_D#[0..63]7

C C

+1.05V_VCCP

12

12

B B

R80

R52

54.9_0402_1%~D

54.9_0402_1%~D

12

12

R57

24.9_0402_1%~D

A A

Layout Note:

H_XRCOMP & H_YRCOMP trace width

and spacing is 10/20

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_VREF

H_XRCOMP

H_XSCOMP

H_YRCOMP

H_YSCOMP

H_SWNG0

H_SWNG1

R90

24.9_0402_1%~D

5

U40A

F1

HD0#

J1

HD1#

H1

HD2#

J6

HD3#

H3

HD4#

K2

HD5#

G1

HD6#

G2

HD7#

K9

HD8#

K1

HD9#

K7

HD10#

J8

HD11#

H4

HD12#

J3

HD13#

K11

HD14#

G4

HD15#

T10

HD16#

W11

HD17#

T3

HD18#

U7

HD19#

U9

HD20#

U11

HD21#

T11

HD22#

W9

HD23#

T1

HD24#

T8

HD25#

T4

HD26#

W7

HD27#

U5

HD28#

T9

HD29#

W6

HD30#

T5

HD31#

AB7

HD32#

AA9

HD33#

W4

HD34#

W3

HD35#

Y3

HD36#

Y7

HD37#

W5

HD38#

Y10

HD39#

AB8

HD40#

W2

HD41#

AA4

HD42#

AA7

HD43#

AA2

HD44#

AA6

HD45#

AA10

HD46#

Y8

HD47#

AA1

HD48#

AB4

HD49#

AC9

HD50#

AB11

HD51#

AC11

HD52#

AB3

HD53#

AC2

HD54#

AD1

HD55#

AD9

HD56#

AC1

HD57#

AD7

HD58#

AC6

HD59#

AB5

HD60#

AD10

HD61#

AD4

HD62#

AC8

HD63#

J13

HVREF0

K13

HVREF1

E1

HXRCOMP

E2

HXSCOMP

Y1

HYRCOMP

U1

HYSCOMP

E4

HXSWING

W1

HYSWING

CALISTOGA A0 _ FCBGA1466~D

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HADSTB#0

HADSTB#1

HOST

HCLKN

HCLKP

HDSTBN#0

HDSTBN#1

HDSTBN#2

HDSTBN#3

HDSTBP#0

HDSTBP#1

HDSTBP#2

HDSTBP#3

HDINV#0

HDINV#1

HDINV#2

HDINV#3

HCPURST#

HADS#

HTRDY#

HDPWR#

HDRDY#

HDEFER#

HHITM#

HHIT#

HLOCK#

HBREQ0#

HBNR#

HBPRI#

HDBSY#

HCPUSLP#

HRS0#

HRS1#

HRS2#

H9

C9

E11

G11

F11

G12

F9

H11

J12

G14

D9

J14

H13

J15

F14

D12

A11

C11

A12

A13

E13

G13

F12

B12

B14

C12

A14

C14

D14

D8

G8

B8

F8

A8

B9

C13

AG1

AG2

K4

T7

Y5

AC4

K3

T6

AA5

AC5

J7

W8

U3

AB10

B7

E8

E7

J9

H8

C3

D4

D3

B3

C7

C6

F6

A7

E3

B4

E6

D6

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_ADSTB#1

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_RESET#

H_ADS#

H_TRDY#

H_DRDY#

H_DEFER#

H_HITM#

H_HIT#

H_LOCK#

H_BR0#

H_BNR#

H_BPRI#

H_DBSY#

H_CPUSLP#

H_RS#0

H_RS#1

H_RS#2

4

H_A#[3..31] 7

H_REQ#[0..4] 7

H_ADSTB#0 7

H_ADSTB#1 7

CLK_MCH_BCLK# 6

CLK_MCH_BCLK 6

H_DSTBN#[0..3] 7

H_DSTBP#[0..3] 7

H_DINV#0 7

H_DINV#1 7

H_DINV#2 7

H_DINV#3 7

H_RESET# 7

H_ADS# 7

H_TRDY# 7

H_DPWR# 7

H_DRDY# 7

H_DEFER# 7

H_HITM# 7

H_HIT# 7

H_LOCK# 7

H_BR0# 7

H_BNR# 7

H_BPRI# 7

H_DBSY# 7

H_CPUSLP# 7,22

H_RS#[0..2] 7

CFG18:19 has

internal pulldown

DMI

DDR MUXING

PM

M_OCDOCMP0

M_OCDOCMP1

CPU_BSEL0

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG

CFG18

CFG19

CFG20

G_CLKP

G_CLKN

D_REF_CLKN

D_REF_CLKP

CLKNC

D_REF_SSCLKN

D_REF_SSCLKP

CLK_REQ#

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

RESERVED6

RESERVED7

RESERVED8

RESERVED9

RESERVED10

RESERVED11

RESERVED12

RESERVED13

RESERVED

PM_EXTTS#0

PM_EXTTS#1

THERMTRIP_MCH#

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

NC0

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC14

NC15

NC16

NC17

NC18

K16

K18

J18

F18

E15

F15

E18

D19

D16

G16

E16

D15

G15

K15

C15

H16

G18

H15

J25

K27

J26

AG33

AF33

A27

A26

C40

D41

H32

A3

A39

A4

A40

AW1

AW41

AY1

BA1

BA2

BA3

BA39

BA40

BA41

C1

AY41

B2

B41

C41

D1

T32

R32

F3

F7

AG11

AF11

H7

J19

A41

A34

D28

D27

A35

10K_0402_5%~D

@

MCH_CLKSEL1

MCH_CLKSEL2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

R336

R253

10K_0402_5%~D

R335

75_0402_5%~D

1 2

CLK_MCH_3GPLL# 6

+3.3V_RUN_R

12

12

CPU_BSEL0 8

MCH_CLKSEL1 6

MCH_CLKSEL2 6

T34PAD~D

T35PAD~D

CFG5 12

CFG6 12

CFG7 12

T41PAD~D

CFG9 12

T42PAD~D

CFG11 12

CFG12 12

CFG13 12

T43PAD~D

T44PAD~D

CFG16 12

T45PAD~D

CFG18 12

CFG19 12

CFG20 12

CLK_MCH_3GPLL 6

DREFCLK# 6

DREFCLK 6

DREF_SSCLK# 6

DREF_SSCLK 6

CLK_3GPLLREQ# 6

+1.05V_VCCP

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Calistoga(1 of 6)

LA-2791

1

10 63Tuesday, Feb ru ar y 07, 2006

of

0.6

Page 11

5

4

3

2

1

D D

DDR_A_BS016

DDR_A_BS116

DDR_A_BS216 DDR_B_BS217

DDR_A_DM[0..7]16

DDR_A_DQS[0..7]16

C C

B B

DDR_A_DQS#[0..7]16

DDR_A_MA[0..13]16

DDR_A_CAS#16

DDR_A_RAS#16

DDR_A_WE#16

T2022 PAD~D

DDR_A_BS0

DDR_A_BS1

DDR_A_BS2

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11 DDR_B_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_CAS#

DDR_A_RAS#

DDR_A_WE#

SA_RCVENIN#

SA_RCVENOUT#

AU12

AV14

BA20

AJ33

AM35

AL26

AN22

AM14

AK33

AT33

AN28

AM22

AN12

AK32

AU33

AN27

AM21

AM12

AY16

AU14

AW16

BA16

BA17

AU16

AV17

AU17

AW17

AT16

AU13

AT17

AV20

AV12

AY13

AW14

AY14

AK23

AK24

AR3

AH4

AN8

AP3

AG5

AL8

AN3

AH5

AL9

SA_BS0

SA_BS1

SA_BS2

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS0#

SA_DQS1#

SA_DQS2#

SA_DQS3#

SA_DQS4#

SA_DQS5#

SA_DQS6#

SA_DQS7#

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_CAS#

SA_RAS#

SA_WE#

SA_RCVENIN#

SA_RCVENOUT#

DDR SYS MEMORY A

CALISTOGA A0 _ FCBGA1466~D

D

U40D

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

AJ35

AJ34

AM31

AM33

AJ36

AK35

AJ32

AH31

AN35

AP33

AR31

AP31

AN38

AM36

AM34

AN33

AK26

AL27

AM26

AN24

AK28

AL28

AM24

AP26

AP23

AL22

AP21

AN20

AL23

AP24

AP20

AT21

AR12

AR14

AP13

AP12

AT13

AT12

AL14

AL12

AK9

AN7

AK8

AK7

AP9

AN9

AT5

AL5

AY2

AW2

AP1

AN2

AV2

AT3

AN1

AL2

AG7

AF9

AG4

AF6

AG9

AH6

AF4

AF8

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_B_DM[0..7]17

DDR_B_DQS[0..7]17

DDR_B_DQS#[0..7]17

DDR_B_MA[0..13]17

DDR_B_BS017

DDR_B_BS117

DDR_B_CAS#17

DDR_B_RAS#17

DDR_B_WE#17

T2023 PAD~D

T2025 PAD~DT2024 PAD~D

DDR_B_BS0

DDR_B_BS1

DDR_B_BS2

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6DDR_A_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA12

DDR_B_MA13

DDR_B_CAS#

DDR_B_RAS#

DDR_B_WE#

SB_RCVENIN#

SB_RCVENOUT#

AT24

AV23

AY28

AK36

AR38

AT36

BA31

AL17

AM39

AT39

AU35

AR29

AR16

AR10

AM40

AU39

AT35

AP29

AP16

AT10

AY23

AW24

AY24

AR28

AT27

AT28

AU27

AV28

AV27

AW27

AV24

BA27

AY27

AR23

AR24

AU23

AR27

AK16

AK18

AH8

BA5

AN4

AR7

AN5

AT7

AP5

E

SB_BS0

SB_BS1

SB_BS2

SB_DM0

SB_DM1

SB_DM2

SB_DM3

SB_DM4

SB_DM5

SB_DM6

SB_DM7

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

SB_DQS0#

SB_DQS1#

SB_DQS2#

SB_DQS3#

SB_DQS4#

SB_DQS5#

SB_DQS6#

SB_DQS7#

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_CAS#

SB_RAS#

SB_WE#

SB_RCVENIN#

SB_RCVENOUT#

U40E

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

DDR SYS MEMORY B

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

CALISTOGA A0 _ FCBGA1466~D

AK39

AJ37

AP39

AR41

AJ38

AK38

AN41

AP41

AT40

AV41

AU38

AV38

AP38

AR40

AW38

AY38

BA38

AV36

AR36

AP36

BA36

AU36

AP35

AP34

AY33

BA33

AT31

AU29

AU31

AW31

AV29

AW29

AM19

AL19

AP14

AN14

AN17

AM16

AP15

AL15

AJ11

AH10

AJ9

AN10

AK13

AH11

AK10

AJ8

BA10

AW10

BA4

AW4

AY10

AY9

AW5

AY5

AV4

AR5

AK4

AK3

AT4

AK5

AJ5

AJ3

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

DDR_B_D[0..63] 17DDR_A_D[0..63] 16

A A

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Calistogo(2 of 6)

LA-2791

11 63Tuesday, Feb ru ar y 07, 2006

1

0.6

of

Page 12

5

4

3

2

1

LOW = Moby Dick

C

SDVO_CTRLDATA52

SDVO_CTRLCLK52

R251

1.5K_0402_1%~D

12

R25

150_0402_1%~D

1 2

1 2

LDDC_CLK19

LDDC_DATA19

LCD_A0+19

LCD_A1+19

LCD_A2+19

LCD_A0-19

LCD_A1-19

LCD_A2-19

LCD_B0+19

LCD_B1+19

LCD_B2+19

LCD_B0-19

LCD_B1-19

LCD_B2-19

LCD_ACLK+19

LCD_ACLK-19

LCD_BCLK+19

LCD_BCLK-19

12

R24

150_0402_1%~D

VGA_VSYNC20

VGA_HSYNC20

12

LCTLA_CLK

LCTLB_DATA

PANEL_BKEN

D D

PANEL_BKEN19

ENVDD19

LVREF for Alviso N.C

C C

B B

A A

for Calistoga to GND

TV_CVBS36

TV_Y36

TV_C36

Close to U40.J22

+3.3V_RUN_R

R283 10K_0402_5%~D

R279 10K_0402_5%~D

1 2

R300 100K_0402_5%~D

SDVO_CTRLDATA

SDVO_CTRLCLK

BIA_PWM_R

PANEL_BKEN

LCTLA_CLK

LCTLB_DATA

LDDC_CLK

LDDC_DATA

L_IBG

12

R23

150_0402_1%~D

Close to U40.J20

VGA_BLU20,36

VGA_GRN20,36

VGA_RED20,36

R314

G_CLK_DDC2

G_DAT_DDC2

R150

255_0402_1%~D

12

TVIREF

4.99K_0402_1%~D

12

U40C

H27

SDVOCTRL_DATA

H28

SDVOCTRL_CLK

B37

LA_DATA0

B34

LA_DATA1

A36

LA_DATA2

C37

LA_DATA#0

B35

LA_DATA#1

A37

LA_DATA#2

F30

LB_DATA0

D29

LB_DATA1

F28

LB_DATA2

G30

LB_DATA#0

D30

LB_DATA#1

F29

LB_DATA#2

A32

LA_CLK

A33

LA_CLK#

E26

LB_CLK

E27

LB_CLK#

D32

LBKLT_CTL

J30

LBKLT_EN

H30

LCTLA_CLK

H29

LCTLB_DATA

G26

LDDC_CLK

G25

LDDC_DATA

F32

LVDD_EN

B38

LIBG

C35

LVBG

C33

LVREFH

C32

LVREFL

A16

TVDAC_A

C18

TVDAC_B

A19

TVDAC_C

J20

TV_IREF

B16

TV_IRTNA

B18

TV_IRTNB

B19

TV_IRTNC

J29

TV_DCONSEL1

K30

TV_DCONSEL0

C26

DDCCLK

C25

DDCDATA

H23

VSYNC

G23

HSYNC

E23

BLUE

D23

BLUE#

C22

GREEN

B22

GREEN#

A21

RED

B21

RED#

J22

CRT_IREF

BIA_PWM19,39

LVDS

TV CRT

CALISTOGA A0 _ FCBGA1466~D

PEGCOMP

D40

EXP_COMPI

EXP_COMPO

PCI-EXPRESS GRAPHICS

+3.3V_RUN_R

5

P

IN1

4

O

IN2

G

3

D38

F34

EXP_RXN0

G38

EXP_RXN1

H34

EXP_RXN2

J38

EXP_RXN3

L34

EXP_RXN4

M38

EXP_RXN5

N34

EXP_RXN6

P38

EXP_RXN7

R34

EXP_RXN8

T38

EXP_RXN9

V34

EXP_RXN10

W38

EXP_RXN11

Y34

EXP_RXN12

AA38

EXP_RXN13

AB34

EXP_RXN14

AC38

EXP_RXN15

D34

EXP_RXP0

F38

EXP_RXP1

G34

EXP_RXP2

H38

EXP_RXP3

J34

EXP_RXP4

L38

EXP_RXP5

M34

EXP_RXP6

N38

EXP_RXP7

P34

EXP_RXP8

R38

EXP_RXP9

T34

EXP_RXP10

V38

EXP_RXP11

W34

EXP_RXP12

Y38

EXP_RXP13

AA34

EXP_RXP14

AB38

EXP_RXP15

EXP_TXN0

EXP_TXN1

EXP_TXN2

EXP_TXN3

EXP_TXN4

EXP_TXN5

EXP_TXN6

EXP_TXN7

EXP_TXN8

EXP_TXN9

EXP_TXN10

EXP_TXN11

EXP_TXN12

EXP_TXN13

EXP_TXN14

EXP_TXN15

EXP_TXP0

EXP_TXP1

EXP_TXP2

EXP_TXP3

EXP_TXP4

EXP_TXP5

EXP_TXP6

EXP_TXP7

EXP_TXP8

EXP_TXP9

EXP_TXP10

EXP_TXP11

EXP_TXP12

EXP_TXP13

EXP_TXP14

EXP_TXP15

1

2

U8

74AHC1G08GW_SOT353-5~D

DVO_RED#_C

F36

DVO_GREEN#_C

G40

DVO_BLUE#_C

H36

DVO_CLK#_C

J40

L36

M40

N36

P40

R36

T40

V36

W40

Y36

AA40

AB36

AC40

DVO_RED_C

D36

DVO_GREEN_C

F40

DVO_BLUE_C

G36

DVO_CLK_C

H40

J36

L40

M36

N40

P36

R40

T36

V40

W36

Y40

AA36

AB40

BIA_PWM_R

R1493

24.9_0402_1%~D

1 2

C1346 0.1U_0402_16V4Z~D

1 2

C1347 0.1U_0402_16V4Z~D

1 2

C1348 0.1U_0402_16V4Z~D

1 2

C1349 0.1U_0402_16V4Z~D

1 2

C1350 0.1U_0402_16V4Z~D

1 2

C1360 0.1U_0402_16V4Z~D

1 2

C1372 0.1U_0402_16V4Z~D

1 2

C1359 0.1U_0402_16V4Z~D

1 2

SDVOB_INT- 52

SDVOB_INT+ 52

VGA_RED

VGA_GRN

VGA_BLU

+1.5VRUN_PCIE

1 2

R261 150_0402_1%~D

1 2

R260 150_0402_1%~D

1 2

R295 150_0402_1%~D

SDVOB_RED- 52

SDVOB_GREEN- 52

SDVOB_BLUE- 52

SDVOB_CLK- 52

SDVOB_RED+ 52

SDVOB_GREEN+ 52

SDVOB_BLUE+ 52

SDVOB_CLK+ 52

Strap Pin Table

CFG5

CFG6

CFG7

CFG9

CFG11

CFG[13:12]

CFG16

(FSB Dynamic ODT)

CFG18

(VCC Select)

CFG19

(DMI Lane Reversal)

SDVO_CTRLDATA

CFG20

(PCIE/SDVO select)

Low = DMI x 2

High = DMI x 4

LOW = Moby Dick

HIGH = Calistoga

Low = DT/Transportable CPU

High = Mobile CPU

Low = Reverse Lane

High = Normal Operation

00 = Reserved

01 = XOR Mode Enabled

10 = All Z Mode Enabled

11 = Normal Operation

(Default)

*

*

*

*

*

Low = Disabled

High = Enabled

Low = 1.05V (Default)

High = 1.5V

Low = Normal

Operation (Default):

Lane number in Order

*

*

*

High = Reverse Lane

Low = No SDVO Device Present

High = SDVO Device Present

Low = Only PCIE or SDVO is

operational.

High = PCIE/SD VO are operating

simu.

G_CLK_DDC2

G_DAT_DDC2

R229

(Default)

(Default)

+3.3V_RUN_R

12

12

2.2K_0402_5%~D

+3.3V_RUN_R

*

*

R232

S

2.2K_0402_5%~D

G

2

G

2

S

CFG510

CFG610

CFG710

CFG910

CFG1110

CFG1210

CFG1310

CFG1610

CFG[3:17] have internal pullup

CFG1810

CFG1910

CFG2010

CFG[18:20] have internal pulldown

D

CLK_DDC2

13

Q31

BSS138W-7-F_SOT323~D

DAT_DDC2

13

D

Q27

BSS138W-7-F_SOT323~D

R307 2.2K_0402_5%~D @

1 2

R67 2.2K_0402_5%~D@

1 2

R281 2.2K_0402_5%~D @

1 2

R282 2.2K_0402_5%~D @

1 2

R357 2.2K_0402_5%~D@

1 2

R288 2.2K_0402_5%~D@

1 2

R323 2.2K_0402_5%~D@

1 2

R346 2.2K_0402_5%~D @

1 2

+3.3V_RUN_R

1 2

1 2

1 2

@

R308 1K_0402_5%~D

R306 1K_0402_5%~D @

R310 1K_0402_5%~D @

CLK_DDC2 20,36

DAT_DDC2 20,36

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Calistoga(3 of 6)

LA-2791

12 63Tuesday, Feb ru ar y 07, 2006

1

0.6

of

Page 13

5

+1.05V_VCCP

CRB 270uF

D D

C391

C C