Page 1

Vinafix.com

5

D D

4

3

2

1

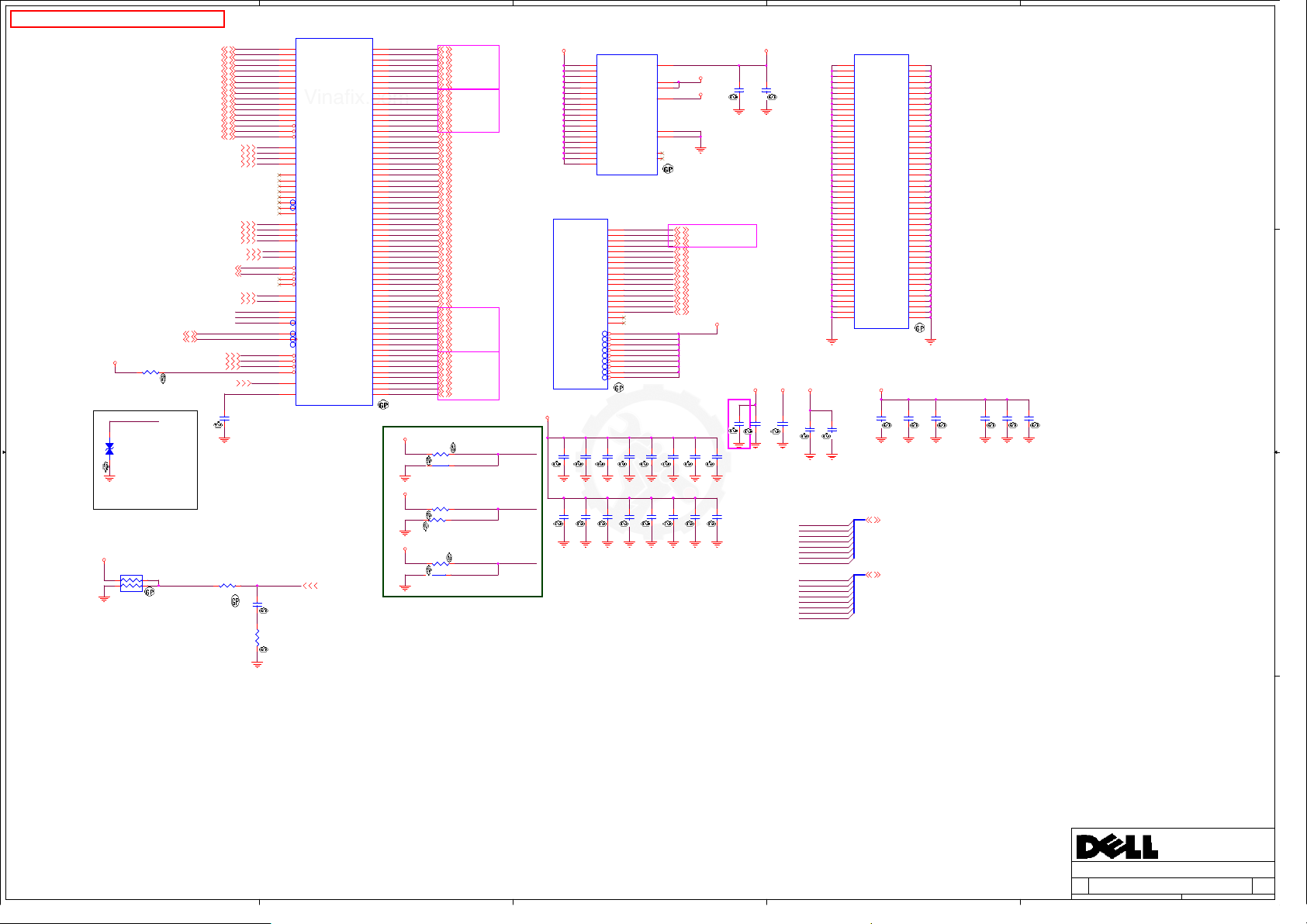

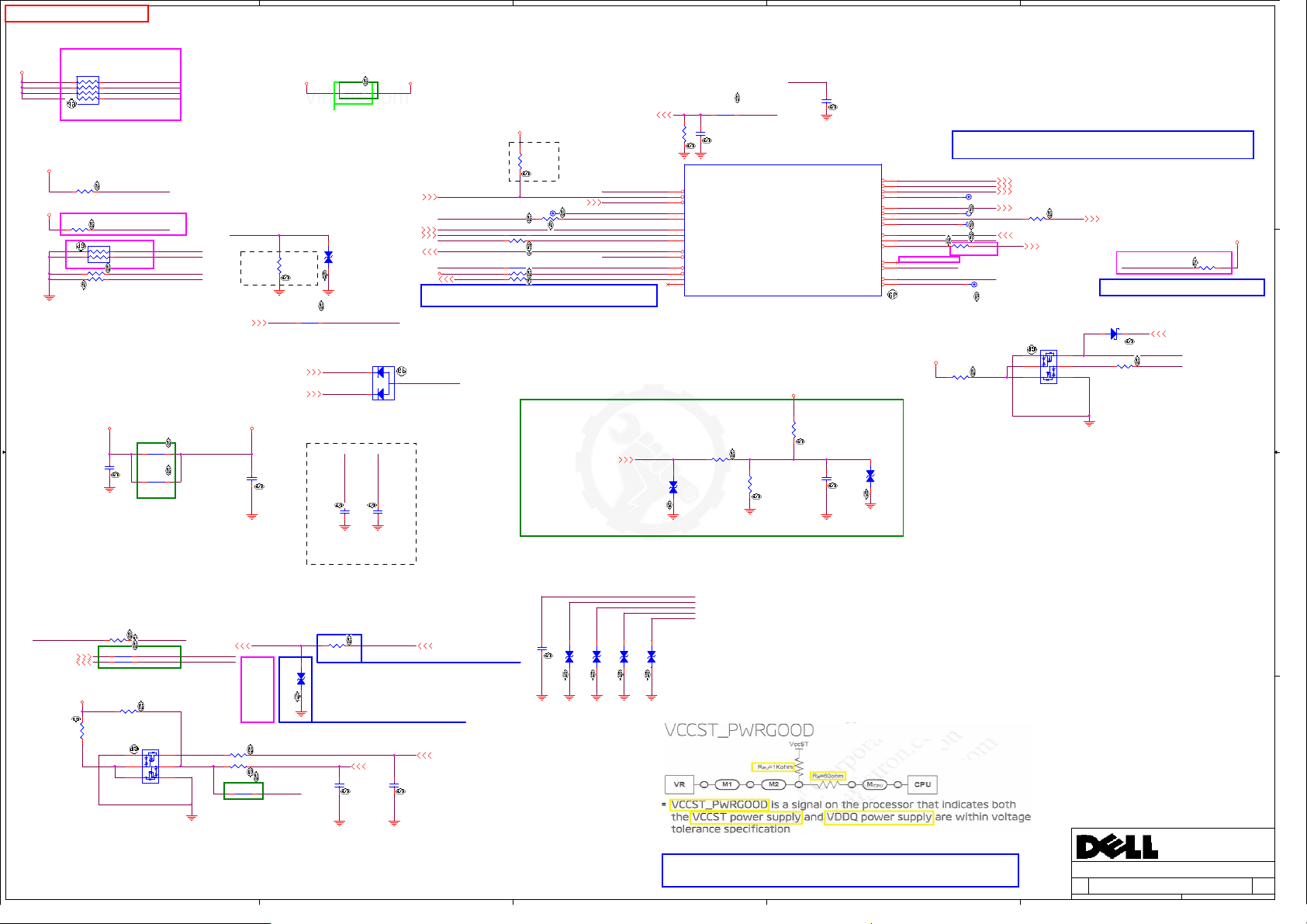

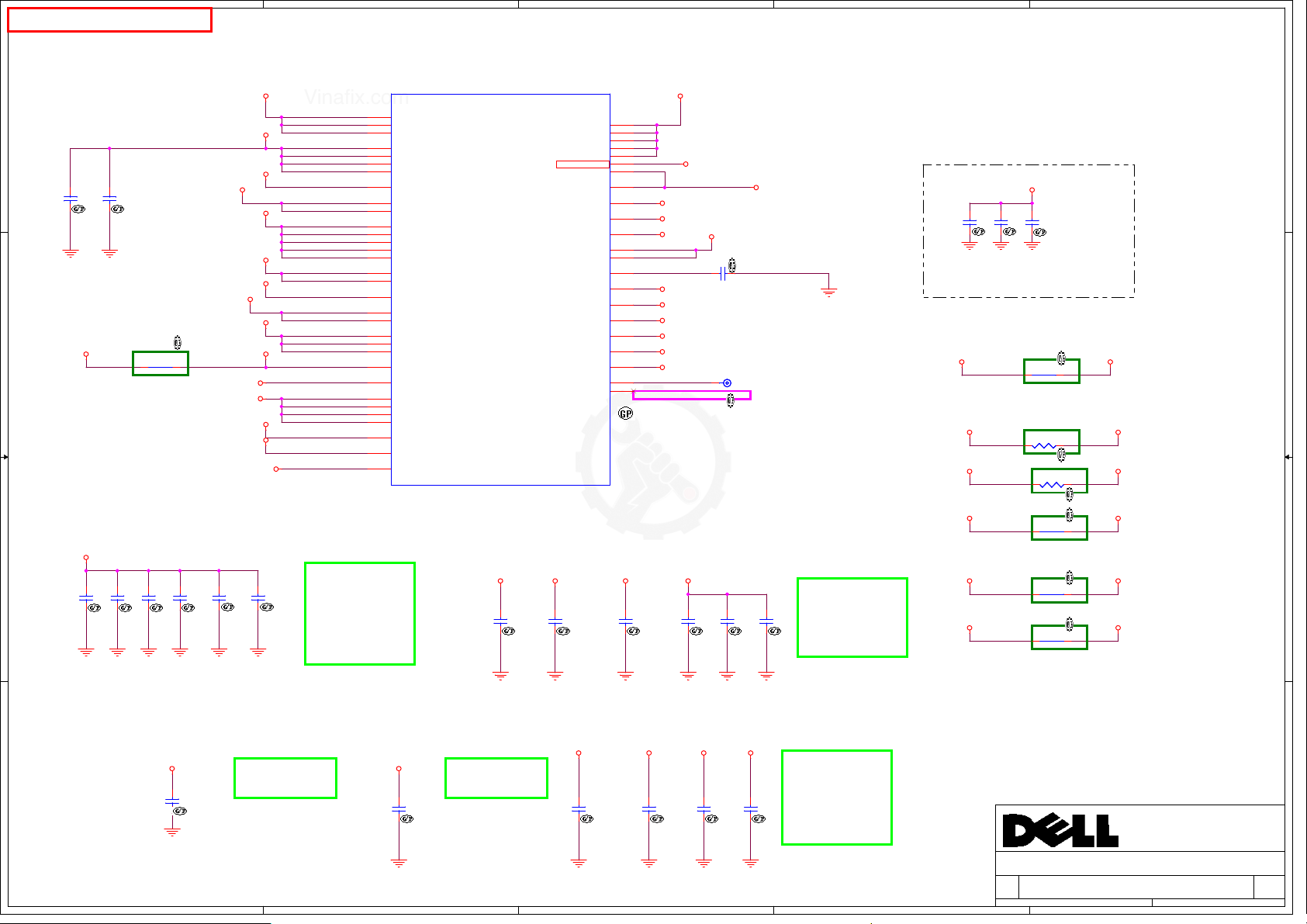

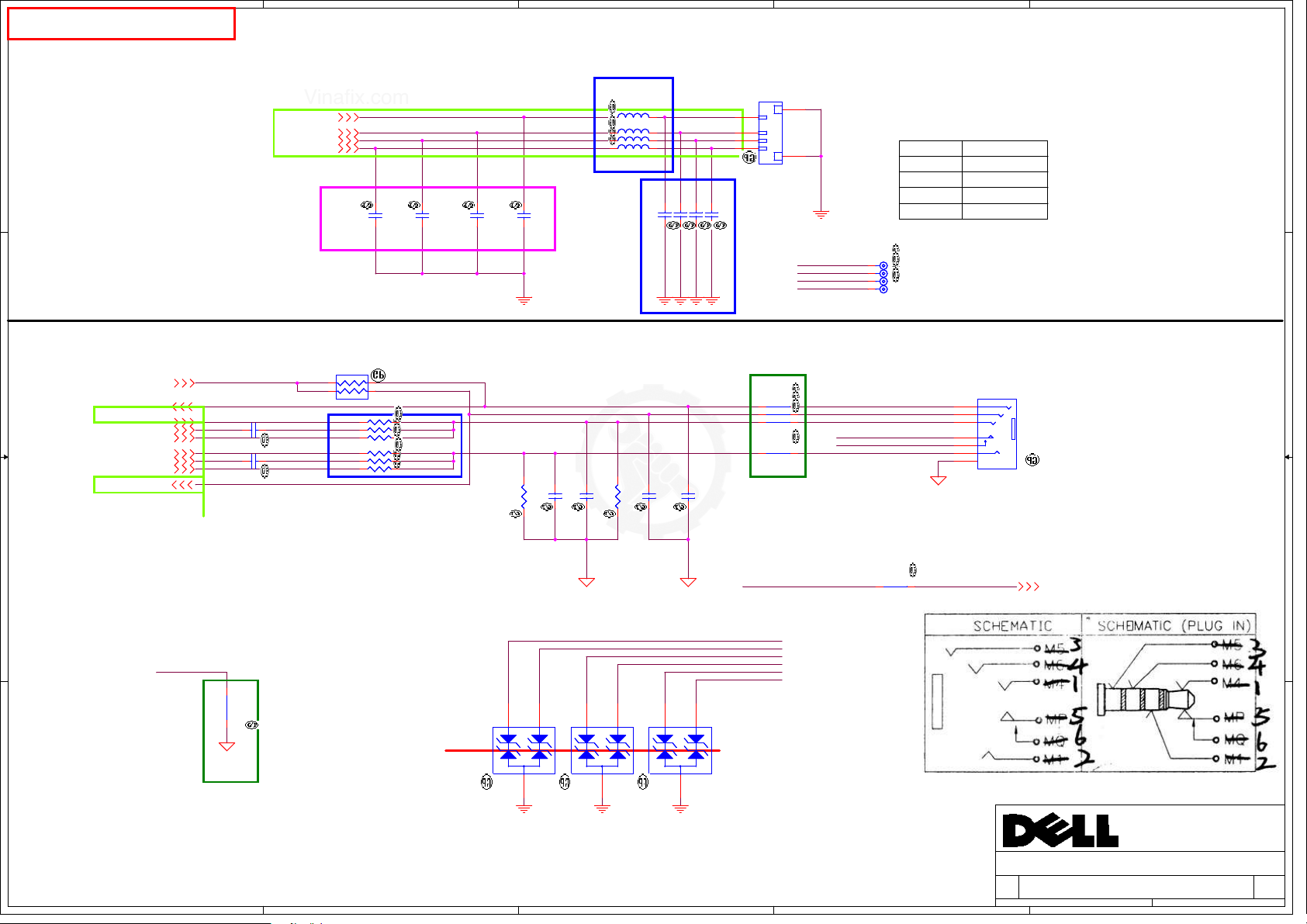

Taos Schematics

Skylake/Kabylake -U

C C

2016-12-23

REV : A00

B B

DY : None Installed

A A

UMA: UMA only installed

OPS: DISCRTE OPTIMUS installed

5

4

3

2

2.DIS

2.DIS

2.DIS

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Monday, December 26, 2016

Monday, December 26, 2016

Monday, December 26, 2016

Date: Sheet of

Date: Sheet of

Date: Sheet of

Cover Page

Cover Page

Cover Page

Taos KBL-U

Taos KBL-U

Taos KBL-U

Taipei Hsien 221, Taiwan, R.O.C.

1 105

1 105

1 105

1

X00

X00

X00

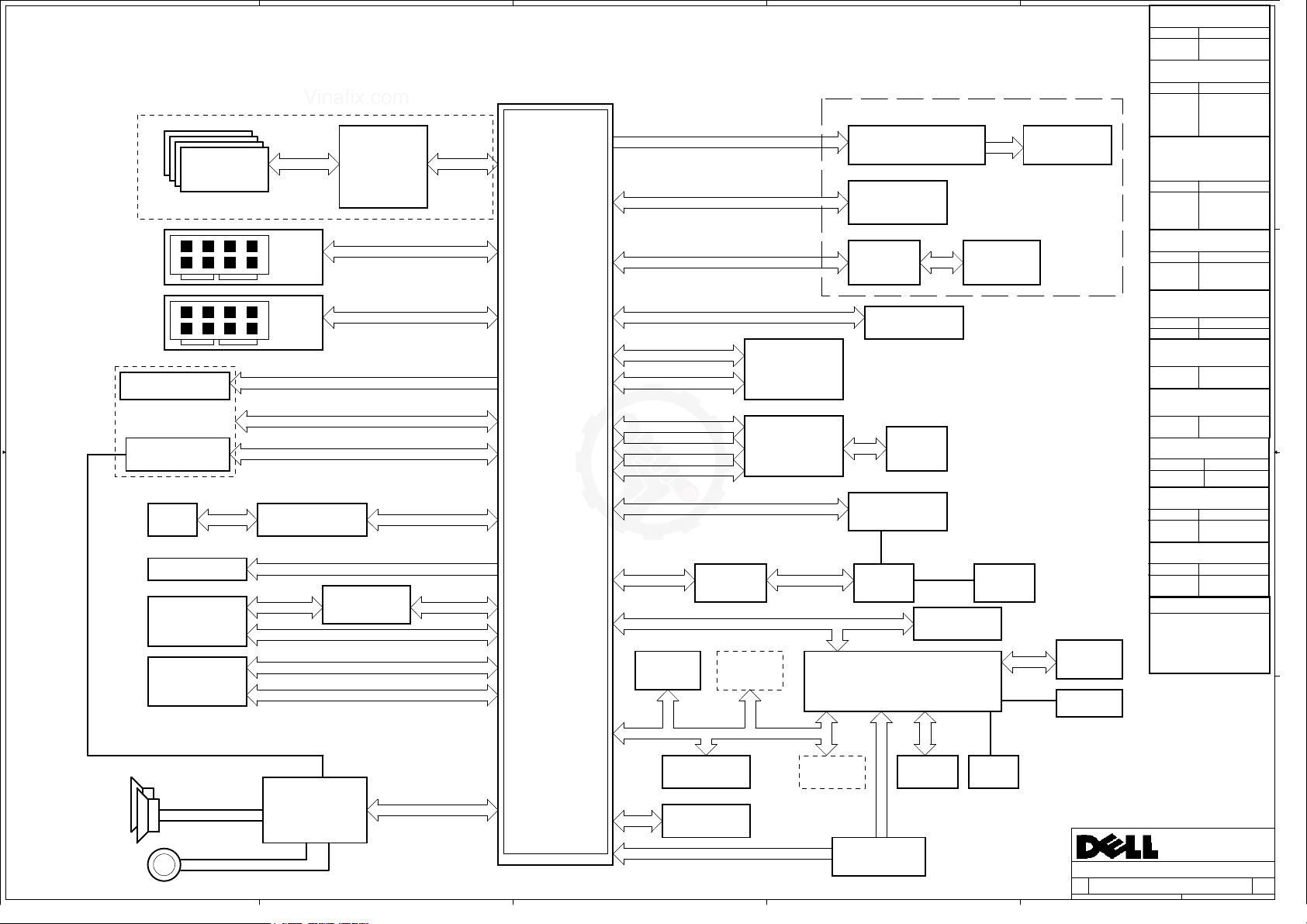

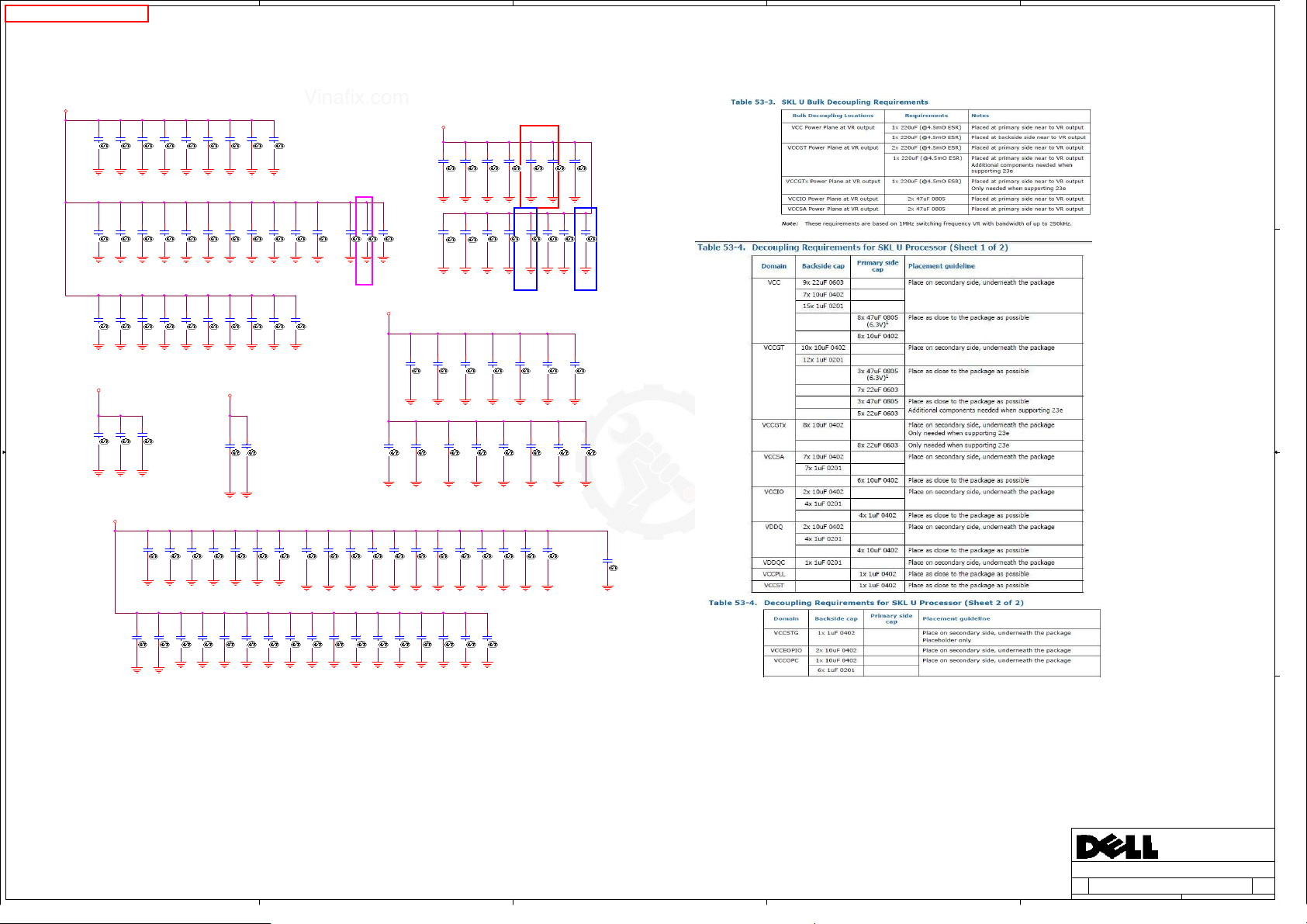

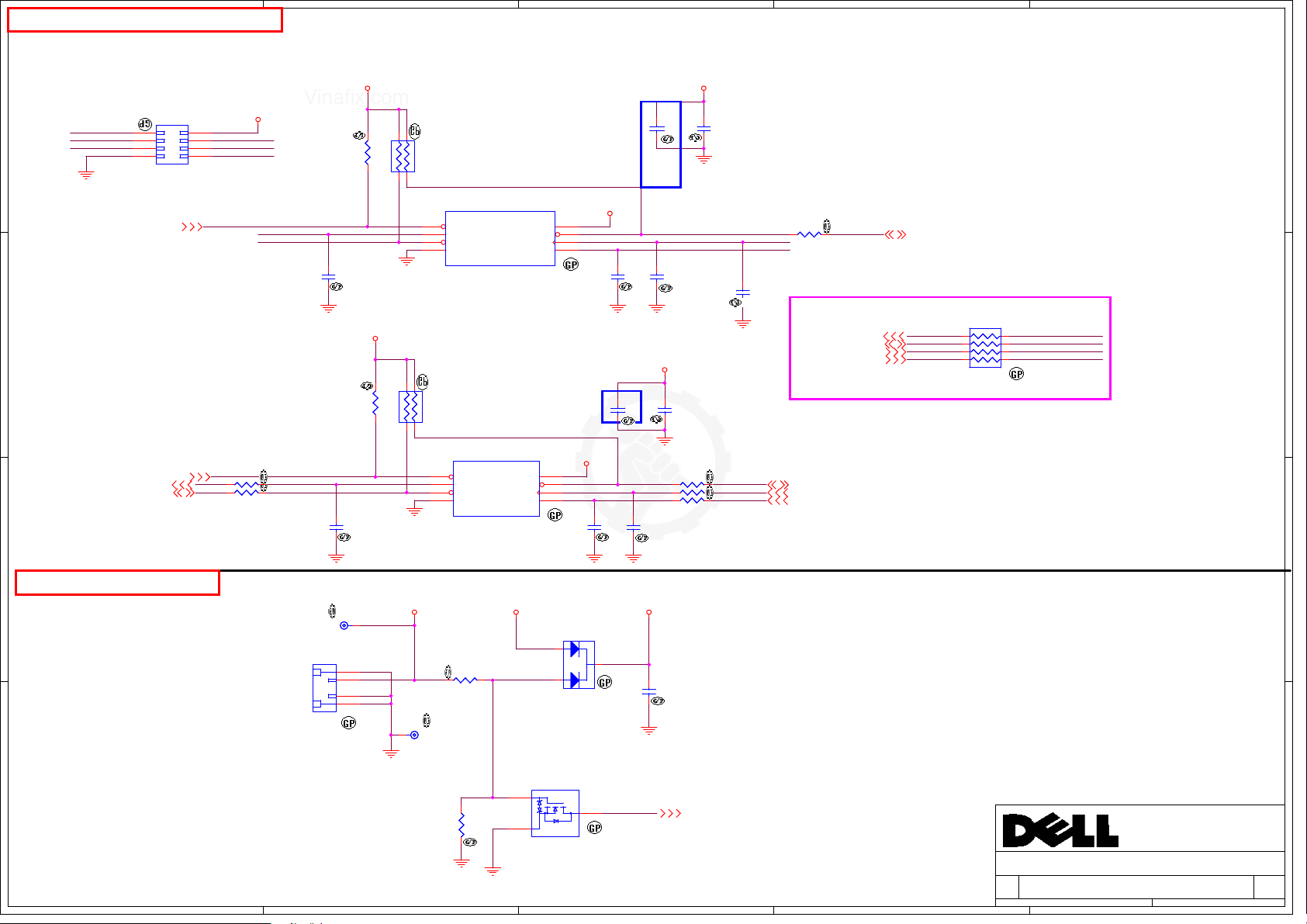

Page 2

Vinafix.com

5

Project code:

Taos14 -->4PD09Z010001

Taos15 -->4PD0A1010001

Taos KBL-U/SKL-U Block Diagram

PCB P/N: 16852

Revision: A00

D D

VRAM(GDDR3) *4

2GB

78,79

DDR3L

DIS only

DDR4

(2133 MHz)

SODIMM A

DDR4

(2133 MHz)

C C

14"/15" LCD

55

Touch Panel

IR Camera

Digital MIC

55

SODIMM B

USB2.0 x 1

USB2.0 x 1

LAN 10/100/1000 RJ45

Conn.

32

B B

HDMI V1.4a

Left side

57

RTL8111HSD

USB2.0 x 1

USB1(USB3.0)

36

Left side

USB3(USB3.0)

35,36

DDR4 2133 MHz Channel A

12

DDR4 2133 MHz Channel B

13

power share

TPS2544RTER-GP

GPU

AMD

R16M-M1-30

18W

76,77,78,79,80

31

4

eDP

PCIE x 1

DDI1

34

USB3.0 x 1

USB2.0 x 1

USB3.0 x 1

PCIE x 4

USB2.0 x 1

Intel CPU

KabyLake U 2+2U

Skylake

15W (UMA&DIS)

SKL PCH-LP

10 USB 2.0/1.1 ports

6 USB 3.0 ports

High Definition Audio

3 SATA ports

6 PCIE ports

LPC I/F

ACPI 5.0

3

DDI2

USB2.0 x 1

USB2.0 x 1

USB2.0

PCIE x 1

USB2.0 x 1

USB3.0 x 1

PCIe/SATA

USB2.0 x 1

SM Bus

SATA x 1

(Gen3)

LPC BUS

Flash ROM

16MB

SPI

HDD Re-driver

SN75LVCP601

RTJR-GP

Flash ROM

25

NGFF WLAN

802.11a/b/g/n

BT V4.0 combo

AC 3160

NGFF WWAN

LTE

60

8MB

25

SATA x 1

(Gen3)

2

DP/VGA Converter

REALTEK RTD2166-CGT

right side

USB2(USB2.0)

CardReader

Realtek

RTS5144

FRINGERPRINT

NB-2023-U

61

62

uSIM

Free Fall Sensor

ST LNG2DM

HDD P11

HDD

60

KBC

SMSC

MEC1416-NU-GP

PS2

92

63

67

interposer

board

LPC debug port

SMBUS

VGA

SD Card Slot

M.2 SSD

68

I2C

24

VGA Conn.

GPIO

Expander

IT8010

FAN

DB

1

CHARGER

BQ24786RUYR-GP

INPUTS

AD+

BT+

SYSTEM DC/DC

SY8288CRAC-GP

INPUTS

DCBATOUT

CPU Core Power

NCP81208MNTXG

NCP81382MNTXG*2

NCP81253MNTBG

INPUTS

DCBATOUT

DCBATOUT +VCCGT

DDR4

APW8861QBI-TRG-GP

INPUTS OUTPUTS

DCBATOUT 1D2V_S3

OUTPUTS

DCBATOUT

OUTPUTS

PWR_5V

5V_S5

5V_AUX_S5

OUTPUTS

VCC_CORE

+VCCSADCBATOUT

0D6V_S0

CPU DCDC-V1D00A

AOZ2261QI-10-GP-U

INPUTS OUTPUTS

DCBATOUT

LDO-V1D8V

APL5930KAI-TRG-GP

3D3V_S5

CPU VCCPRIM_CORE

1V

INPUTS OUTPUTS

1D0V_S5

OUTPUTSINPUTS

1D8V_S5

+VCCPRIM_CORE1D0V_S5

5V/3V S0

G5016KD1U

INPUTS

5V_S5

VCCSTG

APE8939GN3-GP

5V_S5

VCCST

APE8939GN3-GP

OUTPUTS

5V_S0

3D3V_S03D3V_S5

OUTPUTSINPUTS

+VCCIO

+VCCSTG

OUTPUTSINPUTS

+V1.00U_CPU5V_S5

+VCCST_CPU

44

45

46~50

51

53

54

11

40

40

40

PCB LAYER

L1:Top

L2:VCC

L3:Signal

L4:Signal

L5:GND

96

L6:Bottom

26

TPM 2.0

Atmel: ATTPM20P-G1MA1-ABF

LPC

3

(UDFN, 3.3V, SPI)

China TPM

Z32H320TC

I2C

A A

Universal Jack

29

5

2CH SPEAKER

(2CH 2W/4ohm)

29

MIC_IN/GND

HP_R/L

HDA

CODEC

Realtek

ALC3246

HDA

27

4

91

91

Flash ROM

128KB

EC

256KB

Precision Touch pad

24

2

Thermal

NUVOTON

NCT7718W

65

Int. KB

65

2.DIS

2.DIS

2.DIS

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin T ai Wu Rd ., Hsichih,

21F, 88, Sec.1, Hsin T ai Wu Rd ., Hsichih,

21F, 88, Sec.1, Hsin T ai Wu Rd ., Hsichih,

Taipei Hsie n 221, Taiwan, R.O. C.

Taipei Hsie n 221, Taiwan, R.O. C.

Title

Title

Title

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

A2

A2

A2

Date: Sheet of

Date: Sheet of

Date: Sheet of

Taipei Hsie n 221, Taiwan, R.O. C.

Block Diagram

Block Diagram

Block Diagram

Taos KBL-U

Taos KBL-U

Taos KBL-U

1

X00

X00

2 105Monday, Decemb er 26, 2016

2 105Monday, Decemb er 26, 2016

2 105Monday, Decemb er 26, 2016

X00

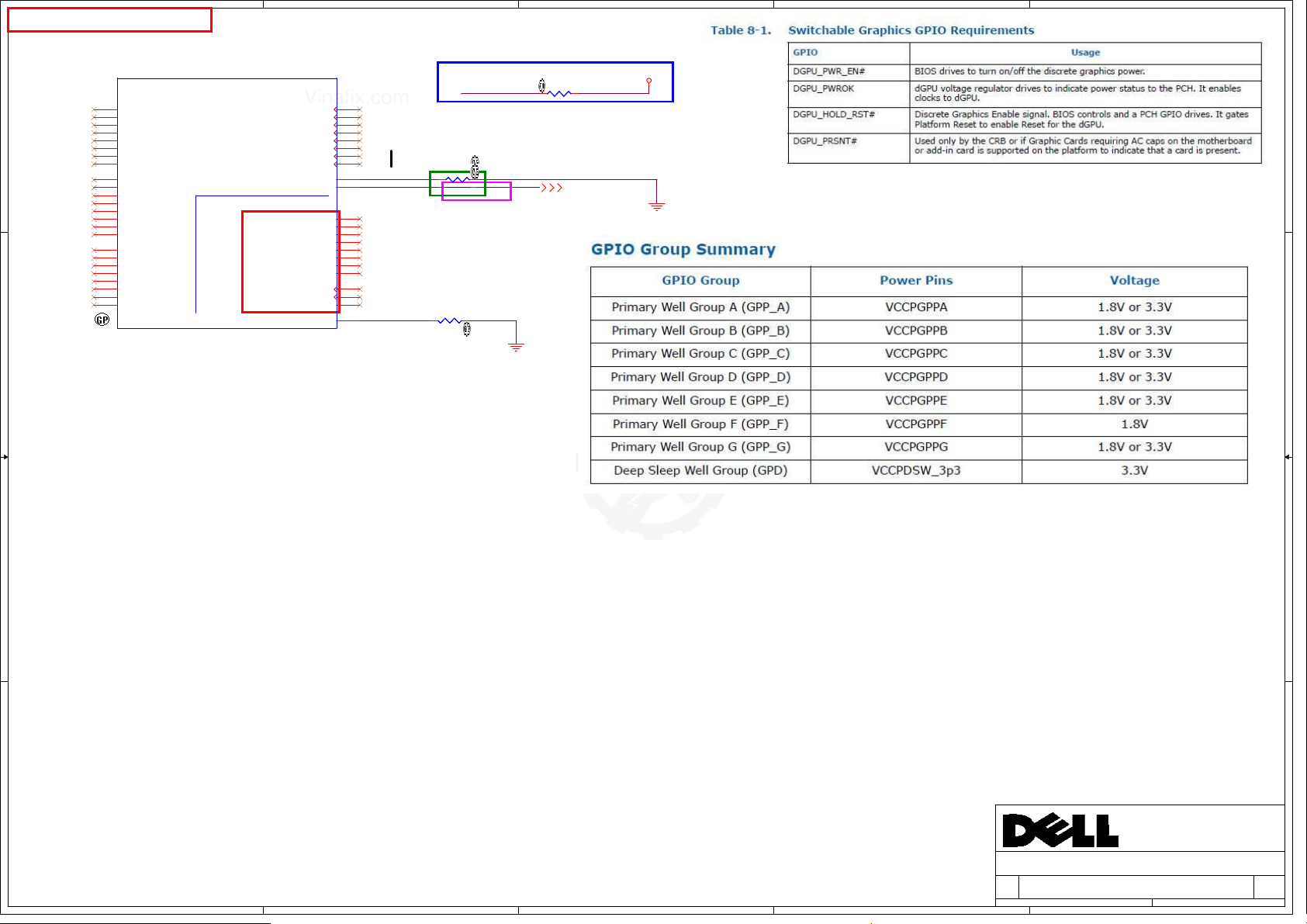

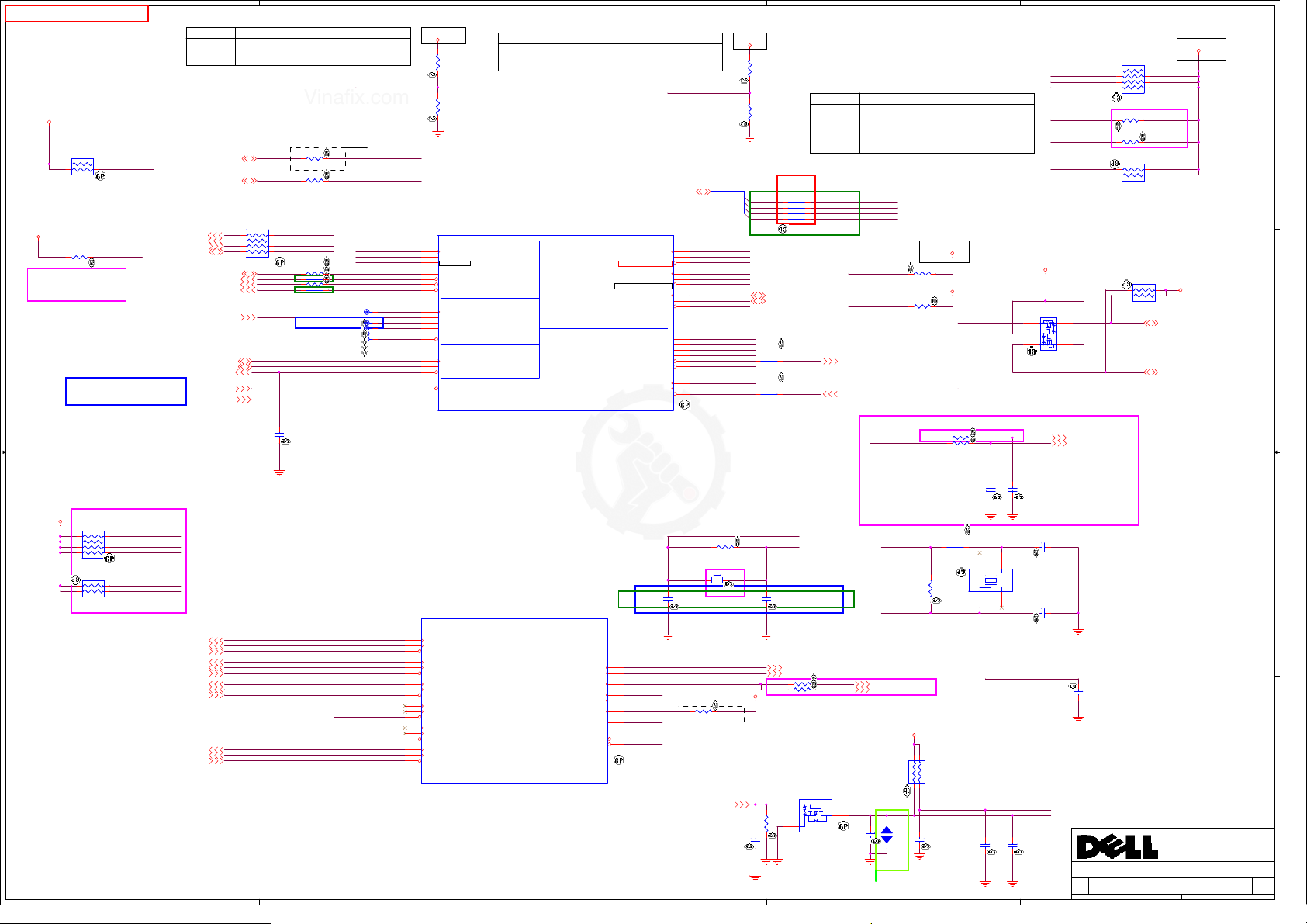

Page 3

Vinafix.com

5

4

3

2

1

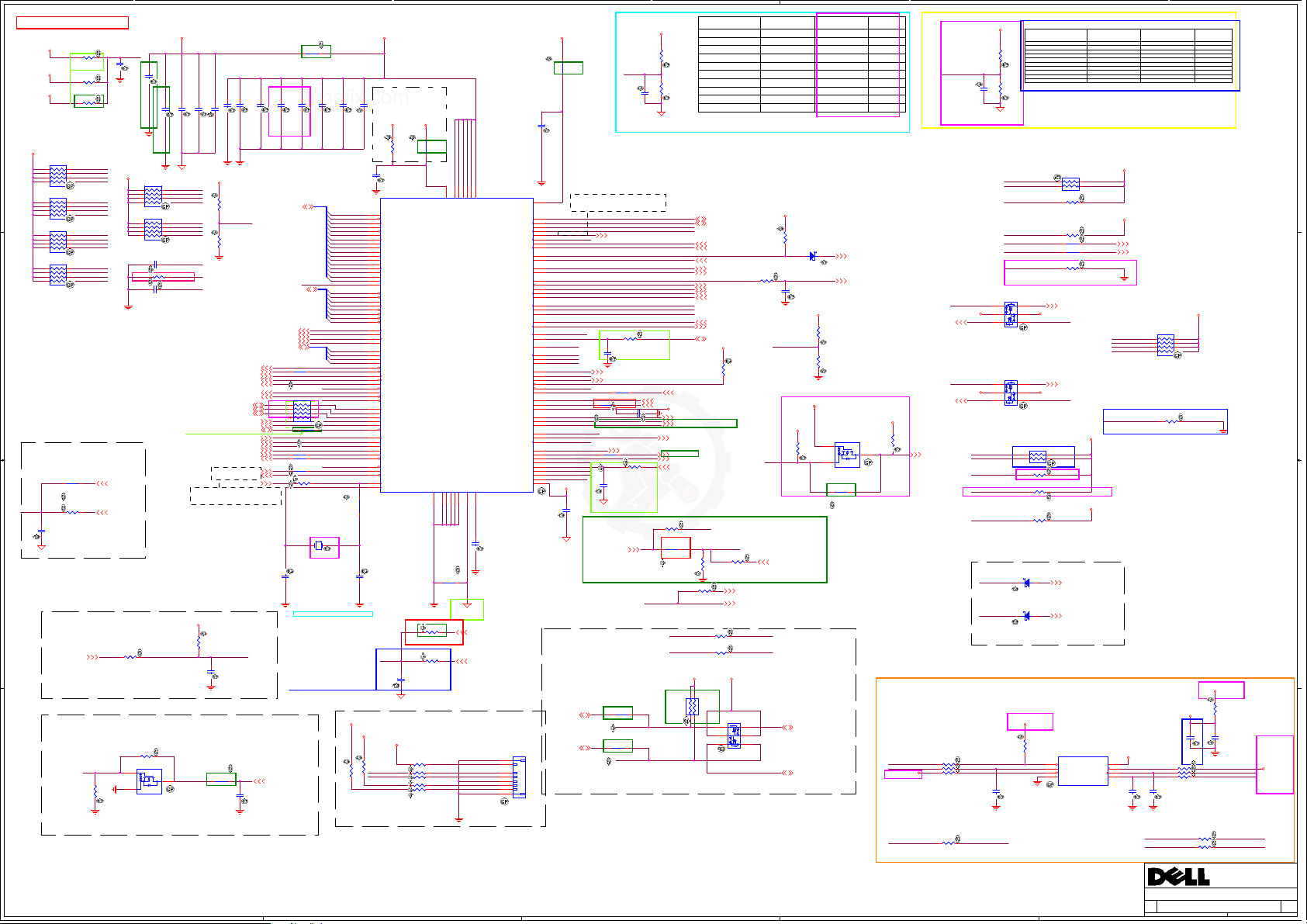

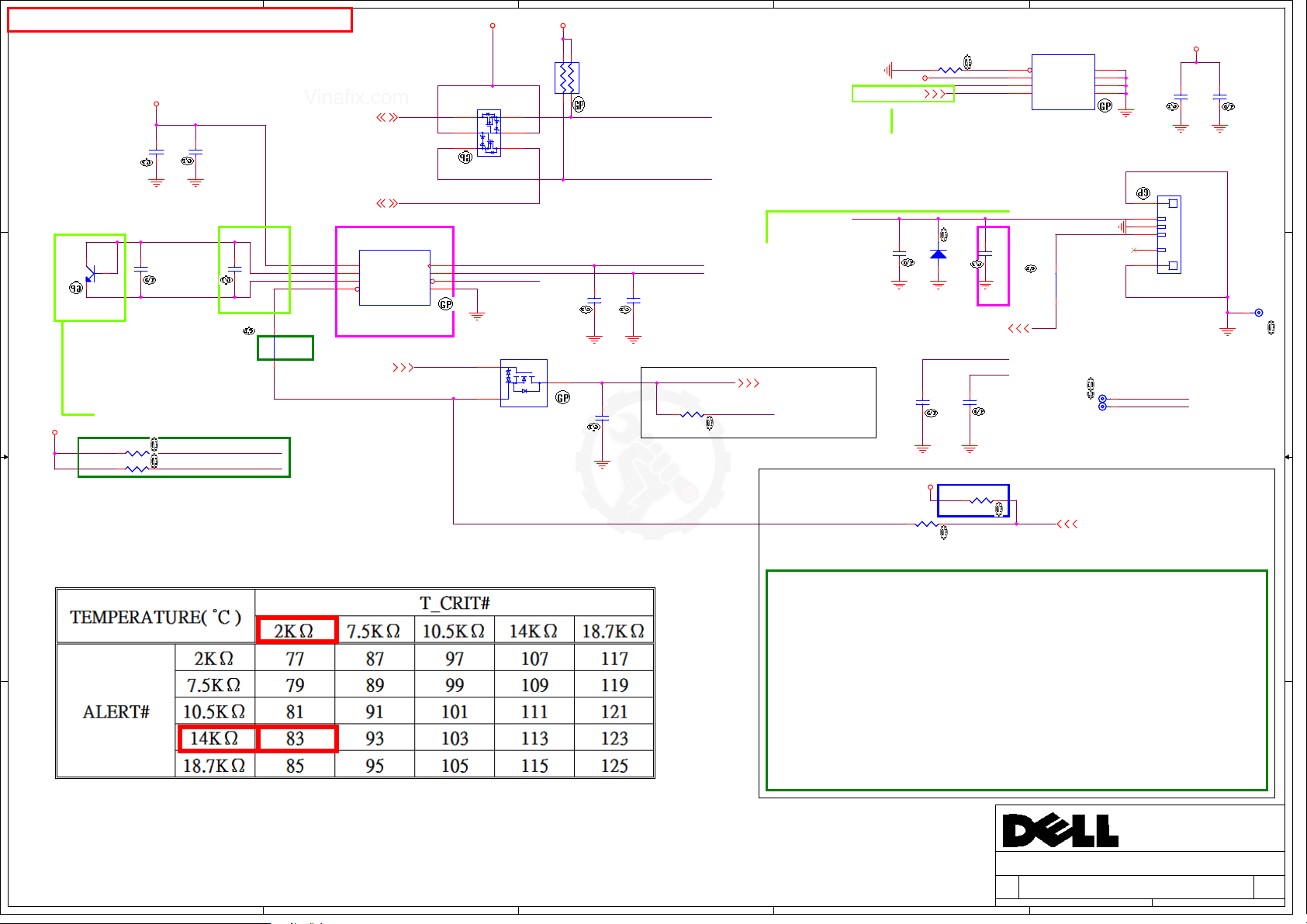

Main Func = CPU

D D

C C

(Blanking)

B B

2.DIS

2.DIS

2.DIS

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

A A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Date: Sheet of

Date: Sheet of

Date: Sheet of

5

4

3

(Reserved)

(Reserved)

(Reserved)

2

Taos KBL-U

Taos KBL-U

Taos KBL-U

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

3 105Monday, December 26, 2016

3 105Monday, December 26, 2016

3 105Monday, December 26, 2016

1

X00

X00

X00

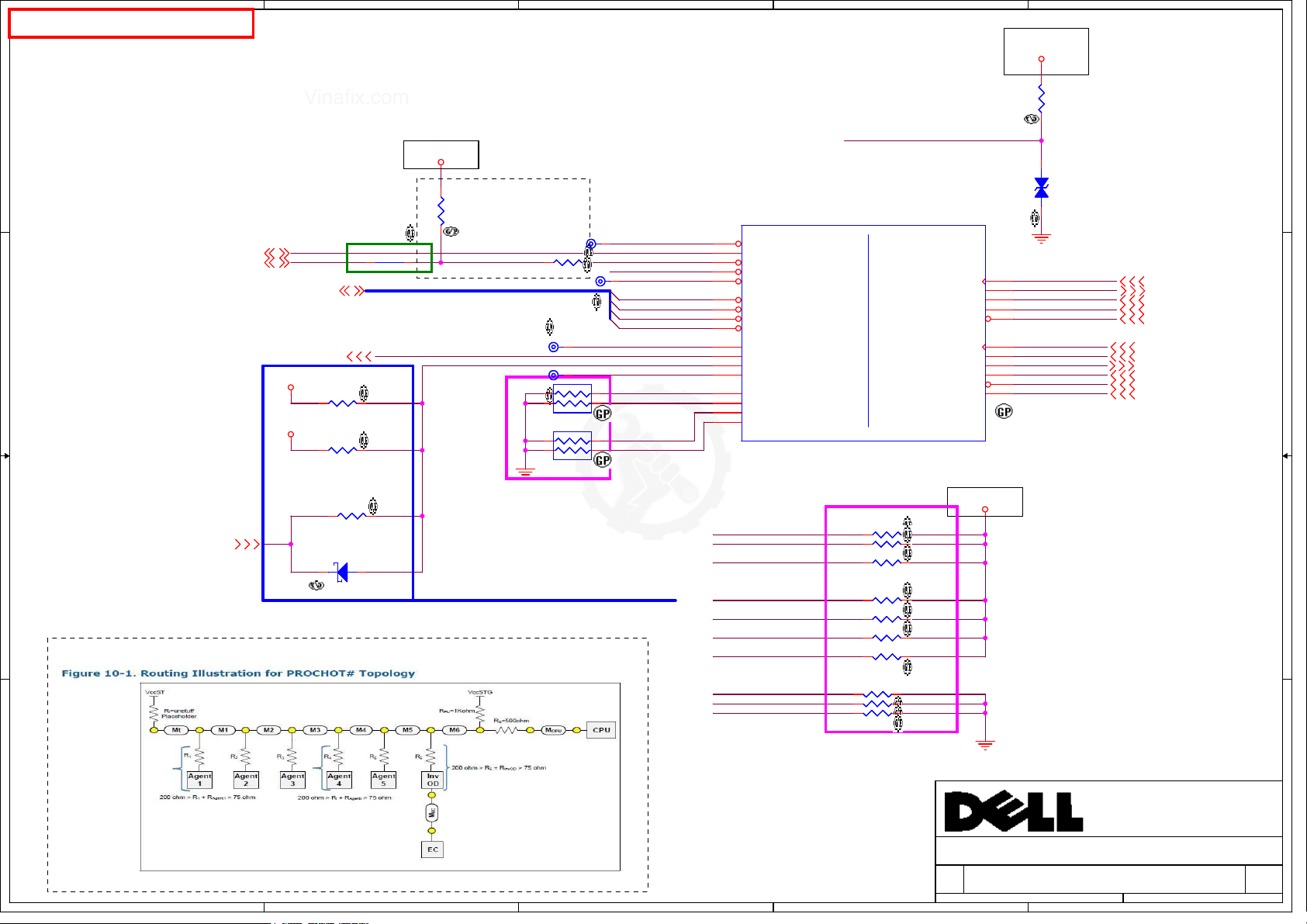

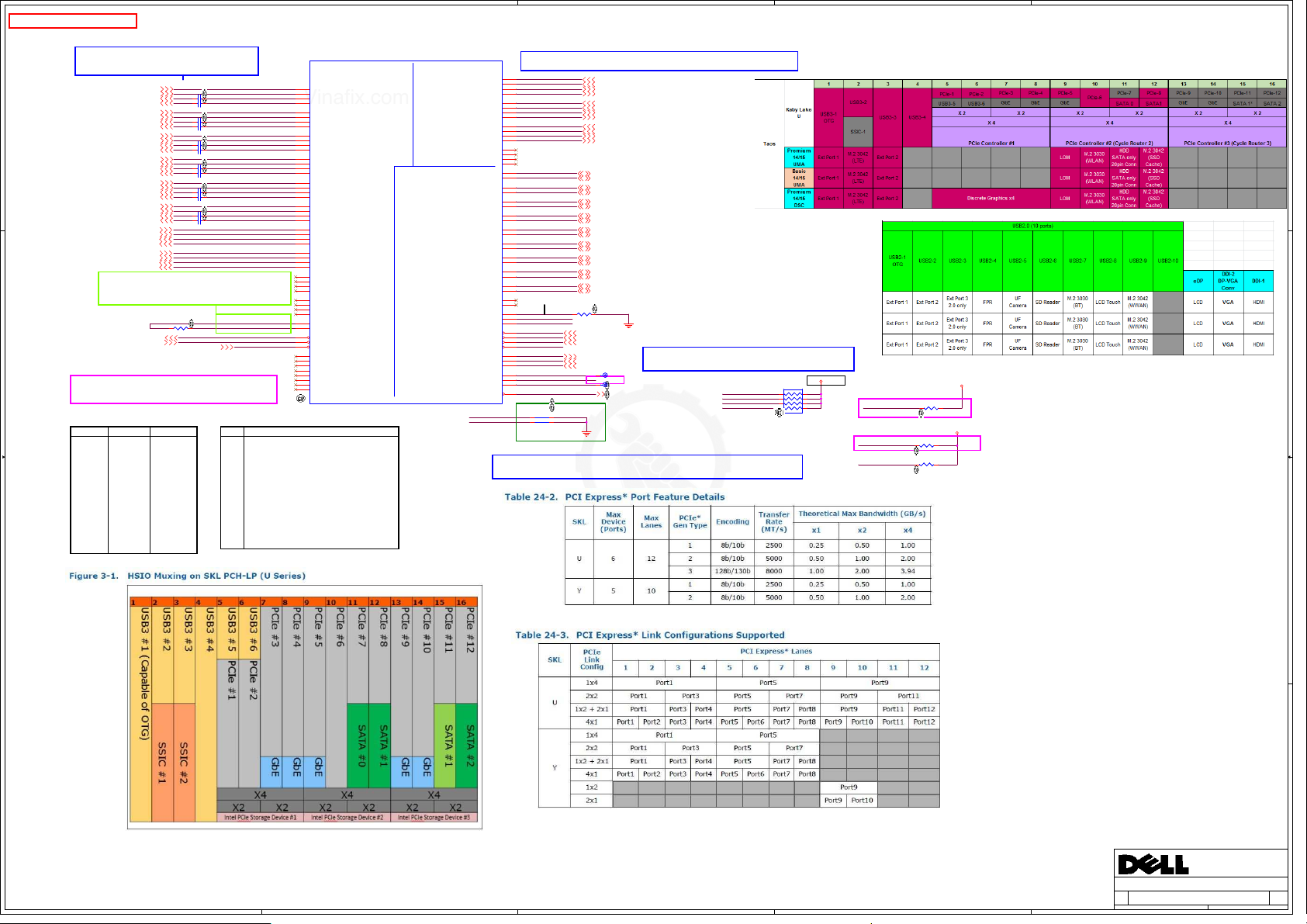

Page 4

Vinafix.com

5

Main Func = CPU

D D

[PECI] and [PROCHOT#]

Impedance control: 50 ohm

H_PECI[24]

H_PROCHOT#[24,44,46]

XDP_BPM[3:0][99]

#543016 Rev0.7: Ra = 500 ohm / Rb = 1k ohm

#544669 Rev0.52:

Ra = 56 ohm (TO BE CHANGED TO 100 OHMS) / Rb = 62 ohm and 150 ohm

C C

INT_TP#[24,65]

B B

TOUCH_PANEL_INTR#[24,55]

3D3V_S5_PCH

3D3V_S0

(#543016) PROCHOT# Routing Guidelines

20161024 0ohm to short pad

R411

R411

1 2

DY

DY

Do Not Stuff

Do Not Stuff

R414

R414

1 2

DS3

DS3

100KR2J-1-GP

100KR2J-1-GP

R410

R410

1 2

NON DS3

NON DS3

Do Not Stuff

Do Not Stuff

D401

D401

DS3

DS3

RB751V-40H-GP

RB751V-40H-GP

K A

83.R2004.G8F

83.R2004.G8F

R404

R404

1 2

Do Not Stuff

Do Not Stuff

4

+VCCSTG

12

Rb

+VCCSTG = 1.0 V

R401

R401

1KR2J-1-GP

1KR2J-1-GP

Do Not Stuff

Do Not Stuff

R403

H_PROCHOT#_R_R H_PROCHOT#_R

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

20160621 Merge R412,R413 to RN401 and R415,R418 to R402

R403

1 2

499R2F-2-GP

499R2F-2-GP

Ra

TP403

TP403

TOUCHPAD_INTR#

TP404

TP404

RN401

RN401

1

2 3

SRN49D9F-GP

SRN49D9F-GP

RN402

RN402

1

2 3

DY

DY

Do Not Stuff

Do Not Stuff

1

1

Add resistor by NON DS3 function

TP401

TP401

H_CATERR#

1

PCH_THERMTRIP

SKTOCC#

1

TP402

TP402

XDP_BPM0

XDP_BPM1

XDP_BPM2

XDP_BPM3

GPP_E3/CPU_GP0

GPP_B4/CPU_GP3

CPU_POPIRCOMP

4

PCH_POPIRCOMP

EDRAM_OPIO_RCOMP

4

EOPIO_RCOMP

3

2

1

#544669 CRB Rev0.52

+VCCST_CPU

12

R419

R419

1KR2J-1-GP

1KR2J-1-GP

PCH_THERMTRIP

12

ED401

ED401

DY

DY

Do Not Stuff

B61

D60

A61

C60

B59

B56

D59

A56

C59

C61

A59

Do Not Stuff

XDP_TCLK [99]

XDP_TDI [99]

XDP_TDO_CPU [99]

XDP_TMS [99]

XDP_TRST# [4,99]

PCH_JTAG_TCK [99]

PCH_JTAG_TDI [99]

PCH_JTAG_TDO [99]

PCH_JTAG_TMS [99]

XDP_TRST# [4,99]

XDP_TCK_JTAGX [99]

CPU1D

CPU1D

D63

CATERR#

A54

PECI

C65

PROCHOT#

C63

THERMTRIP#

A65

SKTOCC#

C55

BPM#[0]

D55

BPM#[1]

B54

BPM#[2]

C56

BPM#[3]

A6

GPP_E3/CPU_GP0

A7

GPP_E7/CPU_GP1

BA5

GPP_B3/CPU_GP2

AY5

GPP_B4/CPU_GP3

AT16

PROC_POPIRCOMP

AU16

PCH_OPIRCOMP

H66

OPCE_RCOMP

H65

OPC_RCOMP

SKYLAKE-U-GP

SKYLAKE-U-GP

SKYLAKE_ULT

SKYLAKE_ULT

CPU MISC

CPU MISC

JTAG

JTAG

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRST#

4 OF 20

4 OF 20

JTAGX

+VCCST_CPU = 1.0 V

XDP_TMS

XDP_TDI

XDP_TDO_CPU

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

XDP_TCK_JTAGX

XDP_TRST#

XDP_TCLK

PCH_JTAG_TCK

20160712 modify Dummy name XDP

1 2

DY

DY

1 2

DY

DY

1 2

DY

DY

1 2

XDP

XDP

1 2

XDP

XDP

1 2

XDP

XDP

1 2

DY

DY

R402 Do Not Stuff

R402 Do Not Stuff

1 2

DY

R406 Do Not Stuff

R406 Do Not Stuff

R407 Do Not Stuff

R407 Do Not Stuff

DY

1 2

XDP

XDP

1 2

DY

DY

R421Do Not Stuff

R421Do Not Stuff

R422Do Not Stuff

R422Do Not Stuff

R423Do Not Stuff

R423Do Not Stuff

R408Do Not Stuff

R408Do Not Stuff

R409Do Not Stuff

R409Do Not Stuff

R416Do Not Stuff

R416Do Not Stuff

R417Do Not Stuff

R417Do Not Stuff

+VCCST_CPU

2.DIS

2.DIS

2.DIS

A A

M1,2,3,4,5: <3 inches

M6: 1-11 inches

MCPU: 0.3-1.5 inches

Mt <0.3 mils

Main route(M1+M2+M3+M4+M5+M6+MCPU): 1-12 inches

5

4

3

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

2

CPU_(JTAG/CPU SIDE BAND)

CPU_(JTAG/CPU SIDE BAND)

CPU_(JTAG/CPU SIDE BAND)

Custom

Custom

Custom

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taos KBL-U

Taos KBL-U

Taos KBL-U

4 105Monday, December 26, 2016

4 105Monday, December 26, 2016

4 105Monday, December 26, 2016

1

X00

X00

X00

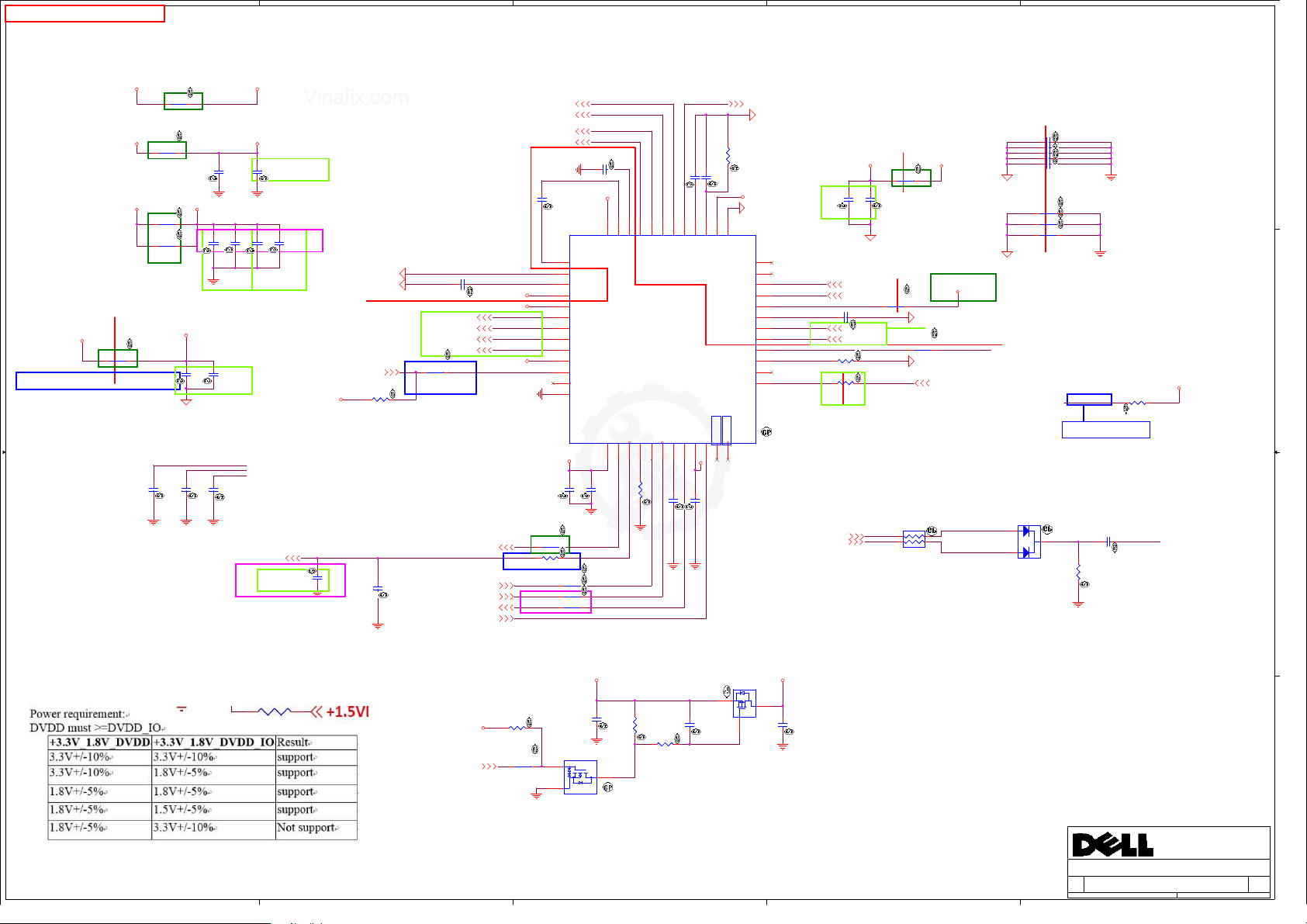

Page 5

Vinafix.com

Main Func = CPU

5

4

3

2

1

DDR4 ball type: Interleaved Type

D D

M_A_DQ0[12]

M_A_DQ1[12]

M_A_DQ2[12]

M_A_DQ[0:7]

M_A_DQ[8:15]

M_A_DQ[32:39]

M_A_DQ[40:47]

M_A_DQ[16:23]

C C

M_A_DQ[24:31]

M_A_DQ[48:55]

M_A_DQ[56:63]

B B

M_A_DQ3[12]

M_A_DQ4[12]

M_A_DQ5[12]

M_A_DQ6[12]

M_A_DQ7[12]

M_A_DQ8[12]

M_A_DQ9[12]

M_A_DQ10[12]

M_A_DQ11[12]

M_A_DQ12[12]

M_A_DQ13[12]

M_A_DQ14[12]

M_A_DQ15[12]

M_A_DQ32[12]

M_A_DQ33[12]

M_A_DQ34[12]

M_A_DQ35[12]

M_A_DQ36[12]

M_A_DQ37[12]

M_A_DQ38[12]

M_A_DQ39[12]

M_A_DQ40[12]

M_A_DQ41[12]

M_A_DQ42[12]

M_A_DQ43[12]

M_A_DQ44[12]

M_A_DQ45[12]

M_A_DQ46[12]

M_A_DQ47[12]

M_A_DQ16[12]

M_A_DQ17[12]

M_A_DQ18[12]

M_A_DQ19[12]

M_A_DQ20[12]

M_A_DQ21[12]

M_A_DQ22[12]

M_A_DQ23[12]

M_A_DQ24[12]

M_A_DQ25[12]

M_A_DQ26[12]

M_A_DQ27[12]

M_A_DQ28[12]

M_A_DQ29[12]

M_A_DQ30[12]

M_A_DQ31[12]

M_A_DQ48[12]

M_A_DQ49[12]

M_A_DQ50[12]

M_A_DQ51[12]

M_A_DQ52[12]

M_A_DQ53[12]

M_A_DQ54[12]

M_A_DQ55[12]

M_A_DQ56[12]

M_A_DQ57[12]

M_A_DQ58[12]

M_A_DQ59[12]

M_A_DQ60[12]

M_A_DQ61[12]

M_A_DQ62[12]

M_A_DQ63[12]

DQ Bit Swapping is allowed within the same byte, and Byte Swapping is allowed within the same channel.

Clock (CLK and CLK#) and Strobe (DQS and DQS#) differential signal swapping within a pair is not allowed. Also differential

clock pair to clock pair swapping within a channel is not allowed.

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

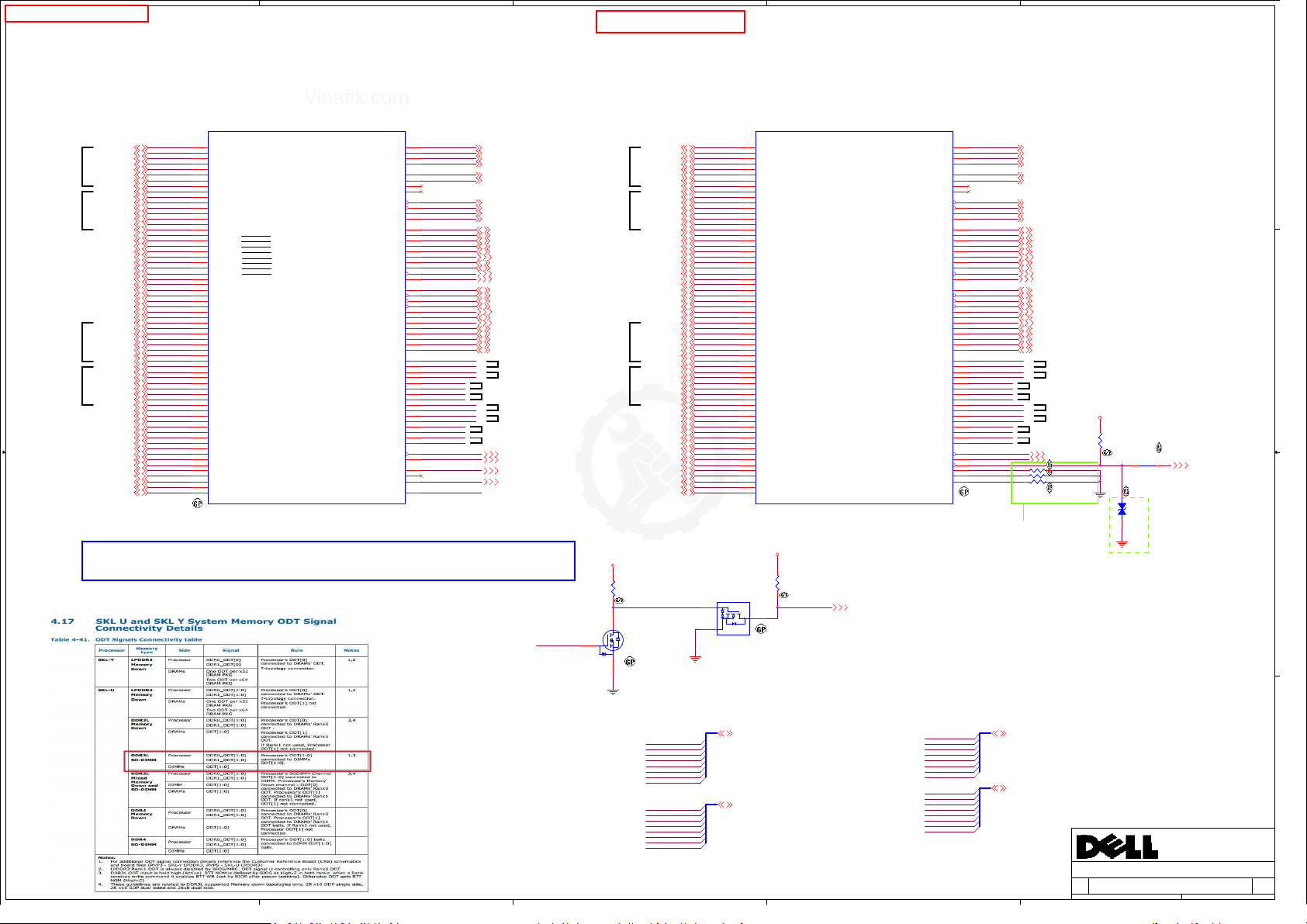

PDG: DDR/ODT

CPU1B

CPU1B

AL71

DDR0_DQ[0]

AL68

DDR0_DQ[1]

AN68

DDR0_DQ[2]

AN69

DDR0_DQ[3]

AL70

DDR0_DQ[4]

AL69

DDR0_DQ[5]

AN70

DDR0_DQ[6]

AN71

DDR0_DQ[7]

AR70

DDR0_DQ[8]

AR68

DDR0_DQ[9]

AU71

DDR0_DQ[10]

AU68

DDR0_DQ[11]

AR71

DDR0_DQ[12]

AR69

DDR0_DQ[13]

AU70

DDR0_DQ[14]

AU69

DDR0_DQ[15]

AF65

DDR1_DQ[0]/DDR0_DQ[16]

AF64

DDR1_DQ[1]/DDR0_DQ[17]

AK65

DDR1_DQ[2]/DDR0_DQ[18]

AK64

DDR1_DQ[3]/DDR0_DQ[19]

AF66

DDR1_DQ[4]/DDR0_DQ[20]

AF67

DDR1_DQ[5]/DDR0_DQ[21]

AK67

DDR1_DQ[6]/DDR0_DQ[22]

AK66

DDR1_DQ[7]/DDR0_DQ[23]

AF70

DDR1_DQ[8]/DDR0_DQ[24]

AF68

DDR1_DQ[9]/DDR0_DQ[25]

AH71

DDR1_DQ[10]/DDR0_DQ[26]

AH68

DDR1_DQ[11]/DDR0_DQ[27]

AF71

DDR1_DQ[12]/DDR0_DQ[28]

AF69

DDR1_DQ[13]/DDR0_DQ[29]

AH70

DDR1_DQ[14]/DDR0_DQ[30]

AH69

DDR1_DQ[15]/DDR0_DQ[31]

BB65

DDR0_DQ[16]/DDR0_DQ[32]

AW65

DDR0_DQ[17]/DDR0_DQ[33]

AW63

DDR0_DQ[18]/DDR0_DQ[34]

AY63

DDR0_DQ[19]/DDR0_DQ[35]

BA65

DDR0_DQ[20]/DDR0_DQ[36]

AY65

DDR0_DQ[21]/DDR0_DQ[37]

BA63

DDR0_DQ[22]/DDR0_DQ[38]

BB63

DDR0_DQ[23]/DDR0_DQ[39]

BA61

DDR0_DQ[24]/DDR0_DQ[40]

AW61

DDR0_DQ[25]/DDR0_DQ[41]

BB59

DDR0_DQ[26]/DDR0_DQ[42]

AW59

DDR0_DQ[27]/DDR0_DQ[43]

BB61

DDR0_DQ[28]/DDR0_DQ[44]

AY61

DDR0_DQ[29]/DDR0_DQ[45]

BA59

DDR0_DQ[30]/DDR0_DQ[46]

AY59

DDR0_DQ[31]/DDR0_DQ[47]

AT66

DDR1_DQ[16]/DDR0_DQ[48]

AU66

DDR1_DQ[17]/DDR0_DQ[49]

AP65

DDR1_DQ[18]/DDR0_DQ[50]

AN65

DDR1_DQ[19]/DDR0_DQ[51]

AN66

DDR1_DQ[20]/DDR0_DQ[52]

AP66

DDR1_DQ[21]/DDR0_DQ[53]

AT65

DDR1_DQ[22]/DDR0_DQ[54]

AU65

DDR1_DQ[23]/DDR0_DQ[55]

AT61

DDR1_DQ[24]/DDR0_DQ[56]

AU61

DDR1_DQ[25]/DDR0_DQ[57]

AP60

DDR1_DQ[26]/DDR0_DQ[58]

AN60

DDR1_DQ[27]/DDR0_DQ[59]

AN61

DDR1_DQ[28]/DDR0_DQ[60]

AP61

DDR1_DQ[29]/DDR0_DQ[61]

AT60

DDR1_DQ[30]/DDR0_DQ[62]

AU60

DDR1_DQ[31]/DDR0_DQ[63]

SKYLAKE-U-GP

SKYLAKE-U-GP

SKYLAKE_ULT

SKYLAKE_ULT

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[ 5]

DDR0_DQ[16]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[ 9]

DDR0_DQ[17]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[ 6]

DDR0_DQ[18]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[ 8]

DDR0_DQ[19]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[ 7]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_DQ[20]

DDR0_DQ[21]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[ 12]

DDR0_DQ[22]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[ 11]

DDR0_DQ[23]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT #

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[ 13]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[ 2]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[ 10]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[ 1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[ 0]

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR CH - A

DDR CH - A

2 OF 20

2 OF 20

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_MA[3]

DDR0_MA[4]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_ALERT#

DDR0_PAR

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

AU53

AT53

AU55

AT55

BA56

BB56

AW56

AY56

AU45

AU43

AT45

AT43

BA51

BB54

BA52

AY52

AW52

AY55

AW54

BA54

BA55

AY54

AU46

AU48

AT46

AU50

AU52

AY51

AT48

AT50

BB50

AY50

BA50

BB52

AM70

AM69

AT69

AT70

AH66

AH65

AG69

AG70

BA64

AY64

AY60

BA60

AR66

AR65

AR61

AR60

AW50

AT52

AY67

AY68

BA67

AW67

M_A_A5

M_A_A9

M_A_A6

M_A_A8

M_A_A7

M_A_A12

M_A_A11

M_A_A13

M_A_A15

M_A_A14

M_A_A16

M_A_A2

M_A_A10

M_A_A1

M_A_A0

M_A_A3

M_A_A4

M_A_DQS_DN0

M_A_DQS_DP0

M_A_DQS_DN1

M_A_DQS_DP1

M_A_DQS_DN4

M_A_DQS_DP4

M_A_DQS_DN5

M_A_DQS_DP5

M_A_DQS_DN2

M_A_DQS_DP2

M_A_DQS_DN3

M_A_DQS_DP3

M_A_DQS_DN6

M_A_DQS_DP6

M_A_DQS_DN7

M_A_DQS_DP7

SM_PGCNTL

M_A_CLK#0 [12]

M_A_CLK0 [12]

M_A_CLK#1 [12]

M_A_CLK1 [12]

M_A_CKE0 [12]

M_A_CKE1 [12]

M_A_CS#0 [12]

M_A_CS#1 [12]

M_A_DIMA_ODT0 [12]

M_A_DIMA_ODT1 [12]

M_A_A5 [12]

M_A_A9 [12]

M_A_A6 [12]

M_A_A8 [12]

M_A_A7 [12]

M_A_BG0 [12]

M_A_A12 [12]

M_A_A11 [12]

M_A_ACT_N [12]

M_A_BG1 [12]

M_A_A13 [12]

M_A_A15 [12]

M_A_A14 [12]

M_A_A16 [12]

M_A_BA0 [12]

M_A_A2 [12]

M_A_BA1 [12]

M_A_A10 [12]

M_A_A1 [12]

M_A_A0 [12]

M_A_A3 [12]

M_A_A4 [12]

M_A_DQS0

M_A_DQS1

M_A_DQS4

M_A_DQS5

M_A_DQS2

M_A_DQS3

M_A_DQS6

M_A_DQS7

M_A_ALERT_N [12]

M_A_PARITY [12]

V_SM_VREF_CN TA [12]

V_SM_VREF_CN TB [13]

SM_PGCNTL

M_B_DQ[0:7]

M_B_DQ[8:15]

M_B_DQ[32:39]

M_B_DQ[40:47]

M_B_DQ[16:23]

M_B_DQ[24:31]

M_B_DQ[48:55]

M_B_DQ[56:63]

3D3V_S5

12

DS

G

R507

R507

10KR2J-3-GP

10KR2J-3-GP

Q501

Q501

DMN5L06K-7-G P

DMN5L06K-7-G P

84.05067.031

84.05067.031

Q502_G

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_DQ0[13]

M_B_DQ1[13]

M_B_DQ2[13]

M_B_DQ3[13]

M_B_DQ4[13]

M_B_DQ5[13]

M_B_DQ6[13]

M_B_DQ7[13]

M_B_DQ8[13]

M_B_DQ9[13]

M_B_DQ10[13]

M_B_DQ11[13]

M_B_DQ12[13]

M_B_DQ13[13]

M_B_DQ14[13]

M_B_DQ15[13]

M_B_DQ32[13]

M_B_DQ33[13]

M_B_DQ34[13]

M_B_DQ35[13]

M_B_DQ36[13]

M_B_DQ37[13]

M_B_DQ38[13]

M_B_DQ39[13]

M_B_DQ40[13]

M_B_DQ41[13]

M_B_DQ42[13]

M_B_DQ43[13]

M_B_DQ44[13]

M_B_DQ45[13]

M_B_DQ46[13]

M_B_DQ47[13]

M_B_DQ16[13]

M_B_DQ17[13]

M_B_DQ18[13]

M_B_DQ19[13]

M_B_DQ20[13]

M_B_DQ21[13]

M_B_DQ22[13]

M_B_DQ23[13]

M_B_DQ24[13]

M_B_DQ25[13]

M_B_DQ26[13]

M_B_DQ27[13]

M_B_DQ28[13]

M_B_DQ29[13]

M_B_DQ30[13]

M_B_DQ31[13]

M_B_DQ48[13]

M_B_DQ49[13]

M_B_DQ50[13]

M_B_DQ51[13]

M_B_DQ52[13]

M_B_DQ53[13]

M_B_DQ54[13]

M_B_DQ55[13]

M_B_DQ56[13]

M_B_DQ57[13]

M_B_DQ58[13]

M_B_DQ59[13]

M_B_DQ60[13]

M_B_DQ61[13]

M_B_DQ62[13]

M_B_DQ63[13]

AY39

AW39

AY37

AW37

BB39

BA39

BA37

BB37

AY35

AW35

AY33

AW33

BB35

BA35

BA33

BB33

AU40

AT40

AT37

AU37

AR40

AP40

AP37

AR37

AT33

AU33

AU30

AT30

AR33

AP33

AR30

AP30

AY31

AW31

AY29

AW29

BB31

BA31

BA29

BB29

AY27

AW27

AY25

AW25

BB27

BA27

BA25

BB25

AU27

AT27

AT25

AU25

AP27

AN27

AN25

AP25

AT22

AU22

AU21

AT21

AN22

AP22

AP21

AN21

Q502

Q502

G

S

2N7002K-2-GP

2N7002K-2-GP

84.2N702.J31

84.2N702.J31

2ND = 84.2N702.031

2ND = 84.2N702.031

3rd = 84.07002.I31

3rd = 84.07002.I31

CPU1C

CPU1C

DDR0_DQ[32]/DDR1_DQ[0]

DDR0_DQ[33]/DDR1_DQ[1]

DDR0_DQ[34]/DDR1_DQ[2]

DDR0_DQ[35]/DDR1_DQ[3]

DDR0_DQ[36]/DDR1_DQ[4]

DDR0_DQ[37]/DDR1_DQ[5]

DDR0_DQ[38]/DDR1_DQ[6]

DDR0_DQ[39]/DDR1_DQ[7]

DDR0_DQ[40]/DDR1_DQ[8]

DDR0_DQ[41]/DDR1_DQ[9]

DDR0_DQ[42]/DDR1_DQ[10]

DDR0_DQ[43]/DDR1_DQ[11]

DDR0_DQ[44]/DDR1_DQ[12]

DDR0_DQ[45]/DDR1_DQ[13]

DDR0_DQ[46]/DDR1_DQ[14]

DDR0_DQ[47]/DDR1_DQ[15]

DDR1_DQ[32]/DDR1_DQ[16]

DDR1_DQ[33]/DDR1_DQ[17]

DDR1_DQ[34]/DDR1_DQ[18]

DDR1_DQ[35]/DDR1_DQ[19]

DDR1_DQ[36]/DDR1_DQ[20]

DDR1_DQ[37]/DDR1_DQ[21]

DDR1_DQ[38]/DDR1_DQ[22]

DDR1_DQ[39]/DDR1_DQ[23]

DDR1_DQ[40]/DDR1_DQ[24]

DDR1_DQ[41]/DDR1_DQ[25]

DDR1_DQ[42]/DDR1_DQ[26]

DDR1_DQ[43]/DDR1_DQ[27]

DDR1_DQ[44]/DDR1_DQ[28]

DDR1_DQ[45]/DDR1_DQ[29]

DDR1_DQ[46]/DDR1_DQ[30]

DDR1_DQ[47]/DDR1_DQ[31]

DDR0_DQ[48]/DDR1_DQ[32]

DDR0_DQ[49]/DDR1_DQ[33]

DDR0_DQ[50]/DDR1_DQ[34]

DDR0_DQ[51]/DDR1_DQ[35]

DDR0_DQ[52]/DDR1_DQ[36]

DDR0_DQ[53]/DDR1_DQ[37]

DDR0_DQ[54]/DDR1_DQ[38]

DDR0_DQ[55]/DDR1_DQ[39]

DDR0_DQ[56]/DDR1_DQ[40]

DDR0_DQ[57]/DDR1_DQ[41]

DDR0_DQ[58]/DDR1_DQ[42]

DDR0_DQ[59]/DDR1_DQ[43]

DDR0_DQ[60]/DDR1_DQ[44]

DDR0_DQ[61]/DDR1_DQ[45]

DDR0_DQ[62]/DDR1_DQ[46]

DDR0_DQ[63]/DDR1_DQ[47]

DDR1_DQ[48]

DDR1_DQ[49]

DDR1_DQ[50]

DDR1_DQ[51]

DDR1_DQ[52]

DDR1_DQ[53]

DDR1_DQ[54]

DDR1_DQ[55]

DDR1_DQ[56]

DDR1_DQ[57]

DDR1_DQ[58]

DDR1_DQ[59]

DDR1_DQ[60]

DDR1_DQ[61]

DDR1_DQ[62]

DDR1_DQ[63]

SKYLAKE-U-GP

SKYLAKE-U-GP

3D3V_S0

12

R506

R506

220KR2F-GP

220KR2F-GP

D

SKYLAKE_ULT

SKYLAKE_ULT

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[ 5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[ 9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[ 6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[ 8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[ 7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[ 12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[ 11]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT #

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[ 13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[ 2]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[ 10]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[ 1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[ 0]

DDR CH - B

DDR CH - B

SM_PGCNTL_R [51]

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_MA[3]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR1_MA[4]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DDR1_PAR

DRAM_RESET#

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

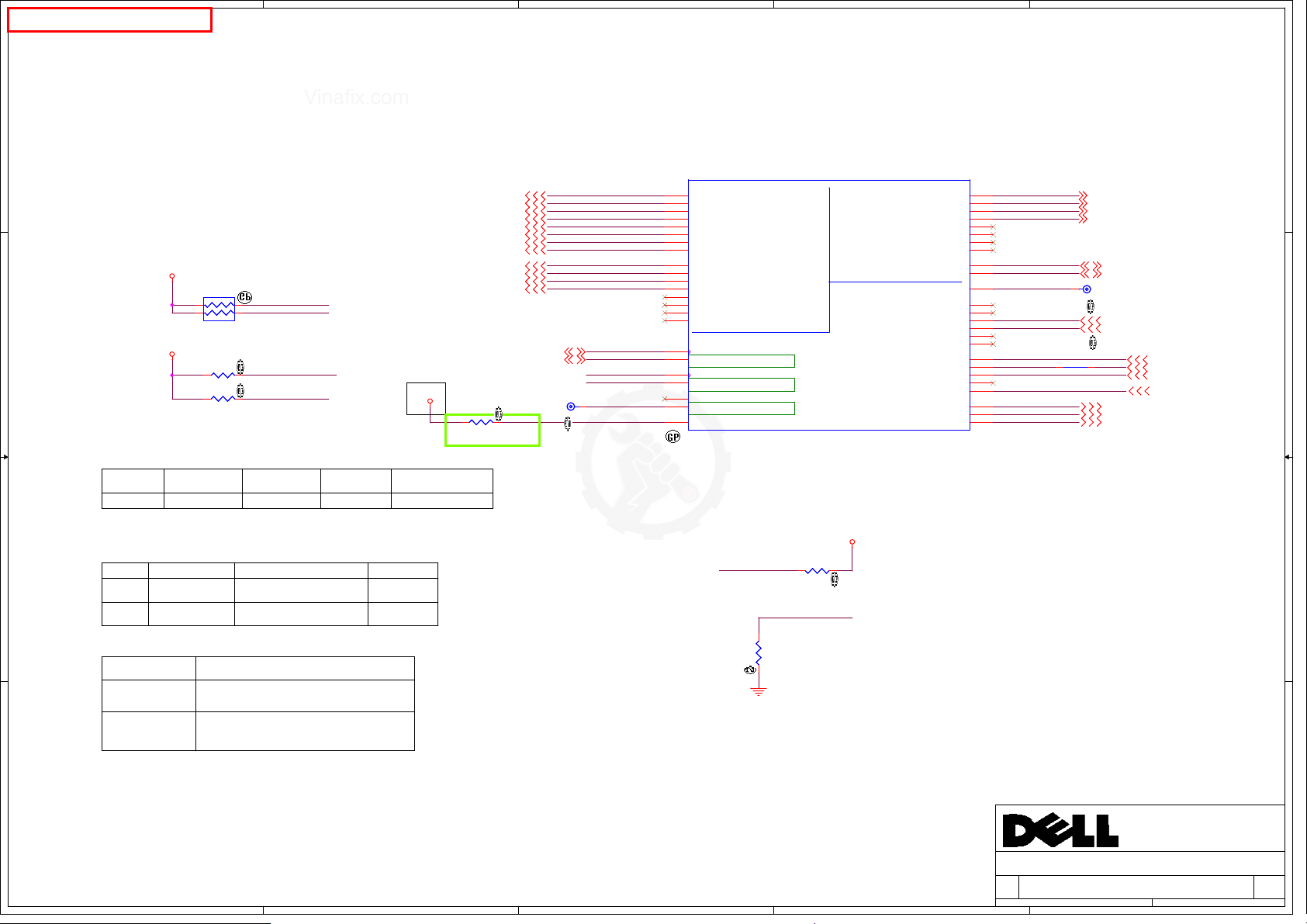

Design Guideline:

Design Guideline:

SM_RCOMP keep routing length less than 500 mils.

SM_RCOMP keep routing length less than 500 mils.

3 OF 20

3 OF 20

AN45

AN46

AP45

AP46

AN56

AP55

AN55

AP53

BB42

AY42

BA42

AW42

AY48

AP50

BA48

BB48

AP48

AP52

AN50

AN48

AN53

AN52

BA43

AY43

AY44

AW44

BB44

AY47

BA44

AW46

AY46

BA46

BB46

BA47

BA38

AY38

AY34

BA34

AT38

AR38

AT32

AR32

BA30

AY30

AY26

BA26

AR25

AR27

AR22

AR21

AN43

AP43

AT13

AR18

AT18

AU18

M_B_A5

M_B_A9

M_B_A6

M_B_A8

M_B_A7

M_B_A12

M_B_A11

M_B_ACT_N

M_B_A13

M_B_A15

M_B_A14

M_B_A16

M_B_A2

M_B_A10

M_B_A1

M_B_A0

M_B_A3

M_B_A4

M_B_DQS_DN0

M_B_DQS_DP0

M_B_DQS_DN1

M_B_DQS_DP1

M_B_DQS_DN4

M_B_DQS_DP4

M_B_DQS_DN5

M_B_DQS_DP5

M_B_DQS_DN2

M_B_DQS_DP2

M_B_DQS_DN3

M_B_DQS_DP3

M_B_DQS_DN6

M_B_DQS_DP6

M_B_DQS_DN7

M_B_DQS_DP7

SM_DRAMRST #

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

#543016

M_B_CLK#0 [13]

M_B_CLK#1 [13]

M_B_CLK0 [13]

M_B_CLK1 [13]

M_B_CKE0 [13]

M_B_CKE1 [13]

M_B_CS#0 [13]

M_B_CS#1 [13]

M_B_DIMB_ODT0 [13]

M_B_DIMB_ODT1 [13]

M_B_A5 [13]

M_B_A9 [13]

M_B_A6 [13]

M_B_A8 [13]

M_B_A7 [13]

M_B_BG0 [13]

M_B_A12 [13]

M_B_A11 [13]

M_B_ACT_N [13]

M_B_BG1 [13]

M_B_A13 [13]

M_B_A15 [13]

M_B_A14 [13]

M_B_A16 [13]

M_B_BA0 [13]

M_B_A2 [13]

M_B_BA1 [13]

M_B_A10 [13]

M_B_A1 [13]

M_B_A0 [13]

M_B_A3 [13]

M_B_A4 [13]

M_B_DQS0

M_B_DQS1

M_B_DQS4

M_B_DQS5

M_B_DQS2

M_B_DQS3

M_B_DQS6

M_B_DQS7

M_B_ALERT_N [13]

M_B_PARITY [13]

R501 121R2F- GPR501 121R2F- GP

1 2

R502 80D6R2F -L-GPR 502 80D6R2F -L-GP

1 2

R503 100R2F- L1-GP-UR503 100R2F- L1-GP-U

1 2

Layout Note:Layout Note:

1D2V_S3

12

close to CPU

R505

R505

470R2F-GP

470R2F-GP

DY

DY

1 2

R504

R504

1 2

Do Not Stuff

Do Not Stuff

ED502

ED502

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

DDR4_DR AMRST# [12,13]

M_A_DQS_DN0

M_A_DQS_DN1

M_A_DQS_DN2

M_A_DQS_DN3

M_A_DQS_DN4

M_A_DQS_DN5

M_A_DQS_DN6

3

M_A_DQS_DN7

M_A_DQS_DP0

M_A_DQS_DP1

M_A_DQS_DP2

M_A_DQS_DP3

M_A_DQS_DP4

M_A_DQS_DP5

M_A_DQS_DP6

M_A_DQS_DP7

A A

5

4

M_A_DQS_DN[7: 0] [12] M_B_DQS_DN[7: 0] [13]

M_A_DQS_DP[7:0] [12]

M_B_DQS_DN0

M_B_DQS_DN1

M_B_DQS_DN2

M_B_DQS_DN3

M_B_DQS_DN4

M_B_DQS_DN5

M_B_DQS_DN6

M_B_DQS_DN7

M_B_DQS_DP0

M_B_DQS_DP1

M_B_DQS_DP2

M_B_DQS_DP3

M_B_DQS_DP4

M_B_DQS_DP5

M_B_DQS_DP6

M_B_DQS_DP7

2

M_B_DQS_DP[7:0] [13]

2.DIS

2.DIS

2.DIS

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin T ai Wu Rd ., Hsichih,

21F, 88, Sec.1, Hsin T ai Wu Rd ., Hsichih,

21F, 88, Sec.1, Hsin T ai Wu Rd ., Hsichih,

Taipei Hsie n 221, Taiwan, R.O. C.

Taipei Hsie n 221, Taiwan, R.O. C.

Title

Title

Title

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

A2

A2

A2

Date: Sheet of

Date: Sheet of

Date: Sheet of

Taipei Hsie n 221, Taiwan, R.O. C.

CPU_(DDR)

CPU_(DDR)

CPU_(DDR)

Taos KBL-U

Taos KBL-U

Taos KBL-U

1

5 105Monday, Decemb er 26, 2016

5 105Monday, Decemb er 26, 2016

5 105Monday, Decemb er 26, 2016

X00

X00

X00

Page 6

Vinafix.com

5

4

3

2

1

Main Func = CPU

CPU1S

CPU1S

RESERVED SIGNALS-1

CFG[19:0][99]

D D

ITP_PMODE[99]

C C

TP601Do Not Stuff TP601Do Not Stuff

TP602Do Not Stuff TP602Do Not Stuff

B B

PCH strap pin:

CFG3

DY

DY

12

R604

R604

Do Not Stuff

Do Not Stuff

12

1

1

R60149D9R2F-GP R60149D9R2F-GP

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG_RCOMP

RSVD_TP_BA70

RSVD_TP_BA68

G69

G68

H70

G71

H69

G70

E63

E66

E60

AY2

AY1

K46

K45

AL25

AL27

C71

B70

A52

BA70

BA68

G65

E61

E68

B67

D65

D67

E70

C68

D68

C67

F71

F70

F63

F66

F60

J71

J68

F65

F61

E8

D1

D3

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[16]

CFG[17]

CFG[18]

CFG[19]

CFG_RCOMP

ITP_PMODE

RSVD#AY2

RSVD#AY1

RSVD#D1

RSVD#D3

RSVD#K46

RSVD#K45

RSVD#AL25

RSVD#AL27

RSVD#C71

RSVD#B70

RSVD#F60

RSVD#A52

RSVD_TP#BA70

RSVD_TP#BA68

RSVD#J71

RSVD#J68

VSS

VSS

RSVD#F61

RSVD#E61

SKYLAKE-U-GP

SKYLAKE-U-GP

[BDW Only]PHYSICAL_DEBUG_ENABLED (DFX PRIVACY)

0 : ENABLED

CFG[3]

SET DFX ENABLED BIT IN DEBUG INTERFACE MSR

RESERVED SIGNALS-1

SKYLAKE_ULT

SKYLAKE_ULT

RSVD_TP_AW71

RSVD_TP_AW70

1 : DISABLED

CFG4

12

R605

R605

1KR2J-1-GP

1KR2J-1-GP

(#543016)

DISPLAY PORT PRESENCE STRAP

0 : ENABLED

CFG[4]

An external Display Port device is connected to the Embedded Display Port.

1 : DISABLED (Default)

No Physical Display Port attached to Embedded DisplayPort*. No connect for disable.

19 OF 20

19 OF 20

RSVD_TP#BB68

RSVD_TP#BB69

RSVD_TP#AK13

RSVD_TP#AK12

RSVD#BB2

RSVD#BA3

TP5

TP6

RSVD#D5

RSVD#D4

RSVD#B2

RSVD#C2

RSVD#B3

RSVD#A3

RSVD#AW1

RSVD#E1

RSVD#E2

RSVD#BA4

RSVD#BB4

RSVD#A4

RSVD#C4

TP4

RSVD#A69

RSVD#B69

RSVD#AY3

RSVD#D71

RSVD#C70

RSVD#C54

RSVD#D54

TP1

TP2

VSS

ZVM#

RSVD_TP#AW71

RSVD_TP#AW70

MSM#

PROC_SELECT#

BB68

BB69

AK13

AK12

BB2

BA3

AU5

AT5

D5

D4

B2

C2

B3

A3

AW1

E1

E2

BA4

BB4

A4

C4

BB5

A69

B69

AY3

D71

C70

C54

D54

AY4

BB3

AY71

AR56

AW71

AW70

AP56

C64

RSVD_TP_BB68

RSVD_TP_BB69

RSVD_TP_AK13

RSVD_TP_AK12

TP5_AU5

TP6_AT5

TP4_BB5

TP1_AY4

TP2_BB3

VSS_AY71

ZVM#

RSVD_TP_AW71

RSVD_TP_AW70

MSM#

PROC_SELECT#

R602

R602

1 2

Do Not Stuff

Do Not Stuff

1 2

R603

R603

Do Not Stuff

Do Not Stuff

DY

DY

1

1

1

1

1

1

1

1

1

1

1

1

1

TP603 Do Not StuffTP603 Do Not Stuff

TP604 Do Not StuffTP604 Do Not Stuff

TP605 Do Not StuffTP605 Do Not Stuff

TP606 Do Not StuffTP606 Do Not Stuff

TP607 Do Not StuffTP607 Do Not Stuff

TP608 Do Not StuffTP608 Do Not Stuff

TP609 Do Not StuffTP609 Do Not Stuff

TP610 Do Not StuffTP610 Do Not Stuff

TP611 Do Not StuffTP611 Do Not Stuff

TP616 Do Not StuffTP616 Do Not Stuff

TP614 Do Not StuffTP614 Do Not Stuff

TP615 Do Not StuffTP615 Do Not Stuff

TP617 Do Not StuffTP617 Do Not Stuff

#54469 CRB.

CFG TERMINATIONS

20140807 david

#544669 Rev0.52 (CRB)

+VCCST_CPU

A A

5

SKL(#543016):

Processor strap CFG[4] should be pulled low to enable embedded DisplayPort*

4

3

2.DIS

2.DIS

2.DIS

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

CPU_(RESERVED)

CPU_(RESERVED)

CPU_(RESERVED)

Taos KBL-U

Taos KBL-U

Taos KBL-U

6 105Monday, December 26, 2016

6 105Monday, December 26, 2016

6 105Monday, December 26, 2016

1

X00

X00

X00

Page 7

Vinafix.com

5

4

3

2

1

Main Func = CPU

CPU1M

AA63

AA64

AA66

AA67

AA69

AA70

AA71

AC64

AC65

AC66

AC67

AC68

AC69

AC70

AC71

A48

A53

A58

A62

A66

J43

J45

J46

J48

J50

J52

J53

J55

J56

J58

J60

K48

K50

K52

K53

K55

K56

K58

K60

L62

L63

L64

L65

L66

L67

L68

L69

L70

L71

M62

N63

N64

N66

N67

N69

J70

J69

CPU1M

CPU POWER 2 OF 4

CPU POWER 2 OF 4

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT_SENSE

VSSGT_SENSE

SKYLAKE-U-GP

SKYLAKE-U-GP

SKYLAKE_ULT

SKYLAKE_ULT

+VCCGT

CPU1L

AM32

AM33

AM35

AM37

AM38

AG62

AK33

AK35

AK37

AK38

AK40

AL33

AL37

AL40

AK32

AB62

AC63

AE63

AE62

AL63

AJ62

A30

A34

A39

A44

G30

K32

P62

V62

H63

G61

CPU1L

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

RSVD_K32

RSVD#K32

RSVD_AK32

RSVD#AK32

VCCOPC

VCCOPC

VCCOPC

VCC_OPC_1P8

VCC_OPC_1P8

VCCOPC_SENSE

VSSOPC_SENSE

VCCEOPIO

VCCEOPIO

VCCEOPIO_SENSE

VSSEOPIO_SENSE

SKYLAKE-U-GP

SKYLAKE-U-GP

CPU POWER 1 OF 4

CPU POWER 1 OF 4

SKYLAKE_ULT

SKYLAKE_ULT

VCC_CORE VCC_C ORE

D D

12

FC701Do Not StuffDYFC701Do Not Stuff

DY

TP704Do N ot Stuff TP7 04Do Not Stuff

C C

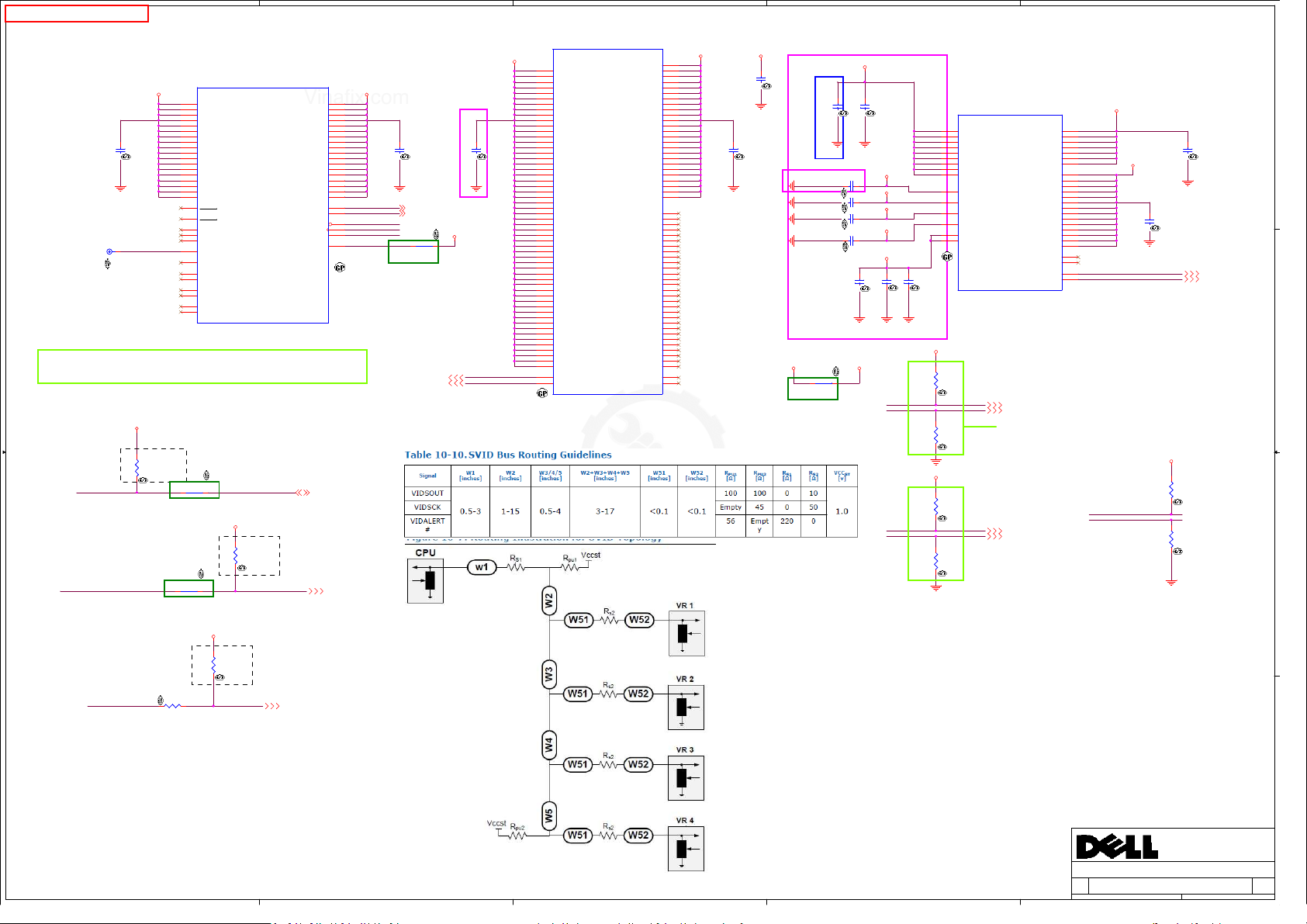

Layout Note:

The total Length of Data and Clock (from CPU to each VR) must be equal (±0.1 inch).

Route the Alert signal between the Clock and the Data signals.

VCC_OPC_1P8 _H63

1

12 OF 20

12 OF 20

VCC_SENSE

VSS_SENSE

VIDALERT#

VIDSCK

VIDSOUT

VCCSTG

G32

VCC

G33

VCC

G35

VCC

G37

VCC

G38

VCC

G40

VCC

G42

VCC

J30

VCC

J33

VCC

J37

VCC

J40

VCC

K33

VCC

K35

VCC

K37

VCC

K38

VCC

K40

VCC

K42

VCC

K43

VCC

E32

E33

H_CPU_SVIDALR T#

B63

H_CPU_SVIDC LK

A63

H_CPU_SVIDD AT

D64

+VCCFUSE PRG

G20

20160607 add 0.1u to +Vccgt don’t DY

12

FC702Do Not StuffDYFC702Do Not Stuff

DY

VCC_SENSE [7,46]

VSS_SENSE [7,46 ]

R703

R703

1 2

Do Not Stuff

Do Not Stuff

20161024 0ohm to short pad

VCCGT_SEN SE[7,46]

VSSGT_SENSE[7,46]

+VCCSTG

12

FC703SCD1U25V2KX-GP

FC703SCD1U25V2KX-GP

WWAN

WWAN

SVID DATA

+VCCST_CP U

CLOSE TO CPU

H_CPU_SVIDD AT

SVID CLOCK

B B

H_CPU_SVIDC LK

12

R726

R726

#543016

100R2F-L1-GP- U

100R2F-L1-GP- U

1 2

20161024 0ohm to short pad

Do Not Stuff

Do Not Stuff

R732

R732

1 2

20161024 0ohm to short pad

Do Not Stuff

Do Not Stuff

R709

R709

+VCCST_CP U

12

R723

R723

DY

DY

Do Not Stuff

Do Not Stuff

#543016

CLOSE TO VR

VR_SVID_DATA [46]

VR_SVID_CLK [46]

SVID_543016:

13 OF 20

13 OF 20

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX

VCCGTX_SENSE

VSSGTX_SENSE

N70

N71

R63

R64

R65

R66

R67

R68

R69

R70

R71

T62

U65

U68

U71

W63

W64

W65

W66

W67

W68

W69

W70

W71

Y62

AK42

AK43

AK45

AK46

AK48

AK50

AK52

AK53

AK55

AK56

AK58

AK60

AK70

AL43

AL46

AL50

AL53

AL56

AL60

AM48

AM50

AM52

AM53

AM56

AM58

AU58

AU63

BB57

BB66

AK62

AL61

+VCCGT

+VDDQ_CPU _CLK

12

FC704Do Not StuffDYFC704Do Not Stuff

DY

20160617 follow up vegas as the same DY

12

DY

DY

20160822 DY to stuff 1u to 470P by RF

C722

C722

Do Not Stuff

Do Not Stuff

FC705

FC705

20160712 stuff by location

#544669 CRB.

R705

R705

1 2

Do Not Stuff

Do Not Stuff

20161024 0ohm to short pad

SC470P50V2KX-L-GP

SC470P50V2KX-L-GP

WWAN

WWAN

12

DY

DY

DY

DY

DY

DY

+VDDQ_CPU _CLK1D2V_S3

1D2V_S3

12

12

12

12

FC708Do Not StuffDYFC708Do Not Stuff

DY

DY

DY

12

12

C719

C719

Do Not Stuff

Do Not Stuff

+VDDQ_CPU _CLK

C715S C10U6D3V3MX- GP C715SC10U6D3V3MX-GP

+VCCST_CP U

C716D o Not Stuff

C716D o Not Stuff

+VCCSTG

C717D o Not Stuff

C717D o Not Stuff

1D2V_S3

C718D o Not Stuff

C718D o Not Stuff

+V1.00U_CPU

12

AK28

AK30

AL30

AL42

AM28

AM30

AM42

AK23

AK25

G23

G25

G27

G28

J22

J23

J27

K23

K25

K27

K28

K30

AM23

AM22

H21

H20

+VCCIO

+VCCIO(ICCMAX.=2.73A)

+VCCSA

VCCSA_SENS E

VSSSA_SENSE

12

FC706Do Not StuffDYFC706Do Not Stuff

DY

12

FC707Do Not StuffDYFC707Do Not Stuff

DY

VSSSA_SENSE [46]

VCCSA_SENS E [ 46]

+VCCSA

12

R735

R735

100R2F-L1-GP- U

100R2F-L1-GP- U

12

R734

R734

100R2F-L1-GP- U

100R2F-L1-GP- U

CPU1N

CPU1N

CPU POWER 3 OF 4

CPU POWER 3 OF 4

AU23

VDDQ

AU28

VDDQ

AU35

VDDQ

AU42

VDDQ

BB23

VDDQ

BB32

VDDQ

BB41

VDDQ

BB47

VDDQ

BB51

VDDQ

AM40

0.12 A

C721

C721

Do Not Stuff

Do Not Stuff

VCC_CORE

+VCCGT

A18

A22

AL23

K20

K21

12

R719

R719

100R2F-L1-GP- U

100R2F-L1-GP- U

12

R720

R720

100R2F-L1-GP- U

100R2F-L1-GP- U

12

R721

R721

100R2F-L1-GP- U

100R2F-L1-GP- U

12

R722

R722

100R2F-L1-GP- U

100R2F-L1-GP- U

VDDQC

VCCST

VCCSTG

VCCPLL_OC

VCCPLL

VCCPLL

SKYLAKE-U-GP

SKYLAKE-U-GP

0.04 A

12

C720

C720

DY

DY

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

14 OF 20

14 OF 20

VCCIO

VCCIO

SKYLAKE_ULT

SKYLAKE_ULT

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCIO_SENSE

VSSIO_SENSE

VSSSA_SENSE

VCCSA_SENSE

VCC_SENSE [7,46]

VSS_SENSE [7,46]

Layout Note:

1. Place close to CPU

2. VCC_SENSE/ VSS_SENSE

impedance=50 ohm

3. Length match<25mil

VCCGT_SEN SE [7,46]

VSSGT_SENSE [7,46]

+VCCST_CP U

#543016

12

CLOSE TO CPU

R727

R727

56R2J-4-GP

56R2J-4-GP

R728

H_CPU_SVIDALR T#

A A

R728

12

220R2J-L2-GP

220R2J-L2-GP

5

VR_SVID_ALERT# [46]

2.DIS

2.DIS

2.DIS

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin T ai Wu Rd ., Hsichih,

21F, 88, Sec.1, Hsin T ai Wu Rd ., Hsichih,

21F, 88, Sec.1, Hsin T ai Wu Rd ., Hsichih,

Taipei Hsie n 221, Taiwan, R.O. C.

Taipei Hsie n 221, Taiwan, R.O. C.

Title

Title

Title

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

A2

A2

A2

Monday, Decemb er 26, 2016

Monday, Decemb er 26, 2016

Monday, Decemb er 26, 2016

Date: Sheet of

Date: Sheet of

4

3

2

Date: Sheet of

Taipei Hsie n 221, Taiwan, R.O. C.

CPU(VCC_CORE)

CPU(VCC_CORE)

CPU(VCC_CORE)

Taos KBL-U

Taos KBL-U

Taos KBL-U

1

7 105

7 105

7 105

X00

X00

X00

Page 8

Vinafix.com

5

4

3

2

1

Main Func = CPU

D D

CPU1A

CPU1A

SKYLAKE_ULT

HDMI_DATA2#[57]

HDMI_DATA2[57]

HDMI

3D3V_S0

RN801

RN801

2 3

1

SRN2K2J-1-GP

SRN2K2J-1-GP

C C

3D3V_S0

R804

R804

1 2

2K2R2J-2-GP

2K2R2J-2-GP

R803

R803

1 2

Do Not Stuff

Do Not Stuff

DY

DY

CPU_DP1_CTRL_DATA

CPU_DP1_CTRL_CLK

4

CPU_DP2_CTRL_DATA

CPU_DP2_CTRL_CLK

DP to VGA

HDMI

Check

+VCCIO

HDMI_DATA1#[57]

HDMI_DATA1[57]

HDMI_DATA0#[57]

HDMI_DATA0[57]

HDMI_CLK#[57]

PCH_DPC_N0[66]

PCH_DPC_P0[66]

PCH_DPC_N1[66]

PCH_DPC_P1[66]

R801

R801

1 2

24D9R2F-L-GP

24D9R2F-L-GP

HDMI_CLK[57]

CPU_DP1_CTRL_CLK[57]

CPU_DP1_CTRL_DATA[57]

Do Not Stuff

Do Not Stuff

TP802

TP802

CPU_DP2_CTRL_CLK

CPU_DP2_CTRL_DATA

DDPD_CTRLDATA

1

EDP_COMP

(#543016) eDP_RCOMP Guideline

Signal Trace

Width

eDP_RCOMP 20 mils 25 mils 24.9 Ω ±1%

Isolation

Spacing

Resistor

Value

Length

Max = 100 mils

E55

DDI1_TXN[0]

F55

DDI1_TXP[0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[2]

F56

DDI1_TXN[3]

G56

DDI1_TXP[3]

C50

DDI2_TXN[0]

D50

DDI2_TXP[0]

C52

DDI2_TXN[1]

D52

DDI2_TXP[1]

A50

DDI2_TXN[2]

B50

DDI2_TXP[2]

D51

DDI2_TXN[3]

C51

DDI2_TXP[3]

L13

GPP_E18/DDPB_CTRLCLK

L12

GPP_E19/DDPB_CTRLDATA

N7

GPP_E20/DDPC_CTRLCLK

N8

GPP_E21/DDPC_CTRLDATA

N11

GPP_E22

N12

GPP_E23

E52

EDP_RCOMP

SKYLAKE-U-GP

SKYLAKE-U-GP

(#543016) The Skylake U/Y processor supports only two DDI ports - Port 1 and Port 2.

SKYLAKE_ULT

DDI

DDI

DISPLAY SIDEBANDS

DISPLAY SIDEBANDS

Strap

Strap

Strap

EDP

EDP

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

1 OF 20

1 OF 20

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

RSVD#G46

RSVD#F46

GPP_E17/EDP_HPD

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

C47

C46

D46

C45

A45

B45

A47

B47

E45

F45

B52

G50

F50

E48

F48

G46

F46

L9

L7

L6

N9

L10

R12

R11

U13

EDP_DISP_UTIL

CPU_DP2_HPD1

1

R805

R805

1 2

Do Not Stuff

Do Not Stuff

eDP_TX_CPU_N0 [55]

eDP_TX_CPU_P0 [55]

eDP_TX_CPU_N1 [55]

eDP_TX_CPU_P1 [55]

eDP_AUX_CPU_N [55]

eDP_AUX_CPU_P [55]

TP801 Do Not StuffTP801 Do Not Stuff

PCH_DPC_AUXN [66]

PCH_DPC_AUXP [66]

CPU_DP1_HPD [57]

CPU_DP2_HPD [66]

SIO_EXT_SMI#_R [24]

EDP_HPD [55]

L_BKLT_EN [24]

L_BKLT_CTRL [55]

EDP_VDD_EN [55]

3D3V_S0

(#543016) DDI Disabling and Termination Guidelines

B B

Port Strap Enable Port Disable Port

Port 1

Port 2

DDPB_CTRLDATA

DDPC_CTRLDATA

PU to 3.3 V with 2.2-k

±5% resistor

PU to 3.3 V with 2.2-k

±5% resistor

NC

NC

SIO_EXT_SMI#_R

Strap pin:

Port B /

Port C Detected

DDPB_CTRLDATA

DDPC_CTRLDATA

These two signals have weak internal pull-down.

Design Guideline:

Skylake processor signal eDP_RCOMP should be connected to the VCCIO rail via a single 24.9 ±1% Ω resistor.

A A

5

Sampled at rising edge of PCH_PWROK

0 = Port B is not detected.

1 = Port B is detected.

*

0 = Port C is not detected.

1 = Port C is detected.

*

4

3

12

R806

R806

100KR2J-1-GP

100KR2J-1-GP

R802 10KR2J-3-GPR802 10KR2J-3-GP

1 2

CPU_DP2_HPD

2.DIS

2.DIS

2.DIS

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

CPU_(DISPLAY)

CPU_(DISPLAY)

CPU_(DISPLAY)

Taos KBL-U

Taos KBL-U

Taos KBL-U

8 105Monday, December 26, 2016

8 105Monday, December 26, 2016

8 105Monday, December 26, 2016

1

X00

X00

X00

Page 9

Vinafix.com

5

4

3

2

1

Main Func = CPU

D D

C C

(Blanking)

B B

2.DIS

2.DIS

2.DIS

Wistron Corporation

Wistron Corporation

A A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Date: Sheet of

Date: Sheet of

5

4

3

Date: Sheet of

(Reserved)

(Reserved)

(Reserved)

2

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taos KBL-U

Taos KBL-U

Taos KBL-U

9 105Monday, December 26, 2016

9 105Monday, December 26, 2016

9 105Monday, December 26, 2016

1

X00

X00

X00

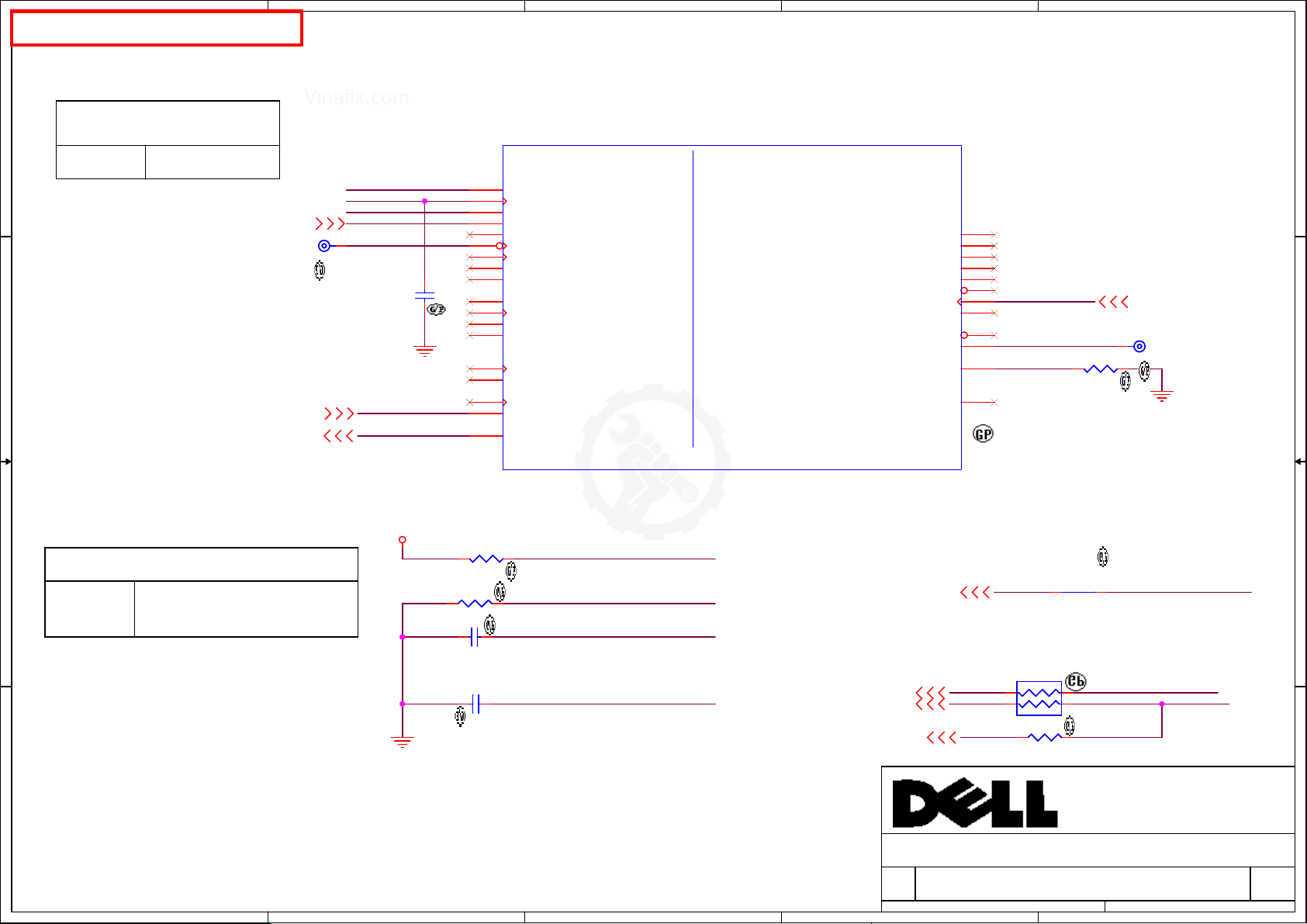

Page 10

Vinafix.com

Main Func = CPU

5

4

3

2

1

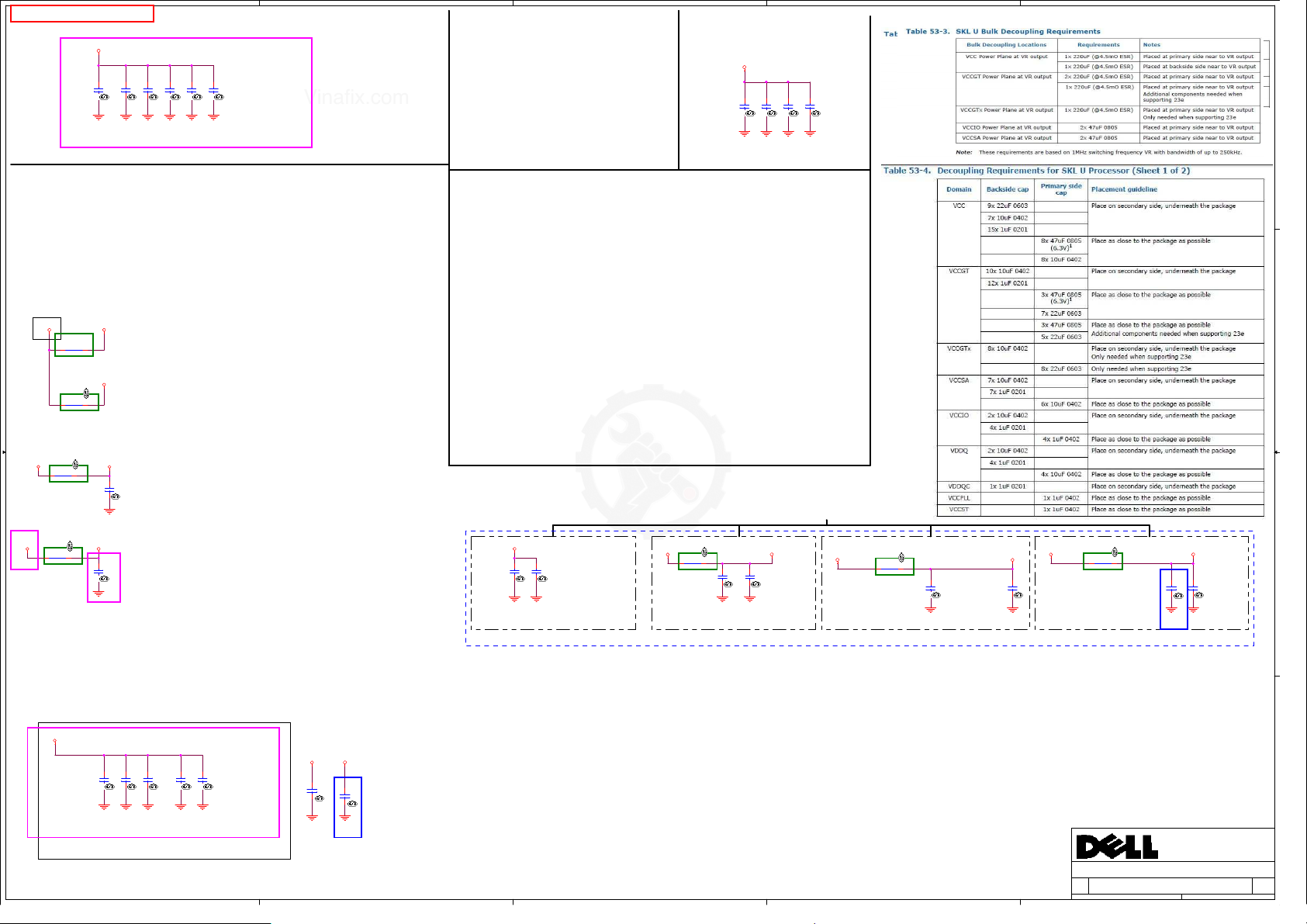

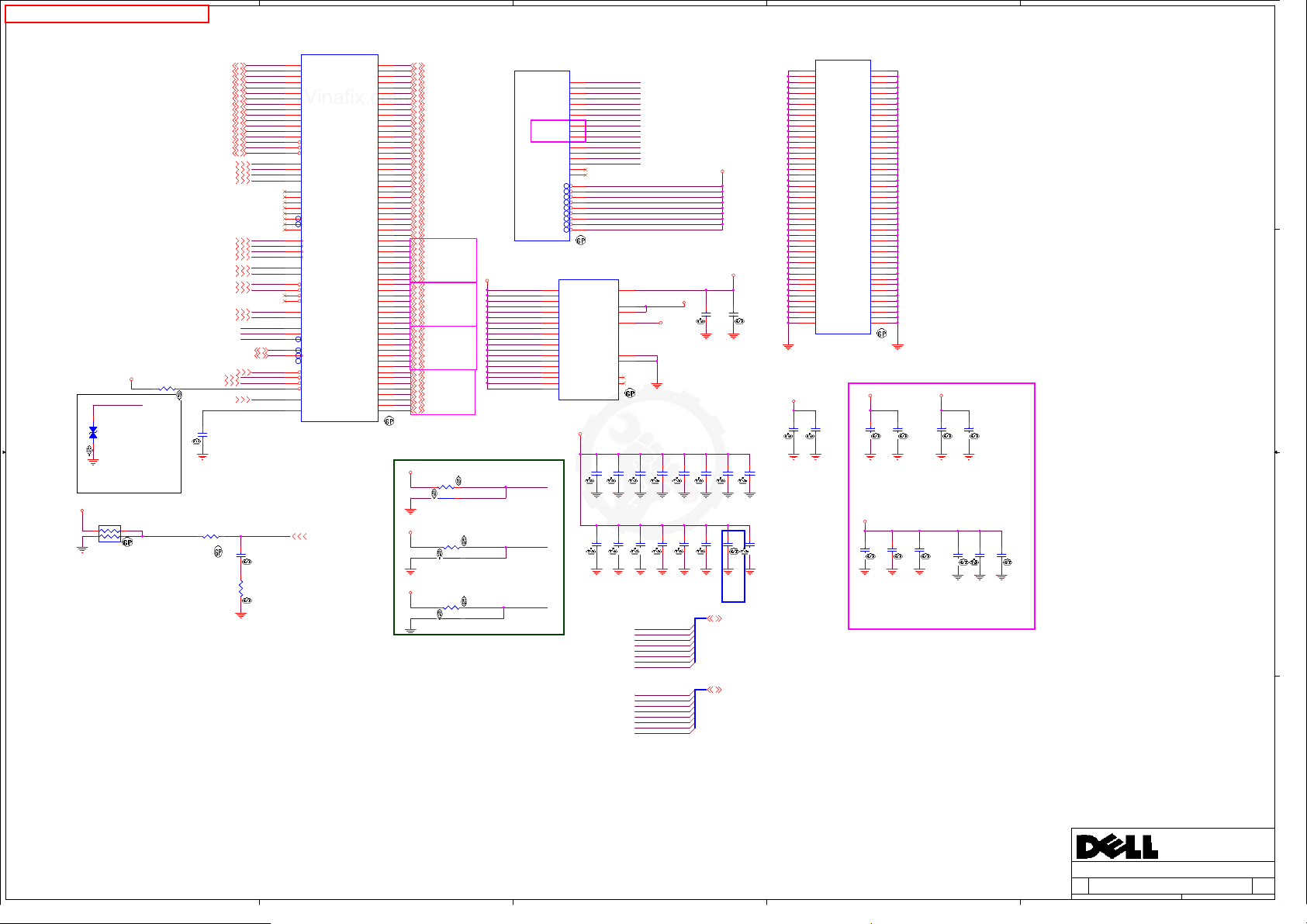

(#543016 PDG)

CORE

D D

C C

VCC_CORE

+VCCIO

PC1001

PC1001

12

PC1010

PC1010

12

PC1021

PC1021

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1002

PC1002

12

PC1011

PC1011

12

PC1022

PC1022

12

PC1003

PC1003

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1012

PC1012

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1023

PC1023

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

22U 0603 x 30

PC1005

PC1005

PC1004

PC1004

12

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1014

PC1014

PC1013

PC1013

12

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1024

PC1024

PC1025

PC1025

12

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1006

PC1006

12

PC1015

PC1015

12

PC1026

PC1026

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1008

PC1008

PC1007

PC1007

12

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1016

PC1016

PC1017

PC1017

12

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1027

PC1027

PC1028

PC1028

12

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

+VCCPRIM_COR E

PC1009

PC1009

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

20160607 add 0.1U to Vcc_CoreF DON’T DY

PC1019

PC1019

PC1020

PC1020

PC1018

PC1018

12

12

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1030

PC1030

PC1029

PC1029

12

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

FC1002SCD1U25V2KX-GP

FC1002SCD1U25V2KX-GP

FC1001Do Not StuffDYFC1001Do Not Stuff

FC1003Do Not StuffDYFC1003Do Not Stuff

WWAN

WWAN

DY

DY

20160822 change 22u to 10 u and stuff by EMI

+VCCSA

12

VCCSA

1D2V_S3

1D2V_S3

12

PC1056SC10U6D3V3MX-GP PC1056SC10U6D3V3MX-GP

PC1055SC10U6D3V3MX-GP PC1055SC10U6D3V3MX-GP

12

EC1063Do Not StuffDYEC1063Do Not Stuff

EC1062Do Not StuffDYEC1062Do Not Stuff

DY

DY

PC1046

PC1046

PC1048

PC1048

12

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

20160822 stuff by EMI

20161208 change stuff to DY

12

12

12

PC1058SC10U6D3V3MX-GP PC1058SC10U6D3V3MX-GP

PC1057SC10U6D3V3MX-GP PC1057SC10U6D3V3MX-GP

12

12

12

EC1001Do Not StuffDYEC1001Do Not Stuff

PC1064

PC1064

DY

DY

DY

Do Not Stuff

Do Not Stuff

20160822 change EC to FC ,DY to stuff and 1u to 470P by RF

EC1059Do Not StuffDYEC1059Do Not Stuff

DY

FC1006

FC1006

SC470P50V2KX-L-GP

SC470P50V2KX-L-GP

WWAN

WWAN

12

12

12

EC1060Do Not StuffDYEC1060Do Not Stuff

DY

12

EC1004Do Not StuffDYEC1004Do Not Stuff

DY

10U 0603 x 4

12

PC1061Do Not StuffDYPC1061Do Not Stuff

DY

12

FC1005

FC1005

EC1002Do Not StuffDYEC1002Do Not Stuff

SC470P50V2KX-L-GP

SC470P50V2KX-L-GP

WWAN

WWAN

DY

22U 0603 x 9

PC1053

PC1049

PC1049

12

PC1050

PC1050

PC1051

PC1051

12

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1053

PC1052

PC1052

12

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

DY

DY

12

20160822 stuff by EMI

20160823 change EMI to RD and 1u to 470P

Do Not Stuff

Do Not Stuff

+VCCIO(ICCMAX.=2.73A)

12

12

12

PC1037Do Not StuffDYPC1037Do Not Stuff

PC1036S C22U6D3V3MX-1-GP PC1036SC22U6D3V3MX-1-GP

PC1035S C22U6D3V3MX-1-GP PC1035SC22U6D3V3MX-1-GP

B B

+VCCGT

DY

VCCGT

PC1031

PC1031

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1032

PC1032

12

PC1033

PC1033

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1038

PC1038

PC1039

PC1039

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

22U 0603 x28

PC1034

PC1034

PC1041

PC1041

12

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1097

PC1097

PC1098

Do Not Stuff

Do Not Stuff

PC1079

PC1079

12

PC1098

12

12

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

DY

DY

DY

DY

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

FC1004Do Not StuffDYFC1004Do Not Stuff

DY

PC1068

PC1066

PC1074

PC1074

12

PC1065

PC1065

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1075

PC1075

12

PC1066

12

DY

DY

PC1076

PC1076

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1047

PC1047

PC1054

PC1070

PC1070

12

PC1054

12

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1072

PC1072

PC1071

PC1071

PC1073

PC1073

12

12

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

PC1069

PC1069

PC1044

PC1042

PC1042

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1044

PC1043

PC1043

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1068

PC1067

PC1067

12

12

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

DY

DY

DY

DY

PC1078

PC1078

PC1077

PC1077

12

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1094

PC1085

PC1085

PC1086

PC1084

PC1084

12

PC1086

12

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1080

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

A A

5

12

12

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

PC1083

PC1083

PC1081

PC1081

PC1082

PC1082

PC1080

PC1087

PC1087

12

PC1089

PC1089

PC1090

PC1090

PC1088

PC1088

12

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

DY

DY

PC1091

PC1091

12

12

12

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

DY

DY

DY

DY

DY

DY

4

PC1092

PC1092

12

PC1094

PC1093

PC1093

PC1095

PC1095

PC1096

PC1096

12

12

12

12

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

DY

DY

Do Not Stuff

Do Not Stuff

DY

DY

Do Not Stuff

DY

DY

DY

DY

2.DIS

2.DIS

2.DIS

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin T ai Wu Rd ., Hsichih,

21F, 88, Sec.1, Hsin T ai Wu Rd ., Hsichih,

21F, 88, Sec.1, Hsin T ai Wu Rd ., Hsichih,

Taipei Hsie n 221, Taiwan, R.O. C.

Taipei Hsie n 221, Taiwan, R.O. C.

Title

Title

Title

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

A2

A2

A2

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

Taipei Hsie n 221, Taiwan, R.O. C.

CPU_(Power CAP1)

CPU_(Power CAP1)

CPU_(Power CAP1)

Taos KBL-U

Taos KBL-U

Taos KBL-U

1

X00

X00

10 105Monday, Decemb er 26, 2016

10 105Monday, Decemb er 26, 2016

10 105Monday, Decemb er 26, 2016

X00

Page 11

Vinafix.com

5

4

3

2

1

Main Func = CPU

20160712 DY

+VCCGT

12

12

12

C1136

C1136

C1138

C1138

DY

DY

DY

DY

DY

DY

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

D D

12

C1147

C1147

12

12

C1150

C1150

C1149

C1149

C1148

C1148

DY

DY

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

1U 0402 x 6

DY

DY

DY

DY

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

+VCCIO

+VCCIO(ICCMAX.=2.73A)

12

12

C1151

C1151

C1152

C1152

SC1U10V2KX-1GP

SC1U10V2KX-1GP

VCCIO

12

12

C1153

C1153

C1154

C1154

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

PCH DERIVED RAILS

R1117

R1117

1 2

Do Not Stuff

Do Not Stuff

R1118

R1118

1 2

Do Not Stuff

Do Not Stuff

R1112

R1112

Do Not Stuff

Do Not Stuff

+VCCPRIM_COR E

20161026 0ohm to short pad

+V1.00A_SIP

C1113

Do Not StuffDYC1113

Do Not Stuff

12

DY

1D0V_S5

C C

20161024 0ohm to short pad

3D3V_S5_PCH +V3.3A_SIP

1 2

20161024 0ohm to short pad

+VCCMPHYGTAON_1P0(ICCMAX.=2.12A)

20160630 change +1.8V to 1D8V_S5

1D8V_S5 +V1.8A_S IP

R1139

R1139

1 2

B B

A A

Do Not Stuff

Do Not Stuff

20161024 0ohm to short pad

20160712 DY

VCC_CORE

C1122

Do Not StuffDYC1122

Do Not Stuff

12

DY

20160712 DY

+V3.3A_SIP

12

12

12

12

C1103

C1103

C1101

C1101

C1102

C1102

DY

DY

DY

DY

DY

DY

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

12

C1116

C1116

C1117

C1117

DY

DY

DY

DY

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

1U 0402 x 5

+V3.3A_SIP

C1123

Do Not StuffDYC1123

Do Not Stuff

20160720 change 78.10623.51L to 78.10610.5BL

12

12

DY

C1183

C1183

+VCCMPHYGTA ON_1P0_LS_SIP

12

12

C1182

C1174

C1174

C1182

SC1U10V2KX-1GP

SC1U10V2KX-1GP

DY

DY

+VCCMPHYGTA ON_1P0_LS_SIP

R1101

R1101

Do Not Stuff

Do Not Stuff

1 2

Do Not Stuff

Do Not Stuff

20161024 0ohm to short pad

+VCCAPLLEBB_1 P0 +VCCMPHYGTA ON_1P0_LS_SIP

C1180

C1180

C1173

C1173

12

12

DY

DY

Do Not Stuff

Do Not Stuff

SC1U10V2KX-1GP

SC1U10V2KX-1GP

+VCCMPHYGTA ON_1P0_LS_SIP

R1102

R1102

1 2

Do Not Stuff

Do Not Stuff

20161024 0ohm to short pad

+VCCAMPHYPLL_1P 0_L

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

C1181

C1181

C1172

C1172

SC1U10V2KX-1GP

SC1U10V2KX-1GP

12

20161024 0ohm to short pad

20160720 change 78.10623.51L to 78.10610.5BL

R1106

R1106

1 2

Do Not Stuff

Do Not Stuff

+VCCSRAM_1P 0

12

12

C1176

C1176

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

C1175

C1175

SC1U10V2KX-1GP

SC1U10V2KX-1GP

U-line 23e 28W

IccMax current-10ms max = 34 A

5

2.DIS

2.DIS

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

4

3

2

2.DIS

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin T ai Wu Rd ., Hsichih,

21F, 88, Sec.1, Hsin T ai Wu Rd ., Hsichih,

21F, 88, Sec.1, Hsin T ai Wu Rd ., Hsichih,

Taipei Hsie n 221, Taiwan, R.O. C.

Taipei Hsie n 221, Taiwan, R.O. C.

Title

Title

Title

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

A2

A2

A2

Date: Sheet of

Date: Sheet of

Date: Sheet of

Taipei Hsie n 221, Taiwan, R.O. C.

CPU_(Power CAP2)

CPU_(Power CAP2)

CPU_(Power CAP2)

Taos KBL-U

Taos KBL-U

Taos KBL-U

1

11 105Monday, Decemb er 26, 2016

11 105Monday, Decemb er 26, 2016

11 105Monday, Decemb er 26, 2016

X00

X00

X00

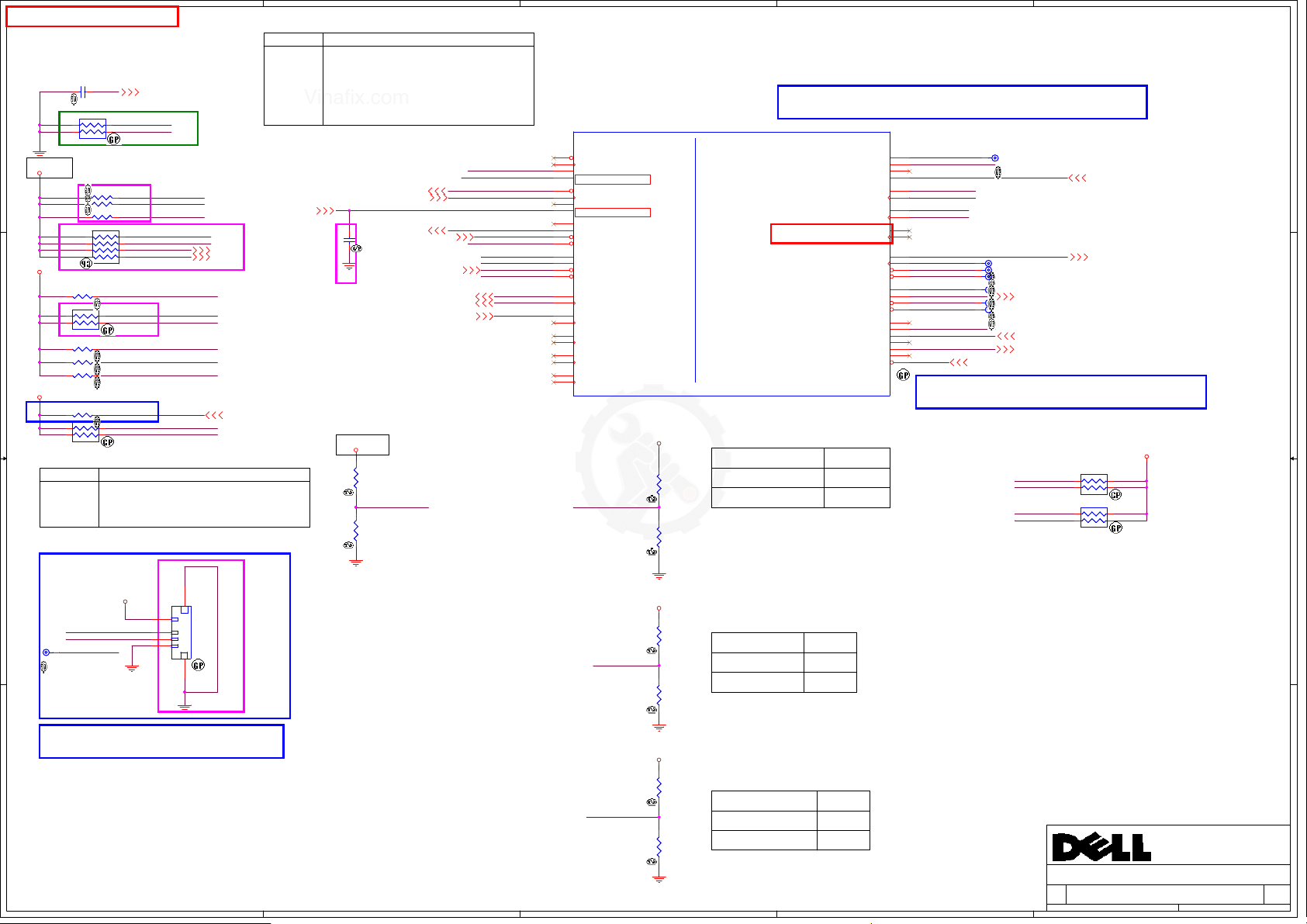

Page 12

Vinafix.com

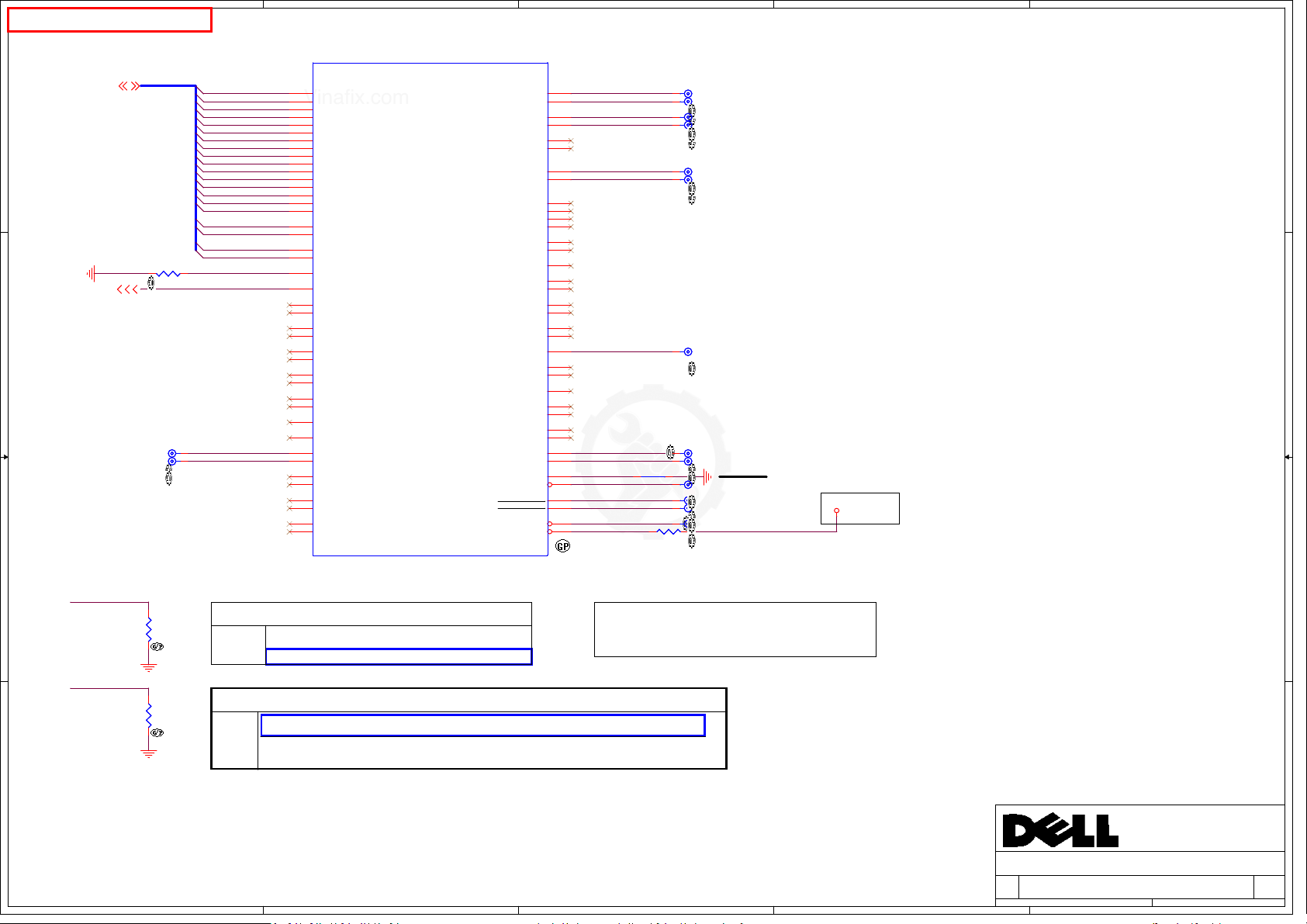

Main Func = DDR SODIMM

5

4

3

2

1

20160815 DM1 DM2 change symbol

M_A_A0[5]

M_A_A1[5]

M_A_A2[5]

M_A_A3[5]

M_A_A4[5]

M_A_A5[5]

M_A_A6[5]

M_A_A7[5]

M_A_A8[5]

D D

C C

1D2V_S3

1 2

R1215 Do Not Stuff

ED1217

ED1217

Do Not Stuff

Do Not Stuff

R1215 Do Not Stuff

DDR4_DR AMRST#

12

DY

DY

M_A_A9[5]

M_A_A10[5]

M_A_A11[5]

M_A_A12[5]

M_A_A13[5]

M_A_A14[5]

M_A_A15[5]

M_A_A16[5]

M_A_BA0[5]

M_A_BA1[5]

M_A_BG0[5]

M_A_BG1[5]

M_A_CLK0[5]

M_A_CLK#0[5]

M_A_CLK1[5]

M_A_CLK#1[5]

M_A_CKE0[5]

M_A_CKE1[5]

M_A_CS#0[5]

M_A_CS#1[5]

M_A_DIMA_ODT0[5]

M_A_DIMA_ODT1[5]

DDR4_DR AMRST#[5,13]

M_A_ACT_N[5]

M_A_ALERT_N[5]

DY

DY

M_A_PARITY[5]

12

C1229

C1229

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

PCH_SMBDAT A[13,18,65,66,67,99]

PCH_SMBCLK[13,18,65,66,67,99]

SA0_CHA_DIM0

SA1_CHA_DIM0

SA2_CHA_DIM0

TS#_DIMM0_1

M_VREF_CA_D IMMA

DM1A

DM1A

144

A0

133

A1

132

A2

131

A3

128

A4

126

A5

127

A6

122

A7

125

A8

121

A9

146

A10/AP

120

A11

119

A12

158

A13

151

WE#/A14

156

CAS#/A15

152

RAS#/A16

150

BA0

145

BA1

115

BG0

113

BG1

92

CB0/NC

91

CB1/NC

101

CB2/NC

105

CB3/NC

88

CB4/NC

87

CB5/NC

100

CB6/NC

104

CB7/NC

137

CK0_T

139

CK0_C

138

CK1_T/NF

140

CK1_C/NF

109

CKE0

110

CKE1

149

CS0#

157

CS1#

162

C0/CS2#/NC

165

C1/CS3#/NC

155

ODT0

161

ODT1

256

SA0

260

SA1

166

SA2

254

SDA

253

SCL

108

RESET#

114

ACT#

116

ALERT#

134

EVENT#/NF

143

PARITY

164

VREFCA

DDR4-260P-9-GP-U

DDR4-260P-9-GP-U

062.10011.00J1

062.10011.00J1

Layout note: closed to Dimm

1D2V_S3

RN1201

RN1201

1

4

2 3

SRN1KJ-7-G P

SRN1KJ-7-G P

B B

M_VREF_CA_D IMMA

R1206

R1206

1 2

2R2F-GP

2R2F-GP

12

C1222

C1222

SCD022U16V2KX -3GP

SCD022U16V2KX -3GP

+V_VREF_PATH 1

12

R1209

R1209

24D9R2F-L-G P

24D9R2F-L-G P

V_SM_VREF_CN TA [5]

1 OF 4

1 OF 4

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

4 OF 4

DM1D

4 OF 4

0D6V_S0

12

C1225

C1225

10

14

15

18

19

22

23

26

27

30

31

35

36

39

40

43

44

47

48

51

52

56

57

60

61

64

65

68

69

72

73

77

78

81

82

85

86

89

90

93

94

98

SC1U10V2KX-1GP

SC1U10V2KX-1GP

DM1D

VSS1VSS

2

VSS

5

VSS

6

VSS

9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

DDR4-260P-9-GP-U

DDR4-260P-9-GP-U

12

C1226

C1226

SC1U10V2KX-1GP

SC1U10V2KX-1GP

99

102

VSS

103

VSS

106

VSS

107

VSS

167

VSS

168

VSS

171

VSS

172

VSS

175

VSS

176

VSS

180

VSS

181

VSS

184

VSS

185

VSS

188

VSS

189

VSS

192

VSS

193

VSS

196

VSS

197

VSS

201

VSS

202

VSS

205

VSS

206

VSS

209

VSS

210

VSS

213

VSS

214

VSS

217

VSS

218

VSS

222

VSS

223

VSS

226

VSS

227

VSS

230

VSS

231

VSS

234

VSS

235

VSS

238

VSS

239

VSS

243

VSS

244

VSS

247

VSS

248

VSS

251

VSS

252

VSS

UN 0225

0D6V_S0

12

12

C1223

C1223

C1230

C1230

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

DY

DY

DY

DY

for placement modifu 2015/10/19

2D5V_S3

12

12

C1211

C1211

DY

DY

12

C1231

C1231

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

DY

DY

DY

DY

C1232

C1232

0D6V_S0

DY

DY

Do Not Stuff

Do Not Stuff

12