Dell Latitude 3330 Schematics

Vinafix.com

5

4

3

2

1

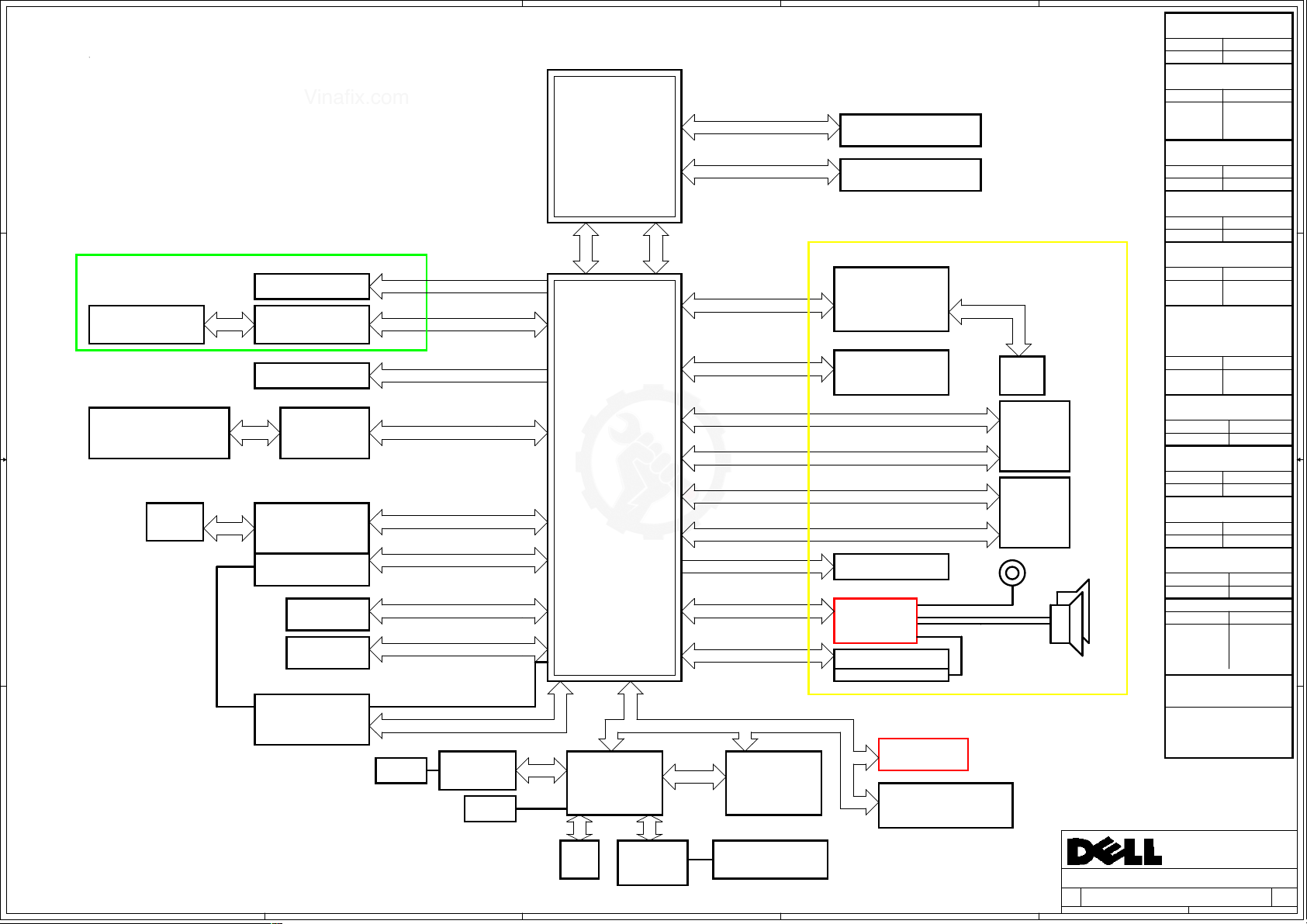

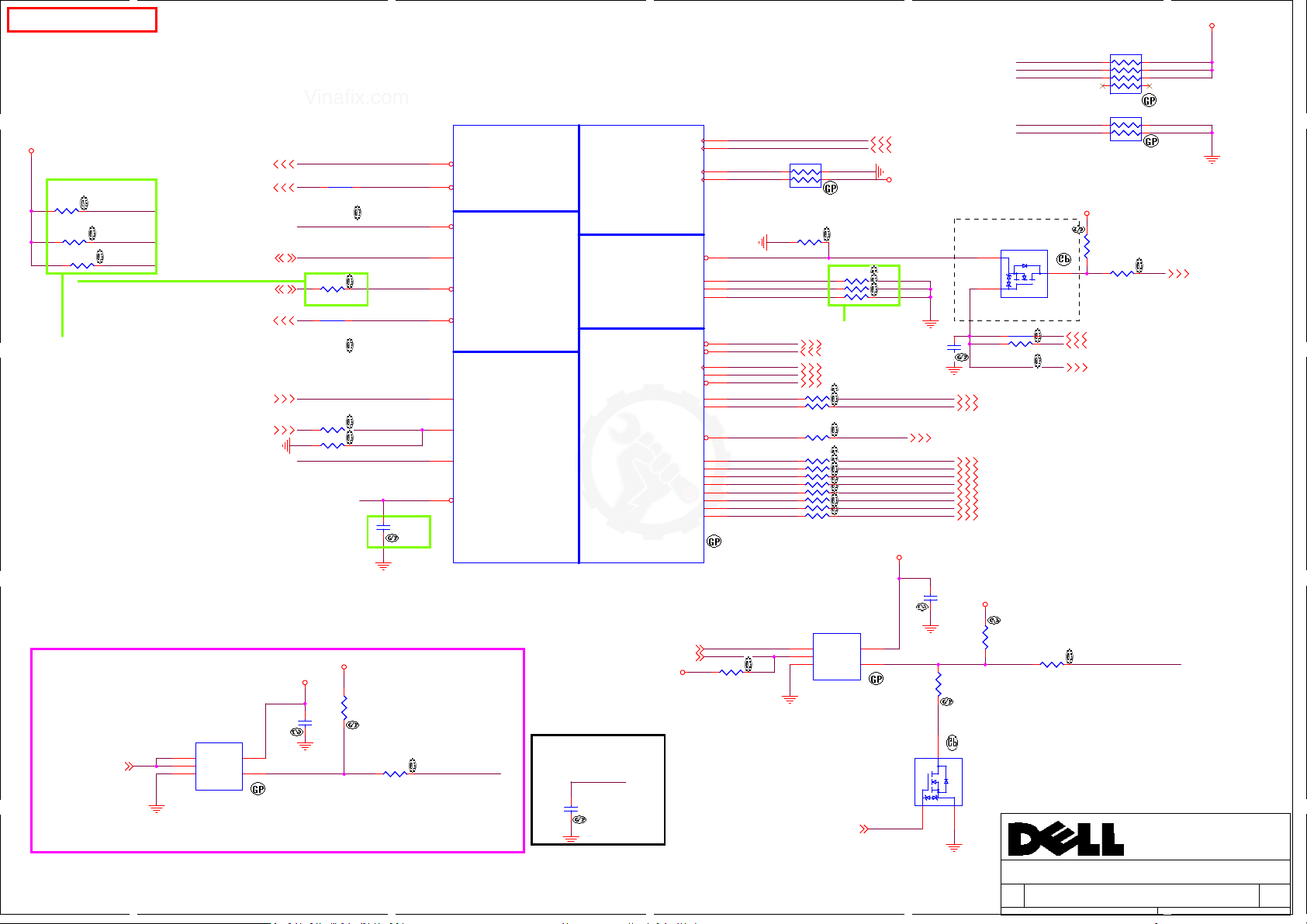

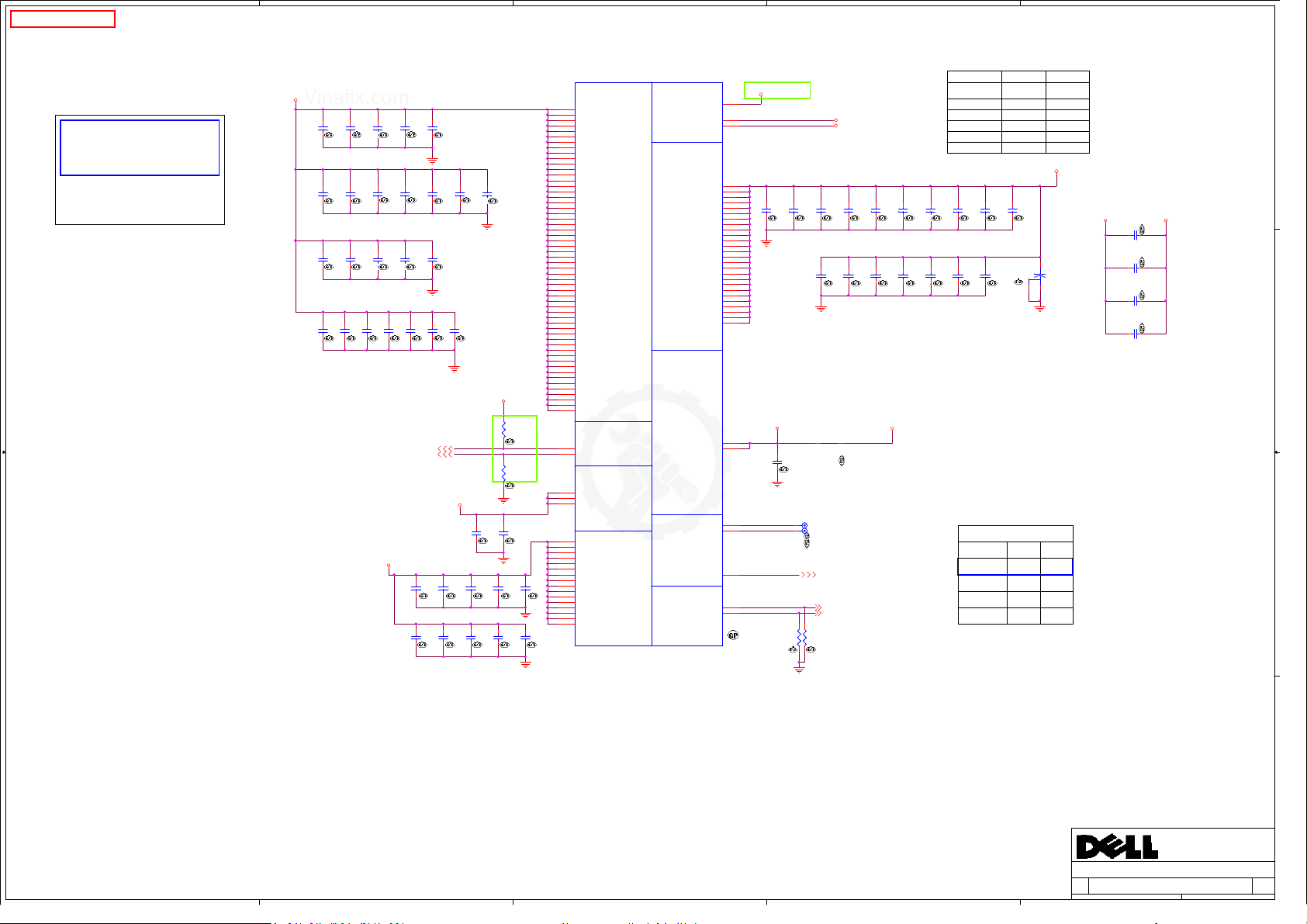

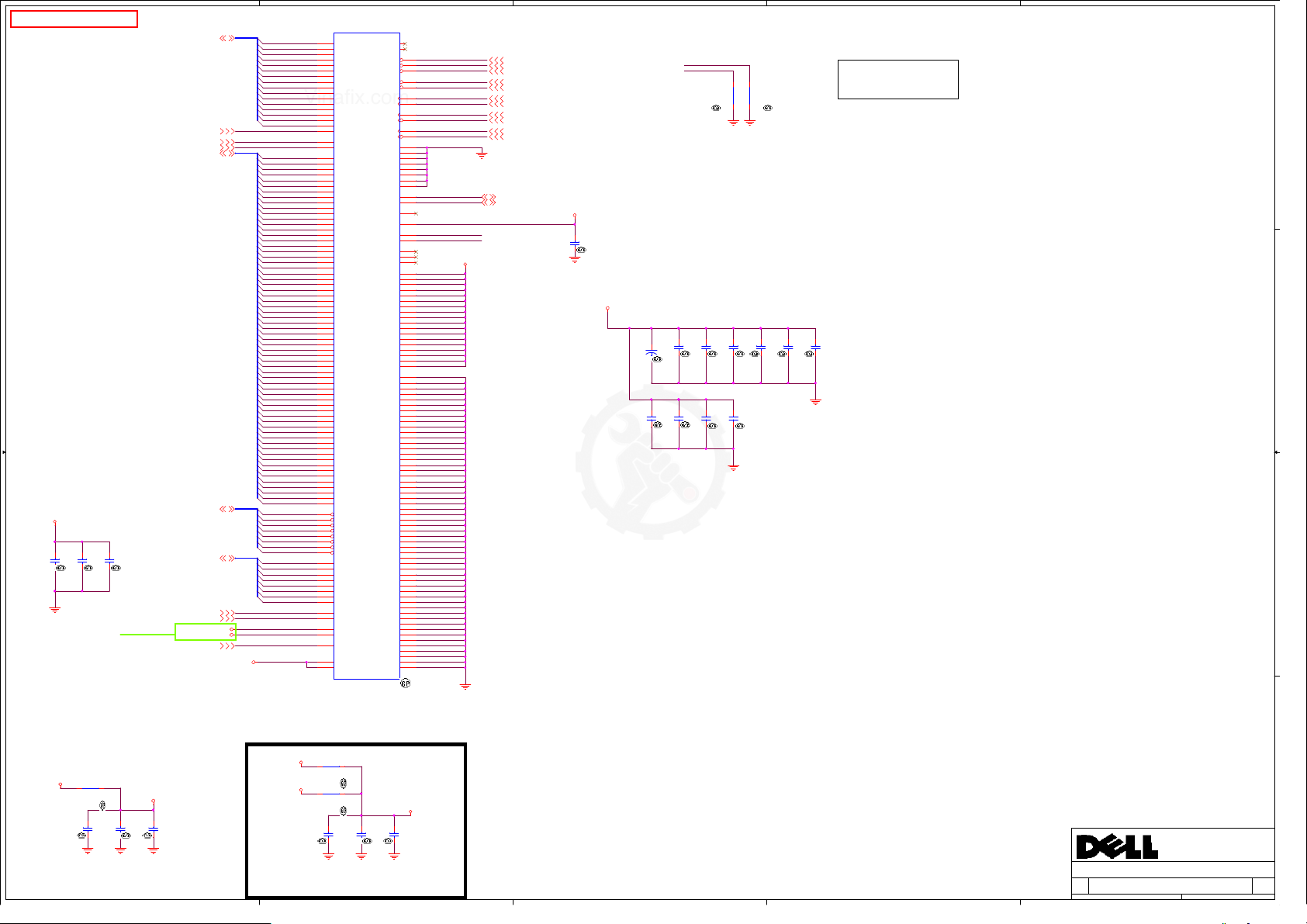

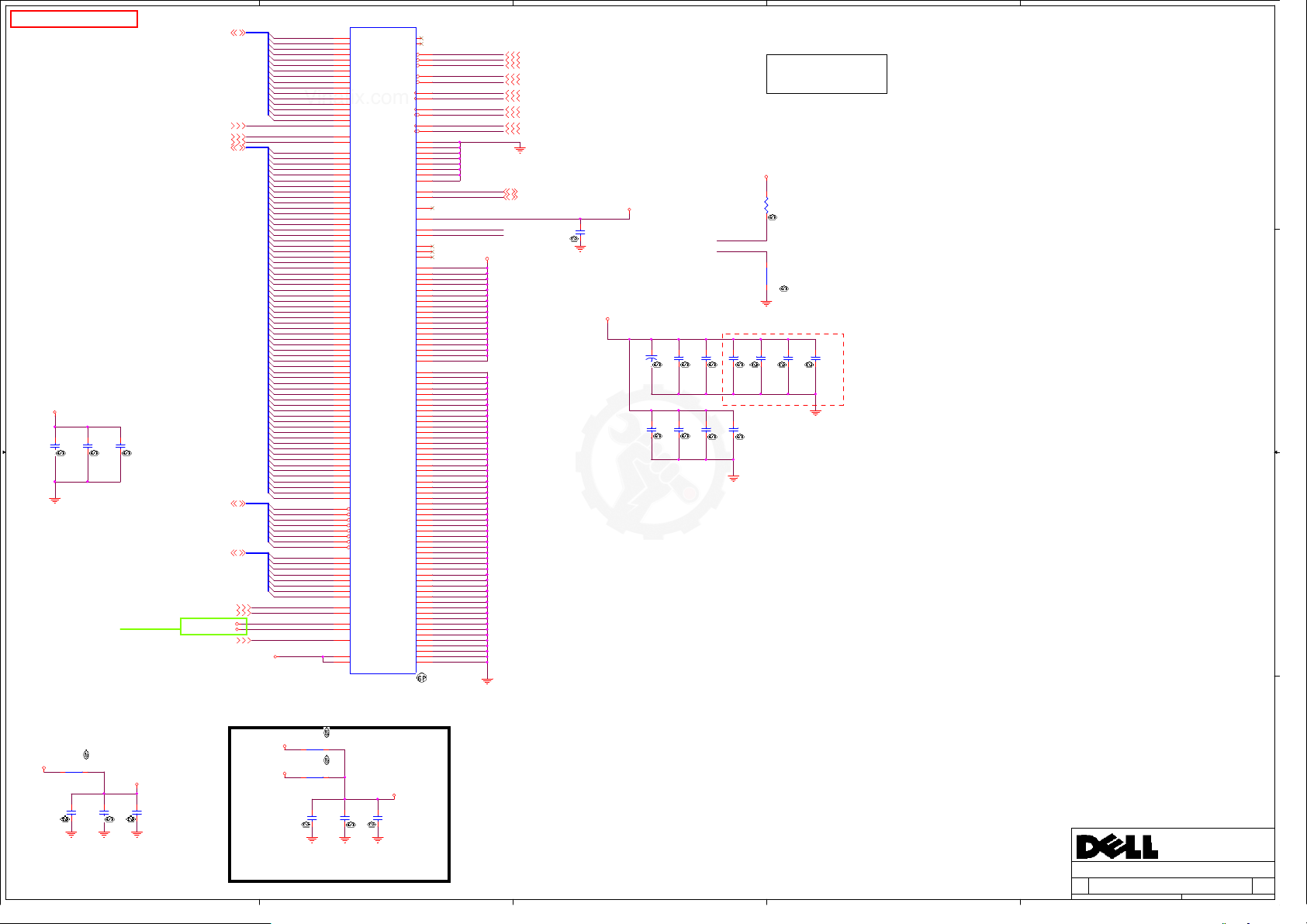

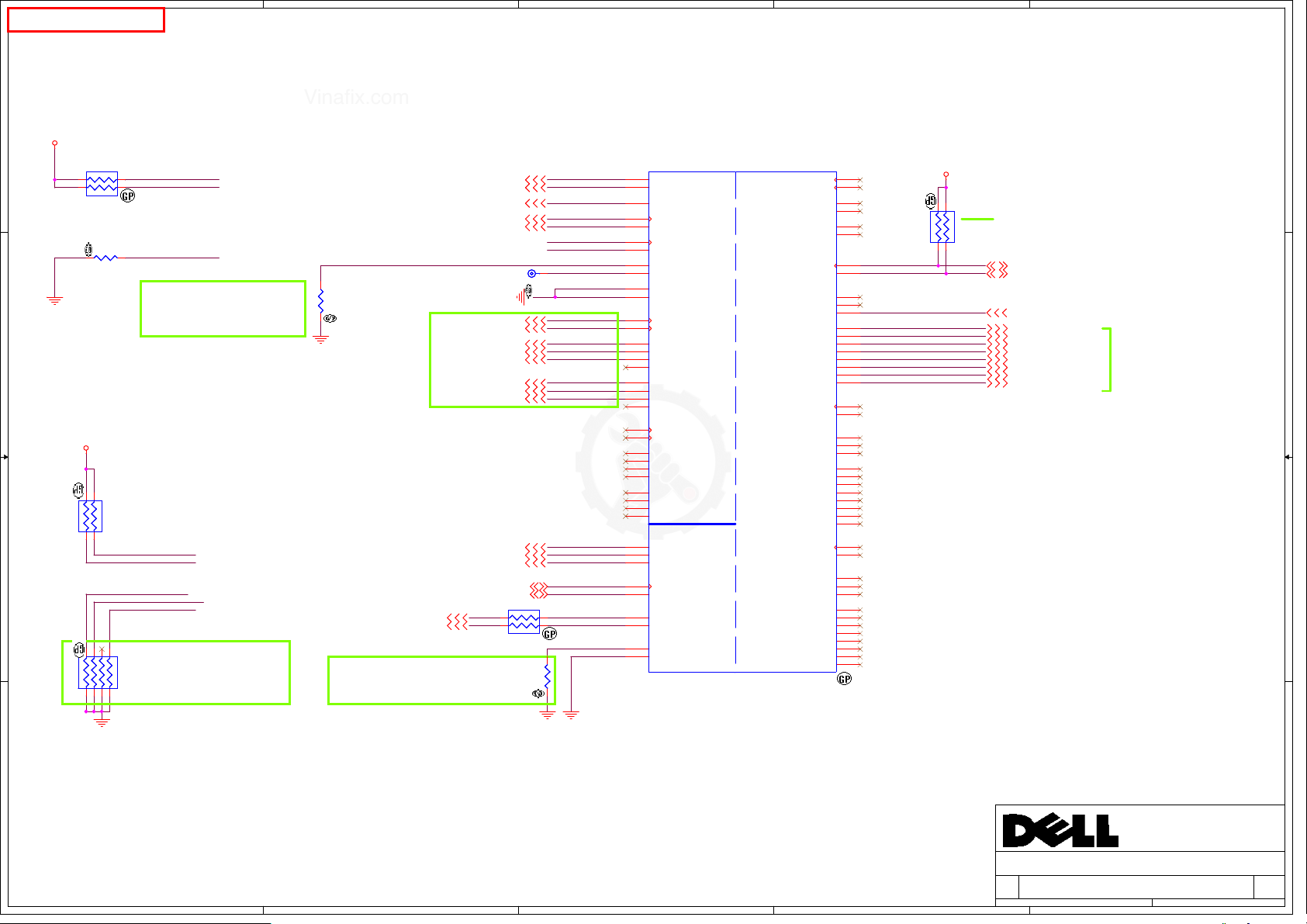

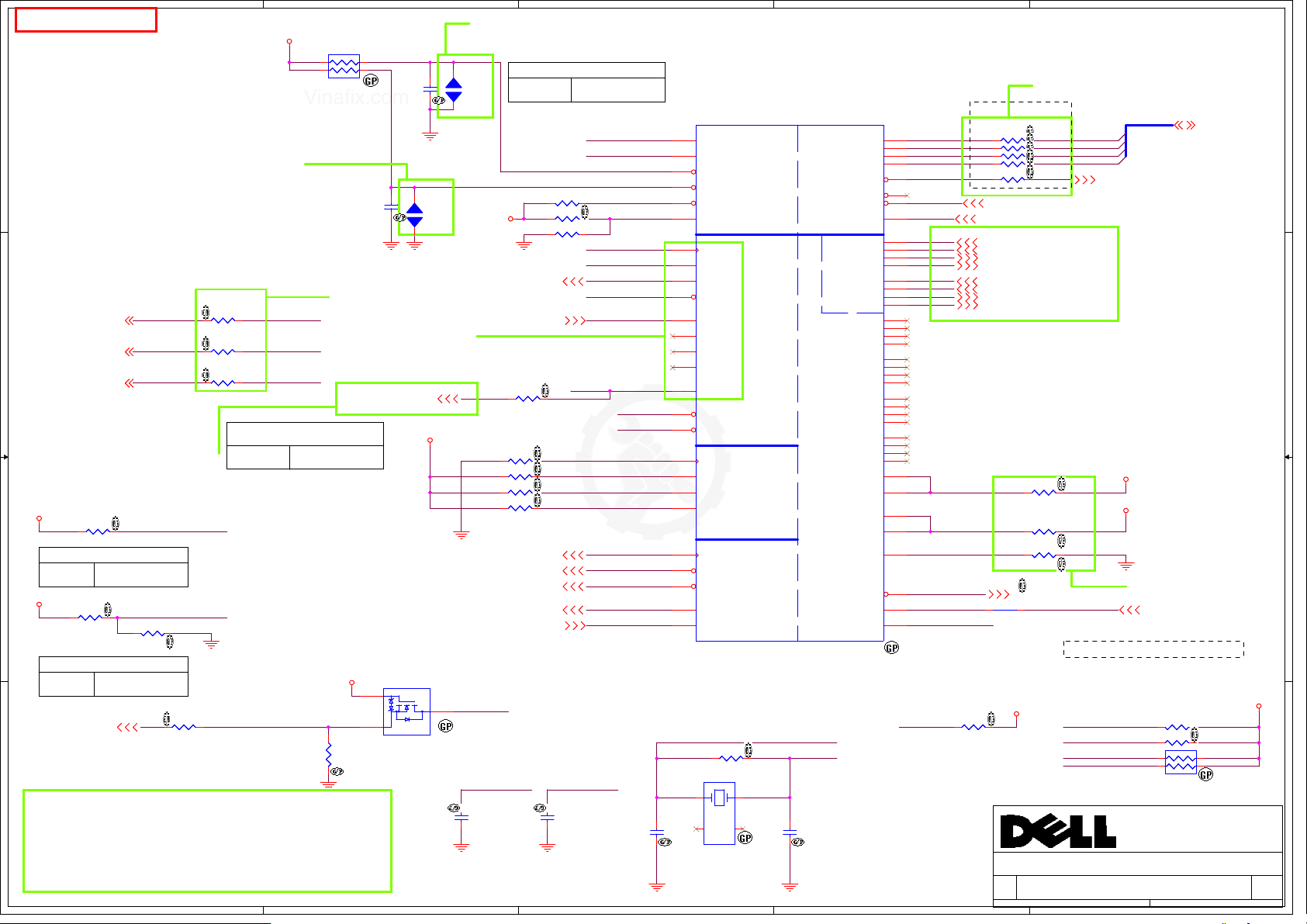

Austin 13" Schematics Document

D D

Ivy Bridge ULV

Panther Point

2013-02-26

C C

DY : None Installed

B B

REV : A00

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Tuesday, February 26, 2013

Tuesday, February 26, 2013

Tuesday, February 26, 2013

Date: Sheet of

Date: Sheet of

Date: Sheet of

Cover Page

Cover Page

Cover Page

Austin 13

Austin 13

Austin 13

Taipei Hsien 221, Taiwan, R.O.C.

1 106

1 106

1 106

1

A00

A00

A00

Vinafix.com

5

D D

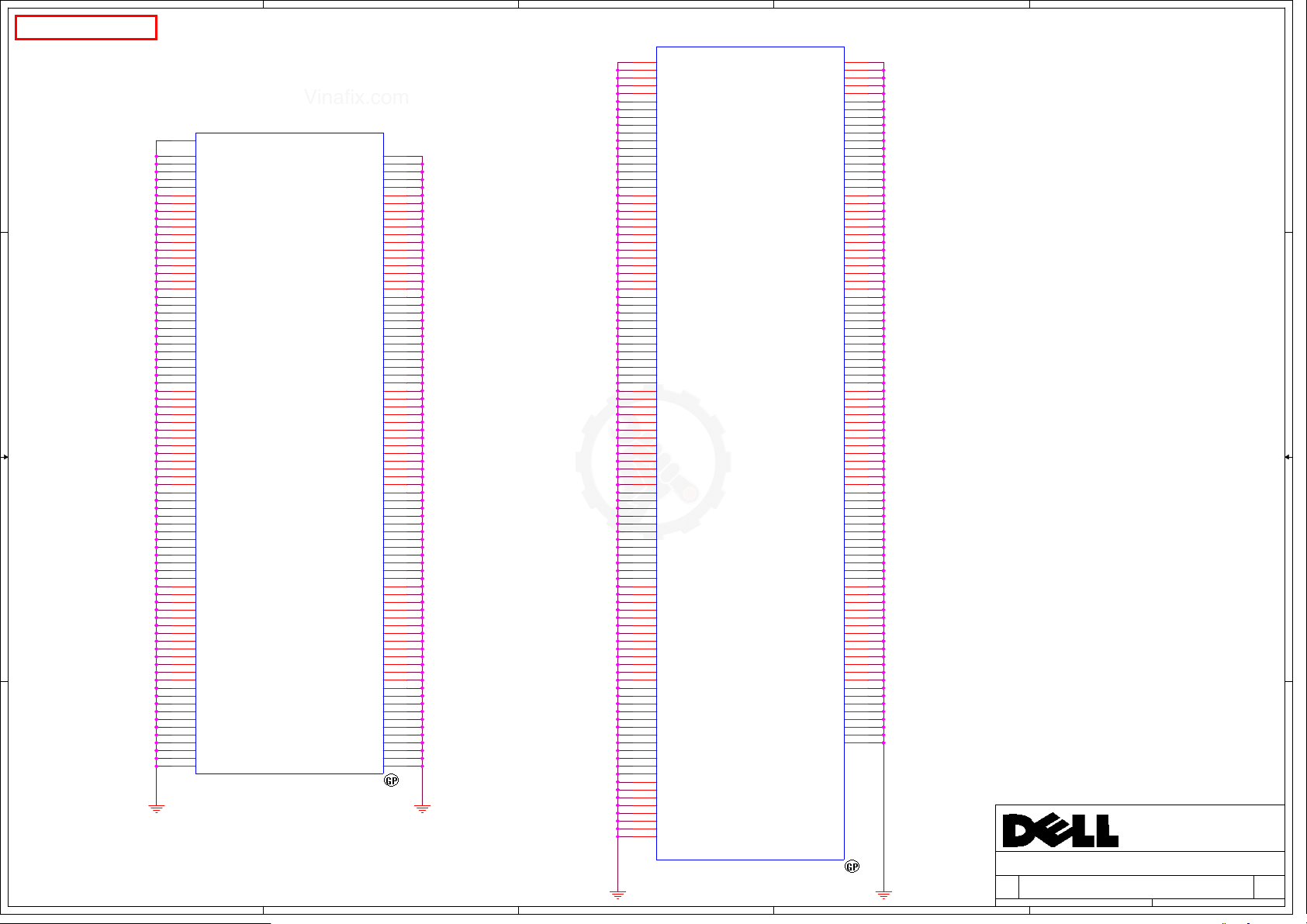

HDMI board

HDMI

USB 2.0 + Power share

CONN

C C

USB PowerShare

PERICOM

PI5USB1457AZAE

LCD

Connector

SD/SDHC/SDXC/SD UHS-I

MMC/MMC+, MS/MS Pro

CardReader

O2

OZ600FJ0

Mini-Card

Micro SIM

66

INT 2 SATA GenIII x 1

B B

WWAN/MSATA

HDD

Flash ROM

8MB

Flash ROM

4MB

FFS

ST

LNG3DM

A A

5

4

51

49

3274

66

56

60

60

51

FAN

4

3

Austin 13 Block Diagram

Intel CPU

TMDS

USB2.0 x 1

LVDS

PCIE x 1

SATA GEN3 & USB2.0*1

SPI BUS

SPI BUS

INT1

SMBUS

Thermal

SMSC

EMC4021

JTAG

28

BC Link

Ivy Bridge

17W

BGA1023

4,5,6,7,8,9,10

DMIx4FDIx4x2

Intel

PCH

Panther Point

BGA989

HM77

14 USB 2.0/1.1 ports

4 USB 3.0 ports

High Definition Audio

6 SATA ports

8 PCIE ports

LPC I/F

ACPI 4.0a

17,18,19,20,21,22,23,24,25

KBC

SMSC

MEC5055

PS2

Touch

PAD

69 69

27

Keyboard

controller

EC1117

3

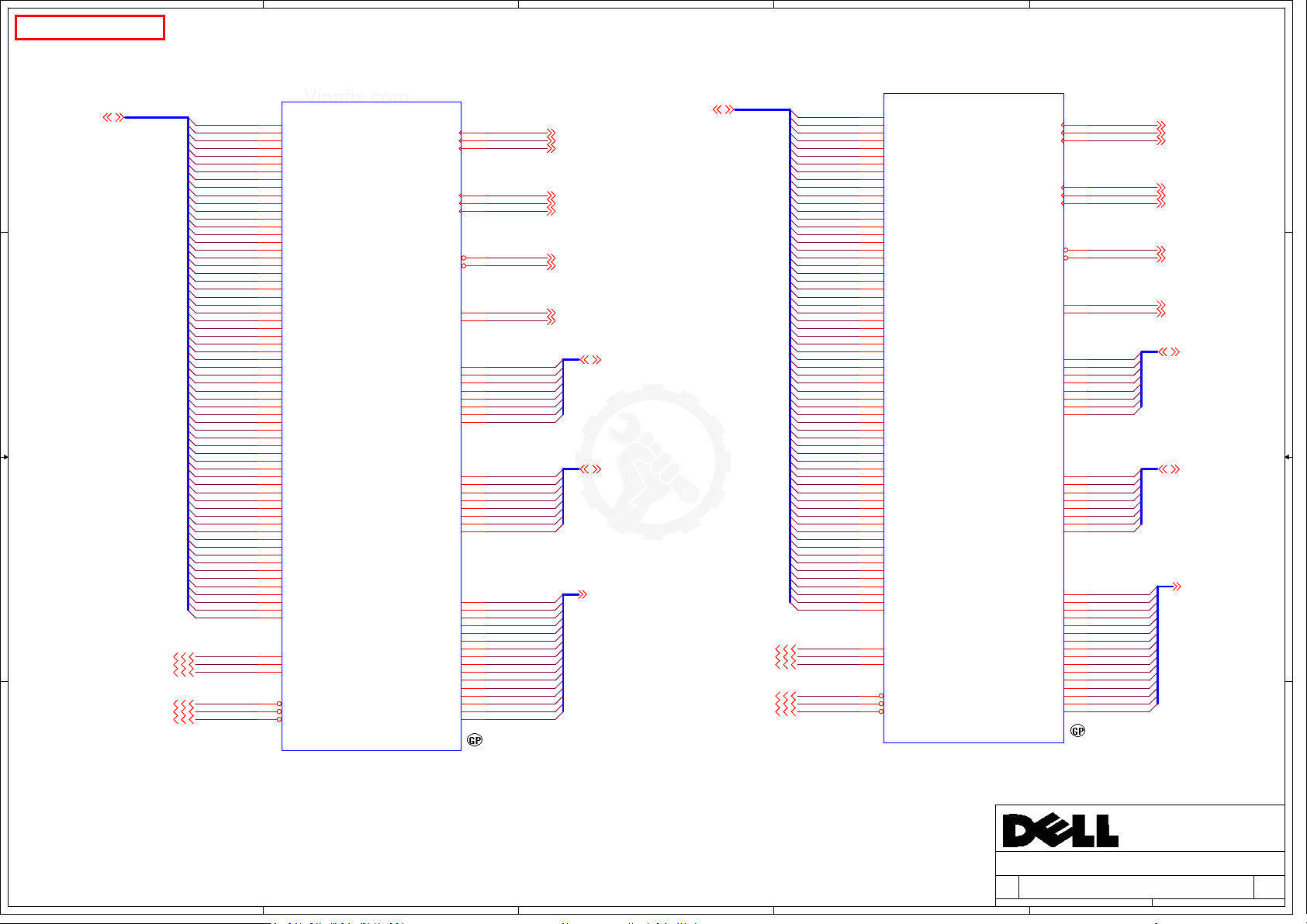

DDRIII 1600MHz Channel A

DDRIII 1600MHz Channel B

PCIE x 1

USB3.0 x 1

USB2.0 x 1

USB3.0 x 1

USB2.0 x 1

HDA

USB2.0 x 1

LPC BUS

BC link

BC Link

Int. KB

(Backlight supported)

69

USB2.0 x 1PCIE x 1

RGB CRT

SIO Expander

SMSC

ECE5048

2

Project Code:

PCB P/N :

Revision :

DDRIII1600MHz

DDRIII1600MHz

Slot A

Slot B

LAN

Intel Lewisville

82579LM

14

15

31

91.4LA01.001

12275

A00

1

CHARGER

ISL88731CHRTZ

INPUTS

AD+

SYSTEM DC/DC

TPS51125RGER

INPUTS

DCBATOUT +5V_ALW

VT1318+VT1323

INPUTS

+5V_ALW

INPUTS

+5V_ALW

INPUTS

+5V_ALW

+3.3V_ALW

5V_PWR_2

+3.3V_ALW2

+3.3V_ALW

+15V_ALW

CPU DC/DC

GFX DC/DC

VT1318+VT1323

VCC_GFXCORE

SYSTEM DC/DC

VT386+RT8085

+1.05V_RUN_VTT

SYSTEM DC/DC

OUTPUTS

BT+

OUTPUTS

OUTPUTS

VCC_CORE

OUTPUTS

OUTPUTS

+1.05V_M

40

41

42,43

44

45

RT8207

Mini-Card

802.11a/b/g/n

BT V4.0 combo

CRT

Codec

IDT

29 58

92HD93

Camera

Internal Digital MIC

49

RJ45

Right side

USB 3.0

Right side

USB 3.0

Combo Jack

2CH Speaker

Daughter Board

INPUTS

DCBATOUT

26

SYSTEM DC/DC

INPUTS

+3.3V_ALW

SYSTEM DC/DC

INPUTS

+3.3V_ALW

SYSTEM DC/DC

INPUTS OUTPUTS

+5V_ALW

INPUTS OUTPUTS

26

INPUTS OUTPUTS

+1.35V_MEM

+5V_ALW

+1.05V_N +1.05V_RUN

+3.3V_ALW +3.3V_M

+3.3V_ALW

+5V_ALW

OUTPUTS

+1.35V_MEM

+0.675_DDR_VTT

+V_DDR_REF

RT8068A

OUTPUTS

+1.8V_RUN

APL5930

OUTPUTS

+1.5V_RUN

SY8037

+VCC_SA

N.A

Switches

+1.35V_CPU_VDDQ

+5V_RUN

+3.3V_RUN+3.3V_ALW

+3.3V_ALW_PCH

+5V_ALW_PCH

46

47

47

48

PCB LAYER

L1:Top

L2:GND

L3:Signal

LPC debug port

71

L4:Signal

TPM

78

AT97SC3204-X2A1D-AB

77

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

Block Diagram

Block Diagram

Block Diagram

Austin 13

Austin 13

Austin 13

1

L5:GND

L6:Bottom

2 106Tuesday, February 26, 2013

2 106Tuesday, February 26, 2013

2 106Tuesday, February 26, 2013

A00

A00

A00

Vinafix.com

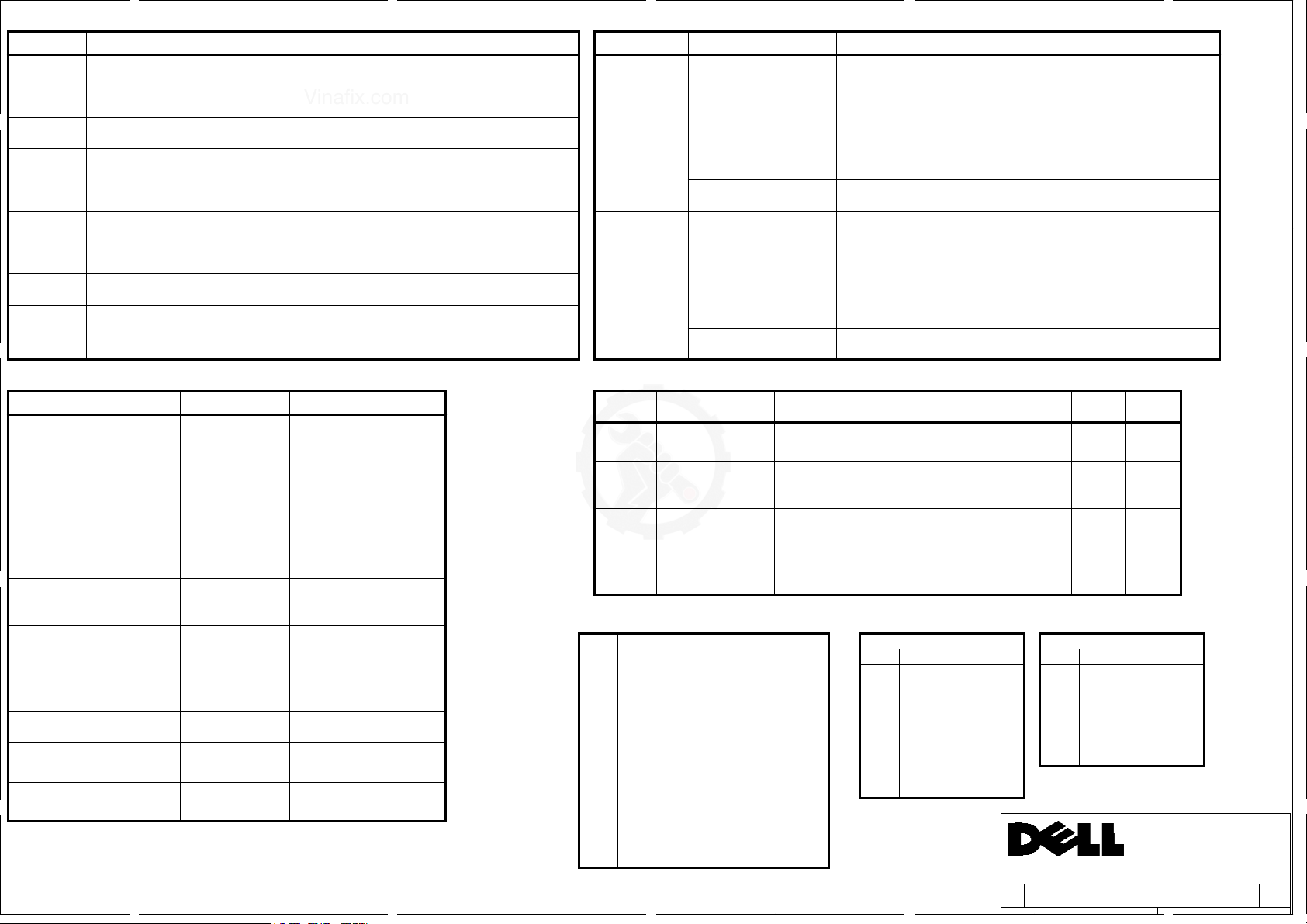

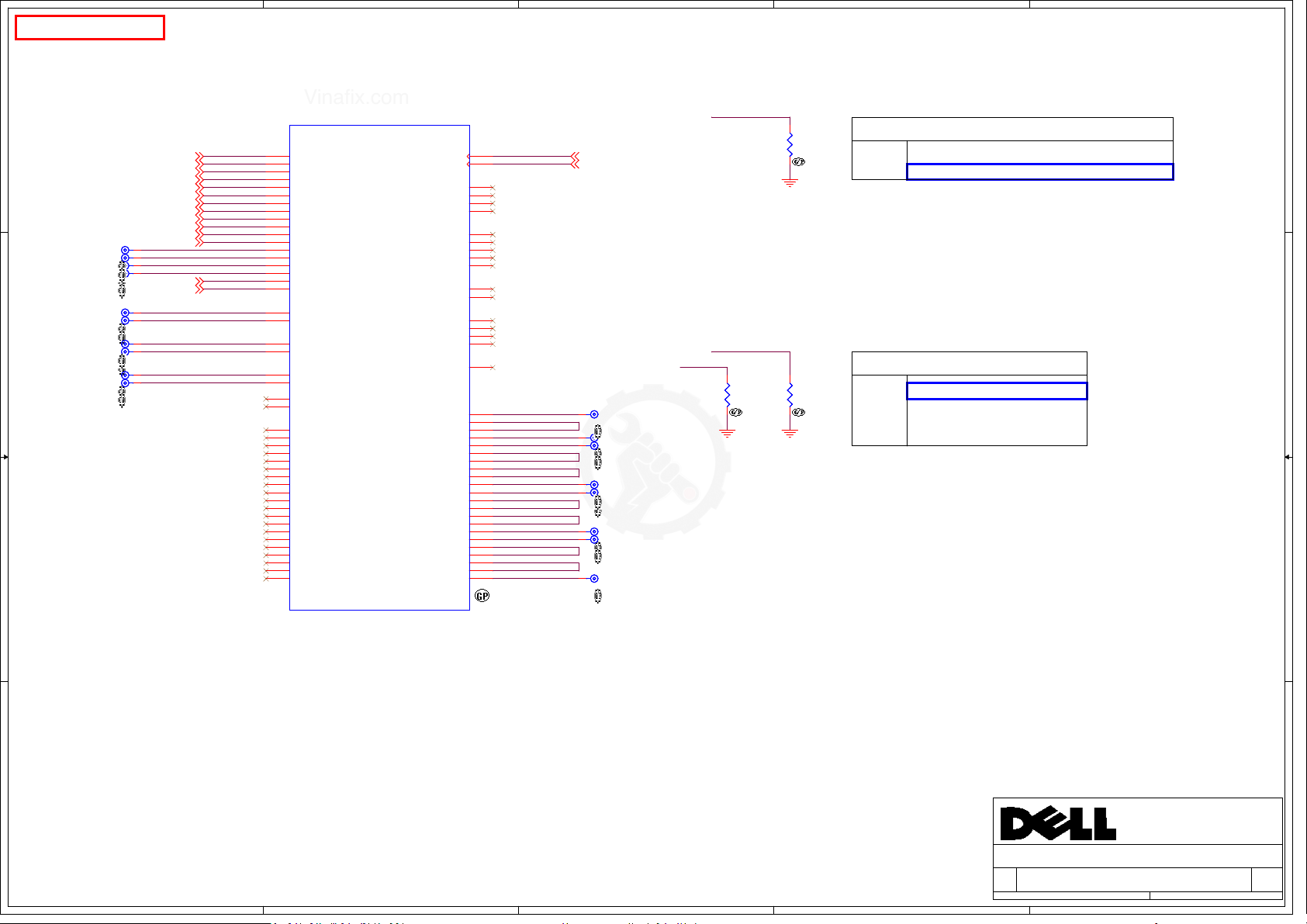

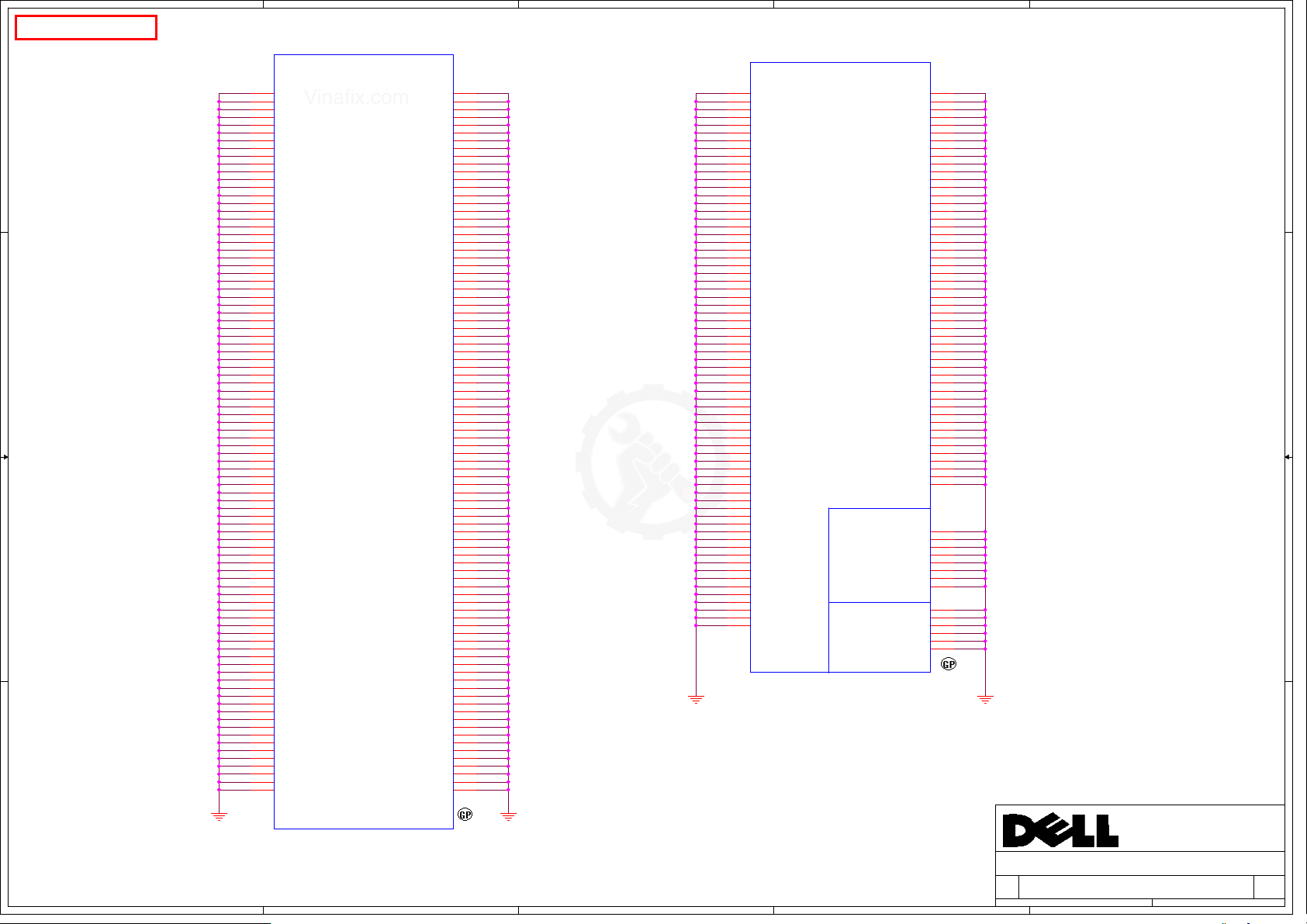

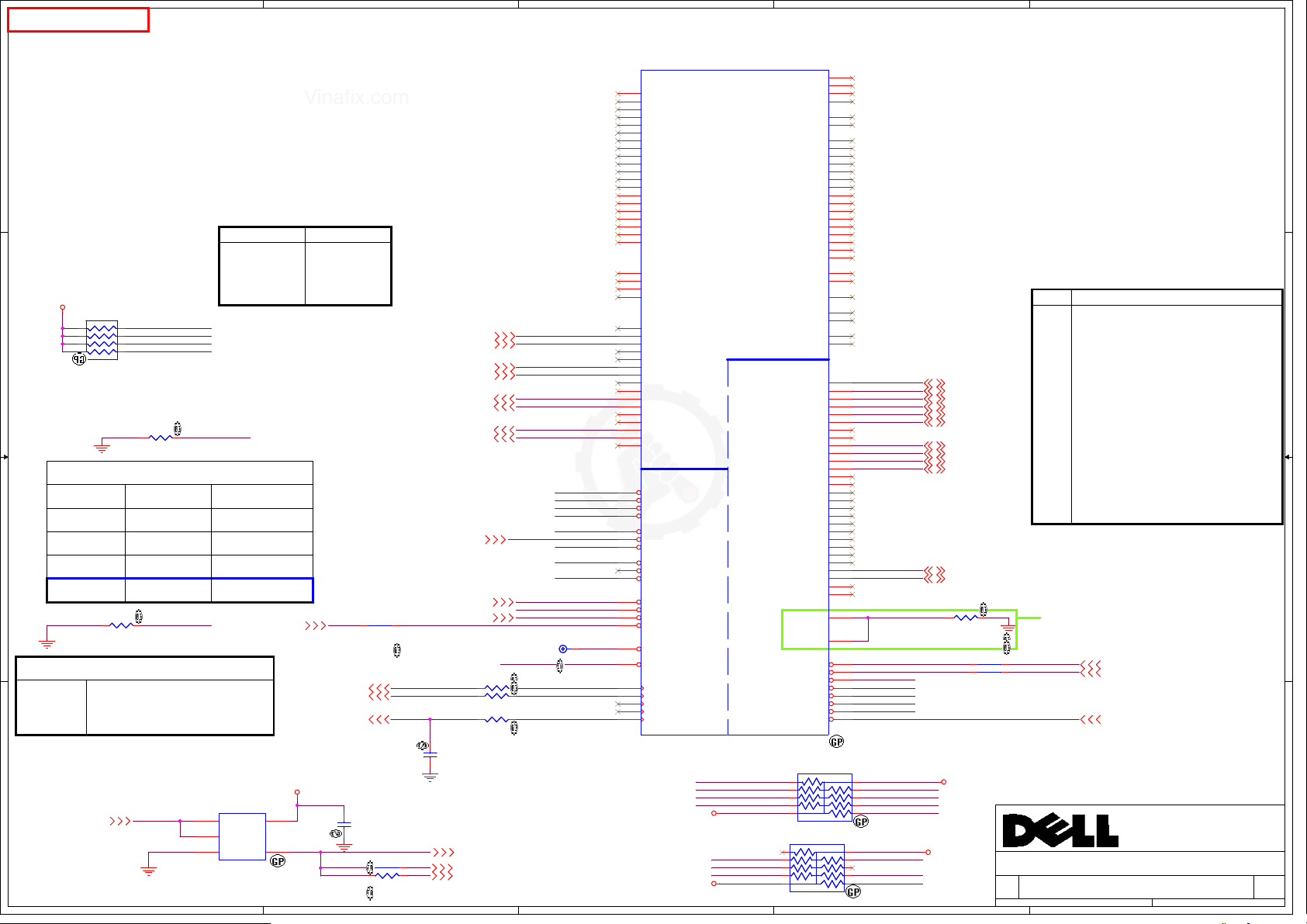

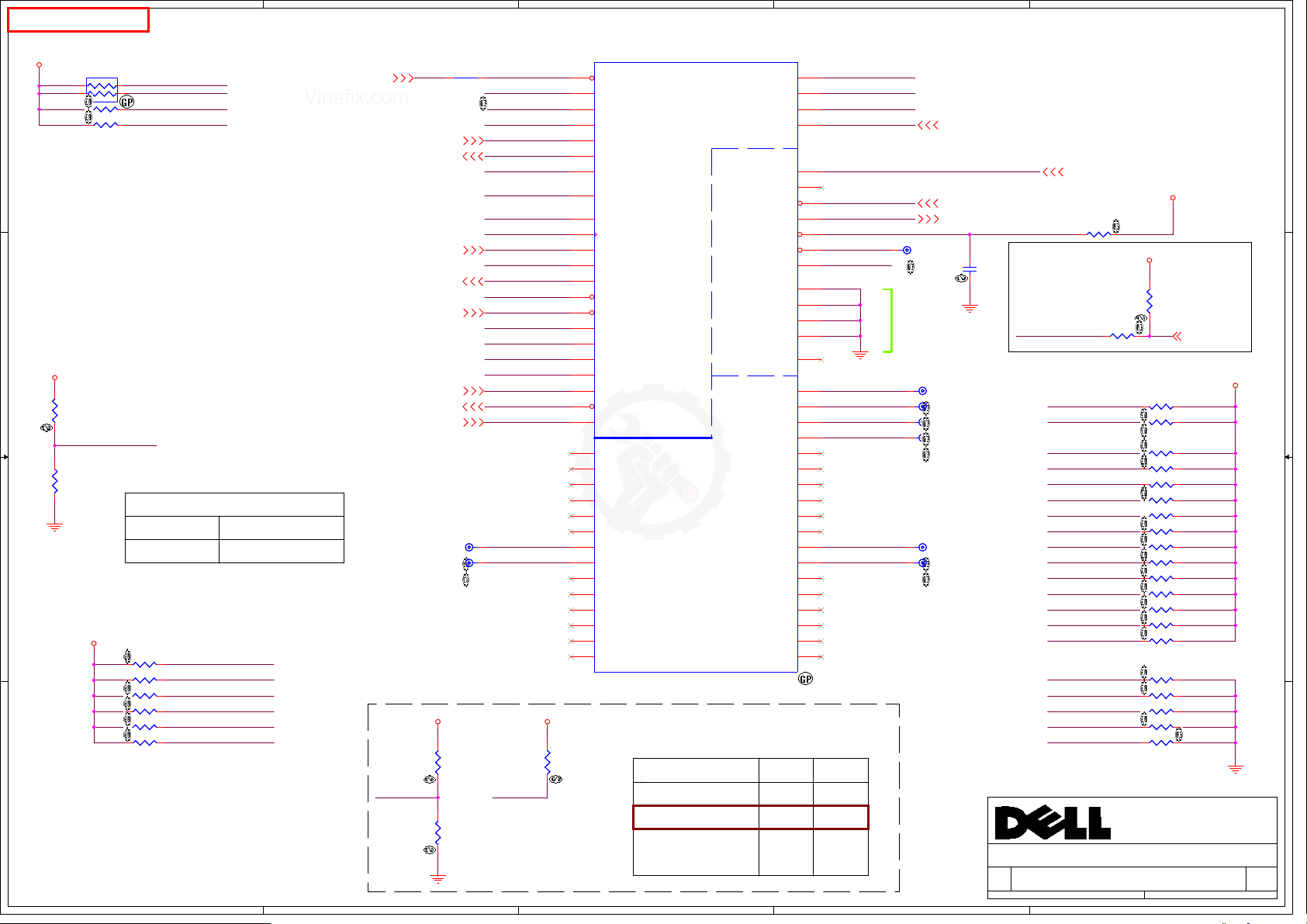

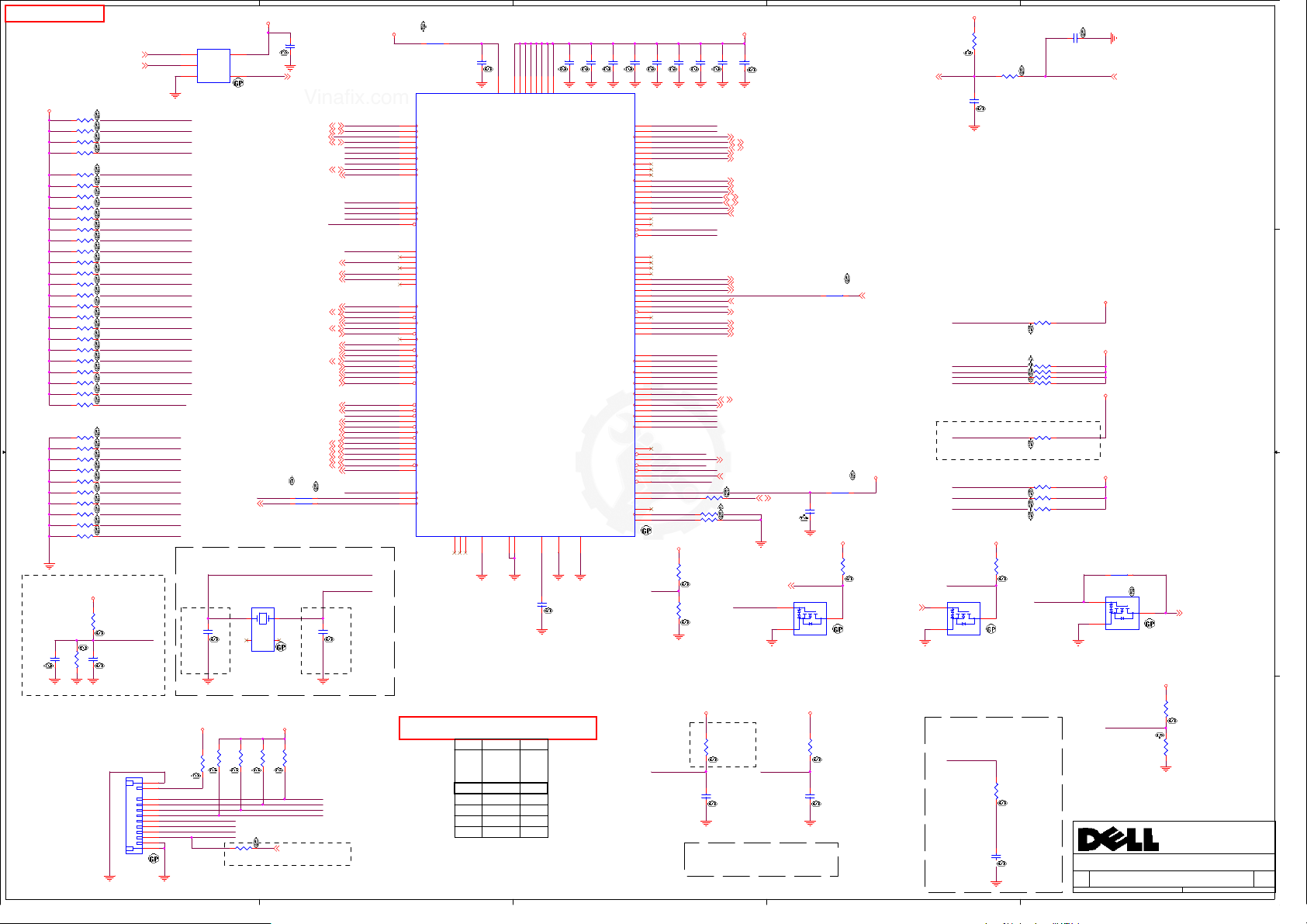

PCH Strapping

A

Name Schematics Notes

Chief River Schematic Checklist Rev.0_72

B

Sandy & Ivy Bridge Compatibility

C

Pin Name Configuration Schematic Notes

D

Chief River Schematic Checklist Rev.0_xx

E

SPKR

INIT3_3V# Weak internal pull-up. Leave as "No Connect".

4 4

INTVRMEN

GNT3#/GPIO55

GNT2#/GPIO53

GNT1#/GPIO51

DF_TVS

HAD_DOCK_EN#

/GPIO[33]

HDA_SDO Weak internal pull-down. Do not pull high. Sampled at rising edge of RSMRST#.

HDA_SYNC

GPIO15

3 3

Power Plane

+5V_RUN

+3.3V_RUN

+1.8V_RUN

+1.5V_RUN

+1.05V_RUN_VTT

+1.05V_M

+VCC_SA

+VCC_CORE

+VCC_GFXCORE

2 2

+1.35V_MEM

+0.675V_DDR_VTT

The signal has a weak internal pull-down.

If the signal is sampled high, this indicates that the system is strapped to the

"No Reboot" mode (Panther Point will disable the TCO Timer system reboot feature).

Integrated 1 V VRMs is enabled when high, External when low.

GNT[3:0]# functionality is not available on Mobile.

Mobile: Used as GPIO only

Pull-up resistors are not required on these signals.

If pull-ups are used, they should be tied to the Vcc3_3power rail.

DF_TVS needs to be pulled up to VccDFTERM power rail through 2.2 kOhms ±5% resistor.

This signal controls the external Intel HD Audio docking isolation logic. This is

an active-low-signal. When deasserted the external docking switch is in isolate mode.

When asserted the external docking switch electrically connects the Intel HD Audio

dock signals to the corresponding Panther Point signals. This signal can instead

be used as GPIO33.

Weak internal pull-down. Do not pull high. Sampled at rising edge of RSMRST#.

Low (0)

Intel ME Crypto Transport Layer Security (TLS) cipher suite with no confidentiality

High (1)

Intel ME Crypto Transport Layer Security (TLS) cipher suite with confidentiality

Voltage DescriptionActice StatusPower Plane

5V

3.3V

1.8V

1.5V

1.05V

1.05V

0.75V~0.9V

0.3V to 1.3V

0 to 1.25V

1.5V

0.75V

S0

S3

CPU Core Rail

Graphics Core Rail

DDR3 VREF

PROC_SELECT#

&

DF_TVS

VCCIO_SEL

VCCSA_VID[0:1]

Sandy Bridge + Ivy Bridge

Ivy Bridge

Sandy Bridge + Ivy Bridge

Ivy Bridge

Sandy Bridge + Ivy Bridge

Ivy Bridge

Sandy Bridge + Ivy Bridge

Ivy Bridge

Processor Strapping

Pin Name Strap Description

CFG[2]

CFG[4]

CFG[6:5]

PCI-Express Static

Lane Reversal

PCI-Express

Port Bifurcation

Straps

DDR3 VREF, M1 and M3 function are required.

No change.

Connect DF_TVS signal of the PCH to PROC_SELECT# of the processor

through a 1K±5% series resistor. PROC_SELECT# also needs a 2.2K±5%

pull up resistor to PCH VccDFTERM rail.

No change.

The POR for Ivy Bridge mobile parts is now 1.05 V. There is no

longer a need for a separate VR for the processor at 1.0 V and

the PCH at 1.05 V. A single VR may be shared for both.

No change.

VCCSA[0:1] are the select pin of VCCSA's power control.

No change.

Chief River Schematic Checklist Rev.0_72

Configuration (Default value for each bit is

1 unless specified otherwise)

1:

Normal Operation.

Lane Numbers Reversed 15 -> 0, 14 -> 1, ...

0:

Disabled - No Physical Display Port attached to

1:

Embedded DisplayPort.

Enabled - An external Display Port device is

0:

connectd to the EMBEDDED display Port

11:

1x16 PCI Express

2 x8 - PCI Express

10:

Reserved

01:

1x8, 2x4 PCI Express

00:

Default

Value

1

1

11

POP

Value

1

1

11

PCIE Table SATA TableUSB Table

BT+

DCBATOUT

+15V_ALW

+5V_ALW

+3.3V_ALW

+3.3V_LAN 3.3V

+3.3V_ALW2 DSW, Sx ON for supporting

RTC_AUX_S5

1 1

6V~14.1V

6V~14.1V

15V

5V

3.3V

3.3V

3.3V

All S states

WOL_EN

G3, Sx

AC Brick Mode only

Legacy WOL

Deep Sleep states

Powered by Li Coin Cell

in G3 and +V3ALW in Sx

Pair

USB0(Left side-HDMI/B)

0

USB1(Right side-IO/B, for USB3.0)

1

USB2(Right side-IO/B, for USB3.0)

2

NC

3

WLAN

4

WWAN

5

NC

6

NC

7

NC

8

NC

9

NC

10

NC

11

CAMERA

12

NC

13

Device

Lane

1

2

3

4

5

6

7

8

PCIE

Device

NC

WLAN

NC

NC

NC

Card Reader

Onboard LAN

NC

SATA

Pair

0

1

2

3

4

5

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

Device

HDD1

mSATA

NC

NC

NC

NC

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Table of Content

Table of Content

Table of Content

Austin 13

Austin 13

Austin 13

3 106Tuesday, February 26, 2013

3 106Tuesday, February 26, 2013

3 106Tuesday, February 26, 2013

A00

A00

A00

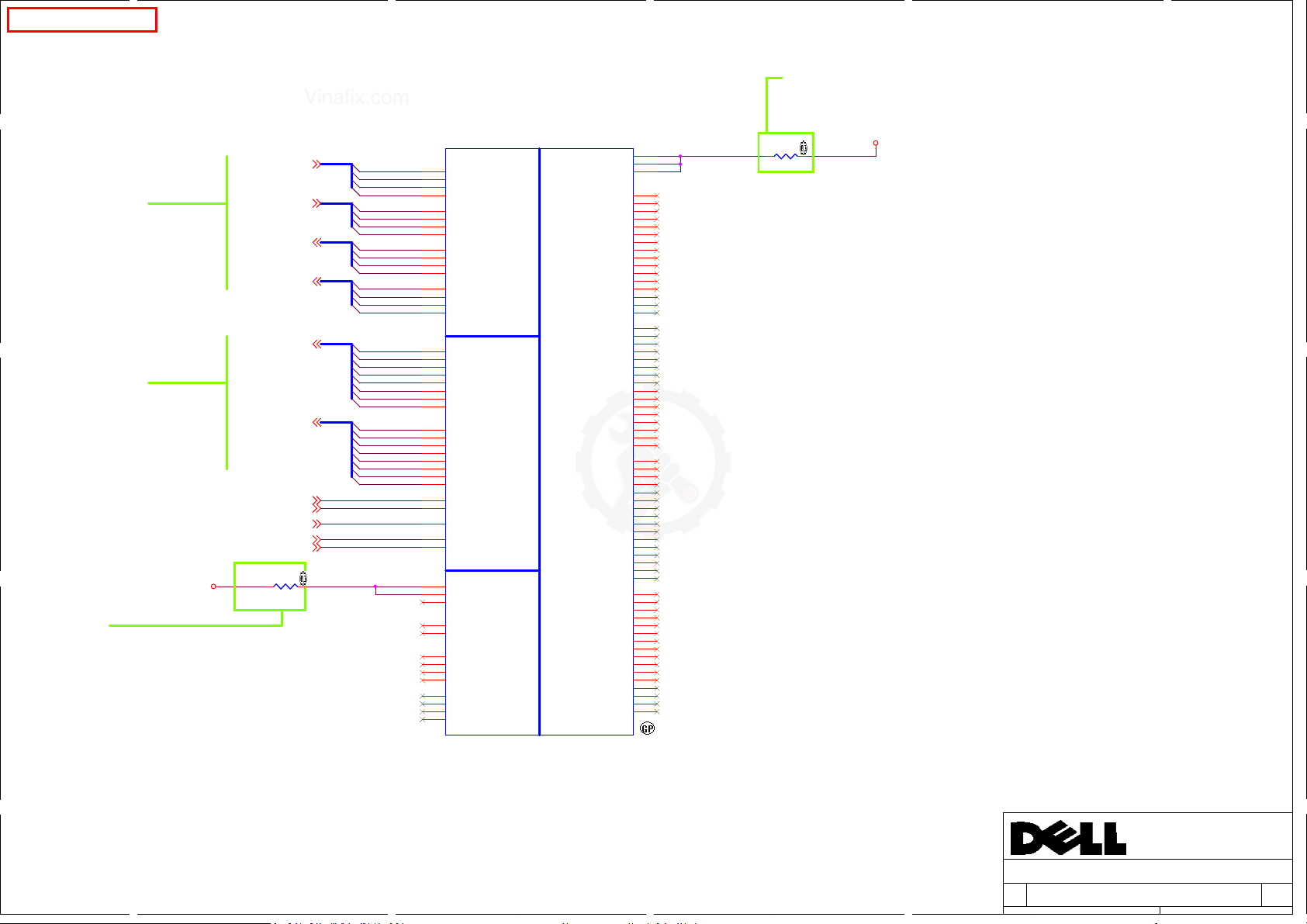

Vinafix.com

5

4

3

2

1

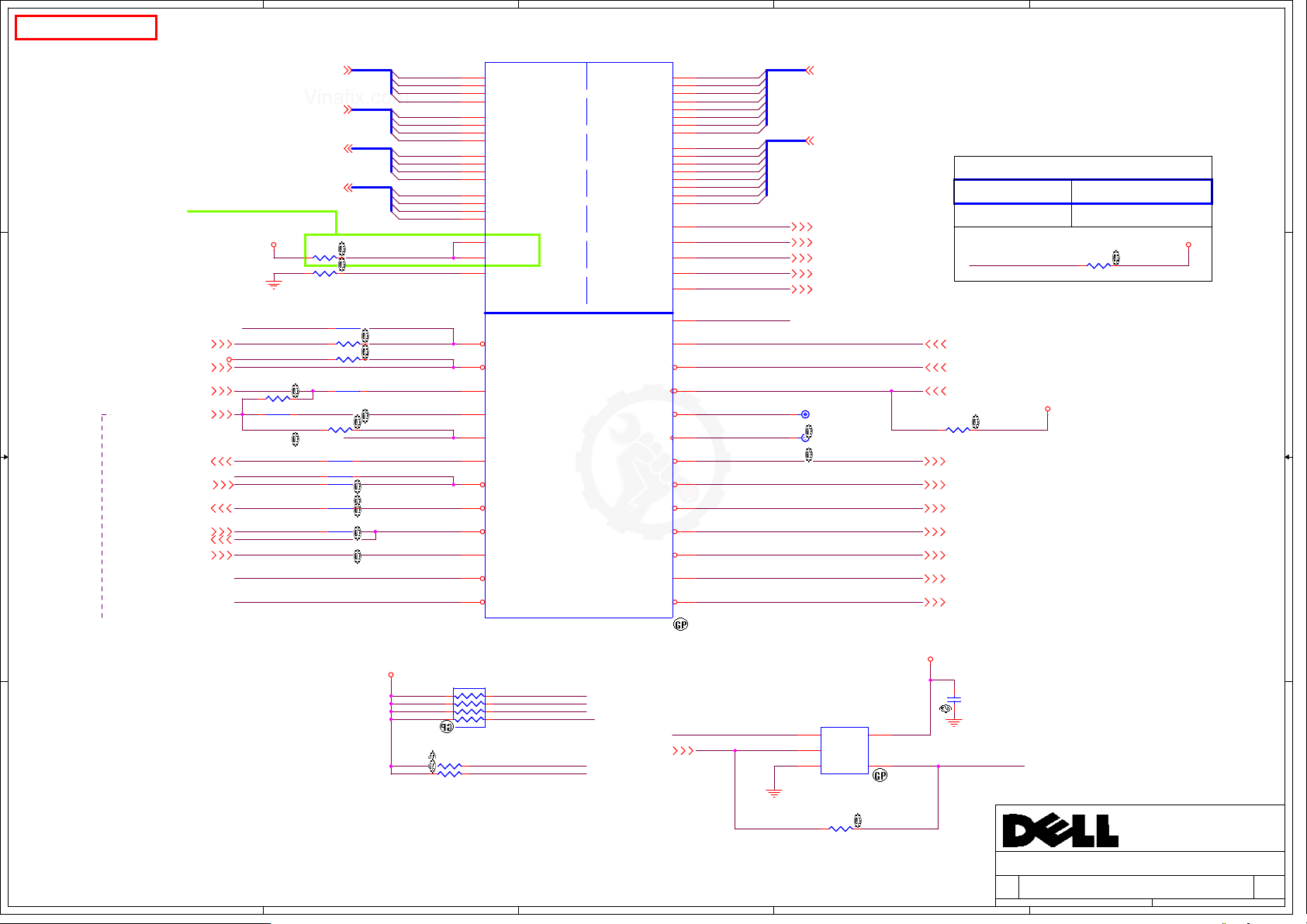

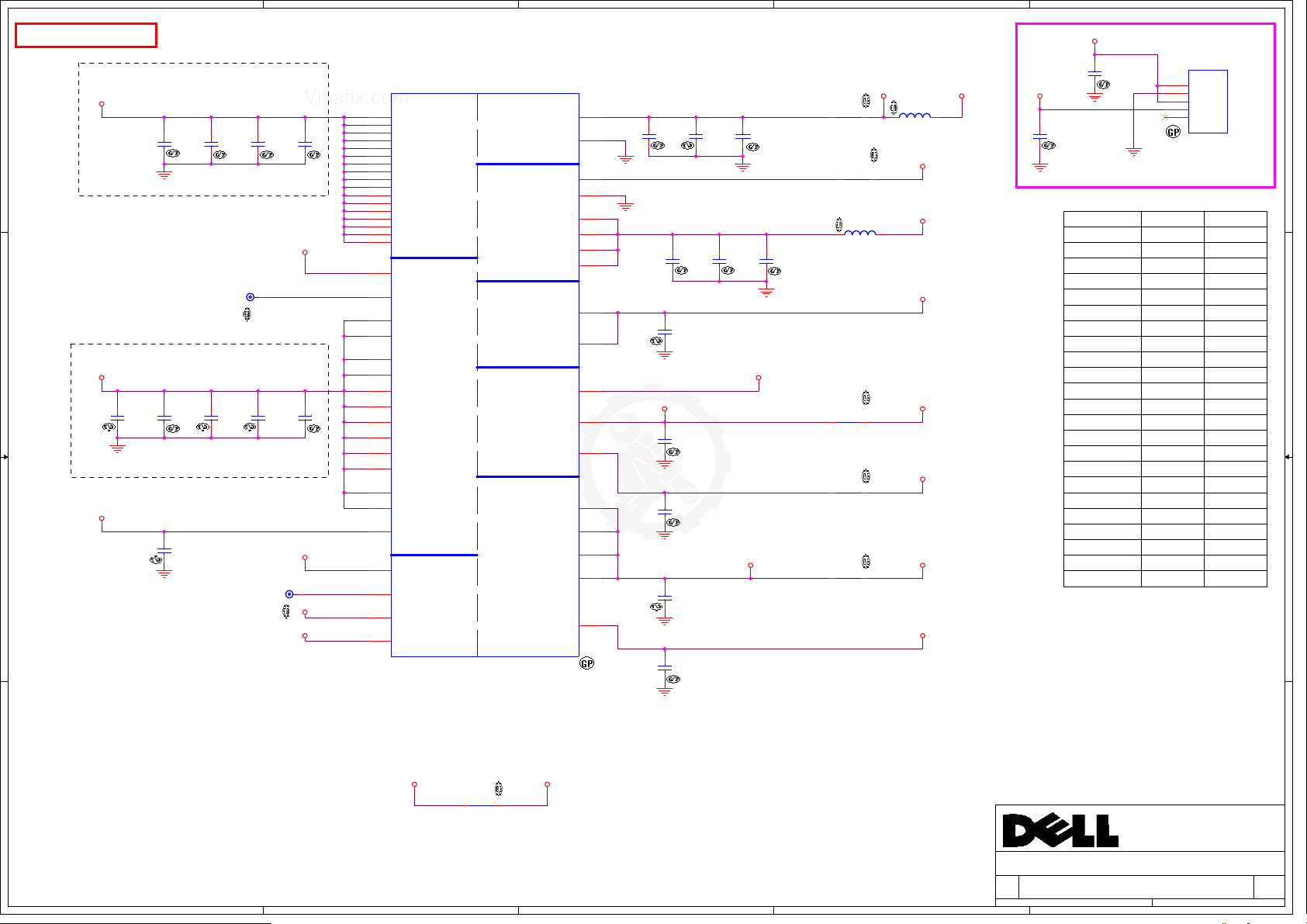

SSID = CPU

Layout Note:

Signal Routing Guideline:

PEG_ICOMPO keep W/S=12/15 mils and routing length less than 500 mils.

D D

1 OF 9

CPU1A

CPU1A

DMI_TXN[3:0](19)

Layout Note:

DMI trace length 2000~8000mil

C C

Layout Note:

FDI trace length 2000~6500mil

B B

Layout Note:

Signal Routing Guideline:

EDP_ICOMPO keep W/S=12/15 mils and routing length less than 500 mils.

EDP_COMPIO keep W/S=4/15 mils and routing length less than 500 mils.

+1.05V_RUN_VTT

DMI_TXP[3:0](19)

DMI_RXN[3:0](19)

DMI_RXP[3:0](19)

FDI_TXN[7:0](19)

FDI_TXP[7:0](19)

FDI_FSYNC0(19)

FDI_FSYNC1(19)

FDI_INT(19)

FDI_LSYNC0(19)

FDI_LSYNC1(19)

R402 24D9R2F-L-GPR402 24D9R2F-L-GP

1 2

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

FDI_TXN0

FDI_TXN1

FDI_TXN2

FDI_TXN3

FDI_TXN4

FDI_TXN5

FDI_TXN6

FDI_TXN7

FDI_TXP0

FDI_TXP1

FDI_TXP2

FDI_TXP3

FDI_TXP4

FDI_TXP5

FDI_TXP6

FDI_TXP7

FDI_FSYNC0

FDI_FSYNC1

FDI_INT

FDI_LSYNC0

FDI_LSYNC1

DP_COMP

M2

DMI_RX#0

P6

DMI_RX#1

P1

DMI_RX#2

P10

DMI_RX#3

N3

DMI_RX0

P7

DMI_RX1

P3

DMI_RX2

P11

DMI_RX3

K1

DMI_TX#0

M8

DMI_TX#1

N4

DMI_TX#2

R2

DMI_TX#3

K3

DMI_TX0

M7

DMI_TX1

P4

DMI_TX2

T3

DMI_TX3

U7

FDI0_TX#0

W11

FDI0_TX#1

W1

FDI0_TX#2

AA6

FDI0_TX#3

W6

FDI1_TX#0

V4

FDI1_TX#1

Y2

FDI1_TX#2

AC9

FDI1_TX#3

U6

FDI0_TX0

W10

FDI0_TX1

W3

FDI0_TX2

AA7

FDI0_TX3

W7

FDI1_TX0

T4

FDI1_TX1

AA3

FDI1_TX2

AC8

FDI1_TX3

AA11

FDI0_FSYNC

AC12

FDI1_FSYNC

U11

FDI_INT

AA10

FDI0_LSYNC

AG8

FDI1_LSYNC

AF3

EDP_COMPIO

AD2

EDP_ICOMPO

AG11

EDP_HPD#

AG4

EDP_AUX#

AF4

EDP_AUX

AC3

EDP_TX#0

AC4

EDP_TX#1

AE11

EDP_TX#2

AE7

EDP_TX#3

AC1

EDP_TX0

AA4

EDP_TX1

AE10

EDP_TX2

AE6

EDP_TX3

IVY-BRIDGE-GP-NF

IVY-BRIDGE-GP-NF

71.00IVY.A0U

71.00IVY.A0U

DMI

DMI

Intel(R) FDI

Intel(R) FDI

eDP

eDP

1 OF 9

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RX#0

PEG_RX#1

PEG_RX#2

PEG_RX#3

PEG_RX#4

PEG_RX#5

PEG_RX#6

PEG_RX#7

PEG_RX#8

PEG_RX#9

PEG_RX#10

PEG_RX#11

PEG_RX#12

PEG_RX#13

PEG_RX#14

PEG_RX#15

PEG_RX0

PEG_RX1

PEG_RX2

PEG_RX3

PEG_RX4

PEG_RX5

PEG_RX6

PEG_RX7

PEG_RX8

PEG_RX9

PEG_RX10

PEG_RX11

PEG_RX12

PEG_RX13

PEG_RX14

PEG_RX15

PEG_TX#0

PEG_TX#1

PEG_TX#2

PEG_TX#3

PEG_TX#4

PEG_TX#5

PEG_TX#6

PEG_TX#7

PEG_TX#8

PEG_TX#9

PEG_TX#10

PEG_TX#11

PEG_TX#12

PEG_TX#13

PEG_TX#14

PEG_TX#15

PCI EXPRESS -- GRAPHICS

PCI EXPRESS -- GRAPHICS

PEG_TX0

PEG_TX1

PEG_TX2

PEG_TX3

PEG_TX4

PEG_TX5

PEG_TX6

PEG_TX7

PEG_TX8

PEG_TX9

PEG_TX10

PEG_TX11

PEG_TX12

PEG_TX13

PEG_TX14

PEG_TX15

G3

G1

G4

H22

J21

B22

D21

A19

D17

B14

D13

A11

B10

G8

A8

B6

H8

E5

K7

K22

K19

C21

D19

C19

D16

C13

D12

C11

C9

F8

C8

C5

H6

F6

K6

G22

C23

D23

F21

H19

C17

K15

F17

F14

A15

J14

H13

M10

F10

D9

J4

F22

A23

D24

E21

G19

B18

K17

G17

E14

C15

K13

G13

K10

G10

D8

K4

PEG_IRCOMP_R

R401 24D9R2F-L-GPR401 24D9R2F-L-GP

PEG_ICOMPI & PEG_RCOMPO keep W/S=4/15 mils and routing length less than 500 mils.

+1.05V_RUN_VTT

1 2

<Core Design>

<Core Design>

A A

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

CPU(PCIE/DMI/FDI)

CPU(PCIE/DMI/FDI)

CPU(PCIE/DMI/FDI)

Austin 13

Austin 13

Austin 13

4 106Tuesday, February 26, 2013

4 106Tuesday, February 26, 2013

4 106Tuesday, February 26, 2013

A00

A00

A00

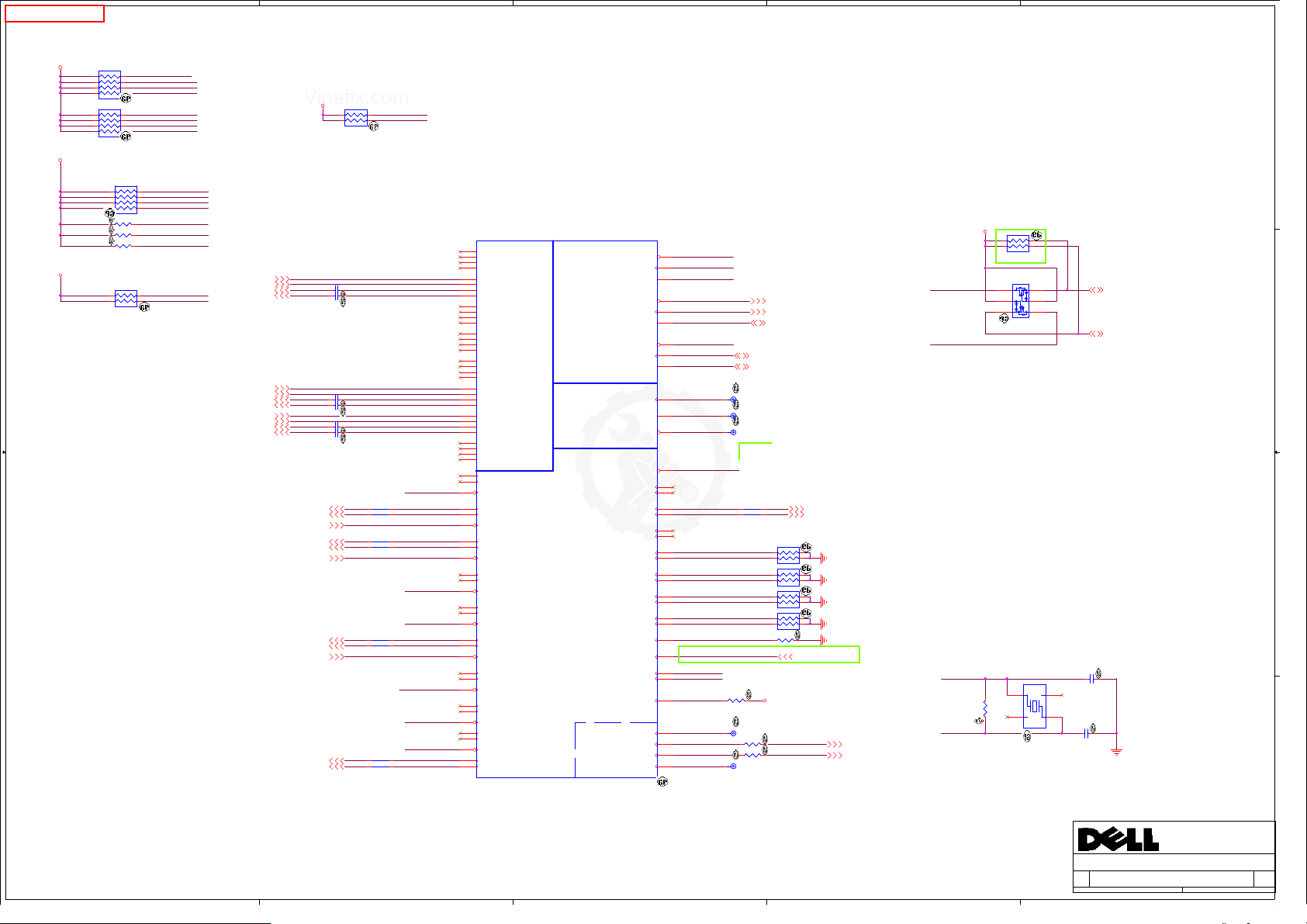

Vinafix.com

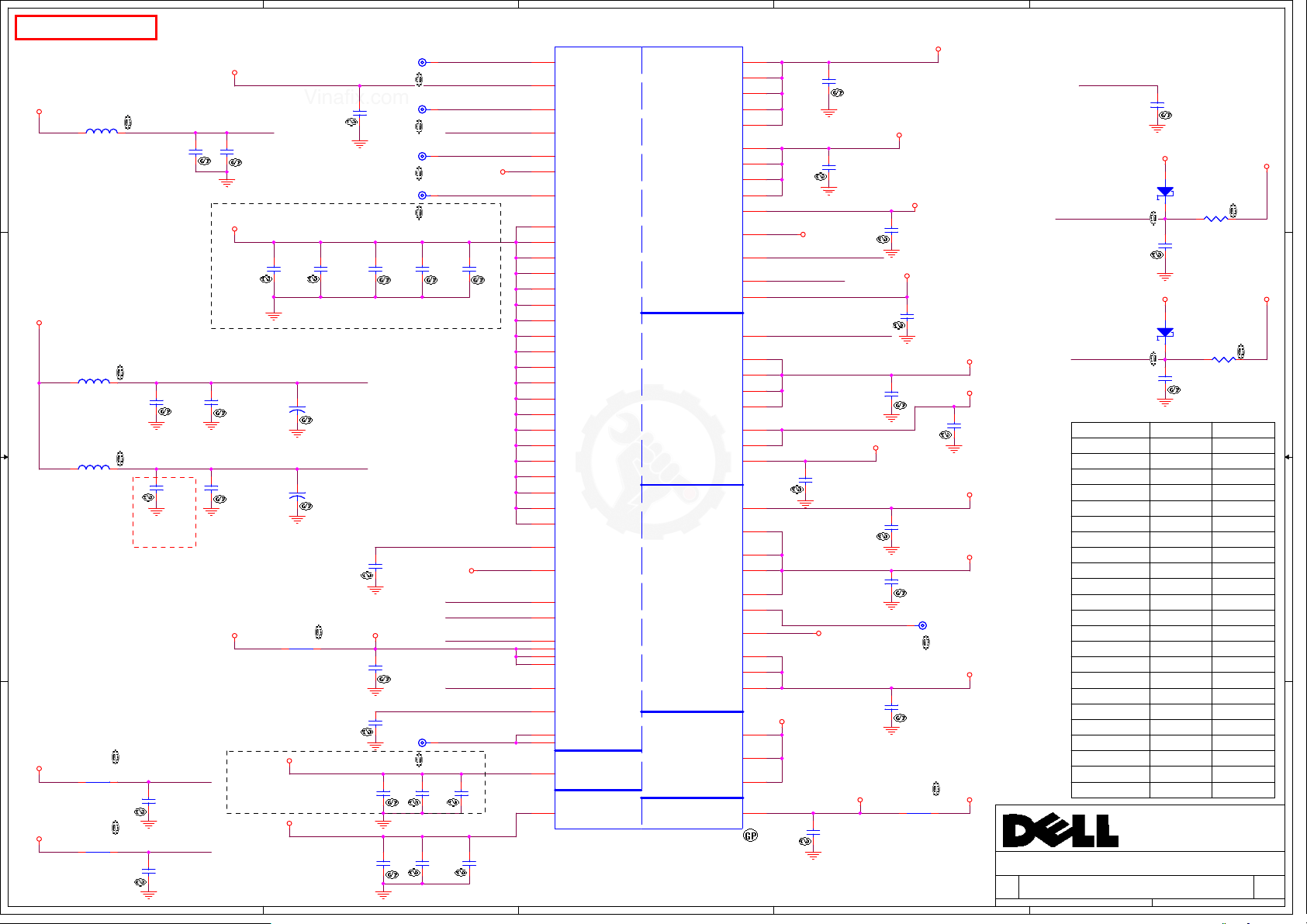

SSID = CPU

5

D D

+1.05V_RUN_VTT

H_SNB_IVB#(22)

R502

R502

1 2

56R2J-4-GP

56R2J-4-GP

C C

H_THERMTRIP#

DY

DY

R501

R501

1 2

62R2J-GP

62R2J-GP

R505 49D9R2F-GP

R505 49D9R2F-GP

H_PROCHOT#

H_CATERR#

1 2

DY

DY

Layout Note:

R501, R513 place near to CPU

CPU_DETECT#(78)

H_PECI(27)

H_PROCHOT#(27,40)

H_THERMTRIP#(28)

H_PM_SYNC(19)

H_CPUPW RGD(22,71)

B B

1 2

R512 0R0402-PAD-2-GPR512 0R0402-PAD-2-GP

R513

R513

1 2

56R2J-4-GP

56R2J-4-GP

1 2

R514 0R0402-PAD-2-GPR514 0R0402-PAD-2-GP

1 2

R504 1KR2J-1-GPR504 1KR2J-1-GP

1 2

DY

DY

R503 10KR2J-3-GP

R503 10KR2J-3-GP

PM_DRAM_PWRGD_CPU

4

CPU1B

CPU1B

F49

PROC_SELECT#

CPU_DETECT#_R

H_CATERR#

H_PECI

H_PROCHOT#_R

H_THERMTRIP#_R

H_PM_SYNC

H_CPUPW RGD_R

BUF_CPU_RST#

12

Layout Note:

C501 place near to CPU

C57

C49

A48

C45

D45

C48

B46

BE45

D44

C501

C501

SC100P50V2JN-3GP

SC100P50V2JN-3GP

PROC_DETECT#

CATERR#

PECI

PROCHOT#

THERMTRIP#

PM_SYNC

UNCOREPWRGOOD

SM_DRAMPWROK

RESET#

IVY-BRIDGE-GP-NF

IVY-BRIDGE-GP-NF

71.00IVY.A0U

71.00IVY.A0U

3

2 OF 9

2 OF 9

CLK_EXP_P

J3

MISC

MISC

CLOCKS

CLOCKS

THERMAL

THERMAL

DDR3

MISC

DDR3

MISC

PWR MANAGEMENT

PWR MANAGEMENT

JTAG & BPM

JTAG & BPM

BCLK

BCLK#

DPLL_REF_CLK

DPLL_REF_CLK#

SM_DRAMRST#

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

PRDY#

PREQ#

TCK

TMS

TRST#

TDO

DBR#

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

TDI

CLK_EXP_N

H2

CLK_DP_P_R

AG3

CLK_DP_N_R

AG1

DDR3_DRAMRST#_CPU

AT30

SM_RCOMP_0

BF44

SM_RCOMP_1

BE43

SM_RCOMP_2

BG43

Signal Routing Guideline:

SM_RCOMP keep routing length less than 500 mils.

Trace width = 15mil

XDP_PRDY#

N53

XDP_PREQ#

N55

XDP_TCLK

L56

XDP_TMS

L55

XDP_TRST#

J58

XDP_TDI_R

M60

XDP_TDO_R

L59

XDP_DBRESET#_R

K58

XDP_OBS0_R

G58

XDP_OBS1_R

E55

XDP_OBS2_R

E59

XDP_OBS3_R

G55

XDP_OBS4_R

G59

XDP_OBS5_R

H60

XDP_OBS6_R

J59

XDP_OBS7_R

J61

RN503

RN503

1

2 3

4

SRN1KJ-7-GP

SRN1KJ-7-GP

R507

R507

4K99R2F-L-GP

4K99R2F-L-GP

1 2

R506 140R2F-GPR506 140R2F-GP

1 2

R508 25D5R2F-GPR508 25D5R2F-GP

1 2

R511 200R2F-L-GPR511 200R2F-L-GP

1 2

XDP_PRDY# (71)

XDP_PREQ# (71)

XDP_TMS (71)

XDP_TRST# (71)

1 2

XDP

XDP

R531 0R2J-2-GP

R531 0R2J-2-GP

1 2

XDP

XDP

R530 0R2J-2-GP

R530 0R2J-2-GP

1 2

R529 0R2J-2-GPR529 0R2J-2-GP

1 2

XDP

XDP

R515 0R2J-2-GP

R515 0R2J-2-GP

1 2

XDP

XDP

R516 0R2J-2-GP

R516 0R2J-2-GP

1 2

XDP

XDP

R523 0R2J-2-GP

R523 0R2J-2-GP

1 2

XDP

XDP

R524 0R2J-2-GP

R524 0R2J-2-GP

1 2

XDP

XDP

R525 0R2J-2-GP

R525 0R2J-2-GP

1 2

XDP

XDP

R526 0R2J-2-GP

R526 0R2J-2-GP

1 2

XDP

XDP

R527 0R2J-2-GP

R527 0R2J-2-GP

1 2

XDP

XDP

R528 0R2J-2-GP

R528 0R2J-2-GP

2

CLK_EXP_P (20)

CLK_EXP_N (20)

+1.05V_RUN_VTT

XDP_TDI

XDP_TDO

XDP_OBS0

XDP_OBS1

XDP_OBS2

XDP_OBS3

XDP_OBS4

XDP_OBS5

XDP_OBS6

XDP_OBS7

+3.3V_ALW_PCH

A00_0206

S

G

SCD047U16V2KX-1-GP

SCD047U16V2KX-1-GP

12

R532 0R0402-PAD-2-GPR532 0R0402-PAD-2-GP

C505

C505

R533 0R2J-2-GP

R533 0R2J-2-GP

XDP_TDI (71)

XDP_TDO (71)

XDP_DBRESET# (19,71)

XDP_OBS0 (71)

XDP_OBS1 (71)

XDP_OBS2 (71)

XDP_OBS3 (71)

XDP_OBS4 (71)

XDP_OBS5 (71)

XDP_OBS6 (71)

XDP_OBS7 (71)

C504

SCD1U16V2KX-3GP

C504

SCD1U16V2KX-3GP

12

+1.35V_CPU_VDDQ

XDP_TDI

XDP_TMS

XDP_TDO

XDP_TRST#

XDP_TCLK

Q511

Q511

D

2N7002K-2-GP

2N7002K-2-GP

84.2N702.J31

84.2N702.J31

2ND = 84.2N702.031

2ND = 84.2N702.031

3rd = 84.2N702.W31

3rd = 84.2N702.W31

1 2

1 2

DY

DY

RN501

RN501

1

8

2

7

3

6

XDP

XDP

4 5

SRN51J-1-GP

SRN51J-1-GP

RN502

RN502

1

4

2 3

XDP

XDP

SRN51J-GP

SRN51J-GP

+1.35V_MEM

R535

R535

1KR2J-1-GP

1KR2J-1-GP

1 2

1 2

R534

R534

1KR2J-1-GP

1KR2J-1-GP

DDR_HVREF_RST_PCH (20)

DDR_HVREF_RST_GATE (27)

DDR_HVREF_RST (12)XDP_TCLK (71)

1

+1.05V_RUN_VTT

DDR3_DRAMRST# (14,15)

U502

U502

RUNPWROK(27,78)

PM_DRAM_PWRGD(19)

+3.3V_ALW_PCH

H_PECI

EC501

EC501

SC100P50V2JN-3GP

SC100P50V2JN-3GP

1 2

R519 200R2F-L-GPR519 200R2F-L-GP

Buffered reset to CPU

U501

U501

1

B

PCH_PLTRST#(18)

A A

2

A

GND3Y

74AHC1G09GW-GP

74AHC1G09GW-GP

73.01G09.0AB

73.01G09.0AB

2ND = 73.01G09.BAH

2ND = 73.01G09.BAH

3rd = 73.7SH09.0AG

3rd = 73.7SH09.0AG

Open Drain Buffer

VCC

5

BUFO_CPU_RST# BUF_CPU_RST#

4

+3.3V_RUN

12

+1.05V_RUN_VTT

12

C503

SCD1U16V2KX-3GP

C503

SCD1U16V2KX-3GP

R518

R518

75R2J-1-GP

75R2J-1-GP

1 2

R517 43R2J-GPR517 43R2J-GP

DY

DY

12

1

B

2

A

GND3Y

74AHC1G09GW-GP

74AHC1G09GW-GP

73.01G09.0AB

73.01G09.0AB

2ND = 73.01G09.BAH

2ND = 73.01G09.BAH

3rd = 73.7SH09.0AG

3rd = 73.7SH09.0AG

Open Drain Buffer

RUN_ON_CPU1.5VS3#(36)

5

VCC

RUNPWROK_AND PM_DRAM_PWRGD_CPU

4

DY

DY

DY

DY

G

12

Q510_D

D

R522

R522

39R2J-L-GP

39R2J-L-GP

S

R520

R520

200R2F-L-GP

200R2F-L-GP

1 2

1 2

R521 130R2F-1-GPR521 130R2F-1-GP

Q510

Q510

2N7002K-2-GP

2N7002K-2-GP

84.2N702.J31

84.2N702.J31

2ND = 84.2N702.031

2ND = 84.2N702.031

3rd = 84.07002.I31

3rd = 84.07002.I31

4th = 84.2N702.W31

4th = 84.2N702.W31

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

CPU(THERMAL/CLOCK/PM)

CPU(THERMAL/CLOCK/PM)

CPU(THERMAL/CLOCK/PM)

Taipei Hsien 221, Taiwan, R.O.C.

Austin 13

Austin 13

Austin 13

5 106Tuesday, February 26, 2013

5 106Tuesday, February 26, 2013

5 106Tuesday, February 26, 2013

A00

A00

A00

Vinafix.com

5

4

3

2

1

SSID = CPU

4 OF 9

CPU1D

AL4

AL1

AN3

AR4

AK4

AK3

AN4

AR1

AU4

AT2

AV4

BA4

AU3

AR3

AY2

BA3

BE9

BD9

BD13

BF12

BF8

BD10

BD14

BE13

BF16

BE17

BE18

BE21

BE14

BG14

BG18

BF19

BD50

BF48

BD53

BF52

BD49

BE49

BD54

BE53

BF56

BE57

BC59

AY60

BE54

BG54

BA58

AW59

AW58

AU58

AN61

AN59

AU59

AU61

AN58

AR58

AK58

AL58

AG58

AG59

AM60

AL59

AF61

AH60

BG39

BD42

AT22

AV43

BF40

BD45

CPU1D

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

SB_BS0

SB_BS1

SB_BS2

SB_CAS#

SB_RAS#

SB_WE#

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

3 OF 9

CPU1C

D D

C C

B B

M_A_DQ[63:0](14)

M_A_DQ[63:0]

M_A_BS0(14)

M_A_BS1(14)

M_A_BS2(14)

M_A_CAS#(14)

M_A_RAS#(14)

M_A_WE#(14)

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

AG6

AP11

AJ10

AR11

AP6

AU6

AV9

AR6

AP8

AT13

AU13

BC7

BB7

BA13

BB11

BA7

BA9

BB9

AY13

AV14

AR14

AY17

AR19

BA14

AU14

BB14

BB17

BA45

AR43

AW48

BC48

BC45

AR45

AT48

AY48

BA49

AV49

BB51

AY53

BB49

AU49

BA53

BB55

BA55

AV56

AP50

AP53

AV54

AT54

AP56

AP52

AN57

AN53

AG56

AG53

AN55

AN52

AG55

AK56

BD37

BF36

BA28

BE39

BD39

AT41

AJ6

AL6

AJ8

AL8

AL7

CPU1C

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

SA_BS0

SA_BS1

SA_BS2

SA_CAS#

SA_RAS#

SA_WE#

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

3 OF 9

SA_CK0

SA_CK#0

SA_CKE0

SA_CK1

SA_CK#1

SA_CKE1

SA_CS#0

SA_CS#1

SA_ODT0

SA_ODT1

SA_DQS#0

SA_DQS#1

SA_DQS#2

SA_DQS#3

SA_DQS#4

SA_DQS#5

SA_DQS#6

SA_DQS#7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

AU36

AV36

AY26

AT40

AU40

BB26

BB40

BC41

AY40

BA41

AL11

AR8

AV11

AT17

AV45

AY51

AT55

AK55

AJ11

AR10

AY11

AU17

AW45

AV51

AT56

AK54

BG35

BB34

BE35

BD35

AT34

AU34

BB32

AT32

AY32

AV32

BE37

BA30

BC30

AW41

AY28

AU26

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DIMA_CLK_DDR0 (14)

M_A_DIMA_CLK_DDR#0 (14)

M_A_DIMA_CKE0 (14)

M_A_DIMA_CLK_DDR1 (14)

M_A_DIMA_CLK_DDR#1 (14)

M_A_DIMA_CKE1 (14)

M_A_DIMA_CS#0 (14)

M_A_DIMA_CS#1 (14)

M_A_DIMA_ODT0 (14)

M_A_DIMA_ODT1 (14)

M_A_DQS#[7:0] (14)

M_A_DQS[7:0] (14)

M_A_A[15:0] (14)

M_B_DQ[63:0](15)

M_B_DQ[63:0]

M_B_BS0(15)

M_B_BS1(15)

M_B_BS2(15)

M_B_CAS#(15)

M_B_RAS#(15)

M_B_WE#(15)

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

4 OF 9

SB_CK0

SB_CK#0

SB_CKE0

SB_CK1

SB_CK#1

SB_CKE1

SB_CS#0

SB_CS#1

SB_ODT0

SB_ODT1

SB_DQS#0

SB_DQS#1

SB_DQS#2

SB_DQS#3

SB_DQS#4

SB_DQS#5

SB_DQS#6

SB_DQS#7

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

BA34

AY34

AR22

BA36

BB36

BF27

BE41

BE47

AT43

BG47

AL3

AV3

BG11

BD17

BG51

BA59

AT60

AK59

AM2

AV1

BE11

BD18

BE51

BA61

AR59

AK61

BF32

BE33

BD33

AU30

BD30

AV30

BG30

BD29

BE30

BE28

BD43

AT28

AV28

BD46

AT26

AU22

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_DIMB_CLK_DDR0 (15)

M_B_DIMB_CLK_DDR#0 (15)

M_B_DIMB_CKE0 (15)

M_B_DIMB_CLK_DDR1 (15)

M_B_DIMB_CLK_DDR#1 (15)

M_B_DIMB_CKE1 (15)

M_B_DIMB_CS#0 (15)

M_B_DIMB_CS#1 (15)

M_B_DIMB_ODT0 (15)

M_B_DIMB_ODT1 (15)

M_B_DQS#[7:0] (15)

M_B_DQS[7:0] (15)

M_B_A[15:0] (15)

IVY-BRIDGE-GP-NF

IVY-BRIDGE-GP-NF

IVY-BRIDGE-GP-NF

71.00IVY.A0U

71.00IVY.A0U

A A

5

4

3

IVY-BRIDGE-GP-NF

71.00IVY.A0U

71.00IVY.A0U

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Tuesday, February 26, 2013

Tuesday, February 26, 2013

Tuesday, February 26, 2013

Date: Sheet of

Date: Sheet of

Date: Sheet of

CPU (DDR)

CPU (DDR)

CPU (DDR)

Austin 13

Austin 13

Austin 13

Taipei Hsien 221, Taiwan, R.O.C.

6 106

6 106

6 106

1

A00

A00

A00

Vinafix.com

5

SSID = CPU

4

3

2

1

CFG6

CFG2

CFG5

DY

DY

12

R701

R701

1KR2J-1-GP

1KR2J-1-GP

DY

DY

DY

DY

12

12

R702

R702

1KR2J-1-GP

1KR2J-1-GP

R704

R704

1KR2J-1-GP

1KR2J-1-GP

PEG Static Lane Reversal

CFG[2]

1: Normal Operation; Lane #

definition matches socket pin map definition

0:Lane Reversed

PCIE Port Bifurcation Straps

CFG[6:5]

11:

1x16 PCI Express

2 x8 - PCI Express

10:

Reserved

01:

1x8, 2x4 PCI Express

00:

5 OF 9

CPU1E

D D

CFG0(71)

CFG1(71)

CFG2(71)

CFG3(71)

CFG4(71)

CFG5(71)

CFG6(71)

CFG7(71)

CFG8(71)

CFG9(71)

CFG10(71)

TP701TPAD14-OP-GP TP701TPAD14-OP-GP

TP702TPAD14-OP-GP TP702TPAD14-OP-GP

TP703TPAD14-OP-GP TP703TPAD14-OP-GP

TP704TPAD14-OP-GP TP704TPAD14-OP-GP

TP715TPAD14-OP-GP TP715TPAD14-OP-GP

TP716TPAD14-OP-GP TP716TPAD14-OP-GP

C C

B B

TP717TPAD14-OP-GP TP717TPAD14-OP-GP

TP718TPAD14-OP-GP TP718TPAD14-OP-GP

TP719TPAD14-OP-GP TP719TPAD14-OP-GP

TP720TPAD14-OP-GP TP720TPAD14-OP-GP

CFG11(71)

1

1

1

1

CFG16(71)

CFG17(71)

VCC_VAL_SENSE

1

VSS_VAL_SENSE

1

VAXG_VAL_SENSE

1

VSSAXG_VAL_SENSE

1

VCC_DIE_SENSE

1

VSS_DIE_SENSE

1

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CPU1E

B50

CFG0

C51

CFG1

B54

CFG2

D53

CFG3

A51

CFG4

C53

CFG5

C55

CFG6

H49

CFG7

A55

CFG8

H51

CFG9

K49

CFG10

K53

CFG11

F53

CFG12

G53

CFG13

L51

CFG14

F51

CFG15

D52

CFG16

L53

CFG17

H43

VCC_VAL_SENSE

K43

VSS_VAL_SENSE

H45

VAXG_VAL_SENSE

K45

VSSAXG_VAL_SENSE

F48

VCC_DIE_SENSE

G48

RSVD47

H48

RSVD6

K48

RSVD7

BA19

RSVD8

AV19

RSVD9

AT21

RSVD10

BB21

RSVD11

BB19

RSVD12

AY21

RSVD13

BA22

RSVD14

AY22

RSVD15

AU19

RSVD16

AU21

RSVD17

BD21

RSVD18

BD22

RSVD19

BD25

RSVD20

BD26

RSVD21

BG22

RSVD22

BE22

RSVD23

BG26

RSVD24

BE26

RSVD25

BF23

RSVD26

BE24

RSVD27

RESERVED

RESERVED

5 OF 9

BCLK_ITP

BCLK_ITP#

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

RSVD39

RSVD40

RSVD41

RSVD42

RSVD43

RSVD44

RSVD45

DC_TEST_A4

DC_TEST_C4

DC_TEST_D3

DC_TEST_D1

DC_TEST_A58

DC_TEST_A59

DC_TEST_C59

DC_TEST_A61

DC_TEST_C61

DC_TEST_D61

DC_TEST_BD61

DC_TEST_BE61

DC_TEST_BE59

DC_TEST_BG61

DC_TEST_BG59

DC_TEST_BG58

DC_TEST_BG4

DC_TEST_BG3

DC_TEST_BE3

DC_TEST_BG1

DC_TEST_BE1

DC_TEST_BD1

N59

N58

N42

L42

L45

L47

M13

M14

U14

W14

P13

AT49

K24

AH2

AG13

AM14

AM15

N50

TP_DC_TEST_A4

A4

C4

DC_TEST_C4_D3

D3

TP_DC_TEST_D1

D1

TP_DC_TEST_A58

A58

A59

TP_DC_TEST_A59_C59

C59

A61

TP_DC_TEST_A61_C61

C61

TP_DC_TEST_D61

D61

TP_DC_TEST_BD61

BD61

BE61

TP_DC_TEST_BE59_BE61

BE59

BG61

DC_TEST_BG59_BG61

BG59

TP_DC_TEST_BG58

BG58

TP_DC_TEST_BG4

BG4

BG3

DC_TEST_BE3_BG3

BE3

BG1

DC_TEST_BE1_BG1

BE1

TP_DC_TEST_BD1

BD1

CLK_XDP_ITP (71)

CLK_XDP_ITP# (71)

TP723 TPAD14-OP-GPTP723 TPAD14-OP-GP

1

TP724 TPAD14-OP-GPTP724 TPAD14-OP-GP

1

TP725 TPAD14-OP-GPTP725 TPAD14-OP-GP

1

TP726 TPAD14-OP-GPTP726 TPAD14-OP-GP

1

TP727 TPAD14-OP-GPTP727 TPAD14-OP-GP

1

TP728 TPAD14-OP-GPTP728 TPAD14-OP-GP

1

TP729 TPAD14-OP-GPTP729 TPAD14-OP-GP

1

TP730 TPAD14-OP-GPTP730 TPAD14-OP-GP

1

IVY-BRIDGE-GP-NF

IVY-BRIDGE-GP-NF

71.00IVY.A0U

71.00IVY.A0U

<Core Design>

<Core Design>

A A

5

4

3

2

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Tuesday, February 26, 2013

Tuesday, February 26, 2013

Tuesday, February 26, 2013

Date: Sheet of

Date: Sheet of

Date: Sheet of

CPU (RESERVED)

CPU (RESERVED)

CPU (RESERVED)

Austin 13

Austin 13

Austin 13

Taipei Hsien 221, Taiwan, R.O.C.

7 106

7 106

7 106

1

A00

A00

A00

Vinafix.com

5

4

3

2

1

SSID = CPU

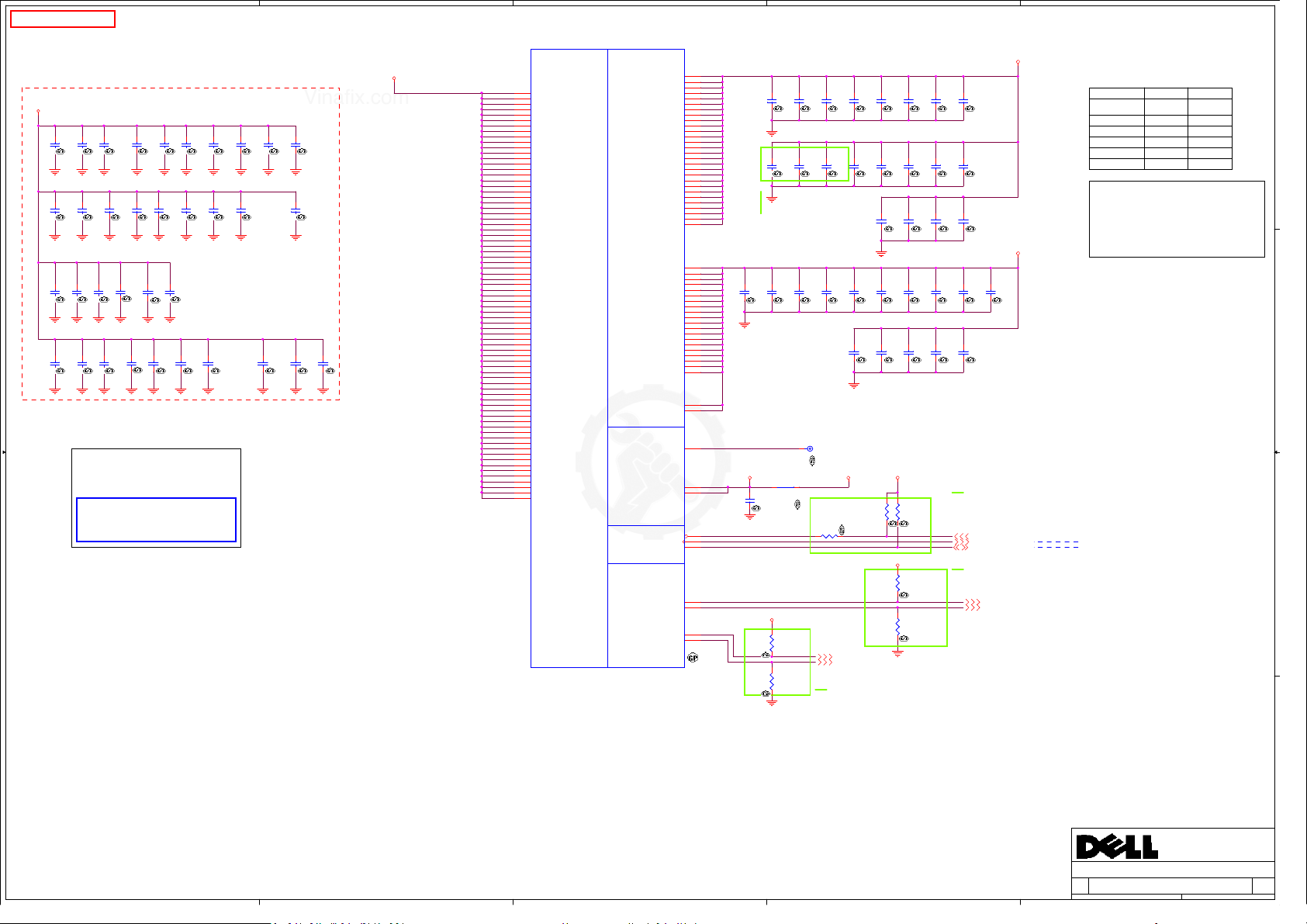

POWER

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

VCC72

VCC73

VCC74

VCC75

VCC76

POWER

CORE SUPPLY

CORE SUPPLY

CPU1F

CPU1F

VCC_CORE

VCC_CORE

D D

12

12

C801

C801

C821

C821

DY

DY

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

12

C811

C811

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

12

C825

C825

C830

C830

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C C

B B

12

12

C802

C802

C803

C803

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

VCC Output Decoupling Recommendation:

1.9m ohm loadline design:(for SV)

470u x 4(Remove)

22u x 20(0805)

2.2u x 35(0402)

2.9m ohm loadline design:(for ULV/LV)

330u x 3(Remove)

22u x 12(0805)

2.2u x 16(0402)

12

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C812

C812

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C831

C831

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C814

C814

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

12

12

C804

C804

C822

C822

C813

C813

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C805

C805

C806

C806

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

DY

DY

C832

C832

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

12

12

C823

C823

C824

C824

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

12

C843

C843

C847

C847

DY

DY

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

12

C815

C815

C817

C817

C819

C819

DY

DY

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C807

C807

C808

C808

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

12

C828

C828

C816

C816

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C833

C833

DY

DY

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C818

C818

SC22U6D3V3MX-1-GP

SC22U6D3V3MX-1-GP

12

C809

C809

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

22 uf x24

10 uf x7

2.2uf x2

12

C827

C827

SC2D2U6D3V2MX-GP

SC2D2U6D3V2MX-GP

12

C810

C810

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C820

C820

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

12

C840

C840

C829

C829

DY

DY

DY

DY

SC2D2U6D3V2MX-GP

SC2D2U6D3V2MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

33A

A26

A29

A31

A34

A35

A38

A39

A42

C26

C27

C32

C34

C37

C39

C42

D27

D32

D34

D37

D39

D42

E26

E28

E32

E34

E37

E38

F25

F26

F28

F32

F34

F37

F38

F42

G42

H25

H26

H28

H29

H32

H34

H35

H37

H38

H40

J25

J26

J28

J29

J32

J34

J35

J37

J38

J40

J42

K26

K27

K29

K32

K34

K35

K37

K39

K42

L25

L28

L33

L36

L40

N26

N30

N34

N38

IVY-BRIDGE-GP-N F

IVY-BRIDGE-GP-N F

71.00IVY.A0U

71.00IVY.A0U

6 OF 9

6 OF 9

VCCIO1

VCCIO3

VCCIO4

VCCIO5

VCCIO6

VCCIO7

VCCIO8

VCCIO9

VCCIO10

VCCIO11

VCCIO12

VCCIO13

VCCIO14

VCCIO15

VCCIO16

VCCIO17

VCCIO18

VCCIO19

VCCIO20

VCCIO21

VCCIO22

VCCIO23

VCCIO24

VCCIO25

VCCIO26

VCCIO27

VCCIO28

VCCIO29

VCCIO30

VCCIO31

VCCIO32

PEG IO AND DDR IO

PEG IO AND DDR IO

VCCIO33

VCCIO34

VCCIO35

VCCIO36

VCCIO37

VCCIO38

VCCIO39

VCCIO40

VCCIO41

VCCIO42

VCCIO43

VCCIO44

VCCIO45

VCCIO46

VCCIO47

VCCIO48

VCCIO49

VCCIO50

VCCIO51

VCCIO_SEL

VCCPQE1

VCCPQE2

RAILS

RAILS

VIDALERT#

VIDSCLK

VIDSOUT

SVID QUIET

SVID QUIET

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

VSS_SENSE_VCCIO

SENSE LINES

SENSE LINES

AF46

AG48

AG50

AG51

AJ17

AJ21

AJ25

AJ43

AJ47

AK50

AK51

AL14

AL15

AL16

AL20

AL22

AL26

AL45

AL48

AM16

AM17

AM21

AM43

AM47

AN20

AN42

AN45

AN48

AA14

AA15

AB17

AB20

AC13

AD16

AD18

AD21

AE14

AE15

AF16

AF18

AF20

AG15

AG16

AG17

AG20

AG21

AJ14

AJ15

W16

W17

BC22

AM25

AN22

A44

B43

C44

F43

G43

AN16

AN17

H_CPU_SVIDALR T#

H_CPU_SVIDC LK

H_CPU_SVIDD AT

VCCSENSE

VSSSENSE

12

DY

H_SNB_IVB#_PW RCTRL

+V1.05S_VCCPQE _R

C862

SC1U6D3V2KX-GPDYC862

SC1U6D3V2KX-GP

12

12

DY

DY

12

12

C871

C871

DY

DY

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

Added, cause the

1.05V far away CPU

C885

SC1U6D3V2KX-GPDYC885

SC1U6D3V2KX-GP

C883

SC1U6D3V2KX-GPDYC883

SC1U6D3V2KX-GP

12

12

DY

DY

1

1 2

R812 0R0402-PAD-2-GPR812 0R0402-PAD-2-GP

12

C826

C826

SC1U6D3V2KX- GP

SC1U6D3V2KX- GP

+1.05V_RUN_VT T

12

R807

R807

10R2F-L-GP

10R2F-L-GP

12

R806

R806

10R2F-L-GP

10R2F-L-GP

C869

SC1U6D3V2KX-GPDYC869

SC1U6D3V2KX-GP

C866

SC1U6D3V2KX-GPDYC866

C864

SC1U6D3V2KX-GPDYC864

SC1U6D3V2KX-GP

C872

C872

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C884

SC1U6D3V2KX-GPDYC884

SC1U6D3V2KX-GP

R803

R803

43R2J-GP

43R2J-GP

1 2

SC1U6D3V2KX-GP

C865

SC1U6D3V2KX-GPDYC865

SC1U6D3V2KX-GP

12

12

DY

DY

C874

SC1U6D3V2KX-GP

C874

SC1U6D3V2KX-GP

12

12

C873

C873

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C886

SC1U6D3V2KX-GP

C886

SC1U6D3V2KX-GP

C888

SC1U6D3V2KX-GP

C888

SC1U6D3V2KX-GP

12

12

C895

SC10U6D3V3MX-GPDYC895

SC10U6D3V3MX-GP

12

DY

TP801 TP AD14-OP-GPTP801 TPAD14-OP- GP

75R2F-2-GP

75R2F-2-GP

VCCIO_SENSE (45)

VSSIO_SENSE ( 45)

Layout Note:

1. PH/PL resisors place close CPU

2. SENSE signal recommend differential routing

R805

R805

12

DY

12

12

12

DY

12

DY

C876

SC1U6D3V2KX-GP

C876

SC1U6D3V2KX-GP

C879

SC10U6D3V3MX-GP

C879

SC10U6D3V3MX-GP

C887

SC1U6D3V2KX-GPDYC887

SC1U6D3V2KX-GP

C897

SC10U6D3V3MX-GPDYC897

SC10U6D3V3MX-GP

+1.05V_RUN_VT T+1.05V_R UN_VTT

12

12

VCC_CORE

12

12

C867

SC1U6D3V2KX-GPDYC867

SC1U6D3V2KX-GP

12

DY

C875

SC1U6D3V2KX-GP

C875

SC1U6D3V2KX-GP

12

C880

SC10U6D3V3MX-GP

C880

SC10U6D3V3MX-GP

12

C889

SC1U6D3V2KX-GPDYC889

SC1U6D3V2KX-GP

12

DY

C893

SC10U6D3V3MX-GP

C893

SC10U6D3V3MX-GP

12

R804

R804

130R2F-1-GP

130R2F-1-GP

R801

R801

100R2F-L1-GP- U

100R2F-L1-GP- U

R802

R802

100R2F-L1-GP- U

100R2F-L1-GP- U

DY

DY

DY

8.5A

C868

SC1U6D3V2KX-GPDYC868

SC1U6D3V2KX-GP

12

DY

C877

SC1U6D3V2KX-GP

C877

SC1U6D3V2KX-GP

12

C881

SC10U6D3V3MX-GPDYC881

SC10U6D3V3MX-GP

12

C890

SC1U6D3V2KX-GP

C890

SC1U6D3V2KX-GP

12

DY

C894

SC10U6D3V3MX-GPDYC894

SC10U6D3V3MX-GP

12

DY

+1.05V_RUN_VT T

C870

SC1U6D3V2KX-GPDYC870

SC1U6D3V2KX-GP

12

C878

SC1U6D3V2KX-GP

C878

SC1U6D3V2KX-GP

12

C882

SC10U6D3V3MX-GP

C882

SC10U6D3V3MX-GP

12

C891

SC1U6D3V2KX-GPDYC891

SC1U6D3V2KX-GP

12

C896

SC10U6D3V3MX-GPDYC896

SC10U6D3V3MX-GP

12

Layout Note:

R803, R804, R805 need close to CPU

Alert# signal must be routed between the Clock and Data

lines to reduce the cross talk between them

VR_SVID_ALERT# (42)

H_CPU_SVIDC LK (42)

H_CPU_SVIDD AT (42)

Layout Note:

1. PH/PL resisors place close CPU

2. SENSE signal recommend differential routing

+1.05V_RUN_VT T

C892

SC1U6D3V2KX-GPDYC892

SC1U6D3V2KX-GP

12

DY

VCCSENSE (42)

VSSSENSE (42)

22 uf x3

10 ufx9

1 uf x23

Voltage Rail

VCC_CORE(ULV)

VAXG(ULV)

VCCIO

VDDQ 1.5

VCCSA

VCCPLL

VCCIO Output Decoupling Recommendation:

330u x 2(Remove)

10u x 10(0603)

1u x 26(0402)

VCCPQ Output Decoupling Recommendation:

1u x 1(0402)

Need place Pull Hi

at IMVP page

Voltage(V)

0.3~1.52

0~1.52

1.05

0.9

1.8

Iccmax(A)

33

33

8.5

5

4

1.2

A A

<Core Desig n>

<Core Desig n>

<Core Desig n>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin T ai Wu Rd ., Hsichih,

21F, 88, Sec.1, Hsin T ai Wu Rd ., Hsichih,

21F, 88, Sec.1, Hsin T ai Wu Rd ., Hsichih,

Taipei Hsie n 221, Taiwan, R.O. C.

Taipei Hsie n 221, Taiwan, R.O. C.

Title

Title

Title

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

A2

A2

A2

Tuesday, Febr uary 26, 2013

Tuesday, Febr uary 26, 2013

Tuesday, Febr uary 26, 2013

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Taipei Hsie n 221, Taiwan, R.O. C.

CPU (VCC_CORE)

CPU (VCC_CORE)

CPU (VCC_CORE)

Austin 13

Austin 13

Austin 13

1

8 106

8 106

8 106

A00

A00

A00

Vinafix.com

5

4

3

2

1

SSID = CPU

Layout Note:

POWER

CPU1G

VCC_GFXCO RE

D D

C C

B B

VCCAXG Output Decoupling Recommendation:

3.9m ohm loadline design:(for GT2)

470u x 2(remove)

22u x 6(0805)

10u x 6(0603)

1u x 11(0402)

4.6m ohm loadline design:(for GT1)

330u x 2(remove)

22u x 5(0805)

10u x 6(0603)

1u x 6(0402)

VCCPLL Output Decoupling Recommendation:

330u x 1(Remove)

1u x 2(0402)

VCCSA Output Decoupling Recommendation:

330u x 1(Remove)

10u x 5(0603)

1u x 5(0402)

22 uf x17

1 uf x7

12

12

C901

C901

12

C955

C955

12

C906

C906

12

Layout Note:

1. PH/PL resisors place close CPU

2. SENSE signal recommend differential routing

12

C902

C902

C903

C903

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

12

C923

C923

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

12

C907

C907

C908

C908

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

12

C912

C912

C914

C914

C913

C913

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

+VCC_SA

12

12

C905

C905

C904

C904

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

12

C921

C921

C920

C920

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

VCC_AXG_SEN SE(42)

VSS_AXG_SENSE(42)

C922

C922

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

12

C909

C909

C910

C910

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

12

C915

C915

C916

C916

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

6A

C930

SC10U6D3V3MX-GPDYC930

SC10U6D3V3MX-GP

C929

SC10U6D3V3MX-GPDYC929

SC10U6D3V3MX-GP

12

DY

DY

C935

SC1U6D3V2KX-GP

C935

SC1U6D3V2KX-GP

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C917

C917

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

+1.8V_RUN

12

C934

C934

12

33A

12

12

C919

C919

C911

C911

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C918

C918

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

VCC_GFXCO RE

12

R903

R903

100R2F-L1-GP- U

100R2F-L1-GP- U

VCC_AXG_SEN SE

VSS_AXG_SENSE

12

R904

R904

100R2F-L1-GP- U

100R2F-L1-GP- U

1.2A

C925

SC1U6D3V2KX-GP

C925

SC1U6D3V2KX-GP

C924

SC1U6D3V2KX-GPDYC924

SC1U6D3V2KX-GP

12

12

DY

C927

SC10U6D3V3MX-GPDYC927

SC10U6D3V3MX-GP

C926

SC10U6D3V3MX-GPDYC926

C928

SC10U6D3V3MX-GPDYC928

SC10U6D3V3MX-GP

DY

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

DY

SC10U6D3V3MX-GP

12

12

C933

12

12

DY

DY

SC1U6D3V2KX-GPDYC933

SC1U6D3V2KX-GP

C932

SC1U6D3V2KX-GPDYC932

SC1U6D3V2KX-GP

12

12

DY

DY

CPU1G

AA46

VAXG1

AB47

VAXG2

AB50

VAXG3

AB51

VAXG4

AB52

VAXG5

AB53

VAXG6

AB55

VAXG7

AB56

VAXG8

AB58

VAXG9

AB59

VAXG10

AC61

VAXG11

AD47

VAXG12

AD48

VAXG13

AD50

VAXG14

AD51

VAXG15

AD52

VAXG16

AD53

VAXG17

AD55

VAXG18

AD56

VAXG19

AD58

VAXG20

AD59

VAXG21

AE46

VAXG22

N45

VAXG23

P47

VAXG24

P48

VAXG25

P50

VAXG26

P51

VAXG27

P52

VAXG28

P53

VAXG29

P55

VAXG30

P56

VAXG31

P61

VAXG32

T48

VAXG33

T58

VAXG34

T59

VAXG35

T61

VAXG36

U46

VAXG37

V47

VAXG38

V48

VAXG39

V50

VAXG40

V51

VAXG41

V52

VAXG42

V53

VAXG43

V55

VAXG44

V56

VAXG45

V58

VAXG46

V59

VAXG47

W50

VAXG48

W51

VAXG49

W52

VAXG50

W53

VAXG51

W55

VAXG52

W56

VAXG53

W61

VAXG54

Y48

VAXG55

Y61

VAXG56

F45

VAXG_SENSE

G45

VSSAXG_SENSE

BB3

VCCPLL1

BC1

VCCPLL2

BC4

VCCPLL3

L17

VCCSA1

L21

VCCSA2

N16

VCCSA3

N20

VCCSA4

N22

VCCSA5

P17

VCCSA6

P20

VCCSA7

R16

VCCSA8

R18

VCCSA9

R21

VCCSA10

U15

VCCSA11

V16

VCCSA12

V17

VCCSA13

V18

VCCSA14

V21

VCCSA15

W20

VCCSA16

C931

SC1U6D3V2KX-GPDYC931

SC1U6D3V2KX-GP

IVY-BRIDGE-GP-N F

IVY-BRIDGE-GP-N F

71.00IVY.A0U

71.00IVY.A0U

POWER

GRAPHICS

GRAPHICS

SENSE

LINES

SENSE

LINES

1.8V RAIL

1.8V RAIL

SA RAIL

SA RAIL

VCCSA VID

VCCSA VID

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

VREF

VREF

DDR3 - 1.5V RAILS

DDR3 - 1.5V RAILS

QUIET RAILS

QUIET RAILS

VDDQ_SENSE

VSS_SENSE_VDDQ

VCCSA_SENSE

SENSE LINES

SENSE LINES

VCCSA_VID0

VCCSA_VID1

lines

lines

SM_VREF

+V_SM_VREF_CNT should have 10 mil trace width

7 OF 9

7 OF 9

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VDDQ17

VDDQ18

VDDQ19

VDDQ20

VDDQ21

VDDQ22

VDDQ23

VDDQ24

VDDQ25

VDDQ26

VCCDQ1

VCCDQ2

+V_SM_VREF_C NT

AY43

+DIMM0_1_VREF_CP U

BE7

+DIMM0_1_CA_CPU

BG7

AJ28

AJ33

AJ36

AJ40

AL30

AL34

AL38

AL42

AM33

AM36

AM40

AN30

AN34

AN38

AR26

AR28

AR30

AR32

AR34

AR36

AR40

AV41

AW26

BA40

BB28

BG33

AM28

AN26

TP_VDDQ_SEN SE

BC43

TP_VDDQ_VSS

BA43

U10

VCCSA_SEL0

D48

VCCSA_SEL1

D49

C944

C944

12

1KR2J-1-GP

1KR2J-1-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

12

DY

C954

SC1U6D3V2KX-GP

C954

SC1U6D3V2KX-GP

12

1

1

12

R911

R911

+DIMM0_1_VREF_CP U

+DIMM0_1_CA_CPU

5A

C945

SC1U6D3V2KX-GPDYC945

SC1U6D3V2KX-GP

C946

SC1U6D3V2KX-GPDYC946

SC1U6D3V2KX-GP

12

DY

C936

SC10U6D3V3MX-GPDYC936

SC10U6D3V3MX-GP

12

DY

VDDQ Output Decoupling Recommendation:

330u x 1(Remove)

10u x 8(0603)

1u x 10(0402)

VCCDQ Output Decoupling Recommendation:

1u x 1(0402)

1 2

R909 0R0402-PAD-2-GPR909 0R0402-PAD-2-GP

TP901 TP AD14-OP-GPTP901 TPAD14-OP- GP

TP902 TP AD14-OP-GPTP902 TPAD14-OP- GP

VCCSA_SENS E (48)

VCCSA_SEL0 ( 48)

VCCSA_SEL1 ( 48)

12

R910

R910

1KR2J-1-GP

1KR2J-1-GP

C947

SC1U6D3V2KX-GPDYC947

SC1U6D3V2KX-GP

12

DY

C937

SC10U6D3V3MX-GP

C937

SC10U6D3V3MX-GP

12

10 uf x8

1 uf x10

C948

SC1U6D3V2KX-GPDYC948

SC1U6D3V2KX-GP

12

12

DY

DY

C938

SC10U6D3V3MX-GPDYC938

SC10U6D3V3MX-GP

12

12

DY

DY

+1.35V_CPU_VD DQ+V1.35S_VCCD_ Q

C949

SC1U6D3V2KX-GPDYC949

SC1U6D3V2KX-GP

12

DY

C939

SC10U6D3V3MX-GPDYC939

SC10U6D3V3MX-GP

12

Voltage Rail

VCC_CORE(ULV)

VAXG(ULV)

VCCIO

VDDQ 1.5

VCCSA

VCCPLL

C951

SC1U6D3V2KX-GPDYC951

SC1U6D3V2KX-GP

C950

SC1U6D3V2KX-GPDYC950

SC1U6D3V2KX-GP

12

12

DY

C941

SC10U6D3V3MX-GP

C941

SC10U6D3V3MX-GP

C940

SC10U6D3V3MX-GP

C940

SC10U6D3V3MX-GP

12

12

DY

VCCSA Power Select

Voltage(V)

0.9

0.85

0.775

0.75

Voltage(V)

0.3~1.52

0~1.52

C952

SC1U6D3V2KX-GP

C952

SC1U6D3V2KX-GP

12

DY

C942

SC10U6D3V3MX-GPDYC942

SC10U6D3V3MX-GP

VID[0] VID[1]

1.05

0.9

1.8

+1.35V_CPU_VD DQ

C953

SC1U6D3V2KX-GPDYC953

SC1U6D3V2KX-GP

DY

3

0

0 1

Iccmax(A)

33

33

8.5

5

6

1.2

+1.35V_MEM+1.35V_CPU_VD DQ

C957

C957

1 2

SCD1U16V2KX- 3GP

SCD1U16V2KX- 3GP

C958

PTC901

ST330U2D5VDM-24-GP-UDYPTC901

ST330U2D5VDM-24-GP-U

12

Layout Note:

For S3 reduction circuit's 1D5V return pass.

C958

1 2

SCD1U16V2KX- 3GP

SCD1U16V2KX- 3GP

C959

C959

1 2

SCD1U16V2KX- 3GP

SCD1U16V2KX- 3GP

C960

C960

1 2

SCD1U16V2KX- 3GP

SCD1U16V2KX- 3GP

0

01

11

A A

<Core Desig n>

<Core Desig n>

<Core Desig n>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin T ai Wu Rd ., Hsichih,

21F, 88, Sec.1, Hsin T ai Wu Rd ., Hsichih,

21F, 88, Sec.1, Hsin T ai Wu Rd ., Hsichih,

Taipei Hsie n 221, Taiwan, R.O. C.

Taipei Hsie n 221, Taiwan, R.O. C.

Title

Title

Title

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

A2

A2

A2

Tuesday, Febr uary 26, 2013

Tuesday, Febr uary 26, 2013

Tuesday, Febr uary 26, 2013

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Taipei Hsie n 221, Taiwan, R.O. C.

CPU (VCC_GFXCORE)

CPU (VCC_GFXCORE)

CPU (VCC_GFXCORE)

Austin 13

Austin 13

Austin 13

1

9 106

9 106

9 106

A00

A00

A00

Vinafix.com

5

SSID = CPU

CPU1H

CPU1H

4

8 OF 9

8 OF 9

3

CPU1I

CPU1I

2

9 OF 9

9 OF 9

1

A13

VSS1

A17

VSS2

A21

VSS3

A25

VSS4

D D

C C

B B

A A

A28

A33

A37

A40

A45

A49

A53

AA1

AA13

AA50

AA51

AA52

AA53

AA55

AA56

AA8

AB16

AB18

AB21

AB48

AB61

AC10

AC14

AC46

AC6

AD17

AD20

AD4

AD61

AE13

AE8

AF1

AF17

AF21

AF47

AF48

AF50

AF51

AF52

AF53

AF55

AF56

AF58

AF59

AG10

AG14

AG18

AG47

AG52

AG61

AG7

AH4

AH58

AJ13

AJ16

AJ20

AJ22

AJ26

AJ30

AJ34

AJ38

AJ42

AJ45

AJ48

AJ7

AK1

AK52

AL10

AL13

AL17

AL21

AL25

AL28

AL33

AL36

AL40

AL43

AL47

AL61

AM13

AM20

AM22

AM26

AM30

AM34

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

A9

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS

VSS

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

AM38

AM4

AM42

AM45

AM48

AM58

AN1

AN21

AN25

AN28

AN33

AN36

AN40

AN43

AN47

AN50

AN54

AP10

AP51

AP55

AP7

AR13

AR17

AR21

AR41

AR48

AR61

AR7

AT14

AT19

AT36

AT4

AT45

AT52

AT58

AU1

AU11

AU28

AU32

AU51

AU7

AV17

AV21

AV22

AV34

AV40

AV48

AV55

AW13

AW43

AW61

AW7

AY14

AY19

AY30

AY36

AY4

AY41

AY45

AY49

AY55

AY58

AY9

BA1

BA11

BA17

BA21

BA26

BA32

BA48

BA51

BB53

BC13

BC5

BC57

BD12

BD16

BD19

BD23

BD27

BD32

BD36

BD40

BD44

BD48

BD52

BD56

BD8

BE5

BG13

BG17

BG21

BG24

BG28

BG37

BG41

BG45

BG49

BG53

BG9

C29

C35

C40

D10

D14

D18

D22

D26

D29

D35

D4

D40

D43

D46

D50

D54

D58

D6

E25

E29

E3

E35

E40

F13

F15

F19

F29

F35

F40

F55

G51

G6

G61

H10

H14

H17

H21

H4

H53

H58

J1

J49

J55

K11

K21

K51

K8

L16

L20

L22

L26

L30

L34

L38

L43

L48

L61

M11

M15

IVY-BRIDGE-GP-NF

IVY-BRIDGE-GP-NF

71.00IVY.A0U

71.00IVY.A0U

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS227

VSS228

VSS229

VSS230

VSS231

VSS232

VSS233

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

VSS246

VSS247

VSS248

VSS249

VSS

VSS

NCTF TEST PINA5,A57,BC61,BG5

NCTF TEST PINA5,A57,BC61,BG5

NCTF

NCTF

VSS_NCTF_1#A5

VSS_NCTF_2#A57

VSS_NCTF_3#BC61

VSS_NCTF_8#BG5

VSS_NCTF_9#BG57

VSS_NCTF_10#C3

VSS_NCTF_13#E1

VSS_NCTF_14#E61

BG57,C3,E1,E61

BG57,C3,E1,E61

VSS_NCTF_4

VSS_NCTF_5

VSS_NCTF_6

VSS_NCTF_7

VSS_NCTF_11

VSS_NCTF_12

VSS250

VSS251

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

VSS258

VSS259

VSS260

VSS261

VSS262

VSS263

VSS264

VSS265

VSS266

VSS267

VSS268

VSS269

VSS270

VSS271

VSS272

VSS273

VSS274

VSS275

VSS276

VSS277

VSS278

VSS279

VSS280

VSS281

VSS282

VSS283

VSS284

VSS285

VSS286

VSS287

VSS288

VSS289

VSS290

VSS291

VSS292

VSS293

VSS294

VSS295

VSS296

VSS297

VSS298

VSS299

VSS300

M4

M58

M6

N1

N17

N21

N25

N28

N33

N36

N40

N43

N47

N48

N51

N52

N56

N61

P14

P16

P18

P21

P58

P59

P9

R17

R20

R4

R46

T1

T47

T50

T51

T52

T53

T55

T56

U13

U8

V20

V61

W13

W15

W18

W21

W46

W8

Y4

Y47

Y58

Y59

A5

A57

BC61

BG5

BG57

C3

E1

E61

BD3

BD59

BE4

BE58

C58

D59

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

IVY-BRIDGE-GP-NF

IVY-BRIDGE-GP-NF

71.00IVY.A0U

71.00IVY.A0U

5

4

3

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Tuesday, February 26, 2013

Tuesday, February 26, 2013

Tuesday, February 26, 2013

Date: Sheet of

Date: Sheet of

Date: Sheet of

CPU (VSS)

CPU (VSS)

CPU (VSS)

Austin 13

Austin 13

Austin 13

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

10 106

10 106

10 106

1

A00

A00

A00

Vinafix.com

5

D D

C C

4

3

2

1

(Blanking)

B B

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Tuesday, February 26, 2013

Tuesday, February 26, 2013

Tuesday, February 26, 2013

Date: Sheet of

Date: Sheet of

Date: Sheet of

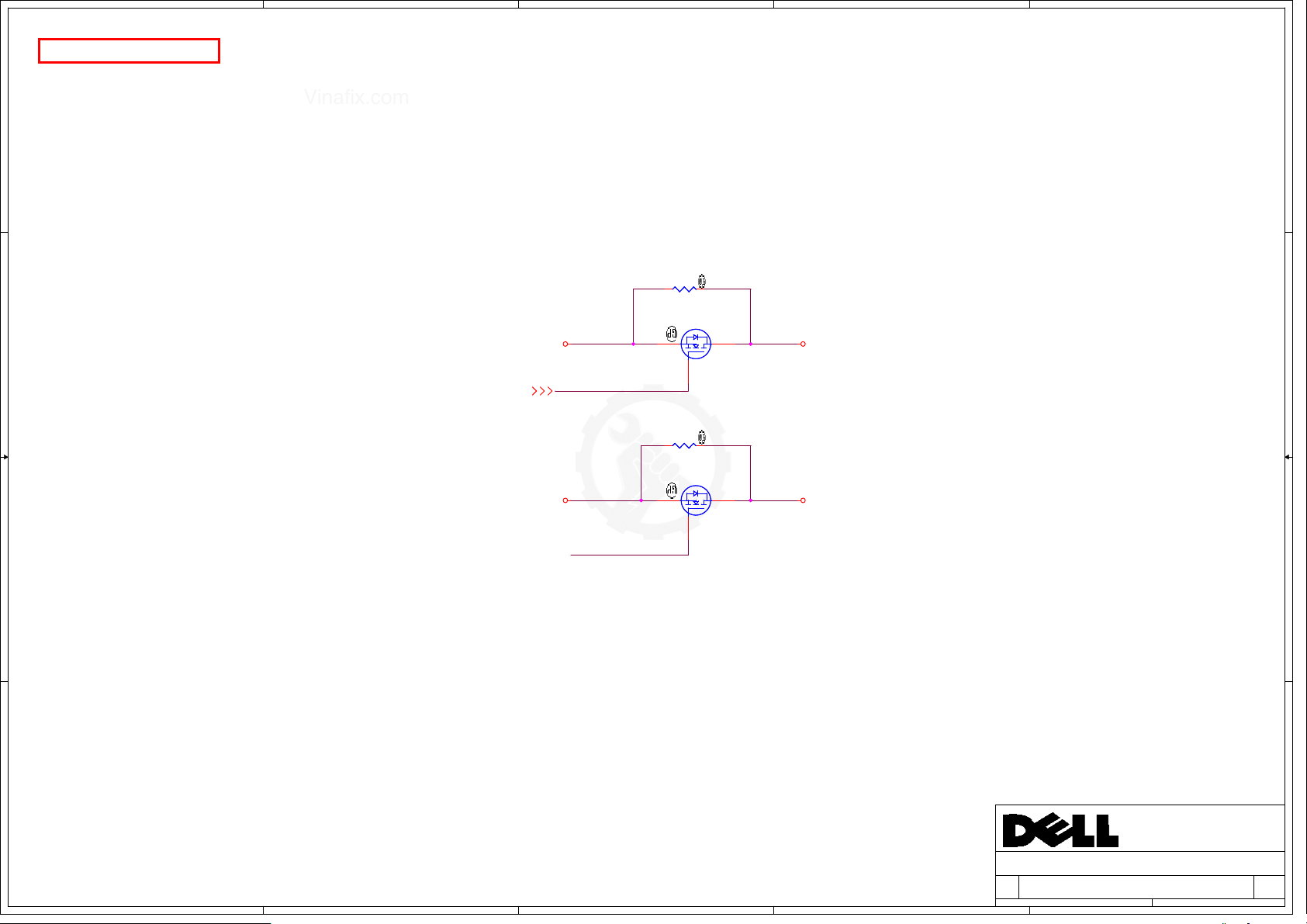

XDP

XDP

XDP

Austin 13

Austin 13

Austin 13

Taipei Hsien 221, Taiwan, R.O.C.

11 106

11 106

11 106

1

A00

A00

A00

Vinafix.com

5

4

3

2

1

SSID = MEMORY

D D

R1203

R1203

0R2J-2-GP

0R2J-2-GP

1 2

DY

DY

Q1201

Q1201

AP2302GN-GP

AP2302GN-GP

DY

DY

G

Q1202

Q1202

G

DS

84.02302.A31

84.02302.A31

2nd = 84.02302.B31