Dell INSPIRON N5030 Schematics

5

D D

4

3

2

1

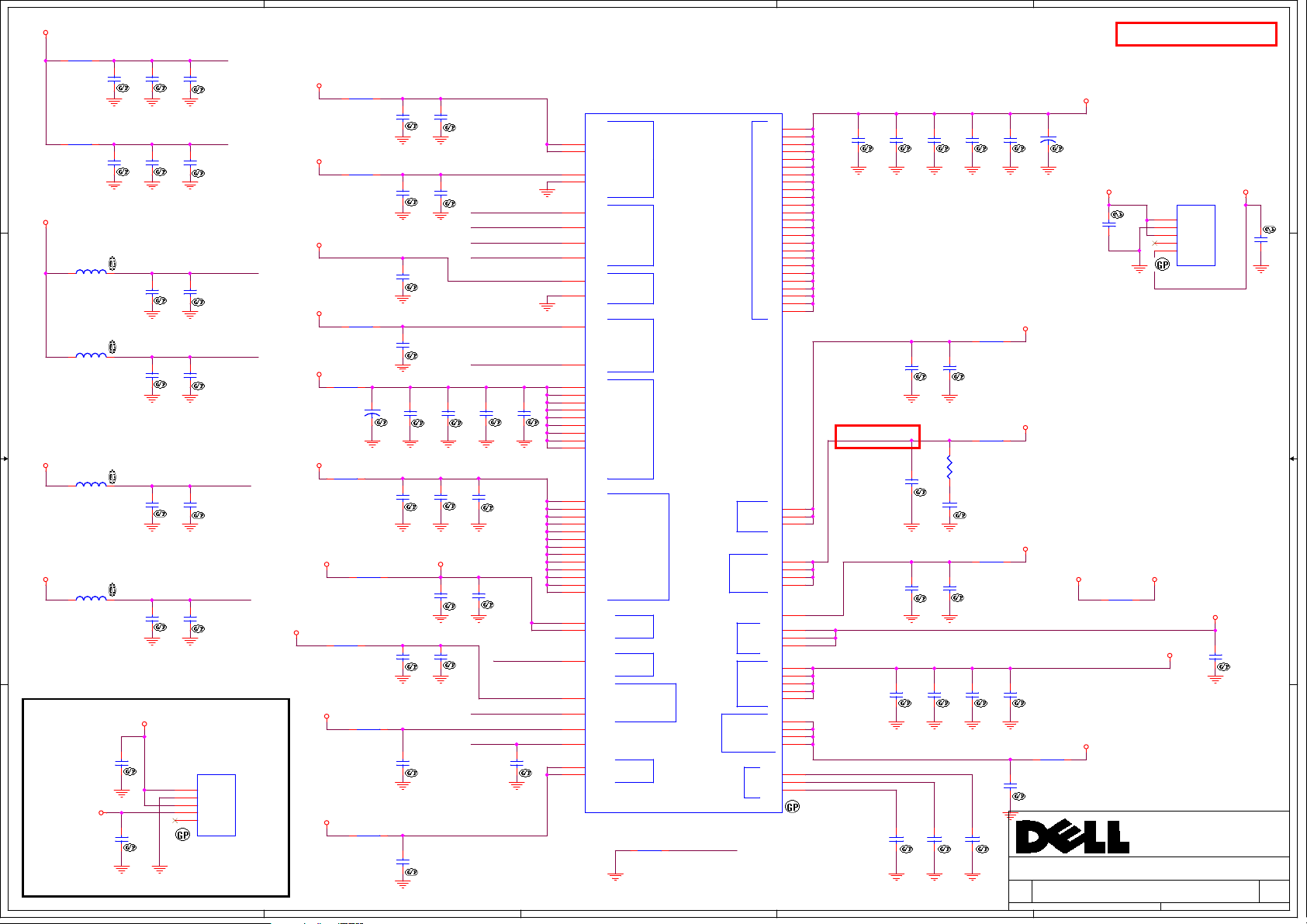

DJ2 Montevina UMA Schematics Document

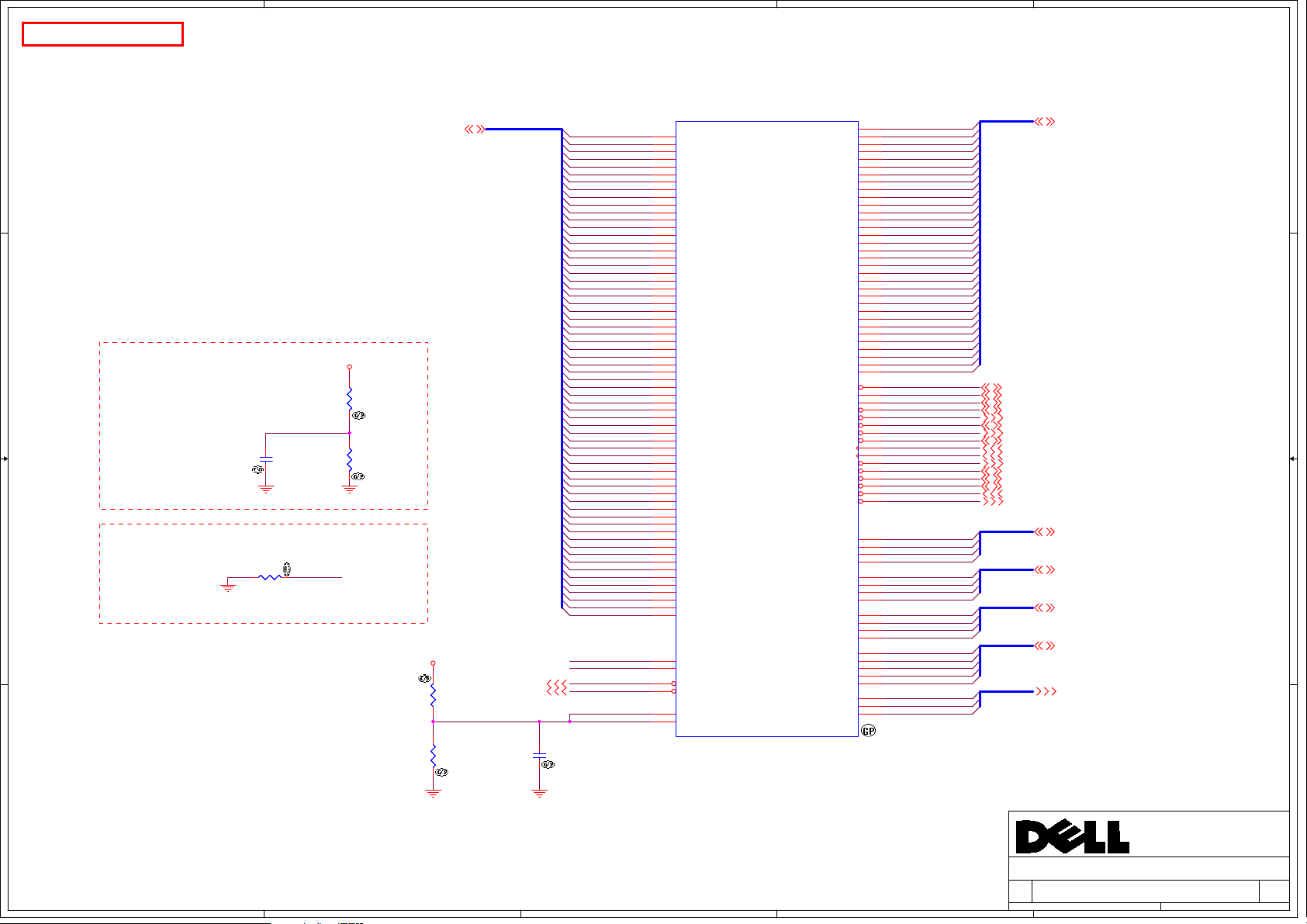

uFCPGA Mobile Penryn

C C

Intel GM45+ICH9M

2010-06-02

REV : X00

B B

DY : Nopop Component

HDMI : Pop for HDMI

GIGA : Pop for GIGA LAN

10/100 : Pop for 10/100 LAN

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1 , Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1 , Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1 , Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

DJ2 Montevina UMA

DJ2 Montevina UMA

DJ2 Montevina UMA

Taipei Hsien 221, Taiwan, R.O.C.

Cover Page

Cover Page

Cover Page

1

1 88Wednesd ay, June 02, 201 0

1 88Wednesd ay, June 02, 201 0

1 88Wednesd ay, June 02, 201 0

X00

X00

X00

5

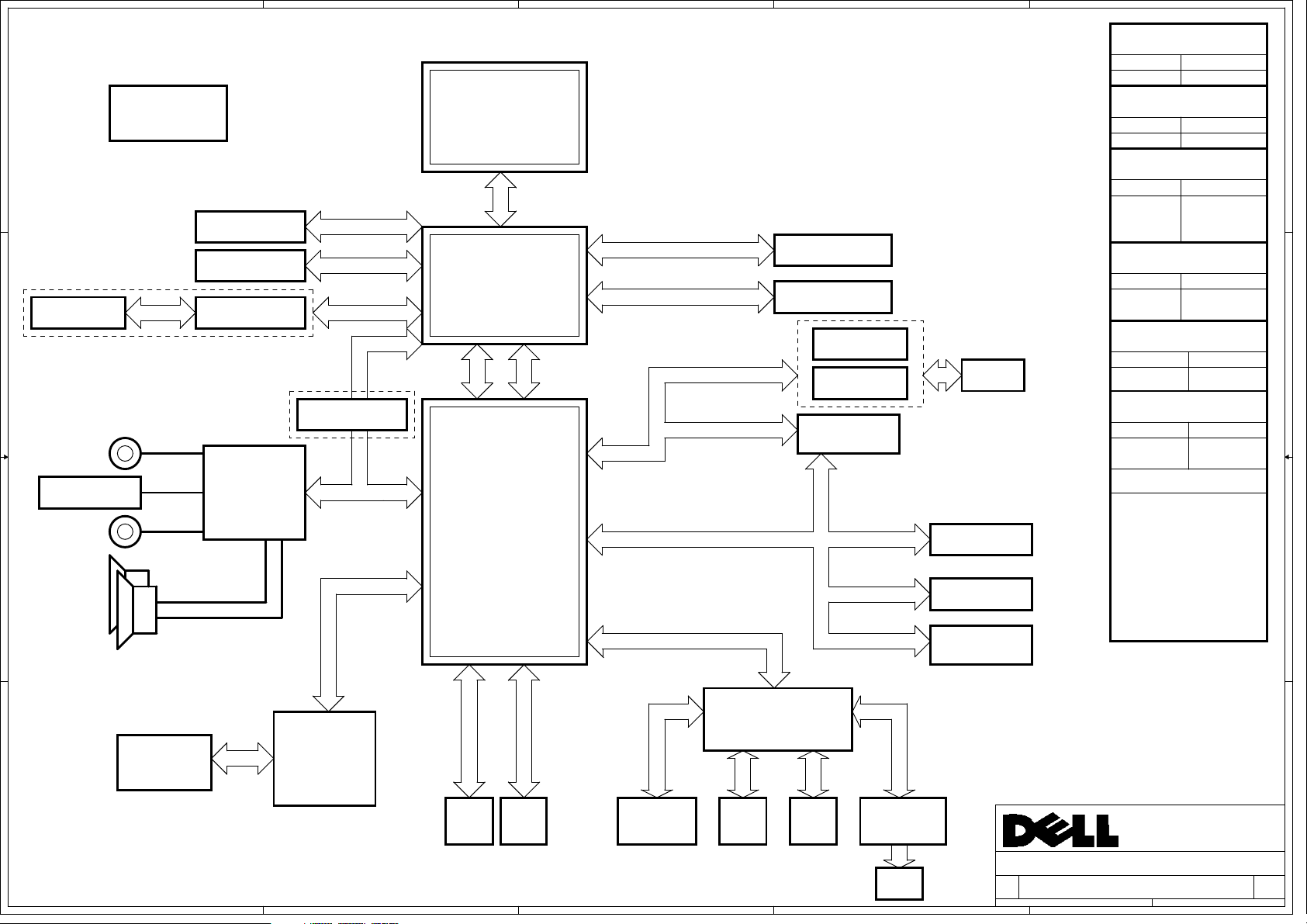

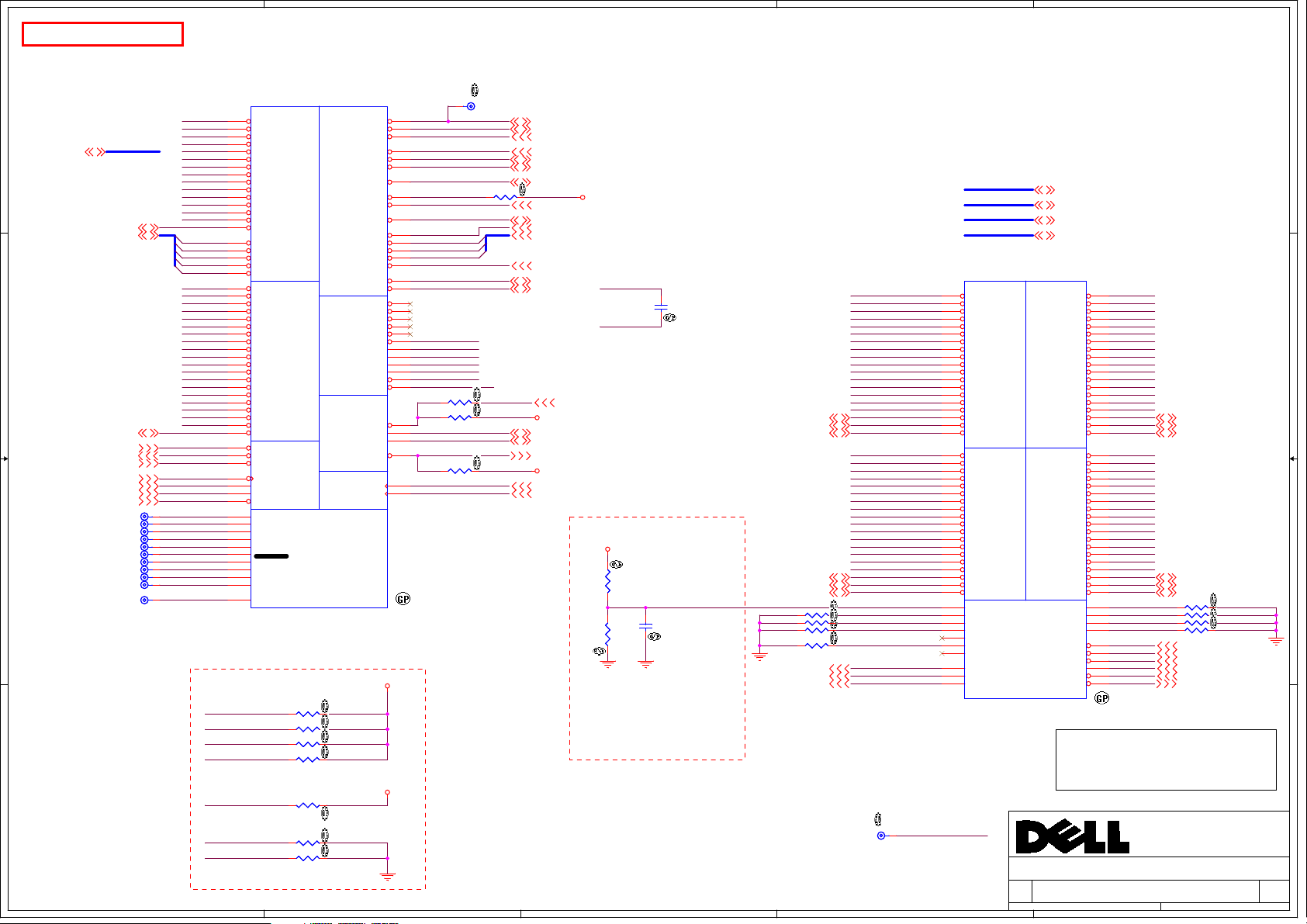

J2 Montevina UMA Block Diagram

D

Clock Generator

LG8SP513VTR

D D

HDMI

(Reserved)

C C

S

57

7

CRT

LCD

Level shift

(Reserved)

55

LVDS(Dual Channel)

54

57

RGB CRT

HDMI

Level shift

(Reserved)

MIC IN

Internal Analog MIC

HP1

B B

60

60

60

60

Azalia

CODEC

Realtek

ALC269Q

30

2CH SPEAKER

(1CH 1W/4ohm)

AZALIA

AZALIA

USB2.0

4

I

ntel Mobile CPU

enryn

P

S

ocket P

Intel

GM45

AGTL + CPU I/F

DDR Memory I/F

External Graphics

10,11,12,13,14,15

DMIx4 C-LINK

57

Intel

ICH9-M

USB 2.0/1.1 ports (12)

PCI Express ports (8)

High Definition Audio

SATA ports (4)

LPC I/F

ACPI 1.1

PCI/PCI BRIDGE

8

,9

FSB

800/1066MHz

20,21,22,23

3

P

PCB P/N : 48.4EM25.0SA

Revision : 10240 -SA

DDRIII 800/1066 Channel A

DDRIII 800/1066 Channel B

PCIE x 1

PCIE x 1

PCIE

USB 2.0

LPC Bus

2

roject code : 91.4EM01.001

DDRIII

800/1066

DDRIII

800/1066

DIMM1

DIMM2

10/100 NIC

Atheros

AR8152

GIGA NIC

Atheros AR8151

1/2 Mini-Card

802.11a/b/g

USB 2.0 x 1

USB 2.0 x 1

USB 2.0 x 1

USB 2.0 x 3

18

19

Option 1 : 10/100

Option 2 : Giga Lan

35

RJ45

61

35

64

CONN

CAMERA

Bluetooth

Left Side:

USB x3

54

73

63

1

C

PU DC/DC

T

I

+

I

+

PS51620

T

PS51218

O

UTPUTS

+

VCC_CORE

O

UTPUTS

+

1.05V_VCCP

NPUTS

PWR_SRC

S

YSTEM DC/DC

NPUTS

PWR_SRC

SYSTEM DC/DC

TPS51125

INPUTS

+PWR_SRC

OUTPUTS

+5V_ALW2

+3.3V_RTC_LDO

+5V_ALW

+3.3V_ALW

+15V_ALW

SYSTEM DC/DC

TPS51116

INPUTS

+PWR_SRC

OUTPUTS

+1.5V_SUS

+0.75V_DDR_VTT

+V_DDR_REF

MAXIM CHARGER

BQ24745

INPUTS

+DC_IN

+PBATT

26

SYSTEM DC/DC

26

INPUTS OUTPUTS

+1.5V_SUS

+5V_ALW

OUTPUTS

+PWR_SRC

Switches

+1.5V_RUN

+5V_RUN

+3.3V_RUN+3.3V_ALW

PCB LAYER

L1: Top

L2: GND

L3: Signal

L4: Signal

L5: VCC

L6: Bottom

47

49

46

50

45

42

SPI

CardReader

ODD

SATA

5959

Flash ROM

2MB

3

62

SD/MMC/MS

71

A A

Realtek

RTS5138

32

SATA

HDD

5

4

NUVOTON

NPCE781BA0DX

Touch

PAD

68

37

ThermalInt.

KB

68 25

EMC2102

Fan

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1 , Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1 , Hsin Tai Wu Rd., Hsichih,

39

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

58

2

Size Document N umber Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

DJ2 Montevina UMA

DJ2 Montevina UMA

DJ2 Montevina UMA

21F, 88, Sec.1 , Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Block Diagram

Block Diagram

Block Diagram

1

X00

X00

2 88Wednesd ay, June 02, 201 0

2 88Wednesd ay, June 02, 201 0

2 88Wednesd ay, June 02, 201 0

X00

KBC

5

D

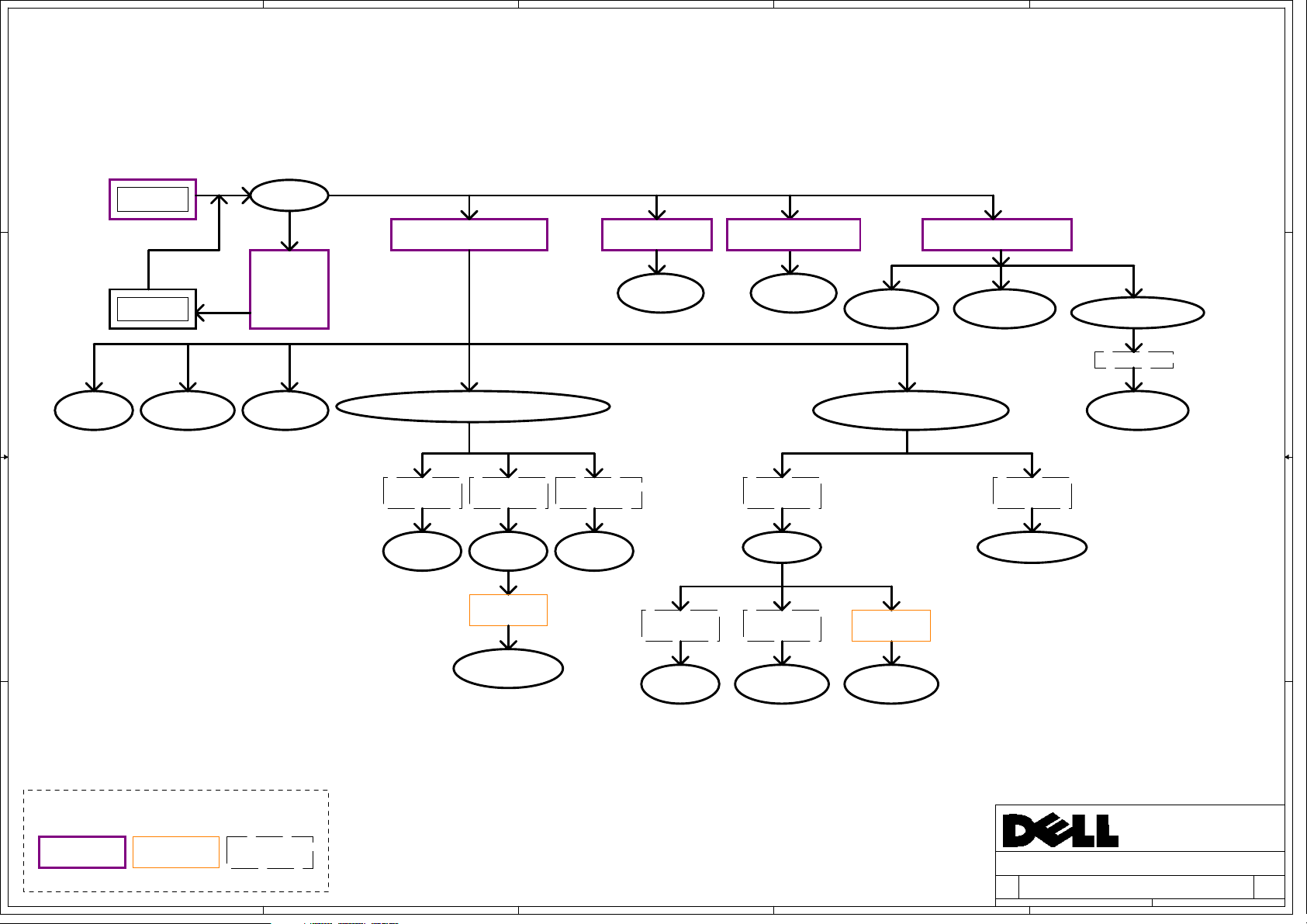

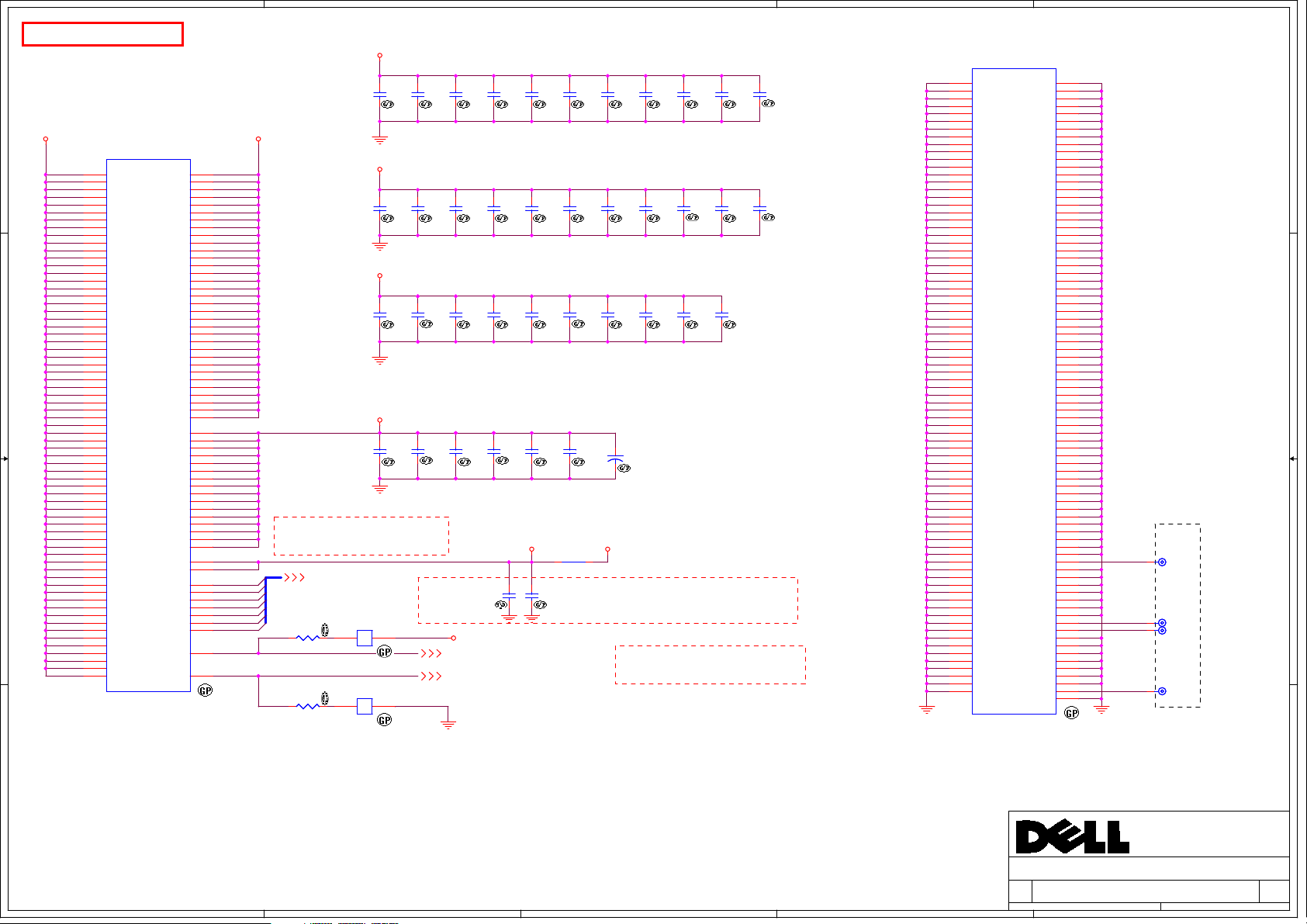

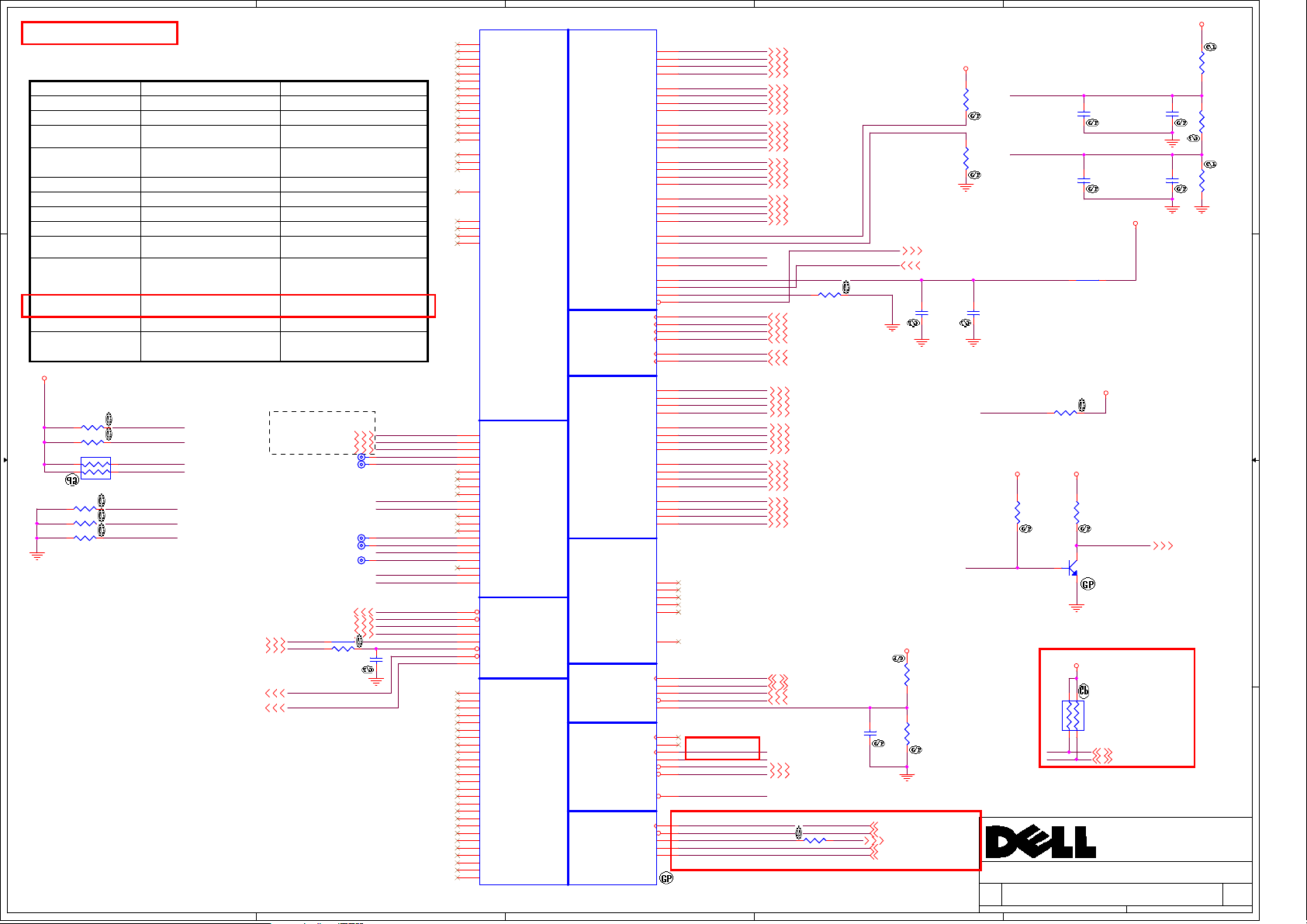

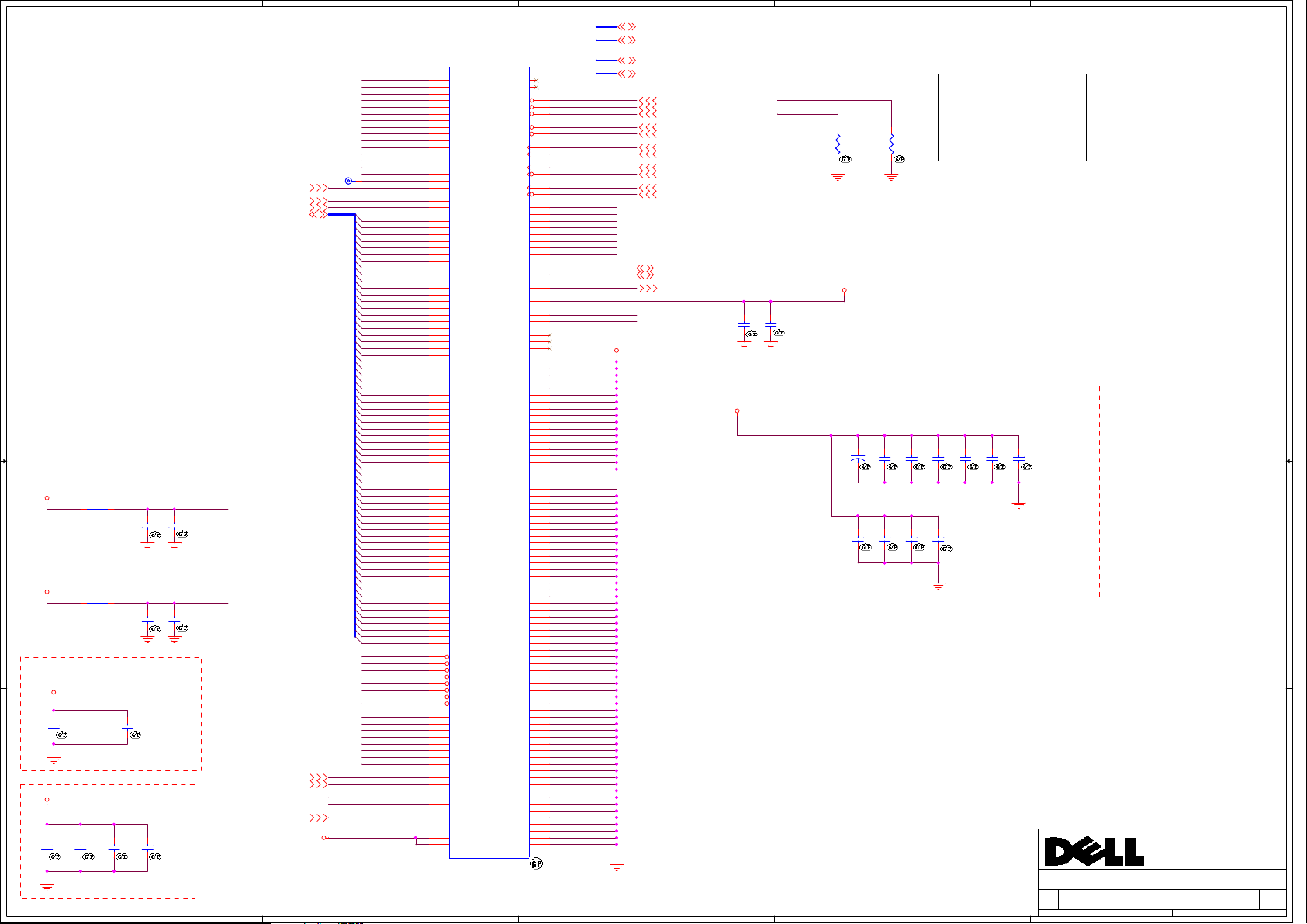

J1 Montevina UMA Power Block Diagram

D D

4

3

2

1

Adapter

+PWR_SRC

TPS51125

TPS51620

TPS51218

TPS51116

Charger

BQ24745

Battery

C C

+15V_ALW

46

B B

+3.3V_RTC_LDO

46

+VCHGR

+5V_ALW2

46

+5V_ALW

G547F2P81U

+5V_USB1

63

46 46

SI4800

+5V_RUN

42

G547F2P81U

+5V_USB2

63

+VCC_CORE

47

+1.05V_VCCP

49

FDS8880

+3.3V_RUN

42

50

+3.3V_ALW

+0.75V_DDR_VTT+V_DDR_REF

50

PA102

+3.3V_LAN 35

+1.5V_SUS

FSD8880

+1.5V_RUN

50

42

G9091

G5285T11U

RTS5159

RT9198

+3.3V_CRT_LDO

15

A A

Power Shape

+LCDVDD

54

Regulator LDO Switch

5

4

3

+3.3V_RUN_CARD

32

+1.8V_NB_S0

15

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1 , Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1 , Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1 , Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Power Block Diagram

Power Block Diagram

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

Power Block Diagram

DJ2 Montevina UMA

DJ2 Montevina UMA

DJ2 Montevina UMA

Taipei Hsien 221, Taiwan, R.O.C.

3 88Friday, May 28, 2010

3 88Friday, May 28, 2010

3 88Friday, May 28, 2010

1

X00

X00

X00

A

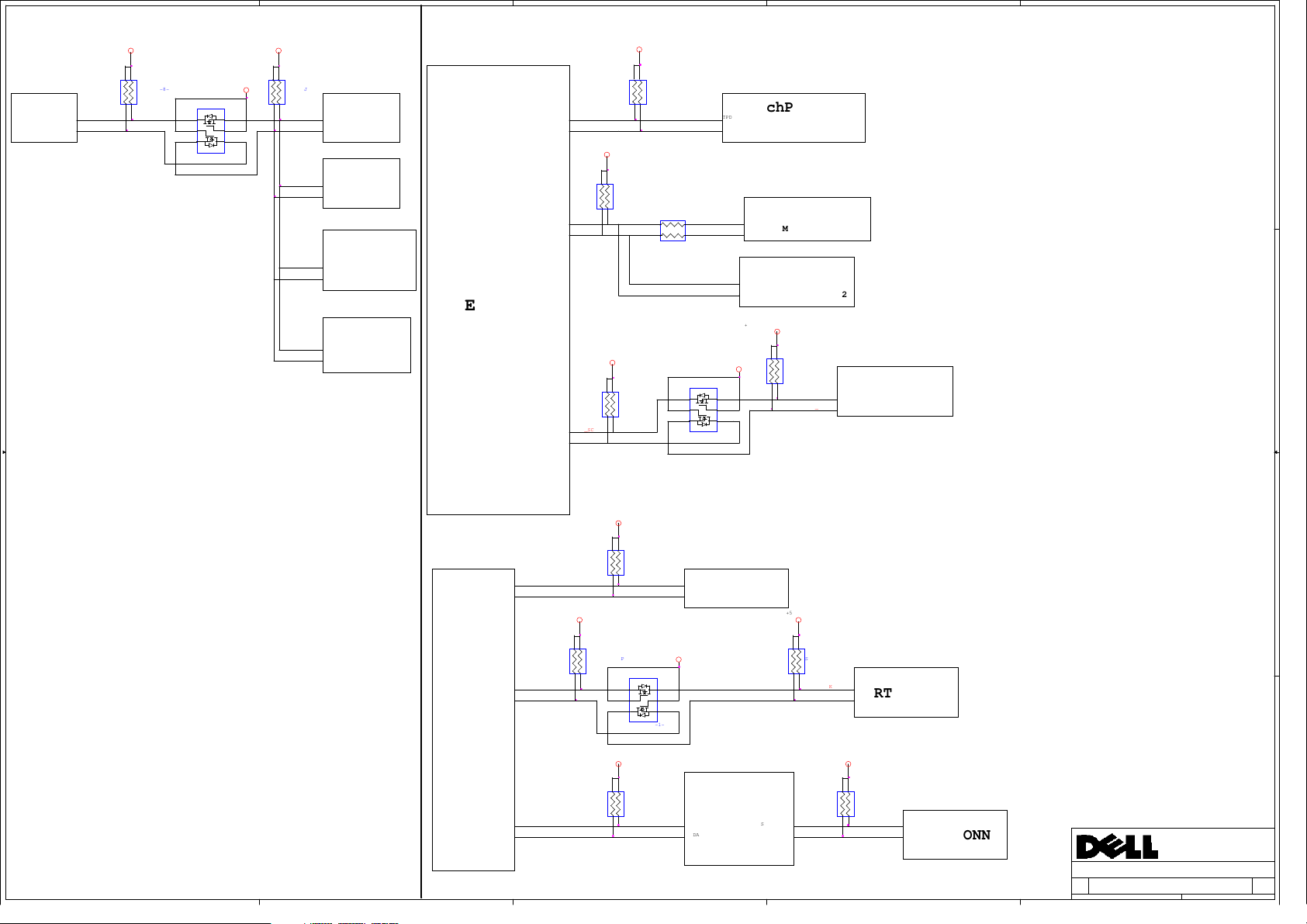

CH SMBus Block Diagram

I

+

3.3V_RUN

‧

3.3V_RUN

+

‧

‧

‧

‧

‧

S

RN4K7J-8-GP

ICH_SMBCLK

ICH_SMBDATA

S

MBus Address:A0

ICH_SMBCLK

ICH_SMBDATA

D

IMM 1

CL

S

SDA

DIMM 2

SCL

SDA

3.3V_ALW

+

‧

S

RN4K7J-8-GP

I

CH

S

S

MBCLK

1 1

SMBDATA

MB_CLK

SMB_DATA

‧

‧

2N7002SPT

SMBus Address:A4

Clock

Generator

ICH_SMBCLK

SCLK

ICH_SMBDATA

SDATA

SMBus address:D2

2 2

ICH_SMBCLK

ICH_SMBDATA

Minicard

WLAN

SMB_CLK

SMB_DATA

B

NPCE781BA0DX

C

BC SMBus Block Diagram

K

+

5V_RUN

‧

S

RN10KJ-5-GP

T

ouchPad Conn.

PSDAT1

P

SCLK1

T

PDATA

TPCLK

+

KBC_PWR

‧

‧

T

PDATA

TPCLK

T

PDATA

TPCLK

‧

SRN4K7J-8-GP

Battery Conn.

CLK_SMB

SMBus address:16

DAT_SMB

BQ24745

SCL

SDA

SMBus address:12

+3.3V_RUN

+3.3V_RUN

‧

‧

‧

‧

KBC

SCL1

SDA1

GPIO61/SCL2

GPIO62/SDA2

BAT_SCL

BAT_SDA

KBC_SCL1

KBC_SDA1

+KBC_PWR

‧

SRN4K7J-8-GP

SRN100J-3-GP

PBAT_SMBCLK1

PBAT_SMBDAT1

2N7002DW-1-GP

SRN4K7J-8-GP

THERM_SCL

THERM_SDA

D

Thermal

SCL

SMBus address:7A

SDA

E

+3.3V_RUN

‧

‧

SRN2K2J-1-GP

+3.3V_RUN

‧

SRN2K2J-1-GP

‧

‧

SRN2K2J-1-GP

‧

2N7002DW-1-GP

C

LCD CONN

+3.3V_RUN

‧

PS8101

HDMI Level Shifter

SCL

SDA

SCL_SINK

SDA_SINK

+5V_CRT_RUN

‧

SRN2K2J-1-GP

‧

‧

DDC_CLK_CON

DDC_DATA_CON

CRT CONN

+5V_RUN

‧

SRN1K5J-GP

DDC_CLK_HDMI

‧

DDC_DATA_HDMI

‧

HDMI CONN

D

<Core Desig n>

<Core Desig n>

<Core Desig n>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., H sichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., H sichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., H sichih,

Taipei Hsie n 221, Taiwan, R.O.C.

Taipei Hsie n 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

A2

A2

A2

DJ2 Montevina UMA

DJ2 Montevina UMA

DJ2 Montevina UMA

Date: Sheet of

Date: Sheet of

Date: Sheet of

Taipei Hsie n 221, Taiwan, R.O.C.

SMBUS Block Diagram

SMBUS Block Diagram

SMBUS Block Diagram

4 88Friday, May 28, 2010

4 88Friday, May 28, 2010

E

4 88Friday, May 28, 2010

X00

X00

X00

3 3

DDC1CLK

DDC1DATA

LDDC_CLK

LDDC_DATA

+3.3V_RUN

‧

VGA

4 4

SDVO_CTRLCLK

SDVO_CTRLDATA

A

B

DDC2CLK

DDC2DATA

GMCH_DDCCLK

GMCH_DDCDATA

MCH_HDMI_CLK

MCH_HDMI_DATA

‧

‧

A

B

C

D

E

T

hermal Block Diagram

1 1

DP1

H_THERMDA

SC470P50V3JN-2GP

2 2

DN1

H_THERMDC

SC470P50V3JN-2GP

THRMDA

THRMDC

CPU

Thermal

EMC2102

DP2

DN2

EMC2102_DP2

SC470P50V3JN-2GP

EMC2102_DN2

PMBS3904-1-GP

A

udio Block Diagram

SPKR_PORT_D_L-/L+

SPKR_PORT_D_R-/R+

HP1_PORT_B_L

HP1_PORT_B_R

Codec

Realtek

ALC269Q

HP0_PORT_A_L

HP0_PORT_A_R

VREFOUT_A_OR_F

2CH SPEAKERS

HP

OUT

MIC

IN

Put between CPU and NB

3 3

DP3

EMC2102_DP3

SC470P50V3JN-2GP

DN3

EMC2102_DN3

4 4

A

B

PMBS3904-1-GP

HW T8 sensor

PORTC_L

PORTC_R

VREFOUT_C

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

C

D

Date: Sheet of

Analog

MIC

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Thermal/Audio Block Diagram

Thermal/Audio Block Diagram

Thermal/Audio Block Diagram

DJ2 Montevina UMA

DJ2 Montevina UMA

DJ2 Montevina UMA

5 88Friday, May 28, 2010

5 88Friday, May 28, 2010

5 88Friday, May 28, 2010

E

X00

X00

X00

A

CH9M Functional Strap Definitions

I

I

U

S

ignal

H

DA_SDOUT

1 1

DA_SYNC PCI Express Port Config

H

GNT2#/

GPIO53

GPIO20 Reserved, Rising Edge

GNT1#/

GPIO51

GNT3#/

GPIO55

2 2

GNT0#

SPI_CS1#/

GPIO58

3 3

SATALED# PCI Express Lane

SPKR

TP3

GPIO33 /

HDA_DOCK_

EN#

(Mobile

Only)

4 4

GPIO49

SPI_MOSI

(Moble

Only)

sage/When Sampled

X

OR Chain Entrance /

PCI Express*

Port Config 1 bit 1

(Port 1-4),

Rising Edge of PWROK

1 bit 0 (Port 1-4),

Rising Edge of PWROK.

PCI Express Port

Config 2 bit 2

(Port 5-6), Rising Edge

of PWROK

of PWROK

ESI Strap (Server Only),

Rising Edge of PWROK.

Top-Block Swap

override. Rising Edge

of PWROK.

Boot BIOS Destination

Selection 1,

Rising Edge of PWROK.

Boot BIOS Destination

Selection 0,

Rising Edge of CLPWROK.

Reversal (Lanes 1-4).

Rising Edge of PWROK.

No Reboot,

Rising Edge of PWROK.

XOR Chain Entrance.

Rising Edge of PWROK.

Flash Descriptor

Security Override Strap.

Rising Edge of PWROK.

DMI Termination

Voltage. Rising Edge

of CLPWROK.

Integrated TPM

Enable. Rising Edge

of CLPWROK.

A

A

llows entrance to XOR Chain t esting when TP3

pulled low at rising edge of PWROK. When TP3

not pulled low at rising edge of PWROK, sets

bit 1 of RPC.PC (Chipset Conf ig Registers: Offset

224h).This signal has a weak internal pull-down.

This signal has a weak intern al pull-down.

Sets bit 0 of RPC.PC (Chipset Config Registers:

Offset 224h)

This signal has a weak intern al pull-up.

Sets bit 2 of RPC.PC2 (Chipse t Config

Registers:Offset 0224h) when sampled low.

This signal has a weak intern al pull-down.

NOTE: This signal should not be pulled high

Tying this strap low configur es DMI for ESIcompatible

operation. This signal has a weak internal

pull-up.

NOTE: ESI compatible mode is for server platforms

only. This signal should not be pulled low for

desktop and mobile.

Sampled low: this indicates t hat the

system is strapped to the “to p-block swap”

mode (IntelR ICH9 inverts A16 for all

cycles targeting BIOS space). The status of

this strap is readable via th e Top Swap bit

(Chipset Config Registers:Off set 3414h:

bit 0). Note that software wi ll not be able

to clear the Top-Swap bit unt il the system

is rebooted without GNT3# bei ng pulled down.

Controllable via Boot BIOS De stination

bit (Chipset Config Registers :Offset 3410h:bit 11).

This strap is used in conjunc tion with Boot BIOS

Destination Selection 0 strap .

Bit11

(GNT0#)

Controllable via Boot BIOS De stination

bit (Chipset Config Registers :Offset 3410h:bit 10).

This strap is used in conjunc tion with Boot BIOS

Destination Selection 1 strap .

Bit11

(GNT0#)

Signal has weak internal pull -up. Sets bit 27 of

MPC.LR (Device 28: Function 0 : Offset D8)

Sampled high: this indicates that the system

is strapped to the “No Reboot ” mode (ICH9 will

disable the TCO Timer system reboot feature). The

status of this strap is reada ble via the NO REBOOT

bit (Chipset Config Registers :Offset 3410h:bit 5).

This signal should not be pul l low unless using

XOR Chain testing.

Sampled low: the Flash Descri ptor Security will be

overridden. Sampled high: the security measures will be

in effect. This strap should only be enabled in

manufacturing environments.

The signal is required to be high for mobile

applications.

Sampled low: the Integrated T PM will be disabled.

Sampled high: the MCH TPM ena ble strap is sampled low

and the TPM Disable bit is cl ear, the Integrated TPM

will be enabled.

NOTE: This signal is required to be floating or pulled

low for desktop applications.

Bit 10

(SPI_CS1#)

0 1 SPI

1 0 PCI

1 1 LPC

0 0 Reserved

Bit 10

(SPI_CS1#)

0 1 SPI

1 0 PCI

1 1 LPC

0 0 Reserved

CH9 EDS 642879 Rev.2.3

C

omment

Boot BIOS

Destination

B

Boot BIOS

Destination

B

C

I

CH9 Integrated pull-up

and pull-down Resistors

I

CH9 EDS 642879 Rev.2.3

S

IGNAL

L_CLK[1:0]

C

C

L_DATA[1:0]

C

L_RST0#

DPRSLPVR/GPIO16

HDA_BIT_CLK

HDA_DOCK_EN#/GPIO33

HDA_RST#

HDA_SDIN[3:0]

HDA_SDOUT

HDA_SYNC

GNT0#, GNT[3:1]#/

GPIO[55,53,51]

GPIO20

GPIO49

LAD[3:0]# / FHW[3:0]#

LAN_RXD[2:0]

LDRQ0

LDRQ1 / GPIO23

PME#

PWRBTN#

SATALED#

SPI_CS1# /

GPIO58 (Desktop Only) /

CLGPIO6 (Digital Office Only)

SPI_MOSI

SPI_MISO

SPKR

TACH[3:0]

TP3

USB[11:0][P,N]

R

esistor Type/Value

PULL-UP 20K

PULL-UP 20K

P

ULL-UP 10K

PULL-DOWN 20K

PULL-DOWN 20K

PULL-UP 20K

PULL-DOWN 20K

PULL-DOWN 20K

PULL-DOWN 20K

PULL-DOWN 20K

PULL-UP 20K

PULL-DOWN 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 15K

PULL-UP 20K

PULL-DOWN 20K

PULL-UP 20K

PULL-DOWN 20K

PULL-UP 20K

PULL-UP 20K

PULL-DOWN 15K

PCIE Routing

LANE1

LANE2

MiniCard WLAN

LANE3 LAN

USB Table

USB Pair

0

1

2

3

4

5

6

7

8

9

10

11

Device

USB0

RESERVED

USB2

USB3

BLUETOOTH

RESERVED

WLAN

RESERVED

RESERVED

RESERVED

Card Reader

CAMERA

C

D

antiga chipset and ICH9M I/O controller

C

E

Hub strapping configuration

in NameStrap Description

P

CFG2:0 FSB Frequency

CFG5 DMI x2 Select 0 = DMI x2

CFG6 ITPM Host Interface

CFG7 Intel Management

CFG9

CFG10 PCIE Loopback enable 0 = Enable (Note 3)

CFG12 ALLZ 0 =ALLZ mode enabled (Note 3)

CFG13 XOR

CFG16 FSB Dynamic ODT 0 = Dynamic ODT Disabled

CFG19 DMI Lane Reversal

CFG20

SDVO

_CTRLDATA

(Note4)

L_DDC_DATA Local Flat Panel

DDPC

_CTRLDATA

(Note4)

CFG4:3

CFG8

CFG11

CFG14

CFG15

CFG17

CFG18

NOTE:

1. All strap signals are samp led with respect to the leadin g edge of the GMCH Power OK

(PWROK) signal.

2. iTPM can be disabled by a ‘Soft-Strap’ option in the Fla sh-descriptor section of the

Firmware. This ‘Soft-Strap’ i s activated only after enablin g iTPM via CFG6.

3. Only one of the CFG10/CFG1 2/CFG13 straps can be enabled at any time.

4. DDPC_CTRL_DATA & SDVO_CTRL _DATA straps should both be hi gh to enable Display Port.

engine crypto strap

PCIE Graphics Lane

Digital Display Port

(SDVO/DP/HDMI)

Concurrent with PCIe

SDVO Present

(LFP) Present

Digital Display

Present

Reserved

D

Montevina Platform Design guide 355648 Rev.2.3

onfiguration

000 = FSB1066

010 = FSB800

011 = FSB667

Others = Reserved

1 = DMI x4 (Default)

0 = The iTPM Host Interface i s enabled (Note 2)

1 = The iTPM Host Interface i s disabled (default)

0 = Intel Management Engine C rypto Transport

Layer Security (TLS) cipher s uite with no

confidentiality

1 = Intel Management Engine C rypto TLS cipher

suite with confidentiality (d efault)

0 = Reverse Lanes, 15->0, 14- >1 etc.

1 = Normal operation (default ): Lane Numbered

in Order

1 = Disable (Default)

1 = Disable (Default)

0 = XOR mode enabled (Note 3)

1 = Disable (Default)

1 = Dynamic ODT Enabled (Defa ult)

0 = Normal operation (Default ): Lane Numbered in

Order

1 = Reverse Lanes

DMI x4 mode [MCH->ICH]: (3->0 , 2->1, 1->2 and 0->3)

DMI x2 mode [MCH->ICH]: (3->0 , 2->1)

0 = Only digital DisplayPort (SDVO/DP/HDMI) or

PCIe is operational (default)

1 = Digital DisplayPort (SDVO /DP/HDMI) and

PCIe are operating simultaneo usly via the PEG port

0 = No SDVO/HDMI/DP interface disabled (default)

1 = SDVO/HDMI/DP interface en abled

0 = LFP Disabled (Default)

1 = LFP Card Present; PCIE di sabled

0 = Digital display (HDMI/DP) device absent

(default)

1 = Digital display (HDMI/DP) Device Present

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

C

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Table of Content

Table of Content

Table of Content

DJ2 Montevina UMA

DJ2 Montevina UMA

DJ2 Montevina UMA

E

X00

X00

6 88Friday, May 28, 2010

6 88Friday, May 28, 2010

6 88Friday, May 28, 2010

X00

5

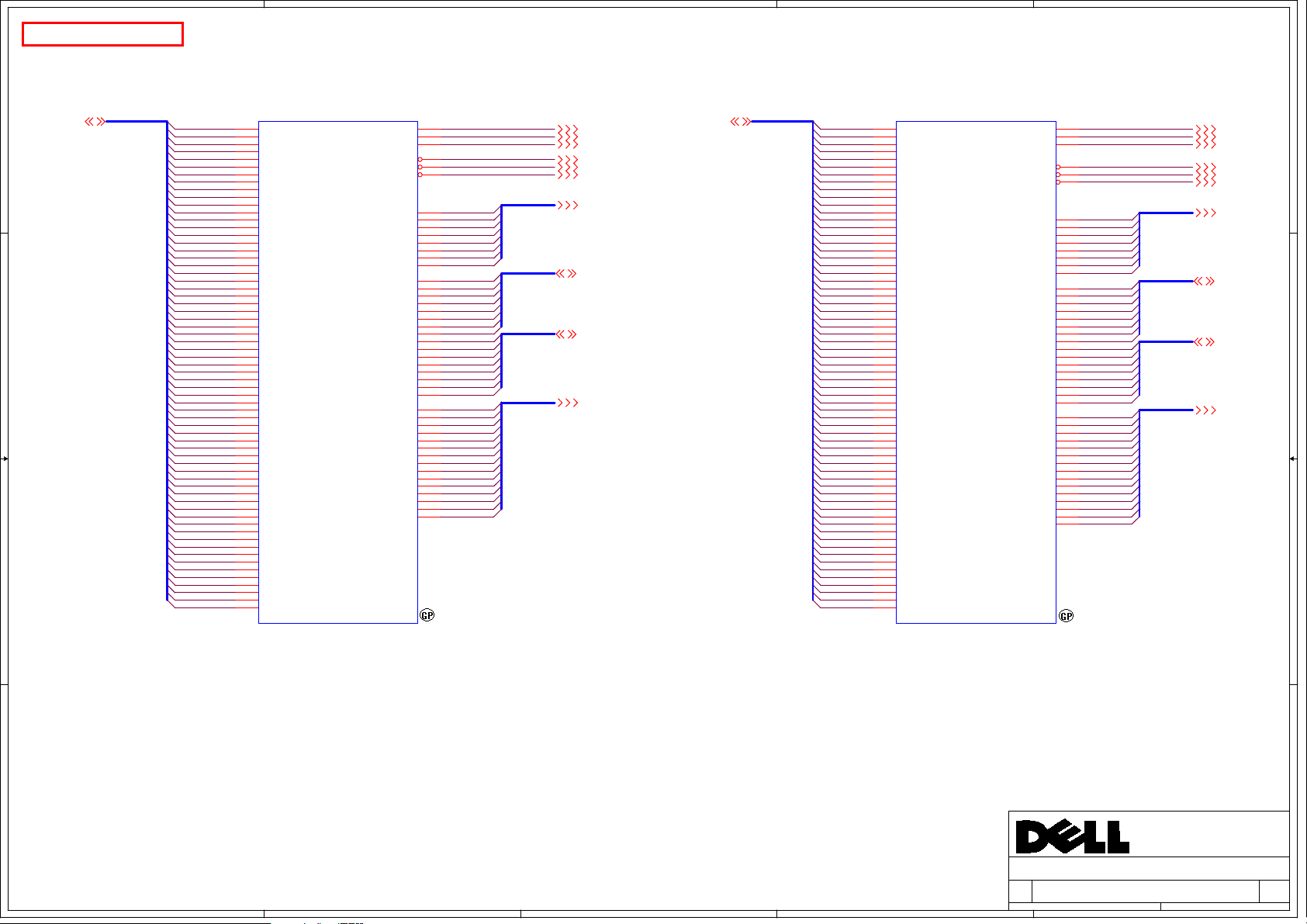

SID = CLOCK

S

1

C706

C706

C701

C701

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

D05V_CK505_IO

12

C707

C707

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

12

C717

C717

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

12

C708

C708

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

12

C718

C718

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

+

1.05V_VCCP

D D

+3.3V_RUN 3D3V_S0_CK505

C C

12

12

1 2

702

702

C

C

SC1U10V3KX-3GP

SC1U10V3KX-3GP

1 2

713

713

C

C

SC1U10V3KX-3GP

SC1U10V3KX-3GP

R

R

704

704

0R0603-PAD

0R0603-PAD

R706

R706

0R0603-PAD

0R0603-PAD

12

C704

C704

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

12

12

714

714

C715

C715

C

C

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

12

C705

C705

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

12

12

C716

C716

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

CLKSATAREQ#22

CLKREQ#_B11

PCLK_FWH58

PCLK_KBC37

CLK_PCI_ICH21

CLK_14M_ICH22

R708 after MP need to be DY

DY

DY

12

12

DY

DY

4

C

1 2

DY

DY

LK_XTAL_IN

C

LK_XTAL_OUT

12

C

C

R701

R701

1 2

22R2J-2-GP

22R2J-2-GP

SC15P50V2JN-2-GP

SC15P50V2JN-2-GP

711

711

CLKSATAREQ#

CLKREQ#_1

PCI2_TME

27_SEL

ITP_EN

FSB

FSC

X

X

701

701

SC12P50V2JN-3GP

C709

C709

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

C719

C719

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

SC12P50V2JN-3GP

CLK_48M_CARD32

CLK_48M_ICH22

H_STP_PCI#22

H_STP_CPU#22

ICH_SMBCLK18,19,22,64

ICH_SMBDATA18,19,22,64

CK_PWRGD22

-1_0519

DY

DY

12

12

C722

C722

C721

C721

DY

DY

SC4D7P50V2CN-1GP

SC4D7P50V2CN-1GP

12

C720

C720

SC4D7P50V2CN-1GP

SC4D7P50V2CN-1GP

1 2

X-14D31818M-37GP

X-14D31818M-37GP

12

710

710

C

C

R705 22R2J-2-GPR705 22R2J-2-GP

1 2

C712 SC4D7P50V2CN-1GP

C712 SC4D7P50V2CN-1GP

R707 475R2F-L1-GPR707 475R2F-L1-GP

1 2

R708 33R2J-2-GPR708 33R2J-2-GP

1 2

R709 33R2J-2-GPR709 33R2J-2-GP

1 2

R710 33R2J-2-GPR710 33R2J-2-GP

1 2

R711 33R2J-2-GPR711 33R2J-2-GP

1 2

SC4D7P50V2CN-1GP

SC4D7P50V2CN-1GP

FSA

3

U

U

3

XN

2

XOUT

17

USB_48/F SA

45

PC_STOP #

44

CPU_STO P#

7

SCLK

6

SDATA

63

CKPW RGD/PWRDW N#

8

PCI0/CR#_A

10

PCI1/CR#_B

11

PCI2/TME

12

PCI3

13

PCI4/GCLK_S EL

14

PCIF0/ITP_EN

64

FSB/TEST _MODE

5

REF0/FSC /TEST_SEL

55

NC#55

2

3

D3V_S0_CK505

4

9

16

46

701

701

62

VDD_48

VDD_PCI

VDD_REF

VDD_SRC

VDD_CPU

VSS_REF

VSS_PCI

VSS_48

1

15

18

1

D05V_CK505_IO

-

1_0525

1_0520 FOR EMI

19

23

27

33

43

52

56

61

VDD_IO

VDD_PLL3

VSS_IO

VSS_SRC

22

30

36

VDD_SRC_IO

VDD_SRC_IO

VDD_SRC_IO

VDD_PLL3_IO

SRCT1/LC DT_100/27M_NS S

SRCC1/LC DT_100/27M_SS

VSS_PLL3

VSS_SRC

VSS_SRC

VSS_CPU

26

49

59

65

CPUC0

VDD_CPU_IO

CPUC1

SRCT8/CP U2_ITPT

SRCC8/CP U2_ITPC

SRCT7/CR #_F

SRCC7/CR #_E

SRCC6

SRCT10

SRCC10

SRCT1/CR #_H

SRCC1/CR #_G

SRCC9

SRCC4

SRCT3/CR #_C

SRCC3/CR #_D

SRCT2/SA TAT

SRCC2/SA TAC

SRCT0/DO T96T

SRCC0/DO T96C

GND

SLG8SP513VTR-GP

SLG8SP513VTR-GP

CPUT0

60

58

CPUT1

57

54

53

51

50

48

SRCT6

47

41

42

40

39

37

SRCT9

38

34

SRCT4

35

31

32

28

29

24

25

20

21

Main = 71.08513.003(SLG)

Main = 71.08513.003(SLG)

Second = 71.09356.00W(ICS)

Second = 71.09356.00W(ICS)

-

CLK_CPU_BCLK_1

CLK_CPU_BCLK#_1

CLK_MCH_BCLK_1

CLK_MCH_BCLK#_1

CLK_PCIE_LAN_1

CLK_PCIE_LAN#_1

CLK_PCIE_ICH_1

CLK_PCIE_ICH#_1

R702 10KR2J-3-GPR702 10KR2J-3-GP

1 2

CLK_PCIE_MINI1_1

CLK_PCIE_MINI1#_1

CLK_MCH_3GPLL_1

CLK_MCH_3GPLL#_1

CLK_PCIE_SATA_1

CLK_PCIE_SATA#_1

MCH_SSCDREFCLK_1

MCH_SSCDREFCLK#_1

CLK_MCH_DREFCLK_1

CLK_MCH_DREFCLK#_1

R723 0R2J-2-GPR723 0R2J-2-GP

1 2

R724 0R2J-2-GPR724 0R2J-2-GP

1 2

R725 0R2J-2-GPR725 0R2J-2-GP

1 2

R726 0R2J-2-GPR726 0R2J-2-GP

1 2

R727 0R2J-2-GPR727 0R2J-2-GP

1 2

R728 0R2J-2-GPR728 0R2J-2-GP

1 2

R729 0R2J-2-GPR729 0R2J-2-GP

1 2

R730 0R2J-2-GPR730 0R2J-2-GP

1 2

R731 0R2J-2-GPR731 0R2J-2-GP

1 2

R732 0R2J-2-GPR732 0R2J-2-GP

1 2

R733 0R2J-2-GPR733 0R2J-2-GP

1 2

R734 0R2J-2-GPR734 0R2J-2-GP

1 2

R735 0R2J-2-GPR735 0R2J-2-GP

1 2

R736 0R2J-2-GPR736 0R2J-2-GP

1 2

R737 0R2J-2-GPR737 0R2J-2-GP

1 2

R738 0R2J-2-GPR738 0R2J-2-GP

1 2

R739 0R2J-2-GPR739 0R2J-2-GP

1 2

R740 0R2J-2-GPR740 0R2J-2-GP

1 2

+3.3V_RUN

1

CLK_CPU_BCLK 8

CLK_CPU_BCLK# 8

CLK_MCH_BCLK 10

CLK_MCH_BCLK# 10

CLK_PCIE_LAN 35

CLK_PCIE_LAN# 35

CLK_PCIE_ICH 21

CLK_PCIE_ICH# 21

-1_0525

MINI1_CLKREQ# 64

CLK_PCIE_MINI1 64

CLK_PCIE_MINI1# 64

CLK_MCH_3GPLL 11

CLK_MCH_3GPLL# 11

CLK_PCIE_SATA 20

CLK_PCIE_SATA# 20

MCH_SSCDREFCLK 11

MCH_SSCDREFCLK# 11

CLK_MCH_DREFCLK 11

CLK_MCH_DREFCLK# 11

B B

3D3V_S0_CK505

12

R712

R712

10KR2J-3-GP

10KR2J-3-GP

12

R715

R715

DY

DY

10KR2J-3-GP

10KR2J-3-GP

ITP_EN

ITP_EN Output

0 SRC8

1 CPU_ITP

3D3V_S0_CK505

12

R713

R713

10KR2J-3-GP

10KR2J-3-GP

12

R716

R716

10KR2J-3-GP

10KR2J-3-GP

DY

DY

PCI2_TME

PCI2_TME Output

0

Overclocking of CPU and SRC allowed

1

Overclocking of CPU and SRC not allowed

R714

R714

10KR2J-3-GP

10KR2J-3-GP

1 2

27_SEL

27_SEL PIN24/25

PIN20/21

96M0 100M

100M1 27M

SEL1

FSB

0 1

0 1

5

SEL0

FSA

1

01

CPU

100M

133M

166M

200M

FSB

533M

667M

800M

1067M266M

CPU_BSEL28

X

CPU_BSEL18

CPU_BSEL08

4

A A

FSC

1

0

0 1

0

0 0 0

SEL2

-1_0527

R717 10KR2J-3-GPR717 10KR2J-3-GP

1 2

R718 0R2J-2-GPR718 0R2J-2-GP

1 2

R719 2K2R2J-2-GPR719 2K2R2J-2-GP

1 2

R720 1KR2J-1-GPR720 1KR2J-1-GP

1 2

R721 1KR2J-1-GPR721 1KR2J-1-GP

1 2

R722 1KR2J-1-GPR722 1KR2J-1-GP

1 2

FSC

FSB

FSA

MCH_CLKSEL0 11

MCH_CLKSEL1 11

MCH_CLKSEL2 11

3

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Clock Generator SLG8SP513VTR

Clock Generator SLG8SP513VTR

Clock Generator SLG8SP513VTR

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

DJ2 Montevina UMA

DJ2 Montevina UMA

DJ2 Montevina UMA

Taipei Hsien 221, Taiwan, R.O.C.

7 88Wednesday, June 02, 2010

7 88Wednesday, June 02, 2010

7 88Wednesday, June 02, 2010

1

X00

X00

X00

5

SID = CPU

S

1

1

OF 4

OF 4

C

C

PU1A

H

D D

H

H

_A#[35..3]10

C C

B B

A A

_A#[35..3]

H_ADSTB#010

H_REQ#[4..0]10

H_ADSTB#110

H_A20M#20

H_FERR#20

H_IGNNE#20

H_STPCLK#20

H_INTR20

H_NMI20

H_SMI#20

TP802TP802

TP803TP803

TP804TP804

TP805TP805

TP806TP806

TP807TP807

TP808TP808

TP809TP809

TP810TP810

TP811TP811

TP812TP812

_A#3

H

_A#4

H

_A#5

H

_A#6

H

_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

RSVD_CPU_1

RSVD_CPU_2

RSVD_CPU_3

RSVD_CPU_4

RSVD_CPU_5

RSVD_CPU_6

RSVD_CPU_7

RSVD_CPU_8

RSVD_CPU_9

RSVD_CPU_10

RSVD_CPU_11

ITP_TMS

ITP_TDI

ITP_BPM#5

ITP_TDO

ITP_DBRESET#

ITP_TCK

ITP_TRST#

PU1A

J4

A

3#

L5

A

4#

L4

A

5#

K5

A

6#

M3

A

7#

N2

A8#

J1

A9#

N3

A10#

P5

A11#

P2

A12#

L2

A13#

P4

A14#

P1

A15#

R1

A16#

M1

ADSTB0#

K3

REQ0#

H2

REQ1#

K2

REQ2#

J3

REQ3#

L1

REQ4#

Y2

A17#

U5

A18#

R3

A19#

W6

A20#

U4

A21#

Y5

A22#

U1

A23#

R4

A24#

T5

A25#

T3

A26#

W2

A27#

W5

A28#

Y4

A29#

U2

A30#

V4

A31#

W3

A32#

AA4

A33#

AB2

A34#

AA3

A35#

V1

ADSTB1#

A6

A20M#

A5

FERR#

C4

IGNNE#

D5

STPCLK#

C6

LINT0

B4

LINT1

A3

SMI#

M4

RSVD#M4

N5

RSVD#N5

T2

RSVD#T2

V3

RSVD#V3

B2

RSVD#B2

D22

C3

D2

D3

F6

B1

TEST7

RSVD#C3

RSVD#D2

RSVD#D2 2

RSVD#D3

RSVD#F6

KEY_NC

BGA479-SKT6-GPU7

BGA479-SKT6-GPU7

62.10079.001

R816 51R2F-2-GPR816 51R2F-2-GP

1 2

R817 51R2F-2-GPR817 51R2F-2-GP

1 2

R818 51R2F-2-GPR818 51R2F-2-GP

1 2

R801 51R2F-2-GP

R801 51R2F-2-GP

1 2

R825 1KR2J-1-GP

R825 1KR2J-1-GP

1 2

R819 51R2F-2-GPR819 51R2F-2-GP

1 2

R820 51R2F-2-GPR820 51R2F-2-GP

1 2

ADDR GROUP 0

ADDR GROUP 0

ADDR GROUP 1

ADDR GROUP 1

ICH

ICH

RESERVED

RESERVED

DY

DY

DY

DY

XDP/ITP SIGNALS CONTROL

XDP/ITP SIGNALS CONTROL

THERMAL

THERMAL

PROCHOT #

THERMTR IP#

HCLK

HCLK

All place within 2" to CPU

5

A

DS#

B

NR#

B

PRI#

D

EFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

RESET#

RS0#

RS1#

RS2#

TRDY#

HIT#

HITM#

BPM0#

BPM1#

BPM2#

BPM3#

PRDY#

PREQ#

TCK

TDO

TMS

TRST#

DBR#

THRMDA

THRMDC

BCLK0

BCLK1

+1.05V_VCCP

+3.3V_RUN

4

H1

E2

G5

H5

F21

E1

F1

CPU_IERR#

D20

B3

H4

H_CPURST#

C1

H_RS#0

F3

H_RS#1

F4

H_RS#2

G3

G2

G6

E4

AD4

AD3

AD1

AC4

AC2

ITP_BPM#5

AC1

ITP_TCK

AC5

ITP_TDI

AA6

TDI

ITP_TDO

AB3

ITP_TMS

AB5

ITP_TRST#

AB6

ITP_DBRESET#

C20

R803 0R2J-2-GP

R803 0R2J-2-GP

R804 56R2J-4-GPR804 56R2J-4-GP

D21

A24

B25

C7

R805 56R2J-4-GP

R805 56R2J-4-GP

A22

A21

4

T

P801TP801

1

R802 56R2J-4-GPR802 56R2J-4-GP

1 2

1 2

DY

DY

1 2

H_THERMDA

H_THERMDC

1 2

DY

DY

3

_ADS# 10

H

H

_BNR# 10

_BPRI# 10

H

H

_DEFER# 10

H_DRDY# 10

H_DBSY# 10

H_BREQ#0 10

H_INIT# 20

H_LOCK# 10

H_CPURST# 10

H_RS#[2..0] 10

H_TRDY# 10

H_HIT# 10

H_HITM# 10

+1.05V_VCCP

H_THERMDA 39

H_THERMDC 39

H_THRMTRIP# 11,20,37,42

+1.05V_VCCP

CLK_CPU_BCLK 7

CLK_CPU_BCLK# 7

+1.05V_VCCP

H_THERMDA

H_THERMDC

H_THERMDA, H_THERMDC routing together,

Trace width / Spacing = 10 / 10 mil

CPU_PROCHOT# 47

+1.05V_VCCP

1 2

12

R812

R812

2KR2F-3-GP

2KR2F-3-GP

Layout notes

Z= 55 Ohm 0.5" MAX for CPU_GTLREF0

12

C849

C849

DY

DY

SC2200P50V2KX-2GP

SC2200P50V2KX-2GP

H_THRMTRIP# should connect to

ICH9 and MCH without T-ing.

R806

R806

1KR2F-3-GP

1KR2F-3-GP

CPU_GTLREF0

12

C801

C801

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

3

H_DSTBN#010

H_DSTBP#010

H_DINV#010

H_DSTBN#110

H_DSTBP#110

H_DINV#110

R808 1KR2J-1-GP

R808 1KR2J-1-GP

1 2

DY

DY

R810 1KR2J-1-GP

R810 1KR2J-1-GP

1 2

DY

DY

R813 1KR2J-1-GP

R813 1KR2J-1-GP

1 2

DY

DY

R815 1KR2J-1-GP

R815 1KR2J-1-GP

1 2

DY

DY

CPU_BSEL07

CPU_BSEL17

CPU_BSEL27

TP813TP813

2

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

TEST1

TEST2

CPU_TEST3

CPU_TEST5

H_CPURST#

1

2

H_DINV#[3..0]

H_DSTBN#[3..0]

H_DSTBP#[3..0]

H_D#[63..0]

CPU1B

CPU1B

E22

D0#

F24

D1#

E26

D2#

G22

D3#

F23

D4#

G25

D5#

E25

D6#

E23

D7#

K24

D8#

G24

D9#

J24

D10#

J23

D11#

H22

D12#

F26

D13#

K22

D14#

H23

D15#

J26

DSTBN0#

H26

DSTBP0#

H25

DINV0#

N22

D16#

K25

D17#

P26

D18#

R23

D19#

L23

D20#

M24

D21#

L22

D22#

M23

D23#

P25

D24#

P23

D25#

P22

D26#

T24

D27#

R24

D28#

L25

D29#

T25

D30#

N25

D31#

L26

DSTBN1#

M26

DSTBP1#

N24

DINV1#

AD26

GTLREF

C23

TEST1

D25

TEST2

C24

TEST3

AF26

TEST4

AF1

TEST5

A26

TEST6

B22

BSEL0

B23

BSEL1

C21

BSEL2

BGA479-SKT6-GPU7

BGA479-SKT6-GPU7

62.10079.001

1

H_DINV#[3..0] 10

H_DSTBN#[3..0] 10

H_DSTBP#[3..0] 10

H_D#[63..0] 10

2 OF 4

2 OF 4

H_D#32

Y22

D32#

D33#

D34#

D35#

DATA GRP0 DATA GRP1

DATA GRP0 DATA GRP1

D36#

D37#

D38#

D39#

D40#

D41#

D42#

DATA GRP2DATA GRP3

DATA GRP2DATA GRP3

D43#

D44#

D45#

D46#

D47#

DSTBN2#

DSTBP2#

DINV2#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DSTBN3#

DSTBP3#

DINV3#

COMP0

MISC

MISC

COMP1

COMP2

COMP3

DPRSTP#

DPSLP#

DPWR #

PWRG OOD

SLP#

PSI#

Layout Note:

Comp0, 2 connect with Zo=27.4 ohm, make

trace length shorter than 0.5 ".

Comp1, 3 connect with Zo=55 o hm, make

trace length shorter than 0.5 ".

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

H_D#33

AB24

H_D#34

V24

H_D#35

V26

H_D#36

V23

H_D#37

T22

H_D#38

U25

H_D#39

U23

H_D#40

Y25

H_D#41

W22

H_D#42

Y23

H_D#43

W24

H_D#44

W25

H_D#45

AA23

H_D#46

AA24

H_D#47

AB25

Y26

AA26

U22

H_D#48

AE24

H_D#49

AD24

H_D#50

AA21

H_D#51

AB22

H_D#52

AB21

H_D#53

AC26

H_D#54

AD20

H_D#55

AE22

H_D#56

AF23

H_D#57

AC25

H_D#58

AE21

H_D#59

AD21

H_D#60

AC22

H_D#61

AD23

H_D#62

AF22

H_D#63

AC23

AE25

AF24

AC20

COMP0

R26

COMP1

U26

COMP2

AA1

COMP3

Y1

E5

B5

D24

D6

D7

AE6

CPU-FSB(1/2)

CPU-FSB(1/2)

CPU-FSB(1/2)

DJ2 Montevina UMA

DJ2 Montevina UMA

DJ2 Montevina UMA

H_DSTBN#2 10

H_DSTBP#2 10

H_DINV#2 10

H_DSTBN#3 10

H_DSTBP#3 10

H_DINV#3 10

R807 27D4R2F-L1-GPR807 27D4R2F-L1-GP

1 2

R809 54D9R2F-L1-GPR809 54D9R2F-L1-GP

1 2

R811 27D4R2F-L1-GPR811 27D4R2F-L1-GP

1 2

R814 54D9R2F-L1-GPR814 54D9R2F-L1-GP

1 2

H_DPRSTP# 11,20,47

H_DPSLP# 20

H_DPWR# 10

H_PWRGOOD 20,42

H_CPUSLP# 10

PSI# 47

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

8 88Wednesday, June 02, 2010

8 88Wednesday, June 02, 2010

8 88Wednesday, June 02, 2010

1

X00

X00

X00

5

SID = CPU

S

D D

+

VCC_CORE

3 OF 4

3 OF 4

CPU1C

CPU1C

A7

VCC

A9

VCC

A10

VCC

A12

VCC

A13

VCC

A15

VCC

A17

VCC

A18

VCC

A20

VCC

B7

VCC

B9

VCC

B10

VCC

B12

VCC

B14

VCC

B15

VCC

B17

VCC

B18

VCC

B20

VCC

C9

VCC

C10

VCC

C12

VCC

C13

VCC

C15

VCC

C C

B B

C17

VCC

C18

VCC

D9

VCC

D10

VCC

D12

VCC

D14

VCC

D15

VCC

D17

VCC

D18

VCC

E7

VCC

E9

VCC

E10

VCC

E12

VCC

E13

VCC

E15

VCC

E17

VCC

E18

VCC

E20

VCC

F7

VCC

F9

VCC

F10

VCC

F12

VCC

F14

VCC

F15

VCC

F17

VCC

F18

VCC

F20

VCC

AA7

VCC

AA9

VCC

AA10

VCC

AA12

VCC

AA13

VCC

AA15

VCC

AA17

VCC

AA18

VCC

AA20

VCC

AB9

VCC

AC10

VCC

AB10

VCC

AB12

VCC

AB14

VCC

AB15

VCC

AB17

VCC

AB18

VCC

BGA479-SKT6-GPU7

BGA479-SKT6-GPU7

62.10079.001

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCA

VCCA

VID0

VID1

VID2

VID3

VID4

VID5

VID6

VCCSENS E

VSSSENS E

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

G21

V6

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

C26

AD6

AF5

AE5

AF4

AE3

AF3

AE2

AF7

AE7

+

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

CPU_VID5

CPU_VID6

VCC_CORE

layout note: "+1.5V_VCCA"

as short as possible

CPU_VID[6..0] 47

R902

R902

1 2

100R2F-L1-GP-U

100R2F-L1-GP-U

R903

R903

1 2

100R2F-L1-GP-U

100R2F-L1-GP-U

+

VCC_CORE

12

D

D

Y

Y

+VCC_CORE

12

+VCC_CORE

12

+1.05V_VCCP

12

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

PG902

PG902

1 2

GAP-CLOSE-PWR-3-GP

GAP-CLOSE-PWR-3-GP

PG901

PG901

1 2

GAP-CLOSE-PWR-3-GP

GAP-CLOSE-PWR-3-GP

4

C902

C902

D

D

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C921

C921

DY

DY

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C923

C923

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C933

C933

12

12

C901

C901

D

D

Y

Y

Y

Y

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

12

C911

C911

DY

DY

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

12

C924

C924

DY

DY

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

12

C934

C934

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

SCD01U16V2KX-3GP

SCD01U16V2KX-3GP

+VCC_CORE

VCC_SENSE 47

VSS_SENSE 47

3

12

12

C903

C903

C904

C920

C920

D

D

Y

Y

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C912

C912

DY

DY

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C925

C925

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C935

C935

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

C939

C939

D

D

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C913

C913

DY

DY

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C926

C926

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C936

C936

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

12

C904

Y

Y

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C914

C914

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C927

C927

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C938

C938

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

1 2

0R0603-PAD

0R0603-PAD

12

C940

C940

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

D

D

R901

R901

12

12

C905

C905

Y

Y

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C915

C915

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C928

C928

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C937

C937

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

+1.5V_RUN+1.5V_VCCA

12

C906

C906

C907

D

D

DY

DY

DY

DY

Y

Y

12

12

DY

DY

C907

D

D

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C922

C922

C916

C916

DY

DY

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C930

C930

C929

C929

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

TC901

TC901

ST220U2D5VBM-LGP

ST220U2D5VBM-LGP

Layout Note:

Place as close as possible

to the CPU VCCA pin.

VCC_SENSE and VSS_SENSE lines

should be of equal length.

12

12

C908

C908

Y

Y

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C917

C917

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C931

C931

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C909

C909

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

12

C918

C918

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C932

C932

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C

C

910

910

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C919

C919

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

2

OF 4

OF 4

4

4

C

C

PU1D

PU1D

A4

V

SS

A8

V

SS

A11

V

SS

A14

V

SS

A16

V

SS

A19

V

SS

A23

V

SS

AF2

V

SS

B6

V

SS

B8

V

SS

B11

VSS

B13

VSS

B16

VSS

B19

VSS

B21

VSS

B24

VSS

C5

VSS

C8

VSS

C11

VSS

C14

VSS

C16

VSS

C19

VSS

C2

VSS

C22

VSS

C25

VSS

D1

VSS

D4

VSS

D8

VSS

D11

VSS

D13

VSS

D16

VSS

D19

VSS

D23

VSS

D26

VSS

E3

VSS

E6

VSS

E8

VSS

E11

VSS

E14

VSS

E16

VSS

E19

VSS

E21

VSS

E24

VSS

F5

VSS

F8

VSS

F11

VSS

F13

VSS

F16

VSS

F19

VSS

F2

VSS

F22

VSS

F25

VSS

G4

VSS

G1

VSS

G23

VSS

G26

VSS

H3

VSS

H6

VSS

H21

VSS

H24

VSS

J2

VSS

J5

VSS

J22

VSS

J25

VSS

K1

VSS

K4

VSS

K23

VSS

K26

VSS

L3

VSS

L6

VSS

L21

VSS

L24

VSS

M2

VSS

M5

VSS

M22

VSS

M25

VSS

N1

VSS

N4

VSS

N23

VSS

N26

VSS

P3

VSS

BGA479-SKT6-GPU7

BGA479-SKT6-GPU7

62.10079.001

V

V

V

V

V

V

V

V

V

V

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

P6

SS

P21

SS

P24

SS

R2

SS

R5

SS

R22

SS

R25

SS

T1

SS

T4

SS

T23

SS

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

A2

AF6

AF8

AF11

AF13

AF16

AF19

AF21

A25

AF25

CPU_GND1

CPU_GND2

CPU_GND3

CPU_GND4

1

NCTF

PIN

TP902TP902

TP901TP901

TP903TP903

TP904TP904

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

DJ2 Montevina UMA

DJ2 Montevina UMA

DJ2 Montevina UMA

Taipei Hsien 221, Taiwan, R.O.C.

CPU-Power(2/2)

CPU-Power(2/2)

CPU-Power(2/2)

9 88Wednesday, June 02, 2010

9 88Wednesday, June 02, 2010

9 88Wednesday, June 02, 2010

1

X00

X00

X00

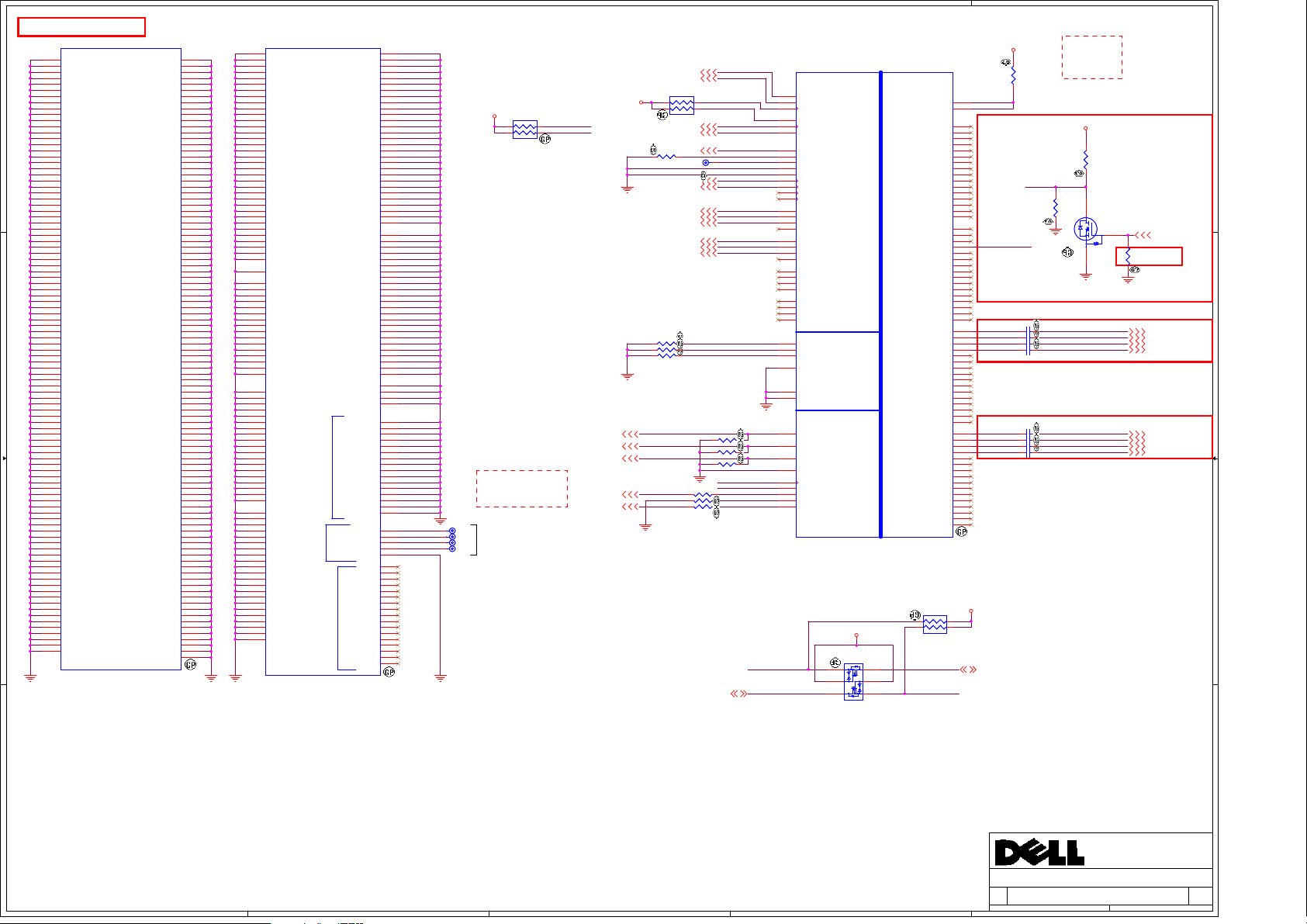

SID = MCH

S

5

4

3

2

1

1

1

OF 10

N

N

B1A

D D

C C

H_SWING routing Trace width and

Spacing use 10 / 20 mil

H_SWING Resistors and

Capacitors close MCH

500 mil ( MAX )

12

H_RCOMP routing Trace width and

Spacing use 10 / 20 mil

B B

1 2

R1003

R1003

+1.05V_VCCP

H_SWING

C1002

C1002

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

H_RCOMP

24D9R2F-L-GP

24D9R2F-L-GP

12

R1002

R1002

221R2F-2-GP

221R2F-2-GP

12

R1001

R1001

100R2F-L1-GP-U

100R2F-L1-GP-U

_D#[63..0]8

H

Place R1001 near to the chip ( < 0.5")

+1.05V_VCCP

R1004

R1004

1KR2F-3-GP

1KR2F-3-GP

1 2

12

R1005

R1005

2KR2F-3-GP

2KR2F-3-GP

H_AVREF

H

_D#[63..0]

H_CPURST#8

H_CPUSLP#8

12

C1001

C1001

DY

DY

SCD1U16V2KX-3GP

SCD1U16V2KX-3GP

H

_D#0

H

_D#1

H

_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_SWING

H_RCOMP

B1A

F2

H

_D#_0

G8

H

_D#_1

F8

H

_D#_2

E6

H_D#_3

G2

H_D#_4

H6

H_D#_5

H2

H_D#_6

F6

H_D#_7

D4

H_D#_8

H3

H_D#_9

M9

H_D#_10

M11

H_D#_11

J1

H_D#_12

J2

H_D#_13

N12

H_D#_14

J6

H_D#_15

P2

H_D#_16

L2

H_D#_17

R2

H_D#_18

N9

H_D#_19

L6

H_D#_20

M5

H_D#_21

J3

H_D#_22

N2

H_D#_23

R1

H_D#_24

N5

H_D#_25

N6

H_D#_26

P13

H_D#_27

N8

H_D#_28

L7

H_D#_29

N10

H_D#_30

M3

H_D#_31

Y3

H_D#_32

AD14

H_D#_33

Y6

H_D#_34

Y10

H_D#_35

Y12

H_D#_36

Y14

H_D#_37

Y7

H_D#_38

W2

H_D#_39

AA8

H_D#_40

Y9

H_D#_41

AA13

H_D#_42

AA9

H_D#_43

AA11

H_D#_44

AD11

H_D#_45

AD10

H_D#_46

AD13

H_D#_47

AE12

H_D#_48

AE9

H_D#_49

AA2

H_D#_50

AD8

H_D#_51

AA3

H_D#_52

AD3

H_D#_53

AD7

H_D#_54

AE14

H_D#_55

AF3

H_D#_56

AC1

H_D#_57

AE3

H_D#_58

AC3

H_D#_59

AE11

H_D#_60

AE8

H_D#_61

AG2

H_D#_62

AD6

H_D#_63

C5

H_SW ING

E3

H_RCOMP

C12

H_CPURS T#

E11

H_CPUSL P#

A11

H_AVREF

B11

H_DVREF

CANTIGA-GM-GP-U-NF

CANTIGA-GM-GP-U-NF

HOST

HOST

OF 10

H

_A#_3

H

_A#_4

H

_A#_5

H

_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_A#_32

H_A#_33

H_A#_34

H_A#_35

H_ADS#

H_ADSTB #_0

H_ADSTB #_1

H_BNR#

H_BPRI#

H_BREQ#

H_DEFER #

H_DBSY#

HPLL_CL K

HPLL_CL K#

H_DPW R#

H_DRDY#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_DSTBN #_0

H_DSTBN #_1

H_DSTBN #_2

H_DSTBN #_3

H_DSTBP #_0

H_DSTBP #_1

H_DSTBP #_2

H_DSTBP #_3

H_REQ#_ 0

H_REQ#_ 1

H_REQ#_ 2

H_REQ#_ 3

H_REQ#_ 4

H_RS#_0

H_RS#_1

H_RS#_2

A14

C15

F16

H13

C18

M16

J13

P16

R16

N17

M13

E17

P17

F17

G20

B19

J16

E20

H16

J20

L17

A17

B17

L16

C21

J17

H20

B18

K17

B20

F21

K21

L20

H12

B16

G17

A9

F11

G12

E9

B10

AH7

AH6

J11

F9

H9

E12

H11

C9

J8

L3

Y13

Y1

L10

M7

AA5

AE6

L9

M8

AA6

AE5

B15

K13

F13

B13

B14

B6

F12

C8

H

_A#3

H

_A#4

H

_A#5

H

_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

H

_A#[35..3]

H_ADS# 8

H_ADSTB#0 8

H_ADSTB#1 8

H_BNR# 8

H_BPRI# 8

H_BREQ#0 8

H_DEFER# 8

H_DBSY# 8

CLK_MCH_BCLK 7

CLK_MCH_BCLK# 7

H_DPWR# 8

H_DRDY# 8

H_HIT# 8

H_HITM# 8

H_LOCK# 8

H_TRDY# 8

H_DINV#[3..0]

H_DSTBN#[3..0]

H_DSTBP#[3..0]

H_REQ#[4..0]

H_RS#[2..0]

_A#[35..3] 8

H

H_DINV#[3..0] 8

H_DSTBN#[3..0] 8

H_DSTBP#[3..0] 8

H_REQ#[4..0] 8

H_RS#[2..0] 8

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

DJ2 Montevina UMA

DJ2 Montevina UMA

DJ2 Montevina UMA

Taipei Hsien 221, Taiwan, R.O.C.

Cantiga-Host(1/6)

Cantiga-Host(1/6)

Cantiga-Host(1/6)

10 88Wednesday, June 02, 2010

10 88Wednesday, June 02, 2010

10 88Wednesday, June 02, 2010

1

X00

X00

X00

5

SID = MCH

S

i

s current setting

*

CFG Strap

CFG 5

D D

CFG 6

CFG 7

TLS cipher suite with

no confidentiality

CFG 9 P CIE GFX lane r eversed

ow

L

D

MI X 2

I

TPM enable

DMI X 4

ITPM disable

TLS cipher suite with

confidentiality

PCIE GFX lane

numbered in oder

CFG 10 PCIE loopback enable PCIE loopback disable

CFG 12 ALLZ mode enable ALLZ mode disable

CFG 13 XOR mode enable XOR mode disable

CFG 16

CFG 19

DMI Lane Reserved

CFG 20

SDVO concurrent

with PCIE

SDVO_CTRLDATA

FSB dynamic ODT disable

Normal operation Reverse DMI lanes

Only PCIE or SDVO

is operational

SDVO interface disable

L_DDC_DATA LFP disable LFP card present

SDVO/iHDMI/DP

C C

DDPC_CTRLDATA

+3.3V_RUN

R1112 4K02R2F-GP

R1112 4K02R2F-GP

1 2

DY

DY

R1113 4K02R2F-GP

R1113 4K02R2F-GP

1 2

DY

DY

RN1102

RN1102

4

SRN10KJ-5-GP

SRN10KJ-5-GP

R1118 4K02R2F-GP

R1118 4K02R2F-GP

1 2

DY

DY

R1119 2K21R2F-GP

R1119 2K21R2F-GP

1 2

DY

DY

R1124 2K21R2F-GP

R1124 2K21R2F-GP

1 2

DY

DY

B B

A A

interface disabled

CFG19

CFG20

PM_EXTTS#0

1

PM_EXTTS#1

23

CFG9

CFG10

CFG16

5

PM_PW ROK22,37

PLT_RST#21,35,37,57,58,64

H_THRMTRIP#8,20,37, 42

DPRSLPVR22,47

FSB Dynamic ODT enable

*

PCIE and SDVO are

operatiing simultaneously

*

via the PEG port

SDVO interface enable

(HDMI enable)

*

SDVO/iHDMI/DP

interface enabled

*

FSB setting

MCH_CLKSEL07

MCH_CLKSEL17

MCH_CLKSEL27

TP1102TP1102

TP1103TP1103

TP1104TP1104

TP1105TP1105

TP1101TP1101

PM_SYNC#22

H_DPRSTP#8,20,47

PM_EXTTS#018

PM_EXTTS#119

R1125

R1125

1 2

0R0402-PAD

0R0402-PAD

1 2

R1127100R2J-2-GP R1127100R2J-2-GP

SC100P50V2JN-3GP

SC100P50V2JN-3GP

H

igh

C1107

C1107

DY

DY

4

B1B

B1B

N

N

M36

ESERVED#M36

R

N36

R

ESERVED#N36

R33

R

ESERVED#R33

T33

R

ESERVED#T33

AH9

R

ESERVED#AH9

AH10

ESERVED#AH10

R

AH12

R

ESERVED#AH12

AH13

R

ESERVED#AH13

K12

R

AL34

AK34

AN35

AM35

AY21

BG23

BF23

BH18

BF18

-1_0519

AT40

AT11

BG48

BF48

BD48

BC48

BH47

BG47

BE47

BH46

BF46

BG45

BH44

BH43

B31

R25

P25

P20

P24

C25

N24

M24

E21

C23

C24

N21

P21

R20

M20

H21

P29

R28

R29

N33

P32

R32

BH6

BH5

BG4

BH3

BF3

BH2

BG2

BE2

BG1

BF1

BD1

BC1

A47

ESERVED#K12

R

ESERVED#AL34

R

ESERVED#AK34

R

ESERVED#AN35

R

ESERVED#AM35

T24

R

ESERVED#T24

RESERVED#B31

B2

RESERVED#B2

M1

RESERVED#M1

RESERVED#AY21

RESERVED#BG23

RESERVED#BF23

RESERVED#BH18

RESERVED#BF18

T25

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

T21

CFG_13

CFG_14

CFG_15

L21

CFG_16

CFG_17

CFG_18

CFG_19

T28

CFG_20

PM_SYNC#

B7

PM_DPRSTP#

PM_EXT_TS#_0

PM_EXT_TS#_1

PWROK

RSTIN#

T20

THERMTRIP#

DPRSLPVR

NC#BG48

NC#BF48

NC#BD48

NC#BC48

NC#BH47

NC#BG47

NC#BE47

NC#BH46

NC#BF46

NC#BG45

NC#BH44

NC#BH43

NC#BH6

NC#BH5

NC#BG4

NC#BH3

NC#BF3

NC#BH2

NC#BG2

NC#BE2

NC#BG1

NC#BF1

NC#BD1

NC#BC1

F1

NC#F1

NC#A47

CANTIGA-GM-GP -U-NF

CANTIGA-GM-GP -U-NF

RSVD

RSVD

CFG

CFG

PM

PM

NC

NC

MISC

MISC

*

*

*

*

*

*

*

*

*

CFG3

CFG4

CFG9

CFG10

CFG14

CFG15

CFG16

CFG17

CFG19

CFG20

PWRO K_R

RSTIN#

12

4

3

OF 10

OF 10

2

2

AP24

S

A_CK_0

AT21

S

A_CK_1

AV24

S

B_CK_0

AU20

S

B_CK_1

AR24

S

A_CK#_0

AR21

S

A_CK#_1

AU24

S

B_CK#_0

AV20

S

B_CK#_1

BC28

S

A_CKE_0

AY28

S

A_CKE_1

AY36

S

B_CKE_0

BB36

B_CKE_1

S

BA17

SA_CS#_0

AY16

SA_CS#_1

AV16

SB_CS#_0

AR13

SB_CS#_1

BD17

SA_ODT_0

AY17

SA_ODT_1

BF15

SB_ODT_0

AY13

SB_ODT_1

SM_RCOMP

SM_RCOMP#

SM_RCOMP_VOH

SM_RCOMP_VOL

SM_VREF

SM_PWROK

SM_REXT

SM_DRAMRST#

DPLL_REF_CLK

DDR CLK/ CONTROL/COMPENSATION

DDR CLK/ CONTROL/COMPENSATION

DPLL_REF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

PEG_CLK

PEG_CLK#

CLK

CLK

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI

DMI

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

GFX_VID_4

GFX_VR_EN

GRAPHICS VID

GRAPHICS VID

CL_CLK

CL_DATA

CL_PWROK

CL_RST#

MEHDA

MEHDA

CL_VREF

M_RCOMPP

BG22

M_RCOMPN

BH21

SM_RCOMP_VOH

BF28

SM_RCOMP_VOL

BH28

CANTIGA_SM_VREF

AV42

SM_PW ROK

AR36

SM_REXT

BF17

DDR3_DRAMRST#

BC36

CLK_MCH_DREFCLK

B38

CLK_MCH_DREFCLK#

A38

MCH_SSCDREFCLK

E41

MCH_SSCDREFCLK #

F41

F43

E43

AE41

AE37

AE47

AH39

AE40

AE38

AE48

AH40

DMI_IRXN0_MTXN0

AE35

DMI_IRXN1_MTXN1

AE43

DMI_IRXN2_MTXN2

AE46

DMI_IRXN3_MTXN3

AH42

DMI_IRXP0_MTXP0

AD35

DMI_IRXP1_MTXP1

AE44

DMI_IRXP2_MTXP2

AF46

DMI_IRXP3_MTXP3

AH43

B33

B32

G33

F33

E33

C34

AH37

AH36

AN36

AJ35

MCH_CLVREF

AH34

CLK_MCH_3GPLL

CLK_MCH_3GPLL#

DMI_ITXN0_MRXN0

DMI_ITXN1_MRXN1

DMI_ITXN2_MRXN2

DMI_ITXN3_MRXN3

DMI_ITXP0_MRXP0

DMI_ITXP1_MRXP1

DMI_ITXP2_MRXP2

DMI_ITXP3_MRXP3

M

_CLK_DDR0 18

M

_CLK_DDR1 18

M

_CLK_DDR2 19

M

_CLK_DDR3 19

M

_CLK_DDR#0 18

M

_CLK_DDR#1 18

M

_CLK_DDR#2 19

_CLK_DDR#3 19

M

M

_CKE0 18

_CKE1 18

M

M

_CKE2 19

M

_CKE3 19

M_CS#0 18

M_CS#1 18

M_CS#2 19

M_CS#3 19

M_ODT0 18

M_ODT1 18

M_ODT2 19

M_ODT3 19

1 2

R1109

R1109

499R2F-2-GP

499R2F-2-GP

CLK_MCH_DREFCLK 7

CLK_MCH_DREFCLK# 7

MCH_SSCDREFCLK 7

MCH_SSCDREFCLK # 7

CLK_MCH_3GPLL 7

CLK_MCH_3GPLL# 7

DMI_ITXN0_MRXN0 21

DMI_ITXN1_MRXN1 21

DMI_ITXN2_MRXN2 21

DMI_ITXN3_MRXN3 21

DMI_ITXP0_MRXP0 21

DMI_ITXP1_MRXP1 21

DMI_ITXP2_MRXP2 21

DMI_ITXP3_MRXP3 21

DMI_IRXN0_MTXN0 21

DMI_IRXN1_MTXN1 21

DMI_IRXN2_MTXN2 21

DMI_IRXN3_MTXN3 21

DMI_IRXP0_MTXP0 2 1

DMI_IRXP1_MTXP1 2 1

DMI_IRXP2_MTXP2 2 1

DMI_IRXP3_MTXP3 2 1

CL_CLK0 22

CL_DATA0 22

M_PWR OK 22

CL_RST#0 22

MCH_CLVREF ~= 0.35V

CLKREQ#

ICH_SYNC#

TSATN#

HDA_BCLK

HDA_RST#

HDA_SDI

HDA_SDO

HDA_SYNC

3

N28

M28

MCH_HDMI_CLK

G36

MCH_HDMI_DATA

E36

K36

H36

TSATN#

B12

B28

B30

ICH_AZ_MCH_SDIN1_R

B29

C29

A28

-1_0511

CLKREQ#_B 7

MCH_ICH_SYNC# 22

12

HDMI

HDMI

-1_0527

HDA level shift for HDMI

DDPC_CTRLCLK

DDPC_CTRLDATA

SDVO_CTRLCLK

SDVO_CTRLDATA

12

R113633R2J-2-GP

R113633R2J-2-GP

2

R

R

80D6R2F-L-GP

80D6R2F-L-GP

R

R

80D6R2F-L-GP

80D6R2F-L-GP

DDR3_DRAMRST# 18,19

SM_PW ROK 41

12

DY

DY

C1105

C1105

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

+1.05V_VCCP

R1126

R1126

1KR2F-3-GP

1KR2F-3-GP

1 2

12

R1128

R1128

499R2F-2-GP

499R2F-2-GP

C1108

C1108

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

GMCH_HDA_BITCLK 57

GMCH_HDA_RST# 57

GMCH_HDA_SDIN1 57

GMCH_HDA_SDOU T 57

GMCH_HDA_SYNC 57

2

1

+

1.5V_SUS

1103

1103

1105

1105

12

12

DY

DY

12

TSATN#

SC2D2U6D3V3KX-GP

SC2D2U6D3V3KX-GP

SC2D2U6D3V3KX-GP

SC2D2U6D3V3KX-GP

C1106

C1106

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

CLKREQ#_B

12

S

M_RCOMP_VOH

M_RCOMP_VOL

S

1 2

10KR2J-3-GP

10KR2J-3-GP

R1122

R1122

56R2J-4-GP

56R2J-4-GP

C

C

1102

1102

C1104

C1104

R1129

R1129

+3.3V_RUN+1.05V_VCCP

B

DY

DY

+3.3V_RUN

HDMI

HDMI

1 2

0R0603-PAD

0R0603-PAD

DY

DY

4

1

12

SCD01U16V2KX-3GP

SCD01U16V2KX-3GP

12

SCD01U16V2KX-3GP

SCD01U16V2KX-3GP

+V_DDR_REF

R1108

R1108

+3.3V_RUN

12

R1123

R1123

10KR2J-3-GP

10KR2J-3-GP

TSATN#_KBC

C

Q1101

Q1101

MMBT3904W T1G-GP

MMBT3904W T1G-GP

E

RN1103

RN1103

SRN2K2J-1-GP

SRN2K2J-1-GP

2 3

MCH_HDMI_CLK 57

MCH_HDMI_DATA 57

1103

1103

C

C

C1101

C1101

-1_0511

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, H sin Tai Wu Rd., Hsic hih,

21F, 88, Sec.1, H sin Tai Wu Rd., Hsic hih,

21F, 88, Sec.1, H sin Tai Wu Rd., Hsic hih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Cantiga-DMI/CFG(2/6)

Cantiga-DMI/CFG(2/6)

Cantiga-DMI/CFG(2/6)

DJ2 Montevina UMA

DJ2 Montevina UMA

DJ2 Montevina UMA

Taipei Hsien 221, Taiwan, R.O.C.

1

12

12

11 88Wednesday, June 02, 2010

11 88Wednesday, June 02, 2010

11 88Wednesday, June 02, 2010

+

1.5V_SUS

R

R

1102

1102

1KR2F-3-GP

1KR2F-3-GP

1 2

12

R1104

R1104

3K01R2F-3-GP

3K01R2F-3-GP

R1106

R1106

1KR2F-3-GP

1KR2F-3-GP

1 2

TSATN#_KBC 37

X00

X00

X00

SID = MCH

S

5

4

3

2

1

M

M

_A_DQ[63..0]18

D D

C C

B B

_A_DQ[63..0]

M

_A_DQ0

M

_A_DQ1

M

_A_DQ2

M

_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

N

N

B1D

B1D

AJ38

S

A_DQ_0

AJ41

S

A_DQ_1

AN38

S

A_DQ_2

AM38

S

A_DQ_3

AJ36

SA_DQ_4

AJ40

SA_DQ_5

AM44

SA_DQ_6

AM42

SA_DQ_7

AN43

SA_DQ_8

AN44

SA_DQ_9

AU40

SA_DQ_1 0

AT38

SA_DQ_1 1

AN41

SA_DQ_1 2