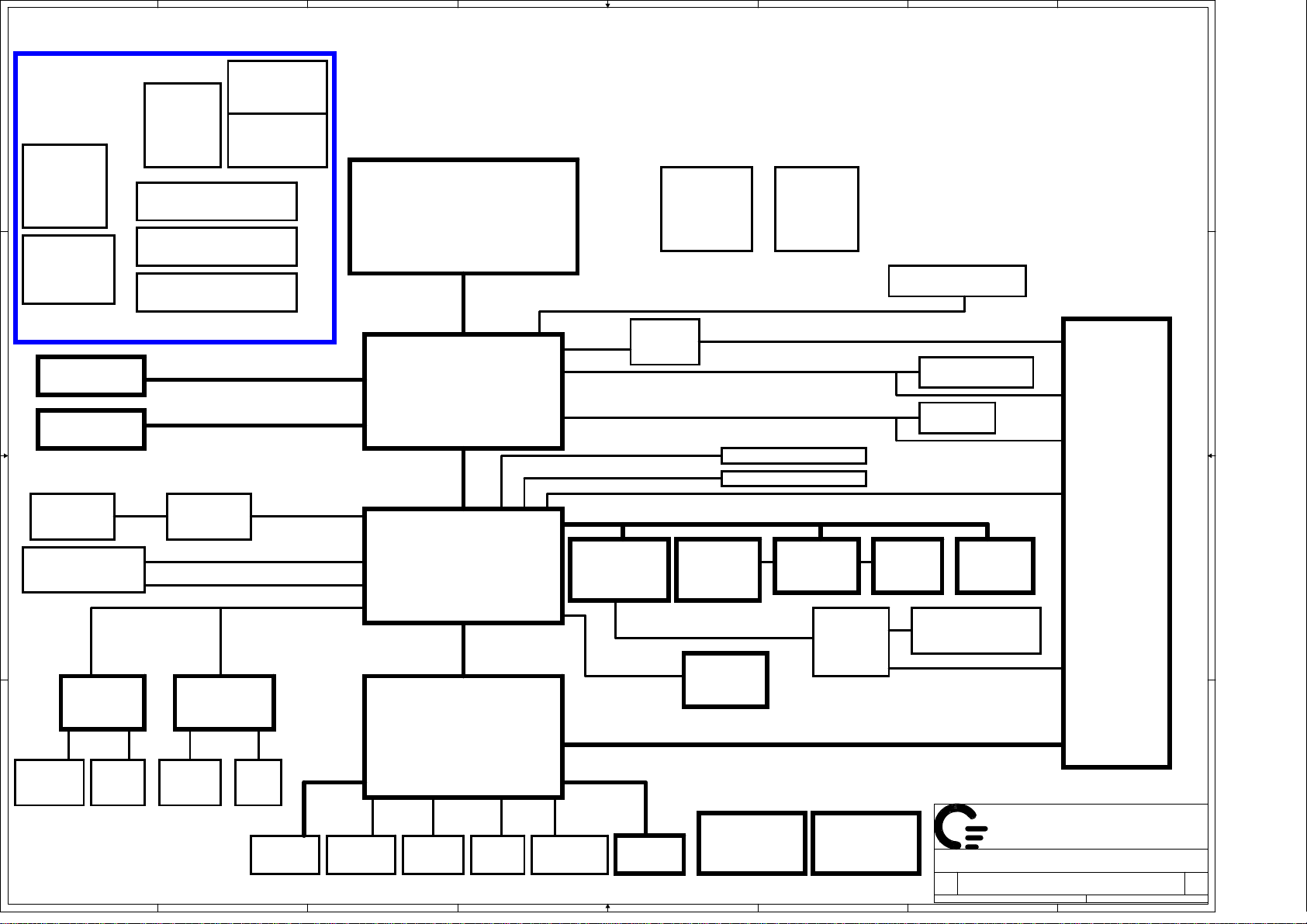

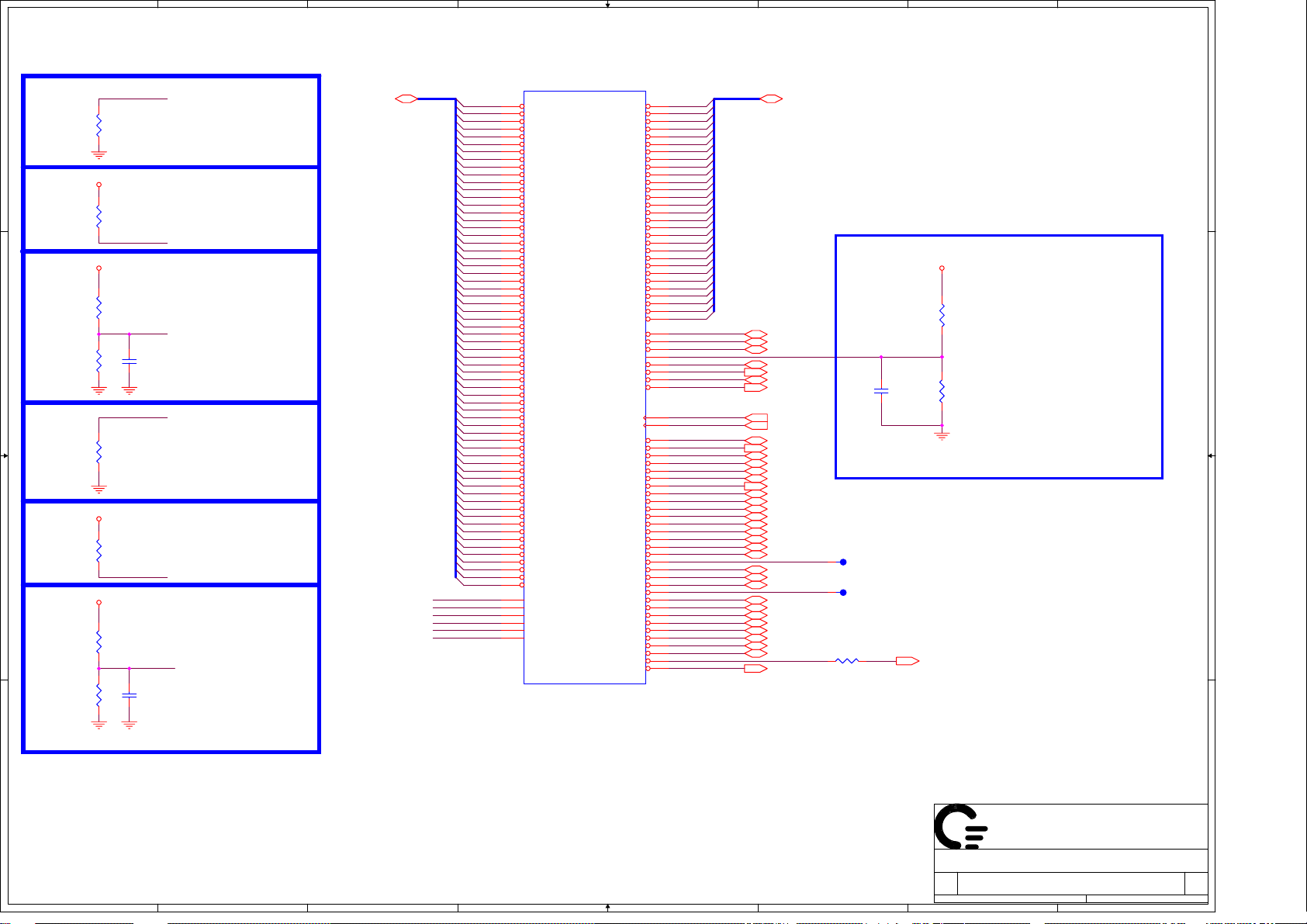

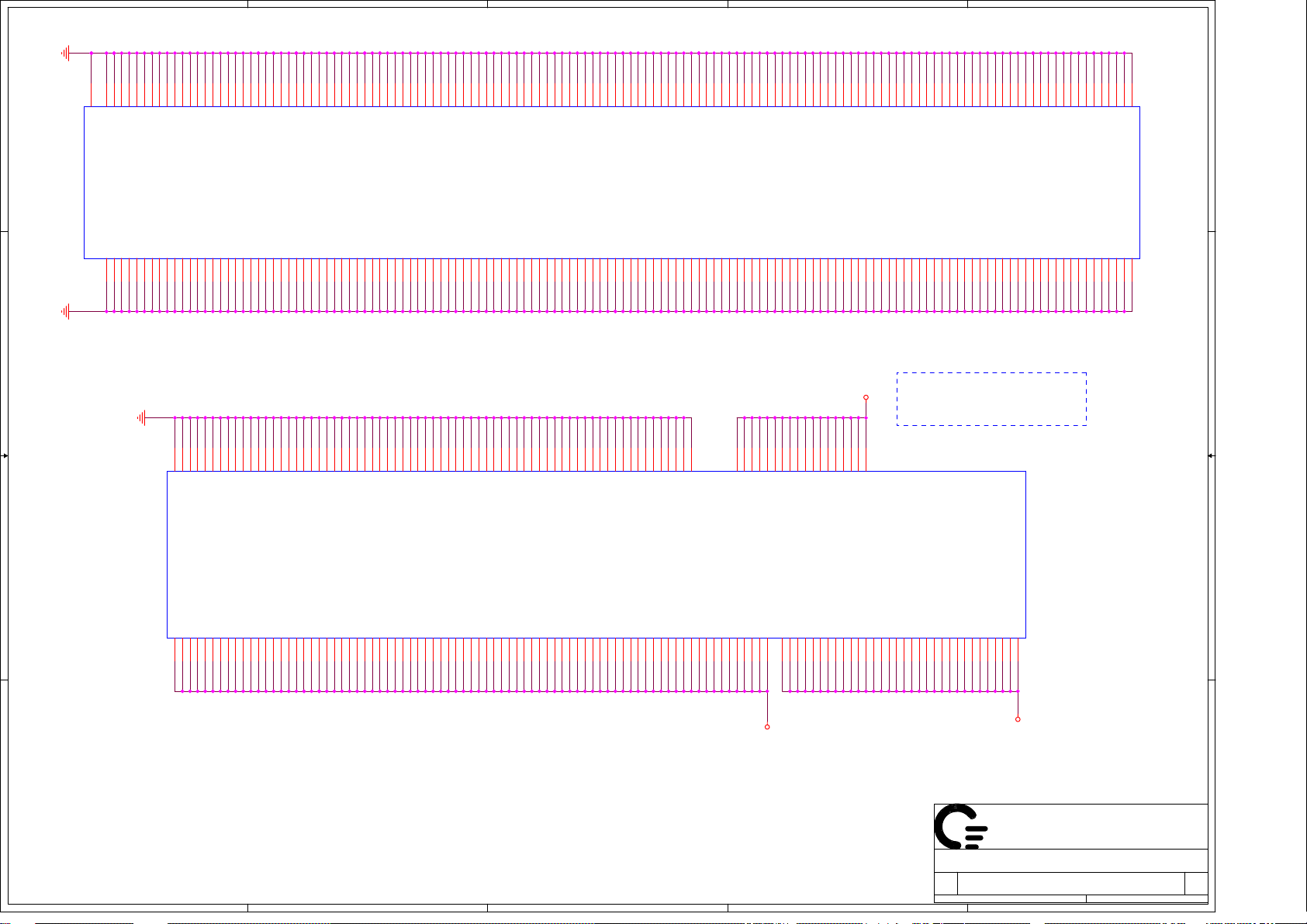

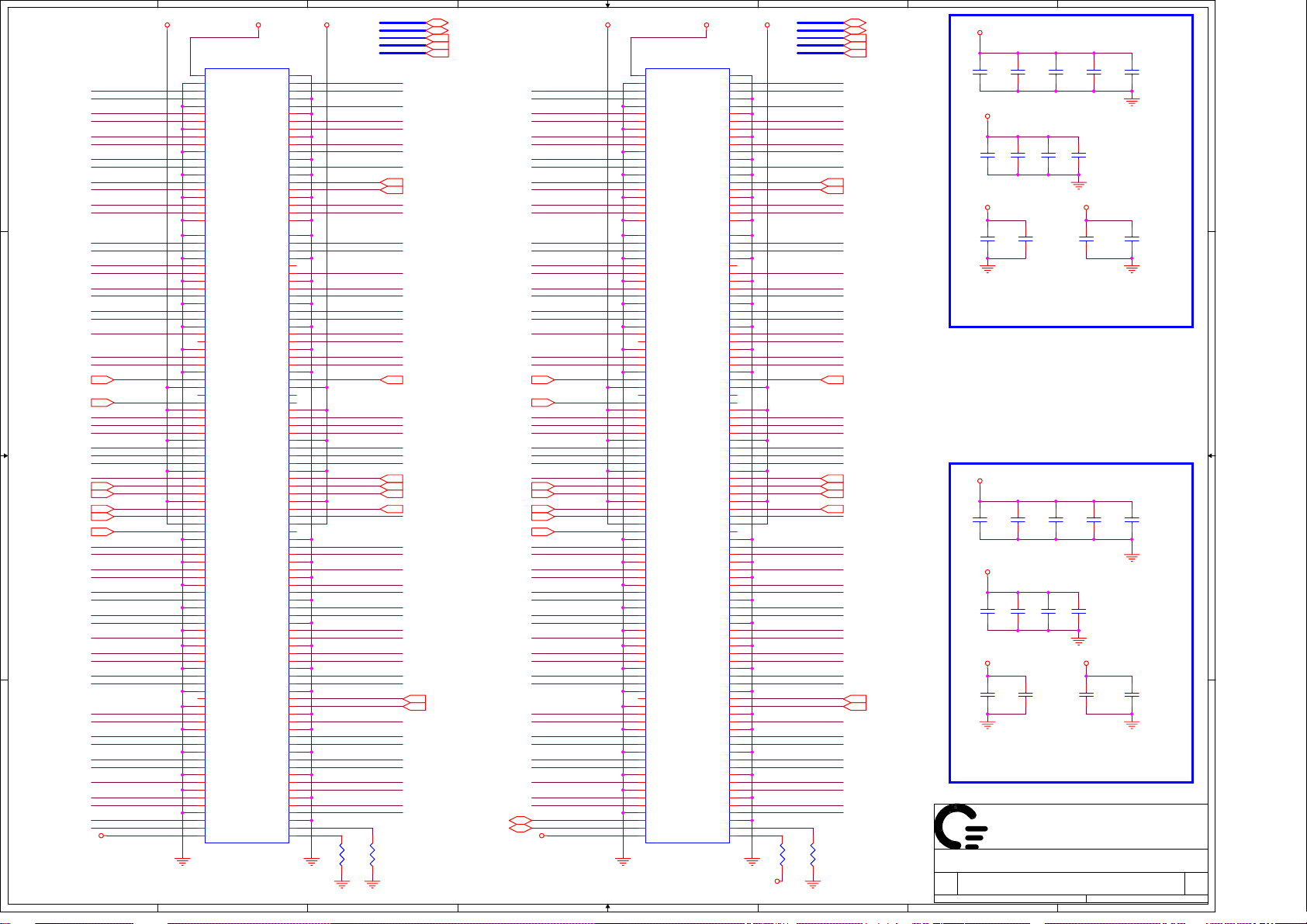

DELL D510, DM3D Schematics

1

2

3

4

5

6

7

8

DRAM Power

DC/DC

A A

+3V_SRC

+5VSUS

PG 45

CPU VR

AC/BATT

PG 42

RUN POWER

SW

PG 46

POWER DC/DC

B B

DDR2-SODIMM1

CONNECTOR

BATT

SELECTOR

BATT

CHARGER

400/533 MHZ DDR II

1.8V, 0.9V

PG 43

1.5VSUS, 1.05V

PG 44

PG 47

PG 40

PG 41

PG 13,14

400/533 MHZ DDR II

DDR2-SODIMM2

PG 13,14

PG 19

PATA

88SA8040

PG 19

USB2.0 1 port(P0)

PATA - HDD

PG 19

Internal Media Bay

C C

CD-ROM

SATA

ATA 66/100

AC97

RJ11 to

DOCK

PG 38

MDC

PG 24

Tip

Ring

PG 24

AUDIO

PG 31,32

S/PDIF to

DOCK

D D

PG 38

Audio

Jacks

PG 34

IrDA

PG 37

1

2

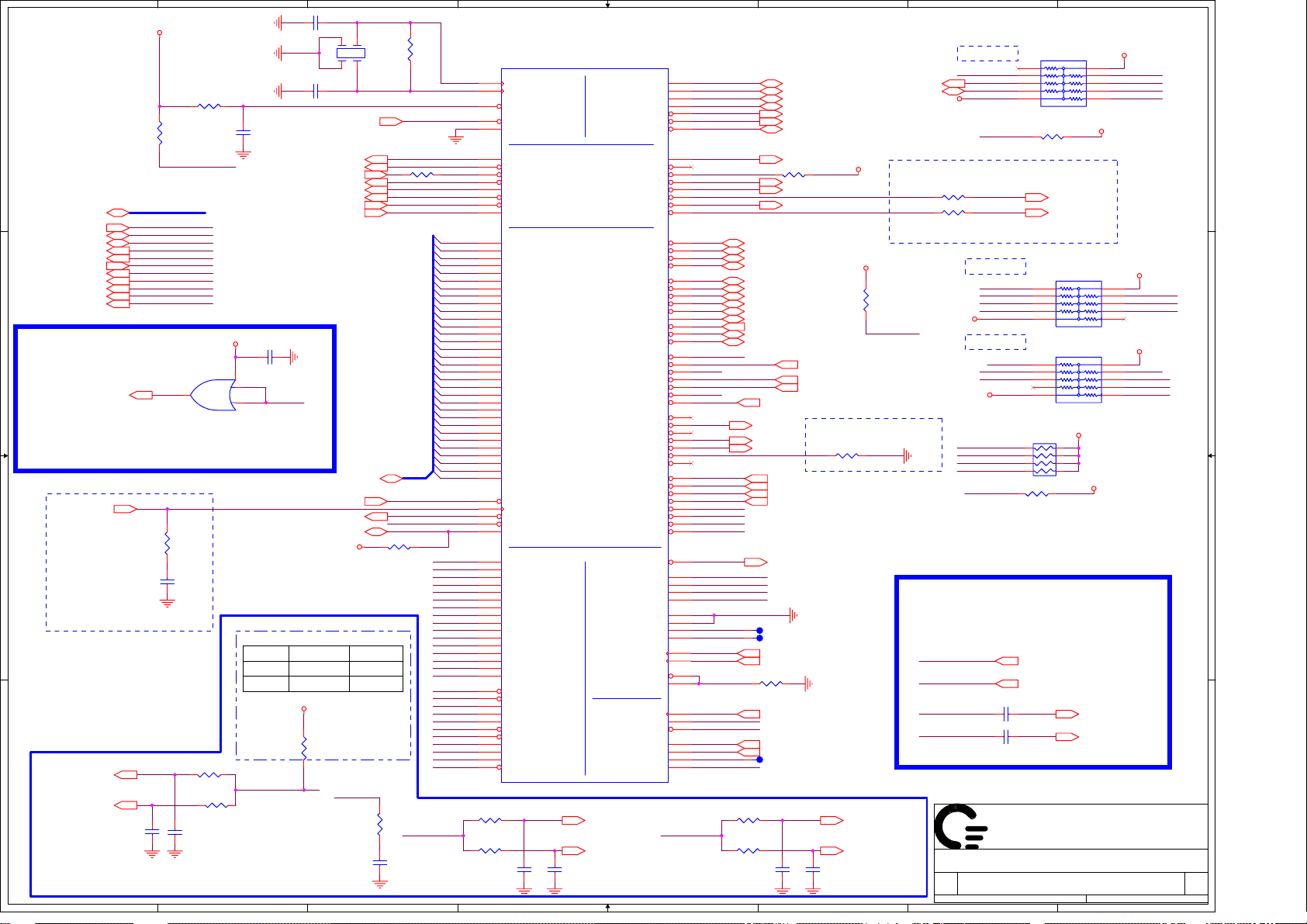

TAHITI-INTEGRATED

Keyboard

PG 26

Dothan

(478 Micro-FCPGA)

PG 3,4

Alviso-GM

1257 PCBGA

PG 5,6,7,8,9

DMI interface

ICH6-M

609 BGA

PG 10,11,12

LPC

LPC

SIO(Macallan 3)

256 Pins LBGA

PG 25,26

PG 27

3

4X133MHZ

ParallelSerial

PG 28

sDVO

USB2.0 (P5,P7)

USB2.0 (P4,P6)

USB2.0 (P1)

LAN (100/10)

BCM4401

PG 35

USB2.0 (P2)

X-Bus

PS/2

Touchpad

PG 30

4

SI1362

PG 16

Flash

PG 29

CLOCKS

PG 15

1394 CONN

PG 22

Bluetooth

PG 30

SWTICH & LED &

IO CONN

PG 32

5

SYSTEM

RESET CKT

LVDS

DVI

TVOUT

VGA

2 Rear Ports

2 right Side

33MHz PCI

CARDBUS

PCI4515

PG 21

PG 39

PG 32

PG 32

E-Switch

PI3L110Q

DOCK LPC

FAN & THERMAL

PG 31

PG 36

6

Panel Connector

PG 17

S-Video

PG 18

CRT

PG 18

PCMCIA

CON.

PG 21

MINI-PCI

Wireless LAN

I/O Board CONN

PG 32

Title

Schematic Block Diagram1

Size Document Number Rev

Tahiti 1A

Date: Sheet

星期二

PG 23

QUANTA

COMPUTER

29, 2005

三月

7

DOCKING

CONNECTOR

PG 38

of

149,

8

1

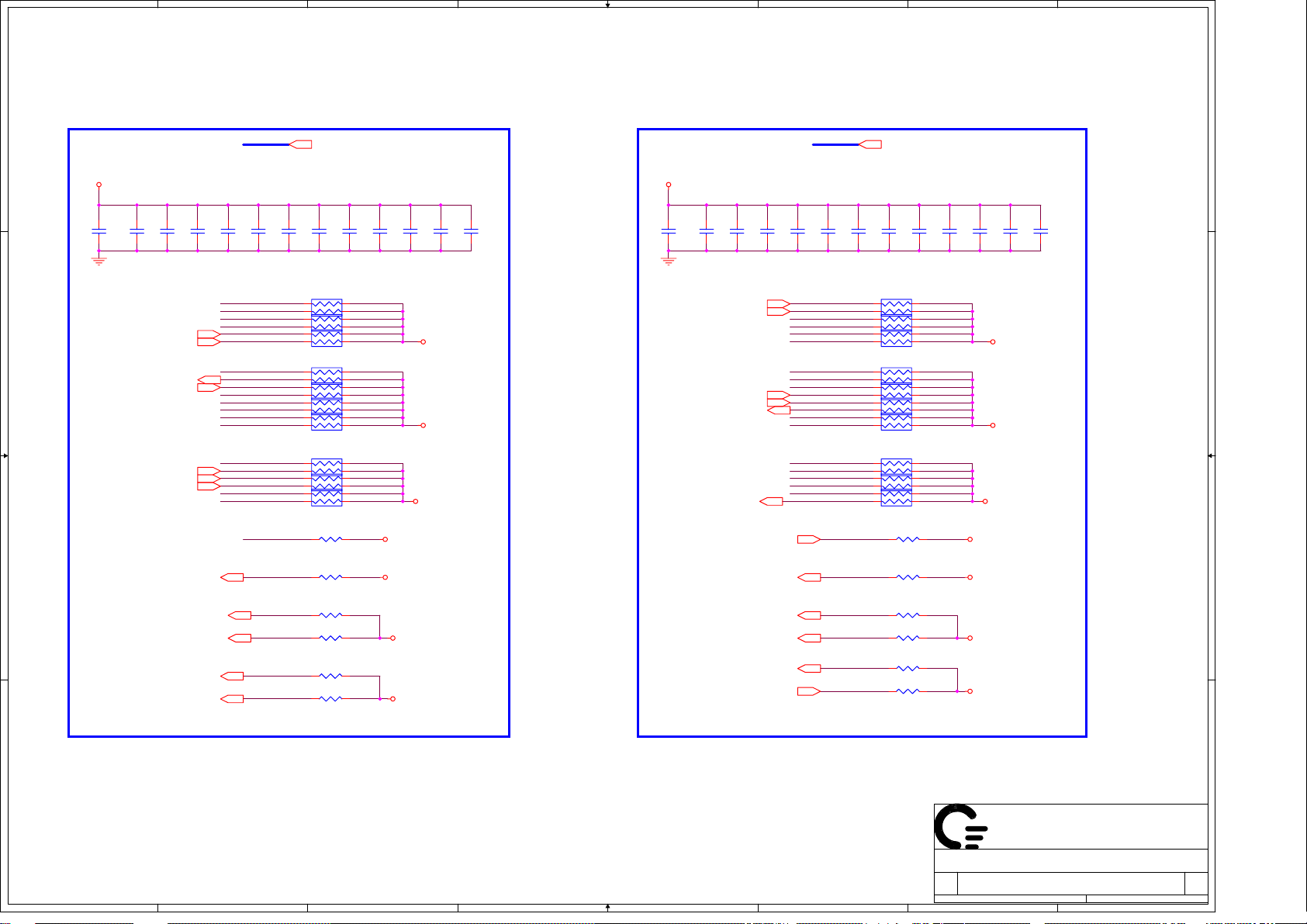

Pg# Description

1

Schematic Block Diagram 1

2

Front Page

3-4

A A

B B

C C

Dothan

5-9

Alviso

10-12

ICH6

13-14

DDRII SO-DIMM(200P)

15

Clock Generator

16

SI1362

17

LCD Conn. & SSP

18

CRT & TV Conn.

19

SATA & IDE Conn.

20

PAD & Screw Hole

21

TI PIC4510

22

CB/1394 CONN

23

Mini PCI Conn.

24

MDC Conn.

25-26

SIO (LPC47N354)

27 Parallel Port

28

Serial Port

29

Flash ROM

30

Touch Pad CONN.& Bluetooth CONN

31

Switch Board Conn. & LED & IO Board

FAN & Thermal

32

33-34

Audio CODEC (STAC9751) & Phone Jack

LAN Interface

35-36

37

FIR

38

MISCELLANEA

2

INDEX

3

DNI LIST

4

5

6

Power & Ground

Label Description

DC_IN+

PBATT+

PWR_SRC

VHCORE

1.05V AGTL+ POWER (1.05V) I/O

+3VRUN

+3VSUS

+5VALW

+5VRUN

+5VSUS

+5VHDD

+5VMOD

STRB#/5V

+5VRUN

VDDA

1_8VSUS

1_8VRUN

+3VALW 8051 POWER (3V)

V1_5RUN

GND ALL PAGES DIGIT AL GROUND

Pg#

AC ADAPTER (20V)

MAIN BATTERY + (10~17V)

MAIN POWER (10~20V)

CPU CORE POWER (1.25/1.15V)

SLP_S3# CTRLD POWER

SLP_S5# CTRLD POWER

8051 POWER (5V)

SLP_S3# CTRLD POWER

SLP_S5# CTRLD POWER

HDD POWER (5V)

MODULE POWER (5V)

EXTERNAL FDD POWER (5V)

FAN POWER (5V)

AUDIO ANALOG POWER (5V)

RESUME WELL IN ICH

SLP_S3# CTRLD POWER

ALVISO POWE R Non -CPU I/O

COMBO CONN GND

7

8

Control Signal

RUNPWROK

RUNPWROK

RUN_ON

SUS_ON

RUN_ON

SUS_ON

HDDC_EN#

MODC_EN#

FDD/LPT#

FAN_OFF/ON#

RUN_ON

39 Docking Conn.

40

SYSTEM RESET/POWER GOOD

41-42

Battery Selector & Charger

43

CPU Power

44

1.8VSUS/0.9V

D D

45

1.5V/1.05V

46

D/D Power

47

RUN Power Switch

48

RUN POWER SW

1

QUANTA

Title

Size Document Number Rev

2

3

4

5

6

Date: Sheet

COMPUTER

Index, DNI, Power & Ground

Tahiti(DM3L) 1A

星期二

29, 2005

三月

7

of

249,

8

1

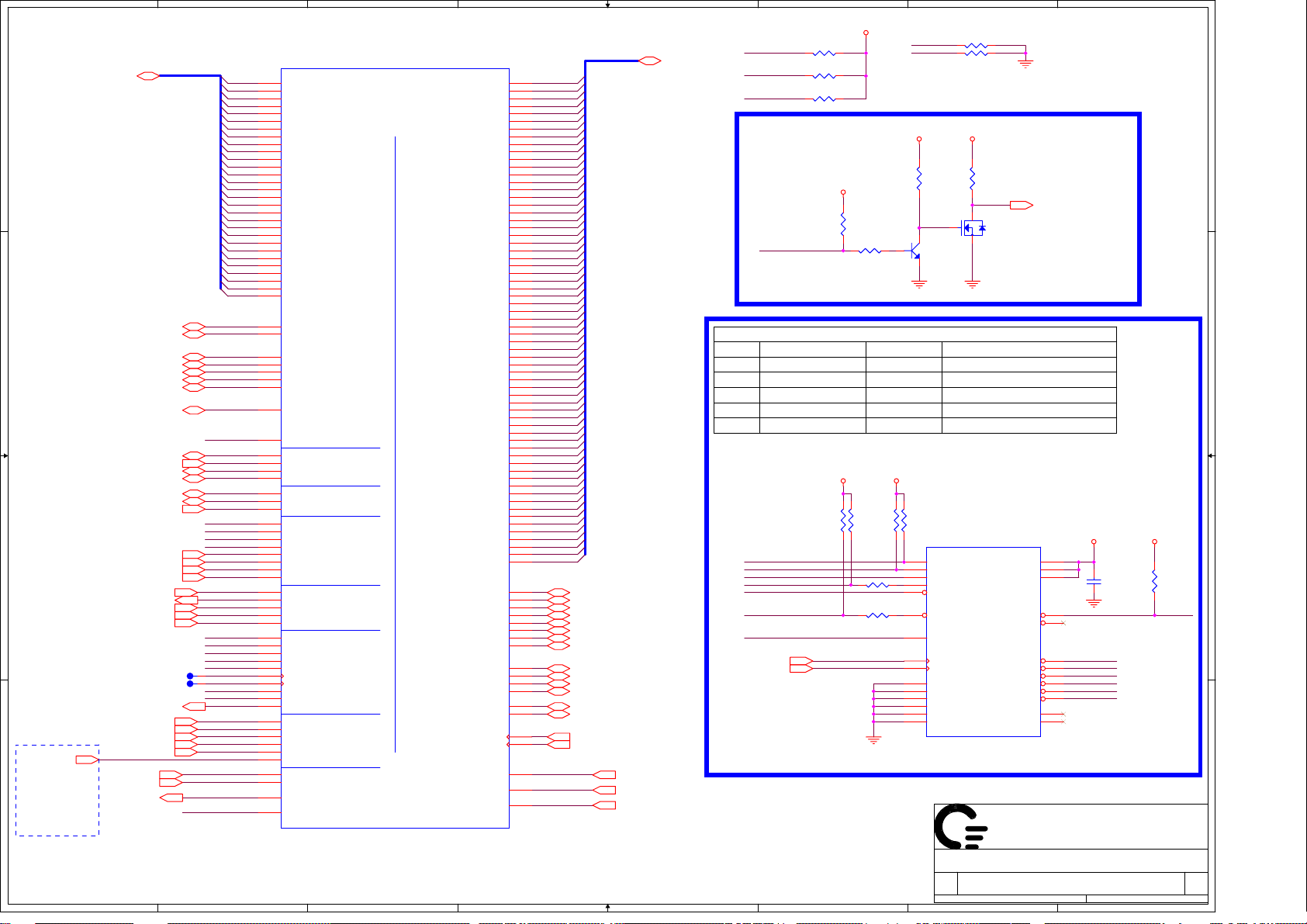

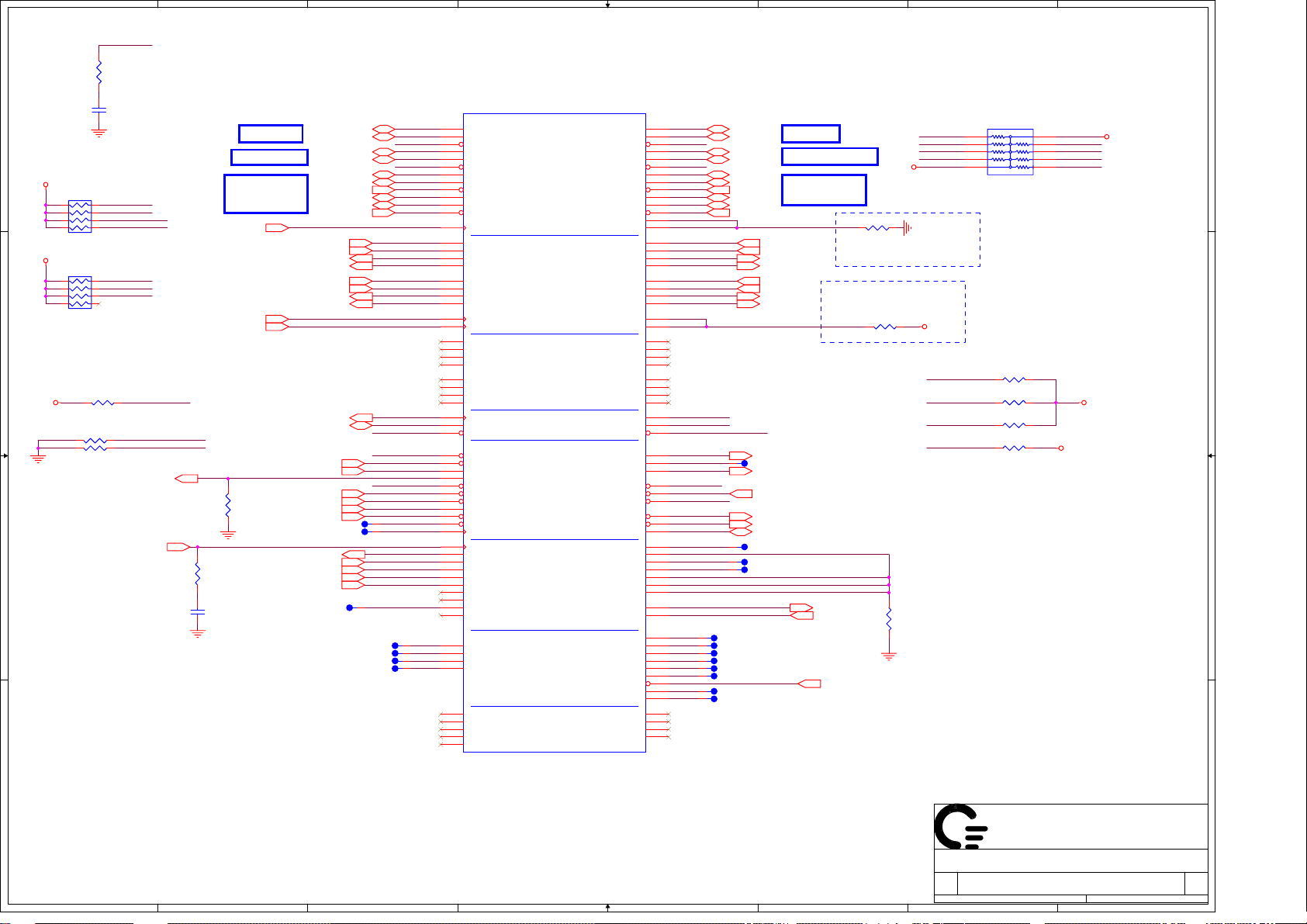

HADSTB0#5

HADSTB1#5

IGNNE#10

INTR10

NMI10

STPCLK#10

CPUSLP#5,10

DPSLP#10

HREQ#05

HREQ#15

HREQ#25

HREQ#35

HREQ#45

ADS#5

HBREQ0#5

BPRI#5

BNR#5

HLOCK#5

HIT#5

HITM#5

DEFER#5

HTRDY#5

RS#05

RS#15

RS#25

A20M#10

FERR#10

SMI#10

T11 PAD

T7 PAD

DBR#39

HA#[3..31]

HA#[3..31]5

A A

B B

C C

CPUPWRGD10

DPRSTP#10

G1: NC for

D D

Dothan and

DPRSTP# for

Yonah

THERMDA31

THERMDC31

THERMTRIP#31

1

2

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

IERR#

BPM0#

BPM1#

BPM2#

BPM3#

A20M#

FERR#

IGNNE#

CPUPWRGD

SMI#

TCK

TDO

TDI

TMS

TRST#

PREQ#

PRDY#

DBR#

STPCLK#

CPUSLP#

DPSLP#

THERMDA

THERMDC

THERMTRIP#

CPU_PROCHOT#

2

AA3

AA2

AF4

AC4

AC7

AC3

AD3

AE4

AD2

AB4

AC6

AD5

AE2

AD6

AF3

AE1

AF1

AE5

A13

A12

C12

C11

B13

A16

A15

B10

A10

B18

A18

C17

B17

P4

U4

V3

R3

V2

W1

T4

W2

Y4

Y1

U1

Y3

U3

R2

P3

T2

P1

T1

N2

A4

N4

J3

L1

J2

K3

K4

L4

C8

B8

A9

C9

M3

H1

K1

L2

C2

D3

A3

E4

B4

A7

D1

D4

C6

A6

B7

G1

U7A

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

ADSTB0#

ADSTB1#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

ADS#

IERR#

BREQ0#

BPRI#

BNR#

LOCK#

HIT#

HITM#

DEFER#

BPM0#

BPM1#

BPM2#

BPM3#

TRDY#

RS0#

RS1#

RS2#

A20M#

FERR#

IGNNE#

PWRGOOD

SMI#

TCK

TDO

TDI

TMS

TRST#

ITP_CLK0

ITP_CLK1

PREQ#

PRDY#

DBR#

LINT0

LINT1

STPCLK#

SLP#

DPSLP#

DPRSTP#

THERMDA

THERMDC

THERMTRIP#

PROCHOT#

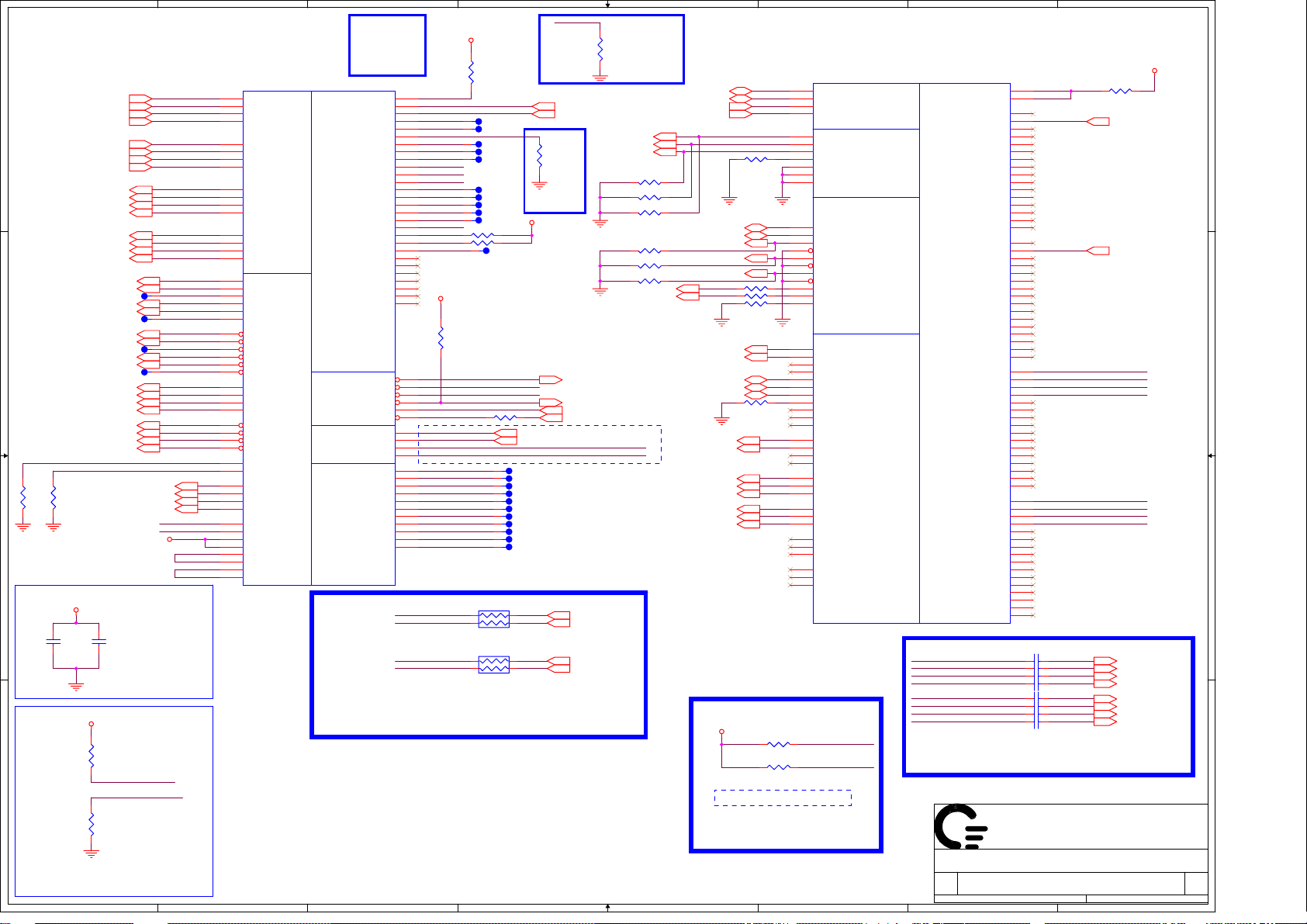

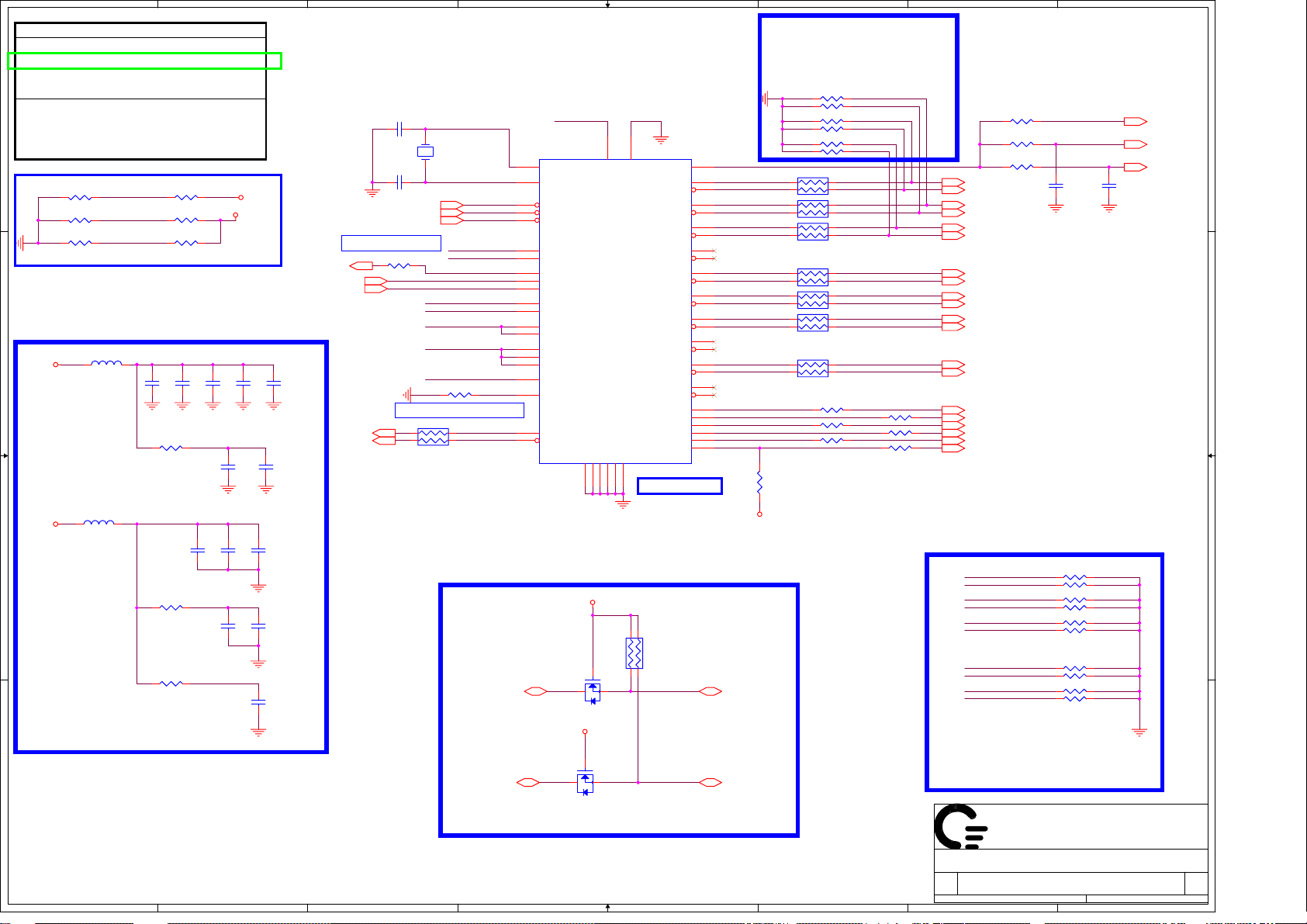

Dothan Processor

Dothan

REQUEST

PHASE

SIGNALS

ERROR

SIGNALS

ARBITRATION

PHASE

SIGNALS

SNOOP PHASE

SIGNALS

RESPONSE

PHASE

SIGNALS

PC

COMPATIBILITY

SIGNALS

DIAGNOSTIC

& TEST

SIGNALS

EXECUTION

CONTROL

SIGNALS

THERMAL DIODE

3

1 OF 3

3

DATA

PHASE

SIGNALS

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DSTBN0#

DSTBP0#

DSTBN1#

DSTBP1#

DSTBN2#

DSTBP2#

DSTBN3#

DSTBP3#

DINV0#

DINV1#

DINV2#

DINV3#

DBSY#

DRDY#

BCLK1

BCLK0

INIT#

RESET#

DPWR#

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

A19

A25

A22

B21

A24

B26

A21

B20

C20

B24

D24

E24

C26

B23

E23

C25

H23

G25

L23

M26

H24

F25

G24

J23

M23

J25

L26

N24

M25

H26

N25

K25

Y26

AA24

T25

U23

V23

R24

R26

R23

AA23

U26

V24

U25

V26

Y23

AA26

Y25

AB25

AC23

AB24

AC20

AC22

AC25

AD23

AE22

AF23

AD24

AF20

AE21

AD21

AF25

AF22

AF26

C23

C22

K24

L24

W25

W24

AE24

AE25

D25

J26

T24

AD20

M2

H2

B14

B15

B5

B11

C19

4

CPUINIT#

CPURST#

4

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HD#[0..63]

HDSTBN0# 5

HDSTBP0# 5

HDSTBN1# 5

HDSTBP1# 5

HDSTBN2# 5

HDSTBP2# 5

HDSTBN3# 5

HDSTBP3# 5

HDBI0# 5

HDBI1# 5

HDBI2# 5

HDBI3# 5

DBSY# 5

DRDY# 5

HCLK_CPU# 15

HCLK_CPU 15

CPUINIT# 10

CPURST# 5

DPWR# 5

5

HD#[0..63] 5

5

6

VCCP

THERMTRIP#

IERR#

CPUPWRGD

R25 56

1 2

R30 56

1 2

R31 200

1 2

CPU_PROCHOT#

VCCP

12

R24

56

R23

*330_NC

Thermal Level Shift

ITP disable guidelines

Signal

TDI

TMS

TRST#

TDO

Resistor Value

150 ohm +/- 5%

39 ohm +/- 5% VTT

680 ohm +/- 5% GND

27 ohm +/- 5%TCK

Open

Note: Populate All NC component when

ITP connector is populated.

R236

54.9/F

TDI

TMS

TCK

TDO

TRST#

CPURST#

TCK

HCLK_ITP#15

HCLK_ITP15

Connect To Resistor Placement

VCCP VCCP

12

12

R239

R238

39.2/F

54.9/F

1 2

R237 *22.6/F_NC

1 2

R235 *22.6/F_NC

ITP DEBUG PORT

6

TCK

TRST#

+3VRUN +3VALW

R22

*1.5K_NC

1 2

Q11

12

2

*3904_NC

1 3

VTT

GND

VTT

12

12

R240

150

JITP2

1

TDI

2

TMS

5

TCK

7

TDO

3

TRST#

12

RESET#

11

FBO

8

BCLKN

9

BCLKP

10

GND0

14

GND1

16

GND2

18

GND3

20

GND4

22

GND5

*ITP700_NC

Title

Size Document Number Rev

Date: Sheet

R29 27.4/F

1 2

1 2

R28 680

2

7

R34

*330_NC

1 2

31

Q12

*RHU002N06_NC

PROCHOT# 26

8

Within 2.0" of the CPU

Within 2.0" of the CPU

Within 2.0" of the CPU

Within 2.0" of the CPU

Within 2.0" of the CPU

VTT0

VTT1

VTAP

DBR#

DBA#

BPM0#

BPM1#

BPM2#

BPM3#

BPM4#

BPM5#

NC0

NC1

VCCP

27

28

26

25

24

BPM0#

23

BPM1#

21

BPM2#

19

BPM3#

17

PRDY#

15

PREQ#

13

4

6

C359

*.1U_10V_NC

1 2

DBR#

+3VSUS

12

QUANTA

COMPUTER

Dothan Processor (HOST)

Tahiti(DM3L) 1A

星期二

29, 2005

三月

7

of

349,

8

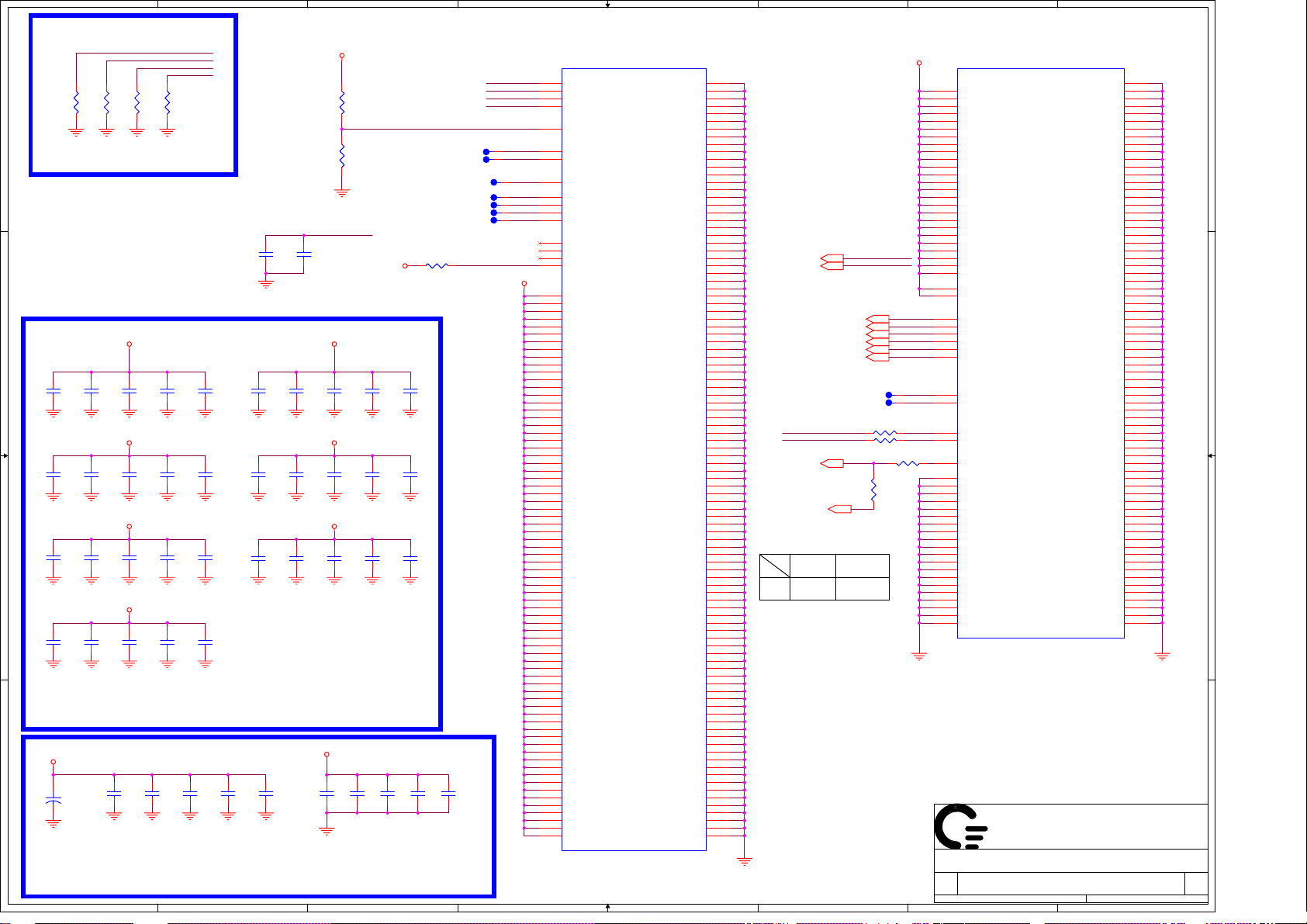

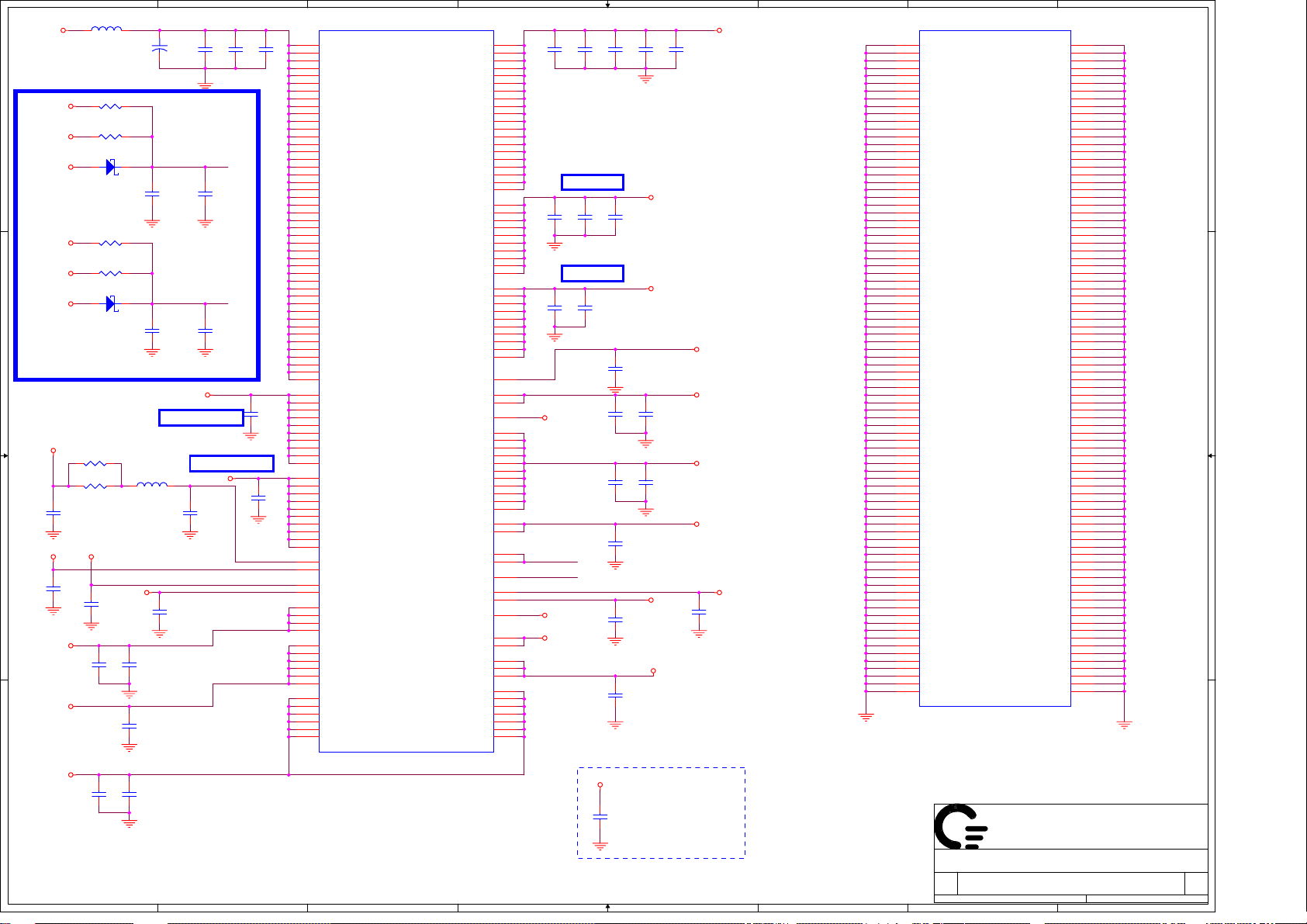

R234

150

1

2

3

4

5

6

7

8

COMP0

COMP1

COMP2

COMP3

R20

R19

R211

1 2

12

C334

10U_4V

12

C310

10U_4V

12

C278

10U_4V

C303

10U_4V

1 2

27.4/F

R212

54.9/F

1 2

12

C290

10U_4V

12

C307

10U_4V

12

C283

10U_4V

C282

10U_4V

1 2

12

C286

10U_4V

12

C329

10U_4V

12

C336

10U_4V

C305

10U_4V

1 2

12

.01U

12

C31

10U_4V

12

C335

10U_4V

C332

10U_4V

1 2

C42

27.4/F

54.9/F

1 2

C328

C280

C291

C279

12

C287

10U_4V

12

C34

10U_4V

12

C309

10U_4V

C331

10U_4V

1 2

1 2

VHCORE

VHCORE

VHCORE

A A

18mils Trace Width of COMP0,2

5mils Trace Width of COMP1,3

B B

12

10U_4V

12

10U_4V

12

C C

10U_4V

10U_4V

1 2

VHCORE

Total caps = 1670 uF > 1430 uF (Intel Recommendation)

ESR = 9m ohm/4 // 5m ohm/35 ---> = 0.1343m ohm

VCCP

C43

150U/6.3V

1

12

C314

.1U_10V

12

C322

.1U_10V

12

C315

.1U_10V

2

12

C321

.1U_10V

12

C325

.1U_10V

C, mF---------ESR, mW-----------ESL, nH

1 x 150 mF-----42 mW (typ) / 2--------2.5 nH / 12

10 x 0.1 mF----16 mW (typ) / 10-------0.6 nH / 10

D D

12

+

12

10U_4V

12

C302

10U_4V

12

C26

10U_4V

C330

10U_4V

1 2

VCCP

Z0 = 55 ohm, 25 mils

spacing for switching

R16

signals

1K/F

1 2

R15

2K/F

1 2

CPU_VCCA

C41

+1_5VRUN

VHCORE

12

12

C288

10U_4V

10U_4V

VHCORE

12

12

C285

10U_4V

10U_4V

VHCOREVHCORE

C289

10U_4V

10U_4V

1 2

1 2

VCCP

12

12

C313

C317

.1U_10V

.1U_10V

C284

C333

C304

3

12

C316

.1U_10V

R21 0_0603

12

C281

10U_4V

12

C308

10U_4V

C306

10U_4V

1 2

12

C323

.1U_10V

T9 PAD

T47 PAD

T10 PAD

T8 PAD

T2 PAD

T5 PAD

T6 PAD

12

12

C324

.1U_10V

COMP0

COMP1

COMP2

COMP3

GTLREF0

TEST1

TEST2

VHCORE

P25

P26

AB2

AB1

AD26

C5

F23

B2

C3

AF7

AC1

E26

AC26

N1

B1

F26

D18

D20

D22

E17

E19

E21

F18

F20

F22

G5

G21

H6

H22

J21

K22

U5

V6

V22

W5

W21

Y22

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AB6

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC9

AC11

AC13

AC15

AC17

AC19

AD8

AD10

AD12

AD14

AD16

AD18

AE9

AE11

AE13

AE15

AE17

AE19

AF8

AF10

AF12

AF14

AF16

AF18

4

U7B

COMP0

COMP1

COMP2

COMP3

GTLREF0

TEST1

TEST2

NC1

RSVD2

RSVD3

RSVD4

RSVD5

VCCA3

VCCA2

VCCA1

VCCA0

D6

VCC00

D8

VCC01

VCC02

VCC03

VCC04

E5

VCC05

E7

VCC06

E9

VCC07

VCC08

VCC09

VCC10

F6

VCC11

F8

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

J5

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

Y6

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

Dothan Processor

Dothan

2 OF 3

POWER,

GROUND,

RESERVED

SIGNALS

VSS00

VSS01

VSS02

VSS03

VSS04

VSS05

VSS06

VSS07

VSS08

VSS09

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

5

A2

A5

A8

A11

A14

A17

A20

A23

A26

B3

B6

B9

B12

B16

B19

B22

B25

C1

C4

C7

C10

C13

C15

C18

C21

C24

D2

D5

D7

D9

D11

D13

D15

D17

D19

D21

D23

D26

E3

E6

E8

E10

E12

E14

E16

E18

E20

E22

E25

F1

F4

F5

F7

F9

F11

F13

F15

F17

F19

F21

F24

G2

G6

G22

G23

G26

H3

H5

H21

H25

J1

J4

J6

J22

J24

K2

K5

K21

K23

K26

L3

L6

L22

L25

M1

M4

M5

M21

M24

N3

N6

N22

N23

N26

P2

P5

P21

P24

R1

R4

SELPSB2_CLK6,15

SELPSB1_CLK6,15

CPU_VID042

CPU_VID142

CPU_VID242

CPU_VID342

CPU_VID442

CPU_VID542

Differential Probe

Test Using

SELPSB2_CLK

SELPSB1_CLK

PSI

STP_CPU#11,15,42

NO PSI (Power Saving

Indicator )

DothanA

R26 Install

NC

6

SELPSB2_CLK

SELPSB1_CLKCPU_VCCA

T3 PA D

T4 PA D

R26

1 2

1 2

R27 0

R32 *0_NC

R33

*0_NC

1 2

DothanB

0

VCCP

BSEL0

BSEL1

12

D10

VCCP0

D12

VCCP1

D14

VCCP2

D16

VCCP3

E11

VCCP4

E13

VCCP5

E15

VCCP6

F10

VCCP7

F12

VCCP8

F14

VCCP9

F16

VCCP10

K6

VCCP11

L5

VCCP12

L21

VCCP13

M6

VCCP14

M22

VCCP15

N5

VCCP16

N21

VCCP17

P6

VCCP18

P22

VCCP19

R5

VCCP20

R21

VCCP21

T6

VCCP22

T22

VCCP23

U21

VCCP24

P23

VCCQ0

W4

VCCQ1

E2

VID0

F2

VID1

F3

VID2

G3

VID3

G4

VID4

H4

VID5

AE7

VCCSENSE

AF6

VSSSENSE

C16

BSEL0

C14

BSEL1

E1

PSI

R6

VSS100

R22

VSS101

R25

VSS102

T3

VSS103

T5

VSS104

T21

VSS105

T23

VSS106

T26

VSS107

U2

VSS108

U6

VSS109

U22

VSS110

U24

VSS111

V1

VSS112

V4

VSS113

V5

VSS114

V21

VSS115

V25

VSS116

W3

VSS117

W6

VSS118

W22

VSS119

Dothan Processor

U7C

Dothan

3 OF 3

POWER, GROUND AND NC

VID

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

QUANTA

Title

Size Document Number Rev

Date: Sheet

COMPUTER

Dothan Processor (POWER)

Tahiti(DM3L) 1A

星期二

29, 2005

三月

7

W23

W26

Y2

Y5

Y21

Y24

AA1

AA4

AA6

AA8

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AA25

AB3

AB5

AB7

AB9

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AB26

AC2

AC5

AC8

AC10

AC12

AC14

AC16

AC18

AC21

AC24

AD1

AD4

AD7

AD9

AD11

AD13

AD15

AD17

AD19

AD22

AD25

AE3

AE6

AE8

AE10

AE12

AE14

AE16

AE18

AE20

AE23

AE26

AF2

AF5

AF9

AF11

AF13

AF15

AF17

AF19

AF21

AF24

of

449,

8

1

2

3

4

5

6

7

8

HXRCOMP

12

R50

100/F

R56

100/F

VCCP

VCCP

VCCP

VCCP

12

12

12

12

12

12

12

R44

24.9/F

R43

54.9/F

HXSCOMP

R48

221/F

HXSWING

.1U_10V

1 2

HYRCOMP

R63

24.9/F

R51

54.9/F

HYSCOMP

R53

221/F

HYSWING

.1U_10V

1 2

C72

C82

A A

B B

C C

One pulled-down

resistor per pin.

Trace should be

10-mil wide with

20-mil spacing.

Signal voltage

level =

0.3125*VCCP.

C1a=0.1 µF. C1b=0.1

µF.Trace should be

10-mil wide with

20-mil spacing..

One pulled-down

resistor per pin.

Trace should be

10-mil wide with

20-mil spacing.

Signal voltage

level =

0.3125*VCCP.

C1a=0.1 µF. C1b=0.1

µF.Trace should be

10-mil wide with

20-mil spacing..

HD#[0..63]3

HD#[0..63]

HXRCOMP

HXSCOMP

HXSWING

HYRCOMP

HYSCOMP

HYSWING

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

E4

E1

F4

H7

E2

F1

E3

D3

K7

F2

J7

J8

H6

F3

K8

H5

H1

H2

K5

K6

J4

G3

H3

J1

L5

K4

J5

P7

L7

J3

P5

L3

U7

V6

R6

R5

P3

T8

R7

R8

U8

R4

T4

T5

R1

T3

V8

U6

W6

U3

V5

W8

W7

U2

U1

Y5

Y2

V4

Y7

W1

W3

Y3

Y6

W2

C1

C2

D1

T1

L1

P1

U11A

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

HXRCOMP

HXSCOMP

HXSWING

HYRCOMP

HYSCOMP

HYSWING

ALVISO

HOST

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HADS#

HADSTB0#

HADSTB1#

HVREF

HBNR#

HBPRI#

BREQ0#

HCPURST#

HCLKINN

HCLKINP

HDBSY#

HDEFER#

HDINV#0

HDINV#1

HDINV#2

HDINV#3

HDPWR#

HDRDY#

HDSTBN0#

HDSTBN1#

HDSTBN2#

HDSTBN3#

HDSTBP0#

HDSTBP1#

HDSTBP2#

HDSTBP3#

HEDRDY#

HHIT#

HHITM#

HLOCK#

HPCREQ#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HRS0#

HRS1#

HRS2#

HCPUSLP#

HTRDY#

G9

C9

E9

B7

A10

F9

D8

B10

E10

G10

D9

E11

F10

G11

G13

C10

C11

D11

C12

B13

A12

F12

G12

E12

C13

B11

D13

A13

F13

F8

B9

E13

J11

A5

D5

E7

H10

AB1

AB2

C6

E6

H8

K3

T7

U5

G6

F7

G4

K1

R3

V3

G5

K2

R2

W4

F6

D4

D6

B3

A11

A7

D7

B8

C7

A8

A4

C5

B4

G8

B5

HA#[3..31]

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HCPUSLP#_GMCH

HA#[3..31] 3

ADS# 3

HADSTB0# 3

HADSTB1# 3

BNR# 3

BPRI# 3

HBREQ0# 3

CPURST# 3

HCLK_MCH# 15

HCLK_MCH 15

DBSY# 3

DEFER# 3

HDBI0# 3

HDBI1# 3

HDBI2# 3

HDBI3# 3

DPWR# 3

DRDY# 3

HDSTBN0# 3

HDSTBN1# 3

HDSTBN2# 3

HDSTBN3# 3

HDSTBP0# 3

HDSTBP1# 3

HDSTBP2# 3

HDSTBP3# 3

HIT# 3

HITM# 3

HLOCK# 3

HREQ#0 3

HREQ#1 3

HREQ#2 3

HREQ#3 3

HREQ#4 3

RS#0 3

RS#1 3

RS#2 3

HTRDY# 3

VCCP

R284

100/F

1 2

Signal voltage level = 2/3 of

VCCP. One 0.1 µF decoupling

capacitor should be placed 100

12

mils or less from GMCH pin.

R276

200/F

12

C381

.1U_10V

HVREF

Concern about HVREF

Trace Length & Width

T77

PAD

T15

PAD

R37

1 2

0

CPUSLP# 3,10

Do not install R37 for Dothan-A and

install for Dothan-B

Concern about Trace Length and Width

D D

QUANTA

Title

Size Document Number Rev

1

2

3

4

5

6

Date: Sheet

COMPUTER

Alviso (Host)

Tahiti(DM3L) 1A

星期二

29, 2005

三月

7

of

549,

8

1

DMI_TXN011

DMI_TXN111

DMI_TXN211

CLK_SDRAM0#13

CLK_SDRAM1#13

CLK_SDRAM3#13

CLK_SDRAM4#13

12

R315

*40.2/F_NC

SMDDR_VREF

12

C714

.1U_10V

+1_8VSUS

1

DMI_TXN311

DMI_TXP011

DMI_TXP111

DMI_TXP211

DMI_TXP311

DMI_RXN011

DMI_RXN111

DMI_RXN211

DMI_RXN311

DMI_RXP011

DMI_RXP111

DMI_RXP211

DMI_RXP311

CLK_SDRAM013

CLK_SDRAM113

PAD

T94

CLK_SDRAM313

CLK_SDRAM413

T89PAD

T90PAD

PAD

T91

CKE013,14

CKE113,14

CKE213,14

CKE313,14

SM_CS0#13,14

SM_CS1#13,14

SM_CS2#13,14

SM_CS3#13,14

SMDDR_VREF

12

C715

.1U_10V

Place these 2 Caps near

Alviso SMVREF pins.

12

R326

80.6/F

M_RCOMPN

M_RCOMPP

12

R318

80.6/F

M_OCDCOMP0

M_OCDCOMP1

M_ODT013,14

M_ODT113,14

M_ODT213,14

M_ODT313,14

CLK_SDRAM2

CLK_SDRAM5

CLK_SDRAM2#

CLK_SDRAM5#

CKE0

CKE1

CKE2

CKE3

SM_CS0#

SM_CS1#

SM_CS2#

SM_CS3#

M_RCOMPN

M_RCOMPP

SMXSLEW

SMYSLEW

A A

B B

12

R314

*40.2/F_NC

C C

D D

On-Die OCD driver

compensation (DDR2 only)

AA31

AB35

AC31

AD35

AA35

AB31

AC35

AA33

AB37

AC33

AD37

AA37

AB33

AC37

AM33

AE11

AJ34

AC10

AN33

AE10

AJ33

AD10

AP21

AM21

AH21

AK21

AN16

AM14

AH15

AG16

AF22

AF16

AP14

AL15

AM11

AN10

AK10

AK11

AF37

AD1

AE27

AE28

AF9

AF10

2

Y31

Y33

AL1

AF6

AK1

AF5

2

U11C

DMIRXN0

DMIRXN1

DMIRXN2

DMIRXN3

DMIRXP0

DMIRXP1

DMIRXP2

DMIRXP3

DMITXN0

DMITXN1

DMITXN2

DMITXN3

DMITXP0

DMITXP1

DMITXP2

DMITXP3

SM_CK0

SM_CK1

SM_CK2

SM_CK3

SM_CK4

SM_CK5

SM_CK0#

SM_CK1#

SM_CK2#

SM_CK3#

SM_CK4#

SM_CK5#

SM_CKE0

SM_CKE1

SM_CKE2

SM_CKE3

SM_CS0#

SM_CS1#

SM_CS2#

SM_CS3#

SM_OCDCOMP0

SM_OCDCOMP1

SM_ODT0

SM_ODT1

SM_ODT2

SM_ODT3

SMRCOMPN

SMRCOMPP

SMVREF0

SMVREF1

SMXSLEWIN

SMXSLEWOUT

SMYSLEWIN

SMYSLEWOUT

ALVISO

CFG[2:0]

001=FSB533

010=FSB800

101=FSB400

DMIDDR MUXING

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

CFG/RSVDPMLCKNC

BM_BUSY#

EXT_TS0#

EXT_TS1#

THRMTRIP#

PWROK

RSTIN#

DREF_CLKN

DREF_CLKP

DREF_SSCLKN

DREF_SSCLKP

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

3

VCCP

12

CFG0

G16

SELPSB1_CLK

H13

SELPSB2_CLK

G14

CFG3

F16

CFG4

F15

CFG5

G15

CFG6

E16

CFG7

D17

CFG8

J16

CFG9

D15

CFG10

E15

CFG11

D14

CFG12

E14

CFG13

H12

CFG14

C14

CFG15

H15

CFG16

J15

CFG17

H14

CFG18

G22

G23

D23

G25

G24

J17

A31

A30

D26

D25

J23

J21

H22

F5

AD30

AE29

A24

A23

C37

D37

AP37

AN37

AP36

AP2

AP1

AN1

B1

A2

B37

A36

A37

3

DREFSSCLK#_R

DREFSSCLK_R

DREFSSCLK#_R

DREFSSCLK_R

R269 *1K_NC

CFG19

R271 *1K_NC

CFG20

VCCP

R49

56

1 2

PLTRST#_R

DOT96#

DOT96

TP_NC1

TP_NC2

TP_NC3

TP_NC4

TP_NC5

TP_NC6

TP_NC7

TP_NC8

TP_NC9

TP_NC10

TP_NC11

1

3

3

1

Populate RP2 if using CK-SSCD.

Populate Rp12 if using CK410M

R286

10K

T66

PAD

T68

PAD

T59 PAD

T53 PAD

T74 PAD

T48 PAD

T67 PAD

T49 PAD

T71 PAD

T75 PAD

T138

PM_EXTTS#0

PM_EXTTS#1

1 2

R312 100

RP2

*4P2R-S-0_NC

RP12

4P2R-S-0

4

Low=DMIx2

High=DMIx4

PAD

DOT96# 15

DOT96 15

T40

PAD

T39

PAD

T42

PAD

T98

PAD

T41

PAD

T97

PAD

T16

PAD

T17

PAD

T12

PAD

T14

PAD

T13

PAD

2

4

4

2

4

CFG6

SELPSB1_CLK 4,15

SELPSB2_CLK 4,15

12

R273

*2.2K_NC

+2.5VRUN

PM_BMBUSY# 11

THERMTRIP_GMCH# 31

IMVP_PWRGD 11,39,42

PLTRST# 10,11,16,19,25

DREFSSCLK#_R

DREFSSCLK_R

DREFSSCLK# 17

DREFSSCLK 17

DOT100#_SS 15

DOT100_SS 15

12

R254

2.2K

Low=DDR2

High=DDR1

TV_COMP18,38

TV_Y/G18,38

TV_C/R18,38

R241 150/F

1 2

R248 150/F

1 2

R243 150/F

1 2

R267 *150 /F _N C

1 2

R251 *150/F_NC

1 2

R242 *150/F_NC

1 2

VGAVSYNC18

VGAHSYNC18

REFCLK/SSCLK

5

SDVO_CTRLDATA16

SDVO_CTRLCLK16

CLK_MCH_3GPLL#15

CLK_MCH_3GPLL15

1 2

R277

4.99K/F

CLK_DDC218

DAT_DDC218

VGA_BLU18,38

VGA_GRN18,38

VGA_RED18,38

R275 39

1 2

R274 39

1 2

1 2

R285

255/F

BIA_PWM25

FPBACK17

DDC_CLK17

DDC_DATA17

FPVCC17,26

1 2

R247

1.5K/F

TXLCLKOUT-17

TXLCLKOUT+17

TXLOUT0-17

TXLOUT1-17

TXLOUT2-17

TXLOUT0+17

TXLOUT1+17

TXLOUT2+17

+2.5VRUN

R282 10K

1 2

R283 10K

1 2

For Memory throttling

External Thermal Sensor Input

5

AB29

AC29

H24

H25

A15

C16

A17

B15

B16

B17

E24

E23

E21

D21

C20

B20

A19

B19

H21

G21

E25

F25

C23

C22

F23

F22

F26

C33

C31

F28

F27

B30

B29

C25

C24

B34

B33

B32

A34

A33

B31

C29

D28

C27

C28

D27

C26

J18

J20

6

U11F

SDVOCTRL_DATA

SDVOCTRL_CLK

GCLKN

GCLKP

TVDAC_A

TVDAC_B

TVDAC_C

TV_REFSET

TV_IRTNA

TV_IRTNB

TV_IRTNC

DDCCLK

DDCDATA

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

VSYNC

HSYNC

REFSET

LBKLT_CTRL

LBKLT_EN

LCTLA_CLK

LCTLB_DATA

LDDC_CLK

LDDC_DATA

LVDD_EN

LIBG

LVBG

LVREFH

LVREFL

LACLKN

LACLKP

LBCLKN

LBCLKP

LADATAN0

LADATAN1

LADATAN2

LADATAP0

LADATAP1

LADATAP2

LBDATAN0

LBDATAN1

LBDATAN2

LBDATAP0

LBDATAP1

LBDATAP2

ALVISO

PM_EXTTS#0

PM_EXTTS#1

6

7

SDVOB_R-_C

SDVOB_G-_C

SDVOB_B-_C

SDVOB_CLK-_C

SDVOB_R+_C

SDVOB_G+_C

SDVOB_B+_C

SDVOB_CLK+_C

R268 24.9/F

1 2

SDVOB_INT- 16

SDVOB_INT+ 16

MISC

TV VGA LVDS

EXP_COMPI

EXP_ICOMPO

EXP_RXN0

EXP_RXN1

EXP_RXN2

EXP_RXN3

EXP_RXN4

EXP_RXN5

EXP_RXN6

EXP_RXN7

EXP_RXN8

EXP_RXN9

EXP_RXN10

EXP_RXN11

EXP_RXN12

EXP_RXN13

EXP_RXN14

EXP_RXN15

EXP_RXP0

EXP_RXP1

EXP_RXP2

EXP_RXP3

EXP_RXP4

EXP_RXP5

EXP_RXP6

EXP_RXP7

EXP_RXP8

EXP_RXP9

EXP_RXP10

EXP_RXP11

EXP_RXP12

EXP_RXP13

EXP_RXP14

EXP_RXP15

EXP_TXN0

EXP_TXN1

EXP_TXN2

EXP_TXN3

EXP_TXN4

EXP_TXN5

EXP_TXN6

EXP_TXN7

PCI-EXPRESS GRAPHICS

EXP_TXN8

EXP_TXN9

EXP_TXN10

EXP_TXN11

EXP_TXN12

EXP_TXN13

EXP_TXN14

EXP_TXN15

EXP_TXP10

EXP_TXP11

EXP_TXP12

EXP_TXP13

EXP_TXP14

EXP_TXP15

SDVOB_R-_C

SDVOB_G-_C

SDVOB_B-_C

SDVOB_CLK-_C

SDVOB_R+_C

SDVOB_G+_C

SDVOB_B+_C

SDVOB_CLK+_C

EXP_TXP0

EXP_TXP1

EXP_TXP2

EXP_TXP3

EXP_TXP4

EXP_TXP5

EXP_TXP6

EXP_TXP7

EXP_TXP8

EXP_TXP9

C67 .1U_10V

C49 .1U_10V

C69 .1U_10V

C51 .1U_10V

C66 .1U_10V

C48 .1U_10V

C68 .1U_10V

C50 .1U_10V

D36

D34

E30

F34

G30

H34

J30

K34

L30

M34

N30

P34

R30

T34

U30

V34

W30

Y34

D30

E34

F30

G34

H30

J34

K30

L34

M30

N34

P30

R34

T30

U34

V30

W34

E32

F36

G32

H36

J32

K36

L32

M36

N32

P36

R32

T36

U32

V36

W32

Y36

D32

E36

F32

G36

H32

J36

K32

L36

M32

N36

P32

R36

T32

U36

V32

W36

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

VCC3G_PCIE_R

SDVO Output

QUANTA

Title

Size Document Number Rev

Custom

Date: Sheet

COMPUTER

Alviso (VGA,DMI)

Tahiti(DM3L) 1A

星期二

29, 2005

三月

7

8

VCC3G_PCIE

SDVOB_R- 16

SDVOB_G- 16

SDVOB_B- 16

SDVOB_CLK- 16

SDVOB_R+ 16

SDVOB_G+ 16

SDVOB_B+ 16

SDVOB_CLK+ 16

of

649,

8

1

A A

2

3

4

5

6

7

8

R_A_MD[0..63]13

B B

C C

R_A_MD0

R_A_MD1

R_A_MD2

R_A_MD3

R_A_MD4

R_A_MD5

R_A_MD6

R_A_MD7

R_A_MD8

R_A_MD9

R_A_MD10

R_A_MD11

R_A_MD12

R_A_MD13

R_A_MD14

R_A_MD15

R_A_MD16

R_A_MD17

R_A_MD18

R_A_MD19

R_A_MD20

R_A_MD21

R_A_MD22

R_A_MD23

R_A_MD24

R_A_MD25

R_A_MD26

R_A_MD27

R_A_MD28

R_A_MD29

R_A_MD30

R_A_MD31

R_A_MD32

R_A_MD33

R_A_MD34

R_A_MD35

R_A_MD37

R_A_MD38

R_A_MD39

R_A_MD40

R_A_MD41

R_A_MD42

R_A_MD43

R_A_MD44

R_A_MD45

R_A_MD46

R_A_MD47

R_A_MD48

R_A_MD49

R_A_MD50

R_A_MD51

R_A_MD52

R_A_MD53

R_A_MD54

R_A_MD55

R_A_MD56

R_A_MD57

R_A_MD58

R_A_MD59

R_A_MD60

R_A_MD61

R_A_MD62

R_A_MD63

AG35

AH35

AL35

AL37

AH36

AJ35

AK37

AL34

AM36

AN35

AP32

AM31

AM34

AM35

AL32

AM32

AN31

AP31

AN28

AP28

AL30

AM30

AM28

AL28

AP27

AM27

AM23

AM22

AL23

AM24

AN22

AP22

AM9

AL9

AL6

AP7

AP11

AP10

AL7

AM7

AN5

AN6

AN3

AP3

AP6

AM6

AL4

AM3

AK2

AK3

AG2

AG1

AL3

AM2

AH3

AG3

AF3

AE3

AD6

AC4

AF2

AF1

AD4

AD5

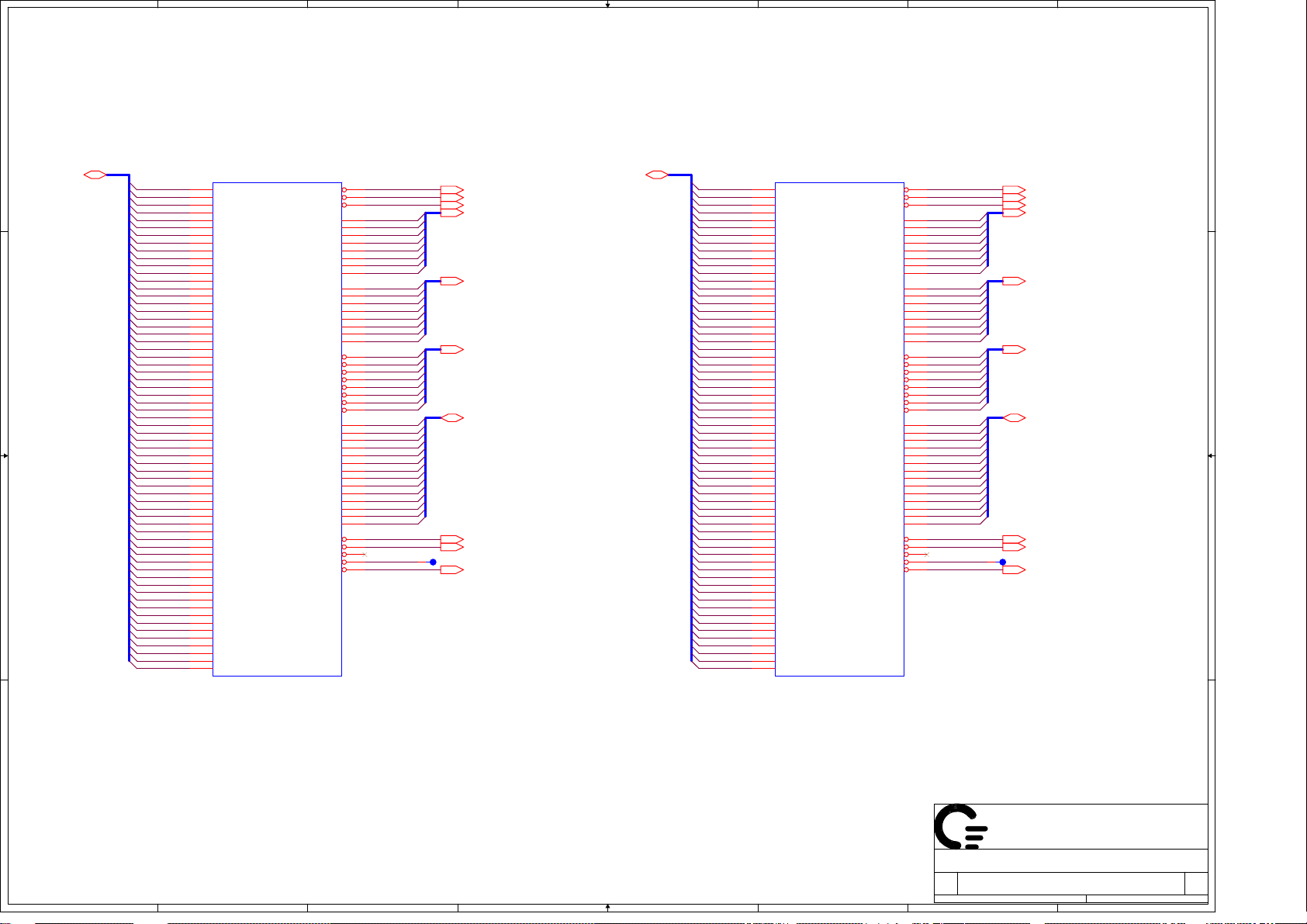

U11B

SADQ0

SADQ1

SADQ2

SADQ3

SADQ4

SADQ5

SADQ6

SADQ7

SADQ8

SADQ9

SADQ10

SADQ11

SADQ12

SADQ13

SADQ14

SADQ15

SADQ16

SADQ17

SADQ18

SADQ19

SADQ20

SADQ21

SADQ22

SADQ23

SADQ24

SADQ25

SADQ26

SADQ27

SADQ28

SADQ29

SADQ30

SADQ31

SADQ32

SADQ33

SADQ34

SADQ35

SADQ36

SADQ37

SADQ38

SADQ39

SADQ40

SADQ41

SADQ42

SADQ43

SADQ44

SADQ45

SADQ46

SADQ47

SADQ48

SADQ49

SADQ50

SADQ51

SADQ52

SADQ53

SADQ54

SADQ55

SADQ56

SADQ57

SADQ58

SADQ59

SADQ60

SADQ61

SADQ62

SADQ63

ALVISO

SA_BS0#

SA_BS1#

SA_BS2#

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS0#

SA_DQS1#

SA_DQS2#

SA_DQS3#

SA_DQS4#

SA_DQS5#

SA_DQS6#

SA_DQS7#

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

DDR SYSTEM MEMORY A

SA_CAS#

SA_RAS#

SA_RCVENIN#

SA_RCVENOUT#

SA_WE#

AK15

AK16

AL21

AJ37

AP35

AL29

AP24

AP9

AP4

AJ2

AD3

AK36

AP33

AN29

AP23

AM8

AM4

AJ1

AE5

AK35

AP34

AN30

AN23

AN8

AM5

AH1

AE4

AL17

AP17

AP18

AM17

AN18

AM18

AL19

AP20

AM19

AL20

AM16

AN20

AM20

AM15

AN15

AP16

AF29

AF28

AP15

R_A_BS0#

R_A_BS1#

R_A_BS2#

R_A_DM0

R_A_DM1

R_A_DM2

R_A_DM3

R_A_DM4

R_A_DM5

R_A_DM6

R_A_DM7

R_A_DQS0

R_A_DQS1

R_A_DQS2

R_A_DQS3

R_A_DQS4

R_A_DQS5

R_A_DQS6

R_A_DQS7

R_A_DQS#0

R_A_DQS#1

R_A_DQS#2

R_A_DQS#3

R_A_DQS#4

R_A_DQS#5

R_A_DQS#6

R_A_DQS#7

R_A_MA0

R_A_MA1

R_A_MA2

R_A_MA3

R_A_MA4

R_A_MA5

R_A_MA6

R_A_MA7

R_A_MA8

R_A_MA9

R_A_MA10

R_A_MA11

R_A_MA12

R_A_MA13

R_A_SCASA#

R_A_SRASA#

R_A_BMWEA#

PAD

R_A_BS0# 13,14

R_A_BS1# 13,14

R_A_BS2# 13,14

R_A_DM[0..7] 13

R_A_DQS[0..7] 13

R_A_DQS#[0..7] 13

R_A_MA[0..13] 13,14

R_A_SCASA# 13,14

R_A_SRASA# 13,14

T123

R_A_BMWEA# 13,14

R_B_MD[0..63]13

R_B_MD0

R_B_MD1

R_B_MD2

R_B_MD3

R_B_MD4

R_B_MD5

R_B_MD6

R_B_MD7

R_B_MD8

R_B_MD9

R_B_MD10

R_B_MD11

R_B_MD12

R_B_MD13

R_B_MD14

R_B_MD15

R_B_MD16

R_B_MD17

R_B_MD18

R_B_MD19

R_B_MD20

R_B_MD21

R_B_MD22

R_B_MD23

R_B_MD24

R_B_MD25

R_B_MD26

R_B_MD27

R_B_MD28

R_B_MD29

R_B_MD30

R_B_MD31

R_B_MD32

R_B_MD33

R_B_MD34

R_B_MD35

R_B_MD36R_A_MD36

R_B_MD37

R_B_MD38

R_B_MD39

R_B_MD40

R_B_MD41

R_B_MD42

R_B_MD43

R_B_MD44

R_B_MD45

R_B_MD46

R_B_MD47

R_B_MD48

R_B_MD49

R_B_MD50

R_B_MD51

R_B_MD52

R_B_MD53

R_B_MD54

R_B_MD55

R_B_MD56

R_B_MD57

R_B_MD58

R_B_MD59

R_B_MD60

R_B_MD61

R_B_MD62

R_B_MD63

AE31

AE32

AG32

AG36

AE34

AE33

AF31

AF30

AH33

AH32

AK31

AG30

AG34

AG33

AH31

AJ31

AK30

AJ30

AH29

AH28

AK29

AH30

AH27

AG28

AF24

AG23

AJ22

AK22

AH24

AH23

AG22

AJ21

AG10

AG9

AG8

AH8

AH11

AH10

AK9

AK6

AH5

AK8

AK4

AG5

AG4

AD8

AD9

AH4

AG6

AE8

AD7

AC5

AB8

AB6

AA8

AC8

AC7

AA4

AA5

U11G

SBDQ0

SBDQ1

SBDQ2

SBDQ3

SBDQ4

SBDQ5

SBDQ6

SBDQ7

SBDQ8

SBDQ9

SBDQ10

SBDQ11

SBDQ12

SBDQ13

SBDQ14

SBDQ15

SBDQ16

SBDQ17

SBDQ18

SBDQ19

SBDQ20

SBDQ21

SBDQ22

SBDQ23

SBDQ24

SBDQ25

SBDQ26

SBDQ27

SBDQ28

SBDQ29

SBDQ30

SBDQ31

SBDQ32

SBDQ33

SBDQ34

SBDQ35

SBDQ36

SBDQ37

AJ9

SBDQ38

SBDQ39

AJ7

SBDQ40

SBDQ41

AJ4

SBDQ42

SBDQ43

SBDQ44

AJ8

SBDQ45

AJ5

SBDQ46

SBDQ47

SBDQ48

SBDQ49

SBDQ50

SBDQ51

SBDQ52

SBDQ53

SBDQ54

SBDQ55

SBDQ56

SBDQ57

SBDQ58

SBDQ59

SBDQ60

SBDQ61

SBDQ62

SBDQ63

ALVISO

SB_BS0#

SB_BS1#

SB_BS2#

SB_DM0

SB_DM1

SB_DM2

SB_DM3

SB_DM4

SB_DM5

SB_DM6

SB_DM7

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

SB_DQS0#

SB_DQS1#

SB_DQS2#

SB_DQS3#

SB_DQS4#

SB_DQS5#

SB_DQS6#

SB_DQS7#

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

DDR SYSTEM MEMORY B

SB_CAS#

SB_RAS#

SB_RCVENIN#

SB_RCVENOUT#

SB_WE#

AJ15

AG17

AG21

AF32

AK34

AK27

AK24

AJ10

AK5

AE7

AB7

AF34

AK32

AJ28

AK23

AM10

AH6

AF8

AB4

AF35

AK33

AK28

AJ23

AL10

AH7

AF7

AB5

AH17

AK17

AH18

AJ18

AK18

AJ19

AK19

AH19

AJ20

AH20

AJ16

AG18

AG20

AG15

AH14

AK14

AF15

AF14

AH16

R_B_BS0#

R_B_BS1#

R_B_BS2#

R_B_DM0

R_B_DM1

R_B_DM2

R_B_DM3

R_B_DM4

R_B_DM5

R_B_DM6

R_B_DM7

R_B_DQS0

R_B_DQS1

R_B_DQS2

R_B_DQS3

R_B_DQS4

R_B_DQS5

R_B_DQS6

R_B_DQS7

R_B_DQS#0

R_B_DQS#1

R_B_DQS#2

R_B_DQS#3

R_B_DQS#4

R_B_DQS#5

R_B_DQS#6

R_B_DQS#7

R_B_MA0

R_B_MA1

R_B_MA2

R_B_MA3

R_B_MA4

R_B_MA5

R_B_MA6

R_B_MA7

R_B_MA8

R_B_MA9

R_B_MA10

R_B_MA11

R_B_MA12

R_B_MA13

R_B_SCASA#

R_B_SRASA#

R_B_BMWEA#

PAD

R_B_BS0# 13,14

R_B_BS1# 13,14

R_B_BS2# 13,14

R_B_DM[0..7] 13

R_B_DQS[0..7] 13

R_B_DQS#[0..7] 13

R_B_MA[0..13] 13,14

R_B_SCASA# 13,14

R_B_SRASA# 13,14

T124

R_B_BMWEA# 13,14

D D

QUANTA

Title

Size Document Number Rev

1

2

3

4

5

6

Date: Sheet

COMPUTER

Alviso (DDR)

Tahiti(DM3L) 1A

星期二

29, 2005

三月

7

of

749,

8

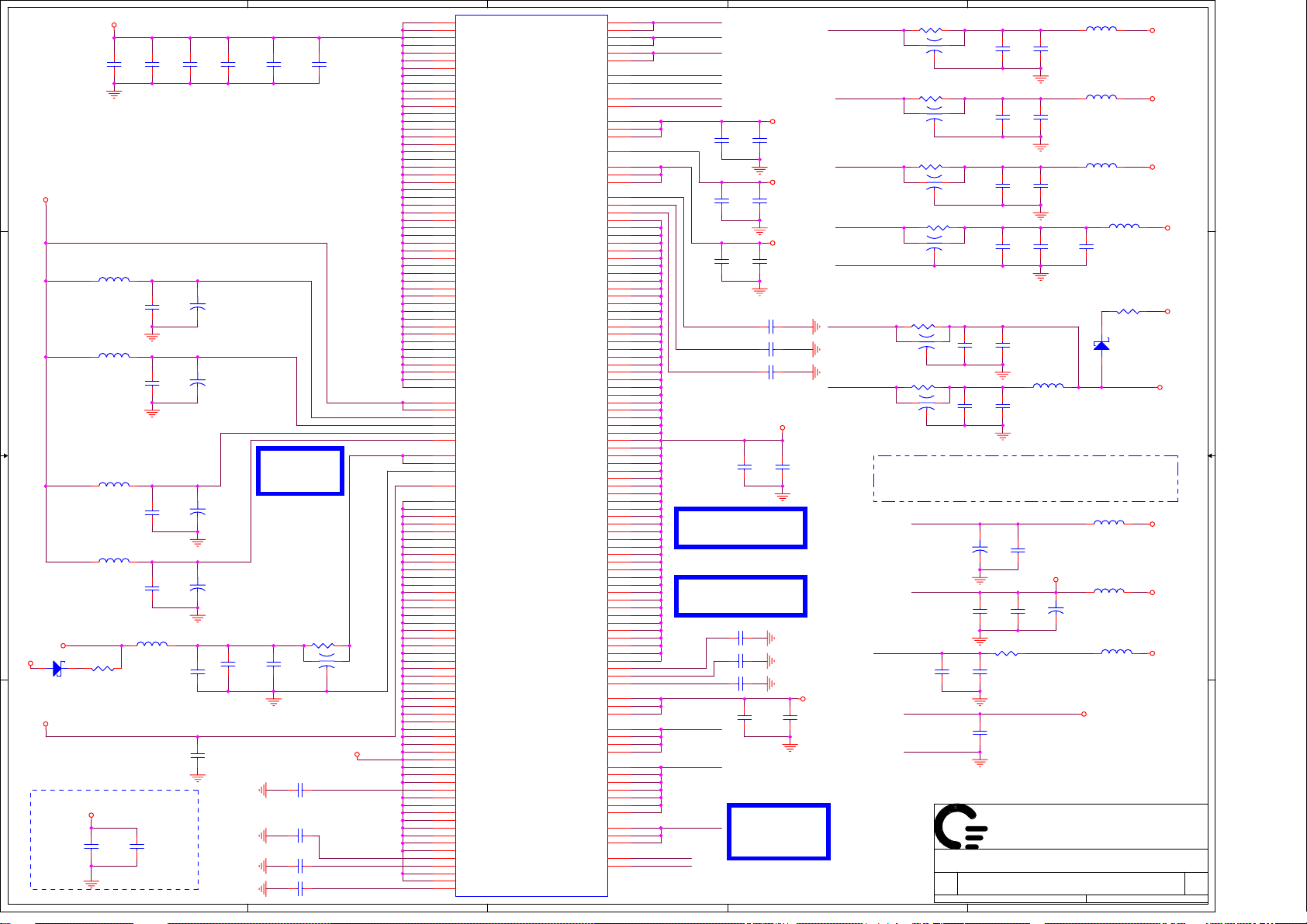

5

VCCP

12

12

12

C385

.1U_10V

12

C366

.1U_10V

12

C368

.1U_10V

12

C88

.1U_10V

12

C90

.1U_10V

12

C723

*10U_4V_NC

C54

4.7U_10V_0805

12

C388

.1U_10V

12

+

12

+

12

+

12

+

12

12

VCCA_DPLLA

C44

470U_4V

VCCA_DPLLB

C341

470U_4V

C86

150U_2V_L

VCCA_MPLL

C96

150U_2V_L

C380

.1U_10V

C393

.1U_10V

D D

+1_5VRUN

L12

12

10uH

C C

B B

+2.5VRUN

VCCP

D16

2 1

RB751V

+2.5VRUN

A A

1.05V(VTT - FSB POWER SUPPLY)

L16

10uH

L18

BLM11A121S

L19

BLM11A121S

R230 10

VCCP

12

C409

2.2U_6.3V

12

12

12

L31

BLM18PG181SN1

12

12

5

C55

10U_4V

VCCA_HPLL

VCCA_CRTDAC

12

C345

.1U_10V

12

12

C78

10U_4V

ALL PLL POWER

Needs To Have

Clear Power(No

Any Noise)

R231 0

1 2

12

C346

3

.022U

C60 .47U_10V

1 2

C59 .47U_10V

1 2

C84 .22U_10V

1 2

C73 .22U_10V

1 2

4

C56

10U_4V

VCCA_CRTDAC_R

1

C353

2

*22nF_3P_NC

VCCP

VCCP_GMCH_CAP1

VCCP_GMCH_CAP2

VCCP_GMCH_CAP3

VCCP_GMCH_CAP4

4

T29

R29

N29

M29

K29

J29

V28

U28

T28

R28

P28

N28

M28

L28

K28

J28

H28

G28

V27

U27

T27

R27

P27

N27

M27

L27

K27

J27

H27

K26

H26

K25

J25

K24

K23

K22

K21

W20

U20

T20

K20

V19

U19

K19

W18

V18

T18

K18

K17

AC2

AC1

B23

C35

AA1

AA2

F19

E19

G19

H20

K13

J13

K12

W11

V11

U11

T11

R11

P11

N11

M11

L11

K11

W10

V10

U10

T10

R10

P10

N10

M10

K10

J10

Y9

W9

U9

R9

P9

N9

M9

L9

J9

N8

M8

N7

M7

N6

M6

A6

N5

M5

N4

M4

N3

M3

N2

M2

B2

V1

N1

M1

G1

VCC0

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCCH_MPLL1

VCCH_MPLL0

VCCA_DPLLA

VCCA_DPLLB

VCCA_HPLL

VCCA_MPLL

VCCA_CRTDAC0

VCCA_CRTDAC1

VSSA_CRTDAC

VCC_SYNC

VTT0

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

VTT10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VTT23

VTT24

VTT25

VTT26

VTT27

VTT28

VTT29

VTT30

VTT31

VTT32

VTT33

VTT34

VTT35

VTT36

VTT37

VTT38

VTT39

VTT40

VTT41

VTT42

VTT43

VTT44

VTT45

VTT46

VTT47

VTT48

VTT49

VTT50

VTT51

U11H

ALVISO

VCCA_TVDACA0

VCCA_TVDACA1

VCCA_TVDACB0

VCCA_TVDACB1

VCCA_TVDACC0

VCCA_TVDACC1

VCCA_TVBG

VSSA_TVBG

VCCD_TVDAC

VCCDQ_TVDAC

VCCD_LVDS0

VCCD_LVDS1

VCCD_LVDS2

VCCA_LVDS

POWER

VCCTX_LVDS0

VCCTX_LVDS1

VCCTX_LVDS2

VCCA_3GPLL0

VCCA_3GPLL1

VCCA_3GPLL2

VCCA_3GBG

VSSA_3GBG

VCCHV0

VCCHV1

VCCHV2

VCCSM0

VCCSM1

VCCSM2

VCCSM3

VCCSM4

VCCSM5

VCCSM6

VCCSM7

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

VCCSM15

VCCSM16

VCCSM17

VCCSM18

VCCSM19

VCCSM20

VCCSM21

VCCSM22

VCCSM23

VCCSM24

VCCSM25

VCCSM26

VCCSM27

VCCSM28

VCCSM29

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCSM34

VCCSM35

VCCSM36

VCCSM37

VCCSM38

VCCSM39

VCCSM40

VCCSM41

VCCSM42

VCCSM43

VCCSM44

VCCSM45

VCCSM46

VCCSM47

VCCSM48

VCCSM49

VCCSM50

VCCSM51

VCCSM52

VCCSM53

VCCSM54

VCCSM55

VCCSM56

VCCSM57

VCCSM58

VCCSM59

VCCSM60

VCCSM61

VCCSM62

VCCSM63

VCCSM64

VCCA_SM0

VCCA_SM1

VCCA_SM2

VCCA_SM3

VCC3G0

VCC3G1

VCC3G2

VCC3G3

VCC3G4

VCC3G5

VCC3G6

3

F17

E17

D18

C18

F18

E18

H18

G18

D19

H17

B26

B25

A25

A35

B22

B21

A21

AM37

AH37

AP29

AD28

AD27

AC27

AP26

AN26

AM26

AL26

AK26

AJ26

AH26

AG26

AF26

AE26

AP25

AN25

AM25

AL25

AK25

AJ25

AH25

AG25

AF25

AE25

AE24

AE23

AE22

AE21

AE20

AE19

AE18

AE17

AE16

AE15

AE14

AP13

AN13

AM13

AL13

AK13

AJ13

AH13

AG13

AF13

AE13

AP12

AN12

AM12

AL12

AK12

AJ12

AH12

AG12

AF12

AE12

AD11

AC11

AB11

AB10

AB9

AP8

AM1

AE1

B28

A28

A27

AF20

AP19

AF19

AF18

AE37

W37

U37

R37

N37

L37

J37

Y29

Y28

Y27

F37

G37

3

VCC_TVDACA_R

VCC_TVDACB_R

VCC_TVDACC_R

VCC_TVBG_R

VSS_TVBG

VCCD_TVDAC_R

VCCQ_TVDAC_R

Note: All VCCSM pins

shorted internally.

Note: All VCCSM pins

shorted internally.

V1.8_DDR_CAP6

V1.8_DDR_CAP3

V1.8_DDR_CAP4

VCC_DDRDLL

VCC3G_PCIE

VCCA_3GPLL

VCCA_3GBG

VSSA_3GBG

12

C363

.1U_10V

12

C355

.01U

12

C361

.1U_10V

V1.8_DDR_CAP1

V1.8_DDR_CAP2

V1.8_DDR_CAP5

C422 .1U_10V

1 2

C423 .1U_10V

1 2

C91 .1U_10V

1 2

ALL PLL POWER

Needs To Have

Clear Power(No

Any Noise)

12

C45

10U_4V

12

C367

.1U_10V

12

C53

10U_4V

C425 .1U_10V

1 2

C415 .1U_10V

1 2

C428 .1U_10V

1 2

+1_8VSUS

12

C107

10U_4V

12

C373

.1U_10V

+1_5VRUN

+2.5VRUN

+2.5VRUN

12

C106

10U_4V

12

C57

4.7U_10V_0805

+2.5VRUN

2

VCC_TVDACA_R

VCC_TVDACB_R

VCC_TVDACC_R

VCC_TVBG_R

VSS_TVBG

VCCD_TVDAC_R

*22nF_3P_NC

VCCQ_TVDAC_R

*22nF_3P_NC

2

1

12

12

12

12

C338

.1U_10V

C52

.1U_10V

C343

.1U_10V

C47

.1U_10V

12

+

L29

BLM18PG181SN1

L14

BLM18PG181SN1

L30

BLM18PG181SN1

12

12

C74

150U_2V_L

+2.5VRUN

12

12

12

L13

BLM18PG181SN1

C716

2.2U_6.3V

R35 10

D6

RB751V

2 1

L20

12

BLM18PG330SN1

L34

12

BLM18PG330SN1

L33

12

BLM18PG181SN1

12

12

R219 0

1 2

1

3

C340

2

*22nF_3P_NC

R39 0

1 2

1

3

C62

2

*22nF_3P_NC

R226 0

1 2

1

3

C351

2

*22nF_3P_NC

R36 0

1 2

1

3

C58

2

*22nF_3P_NC

R227 0

1 2

3

C352

R38 0

1 2

3

C61

Note: Choose the Inductor with Low-DC loss and

High-Impedance at over 100MHz to isolate

SSN/SN(Switch Noise) from other aggressor .

VCCA_3GPLL

1

2

1

2

VCC_DDRDLL

VCC3G_PCIE

12

C408

.1U_10V

VCCA_3GBG

VSSA_3GBG

12

.022U

12

.022U

VCCD_TVDAC

C347

VCCQ_TVDAC

C64

12

C110

+

100U

12

C76

10U_4V

R278

1 2

12

0.5/F

C376

10U_4V

12

C354

.1U_10V

VCC_TVDACA

12

C339

.022U

VCC_TVDACB

12

C65

.022U

VCC_TVDACC

12

C344

.022U

VCC_TVBG

12

C46

.022U

12

C342

.1U_10V

12

C63

.1U_10V

12

C412

.1U_10V

12

C77

10U_4V

L15

BLM18PG181SN1

VCC3G_PCIE

VCCA_3GPLL_R

QUANTA

Title

Size Document Number Rev

Date: Sheet

COMPUTER

Alviso (Power)

Tahiti(DM3L) 1A

星期二

29, 2005

三月

1

of

849,

+3VRUN

+3VRUN

+3VRUN

+3VRUN

+3VRUN

+1_5VRUN

+1_5VRUN

+1_5VRUN

+1_5VRUN

5

4

3

2

1

B36

G2

D2

Y1

D D

C C

VSS270

VSS271

VSSALVDS

VSS134

VSS135

B24

D24

VSS269

VSS133

F24

AL24

J2

VSS268

VSS132

J24

AG24

A26

AN24

VSS266

VSS267

VSS130

VSS131

E27

AJ24

G26

E26

VSS264

VSS265

VSS128

VSS129

G27

W27

J26

VSS262

VSS263

VSS126

VSS127

AA27

Y12

VSS_NCTF68

T2

P2

L2

B27

VSS258

VSS259

VSS260

VSS261

VSS122

VSS123

VSS124

VSS125

AJ27

AF27

AB27

AG27

L14

AA13

Y13

AA12

VSS_NCTF64

VSS_NCTF65

VSS_NCTF66

VSS_NCTF67

AE2

AD2

V2

VSS255

VSS256

VSS257

VSS119

VSS120

VSS121

E28

AL27

AN27

P14

N14

M14

VSS_NCTF61

VSS_NCTF62

VSS_NCTF63

A3

AN2

AL2

AH2

VSS251

VSS252

VSS253

VSS254

VSS115

VSS116

VSS117

VSS118

W28

AB28

AA28

AC28

V14

U14

T14

R14

VSS_NCTF57

VSS_NCTF58

VSS_NCTF59

VSS_NCTF60

AB3

AA3

C3

VSS248

VSS249

VSS250

VSS112

VSS113

VSS114

E29

A29

D29

AA14

Y14

W14

VSS_NCTF54

VSS_NCTF55

VSS_NCTF56

H4

C4

AJ3

AC3

VSS244

VSS245

VSS246

VSS247

VSS108

VSS109

VSS110

VSS111

L29

F29

H29

G29

N15

M15

L15

AB14

VSS_NCTF50

VSS_NCTF51

VSS_NCTF52

VSS_NCTF53

U4

P4

L4

VSS241

VSS242

VSS243

VSS105

VSS106

VSS107

V29

P29

U29

T15

R15

P15

VSS_NCTF47

VSS_NCTF48

VSS_NCTF49

E5

AN4

AF4

Y4

VSS237

VSS238

VSS239

VSS240

VSS101

VSS102

VSS103

VSS104

W29

AA29

AD29

AG29

Y15

W15

V15

U15

VSS_NCTF43

VSS_NCTF44

VSS_NCTF45

VSS_NCTF46

AP5

AL5

W5

VSS234

VSS235

VSS236

VSS98

VSS99

VSS100

C30

AJ29

AM29

L16

AB15

AA15

VSS_NCTF40

VSS_NCTF41

VSS_NCTF42

P6

L6

J6

B6

VSS230

VSS231

VSS232

VSS233

VSS94

VSS95

VSS96

VSS97

Y30

AB30

AA30

AC30

R16

P16

N16

M16

VSS_NCTF36

VSS_NCTF37

VSS_NCTF38

VSS_NCTF39

AC6

AA6

T6

VSS227

VSS228

VSS229

VSS91

VSS92

VSS93

D31

AP30

AE30

V16

U16

T16

VSS_NCTF33

VSS_NCTF34

VSS_NCTF35

V7

G7

AJ6

AE6

VSS223

VSS224

VSS225

VSS226

VSS87

VSS88

VSS89

VSS90

F31

E31

H31

G31

AB16

AA16

Y16

W16

VSS_NCTF29

VSS_NCTF30

VSS_NCTF31

VSS_NCTF32

AK7

AG7

AA7

VSS220

VSS221

VSS222

VSS84

VSS85

VSS86

J31

L31

K31

AA17

Y17

R17

VSS_NCTF26

VSS_NCTF27

VSS_NCTF28

L8

E8

C8

AN7

VSS216

VSS217

VSS218

VSS219

VSS80

VSS81

VSS82

VSS83

P31

R31

N31

M31

AA19

AB18

AA18

AB17

VSS_NCTF22

VSS_NCTF23

VSS_NCTF24

VSS_NCTF25

AL8

Y8

P8

VSS213

VSS214

VSS215

U11E

ALVISO

VSS77

VSS78

VSS79

T31

V31

U31

AB20

AA20

AB19

VSS_NCTF19

VSS_NCTF20

VSS_NCTF21

T9

K9

H9

A9

VSS209

VSS210

VSS211

VSS212

VSS

VSS73

VSS74

VSS75

VSS76

W31

AL31

AD31

AG31

AB21

AA21

Y21

R21

VSS_NCTF15

VSS_NCTF16

VSS_NCTF17

VSS_NCTF18

AC9

AA9

V9

VSS206

VSS207

VSS208

VSS70

VSS71

VSS72

Y32

A32

C32

AB22

AA22

Y22

VSS_NCTF12

VSS_NCTF13

VSS_NCTF14

D10

AN9

AH9

AE9

VSS202

VSS203

VSS204

VSS205

VSS66

VSS67

VSS68

VSS69

AB32

AA32

AD32

AC32

Y24

AB23

AA23

Y23

VSS_NCTF8

VSS_NCTF9

VSS_NCTF10

VSS_NCTF11

AA10

Y10

L10

VSS199

VSS200

VSS201

VSS63

VSS64

VSS65

D33

AJ32

AN32

Y25

AB24

AA24

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

AA11

Y11

H11

F11

VSS196

VSS197

VSS198

VSS60

VSS61

VSS62

F33

E33

H33

G33

AA26

Y26

AB25

AA25

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

AJ11

AG11

AF11

VSS192

VSS193

VSS194

VSS195

VSS56

VSS57

VSS58

VSS59

J33

L33

K33

AB26

VSS_NCTF0

VSS_NCTF1

AN11

AL11

VSS191

VSS55

N33

M33

B12

VSS189

VSS190

VSS53

VSS54

P33

D12

R33

L12

B14

A14

J12

VSS185

VSS186

VSS187

VSS188

VSS49

VSS50

VSS51

VSS52

T33

V33

U33

P12

N12

M12

VTT_NCTF14

VTT_NCTF15

VTT_NCTF16

VTT_NCTF17

AG14

K14

J14

F14

VSS181

VSS182

VSS183

VSS184

VSS45

VSS46

VSS47

VSS48

W33

AL33

AF33

AD33

V12

U12

T12

R12

VTT_NCTF10

VTT_NCTF11

VTT_NCTF12

VTT_NCTF13

AN14

AL14

AJ14

VSS178

VSS179

VSS180

VSS42

VSS43

VSS44

C34

AB34

AA34

M13

L13

W12

VTT_NCTF7

VTT_NCTF8

VTT_NCTF9

D16

A16

K15

C15

VSS175

VSS176

VSS177

VSS39

VSS40

VSS41

AN34

AH34

AD34

AC34

T13

R13

P13

N13

VTT_NCTF4

VTT_NCTF5

VTT_NCTF6

AL16

K16

H16

VSS171

VSS172

VSS173

VSS174

VSS35

VSS36

VSS37

VSS38

E35

B35

D35

VCCP

W13

V13

U13

VTT_NCTF0

VTT_NCTF1

VTT_NCTF2

VTT_NCTF3

B18

A18

AN17

AJ17

AF17

G17

C17

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

J35

L35

F35

K35

H35

G35

M35

All NCTF Pin is to enchance the

solder Joint Characteristic

Thermal Expansion (CTE) mismatch

of the Die to package interface.

AL18

U18

VSS163

VSS27

P35

N35

H19

C19

VSS161

VSS162

VSS25

VSS26

T35

R35

T19

J19

VSS159

VSS160

VSS23

VSS24

V35

U35

W19

VSS157

VSS158

VSS21

VSS22

W35

AN19

AG19

VSS156

VSS20

Y35

AE35

D20

A20

VSS154

VSS155

VSS18

VSS19

C36

AA36

F20

E20

VSS152

VSS153

VSS16

VSS17

AB36

AC36

G20

VSS150

VSS151

VSS14

VSS15

AD36

AK20

V20

VSS149

VSS13

AF36

AE36

F21

C21

VSS147

VSS148

VSS11

VSS12

AJ36

AL36

AF21

VSS145

VSS146

VSS9

VSS10

AN36

A22

AN21

VSS144

VSS8

E37

H37

VSS143

VSS7

E22

D22

VSS142

VSS6

K37

M37

AH22

J22

VSS140

VSS141

VSS4

VSS5

T37

P37

H23

AL22

VSS138

VSS139

VSS2

VSS3

Y37

V37

AF23

VSS136

VSS137

VSS0

VSS1

AG37

U11D

NCTF

W21

ALVISO

VCCSM_NCTF0

VCCSM_NCTF1

VCCSM_NCTF2

VCCSM_NCTF3

VCCSM_NCTF4

VCCSM_NCTF5

VCCSM_NCTF6

VCCSM_NCTF7

VCCSM_NCTF8

VCCSM_NCTF9

VCCSM_NCTF10

VCCSM_NCTF11

VCCSM_NCTF12

VCCSM_NCTF13

VCCSM_NCTF14

VCCSM_NCTF15

VCCSM_NCTF16

VCCSM_NCTF17

VCCSM_NCTF18

VCCSM_NCTF19

VCCSM_NCTF20

VCCSM_NCTF21

VCCSM_NCTF22

VCCSM_NCTF23

VCCSM_NCTF24

VCCSM_NCTF25

VCCSM_NCTF26

VCCSM_NCTF27

VCCSM_NCTF28

VCCSM_NCTF29

VCCSM_NCTF30

VCCSM_NCTF31

VCC_NCTF0

VCC_NCTF1

VCC_NCTF2

VCC_NCTF3

VCC_NCTF4

VCC_NCTF5

VCC_NCTF6

VCC_NCTF7

VCC_NCTF8

VCC_NCTF9

VCC_NCTF10

VCC_NCTF11

VCC_NCTF12

VCC_NCTF13

VCC_NCTF14

VCC_NCTF15

VCC_NCTF16

VCC_NCTF17

VCC_NCTF18

VCC_NCTF19

VCC_NCTF20

VCC_NCTF21

VCC_NCTF22

VCC_NCTF23

VCC_NCTF24

VCC_NCTF25

VCC_NCTF26

VCC_NCTF27

VCC_NCTF28

VCC_NCTF29

VCC_NCTF30

VCC_NCTF31

VCC_NCTF32

VCC_NCTF33

VCC_NCTF34

VCC_NCTF35

VCC_NCTF36

VCC_NCTF37

VCC_NCTF38

VCC_NCTF39

VCC_NCTF40

VCC_NCTF41

VCC_NCTF42

VCC_NCTF43

VCC_NCTF44

VCC_NCTF45

L22

N22

M22

L23

T22

V22

P22

R22

N23

U22

M23

W22

L24

T23

V23

P23

R23

N24

U23

M24

W23

L25

T24

V24

P24

R24

N25

U24

M25

W24

L26

W25

T26

V26

P26

U26

R26

N26

M26

W26

VCCP

AB12

AC12

AD12

AB13

AC13

AD13

AC14

AD14

AC15

AD15

AC16

AD16

AC17

AD17

AC18

AD18

AC19

AD19

AC20

AD20

AC21

AD21

AC22

AD22

AC23

AD23

AC24

AD24

AC25

AD26

AC26

AD25

+1_8VSUS

T25

V25

P25

U25

R25

B B

VCC_NCTF46

VCC_NCTF47

VCC_NCTF48

VCC_NCTF49

VCC_NCTF50

VCC_NCTF51

VCC_NCTF52

VCC_NCTF53

VCC_NCTF54

VCC_NCTF55

VCC_NCTF56

VCC_NCTF57

VCC_NCTF58

VCC_NCTF59

VCC_NCTF60

VCC_NCTF61

VCC_NCTF62

VCC_NCTF63

VCC_NCTF64

VCC_NCTF65

VCC_NCTF66

VCC_NCTF67

VCC_NCTF68

VCC_NCTF69

VCC_NCTF70

VCC_NCTF71

VCC_NCTF72

VCC_NCTF73

VCC_NCTF74

VCC_NCTF75

VCC_NCTF76

VCC_NCTF77

VCC_NCTF78

L21

L20

L19

L17

M17

A A

L18

T17

V17

P17

U17

N17

W17

Y18

P18

N19

R18

N18

M19

M18

P20

Y19

P19

N20

R19

M20

T21

V21

P21

Y20

U21

N21

R20

M21

QUANTA

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

COMPUTER

Alviso (VSS,NCTF)

Tahiti(DM3L) 1A

星期二

29, 2005

三月

1

of

949,

1

VCCRTC

A A

PDD[0..15]19

PDDREQ19

PDIOW#19

PDIOR#19

PIORDY19

PDDACK#19

IRQ1419

PDA119

PDA019

PDCS1#19

PDA219

PDCS3#19

Reset Circuit

B B

(NB/PCI/PCIE)

PLTRST#6,11,16,19,25

PCLK_ICH15

C C

12

R153

100K

SM_INTRUDER#

PDD[0..15]

PDDREQ

PDIOW#

PDIOR#

PIORDY

PDDACK#

IRQ14

PDA1

PDA0

PDCS1#

PDA2

PDCS3#

4

R422

*33_NC

1 2

C546

*18P_NC

1 2

AC-Terminator

IAC_SYNC_MDC24

D D

IAC_SYNC_AUDIO33

C214

22P

12

C216

*10P_NC

1 2

AC97-MDC & AUDIO

1

R154 20K/F

U17

7SH32

R143 39

12

R142 39

2

+3VSUS

5

2

1

X1,X2 Docking

IAC_SYNC Port X Line R144

C227

1U_10V

C215

.047U

C228 15P

C222 15P

12

PLTRST#_1

12

12

SM_INTRUDER#31

CPUINIT#3

+3VRUN

NMI3

A20M#3

FERR#3

IGNNE#3

INTR3

RCIN#25

GATEA2026

ICH_PME#25

PCIRST#21,23,35

CLKRUN#21,23,25,35

101X2,2X1

4X1