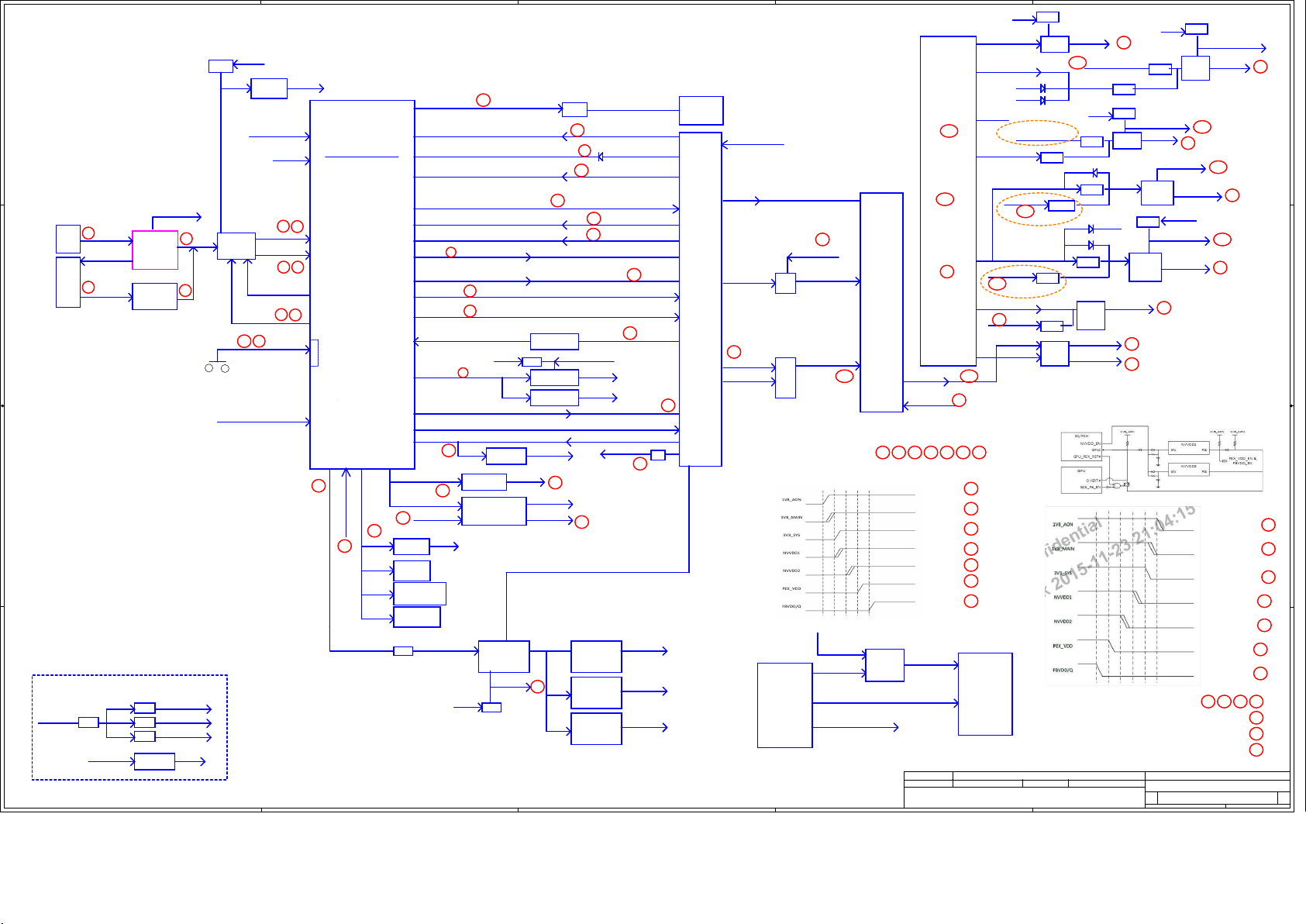

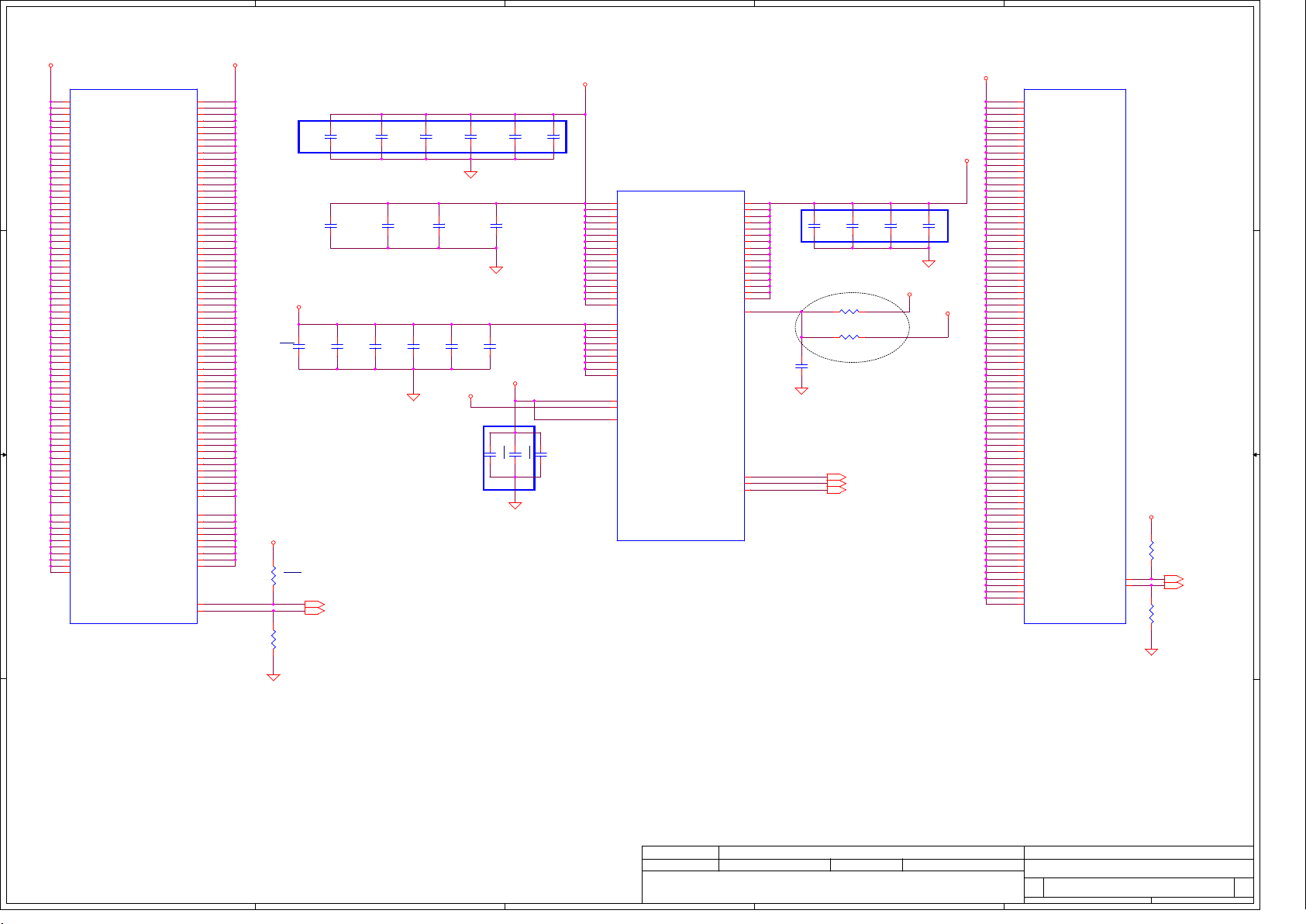

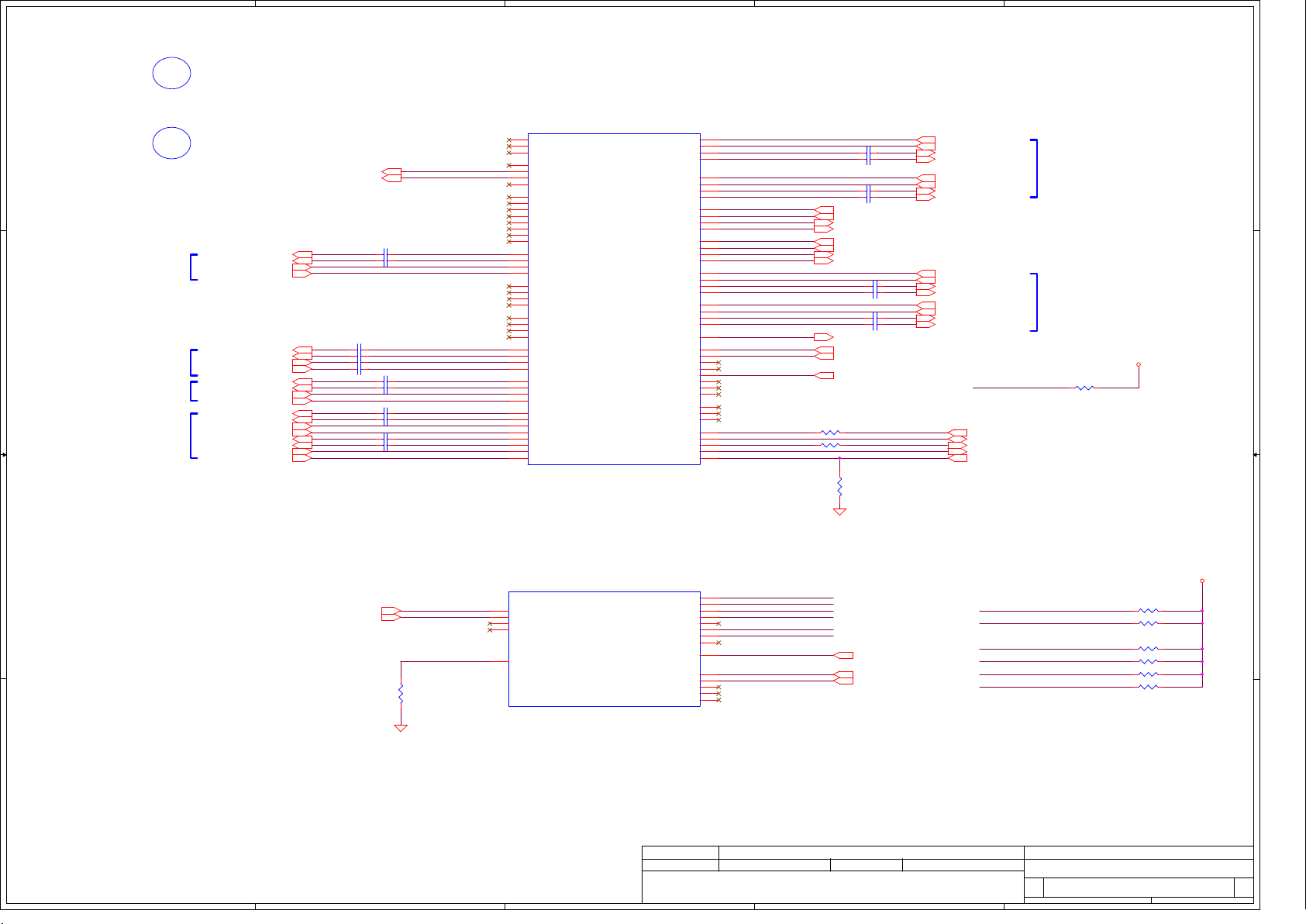

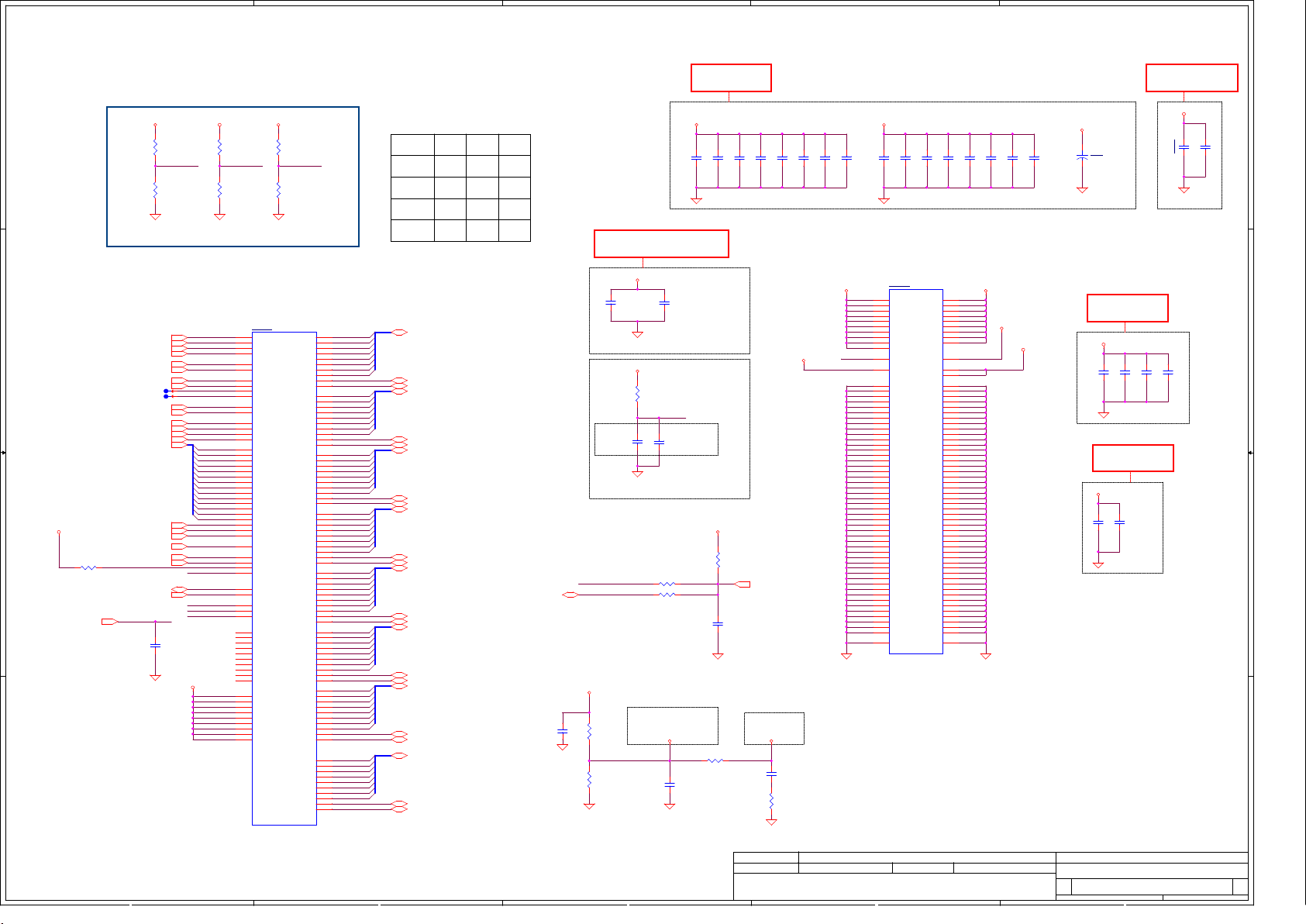

Dell Alienware Area 51M Schematics

A

1 1

B

C

D

E

LA-G881P

Coffee Lake-S 95W

CNL PCH-H with nVIDIA N18E

2 2

REV : 1.0

2018.12.14

@ : Nopop Component

EMI@,ESD@,RF@ : EMI/ESD/RF part

CONN@ : Connector Component

@EMI@,@ESD@,@RF@ : Total debug Component

3 3

CNVI@:For WLAN

NOCP@/OCP@:For Hinge up OCP

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2018/03/29 2019/03/29

2018/03/29 2019/03/29

2018/03/29 2019/03/29

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date : Sheet of

Date : Sheet of

D

Date : Sheet of

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

LA-G881P

LA-G881P

LA-G881P

E

1.0

1.0

1 101Tuesday, January 08, 201 9

1 101Tuesday, January 08, 201 9

1 101Tuesday, January 08, 201 9

1.0

A

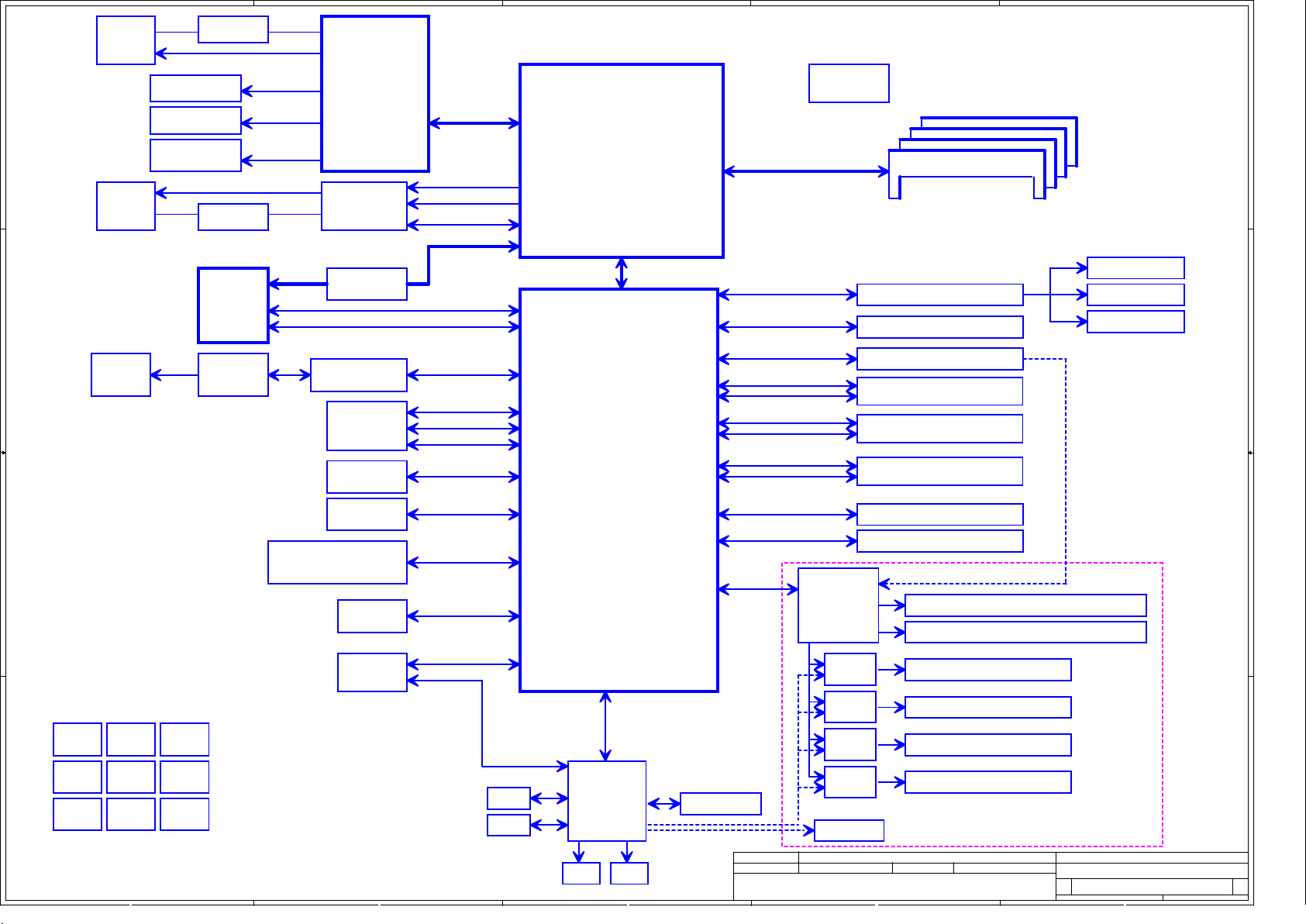

HDMI 2.0

P.30

I2C

DP4+3

DP 1.4

eDP 1.3

I2C/USB2

Thunderbolt

Alpine Ridge SP

USB3.1

TypeC

connector

1 1

USB3.1

TypeC

connector

USB PD

Mini DP

connector

HDMI

connector

eDP panel

support G-SYNC

CYPD4126

P.26

P.27

P.25

CIO/USB3.1

USB PD

TPS65982DC

B

DGFF CARD

N18E-G1

N18E-G2

N18E-G3

P.28~ 29P.30

P.46

PEG(Gen3)x8

port8~port15

DP 1.4 (DDI 1)

DP 1.4 (DDI 2)

PCIE(Gen3)x4

port21~port24

C

Block Diagram

P.7~1 5

Intel CPU

Coffee Lake-S

LGA881P

95W

FFS

KXCNL-1010

Memory Bus 2DPC

1.2V DDR4 2133 MHz

P.36

D

DDR4-SODIMM x4

E

P.12~ 15

PEG(Gen3)x4

P.31

Caldera

connector

2 2

3 3

RJ45

connector

P.33

Transformer

QVPA2014R

2.5GB

P.33

30 pin connector with

cable 2.5 HDD x1

PCIe re-driver

DS80PCI402

2.5 Gigabit LAN

RTL8125-CG

M.2 2230

WiFi + BT

Intel/Killer

SSD1 M.2 2280

PCIe+SATA

SSD2 M.2 2280

PCIe+SATA

SPI ROM

128Mbit

P.32

P.33

P.34

P.35

P.35

P.36

P.17

P.39

Touch pad

port4~port7

USB3.0 port8

USB2.0 port3

PCI-E port15

PCI-E port16

USB2.0 port14

CNVi

PCI-E port 17~20

SATA 3.0

PCI-E port 09~12

SATA3.0

SATA3.0

option:HDD

SPI

I2C

DMI x 4

Intel PCH

CNL PCH-H

BGA 874

Z390

P.16~ 22

USB2.0 port4

USB2.0 port10

USB2.0 port7

USB3.0 port6

USB2.0 port1

USB3.0 port7

USB2.0 port2

USB3.0 port5

USB2.0 port8

USB2.0 port9

ISH

HD Audio

Audio codec

Realtek

ALC3282

I2S

AMP TI

TAS2557

AlienFX / ELC , STM32F070CB

Keyboard

Digital camera(with digital MIC)

USB connector 1 , left side

USB3.0(Gen1) with power share

USB TypeA connector 2

USB3.0(Gen1) right side

USB TypeA connector 3

USB3.0(Gen1) Right side

Tobii (17" only)

Gyro+Accel Sensor

digital MIC

Headphone/MIC Global headset combo JACK

Headphone/MIC Retaskable combo JACK

Speaker

P.38

P.41

P.26

P.27

P.27

P.25

P.23

Head/B

Tron/B

PWR/B

P.46

P.39

P.39

AMP TI

TAS2557

DC in

Battery

3V/5V

4 4

System

1.2V

1.00V

2.5V

CPU

Vcore

dGPU

Core

Charger

dGPU

1.35V

A

B

PS2

KC3810

KC3810

P.42

P.42

eSPI Bus

I2C

FAN1 FAN2

ENE

KB95 42QB

P.43

C

SMBI2C

Thermal Sensor

SPI

AMP TI

TAS2557

AMP TI

P.37

TAS2557

Hall Sensor

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE P ROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE P ROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE P ROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET M AY NOT BE TRANS FERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET M AY NOT BE TRANS FERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET M AY NOT BE TRANS FERED FROM THE CUSTODY OF TH E COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO A NY THIRD PARTY WITHOUT PRIOR WRITTE N CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO A NY THIRD PARTY WITHOUT PRIOR WRITTE N CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO A NY THIRD PARTY WITHOUT PRIOR WRITTE N CONSENT OF COMPAL ELECTRONICS, INC.

2018/03/29 2019/03/29

2018/03/29 2019/03/29

2018/03/29 2019/03/29

Speaker

Speaker

Speaker

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Audio/B

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Block Diagrams

Block Diagrams

Block Diagrams

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

LA-G881P

LA-G881P

LA-G881P

Date : Sheet of

Date : Sheet of

Date : Sheet of

E

2 101Tuesday, January 08, 2019

2 101Tuesday, January 08, 2019

2 101Tuesday, January 08, 2019

1.0

1.0

1.0

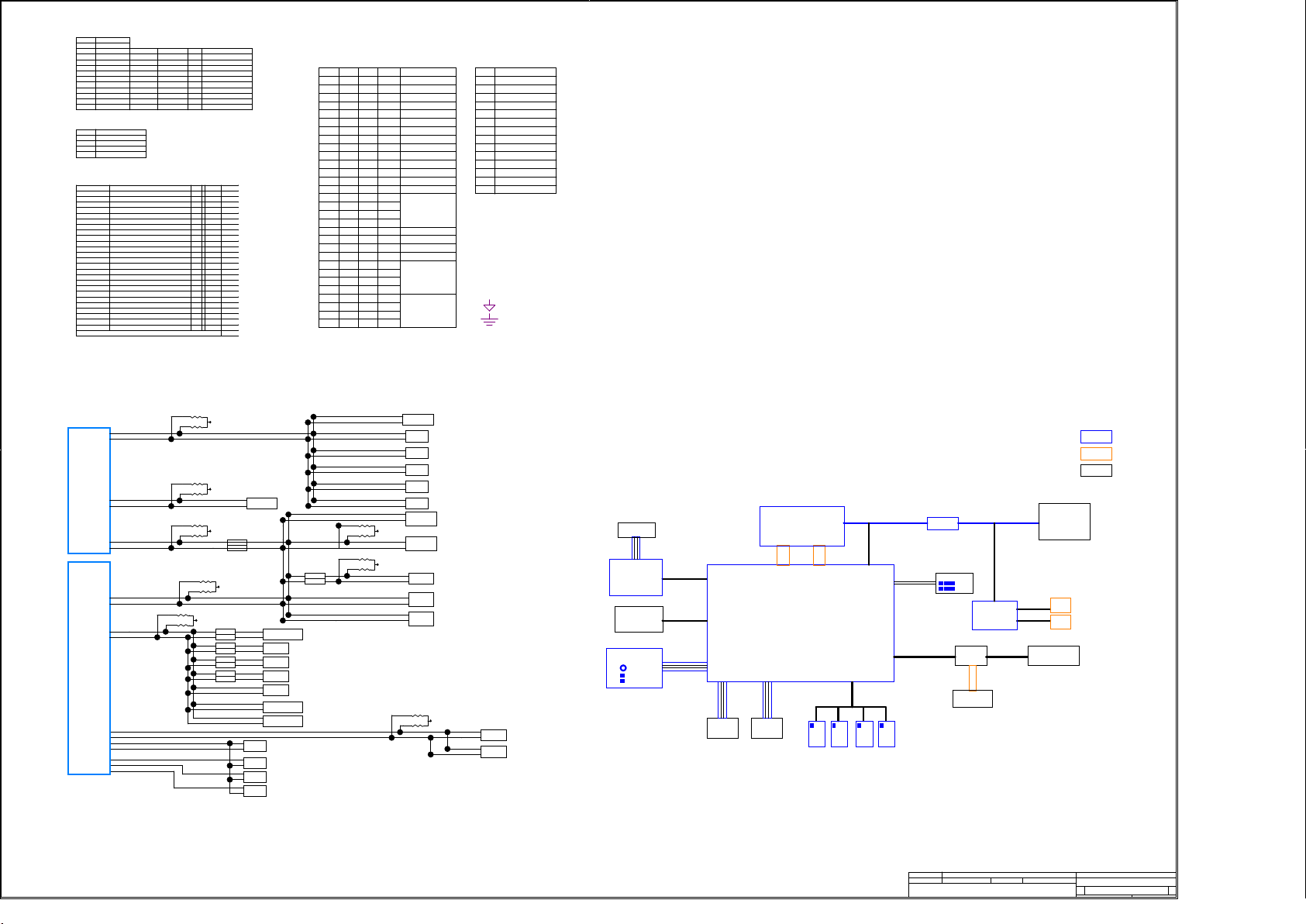

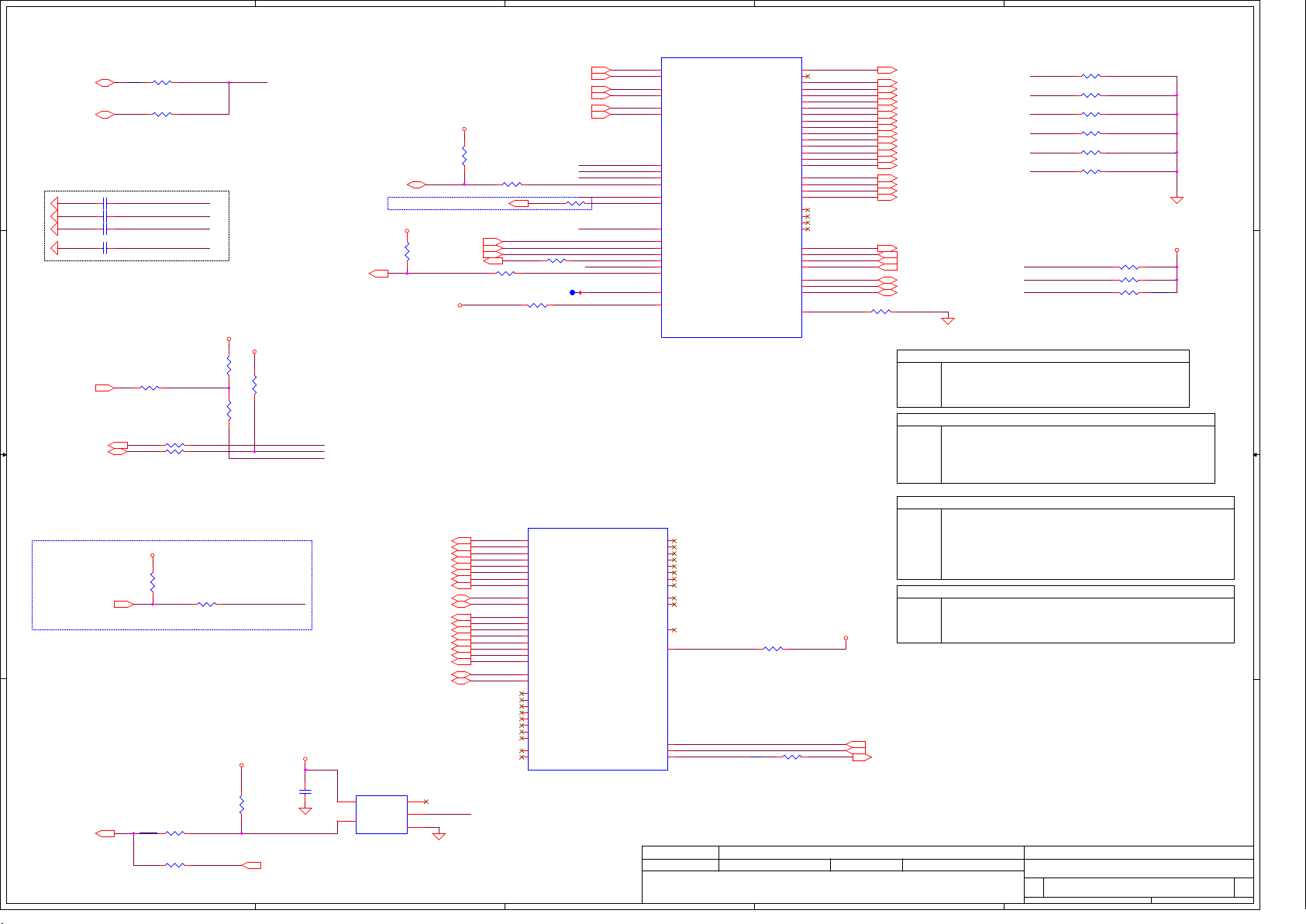

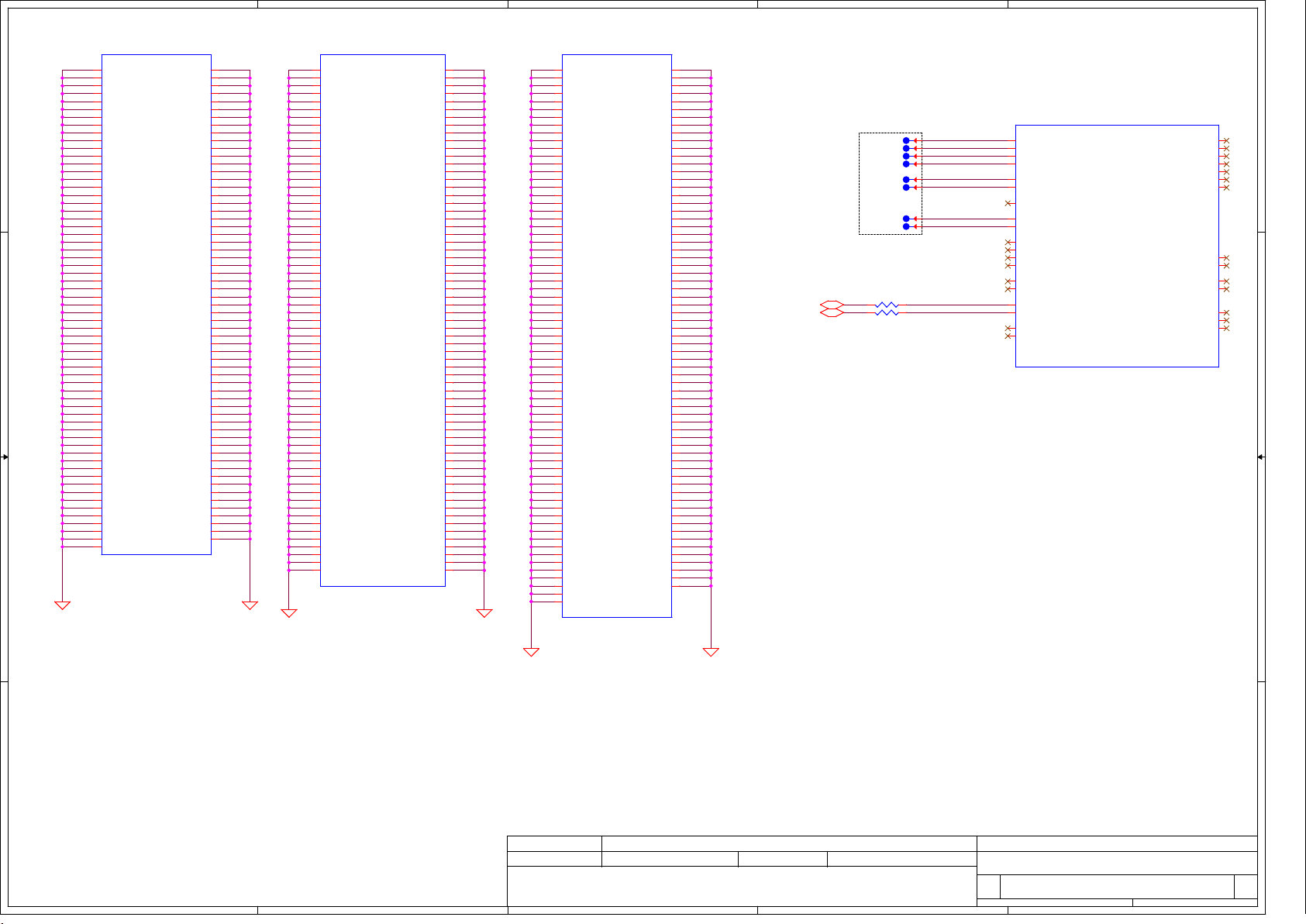

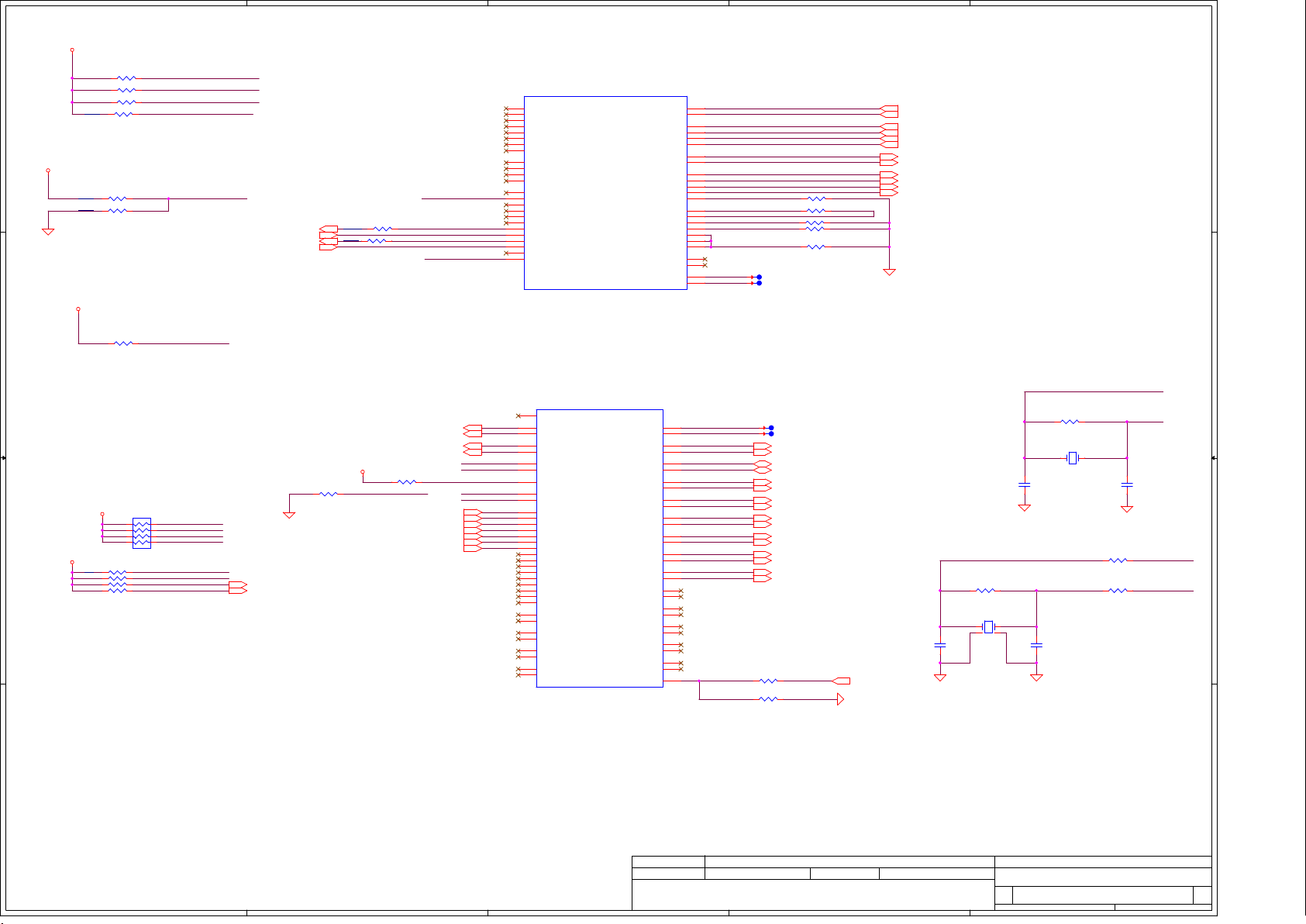

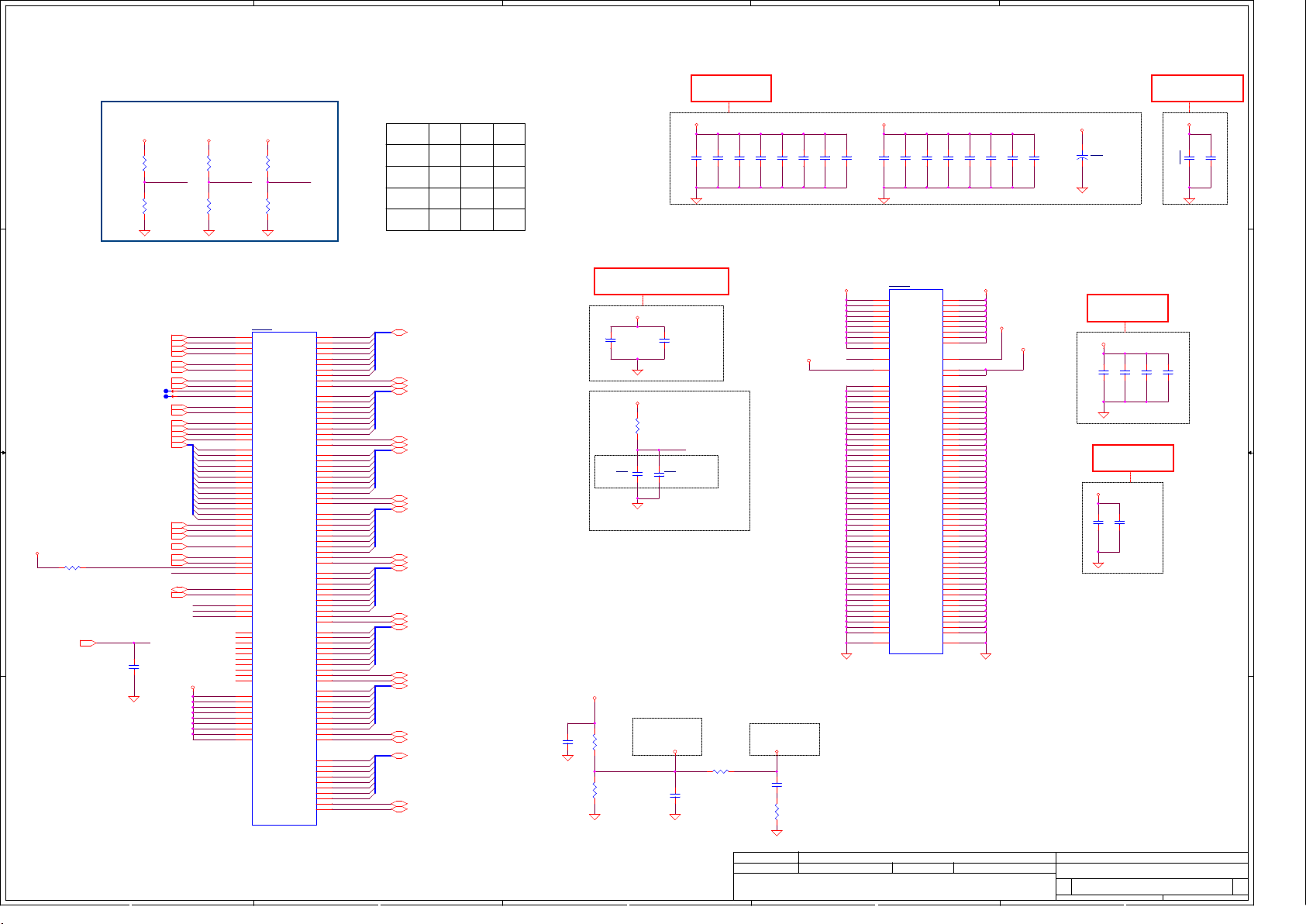

Board ID Table for AD channel

Vcc 3.3V +/- 1%

100K +/- 1%Ra

Board ID

Rb V min

0

0 0.000 V

1

12K +/- 1%

2

15K +/- 1%

3

20K +/- 1%

27K +/- 1%

4

33K +/- 1%

5

43K +/- 1%

6

7 56K +/- 1%

8975K +/- 1% 1.398V

Board ID table

PCB Revision

NV

0

EVT

1

DVT-1

2

DVT-2

3

Pilot

Voltage Rails

Power Plane Description

VIN

Adapter power supply

BATT+

Battery power supply

+19VB

AC or battery power rail for power circuit

+VCC_COR E

Core voltage for CPU

Sliced graphics power rail

+VCC_GT

+0.6VS_VTT DDR +0.6VS power rail for DDR terminator

+1VALW System +1VALW power rail

+1V_PRI M System +1V ALW power rail

+VCCI O +1.0VS IO power rail

+VGA_PCI E +1.0VS power rail for GPU

+MEM_GFX +1.5VS power rail for GPU

DDR-IV +1.2V power rail+1.2V_V DDQ

+1VS_VCCST

+1.0V power rail for CPU

+1VS_VCCSTG

+1.0VS power rail for CPU

+3VALW System +3VALW always on power rail

+3VLP +19VB to +3VLP power rail for suspend power

+3VALW_DS W +3VALW power for PCH DSW rails

+3V_LAN +3VALW power for LAN power rails

+3VS

System +3VS power rail

+1.8VALW +1.8VALW power rail for PCH

+3VS power rail for GPU+3VGS

+5VALW

System +5VALW power rail

+5VS System +5VS power rail

RTC power

+3VL_RTC

System Agent power rail

+VCC_SA

Note : O N* means that this power plane is ON only with AC power available, otherwise it is OFF

V typ

AD_BID

AD_BIDVAD_BID

0.000V 0.300V

0.347V

0.423V 0.430V

0.541V

0.691V

0.807V

0.978V 0.992V

1.169V

1.634V 1.667V

0.360V

0.354V

0.438V

0.550V

0.559V

0.713V

0.702V

0.819V

0.831V

1.006V

1.200V

1.185V

1.414V 1.430V0x65 - 0x76

S0S3S4 / S5

N/A

N/A

N/A

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

max

EC AD3

0x00 - 0x13

0x14 - 0x1E

0x1F - 0x25

0x26 - 0x30

0x31 - 0x3A

0x3B - 0x45

0x46 - 0x54

0x55 - 0x64

0x77 - 0x87100K +/- 1% 1.650V

N/A

N/A

N/A

N/A

N/A

N/A

OFF

OFF

OFF

OFF

OFF

OFF

ON*ONON

ON*

ON

OFF

OFF

OFF

OFF

OFF

OFF

OFF

ON

OFF

ON

OFF

OFF

ON*

ON

ON

ON

ON*

ON

ON*

ON

OFF

OFF

OFF

OFF

OFF

OFF

ON*

ON

OFF

OFF

ON

ON

OFFOFFON

PCH-H Z390

HSIO

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

USB3.1

10

2

3

4

5

6

7

8

9

PCIe SATA3

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

Function

JUSB3

JUSB1(Powershare)

JUSB2

Caldera

JSSD2 , 2280

SATA/PCIe x4

0a

1a

JHDD

0b

1b

LAN

2

3

WLAN

4

5

JSSD1 , 2280

SATA/PCIe x4

Thunderbolt

Function

USB2

1

JUSB1(Powershare)1

2

JUSB2

3

Caldera

4

ELC

5

6

7

Camera

8

JUSB3

9

Tobii

10

Per-key

Thunderbolt PD

11

12

13

Bluetooth

14

Symbol Note :

A

Digital Ground

Analog Ground

1K

2.2K

2.2K

1K

499

499

1K

1K

2.2K

2.2K

+3VALW

+3VS

+3VS

SMBUS Address [ 0x6A]

11

PI6CEQ20200

10

+3V_PCH

N-MOS

N-MOS

+3VS

0 ohm

SCL

0 ohm

SDA

100 ohm

100 ohm

0 ohm PUS1

0 ohm

0 ohm PUS2

0 ohm

AMP

TAS2557

AMP

TAS2557

AMP

TAS2557

AMP

TAS2557

EC_SMB_CK2

EC_SMB_DA 2

4

3

5

6

22

21

22

21

B5

A5

50

49

11

10

PU703

Power Charger

PBATT1

ISL95338

ISL95338

UT4

TPS65982

UT6

DS80PCI402S Q

UT7

PI6CEQ20200

SMBUS Address [?]

N-MOS

N-MOS

SMBUS Address [ 0x12]

SMBUS Address [ 0x16]

SMBUS Address [ 0x90]

SMBUS Address [ 0x92]

SMBUS Address [ 0x70]

SMBUS Address [0x]

SMBUS Address [0x]

SMBUS Address [ 0x9A]

BE26

PCH_SMBCLK

BF26

1 1

Cannon Lak e

PCH-H

ENE

KB9542Q B

PCH_SMBDATA

BF25

SML0CLK

BE24

SML0DATA

BF27

SML1CLK

BE27

SML1DATA

79

EC_SMB_CK2

80

EC_SMB_DA 2

77

EC_SMB_CK1

78

EC_SMB_DA 1

17

EC_ESB_CLK

18

EC_ESB_DAT

119/120/12 6

AMP_SPI_MISO/AMP_SPI_MOSI/A MP_SPI _SCL K

128

AMP_SPI_CS_L1

68

AMP_SPI_CS_L2

34

AMP_SPI_CS_R1

15

AMP_SPI_CS_R2

4.7K

4.7K

4.7K

4.7K

VGA_SMB_CK2

VGA_SMB_DA2

4

Free Fall Sensor

SMBUS Address [ 0x1D]

6

253

DIMM1

SMBUS Address [ 0xA0]

254

253

DIMM2

SMBUS Address [ 0xA2]

254

253

DIMM3

SMBUS Address [ 0xA4]

254

253

DIMM4

SMBUS Address [ 0xA6]

254

15

JTP

SMBUS Address [0x2C]

16

10

U2407

SMBUS Address [ 0x9A]

Thermal sensor

9

+3VS

U2408

SMBUS Address [ 0x98]

8

Thermal sensor

7

+3VS

UG9

BJ8

SMBUS Address [0x9E]

GPU

BH8

UM8

SMBUS Address [0xB2]

PCIE redriver

50

49

16

JPK

SMBUS Address [0xC2]

Per-key KB

17

4.7k

+3VALW

4.7k

UE6

1

KB3810

4

UE10

1

KB3810

4

Speaker x4

Audio/B

Lid +Codec

AMP x4 +AMP PWR

Battery

PWR TBN/B

on / off SW

LED x2

Default:FPC

DTC:PCB

Wire 30 Pin

Wire 13 Pin

FFC 6 Pin

Coaxia/wire 20 pin

Fbeam FPC 68 Pin x2

JAUDIO

JPWR

JHDD

2.5" HDD

20 Pin

Per-key

Keyboard

DGFF

JDGFF1 JDGFF 2

M/B

Backlight FPC

6 Pin

KSI/KSO FPC

20 Pin

Tron light

LED x 1

Coaxial/Wir e

30/ 40 Pin(eDP+MIC+Camera)

JTRON

Wire

24Pin

6 Pin6 Pin 6 Pin6 Pin

Tron light

LED x 1

LED x 1

Wire 10Pin

Alien Head 6Pin+LCDVDD 4Pin

FFC 16 Pi n

JTP

Wire 6 Pin

Tron light

Tron light

LED x 1

Hinge

TP module

LED x 6

Tobii Host

FPC

Tobii Eye Sensor

Coaxial/Wire(eDP+LC DVDD)

30 Pin(60Hz)

40 Pin(144Hz)

Wire 14Pin

(Alien Head+MIC+Camera)

Function/B

Thermal sensor

Wire 2 Pin

4Pin - 2Pin

30 Pin

|

24 Pin

FFC 6 Pin

FFC 10 Pi n

Tobii Illumination

Panel

Head/B

LEDx2

Cemera

PCB

FPC

Module

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Compal Secret Data

Compal Secret Data

Compal Secret Data

2018/03/29 2019/03/29

2018/03/29 2019/03/29

2018/03/29 2019/03/29

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Notes List

Notes List

Notes List

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

LA-G881P

LA-G881P

LA-G881P

Date: Sheet o f

Date: Sheet o f

Date: Sheet o f

1.0

1.0

1.0

3 101Tuesday, January 08, 2019

3 101Tuesday, January 08, 2019

3 101Tuesday, January 08, 2019

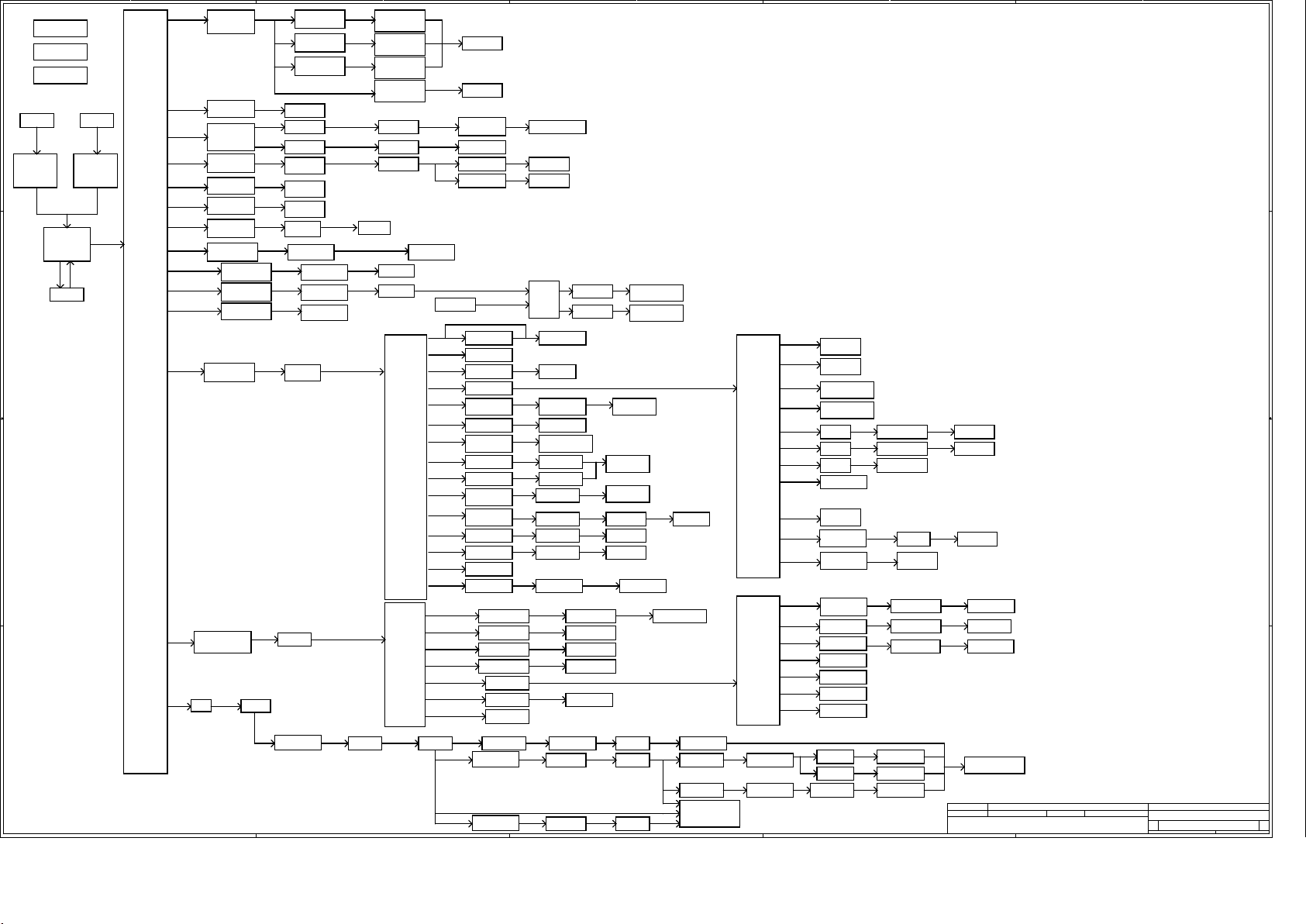

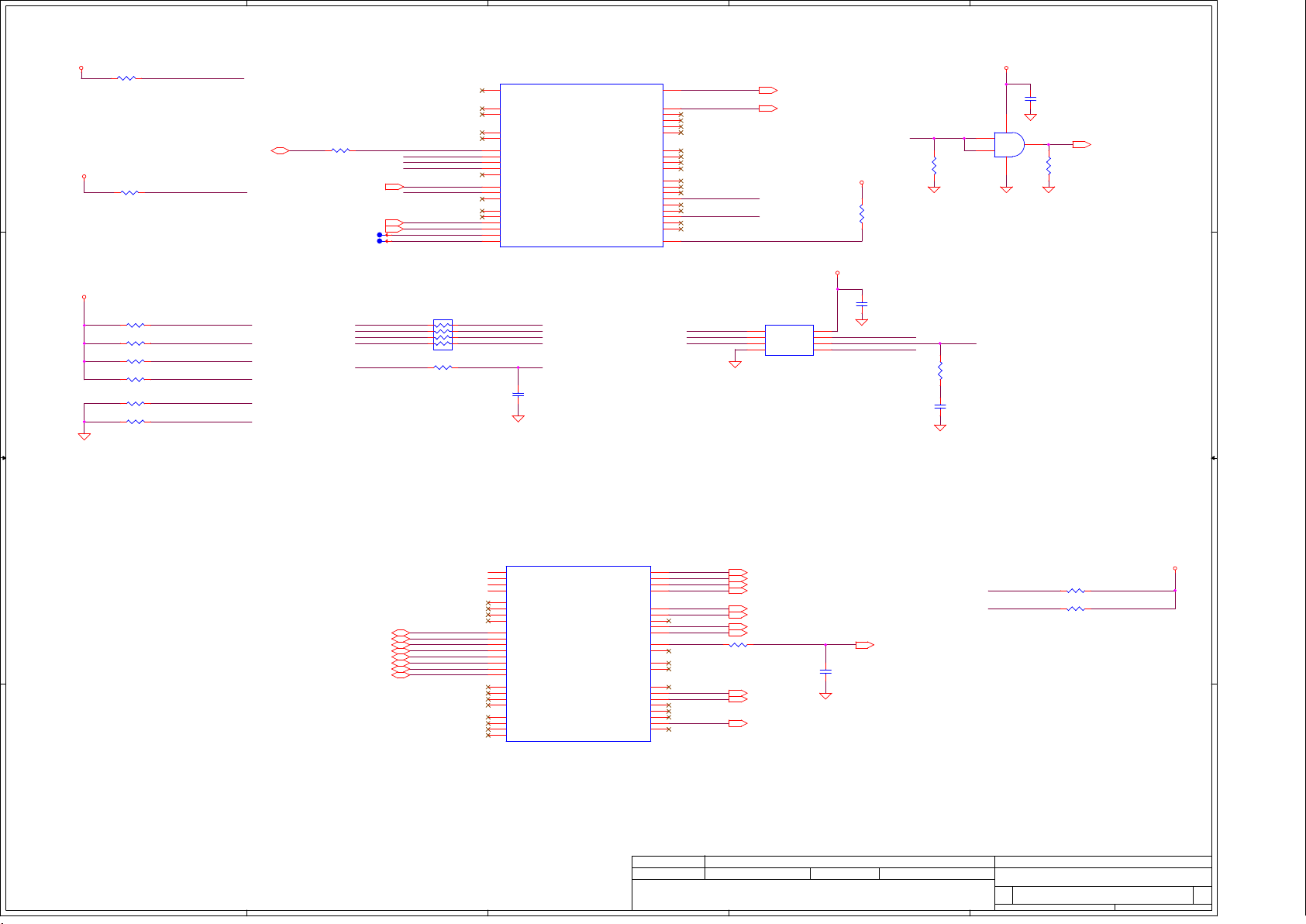

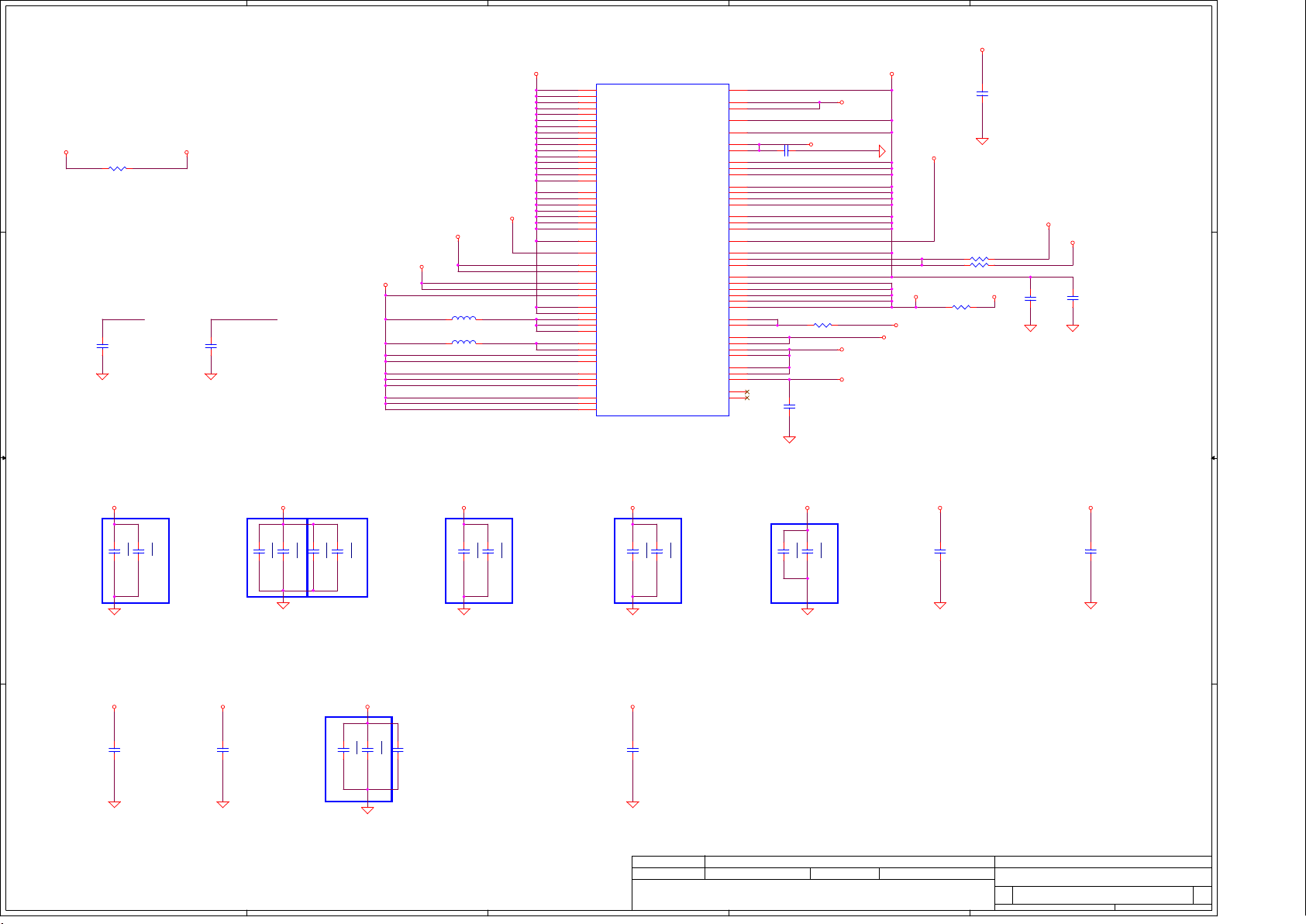

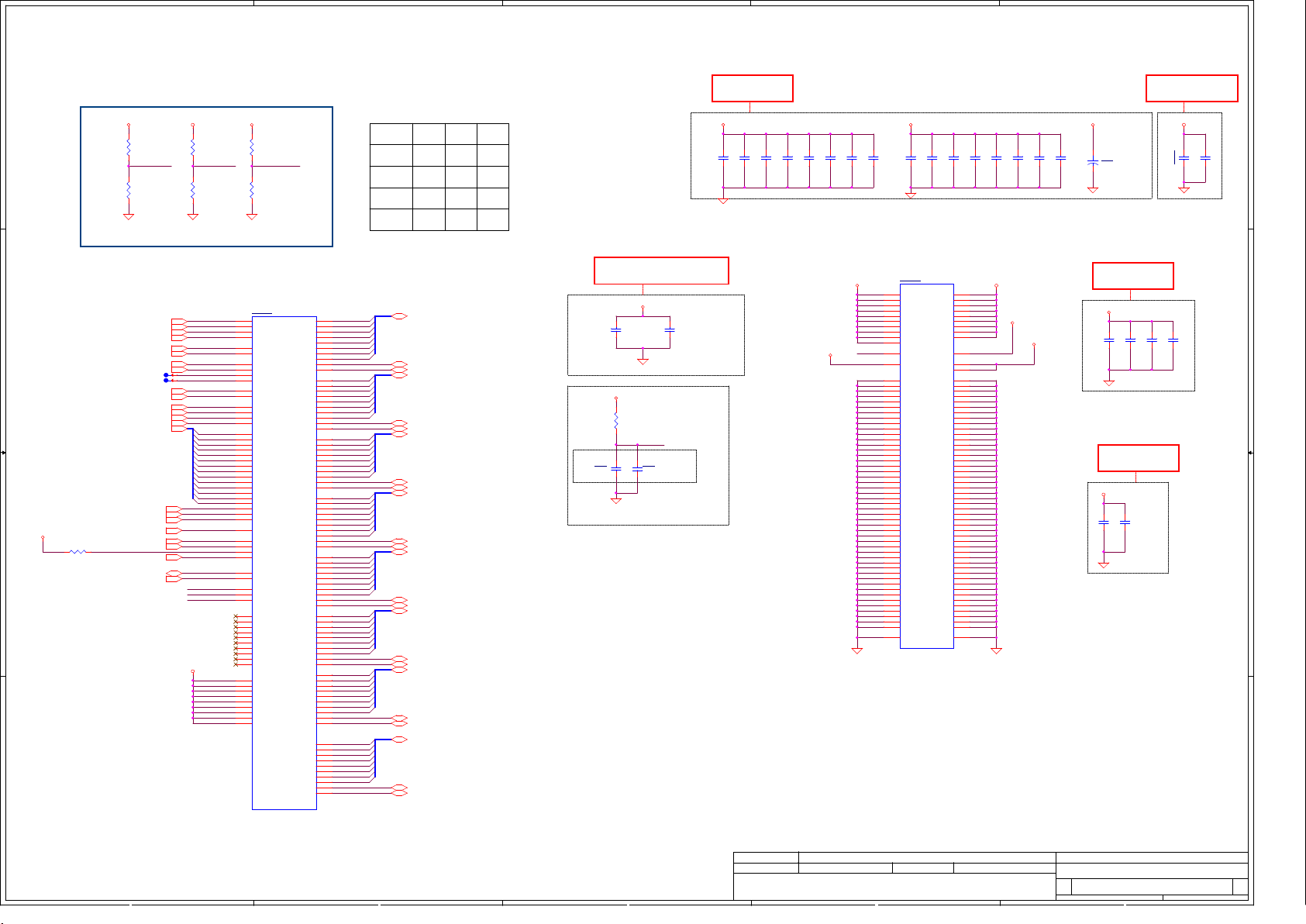

5

IMVP_VR_ON

ISL95829CH RTZ

MB

(PUZ01)

Audio Board

DGFF Board

IMVP_VR_ON

SYSON

PCH_PWR _EN

NVVDD1_EN

NVVDD2_EN

FBVDD/Q_EN

NVVDD2_PGOOD

PCH_PWR_EN

3/5V_B+

(PU301)

3/5V_B+

TPS512 25CRUKR

(PU301)

PQ8 B+_BIAS

ISL95870 BHRZ

(PUA01)

RT8207PGQW

(PU201)

TPS512 12DSCR

(PU101)

UP9511PQG J

(PU6000)

UP1666 QQKF

(PU6400)

SY8286RAC

(PU509)

RT8812AGQW

(PUW1)

SY8286RAC

(PU801)

SY8286RAC

(PU1801)

Fuse +INV_PWR _SRC

EC_EN_AMP

D D

ADAPTER

ISL95338HRT Z

(PUS1)

ADAPTER

ISL95338HRT Z

(PUS2)

+SDC_IN

CHARGE R

ISL88739AHR Z

(PU703)

+PWR_SRC

ISL88739A

BATTERY

C C

B B

A A

5

ISL6617CR Z

(PUI07)

ISL6617CR Z

(PUI08)

ISL6617CR Z

(PUI09)

+VCCSA

13600mA

+1.2VP

2100mA

+0.6VSP

5820mA

+1VALWP

118000mA

+NVVDD 1

39000mA

+NVVDD 2

4480mA

+VCCIOP +VCC IO

23000mA

+1.35VS_VG AP

2100mA

2100mA

9128mA

+3VALWP

13330mA

+5VALWP

SY8286C RAC

(PU501)

(PJP200 PJP201)

(PJP102 PJP103)

(PJPF02)SUSP#

+1.0VS_VGAP

+1.8VSP

(PJP301)TPS512 25CRUKR

(PJP302 PJP303)

4400mA

(PJP202)

(PJPW2, PJPW3, PJPW4)

(PJP801)

(PJP1802)

(PJP304)

+5VP_AMP

4

SIC632CDT1 GE3

(PUI01)

(PUI02)

SIC632CDT1 GE3

(PUI01)

(PUI02)

SIC632CDT1 GE3

(PUI01)

(PUI02)

SIC632CDT1 GE3

(PU507)

(PU510)

+1.2V_DD R

+0.6VS

+1VALW

+PEX_V DD

+1.8VALW

+3VALW

+5VALW

(PJP502)

4

+1.35VS_VG A

PCH_PWR _EN

SUSP#

EN_WOL#

3V_ELC_O N

PCH_ENVD D

SUSP#

PCH_PWR _EN

USB_PWR_ EN

PWRSHARE_EN_ EC#

USB_PWR_ EN

SUSP#

5VS_GATE

+5V_AMP

+VCC_C ORE

+VCCGT

SYSON

SUSP#

+1V8_AON

APE8937GN2

(UZ21)

JDIMM1/2 /3/ 4

TPS22961

(U19)

TPS22961

(U20)

1V8_AON_EN

KB9542 QB

(UE5)

KC3810

(UE6/ UE10)

SY6288C20 AAC

(U18)

AOZ1331

(U17)

SY6288D20 AAC

(UL14)

1V8_MAIN_EN

+1.2V_V CCPLL_OC

+VCCST

+VCCSTG

AOZ1331

(UG12)

+EC_VC CA

+3V_PC H

+3VALW_LAN

+3VALW_PDRT53

SY6288C20 AAC

(UE9)

RT95

RT97

AOZ1334DI-02

(UV64)

AOZ1334DI-02

(U16)

(RT111)TP_EN

AOZ1336 TP Conn.

RN22

DS80PCI40 2SQ

(UT6)

RT9059G SP

(PU1801)

RT9059G SP

(PU2501)

SY6288C20 AAC

(UU3)

TPS2546 RTER

(UU1)

TPS258 10RVCR

(UU7)

AOZ1331

(U17)

SY6288D20 AAC

(UE12)

+3.3V_EL C

+3VALW_TBT ALPINE- RIDGE

+3VS_TBT _SX

+LCDVD D

+3VSP_S SD

+3VS_T OUCH

+3V_WLAN

+1.8VSP

(PJP1301)PM_SLP_S4#

JKB1

EM5209VF

(UA11)

RT9058-33G X

RT9059G SP

(PU1301)

+5VS_AUDI O

105mA

+3.3VP_AMP +3.3V_AMP

266mA

+1.8VP_AMP +1.8V_AMP

3

+1V8_AON

+1V8_MAIN N17E-G1 G B4-256

N17E-G1 GB4-256

(UG9)

(UG9)

(J5)

RTL8125-C G

(UL1)

(UT1)

EDP FC Conn.

(JFC)

(JP6)

+3VALW_SS D

(JTP)(UT5)

NGFF Conn.

(JWLAN)

(PJP1802)

+1.8VALW

+2.5V_MEMP

(PJP2502)

+5V_US B_PWR2

+5V_US B_PWR1

+5V_U SBC_VBUS

(J4)

+5V_TOBII

(PJP402)

(PJP1303)

3

NGFF Conn.

(JSSD1/2)

+2.5V _MEM

+5VS_ AVDD1LA31

EM5209VF

(UA11)(PU401)

AOZ1336

(UT5)

TAS2557YZR

(UA3/UA5/UA6/UA7 )

+3VS

+5VS

+3VS_AUDI O

+1.8VS_AUDI O

F75305M

(U2407)

F75397M

(U2408)

PI6CEQ20200L IEX

(UM4)

DS80PCI4 02

(UM8)

(RT111)TP_EN

AOZ1336 TP Conn.

(UT5)

RN20

RH614

KXCNL-10 10

(US1)

JEDP Conn.

(JEDP)

AP2337SA-7

(UV18)

3V3_SYS_EN

TPS2296 1DNYR

(UG14)

RT9297GQW

(PU1201)

SI3456DD V

(Q2409)

FV3

(JP3)

+5V_H DD

+3VS_TOUCH

+3V_WLAN

+3VS_ACC

JPK

JKBB L

JKB3

LA33

LA32

+3VS_ CPVDD

+3.3V_1.8V _DVDD

+1.8VS_ AVDD2RA201

2

(JTP)

NGFF Conn.

(JWLAN)

+3VS_D P

JDP Conn.

+3V3_SYS

+12VP +1 2V_FAN

+5VS_TP_ LED

(PJP1202)

JTP Conn.

+HDMI_5V_OU T JHDMI Conn.

ALC3282-CG

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

(UA1)

Compal Secret Data

Compal Secret Data

Compal Secret Data

2018/03 /29 2019/03 /29

2018/03 /29 2019/03 /29

2018/03 /29 2019/03 /29

Deciphered Date

Deciphered Date

Deciphered Date

1

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Power MAP

Power MAP

Power MAP

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

LA-G881P

LA-G881P

LA-G881P

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

4 101Tuesday, January 08, 2019

4 101Tuesday, January 08, 2019

4 101Tuesday, January 08, 2019

1.0

1.0

1.0

5

+5VALW

PR14

PQ3

B+_BIAS

SI3457CDV

D D

PMOS

DGPU_PWR_EN

1

ACIN

110 110

POK

ACIN

A1

AC

VIN

MODE

BATT+

DC

MODE

B1

C C

BATT+

5

PU700

BQ24780SRU YR

CHARGER

PQ703

NMOS

7

A2

PU100

B+

TPS51225

CRUKR

B2

SW1

A5

B6

+3VALW

+5VALW

+3VLP,VL

B3

A3

VCOUT0_PH#

A4

B5

EC_ON

A6

B4

ON/OFFBTN#

UE5

EC90 22QD

104

112

114

+1VALWP_PGOOD

122

101

121

15

B B

VR_PWRGD

IMVP_VR_ ON

16

IMVP_VR_ ON

for power down sequence

A A

Q8A

@

PM_SLP_ S4#

Q7A

@

Q7B

@

Q8B

@

DMN65D8LDW

(Q9)

@

5

IMVP_VR_ ON

H_VCCST_PWR GDPM_SLP_ S3#

SUSP#

SYSON

4

123

71

38

6

97

74

127

100

13

107

H_VCCST_PWR GD

SUSACK# 9

PCH_DPWROK

EC_RSMRST#

PCIRST#

PCH_PWR_EN

15

ME_SUS_PWR_A CK

PM_SLP_SUS#

PBTN_ OUT#

PM_SLP_ S5#

PM_SLP_ S3#

7

10

4

+3VALW +1VALWP_PGOOD

9

PR301

3

ACIN1_AV_IN

9

TC7SH08 FU

(UH3)

TPS512212

(PU300)

SY6288C20AAC

(U18)

11

7a

8

12

14

+1VALW

+3V_PCH

32

PM_SLP_ S4#

73

15

SYSON

13a

SYSON

SM_PG_CTRL

+3VS

13

95

116

14a

AOZ1331

SUSP#

(U17)

+5VS, +3VS

SY8286RAC

SUSP#

(PU509)

+VCCIO

APE8937GN2

SUSP#

(UZ21)

+1.2V_VCCPLL_OC

TPS22961DNYR

SUSP#

(U20)

+VCCSTG

TPS22961DNYR

(U19)

8

RT8207MZQW

(PU201)

7

43,44,45

7

SY8003DF C

(PU13 00)

+VCCST

+2.5V _MEMP

+1.2VP

+0.6VSP

13b

15a

SVID Bus

+3VS

48

PR515

ISL95855

(PU500)

47

VR_PWRGD

SIC632

(PU502/503/504)

16

SIC632

(PU507/510)

SIC531

(PU511)

PR523

AC_PRESENT

18

19

PCH_PWROK

SM_PG_CTRL

+VCC_CORE

+VCCGT

+VCCSA

3

SYS_PWROK

PCH_PLTRST#

KB_RST #

UC1

15

SOC

H13RH154

CPU1

BD19

BB15

BB13

AT13106

AJ44

AJ39

AW27

DGPU_PWROK

GPU_GC6_FB_EN

BA1314

AW15

BB19

PCH

UH1

AY1

BC24 BL26

AV11

BA11

BB27

17

AW11

AT172

BD15

BT13

BH29

BH31

BH32

DGPU_HOLD_RST #

AL36

PCH_PLTRST#

BB27

G9

SVID Bus

UE6

KC38 10

+1.35VS_VGA_PGOOD

QG5

SYS_PEX_RST_ MON#

UG10

G8

PEX_CLKREQ#CLKREQ#_GPU

GPU power on

PCH_PLTRST#

CALDER A_RST#

16

CALDERA_ PWRGD

15

DGPU_PWROK

19

BB5

GPU

UG9

BE2

G10

BE1

G0 G1 G2 G4 G5 G6 G7

UM3

TC7SH08 FU

2

1V8_MAIN_EN

+1V8_AON

Compal Net

+1.8VS_AON

+1.8VS_ MAIN

+3V3_SYS

+NVVDD1

+NVVDD2

+PEX_VDD

+1.35VS_ VGA

CDRA_R ST#

G5A

G4A

UE10

KC3810

G3

15

16

GPU_GC6_FB_EN

+1.0VS_VGA_PGOOD

OVERT#

10

NVVDD2_PGOO D

17

NVVDD1_PGOO D

19

+3V3_SYS

20

22

G1A

G1

G1

G2

G3

G4

G5

G6

G7

22

JCDRA

Caldera

2

1V8_EN

FBVDD/Q_EN

PEX_VDD_EN

1.8VS_PGOOD

NVVDD_EN

1.8VS_PGOOD

G0A

Will M odify

3V3_SYS_EN

G2

1V8_MAIN_EN

1V8_AON_EN

+3VS

PR802

DG5

DG5

Will M odify

NVVDD1_PGOO D

PR823

NVVDD_EN

G0A

Will M odify

PR6103

@

10K

PG515

PU802

UG12

PR6201

@

+1.8VALW

G6A

+1.0VS_VGA_PGOOD

FBVDD/Q_EN

+3VS

PR801

DG6

PR6230

DG3 OVERT#

DG3

NVVDD1_EN

PR6131

SY6288+1V8_MAIN

+1V8_MAIN

+1V8_AON

G0

PR8216

PR821

+1.0VS_VGA_PGOOD

9

PU800

SY8286

NVVDD2_EN

+3V3_SYS

G2

G1

1

+3VS

PR8212

20K

+PEX_VDD

NVVDD2_PGOO D

13

PU6200

NCP81278

+3V3_SYS

PR6107

NVVDD1_PGOO D

13

PU6100 +NVVDD1

NCP81278

G3UG14

GPU power off

PR8204

+1.35VS_VGA_PGOOD

PU8200

RT8812A

G6A

G6

+NVVDD2

G7 G6 G5 G4

+1.35VS_ VGA

G5A

G5

G4A

G4

Compal Net

+1.8VS_AON

+1.8VS_ MAIN

+3V3_SYS

+NVVDD1

+NVVDD2

+PEX_VDD

+1.35VS_ VGA

G7

G1

G2

G3

G4

G5

G6

G7

G3

G2

G1

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

2018/03/29 2019/03/29

2018/03/29 2019/03/29

2018/03/29 2019/03/29

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Power Sequence

Power Sequence

Power Sequence

Size

Size

Size

Document Number Rev

Document Number Rev

Document Number Rev

LA-G881P

LA-G881P

LA-G881P

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

5 101Tuesday, January 08 , 2019

5 101Tuesday, January 08 , 2019

5 101Tuesday, January 08 , 2019

1.0

1.0

1.0

5

4

3

2

1

UC1E

PCH_CPU_BC LK_P<15>

PCH_CPU_BC LK_N<15>

PCH_CPU_PC IBCLK_P<15>

PCH_CPU_PC IBCLK_N<15>

CPU_24MHZ_ P<15>

CPU_24MHZ_ N<15>

1 2

RC4 499_040 2_1%

1 2

RC356 0_040 2_5%

RC5

1 2

20_0402_1 %

TC2

1 2

RC693 51_040 2_1%

H_CPU_SVIDALRT#

VR_SVID_CLK_R

VR_SVID_OUT_R

H_PROCHOT# _R

DDR_VTT_C NTL

@

VCCST_PW EGD_R

CPU_PLTRS T#

PM_DOWN_ R

12

CPU_PECI

THERMTRIP#_ R

PROC_SELECT #

H_CATERR#

+1.05V_VCCST

RC16

RC19

CPU_PECI

12

12

+1.05V_VCCST

12

RC17

100_0402_ 1%

VR_SVID_CLK_R

VR_SVID_OUT_R

H_CPU_SVIDALRT#

+1.05V_VCCST

12

RC3

1K_0402_1 %

H_PROCHOT#<58,82,85,91>

Orion use

+1.05V_VCCST

12

RC2

1K_0402_1 %

H_THERMT RIP#<13>

H_CPUPW RGD<12>

CPU_PLTRS T#<13 >

H_PM_SYNC_R<13>

H_PM_DOW N<13>

+1.05V_VCCST

PROC_DETEC T#<13>

R395 0_0402_5%

1 2

EC_PECI<58>

D D

H_PECI<13>

CC1

CC2

CC3

CC4

R394 0_0402_5%

RC11 43_0402_1%@

ESD@

@ESD@

@ESD@

ESD@

CPU_PLTRS T#

CPU_PECI

H_PM_SYNC_R

H_CPUPW RGD

12

100P_0402 _50V8J

12

5P_0402_5 0V8C

12

100P_0402 _50V8J

12

100P_0402 _50V8J

12

ESD request Close to CPU as possible

C C

56_0402_1 %

R396

VR_SVID_ALRT#_L

VR_SVID_ALRT#<91>

To Power

VR_SVID_CLK<91>

VR_SVID_OUT<91>

1 2

0_0402_5%

220_0402_ 1%

1 2

R397 0_0402_5%

1 2

R398 0_0402_5%

W5

BCLKP

W4

BCLKN

W1

PCI_BCLKP

W2

PCI_BCLKN

K9

CLK24P

J9

CLK24N

E39

VIDALERT#

E38

VIDSCK

E40

VIDSOUT

C39

PROCHOT#

AC36

DDR_VTT_CNTL

AC38

SKTOCC#

U2

VCCST_PWRGD

F8

PROCPWRGD

E7

RESET#

E8

PM_SYNC

D8

PM_DOWN

G7

PECI

D11

THERMTRIP#

AB36

PROC_SELECT#

D13

CATERR#

CFL_S62_IP_CR B_CFLS_LGA

@

PROC_PREQ#

PROC_PRDY#

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_17

CFG_16

CFG_19

CFG_18

BPM#_0

BPM#_1

BPM#_2

BPM#_3

PROC_TDO

PROC_TDI

PROC_TMS

PROC_TCK

PROC_TRST#

CFG_RCOMP

H15

F15

F16

H16

F19

H18

G21

H20

G16

E16

F17

H17

G20

F20

F21

H19

F14

E14

F18

G18

D16

D17

G14

H14

XDP_TDO

H13

XDP_TDI

G12

XDP_TMS

F13

PCH_JTAG_TC K

F11

CPU_XDP_TRS T#

F12

XDP_PREQ#

B9

XDP_PRDY#

B10

CFG_RCOMP

M11

CFG0 <79>

CFG2 <79>

CFG3 <79>

CFG4 <79>

CFG5 <79>

CFG6 <79>

CFG7 <79>

CFG8 <79>

CFG9 <79>

CFG10 <79>

CFG11 <79>

CFG12 <79>

CFG13 <79>

CFG14 <79>

CFG15 <79>

CFG17 <79>

CFG16 <79>

CFG19 <79>

CFG18 <79>

XDP_TDO <1 2,79>

XDP_TDI < 12,79>

XDP_TMS <12,79>

PCH_JTAG_TC K < 12,79>

CPU_XDP_TRS T# <17,79 >

XDP_PREQ# <17,79>

XDP_PRDY# < 17,79>

1 2

RC26 49.9_0402_ 1%

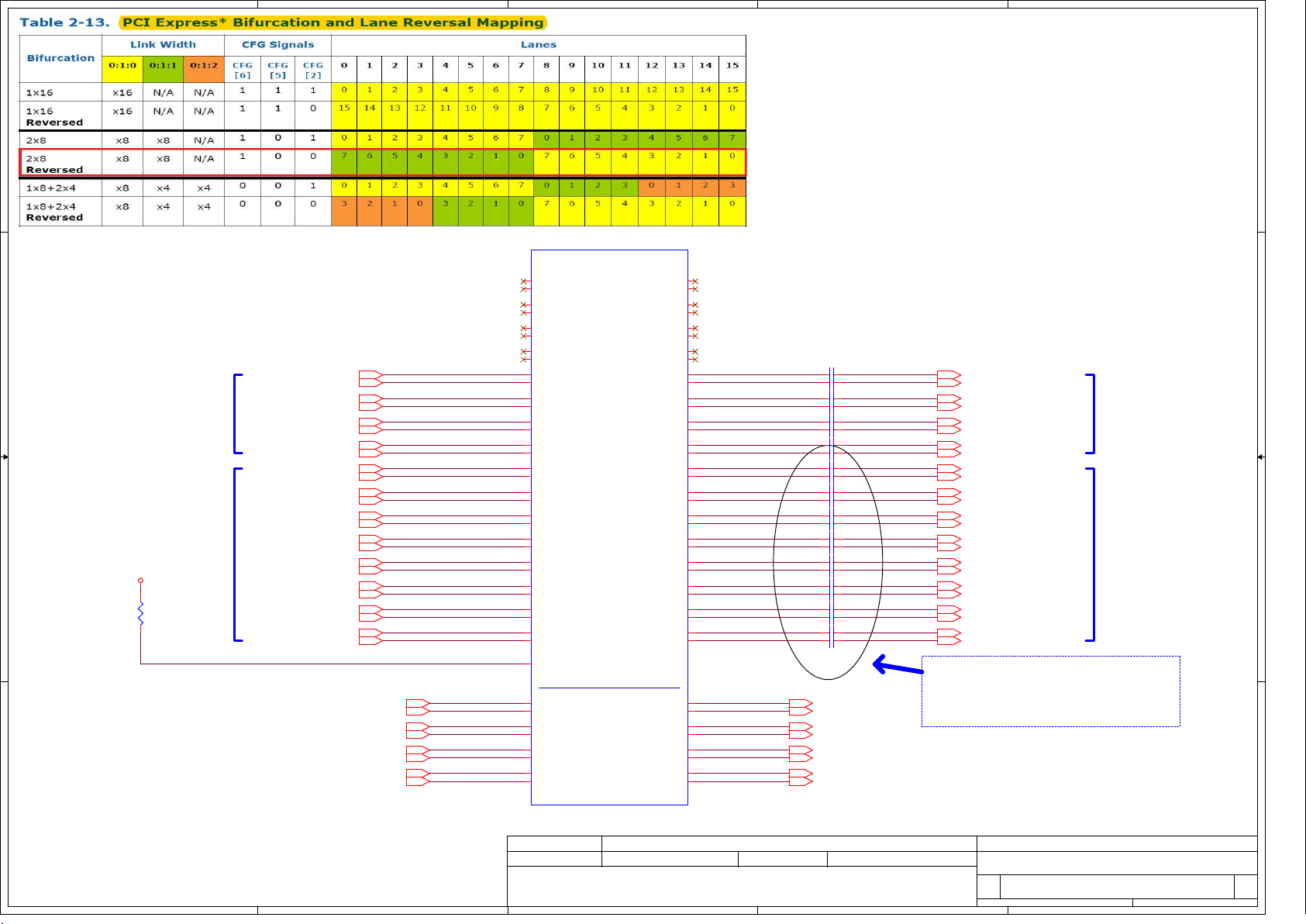

PCI EXPRESS STATIC LANE REVERSAL FOR ALL PEG PORTS

CFG2

Display Port Presence Strap

CFG4

1 2

CFG0

CFG2

CFG4

CFG5

CFG6

CFG7

XDP_TMS

XDP_TDI

XDP_TDO

@

RH637 1K_0402_5%

1 2

RH184 1K_0402_5%

1 2

@

RH185 1K_0402_5%

1 2

RH186 1K_ 0402_5%

1 2

RH187 1K_ 0402_5%

1 2

@

RH188 1K_0402_5%

12

RH10351_0402_5 % CMC@

12

RH49551_0402_5 % CMC@

12

RH627100_0402_ 1% CMC@

CFL-S schematic check list v1.6 P16

1: Normal Operation; Lane # definition

matches socket pin map definition

0:Lane Reversed

*

1 : Disabled; No Physical Display Port

attached to Embedded Display Port

*

0 : Enabled; An external Display Port device is

connected to the Embedded Display Port

+1.05V_VCCST

PCIE Port Bifurcation Straps

To Thunderbolt

CPU_DP1_P0<42>

+1.05V_VCCST

B B

H_VCCST_PW RGD<58,78>

A A

To Power

SM_PG_CTRL<87 >

12

RC12

1K_0402_5 %

1 2

RC13 60.4_040 2_1%

@

1 2

RC684 0_04 02_5%

1 2

RC685 0_04 02_5%

5

@

RH525

330K_0402 _5%

VCCST_PW EGD_R

+3VS

@

12

CH197

0.1U_0402_ 10V7K

PM_SLP_S3# < 12,58,62,78,83,85>

+1.2V_DDR

1

2

For ODT & VTT

power control

UC2

5

4

74AUP1G07GW _TSSOP5

@

CPU_DP1_N 0<42>

CPU_DP1_P1<42>

CPU_DP1_N 1<42>

CPU_DP1_P2<42>

CPU_DP1_N 2<42>

CPU_DP1_P3<42>

CPU_DP1_N 3<42>

CPU_DP1_AUXP<42>

CPU_DP1_AUXN<42>

CPU_DP2_P0<42>

CPU_DP2_N 0<42>

CPU_DP2_P1<42>

CPU_DP2_N 1<42>

CPU_DP2_P2<42>

CPU_DP2_N 2<42>

CPU_DP2_P3<42>

CPU_DP2_N 3<42>

CPU_DP2_AUXP<42>

CPU_DP2_AUXN<42>

1

NC

VCC

Y

4

GND

A

2

3

DDR_VTT_C NTL

UC1D

C21

DDI1_TXP_0

D21

DDI1_TXN_0

D22

DDI1_TXP_1

E22

DDI1_TXN_1

B23

DDI1_TXP_2

A23

DDI1_TXN_2

C23

DDI1_TXP_3

D23

DDI1_TXN_3

B13

DDI1_AUXP

C13

DDI1_AUXN

B18

DDI2_TXP_0

A18

DDI2_TXN_0

D18

DDI2_TXP_1

E18

DDI2_TXN_1

C19

DDI2_TXP_2

D19

DDI2_TXN_2

D20

DDI2_TXP_3

E20

DDI2_TXN_3

A12

DDI2_AUXP

B12

DDI2_AUXN

B14

DDI3_TXP_0

A14

DDI3_TXN_0

C15

DDI3_TXP_1

B15

DDI3_TXN_1

B16

DDI3_TXP_2

A16

DDI3_TXN_2

C17

DDI3_TXP_3

B17

DDI3_TXN_3

B11

DDI3_AUXP

C11

DDI3_AUXN

CFL_S62_IP_CR B_CFLS_LGA

@

E10

EDP_TXP_0

D10

EDP_TXN_0

D9

EDP_TXP_1

C9

EDP_TXN_1

H10

EDP_TXN_2

G10

EDP_TXP_2

G9

EDP_TXN_3

F9

EDP_TXP_3

D12

EDP_AUXP

E12

EDP_AUXN

DISP_RCOMP

D14

EDP_RCOMP

M9

V3

V2

U1

RC10 24.9_0402_1%

EDP_RCOMP

Min Trace Width = 20 mils

Isolation Spacing = 25 mils

Trace Length < 100 mils

CPU_DISPA_SDI

12

1 2

RC1 30_0402_5 %

+VCCIO

RC1 Close to CPU

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2018/03/29 2019/03/29

2018/03/29 2019/03/29

2018/03/29 2019/03/29

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

EDP_DISP_UTIL

PROC_AUDIO_CLK

PROC_AUDIO_SDI

PROC_AUDIO_SDO

CFG[6: 5]

CPU_DISPA_BCLK <12>

CPU_DISPA_SDO <12>

CPU_DISPA_SDI_R <1 2>

2

11: (Default) x16 - Device 1 functions 1 and 2 disabled

10: x8, x8 - Device 1 function 1 enabled ; function 2

disabled

01: Reserved - (Device 1 function 1 disabled ; function

2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

*

PEG DEFER TRAINING

CFG7

1: (Default) PEG Train immediately following xxRESETB

de assertion

*

0: PEG Wait for BIOS for training

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date : Sheet of

Date : Sheet of

Date : Sheet of

Compal Electronics, Inc.

CFL-S JTAG/XDP/DDI

CFL-S JTAG/XDP/DDI

CFL-S JTAG/XDP/DDI

LA-G881P

LA-G881P

LA-G881P

1.0

1.0

6 101Tuesday, January 08, 201 9

6 101Tuesday, January 08, 201 9

1

6 101Tuesday, January 08, 201 9

1.0

5

D D

4

UC1C

3

2

1

B8

PEG_RXP_0

B7

PEG_RXN_0

C7

PEG_RXP_1

C6

PEG_RXN_1

D6

PEG_RXP_2

D5

C C

PEG_CRX _GTX_P11<74>

PEG_CRX _GTX_N11<74>

PEG_CRX _GTX_P10<74>

Caldera TX

GPU TX

B B

PEG_RCOMP

Trace Width = 5 mils

Trace Spacing to Other Signals =15 mils

Trace Length < 600 mils

A A

+VCCIO

12

RC14

24.9_040 2_1%

PEG_RCO MP

PEG_CRX _GTX_N10<74>

PEG_CRX _GTX_P9<74>

PEG_CRX _GTX_N9<74>

PEG_CRX _GTX_P8<74>

PEG_CRX _GTX_N8<74>

PEG_CRX _GTX_P7<37>

PEG_CRX _GTX_N7<37>

PEG_CRX _GTX_P6<37>

PEG_CRX _GTX_N6<37>

PEG_CRX _GTX_P5<37>

PEG_CRX _GTX_N5<37>

PEG_CRX _GTX_P4<37>

PEG_CRX _GTX_N4<37>

PEG_CRX _GTX_P3<37>

PEG_CRX _GTX_N3<37>

PEG_CRX _GTX_P2<37>

PEG_CRX _GTX_N2<37>

PEG_CRX _GTX_P1<37>

PEG_CRX _GTX_N1<37>

PEG_CRX _GTX_P0<37>

PEG_CRX _GTX_N0<37>

DMI_CRX_P TX_P0<14>

DMI_CRX_P TX_N0<14>

DMI_CRX_P TX_P1<14>

DMI_CRX_P TX_N1<14>

DMI_CRX_P TX_P2<14>

DMI_CRX_P TX_N2<14>

DMI_CRX_P TX_P3<14>

DMI_CRX_P TX_N3<14>

DMI_CRX_P TX_P0

DMI_CRX_P TX_N0

DMI_CRX_P TX_P1

DMI_CRX_P TX_N1

DMI_CRX_P TX_P2

DMI_CRX_P TX_N2

DMI_CRX_P TX_P3

DMI_CRX_P TX_N3

PEG_RXN_2

E5

PEG_RXP_3

E4

PEG_RXN_3

F6

PEG_RXP_4

F5

PEG_RXN_4

G5

PEG_RXP_5

G4

PEG_RXN_5

H6

PEG_RXP_6

H5

PEG_RXN_6

J5

PEG_RXP_7

J4

PEG_RXN_7

K6

PEG_RXP_8

K5

PEG_RXN_8

L5

PEG_RXP_9

L4

PEG_RXN_9

M6

PEG_RXP_10

M5

PEG_RXN_10

N5

PEG_RXP_11

N4

PEG_RXN_11

P6

PEG_RXP_12

P5

PEG_RXN_12

R5

PEG_RXP_13

R4

PEG_RXN_13

T6

PEG_RXP_14

T5

PEG_RXN_14

U5

PEG_RXP_15

U4

PEG_RXN_15

L7

PEG_RCOMP

Y3

DMI_RXP_0

Y4

DMI_RXN_0

AA4

DMI_RXP_1

AA5

DMI_RXN_1

AB4

DMI_RXP_2

AB3

DMI_RXN_2

AC4

DMI_RXP_3

AC5

DMI_RXN_3

CFL_S62 _IP_CRB_CFLS_L GA

@

PEG_TXP_0

PEG_TXN_0

PEG_TXP_1

PEG_TXN_1

PEG_TXP_2

PEG_TXN_2

PEG_TXP_3

PEG_TXN_3

PEG_TXP_4

PEG_TXN_4

PEG_TXP_5

PEG_TXN_5

PEG_TXP_6

PEG_TXN_6

PEG_TXP_7

PEG_TXN_7

PEG_TXP_8

PEG_TXN_8

PEG_TXP_9

PEG_TXN_9

PEG_TXP_10

PEG_TXN_10

PEG_TXP_11

PEG_TXN_11

PEG_TXP_12

PEG_TXN_12

PEG_TXP_13

PEG_TXN_13

PEG_TXP_14

PEG_TXN_14

PEG_TXP_15

PEG_TXN_15

DMI_TXP_0

DMI_TXN_0

DMI_TXP_1

DMI_TXN_1

DMI_TXP_2

DMI_TXN_2

DMI_TXP_3

DMI_TXN_3

A5

A6

B4

B5

C3

C4

D2

D3

PEG_CTX _GRX_P11

E1

PEG_CTX _GRX_N11

E2

PEG_CTX _GRX_P10

F2

PEG_CTX _GRX_N10

F3

PEG_CTX _GRX_P9

G1

PEG_CTX _GRX_N9

G2

PEG_CTX _GRX_P8

H2

PEG_CTX _GRX_N8

H3

PEG_CTX _GRX_P7

J1

PEG_CTX _GRX_N7

J2

PEG_CTX _GRX_P6

K2

PEG_CTX _GRX_N6

K3

PEG_CTX _GRX_P5

L1

PEG_CTX _GRX_N5

L2

PEG_CTX _GRX_P4

M2

PEG_CTX _GRX_N4

M3

PEG_CTX _GRX_P3

N1

PEG_CTX _GRX_N3

N2

PEG_CTX _GRX_P2

P2

PEG_CTX _GRX_N2

P3

PEG_CTX _GRX_P1

R2

PEG_CTX _GRX_N1

R1

PEG_CTX _GRX_P0

T2

PEG_CTX _GRX_N0

T3

DMI_CTX_P RX_P0

AC2

DMI_CTX_P RX_N0

AC1

DMI_CTX_P RX_P1

AD3

DMI_CTX_P RX_N1

AD2

DMI_CTX_P RX_P2

AE2

DMI_CTX_P RX_N2

AE1

DMI_CTX_P RX_P3

AF2

DMI_CTX_P RX_N3

AF3

1 2

CC58 0.22U_0201 _6.3V

1 2

CC63 0.22U_0201 _6.3V

1 2

CC61 0.22U_0201 _6.3V

1 2

CC62 0.22U_0201 _6.3V

1 2

CC59 0.22U_0201 _6.3V

1 2

CC56 0.22U_0201 _6.3V

1 2

CC57 0.22U_0201 _6.3V

1 2

CC60 0.22U_0201 _6.3V

1 2

CC20 0.22U_0402 _6.3V7K

1 2

CC21 0.22U_0402 _6.3V7K

1 2

CC18 0.22U_0402 _6.3V7K

1 2

CC19 0.22U_0402 _6.3V7K

1 2

CC16 0.22U_0402 _6.3V7K

1 2

CC17 0.22U_0402 _6.3V7K

1 2

CC14 0.22U_0402 _6.3V7K

1 2

CC15 0.22U_0402 _6.3V7K

1 2

CC12 0.22U_0402 _6.3V7K

1 2

CC13 0.22U_0402 _6.3V7K

1 2

CC10 0.22U_0402 _6.3V7K

1 2

CC11 0.22U_0402 _6.3V7K

1 2

CC8 0.22U_0402_6 .3V7K

1 2

CC9 0.22U_0402_6 .3V7K

1 2

CC6 0.22U_0402_6 .3V7K

1 2

CC7 0.22U_0402_6 .3V7K

DMI_CTX_P RX_P0 <14 >

DMI_CTX_P RX_N0 < 14>

DMI_CTX_P RX_P1 <14 >

DMI_CTX_P RX_N1 < 14>

DMI_CTX_P RX_P2 <14 >

DMI_CTX_P RX_N2 < 14>

DMI_CTX_P RX_P3 <14 >

DMI_CTX_P RX_N3 < 14>

PEG_CTX _C_GRX_P11 <74>

PEG_CTX _C_GRX_N11 <74>

PEG_CTX _C_GRX_P10 <74>

PEG_CTX _C_GRX_N10 <74>

PEG_CTX _C_GRX_P9 < 74>

PEG_CTX _C_GRX_N9 <74>

PEG_CTX _C_GRX_P8 < 74>

PEG_CTX _C_GRX_N8 <74>

PEG_CTX _C_GRX_P7 <37>

PEG_CTX _C_GRX_N7 <37>

PEG_CTX _C_GRX_P6 <37>

PEG_CTX _C_GRX_N6 <37>

PEG_CTX _C_GRX_P5 <37>

PEG_CTX _C_GRX_N5 <37>

PEG_CTX _C_GRX_P4 <37>

PEG_CTX _C_GRX_N4 <37>

PEG_CTX _C_GRX_P3 <37>

PEG_CTX _C_GRX_N3 <37>

PEG_CTX _C_GRX_P2 <37>

PEG_CTX _C_GRX_N2 <37>

PEG_CTX _C_GRX_P1 <37>

PEG_CTX _C_GRX_N1 <37>

PEG_CTX _C_GRX_P0 <37>

PEG_CTX _C_GRX_N0 <37>

Typ- suggest 220nF. The change in AC capacitor

value from 100nF to 220nF is to enable

compatibility with future platforms having PCIE

Gen3 (8GT/s)

Caldera RX

GPU RX

Security Classificat ion

Security Classificat ion

Security Classificat ion

2018/03/ 29 2019/03/ 29

2018/03/ 29 2019/03/ 29

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

2018/03/ 29 2019/03/ 29

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Docu ment Number Re v

Size Docu ment Number Re v

Size Docu ment Number Re v

Custom

Custom

Custom

Date : Sheet o f

Date : Sheet o f

2

Date : Sheet o f

Compal Electronics, Inc.

CFL-S DMI/PEG

CFL-S DMI/PEG

CFL-S DMI/PEG

LA-G881P

LA-G881P

LA-G881P

7 101Tuesday, January 08, 201 9

7 101Tuesday, January 08, 201 9

7 101Tuesday, January 08, 201 9

1

1.0

1.0

1.0

5

4

3

2

1

DDR_A_D[0..63]<23,25>

DDR_A_MA[0..13]<23,25>

UC1A

AE38

DDR0_DQ_0/DDR0_DQ_0

AE37

DDR0_DQ_1/DDR0_DQ_1

AG38

DDR0_DQ_2/DDR0_DQ_2

AG37

DDR0_DQ_3/DDR0_DQ_3

AE39

DDR0_DQ_4/DDR0_DQ_4

AE40

DDR0_DQ_5/DDR0_DQ_5

AG39

DDR0_DQ_6/DDR0_DQ_6

AG40

DDR0_DQ_7/DDR0_DQ_7

AJ38

DDR0_DQ_8/DDR0_DQ_8

AJ37

DDR0_DQ_9/DDR0_DQ_9

AL38

DDR0_DQ_10/DDR0_DQ_10

AL37

DDR0_DQ_11/DDR0_DQ_11

AJ40

DDR0_DQ_12/DDR0_DQ_12

AJ39

DDR0_DQ_13/DDR0_DQ_13

AL39

DDR0_DQ_14/DDR0_DQ_14

AL40

DDR0_DQ_15/DDR0_DQ_15

AN38

DDR0_DQ_16/DDR0_DQ_32

AN40

DDR0_DQ_17/DDR0_DQ_33

AR38

DDR0_DQ_18/DDR0_DQ_34

AR37

DDR0_DQ_19/DDR0_DQ_35

AN39

DDR0_DQ_20/DDR0_DQ_36

AN37

DDR0_DQ_21/DDR0_DQ_37

AR39

DDR0_DQ_22/DDR0_DQ_38

AR40

DDR0_DQ_23/DDR0_DQ_39

AW37

DDR0_DQ_24/DDR0_DQ_40

AU38

DDR0_DQ_25/DDR0_DQ_41

AV35

DDR0_DQ_26/DDR0_DQ_42

AW35

DDR0_DQ_27/DDR0_DQ_43

AU37

DDR0_DQ_28/DDR0_DQ_44

AV37

DDR0_DQ_29/DDR0_DQ_45

AT35

DDR0_DQ_30/DDR0_DQ_46

AU35

DDR0_DQ_31/DDR0_DQ_47

AY8

DDR0_DQ_32/DDR1_DQ_0

AW8

DDR0_DQ_33/DDR1_DQ_1

AV6

DDR0_DQ_34/DDR1_DQ_2

AU6

DDR0_DQ_35/DDR1_DQ_3

AU8

DDR0_DQ_36/DDR1_DQ_4

AV8

DDR0_DQ_37/DDR1_DQ_5

AW6

DDR0_DQ_38/DDR1_DQ_6

AY6

DDR0_DQ_39/DDR1_DQ_7

AY4

DDR0_DQ_40/DDR1_DQ_8

AV4

DDR0_DQ_41/DDR1_DQ_9

AT1

DDR0_DQ_42/DDR1_DQ_10

AT2

DDR0_DQ_43/DDR1_DQ_11

AV3

DDR0_DQ_44/DDR1_DQ_12

AW4

DDR0_DQ_45/DDR1_DQ_13

AT4

DDR0_DQ_46/DDR1_DQ_14

AT3

DDR0_DQ_47/DDR1_DQ_15

AP2

DDR0_DQ_48/DDR1_DQ_32

AM4

DDR0_DQ_49/DDR1_DQ_33

AP3

DDR0_DQ_50/DDR1_DQ_34

AM3

DDR0_DQ_51/DDR1_DQ_35

AP4

DDR0_DQ_52/DDR1_DQ_36

AM2

DDR0_DQ_53/DDR1_DQ_37

AP1

DDR0_DQ_54/DDR1_DQ_38

AM1

DDR0_DQ_55/DDR1_DQ_39

AK3

DDR0_DQ_56/DDR1_DQ_40

AH1

DDR0_DQ_57/DDR1_DQ_41

AK4

DDR0_DQ_58/DDR1_DQ_42

AH2

DDR0_DQ_59/DDR1_DQ_43

AH4

DDR0_DQ_60/DDR1_DQ_44

AK2

DDR0_DQ_61/DDR1_DQ_45

AH3

DDR0_DQ_62/DDR1_DQ_46

AK1

DDR0_DQ_63/DDR1_DQ_47

AU33

DDR0_ECC_0

AT33

DDR0_ECC_1

AW33

DDR0_ECC_2

AV31

DDR0_ECC_3

AU31

DDR0_ECC_4

AV33

DDR0_ECC_5

AW31

DDR0_ECC_6

AY31

DDR0_ECC_7

DDR CHANNEL A

CFL_S62_IP_CR B_CFLS_LGA

@

DDR_A_DQS#[0..7]<23 ,25>

DDR_A_DQS[0..7]<23,25>

D D

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

C C

B B

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

Channel A Channel B

DDR0_CKP_0

DDR0_CKN_0

DDR0_CKP_1

DDR0_CKN_1

DDR0_CKP_2

DDR0_CKN_2

DDR0_CKP_3

DDR0_CKN_3

DDR0_CKE_0

DDR0_CKE_1

DDR0_CKE_2

DDR0_CKE_3

DDR0_CS#_0

DDR0_CS#_1

DDR0_CS#_2

DDR0_CS#_3

DDR0_ODT_0

DDR0_ODT_1

DDR0_ODT_2

DDR0_ODT_3

DDR0_BA_0

DDR0_BA_1

DDR0_BG_0

DDR0_MA_16

DDR0_MA_14

DDR0_MA_15

DDR0_MA_0

DDR0_MA_1

DDR0_MA_2

DDR0_MA_3

DDR0_MA_4

DDR0_MA_5

DDR0_MA_6

DDR0_MA_7

DDR0_MA_8

DDR0_MA_9

DDR0_MA_10

DDR0_MA_11

DDR0_MA_12

DDR0_MA_13

DDR0_BG_1

DDR0_ACT#

DDR0_PAR

DDR0_ALERT#

DDR0_DQSN_0/DDR0_DQSN_0

DDR0_DQSN_1/DDR0_DQSN_1

DDR0_DQSN_2/DDR0_DQSN_4

DDR0_DQSN_3/DDR0_DQSN_5

DDR0_DQSN_4/DDR1_DQSN_0

DDR0_DQSN_5/DDR1_DQSN_1

DDR0_DQSN_6/DDR1_DQSN_4

DDR0_DQSN_7/DDR1_DQSN_5

DDR0_DQSP_0/DDR0_DQSP_0

DDR0_DQSP_1/DDR0_DQSP_1

DDR0_DQSP_2/DDR0_DQSP_4

DDR0_DQSP_3/DDR0_DQSP_5

DDR0_DQSP_4/DDR1_DQSP_0

DDR0_DQSP_5/DDR1_DQSP_1

DDR0_DQSP_6/DDR1_DQSP_4

DDR0_DQSP_7/DDR1_DQSP_5

DDR0_DQSP_8/DDR0_DQSP_8

DDR0_DQSN_8/DDR0_DQSN_8

AW18

AV18

AW17

AY17

AW16

AV16

AT16

AU16

AY24

AW24

AV24

AV25

AW12

AU11

AV13

AV10

AW11

AU14

AU12

AY10

AY13

AV15

AW23

AW13

AV14

AY11

AW15

AU18

AU17

AV19

AT19

AU20

AV20

AU21

AT20

AT22

AY14

AU22

AV22

AV12

AV23

AU24

AY15

AT23

AF39

AK39

AP39

AU36

AW7

AU3

AN3

AJ3

AF38

AK38

AP38

AV36

AV7

AU2

AN2

AJ2

AV32

AU32

DDR_A_BA0

DDR_A_BA1

DDR_A_BG0

DDR_A_RAS#

DDR_A_WE #

DDR_A_CAS#

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_BG1

DDR_A_ACT#

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_CLK0 <25>

DDR_A_CLK#0 <25>

DDR_A_CLK1 <25>

DDR_A_CLK#1 <25>

DDR_A_CLK2 <23>

DDR_A_CLK#2 <23>

DDR_A_CLK3 <23>

DDR_A_CLK#3 <23>

DDR_A_CKE0 <25>

DDR_A_CKE1 <25>

DDR_A_CKE2 <23>

DDR_A_CKE3 <23>

DDR_A_CS#0 <25>

DDR_A_CS#1 <25>

DDR_A_CS#2 <23>

DDR_A_CS#3 <23>

DDR_A_ODT0 <25>

DDR_A_ODT1 <25>

DDR_A_ODT2 <23>

DDR_A_ODT3 <23>

DDR_A_BA0 <23,25>

DDR_A_BA1 <23,25>

DDR_A_BG0 < 23,25>

DDR_A_RAS# <23,25>

DDR_A_WE # <23,25>

DDR_A_CAS# <23,25>

DDR_A_BG1 < 23,25>

DDR_A_ACT# <23,25>

DDR_A_PAR <23,25>

DDR_A_ALERT# <23,25> DDR_B_ALERT # <24,26>

DIMM2

DIMM1

DIMM2

DIMM1

DIMM2

DIMM1

DIMM2

DIMM1

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

DDR_B_D[0..63 ]<24,26>

DDR_B_MA[0..13]<24,26>

DDR_B_DQS# [0..7]< 24,26>

DDR_B_DQS[0 ..7]< 24,26>

UC1B

AD34

DDR1_DQ_0/DDR0_DQ_16

AD35

DDR1_DQ_1/DDR0_DQ_17

AG35

DDR1_DQ_2/DDR0_DQ_18

AH35

DDR1_DQ_3/DDR0_DQ_19

AE35

DDR1_DQ_4/DDR0_DQ_20

AE34

DDR1_DQ_5/DDR0_DQ_21

AG34

DDR1_DQ_6/DDR0_DQ_22

AH34

DDR1_DQ_7/DDR0_DQ_23

AK35

DDR1_DQ_8/DDR0_DQ_24

AL35

DDR1_DQ_9/DDR0_DQ_25

AK32

DDR1_DQ_10/DDR0_DQ_26

AL32

DDR1_DQ_11/DDR0_DQ_27

AK34

DDR1_DQ_12/DDR0_DQ_28

AL34

DDR1_DQ_13/DDR0_DQ_29

AK31

DDR1_DQ_14/DDR0_DQ_30

AL31

DDR1_DQ_15/DDR0_DQ_31

AP35

DDR1_DQ_16/DDR0_DQ_48

AN35

DDR1_DQ_17/DDR0_DQ_49

AN32

DDR1_DQ_18/DDR0_DQ_50

AP32

DDR1_DQ_19/DDR0_DQ_51

AN34

DDR1_DQ_20/DDR0_DQ_52

AP34

DDR1_DQ_21/DDR0_DQ_53

AN31

DDR1_DQ_22/DDR0_DQ_54

AP31

DDR1_DQ_23/DDR0_DQ_55

AL29

DDR1_DQ_24/DDR0_DQ_56

AM29

DDR1_DQ_25/DDR0_DQ_57

AP29

DDR1_DQ_26/DDR0_DQ_58

AR29

DDR1_DQ_27/DDR0_DQ_59

AM28

DDR1_DQ_28/DDR0_DQ_60

AL28

DDR1_DQ_29/DDR0_DQ_61

AR28

DDR1_DQ_30/DDR0_DQ_62

AP28

DDR1_DQ_31/DDR0_DQ_63

AR12

DDR1_DQ_32/DDR1_DQ_16

AP12

DDR1_DQ_33/DDR1_DQ_17

AM13

DDR1_DQ_34/DDR1_DQ_18

AL13

DDR1_DQ_35/DDR1_DQ_19

AR13

DDR1_DQ_36/DDR1_DQ_20

AP13

DDR1_DQ_37/DDR1_DQ_21

AM12

DDR1_DQ_38/DDR1_DQ_22

AL12

DDR1_DQ_39/DDR1_DQ_23

AP10

DDR1_DQ_40/DDR1_DQ_24

AR10

DDR1_DQ_41/DDR1_DQ_25

AR7

DDR1_DQ_42/DDR1_DQ_26

AP7

DDR1_DQ_43/DDR1_DQ_27

AR9

DDR1_DQ_44/DDR1_DQ_28

AP9

DDR1_DQ_45/DDR1_DQ_29

AR6

DDR1_DQ_46/DDR1_DQ_30

AP6

DDR1_DQ_47/DDR1_DQ_31

AM10

DDR1_DQ_48/DDR1_DQ_48

AL10

DDR1_DQ_49/DDR1_DQ_49

AM7

DDR1_DQ_50/DDR1_DQ_50

AL7

DDR1_DQ_51/DDR1_DQ_51

AM9

DDR1_DQ_52/DDR1_DQ_52

AL9

DDR1_DQ_53/DDR1_DQ_53

AM6

DDR1_DQ_54/DDR1_DQ_54

AL6

DDR1_DQ_55/DDR1_DQ_55

AJ6

DDR1_DQ_56/DDR1_DQ_56

AJ7

DDR1_DQ_57/DDR1_DQ_57

AE6

DDR1_DQ_58/DDR1_DQ_58

AF7

DDR1_DQ_59/DDR1_DQ_59

AH7

DDR1_DQ_60/DDR1_DQ_60

AH6

DDR1_DQ_61/DDR1_DQ_61

AE7

DDR1_DQ_62/DDR1_DQ_62

AF6

DDR1_DQ_63/DDR1_DQ_63

AR25

DDR1_ECC_0

AR26

DDR1_ECC_1

AM26

DDR1_ECC_2

AM25

DDR1_ECC_3

AP26

DDR1_ECC_4

AP25

DDR1_ECC_5

AL25

DDR1_ECC_6

AL26

DDR1_ECC_7

CFL_S62_IP_CR B_CFLS_LGA

@

DDR CHANNEL B

DDR1_CKP_0

DDR1_CKN_0

DDR1_CKP_1

DDR1_CKN_1

DDR1_CKP_2

DDR1_CKN_2

DDR1_CKP_3

DDR1_CKN_3

DDR1_CKE_0

DDR1_CKE_1

DDR1_CKE_2

DDR1_CKE_3

DDR1_CS#_0

DDR1_CS#_1

DDR1_CS#_2

DDR1_CS#_3

DDR1_ODT_0

DDR1_ODT_1

DDR1_ODT_2

DDR1_ODT_3

DDR1_MA_16

DDR1_MA_14

DDR1_MA_15

DDR1_BA_0

DDR1_BA_1

DDR1_BG_0

DDR1_MA_0

DDR1_MA_1

DDR1_MA_2

DDR1_MA_3

DDR1_MA_4

DDR1_MA_5

DDR1_MA_6

DDR1_MA_7

DDR1_MA_8

DDR1_MA_9

DDR1_MA_10

DDR1_MA_11

DDR1_MA_12

DDR1_MA_13

DDR1_BG_1

DDR1_ACT#

DDR1_PAR

DDR1_ALERT#

DDR1_DQSN_0/DDR0_DQSN_2

DDR1_DQSN_1/DDR0_DQSN_3

DDR1_DQSN_2/DDR0_DQSN_6

DDR1_DQSN_3/DDR0_DQSN_7

DDR1_DQSN_4/DDR1_DQSN_2

DDR1_DQSN_5/DDR1_DQSN_3

DDR1_DQSN_6/DDR1_DQSN_6

DDR1_DQSN_7/DDR1_DQSN_7

DDR1_DQSP_0/DDR0_DQSP_2

DDR1_DQSP_1/DDR0_DQSP_3

DDR1_DQSP_2/DDR0_DQSP_6

DDR1_DQSP_3/DDR0_DQSP_7

DDR1_DQSP_4/DDR1_DQSP_2

DDR1_DQSP_5/DDR1_DQSP_3

DDR1_DQSP_6/DDR1_DQSP_6

DDR1_DQSP_7/DDR1_DQSP_7

DDR1_DQSP_8/DDR1_DQSP_8

DDR1_DQSN_8/DDR1_DQSN_8

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

AM20

AM21

AP22

AP21

AN20

AN21

AP19

AP20

AY29

AV29

AW29

AU29

AP17

AN15

AN17

AM15

AM16

AL16

AP15

AL15

DDR_B_RAS#

AN18

DDR_B_W E#

AL17

DDR_B_CAS#

AP16

AL18

AM18

AW28

AL19

AL22

AM22

AM23

AP23

AL23

AW26

AY26

AU26

AW27

AP18

AU27

AV27

AR15

AY28

AU28

AL20

AY25

AF34

AK33

AN33

AN29

AN13

AR8

AM8

AG6

AF35

AL33

AP33

AN28

AN12

AP8

AL8

AG7

AN25

AN26

AB40

AC40

AC39

DDR_B_BA0

DDR_B_BA1

DDR_B_BG0

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_BG1

DDR_B_ACT#

DDR_B_DQS# 0

DDR_B_DQS# 1

DDR_B_DQS# 2

DDR_B_DQS# 3

DDR_B_DQS# 4

DDR_B_DQS# 5

DDR_B_DQS# 6

DDR_B_DQS# 7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

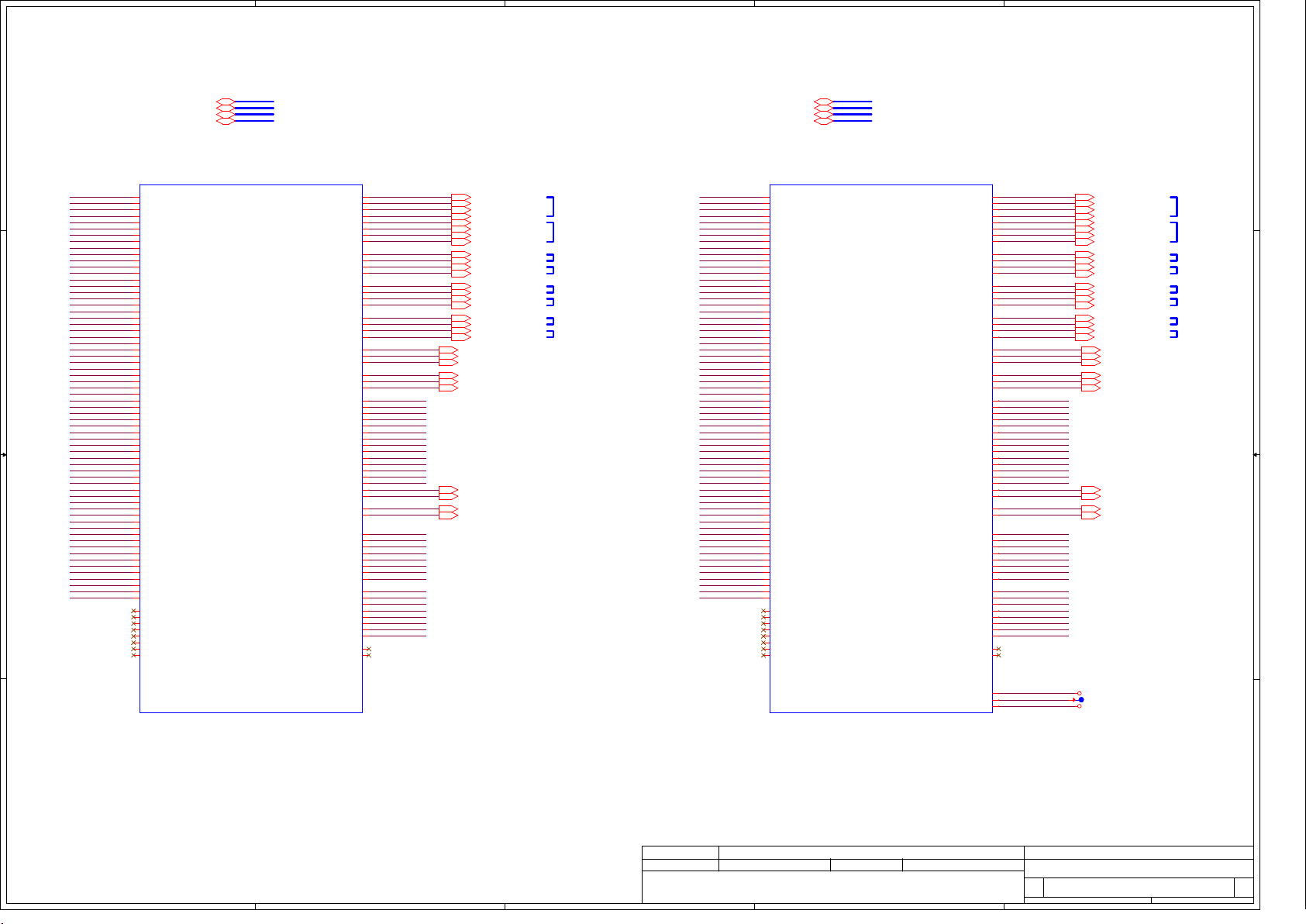

Trace width / Spacing = 10 / 12 mils

SA_DIMM_VREFDQ

Trace width / Spacing = 10 / 12 mils

+0.6V_VREF_CA

TC7

+0.6V_VREF_DQ

DDR_B_CLK 0 <26>

DDR_B_CLK #0 <26>

DDR_B_CLK 1 <26>

DDR_B_CLK #1 <26>

DDR_B_CLK 2 <24>

DDR_B_CLK #2 <24>

DDR_B_CLK 3 <24>

DDR_B_CLK #3 <24>

DDR_B_CKE0 <26>

DDR_B_CKE1 <26>

DDR_B_CKE2 <24>

DDR_B_CKE3 <24>

DDR_B_CS# 0 <26>

DDR_B_CS# 1 <26>

DDR_B_CS# 2 <24>

DDR_B_CS# 3 <24>

DDR_B_ODT 0 <2 6>

DDR_B_ODT 1 <2 6>

DDR_B_ODT 2 <2 4>

DDR_B_ODT 3 <2 4>

DDR_B_RAS# <24,26>

DDR_B_W E# <24,26>

DDR_B_CAS# <24,26>

DDR_B_BA0 <24,26>

DDR_B_BA1 <24,26>

DDR_B_BG0 < 24,26>

DDR_B_BG1 < 24,26>

DDR_B_ACT# <24,26>

DDR_B_PAR <24,26>

DIMM4

DIMM3

DIMM4

DIMM3

DIMM4

DIMM3

DIMM4

DIMM3

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2018/03/29 2019/03/29

2018/03/29 2019/03/29

2018/03/29 2019/03/29

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date : Sheet of

Date : Sheet of

2

Date : Sheet of

Compal Electronics, Inc.

CFL-S DDR4

CFL-S DDR4

CFL-S DDR4

LA-G881P

LA-G881P

LA-G881P

1

8 101Tuesday, January 08, 201 9

8 101Tuesday, January 08, 201 9

8 101Tuesday, January 08, 201 9

1.0

1.0

1.0

5

4

3

2

1

+VCC_CORE +VCC_CORE

49A

D D

C C

B B

UC1G

A25

VCC1

A26

VCC2

A27

VCC3

A28

VCC4

A29

VCC5

A30

VCC6

B25

VCC24

B27

VCC25

B29

VCC26

B31

VCC27

B32

VCC28

B33

VCC29

B34

VCC30

B35

VCC31

B36

VCC32

B37

VCC33

C25

VCC34

C26

VCC35

C27

VCC36

C28

VCC37

C29

VCC38

C30

VCC39

C32

VCC40

C34

VCC41

C36

VCC42

D25

VCC43

D27

VCC44

D29

VCC45

D31

VCC46

D32

VCC47

D33

VCC48

D34

VCC49

D35

VCC50

D36

VCC51

E24

VCC52

E25

VCC53

E26

VCC54

E27

VCC55

E28

VCC56

E29

VCC57

E30

VCC58

E32

VCC59

E34

VCC60

E36

VCC61

F23

VCC62

F24

VCC63

F25

VCC64

F27

VCC65

F29

VCC66

F31

VCC67

G30

VCC80

G32

VCC81

H22

VCC84

H23

VCC85

H25

VCC86

H27

VCC87

H29

VCC88

H31

VCC89

AJ11

VCC7

AJ13

VCC9

AJ15

VCC11

AJ17

VCC13

AJ19

VCC15

AJ21

VCC17

M32

VCC146

L31

VCC134

K32

VCC115

J33

VCC104

H33

VCC91

G34

VCC82

AJ25

VCC18

AJ26

VCC19

AJ27

VCC20

AJ28

VCC21

CFL_S62_IP_CR B_CFLS_LGA

@

VCC90

VCC93

VCC68

VCC69

VCC70

VCC73

VCC74

VCC75

VCC76

VCC77

VCC78

VCC79

VCC94

VCC95

VCC96

VCC97

VCC98

VCC99

VCC100

VCC101

VCC102

VCC103

VCC106

VCC107

VCC108

VCC109

VCC110

VCC111

VCC112

VCC113

VCC114

VCC117

VCC118

VCC119

VCC120

VCC121

VCC122

VCC123

VCC124

VCC125

VCC126

VCC127

VCC128

VCC129

VCC130

VCC131

VCC132

VCC133

VCC136

VCC137

VCC138

VCC139

VCC140

VCC141

VCC142

VCC143

VCC144

VCC145

VCC8

VCC10

VCC12

VCC14

VCC16

VCC22

VCC23

VCC71

VCC72

VCC83

VCC92

VCC105

VCC116

VCC135

VCC_SENSE

VSS_SENSE

H32

J21

F32

F33

F34

G23

G24

G25

G26

G27

G28

G29

J22

J23

J24

J25

J26

J27

J28

J29

J30

J31

K16

K18

K20

K21

K23

K25

K27

K29

K31

L14

L15

L16

L17

L18

L19

L20

L21

L22

L23

L24

L25

L26

L27

L28

L29

L30

M13

M14

M16

M18

M20

M22

M24

M26

M28

M30

AJ12

AJ14

AJ16

AJ18

AJ20

AJ29

AK21

F35

F37

G35

H34

J35

K34

L33

C38

D38

22U_0805_ 6.3V6M~D

+VCC_CORE

12

12

1

CC52

2

47U_0805_ 6.3V6M

1

CC29

22U_0603_ 6.3V6M

1

CC33

2

22U_0603_ 6.3V6M

2

1

2

22U_0603_ 6.3V6M

22U_0603_ 6.3V6M

+VCCIO

CC32

9/12:change from SE000000I10 to SE00000M000*2

RC197

100_0402_ 1%

VCORE_VCC_SEN <91>

VCORE_VSS_SEN <91>

RC686

100_0402_ 1%

PLACE ALL BELOW CAPS ON

TOP SIDE NEAR CPU SOCKET

47U_0805_ 6.3V6M

1

CC51

CC50

2

47U_0805_ 6.3V6M

PLACE ALL ABOVE CAPS ON

TOP SIDE OF CPU CAVITY

1

CC28

22U_0603_ 6.3V6M

2

PLACE ALL ABOVE CAPS ON

TOP SIDE OF CPU CAVITY

22U_0603_ 6.3V6M

1

CC34

CC35

2

1

2

1

CC26

2

1

CC36

2

22U_0603_ 6.3V6M

47U_0805_ 6.3V6M

CC49

22U_0603_ 6.3V6M

22U_0603_ 6.3V6M

1

2

+1.05V_VCCST

Place as close to socket as possible

1

2

CC27

CC37

1

CC47

2

22U_0603_ 6.3V6M

1

2

0.95V/5.5A

1

2

+1.05V_VCCST

22U_0603_6.3V6M

CC38

1

1

2

2

22U_0603_ 6.3V6M

1

CC48

2

1.05V / 11A

1.05V/120mA

22U_0603_6.3V6M

CC30

1

CC31

1U_0201_6 .3V6M

2

SE00000UC0 0

+VCCSA

UC1I

AA7

VCCSA2

AB6

VCCSA3

AB7

VCCSA4

AB8

VCCSA5

AC7

VCCSA6

AC8

VCCSA7

N7

VCCSA8

P7

VCCSA9

R7

VCCSA10

T7

VCCSA11

U7

VCCSA12

Y6

VCCSA15

Y7

VCCSA16

Y8

VCCSA17

W7

VCCSA14

V7

VCCSA13

AA6

VCCSA1

AK11

VCCIO2

AK14

VCCIO3

AK24

VCCIO4

AJ23

VCCIO1

M8

VCCIO5

P8

VCCIO6

T8

VCCIO7

U8

VCCIO8

W8

VCCIO9

V5

VCCST1

V6

VCCST2

V4

VCCPLL

CFL_S62_IP_CR B_CFLS_LGA

@

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VCCPLL_OC

VCCSA_SENSE

VCCIO_SENSE

VSS_SAIO_SENSE

AT18

AT21

AU13

AU15

AU19

AU23

AV11

AV17

AV21

AW10

AW14

AW25

AY12

AY16

AY18

AY23

AJ9

100mA

AD5

AF4

AE4

PLACE ALL BELOW CAPS ON

TOP SIDE NEAR CPU SOCKET

2.5A

VCCPLL_OC

VCCSA_SENSE

VCCIO_SENSE

VSSSAIO_SENSE

1

CC22

2

22U_0603_ 6.3V6M

RC21 0_0402_5%

RC25 0_0402_5%

2

CC46

1U_0201_6 .3V6M

SE00000UC0 0

1

22U_0603_ 6.3V6M

CC23

S0IX@

1 2

NS0IX@

1 2

For NON-S0IX

@

1

1

CC24

2

2

22U_0603_ 6.3V6M

+1.2V_VCCPLL_OC

VCCSA_SENSE <96>

VCCIO_SENSE <89>

VSSSAIO_SENSE <96>

22U_0603_ 6.3V6M

CC25

+VCCGT

+1.2V_DDR

1

2

+1.2V_DDR

35A

UC1H

AA34

VCCGT1

AA35

VCCGT2

AA36

VCCGT3

AA37

VCCGT4

AA38