Page 1

5-V Low-Drop Fixed Voltage Regulator TLE 4278 G

Features

• Output voltage tolerance ≤±2%

• Very low current consumption

• Separated reset and watchdog output

• Low-drop voltage

• Watchdog

• Adjustable watchdog activating threshold

• Settable reset threshold

• Overtemperature protection

• Reverse polarity protection

• Short-circuit proof

• Suitable for use in automotive electronics

• Wide temperature range

P-DSO-14-4

Type Ordering Code Package

TLE 4278 G Q67006-A9291 P-DSO-14-4 (SMD)

Functional Description

The TLE 4278 is a monolithic integrated low-drop fixed-voltage regulator which can

supply loads up to 200 mA. Th e device is available in the P-DSO-14-4 package. It is

designed to supply micropro cessor syste ms under the severe co nditions of auto motive

applications and there fore is equi pped with additional protection f unctions a gainst ove r

load, short circuit and over temperatu re. Of course the TLE 4278 can also be used in

other applications where a stabilized voltage is required.

An input voltage

in the range of 5.5 V ≤ VI≤ 45 V is regulated to V

I

=5V within an

Qrated

V

accuracy of ±2%.

T

The device operates in the wide temperature range of

= – 40 to 150 °C.

j

Semiconductor Group 1 1998-11-01

Page 2

TLE 4278 G

Two additional features of the TLE 4278 are a load dependent watchdog function as well

as a power on reset and under voltage reset function with an adjustable reset delay time

and adjustable reset switching threshold.

The watchdog function monitors whether the microcontroller is functioning appropriately,

including time base failure s. In the case that there is no positive-going edge within a

certain pulse repetition-time the watchdog output is set to LOW. Programming of the

max. repetition time is done by the reset delay capac itor so that no additional external

components are necessary. To prevent the microcontroller from a automatic reset in

case of missing pulses, the watchdog output WO is separated from the reset output RO

for the TLE 4278. The watchdog output can be used as an interrupt signal for the

microcontroller. Pin WO can be externally connected to pin RO.

When the controller is set to sl eep mode or low power mode its current consumption

drops and no watchdog pulses are create d. In ord er to prev ent th e mic r oco ntrol ler from

unnecessary wake ups due to missing pulses at pin WI the watchdog feature can be

disabled as a function of the load. The switch off threshold is set by an external resistor

to pin WADJ. This function can also be used as a timer, which periodically wakes up the

controller. Therefore the pin WADJ has to be connected to the output Q.

The power on reset feature is necessary for a defined start of the microprocessor when

switching on the application. For a certain delay time after the output voltage of the

regulator has surpassed the reset threshold, a reset signal is generated. The delay time

is set by an external delay capacitor. The under voltage reset circuit supervises the

output voltage. In case VQ falls below the reset threshold the reset output is set LOW

after a short reaction time. The reset LOW signal is generated down to an output voltage

VQ of 1 V. In addition the reset switching threshold can be adjusted by an external

voltage divider. This feature is useful with microprocessors which guarantee a safe

operation down to voltages below the internally set reset threshold of 4.65 V typical.

Semiconductor Group 2 1998-11-01

Page 3

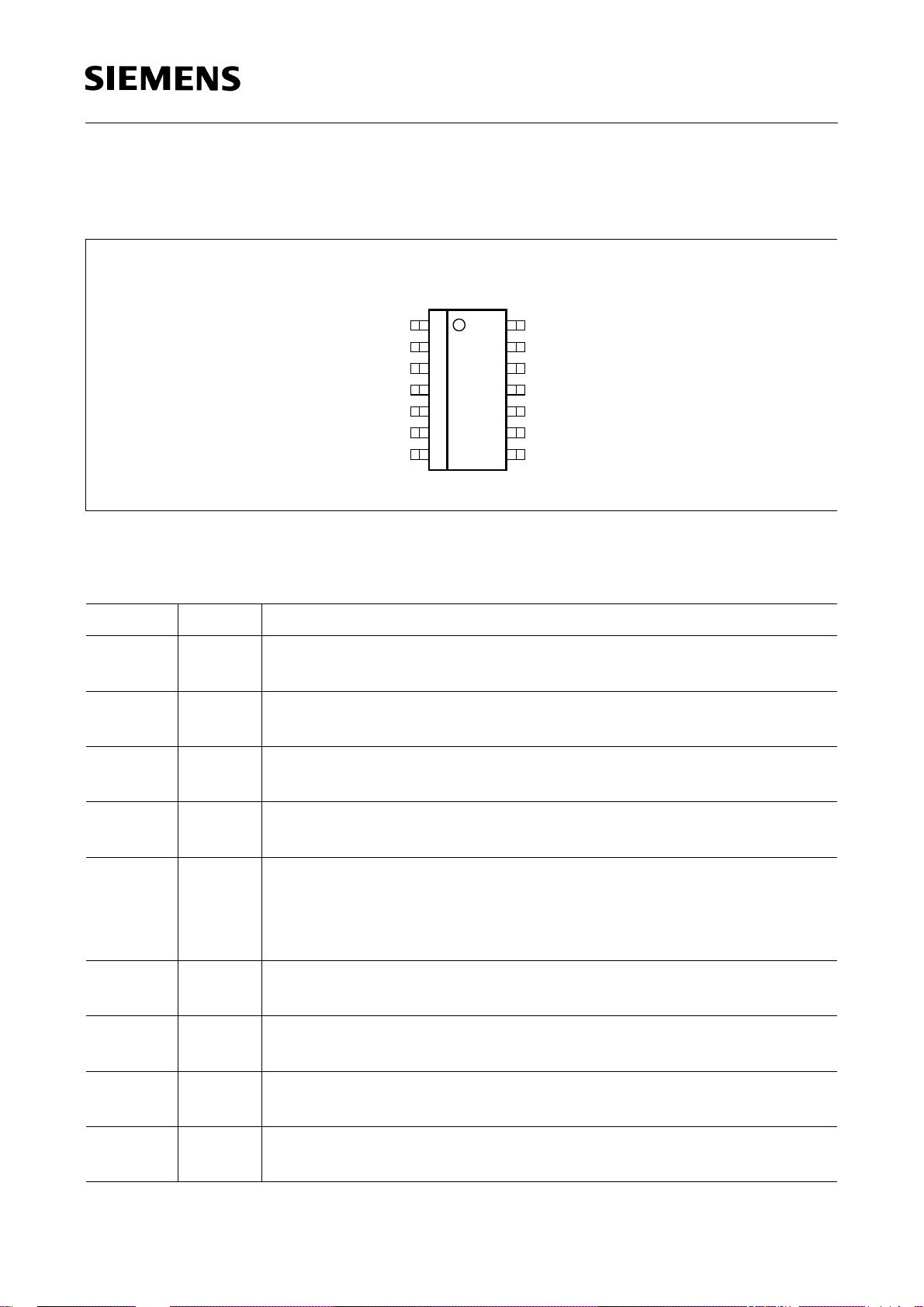

Pin Configuration

(top view)

TLE 4278 G

P-DSO-14-4

WO

WADJ

GND

GND

GND

D

RADJ

1

2

3

4

5

6

7

AEP02113

14

13

12

11

10

RO

V

Ι

GND

GND

GND

9

V

Q

8

W

Ι

Figure 1

Pin Definitions and Functions

Pin Symbol Function

1WOWatchdog Output; the open collector output is connected to the

5-V output via an integrated resistor of 30 kΩ.

2WADJWatchdog Adjust; an external resistor to GND determine the

watchdog activating threshol d.

3, 4, 5,

GND Ground

10, 11, 12

6DReset Delay; connect a capacitor to ground for delay time

adjustment.

7RADJReset Switching Threshold Adjust; for setting the switching

threshold, connect a voltage divider from output to ground. If this

input is connected to ground, the reset is triggered at the internal

threshold.

8WIWatchdog input; positive-edge-triggered input for monitoring a

microcontroller.

9

V

Q

5-V output voltage; block to ground with min. 10 µF capacitor,

ESR < 10 Ω at 10 kHz.

13

V

I

Input voltage; block to ground directly on the IC with ceramic

capacitor.

14 RO Reset output; the open collector output is connected to the

5-V output via an integrated resistor of 30 kΩ.

Semiconductor Group 3 1998-11-01

Page 4

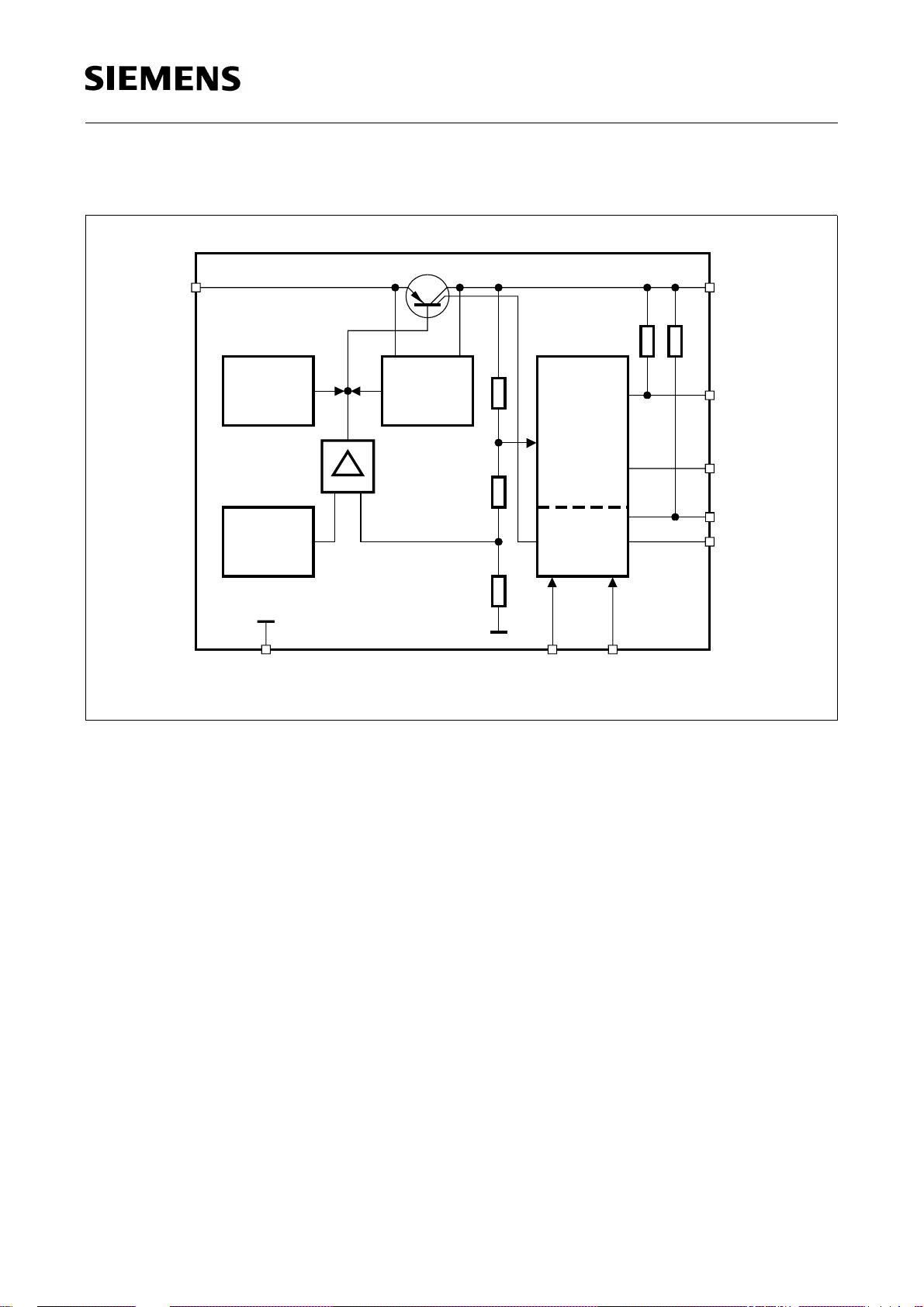

Block Diagram

TLE 4278 G

13

V

Ι

Temperature

Sensor

Protection

Circuit

12

14

V

Q

RO

Reset

Bandgap

Reference

3-5, 10-12

GND

Generator

Control

+

Amplifier

-

7

1

Watchdog

2

WADJ

W

8

Ι

6

AEB02114

RADJ

WO

D

Figure 2

Semiconductor Group 4 1998-11-01

Page 5

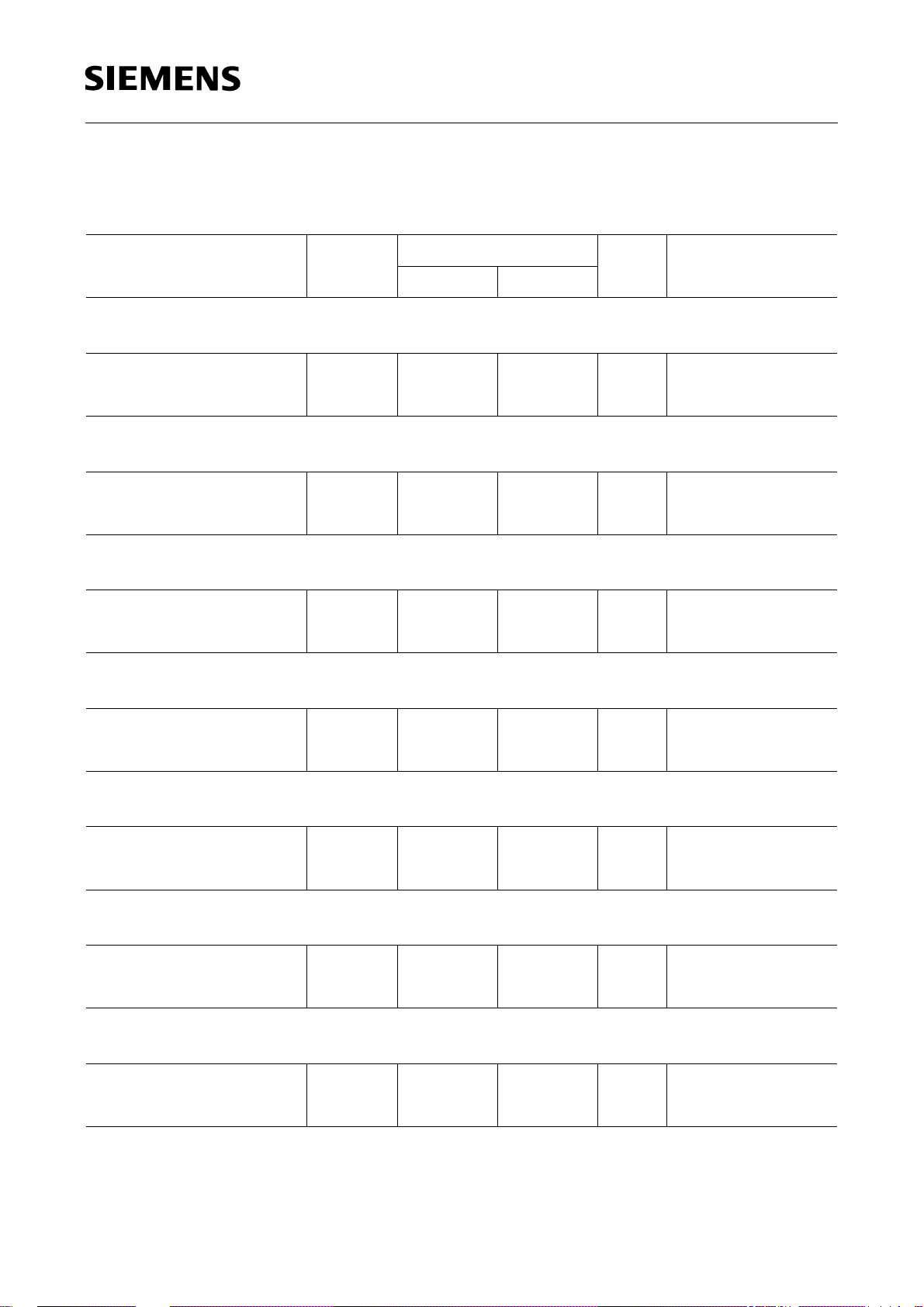

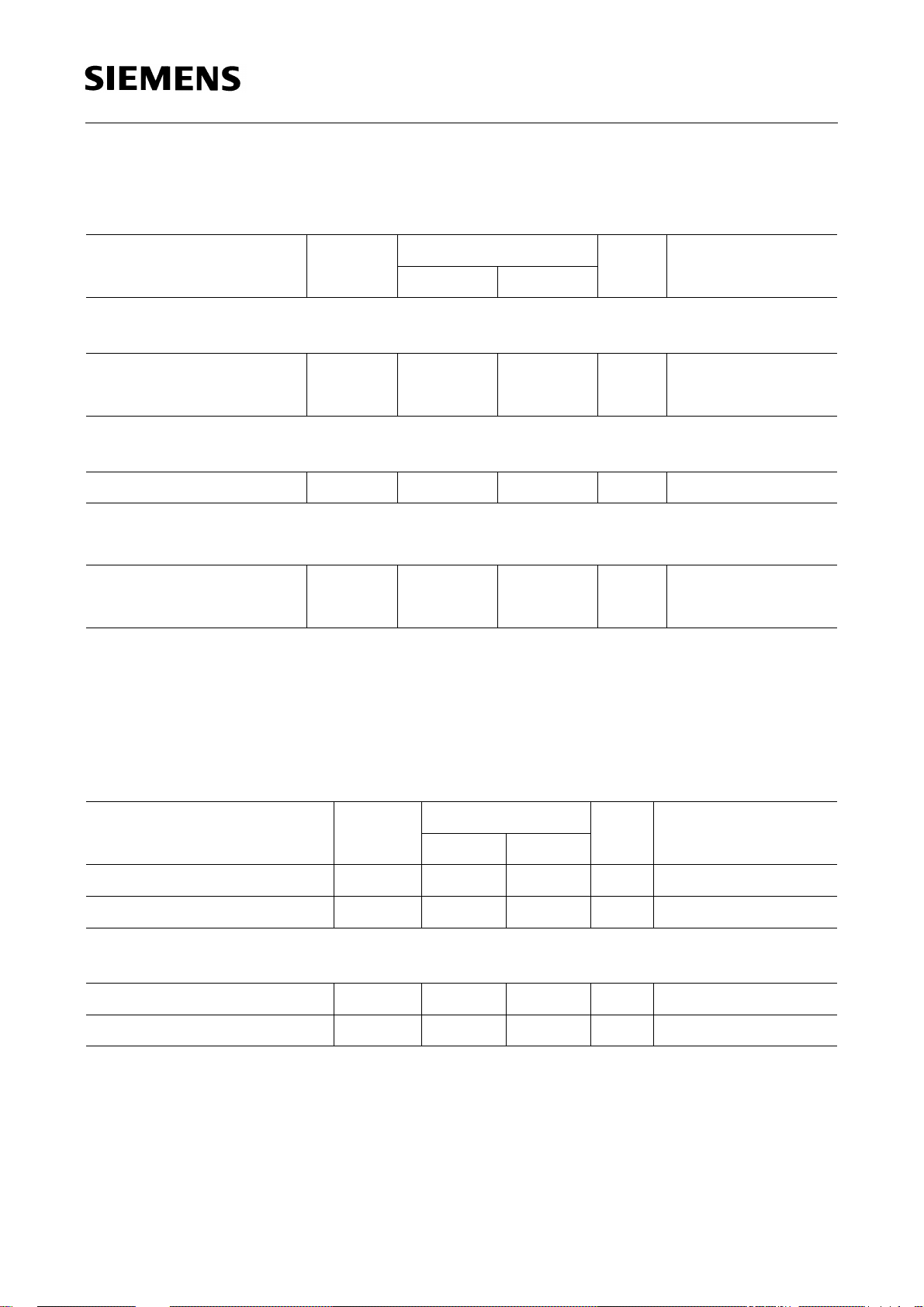

Absolute Maximum Ratings

T

= – 40 to 150 °C

j

Parameter Symbol Limit Values Unit Notes

min. max.

TLE 4278 G

Input Voltage

V

I

Voltage V

Current

Output Voltage

V

Q

I

Voltage V

Current

I

Reset Output RO

Voltage

Current

V

I

Reset Delay D

Voltage

Current

V

I

I

Q

RO

D

I

Q

RO

D

– 42 45 V –

– – mA Internally limited

– 1 25 V –

– – mA Internally limited

– 0.3 25 V –

– 5 5 mA –

– 0.3 7 V –

– 2 2 mA –

Reset Switching Threshold Adjust RADJ

Voltage

Current

V

I

RADJ

RADJ

– 0.3 7 V –

– – mA Internally limited

Watchdog Input WI

Voltage

Current

V

I

WI

WI

– 0.3 7 V –

– – mA Internally limited

Watchdog Output WO

Voltage

Current

Semiconductor Group 5 1998-11-01

V

I

WO

WO

– 0.3 25 V –

– 5 5 mA –

Page 6

Absolute Maximum Ratings (cont’d)

T

= – 40 to 150 °C

j

Parameter Symbol Limit Values Unit Notes

min. max.

Watchdog Adjust WADJ

TLE 4278 G

Voltage

Current

V

WADJ

I

WADJ

– 0.3 7 V –

– – mA Internally limited

Ground GND

Current

I

GND

– 100 50 mA –

Temperatures

Junction temperature

Storage temperature

T

j

T

stg

– 50 150 °C–

– 50 150 °C–

Note: ESD protection according to MIL Std. 883: ± 2 kV.

Maximum ratings are abs olute ratings; exceeding any one of th ese values may

cause irreversible damage to the integrated circuit.

Operating Range

Parameter Symbol Limit Values Unit Notes

min. max.

Input voltage

Junction temperature

V

T

I

j

5.5 45 V –

– 40 150 °C–

Thermal Resistance

Junction ambient

Junction pin

R

R

thj-a

thj-pin

– 70 K/W Measured to pin 4

– 25 K/W Measured to pin 4

Note: In the operating range the functions given in the circuit description are fulfilled.

Semiconductor Group 6 1998-11-01

Page 7

TLE 4278 G

Electrical Characteristics

V

= 13.5 V; – 40 °C ≤ Tj≤ 125 °C (unless otherwise specified)

I

Parameter Symbol Limit Values Unit Test Condition

min. typ. max.

Output voltage

Output voltage

Output current limiting

Current consumption

I

= II – I

q

Q

Current consumption

I

= II – I

q

Q

Current consumption

I

= II– I

q

Q

Drop voltage;

V

= VI – V

DR

Q

V

V

I

I

I

I

V

Q

q

q

q

Load regulation ∆V

Supply voltage

V

∆

regulation

Q

Q

DR

4.90 5.00 5.10 V 1 mA ≤ IQ≤ 150 mA;

V

6 V ≤

≤ 28 V

I

4.8 5.0 5.2 V 1 mA ≤ IQ≤ 50 mA;

V

28 V ≤

≤ 45 V

I

200 350 – mA VQ=4V

– 180 200 µA Tj = 25 °C; IQ = 0 mA

– 180 230 µA IQ = 0 mA;

T

= 85 °C

j

–512mAIQ = 150 mA

– 0.25 0.5 V IQ = 150 mA

Q

Q

–30 –5 – mV IQ = 5 to 150 mA;

V

= 6 V

I

–520mVVI = 6 to 28 V

I

= 5 mA

Q

1)

Reset Generator

Reset threshold

V

RT

4.5 4.65 4.8 V RADJ connected to

GND

Reset headroom ∆

Reset adjust threshold

Reset low voltage

Reset hi gh voltage

Reset pull-up

Charging current I

Semiconductor Group 7 1998-11-01

V

V

RADJTH

V

ROL

V

ROH

R

RO

d

Q,RT

180 300 – mV IQ = 10 mA

1.28 1.35 1.45 V VQ ≥ 3.5 V

– 0.20 0.40 V R

= 10 kΩ to V

ext

V

≥ 1 V

Q

Q

4.5 – – V –

20 30 45 kΩ Internal connected to V

258 µA VD = 1.0 V

Q

Page 8

TLE 4278 G

Electrical Characteristics (cont’d)

V

= 13.5 V; – 40 °C ≤ Tj≤ 125 °C (unless otherwise specified)

I

Parameter Symbol Limit Values Unit Test Condition

min. typ. max.

Upper timing threshold V

Lower reset timing

V

threshold

Delay time

Reset reaction time

t

t

Watchdog

Activating threshold

Current ratio

Slew rate

V

I

V

Watchdog low voltage V

Watchdog high voltage V

Watchdog pull-up

R

Charge current I

Discharge current

I

DU

DRL

d

RR

WADJ

Q/IWADJ

WI

WOL

WOH

WO

d

dis

1.5 1.9 2.3 V –

0.2 0.3 0.4 V –

12 20 28 ms CD = 47 nF

0.4 1.0 2.0 µs CD = 47 nF

1.28 1.35 1.45 V Voltage at WADJ

650 720 800 – IQ ≤ 10 mA

5–– V/µs From 20% up to 80% V

–0.20.4VR

= 10 kΩ to V

ext

Q

4.5 – – V –

20 30 45 kΩ Internal connected to V

258 µA VD = 1.0 V

0.6 1.3 2.0 µA VD = 1.0 V

Q

Q

Upper timing threshold

Lower watchdog timing

V

V

DU

DWL

1.5 1.9 2.3 V –

0.5 0.7 0.9 V –

threshold

Watchdog output period

Watchdog output low

T

t

WP

WR

42 60 80 ms Cd = 47 nF

71319msVQ> V

time

Watchdog trigger time T

1)

Measured when the output voltage VQ has dropped 100 mV from the nominal value.

WT

35 47 61 ms Cd = 47 nF

RT

Semiconductor Group 8 1998-11-01

Page 9

Test Circiut

TLE 4278 G

Figure 3

V

DR

Ι

Ι

C

Ι12Ι

1000 Fµ nF

Ι

WO

Ι

WADJ

Ι

V

WO

V

WADJ

V

V

13 9

CC

470

WO

WADJ

Ι

W

1

TLE 4278

G

2

814

3-5,

6710-12

W

V

Ι

dis

Ι

D

d

C

D

Ι

GND

D

RADJGND

V

RE

V

QΙ

RO

Ι

Q

Q

10 Fµ

Ι

RO

V

RO

V

O

47 nF

AES02115

V

-

VV

=

Outside the control range

O

Ι

Semiconductor Group 9 1998-11-01

Page 10

TLE 4278 G

Application Information

Input, Output

C

The input capacitors

a resistor of approx. 1 Ω in series with

capacitance can be damped. To stabilize the regulation circuit the output capacitor

necessary. Stability is guaranteed at values

operating temperature range.

and CI2 are necessary for compensating line inf luence s. Using

I1

C

, the LC circuit of input i nductivity and input

I1

C

≥ 10 µF with an ESR ≤ 5 Ω within the

Q

C

is

Q

+12 V

C

C

Ι1

Ι2

*)

or short to GND

for internal threshold

Figure 4

Application Circuit

V

Ι

470 nF

C

13 9

TLE 4278G

6210-12

D

D

3-5,

Cooling

Area

47 nF

V

Q

WO

1

RO

14

W

Ι

8

RADJ

7

WADJGND

R R

WADJ

C

R

1

*)

2

Q

22 F

µ

P

µ

AES02116

Semiconductor Group 10 1998-11-01

Page 11

TLE 4278 G

Reset Timing

The power-on reset delay time is defi ned by the charging time of an external capacito r

C

which can be calculated as follows:

d

C

=(∆td× Id)/∆V

d

Definitions: Cd= delay capacitor

t

= delay time

∆

d

I

= charge current, typical 5 mA

d

V = V

∆

V

DU

The reset reaction time

, typical 1.9 V

DU

= upper delay switching threshold at Cd for reset delay time

t

is the time it takes the voltage regulator to set the reset out

rr

LOW after the output voltage has drop ped bel ow the res et thresh old. It i s typic ally 1 µs

C

for delay capacitor o f 4 7 nF. F or o the r v alue s for

the reaction time can be estim ated

d

using the following equation:

t

≈ 20 s/F × C

rr

V

Ι

V

RT

V

Q

d

t

<

RR

Ι

V

d

d

=

dt

C

D

V

DT

V

V

D

t

d

V

RO

Power-on-Reset Voltage Dip Secondary Overload

Thermal

Shutdown

t

RR

Undervoltage

at Input

at OutputSpike

ST

AED01542

Figure 5

Reset Timing (Watchdog Disabled)

Semiconductor Group 11 1998-11-01

Page 12

TLE 4278 G

Reset Switching Threshold

The present default value is 4.65 V. When using the TLE 4278 the reset threshold can

V

be set to 3.5 V <

calculation can be easily done si nce the re set adjust in put current can be neglected . If

this feature is unused, the pin can be left open or even better connected to GND.

R

Definitions: VRT= Reset threshold

V

(Reset adjust input current ≈ 50 nA)

< 4.6 V by connecting an external voltage divider to pin RADJ. The

RTH

= R2× (V

1

= comparator reference voltage, typical 1.35 V

ref

RTH

– V

ref

)/V

ref

TLE 4278 G

V

V

Ι

30 kΩ

>

1

Band-Gap-

Reference

+

-

GND

Band-Gap-

Reference

1.35 V 1.35 V

Q

RO

RADJ

R

1

R

2

AES02553

Figure 6

The reset output pin is internally connected to the 5 V-output Q via a 30 kΩ pull-up

V

resistor. Down to an output voltag e

of typical 1 V the reset LOW sign al at pin RO in

Q

generated.

For the timing of the reset feature please refer to the data sheet, figure 5.

Semiconductor Group 12 1998-11-01

Page 13

TLE 4278 G

Watchdog Activating

The calculation of the externa l resistor w hich a djusts the watch dog sw itch o ff thresh old

can be done by the following equation.

Definitions: V

V

WADJ

R

WADJ

R

I

I

Ι

= V

WADJ

= switch off threshold, typical 1.35 V

WADJ

Q/IWADJ

QACT

= current ratio, typical 720

= switch off load current

Band-Gap-

× (IQ/I

WADJ

Reference

WADJ

)/I

QACT

TLE 4278 G

V

Q

HIGH

Watchdog

+

-

active

LOW

Watchdog

disabled

GND

AES02552

Figure 7

Semiconductor Group 13 1998-11-01

Page 14

TLE 4278 G

Watchdog Timing

The frequency of the watchdog pulses has to be higher than the minimum pulse

C

sequence which is set by the external reset delay capacitor

according to the formulas given in figure 8.

The watchdog output is internally connected to the output Q via a 30 kΩ pull-up resistor.

To generate a watchdo g crea ted res et signal for the mic roco ntroller the pin WO can be

connected to the reset input of the microcontroller. It is also allowed to parallel the

watchdog out to the reset out.

V

W

Ι

V

Ι

. Calculation can be done

d

V

Q

V

D

V

WO

V

-

V

()

WP

DUL

DU

=

=

V

DRL

T

V

DWL

Ι

d

x

Ι

(d+

Ι

dis

)

Ι

dis

Figure 8

Timing of the Watchdog Function

T

WP

T

V

DU

V

DWL

(DU-

C

;

t

D

WR

=

t

WR

VV

)

DWL

C

Ι

d

D

WT

VV

;

(DU-

T

=

WT

DWL

Ι

dis

AED01543

)

C

D

Semiconductor Group 14 1998-11-01

Page 15

Hints for Unused Pins

Symbol Function Connect to

RO Reset output open

D Reset delay open or to output Q

RADJ Reset switching threshold adjust GND

WI Watchdog input GND

WO Watchdog output open

1)

WADJ Watchdog adjust

to output Q via a 270 kΩ resistor:

Watchdog always active

2)

to GND: Watchdog disabled

TLE 4278 G

Semiconductor Group 15 1998-11-01

Page 16

TLE 4278 G

Drop Voltage VDR versus

Output Current

mV

V

DR

700

600

500

400

300

200

100

0

0

I

Q

T

=

C

125

j

T

50 100 150 200 mA

Current Consumption Iq

versus Output Current

AED01544

=

C

25

j

250

Ι

Q

mA

Ι

q

14

12

10

8

6

4

2

0

0 50 150 200

100

V

=13.5 V

Ι

T

=

25

j

I

Q

AED01545

C

250

mA

Ι

Q

Current Consumption I

versus Input Voltage V

mA

Ι

q

10

8

6

4

2

0

0

T

=

C

25

j

=33

Ω

R

L

R

Ω

50=

L

R

Ω

100=

L

10 20 30 40 V

q

I

AED01546

Output Voltage VQ versus

Input Voltage

mA

V

Q

V

I

AED01547

10

8

6

R

Ω

33=

L

4

2

0

0

V

Ι

246 8 V

V

Ι

Semiconductor Group 16 1998-11-01

Page 17

TLE 4278 G

AED01548

-40

0

= 13.5 V

Ι

T

A

040

80 120 C

V

Ι

1

2

3

4

5

6

7

µ

D

V

1.0 V=

d

Ι

dis

Ι

j

Charge Current Id and Discharge

I

Current

versus Temperature T

dis

Switching Voltage V

j

and V

V

D

versus Temperature T

DRL

V

DU, VDWL

j

AED01549

2.8

V

= 13.5 V

Ι

2.4

2.0

V

DU

1.6

1.2

0.8

0.4

V

V

DWL

DRL

0

-40

040

80 120 C

T

j

Output Voltage VQ versus

Temperature

V

V

Q

5.1

5.0

4.9

4.8

T

j

V

=

Ι

13.5 V

AED01550

Output Current Limit IQ versus

Input Voltage

mA

Ι

Q

250

200

150

100

V

I

AED01551

T

=

C

25

j

4.7

50

4.6

-40

04080 120 V

T

j

0

0

10 20 30 40 V

V

j

Semiconductor Group 17 1998-11-01

Page 18

Package Outlines

P-DSO-14-4

(Plastic Dual Small Outline Package)

-0.1

0.2

-0.2

1.45

4

-0.2

1.75 max

TLE 4278 G

0.35 x 45˚

1)

+0.06

0.19

0.35

1.27

+0.15

2)

0.1

0.2 14x

±0.2

6

0.4

+0.8

8˚ max.

14 8

17

8.75

-0.2

1)

Index Marking

1) Does not include plastic or metal protrusion of 0.15 max. per side

2) Does not include dambar protrusion of 0.05 max. per side

GPS05093

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book “Package Information”.

SMD = Surface Mounted Device

Dimensions in mm

Semiconductor Group 18 1998-11-01

Loading...

Loading...