Page 1

A

1 1

B

C

D

E

Compal Confidential

2 2

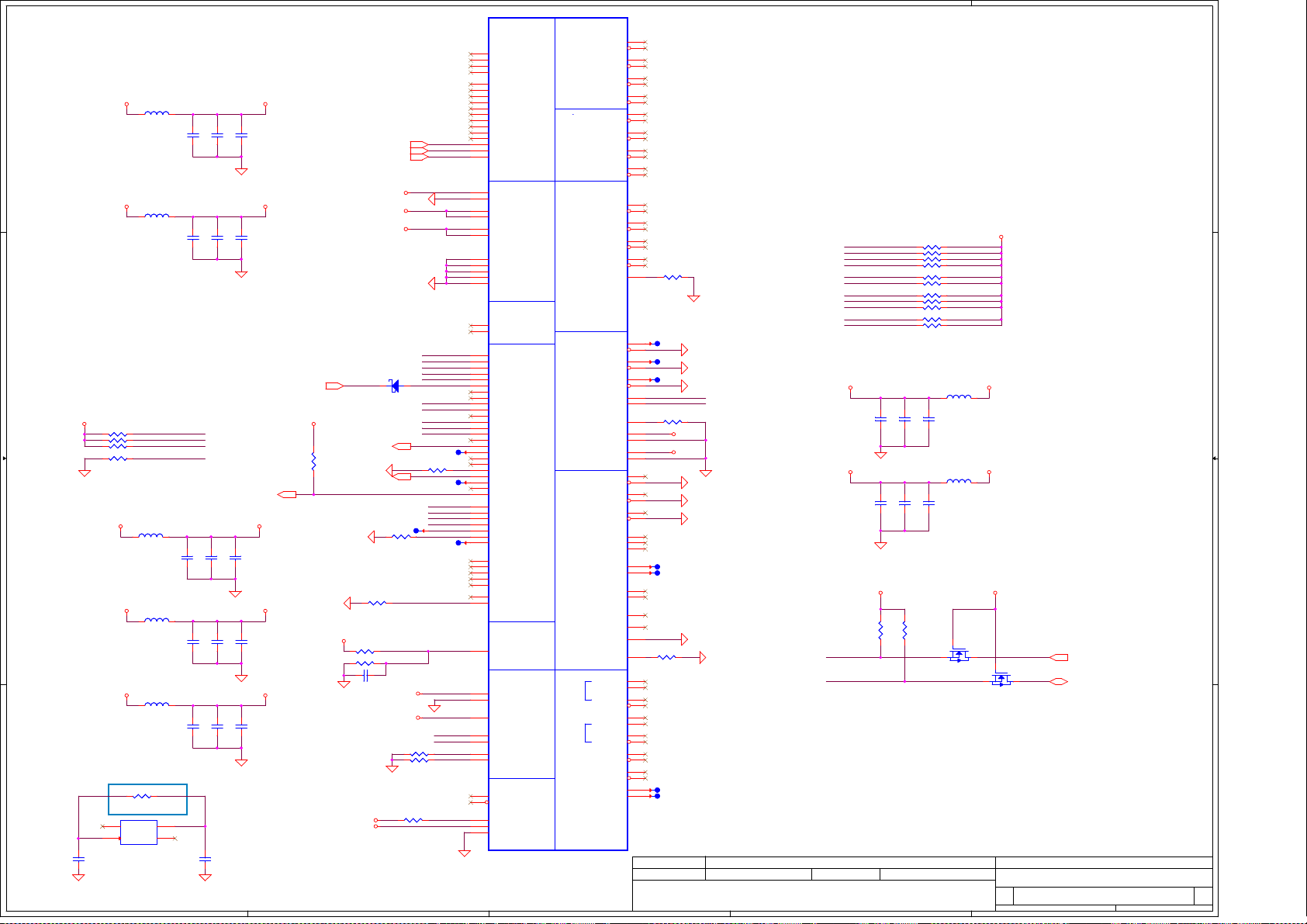

VIUS5 LA-9001P M/B Schematics Document

AMD FP2 Processor with DDRIII + Husdon M3 FCH

AMD VGA Seymour XT

3 3

2012-05-31

REV:0.3

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

C

2012/01/15 2013/01/15

2012/01/15 2013/01/15

2012/01/15 2013/01/15

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

VAUS5 LA9001P M/B

VAUS5 LA9001P M/B

VAUS5 LA9001P M/B

E

1 50Thursday, May 31, 2012

1 50Thursday, May 31, 2012

1 50Thursday, May 31, 2012

0.3

0.3

0.3

www.qdzbwx.com

Page 2

A

Compal confidential

File Name :

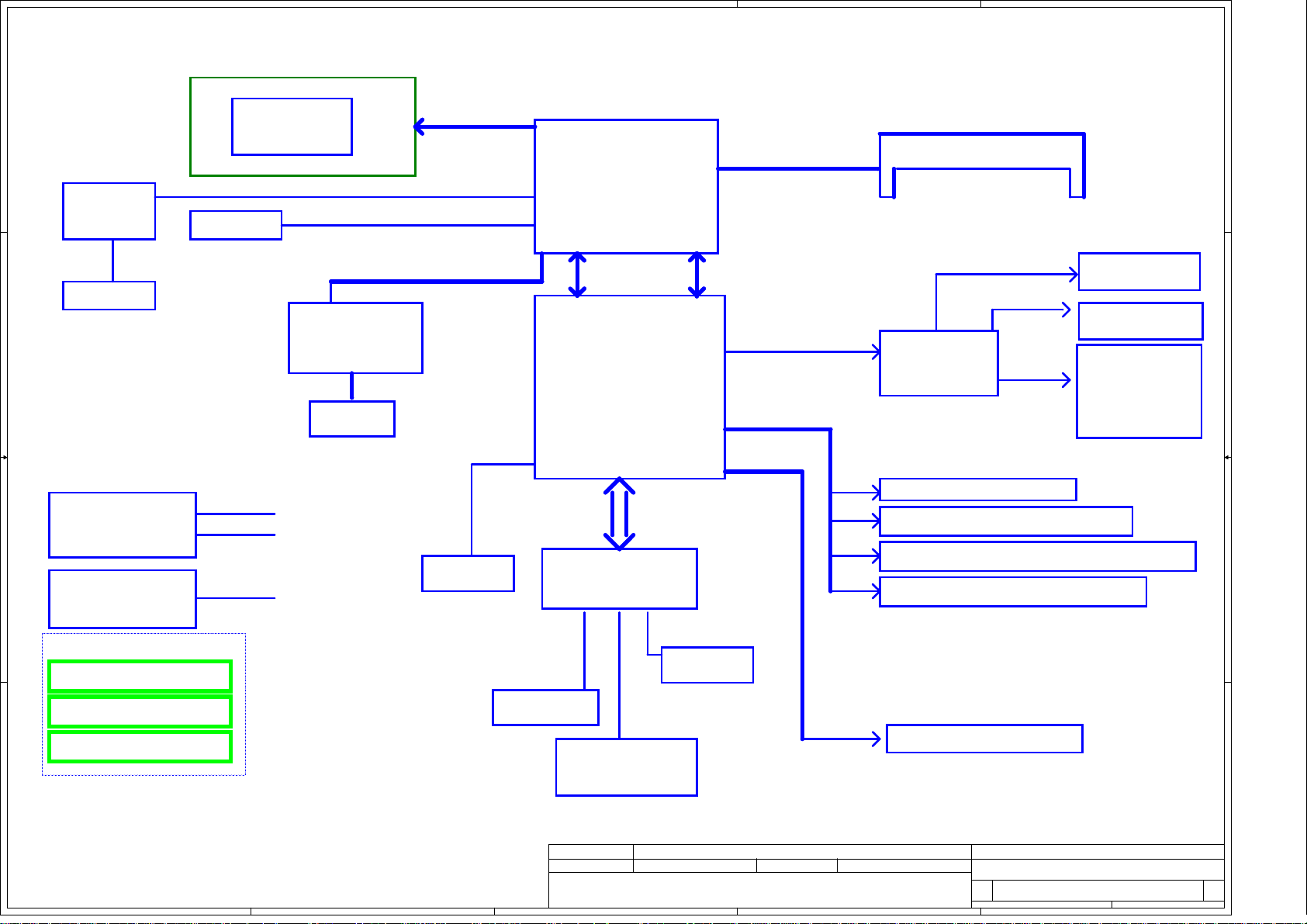

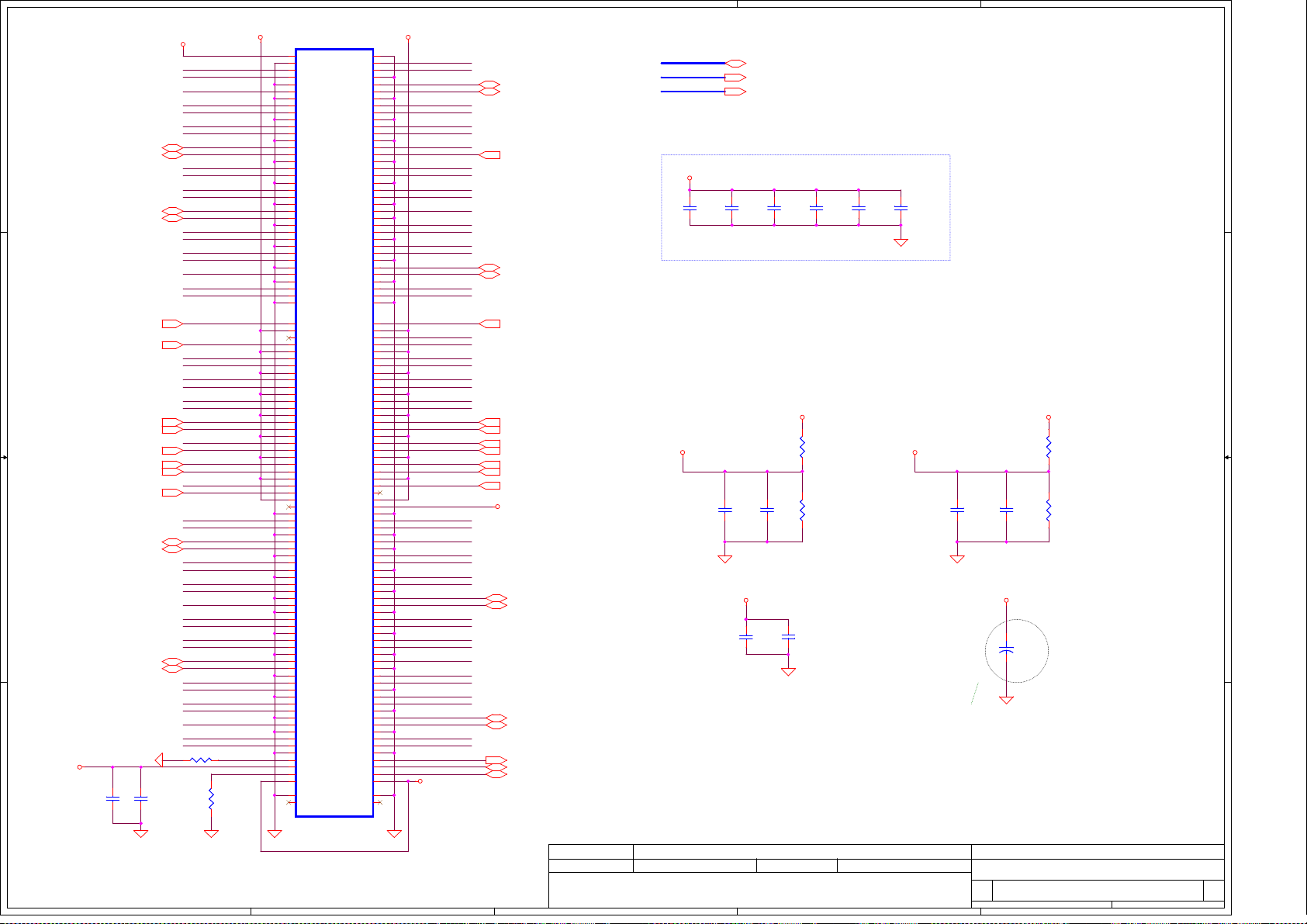

AMD Seymour XT

B

C

D

E

1 1

VRAM

128x16, 64x16

DDR3 x 4

page 15,~21

LVDS

translator

RTD2132S

page 22 page 24

HDMI Conn.

4 * x1 PCI-E 2.0

LVDS Conn.

page 23

2 2

PCI Express

Mini card Slot 1

WLAN

3 3

page 25

PCI Express

Mini card Slot 2

page 25

USB(reserve for WiMAX)

PCI-E(WLAN)

SATA(SSD)

GPP0

LAN(10/100/Giga)

Realtek

8105E-VD (10/100)

8111F-CGT (Giga)

page 26

RJ45 CONN

page 27

SPI ROM

Gen2PCIE x 8

DP Port0

DP Port2

page 11

AMD FP2 APU

Trinity

BGA 813 pin

27mm x 30mm

page 5,~8

x4 UMI Gen. 1

2.5GT/s per lane

Hudson M3

uFCBGA-656

24.5mm x 24.5mm

page 10,~14

LPC BUS

EC

ENE KB9012

page 31

Memory BUS(DDRIII)

Dual Channel

1.5V DDRIII 1333MT/s

Upgradeable to 4G Memory

AZALIA

1*USB3.0,6*USB2.0

1*SATA serial

204pin DDRIII-SO-DIMM X 1

BANK 0, 1

page 9

2Channel Speaker

Single Digital MIC

IO Board page 32

Audio Codec

RealTek

ALC259-VC2

CMOS Camera

page 30

page 23

USB PORT 3.0 x1(Left)

Audio Combo Jack

(APPLE type)

Stereo

HeadPhone Output

Microphone Input

IO Board

page 33

Card Reader RTS 5178 (2in1)

USB PORT 2.0 x2(Right)

page 32

IO Board

page 30

page 32

page 32

IO Board

www.qdzbwx.com

Sub-borad

POWER Board

LED Board

IO Board

4 4

A

B

Touch Pad

page 32

Thermal Sensor

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

C

Int.KBD

page 32

SATA1

page 28

Compal Secret Data

Compal Secret Data

2012/01/15 2013/01/15

2012/01/15 2013/01/15

2012/01/15 2013/01/15

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

SATA2.0 HDD CONN

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

page 29

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

MB Block Diagram

MB Block Diagram

MB Block Diagram

VAUS5 LA9001P M/B

VAUS5 LA9001P M/B

VAUS5 LA9001P M/B

2 50Friday, May 25, 2012

2 50Friday, May 25, 2012

2 50Friday, May 25, 2012

E

0.3

0.3

0.3

Page 3

A

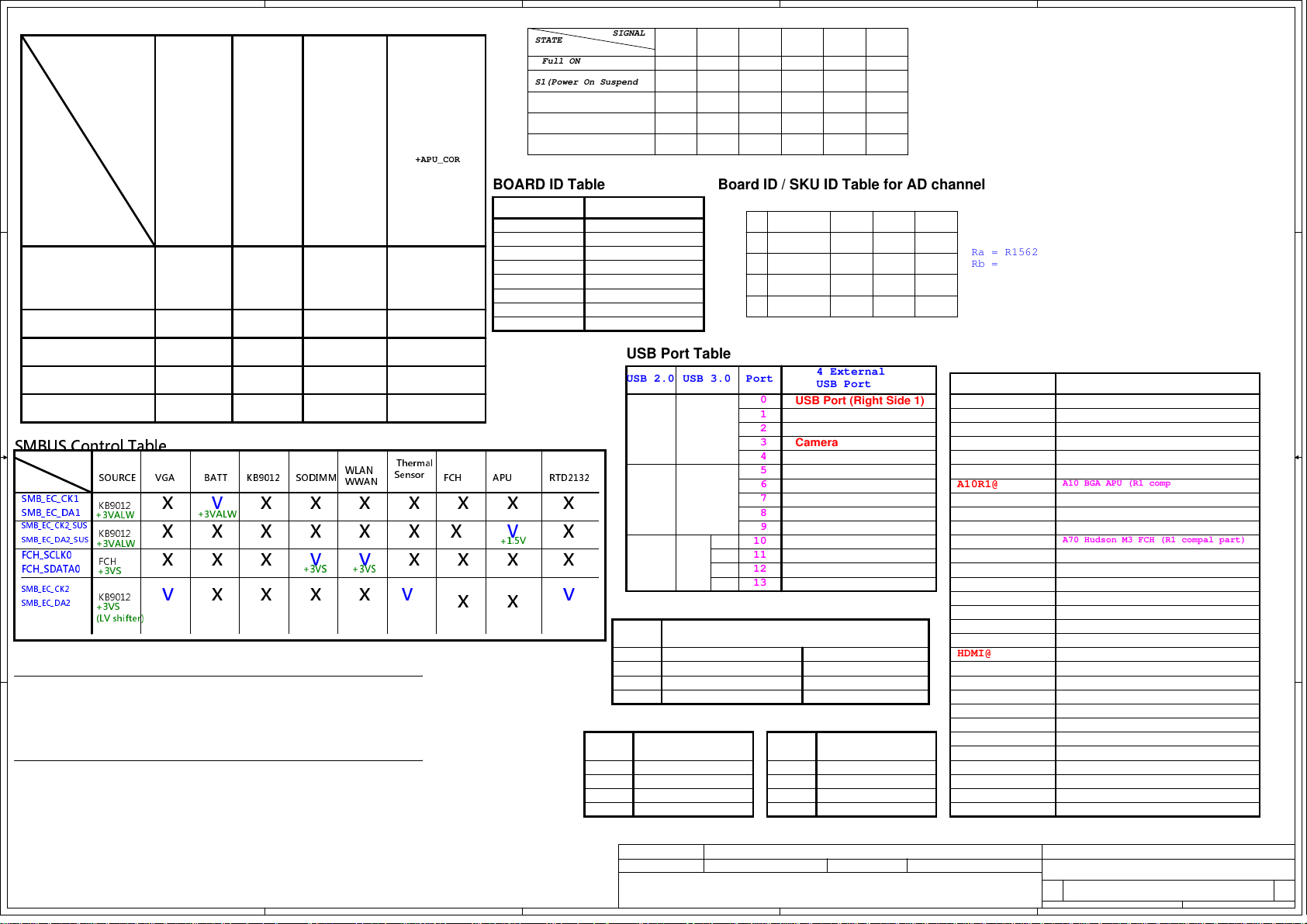

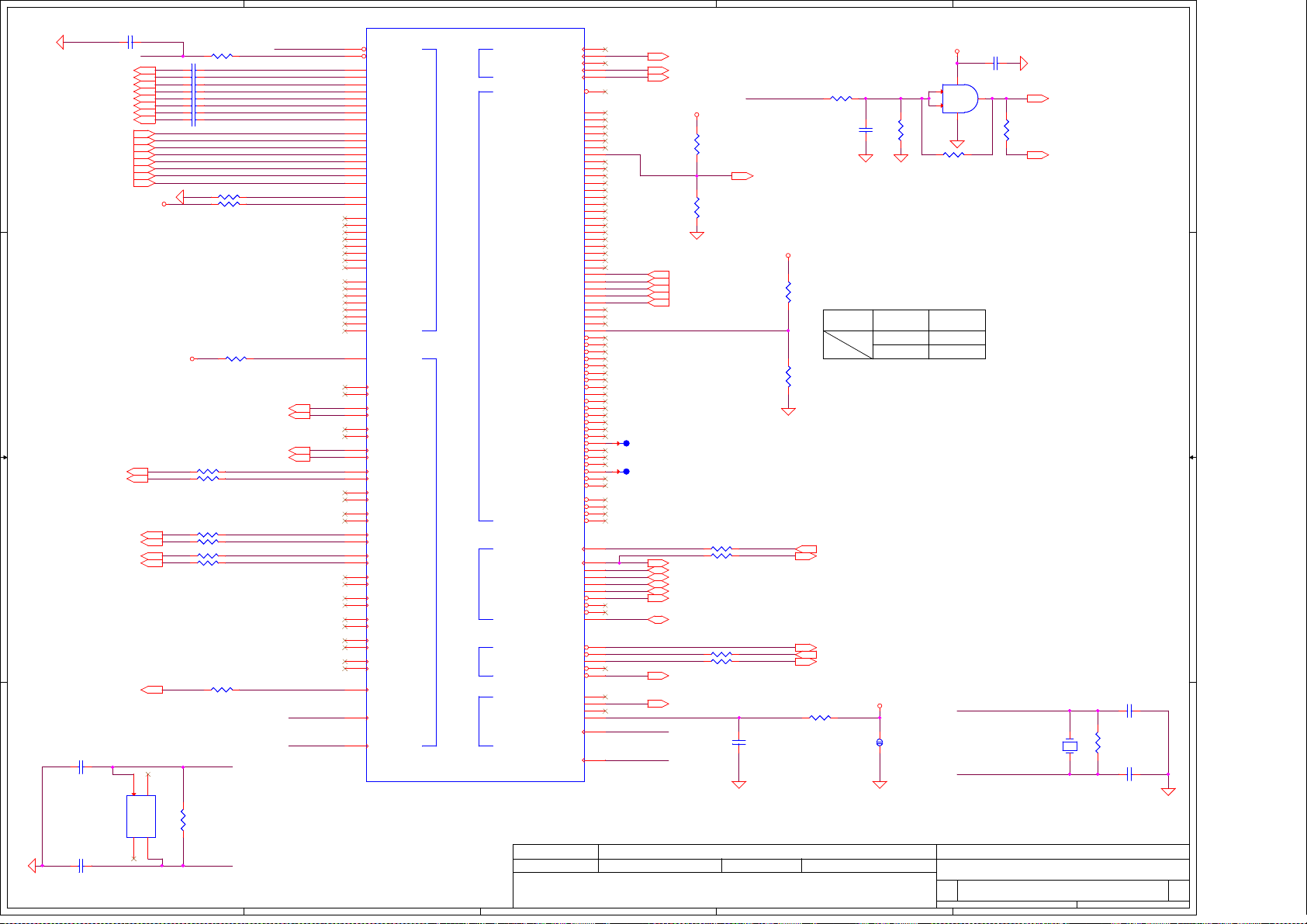

Voltage Rails

power

plane

1 1

+B

State

S0

S3

2 2

S5 S4/AC

S5 S4/ Battery only

S5 S4/AC & Battery

don't exist

O

O

O

O

X

+5VALW

+3VALW

+1.1VALW

O

O

O

X

X X X

+1.5V

+1.5V_APU

O

X X

X

SMBUS Control Table

SOURCE

SMB_EC_CK1

SMB_EC_DA1

SMB_EC_CK2_SUS

SMB_EC_DA2_SUS

FCH_SCLK0

FCH_SDATA0

3 3

SMB_EC_CK2

SMB_EC_DA2

KB9012

+3VALW

KB9012

+3VALW

FCH

+3VS

KB9012

+3VS

(LV shifter)

EC SM Bus1 address

Device

Smart Battery

Address Address

0001 011X b

FCH SM Bus address

Device Address

DDR DIMM1

4 4

VGA BATT KB9012 SODIMM

X V

+3VALW

X

X

X

V V V

1001 000Xb

X

X X

X

X X

EC SM Bus2 address

Device

Thermal Sen sor

SB-TSI(default)

VGA(thermal)

RTD2132S

WLAN

WWAN

X

X

V

+3VS +3VS

X

XX

V

1001_101xb

1001_100xb

1000_001xb

1010_1000b

B

+5VS

+3VS

+2.5VS

+1.5VS

+1.2VS

+1.1VS

+0.75VS

+APU_CORE

+APU_CORE_NB

+VGA_CORE

+3.3VGS

+1.8VGS

+1.5VGS

+1.0VGS

Thermal

Sensor

X

X

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

SIGNAL

C

SLP_S3# SLP_S5# +VALW +V +VS Clock

ON

ON

ON

ON

ON

ONONON ON

ON

ON

OFF

OFF

OFF

OFF

OFF

HIGH HIGH

HIGHHIGH

HIGH

HIGH

LOW

HIGH

LOW LOW

LOW

OFF

OFF

OFF

D

E

Board ID / SKU ID Table for AD channelBOARD ID Table

Board ID

0

1

2

3

OO

4

5

6

X

7

PCB Revision

0.3

ID BRD ID R a Rb Vab

x

0

0V

0.25V

0.5V

0.82VR01 EVT

1

2

3

R10 MP0

R03 PVT

R02 DVT

100K

100K

100K

8.2K

18K

33K

Ra = R1562

Rb = R1564

USB Port Table

X

USB 3.0USB 2.0 Port

0

1

2

3

4 External

USB Port

USB Port (Right Side 1)

USB Port (Right Side 2)

Mini Card(WLAN)

Camera

4

5

FCH

X

XX XX

X

X

APU RTD2132

X X

V

+1.5V

X X

X

0

1

XHCI

2

3

USB OC MAPPING

CardReader

6

7

8

9

10

USB Port (Left Side)

11

12

13

OC# USB Port

0

1

USB20 port10

USB20 port0 port1

USB30 port0

2

3

APU PCIE PORT LIST

Port Device

1

LAN

2

WLAN

3

4

FCH PCIE PORT LIST

Port Device

1

2

3

4

BOM Structure Table

BTO ItemBOM Structure

A4R1@

A4R3@

A6R1@

A6R3@

A8R1@

A8R3@

A10R1@

A10R3@

SXTR1@

SXTR3@

A70MR1@

A70MR3@

PX@

CMOS@

UMA@

GAS@

8105@

GIGA@

HDMI@

NONAOAC@

AOAC@

ME@

DEBUG@

@

SSD@

A4 BGA APU (R1 compal part)

A4 BGA APU (R3 compal part)

A6 BGA APU (R1 compal part)

A6 BGA APU (R3 compal part)

A8 BGA APU (R1 compal part)

A8 BGA APU (R3 compal part)

A10 BGA APU (R1 compal part)

A10 BGA APU (R3 compal part)

Seymour XT GPU (R1 compal part)

Seymour XT GPU (R3 compal part)

A70 Hudson M3 FCH (R1 compal part)

A70 Hudson M3 FCH (R3 compal part)

Common VGA circuit

CMOS Camera part

UMA strap pin

Gastube

RTL8105E

RTL8111F

HDMI part

No AOAC function

support AOAC function

ME part

Debug Switch (MP will remove)

Unpop

SSD part

www.qdzbwx.com

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

C

2012/01/15 2013/01/15

2012/01/15 2013/01/15

2012/01/15 2013/01/15

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

Notes List

Notes List

Notes List

VAUS5 LA9001P M/B

VAUS5 LA9001P M/B

VAUS5 LA9001P M/B

E

3 50Tuesday, May 29, 2012

3 50Tuesday, May 29, 2012

3 50Tuesday, May 29, 2012

0.3

0.3

0.3

Page 4

A

B

C

D

E

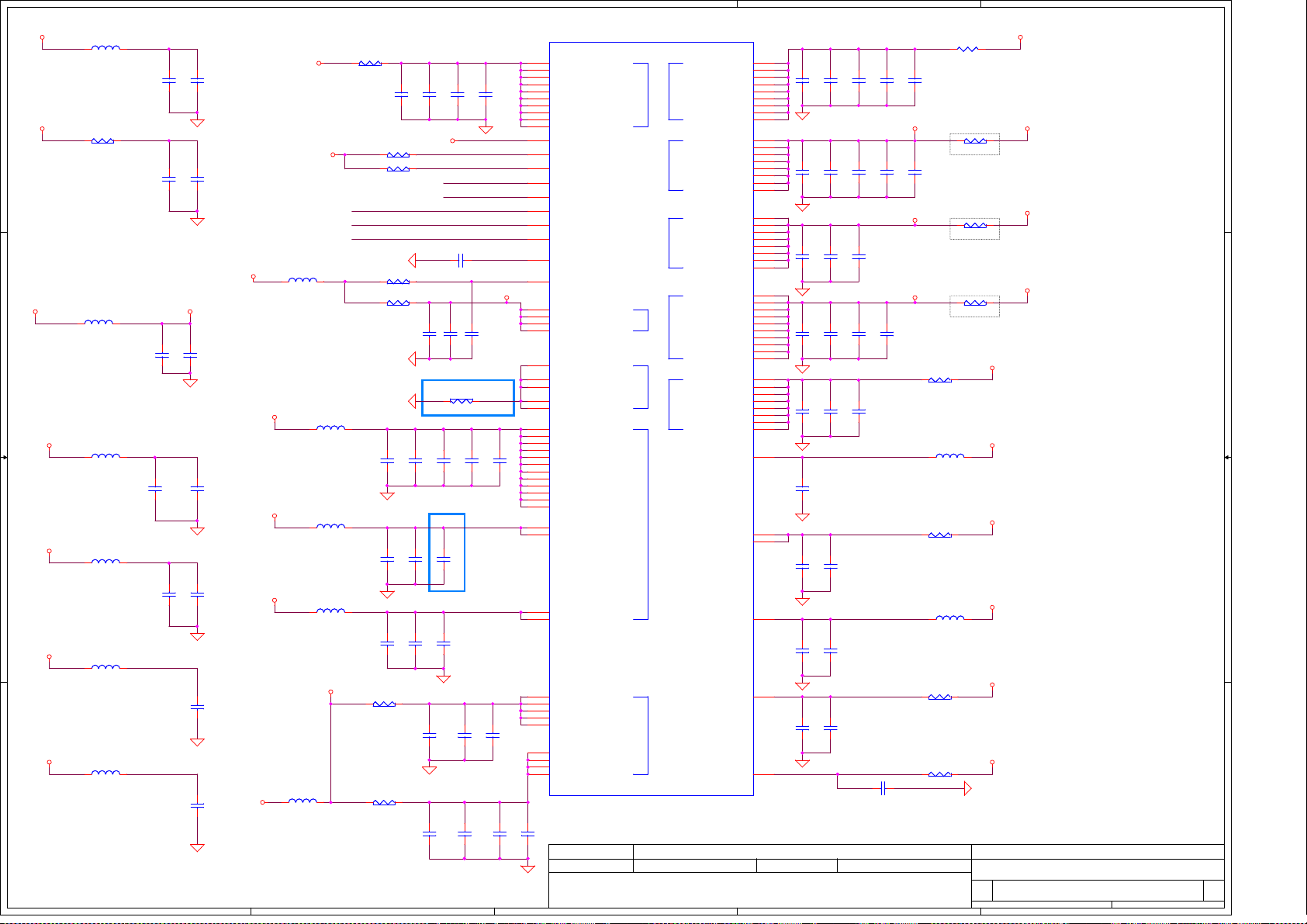

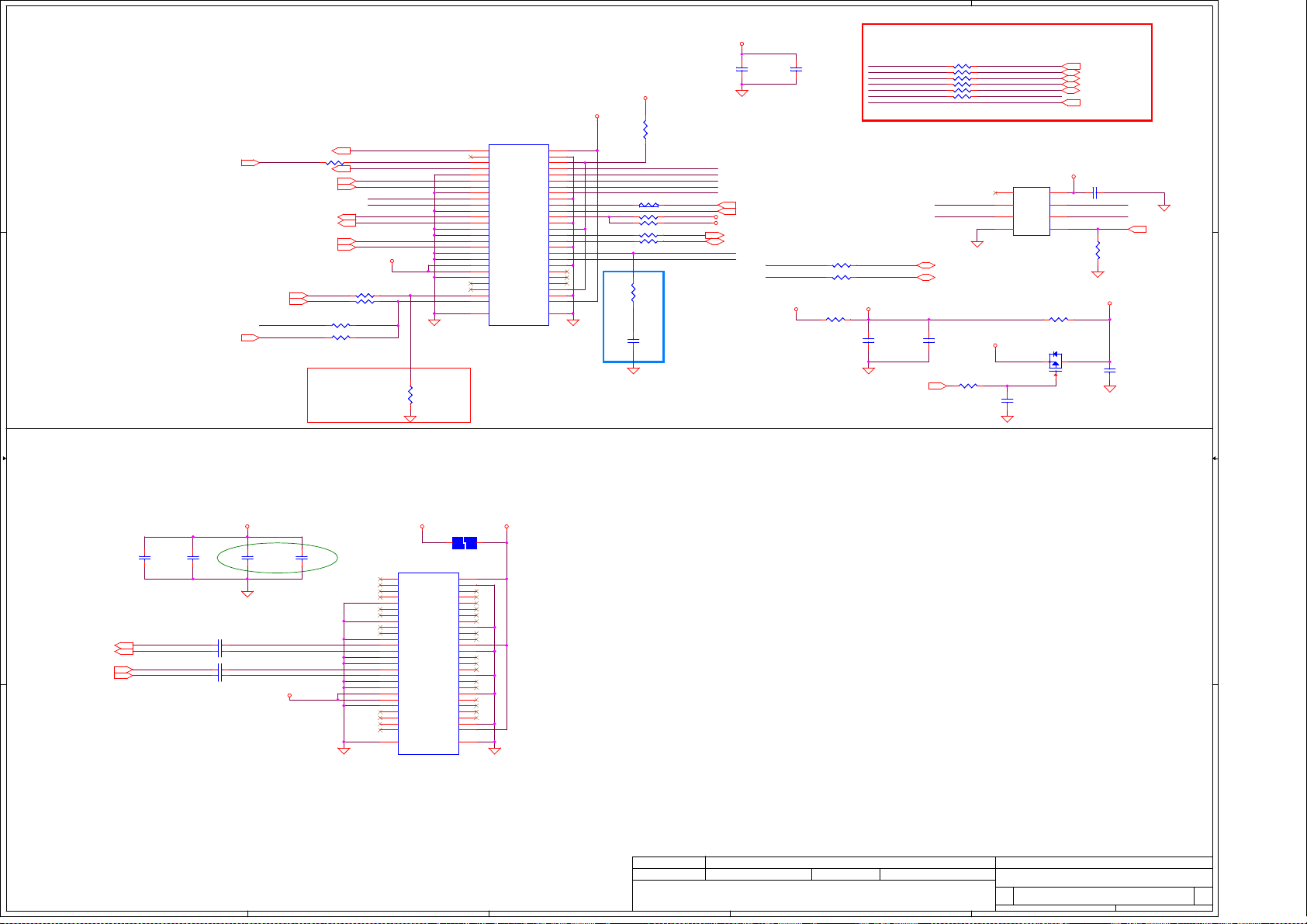

Power-Up/Down Sequence

"Thames" has the following requirements with regards to power-supply sequencing

to avoid damaging the ASIC:

All the ASIC supplies, except for VDDR3, must fully reach their respective

‧

nominal voltages within 20 ms of the start of the ramp-up sequence, though a

1 1

shorter ramp-up duration is preferred. There is no timing requirement on the

ramp up of VDDR3 relative to other power rails.

The external pull-up resistors on the DDC/AUX signals (if applicable) should

‧

ramp up before or after both VDDC and VDD_CT have ramped up.

VDDC and VDD_CT should not ramp up simultaneously. For example, VDDC

‧

should reach 90% before VDD_CT starts to ramp up (or vice versa). For BACO

enabled designs, VDDC must ramp up before VDD_CT at system power up.

For power down, reversing the ramp-up sequence is recommended

‧

VDDR3(3.3VGS)

Without BACO option :

PE_GPIO0 : Low -> Reset dGPU ; High ->Normal operation

PE_GPIO1 : Low -> dGPU Power OFF ; High -> dGPU Power ON

BACO option :

PE_GPIO0 : High ->Normal operation (dGPU is not reset on BACO mode)

PE_GPIO1 : Low -> dGPU Power OFF ; High -> dGPU Power ON (always High)

dGPU Power Pins Max current

PCIE_PVDD, PCIE_VDDR, TSVDD, VDDR4, VDD_CT,

DPE_PVDD, DP[F:E]_VDD18, DP[D:A]_PVDD,

DP[D:A]_VDD18, AVDD, VDD1DI, A2VDDQ, VDD2DI,

DPLL_PVDD, MPV18, and SPV18

DP[F:E]_VDD10, DP[D:A]_VDD10, DPLL_VDDC, and

SPV10

PCIE_VDDC

VDDR3

BIF_VDDC (current consumption = 55mA@1.0V, in

BACO mode)

VDDR1

VDDC/VDDCI

Voltage

1.8V

1.0V

1.0V

3.3V

Same as

VDDC

1.5V

TBD

PX 3.0

OFF

OFF

OFF

OFF

OFF

OFF

OFF

BACO Mode

ON

ON

ON

ON

ON

Same as

PCIE_VDDC

OFF

OFF

1679mA

775mA

1.1A

60mA

70mA

1.2A

28

PCIE_VDDC(1.0V)

2 2

VDDR1(1.5VGS)

VDDC/VDDCI(1.12V)

VDD_CT(1.8V)

PERSTb

REFCLK

Straps Reset

Straps Valid

3 3

Global ASIC Reset

PX5.0

less than 20ms (Seymour)

4 4

A

T4+16clock

B

iGPU

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2012/01/15 2013/01/15

2012/01/15 2013/01/15

2012/01/15 2013/01/15

PE_GPIO0(PXS_RST#)

PE_GPIO1(PXS_PWREN)

+3.3VALW

+1.5V_IO

+5VLAW

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

MOS

PWM

Regulator

dGPU

1

2

5

+3.3VGS

+1.0VGS

+1.8VGS

+VGA_CORE

BIF_VDDC

Short PX_MODE and PX_PWREN

B+

Regulator

+B

Regulator

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

+1.5VGS

3

+VGA_CORE

4

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

VGA Notes List

VGA Notes List

VGA Notes List

VAUS5 LA9001P M/B

VAUS5 LA9001P M/B

VAUS5 LA9001P M/B

E

www.qdzbwx.com

0.3

0.3

4 50Friday, May 25, 2012

4 50Friday, May 25, 2012

4 50Friday, May 25, 2012

0.3

Page 5

A

B

C

D

E

PCIE_CRX_GTX_P[0..7]<15>

UCPU1A

UCPU1A

PCIE_CRX_GTX_P0

PCIE_CRX_GTX_N0

PCIE_CRX_GTX_P1

PCIE_CRX_GTX_N1

1 1

PCIE_CRX_DTX_P0<26>

PCIE_CRX_DTX_N0<26>

PCIE_CRX_DTX_P1<25>

2 2

PCIE_CRX_DTX_N1<25>

UMI_RXP0<10>

UMI_RXN0<10>

UMI_RXP1<10>

UMI_RXN1<10>

UMI_RXP2<10>

UMI_RXN2<10>

UMI_RXP3<10>

UMI_RXN3<10>

+1.2VS

PCIE_CRX_GTX_P2

PCIE_CRX_GTX_N2

PCIE_CRX_GTX_P3

PCIE_CRX_GTX_N3

PCIE_CRX_GTX_P4

PCIE_CRX_GTX_N4

PCIE_CRX_GTX_P5

PCIE_CRX_GTX_N5

PCIE_CRX_GTX_P6

PCIE_CRX_GTX_N6

PCIE_CRX_GTX_P7

PCIE_CRX_GTX_N7

1 2

R1 196_0 402_1%R1 196_0 402_1%

P_ZVDDP

AP1

P_GFX_RXP[0]

AP2

P_GFX_RXN[0]

AM1

P_GFX_RXP[1]

AM2

P_GFX_RXN[1]

AK3

P_GFX_RXP[2]

AK4

P_GFX_RXN[2]

AJ1

P_GFX_RXP[3]

AJ2

P_GFX_RXN[3]

AH4

P_GFX_RXP[4]

AH3

P_GFX_RXN[4]

AF2

P_GFX_RXP[5]

AF1

P_GFX_RXN[5]

AD1

P_GFX_RXP[6]

AD2

P_GFX_RXN[6]

AB3

P_GFX_RXP[7]

AB4

P_GFX_RXN[7]

AA1

P_GFX_RXP[8]

AA2

P_GFX_RXN[8]

Y4

P_GFX_RXP[9]

Y3

P_GFX_RXN[9]

V2

P_GFX_RXP[10]

V1

P_GFX_RXN[10]

T1

P_GFX_RXP[11]

T2

P_GFX_RXN[11]

P3

P_GFX_RXP[12]

P4

P_GFX_RXN[12]

N1

P_GFX_RXP[13]

N2

P_GFX_RXN[13]

M4

P_GFX_RXP[14]

M3

P_GFX_RXN[14]

K2

P_GFX_RXP[15]

K1

P_GFX_RXN[15]

AH5

P_GPP_RXP[0]

AH6

P_GPP_RXN[0]

AG5

P_GPP_RXP[1]

AG6

P_GPP_RXN[1]

AE6

P_GPP_RXP[2]

AE5

P_GPP_RXN[2]

AD6

P_GPP_RXP[3]

AD5

P_GPP_RXN[3]

AM10

P_UMI_RXP[0]

AN10

P_UMI_RXN[0]

AN8

P_UMI_RXP[1]

AM8

P_UMI_RXN[1]

AP8

P_UMI_RXP[2]

AR8

P_UMI_RXN[2]

AR7

P_UMI_RXP[3]

AP7

P_UMI_RXN[3]

AR11

P_ZVDDP

TRINITY-A8-SERIES_BGA813

TRINITY-A8-SERIES_BGA813

A8R3@

A8R3@

P_GFX_TXP[0]

P_GFX_TXN[0]

P_GFX_TXP[1]

P_GFX_TXN[1]

P_GFX_TXP[2]

P_GFX_TXN[2]

P_GFX_TXP[3]

P_GFX_TXN[3]

P_GFX_TXP[4]

P_GFX_TXN[4]

P_GFX_TXP[5]

P_GFX_TXN[5]

P_GFX_TXP[6]

P_GFX_TXN[6]

P_GFX_TXP[7]

P_GFX_TXN[7]

P_GFX_TXP[8]

GRAPHICSGPPUMI

GRAPHICSGPPUMI

P_GFX_TXN[8]

P_GFX_TXP[9]

P_GFX_TXN[9]

P_GFX_TXP[10]

P_GFX_TXN[10]

P_GFX_TXP[11]

P_GFX_TXN[11]

P_GFX_TXP[12]

P_GFX_TXN[12]

P_GFX_TXP[13]

P_GFX_TXN[13]

P_GFX_TXP[14]

P_GFX_TXN[14]

P_GFX_TXP[15]

P_GFX_TXN[15]

P_GPP_TXP[0]

P_GPP_TXN[0]

P_GPP_TXP[1]

P_GPP_TXN[1]

P_GPP_TXP[2]

P_GPP_TXN[2]

P_GPP_TXP[3]

P_GPP_TXN[3]

P_UMI_TXP[0]

P_UMI_TXN[0]

P_UMI_TXP[1]

P_UMI_TXN[1]

P_UMI_TXP[2]

P_UMI_TXN[2]

P_UMI_TXP[3]

P_UMI_TXN[3]

P_ZVSS

AN1

AN2

AM4

AM3

AK2

AK1

AH1

AH2

AF3

AF4

AE1

AE2

AD4

AD3

AB2

AB1

Y1

Y2

V3

V4

U1

U2

T4

T3

P2

P1

M1

M2

K3

K4

J1

J2

AG7

AG8

AE7

AE8

AD7

AD8

AB6

AB5

AN6

AM6

AP6

AR6

AP4

AR4

AP3

AR3

AP11

Compensation Resistor to VSS Compensation Resistor to VDDP

PCIE_CTX_C_GRX_P0

PCIE_CTX_C_GRX_N0

PCIE_CTX_C_GRX_P1

PCIE_CTX_C_GRX_N1

PCIE_CTX_C_GRX_P2

PCIE_CTX_C_GRX_N2

PCIE_CTX_C_GRX_P3

PCIE_CTX_C_GRX_N3

PCIE_CTX_C_GRX_P4

PCIE_CTX_C_GRX_N4

PCIE_CTX_C_GRX_P5

PCIE_CTX_C_GRX_N5

PCIE_CTX_C_GRX_P6

PCIE_CTX_C_GRX_N6

PCIE_CTX_C_GRX_P7

PCIE_CTX_C_GRX_N7

PCIE_CTX_C_DRX_P0

PCIE_CTX_C_DRX_N0

PCIE_CTX_C_DRX_P1

PCIE_CTX_C_DRX_N1

UMI_TXP0_C

UMI_TXN0_C

UMI_TXP1_C

UMI_TXN1_C

UMI_TXP2_C

UMI_TXN2_C

UMI_TXP3_C

UMI_TXN3_C

1 2

P_ZVSS

R2 196_0 402_1%R2 196_0 402_1%

1 2

C1 0.1U_0402_16V7KPX@C1 0.1U_0402_16V7KPX@

1 2

C2 0.1U_0402_16V7KPX@C2 0.1U_0402_16V7KPX@

1 2

C3 0.1U_0402_16V7KPX@C3 0.1U_0402_16V7KPX@

1 2

C4 0.1U_0402_16V7KPX@C4 0.1U_0402_16V7KPX@

1 2

C5 0.1U_0402_16V7KPX@C5 0.1U_0402_16V7KPX@

1 2

C6 0.1U_0402_16V7KPX@C6 0.1U_0402_16V7KPX@

1 2

C7 0.1U_0402_16V7KPX@C7 0.1U_0402_16V7KPX@

1 2

C8 0.1U_0402_16V7KPX@C8 0.1U_0402_16V7KPX@

1 2

C9 0.1U_0402_16V7KPX@C9 0.1U_0402_16V7KPX@

1 2

C10 0.1U_0402_16V7KPX@C10 0.1U_0402_16V7KPX@

1 2

C11 0.1U_0402_16V7KPX@C11 0.1U_0402_16V7KPX@

1 2

C12 0.1U_0402_16V7KPX@C12 0.1U_0402_16V7KPX@

1 2

C13 0.1U_0402_16V7KPX@C13 0.1U_0402_16V7KPX@

1 2

C14 0.1U_0402_16V7KPX@C14 0.1U_0402_16V7KPX@

1 2

C15 0.1U_0402_16V7KPX@C15 0.1U_0402_16V7KPX@

1 2

C16 0.1U_0402_16V7KPX@C16 0.1U_0402_16V7KPX@

1 2

C33 0.1U_0402_16V7KC33 0.1U_0402_16V7K

1 2

C34 0.1U_0402_16V7KC34 0.1U_0402_16V7K

1 2

C35 0.1U_0402_16V7KC35 0.1U_0402_16V7K

1 2

C36 0.1U_0402_16V7KC36 0.1U_0402_16V7K

1 2

C37 0.1U_0402_16V7KC37 0.1U_0402_16V7K

1 2

C38 0.1U_0402_16V7KC38 0.1U_0402_16V7K

1 2

C39 0.1U_0402_16V7KC39 0.1U_0402_16V7K

1 2

C40 0.1U_0402_16V7KC40 0.1U_0402_16V7K

1 2

C41 0.1U_0402_16V7KC41 0.1U_0402_16V7K

1 2

C42 0.1U_0402_16V7KC42 0.1U_0402_16V7K

1 2

C43 0.1U_0402_16V7KC43 0.1U_0402_16V7K

1 2

C44 0.1U_0402_16V7KC44 0.1U_0402_16V7K

PCIE_CTX_GRX_P[0..7] < 15>

PCIE_CTX_GRX_N[0..7] <15>PCIE_CRX_GTX_N[0..7]<15>

PCIE_CTX_GRX_P0

PCIE_CTX_GRX_N0

PCIE_CTX_GRX_P1

PCIE_CTX_GRX_N1

PCIE_CTX_GRX_P2

PCIE_CTX_GRX_N2

PCIE_CTX_GRX_P3

PCIE_CTX_GRX_N3

PCIE_CTX_GRX_P4

PCIE_CTX_GRX_N4

PCIE_CTX_GRX_P5

PCIE_CTX_GRX_N5

PCIE_CTX_GRX_P6

PCIE_CTX_GRX_N6

PCIE_CTX_GRX_P7

PCIE_CTX_GRX_N7

PCIE_CTX_DRX_P0 <26>

PCIE_CTX_DRX_N0 <26>

PCIE_CTX_DRX_P1 <25>

PCIE_CTX_DRX_N1 <25>

UMI_TXP0 <10>

UMI_TXN0 <10>

UMI_TXP1 <10>

UMI_TXN1 <10>

UMI_TXP2 <10>

UMI_TXN2 <10>

UMI_TXP3 <10>

UMI_TXN3 <10>

LAN

WLAN

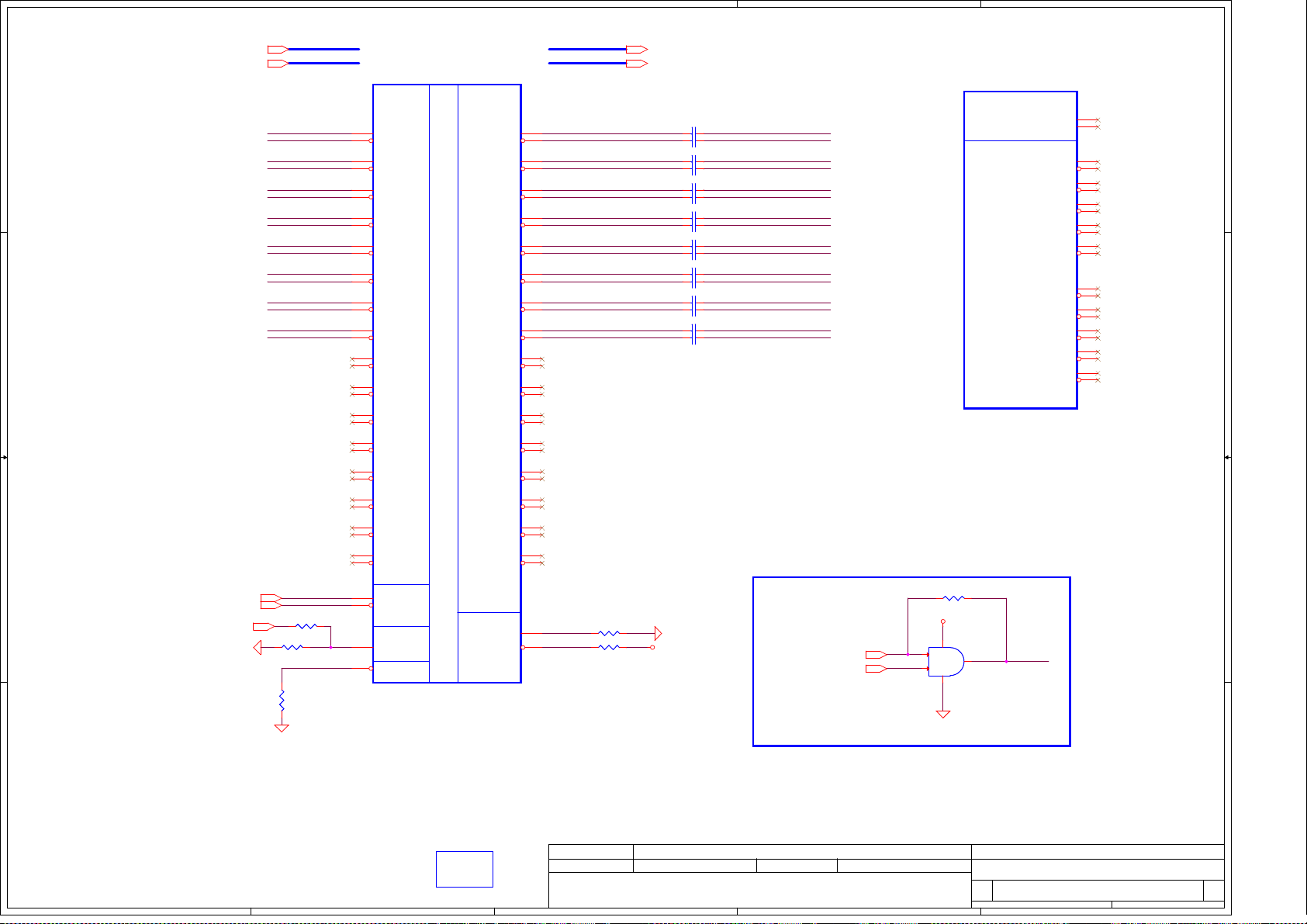

All power supplies in Power Sequencing Group A must be stable and within specification before

any power supply in Power Sequencing Group B is greater than 10 percent of its specified typical

operating value.

3 3

All power supplies in Power Sequencing Group B must be stable and within specification one ms

before the assertion of PWROK.

No sequencing relationships are required between the power sequencing groups during S3 entry.

DDR3 compatible processors require VDDIO to remain powered and within specification during the

S3 sleep state. All other processor power supply planes are powered down during S3.

Power Sequence of APU

+1.5V (+1.5V_APU)

UCPU1

A4R3@UCPU1

A4R3@

UCPU1

A6R3@UCPU1

A6R3@

UCPU1

A10R3@UCPU1

A10R3@

ZZZ1

ZZZ1

+2.5VS (+APU_VDDA)

+1.5VS

A6 SERIES ZM212169E2451 2.1G BGA813

A4 SERIES ZM198169E2351 1.9G BGA813

A4 SERIES ZM198169E2351 1.9G BGA813

UCPU1

4 4

A4 SERIES AM4355SHE23HJ 1.9G BGA813

A4 SERIES AM4355SHE23HJ 1.9G BGA813

UCPU1

A8 SERIES AM4555SHE44HJ 1.6G BGA813

A8 SERIES AM4555SHE44HJ 1.6G BGA813

A

A4R1@UCPU1

A4R1@

A8R1@UCPU1

A8R1@

B

A6 SERIES ZM212169E2451 2.1G BGA813

UCPU1

A6R1@UCPU1

A6R1@

A6 SERIES AM4455SHE24HJ 2.1G BGA813

A6 SERIES AM4455SHE24HJ 2.1G BGA813

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

A10 SERIES ZM202268E4451 2G BGA813P

A10 SERIES ZM202268E4451 2G BGA813P

A10 SERIES AM4655SIE44HJ 2G BGA813P

A10 SERIES AM4655SIE44HJ 2G BGA813P

Issued Date

Issued Date

Issued Date

C

LA9001P

LA9001P

DA60000TW00

UCPU1

A10R1@UCPU1

A10R1@

2012/01/15 2013/01/15

2012/01/15 2013/01/15

2012/01/15 2013/01/15

DA60000TW00

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

+APU_CORE

+APU_CORE_NB

+1.2VS

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

FP2 PCIE/UMI

FP2 PCIE/UMI

FP2 PCIE/UMI

VAUS5 LA9001P M/B

VAUS5 LA9001P M/B

VAUS5 LA9001P M/B

E

5 50Tuesday, May 29, 2012

5 50Tuesday, May 29, 2012

5 50Tuesday, May 29, 2012

Group A

Group B

0.3

0.3

0.3

www.qdzbwx.com

Page 6

A

B

C

D

E

1 1

2 2

3 3

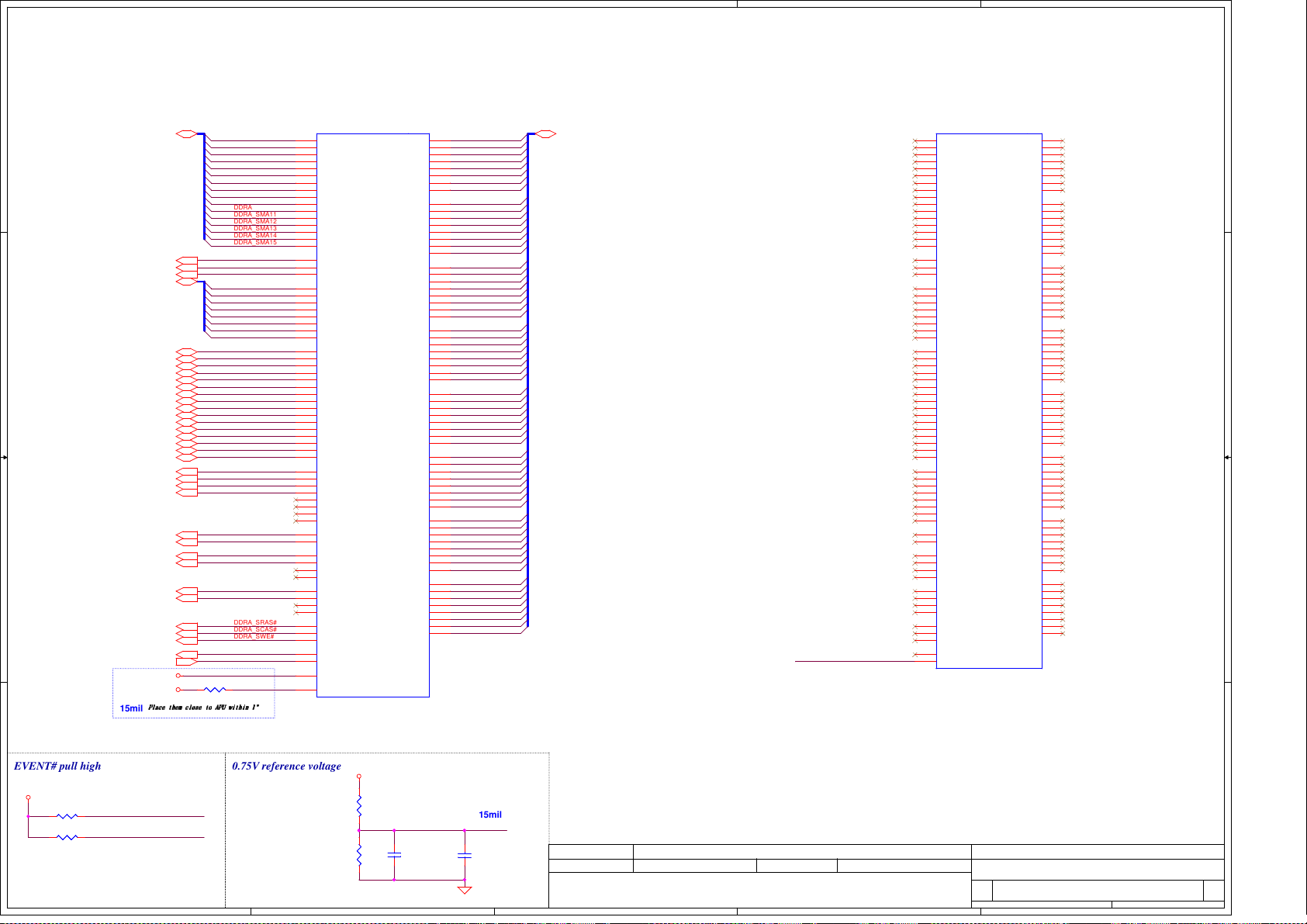

DDRA_SMA[15..0]<9>

DDRA_SBS0#<9>

DDRA_SBS1#<9>

DDRA_SBS2#<9>

DDRA_SDM[7..0]<9>

DDRA_SDQS0<9>

DDRA_SDQS0#<9>

DDRA_SDQS1<9>

DDRA_SDQS1#<9>

DDRA_SDQS2<9>

DDRA_SDQS2#<9>

DDRA_SDQS3<9>

DDRA_SDQS3#<9>

DDRA_SDQS4<9>

DDRA_SDQS4#<9>

DDRA_SDQS5<9>

DDRA_SDQS5#<9>

DDRA_SDQS6<9>

DDRA_SDQS6#<9>

DDRA_SDQS7<9>

DDRA_SDQS7#<9>

DDRA_CLK0<9>

DDRA_CLK0#<9>

DDRA_CLK1<9>

DDRA_CLK1#<9>

DDRA_CKE0<9>

DDRA_CKE1<9>

DDRA_ODT0<9>

DDRA_ODT1<9>

DDRA_SCS0#<9>

DDRA_SCS1#<9>

DDRA_SRAS#<9>

DDRA_SCAS#<9>

DDRA_SWE#<9>

MEM_MA_RST#<9>

MEM_MA_EVENT#<9>

+MEM_VREF

+1.5V_APU

Place them close to APU within 1"

Place them close to APU within 1"

Place them close to APU within 1"Place them close to APU within 1"

15mil

DDRA_SMA0

DDRA_SMA1

DDRA_SMA2

DDRA_SMA3

DDRA_SMA4

DDRA_SMA5

DDRA_SMA6

DDRA_SMA7

DDRA_SMA8

DDRA_SMA9

DDRA_SMA10

DDRA_SMA11

DDRA_SMA12

DDRA_SMA13

DDRA_SMA14

DDRA_SMA15

DDRA_SBS0#

DDRA_SBS1#

DDRA_SBS2#

DDRA_SDM0

DDRA_SDM1

DDRA_SDM2

DDRA_SDM3

DDRA_SDM4

DDRA_SDM5

DDRA_SDM6

DDRA_SDM7

DDRA_SDQS0

DDRA_SDQS0#

DDRA_SDQS1

DDRA_SDQS1#

DDRA_SDQS2

DDRA_SDQS2#

DDRA_SDQS3

DDRA_SDQS3#

DDRA_SDQS4

DDRA_SDQS4#

DDRA_SDQS5

DDRA_SDQS5#

DDRA_SDQS6

DDRA_SDQS6#

DDRA_SDQS7

DDRA_SDQS7#

DDRA_CLK0

DDRA_CLK0#

DDRA_CLK1

DDRA_CLK1#

DDRA_CKE0

DDRA_CKE1

DDRA_ODT0

DDRA_ODT1

DDRA_SCS0#

DDRA_SCS1#

DDRA_SRAS#

DDRA_SCAS#

DDRA_SWE#

MEM_MA_RST#

MEM_MA_EVENT#

1 2

R3 39.2_0402_1%R3 39.2_0402_1%

M_ZVDDIO

UCPU1B

UCPU1B

AA28

MA_ADD[0]

R29

MA_ADD[1]

T30

MA_ADD[2]

R28

MA_ADD[3]

R26

MA_ADD[4]

P26

MA_ADD[5]

P27

MA_ADD[6]

P30

MA_ADD[7]

P29

MA_ADD[8]

M28

MA_ADD[9]

AB26

MA_ADD[10]

M26

MA_ADD[11]

M29

MA_ADD[12]

AE27

MA_ADD[13]

L26

MA_ADD[14]

L27

MA_ADD[15]

AB27

MA_BANK[0]

AA29

MA_BANK[1]

M30

MA_BANK[2]

D16

MA_DM[0]

D20

MA_DM[1]

E25

MA_DM[2]

F30

MA_DM[3]

AK29

MA_DM[4]

AL25

MA_DM[5]

AM20

MA_DM[6]

AM16

MA_DM[7]

G17

MA_DQS_H[0]

H17

MA_DQS_L[0]

F22

MA_DQS_H[1]

G22

MA_DQS_L[1]

E26

MA_DQS_H[2]

F26

MA_DQS_L[2]

H30

MA_DQS_H[3]

G30

MA_DQS_L[3]

AL29

MA_DQS_H[4]

AL30

MA_DQS_L[4]

AH25

MA_DQS_H[5]

AJ25

MA_DQS_L[5]

AK20

MA_DQS_H[6]

AL20

MA_DQS_L[6]

AK15

MA_DQS_H[7]

AL15

MA_DQS_L[7]

W29

MA_CLK_H[0]

Y30

MA_CLK_L[0]

W26

MA_CLK_H[1]

W27

MA_CLK_L[1]

U29

MA_CLK_H[2]

V30

MA_CLK_L[2]

U26

MA_CLK_H[3]

U27

MA_CLK_L[3]

L29

MA_CKE[0]

K30

MA_CKE[1]

AD30

MA0_ODT[0]

AG28

MA0_ODT[1]

AE26

MA1_ODT[0]

AG29

MA1_ODT[1]

AD26

MA0_CS_L[0]

AE29

MA0_CS_L[1]

AB30

MA1_CS_L[0]

AF30

MA1_CS_L[1]

AB29

MA_RAS_L

AD29

MA_CAS_L

AD28

MA_WE_L

J28

MA_RESET_L

AA26

MA_EVENT_L

G32

M_VREF

AJ32

M_ZVDDIO

TRINITY-A8-SERIES_BGA813

TRINITY-A8-SERIES_BGA813

A8R3@

A8R3@

MA_DATA[0]

MA_DATA[1]

MA_DATA[2]

MA_DATA[3]

MA_DATA[4]

MA_DATA[5]

MA_DATA[6]

MA_DATA[7]

MA_DATA[8]

MA_DATA[9]

MA_DATA[10]

MA_DATA[11]

MA_DATA[12]

MA_DATA[13]

MA_DATA[14]

MA_DATA[15]

MA_DATA[16]

MA_DATA[17]

MA_DATA[18]

MA_DATA[19]

MA_DATA[20]

MA_DATA[21]

MA_DATA[22]

MA_DATA[23]

MA_DATA[24]

MA_DATA[25]

MA_DATA[26]

MA_DATA[27]

MA_DATA[28]

MA_DATA[29]

MA_DATA[30]

MA_DATA[31]

MA_DATA[32]

MA_DATA[33]

MA_DATA[34]

MA_DATA[35]

MA_DATA[36]

MA_DATA[37]

MA_DATA[38]

MA_DATA[39]

MA_DATA[40]

MA_DATA[41]

MA_DATA[42]

MA_DATA[43]

MA_DATA[44]

MA_DATA[45]

MA_DATA[46]

MA_DATA[47]

MA_DATA[48]

MA_DATA[49]

MA_DATA[50]

MA_DATA[51]

MA_DATA[52]

MA_DATA[53]

MA_DATA[54]

MA_DATA[55]

MA_DATA[56]

MA_DATA[57]

MA_DATA[58]

MA_DATA[59]

MA_DATA[60]

MA_DATA[61]

MA_DATA[62]

MA_DATA[63]

F15

E15

H19

F19

E14

H15

E17

D18

G20

E20

H23

G23

E19

H20

E22

D22

H25

F25

D28

D29

E23

D24

D26

D27

G28

G29

H27

J29

E28

F27

H29

H28

AH29

AJ30

AM28

AM27

AH27

AH28

AJ29

AK27

AK26

AJ26

AK23

AJ23

AM26

AL26

AM24

AL23

AK22

AH22

AK19

AH19

AM22

AL22

AJ20

AL19

AK17

AJ17

AK14

AH14

AM18

AL17

AH15

AL14

DDRA_SDQ0

DDRA_SDQ1

DDRA_SDQ2

DDRA_SDQ3

DDRA_SDQ4

DDRA_SDQ5

DDRA_SDQ6

DDRA_SDQ7

DDRA_SDQ8

DDRA_SDQ9

DDRA_SDQ10

DDRA_SDQ11

DDRA_SDQ12

DDRA_SDQ13

DDRA_SDQ14

DDRA_SDQ15

DDRA_SDQ16

DDRA_SDQ17

DDRA_SDQ18

DDRA_SDQ19

DDRA_SDQ20

DDRA_SDQ21

DDRA_SDQ22

DDRA_SDQ23

DDRA_SDQ24

DDRA_SDQ25

DDRA_SDQ26

DDRA_SDQ27

DDRA_SDQ28

DDRA_SDQ29

DDRA_SDQ30

DDRA_SDQ31

DDRA_SDQ32

DDRA_SDQ33

DDRA_SDQ34

DDRA_SDQ35

DDRA_SDQ36

DDRA_SDQ37

DDRA_SDQ38

DDRA_SDQ39

DDRA_SDQ40

DDRA_SDQ41

DDRA_SDQ42

DDRA_SDQ43

DDRA_SDQ44

DDRA_SDQ45

DDRA_SDQ46

DDRA_SDQ47

DDRA_SDQ48

DDRA_SDQ49

DDRA_SDQ50

DDRA_SDQ51

DDRA_SDQ52

DDRA_SDQ53

DDRA_SDQ54

DDRA_SDQ55

DDRA_SDQ56

DDRA_SDQ57

DDRA_SDQ58

DDRA_SDQ59

DDRA_SDQ60

DDRA_SDQ61

DDRA_SDQ62

DDRA_SDQ63

DDRA_SDQ[63..0] <9>

MEM_MB_EVENT#

UCPU1C

UCPU1C

Y33

MB_ADD[0]

R32

MB_ADD[1]

T31

MB_ADD[2]

P33

MB_ADD[3]

P32

MB_ADD[4]

P31

MB_ADD[5]

N32

MB_ADD[6]

M33

MB_ADD[7]

M32

MB_ADD[8]

L32

MB_ADD[9]

AB31

MB_ADD[10]

M31

MB_ADD[11]

K32

MB_ADD[12]

AF33

MB_ADD[13]

K33

MB_ADD[14]

J32

MB_ADD[15]

AB33

MB_BANK[0]

AA32

MB_BANK[1]

K31

MB_BANK[2]

C18

MB_DM[0]

B23

MB_DM[1]

C28

MB_DM[2]

D31

MB_DM[3]

AM31

MB_DM[4]

AN30

MB_DM[5]

AR24

MB_DM[6]

AN18

MB_DM[7]

B18

MB_DQS_H[0]

A18

MB_DQS_L[0]

B24

MB_DQS_H[1]

A24

MB_DQS_L[1]

B30

MB_DQS_H[2]

B29

MB_DQS_L[2]

D32

MB_DQS_H[3]

D33

MB_DQS_L[3]

AM32

MB_DQS_H[4]

AM33

MB_DQS_L[4]

AN28

MB_DQS_H[5]

AP29

MB_DQS_L[5]

AP23

MB_DQS_H[6]

AP24

MB_DQS_L[6]

AR18

MB_DQS_H[7]

AP18

MB_DQS_L[7]

W32

MB_CLK_H[0]

Y32

MB_CLK_L[0]

V33

MB_CLK_H[1]

V32

MB_CLK_L[1]

U32

MB_CLK_H[2]

V31

MB_CLK_L[2]

T33

MB_CLK_H[3]

T32

MB_CLK_L[3]

H32

MB_CKE[0]

H33

MB_CKE[1]

AF31

MB0_ODT[0]

AH31

MB0_ODT[1]

AE32

MB1_ODT[0]

AH33

MB1_ODT[1]

AD31

MB0_CS_L[0]

AF32

MB0_CS_L[1]

AC32

MB1_CS_L[0]

AG32

MB1_CS_L[1]

AB32

MB_RAS_L

AD32

MB_CAS_L

AD33

MB_WE_L

H31

MB_RESET_L

Y31

MB_EVENT_L

TRINITY-A8-SERIES_BGA813

TRINITY-A8-SERIES_BGA813

A8R3@

A8R3@

MB_DATA[0]

MB_DATA[1]

MB_DATA[2]

MB_DATA[3]

MB_DATA[4]

MB_DATA[5]

MB_DATA[6]

MB_DATA[7]

MB_DATA[8]

MB_DATA[9]

MB_DATA[10]

MB_DATA[11]

MB_DATA[12]

MB_DATA[13]

MB_DATA[14]

MB_DATA[15]

MB_DATA[16]

MB_DATA[17]

MB_DATA[18]

MB_DATA[19]

MB_DATA[20]

MB_DATA[21]

MB_DATA[22]

MB_DATA[23]

MB_DATA[24]

MB_DATA[25]

MB_DATA[26]

MB_DATA[27]

MB_DATA[28]

MB_DATA[29]

MB_DATA[30]

MB_DATA[31]

MB_DATA[32]

MB_DATA[33]

MB_DATA[34]

MB_DATA[35]

MB_DATA[36]

MB_DATA[37]

MB_DATA[38]

MB_DATA[39]

MB_DATA[40]

MB_DATA[41]

MB_DATA[42]

MB_DATA[43]

MB_DATA[44]

MB_DATA[45]

MB_DATA[46]

MB_DATA[47]

MB_DATA[48]

MB_DATA[49]

MB_DATA[50]

MB_DATA[51]

MB_DATA[52]

MB_DATA[53]

MB_DATA[54]

MB_DATA[55]

MB_DATA[56]

MB_DATA[57]

MB_DATA[58]

MB_DATA[59]

MB_DATA[60]

MB_DATA[61]

MB_DATA[62]

MB_DATA[63]

C16

B17

B20

C20

A16

B16

B19

A20

B22

C22

A26

B26

B21

A22

C24

B25

A28

B28

B31

A32

C26

B27

A30

C30

B33

C32

F33

F32

B32

C31

E32

F31

AK32

AL32

AP32

AN31

AK31

AK33

AN32

AP33

AP30

AR30

AP27

AN26

AR32

AP31

AR28

AP28

AP25

AN24

AR22

AP21

AP26

AR26

AN22

AP22

AR20

AP19

AP16

AR16

AN20

AP20

AP17

AN16

www.qdzbwx.com

EVENT# pull high 0.75V reference voltage

+1.5V_APU

4 4

1 2

R5 1K_0402_5%R5 1K_0402_5%

1 2

R6 1K_0402_5%R6 1K_0402_5%

MEM_MA_EVENT#

MEM_MB_EVENT#

A

R4

R4

1K_0402_1%

1K_0402_1%

R7

R7

1K_0402_1%

1K_0402_1%

+1.5V_APU

1 2

1 2

B

1

C45

C45

1000P_0402_50V7K

1000P_0402_50V7K

2

15mil

+MEM_VREF

2

C46

C46

0.1U_0402_16V7K

0.1U_0402_16V7K

1

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

C

2012/01/15 2013/01/15

2012/01/15 2013/01/15

2012/01/15 2013/01/15

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Compal Electronics, Inc.

FP2 DDRIII Memory I/F

FP2 DDRIII Memory I/F

FP2 DDRIII Memory I/F

VAUS5 LA9001P M/B

VAUS5 LA9001P M/B

VAUS5 LA9001P M/B

6 50Tuesday, May 29, 2012

6 50Tuesday, May 29, 2012

6 50Tuesday, May 29, 2012

E

0.3

0.3

0.3

Page 7

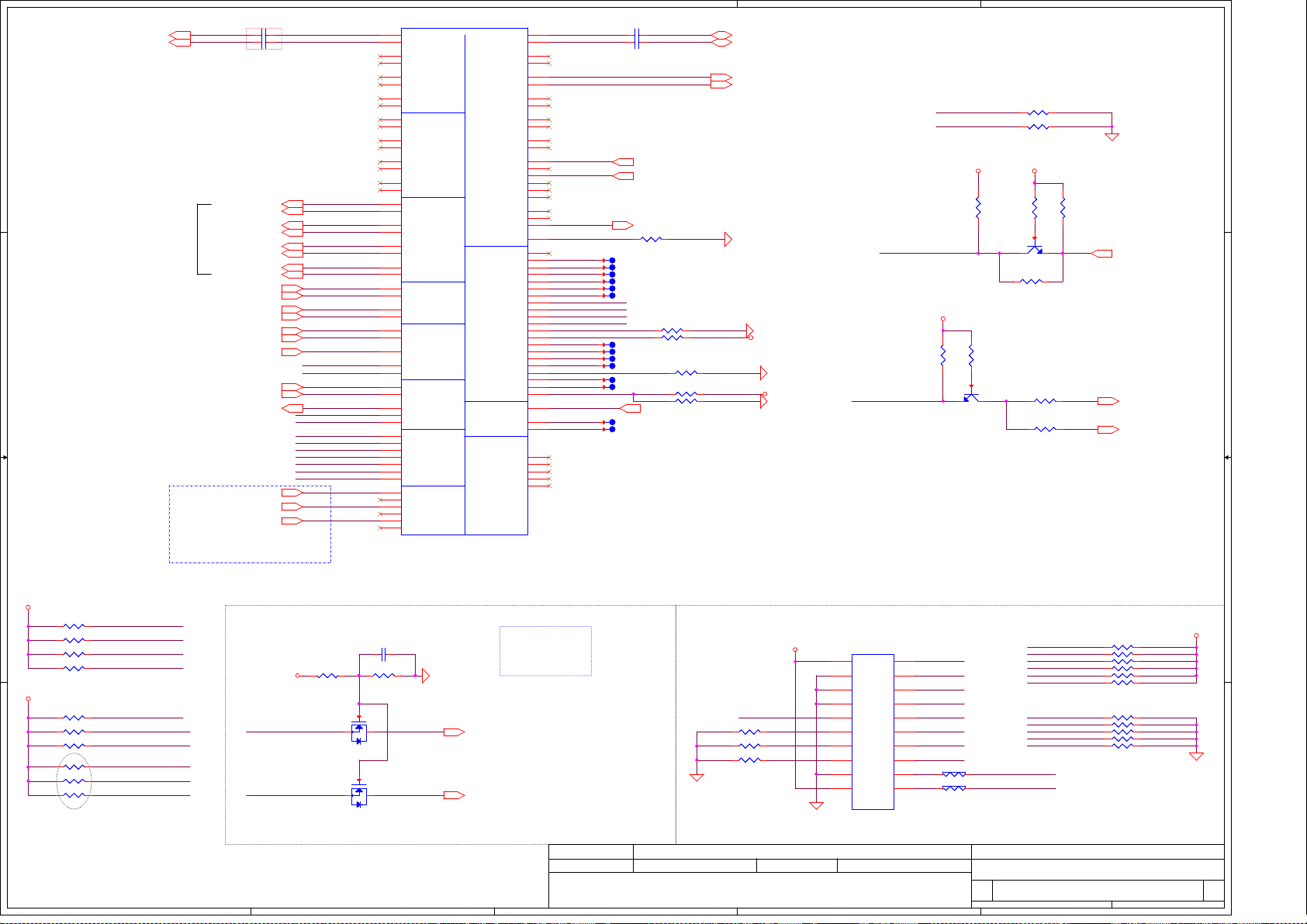

A

Place near APU

1 2

LVDS

1 1

DP0_TXP0_C<22>

DP0_TXN0_C<22>

HDMI

2 2

3 3

C47 0.1U_0402_16V7KC47 0.1U_0402_16V7K

1 2

C4888 0.1U_0402_16V7KC4888 0.1U_0402_16V7K

DP2_TXP0<24>

DP2_TXN0<24>

DP2_TXP1<24>

DP2_TXN1<24>

DP2_TXP2<24>

DP2_TXN2<24>

DP2_TXP3<24>

DP2_TXN3<24>

APU_CLK<10>

APU_CLK#<10>

APU_DISP_CLK<10>

APU_DISP_CLK#<10>

APU_SVC<43>

APU_SVD<43>

APU_SVT<43>

APU_RST#<10>

APU_PWRGD<10,43>

APU_PROCHOT#<10>

APU_VDD_SEN_L<43>

APU_VDDNB_SEN_H<43>

APU_VDD_SEN_H<43>

Route as differential

with APU_VDD_SEN_L

APU_SIC

APU_SID

APU_PWRGD

APU_THERMTRIP#

ALERT_L

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_TRST#

APU_DBRDY

APU_DBREQ#

DP0_TXP0

DP0_TXN0

B

UCPU1D

UCPU1D

H2

DP0_TXP[0]

H1

DP0_TXN[0]

H3

DP0_TXP[1]

H4

DP0_TXN[1]

F4

DP0_TXP[2]

F3

DP0_TXN[2]

F1

DP0_TXP[3]

F2

DP0_TXN[3]

E2

DP1_TXP[0]

E1

DP1_TXN[0]

D4

DP1_TXP[1]

D3

DP1_TXN[1]

D1

DP1_TXP[2]

D2

DP1_TXN[2]

C1

DP1_TXP[3]

C2

DP1_TXN[3]

B2

DP2_TXP[0]

A2

DP2_TXN[0]

B3

DP2_TXP[1]

A3

DP2_TXN[1]

B4

DP2_TXP[2]

A4

DP2_TXN[2]

B5

DP2_TXP[3]

A5

DP2_TXN[3]

AL9

CLKIN_H

AK9

CLKIN_L

AL7

DISP_CLKIN_H

AK7

DISP_CLKIN_L

E5

SVC

E6

SVD

D6

SVT

AJ11

SIC

AH11

SID

AK11

RESET_L

AH9

PWROK

AL12

PROCHOT_L

AK5

THERMTRIP_L

AR10

ALERT_L

E11

TDI

G11

TDO

H12

TCK

F11

TMS

H11

TRST_L

E8

DBRDY

E7

DBREQ_L

G6

VSS_SENSE

H6

VDDP_SENSE

H5

VDDNB_SENSE

G7

VDDIO_SENSE

G5

VDD_SENSE

H7

VDDR_SENSE

TRINITY-A8-SERIES_BGA813

TRINITY-A8-SERIES_BGA813

A8R3@

A8R3@

DISPLAY PORT 0DISPLAY PORT 1DISPLAY PORT 2CLKSER.CTRLJTAGSENSE

DISPLAY PORT 0DISPLAY PORT 1DISPLAY PORT 2CLKSER.CTRLJTAGSENSE

DP0_AUXP

DP0_AUXN

DP1_AUXP

DP1_AUXN

DP2_AUXP

DP2_AUXN

DP3_AUXP

DP3_AUXN

DP4_AUXP

DP4_AUXN

DP5_AUXP

DP5_AUXN

DP0_HPD

DISPLAY PORT MISC.RSVD TEST

DISPLAY PORT MISC.RSVD TEST

DP1_HPD

DP2_HPD

DP3_HPD

DP4_HPD

DP5_HPD

DP_BLON

DP_DIGON

DP_VARY_BL

DP_AUX_ZVSS

TEST6

TEST9

TEST10

TEST14

TEST15

TEST16

TEST17

TEST18

TEST19

TEST20

TEST24

TEST25_H

TEST25_L

TEST28_H

TEST28_L

TEST30_H

TEST30_L

TEST31

TEST32_H

TEST32_L

TEST35

DMAACTIVE_L

TEST4

TEST5

RSVD

RSVD

RSVD

RSVD

RSVD

M5

M6

L5

L6

J5

J6

P5

P6

R5

R6

U5

U6

M7

L7

J7

P7

R7

U7

C6

D7

A6

B6

AL6

Y23

V23

G9

F9

E9

G8

F12

E12

F14

G12

AJ8

AH8

G14

H14

V25

Y25

AH32

R25

T25

AL5

AP10

T23

R23

L8

P8

AH12

AJ12

AK12

DP0_AUXP

DP0_AUXN

DP_AUX_ZVSS

APU_TEST18

APU_TEST19

APU_TEST20

APU_TEST24

TEST25_H

TEST25_L

APU_TEST31

APU_TEST35

C

1 2

C49 0.1U_0402_16V7KC49 0.1U_0402_16V7K

1 2

C5088 0.1U_0402_16V7KC5088 0.1U_0402_16V7K

LVDS_HPD <22>

HDMI_DET <24>

DP_INT_PWM <22>

1 2

R15 150_0402_1%R15 150_0402_1%

T1T1

T2T2

T3T3

T4T4

T5T5

T6T6

1 2

R17 510_0402_1%R17 510_0402_1%

1 2

R18 510_0402_1%R18 510_0402_1%

T7T7

T8T8

T17T17

T18T18

T19T19

T20T20

T9T9

T10T10

1 2

R21 39.2_0402_1%R21 39.2_0402_1%

1 2

R22 300_0402_5%HDMI@R22 300_0402_5%HDMI@

1 2

R23 300_0402_5%@R23 300_0402_5%@

ALLOW_STOP <10>

DP0_AUXP_C <22>

DP0_AUXN_C <22>

HDMI_CLK < 24>

HDMI_DATA <24>

+1.2VS

+1.5V_APU

D

To LVDS

Translater

To HDMI

Asserted as an input to force the

processor into the HTC-active state

APU_PROCHOT#

THERMTRIP shutdown

temperature: 125 degree

1K_0402_5%

1K_0402_5%

APU_THERMTRIP#

DP0_AUXP

DP0_AUXN

R12

R12

1K_0402_5%

1K_0402_5%

1 2

+1.5V_APU

R19

R19

12

1 2

B

B

2

E

E

3 1

MMBT3904_NL_SOT23-3

MMBT3904_NL_SOT23-3

R10 1.8K_0402_5%R10 1.8K_0402_5%

R11 1.8K_0402_5%R11 1.8K_0402_5%

10K_0402_5%

10K_0402_5%

MMBT3904_NL_SOT23-3

MMBT3904_NL_SOT23-3

R16 0_0402_5%R16 0_0402_5%

R20

R20

10K_0402_5%

10K_0402_5%

Q2

Q2

C

C

12

12

+3VS+1.5V_APU

12

12

R14

R14

@

@

2

B

B

Q1

@

Q1

@

E

E

31

C

C

1 2

Indicates to the FCH that a thermal trip

has occurred. Its assertion will cause the FCH to

transition the system to S5 immediately

1 2

R24 0_0402_5%R24 0_0402_5%

1 2

R25 0_0402_5%@R25 0_0402_5%@

R13

R13

10K_0402_5%

10K_0402_5%

@

@

E

H_PROCHOT# <31,36,43>

H_THERMTRIP# <12>

MAINPWON <31,36,38>

+1.5V_APU

1 2

R215 1K_0402_5%R215 1K_0402_5%

1 2

R26 1K_0402_5%R26 1K_0402_5%

1 2

R28 1K_0402_5%R28 1K_0402_5%

1 2

R31 1K_0402_5%R31 1K_0402_5%

+1.5VS

1 2

R36 1K_0402_5%@R36 1K_0402_5%@

1 2

R38 300_0402_5%R38 300_0402_5%

1 2

R40 300_0402_5%R40 300_0402_5%

@

@

1 2

R45 1K_0402_5%

R45 1K_0402_5%

@

@

1 2

R48 1K_0402_5%

R48 1K_0402_5%

@

@

1 2

R50 1K_0402_5%

R50 1K_0402_5%

4 4

A

ALLOW_STOP

APU_SIC

APU_SID

ALERT_L

ALLOW_STOP

APU_RST#

APU_PWRGD

APU_SVT

APU_SVC

APU_SVD

CPU TSI interface level shift

1 2

R32

R32

+3VS

31.6K_0402_1%

31.6K_0402_1%

APU_SID

BSH111 1N_SOT23-3

BSH111 1N_SOT23-3

APU_SIC

BSH111 1N_SOT23-3

BSH111 1N_SOT23-3

1 2

C5988 0.1U_0402_16V4ZC5988 0.1U_0402_16V4Z

1 2

R33

R33

30K_0402_1%

30K_0402_1%

G

G

2

Q3

Q3

13

D

S

D

S

G

G

2

Q4

Q4

13

D

S

D

S

B

BSH111, the Vgs is:

min = 0.4V

Max = 1.3V

EC_SMB_DA2_SUS <31>

EC_SMB_CK2_SUS <31>

+1.5V_APU

APU_TRST#

1 2

To EC

R42 10K_0402_5%R42 10K_0402_5%

1 2

R46 10K_0402_5%R46 10K_0402_5%

1 2

R49 10K_0402_5%R49 10K_0402_5%

To EC

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

C

2012/01/15 2013/01/15

2012/01/15 2013/01/15

2012/01/15 2013/01/15

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

JHDT1

JHDT1

1

1

2

3

3

4

5

5

6

7

7

8

9

9

10

11

11

12

13

13

14

15

15

16

17

17

18

19

19

20

SAMTE_ASP-136446-07-B

SAMTE_ASP-136446-07-B

@

@

D

2

4

6

8

10

12

14

16

18

20

APU_TCK

APU_TMS

APU_TDI

APU_TDO

APU_PWRGD

APU_RST#

APU_DBRDY

APU_DBREQ#

R51 0_0402_5%@R51 0_0402_5%@

R52 0_0402_5%@R52 0_0402_5%@

12

12

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

HDT Debug conn

APU_DBREQ#

APU_TCK

APU_TMS

APU_TDI

APU_TDO

APU_TRST#

APU_TEST18

APU_TEST19

APU_TEST20

APU_TEST24

APU_DBRDY

APU_TEST19

APU_TEST18

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Compal Electronics, Inc.

FP2 Display/MISC/HDT

FP2 Display/MISC/HDT

FP2 Display/MISC/HDT

VAUS5 LA9001P M/B

VAUS5 LA9001P M/B

VAUS5 LA9001P M/B

1 2

R27 1K_0402_5%R27 1K_0402_5%

1 2

R29 1K_0402_5%R29 1K_0402_5%

1 2

R30 1K_0402_5%R30 1K_0402_5%

1 2

R34 1K_0402_5%R34 1K_0402_5%

1 2

R35 1K_0402_5%@R35 1K_0402_5%@

1 2

R37 1K_0402_5%R37 1K_0402_5%

1 2

R39 1K_0402_5%R39 1K_0402_5%

1 2

R41 1K_0402_5%R41 1K_0402_5%

1 2

R43 1K_0402_5%R43 1K_0402_5%

1 2

R44 1K_0402_5%R44 1K_0402_5%

1 2

R47 1K_0402_5%@R47 1K_0402_5%@

E

+1.5V_APU

7 50Tuesday, May 29, 2012

7 50Tuesday, May 29, 2012

7 50Tuesday, May 29, 2012

0.3

0.3

0.3

www.qdzbwx.com

Page 8

A

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDR

VDDR

VDDR

VDDR

VDDR

V17

V19

V20

V22

W8

AA8

AA9

AA11

AA12

AA14

AA15

AA17

AA19

AA20

AA22

AD9

AD11

AD12

AD14

AD15

AD17

AD19

AD20

AD22

AG12

AG14

AG15

AG17

AG19

AG20

AG22

B11

B12

B13

B14

B15

C8

C10

C12

C14

D8

D10

D12

D14

M9

N9

W33

AA23

AA25

AA27

AA30

AA33

AB28

AC30

AC33

AD23

AD25

AD27

AE28

AE30

AE33

AG23

AG25

AG27

AG30

AG33

AN14

AP14

AP15

AR14

AR15

+APU_CORE

+APU_CORE_NB

+VDDNB_CAP

+1.5V_APU

+1.2VS

+APU_CORE

1 1

+APU_CORE_NB

2 2

+1.5V_APU

3 3

+1.2VS

+VDDP_CAP

+APU_VDDA

4 4

UCPU1E

UCPU1E

J12

VDD

J14

VDD

J15

VDD

J17

VDD

J19

VDD

J20

VDD

J22

VDD

M11

VDD

M12

VDD

M14

VDD

M15

VDD

M17

VDD

M19

VDD

M20

VDD

M22

VDD

R8

VDD

R9

VDD

R11

VDD

R12

VDD

R14

VDD

R15

VDD

R17

VDD

R19

VDD

R20

VDD

R22

VDD

U8

VDD

V9

VDD

V11

VDD

V12

VDD

V14

VDD

V15

VDD

A7

VDDNB

A8

VDDNB

A9

VDDNB

A10

VDDNB

A11

VDDNB

A12

VDDNB

A13

VDDNB

A14

VDDNB

A15

VDDNB

B7

VDDNB

B8

VDDNB

B9

VDDNB

B10

VDDNB

J33

VDDIO

K23

VDDIO

K25

VDDIO

L28

VDDIO

L30

VDDIO

L33

VDDIO

M27

VDDIO

N23

VDDIO

N25

VDDIO

N30

VDDIO

N33

VDDIO

P28

VDDIO

R27

VDDIO

R30

VDDIO

R33

VDDIO

U28

VDDIO

U30

VDDIO

U33

VDDIO

W28

VDDIO

W30

VDDIO

AM12

VDDP

AN12

VDDP

AP12

VDDP

AP13

VDDP

AR12

VDDP

AR13

VDDP

AA6

VDDP_CAP

AA7

VDDP_CAP

AM13

VDDA

AM14

VDDA

TRINITY-A8-SERIES_BGA813

TRINITY-A8-SERIES_BGA813

A8R3@

A8R3@

VDDNB_CAP

VDDNB_CAP

B

+1.5V_APU

+1.2VS

C121 22U_0603_6.3V6MC121 22U_0603_6.3V6M

C122 22U_0603_6.3V6MC122 22U_0603_6.3V6M

1

2

Northbridge Power Pins

for Remote Decoupling

+VDDP_CAP

close to APU

C

Decoupling betw een CPU and DI MMs

across VDDIO an d VSS split

C69 0.22U_0402_10V4ZC69 0.22U_0402_10V4Z

C71 0.22U_0402_10V4ZC71 0.22U_0402_10V4Z

C64 4.7U_0603_6.3V6KC64 4.7U_0603_6.3V6K

C62 22U_0805_6.3V6MC62 22U_0805_6.3V6M

C63 22U_0805_6.3V6MC63 22U_0805_6.3V6M

1

2

C66 4.7U_0603_6.3V6KC66 4.7U_0603_6.3V6K

C65 4.7U_0603_6.3V6KC65 4.7U_0603_6.3V6K

C67 4.7U_0603_6.3V6KC67 4.7U_0603_6.3V6K

1

1

2

2

C68 0.22U_0402_10V4ZC68 0.22U_0402_10V4Z

1

1

1

1

2

2

2

2

C72 0.22U_0402_10V4ZC72 0.22U_0402_10V4Z

C70 0.22U_0402_10V4ZC70 0.22U_0402_10V4Z

1

2

C73 0.22U_0402_10V4ZC73 0.22U_0402_10V4Z

1

1

1

1

2

2

2

2

C77 0.22U_0402_10V4ZC77 0.22U_0402_10V4Z

C74 0.22U_0402_10V4ZC74 0.22U_0402_10V4Z

C75 0.22U_0402_10V4ZC75 0.22U_0402_10V4Z

C76 0.22U_0402_10V4ZC76 0.22U_0402_10V4Z

1

1

1

1

2

2

2

2

C81 180P_0402_50V8JC81 180P_0402_50V8J

C78 180P_0402_50V8JC78 180P_0402_50V8J

C79 180P_0402_50V8JC79 180P_0402_50V8J

C80 180P_0402_50V8JC80 180P_0402_50V8J

330U_B2_2.5VM_R15M

330U_B2_2.5VM_R15M

1

1

1

1

2

2

2

2

+1.5V

C82

C82

1

+

+

@

@

2

C99 4.7U_0603_6.3V6KC99 4.7U_0603_6.3V6K

1

2

VDDR VDDP

C87 4.7U_0603_6.3V6KC87 4.7U_0603_6.3V6K

C85 0.01U_0402_16V7KC85 0.01U_0402_16V7K

C86 0.01U_0402_16V7KC86 0.01U_0402_16V7K

1

1

2

2

C124 22U_0603_6.3V6MC124 22U_0603_6.3V6M

C125 180P_0402_50V8JC125 180P_0402_50V8J

C123 22U_0603_6.3V6MC123 22U_0603_6.3V6M

1

1

1

1

2

2

2

2

C90 0.22U_0402_10V4ZC90 0.22U_0402_10V4Z

C89 0.22U_0402_10V4ZC89 0.22U_0402_10V4Z

C88 4.7U_0603_6.3V6KC88 4.7U_0603_6.3V6K

1

2

1

1

1

2

2

2

FBMA-L11-201209-221LMA30T_0805

FBMA-L11-201209-221LMA30T_0805

L1

L1

+2.5VS

C91 1000P_0402_50V7 KC91 1000P_0402_50V7 K

C94 180P_0402_50V8JC94 180P_0402_50V8J

C93 180P_0402_50V8JC93 180P_0402_50V8J

C92 1000P_0402_50V7 KC92 1000P_0402_50V7 K

1

1

1

1

2

2

2

2

12

C128 3300P_0402_50V7-KC128 3300P_0402_50V7-K

C127 0.22U_0402_10V4ZC127 0.22U_0402_10V4Z

C126 4.7U_0603_6.3V6KC126 4.7U_0603_6.3V6K

1

1

1

2

2

2

+APU_VDDA

C129 1000P_0402_50V7KC12 9 10 00P_0402_50V7K

1

2

+1.2VS

C113 0.22U_0402_10V4ZC113 0.22U_0402_10V4Z

C114 0.22U_0402_10V4ZC114 0.22U_0402_10V4Z

C115 1000P_0402_50V7KC11 5 1000P_040 2_50V7K

1

1

2

2

J5

@J5

@

+1.5V +1.5V_APU

1 2

PAD-OPEN 4x4m

PAD-OPEN 4x4m

Need Short

C130 22U_0603_6.3V6MC130 22U_0603_6.3V6M

C131 22U_0603_6.3V6MC131 22U_0603_6.3V6M

1

1

2

2

D

A17

A19

A21

A23

A25

A27

A29

A31

B1

C3

C4

C33

D5

D9

D11

D13

M23

M25

D15

D17

D19

D21

D23

D25

D30

E4

E27

E29

E30

E33

F5

F6

F7

F8

F17

F20

F23

F28

F29

G1

G2

G4

G15

G19

G25

G26

G27

G33

H8

H9

H22

H26

J4

J8

J9

J11

J23

J25

J26

J27

J30

K9

K11

K12

K14

K15

K17

K19

K20

K22

L1

L2

L4

M8

N4

N11

N12

N14

N15

N17

N19

N20

N22

R1

R2

R4

T9

T11

T12

T14

T15

T17

T19

T20

T22

U4

W1

W2

W4

W5

W6

W7

Y9

C100 4.7U_0603_6.3V6KC100 4.7U_0603_6.3V6K

C101 4.7U_0603_6.3V6KC101 4.7U_0603_6.3V6K

1

2

C116 1000P_0402_50V7KC11 6 1000P_040 2_50V7K

1

1

2

2

C104 0.22U_0402_10V4ZC104 0.22U_0402_10V4Z

C102 4.7U_0603_6.3V6KC102 4.7U_0603_6.3V6K

1

2

C117 180P_0402_50V8JC117 180P_0402_50V8J

C105 0.22U_0402_10V4ZC105 0.22U_0402_10V4Z

C103 0.22U_0402_10V4ZC103 0.22U_0402_10V4Z

1

1

1

2

2

2

C118 180P_0402_50V8JC118 180P_0402_50V8J

1

1

2

2

C108 180P_0402_50V8JC108 180P_0402_50V8J

C106 0.22U_0402_10V4ZC106 0.22U_0402_10V4Z

C107 180P_0402_50V8JC107 180P_0402_50V8J

1

2

1

1

1

2

2

2

E

UCPU1F

UCPU1F

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

TRINITY-A8-SERIES_BGA813

TRINITY-A8-SERIES_BGA813

A8R3@

A8R3@

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

Y11

Y12

Y14

Y15

Y17

Y19

Y20

Y22

AA4

AA5

AB7

AB8

AC1

AC2

AC4

AC9

AC11

AC12

AC14

AC15

AC17

AC19

AC20

AC22

AC23

AC25

AE4

AF9

AF11

AF12

AF14

AF15

AF17

AF19

AF20

AF22

AF23

AF25

AG1

AG2

AG4

AG9

AG11

AG26

AH7

AH17

AH20

AH23

AH26

AH30

AJ4

AJ5

AJ6

AJ7

AJ9

AJ14

AJ15

AJ19

AJ22

AJ27

AJ28

AJ33

AK6

AK8

AK25

AK28

AK30

AL1

AL2

AL4

AL8

AL11

AL27

AL28

AL33

AM5

AM7

AM9

AM11

AM15

AM17

AM19

AM21

AM23

AM25

AM29

AM30

AN3

AN4

AN33

AP5

AP9

AR2

AR5

AR9

AR17

AR19

AR21

AR23

AR25

AR27

AR29

AR31

www.qdzbwx.com

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

C

2012/01/15 2013/01/15

2012/01/15 2013/01/15

2012/01/15 2013/01/15

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

FP2 PW R / GND

FP2 PW R / GND

FP2 PW R / GND

VAUS5 LA9001P M/B

VAUS5 LA9001P M/B

VAUS5 LA9001P M/B

8 50Tuesday, May 29, 2012

8 50Tuesday, May 29, 2012

8 50Tuesday, May 29, 2012

E

0.3

0.3

0.3

Page 9

A

B

C

D

E

+VREF_DQ

DDRA_SDQ0

DDRA_SDQ1

DDRA_SDM0

DDRA_SDQ2

1 1

DDRA_SDQS1#<6>

DDRA_SDQS1<6>

DDRA_SDQS2#<6>

DDRA_SDQS2<6>

DDRA_CKE0<6>

C145

C145

DDRA_SDQS4#<6>

DDRA_SDQS4<6>

DDRA_SDQS6#<6>

DDRA_SDQS6<6>

DDRA_SBS2#<6>

DDRA_CLK0<6>

DDRA_CLK0#<6>

DDRA_SBS0#<6>

DDRA_SWE#<6>

DDRA_SCAS#<6>

DDRA_SCS1#<6>

1

2

1

C146

C146

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

A

2 2

3 3

+3VS

4 4

2.2U_0603_6.3V6K

2.2U_0603_6.3V6K

DDRA_SDQ3

DDRA_SDQ8

DDRA_SDQ9

DDRA_SDQS1#

DDRA_SDQS1

DDRA_SDQ10

DDRA_SDQ11

DDRA_SDQ16

DDRA_SDQ17

DDRA_SDQS2#

DDRA_SDQS2

DDRA_SDQ19

DDRA_SDQ24

DDRA_SDQ25

DDRA_SDM3

DDRA_SDQ26

DDRA_SDQ27

DDRA_CKE0

DDRA_SBS2#

DDRA_SMA12

DDRA_SMA9

DDRA_SMA8

DDRA_SMA5

DDRA_SMA3

DDRA_SMA1

DDRA_CLK0

DDRA_CLK0#

DDRA_SMA10

DDRA_SBS0#

DDRA_SWE#

DDRA_SCAS#

DDRA_SMA13

DDRA_SCS1#

DDRA_SDQ32

DDRA_SDQ33

DDRA_SDQS4#

DDRA_SDQS4

DDRA_SDQ34

DDRA_SDQ35

DDRA_SDQ40

DDRA_SDQ41

DDRA_SDM5

DDRA_SDQ42

DDRA_SDQ43

DDRA_SDQ48

DDRA_SDQ49

DDRA_SDQS6#

DDRA_SDQS6

DDRA_SDQ50

DDRA_SDQ51

DDRA_SDQ56

DDRA_SDQ57

DDRA_SDM7

DDRA_SDQ58

DDRA_SDQ59

1 2

R57 10K_0402_5%R57 10K_0402_5%

+1.5V +1.5V

JDIMM1

JDIMM1

1

VREF_DQ

3

VSS

5

DQ0

7

DQ1

9

VSS

11

DM0

13

VSS

15

DQ2

17

DQ3

19

VSS

21

DQ8

23

DQ9

25

VSS

27

DQS1#

29

DQS1

31

VSS

33

DQ10

35

DQ11

37

VSS

39

DQ16

41

DQ17

43

VSS

45

DQS2#

47

DQS2

49

VSS

51

DQ18

53

DQ19

55

VSS

57

DQ24

59

DQ25

61

VSS

63

DM3

65

VSS

67

DQ26

69

DQ27

71

VSS

73

CKE0

75

VDD

77

NC

79

BA2

81

VDD

83

A12/BC#

85

A9

87

VDD

89

A8

91

A5

93

VDD

95

A3

97

A1

99

VDD

101

CK0

103

CK0#

105

VDD

107

A10/AP

109

BA0

111

VDD

113

WE#

115

CAS#

117

VDD

119

A13

121

S1#

123

VDD

125

TEST

127

VSS

129

DQ32

131

DQ33

133

VSS

135

DQS4#

137

DQS4

139

VSS

141

DQ34

143

DQ35

145

VSS

147

DQ40

149

DQ41

151

VSS

153

DM5

155

VSS

157

DQ42

159

DQ43

161

VSS

163

DQ48

165

DQ49

167

VSS

169

DQS6#

171

DQS6

173

VSS

175

DQ50

177

DQ51

179

VSS

181

DQ56

183

DQ57

185

VSS

187

DM7

189

VSS

191

DQ58

193

DQ59

195

VSS

197

SA0

199

VDDSPD

201

SA1

12

R58

R58

10K_0402_5%

10K_0402_5%

203

VTT

205

GND1

207

BOSS1

LCN_DAN06-K4406-0103

LCN_DAN06-K4406-0103

ME@

ME@

Reverse Type H:4mm

<Address: 00>

DQS0#

DQS0

DQ12

DQ13

DM1

RESET#

VSS

DQ14

DQ15

VSS

DQ20

DQ21

VSS

DM2

VSS

DQ22

DQ23

VSS

DQ28

DQ29

VSS

DQS3#

DQS3

VSS

DQ30

DQ31

VSS

CKE1

VDD

VDD

VDD

VDD

VDD

CK1#

VDD

RAS#

VDD

ODT0

VDD

ODT1

VDD

VREF_CA

VSS

DQ36

DQ37

VSS

DM4

VSS

DQ38

DQ39

VSS

DQ44

DQ45

VSS

DQS5#

DQS5

VSS

DQ46

DQ47

VSS

DQ52

DQ53

VSS

DM6

VSS

DQ54

DQ55

VSS

DQ60

DQ61

VSS

DQS7#

DQS7

VSS

DQ62

DQ63

VSS

EVENT#

SDA

GND2

BOSS2

VSS

DQ4

DQ5

VSS

VSS

DQ6

DQ7

VSS

VSS

A15

A14

A11

CK1

BA1

S0#

SCL

VTT

2

4

DDRA_SDQ4

6

DDRA_SDQ5

8

10

DDRA_SDQS0#

12

DDRA_SDQS0

14

16

DDRA_SDQ6

18

DDRA_SDQ7

20

22

DDRA_SDQ12

24

DDRA_SDQ13

26

28

DDRA_SDM1

30

MEM_MA_RST#

32

34

DDRA_SDQ14

36

DDRA_SDQ15

38

40

DDRA_SDQ20

42

DDRA_SDQ21

44

46

DDRA_SDM2

48

50

DDRA_SDQ22

52

DDRA_SDQ23DDRA_SDQ18

54

56

DDRA_SDQ28

58

DDRA_SDQ29

60

62

DDRA_SDQS3#

64

DDRA_SDQS3

66

68

DDRA_SDQ30

70

DDRA_SDQ31

72

74

DDRA_CKE1

76

78

DDRA_SMA15

80

DDRA_SMA14

82

84

DDRA_SMA11

86

A7

A6

A4

A2

A0

NC

DDRA_SMA7

88

90

DDRA_SMA6

92

DDRA_SMA4

94

96

DDRA_SMA2

98

DDRA_SMA0

100

102

DDRA_CLK1

104

DDRA_CLK1#

106

108

DDRA_SBS1#

110

DDRA_SRAS#

112

114

DDRA_SCS0#

116

DDRA_ODT0

118

120

DDRA_ODT1

122

124

126

128

130

DDRA_SDQ36

132

DDRA_SDQ37

134

136

DDRA_SDM4

138

140

DDRA_SDQ38

142

DDRA_SDQ39

144

146

DDRA_SDQ44

148

DDRA_SDQ45

150

152

DDRA_SDQS5#

154

DDRA_SDQS5

156

158

DDRA_SDQ46

160

DDRA_SDQ47

162

164

DDRA_SDQ52

166

DDRA_SDQ53

168

170

DDRA_SDM6

172

174

DDRA_SDQ54

176

DDRA_SDQ55

178

180

DDRA_SDQ60

182

DDRA_SDQ61

184

186

DDRA_SDQS7#

188

DDRA_SDQS7

190

192

DDRA_SDQ62

194

DDRA_SDQ63

196

198

MEM_MA_EVENT#

200

202

204

+0.75VS

206

208

B

DDRA_SDQS0# <6>

DDRA_SDQS0 <6>

MEM_MA_RST# <6>

DDRA_SDQS3# <6>

DDRA_SDQS3 <6>

DDRA_CKE1 <6>

DDRA_CLK1 <6>

DDRA_CLK1# <6>

DDRA_SBS1# <6 >