Page 1

A

1 1

B

C

D

E

2 2

Compal Confidential

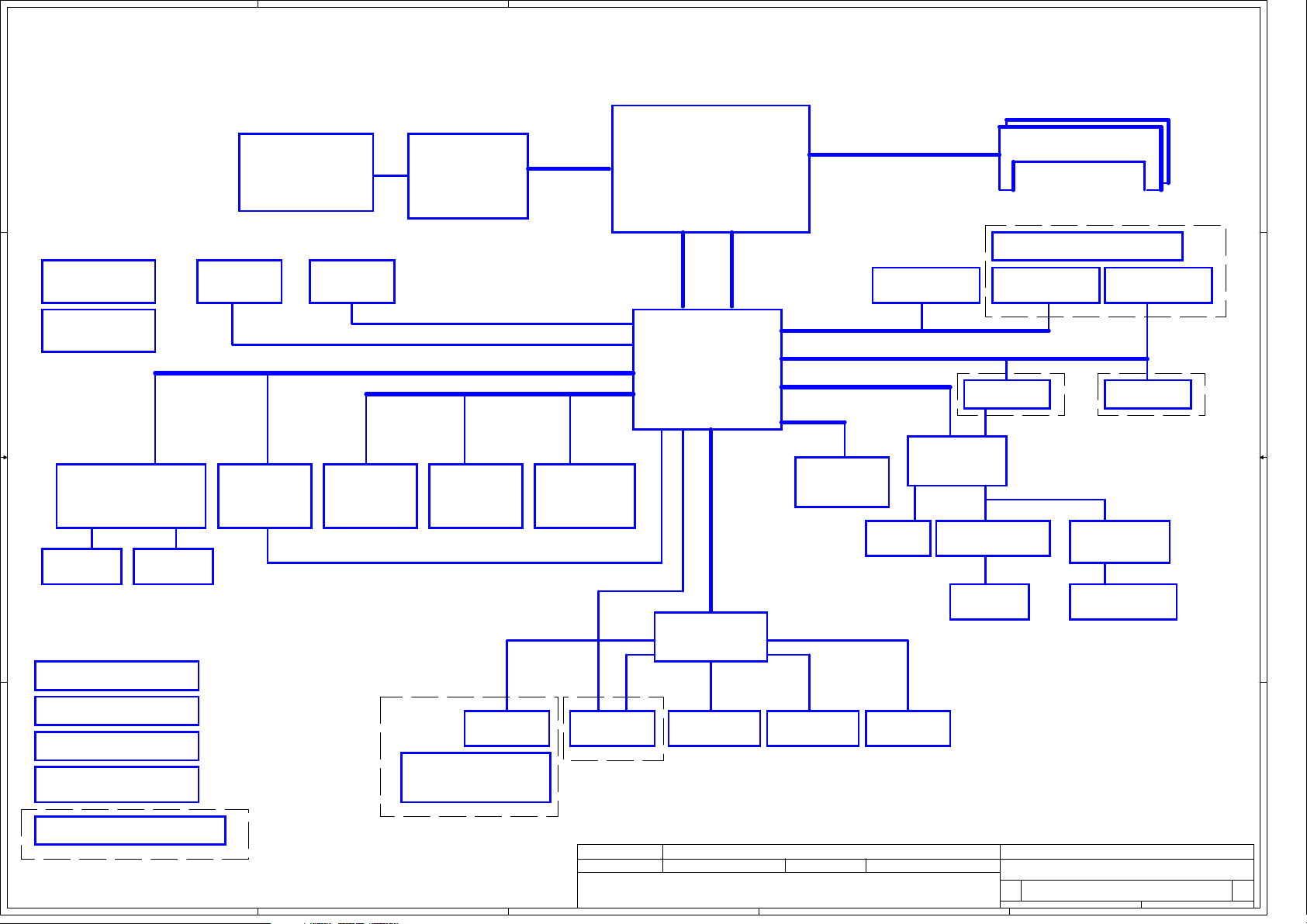

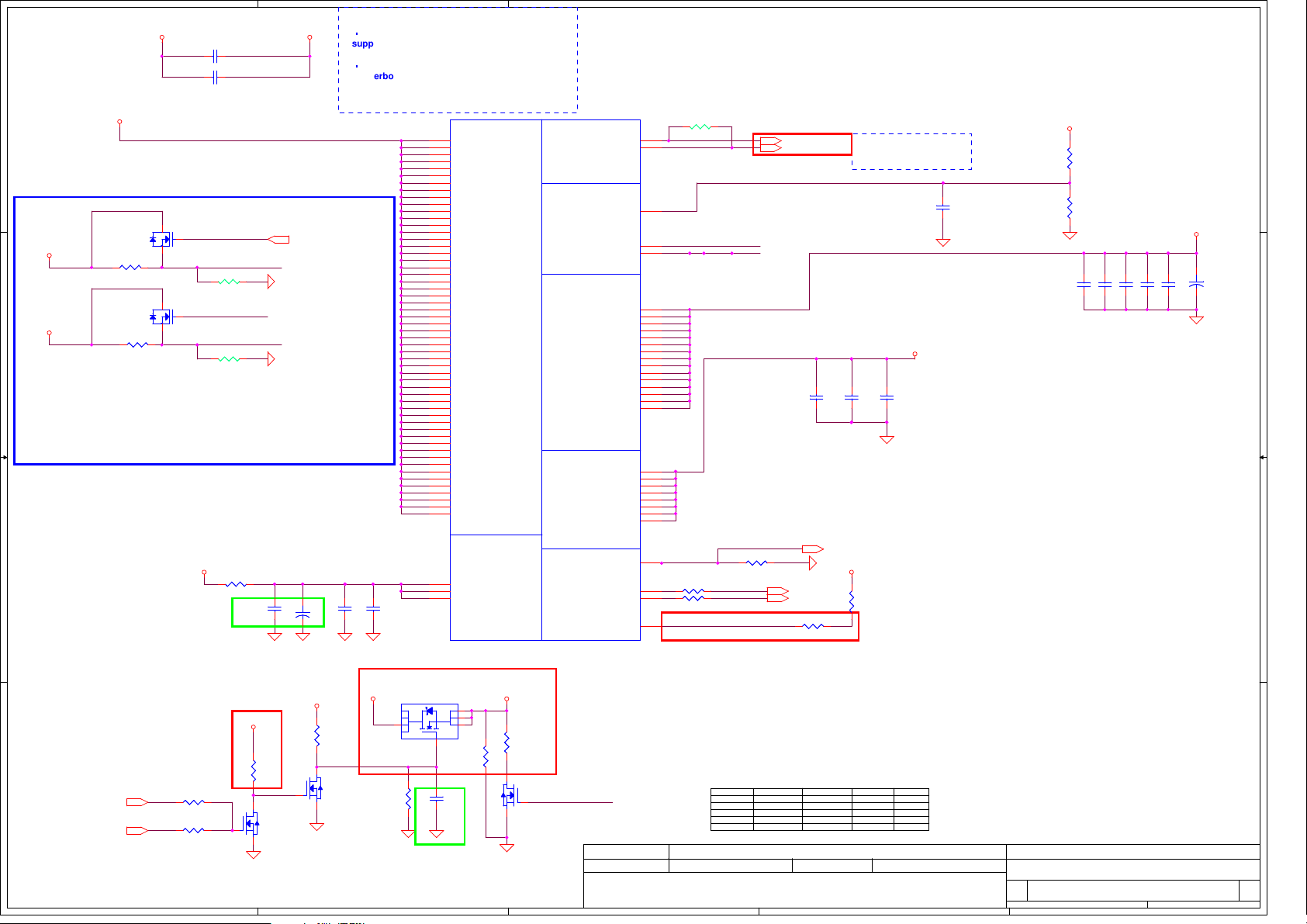

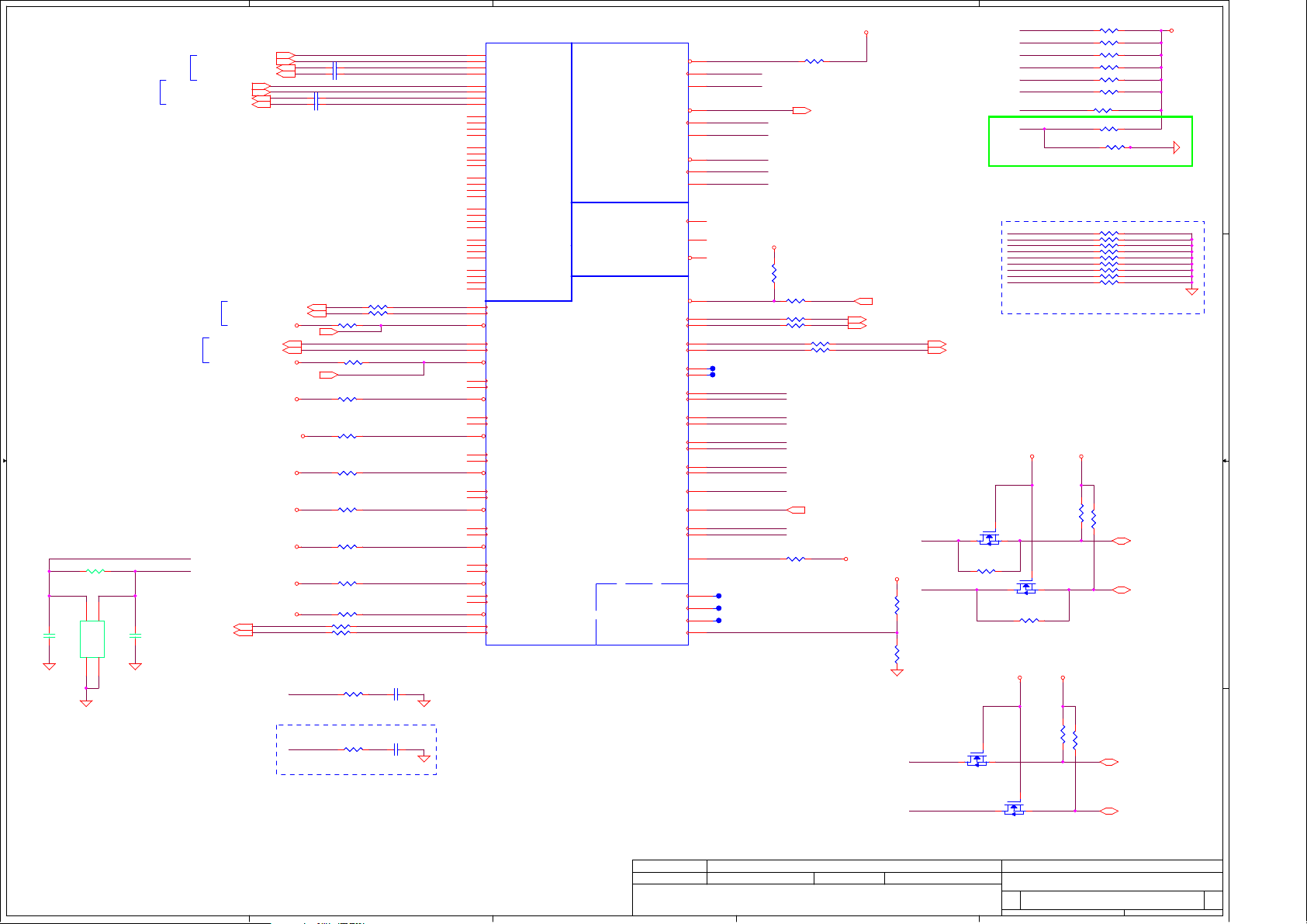

PAGANI M/B Schematics Document

Intel Ivy Bridge Processor with DDRIII + Panther Point

Date : 2011/11/22

3 3

Version 0.1

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2011/06/29 2011/06/29

2011/06/29 2011/06/29

2011/06/29 2011/06/29

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

Block Diagrams

Block Diagrams

Block Diagrams

LA-8711

LA-8711

LA-8711

E

0.1

0.1

1 57Sunday, November 27, 2011

1 57Sunday, November 27, 2011

1 57Sunday, November 27, 2011

0.1

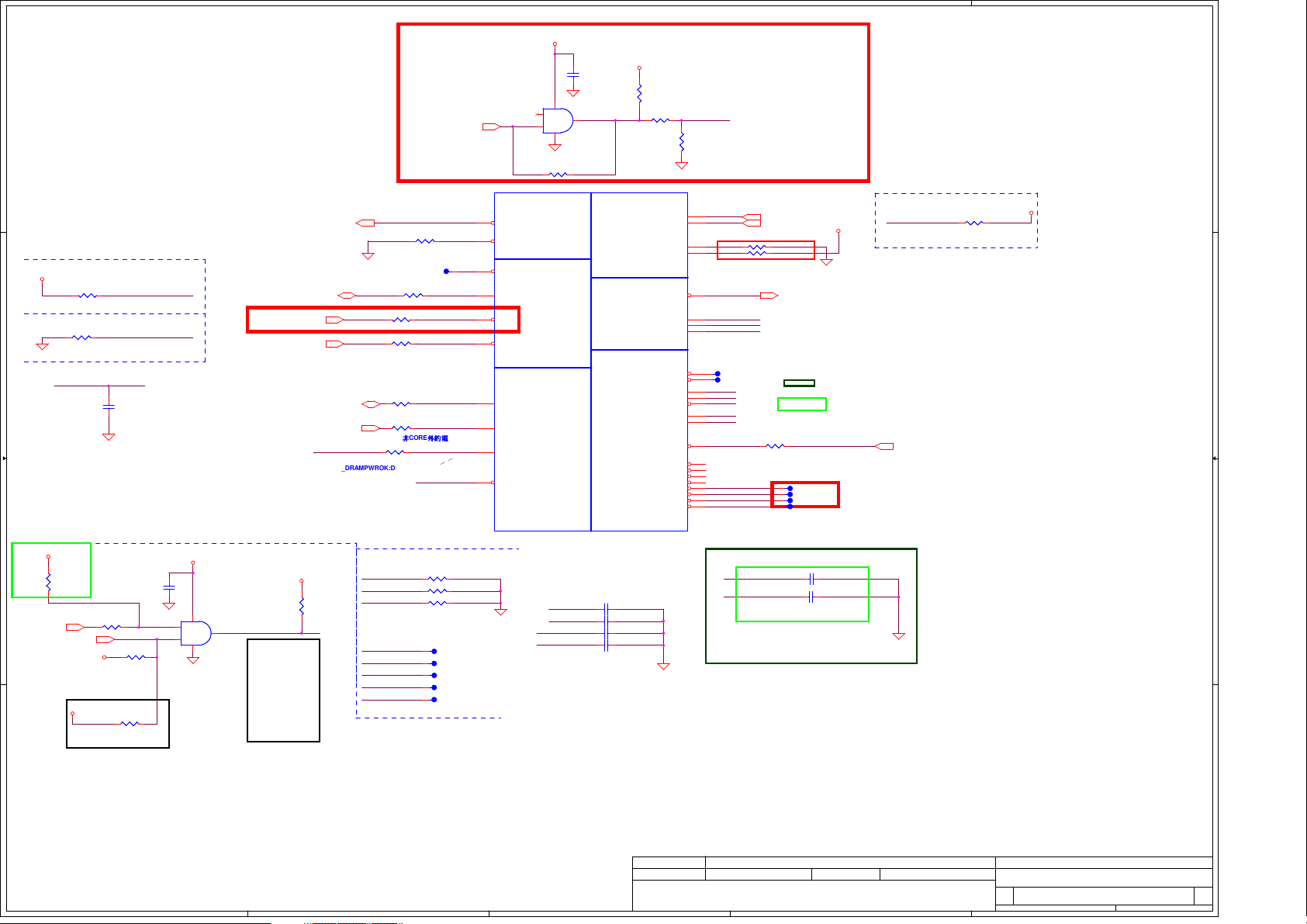

Page 2

A

Compal Confidential

Model Name : Zonda

B

C

D

E

1 1

File Name : LA8711P

2011/11/22

64Mx16

128Mx16

VRAMx8pcs

DDRIII

page27 ~ 29

128Bit

AMD

Chelsea Pro

25W

page21 ~ 26

PEG 2.0 x16

Intel

IVY Bridge

SV Processor

rPGA 988B

31mm*24mm

page4 ~ 10

DMI x4FDI x8

Accelerometer

page42

HP3DC2

HDMI Conn.

page29 page32

FAN conn.

2 2

page37

X1

X1

LVDS Conn.

PCI-Express x 2 (PCIE2.0 5GT/s)

SATAx3

X1

GEN1 1.5Gb/S GEN3 6Gb/S

LVDS(1Ch)

HDMI

X1

GEN3 6Gb/S

100MHz

100MHz

X1

100MHz

2.7GT/s

Intel

Panther Point

PCH

989pin BGA

25mm*25mm

100MHz

5GT/s

page13 ~ 20

DDR3 1333/1600MHz 1.5V

DDR3L 1333MHz 1.35V

Dual Channel

USB3.0 x2

3.0 port1,2

X2

USB 3.0 x3

USB 2.0 x4

HD Audio

SPI

page35

HD webcam

DDR3-SO-DIMM X 2

BANK 0, 1, 2, 3

page11 ~ 12

HDD LED & PWR LED

USB3.0 x1

3.0 port3

X1

X1

port8

D-MIC(daul)

ModuleModule

Daughter board

USB2.0 x1

USB charger

X1

X1

port3

Finger print

port9

HDA Codec

port2

Card Reader

/LAN controller

RTL8411

3 3

RJ45

page34 page34

SD socket

WLAN&BT

(mini card)

port 10

JMINI1

page31

X1

port2

SATA ODD

page33 page33 page33page34

port1

m-SATA

(mini card)

JMINI2

port0port1

SATA HDD

USB 2.0 x1

LPC BUS

33MHz

BIOS SPI ROM,

8MB

page33

SPK conn HP Amp

IDT 92HD91

page41

page38

Sub Woofer Amp

HPA2011

page40

Sub Woofer

conn

page35

page39

HPA00929

HP&MIC

Combo jack

page41

ENE KB932

page36

CRT

page30

SM bus

PS2 SPI

LED

RTC CKT.

DC/DC interface CKT.

4 4

ODD connector board

A

page37

page14

page43

Daughter board

Lid switch FAN/LED

Power On/Off CKT.

& PWR BTN LED

B

Daughter board

Touch Pad

TP BTN on daughter board

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

Int.KBD

2011/06/29 2011/06/29

2011/06/29 2011/06/29

2011/06/29 2011/06/29

EC ROM,

256kB

page36 page37page37page37

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Block Diagrams

Block Diagrams

Block Diagrams

LA-8711

LA-8711

LA-8711

E

2 57Sunday, November 27, 2011

2 57Sunday, November 27, 2011

2 57Sunday, November 27, 2011

0.1

0.1

0.1

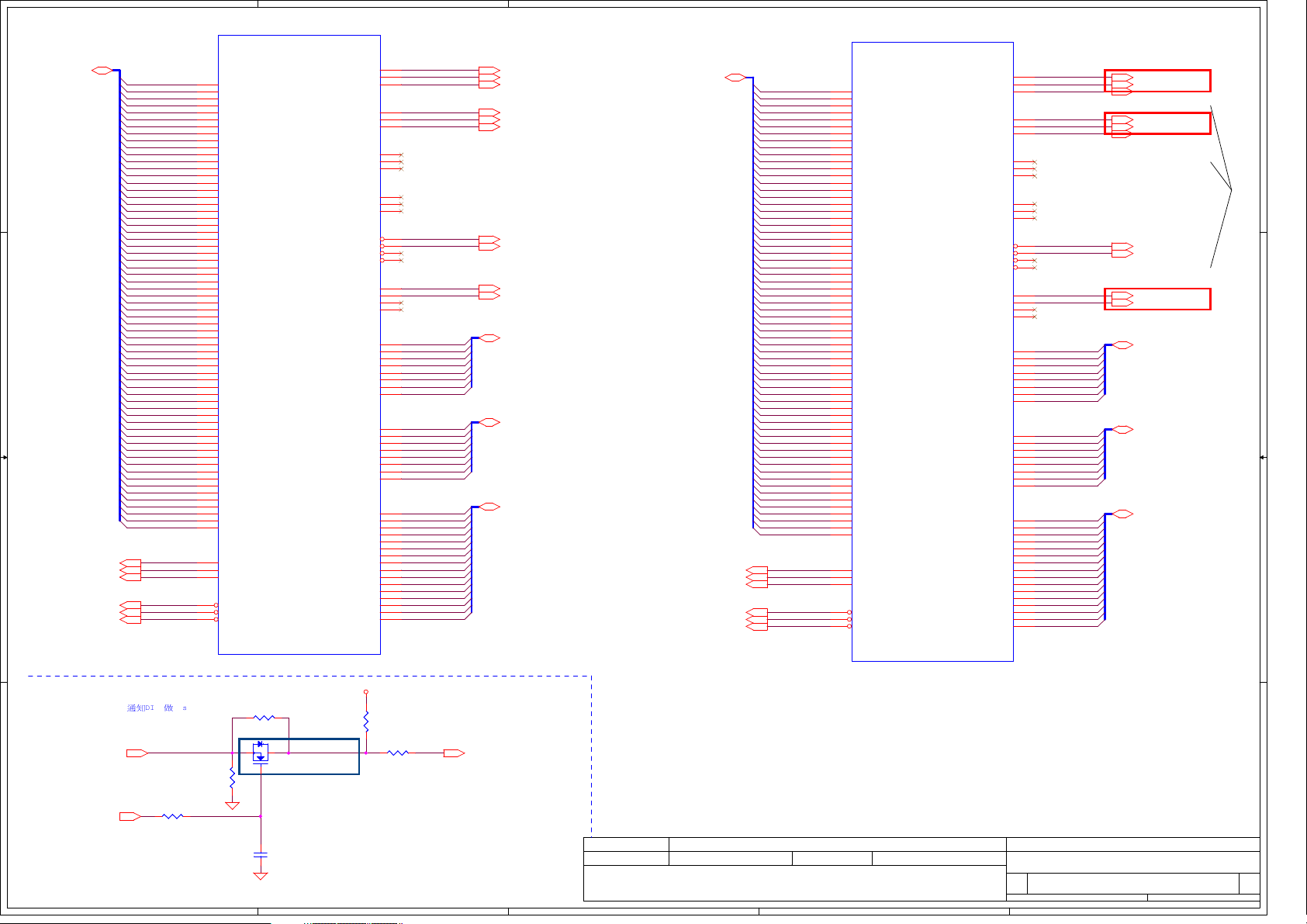

Page 3

A

B

C

D

E

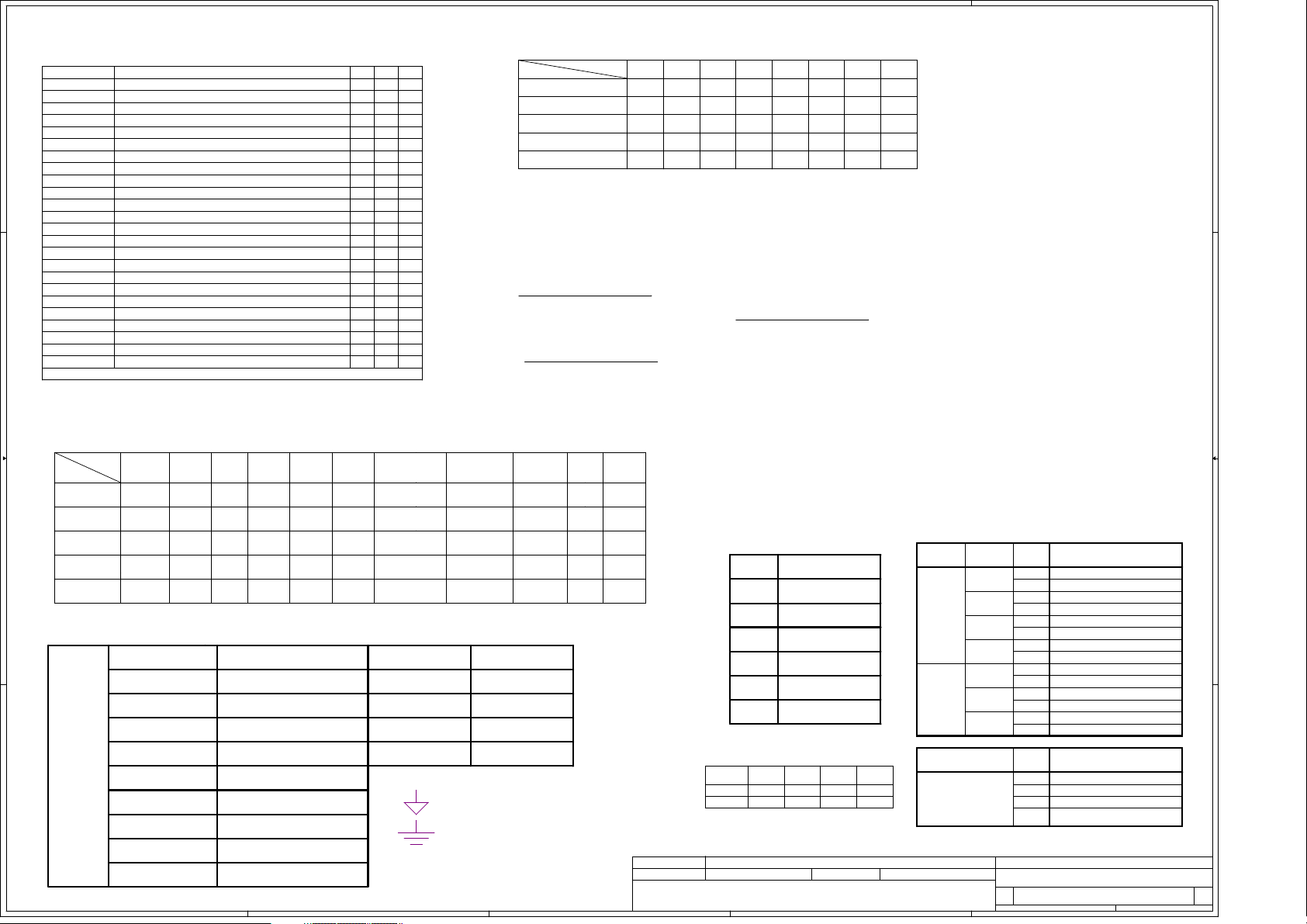

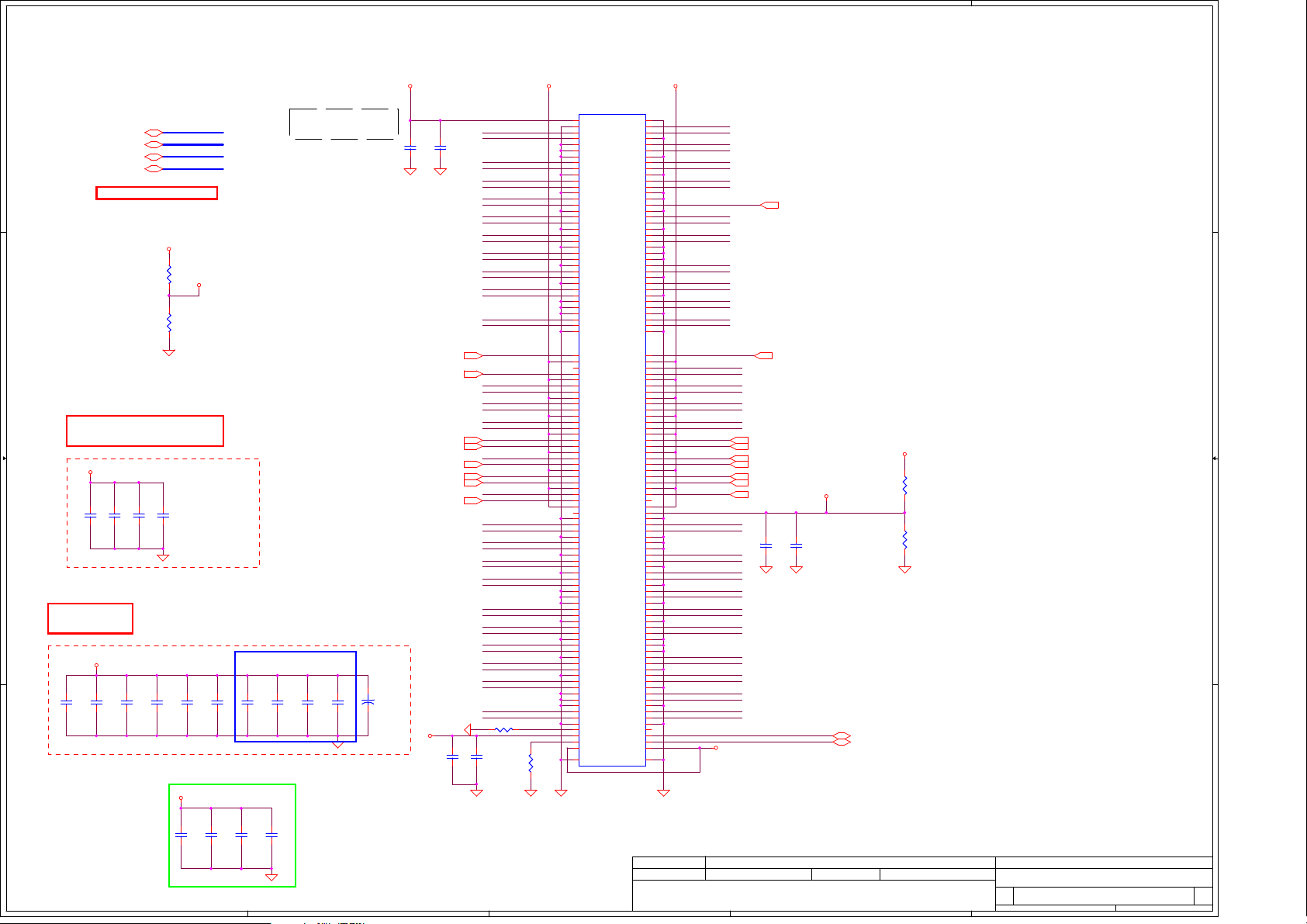

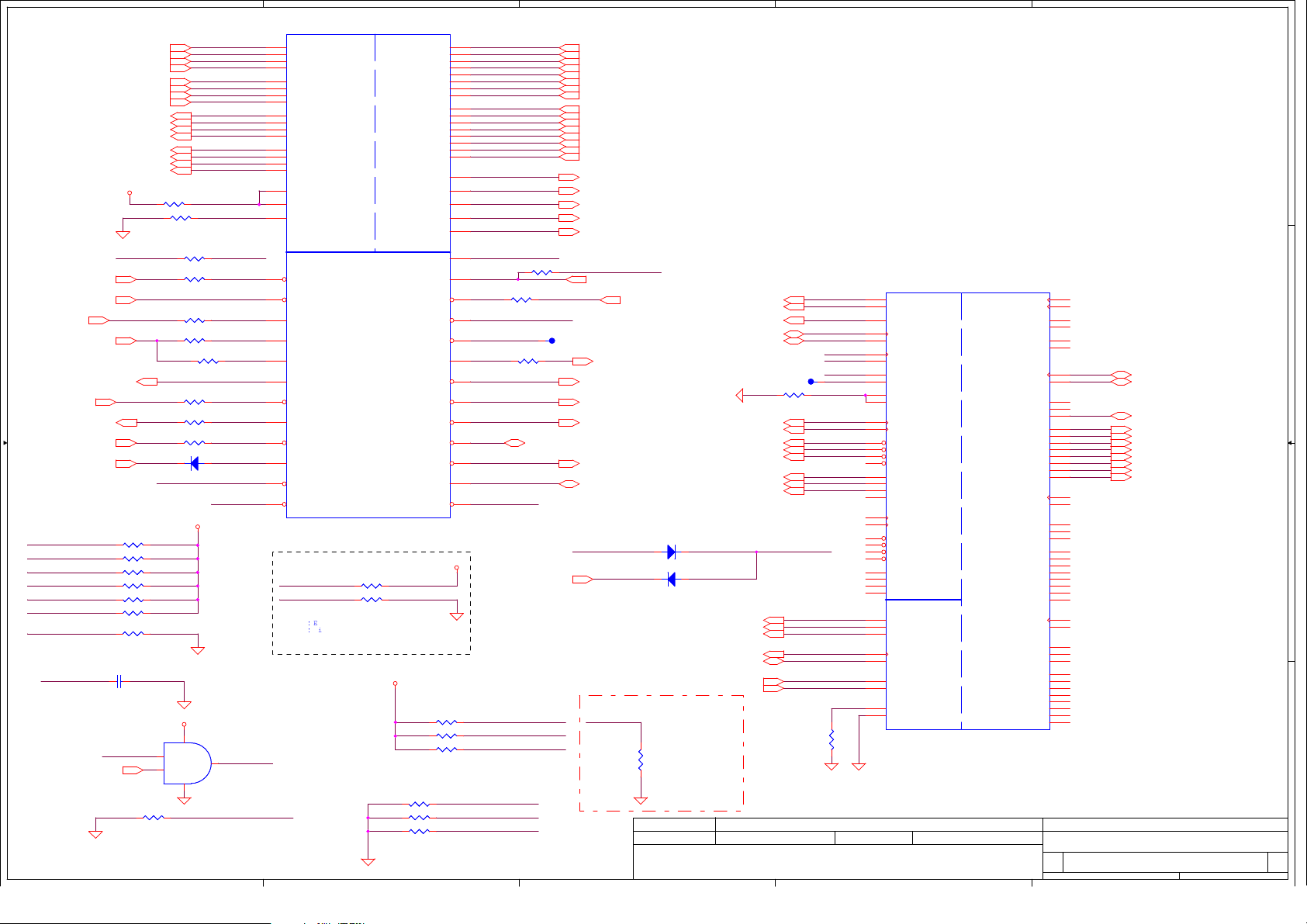

Voltage Rails

V

SIGNAL

SLP_S1# SLP_S3# SLP_S4# SLP_S5# +VALW +V +VS Clock

ON

ON

ON

ON

ON

ONONON ON

ON

OFF

OFF

Address

1010 0110b

HIGH HIGH HIGH HIGH

LOW

LOW

LOW LOW LOW LOW

Address

0001 011X b

0101001b

1010 0000b

HP AMP

LOW

HIGHHIGHHIGH

HIGH

HIGH

LOWLOWLOW

HIGH

EC SM Bus2 address

Device

PCH (Reserve)

V

SATA

SATA0

SATA1

SATA2

SATA3

SATA4

SATA5

UMA

DIS

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

C

2011/11/02 2011/11/02

2011/11/02 2011/11/02

2011/11/02 2011/11/02

DESTINATION

HDD,JHDD1

m-SATA,JMINI2

ODD, JODD1

None

None

None

CONN@@Option

X

X

XX

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

PX@

X

V

ON

LOW

OFF

OFF

OFF

OFF

OFF

OFF

USB Port Table

USB 2.0 USB 1.1 Port

0

1

2

3

4

5

6

7

8

9

10

11

12

13

EHCI1

EHCI2

UHCI0

UHCI1

UHCI2

UHCI3

UHCI4

UHCI5

UHCI6

USB 3.0 Port

0

1

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

1 External

USB Port

USB3.0

USB3.0

USB3.0

USB2.0 FRP

X

m-SATA

X

X

Camera

USB2.0 and sleep charger

minPCIE-WLAN/BT

X

X

X

3 External

USB Port

USB3.0

USB3.0

USB3.0(SB)

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Notes List

Notes List

Notes List

LA-8711

LA-8711

LA-8711

E

3 57Sunday, November 27, 2011

3 57Sunday, November 27, 2011

3 57Sunday, November 27, 2011

0.1

0.1

0.1

S1

Power Plane Description

VIN

BATT+

B+

+CPU_CORE

1 1

+VGFX_CORE Core voltage for UM A graphic

+0.75VS

+1.05VS_VCCP

+VCCP

+1.5V

+1.5VS

+1.8VS

+3VALW

+3VALW_EC

+LAN_VDD_3V3

+3V_PCH

+3VS

+5VALW

+5V_PCH

+5VS

2 2

+VSB

+RTCVCC

Note : ON* means that t his power plane is ON only with AC power av ailable, otherwise it is OFF.

SMBUS Control Table

EC_SMB_CK1

EC_SMB_DA1

EC_SMB_CK2

EC_SMB_DA2

PCH_SMBCLK

PCH_SMBDATA

PCH_SML0CLK

3 3

PCH_SML0DATA

PCH_SML1CLK

PCH_SML1DATA

Adapter power supply (19V)

Battery power supply (12.6V)

AC or battery power rail f or power circuit.

Core voltage for CPU

+0.75VP to +0.75VS switched power rail for DDR terminator

+V1.05SP to +1.05VS_VCCP switched power r ail for CPU

+VCCP (1.05V ) power for PCH

+1.5VP to +1.5V power rail for DDRIII (1.35V OR 1.5V)

+1.5VS switched power rail

(+5VALW ) to 1.8V switched power rail to PCH

+3VALW always on power rail

+3VALW always to KBC

+3VALW to +LAN_VDD_3V3 power rail for LAN

+3VALW to +3V_PCH power rail for PCH (Short Jumper)

+3VALW to +3VS power rail

+5VALWP to +5VALW power rail

+5VALW to +5V_PCH power rail for PCH (Short resister)

+5VALW to +5VS switched power rail OFFONOFF

B+ to +VSB always on power rail f or sequence control

RTC power

BATT

SOURCE

KB930

KB930

PCH

PCH

PCH

WLAN

Charger

MIINI1

V

TP

V

V

DESTINATIONDIFFERENTIAL

S3 S5

N/A N/A N/A

N/A N/A N/A

ON

ON

ON

ON

ON

ON ON

ON

ON

ON

ON ON ON*

ON ON

ON ON

ON

ON

ON ON

ON

ON

SODIMMBATT

N/AN/AN/A

OFF

OFF

OFF OFF

OFF OFF

OFF OFF

OFF OFF

OFF

OFF OFF

OFF

OFF

ON ON*

ON*

ON*

OFF

OFF

ON ON*

ON*

ON ON*

ONON

EC_SMB_CK2

EC_SMB_DA2

PCH_SML1CLK

PCH_SML1DATA

V

V

V

FLEX CLOCKS DESTINATION

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

EC SM Bus1 address

Device

Smart Battery

G-sensor

PCH SM Bus address

Device Address

DDR DIMM0

DDR DIMM1

Mini Card1

Mini Card2

TP module

G-Sensor GPU

V

CLKOUT_PCIE0 CR+ Giga LAN CLKOUTFLEX0 None

CLKOUT_PCIE1

CLKOUT_PCIE2

CLK

CLKOUT_PCIE3

CLKOUT_PCIE4

4 4

CLKOUT_PCIE5

WLAN

None

None

None

None

NoneCLKOUT_PCIE6

CLKOUTFLEX1

CLKOUTFLEX2

CLKOUTFLEX3

Symbol Note :

: means Digital Ground

: means Analog Ground

None

None

None

CLKOUT_PCIE7 None

CLKOUT_PEG_B

A

None

B

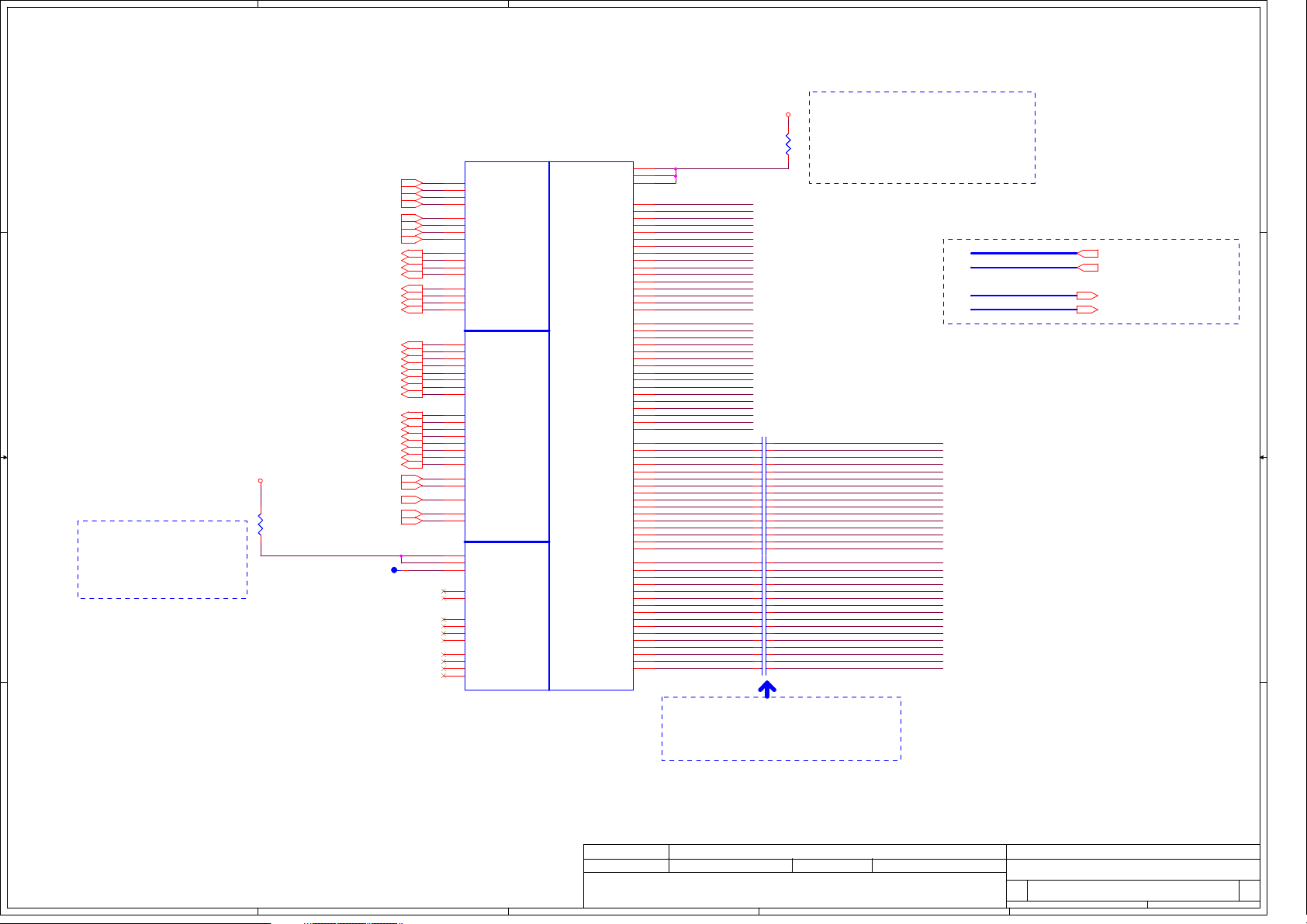

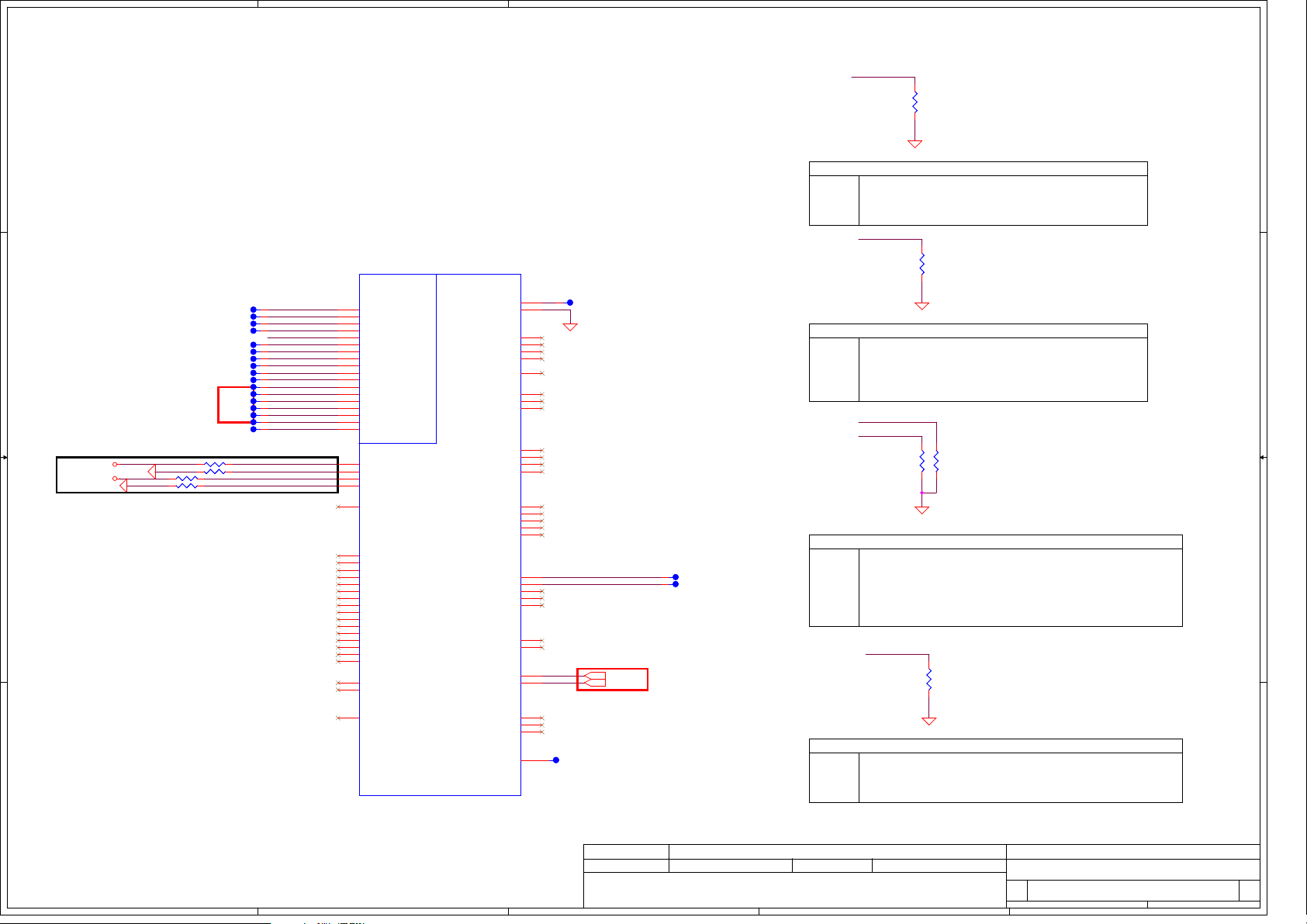

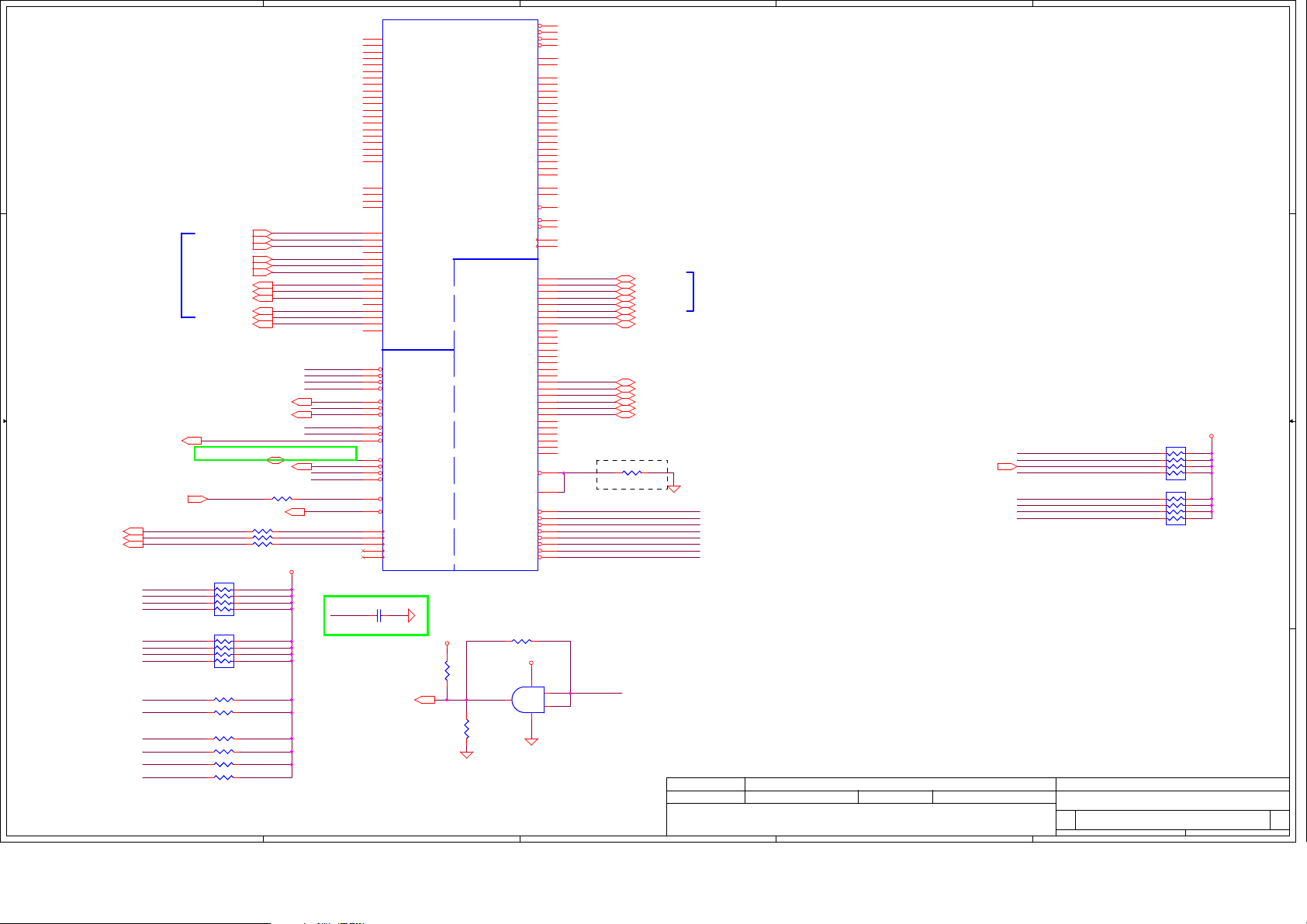

Page 4

5

D D

C C

+1.05VS

12

RC2

RC2

24.9_0402_1%

24.9_0402_1%

eDP_COMPIO and ICOMPO signals

should be shorted near balls

B B

and routed with typical

impedance <25 mohms

NOTE:eDP_COMPIO and eDP_ICOMPO

should not be l eft floating ev en if Internal

Graphic is disa bled since they are shared

with other inte rfaces

4

JCPUA

JCPUA

EDP_COMP

B27

DMI_RX#[0]

B25

DMI_RX#[1]

A25

DMI_RX#[2]

B24

DMI_RX#[3]

B28

DMI_RX[0]

B26

DMI_RX[1]

A24

DMI_RX[2]

B23

DMI_RX[3]

G21

DMI_TX#[0]

E22

DMI_TX#[1]

F21

DMI_TX#[2]

D21

DMI_TX#[3]

G22

DMI_TX[0]

D22

DMI_TX[1]

F20

DMI_TX[2]

C21

DMI_TX[3]

A21

FDI0_TX#[0]

H19

FDI0_TX#[1]

E19

FDI0_TX#[2]

F18

FDI0_TX#[3]

B21

FDI1_TX#[0]

C20

FDI1_TX#[1]

D18

FDI1_TX#[2]

E17

FDI1_TX#[3]

A22

FDI0_TX[0]

G19

FDI0_TX[1]

E20

FDI0_TX[2]

G18

FDI0_TX[3]

B20

FDI1_TX[0]

C19

FDI1_TX[1]

D19

FDI1_TX[2]

F17

FDI1_TX[3]

J18

FDI0_FSYNC

J17

FDI1_FSYNC

H20

FDI_INT

J19

FDI0_LSYNC

H17

FDI1_LSYNC

A18

eDP_COMPIO

A17

eDP_ICOMPO

B16

eDP_HPD#

C15

eDP_AUX

D15

eDP_AUX#

C17

eDP_TX[0]

F16

eDP_TX[1]

C16

eDP_TX[2]

G15

eDP_TX[3]

C18

eDP_TX#[0]

E16

eDP_TX#[1]

D16

eDP_TX#[2]

F15

eDP_TX#[3]

TYCO_2013620-2_IVY BRIDGE

TYCO_2013620-2_IVY BRIDGE

@

@

PEG_RCOMPO

DMI

DMI

Intel(R) FDI

Intel(R) FDI

PCI EXPRESS* - GRAPHICS

PCI EXPRESS* - GRAPHICS

eDP

eDP

DMI_CRX_PTX_N015

DMI_CRX_PTX_N115

DMI_CRX_PTX_N215

DMI_CRX_PTX_N315

DMI_CRX_PTX_P015

DMI_CRX_PTX_P115

DMI_CRX_PTX_P215

DMI_CRX_PTX_P315

DMI_CTX_PRX_N015

DMI_CTX_PRX_N115

DMI_CTX_PRX_N215

DMI_CTX_PRX_N315

DMI_CTX_PRX_P015

DMI_CTX_PRX_P115

DMI_CTX_PRX_P215

DMI_CTX_PRX_P315

FDI_CTX_PRX_N015

FDI_CTX_PRX_N115

FDI_CTX_PRX_N215

FDI_CTX_PRX_N315

FDI_CTX_PRX_N415

FDI_CTX_PRX_N515

FDI_CTX_PRX_N615

FDI_CTX_PRX_N715

FDI_CTX_PRX_P015

FDI_CTX_PRX_P115

FDI_CTX_PRX_P215

FDI_CTX_PRX_P315

FDI_CTX_PRX_P415

FDI_CTX_PRX_P515

FDI_CTX_PRX_P615

FDI_CTX_PRX_P715

FDI_FSYNC015

FDI_FSYNC115

FDI_INT15

FDI_LSYNC015

FDI_LSYNC115

T20 PADT20 PAD

PEG_ICOMPI

PEG_ICOMPO

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PEG_TX#[15]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

3

PEG_ICOMPI and RCOMPO signals should be

+1.05VS

shorted and routed

with - max length = 500 mils - typical

12

RC1

RC1

24.9_0402_1%

24.9_0402_1%

PEG_COMP

J22

J21

H22

PEG_GTX_C_HRX_N15

K33

PEG_GTX_C_HRX_N14

M35

PEG_GTX_C_HRX_N13

L34

PEG_GTX_C_HRX_N12

J35

PEG_GTX_C_HRX_N11

J32

PEG_GTX_C_HRX_N10

H34

PEG_GTX_C_HRX_N9

H31

PEG_GTX_C_HRX_N8

G33

PEG_GTX_C_HRX_N7

G30

PEG_GTX_C_HRX_N6

F35

PEG_GTX_C_HRX_N5

E34

PEG_GTX_C_HRX_N4

E32

PEG_GTX_C_HRX_N3

D33

PEG_GTX_C_HRX_N2

D31

PEG_GTX_C_HRX_N1

B33

PEG_GTX_C_HRX_N0

C32

PEG_GTX_C_HRX_P15

J33

PEG_GTX_C_HRX_P14

L35

PEG_GTX_C_HRX_P13

K34

PEG_GTX_C_HRX_P12

H35

PEG_GTX_C_HRX_P11

H32

PEG_GTX_C_HRX_P10

G34

PEG_GTX_C_HRX_P9

G31

PEG_GTX_C_HRX_P8

F33

PEG_GTX_C_HRX_P7

F30

PEG_GTX_C_HRX_P6

E35

PEG_GTX_C_HRX_P5

E33

PEG_GTX_C_HRX_P4

F32

PEG_GTX_C_HRX_P3

D34

PEG_GTX_C_HRX_P2

E31

PEG_GTX_C_HRX_P1

C33

PEG_GTX_C_HRX_P0

B32

PEG_HTX_GRX_N15 PEG_HTX_C_GRX_N15

M29

PEG_HTX_GRX_N14 PEG_HTX_C_GRX_N14

M32

PEG_HTX_GRX_N13 PEG_HTX_C_GRX_N13

M31

PEG_HTX_GRX_N12 PEG_HTX_C_GRX_N12

L32

PEG_HTX_GRX_N11 PEG_HTX_C_GRX_N11

L29

PEG_HTX_GRX_N10 PEG_HTX_C_GRX_N10

K31

PEG_HTX_GRX_N9 PEG_HTX_C_GRX_N9

K28

PEG_HTX_GRX_N8 PEG_HTX_C_GRX_N8

J30

PEG_HTX_GRX_N7 PEG_HTX_C_GRX_N7

J28

PEG_HTX_GRX_N6 PEG_HTX_C_GRX_N6

H29

PEG_HTX_GRX_N5 PEG_HTX_C_GRX_N5

G27

PEG_HTX_GRX_N4 PEG_HTX_C_GRX_N4

E29

PEG_HTX_GRX_N3 PEG_HTX_C_GRX_N3

F27

PEG_HTX_GRX_N2 PEG_HTX_C_GRX_N2

D28

PEG_HTX_GRX_N1 PEG_HTX_C_GRX_N1

F26

PEG_HTX_GRX_N0 PEG_HTX_C_GRX_N0

E25

PEG_HTX_GRX_P15 PEG_HTX_C_GRX_P15

M28

PEG_HTX_GRX_P14 PEG_HTX_C_GRX_P14

M33

PEG_HTX_GRX_P13 PEG_HTX_C_GRX_P13

M30

PEG_HTX_GRX_P12 PEG_HTX_C_GRX_P12

L31

PEG_HTX_GRX_P11 PEG_HTX_C_GRX_P11

L28

PEG_HTX_GRX_P10 PEG_HTX_C_GRX_P10

K30

PEG_HTX_GRX_P9 PEG_HTX_C_GRX_P9

K27

PEG_HTX_GRX_P8 PEG_HTX_C_GRX_P8

J29

PEG_HTX_GRX_P7 PEG_HTX_C_GRX_P7

J27

PEG_HTX_GRX_P6 PEG_HTX_C_GRX_P6

H28

PEG_HTX_GRX_P5 PEG_HTX_C_GRX_P5

G28

PEG_HTX_GRX_P4 PEG_HTX_C_GRX_P4

E28

PEG_HTX_GRX_P3 PEG_HTX_C_GRX_P3

F28

PEG_HTX_GRX_P2 PEG_HTX_C_GRX_P2

D27

PEG_HTX_GRX_P1 PEG_HTX_C_GRX_P1

E26

PEG_HTX_GRX_P0 PEG_HTX_C_GRX_P0

D25

CU33 0.1U_0402_10V6KPX@CU33 0.1U_0402_10V6KPX@

CU34 0.1U_0402_10V6KPX@CU34 0.1U_0402_10V6KPX@

CU35 0.1U_0402_10V6KPX@CU35 0.1U_0402_10V6KPX@

CU36 0.1U_0402_10V6KPX@CU36 0.1U_0402_10V6KPX@

CU37 0.1U_0402_10V6KPX@CU37 0.1U_0402_10V6KPX@

CU38 0.1U_0402_10V6KPX@CU38 0.1U_0402_10V6KPX@

CU39 0.1U_0402_10V6KPX@CU39 0.1U_0402_10V6KPX@

CU40 0.1U_0402_10V6KPX@CU40 0.1U_0402_10V6KPX@

CU41 0.1U_0402_10V6KPX@CU41 0.1U_0402_10V6KPX@

CU42 0.1U_0402_10V6KPX@CU42 0.1U_0402_10V6KPX@

CU43 0.1U_0402_10V6KPX@CU43 0.1U_0402_10V6KPX@

CU44 0.1U_0402_10V6KPX@CU44 0.1U_0402_10V6KPX@

CU45 0.1U_0402_10V6KPX@CU45 0.1U_0402_10V6KPX@

CU46 0.1U_0402_10V6KPX@CU46 0.1U_0402_10V6KPX@

CU47 0.1U_0402_10V6KPX@CU47 0.1U_0402_10V6KPX@

CU48 0.1U_0402_10V6KPX@CU48 0.1U_0402_10V6KPX@

CU49 0.1U_0402_10V6KPX@CU49 0.1U_0402_10V6KPX@

CU50 0.1U_0402_10V6KPX@CU50 0.1U_0402_10V6KPX@

CU51 0.1U_0402_10V6KPX@CU51 0.1U_0402_10V6KPX@

CU52 0.1U_0402_10V6KPX@CU52 0.1U_0402_10V6KPX@

CU53 0.1U_0402_10V6KPX@CU53 0.1U_0402_10V6KPX@

CU54 0.1U_0402_10V6KPX@CU54 0.1U_0402_10V6KPX@

CU55 0.1U_0402_10V6KPX@CU55 0.1U_0402_10V6KPX@

CU56 0.1U_0402_10V6KPX@CU56 0.1U_0402_10V6KPX@

CU57 0.1U_0402_10V6KPX@CU57 0.1U_0402_10V6KPX@

CU58 0.1U_0402_10V6KPX@CU58 0.1U_0402_10V6KPX@

CU59 0.1U_0402_10V6KPX@CU59 0.1U_0402_10V6KPX@

CU60 0.1U_0402_10V6KPX@CU60 0.1U_0402_10V6KPX@

CU61 0.1U_0402_10V6KPX@CU61 0.1U_0402_10V6KPX@

CU62 0.1U_0402_10V6KPX@CU62 0.1U_0402_10V6KPX@

CU63 0.1U_0402_10V6KPX@CU63 0.1U_0402_10V6KPX@

CU64 0.1U_0402_10V6KPX@CU64 0.1U_0402_10V6KPX@

impedance = 43 mohms

PEG_ICOMPO signals should be routed with max length = 500 mils

- typical impedance = 14.5 mohms

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

2

<PEG>

10/05 Change to 0.22uF.

Typ- suggest 220nF. The change in AC capacitor value from

180nF to 265nF is to enable compatibility with future platforms

having PCIE Gen3 (8GT/s)

11/23 AC-coupling capacitor is 0.1u.Chelsea only support GEN2.

PEG_GTX_C_HRX_N[0..15]

PEG_GTX_C_HRX_P[0..15]

PEG_HTX_C_GRX_N[0..15]

PEG_HTX_C_GRX_P[0..15]

<PEG>

1

PEG_GTX_C_HRX_N[0..15] 21

PEG_GTX_C_HRX_P[0..15] 21

PEG_HTX_C_GRX_N[0..15] 21

PEG_HTX_C_GRX_P[0..15] 21

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2011/11/02 2011/11/02

2011/11/02 2011/11/02

2011/11/02 2011/11/02

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

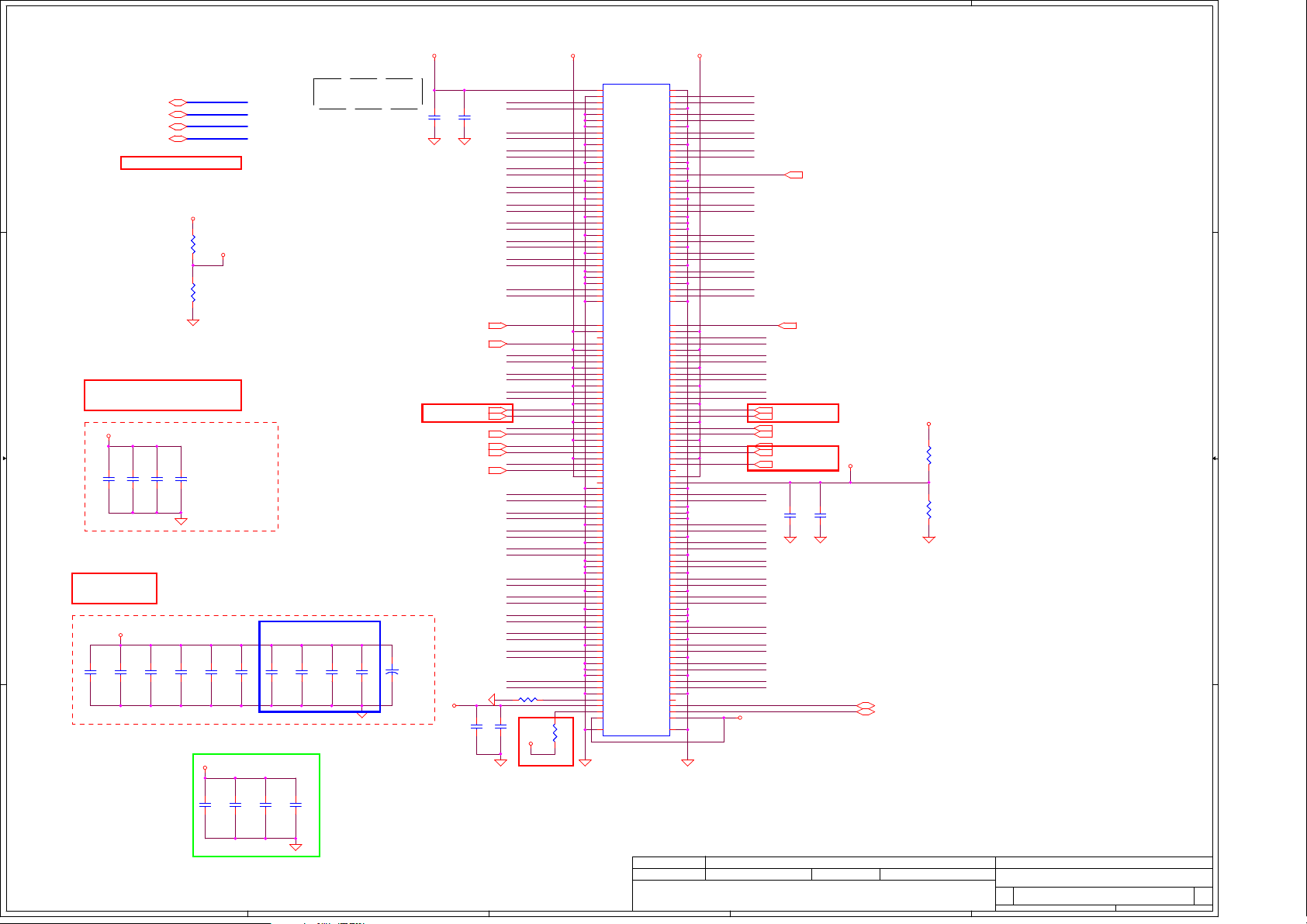

PROCESSOR(1/7) DMI,FDI,PEG

PROCESSOR(1/7) DMI,FDI,PEG

PROCESSOR(1/7) DMI,FDI,PEG

LA-8551P

1

4 57Sunday, November 27, 2011

4 57Sunday, November 27, 2011

4 57Sunday, November 27, 2011

0.1

0.1

0.1

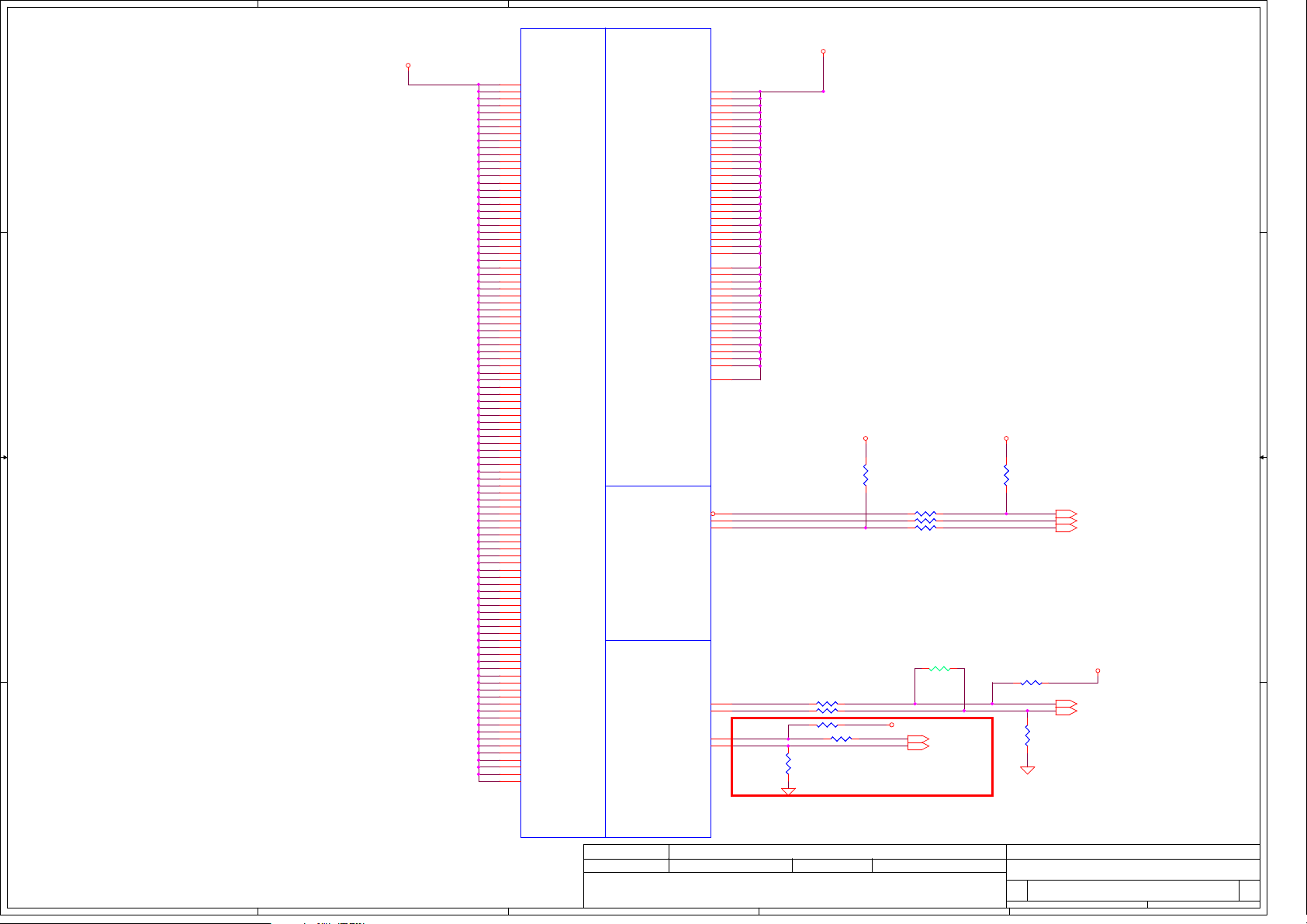

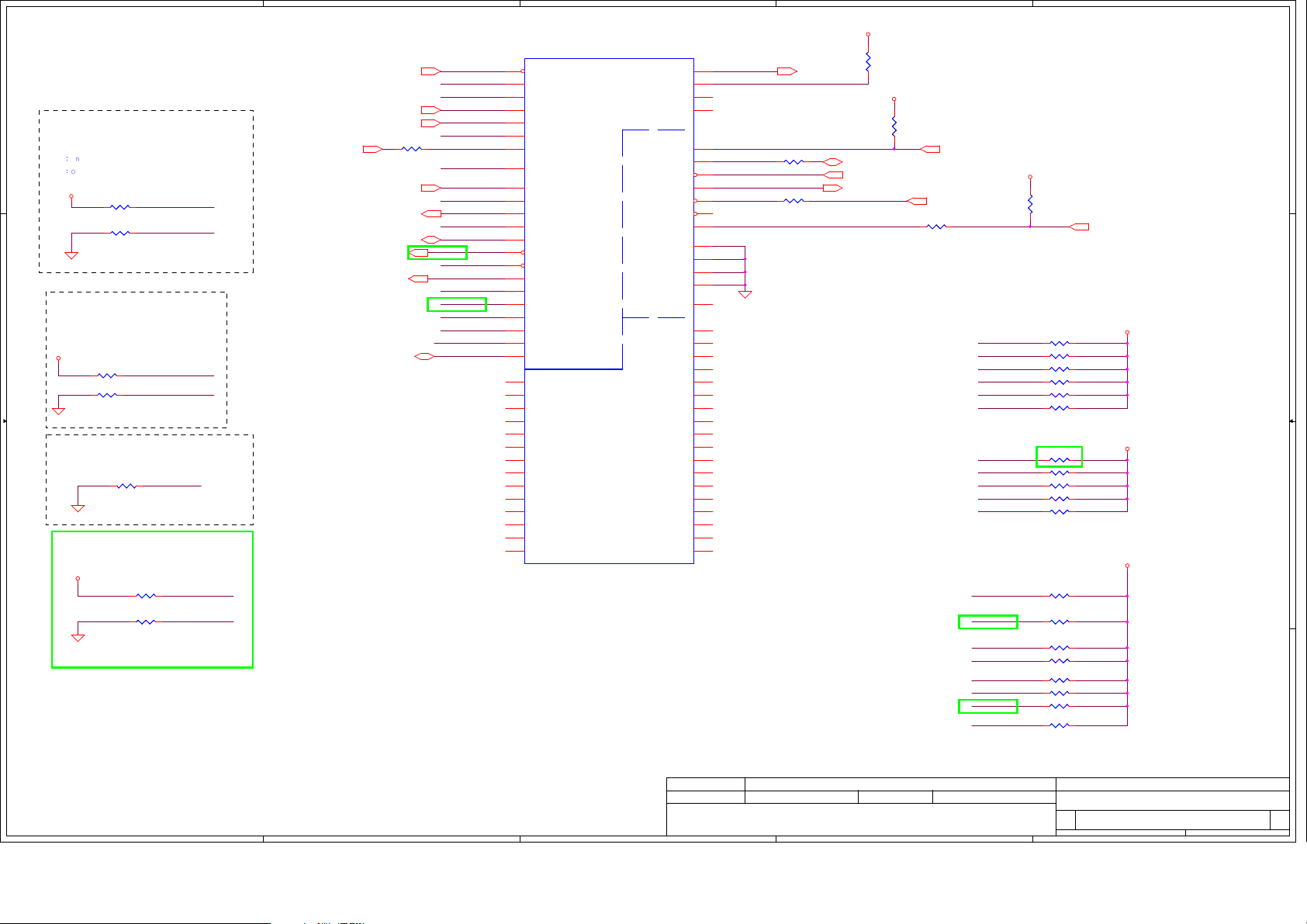

Page 5

5

D D

PROC_DETECT (Processor Detect): pulled to

ground on the processor package. There is no

connection to the processor silicon for this

signal. System board designers may use this

+1.05VS

C C

Processor Pullups

RC8 62_0402_5%RC8 62_0402_5%

RC11 10K_0402_5%RC11 10K_0402_5%

H_PROCHOT#

12

12

12

C4680

C4680

47P_0402_50V8J

47P_0402_50V8J

H_PROCHOT#

H_CPUPWRGD_R

signal to determine if the processor is present

H_SNB_IVB#17

H_PECI17,36 H_DRAMRST# 6

H_PROCHOT#36,47

H_THEMTRIP#17

H_PM_SYNC15

H_CPUPWRGD17

SI# 10/02 Change to Pull High +3VS

+3VS

B B

RC81

RC81

10K_0402_5%

10K_0402_5%

1 2

SYS_PWROK15

PM_DRAM_PWRGD15

+3V_PCH

@ RC27

@

0_0402_5%

0_0402_5%

1 2

+3VS

0.1U_0402_16V4Z

0.1U_0402_16V4Z

RC27

RC28

RC28

@

@

1 2

200_0402_5%

200_0402_5%

RC30

RC30

1 2

200_0402_5%

200_0402_5%

1

CC2

CC2

2

1

2

Part Number = SA00003Y000

Part Number = SA00003Y000

+3VALW

UC2

UC2

74AHC1G09GW_TSSOP5

74AHC1G09GW_TSSOP5

5

P

B

4

O

A

G

3

PM_SYS_PWRGD_BUF

+1.5V_CPU_VDDQ

12

RC25

RC25

200_0402_5%

200_0402_5%

Remove mos for layout

4

+3VS

Check circuit!!!

5

@ UC1

@

1

P

NC

PLT_RST#

PLT_RST#16,21,31,34,36

This pin is for compability with future

platforms. A pull up resistor to VCCIO is

required if connected to the DF_TVS strap

on the PCH.

@

@

1 2

RC7 10K_0402_5%

RC7 10K_0402_5%

1 2

RC9 0_0402_5%RC9 0_0402_5%

H_PROCHOT#

RC10 56_0402_5%RC10 56_0402_5%

H_THEMTRIP# H_THEMTRIP#_R

UNCOREPWRGOOD:

RC18 130_0402_5%RC18 130_0402_5%

SM_DRAMPWROK:DRAM power ok

H_PROCHOT#_R

1 2

1 2

RC12 0_0402_5%RC12 0_0402_5%

1 2

RC13 0_0402_5%RC13 0_0402_5%

RC16

RC16

0_0402_5%

0_0402_5%

H_CPUPWRGD_R

1 2

非非非非

CORE

PM_DRAM_PWRGD_RPM_SYS_PWRGD_BUF

1 2

BUF_CPU_RST#

T5PAD @T5PAD @

H_PM_SYNC_R

外外外外外外外外外外外外

H_PECI_ISO

OK

C26

AN34

AL33

AN33

AL32

AN32

AM34

AP33

V8

AR33

DDR3 Compensation Signals

SM_RCOMP0

RC23 140_0402_1%RC23 140_0402_1%

SM_RCOMP1

RC24 25.5_0402_1%RC24 25.5_0402_1%

SM_RCOMP2

RC26 200_0402_1%RC26 200_0402_1%

12

12

12

PU/PD for JTAG signals

XDP_TMS

XDP_TDI

XDP_TDO

XDP_TCK

XDP_TRST#

2011.10.18 dele te all reserved XDP conponent.

Just reserve te st point for XDP.

T40 PAD@T40 PAD@

T41 PAD@T41 PAD@

T42 PAD@T42 PAD@

T43 PAD@T43 PAD@

T46 PAD@T46 PAD@

2

A

3

R956

R956

0_0402_5%

0_0402_5%

1 2

JCPUB

JCPUB

PROC_SELECT#

SKTOCC#

CATERR#

PECI

PROCHOT#

THERMTRIP#

PM_SYNC

UNCOREPWRGOOD

SM_DRAMPWROK

RESET#

TYCO_2013620-2_IVY BRIDGE

TYCO_2013620-2_IVY BRIDGE

@

@

XDP_TRST#

PLT_RST#

PM_SYS_PWRGD_BUF

BUF_CPU_RST#

G

3

Buffered reset to CPU

1

CC1

@ CC1

@

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

UC1

BUFO_CPU_RST#

4

Y

SN74LVC1G07DCKR_SC70-5

SN74LVC1G07DCKR_SC70-5

MISCTHERMALPWR MANAGEMENT

MISCTHERMALPWR MANAGEMENT

CLOCKS

CLOCKS

DDR3

DDR3

JTAG & BPM

JTAG & BPM

C263 0.1U_0402_16V7KC263 0.1U_0402_16V7K

1 2

C264 220P_0402_50V7KC264 220P_0402_50V7K

1 2

C265 100P_0402_50V8J@C265 100P_0402_50V8J@

1 2

C266 220P_0402_50V7KC266 220P_0402_50V7K

1 2

+1.05VS

12

@

@

RC3

RC3

75_0402_5%

75_0402_5%

1.5K_0402_1%

1.5K_0402_1%

DPLL_REF_CLK

DPLL_REF_CLK#

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

MISC

MISC

Reset# signal is driven by the PCH to multiple agents on the platform.

PCH Reset# output DC levels are 0-V and 3.3 V,

processor Reset input DC levels are 0V and 1.0 V.

Processor high-voltage level is lower than PCH high v oltage level,

therefore a voltage level shifter is required on the R eset# signal.

In order for Reset# to meet the signal quality requirement at the input to

the processor OD buffer must be plac ed on the motherboard between

the PCH and the processor.

RC4

RC4

BCLK

BCLK#

11/21 follow QAZ60 cost down CPU_RST#

BUF_CPU_RST#

12

12

RC6

RC6

750_0402_1%

750_0402_1%

Requires a series resistor of 43±5% between processor and PC H.

It also a needs an Rtt of 75±5% to VCCP after the OD

buffer and before the series resistor.

A28

A27

A16

A15

CLK_CPU_DMI 14

CLK_CPU_DMI# 14

RC84 1K_0402_5%RC84 1K_0402_5%

RC85 1K_0402_5%RC85 1K_0402_5%

12

12

ITP CLK change to part E.

H_DRAMRST#

R8

SM_RCOMP0

AK1

SM_RCOMP1

A5

SM_RCOMP2

A4

PAD

PAD

T35

T35

PAD

PAD

@

@

T39

T39

@

@

AP29

PRDY#

AP27

PREQ#

XDP_TCK

AR26

TCK

XDP_TMS

AR27

TMS

XDP_TRST#

AP30

TRST#

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

XDP_TDI

AR28

TDI

XDP_TDO

AP26

TDO

AL35

AT28

AR29

AR30

AT30

XDP_BPM#4_R

AP32

XDP_BPM#5_R

AR31

XDP_BPM#6_R

AT31

XDP_BPM#7_R

AR32

SI# 8/16 Reserve RC81~RC85 by ESD request

RC17 0_0402_5%RC17 0_0402_5%

1 2

2011.10.18 dele te all reserved XDP conponent.

Just reserve te st point for XDP.

XDP_DBRESET#_R

H_CPUPWRGD_R

SI# 8/19 BOM

C118 220P

C266 220P

C264 220P

C263 0.1u

CC4 0.1u ok

2

100MHz

+1.05VS

6/27 Add ESD solution

XDP_DBRESET#XDP_DBRESET#_R

T60 PAD@T60 PAD@

T61 PAD@T61 PAD@

T62 PAD@T62 PAD@

T63 PAD@T63 PAD@

CC4 0.1U_0402_16V7K

CC4 0.1U_0402_16V7K

12

<BOM Structure>

<BOM Structure>

C118 220P_0402_50V7KC118 220P_0402_50V7K

1 2

6/27 Add ESD solution

XDP_DBRESET#

XDP_DBRESET# 15

RC5 1K_0402_5%RC5 1K_0402_5%

circuit check 10k

12

1

+3VS

Sharing add for module desige

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

5

4

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

3

2011/11/02 2011/11/02

2011/11/02 2011/11/02

2011/11/02 2011/11/02

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Title

Title

Title

PROCESSOR(2/7) PM,XDP,CLK

PROCESSOR(2/7) PM,XDP,CLK

PROCESSOR(2/7) PM,XDP,CLK

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

LA-8041P

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

5 57Sunday, November 27, 2011

5 57Sunday, November 27, 2011

5 57Sunday, November 27, 2011

0.1

0.1

0.1

Page 6

5

JCPUC

JCPUC

4

3

JCPUD

JCPUD

2

1

DDR_A_D[0..63]11

D D

C C

DDR_A_BS01 1

B B

DDR_A_BS11 1

DDR_A_BS21 1

DDR_A_CAS#11

DDR_A_RAS#11

DDR_A_WE#11

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

AP11

AN11

AL12

AM12

AM11

AL11

AP12

AN12

AJ14

AH14

AL15

AK15

AL14

AK14

AJ15

AH15

AE10

AF10

G10

N10

M10

AG6

AG5

AK6

AK5

AH5

AH6

AK8

AK9

AH8

AH9

AL9

AL8

AE8

AD9

AF9

F10

AJ5

AJ6

AJ8

AJ9

C5

D5

D3

D2

D6

C6

C2

C3

F8

G9

F9

F7

G8

G7

K4

K5

K1

K2

M8

N8

N7

M9

N9

M7

V6

J1

J5

J4

J2

SA_DQ[0]

SA_DQ[1]

SA_DQ[2]

SA_DQ[3]

SA_DQ[4]

SA_DQ[5]

SA_DQ[6]

SA_DQ[7]

SA_DQ[8]

SA_DQ[9]

SA_DQ[10]

SA_DQ[11]

SA_DQ[12]

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

SA_DQ[16]

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CAS#

SA_RAS#

SA_WE#

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

RSVD_TP[10]

SA_CLK[0]

SA_CLK#[0]

SA_CKE[0]

SA_CLK[1]

SA_CLK#[1]

SA_CKE[1]

RSVD_TP[1]

RSVD_TP[2]

RSVD_TP[3]

RSVD_TP[4]

RSVD_TP[5]

RSVD_TP[6]

SA_CS#[0]

SA_CS#[1]

RSVD_TP[7]

RSVD_TP[8]

SA_ODT[0]

SA_ODT[1]

RSVD_TP[9]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AB6

AA6

V9

AA5

AB5

V10

AB4

AA4

W9

AB3

AA3

W10

AK3

AL3

AG1

AH1

AH3

AG3

AG2

AH2

C4

G6

J3

M6

AL6

AM8

AR12

AM15

D4

F6

K3

N6

AL5

AM9

AR11

AM14

AD10

W1

W2

W7

V3

V2

W3

W6

V1

W5

AD8

V4

W4

AF8

V5

V7

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

M_CLK_DDR0 11

M_CLK_DDR#0 11

DDR_CKE0_DIMMA 11

M_CLK_DDR1 11

M_CLK_DDR#1 11

DDR_CKE1_DIMMA 11

DDR_CS0_DIMMA# 11

DDR_CS1_DIMMA# 11

M_ODT0 11

M_ODT1 11

DDR_A_DQS#[0..7] 11

DDR_A_DQS[0..7] 11

DDR_A_MA[0..15] 11

DDR_B_D[0..63]12

DDR_B_BS012

DDR_B_BS112

DDR_B_BS212

DDR_B_CAS#12

DDR_B_RAS#12

DDR_B_WE#12

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

D10

K10

AM5

AM6

AR3

AP3

AN3

AN2

AN1

AP2

AP5

AN9

AT5

AT6

AP6

AN8

AR6

AR5

AR9

AJ11

AT8

AT9

AH11

AR8

AJ12

AH12

AT11

AN14

AR14

AT14

AT12

AN15

AR15

AT15

AA9

AA7

AA10

AB8

AB9

J10

C9

A7

C8

A9

A8

D9

D8

G4

F4

F1

G1

G5

F5

F2

G2

J7

J8

K9

J9

K8

K7

M5

N4

N2

N1

M4

N5

M2

M1

R6

SB_DQ[0]

SB_DQ[1]

SB_DQ[2]

SB_DQ[3]

SB_DQ[4]

SB_DQ[5]

SB_DQ[6]

SB_DQ[7]

SB_DQ[8]

SB_DQ[9]

SB_DQ[10]

SB_DQ[11]

SB_DQ[12]

SB_DQ[13]

SB_DQ[14]

SB_DQ[15]

SB_DQ[16]

SB_DQ[17]

SB_DQ[18]

SB_DQ[19]

SB_DQ[20]

SB_DQ[21]

SB_DQ[22]

SB_DQ[23]

SB_DQ[24]

SB_DQ[25]

SB_DQ[26]

SB_DQ[27]

SB_DQ[28]

SB_DQ[29]

SB_DQ[30]

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

SB_BS[0]

SB_BS[1]

SB_BS[2]

SB_CAS#

SB_RAS#

SB_WE#

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

RSVD_TP[11]

RSVD_TP[12]

RSVD_TP[13]

RSVD_TP[14]

RSVD_TP[15]

RSVD_TP[16]

RSVD_TP[17]

RSVD_TP[18]

RSVD_TP[19]

RSVD_TP[20]

SB_CLK[0]

SB_CLK#[0]

SB_CKE[0]

SB_CLK[1]

SB_CLK#[1]

SB_CKE[1]

SB_CS#[0]

SB_CS#[1]

SB_ODT[0]

SB_ODT[1]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

AE2

AD2

R9

AE1

AD1

R10

AB2

AA2

T9

AA1

AB1

T10

AD3

AE3

AD6

AE6

AE4

AD4

AD5

AE5

D7

F3

K6

N3

AN5

AP9

AK12

AP15

C7

G3

J6

M3

AN6

AP8

AK11

AP14

AA8

T7

R7

T6

T2

T4

T3

R2

T5

R3

AB7

R1

T1

AB10

R5

R4

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

M_CLK_DDR2 12

M_CLK_DDR#2 12

DDR_CKE0_DIMMB 12

M_CLK_DDR3 12

M_CLK_DDR#3 12

DDR_CKE1_DIMMB 12

10/05 change net name.

DDR_CS0_DIMMB# 12

DDR_CS1_DIMMB# 12

M_ODT2 12

M_ODT3 12

DDR_B_DQS#[0..7] 12

DDR_B_DQS[0..7] 12

DDR_B_MA[0..15] 12

TYCO_2013620-2_IVY BRIDGE

TYCO_2013620-2_IVY BRIDGE

@

@

RC35

@RC35

@

0_0402_5%

RC38

RC38

0_0402_5%

1 2

D

S

D

S

DDR3_DRAMRST#_RH_DRAMRST#

13

QC2

QC2

BSS138_NL_SOT23-3

BSS138_NL_SOT23-3

G

G

2

9/7 Folllow PAJ80 BOM by Light

del: SB501380020

1 2

add: SB00000QO00

1

CC3

CC3

0.047U_0402_16V4Z

0.047U_0402_16V4Z

2

CPU通通DIMM做reset

H_DRAMRST#5

4.99K_0402_1%

4.99K_0402_1%

A A

DRAMRST_CNTRL_PC H9,14

5

RC39

RC39

0_0402_5%

0_0402_5%

1 2

DRAMRST_CNTRL

RC36

RC36

1K_0402_5%

1K_0402_5%

+1.5V

12

1 2

RC37

RC37

1K_0402_5%

1K_0402_5%

S0

DRAMRST_CNTRL_P CH hgih ,MOS O N

H_DRAMRST# HIGH ,DDR3_DRAMRST# HIGH

Dimm not reset

S3

DRAMRST_CNTRL_P CH Low ,MOS OF F

H_DRAMRST# lo,D DR3_DRAMRST# HI GH

Dimm not reset

S4,5

DRAMRST_CNTRL_P CH Low ,MOS OF F

H_DRAMRST# lo,D DR3_DRAMRST# lo w

Dimm reset

4

DDR3_DRAMRST# 11,12

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2011/11/02 2011/11/02

2011/11/02 2011/11/02

2011/11/02 2011/11/02

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

TYCO_2013620-2_IVY BRIDGE

TYCO_2013620-2_IVY BRIDGE

@

@

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

PROCESSOR(3/7) DDRIII

PROCESSOR(3/7) DDRIII

PROCESSOR(3/7) DDRIII

LA-8041P

1

6 57Sunday, November 27, 2011

6 57Sunday, November 27, 2011

6 57Sunday, November 27, 2011

0.1

0.1

0.1

Page 7

5

4

3

2

1

CFG Straps for Processor

CFG2

D D

change to install

12

RC40

RC40

1K_0402_1%

1K_0402_1%

Change to part G.

PEG Static Lane Reversal - CFG2 is for the 16x

CFG2

JCPUE

JCPUE

T3PAD T3PAD

CLK_RES_ITP 14

CLK_RES_ITP# 14

ITP CLK change from part C.

T64PAD T64PAD

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD37

RSVD38

RSVD39

RSVD40

RSVD51

RSVD52

BCLK_ITP

BCLK_ITP#

KEY

AH27

AH26

L7

AG7

AE7

AK2

W8

AT26

AM33

AJ27

T8

J16

H16

G16

AR35

AT34

AT33

AP35

AR34

B34

A33

A34

B35

C35

AJ32

AK32

AN35

AM35

AT2

AT1

AR1

B1

CPU_RSVD6

CPU_RSVD7

RESERVED

RESERVED

VCC_DIE_SENSE

VSS_DIE_SENSE

RSVD_NCTF1

RSVD_NCTF2

RSVD_NCTF3

RSVD_NCTF4

RSVD_NCTF5

RSVD_NCTF6

RSVD_NCTF7

RSVD_NCTF8

RSVD_NCTF9

RSVD_NCTF10

RSVD_NCTF11

RSVD_NCTF12

RSVD_NCTF13

CFG0

T9T9

CFG1

T6T6

CFG2

T10T10

CFG3

T11T11

CFG4

CFG5

1 2

12

T12T12

T13T13

T7T7

T8T8

T14T14

T15T15

T16T16

T47T47

T48T48

T58T58

T59T59

T17T17

T18T18

49.9_0402_1%

49.9_0402_1%

12

VSSAXG_VAL_SENSE

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

VCC_VAL_SENSE

VSS_VAL_SENSE

VAXG_VAL_SENSE

C C

2011.10.18 delete XDP resistor

just reserve test point for XDP.

+VGFX_CORE

+CPU_CORE

Just modify PWR to correct ,

didn't change net-name to save layout time;must modify on SI phase

B B

A A

RC42 4 9.9_0402_1%RC42 4 9.9_0402_1%

RC44 49.9_0402_1%RC44 49.9_0402_1%

RC43

RC43

1 2

RC45 4 9.9_0402_1%RC45 4 9.9_0402_1%

AK28

CFG[0]

AK29

CFG[1]

AL26

CFG[2]

AL27

CFG[3]

AK26

CFG[4]

AL29

CFG[5]

AL30

CFG[6]

AM31

CFG[7]

AM32

CFG[8]

AM30

CFG[9]

AM28

CFG[10]

AM26

CFG[11]

AN28

CFG[12]

AN31

CFG[13]

AN26

CFG[14]

AM27

CFG[15]

AK31

CFG[16]

AN29

CFG[17]

AJ31

VAXG_VAL_SENSE

AH31

VSSAXG_VAL_SENSE

AJ33

VCC_VAL_SENSE

AH33

VSS_VAL_SENSE

AJ26

RSVD5

F25

RSVD8

F24

RSVD9

F23

RSVD10

D24

RSVD11

G25

RSVD12

G24

RSVD13

E23

RSVD14

D23

RSVD15

C30

RSVD16

A31

RSVD17

B30

RSVD18

B29

RSVD19

D30

RSVD20

B31

RSVD21

A30

RSVD22

C29

RSVD23

J20

RSVD24

B18

RSVD25

J15

RSVD27

TYCO_2013620-2_IVY BRIDGE

TYCO_2013620-2_IVY BRIDGE

@

@

CFG

CFG

change to install

T21T21

T22T22

Display Port Presence Strap

CFG4

PCIE Port Bifurcation Straps

CFG[6:5]

PEG DEFER TRAINING

CFG7

1: Normal Operation; Lane # definition matches

socket pin map definition

*

0:Lane Reversed

CFG4

*

1K_0402_1%

1K_0402_1%

12

RC41

RC41

1K_0402_1%

1K_0402_1%

1 : Disabled; No Physical Display Port

attached to Embedded Display Port

0 : Enabled; An external Display Port device is

connected to the Embedded Display Port

CFG6

CFG5

RC48

RC48

12

12

RC49

UMA@RC49

UMA@

1K_0402_1%

1K_0402_1%

@

@

11: (Default) x16 - Device 1 functions 1 and 2 disabled

10: x8, x8 - Device 1 function 1 enabled ; function 2

disabled

01: Reserved - (Device 1 function 1 disabled ; function

2 enabled)

*

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

CFG7

*

12

RC50

@RC50

@

1K_0402_1%

1K_0402_1%

1: (Default) PEG Train immediately following

xxRESETB de assertion

0: PEG Wait for BIOS for training

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2011/11/02 2011/11/02

2011/11/02 2011/11/02

2011/11/02 2011/11/02

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

PROCESSOR(4/7) RSVD,CFG

PROCESSOR(4/7) RSVD,CFG

PROCESSOR(4/7) RSVD,CFG

LA-8041P

1

7 57Sunday, November 27, 2011

7 57Sunday, November 27, 2011

7 57Sunday, November 27, 2011

0.1

0.1

0.1

Page 8

5

D D

C C

B B

A A

4

+CPU_CORE

AG35

AG34

AG33

AG32

AG31

AG30

AG29

AG28

AG27

AG26

AF35

AF34

AF33

AF32

AF31

AF30

AF29

AF28

AF27

AF26

AD35

AD34

AD33

AD32

AD31

AD30

AD29

AD28

AD27

AD26

AC35

AC34

AC33

AC32

AC31

AC30

AC29

AC28

AC27

AC26

AA35

AA34

AA33

AA32

AA31

AA30

AA29

AA28

AA27

AA26

3

POWER

JCPUF

JCPUF

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

Y35

VCC51

Y34

VCC52

Y33

VCC53

Y32

VCC54

Y31

VCC55

Y30

VCC56

Y29

VCC57

Y28

VCC58

Y27

VCC59

Y26

VCC60

V35

VCC61

V34

VCC62

V33

VCC63

V32

VCC64

V31

VCC65

V30

VCC66

V29

VCC67

V28

VCC68

V27

VCC69

V26

VCC70

U35

VCC71

U34

VCC72

U33

VCC73

U32

VCC74

U31

VCC75

U30

VCC76

U29

VCC77

U28

VCC78

U27

VCC79

U26

VCC80

R35

VCC81

R34

VCC82

R33

VCC83

R32

VCC84

R31

VCC85

R30

VCC86

R29

VCC87

R28

VCC88

R27

VCC89

R26

VCC90

P35

VCC91

P34

VCC92

P33

VCC93

P32

VCC94

P31

VCC95

P30

VCC96

P29

VCC97

P28

VCC98

P27

VCC99

P26

VCC100

POWER

CORE SUPPLY

CORE SUPPLY

PEG AND DDR

PEG AND DDR

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

VSS_SENSE_VCCIO

SENSE LINES SVID

SENSE LINES SVID

VCCIO1

VCCIO2

VCCIO3

VCCIO4

VCCIO5

VCCIO6

VCCIO7

VCCIO8

VCCIO9

VCCIO10

VCCIO11

VCCIO12

VCCIO13

VCCIO14

VCCIO15

VCCIO16

VCCIO17

VCCIO18

VCCIO19

VCCIO20

VCCIO21

VCCIO22

VCCIO23

VCCIO24

VCCIO25

VCCIO26

VCCIO27

VCCIO28

VCCIO29

VCCIO30

VCCIO31

VCCIO32

VCCIO33

VCCIO34

VCCIO35

VCCIO36

VCCIO37

VCCIO38

VCCIO39

VCCIO40

VIDALERT#

VIDSCLK

VIDSOUT

AH13

AH10

AG10

AC10

Y10

U10

P10

L10

J14

J13

J12

J11

H14

H12

H11

G14

G13

G12

F14

F13

F12

F11

E14

E12

E11

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

J23

H_CPU_SVIDALRT#

AJ29

H_CPU_SVIDCLK

AJ30

H_CPU_SVIDDAT

AJ28

VCCSENSE_R

AJ35

VSSSENSE_R

AJ34

VCCIO_SENSE_R

B10

VSS_SENSE_VCCIO

A10

+1.05VS

RC61 0_0402_5%RC61 0_0402_5%

1 2

RC62 0_0402_5%RC62 0_0402_5%

1 2

RC63

RC63

1 2

10_0402_1%

10_0402_1%

RC65 0_0402_5%RC65 0_0402_5%

1 2

12

RC66

RC66

10_0402_1%

10_0402_1%

10/05 mount.

(follow check list)

2

+1.05VS

12

RC55

RC55

130_0402_5%

130_0402_5%

RC57 43_0402_1%RC57 43_0402_1%

1 2

RC58 0_0402_5%RC58 0_0402_5%

1 2

RC59 0_0402_5%RC59 0_0402_5%

1 2

+1.05VS

RC121

RC121

1 2

100_0402_1%~D

100_0402_1%~D

@

@

VCCIO_SENSE 50

VSS_SENSE_VCCIO 50

+1.05VS

12

RC56

RC56

75_0402_5%

75_0402_5%

1 2

RC60 1 00_0402_1%RC60 1 00_0402_1%

12

RC64

RC64

100_0402_1%

100_0402_1%

Place the PU

resistors close to VR

VR_SVID_ALRT# 55

VR_SVID_CLK 55

VR_SVID_DAT 55

+CPU_CORE

Place the PU

resistors close to CPU

VCCSENSE 55

VSSSENSE 55

1

TYCO_2013620-2_IVY BRIDGE

TYCO_2013620-2_IVY BRIDGE

@

@

5

4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2011/11/02 2011/11/02

2011/11/02 2011/11/02

2011/11/02 2011/11/02

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

PROCESSOR(5/7) PWR,BYPASS

PROCESSOR(5/7) PWR,BYPASS

PROCESSOR(5/7) PWR,BYPASS

LA-8041P

1

8 57Sunday, November 27, 2011

8 57Sunday, November 27, 2011

8 57Sunday, November 27, 2011

0.1

0.1

0.1

Page 9

5

4

3

2

1

+1.5V_CPU_VDDQ +1.5V

CC74 0.1U_0402_10V7KCC74 0.1U_0402_10V7K

CC75 0.1U_0402_10V7KCC75 0.1U_0402_10V7K

D D

+V_DDR_REFA

+V_DDR_REFB

C C

+VGFX_CORE

RC15

RC15

1 2

0_0402_5%@

0_0402_5%@

RC82

RC82

1 2

0_0402_5%@

0_0402_5%@

QC7

QC7

SB000002X00

SB000002X00

13

D

D

BSS138W-7-F_SOT323-3

BSS138W-7-F_SOT323-3

S

S

QC8

QC8

SB000002X00

SB000002X00

13

D

D

BSS138W-7-F_SOT323-3

BSS138W-7-F_SOT323-3

S

S

12

12

DRAMRST_CNTRL_PC H

2

G

G

+V_DDR_REFA_R

RC14

RC14

1 2

1K_0402_1%@

1K_0402_1%@

DRAMRST_CNTRL_PC H

2

G

G

+V_DDR_REFB_R

RC83

RC83

1 2

1K_0402_1%@

1K_0402_1%@

DRAMRST_CNTRL_PC H 6,14

For Chief River only

M3 Circuit (Processor Generated SO-DIMM VREF_DQ)

10/03 add +V_DDR_REFB

+1.8VS

RC77

B B

SI# 7/29 Add CC 26 10uF and res erve 330U on 1. 8V power Rail

RC77

0_0805_5%

0_0805_5%

1 2

10U_0603_6.3V6M

10U_0603_6.3V6M

1

1

CC26

CC26

+

+

2

2

330U_D2_2VM_R6M

330U_D2_2VM_R6M

Can connect to GND if motherboard only

‧‧‧‧

supports external graphics and if GFX VR is not

stuffed in a common motherboard design,

VAXG can be left floating in a common

‧‧‧‧

motherboard design (Gfx VR keeps VAXG from

floating) if the VR is stuffed

JCPUG

JCPUG

AT24

VAXG1

AT23

VAXG2

AT21

VAXG3

AT20

VAXG4

AT18

VAXG5

AT17

VAXG6

AR24

VAXG7

AR23

VAXG8

AR21

VAXG9

AR20

VAXG10

AR18

VAXG11

AR17

VAXG12

AP24

VAXG13

AP23

VAXG14

AP21

VAXG15

AP20

VAXG16

AP18

VAXG17

AP17

VAXG18

AN24

VAXG19

AN23

VAXG20

AN21

VAXG21

AN20

VAXG22

AN18

VAXG23

AN17

VAXG24

AM24

VAXG25

AM23

VAXG26

AM21

VAXG27

AM20

VAXG28

AM18

VAXG29

AM17

VAXG30

AL24

VAXG31

AL23

VAXG32

AL21

VAXG33

AL20

VAXG34

AL18

VAXG35

AL17

VAXG36

AK24

VAXG37

AK23

VAXG38

AK21

VAXG39

AK20

VAXG40

AK18

VAXG41

AK17

VAXG42

AJ24

VAXG43

AJ23

VAXG44

AJ21

VAXG45

AJ20

VAXG46

AJ18

VAXG47

AJ17

VAXG48

AH24

VAXG49

AH23

VAXG50

AH21

VAXG51

AH20

VAXG52

AH18

VAXG53

AH17

VAXG54

+1.8VS_VCCPLL

CC121

1U_0402_6.3V6K

CC121

1U_0402_6.3V6K

CC122

1U_0402_6.3V6K

CC122

CC120

CC120

@

@

1U_0402_6.3V6K

1

1

2

2

B6

VCCPLL1

A6

VCCPLL2

A2

VCCPLL3

TYCO_2013620-2_IVY BRIDGE

TYCO_2013620-2_IVY BRIDGE

@

@

POWER

POWER

SENSE

SENSE

GRAPHICS

GRAPHICS

1.8V RAIL

1.8V RAIL

VAXG_SENSE

VSSAXG_SENSE

LINES

LINES

SM_VREF

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

VREFMISC

VREFMISC

DDR3 -1.5V RAILS

DDR3 -1.5V RAILS

SA RAIL

SA RAIL

VCCSA_SENSE

VCCSA_VID[0]

VCCSA_VID[1]

VCCIO_SEL

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VCCSA1

VCCSA2

VCCSA3

VCCSA4

VCCSA5

VCCSA6

VCCSA7

VCCSA8

RC157 100_0402_1%~D@RC157 100_0402_1%~D@

AK35

AK34

AL1

B4

D1

AF7

AF4

AF1

AC7

AC4

AC1

Y7

Y4

Y1

U7

U4

U1

P7

P4

P1

M27

M26

L26

J26

J25

J24

H26

H25

VCCSA_SENSE

H23

0_0402_5%

0_0402_5%

C22

C24

RC80 0_0402_5%RC80 0_0402_5%

A19

100±5% pull-up to VCC;

1 2

+V_SM_VREF_CNT

+V_DDR_REFA_R

+V_DDR_REFB_R

100±5% pull-down to GND.

VCC_AXG_SENSE 55

VSS_AXG_SENSE 55

QC4 Change to SA0000JA00 for small package

1016

10U_0603_6.3V6M

10U_0603_6.3V6M

1

CC22

CC22

2

11/21 follow PBL22 design remove 10u*2, 1U*5

1 2

RC78 0 _0402_5%@RC78 0_0402_5%@

VCCSA_VID0

RC79

RC79

1 2

1 2

VCCP_PWRCTR L_R

VCCSA_VID1

VCCSA_VID0 52

VCCSA_VID1 52

10K_0402_5%

10K_0402_5%

1 2

RC53

RC53

@

@

CPU EDS descript as follow:

+V_SM_VREF should

have 20 mil trace width

1

CC79

CC79

0.1U_0402_16V4Z

0.1U_0402_16V4Z

11/21 follow PBL22 design remove 10u*2, 1U*8;

keep 10U*5

+VCCSA

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

CC21

CC21

VCCSA_SENSE 52

+1.05VS

1

CC24

CC24

2

12

RC52

75_0402_5%

75_0402_5%

1

2

@RC52

@

2

+VCCSA

Delete CC25 330U cap 10.19

(after check with power)

+1.5V_CPU_VDDQ

12

RC68

RC68

1K_0402_1%

1K_0402_1%

12

RC69

RC69

1K_0402_1%

1K_0402_1%

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

1

CC95

CC95

2

1

1

1

CC97

CC97

CC96

CC96

2

2

2

+1.5V_CPU_VDDQ Source

+1.5V_CPU_VDDQ

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

1

CC99

CC99

CC98

CC98

2

1

+

+

330U_D2_2V_Y

330U_D2_2V_Y

2

CC100

CC100

For Chief River platforms this pin

+1.5V +1.5V_CPU_VDDQ

QC4

+VSB

+3VALW

12

RC72

RC72

100K_0402_5%

RC74

RC74

0_0402_5%

A A

CPU1.5V_S3_GATE36

SUSP#36,43,50,51,52,53

0_0402_5%

1 2

RC75

@RC75

@

0_0402_5%

0_0402_5%

1 2

100K_0402_5%

RUN_ON_CPU1.5VS3#

61

2

2N7002DWH_SOT363-6

2N7002DWH_SOT363-6

QC5A

QC5A

12

34

5

RC70

RC70

100K_0402_5%

100K_0402_5%

RUN_ON_CPU1.5VS3

2N7002DWH_SOT363-6

2N7002DWH_SOT363-6

QC5B

QC5B

330K_0402_5%

330K_0402_5%

SI# BOM Change CC118 0.1u 25V form 0.1u 16V

Follow DG 0.71 page 6

5

QC4

AON6718L_DFN8-5

AON6718L_DFN8-5

5

RC73

RC73

4

12

1

2

3

4

@

@

1

CC118

CC118

2

0.1U_0402_25V6

0.1U_0402_25V6

12

R78

R78

20K_0402_5%

20K_0402_5%

RC71

RC71

470_0603_5%

470_0603_5%

1 2

61

RUN_ON_CPU1.5VS3#

2

Q10A

Q10A

2N7002DWH_SOT363-6

2N7002DWH_SOT363-6

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

should not be used.

VID[0] VID[1] 2011 2012

0 0 0.90 V Yes Yes

0 1 0.80 V Yes Yes

1 0 0.725 V No Yes

1 1 0.675 V No Yes

Compal Secret Data

Compal Secret Data

2011/11/02 2011/11/02

2011/11/02 2011/11/02

2011/11/02 2011/11/02

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

PROCESSOR(6/7) PWR

PROCESSOR(6/7) PWR

PROCESSOR(6/7) PWR

LA-8041P

1

9 57Sunday, November 27, 2011

9 57Sunday, November 27, 2011

9 57Sunday, November 27, 2011

0.1

0.1

0.1

Page 10

5

D D

C C

B B

4

JCPUH

JCPUH

AT35

VSS1

AT32

VSS2

AT29

VSS3

AT27

VSS4

AT25

VSS5

AT22

VSS6

AT19

VSS7

AT16

VSS8

AT13

VSS9

AT10

VSS10

AT7

VSS11

AT4

VSS12

AT3

VSS13

AR25

VSS14

AR22

VSS15

AR19

VSS16

AR16

VSS17

AR13

VSS18

AR10

VSS19

AR7

VSS20

AR4

VSS21

AR2

VSS22

AP34

VSS23

AP31

VSS24

AP28

VSS25

AP25

VSS26

AP22

VSS27

AP19

VSS28

AP16

VSS29

AP13

VSS30

AP10

VSS31

AP7

VSS32

AP4

VSS33

AP1

VSS34

AN30

VSS35

AN27

VSS36

AN25

VSS37

AN22

VSS38

AN19

VSS39

AN16

VSS40

AN13

VSS41

AN10

VSS42

AN7

VSS43

AN4

VSS44

AM29

VSS45

AM25

VSS46

AM22

VSS47

AM19

VSS48

AM16

VSS49

AM13

VSS50

AM10

VSS51

AM7

VSS52

AM4

VSS53

AM3

VSS54

AM2

VSS55

AM1

VSS56

AL34

VSS57

AL31

VSS58

AL28

VSS59

AL25

VSS60

AL22

VSS61

AL19

VSS62

AL16

VSS63

AL13

VSS64

AL10

VSS65

AL7

VSS66

AL4

VSS67

AL2

VSS68

AK33

VSS69

AK30

VSS70

AK27

VSS71

AK25

VSS72

AK22

VSS73

AK19

VSS74

AK16

VSS75

AK13

VSS76

AK10

VSS77

AK7

VSS78

AK4

VSS79

AJ25

VSS80

TYCO_2013620-2_IVY BRIDGE

TYCO_2013620-2_IVY BRIDGE

@

@

VSS

VSS

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111