Datasheet ATmega163L-4PI, ATmega163L-4PC, ATmega163L-4AI, ATmega163L-4AC, ATmega163-8PI Datasheet (ATMEL)

...Page 1

Features

• High-performance, Low- power AVR

– 130 Powerful Instructions – Most Single Clock Cycle Execution

– 32 x 8 General Purpose Working Regist ers

– Fully Static Operation

– Up to 8 MIPS Throughput at 8 MHz

– On-ch ip 2- c y cl e Multiplie r

• Nonvolatile Program and Data Memori es

• Self-programming In-System Programmable Flash Memory

– 16K Bytes with Optional Boot Block (256 - 2K Bytes )

Endurance: 1,000 Write/Erase Cycles

– Boot Section Allows Reprogramming of Program Code without External

Programmer

– Optional Boot Code Section with Independent Lock Bits

– 512 Bytes EEPROM

Endurance: 100,000 Write/Erase Cycles

– 1024 Bytes Internal SRAM

– Programming Lock for Software Security

• Peripheral Features

– Two 8-bit Timer/Counters with Separate Prescaler and Compare Mode

– One 16-bit Timer/Counter with Separate Prescaler, Compare Mode, and Capt ure

Mode

– Real Time Clock with Separat e O scillator and Counter Mode

– Three PWM Channels

– 8-channel, 10-bit ADC

– Byte-oriented Two-wire Serial Interface

– Programmable Serial UART

– Master/Slave SPI Serial Interface

– Programmable Watchdog Timer with Separate On-chip Oscillator

– Analog Comparator

• Special Microcontroller Features

– Power-on Reset and Programmable Brown-ou t Detec ti on

– Internal Calibra ted RC Oscillator

– External and Internal Interrupt Sources

– Four Sleep Modes: Idle, ADC Noise Reduction, Power-save, and Power- dow n

• Power Consumption at 4 MHz, 3.0V, 25°C

– Active 5.0 mA

– Idle Mode 1.9 mA

– Power-down Mode < 1 µA

• I/O and Packages

– 32 Programmable I/O Lines

– 40-pin PDIP and 44-pin TQFP

• Operating Voltag es

– 2.7 - 5.5V for ATmega163L

– 4.0 - 5.5V for ATmega163

• Speed Grades

– 0 - 4 MHz for ATmega163L

– 0 - 8 MHz for ATmega163

®

8-bit Microcontroller

8-bit

Microcontroller

with 16K Bytes

In-System

Programmable

Flash

ATmega163

ATmega163L

Not Recommend for

New Designs. Use

ATmega16.

Rev. 1142E–AVR–02/03

1

Page 2

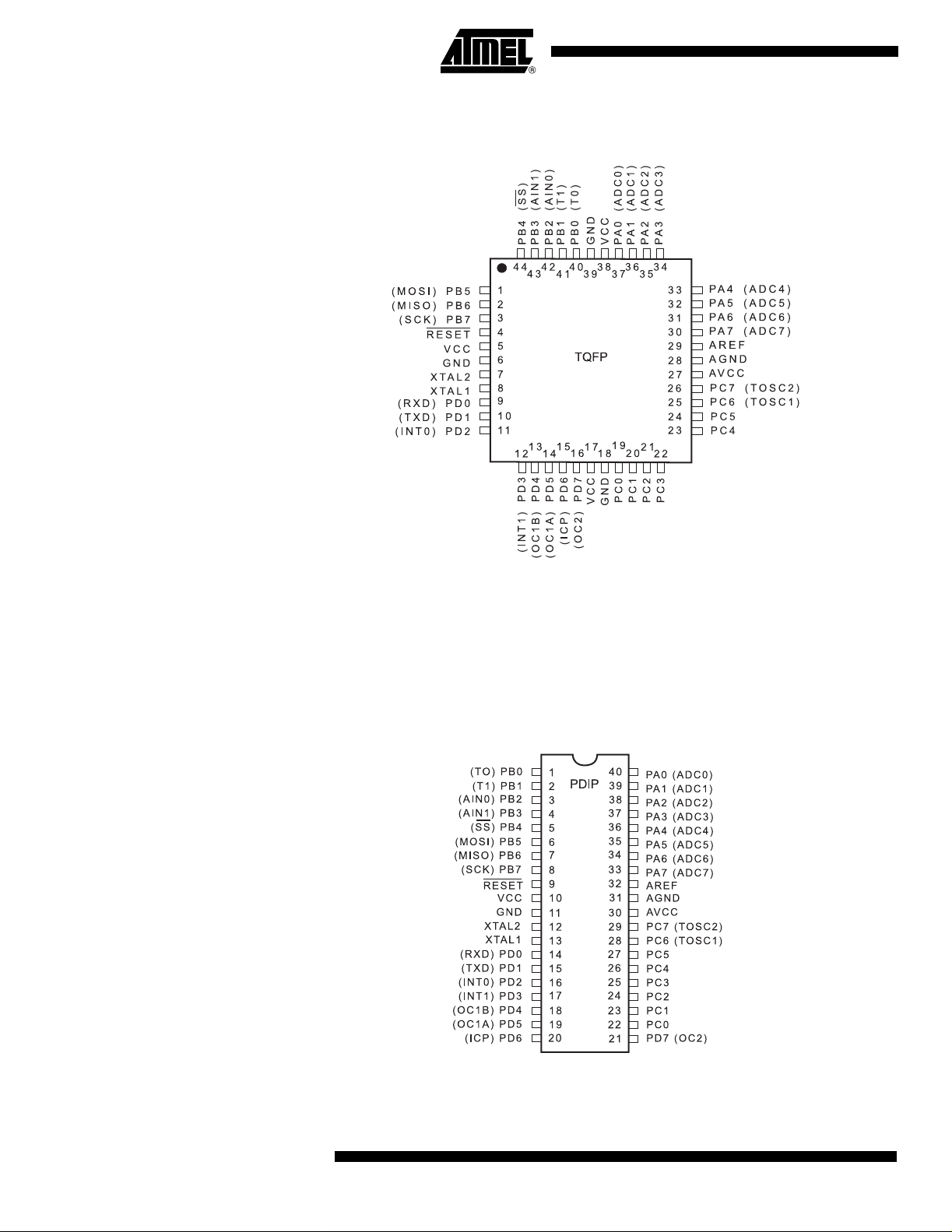

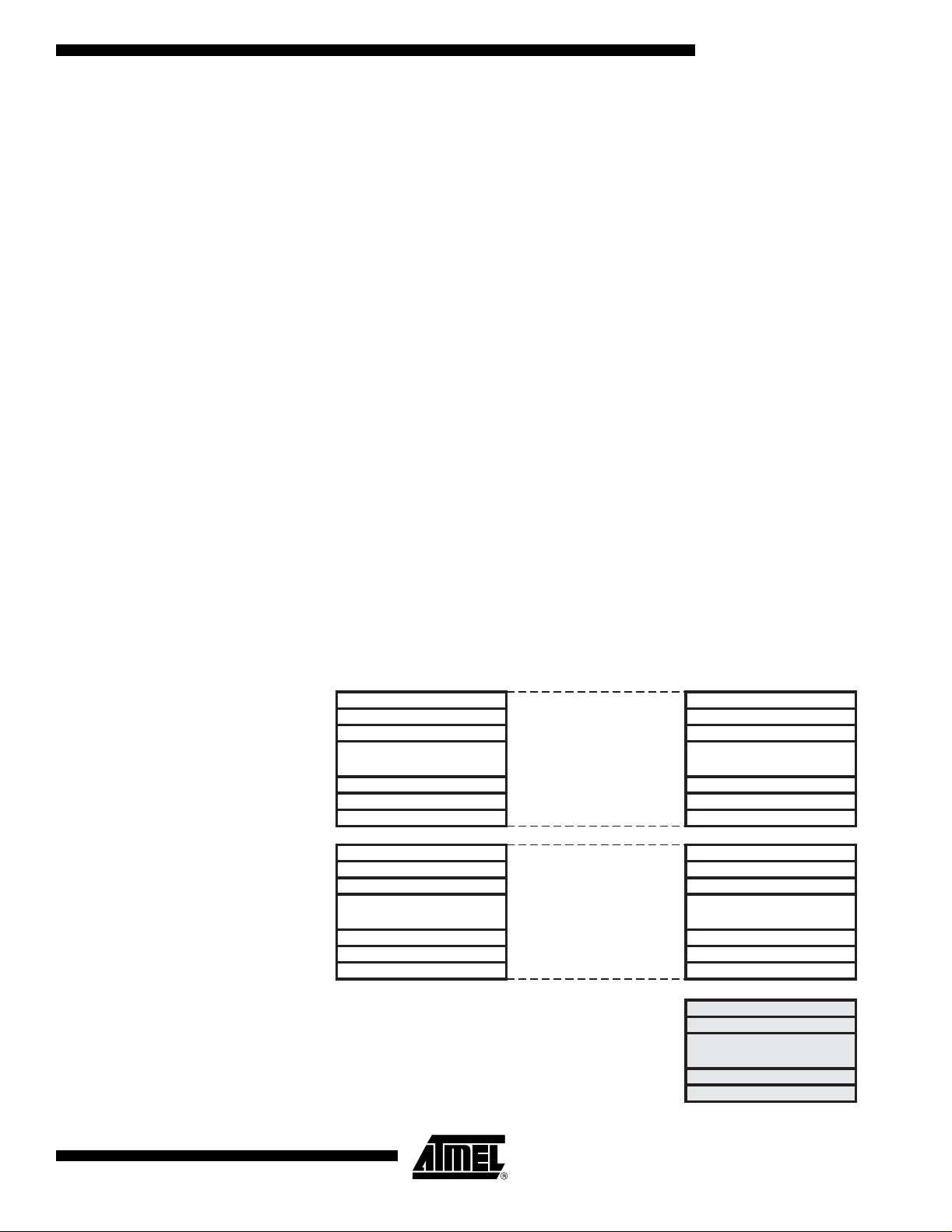

Pin Configurations

(SDA)

(SCL)

(SDA)

(SCL)

2

ATmega163(L)

1142E–AVR–02/03

Page 3

ATmega163(L)

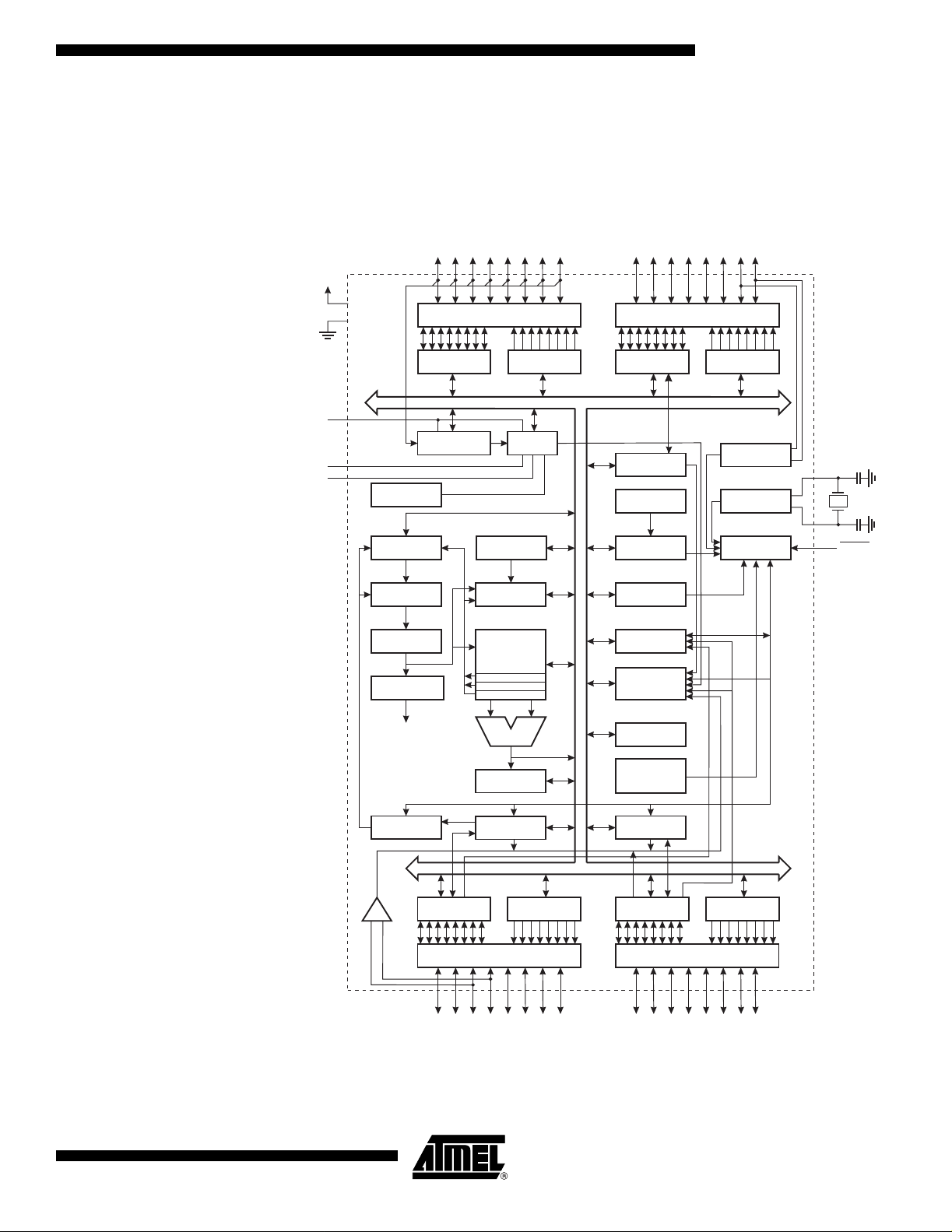

Description The ATmega163 is a low-power CMOS 8-bit microcontroller based on the AVR architec-

ture. By executing powerful instructions in a single clock cycle, the ATmega163

achieves throughputs approaching 1 MIPS per MHz allowing the system designer to

optimize power consumption versus processing speed.

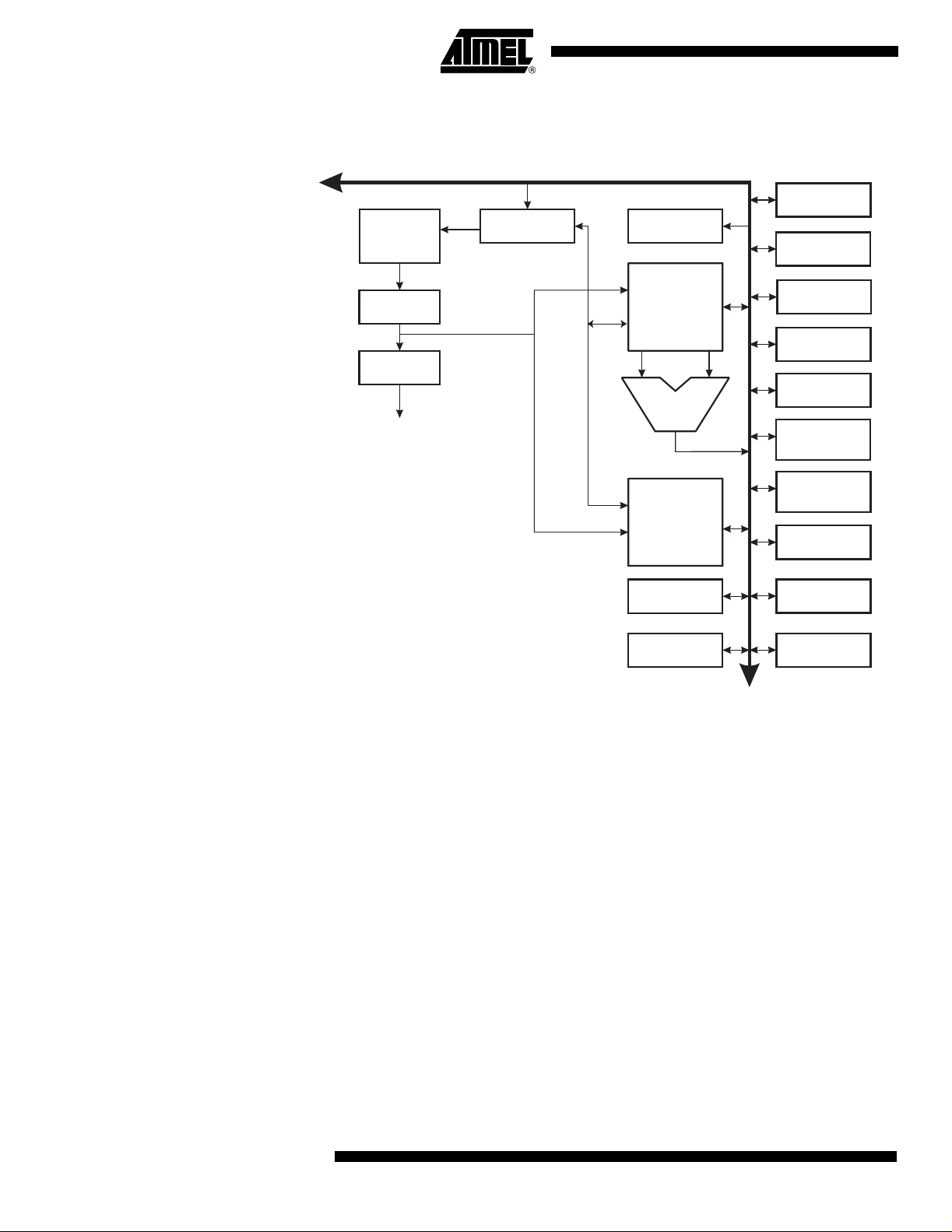

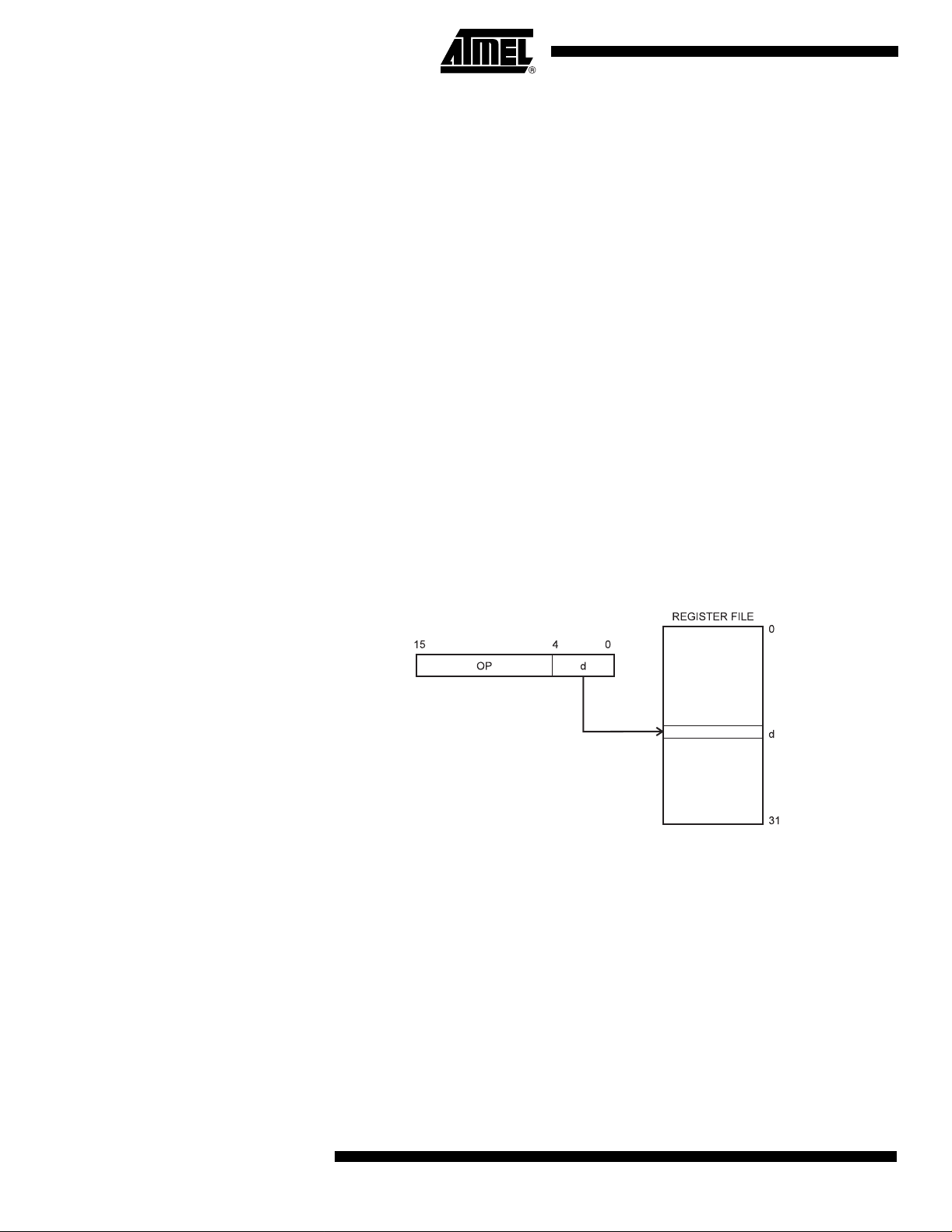

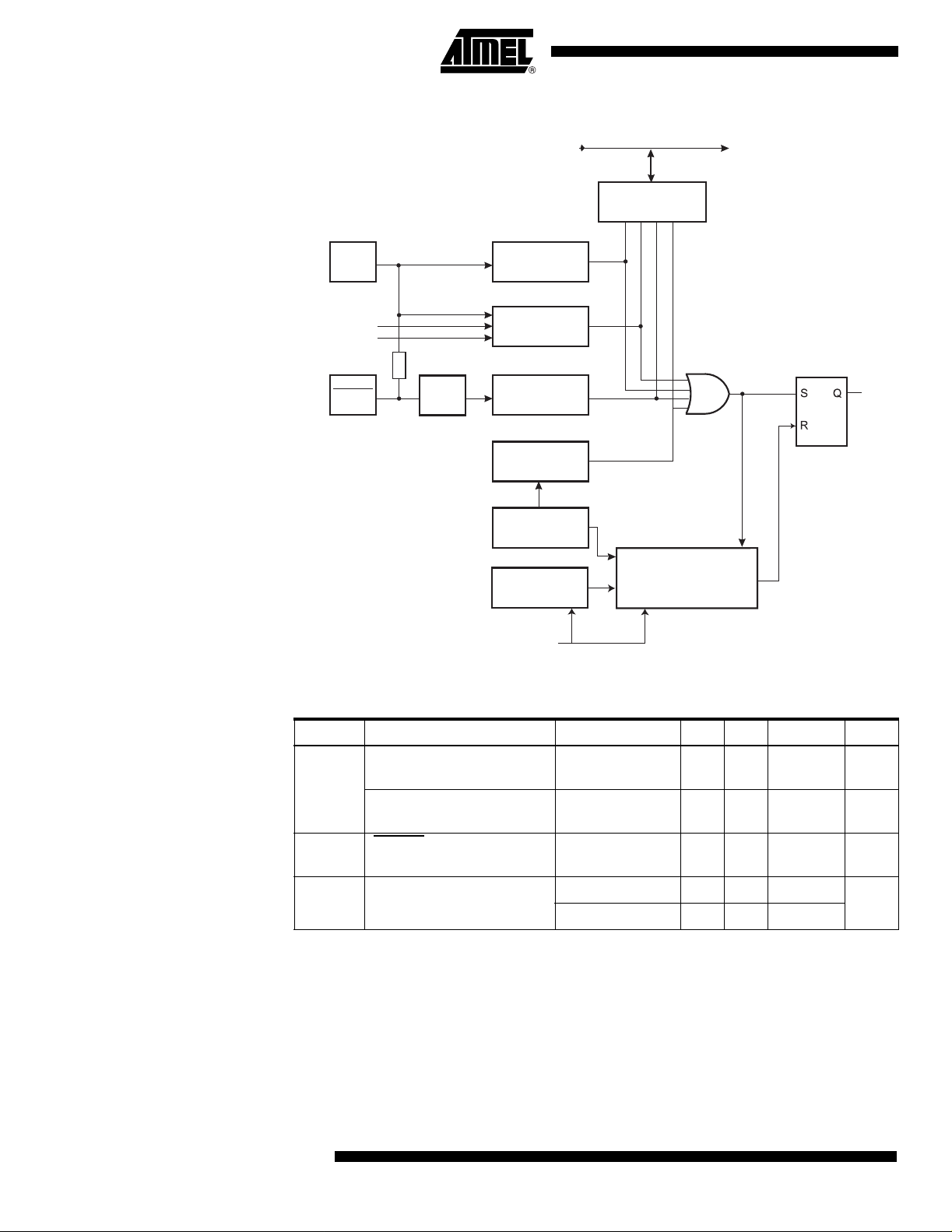

Block Diagram Figure 1. Block Diagram

PA0 - PA7

VCC

PC0 - PC7

GND

AVCC

AGND

AREF

DATA REGISTER

INTERNAL

REFERENCE

PROGRAM

COUNTER

PROGRAM

FLASH

INSTRUCTION

REGISTER

INSTRUCTION

DECODER

CONTROL

LINES

PORTA DRIVERS

PORTA

ANALOG MUX

REG. PORTA

STACK

POINTER

SRAM

GENERAL

PURPOSE

REGISTERS

X

Y

Z

ALU

STATUS

REGISTER

DATA DIR.

ADC

8-BIT DATA BUS

PORTC DRIVERS

DATA REGISTER

PORTC

2-WIRE SERIAL

INTERFACE

INTERNAL

OSCILLATOR

WATCHDOG

TIMER

MCU CONTROL

REGISTER

TIMER/

COUNTERS

INTERRUPT

UNIT

EEPROM

INTERNAL

CALIBRATED

OSCILLATOR

DATA DIR.

REG. PORTC

OSCILLATOR

OSCILLATOR

TIMING AND

CONTROL

XTAL1

XTAL2

RESET

1142E–AVR–02/03

PROGRAMMING

LOGIC

DATA REGISTER

+

ANALOG

COMPARATOR

PORTB

SPI

REG. PORTB

PORTB DRIVERS

PB0 - PB7

DATA DIR.

UART

DATA REGISTER

PORTD

PORTD DRIVERS

PD0 - PD7

DATA DIR.

REG. PORTD

The AVR core combines a rich instruction set with 32 general purpose working registers.

All the 32 re gist ers ar e d irect ly co nnec ted t o t he Ari thme tic Logi c Un it (A LU), allow ing

two independent registers to be accessed in one single instruction executed in one clock

3

Page 4

cycle. The resulting architecture is more code efficient while achieving throughputs up to

ten times faster than conventional CISC microcontrollers.

The ATmega163 provides t he f ollowing featu res: 16K by tes of In-Sy stem Se lf-Programmable Flash, 512 bytes EEPROM, 1024 bytes SRAM, 32 general purpose I/O lines, 32

general purpose worki ng regist ers, three flexib le Timer/Cou nters with compa re modes,

internal and external interrupts, a byte oriented Two-wire Serial Interface, an 8-cha nnel,

10-bit ADC, a program mable Wat chdog Ti mer with internal Osci llator, a program mable

serial UART, an SPI serial port, and four software selectable power saving modes. The

Idle mode stops the CPU while allowing the SRAM, Timer/Counters, SPI port, and interrupt system to continue functioning. The Power-down m ode sa ves the register contents

but freezes the Oscillator, disabling all other chip functions until the next interrupt or

Hardware Reset. In Power-save mode , the asynchrono us Timer Oscillator cont inues to

run, allow ing the u ser to m aintai n a time r base whi le the rest of the device i s slee ping.

The ADC No ise Redu ction mo de stop s the CP U and a ll I/O mo dules exce pt asy nchronous timer and ADC, to minimize switching noise during ADC conversions.

The On-chip ISP Flash can be programmed through an SPI serial interface or a conventional programmer. By installing a Self-Programming Boot Loader, the microcontroller

can be updated within the applica tion without any extern al comp onents. The Boot P rogram can use any interface to download the application program in the Application Flash

memory. By combining an 8-bit CPU with In-System Self-Programmable Flash on a

monolithic chip, the Atmel ATmega163 is a powerful microcontroller that provides a

highly flexible and cost effective solution to many embedded control applications.

The ATmega163 AVR is supported with a full suite of program and system development

tools i nclud ing: C comp ile rs, m acro a sse mbl ers, progra m de bugg er /simu lators , In -Circuit Emulators, and evaluation kits.

Pin Descript i on s

VCC Digital supply voltage. GND Digital ground. Port A (PA7..PA0) Port A serves as the analog inputs to the A/D Converter.

Port A also serves as an 8-bit bi-directional I/O port, if the A/D Converter is not used.

Port pins can provide internal pull-up resistors (selecte d for eac h bit). The P ort A output

buffers can sink 20mA and can drive LED displ ays directly. When pi ns PA0 to PA 7 are

used as inputs and are externally pulled low, they will source current if the internal pullup resistors are activated. The Port A pins are tristated when a reset condition becomes

active, even if the clock is not running.

Port B (PB7..PB0) Port B is an 8-bit bi-directional I/O port with internal pull -up resistors (sele cted for each

bit). The Port B output buffers can sink 20 mA. As in puts, P ort B pins that are ex ternally

pulled low will source current if the pull-up resistors are activated. Port B also serves the

functions of va rious sp eci al feat ures of th e ATm ega83 /163 as list ed on page 117 . T he

Port B pins are tristated when a reset condition becomes active, even if the clock is not

running.

Port C (PC7..PC0) Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected fo r each

bit). The Port C output buffers can sink 20 mA. As inputs, Port C pins that are externally

pulled low wi ll sou rce curren t if the p ull-u p resist ors are a ctivate d. The P ort C pins a re

tristated when a reset condition becomes active, even if the clock is not running.

4

ATmega163(L)

1142E–AVR–02/03

Page 5

ATmega163(L)

Port C also serves the f unc tions of various special features of t he A Tmega163 as listed

on page 124.

Port D (PD7..PD0) Port D is an 8-b it bidi rectiona l I/O port with inte rnal pu ll-up resis tors (sel ected for eac h

bit). The Port D output buffers can sink 20 mA. As inputs, Port D pins that are externally

pulled low will source current if the pull-up resistors are activated. Port D also serves the

functions of various special features of the AT m ega163 as listed on page 128. The Port

D pins are tristated when a reset condition becomes active, even if the clock is not

running.

RESET

Reset input. A low leve l on th is pin for m ore than 50 0 ns w ill generat e a Rese t, eve n if

the clock is not running. Shorter pulses are not guaranteed to generate a Reset.

XTAL1 Input to the inverting Oscillator amplifier and input to the internal clock operating circuit. XTAL2 Output from the inverting Oscillator amplifier. AVCC This is the supply vol tage pin for P ort A an d the A/D Conve rter. I t should b e extern ally

connected to V

nected to V

, even if the ADC is not used. If the ADC is used, it should be con-

CC

through a low-pass filter. See page 105 for details on operation of the

CC

ADC.

AREF AREF is the analog reference input pin for the A/D Converter. For ADC operations, a

voltage in the range 2.5V to AVCC can be applied to this pin.

AGND Analog ground. If the board has a separate analog ground plane, this pin should be con-

nected to this ground plane. Otherwise, connect to GND.

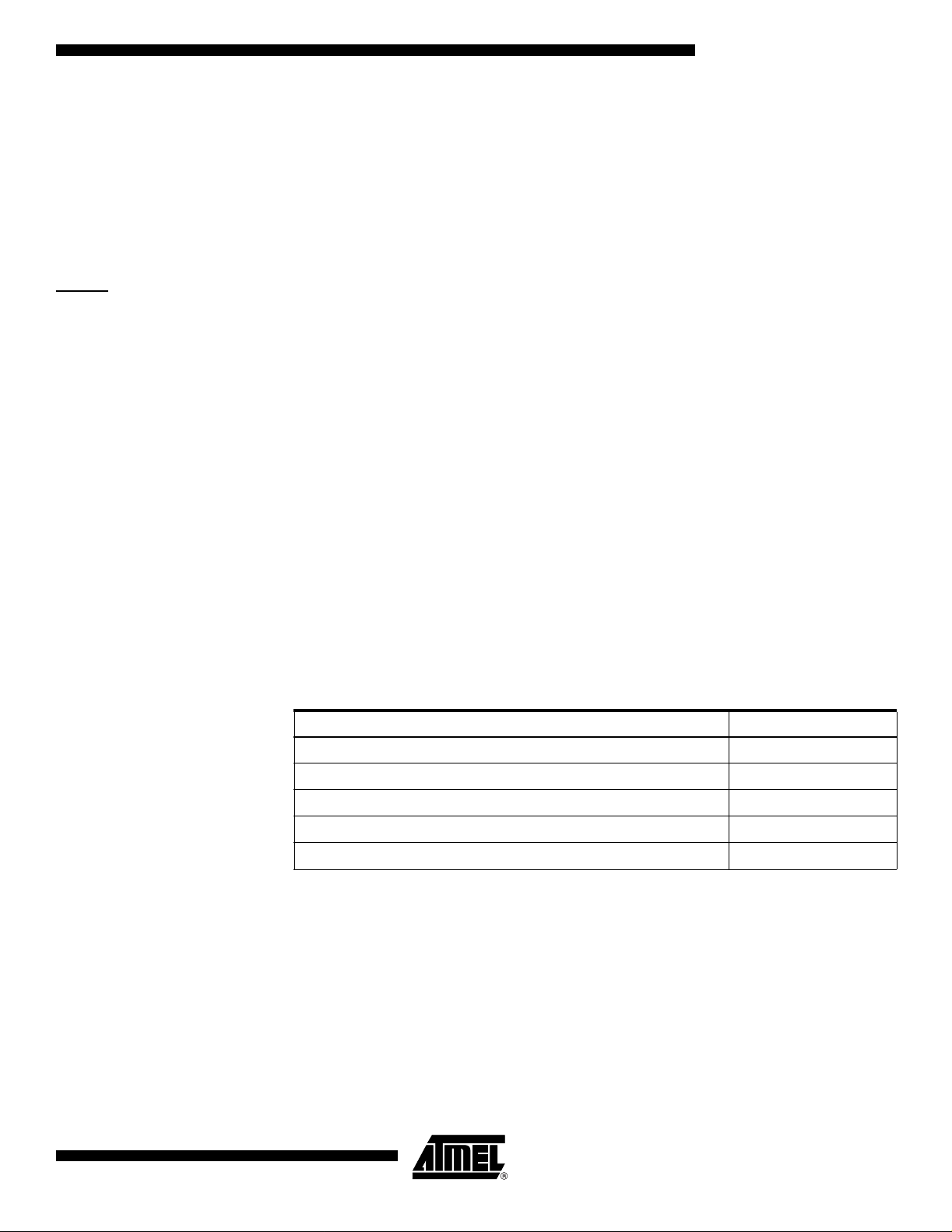

Clock Options The device has the following clock source options, selectable by Flash Fuse bits as

shown:

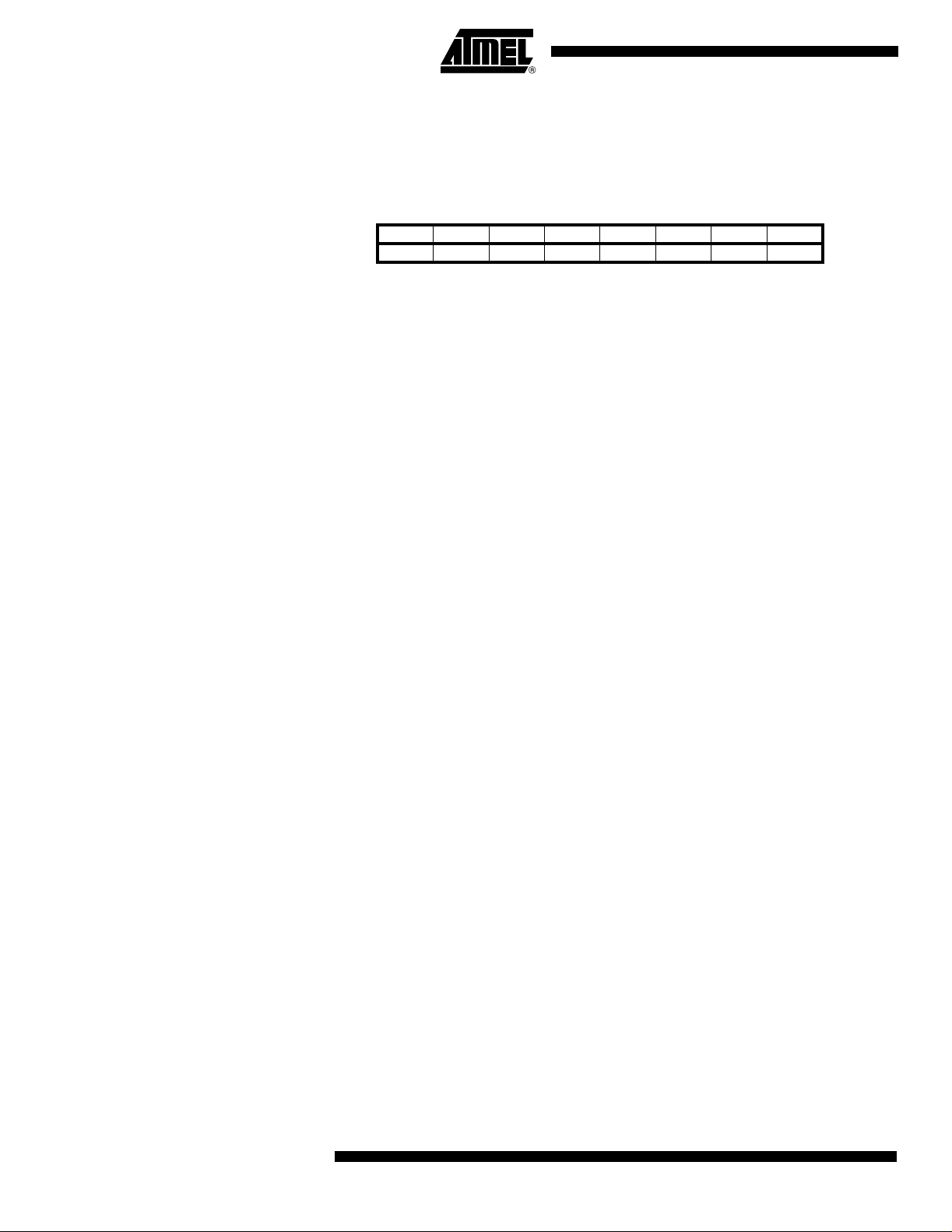

Table 1. Device Clocking Options Select

Device Clocking Option CKSEL3..0

External Crystal/Ceramic Resonator 1111 - 1010

(1)

External Low-frequency Crystal 1001 - 1000

External RC Oscillator 0111 - 0101

Internal RC Oscillator 0100 - 0010

External Clock 0001 - 0000

Note: 1. “1” means unprogrammed, “0” means programmed.

The various choices for each clocking option give different start-up times as shown in

Table 5 on page 25.

Internal RC Oscillator The internal RC Oscillator option is an On-chip Oscillator running at a fixed frequency of

nominally 1 MHz . If sel ected, the device can operate with no external com pone nts. The

device is shipped with this option selected. See “EEPROM Read/Write Access” on page

62 for information on calibrating this Oscillator.

1142E–AVR–02/03

5

Page 6

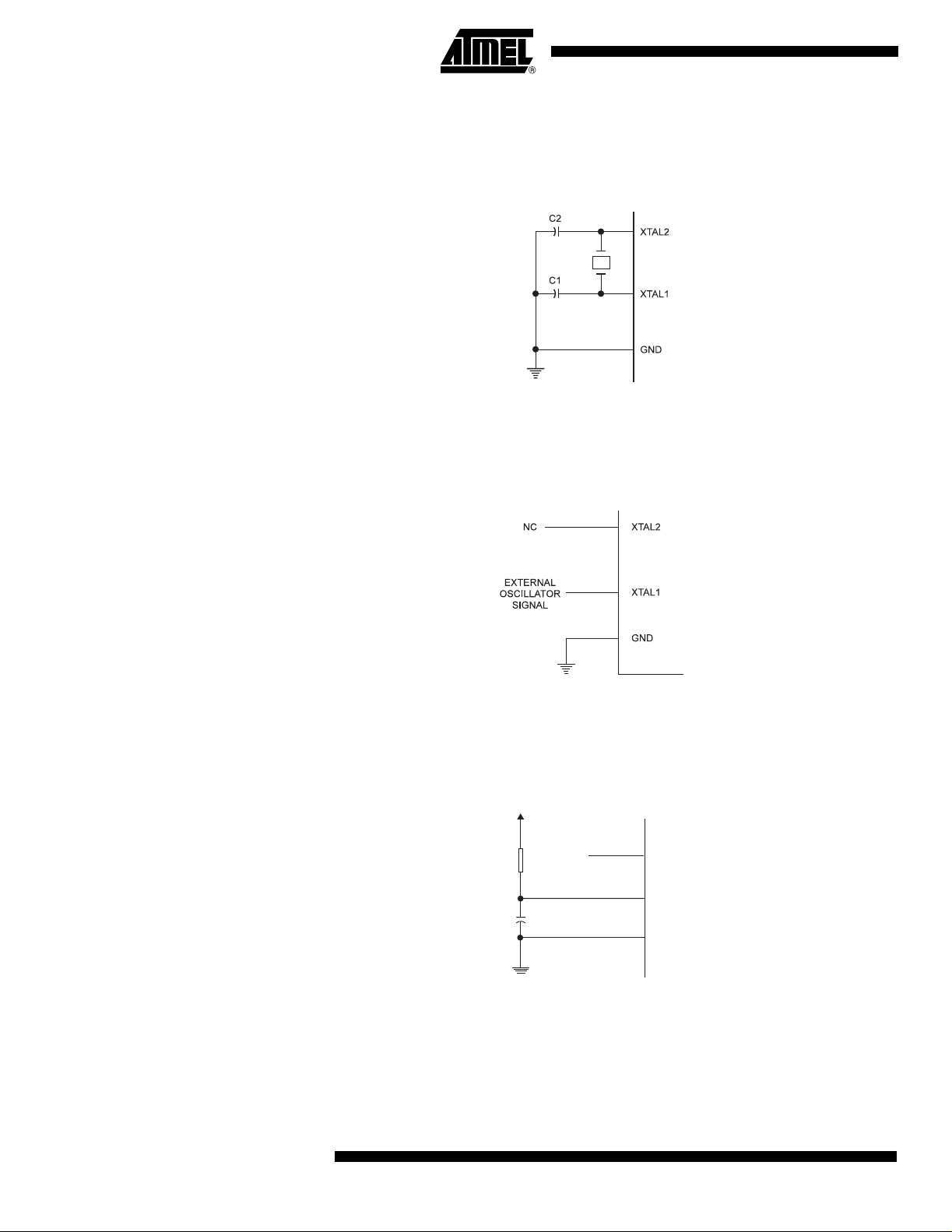

Crystal Oscillator XTAL1 and XTAL2 are input and output, respectively, of an inverting amplifier which can

be configured for use as an On-chip Oscillator, as shown in Figure 2. Either a quartz

crystal or a ceramic resonator may be used.

Figure 2. Oscillator Connections

External Clock To drive the device from an ext ernal clock s ource, XT AL 1 should b e driven as shown i n

Figure 3.

Figure 3. External Clock Drive Configuration

External RC Oscillator For timing insensitive app lications, the ex ternal RC configuration shown i n Figure 4 c an

be used. For details on how to choose R and C, see Table 64 on page 162.

Figure 4. External RC C onfigurati on

V

CC

R

C

NC

XTAL2

XTAL1

GND

Timer Oscillator For the Timer Oscillator pins, TOSC1 and TOSC2, the crystal is connect ed directly

between the pins. No external capacitors are needed. The Oscillator is optimized for use

with a 32,768 Hz watch crystal. Appl ying an e xternal cloc k source to the T OSC1 pin is

not recommended.

6

ATmega163(L)

1142E–AVR–02/03

Page 7

ATmega163(L)

Architectural Overview

The fast-access Register File concept contains 32 x 8-bit general purpose working registers with a single clock cycle access time. This means that during one single clock

cycle, one Arithmetic Logic Unit (ALU) operation is executed. Two ope rands are output

from the Register File, the operation is executed, and the result is stored back in the

Register File – in one clock cycle.

Six of the 32 registers can be used as three 16-bits indirect address register pointers for

Data Spa ce addressi ng – enabling efficient address cal culations. One of the thre e

address pointers is also used as the address pointer for look-up tables in Flash Program

memory. These added function registers are the 16-bits X-, Y-, and Z-register.

The ALU supports arithmetic and logic operat ions between registers or between a c onstant an d a regi ster. Si ng le regis ter ope ratio ns ar e also exec uted in the AL U. Figure 5

shows the ATmega163 AVR Enhanced RISC microcontroller architecture.

In addition to the register operation, the conventional Memory Addressing modes can be

used on the Register File as well. This is enabled by the fact that the Register File is

assigned the 32 lowest Data Space addresses ($00 - $1F), allowing them to be

accessed as though they were ordinary memory locations.

The I/O Memory s pace cont ains 64 a ddresse s for CPU peri pheral func tions as Con trol

Registers, Timer/Counters, A/D-converters, and other I/O functions. The I/O Memory

can be accessed directly, or as the Data Space locations following those of the Register

File, $20 - $5F.

1142E–AVR–02/03

7

Page 8

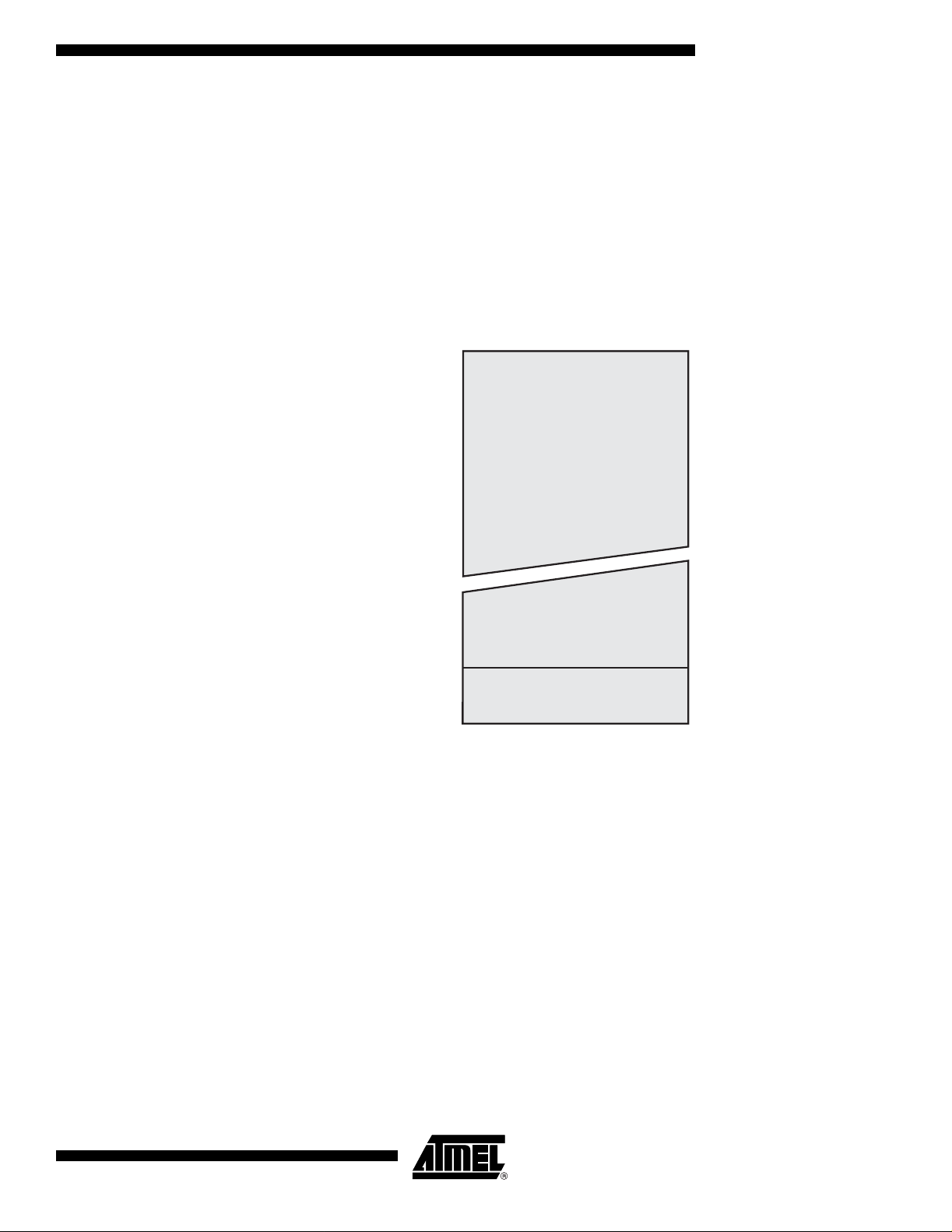

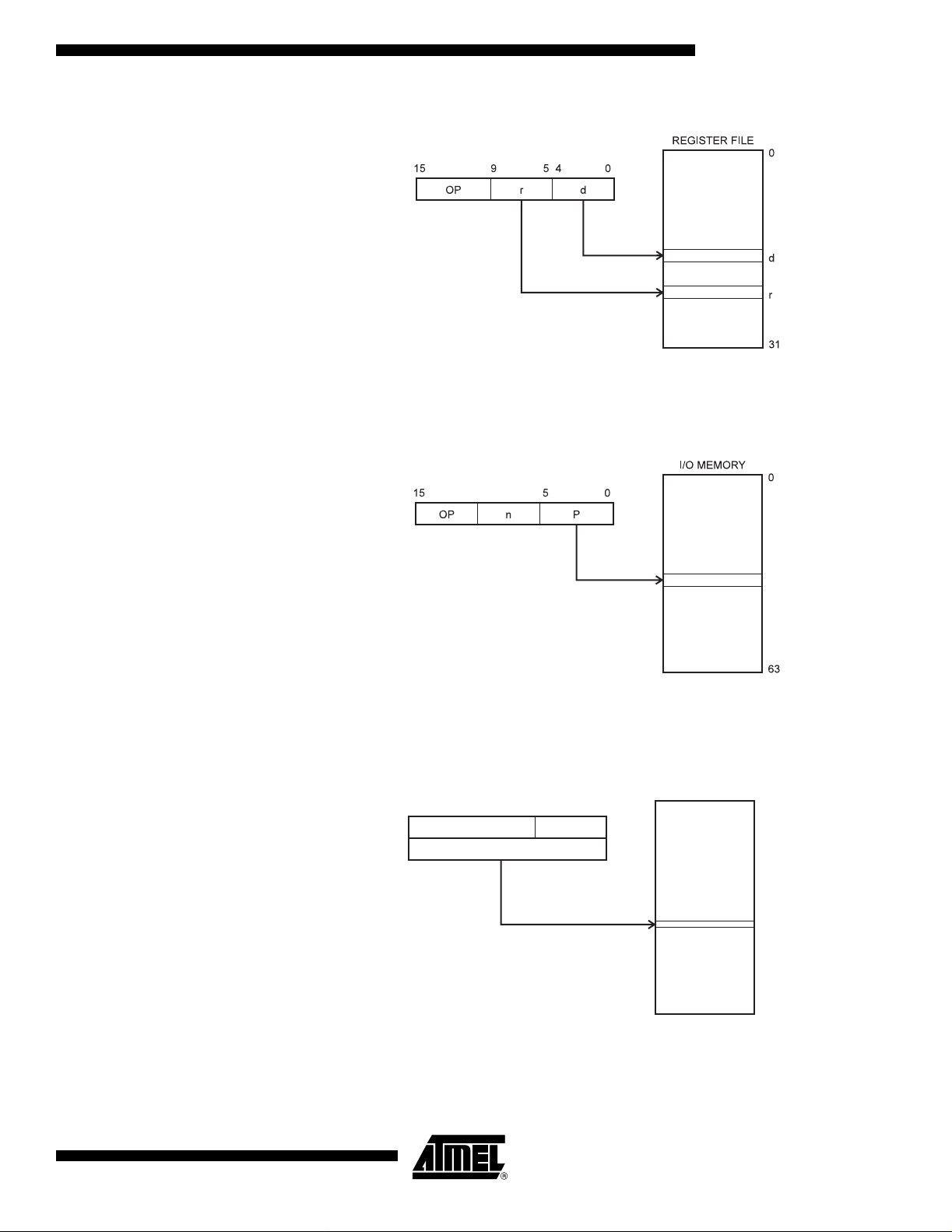

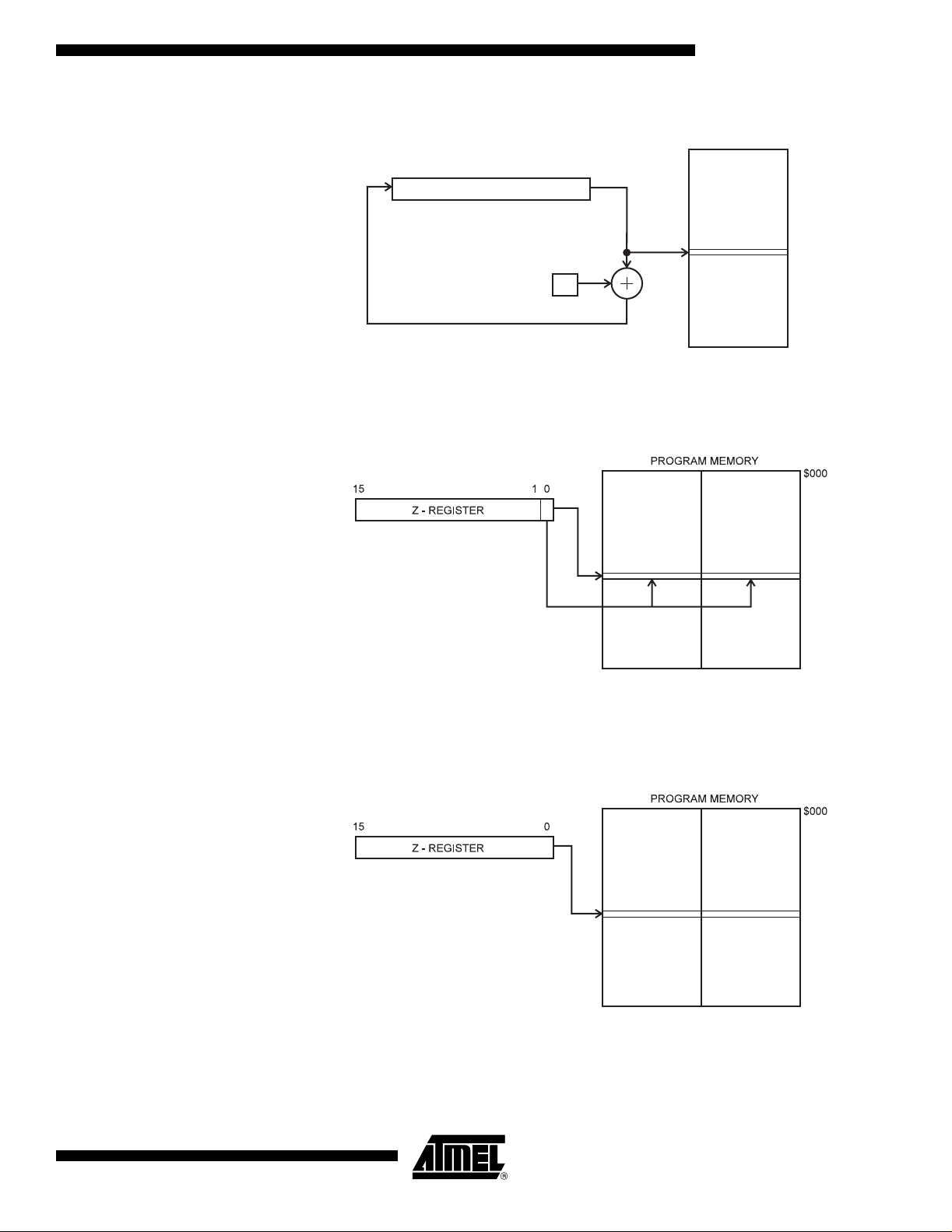

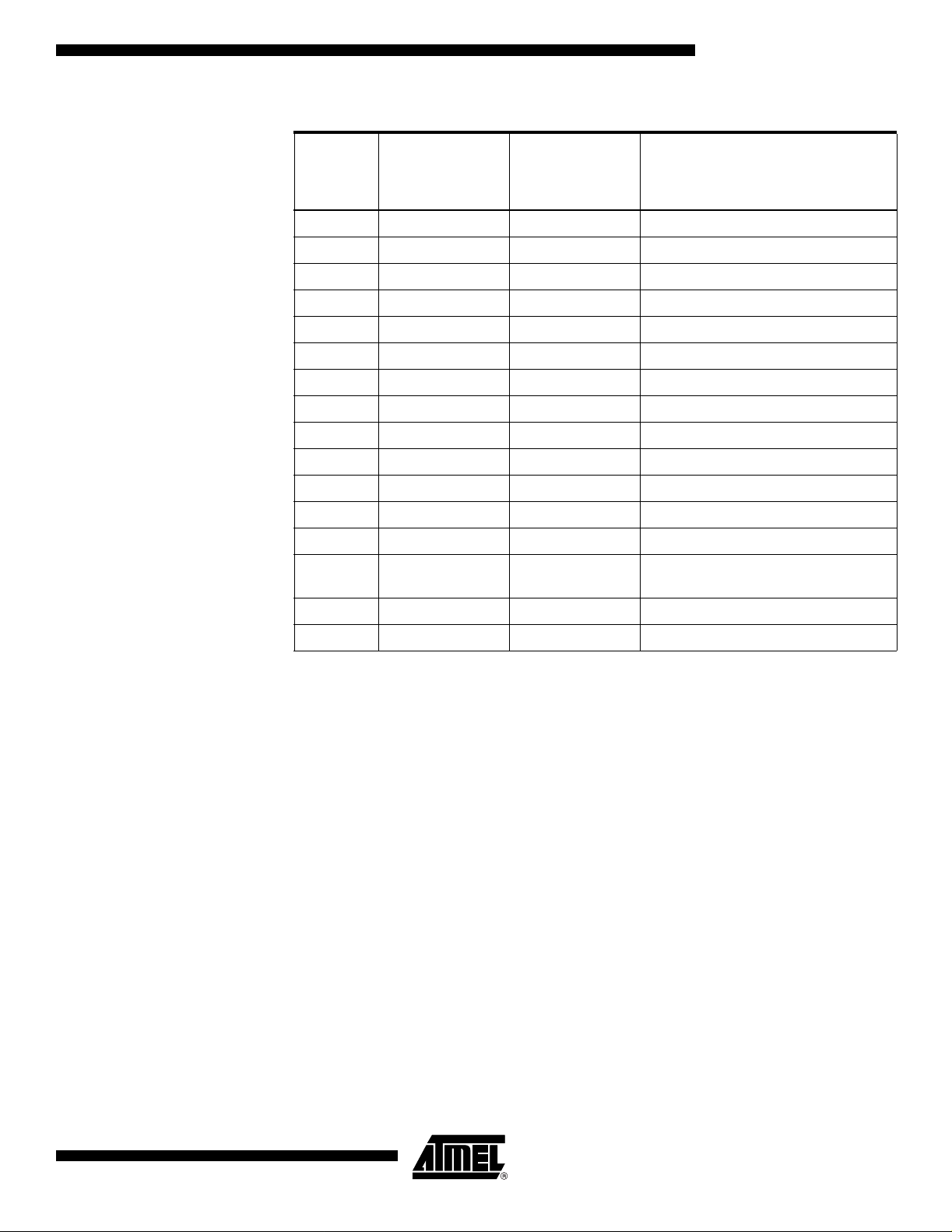

Figure 5. The ATmega163

8K X 16

Program

Memory

AVR

RISC Architecture

Program

Counter

Data Bus 8-bit

Status

and Control

Interrupt

Unit

SPI

Unit

Instruction

Register

Instruction

Decoder

Control Lines

Direct Addressing

Indirect Addressing

32 x 8

General

Purpose

Registrers

ALU

1024 x 8

Data

SRAM

512 x 8

EEPROM

32

I/O Lines

Serial

UART

Two-wire Serial

Interface

8-bit

Timer/Counter

16-bit

Timer/Counter

with PWM

8-bit

Timer/Counter

with PWM

Watchdog

Timer

A/D Converter

Analog

Comparator

The AVR use s a Harvard architecture concept – with separate me mories and bus es f or

program and data. The Program memory is executed with a two stage pipeline. While

one instru ction is bei ng execu ted, the nex t inst ruction i s pre -fetche d from the P rogram

memory. This concept enables instructions to be executed in every clock cycle. The

Program memory is In-System Re-programmable Flash memory.

With the jump and call instructions, the whole 8K word address space is directly

accessed. Most AVR instructions have a single 16-bit word format. Every program

memory address contains a 16- or 32-bit instruction.

Program Flash memory space is divided in two sections, the Boot Program section (256

to 2,048 bytes, see page 134) and the A ppli cation P rogram se ction. Bot h sec tions hav e

dedicated Lo ck bits for write a nd re ad/write pr otection . The SPM in struct ion that wr ites

into the Application Flash memory section is allowed only in the Boot Program section.

During interrupts and subroutine calls, the return address Program Counter (PC) is

stored on the Stack. The Stack is effectively allocated in the general data SRAM, and

consequently the S tack si ze is onl y limited by the total SRAM size and the usage of t he

SRAM. All user programs mus t initialize the SP in the reset routine (before sub routines

or interrupts are execu ted). T he 11-bi t Stack Pointer S P is read/ write acc essibl e in the

I/O s pace.

8

ATmega163(L)

1142E–AVR–02/03

Page 9

ATmega163(L)

The 1,024 bytes data SRAM can be easily accessed through the five different addressing modes supported in the AVR architecture.

The memory spaces in the AVR

A flexible inte rrupt modu le has its Cont rol Reg isters in the I/O space wi th an addi tional

Global Interrupt Enable bit in the Status Register. All interrupts have a separate Interrupt

Vector in the Interrupt Vector table at the beginni ng of the Program m emory. The interrupts have priority in accordance with their Inte rrupt Vector position. The lower the

Interrupt Vector address, the higher the priority.

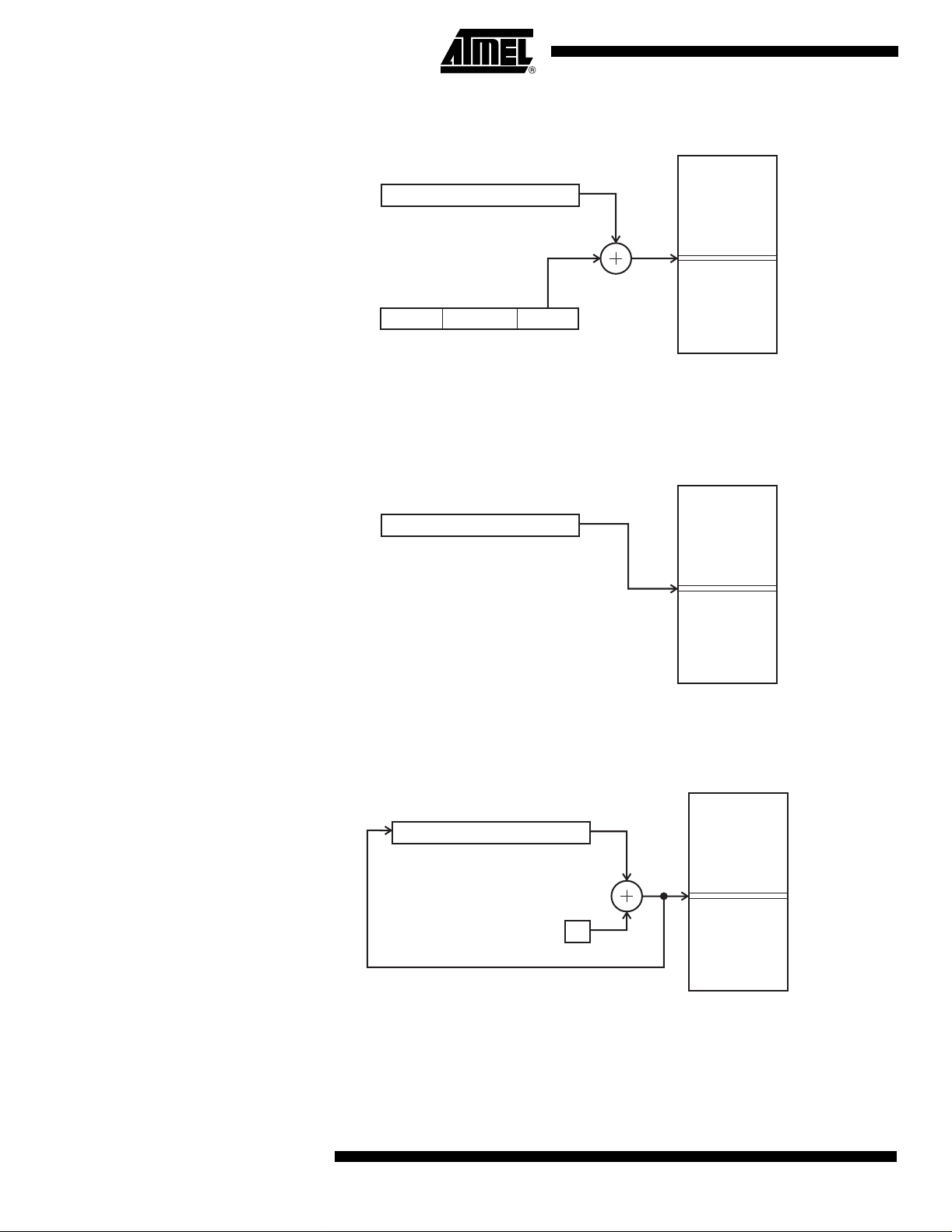

Figure 6. Memory Maps

architecture are all linear and regular memory maps.

Program Memory

$0000

Application Flash Section

Boot Flash Section

$1FFF

1142E–AVR–02/03

9

Page 10

The General Purpose Register File

Figure 7 shows the structure of the 32 general purpose working registers in the CPU.

Figure 7. AVR CPU General Purpose Working Registers

7 0 Addr.

R0 $00

R1 $01

R2 $02

…

R13 $0D

General R14 $0E

Purpose R15 $0F

Working R16 $10

Registers R17 $11

…

R26 $1A X-register Low Byte

R27 $1B X-register High Byte

R28 $1C Y-register Low Byte

R29 $1D Y-register High Byte

R30 $1E Z-register Low Byte

R31 $1F Z-register High Byte

All the register operating instructions in the instruction set have direct and single cycle

access to all registers. The only excepti on is the five con stant arithme tic and logic

instructions SBCI, SU BI, CPI, AND I, and ORI betwee n a constan t and a regis ter, and

the LDI instruction for load immediate constant data. These instructions apply to the

second half of the registers in the Register File – R16..R31. The general SBC, SUB, CP,

AND, and OR and all other operations between two registers or on a single register

apply to the entire Register File.

The X-register, Y-register, and Z-register

As shown in F igu re 7, each register i s a lso assigned a data memory address, m appin g

them directly into the first 32 locations of the user Data Space. Although not being physically implemented as SRAM locations, this memory organization provides great

flexibility in access of the registers, as the X-, Y-, and Z-registers can be set to index any

register in the file.

The registers R26..R31 have some added functions to their general purpose usage.

These registers are address pointers for indirect addressing of the Data Space. The

three indirect address registers X, Y, and Z are defined as:

Figure 8. The X-, Y-, and Z-registers

15 XH XL 0

X - register 7 0 7 0

R27 ($1B) R26 ($1A)

15 YH YL 0

Y - register 7 0 7 0

R29 ($1D) R28 ($1C)

15 ZH ZL 0

Z - register 7 0 7 0

R31 ($1F) R30 ($1E)

10

ATmega163(L)

1142E–AVR–02/03

Page 11

ATmega163(L)

In the diff erent addr essi ng mo des t hese ad dre ss re gister s have f unct ions a s fixe d displacement, automatic increment and decrement (see the descriptions for the different

instructions).

The ALU – Arithmetic Logic U nit

The high-performance AVR ALU operates in direct connection with all the 32 general

purpose working reg isters. Within a single clock cycl e, ALU operations between registers in the Re gis ter File are exe cuted . The A LU ope rati ons are d ivided int o three m ain

categories – arithmetic, logical, and bit-functions. ATm ega163 also provi des a powerful

multiplier sup porting both s igne d/unsigned mult iplication an d fractiona l form at. See the

Instruction Set section for a detailed description.

The In-System SelfProgrammable Flash

Program Memory

The ATme ga163 c ontains 16K bytes On -chip In-Sy stem Self-Pro gramm able Flas h

memory for program storage. Since all instructions are 16- or 32-bit words, the Flash is

organized as 8K x 16. The Flash Program memory space is divided in two sections,

Boot Program section and Application Progra m section.

The Flash memory has an endurance of at least 1,000 write/erase cycles. The

ATmega163 Prog ram Count er (PC) is 13 bits wide, thus address in g the 8,192 Program

Memory locations. The operation of Boot Program section and associated Boot Lock

bits for software protection are described in detail on page 134. See also page 154 for a

detailed description on Flash data serial downloading.

Constant tables can be allocated within the entire Program Memory address space (see

the LPM – Load Program Memory instruction description).

See also page 12 for the different Program Memory Addressing modes.

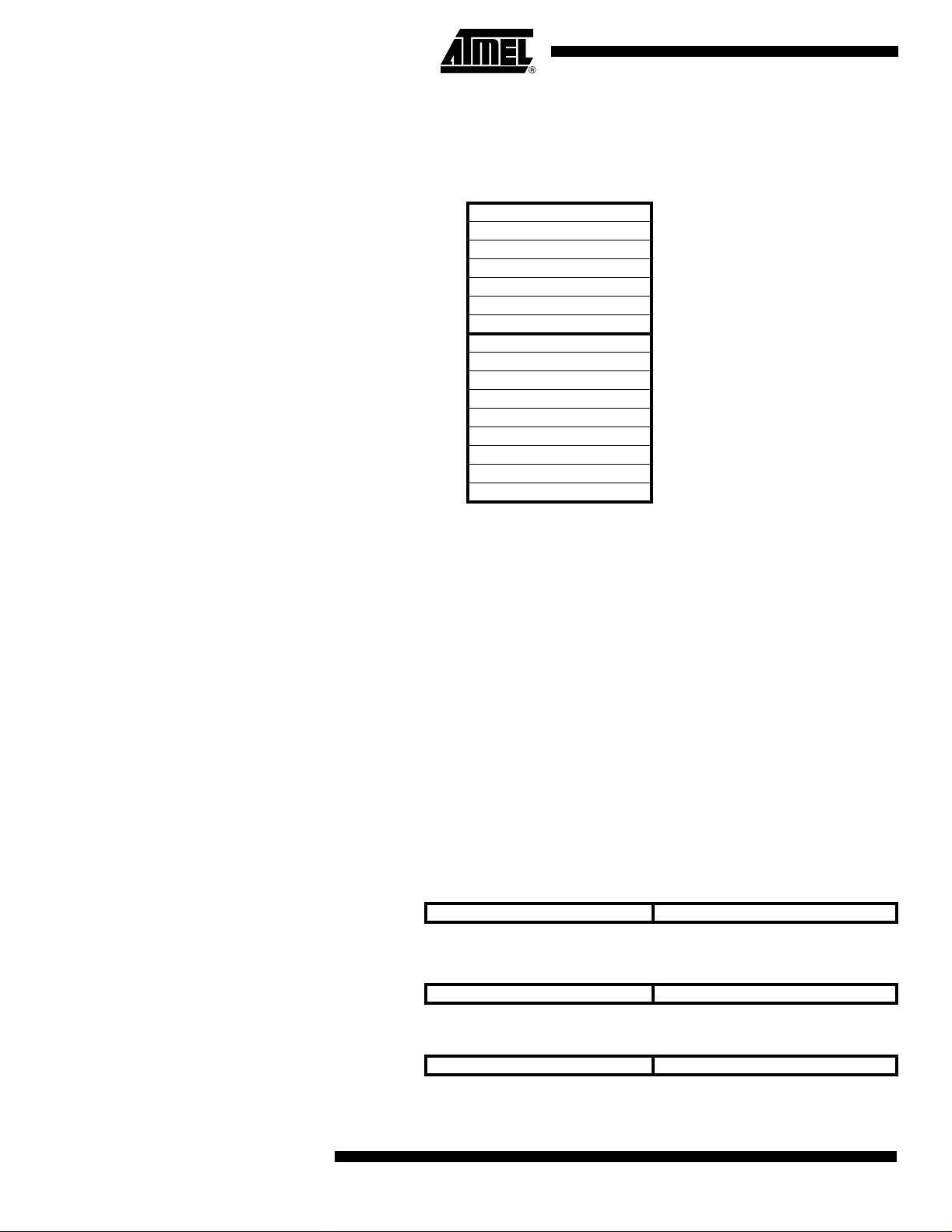

The SRAM Data Memory F igure 9 shows how the ATmega163 SRAM Mem ory is organized.

Figure 9. SRAM Organization

Register File

R0

R1

R2

...

R29

R30

R31

I/O Registers

$00

$01

$02

...

$3D

$3E

$3F

Data Address Space

$0000

$0001

$0002

...

$001D

$001E

$001F

$0020

$0021

$0022

...

$005D

$005E

$005F

Internal SRAM

$0060

$0061

...

$045E

$045F

1142E–AVR–02/03

11

Page 12

The lower 1,120 Data Memory locations address the Register File, the I/O Memory, and

the internal data SR AM. The first 96 loc ations addres s the Register F ile + I/O Memory,

and the next 1,024 locations address the internal data SRAM.

The five different addressing modes for the data memory cover: Direct, Indirect with Displacement, In direc t, Indirect with Pr e-decr emen t, and Ind irect w ith Pos t-increm ent. In

the Register F ile, registers R26 t o R31 feature the indirect Addre ssing Pointer

Registers.

The direct addressing reaches the entire data space.

The Indirect with Displacement mode features a 63 address locations reach from the

base address given by the Y- or Z-register.

When using register indirect addressing modes with automatic pre-decrement and post-

increment, the address registers X, Y, and Z are decremented and incremented.

The 32 general purpose working registers, 64 I/O Registers, and the 1,024 bytes of

internal data S RAM i n the ATme ga163 are a ll acce ssib le throu gh all thes e addre ssin g

modes.

The Program and Data Addressing Modes

Register Direct, Single Register Rd

The AT meg a163 AVR E nha nce d RIS C mic roco ntro ller s uppor ts po wer ful and effi cient

addressing modes for access to the Program Memory (Flash) and Data Memory

(SRAM, Register File, and I/O Memory). This section des cribes t he different ad dressing

modes supported by the AVR architecture. In the figures, OP means the operation code

part of the instruction word. To simplify, not all figures show the exact location of the

addressing bits.

Figure 10. Direct Single Register Addressing

The operand is contained in register d (Rd).

12

ATmega163(L)

1142E–AVR–02/03

Page 13

ATmega163(L)

Register Direct, Two Registers

Figure 11. Direct Register Addressing, Two Registers

Rd And Rr

Operand s ar e co ntain ed i n regi ster r (Rr) a nd d (Rd) . Th e resu lt is stor ed i n regis ter d

(Rd).

I/O Direct Figure 12. I/O Direct Addressing

Operand address is contained in 6 bits of the instruction word. n is the destination or

source register address.

Data Direct Figure 13. Direct Data Addressing

31

OP Rr/Rd

16 LSBs

15 0

20 19

A 16-bit Data Address is contained in the 16 LSBs of a two-word instruction. Rd/Rr

specify the destination or source register.

1142E–AVR–02/03

Data Space

16

$0000

$045F

13

Page 14

Data Indirect with Displacement

Figure 14. Data Indirect with Displacement

15

Y OR Z - REGISTER

0

Data Space

$0000

15

OP an

Operand address is the result of the Y- or Z-register contents added to the address contained in 6 bits of the instruction word.

Data Indirect Figure 15. Data Indirect Addressing

X, Y OR Z - REGISTER

Operand address is the contents of the X-, Y-, or the Z-register.

05610

$045F

Data Space

015

$0000

$045F

Data Indirect with Predecrement

14

ATmega163(L)

Figure 16. Data Indirect Addressing with Pre-decrement

Data Space

015

X, Y OR Z - REGISTER

-1

$0000

$045F

The X-, Y -, or th e Z-reg ister is decre ment ed be fore the opera tio n. Opera nd address is

the decremented contents of the X-, Y-, or the Z-register.

1142E–AVR–02/03

Page 15

ATmega163(L)

Data Indirect with Postincrement

Constant Addressing Using The LPM and SPM Instructions

Figure 17. Data Indirect Addressing with Post-increment

Data Space

015

X, Y OR Z - REGISTER

1

$0000

$045F

The X-, Y-, or the Z-register is incremented after the operation. Operand address is the

content of the X-, Y-, or the Z-register prior to incrementing.

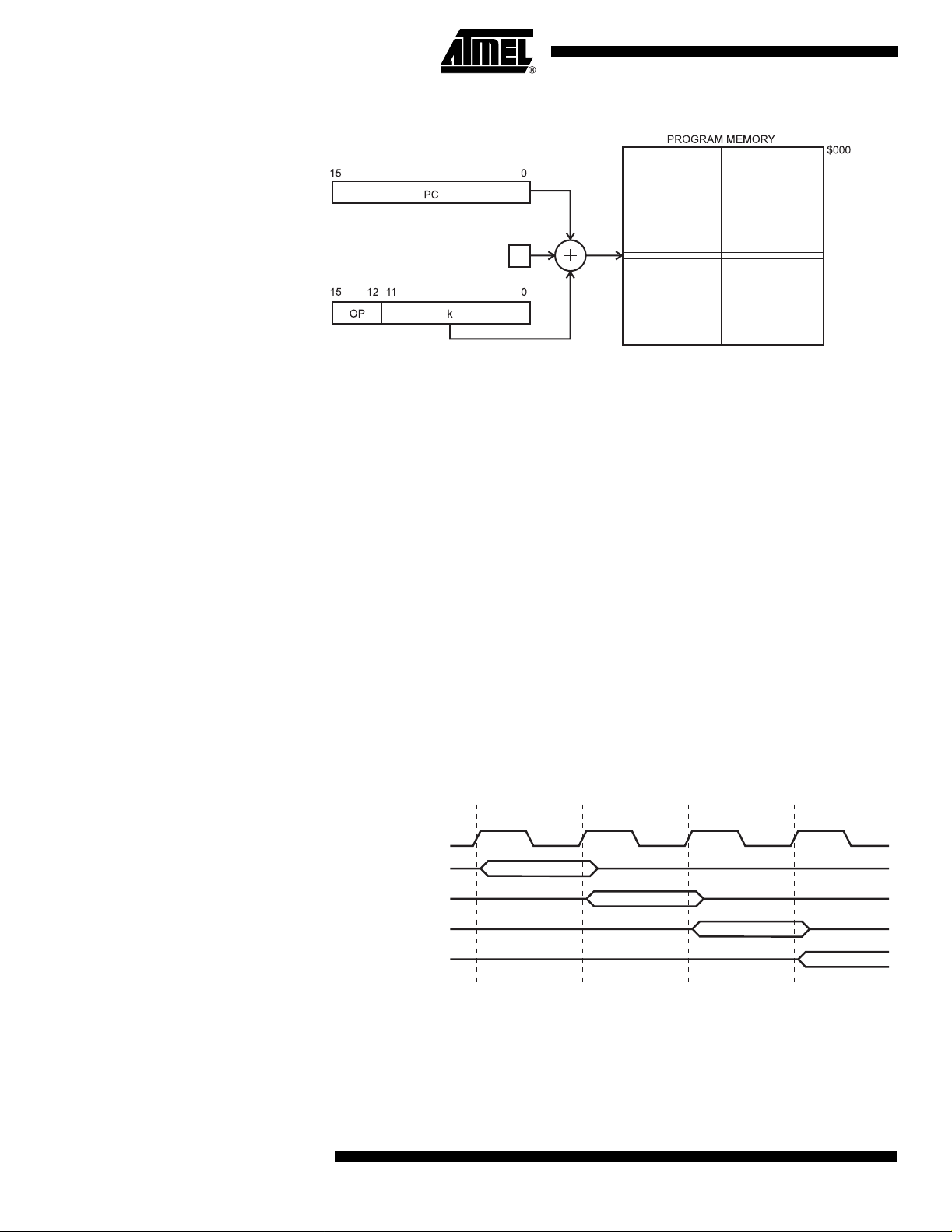

Figure 18. Code Mem ory C onstant Addressin g

Indirect Program Addressing, IJMP and ICALL

$1FFF

Constant byte address is specified by the Z-register contents. The 15 MSBs select word

address (0 - 8K). For LPM, the LSB selects Low Byte if cleared (LSB = 0) or High Byte if

set (LSB = 1). For SPM, the LSB should be cleared.

Figure 19. Indirect Program Memory Addressing

$1FFF

Program execution continues at address contained by the Z-register (i.e., the PC is

loaded with the contents of the Z-register).

1142E–AVR–02/03

15

Page 16

Relative Program Addressing, RJMP and RCALL

Figure 20. Relative Program Memory Addressing

1

$1FFF

Program execution continues at address PC + k + 1.

The relative address k is from -2,048 to 2,047.

The EEPROM Data Memory

Memory Access Times and Instruction Execution Timing

The ATmega163 contains 512 bytes of data EEPROM memory. It is or g anized as a se p arate data space, in which single bytes can be read and written. The EEPROM has an

endurance of at least 100,000 write/erase cycles. The access between the EEPROM

and the CPU is described on page 62 specifying the EEPROM Address Registers, the

EEPROM Data Registe r, and the EEPROM Control Register.

For the SPI data downloading, see page 154 for a detailed description.

This section describes the general ac cess timing co ncepts for in struction ex ecut ion a nd

internal memory access.

The AVR CPU is driven by the System Clock Ø, directly generated from the main Os cillator for the chip. No internal clock division is used.

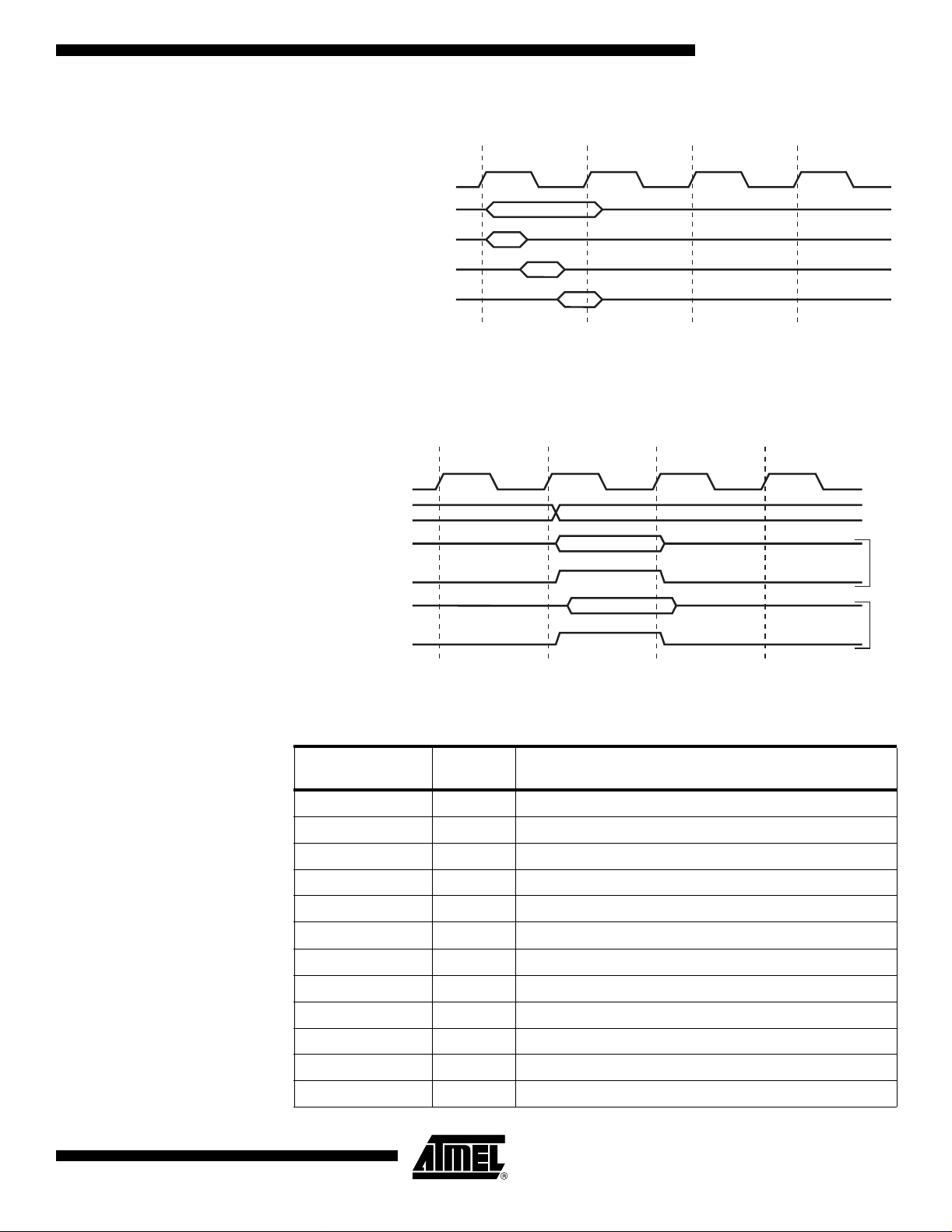

Figure 21 s hows t he pa ralle l instru ctio n fetch es a nd ins truct ion e xecu tions enab led b y

the Harvard architecture and the fast-access Register File concept. This is the basic

pipelining concept to obtain up to 1 MIPS per MHz with the corresponding unique results

for functions per cost, functions per clocks, and functions per power-unit.

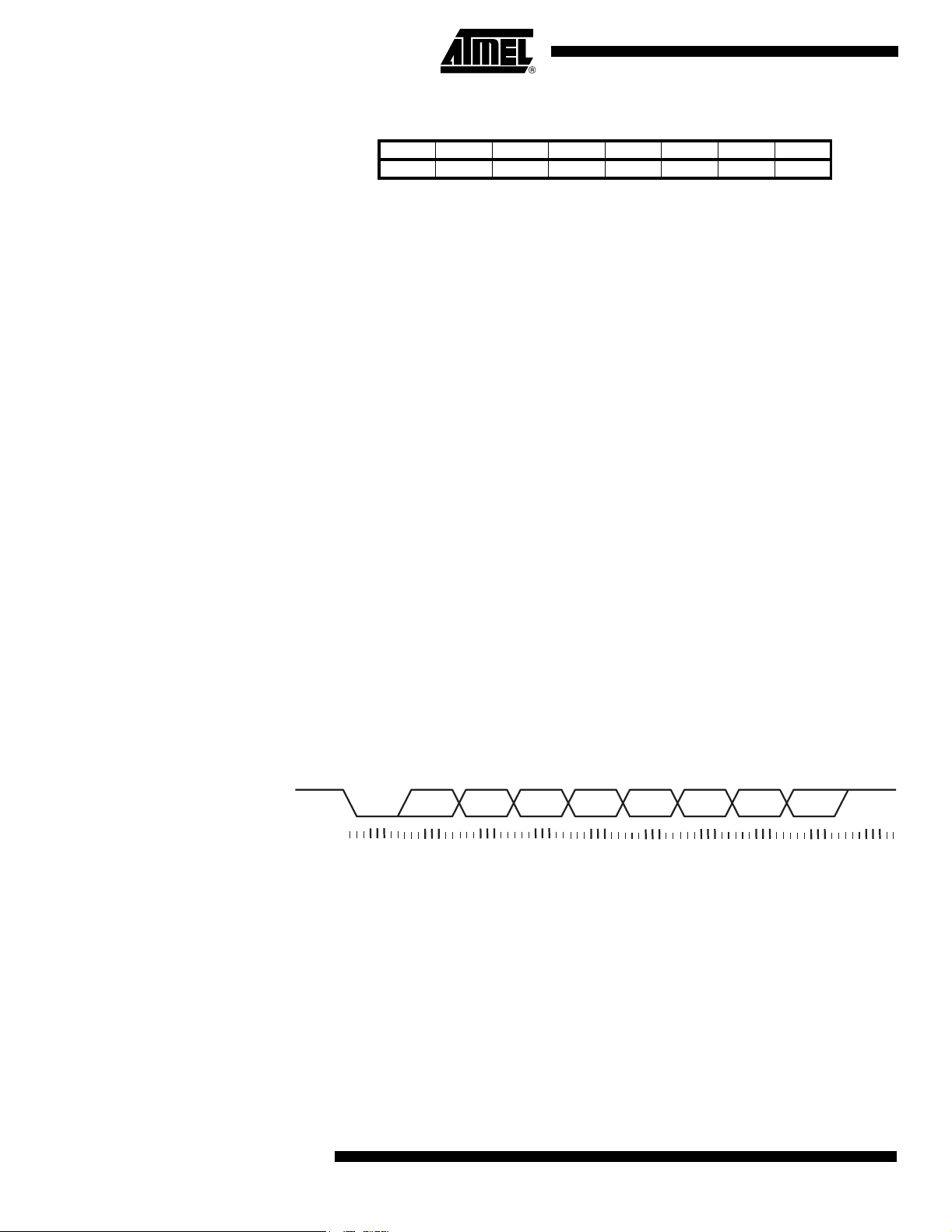

Figure 21. The Parallel Instruction Fetches and Instruction Executions

T1 T2 T3 T4

System Clock Ø

1st Instruction Fetch

1st Instruction Execute

2nd Instruction Fetch

2nd Instruction Execute

3rd Instruction Fetch

3rd Instruction Execute

4th Instruction Fetch

16

Figure 22 shows the internal timing conc ept f or the Regist er F ile. In a singl e clock cy cle

an ALU operation using two register operands is executed, and the result is stored back

to the destination register.

ATmega163(L)

1142E–AVR–02/03

Page 17

ATmega163(L)

Figure 22. Single Cycle ALU Operation

T1 T2 T3 T4

System Clock Ø

Total Execution Time

Register Operands Fetch

ALU Operation Execute

Result Write Back

The internal data SR AM access is pe rformed in tw o System Cl ock cycles as des cribed

in Figure 23.

Figure 23. On-chip Data SRAM Access Cycles

T1 T2 T3 T4

System Clock Ø

Address

Data

WR

Data

RD

Prev. Address

Address

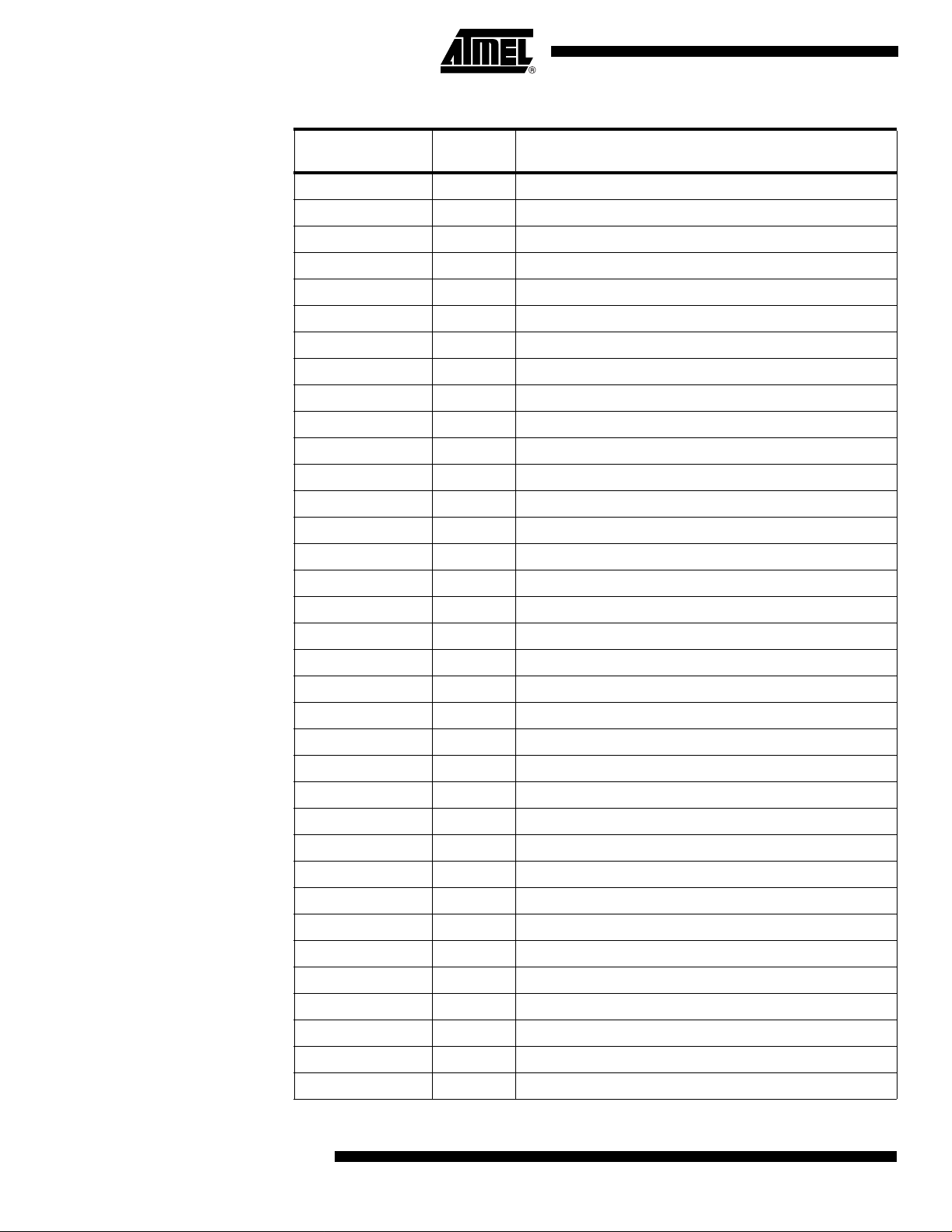

I/O Memory The I/O space definition of the ATmega163 is shown in the following table:

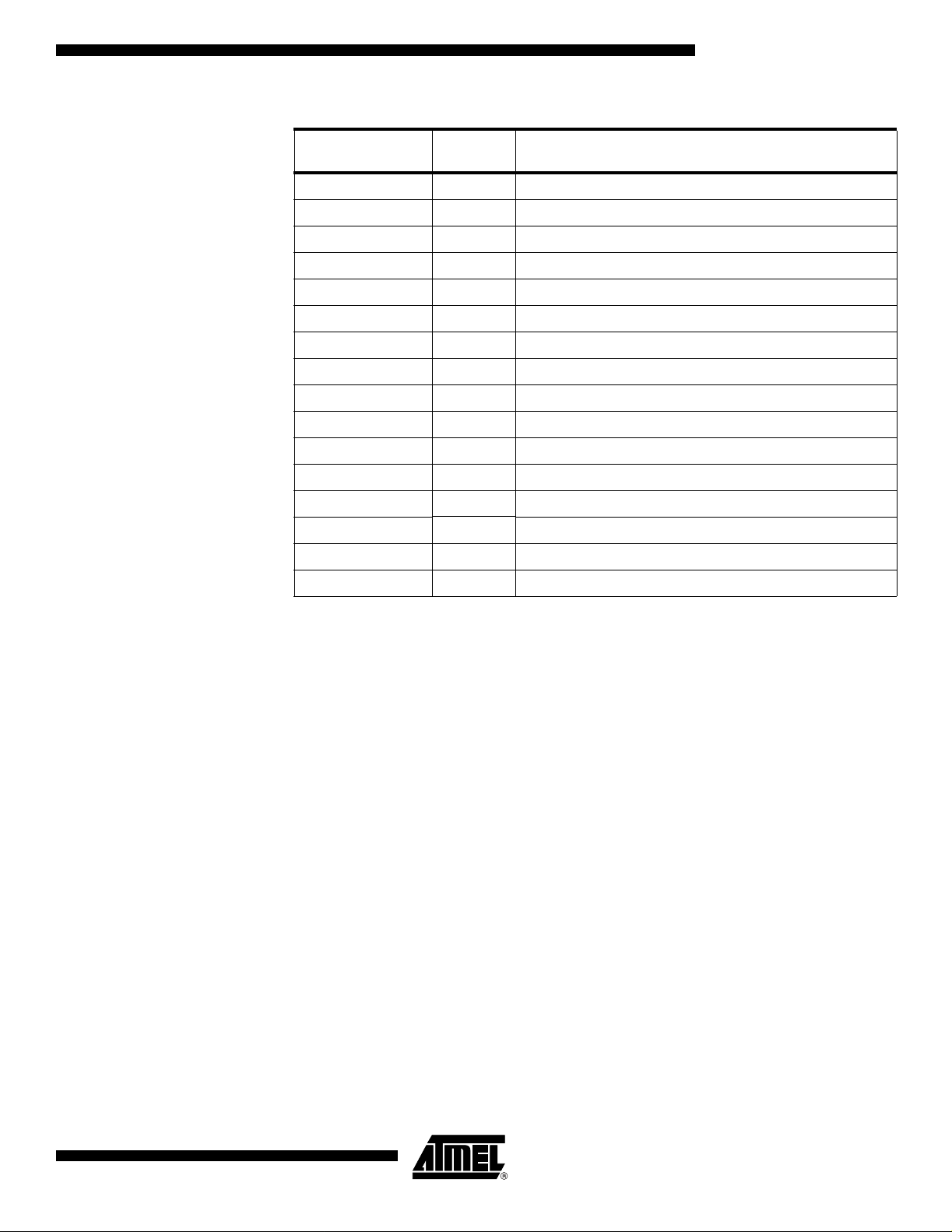

Table 2. ATmega163 I/O Space

I/O Address

(SRAM Address) Name Function

$3F ($5F) SREG Status REGister

$3E ($5E) SPH Stack Pointer High

$3D ($5D) SPL Stack Pointer Low

$3B ($5B) GIMSK General Interrup t MaSK Regis ter

$3A ($5A) GIFR General Interrupt Flag Register

$39 ($59) TIMSK Timer/Counter Int errupt MaSK Register

$38 ($58) TIFR Timer/Counter Interrupt Flag Register

(1)

Write

Read

1142E–AVR–02/03

$37 ($57) SPMCR SPM Control Register

$36 ($56) TWCR Two-wire Serial Interface Control Register

$35 ($55) MCUCR MCU general Control Register

$34 ($54) MCUSR MCU general Status Register

$33 ($53) TCCR0 Timer/Counter0 Cont rol Register

17

Page 18

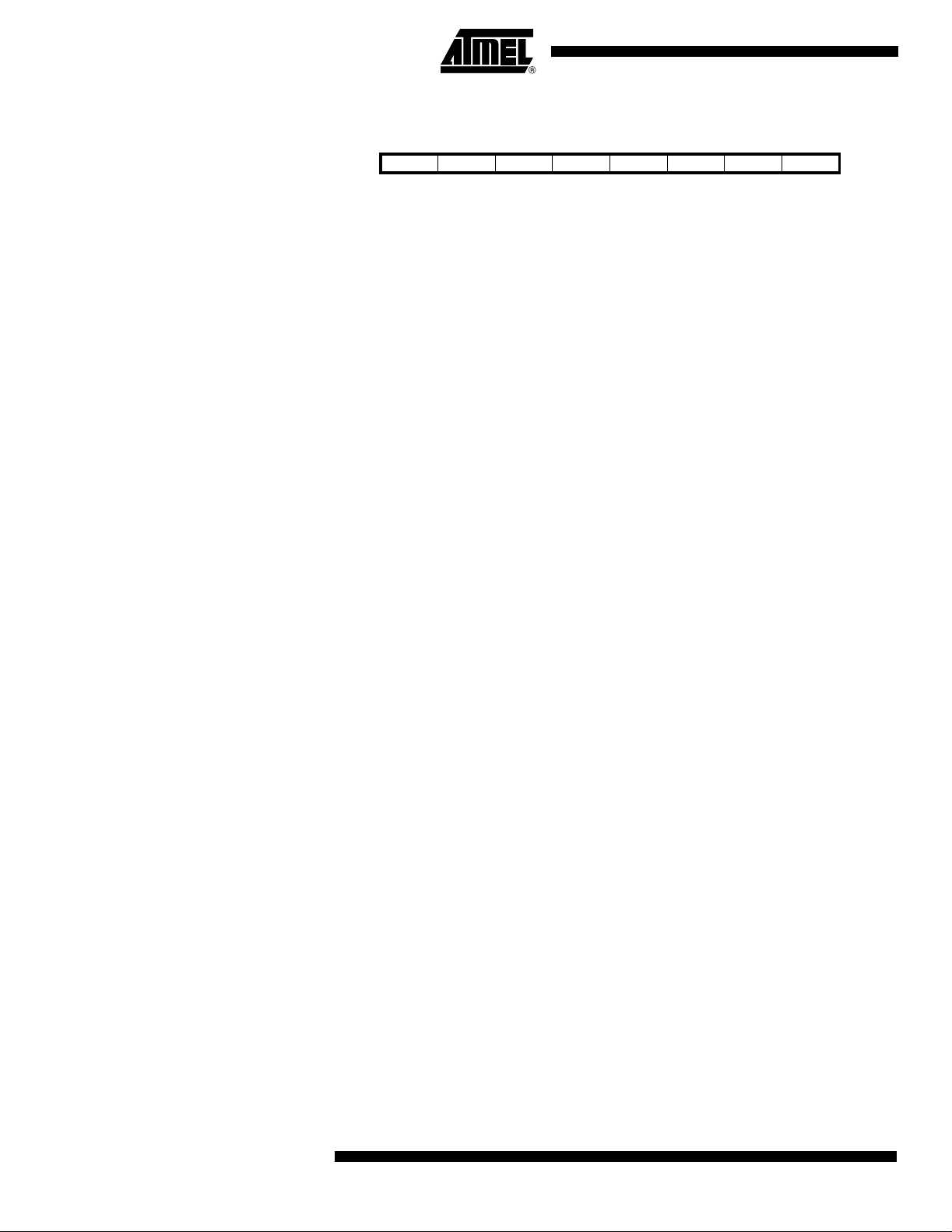

Table 2. ATmega163 I/O Space (Continued)

I/O Address

(SRAM Address) Name Function

$32 ($52) TCNT0 Timer/Counter0 (8-bit)

$31 ($51) OSCCAL Oscillator Calibration Register

$30 ($50) SFIOR Special Function I/O Register

$2F ($4F) TCCR1A Timer/Counter1 Control Register A

$2E ($4E) T CCR1B Timer/Counter1 Control Register B

$2D ($4D) TCNT1H Timer/Counter1 Hig h-byte

$2C ($4C) TCNT1L Timer /Counter1 Low-byte

$2B ($4B) OCR1AH Timer/Counter1 Output Compare Register A High-byte

$2A ($4A) OCR1AL Timer/Counter1 Output Compare Register A Low-byte

$29 ($49) OCR1BH Timer/Counter1 Output Compare Regis ter B High-byte

$28 ($48) OCR1BL Timer/Counter1 Output Compare Regis ter B Low-byte

$27 ($47) ICR1H T/C 1 Input Capture Register High-byte

$26 ($46) ICR1L T/C 1 Input Capture Register Low-byte

$25 ($45) TCCR2 Timer/Counter2 Cont rol Register

$24 ($44) TCNT2 Timer/Counter2 (8-bit)

(1)

$23 ($43) OCR2 Timer/Coun ter 2 O utput Compare Register

$22 ($42) ASSR Asynchronous Mode Status Regi ster

$21 ($41) WDTCR Watchdog Timer Control Register

$20 ($40) UBRRHI UART Baud Rate Register High-byte

$1F ($3F) EEARH EEPROM Address Register High-byte

$1E ($3E) EEARL EEPROM Address Register Low-byte

$1D ($3D) EEDR EEPROM Data Register

$1C ($3C) EECR EEPROM Control Register

$1B ($3B) PORTA Data Register, Port A

$1A ($3A) DDRA Data Direction Regi ster, Port A

$19 ($39) PINA Input Pins, Port A

$18 ($38) PORTB Data Register, Port B

$17 ($37) DDRB Data Direction Register, Port B

$16 ($36) PINB Input Pins, Port B

$15 ($35) PORTC Data Regist er, Port C

$14 ($34) DDRC Data Direction Register, Port C

$13 ($33) PINC Input Pins, Port C

$12 ($32) PORTD Data Regist er, Port D

18

$11 ($31) DDRD Data Direction Register, Port D

$10 ($30) PIND Input Pins, Port D

ATmega163(L)

1142E–AVR–02/03

Page 19

ATmega163(L)

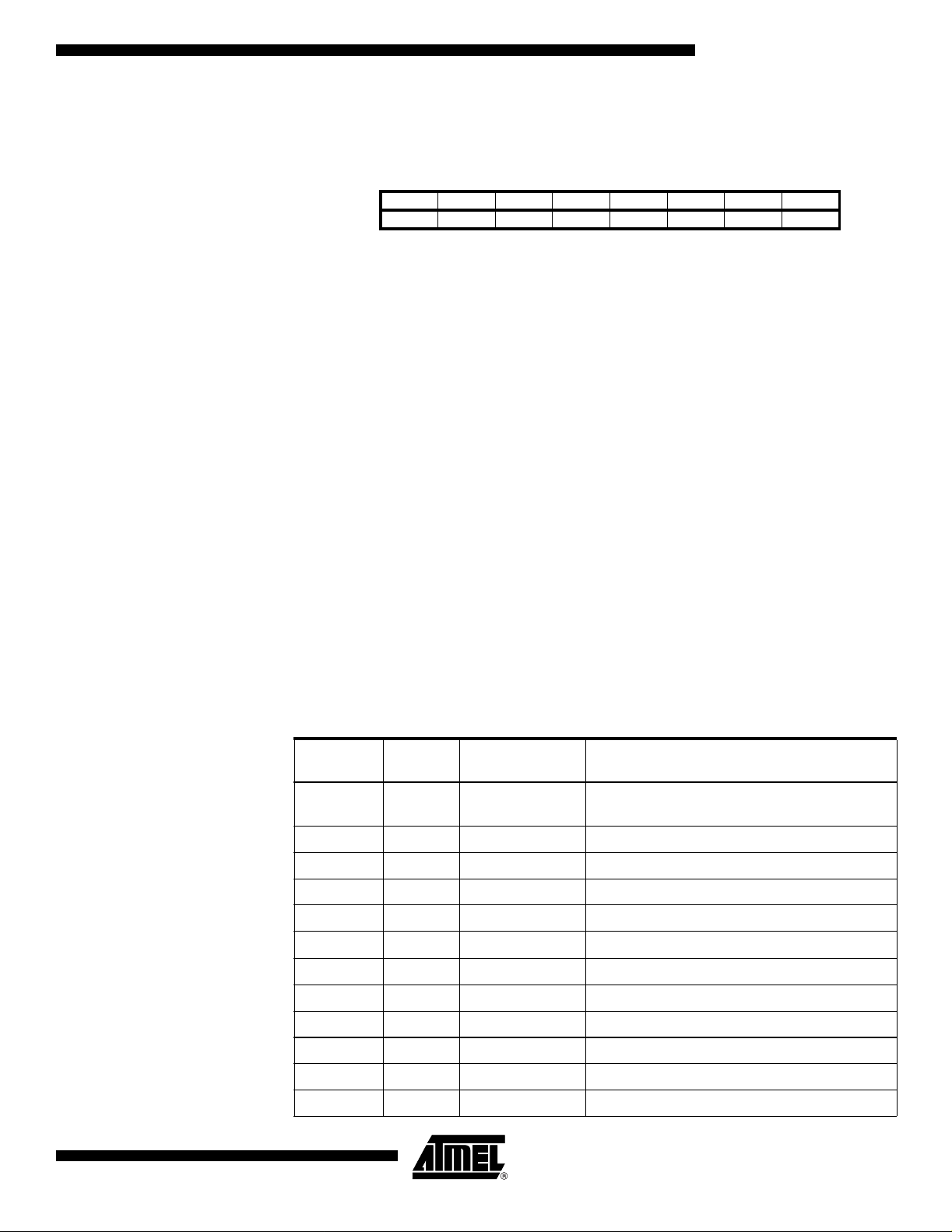

Table 2. ATmega163 I/O Space (Continued)

I/O Address

(SRAM Address) Name Function

$0F ($2F) SPDR SPI I/O Data Register

$0E ($2E) SPSR SPI Status Register

$0D ($2D) SPCR SPI Control Register

$0C ($2C) UDR UART I/O Data Register

$0B ($2B) UCSRA UART Control and Status Register A

$0A ($2A) UCSRB UART Control and Status Register B

$09 ($29) UBRR UART Baud Rate Register

$08 ($28) ACSR Analog Comparator Control and Status Register

$07 ($27) ADMUX ADC Multiplexer Selec t Regi ster

$06 ($26) ADCSR ADC Control and Status Regist er

$05 ($25) ADCH ADC Data Register High

$04 ($24) ADCL ADC Data Register Low

$03 ($23) TWDR Two-wire Serial Interface Data Register

$02 ($22) TWAR Two-wire Serial Interface (Slave) Address Register

$01 ($21) TWSR Two-wire Ser ial Interface Status Regist er

(1)

$00 ($20) TWBR Two-wire Ser ial Interface Bit Rate Register

Note: 1. Reserved and unused locations are not shown in the table.

All ATmega163 I /Os and peripheral s are place d in the I/O space. The I/O locatio ns are

accessed by the IN and OUT instructions, transferring data between the 32 general purpose working registers and the I/O space. I/O Registers within the address range $00 -

$1F are directly bit-accessible using the SBI and CBI instructions. In these registers,

the value of single bits can be checked by using the SBIS and SB IC instructions. Refer

to the instruction set chapter for more details. When using the I/O specific commands IN

and OUT, the I/O addresses $00 - $3F must be used. When addressing I/O Registers as

SRAM, $ 20 mu st be a dded to t hese ad dre sses. A ll I/O Re giste r address es t hrough out

this document are shown with the SRAM address in parentheses.

For compatibility with future devices, reserved bits should be written to zero if accessed.

Reserved I/O memory addresses should never be written.

Some of the Status Flags are cleared by writing a logical one to them. Note that the CBI

and SBI instru ctio ns wi ll op erate o n a ll bits i n th e I/O Regi ster , writin g a on e b ack in to

any Flag read as set, thus clearing the Flag. The CBI and SBI instructions work with registers $00 to $1F only.

The I/O and Peripherals Control Registers are explained in the following sections.

1142E–AVR–02/03

19

Page 20

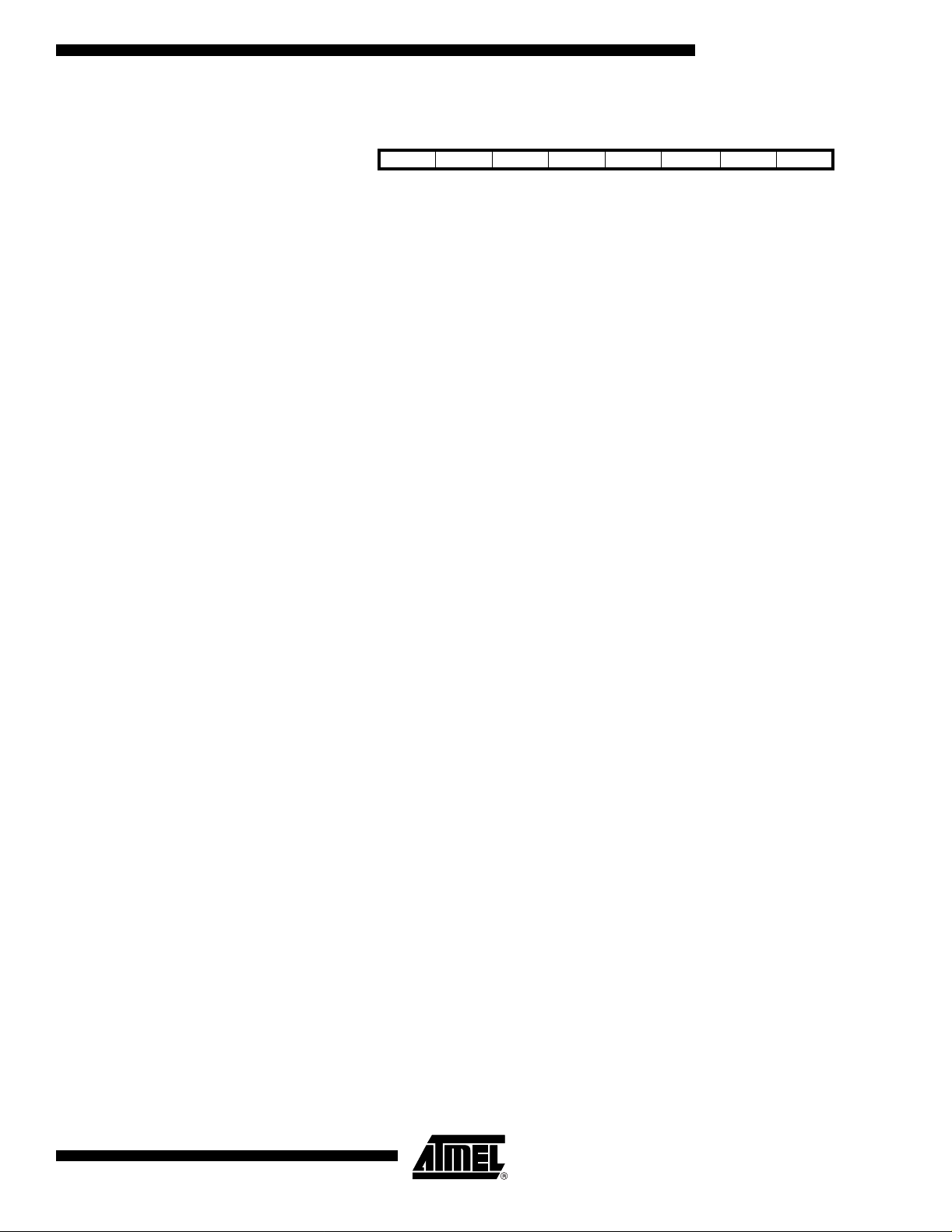

The Status Register – SREG The

Bit 76543210

$3F ($5F) I THSVNZCSREG

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial Value00000000

• Bit 7 – I: Global Interrupt Enable

The Glob al Inte rrupt En able b it must be set (on e) for the inte rrupts to be enab led. The

individu al i nterrup t ena ble c on trol is t hen perf orme d in th e In terrupt Ma sk Regi sters. If

the Global Interrupt Enable Register is cleared (zero), none of the interrupts are enabled

independent of the values of th e Interrupt Ma sk Registers. The I-bit is cleared by hardware after an interrupt ha s occurred, a nd is set by the RETI in struction to e nable

subsequent interrupts.

• Bit 6 – T: Bit Copy Storage

The Bit Co py instruc tions B LD (Bi t LoaD ) and BS T (Bit S Tore ) use th e T-bit a s sourc e

and destination for the operated bit. A bit from a register in the Register File can be copied into T by the BST instruction, and a bit in T can be copied into a bit in a register in the

Register File by the BLD instruction.

• Bit 5 – H: Half Carry Flag

The Half Carry Flag H indicates a half carry in some arithmetic operations. See the

Instruction Set Description for detailed information.

AVR

Status Register – SREG – at I/O space location $3F ($5F) is defined as:

• Bit 4 – S: Sign Bit, S = N

⊕ V

The S-bit is always an exclusive or between the Negative Flag N and the Two’s Complement Overflow Flag V. See the Instruction Set Description for detailed information.

• Bit 3 – V: Two’s Complement Overflow Flag

The Two ’s Com pleme nt O verf low Flag V su ppor ts t wo’s comp lem ent arith meti cs. S ee

the Instruction Set Description for detailed information.

• Bit 2 – N: Negative Flag

The Negative Flag N indicates a negative result in an arithmetic or logic operation. See

the Instruction Set Description for detailed information.

• B i t 1 – Z: Zer o Flag

The Zero Flag Z indicates a zero result in an arithmetic or logic op eration. See the

Instruction Set Description for detailed information.

• Bit 0 – C: Carry Flag

The Carry Flag C indicates a carry in an ari thmetic or logic operation. See the Instruction

Set Description for detailed information.

Note that the Status Register is not automatically stored wh en entering an in terrupt routine and restored when returning from an interrupt routine. This must be handled by

software.

20

ATmega163(L)

1142E–AVR–02/03

Page 21

ATmega163(L)

The Stack Pointer – SP The ATmega163 Stack Pointer is implemented as two 8-bit registers in the I/O space

location s $ 3E ($5E) an d $3 D ( $5D). As the A Tme g a163 data mem ory ha s $46 0 lo cations, 11 bits are used.

Bit 151413121110 9 8

$3E ($5E) – – – – – SP10 SP9 SP8 SPH

$3D ($5D) SP7 SP6 SP5 SP4 SP3 SP2 SP1 SP0 SPL

76543210

Read/Write R R R R R R/W R/W R/W

R/W R/W R/W R/W R/W R/W R/W R/W

Initial Value00000000

00000000

The Stack Pointer poi nts to the dat a S RA M Stack area where the Subrout ine and Interrupt Stacks are located. This Stack space in the data SRAM must be defined by the

program before any sub routine cal ls are executed or in terrupts are enabl ed. The Stack

Pointer must be set to point above $60. The Stack Pointer is decremented by one when

data is pushed ont o the Stack with the PUSH instruc tion, and it is dec remen ted by two

when the return address is pushed onto the Stack with subroutine call and interrupt. The

Stack Pointer is incremented by one when data is popped from the Stack with the POP

instruction, and it is incremented by two when data is popped from the Stack with return

from subroutine RET or return from interrupt RETI.

Reset and Interrupt Handling

The ATmega163 provides 17 different interrupt sources. Thes e interrupts and the separate Res et Vect or, ea ch have a separ ate Prog ram Vec tor in th e Prog ram Mem ory

space. All interrupts are assigned individual enable bits which must be set (one)

together with the I-bit in the Status Register in order to enable the interrupt.

The lowe st ad dres ses in the Pro gram M emo ry sp ace are au toma ticall y def ined as th e

Reset and Interrupt Vectors. Th e complete list of ve ctors is shown in Table 3. Th e list

also determines the priority level s of the different interrupts. The lower the add ress th e

higher is the priority level. RESET has the highe st priority, and next is INT 0 – the E xternal Interrupt Request 0, etc.

Table 3. Reset and Interrupt Vectors

Program

Vector No.

1 $000

2 $002 INT0 External Interrupt Request 0

3 $004 INT1 External Interrupt Request 1

4 $006 TIMER2 COMP Timer/Counter2 Compar e Ma tch

5 $008 TIMER2 OVF Timer/Counter2 Overflow

6 $00A TIMER1 CAPT Timer/Counter1 Capture Event

7 $00C TIMER1 COMPA Timer/Counter1 Compare Match A

Address Source Interrupt Definition

(1)

RESET

External Pin, Power -on Reset, Brown-out

Reset and Watchdog Reset

1142E–AVR–02/03

8 $00E TIMER1 COMPB Timer/Counter1 Compare Match B

9 $010 TIMER1 OVF Timer/Counter1 Overflow

10 $012 TIMER0 OVF Timer/Counter0 Overflow

11 $014 SPI, STC Serial Transfer Co mplete

12 $016 UART, RXC UART, Rx Complete

21

Page 22

Table 3. Reset and Interrupt Vectors (Continued)

Program

Vector No.

Address Source Interrupt Definition

13 $018 UART, UDRE UART Data Register Empty

14 $01A UART, TXC UART, Tx Complete

15 $01C ADC ADC Conversion Complete

16 $01E EE_RDY EEPROM Ready

17 $020 ANA_COMP Analog Comparator

18 $022 TWI Two-wire Serial Interface

Note: 1. When the BOOTRST Fuse is programmed, the device will jump to the Boot Loader

address at reset, see “Boot Loader Support” on page 134.

The most typical and general program setup f or the Reset and Interrupt Vector

Addresses in ATmega163 is:

Address Labels Code Comments

$000 jmp RESET ; Reset Handler

$002 jmp EXT_INT0 ; IRQ0 Handler

$004 jmp EXT_INT1 ; IRQ1 Handler

$006 jmp TIM2_COMP ; Timer2 Compare Handler

$008 jmp TIM2_OVF ; Timer2 Overflow Handler

$00a jmp TIM1_CAPT ; Timer1 Capture Handler

$00c jmp TIM1_COMPA ; Timer1 Compare A Handler

$00e jmp TIM1_COMPB ; Timer1 Compare B Handler

$010 jmp TIM1_OVF ; Timer1 Overflow Handler

$012 jmp TIM0_OVF ; Timer0 Overflow Handler

$014 jmp SPI_STC ; SPI Transfer Complete Handler

$016 jmp UART_RXC ; UART RX Complete Handler

$018 jmp UART_DRE ; UDR Empty Handler

$01a jmp UART_TXC ; UART TX Complete Handler

$01c jmp ADC ; ADC Conversion Complete Interrupt Handler

$01e jmp EE_RDY ; EEPROM Ready Handler

$020 jmp ANA_COMP ; Analog Comparator Handler

$022 jmp TWI ; Two-wire Serial Interface Interrupt Handler

;

$024 MAIN: ldi r16,high(RAMEND) ; Main program start

$025 out SPH,r16 ; Set stack pointer to top of RAM

$026 ldi r16,low(RAMEND)

$027 out SPL,r16

... ... ...

22

ATmega163(L)

1142E–AVR–02/03

Page 23

When the BOO TRS T Fuse is prog ramm ed and the Bo ot sec tion s ize se t to 512 bytes ,

the most ty pical and general program setu p for the Reset and Interrupt Vector

Addresses in ATmega163 is:

Address Labels Code Comments

$002 jmp EXT_INT0 ; IRQ0 Handler

... ... ...

$022 jmp TWI ; Two-wire Serial Interface Interrupt Handler

;

$024 MAIN: ldi r16,high(RAMEND) ; Main program start

$025 out SPH,r16 ; Set stack pointer to top of RAM

$026 ldi r16,low(RAMEND)

$027 out SPL,r16

$028 <instr> xxx

;

.org $1f00

$1f00 jmp RESET ; Reset Handler

Reset Sources T he ATm ega163 has fo ur sources of reset:

• Power-on Reset. The MCU is reset when the supply voltage is below the Power-on

Reset threshold (V

POT

).

• External Reset. The MCU is reset when a low level is present on the RESET

more than 500 ns.

• Watchdog Reset. The MCU is reset when the Watchdog Timer period expires and

the Watchdog is enabled.

• Brown-out Reset. The MCU is reset when the supply voltage V

Brown-out Reset threshold (V

BOT

).

During Reset, all I/O Registers are set to their initial values, and the program starts execution from address $000 (unless the BOOTRST Fuse is programmed, as explained

above). The instruction placed in this address location must be a JMP – absolute jump –

instruction to the reset handling routine. If the program never enables an interrupt

source, the Interrupt Vect ors are not u sed, and reg ular program code c an be pl aced at

these locations. The circuit diagram in Figure 24 shows the Reset Logic. Table 4 and

Table 5 define the timing and electrical parameters of the reset circuitry.

ATmega163(L)

pin for

is below the

CC

1142E–AVR–02/03

23

Page 24

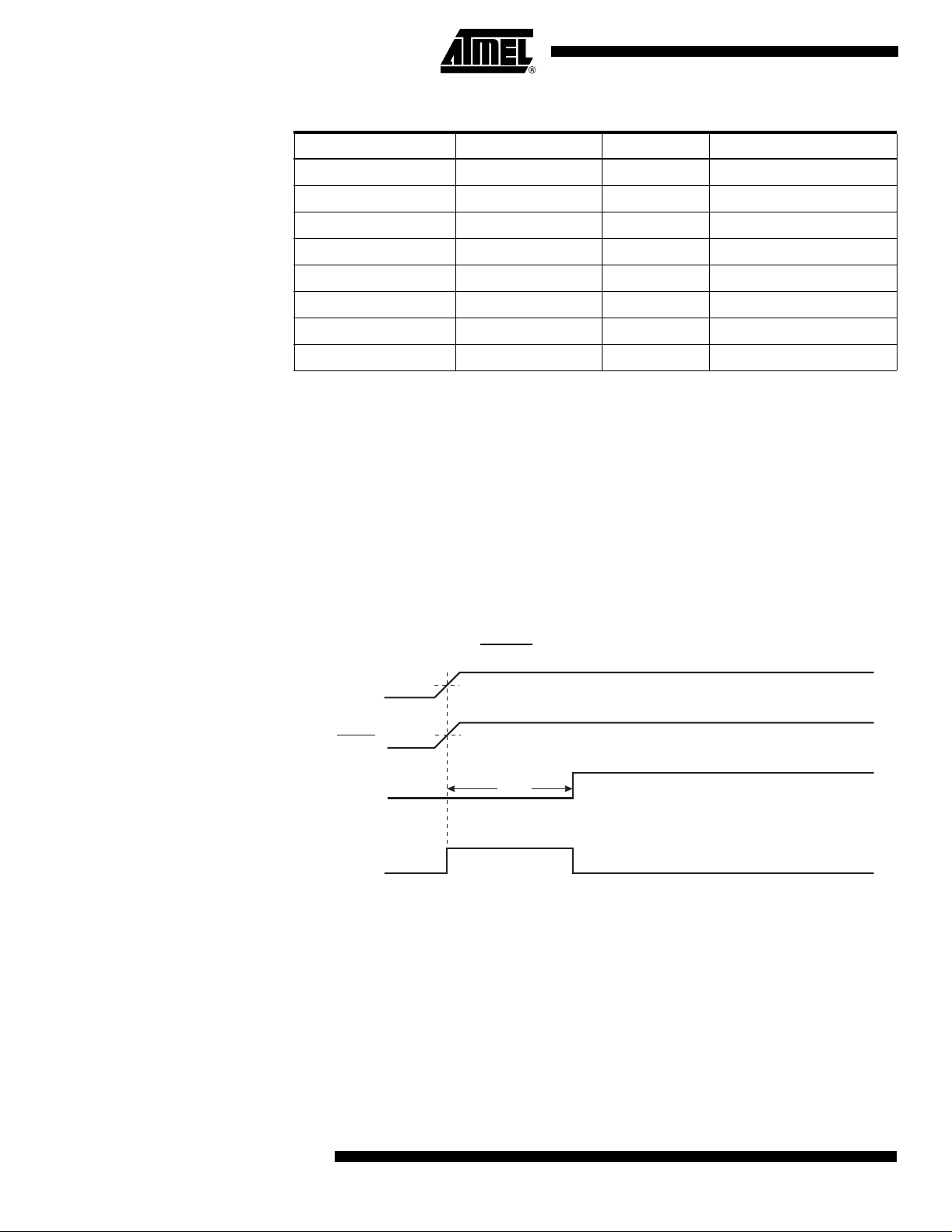

Figure 24. Reset Logic

VCC

Power-on

Reset Circuit

DATA BUS

MCU Status

Register (MCUSR)

BORF

PORF

WDRF

EXTRF

BODEN

BODLEVEL

RESET

100-500kW

SPIKE

FILTER

Brown-out

Reset Circuit

Reset Circuit

Watchdog

Timer

On-chip

RC Oscillator

Clock

Generator

CKSEL[3:0]

CK

Counter Reset

Delay Counters

TIMEOUT

Table 4. Reset Characteristics (VCC = 5.0V)

Symbol Parameter Condition Min Typ Max Units

V

POT

Power-on Reset Thres hold

Voltage (risin g)

1.0 1.4 1.8 V

Internal Reset

24

V

V

Notes: 1. The Power-on Reset will not work unless the supply voltage has been below V

ATmega163(L)

RST

BOT

Power-on Reset Thres hold

Voltage (falling)

(1)

RESET Pin Threshold

Voltage

Brown-out Res et Th reshol d

Voltage

(falling).

0.4 0.6 0.8 V

– – 0.85 V

(BODLEVEL = 1) 2.4 2.7 3.2

(BODLEVEL = 0) 3.5 4.0 4.5

CC

V

V

POT

1142E–AVR–02/03

Page 25

ATmega163(L)

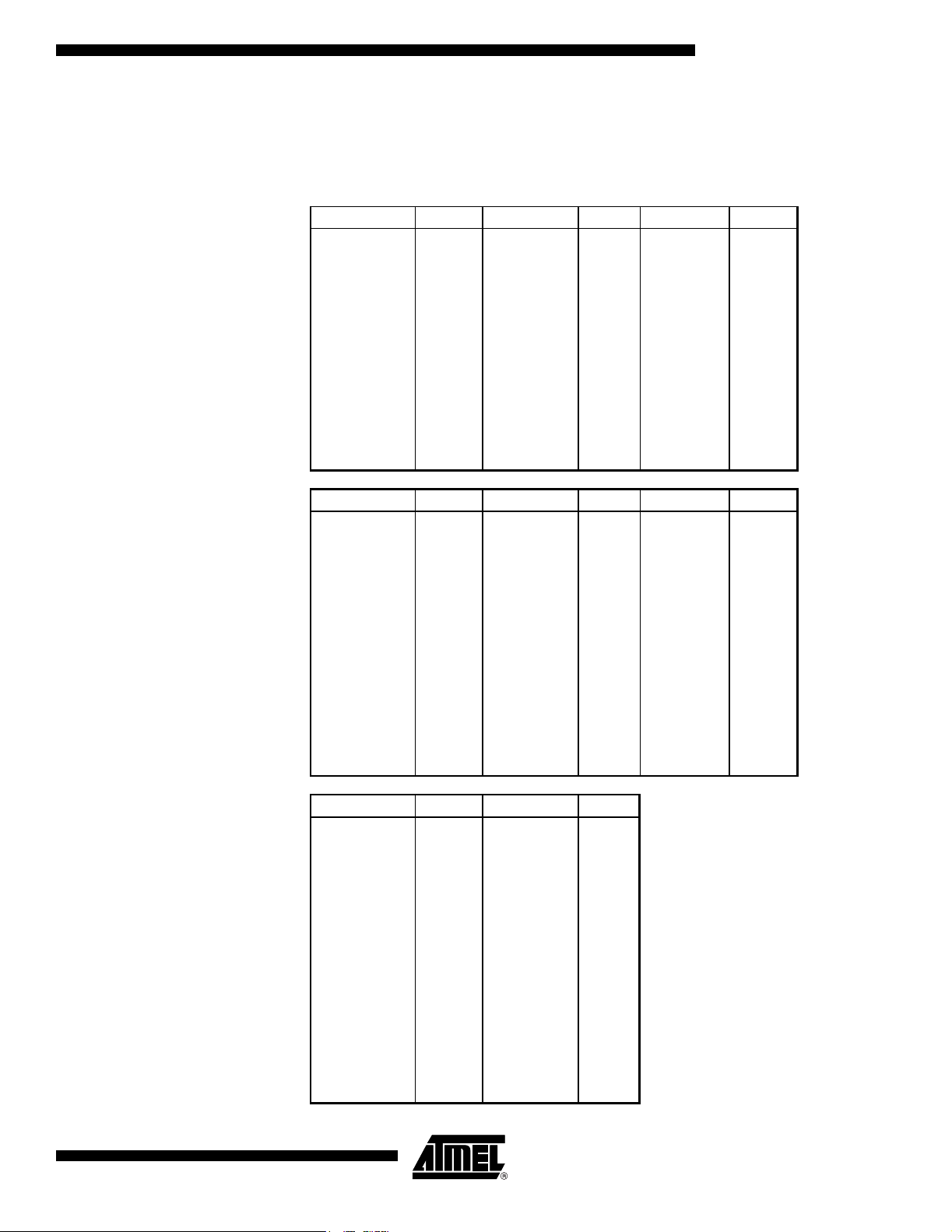

Table 5. Reset Dela y Se lec t io ns

Start-up Time,

V

= 2.7V,

CC

BODLEVEL

Unprogrammed

CKSEL

(2)

(1)

Start-up Time,

V

= 4.0V,

CC

BODLEVEL

Programmed Recommended Usage

(3)

0000 4.2 ms + 6 CK 5.8 ms + 6 CK Ext. Clock, fast rising power

0001 30 µs + 6 CK

(6)

0010

67 ms + 6 CK 92 ms + 6 CK Int. RC Oscillator, slowly rising power

(4)

10 µs + 6 CK

(5)

Ext. Clock, BOD enabled

0011 4.2 ms + 6 CK 5.8 ms + 6 CK Int. RC Oscil lator, fast rising power

0100 30 µs + 6 CK

(4)

10 µs + 6 CK

(5)

Int. RC Oscillator, BOD enabled

0101 67 ms + 6 CK 92 ms + 6 CK Ext. RC Oscillator, slowly risi ng power

0110 4.2 ms + 6 CK 5.8 ms + 6 CK Ext. RC Oscillator, fast ris ing power

0111 30 µs + 6 CK

(4)

10 µs + 6 CK

(5)

Ext. RC Oscillator, BOD enabled

1000 67ms + 32K CK 92 ms + 32K CK Ext. Low-frequency Crystal

1001 67 ms + 1K CK 92 ms + 1K CK Ext. Low-f requency Crystal

1010 67 ms + 16K CK 92 ms + 16K CK Crystal Oscillator, slowly rising power

1011 4.2 ms + 16K CK 5.8 ms + 16K CK Crystal Oscillator, fast rising power

1100 30 µs + 16K CK

(4)

10 µs + 16K CK

1101 67 ms + 1K CK 92 ms + 1K CK

(5)

Crystal Oscillator, BOD enabled

Ceramic Resonator/Ext. Clock, slowly

rising power

1110 4.2 ms + 1K CK 5.8 ms + 1K CK Ceramic Resonator, fast rising power

1111 30 µs + 1K CK

(4)

10 µs + 1K CK

(5)

Ceramic Resonator, BOD enabled

Notes: 1. On power-up, the start -up time is increased with typ. 0. 6 ms.

2. “1” means unprogrammed, “0” means programmed.

3. For possible clock selections, see “Cl ock Options” on page 5.

4. When BODEN is programmed, add 100 µs.

5. When BODEN is programmed, add 25 µs.

6. Default value.

Table 5 shows the Start-up Times from Reset. When the CPU wakes up from Powerdown or Power-sav e, only the clo ck counting part of t he start-up time i s used. The

Watchdog Oscillator is used for timing the real time part of the start-up time. The number

of WDT Oscillator cycles used for each time-out is shown in T a ble 6.

The frequency o f the W at chdog Oscillator is voltage depen dent as shown in the Electrical Characteristics section. The device is shipped with CKSEL = “0010” (Int. RC

Oscillator, slowly rising power).

1142E–AVR–02/03

25

Page 26

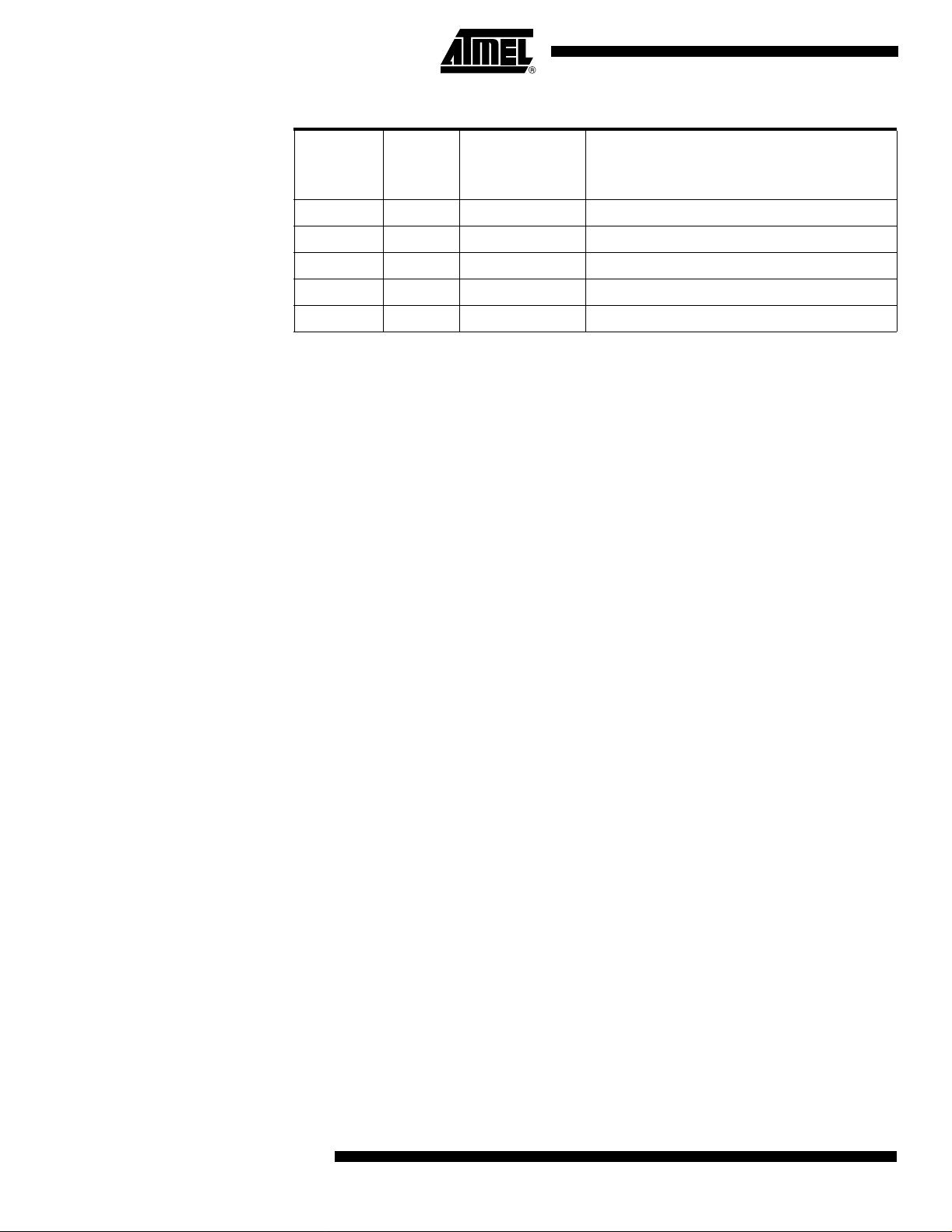

Table 6. Number of Watchdog Osc illa tor C ycl es

(1)

BODLEVEL VCC Condition Time-out Number of Cycles

Unprogrammed 2.7V 30 µs 8

Unprogrammed 2.7V 130 µs 32

Unprogrammed 2.7V 4.2 ms 1K

Unprogrammed 2.7V 67 ms 16K

Programmed 4.0V 10 µs 8

Programmed 4.0V 35 µs 32

Programmed 4.0V 5.8 ms 4K

Programmed 4.0V 92 ms 64K

Note: 1. The Bodlevel Fuse can be used to select start-up times even if the Brown-out Detec-

tion is disabled (BODEN Fuse unprogrammed).

Power-on Reset A Power-on Reset (POR) pulse is generated by an On-chip detection circuit. The detec-

tion level is defined in Table 4. The POR is activated whenever V

is b elo w the

CC

detection level. The POR circuit can be u sed t o trigger the Start-up Reset, as well as t o

detect a failure in supply voltage.

A Power-on Reset (POR) circuit ensures that the device is reset from Power-on. Reaching t he Po w er-o n Rese t th re shol d v ol tage inv oke s a de lay co unt er, w h ich d e term ine s

the delay, for which the device is kept in RESET after V

rise. The Time-out Period of

CC

the dela y count er can be define d by the user t hrou gh th e CK SEL F uses. The d ifferent

selections for the del ay period are p r esente d in Table 5 . T he RESET signal is ac tivat ed

again, without any delay, when the V

decreases below detection level.

CC

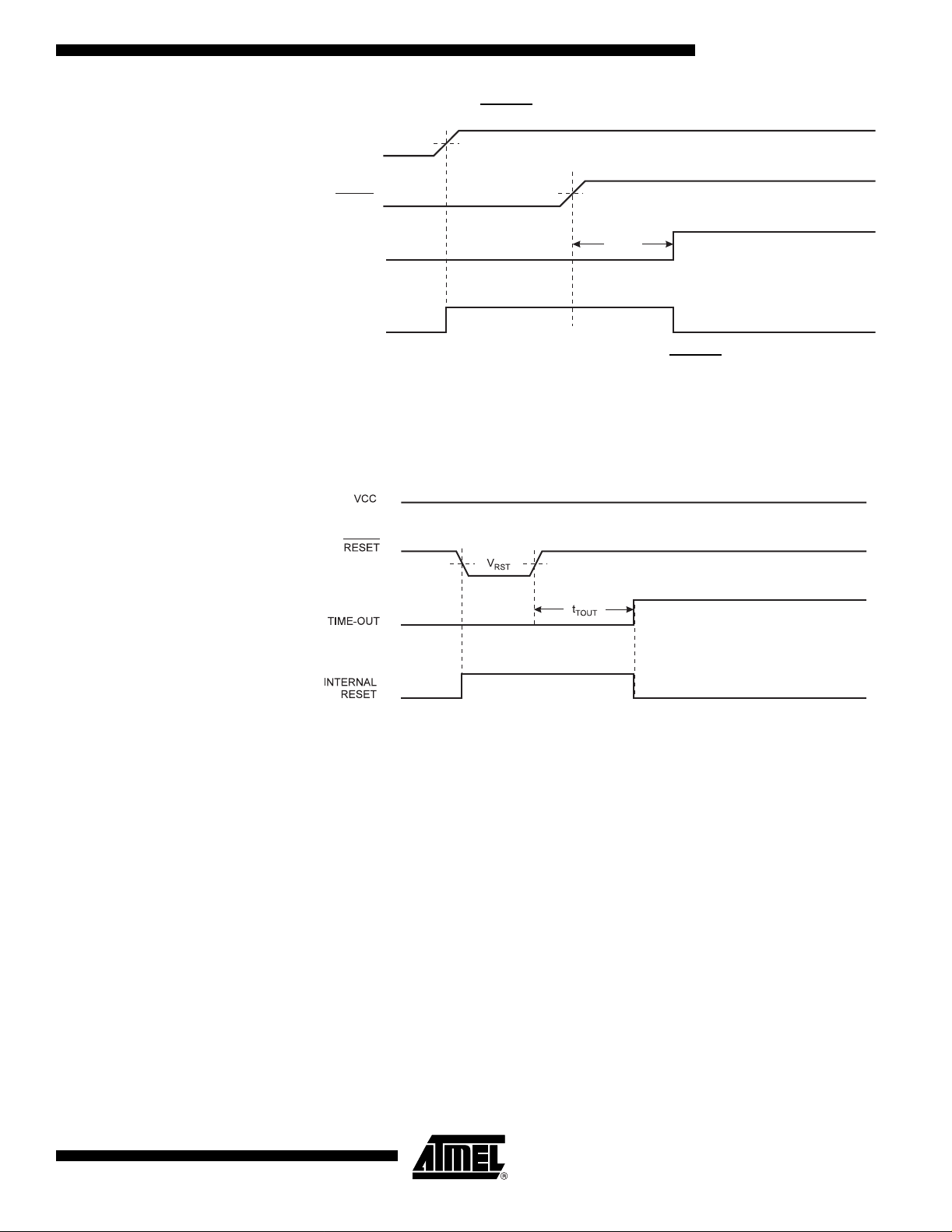

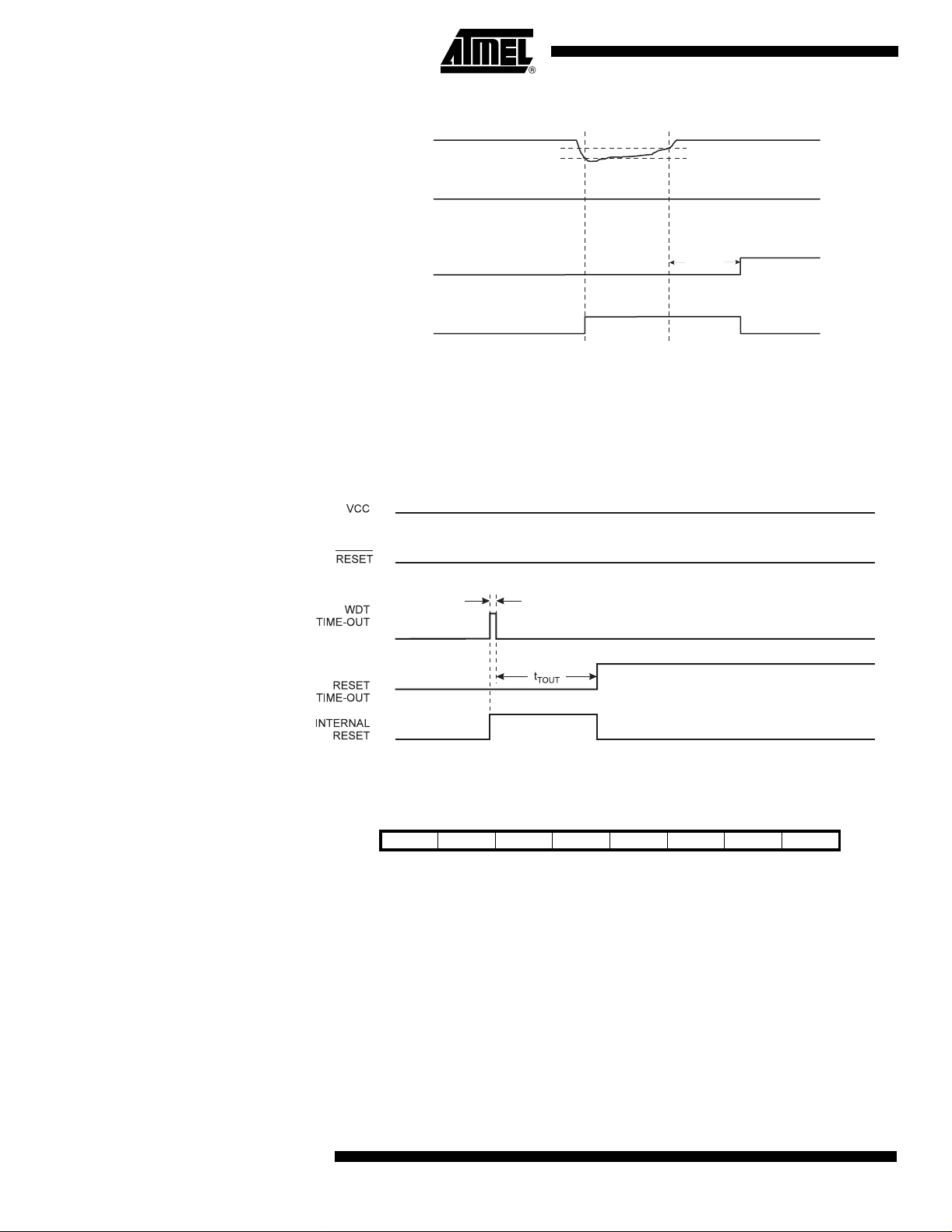

Figure 25. MCU Start-up, RESET

V

VCC

RESET

TIME-OUT

INTERNAL

RESET

POT

V

RST

t

TOUT

Tied to VCC.

26

ATmega163(L)

1142E–AVR–02/03

Page 27

Figure 26. MCU Start-up, RESET Extended Externally

V

VCC

RESET

TIME-OUT

INTERNAL

RESET

POT

V

RST

t

TOUT

ATmega163(L)

External Reset An External Reset is generated by a low level on the RESET

pin. Reset pu lse s long er

than 500 ns will generate a Reset, even if the clock is not running. Shorter pulses are

not guaranteed to generate a Reset. When the applied signal reaches the Reset

Threshold Voltag e – V

Time-out Period t

TOUT

on its positive edge, the delay timer starts the MCU after the

RST

has expired.

Figure 27. External Reset During Operation

Brown-out Detection ATmega1 63 has an On -chip Brow n-out De tect ion (B OD) c ircuit for mo nitori ng t he V

level during the operation. The BOD circuit can be enabled/disabled by the fuse

BODEN. When the BOD is enabled (BODEN programmed), and V

decreases to a

CC

value below the t rigger l evel, the Bro wn-ou t Reset is i mmedia tely activa ted. Whe n V

increases above the trigger level, the B rown-out Reset is deactivated after a delay. T he

delay is defined by the user in the same way as the delay of POR signal, in Table 5. The

trigger level for the BOD can be selected by the fuse BODLEVEL to be 2.7V

(BODLEVEL unprogrammed), or 4.0V (BODLEVEL programmed). The trigger level has

a hysteresis of 50 mV to ensure spike free Brown-out Detection.

CC

CC

1142E–AVR–02/03

The BOD circuit will only detect a drop in V

if the voltage stays below the trigger level

CC

for longer than 9 µs for trigger level 4.0V, 21 µs for trigger level 2.7V (typical values).

27

Page 28

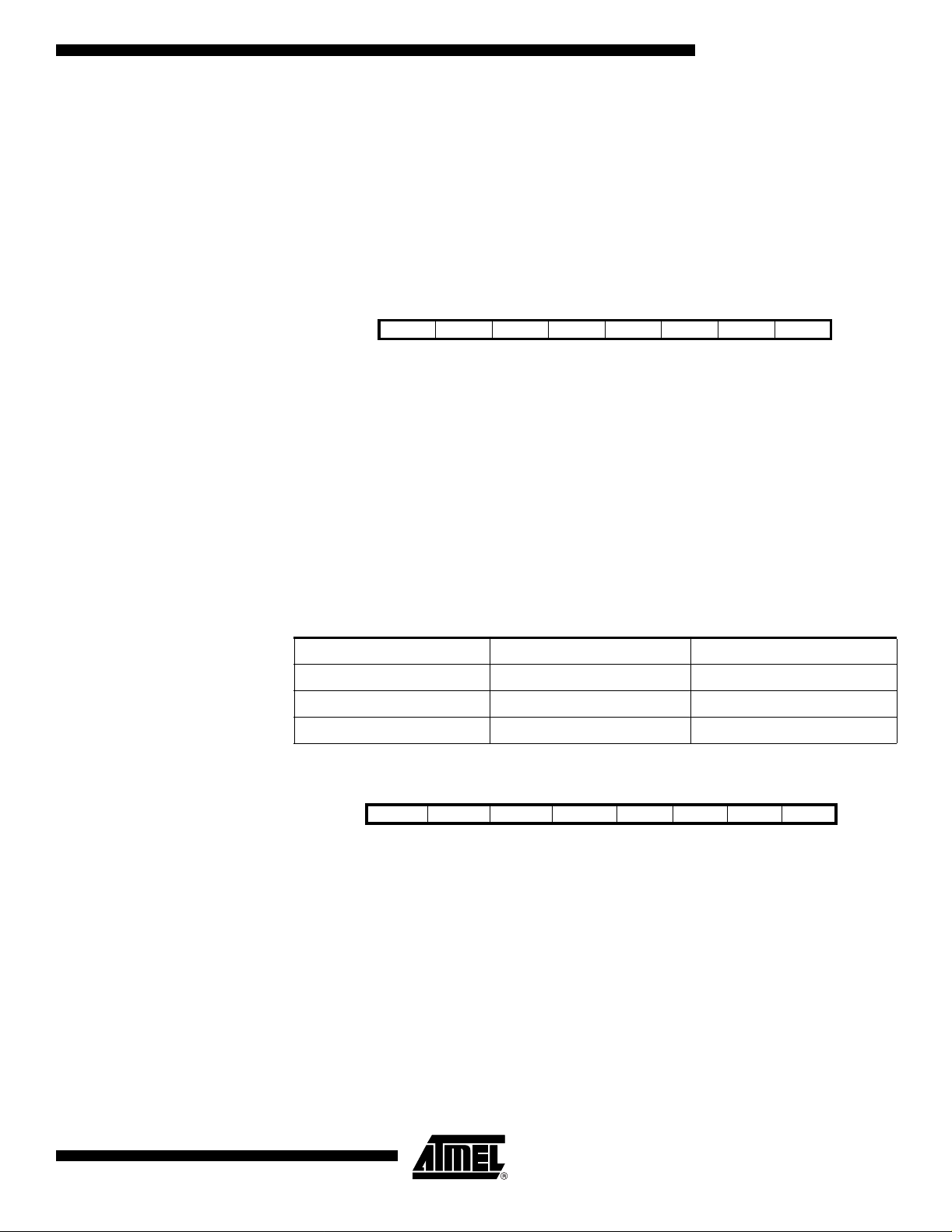

Figure 28. Brown-out Reset During Operation

= V

V

BOT+

t

TOUT

- 25 mV

BOT

VCC

RESET

TIME-OUT

INTERNAL

RESET

The hysteresis on V

BOT

: V

BOT+

= V

V

BOT-

+ 25 mV, V

BOT

BOT-

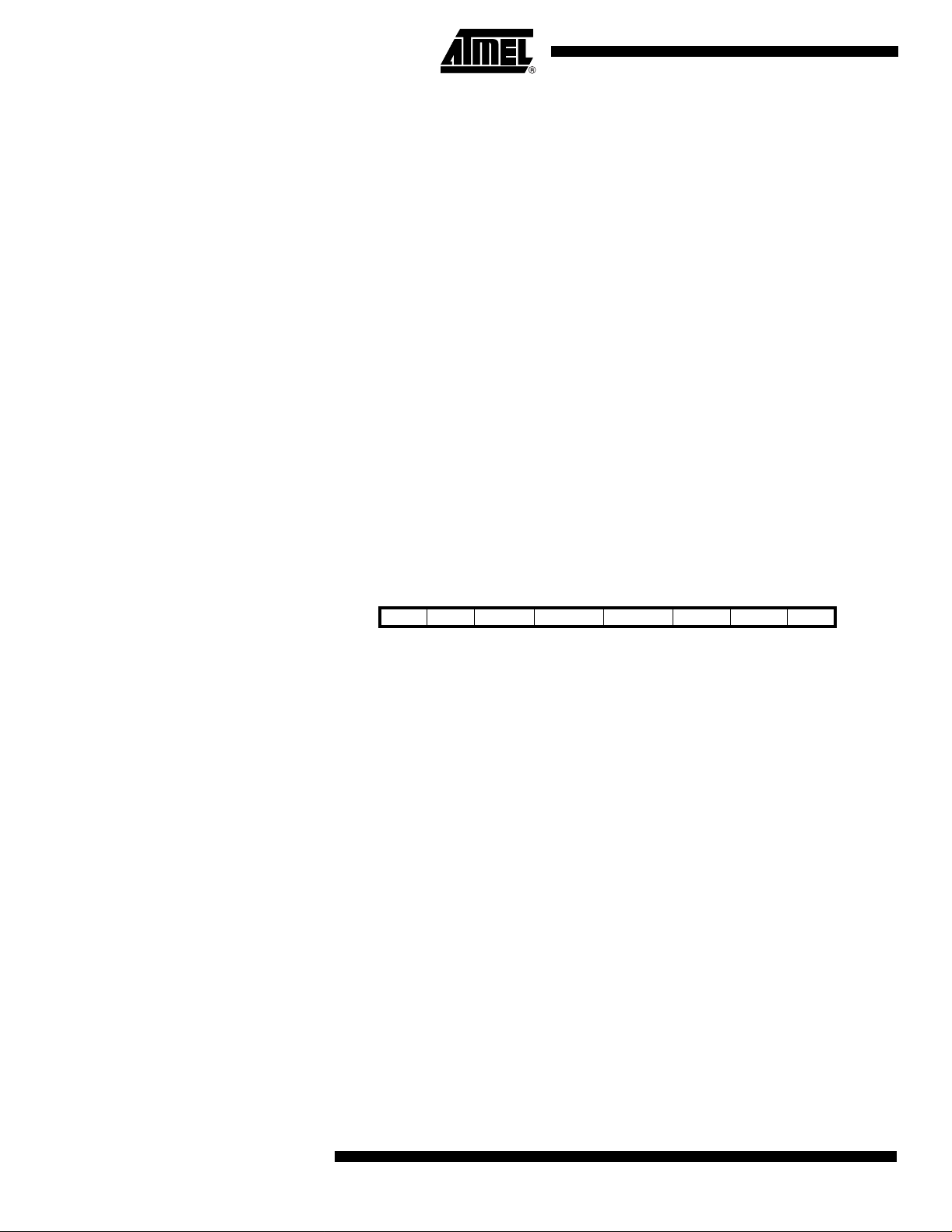

Watchdog Reset When the Watchdog times out, it will generate a short reset pulse of 1 XTAL cycle dura-

tion. On the falling edge of this pulse, the delay timer starts counting the Time-out Period

t

. Refer to page 60 for details on operation of the Watchdog Timer.

TOUT

Figure 29. Watchdog Reset During Operation

MCU Status Register – MCUSR

1 CK Cycle

The MCU Stat us Register p rovid es informati on on which reset source ca used an M CU

Reset.

Bit 76543210

$34 ($54) – – – – WDRF BORF EXTRF PORF MCUSR

Read/Write R R R R R/W R/W R/W R/W

Initial Value 0 0 0 0 See Bit Description

• Bits 7..4 – Res: Reserved Bits

These bits are reserved bits in the ATmega163 and always read as zero.

• Bit 3 – WDRF: Watchdog Reset Flag

This bit is set if a Watchdog Rese t occurs. The bit is reset by a Power-on Re set, or by

writing a logic zero to the Flag.

28

ATmega163(L)

1142E–AVR–02/03

Page 29

ATmega163(L)

• Bit 2 – BORF: Brown-out Reset Flag

This bit is set if a Brow n-ou t Reset occ urs. The bi t is reset by a P ower-on R eset, or by

writing a logic zero to the Flag.

• Bit 1 – EXTRF: Externa l Reset Flag

This bit is set if an External Reset occurs. The bit is reset by a Power-on Res et, or by

writing a logic zero to the flag.

• Bit 0 – PORF: Power-on Reset Flag

This bit is set if a P ower-on Res et occ urs. The bit is reset only by writing a logic zero to

the flag.

To make us e of the Re set Flags t o identify a res et co ndition, the u ser shou ld read an d

then reset the MCUSR as early as possible in the program. If the register is cleared

before another reset occurs, the source of the reset can be found by examining the

Reset Flags.

Internal Voltage Reference ATmega163 features an internal bandgap reference with a nominal voltage of 1.22V.

This re fe renc e is u sed fo r Br own -o ut D ete cti on, an d it ca n be u sed a s an i npu t to th e

Analog Co mparato r and AD C. The 2. 56V ref erence t o the ADC is also ge nera ted from

the internal bandgap reference.

Voltage Reference Enable Signals and St art-up Time

Interrupt H andling The ATmega163 has t wo 8-bit Interrupt Mask Control Registers: GIMSK – General

To save power, the reference is not always turned on. The reference is on during the following situations:

1. When the BOD is enabled (by programming the BODEN Fuse)

2. When the bandgap reference is connected to the Analog Comparator (by setting

the ACBG bit in ACSR) .

3. When the ADC is enabled.

Thus, when the BOD is not enabled, after setting the AC BG bit, the user mu st always

allow the re ferenc e to start up bef ore the out put f rom the Analo g Com par ator is used.

The bandgap reference us es typically 10 µA , and to reduce p ower consum ption in

Power-down mode, the user can avoid the three conditions above to ensure that the reference is turned off before entering Power-down mode.

Interrupt Mask Register and TIMSK – Timer/Counter Interrupt Mask Register.

When an interrupt occurs, the Global Interrupt Enable I-bit is cleared (zero) and all inter-

rupts are disabled. The user software must set (one) the I-bit to enable neste d

interrupts. The I-bit is set (one) when a Return from Interrupt instruction – RETI – is

executed.

When the Program Counter is vectored to the actual Interrupt Vector in order to execute

the interrupt handling routine, hardware clears the corresponding flag that generated the

interrupt. Some of the interrupt flags can also be cleared by writing a logic one to the flag

bit position(s) to be cleared.

1142E–AVR–02/03

If an interrupt condition occurs when the corresponding interrupt enable bit is cleared

(zero), the Interrupt Flag will be set and remembered until the interrupt is enabled, or the

flag is cleared by software.

29

Page 30

If one or more in terrupt cond itions oc cur when the Global Interru pt En able bit is cle ared

(zero), t he co rre spond ing in terru pt fl ag(s) will be se t an d rem ember ed until the G loba l

Interrupt Enable bit is set (one), and will be executed by order of priority.

Note that external level interrupt does not have a flag, and will only be rem embered for

as long as the interrupt condition is present.

Note that the Status Register is not automatically stored wh en entering an in terrupt routine and restored when returning from an interrupt routine. This must be handled by

software.

Interrupt Response Time The interrupt execution response for all the enabled AVR interrupts is four clock cycles

minimum. After four clock cycles the Program Vector address for the actual interrupt

handling routine is executed . During this four clock cycle period, the Program Co unter

(13 bits) is pushed onto the Stack. The vector is normally a jump to the interrupt routine,

and this jump takes three clock cycl e s. If an interrupt occurs during ex ec u ti o n of a multicycle instruction, this instruction is completed before the interrupt is served. If an interrupt occurs when the MCU is in sleep mode, the interrupt execution response time is

increased by four clock cycl es .

A return from an interrupt handling routine takes four clock cycles. During these four

clock cycles, the Program Counter (two bytes) is popped back from the Stack, the Stack

Pointer is incremen ted by two, an d the I Flag in SR EG is set. When

AVR

exits from an

interrupt, it will always return to the main program and execute one more instruction

before any pending interrupt is served.

The General Interrupt Mask Register – GIMSK

Bit 7 6 5 4 3 2 1 0

$3B ($5B) INT1 INT0 – – – – – – GIMSK

Read/Write R/W R/W R R R R R R

Initial Value 0 0 x 0 0 0 0 0

• Bit 7 – INT1: External Interrupt Request 1 Enable

When the IN T1 bit is set (one ) and the I-bi t in the Status Register (S REG) is s et (one),

the external pin interrupt is activated. The Interrupt Sense Control1 bits 1/0 (ISC11 and

ISC10) in the MCU general Control Register (MCUCR) define whether th e external

interrupt is activated on rising and/or falling edge of the INT1 pin or level sensed. Activity

on the p in wi ll caus e an interru pt re ques t ev en if IN T1 is con figure d a s an ou tpu t. Th e

corresponding interrupt of External Interrupt Reques t 1 is executed f rom program memory address $004. See also “External Interrupts”.

• Bit 6 – INT0: External Interrupt Request 0 Enable

When the IN T0 bit is set (one ) and the I-bi t in the Status Register (S REG) is s et (one),

the external pin interrupt is activated. The Interrupt Sense Control0 bits 1/0 (ISC01 and

ISC00) in the MCU General Control Register (MCUCR) define whether the external

interrupt is activated on rising or fall ing edg e of the INT0 pin or level se nsed. Activity on

the pin will cause an interrupt request even if INT0 is configured as an output. The corresponding interrupt of External Interrupt Request 0 is executed from Program Memory

address $002. See also “External Interrupts.”

30

• Bits 5 – Res: Reserved Bits

This bit is reserved in the ATmega163 and the read value is undefined.

ATmega163(L)

1142E–AVR–02/03

Page 31

The Genera l Int errupt Flag Register – GIFR

ATmega163(L)

• Bits 4..0 – Res: Reserved Bits

These bits are reserved bits in the ATmega163 and always read as zero.

Bit 7 6 5 4 3 2 1 0

$3A ($5A) INTF1 INTF0 – – – – – – GIFR

Read/Write R/W R/W R R R R R R

Initial Value 0 0 0 0 0 0 0 0

• B i t 7 – IN TF1: External In te rru pt Fl ag1

When an edge on the INT1 pin triggers an interrupt request, the corres pnding Int errupt

Flag, INTF1, becomes set (one). If the I-bit in SREG and the corresponding Interrupt

Enable bit, INT1 in GIMSK are set (one), th e MC U will jump t o the In terrupt Vecto r. The

Flag is cleared when the interrupt routine is executed. Alternatively, the Flag can be

cleare d by w ri ting a log ical one t o i t. Th is F lag is a lw ays clea red w he n IN T1 is conf igured as a level interrupt.

• B i t 6 – IN TF0: External In te rru pt Fl ag0

When an event on the INT0 pin triggers an interrupt request, the corresponding Interrupt

Flag, INTF0 becomes set (one). If the I-bit in SREG and the corresponding Interrupt

Enable bit, INT0 in GIMSK are set (one), th e MC U will jump t o the In terrupt Vecto r. The

Flag is cleared when the interrupt routine is executed. Alternatively, the Flag can be

cleare d by w ri ting a log ical one t o i t. Th is F lag is a lw ays clea red w he n IN T0 is conf igured as a level interrupt.

The Timer/Counter Interrupt Mask Register – TIMSK

• Bits 5..0 – Res: Reserved Bits

These bits are reserved bits in the ATmega163 and always read as zero.

Bit 7 6 5 4 3 2 1 0

$39 ($59) OCIE2 TOIE2 TICIE1 OCIE1A OCIE1B TOIE1 – TOIE0 TIMSK

Read/Write R/W R/W R/W R/W R/W R/W R R/W

Initial Value 0 0 0 0 0 0 0 0

• Bit 7 – OCIE2: Timer/Counter2 Outp ut Comp are Ma tch Interru pt Enable

When the OCIE2 bit is set (one) and the I-bit in the Status Register is set (one), the

Timer/Counter2 Compare Match Interrupt is enabled. The corresponding interrupt (at

vector $006 ) is e xecute d if a Com pare Ma tch in Timer/Co unte r2 oc curs, i.e ., when the

OCF2 bit is set in the Timer/Counter Interrupt Flag Register – TIFR.

• Bit 6 – TOIE2: Timer/ Counter2 Overflow Interrupt Enable

When the TOIE2 bit is set (one) and the I-bit in the Status Register is set (one), the

Timer/Counter2 Overflow Interrupt is enabled. The corresponding interrupt (at vector

$008) is executed if an overflow in Timer/Counter2 occurs, i.e., when the TOV2 bit is set

in the Timer/Counter Interrupt Flag Register – TIFR.

• Bit 5 – TICIE1: Timer/Counter1 Input Capture Interrupt Enable

1142E–AVR–02/03

When the TICIE1 bit is set (one) and the I-bit in the Status Register is set (one), the

Timer/C ount er1 In pu t Capt ure Ev en t Inter rup t is en ab led. T he co rre spond ing int erru pt

31

Page 32

(at vector $00A) is executed if a capture triggering event occurs on PD6 (ICP), i.e., when

the ICF1 bit is set in the Timer/Counter Interrupt Flag Register – TIFR.

• Bit 4 – OCIE1A: Timer/Coun ter1 Ou tput Comp areA M atch Interru pt Enable

When the OC IE1A bit is s et (one ) and the I- bit in the Sta tus Registe r is set (one), the

Timer/Counter1 Compare A Match Interrupt is enabled. The correspondin g interrupt (at

vector $00C) is executed if a Compare A Match in Timer/Counter1 occurs, i.e., when the

OCF1A bit is set in the Timer/Counter Interrupt Flag Register – TIFR.

• Bit 3 – OCIE1B: Timer/Coun ter1 Ou tput Comp areB M atch Interru pt Enable

When the OC IE1B bit is s et (one ) and the I- bit in the Sta tus Registe r is set (one), the

Timer/Counter1 Compare B Match Interrupt is enabled. The correspondin g interrupt (at

vector $00E) is executed if a Compare B Match in Timer/Counter1 occurs, i.e., when the

OCF1B bit is set in the Timer/Counter Interrupt Flag Register – TIFR.

• Bit 2 – TOIE1: Timer/ Counter1 Overflow Interrupt Enable

When the TOIE1 bit is set (one) and the I-bit in the Status Register is set (one), the

Timer/Counter1 Overflow Interrupt is enabled. The corresponding interrupt (at vector

$010) is executed if an overflow in Timer/Counter1 occurs, i.e., when the TOV1 bit is set

in the Timer/Counter Interrupt Flag Register – TIFR.

• Bit 1 – Res: Reserved Bit

This bit is a reserved bit in the ATmega163 and always reads as zero.

The Timer/Counter Interrupt Flag Register – TIFR

• Bit 0 – TOIE0: Timer/ Counter0 Overflow Interrupt Enable

When the TOIE0 bit is set (one) and the I-bit in the Status Register is set (one), the

Timer/Counter0 Overflow Interrupt is enabled. The corresponding interrupt (at vector

$012) is executed if an overflow in Timer/Counter0 occurs, i.e., when the TOV0 bit is set

in the Timer/Counter Interrupt Flag Register – TIFR.

Bit 7 6 5 4 3 2 1 0

$38 ($58) OCF2 TOV2 ICF1 OCF1A OCF1B TOV1 – TOV0 TIFR

Read/Write R/W R/W R/W R/W R/W R/W R R/W

Initial Value 0 0 0 0 0 0 x 0

• Bit 7 – OCF2: Output Compare Flag2

The OCF2 bit is set (one) when a Compare M atch occurs between the Tim er/Counter2

and the data in OCR2 – Output Compare Register2. OCF2 is cleared by hardware when

executing the corresponding Interrupt Handling Vector. Alternatively, OCF2 is cleared

by writing a lo gic one to th e flag. When the I-b it in SREG , and OCI E2 (Tim er/Counte r2

Compare Match Interrupt Enable), and the OCF2 are set (one), the Timer/Counter2

Comp are Ma t ch In terrupt i s execute d.

• Bit 6 – TOV2: Timer/Counter2 Overflow Flag

The TOV2 bit is set (one) when an overflow occurs in Timer/Counter2. TOV2 is cleared

by hardware when executing the corresponding inteRrupt Handling Vector. Alternatively, TOV2 is cleared by writing a logic one to the flag. When the SREG I-bit, and

TOIE2 (Timer/Counter2 Overflow Interrupt Enable), and TOV2 are set (one), the

32

ATmega163(L)

1142E–AVR–02/03

Page 33

ATmega163(L)

Timer/Counter2 Overflow Interrupt is e xecuted. In up/dow n PWM mode, th is bit is set

when Timer/Counter2 changes counting direction at $00.

• B i t 5 – ICF1 : Input Captu re Fl a g1

The ICF1 bit is set (one) to Flag an Input Capture Event, indicating that the

Timer/Counter1 value has been transferred to the Input Capture Register – ICR1. ICF1

is cleared by hardware when executing the corresponding Interrupt Handling Vector.

Alternatively, ICF1 is cleared by writing a logic one to the flag.

• Bit 4 – OCF1A: Output Compare Flag 1A

The OCF1A bit is set (one) when a Compare Match occurs between the Timer/Counter1

and the data in OCR1A – Out put Com pare Register 1A. OCF1A is cleared by ha rdware

when executing the corresponding Interrupt Handling Vector. Alternatively, OCF1A is

cleared by writing a logic one to the flag. When the I-bit in S REG, and O CIE1A

(Timer/Counter1 Compare Match Interrupt A Enable), and the OCF1A are set (one), the

Timer/Counter1A Compare Match Interrupt is executed.

• Bit 3 – OCF1B: Output Compare Flag 1B

The OCF1B bit is set (one) when a Compare Match occurs between the Timer/Counter1

and the data in OCR1B – Out put Com pare Register 1B. OCF1B is cleared by ha rdware

when executing the corresponding Interrupt Handling Vector. Alternatively, OCF1B is

cleared by writing a logic one to the flag. When the I-bit in S REG, and O CIE1B

(Timer/Counter1 Compare Match Interrupt B Enable), and the OCF1B are set (one), the

Timer/Counter1B Compare Match Interrupt is executed.

• Bit 2 – TOV1: Timer/Counter1 Overflow Flag

The TOV1 is set (one) when an overflow occurs i n T imer/Cou nter1. TOV 1 is c leared by

hardware when executing the corresponding Interrupt Handling Vector. Alternatively,

TOV1 is cl eared by writ ing a logi c on e to the flag. W hen the I-bit in SREG , and TOIE 1

(Timer/Counter1 Overflow Interrupt Enable), and TOV1 are set (one), the

Timer/Counter1 Overflow Interrupt is e xecuted. In up/dow n PWM mode, th is bit is set

when Timer/Counter1 changes counting direction at $0000.

• Bit 1 – Res: Reserved Bit

This bit is a reserved bit in the ATmega163 and the read value is undefined.

• Bit 0 – TOV0: Timer/Counter0 Overflow Flag

The bit TOV0 is set (one) when an overflow occurs in Timer/Counter0. TOV0 is cleared

by hardware when executing the corresponding Interrupt Handl ing Vector. Alternatively,

TOV0 is cleared by writing a logic one to the flag. When the SREG I-bit, and TOIE0

(Timer/Counter0 Overflow Interrupt Enable), and TOV0 are set (one), the

Timer/Counter0 Overflow interrupt is executed.

External Int errupts The external interrupts are triggered by the INT0 and INT1 pins. Observe that, if

enabled, the interrupts will trigger even if the INT0/INT 1 pin s are c on figured as out puts.

This fe ature p rovi des a way of g enera ting a soft ware interru pt. T he ex terna l inte rru pts

can be triggere d by a fal ling or rising edg e or a low lev el. This is set up as indi cated i n

the specification for the MCU Control Register – MCUCR. When the external interrupt is

enabled and is configured as level triggered, the interrupt will trigger as long as the pin i s

held low.

1142E–AVR–02/03

33

Page 34

MCU Control Register – MCUCR

The MCU Control Register contains control bits for general MCU functions.

Bit 76543210

$35 ($55) – SE SM1 SM0 ISC11 ISC10 ISC01 ISC00 MCUCR

Read/Write R R/W R/W R/W R/W R/W R/W R/W

Initial Value00000000

• Bit 7 – Res: Reserved Bit

This bit is a reserved bit in the ATmega163 and always reads as zero.

• Bit 6 – SE: Sleep Enable

The SE bit must be set (one) to make the MCU enter the sleep mode when the SLEEP

instruction is executed. To avoid the MCU en tering the sleep mod e unless it is the programmers purpose, it is recommended to set the Sleep Enable SE bit just before the

execution of the SLEEP instruction.

• Bit s 5, 4 – SM1/SM0: Sleep Mode Se lect Bits 1 and 0

These bits select between the three available sleep modes as shown in Table 7.

Table 7. Sleep Mode Select

SM1 SM0 Sleep Mode

00Idle

0 1 ADC Noise Reduction

1 0 Power-down

11Power-save

• Bits 3, 2 – ISC11, ISC10: Interrupt Sense Control 1 Bit 1 and Bit 0

The External Interrupt 1 is activated by the external pin INT1 if the SREG I-Flag and the

corresponding interrupt mask in the GIMSK are set. The level and edges on the external

INT1 pin that activate t he interrupt are defined in Table 8. Th e value on th e INT1 pin is

sampled before detecting edg es. If edge or togg le interrupt is selected, pulses that last

longer th an one cl ock p eriod w ill gener ate an inte rrupt. Sh orter p ulses are no t guaranteed to generate an interrupt. If low level interrupt is selected, the low level must be held

until the completion of the currently executing instruction to generate an interrupt.

Table 8. Interrupt 1 Sense Control

ISC11 ISC10 Description

0 0 The low level of INT1 generates an interrupt request.

0 1 Any logical change on INT1 generat es an interrupt request.

1 0 The falling edge of INT1 generates an i nterrupt request.

1 1 The rising edge of INT1 generates an interrupt request.

34

ATmega163(L)

1142E–AVR–02/03

Page 35

ATmega163(L)

• Bit 1, 0 – ISC01, ISC00: Interrupt Sense Control 0 Bit 1 and Bit 0

The External Interrupt 0 is activated by the external pin INT0 if the SREG I-Flag and the

corresponding interrupt mask are set. The level and edges on the external INT0 pin that

activate the interrupt are defined in Table 9. The value on t he INT0 pin is sample d

before detecting edges. If edge or toggle interrupt is selected, pulses that last longer

than o ne c lock peri od wi ll g ener ate an i nterru pt. Sho rter pu lses are no t g uar ante ed to

generate an interrupt. If low level interrupt is selected, th e low level must be h eld until

the completion of the currently executing instruction to generate an interrupt.

Table 9. Interrupt 0 Sense Control

ISC01 ISC00 Description

0 0 The low level of INT0 generates an interrupt request.

0 1 Any logical change on INT0 generat es an interrupt request.

1 0 The falling edge of INT0 generates an i nterrupt request.

1 1 The rising edge of INT0 generates an interrupt request.

Sleep Modes To enter any of the four sleep modes, the SE bit in MCUCR must be set (one) and a

SLEEP instruction must be executed. Th e SM1 and SM0 bits in the MCUCR Regis ter

select which sleep mode (Idle, ADC Noise Reduct ion, Power-down, or Power-save) will

be activated by the SLEEP instruction. See Table 7 for a summary. If an enabled interrupt occurs while the MCU is in a sleep mode, the MCU wakes up. The MCU is then

halted for fo ur cycle s, execute s the inte rrupt routine, an d res umes e xecution fro m th e

instruction following SLEEP. The contents of the Register File, SRAM, and I/O memory

are unaltered when the device wakes up from sleep. If a Reset occurs during sleep

mode, the MCU wakes up and executes from the Reset Vector.

Idle Mode When the SM1/SM0 bits are set to 00, the SLEEP instruction makes the MCU enter Idle

mode, stopping t he CPU but allowing SPI, UART, Analog Comp arator, A DC, Two-wi re

Serial Interface, Timer/Count ers, Watchdog , and the interrupt s ystem to continue operating (if enabl ed). Th is ena bles t he M CU t o wake u p fro m exter nal t rigge red in terrupt s

as well as internal ones like the Timer Overflow and UART Receive Complete interrupts.

If wake-up from the Analog Comparator interrupt is not required, the Analog Comparator

can be powered down by setting the ACD bit in the Analog Comparator Control and Status Reg ist er – A CSR . T his w ill redu ce po we r cons ump tio n in I dle Mo de. I f the A DC i s

enabled, a conversion starts automatically when this mode is entered.

ADC Noise Reduction Mode When the SM1/SM0 bits are set to 01, the SLEEP instruction makes the MCU enter

ADC Noise Reduction mode, stopping the CPU but allowing the ADC, the external interrupts, the Two- wire Serial Int erface addre ss wat ch, Timer/ Counter2 an d the W atchdo g

to continue operating (if enabled). This improves the noise environment for the ADC,

enabling higher resolution measurements. If the ADC is enabled, a conversion starts

automatically when this mode is entered. Apart from the ADC Conversion Complete

interrupt, only an External Reset, a Watchd og Reset (if enabled), a Brow n-out Reset, a

Two-wire Serial Interface address match interrupt, or an external level interrupt can

wake up the MCU from ADC Noise Reduction Mode. A Timer/Counter2 Output Compare or overflow event will wake up the MCU, but will not generate an interrupt unless

Timer/Counter2 is clocked asynchronously.

In future devices this is subject to change. It is recommended for future code compatibility to disable Timer/Counter2 interrupts during ADC Noise Reduction mode if the

Timer/Counter2 is clocked synchronously.

1142E–AVR–02/03

35

Page 36

Power-do wn M ode When the SM1/SM0 bits are 10, the SLEEP instruction makes the MCU enter Po wer-

down mode. In this mode, the external Oscillator is stopped, while the external interrupts, the Two-wire Serial Interface address match, and the Watchdog continue

operating (if enabled). Only an External Reset, a Watchdog Reset, a Brown-out Reset, a

Two-wire Serial Interface address match interrupt, or an external level interrupt can

wake up the MCU.

Note that if a lev el triggered inte rrupt is used f or wake-u p from Power-do wn mod e, the

change d leve l mu st be held fo r some time to wa ke u p the M CU . This make s the M C U

less sensitive to noise. The changed level is sam pled twice by the Watc hdog Oscillator

clock, and if the input has the required level during this time, the MCU will w ak e up. The

period of the Watchdog Oscillator i s 1 µs (nominal) at 5. 0V and 25°C. T he frequency of

the Watchdog Oscil lator is v oltage de pendent as shown in the Ele ctrical Characteristics

section.

When wa king up from P ower-d own m ode, t here is a delay f rom the wak e-up co nd ition

occurs until the wake-up becomes effective. This allows the clock to restart and become

stable after having been stopped. The wake-up period is defined by the same CKSEL

Fuses that define the Reset Time-out period, as seen in Table 5 on page 25.

Power-save Mode When the SM1 /SM0 bits are 11, the SLEEP instruction forces the MCU into the Power-

save mode. This mode is identical to Power-down, with one exception:

If Timer/Counter 2 is clocked asynchrono usly, i.e., the AS2 bit in ASSR is set,

Timer/Counter2 will run durin g sleep. Th e device c an wake up from either T imer Ov erflow or Output Compare event from Timer/Counter2 if the corresponding

Timer/Co unt er2 int errupt e nab le bit s are s et in TI MSK , and t he g lobal interr upt e nable

bit in SREG i s se t .

If the asynchronous timer is NOT clocked asynchronously, Power-down mode is recommended instead of Power-save mode because the contents of the registers in the

asynchronous timer should be considered undefined after wake-up in Power-save mode

if AS2 is 0.

36

ATmega163(L)

1142E–AVR–02/03

Page 37

ATmega163(L)

Calibrated Internal RC Oscillator

Oscillator Calibration Register – OSCCAL

The calibrated internal Oscillator provides a fixe d 1 MHz (nominal) clock at 5V and

25°C. This clock may be used as the system clock. See the section “Clock Options” on

page 5 for informat ion on how to select this c lock as th e system c lock. This Oscillator

can be calibrated by writing the calibration byte to the OSCCAL Register. When this

Oscillator is used a s the chip clock, the Watch dog Os cillator will still be used f or the

Watchdog Timer and for the Reset Time-out. At 5V and 25

o

C, the pre-programmed calibration byte gives a frequency within ± 1% of the nominal frequency. For details on how

to use the pre-programmed calibration value, see “Calibration Byte” on page 144.

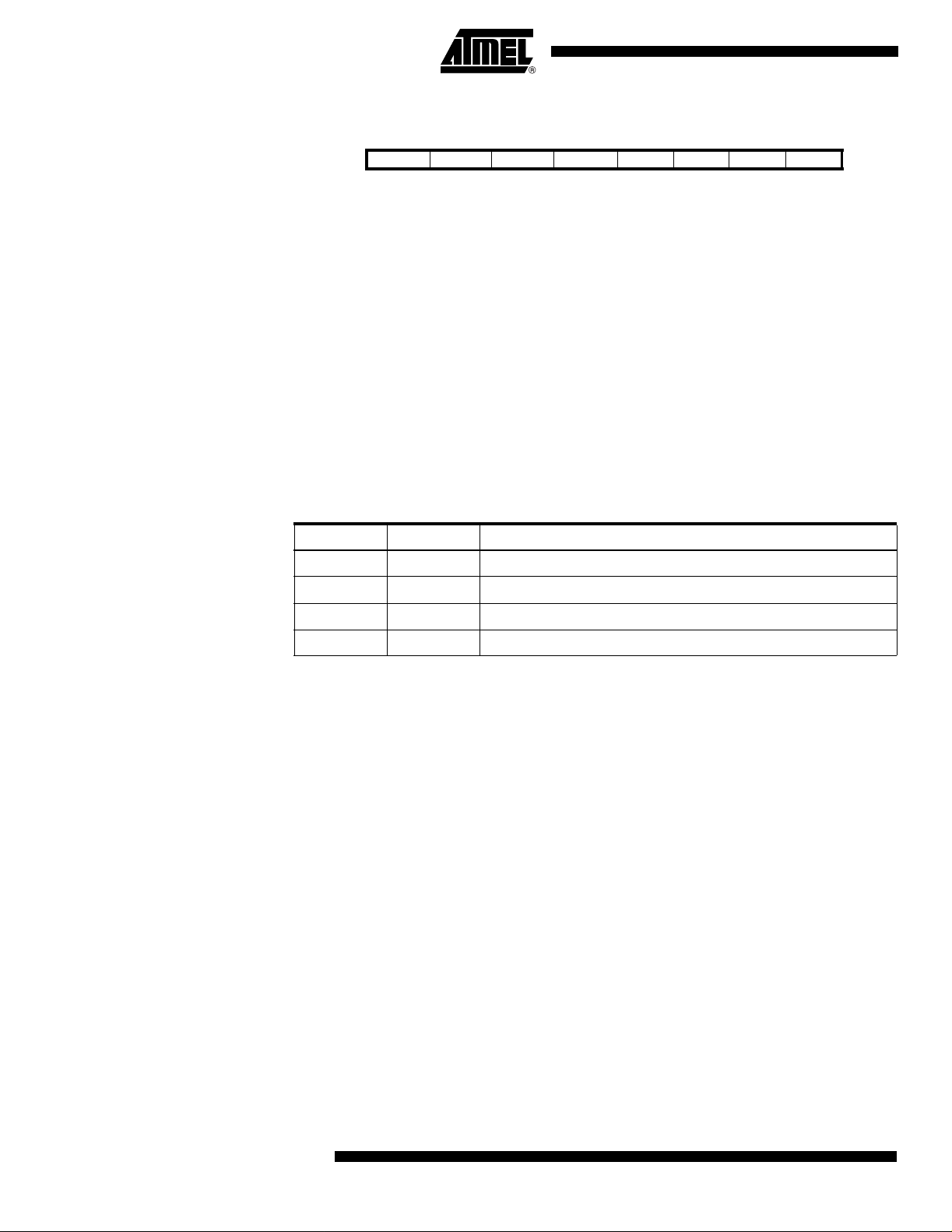

Bit 76543210

$31 ($51) CAL7 CAL6 CAL5 CAL4 CAL3 CAL2 CAL1 CAL0

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial Value00000000

• Bits 7..0 – CAL7..0: Oscillator Calibration Value

Writing the calibration byte to this address will trim the internal Oscillator to remove process variations from the Oscillator frequency. When OSCCAL is zero, the lowest

available frequen cy is c hosen. W riting non-ze ro values to this regis ter will increa se the

frequen cy of t he i nternal Os cillat or. Wri ting $F F t o the re gis ter give s the high est a vai lable frequency.

The calibrated Oscillator is used to time EEPROM and Flash access. If EEPROM or

Flash is written, do not calibrate to more than 10% above the nominal frequency. Otherwise, the EEPROM or Flash write operation may fail. Note that the Oscillator is intended

for calibration to 1.0MHz, thus tuning to other values is not guaranteed.

Special Function I/O Register – SFIOR

Table 10. Internal RC Oscillator Frequency Range.

OSCCAL Value Min Frequency (MHz) Max Frequency (MHz)

$00 0.5 1.0

$7F 0.7 1.5

$FF 1.0 2.0

Bit 7 6 5 4 3 2 1 0

$30 ($50) – – – – ACME PUD PSR2 PSR10 SFIOR

Read/Write R R R R R/W R/W R/W R/W

Initi al Valu e 0 0 0 0 0 0 0 0

• Bit 7..4 – Re s: Res erved Bits