ATMEL ATmega128, ATmega128L User Manual

BDTIC www.bdtic.com/ATMEL

Features

• High-performance, Low-power AVR

• Advanced RISC Architecture

– 133 Powerfu l Instructions – Most Single Clock Cycle Execution

– 32 x 8 General Purpose Workin g Registers + Peripheral Control Registers

– Fully Static Operation

– Up to 16 MIPS Throughput at 16 MHz

– On-chip 2-cycle Multiplier

• High Endurance Non-volatile Memory segmen ts

– 128K Bytes of In-System Self-programmable Flash program memory

– 4K Bytes EEPROM

– 4K Bytes Internal SRAM

– Write/Erase cycles: 10,000 Flash/100,000 EEPROM

– Data retention: 20 years at 85°C/100 years at 25°C

– Optional Boot Code Section with Ind ependent Lock Bits

In-System Programming by On-chip Boot Program

True Read-Whi le-W rite Operati on

– Up to 64K Bytes Optional External Memory Space

– Programming Lock for Software Security

– SPI Interface for In-System Programming

• JTAG (IEEE std. 1149.1 Compliant) Interface

– Boundary-scan Capabilities According to the JTAG Standard

– Extensive On-chip Debug Support

– Programming of Flash, EEPROM, Fuses and Lock Bits through the JTAG Interface

• Peripheral Features

– Two 8-bit Timer/Counters with Separate Prescalers and Compare Modes

– Two Expanded 16-bit Timer/Counters with Separate Prescaler, Comp are Mode and

Capture Mode

– Real Time Counter with Separate Oscillator

– Two 8-bit PWM Channels

– 6 PWM Channels with Programmable Resolution from 2 to 16 Bits

– Output Compare Modulator

– 8-channel, 10-bit ADC

8 Single-ended Channels

7 Differential Channels

2 Differential Channels with Programmable Gain at 1x, 10x, or 200x

– Byte-oriented Two-wire Serial Interface

– Dual Programmable Serial USARTs

– Master/Slave SPI Serial Interface

– Programmable Watchdog Timer with On-chip Oscillator

– On-chip Analog Comparator

• Special Microcontrolle r Features

– Power-on Reset and Programmable Brown-out Detection

– Internal Calibrated RC Oscillator

– External and Internal Interrupt Sources

– Six Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, Standby, and

Extended Standby

– Software Selectable Clock Frequency

– ATmega103 Compatibility Mode Selected by a Fuse

– Global Pull-up Disable

• I/O and Packages

– 53 Programmable I/O Lines

– 64-lead TQFP and 64-pad QFN/MLF

• Operating Voltages

– 2.7 - 5.5V ATmega128L

– 4.5 - 5.5V ATmega128

• Speed Grades

– 0 - 8 MHz ATmega128L

– 0 - 16 MHz ATmega128

®

8-bit Microcontroller

(1)

8-bit

Microcontroller

with 128K Bytes

In-System

Programmable

Flash

ATmega128

ATmega128L

Summary

Rev. 2467RS–AVR–06/08

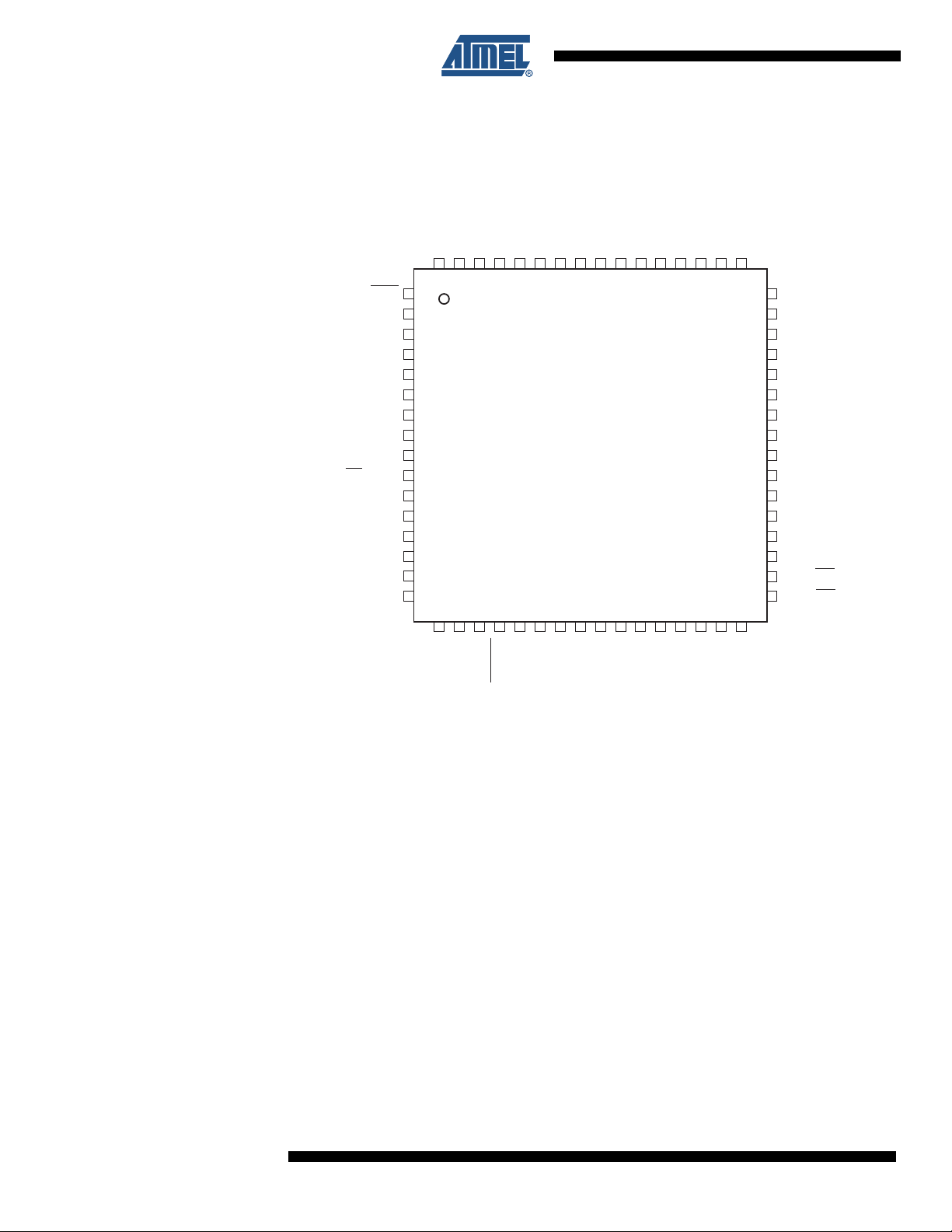

Pin Configurations

Figure 1. Pinout ATmega128

PEN

RXD0/(PDI) PE0

(TXD0/PDO) PE1

(XCK0/AIN0) PE2

(OC3A/AIN1) PE3

(OC3B/INT4) PE4

(OC3C/INT5) PE5

(T3/INT6) PE6

(ICP3/INT7) PE7

(SS) PB0

(SCK) PB1

(MOSI) PB2

(MISO) PB3

(OC0) PB4

(OC1A) PB5

(OC1B) PB6

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

AVCC

GND

64

63

17

18

AREF

PF0 (ADC0)

PF1 (ADC1)

62

61

60

19

20

21

PF2 (ADC2)

PF3 (ADC3)

PF4 (ADC4/TCK)

PF5 (ADC5/TMS)

59

58

57

56

22

23

24

25

PF6 (ADC6/TDO)

PF7 (ADC7/TDI)

GND

VCC

PA0 (AD0)

55

54

53

52

51

26

27

28

29

30

PA1 (AD1)

PA2 (AD2)

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

31

32

PA3 (AD3)

PA4 (AD4)

PA5 (AD5)

PA6 (AD6)

PA7 (AD7)

PG2(ALE)

PC7 (A15)

PC6 (A14)

PC5 (A13)

PC4 (A12)

PC3 (A11)

PC2 (A10)

PC1 (A9)

PC0 (A8)

PG1(RD)

PG0(WR)

VCC

GND

XTAL2

RESET

TOSC2/PG3

TOSC1/PG4

(OC2/OC1C) PB7

Note: The Pinout figure applies to both TQFP and MLF packages. The bottom pad under the QFN/MLF

package should be soldered to ground.

XTAL1

(SCL/INT0) PD0

(SDA/INT1) PD1

(RXD1/INT2) PD2

(T1) PD6

(ICP1) PD4

(TXD1/INT3) PD3

(T2) PD7

(XCK1) PD5

Overview The ATmega128 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC

architecture. By executing powerful instructions in a single clock cycle, the ATmeg a128

achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize

power consumption versus processing speed.

2

ATmega128

2467RS–AVR–06/08

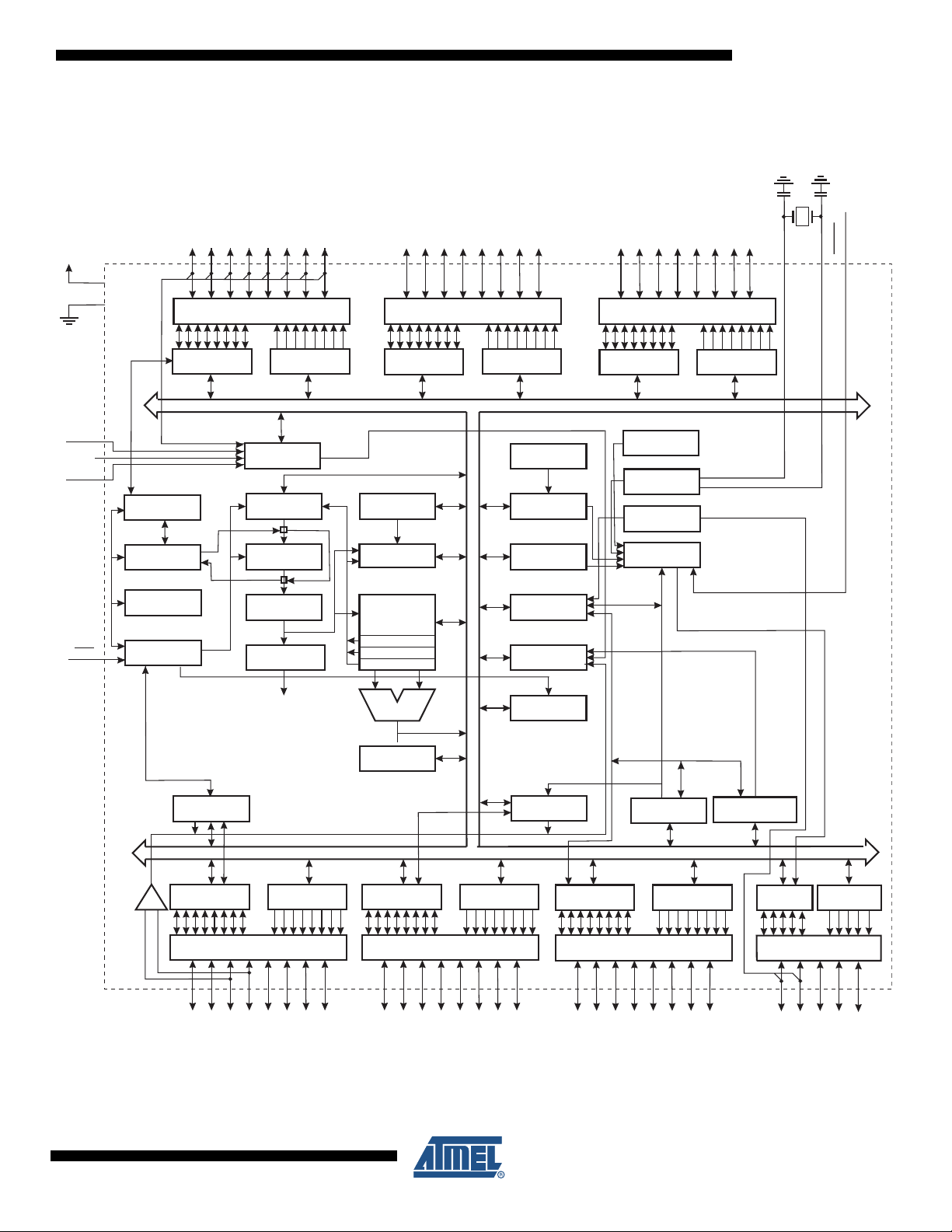

Block Diagram

Figure 2. Block Diagram

ATmega128

VCC

GND

AVCC

AGND

AREF

PEN

DATA REGISTER

JTAG TAP

ON-CHIP DEBUG

BOUNDARY-

SCAN

PROGRAMMING

LOGIC

PORTF DRIVERS

PORTF

DATA DIR.

REG. PORTF

ADC

PROGRAM

COUNTER

PROGRAM

FLASH

INSTRUCTION

REGISTER

INSTRUCTION

DECODER

DATA REGISTER

PORTA

STACK

POINTER

SRAM

GENERAL

PURPOSE

REGISTERS

X

Y

Z

PA0 - PA7PF0 - PF7

PORTA DRIVERS

DATA DIR.

REG. PORTA

8-BIT DATA BUS

INTERNAL

OSCILLATOR

WATCHDOG

TIMER

MCU CONTROL

REGISTER

TIMER/

COUNTERS

INTERRUPT

UNIT

PORTC DRIVERS

DATA REGISTER

PORTC

CALIB. OSC

OSCILLATOR

OSCILLATOR

TIMING AND

CONTROL

PC0 - PC7

DATA DIR.

REG. PORTC

XTAL1

XTAL2

RESET

ANALOG

COMPARATOR

DATA REGISTER

+

-

USART0

PORTE

CONTROL

LINES

DATA DIR.

REG. PORTE

PORTE DRIVERS

ALU

STATUS

REGISTER

DATA REGISTER

PORTB

PORTB DRIVERS

PB0 - PB7PE0 - PE7

DATA DIR.

REG. PORTB

EEPROM

SPI

DATA REGISTER

PORTD

PORTD DRIVERS

PD0 - PD7

USART1

DATA DIR.

REG. PORTD

TWO-WIRE SERIAL

INTERFACE

DATA REG.

PORTG

DATA DIR.

REG. PORTG

PORTG DRIVERS

PG0 - PG4

2467RS–AVR–06/08

3

The AVR core combines a rich instruction set with 32 general purpose working registers. All the

32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent

registers to be accessed in one single instruction executed in one clock cycle. The resulting

architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The ATmega128 provides the following features: 128K bytes of In-System Programmable Flash

with Read-While-Write capabilities, 4K bytes EEPROM, 4K bytes SRAM, 53 general purpose I/O

lines, 32 general purpose working registers, Real Time Counter ( RTC), four flexible

Timer/Counters with compare modes and PWM, 2 USARTs, a byte oriented Two-wire Serial

Interface, an 8-channel, 10-bit ADC with optional differential input stage with programmable

gain, programmable Watchdog Timer with Internal Oscillator, an SPI serial port, IEEE std.

1149.1 compliant JTAG test interface, also used for accessing the On-chip Deb ug system and

programming and six software selectable power saving modes. The Idle mode stops the CPU

while allowing the SRAM, Timer/Counters, SPI port, and interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the Oscillator, disabling all

other chip functions until the next interrupt or Hardware Reset. In Power-save mode, the asynchronous timer continues to run, allowing the user to maintain a timer base while the rest of the

device is sleeping. The ADC Noise Reduction mode stops the CPU and all I/O modules except

Asynchronous Timer and ADC, to minimize switchin g noise during ADC co nversions. In St andby

mode, the Crystal/Resonator Oscillator is running while the rest of the device is sleeping. This

allows very fast start-up combined with low power consumption. In Extended Standby mode,

both the main Oscillator and the Asynchronous Timer continue to run.

The device is manufactured using Atmel’s high-density nonvolatile memory technology. The Onchip ISP Flash allows the program memory to be reprogrammed in-system through an SPI serial

interface, by a conventional nonvolatile memory programmer, or by an On-chip Boot program

running on the AVR core. The boot program can use any interface to download the application

program in the application Flash memory. Software in the Boot Flash section will continue to run

while the Application Flash section is updated, providing true Read-While-Write operation. By

combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip,

the Atmel ATmega128 is a powerful microcontroller that pro vides a highly flexible and co st effective solution to many embedded control applications.

ATmega103 and ATmega128 Compatibility

4

ATmega128

The ATmega128 AVR is supported with a full suite of program and system development tools

including: C compilers, macro assemblers, program debugger/simulators, in-circuit emulators,

and evaluation kits.

The ATmega128 is a highly complex microcontroller where the number of I/O locations supersedes the 64 I/O locations reserved in the AVR instruction set. To ensure backward compatibility

with the ATmega103, all I/O locations present in ATmega103 have the sam e location in

ATmega128. Most additional I/O locati ons are a dded in a n Extended I/O space st arting fr om $60

to $FF, (i.e., in the ATmega103 internal RAM space). These locations can be reached by using

LD/LDS/LDD and ST/STS/STD instructions only, not by using I N and OUT instruct ions. The relocation of the internal RAM space may still be a problem for ATmega103 users. Also, the

increased number of interrupt vectors might be a problem if the code uses absolute addresses.

To solve these problems, an ATmega103 compatibility mode can be selected by programming

the fuse M103C. In this mode, none of the functi ons in the Ext ended I /O sp ace ar e in u se, so the

internal RAM is located as in ATmega103. Also, the Extended Interrupt vectors are removed.

The ATmega128 is 100% pin compatible with ATmega103, and can replace the ATmega103 on

current Printed Circuit Boards. The application note “Replacing ATmega103 by ATmega128”

describes what the user should be aware of replacing the ATmega103 by an ATmega128.

2467RS–AVR–06/08

ATmega128

ATmega103 Compatibility Mode

By programming the M103C fuse, the ATmega128 will be compatible with the ATmega103

regards to RAM, I/O pins and interrupt vectors as describe d above. However, some new fea tures in ATmega128 are not available in this compatibility mode, these features are listed below:

• One USART instead of tw o, Asynchronous mode only. Only the eight least significant bits of

the Baud Rate Register is available.

• One 16 bits Timer/Counter with two compare registers instead of two 16-bit Timer/Counters

with three compare registers.

• Two-wire serial interface is not supported.

• Port C is output only.

• Port G serves alternate functions only (not a general I/O port).

• Port F serves as digital input only in addition to analog input to the ADC.

• Boot Loader capabilities is not supported.

• It is not possible to adjust the frequency of the internal calibrated RC Oscillator.

• The External Memory Interface can not release any Address pins for general I/O, neither

configure different wait-states to different External Memory Address sections.

In addition, there are some other minor differences to make it more compatible to ATmega103:

• Only EXTRF and PORF exists in MCUCSR.

• Timed sequence not required for Watchdog Time-out change.

• External Interrupt pins 3 - 0 serve as level interrupt only.

• USART has no FIFO buffer, so data overrun comes earlier.

Unused I/O bits in ATmega103 should be written to 0 to ensure sa me operation in ATmega128.

Pin Descriptions

VCC Digital supply voltage. GND Ground. Port A (PA7..PA0) Port A is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The

Port A output buffers have symmetrical drive characteristics with both high sink and source

capability. As inputs, Port A pins that are externally pulled low will source current if the pull-up

resistors are activated. The Port A pins are tri-stated when a reset co ndition becomes active,

even if the clock is not running.

Port A also serves the functions of various special features of the ATmega128 as listed on page

73.

Port B (PB7..PB0) Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The

Port B output buffers have symmetrical drive characteristics with both high sink and source

capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up

resistors are activated. The Port B pins are tri-stated when a reset co ndition becomes active,

even if the clock is not running.

Port B also serves the functions of various special features of the ATmega128 as listed on page

74.

Port C (PC7..PC0) Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The

Port C output buffers have symmetrical drive characteristics with both high sink and source

capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up

2467RS–AVR–06/08

5

resistors are activated. The Port C pins are tri-stated when a reset condition becomes active,

even if the clock is not running.

Port C also serves the functions of special features of the ATmega128 as listed on page 77. In

ATmega103 compatibility mode, Port C is output only, and the port C pins are not tri-stated

when a reset condition becomes active.

Note: The ATmega128 is by default shipped in ATmega103 compatibility mode. Thus, if the parts are not

programmed before they are put on the PCB, POR TC will be output during first power up, and until

the ATmega103 compatibility mode is disabled.

Port D (PD7..PD0) Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The

Port D output buffers have symmetrical drive characteristics with both high sink and source

capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up

resistors are activated. The Port D pins are tri-stated when a reset condition becomes active,

even if the clock is not running.

Port D also serves the functions of various special features of the ATmega128 as listed on page

78.

Port E (PE7..PE0) Port E is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The

Port E output buffers have symmetrical drive characteristics with both high sink and source

capability. As inputs, Port E pins that are externally pulled low will source current if the pull-up

resistors are activated. The Port E pins are tri-stated when a reset co ndition becomes active,

even if the clock is not running.

Port E also serves the functions of various special features of the ATmega128 as listed on page

81.

Port F (PF7..PF0) Port F serves as the analog inputs to the A/D Converter.

Port F also serves as an 8-bit bi-directional I/O port, if the A/D Converter is not used. Port pins

can provide internal pull-up resistors (selected for each bit) . The Por t F outpu t buffers ha ve symmetrical drive characteristics with both high sink and source capability. As inputs, Port F pins

that are externally pulled low will source current if the pull-up resistors are activated. The Port F

pins are tri-stated when a res et cond ition beco mes a ctive, ev en if th e clock is not ru nning. If the

JTAG interface is enabled, the pull-up resistors on pins PF7(TDI), PF5(TMS), and PF4(TCK) will

be activated even if a Reset occurs.

The TDO pin is tri-stated unless TAP states that shift out data are entered.

Port F also serves the functions of the JTAG interface.

In ATmega103 compatibility mode, Port F is an input Port only.

Port G (PG4..PG0) Port G is a 5-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The

Port G output buffers have symmetrical drive characteristics with both high sink and source

capability. As inputs, Port G pins that are externally pulled low will source current if the pull-up

resistors are activated. The Port G pins are tri-stated when a reset condition becomes active,

even if the clock is not running.

Port G also serves the functions of various special features.

The port G pins are tri-stated when a reset condition becomes active, even if the clock is not

running.

In ATmega103 compatibility mode, these pins only serve s as strobes signals to the external

memory as well as input to the 32 kHz Oscillator, and the pins are initialized to PG0 = 1, PG1 =

1, and PG2 = 0 asynchronously when a reset condition becomes active, even if the clock is not

running. PG3 and PG4 are oscillator pins.

6

ATmega128

2467RS–AVR–06/08

ATmega128

RESET Reset input. A low level on this pin for longer than the minimum pulse length will generate a

reset, even if the clock is not running. The minimum pulse length is given in Table 19 on page

51. Shorter pulses are not guaranteed to gener ate a reset.

XTAL1 Input to the inverting Oscillator amplifier and input to the internal clock operating circuit. XTAL2 Output from the inverting Oscillator amplifier. AVCC AVCC is the supply voltage pin for Port F and the A/D Converter. It should be externally con-

nected to V

through a low-pass filter.

AREF AREF is the analog reference pin for the A/D Converter. PEN PEN is a programming enable pin for the SPI Serial Programming mode, and is internally pulled

high . By holding this pin low during a Power-on Reset, the device will enter the SPI Serial Programming mode. PEN

, even if the ADC is not used. If the ADC is used, it should be connected to V

CC

has no function during normal operation.

CC

2467RS–AVR–06/08

7

Resources A comprehensive set of development tools, application notes, and datasheets are available for

download on http://www.atmel.com/avr.

ATmega128/L rev. A - M characterization is found in the ATmega128 Appendix A.

Note: 1.

Data Retention Reliability Qualification results show that the projected data retention failure rate is much less

than 1 PPM over 20 years at 85°C or 100 years at 25°C.

8

ATmega128

2467RS–AVR–06/08

Loading...

Loading...