Page 1

AT91SAM9263-EK Evaluation Board

....................................................................................................................

User Guide

6279C–ATARM–02-Jul-07

Page 2

Page 3

Table of Contents

Section 1

Overview .................................................................................................................... 1-1

1.1 Scope................................................................................................................................. 1-1

1.2 Deliverables ....................................................................................................................... 1-1

1.3 AT91SAM9263-EK Evaluation Board ................................................................................ 1-1

Section 2

Setting Up the AT91SAM9263-EK Board................................................................... 2-1

2.1 Electrostatic Warning ......................................................................................................... 2-1

2.2 Requirements..................................................................................................................... 2-1

2.3 Layout ................................................................................................................................ 2-1

2.4 Powering Up the Board...................................................................................................... 2-4

2.5 Backup Power Supply........................................................................................................ 2-4

2.6 Getting Started................................................................................................................... 2-4

2.7 AT91SAM9263-EK Block Diagram .................................................................................... 2-5

Section 3

Board Description.......................................................................................................3-1

3.1 AT91SAM9263 Microcontroller .......................................................................................... 3-1

3.2 AT91SAM9263 Block Diagram .......................................................................................... 3-4

3.3 Memory.............................................................................................................................. 3-5

3.4 Clock Circuitry.................................................................................................................... 3-5

3.5 Reset Circuitry ................................................................................................................... 3-5

3.6 Shutdown Controller ..........................................................................................................3-5

3.7 Power Supply Circuitry.......................................................................................................3-5

3.8 Remote Communication .................................................................................................... 3-5

3.9 Audio Stereo Interface .......................................................................................................3-6

3.10 User Interface .................................................................................................................... 3-6

3.11 Debug Interface ................................................................................................................. 3-6

3.12 Expansion Slot................................................................................................................... 3-6

3.13 PIO Usage ......................................................................................................................... 3-7

Section 4

Configuration..............................................................................................................4-1

4.1 Configuration Jumpers and Straps .................................................................................... 4-1

Section 5

Schematics.................................................................................................................5-1

AT91SAM9263-EK Evaluation Board User Guide i

6279C–ATARM–02-Jul-07

Page 4

Table of Contents (Continued)

5.1 Schematics ........................................................................................................................ 5-1

Section 6

Warning......................................................................................................................6-1

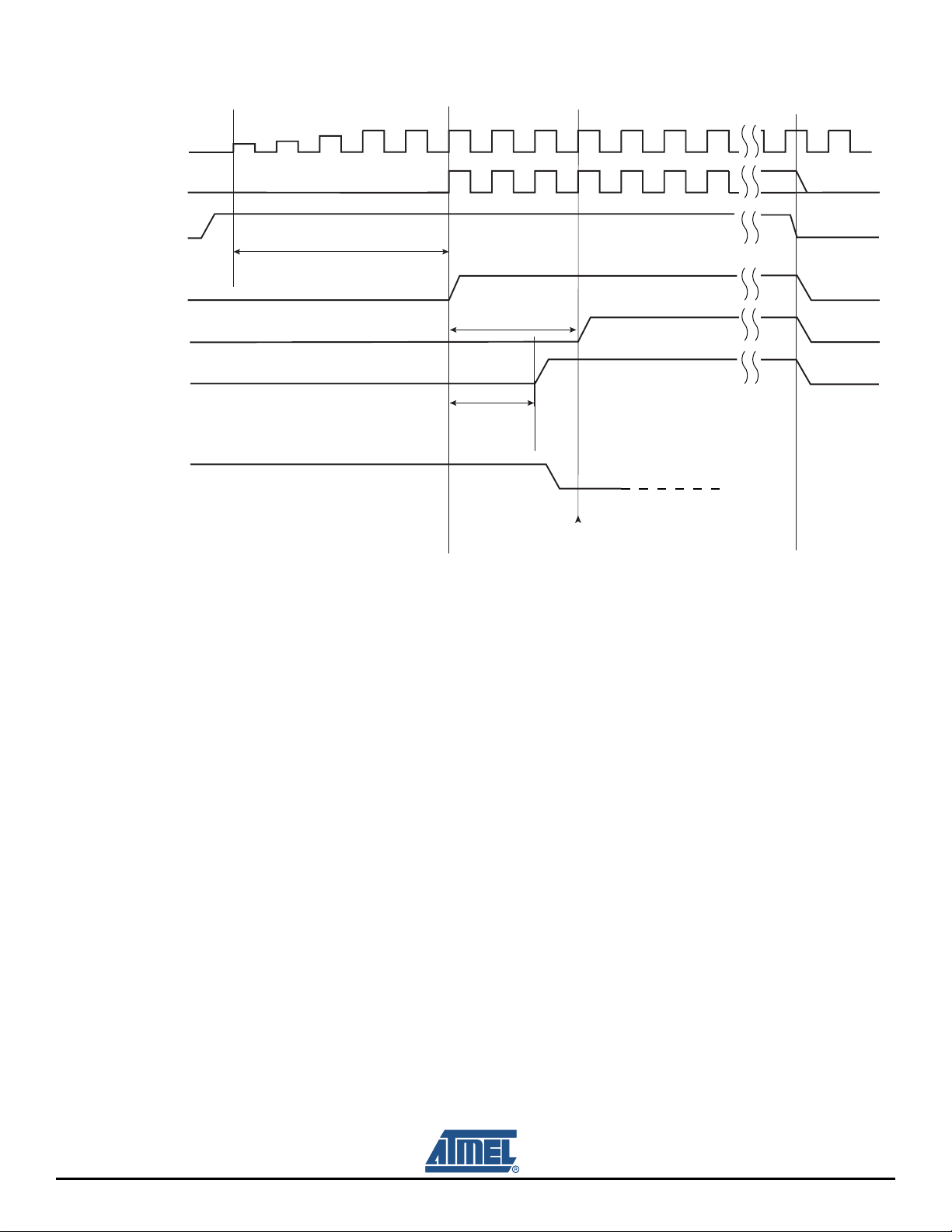

6.1 BMS Signal Sampling ........................................................................................................ 6-1

Section 7

Errata..........................................................................................................................7-1

7.1 JTAGSEL S1 Footprint Selector ........................................................................................ 7-1

7.2 PIO Usage ......................................................................................................................... 7-1

7.3 TWI line pullups for Fast Mode operation .......................................................................... 7-1

Section 8

Revision History .........................................................................................................8-1

8.1 Revision History ................................................................................................................. 8-1

ii AT91SAM9263-EK Evaluation Board User Guide

6279C–ATARM–02-Jul-07

Page 5

1.1 Scope

The AT91SAM9263-EK evaluation kit enables the evaluation of and code development for applications

running on an AT91SAM9263.

This guide focuses on the AT91SAM9263-EK board as an evaluation platform.

1.2 Deliverables

The AT91SAM9263-EK package contains the following items:

! an AT91SAM9263-EK board

! one A/B-type USB cable

! one serial RS232 cable

! one RJ45 crossed Ethernet cable

! one CD-ROM that allows the user to begin evaluating the AT91 ARM

quickly.

Section 1

Overview

®

Thumb® 32-bit microcontroller

1.3 AT91SAM9263-EK Evaluation Board

The board is equipped with an AT91SAM9263 (324-ball LFBGA package) together with the following:

! 64 Mbytes of SDRAM memory

! 4 Mbytes of PSRAM memory on EBI1

! 256 Mbytes of NANDFlash memory

! One NOR Flash memory (footprint only)

! One 1.8” Hard disk connectors

! One TWI serial memory

! One USB device port interface

! Two USB Host port interfaces

! One RS232 serial communication port

! One DBGU serial communication port

! One serial CAN 2.0B communication port

! One JTAG/ICE debug interface

! One Ethernet 100-base TX with three status LEDs

! One AC97 Audio DAC

AT91SAM9263-EK Evaluation Board User Guide 1-1

6279C–ATARM–02-Jul-07

Page 6

Overview

! One 3.5" 1/4 VGA TFT LCD Module with TouchScreen and backlight

! One ISI connector (camera interface)

! One Power LED and two general-purpose LEDs

! Two user input push buttons

! One Wakeup input push button

! One reset push button

! One DataFlash

! One SD/SDIO/MMC card slot

! One Lithium Coin Cell Battery Retainer for 12 mm cell size

®

/SD/SDIO/MMC card slot

1-2 AT91SAM9263-EK Evaluation Board User Guide

6279C–ATARM–02-Jul-07

Page 7

2.1 Electrostatic Warning

The AT91SAM9263-EK evaluation board is shipped in protective anti-static packaging. The board must

not be subjected to high electrostatic potentials. A grounding strap or similar protective device should be

worn when handling the board. Avoid touching the component pins or any other metallic element.

2.2 Requirements

In order to set up the AT91SAM9263-EK evaluation board, the following items are needed:

! the AT91SAM9263-EK evaluation board itself.

! AC/DC power adapter (12V at 1A), 2.1 mm by 5.5 mm

2.3 Layout

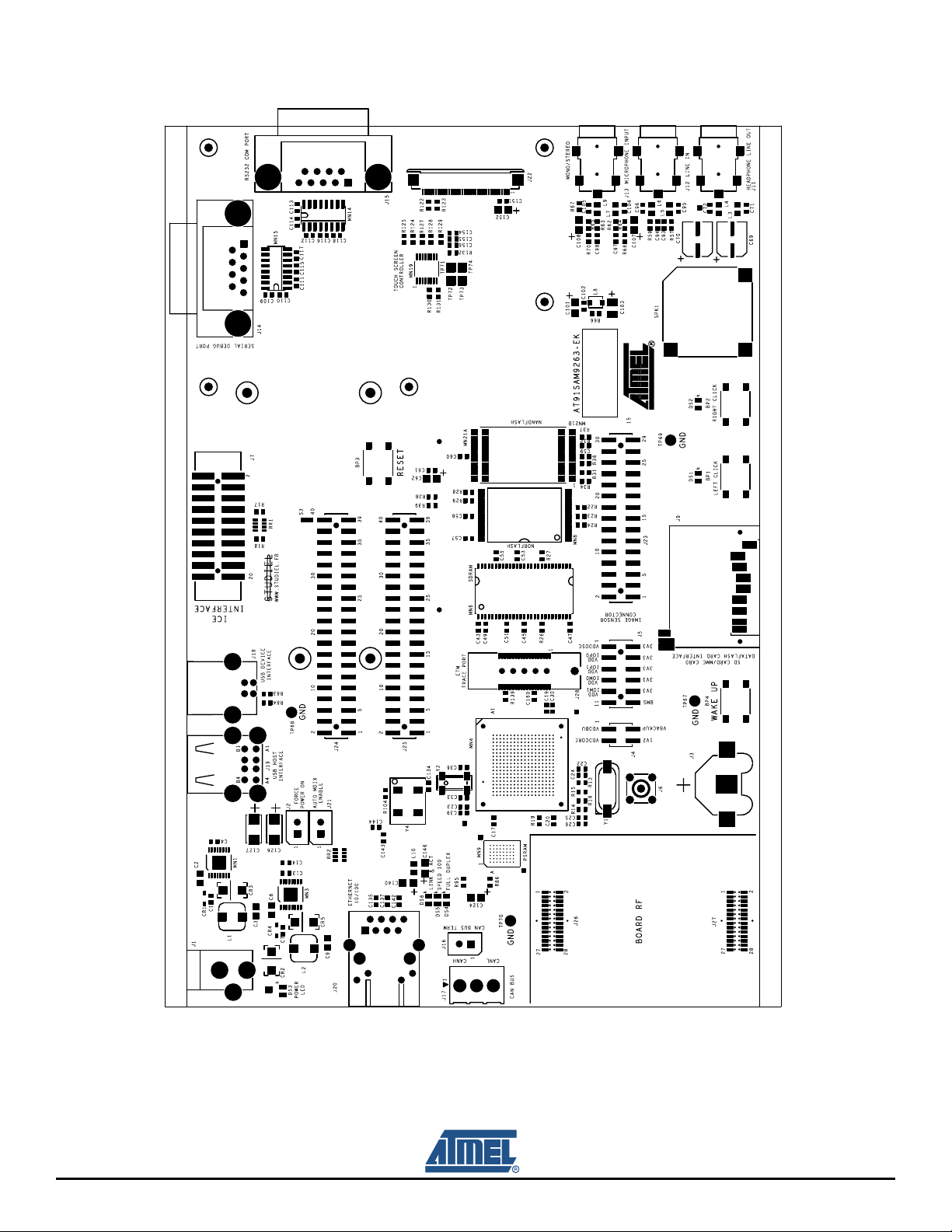

See Figures 2-1 and 2-2.

Section 2

Setting Up the AT91SAM9263-EK Board

AT91SAM9263-EK Evaluation Board User Guide 2-1

6279C–ATARM–02-Jul-07

Page 8

Setting Up the AT91SAM9263-EK Board

Figure 2-1. AT91SAM9263-EK Layout - Top View

2-2 AT91SAM9263-EK Evaluation Board User Guide

6279C–ATARM–02-Jul-07

Page 9

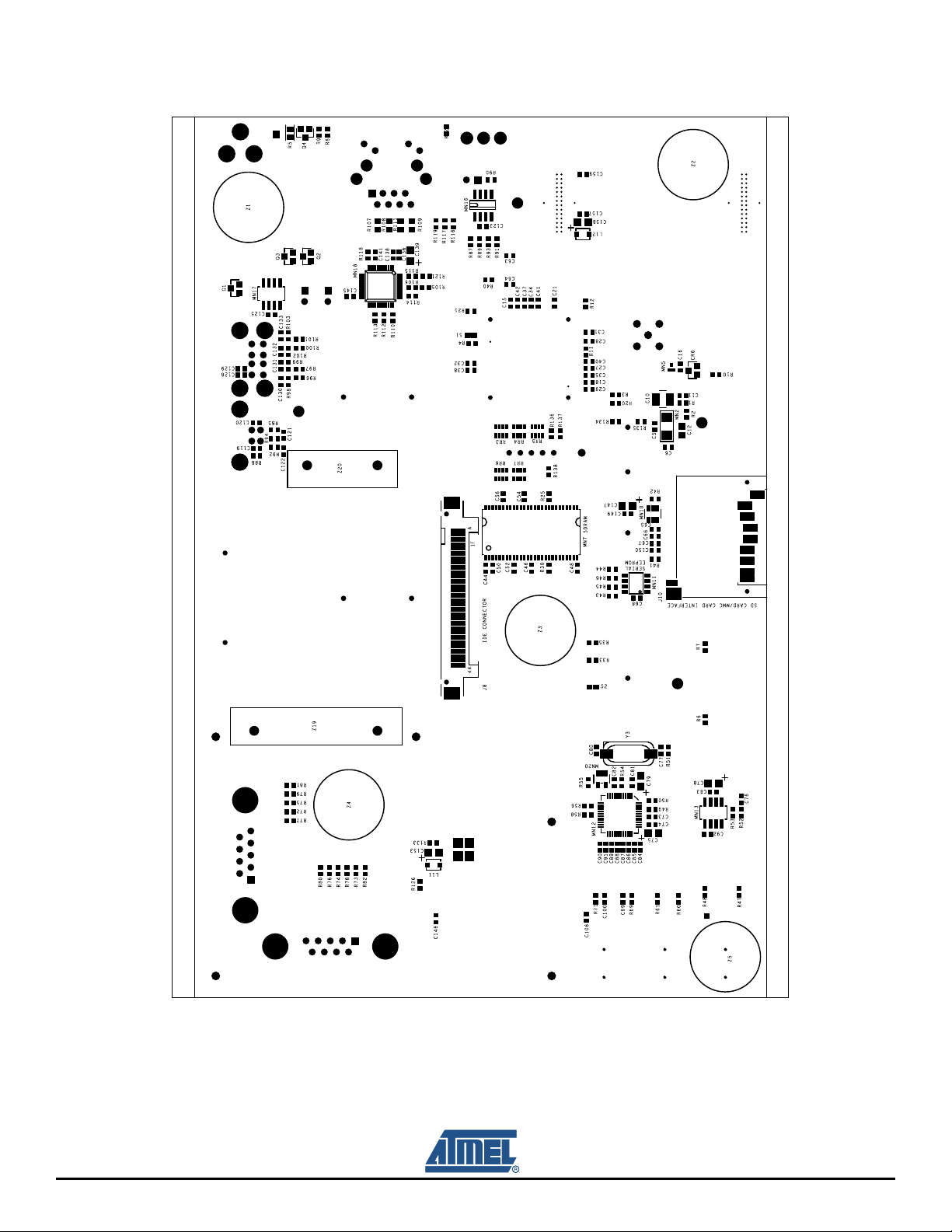

Figure 2-2. AT91SAM9263-EK Layout - Bottom View

Setting Up the AT91SAM9263-EK Board

AT91SAM9263-EK Evaluation Board User Guide 2-3

6279C–ATARM–02-Jul-07

Page 10

Setting Up the AT91SAM9263-EK Board

2.4 Powering Up the Board

The AT91SAM9263-EK requires 12V DC. DC power is supplied to the board via the 2.1 mm by 5.5 mm

socket J1. Coaxial plug center positive standard.

2.5 Backup Power Supply

The user has the possibility to plug a battery (3V Lithium Battery CR1225 or equivalent) in order to permanently power the backup part of the device.

2.6 Getting Started

The AT91SAM9263-EK evaluation board is delivered with a CD-ROM that allows the user to begin evaluation of the AT91 ARM Thumb 32-bit microcontroller quickly. Please refer to the AT91 web site,

http://www.atmel.com/products/AT91/, for the most up-to-date information on getting started with the

AT91SAM9263-EK.

2-4 AT91SAM9263-EK Evaluation Board User Guide

6279C–ATARM–02-Jul-07

Page 11

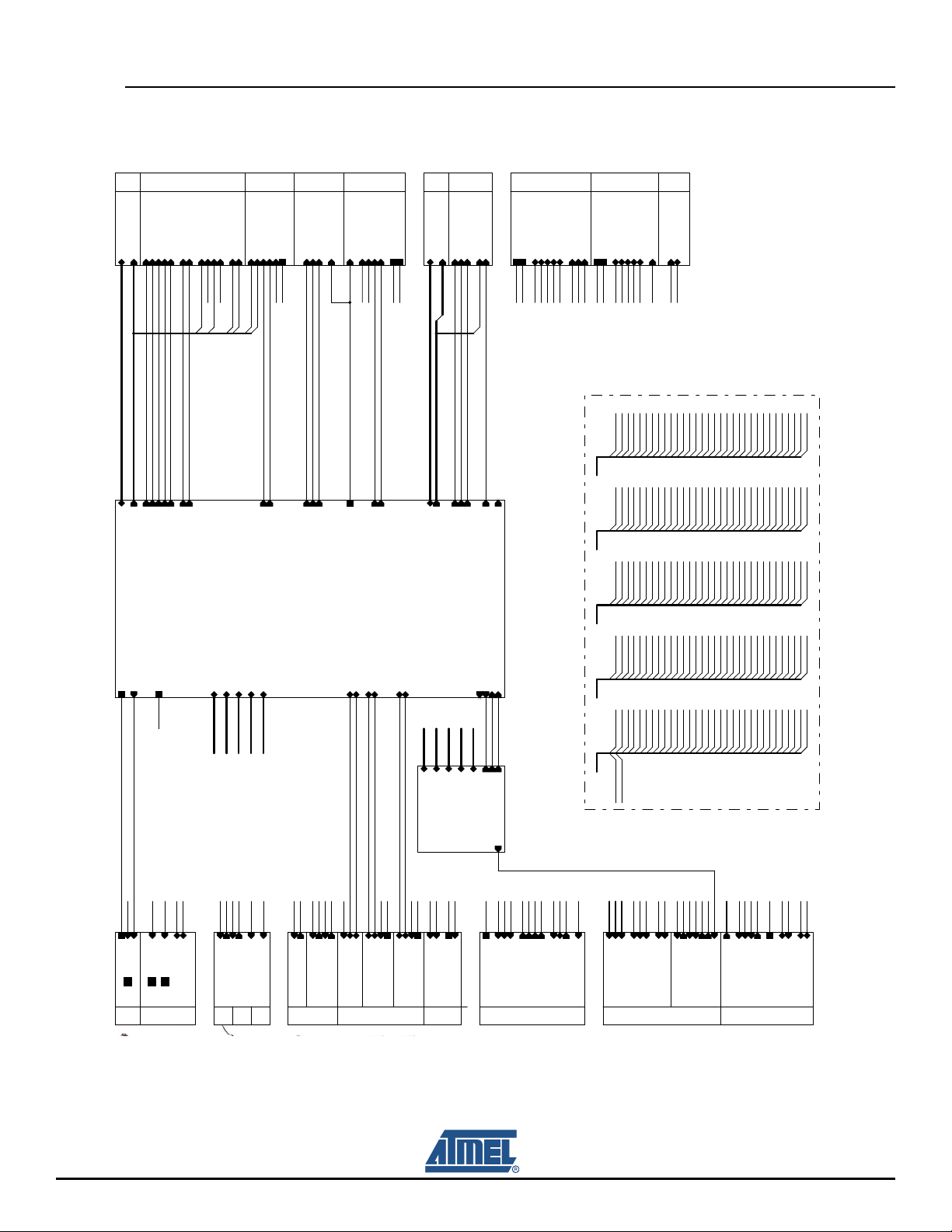

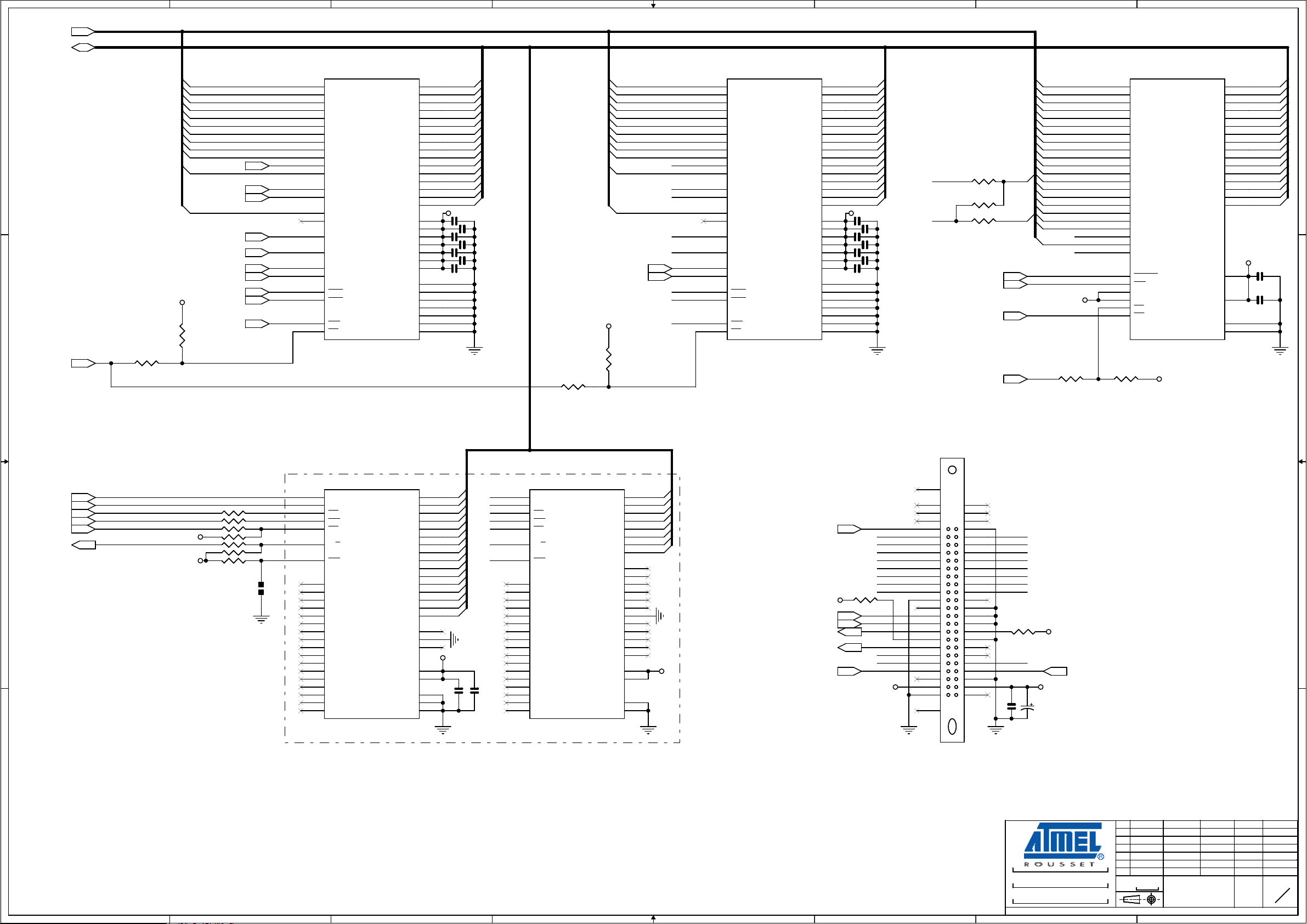

2.7 AT91SAM9263-EK Block Diagram

Figure 2-3. AT91SAM9263-EK Block Diagram

EBI0

SDRAMNANFLASH

NORFLASH1.8" HDD

EBI1PSRAM

Setting Up the AT91SAM9263-EK Board

DATAFLASH

MMC SD/SDIOMMC SD/SDIO

EEPROM

SERIAL

RAS

CAS

SDA10

D[0..31]

A[0..22]

EBI0 MEMORY

EBI0_D[0..31]

EBI0_A[0..22]

EBI0_RAS

EBI0_CAS

EBI0_SDA10

EBI0_A[0..22]

EBI0_D[0..31]

SHDN

VDDISI

VDDBU

AT91SAM9263_BGA324

CARD

READER

SDWE

SDCKE

SDCK

NBS3

NBS1

SDCS

NBS0

NBS2

EBI0_NBS1

EBI0_A1

EBI0_NBS3

EBI0_A0

EBI0_SDCK

EBI0_SDWE

EBI0_SDCKE

EBI0_NCS1/SDCS

PA[0..31]

PB[0..31]

EBI0_A16

BA0

EBI0_A17

NANDOE

NANDWE

NANDCS

RDYBSY

ALE

CLE

BA1

EBI0_A22

PD15

PA22

EBI0_A21

EBI0_NANDOE

EBI0_NANDWE

PC[0..31]

PD[0..31]

PE[0..31]

NCS

NWE

EBI0_NCS0

EBI0_NWE/NWR0/CFWE

NRST

NRD

RESET-

DIOR-

INTRQ

CS1-

IORDY

CS0-

DIOW-

03 - EBI0 MEMORY

EBI1 MEMORY

EBI0_CFCE1

EBI0_CFCE2

PD2

PD3

EBI0_NBS1

EBI0_NBS3

NRST

NRST

EBI0_NRD/CFOE

EBI0_NBS1/NW1/CFIOR

EBI0_NBS3/NW3/CFIOW

HDMA

DDM

HDMB

DDP

HDPA

HDPB

NOE

NWRUBLB

NCS

D[0..15]

A[1..21]

EBI1_A[1..21]

EBI1_D[0..15]

EBI1_A[0..21]

EBI1_A[0..21]

EBI1_D[0..15]

EBI1_NCS0

EBI1_NWE/NWR0/CFWE

04 - EBI1 MEMORY

MCI & TWI

EBI1_A0

EBI1_SDCK

EBI1_NRD/CFOE

EBI1_NBS1/NW1/CFIOR

SIGQ

SIGI

CK16M

PPS

02 - MICROCONTROLLER

PE16

MCI0_DA3

MCI0_DA0

MCI0_DA1

MCI0_DA2

MCI0_CDA

MCI0_WP

MCI0_CD

MCI0_DA0

MCI0_DA1

PE17

MCI0_DA3

MCI0_CDA

MCI0_DA2

MCI0_CK

MCI0_CK

SPI0_SPCK

SPI0_SPCK

CKSEL

PE20

PE18

PE[0..31]

PD[0..31]

PC[0..31]

PB[0..31]

CARD

READER

SDA

MCI1_DA2

MCI1_DA3

PE3 ISI_D3

(IORDY)

PD3

PC3 LCDDEN

PB3 AC97RX

MCI1_DA3

MCI1_CDA

PE4 ISI_D4

PD4

(RIGHTCLIC)

PC4

PB4 TWD

SCL

MCI1_CDA

MCI1_CK

05 - MCI & TWI

TWCK

TWD

MCI1_CK

(MCI0_CD)

(MCI0_WP)

(CKSEL)

(MCI1_WP)

(MCI1_CD)

PE5 ISI_D5

PE6 ISI_D6

PE7 ISI_D7

PE9 ISI_HS YNC

PE10 ISI_VSYNC

PE11 ISI_MCK

PE8 ISI_PCK

PE13 ISI_D9

PE14 ISI_D10

PE15 ISI_D11

PE12 ISI_D8

PE17

PE18

PE19

PE16

PE21 ETXCK

PE22

PE23 ETX0

PE20

(NANDCS)

PD5

PD6

PD7

PD9 EBI0_CFCE2

PD10

PD11

PD8 EBI0_CFCE1

PD13

PD14

PD15

PD12

PD17

PD18

PD19

PD16

PD21

PD22

PD23

PD20

(LEFTCLIC)

PC5

PC6 LCDD2

PC7 LCDD3

PC9 LCDD5

PC10 LCDD6

PC11 LCDD7

PC8 LCDD4

PC13

PC14 LCDD10

PC15 LCDD11

PC12 LCDD13

PC17 LCDD21

PC18 LCDD14

PC19 LCDD15

PC16 LCDD12

PC21

PC22 LCDD18

PC23 LCDD19

PC20

PB5 TWCK

PB6

PB7 PWM0

PB9 LCDCC

PB10 PCK1

PB11 SPI0_NPCS3

PB8 PWM1

PB13

PB14

PB15

PB12

PB17

PB18

PB19

PB16

PB21

PB22

PB23

PB20

PE25 ERX0

PE24 ETX1

PD25

PD24

PC25 ERXDV

PC24 LCDD20

PB25

PB24

PE26 ERX1

PE27 ERXER

PD26

PD27

PC26 LCDD22

PC27 LCDD23

PB26

PB27

PE28 ETXEN

PD28

PC28

PB28

PE29 EMDC

PD29

PC29 PWM2

PB29

PE30 EMDIO

PD30

PC30 DRXD

PB30

(MDINTR)

PE31

PD31

PC31 DTXD

PB31

MCI1_WP

MCI1_CD

MCI1_DA0

MCI1_DA1

PE19

MCI1_DA0

MCI1_DA1

MCI1_DA2

PE1 ISI_D1

PE2 ISI_D2

PE0 ISI_D0

(INTRQ)

PD1

PD2

PD0

PC1 LCDHSYNC

PC2 LCDDOTCK

PC0

PB1 AC97CK

PB2 AC97TX

PB0 AC97FS

VDDISI

PA[0..31]

PB[0..31]

PC[0..31]

PD[0..31]

PE[0..31]

PB[0..31]

PC[0..31]

PD[0..31]

PA[0..31]

PE[0..31]

SIGI

SIGQ

PB[0..31]

PA[0..31]

CLK16M

PE[0..31]

PC[0..31]

PD[0..31]

PA0 MCI0_DA0

PA1 MCI0_CDA

PA2 SPI0_SPCK

PA3 MCI0_DA1

PA5 MCI0_DA3

PA6 MCI1_CK

PA7 MCI1_CDA

PA4 MCI0_DA2

PA9 MCI1_DA1

PA10 MCI1_DA2

PA11 MCI1_DA3

PA8 MCI1_DA0

PA13 CANTX

PA14 CANRX

PA12 MCI0_CK

PA[0..31]

PA0SPI0_MISO

PA1SPI0_MOSI

(RDYBSY)

(CANRS)

(CANRXEN)

(CTRL1)

(CTRL2)

(FLGB)

(ENB)

(FLGA)

PA15 IRQ1

PA17

PA18

PA19

PA16

PA21

PA22

PA23

PA20

(ENA)

PA24

(USBCNX)

PA25

(BUSY)

(PCI)

PA26 TXD0

PA27 RXD0

PA29 CTS0

PA30

PA31

PA28 RTS0

PIO USAGE

CANTX

07 - COMMUNICATION

ETXCK

ETX1

TX_CLK

RMII ETHERNET

RFTS

10 - EXPANSION CONNECTORS

ETX0

ETXEN

ERX1

ERX0

TXD0

TXD1

RXD1

TX_EN

RXD0

ERXDV

ERXER

RX_ER

RX_DV

NRST

PE31

EMDC

EMDIO

MDC

MDIO

NRST

MDINTR

10/100 FAST ETHERNET

LCDD[2..7]

LCD & CAMERA INTERFACE

08 - ETHERNET

LCDD[10..15]

LCDD[18..23]

LCDCC

PA30

LCDHSYNC

LCDDEN

LCDDOTCK

SPI0_MOSI

PCI

DCLK

B[0..5]

DTMG

R[0..5]

G[0..5]

VCTRL

HSYNC

3.5" QVGA

MOSI

SPI0_MISO

SPI0_SPCK

MISO

SPCK

TOUCH SCREEN

LCD INTERFACE

SPI0_NPCS3

IRQ1

IRQ

NPCS

CONTROLLER

PA31

BUSY

RFTS

ISI_D[0..11]

ISI_PCK

ISI_MCK

ISI_VSYNC

ISI_HSYNC

TWCK

TWD

PA17

PA16

VDDISI

SCL

SDA

CTRL1

CTRL2

VDDISI

ISI_PCK

ISI_MCK

ISI_VSYNC

ISI_HSYNC

ISI_D[0..11]

ISI

CAMERA INTERFACE

09 - LCD & CAMERA INTERFACE

PWM0

VDDBU

POWER SUPPLY

POWERLED

SHDN

12VDC

PWM1

PWM2

USERLED1

PC4

PC5

USERLED2

RIGHTCLIC

USER'S

LEFTCLIC

INTERFACE

01 - POWER SUPPLY

AC97

AC97CK

AC97FS

SYNC

AC97TX

BITCLK

AC97RX

SDATA_IN

SDATA_OUT

EXPANSION CONNECTORS

DTXD

DRXD

TXD0

RTS0

RXD0

CTS0

PA25

PA24

DDM

USBCNX

DEVICE

PA23

ENA

DDP

FLGA

HDPA

HDMA

HOST A

USB

PCK1

NRST

CTS

RTS

TXD

DTXD

DRXD

DBGU

SERIAL INTERFACES

RXD

COM0

RS232

RST#

EXT_CLK

AUDIO

MIC OUTIN

06 - AUDIO

PA21

HDPB

HDMB

HOST B

CANRX

CANTX

PA19

PA18

PA20

ENB

FLGB

CANRX

CANRS

CANRXEN

CAN

AT91SAM9263-EK Evaluation Board User Guide 2-5

6279C–ATARM–02-Jul-07

Page 12

Setting Up the AT91SAM9263-EK Board

2-6 AT91SAM9263-EK Evaluation Board User Guide

6279C–ATARM–02-Jul-07

Page 13

3.1 AT91SAM9263 Microcontroller

! Incorporates the ARM926EJ-S

– DSP Instruction Extensions, Jazelle

– 16 Kbyte Data Cache, 16 Kbyte Instruction Cache, Write Buffer

– 200 MIPS at 180 MHz

– Memory Management Unit

– EmbeddedICE

– Mid-level Implementation Embedded Trace Macrocell

! Bus Matrix

– Nine 32-bit-layer Matrix, Allowing a Total of 28.8 Gbps of On-chip Bus Bandwidth

– Boot Mode Select Option, Remap Command

! Embedded Memories

– One 128 Kbyte Internal ROM, Single-cycle Access at Maximum Bus Matrix Speed

– One 80 Kbyte Internal SRAM, Single-cycle Access at Maximum Processor Bus Matrix Speed

– One 16 Kbyte Internal SRAM, Single-cycle Access at Maximum Bus Matrix Speed

! Dual External Bus Interface (EBI0 and EBI1)

– EBI0 Supports SDRAM, Static Memory, ECC-enabled NAND Flash and CompactFlash

– EBI1 Supports SDRAM, Static Memory and ECC-enabled NAND Flash

! DMA Controller (DMAC)

– Acts as one Bus Matrix Master

– Embeds 2 Unidirectional Channels with Programmable Priority, Address Generation, Channel

Buffering and Control

! Twenty Peripheral DMA Controller Channels (PDC)

! LCD Controller

– Supports Passive or Active Displays

– Up to 24 bits per Pixel in TFT Mode, Up to 16 bits per Pixel in STN Color Mode

– Up to 16M Colors in TFT Mode, Resolution Up to 2048x2048, Supports Virtual Screen Buffers

! 2D Graphics Accelerator

– Line Draw, Block Transfer, Polygon Fill, Clipping, Commands Queuing

! Image Sensor Interface

– ITU-R BT. 601/656 External Interface, Programmable Frame Capture Rate

– 12-bit Data Interface for Support of High Sensibility Sensors

– SAV and EAV Synchronization, Preview Path with Scaler, YCbCr Format

™

, Debug Communication Channel Support

™

ARM® Thumb® Processor

®

Tec hn ol ogy fo r J ava® Acceleration

Section 3

Board Description

™

®

AT91SAM9263-EK Evaluation Board User Guide 3-1

6279C–ATARM–02-Jul-07

Page 14

Board Description

! USB 2.0 Full Speed (12 Mbits per second) Host Double Port

– Dual On-chip Transceivers

– Integrated FIFOs and Dedicated DMA Channels

! USB 2.0 Full Speed (12 Mbits per second) Device Port

– On-chip Transceiver, 2,432-byte Configurable Integrated DPRAM

! Ethernet MAC 10/100 Base-T

– Media Independent Interface or Reduced Media Independent Interface

– 28-byte FIFOs and Dedicated DMA Channels for Receive and Transmit

! Fully-featured System Controller, including

– Reset Controller, Shutdown Controller

– Twenty 32-bit Battery Backup Registers for a Total of 80 Bytes

– Clock Generator and Power Management Controller

– Advanced Interrupt Controller and Debug Unit

– Periodic Interval Timer, Watchdog Timer and Double Real-time Timer

! Reset Controller (RSTC)

– Based on Two Power-on Reset Cells, Reset Source Identification and Reset Output Control

! Shutdown Controller (SHDWC)

– Programmable Shutdown Pin Control and Wake-up Circuitry

! Clock Generator (CKGR)

– 32768Hz Low-power Oscillator on Battery Backup Power Supply, Providing a Permanent Slow

Clock

– 3 to 20 MHz On-chip Oscillator and Two Up to 240 MHz PLLs

! Power Management Controller (PMC)

– Very Slow Clock Operating Mode, Software Programmable Power Optimization Capabilities

– Four Programmable External Clock Signals

! Advanced Interrupt Controller (AIC)

– Individually Maskable, Eight-level Priority, Vectored Interrupt Sources

– Two External Interrupt Sources and One Fast Interrupt Source, Spurious Interrupt Protected

! Debug Unit (DBGU)

– 2-wire UART and Support for Debug Communication Channel, Programmable ICE Access

Prevention

! Periodic Interval Timer (PIT)

– 20-bit Interval Timer plus 12-bit Interval Counter

! Watchdog Timer (WDT)

– Key-protected, Programmable Only Once, Windowed 16-bit Counter Running at Slow Clock

! Two Real-time Timers (RTT)

– 32-bit Free-running Backup Counter Running at Slow Clock with 16-bit Prescaler

! Five 32-bit Parallel Input/Output Controllers (PIOA, PIOB, PIOC, PIOD and PIOE)

– 160 Programmable I/O Lines Multiplexed with Up to Two Peripheral I/Os

– Input Change Interrupt Capability on Each I/O Line

– Individually Programmable Open-drain, Pull-up Resistor and Synchronous Output

! One Part 2.0A and Part 2.0B-compliant CAN Controller

3-2 AT91SAM9263-EK Evaluation Board User Guide

6279C–ATARM–02-Jul-07

Page 15

– 16 Fully-programmable Message Object Mailboxes, 16-bit Time Stamp Counter

! Two Multimedia Card Interface (MCI)

– SDCard/SDIO and MultiMediaCard

™

Compliant

– Automatic Protocol Control and Fast Automatic Data Transfers with PDC

– Two SDCard Slots Support on eAch Controller

! Two Synchronous Serial Controllers (SSC)

– Independent Clock and Frame Sync Signals for Each Receiver and Transmitter

– I²S Analog Interface Support, Time Division Multiplex Support

– High-speed Continuous Data Stream Capabilities with 32-bit Data Transfer

! One AC97 Controller (AC97C)

– 6-channel Single AC97 Analog Front End Interface, Slot Assigner

! Three Universal Synchronous/Asynchronous Receiver Transmitters (USART)

– Individual Baud Rate Generator, IrDA

®

Infrared Modulation/Demodulation, Manchester

Encoding/Decoding

– Support for ISO7816 T0/T1 Smart Card, Hardware Handshaking, RS485 Support

! Two Master/Slave Serial Peripheral Interface (SPI)

– 8- to 16-bit Programmable Data Length, Four External Peripheral Chip Selects

– Synchronous Communications at Up to 90Mbits/sec

! One Three-channel 16-bit Timer/Counters (TC)

– Three External Clock Inputs, Two Multi-purpose I/O Pins per Channel

– Double PWM Generation, Capture/Waveform Mode, Up/Down Capability

! One Four-channel 16-bit PWM Controller (PWMC)

! One Two-wire Interface (TWI)

– Master Mode Support, All Two-wire Atmel

! IEEE

! Required Power Supplies

®

1149.1 JTAG Boundary Scan on All Digital Pins

®

EEPROMs Supported

– 1.08V to 1.32V for VDDCORE and VDDBU

– 3.0V to 3.6V for VDDOSC, VDDPLL and VDDIOP0 (Peripheral I/Os)

– 1.65V to 3.6V for VDDIOP1 (Peripheral I/Os)

– Programmable 1.65V to 1.95V or 3.0V to 3.6V for VDDIOM0/VDDIOM1 (Memory I/Os)

! Available in a 324-ball BGA Green Package

Board Description

AT91SAM9263-EK Evaluation Board User Guide 3-3

6279C–ATARM–02-Jul-07

Page 16

6279C–ATARM–02-Jul-07

3-4 AT91SAM9263-EK Evaluation Board User Guide

3.2 AT91SAM9263 Block Diagram

Board Description

Figure 3-1. AT91SAM9263 Block Diagram

SLAVEMASTER

TDI

NTRST

TDO

TMS

TCK

JTAGSEL

RTCK

TCLK

TSYNC

BMS

TPS0-TPS2

TPK0-TPK15

LCDHSYNC

LCDCC

LCDDOTCK

LCDD0-LCDD23

LCDDEN

LCDVSYNC

ERXER-ERXDV

ETXCK-ERXCK-EREFCK

ETXEN-ETXER

ECRS-ECOL

ERX0-ERX3

EMDC

ETX0-ETX3

EF100

EMDIO

HDPA

HDMA

HDMB

HDPB

TST

FIQ

IRQ0-IRQ1

DRXD

DTXD

PCK0-PCK3

PLLRCA

PLLRCB

XIN

XOUT

VDDCORE

VDDBU

XIN32

XOUT32

SHDN

WKUP

VDDCORE

NRST

PLLA

PLLB

OSC

OSC

POR

POR

System

Controller

20GPREG

SHDWC

PDC

MCI0

MCI1

AIC

DBGU

PDC

PMC

PITWDT

RTT0

RTT1

RSTC

TWI

JTAG Boundary Scan

In-Circuit

ARM926EJ-S Processor

Emulator

TCM Interface

ITCM DTCM

Fast SRAM

80 Kbytes

PIOA

PIOB

PIOC

PIOD

PIOE

PDC

USART0

USART1

USART2

SRAM

16 Kbytes

CAN

ICache

16K bytes

128 Kbytes

MMU

Bus Interface

ROM

SPI0

SPI1

DCache

16K bytes

ID

Peripheral

PDC

Bridge

PWMC

ETM

LCD

Controller

LUT

DMA

9-layer Bus Matrix

20-channel

Peripheral

DMA

PDC

TC0

AC97C

TC1

TC2

FIFO

10/100 Ethernet

2-channel

DMA

APB

PDC

SSC0

SSC1

FIFO

MAC

DMA

USB

Device

Transc.

FIFO

DMA

2D

Graphics

Controller

Port

Transc.

USB

OHCI

DMA

DMA

Image

Sensor

Interface

Transc.

EBI0

CompactFlash

NAND Flash

SDRAM

Controller

Static

Memory

Controller

ECC

Controller

EBI1

NAND Flash

SDRAM

Controller

Static

Memory

Controller

ECC

Controller

D0-D15

A0/NBS0

A1/NBS2/NWR2

A2-A15, A18-A20

A16/BA0

A17/BA1

NCS0

NCS1/SDCS

NRD

NWR0/NWE

NWR1/NBS1

NWR3/NBS3

SDCK, SDCKE

RAS, CAS

SDWE, SDA10

NANDOE, NANDWE

A21/NANDALE

A22/NANDCLE

NWAIT

A23-A24

NCS4/CFCS0

NCS5/CFCS1

NCS3/NANDCS

A25/CFRNW

CFCE1-CFCE2

D16-D31

NCS2

D0-D15

A0/NBS0

A1/NWR2

A2-A15/A18-A20

A16/BA0

A17/BA1

NCS0

NRD

NWR0/NWE

NWR1/NBS1

SDCK

A21/NANDALE

A22/NANDCLE

NWAIT

NWR3/NBS3

NCS1/SDCS

NCS2/NANDCS

D16-D31

SDCKE

RAS, CAS

SDWE, SDA10

NANDOE, NANDWE

EBI0_

EBI1_

CDB

DA0-DA3

DB0-DB3

CDA

CK

TWD

TWCK

CTS0-CTS2

RTS0-RTS2

SCK0-SCK2

TXD0-TXD2

RDX0-RDX2

CANTX

CANRX

NPCS2

NPCS3

SPI0_, SPI1_MCI0_, MCI_1

NPCS1

NPCS0

MOSI

SPCK

MISO

PWM0-PWM3

TCLK0-TCLK2

AC97CK

TIOA0-TIOA2

TIOB0-TIOB2

AC97TX

AC97FS

AC97RX

TF0-TF1

TK0-TK1

TD0-TD1

RD0-RD1

DMARQ0_DMARQ3

RF0-RF1

RK0-RK1

DDP

DDM

ISI_PCK

ISI_VSYNC

ISI_HSYNC

ISI_D0-ISI_D11

ISI_MCK

Page 17

3.3 Memory

! 16 Kbytes of Internal data cache

! 16 Kbytes of Internal instruction cache

! 128 Kbytes of Internal ROM

! 80 Kbytes of Internal single-cycle access high-speed SRAM

! 16 Kbytes of Internal single-cycle access high-speed SRAM

! 8 Mbytes of Atmel NOR Flash (not populated)

! 64 Mbytes of SDRAM memory

! 4 Mbytes of PSRAM (EBI1)

! 256 Mbytes of NANDFlash memory

! Atmel TWI serial EEPROM

3.4 Clock Circuitry

! 16.36766 MHz standard crystal for the embedded oscillator

! 32.768 kHz standard crystal for the slow clock oscillator

Board Description

3.5 Reset Circuitry

! Internal reset controller with bi-directional reset pin

! External reset pushbutton

3.6 Shutdown Controller

! Programmable shutdown and Wake-Up

! Wake-up push button

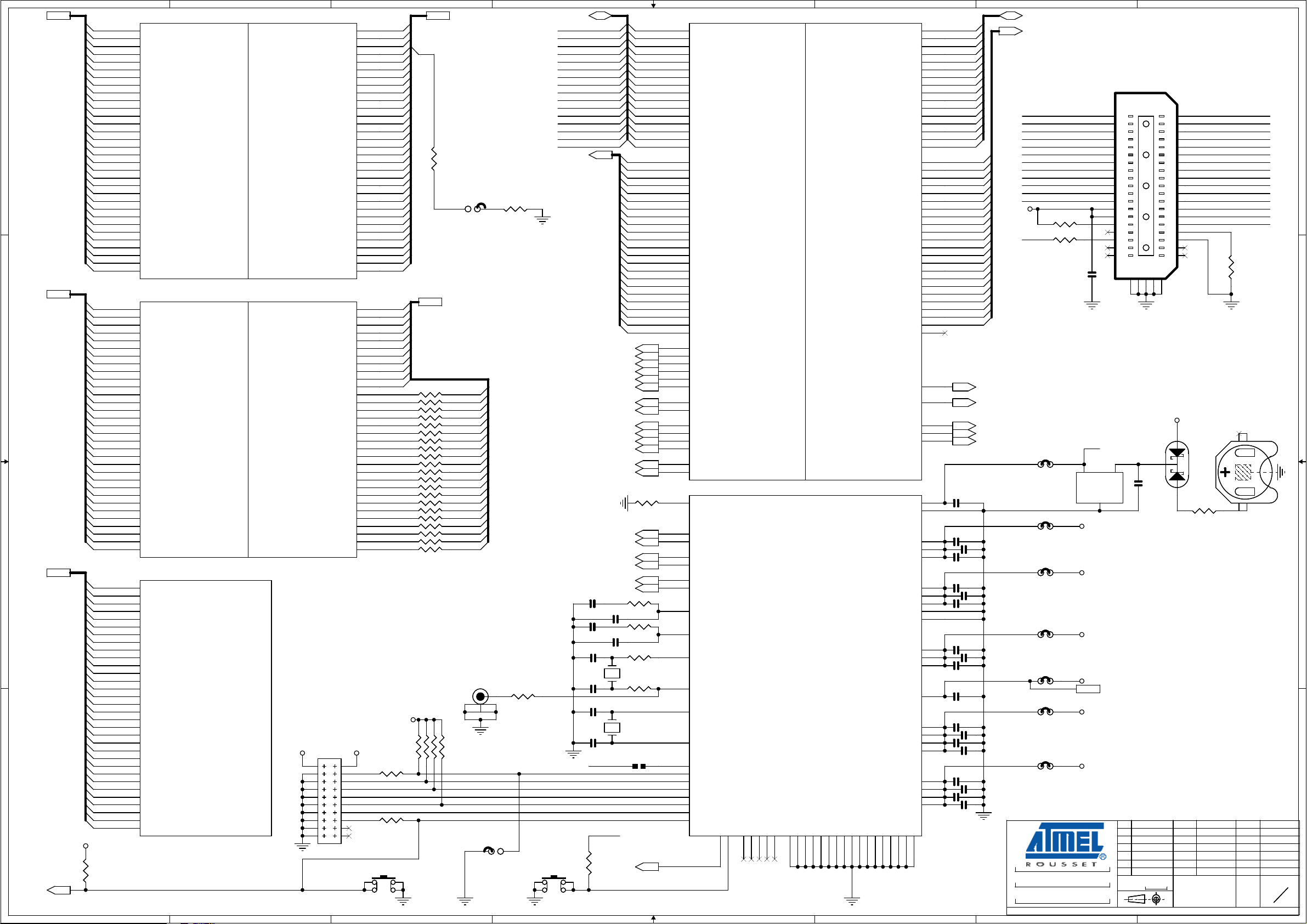

3.7 Power Supply Circuitry

! For dynamic power consumption, the AT91SAM9263 consumes a maximum of 50 mA on VDDCORE

at maximum speed in typical conditions (1.2V, 25°C), processor running full-performance algorithm.

! On-board 1.2V high efficiency step-down Charge Pump regulator with shutdown control

! On-board 3.3V switching regulator with shutdown control

! On-board 5V switching regulator with shutdown control

3.8 Remote Communication

! One RS232 serial communication port

! One serial CAN 2.0B communication port via 3-position printed circuit terminal block

! One USB V2.0 Full-speed Compliant, 12 Mbits per second (UDP)

! Two USB Host ports V2.0 Full-speed Compliant, 12 Mbits per second (UHP)

! One RMII Ethernet 100-base TX with three status LEDs

AT91SAM9263-EK Evaluation Board User Guide 3-5

6279C–ATARM–02-Jul-07

Page 18

Board Description

3.9 Audio Stereo Interface

! One AC'97 2.3 compliant Codec (20-bit PCM DAC)

! One 32-ohm Stereo Headset line-out

! One stereo line input

! One stereo electret microphone input

! One mono 8-ohm amplified speaker

3.10 User Interface

! Two user input pushbuttons

! Two user green LEDs

! One yellow power LED (can be also software controlled)

! One 3.5" ¼ VGA display LCD with Touch Panel and white LED backlight

! One ISI connector (camera interface)

3.11 Debug Interface

! 20-pin JTAG/ICE interface connector

! One Serial interface (DBGU COM Port) via RS-232 DB9 male socket

3.12 Expansion Slot

! One DataFlash/SD/SDIO/MMC card slot

! One SD/SDIO/MMC card slot

! All unused I/Os of the AT91SAM9263 are routed to peripheral extension connectors (J24 and J25).

This allows the developer to add external hardware components or boards.

3-6 AT91SAM9263-EK Evaluation Board User Guide

6279C–ATARM–02-Jul-07

Page 19

Board Description

3.13 PIO Usage

Table 3-1. PIO Controller A

I/O Line Peripheral A Peripheral B Peripheral Usage Powered by

PA0 MCI0_DA0 SPI0_MISO

PA1 MCI0_CDA SPI0_MOSI

PA 2 S PI 0 _ SP C K

PA3 MCI0_DA1 SPI0_NPCS1 SD/MMC/DATAFLASH SOCKET (J9) VDDIOP0

PA4 MCI0_DA2 SPI0_NPCS2 SD/MMC/DATAFLASH SOCKET (J9) VDDIOP0

PA5 MCI0_DA3 SPI0_NPCS0 SD/MMC/DATAFLASH SOCKET (J9) VDDIOP0

PA6 MCI1_CK PCK2 SD/MMC SOCKET (J10) MCI1_CK VDDIOP0

PA7 MCI1_CDA SD/MMC SOCKET (J10) MCI1_CDA VDDIOP0

PA8 MCI1_DA0 SD/MMC SOCKET (J10) MCI1_DA0 VDDIOP0

PA9 MCI1_DA1 SD/MMC SOCKET (J10) MCI1_DA1 VDDIOP0

PA10 MCI1_DA2 SD/MMC SOCKET (J10) MCI1_DA2 VDDIOP0

PA11 MCI1_DA3 SD/MMC SOCKET (J10) MCI1_DA3 VDDIOP0

PA12 MCI0_CK SD/MMC/DATAFLASH SOCKET (J9) MCI0_CK VDDIOP0

PA13 CANTX PCK0 CAN BUS INTERFACE (J17) CANTX VDDIOP0

PA14 CANRX IRQ0 CAN BUS INTERFACE (J17) CANRX VDDIOP0

PA15 TCLK2 IRQ1 TOUCH SCREEN CONTROLLER (MN19) IRQ1 VDDIOP0

PA16 MCI0_CDB EBI1_D16 IMAGE SENSORS CONNECTORS (J23) PA16 as CTRL1 VDDIOM1

PA17 MCI0_DB0 EBI1_D17 IMAGE SENSORS CONNECTORS (J23) PA17 as CTRL2 VDDIOM1

PA18 MCI0_DB1 EBI1_D18 CAN INTERFACE (RXEN) PA18 as RXEN VDDIOM1

PA19 MCI0_DB2 EBI1_D19 CAN INTERFACE (RS) PA19 as RS VDDIOM1

PA20 MCI0_DB3 EBI1_D20 USB HOST B POWER MONITOR (MN17) PA20 as FLGB VDDIOM1

PA21 MCI1_CDB EBI1_D21 USB HOST B POWER CONTROL (MN17) PA21 as ENB VDDIOM1

PA22 MCI1_DB0 EBI1_D22 NANDFLASH (MN12B) PA22 as RDY/BSY VDDIOM1

PA23 MCI1_DB1 EBI1_D23 USB HOST B POWER MONITOR (MN17) PA23 as FLGA VDDIOM1

PA24 MCI1_DB2 EBI1_D24 USB HOST B POWER CONTROL (MN17) PA24 as ENA VDDIOM1

PA25 MCI1_DB3 EBI1_D25 USB DEVICE INTERFACE PA25 as USB_CNX VDDIOM1

PA26 TXD0 EBI1_D26 RS232 COM PORT (J15) TXD0 VDDIOM1

PA27 RXD0 EBI1_D27 RS232 COM PORT (J15) RXD0 VDDIOM1

PA28 RTS0 EBI1_D28 RS232 COM PORT (J15) RTS0 VDDIOM1

PA29 CTS0 EBI1_D29 RS232 COM PORT (J15) CTS0 VDDIOM1

PA30 SCK0 EBI1_D30 LCD PANEL (Power Control In) PA30 as PCI VDDIOM1

PA31 DMARQ0 EBI_D31 TOUCH SCREEN CONTROLLER (MN19) PA31 as BUSY VDDIOM1

SD/MMC/DATAFLASH SOCKET (J9) & TOUCH

SCEEN CONTROLLER

SD/MMC/DATAFLASH SOCKET (J9) & TOUCH

SCEEN CONTROLLER

SD/MMC/DATAFLASH SOCKET (J9) & TOUCH

SCEEN CONTROLLER

MCI0_DA0 or SPI0_MISO VDDIOP0

MCI0_CDA or SPI0_MOSI VDDIOP0

SPI0_SPCK VDDIOP0

AT91SAM9263-EK Evaluation Board User Guide 3-7

6279C–ATARM–02-Jul-07

Page 20

Board Description

Table 3-2. PIO Controller B

I/O Line Peripheral A Peripheral B Peripheral Usage Powered by

PB0 AC97FS TF0 AC97 CODEC (MN12) AC97FS VDDIOP0

PB1 AC97CK TK0 AC97 CODEC (MN12) AC97CK VDDIOP0

PB2 AC97TX TD0 AC97 CODEC (MN12) AC97TX VDDIOP0

PB3 AC97RX RD0 AC97 CODEC (MN12) AC97RX VDDIOP0

PB4 TWD RK0 TWI EEPROM (MN11) TWD / SDA VDDIOP0

PB5 TWCK RF0 TWI EEPROM (MN11) TWCK / SCL VDDIOP0

PB6 TF1 DMARQ1 VDDIOP0

PB7 TK1 PWM0 POWER LED CONTROL (DS3) PB7 or PWM0 VDDIOP0

PB8 TD1 PWM1 USER'S LED1 CONTROL (DS1) PB8 or PWM1 VDDIOP0

PB9 RD1 LCDCC LCD PANEL (backlight control) LCDCC VDDIOP0

PB10 RK1 PCK1 AC97 CODEC (MN12) Optional clock source PCK1 VDDIOP0

PB11 RF1 SPI0_NPCS3 TOUCH SCREEN CONTROLLER (MN19) SPI0_NPCS3 VDDIOP0

PB12 SPI1_MISO VDDIOP0

PB13 SPI1_MOSI VDDIOP0

PB14 SPI1_SPCK VDDIOP0

PB15 SPI1_NPCS0 VDDIOP0

PB16 SPI1_NPCS1 PCK1 VDDIOP0

PB17 SPI1_NPCS2 TIOA2 VDDIOP0

PB18 SPI1_NPCS3 TIOB2 VDDIOP0

PB19 VDDIOP0

PB20 VDDIOP0

PB21 VDDIOP0

PB22 VDDIOP0

PB23 VDDIOP0

PB24 DMARQ3 VDDIOP0

PB25 VDDIOP0

PB26 VDDIOP0

PB27 PWM2 VDDIOP0

PB28 TCLK0 VDDIOP0

PB29 PWM3 VDDIOP0

PB30 VDDIOP0

PB31 VDDIOP0

3-8 AT91SAM9263-EK Evaluation Board User Guide

6279C–ATARM–02-Jul-07

Page 21

Board Description

Table 3-3. PIO Controller C

I/O Line Peripheral A Peripheral B Peripheral Usage Powered by

PC0 LCDVSYNC VDDIOP0

PC1 LCDHSYNC LCD PANEL LCDHSYNC VDDIOP0

PC2 LCDDOTCK LCD PANEL LCDDOTCK VDDIOP0

PC3 LCDDEN PWM1 LCD PANEL LCDDEN VDDIOP0

PC4 LCDD0 LCDD3 USER'S PUSH BUTTON (BP2) PC4 as RIGHT CLICK VDDIOP0

PC5 LCDD1 LCDD4 USER'S PUSH BUTTON (BP1) PC5 as LEFT CLICK VDDIOP0

PC6 LCDD2 LCDD5 LCD PANEL LCDD2 RED VDDIOP0

PC7 LCDD3 LCDD6 LCD PANEL LCDD3 RED VDDIOP0

PC8 LCDD4 LCDD7 LCD PANEL LCDD4 RED VDDIOP0

PC9 LCDD5 LCDD10 LCD PANEL LCDD5 RED VDDIOP0

PC10 LCDD6 LCDD11 LCD PANEL LCDD6 RED VDDIOP0

PC11 LCDD7 LCDD12 LCD PANEL LCDD7 RED VDDIOP0

PC12 LCDD8 LCDD13 LCD PANEL LCDD13 GREEN VDDIOP0

PC13 LCDD9 LCDD14 VDDIOP0

PC14 LCDD10 LCDD15 LCD PANEL LCDD10 GREEN VDDIOP0

PC15 LCDD11 LCDD19 LCD PANEL LCDD11 GREEN VDDIOP0

PC16 LCDD12 LCDD20 LCD PANEL LCDD12 GREEN VDDIOP0

PC17 LCDD13 LCDD21 LCD PANEL LCDD21 BLUE VDDIOP0

PC18 LCDD14 LCDD22 LCD PANEL LCDD14 GREEN VDDIOP0

PC19 LCDD15 LCDD23 LCD PANEL LCDD15 GREEN VDDIOP0

PC20 LCDD16 ETX2 VDDIOP0

PC21 LCDD17 ETX3 VDDIOP0

PC22 LCDD18 ERX2 LCD PANEL LCDD18 BLUE VDDIOP0

PC23 LCDD19 ERX3 LCD PANEL LCDD19 BLUE VDDIOP0

PC24 LCDD20 ETXER LCD PANEL LCDD20 BLUE VDDIOP0

PC25 LCDD21 ERXDV ETHERNET RMII (MN18) ERXDV VDDIOP0

PC26 LCDD22 ECOL LCD PANEL LCDD22 BLUE VDDIOP0

PC27 LCDD23 ERXCK LCD PANEL LCDD23 BLUE VDDIOP0

PC28 PWM0 TCLK1 VDDIOP0

PC29 PCK0 PWM2 USER'S LED2 CONTROL (DS2) PC29 or PWM2 VDDIOP0

PC30 DRXD SERIAL DEBUG PORT (J14) DRXD VDDIOP0

PC31 DTXD SERIAL DEBUG PORT (J14) DTXD VDDIOP0

AT91SAM9263-EK Evaluation Board User Guide 3-9

6279C–ATARM–02-Jul-07

Page 22

Board Description

Table 3-4. PIO Controller D

I/O Line Peripheral A Peripheral B Peripheral Usage Powered by

PD0 TXD1 SPI0_NPCS2 VDDIOP0

PD1 RXD1 SPI0_NPCS3 VDDIOP0

PD2 TXD2 SPI1_NPCS2 HDD CONNECTORS (J8) PD2 as IRQ VDDIOP0

PD3 RXD2 SPI1_NPCS3 HDD CONNECTORS (J8) PD3 as IOREADY VDDIOP0

PD4 FIQ DMARQ2 VDDIOP0

PD5 EBI0_NWAIT RTS2 VDDIOM0

PD6 EBI0_NCS4/CFCS0 CTS2 VDDIOM0

PD7 EBI0_NCS5/CFCS1 RTS1 VDDIOM0

PD8 EBI0_CFCE1 CTS1 HDD CONNECTORS (J8) EBI0_CFCE1 VDDIOM0

PD9 EBI0_CFCE2 SCK2 HDD CONNECTORS (J8) EBI0_CFCE2 VDDIOM0

PD10 SCK1 VDDIOM0

PD11 EBI0_NCS2 TSYNC VDDIOM0

PD12 EBI0_A23 TCLK VDDIOM0

PD13 EBI0_A24 TPS0 VDDIOM0

PD14 EBI0_A25_CFRNW TPS1 VDDIOM0

PD15 EBI0_NCS3/NANDCS TPS2 NANDFLASH (MN12B) EBI0_NCS3/NANDCS VDDIOM0

PD16 EBI0_D16 TPK0 EBI0 SDRAM DATA BUS D16 VDDIOM0

PD17 EBI0_D17 TPK1 EBI0 SDRAM DATA BUS D17 VDDIOM0

PD18 EBI0_D18 TPK2 EBI0 SDRAM DATA BUS D18 VDDIOM0

PD19 EBI0_D19 TPK3 EBI0 SDRAM DATA BUS D19 VDDIOM0

PD20 EBI0_D20 TPK4 EBI0 SDRAM DATA BUS D20 VDDIOM0

PD21 EBI0_D21 TPK5 EBI0 SDRAM DATA BUS D21 VDDIOM0

PD22 EBI0_D22 TPK6 EBI0 SDRAM DATA BUS D22 VDDIOM0

PD23 EBI0_D23 TPK7 EBI0 SDRAM DATA BUS D23 VDDIOM0

PD24 EBI0_D24 TPK8 EBI0 SDRAM DATA BUS D24 VDDIOM0

PD25 EBI0_D25 TPK9 EBI0 SDRAM DATA BUS D25 VDDIOM0

PD26 EBI0_D26 TPK10 EBI0 SDRAM DATA BUS D26 VDDIOM0

PD27 EBI0_D27 TPK11 EBI0 SDRAM DATA BUS D27 VDDIOM0

PD28 EBI0_D28 TPK12 EBI0 SDRAM DATA BUS D28 VDDIOM0

PD29 EBI0_D29 TPK13 EBI0 SDRAM DATA BUS D29 VDDIOM0

PD30 EBI0_D30 TPK14 EBI0 SDRAM DATA BUS D30 VDDIOM0

PD31 EBI0_D31 TPK15 EBI0 SDRAM DATA BUS D31 VDDIOM0

3-10 AT91SAM9263-EK Evaluation Board User Guide

6279C–ATARM–02-Jul-07

Page 23

Board Description

Table 3-5. PIO Controller E

I/O Line Peripheral A Peripheral B Peripheral Usage Powered by

PE0 ISI_D0 IMAGE SENSORS CONNECTORS (J23) ISI_D0 VDDIOP1

PE1 ISI_D1 IMAGE SENSORS CONNECTORS (J23) ISI_D1 VDDIOP1

PE2 ISI_D2 IMAGE SENSORS CONNECTORS (J23) ISI_D2 VDDIOP1

PE3 ISI_D3 IMAGE SENSORS CONNECTORS (J23) ISI_D3 VDDIOP1

PE4 ISI_D4 IMAGE SENSORS CONNECTORS (J23) ISI_D4 VDDIOP1

PE5 ISI_D5 IMAGE SENSORS CONNECTORS (J23) ISI_D5 VDDIOP1

PE6 ISI_D6 IMAGE SENSORS CONNECTORS (J23) ISI_D6 VDDIOP1

PE7 ISI_D7 IMAGE SENSORS CONNECTORS (J23) ISI_D7 VDDIOP1

PE8 ISI_PCK TIOA1 IMAGE SENSORS CONNECTORS (J23) ISI_PCK VDDIOP1

PE9 ISI_HSYNC TIOB1 IMAGE SENSORS CONNECTORS (J23) ISI_HSYNC VDDIOP1

PE10 ISI_VSYNC PWM3 IMAGE SENSORS CONNECTORS (J23) ISI_VSYNC VDDIOP1

PE11 ISI_MCK PCK3 IMAGE SENSORS CONNECTORS (J23) ISI_MCK VDDIOP1

PE12 ISI_D8 IMAGE SENSORS CONNECTORS (J23) ISI_D8 VDDIOP1

PE13 ISI_D9 IMAGE SENSORS CONNECTORS (J23) ISI_D9 VDDIOP1

PE14 ISI_D10 IMAGE SENSORS CONNECTORS (J23) ISI_D10 VDDIOP1

PE15 ISI_D11 IMAGE SENSORS CONNECTORS (J23) ISI_D11 VDDIOP1

PE16 SD/MMC/DATAFLASH SOCKET (J9) PE16 as CD (Card Detect) VDDIOP1

PE17 SD/MMC/DATAFLASH SOCKET (J9) PE17 as WP (Write Protect) VDDIOP1

PE18 TIOA0 SD/MMC SOCKET (J10) PE18 as CD (Card Detect) VDDIOP1

PE19 TIOB0 SD/MMC SOCKET (J10) PE19 as WP (Write Protect) VDDIOP1

PE20 EBI1_NWAIT SD/MMC/DATAFLASH SOCKET (J9)

PE21 ETXCK EBI1_NANDWE ETHERNET RMII (MN18) ETXCK VDDIOM1

PE22 ECRS EBI1_NCS2/NANDCS VDDIOM1

PE23 ETX0 EB1_NANDOE ETHERNET RMII (MN18) ETX0 VDDIOM1

PE24 ETX1 EBI1_NWR3/NBS3 ETHERNET RMII (MN18) ETX1 VDDIOM1

PE25 ERX0 EBI1_NCS1/SDCS ETHERNET RMII (MN18) ERX0 VDDIOM1

PE26 ERX1 ERX1 VDDIOM1

PE27 ERXER EBI1_SDCKE ETHERNET RMII (MN18) ERXER VDDIOM1

PE28 ETXEN EBI1_RAS ETHERNET RMII (MN18) ETXEN VDDIOM1

PE29 EMDC EBI1_CAS ETHERNET RMII (MN18) EMDC VDDIOM1

PE30 EMDIO EBI1_SDWE ETHERNET RMII (MN18) EMDIO VDDIOM1

PE31 EF100 EBI1_SDA10 ETHERNET RMII (MN18) PE31 as IRQ VDDIOM1

PE20 as CKSEL (Clock

Select)

VDDIOM1

AT91SAM9263-EK Evaluation Board User Guide 3-11

6279C–ATARM–02-Jul-07

Page 24

Board Description

3-12 AT91SAM9263-EK Evaluation Board User Guide

6279C–ATARM–02-Jul-07

Page 25

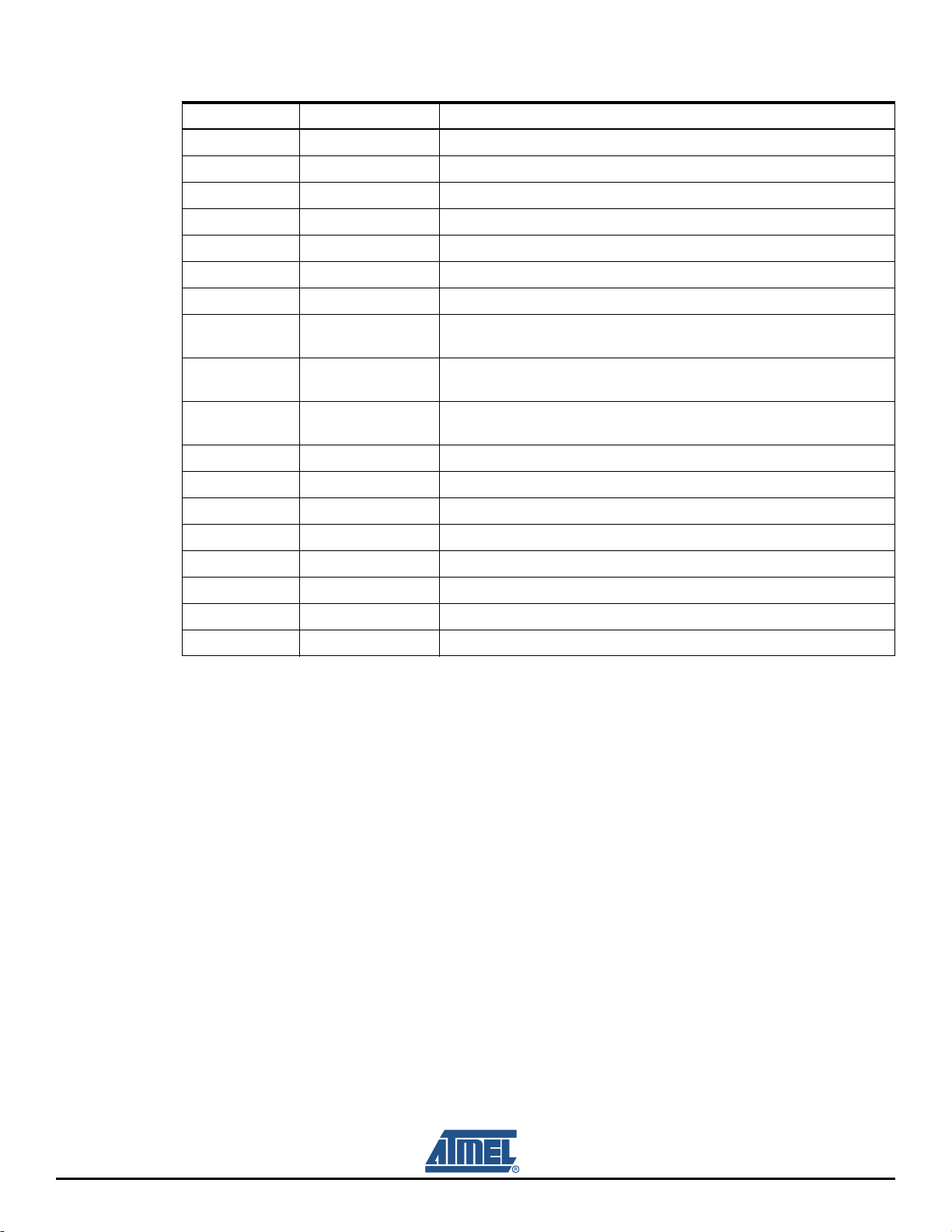

4.1 Configuration Jumpers and Straps

Table 4-1. Configuration Jumpers and Straps

Designation Default Setting Feature

J2 Closed

J4-1 Closed VDDBU jumper

J4-2 Closed VDDCORE jumper

J5-1 Closed VDDOSC jumper

J5-2 Closed VDDIOP0 jumper

J5-3 Closed VDDIOP1 jumper

J5-4 Closed VDDIOM0 jumper

J5.5 Closed VDDIOM1 jumper

Opened Enables Boot on the internal ROM

J5-6

Closed Enables Boot on the NCS0

Section 4

Configuration

Forces power on. To use the software shutdown control, J2 must be

opened and the battery backup inserted in its socket.

(1)

(1)

(1)

(1)

(1)

(1)

(1)

J16 Closed Enables 120 ohms CAN bus resistance termination

J21 Closed Enables Ethernet Auto MDIX control

S1 Opened Selects ICE mode. See

S2 Opened Disables NAND FLASH write protect

S3 Opened Disables 5V power supply on J24, J25 expansion connectors

R17 IN Enables the ICE NTRST input

R18 IN Enables the ICE NRST input

R13 IN

R15 IN

R45 IN Enables the use of the SERIAL EEPROM SCL (PB5)

R46 IN Enables the use of the SERIAL EEPROM SDA (PB4)

R75 IN Enables the use of the DBGU TXD signal (PC31)

R79 IN Enables the use of the DBGU RXD signal (PC30)

R84 IN Enables the use of the USB CNX detection (PA25)

R76 IN Enables the use of the RS232 COM PORT TXD signal (PA26)

R78 IN Enables the use of the RS232 COM PORT RTS signal (PA28)

Enables the use of the Y1 crystal. If an external clock has to be used,

R13 and R15 must be unsoldered and R16/J16 fitted.

Section 7, “Errata”

AT91SAM9263-EK Evaluation Board User Guide 4-1

6279C–ATARM–02-Jul-07

Page 26

Configuration

Table 4-1. Configuration Jumpers and Straps

Designation Default Setting Feature

R80 IN Enables the use of the RS232 COM PORT RXD signal (PA27)

R82 IN Enables the use of the RS232 COM PORT CTS signal (PA29)

R87 IN Enables the use of the CAN BUS driver RS control signal (PA26)

R89 IN Enables the use of the CAN BUS driver CANTXRT RTS signal (PA28)

R91 IN Enables the use of the RS232 COM PORT RXD signal (PA27)

R93 IN Enables the use of the RS232 COM PORT CTS signal (PA29)

R112 IN Enables the use of interrupt ETHERNET PHY (PE31)

R126 IN

R127 IN

R128 IN

Enables the use of TOUCH SCEEN CONTROLLER

(PB11_SPI0_NPCS3)

Enables the use of TOUCH SCEEN CONTROLLER BUSY signal

(PA31)

Enables the use of TOUCH SCEEN CONTROLLER PENIRQ

(PA15_IRQ1)

TP67 N.A GND Test point

TP68 N.A GND Test point

TP69 N.A GND Test point

TP70 N.A GND Test point

TP71 N.A 0 to 3.3V analog user's input

TP72 N.A 0 to 3.3V analog user's input

TP73 N.A AGND of TP71

TP74 N.A AGND of TP72

Note: 1. These jumpers are provided for power consumption measurement use. By default, they are closed. To

use this feature, the user has to open the strap and insert an ammeter.

4-2 AT91SAM9263-EK Evaluation Board User Guide

6279C–ATARM–02-Jul-07

Page 27

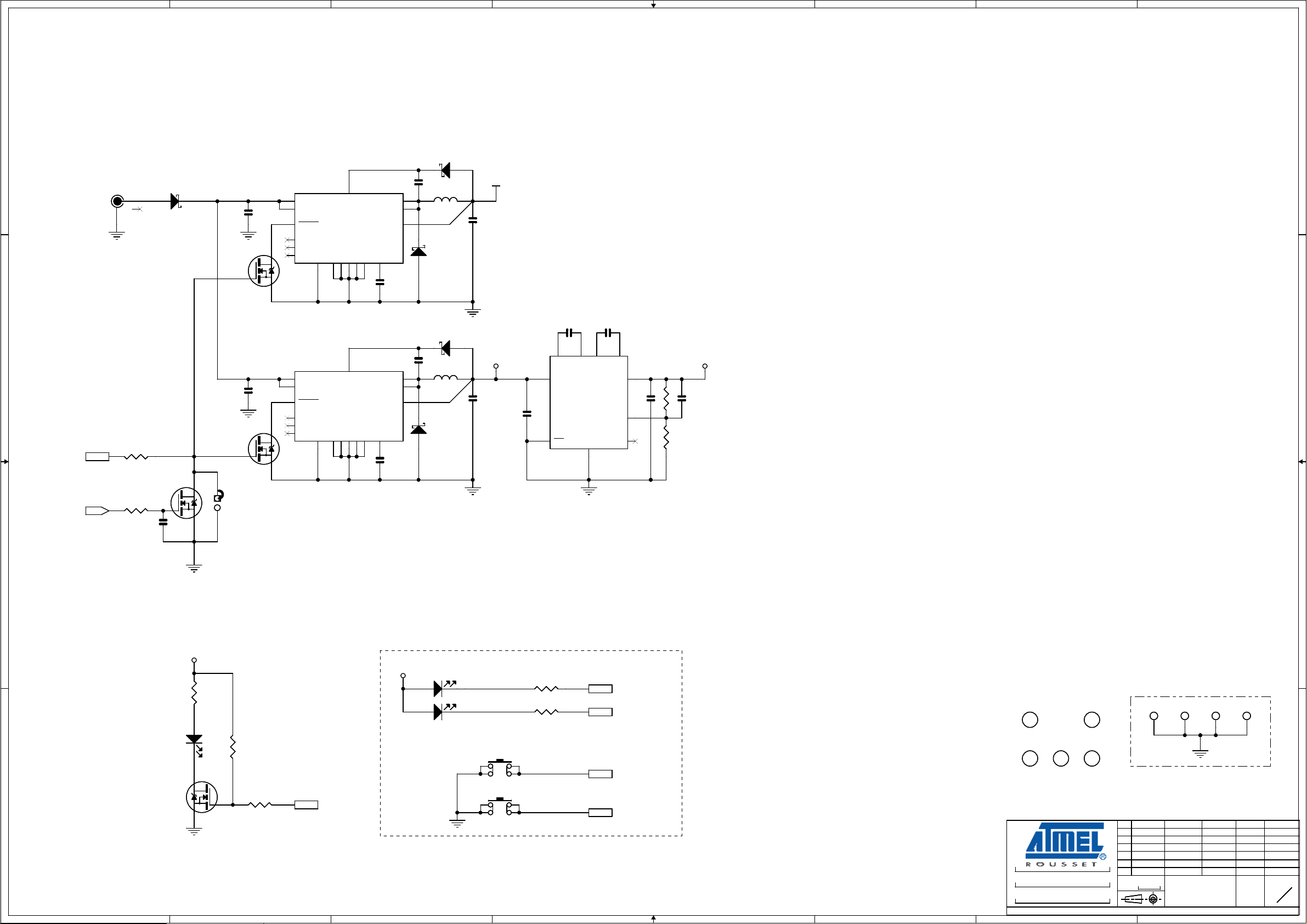

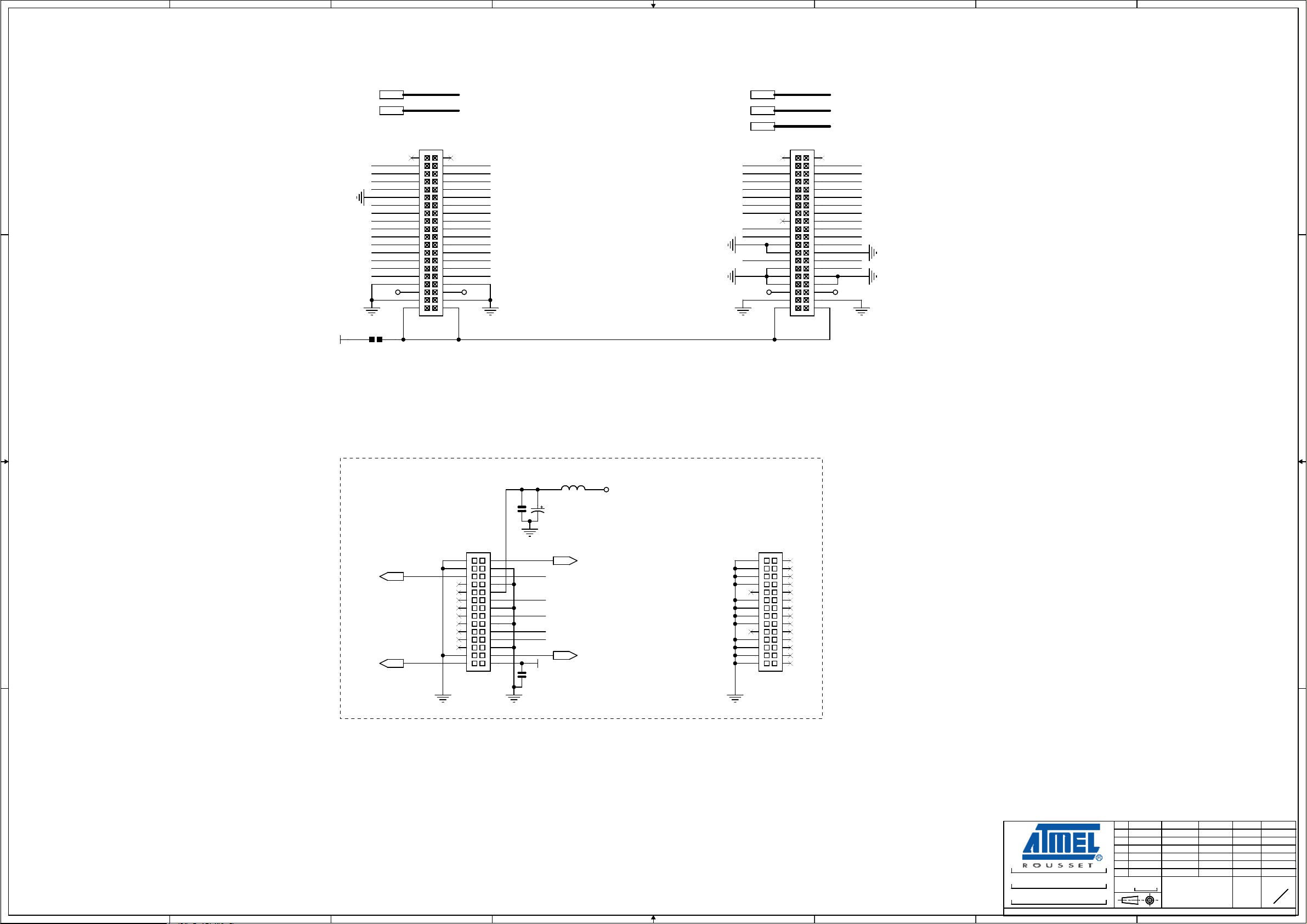

5.1 Schematics

This section contains the following schematics:

! Power Supply

! AT91SAM9263

! EBI0 Memory

! EBI1 Memory

! Serial Memory

! Audio AC97

! Serial Interfaces

! Ethernet

! LCD and ISI

! Expansion

Section 5

Schematics

AT91SAM9263-EK Evaluation Board User Guide 5-1

6279C–ATARM–02-Jul-07

Page 28

8

POWER SUPPLY

VDDBU

POWERLED

12VDC

USER'S

INTERFACE

D D

01 - POWER SUPPLY

AC97

AUDIO

MIC OUTIN

06 - AUDIO

SERIAL INTERFACES

DBGU

RS232

COM0

DEVICE

C C

USB

HOST A

HOST B

CAN

07 - COMMUNICATION

RMII ETHERNET

B B

10/100 FAST ETHERNET

08 - ETHERNET

LCD & CAMERA INTERFACE

3.5" QVGA

LCD INTERFACE

TOUCH SCREEN

CONTROLLER

A A

ISI

CAMERA INTERFACE

09 - LCD & CAMERA INTERFACE

8

SHDN

USERLED1

USERLED2

RIGHTCLIC

LEFTCLIC

SYNC

BITCLK

SDATA_OUT

SDATA_IN

EXT_CLK

RST#

DTXD

DRXD

RXD

USBCNX

DDM

DDP

HDMA

HDPA

ENA

FLGA

HDMB

HDPB

ENB

FLGB

CANRS

CANRXEN

CANRX

CANTX

TX_CLK

TXD1

TXD0

TX_EN

RXD1

RXD0

RX_DV

RX_ER

MDC

MDIO

MDINTR

NRST

R[0..5]

G[0..5]

B[0..5]

HSYNC

DCLK

DTMG

VCTRL

MOSI

MISO

SPCK

NPCS

BUSY

RFTS

ISI_D[0..11]

ISI_MCK

ISI_VSYNC

ISI_HSYNC

ISI_PCK

VDDISI

SDA

CTRL2

CTRL1

TXD

RTS

CTS

PCI

IRQ

SCL

7

PWM0

PWM1

PWM2

PC4

PC5

AC97FS

AC97CK

AC97TX

AC97RX

PCK1

NRST

DTXD

DRXD

TXD0

RXD0

RTS0

CTS0

PA25

PA24

PA23

PA21

PA20

PA19

PA18

CANRX

CANTX

ETXCK

ETX1

ETX0

ETXEN

ERX1

ERX0

ERXDV

ERXER

EMDC

EMDIO

PE31

NRST

LCDD[2..7]

LCDD[10..15]

LCDD[18..23]

LCDHSYNC

LCDDOTCK

LCDDEN

LCDCC

PA30

SPI0_MOSI

SPI0_MISO

SPI0_SPCK

SPI0_NPCS3

IRQ1

PA31

ISI_D[0..11]

ISI_MCK

ISI_VSYNC

ISI_HSYNC

ISI_PCK

VDDISI

TWD

TWCK

PA17

PA16

7

6

EXPANSION CONNECTORS

PA[0..31]

PB[0..31]

PC[0..31]

PD[0..31]

PE[0..31]

CLK16M

SIGI

RFTS

10 - EXPANSION CONNECTORS

SIGQ

PIO USAGE

6

PA[0..31]

PA0SPI0_MISO

PA1SPI0_MOSI

VDDISI

PA[0..31]

PB[0..31]

PC[0..31]

PD[0..31]

PE[0..31]

PA[0..31]

PB[0..31]

PC[0..31]

PD[0..31]

PE[0..31]

PA0 MCI0_DA0

PA1 MCI0_CDA

PA2 SPI0_SPCK

PA3 MCI0_DA1

PA4 MCI0_DA2

PA5 MCI0_DA3

PA6 MCI1_CK

PA7 MCI1_CDA

PA8 MCI1_DA0

PA9 MCI1_DA1

PA10 MCI1_DA2

PA11 MCI1_DA3

PA12 MCI0_CK

PA13 CANTX

PA14 CANRX

PA15 IRQ1

PA16

(CTRL1)

PA17

(CTRL2)

PA18

(CANRXEN)

PA19

(CANRS)

PA20

(FLGB)

PA21

(ENB)

PA22

(RDYBSY)

PA23

(FLGA)

PA24

(ENA)

PA25

(USBCNX)

PA26 TXD0

PA27 RXD0

PA28 RTS0

PA29 CTS0

PA30

(PCI)

PA31

(BUSY)

5

AT91SAM9263_BGA324

VDDBU

SHDN

VDDISI

PA[0..31]

PB[0..31]

PC[0..31]

PD[0..31]

PE[0..31]

DDM

DDP

HDMA

HDPA

HDMB

HDPB

PPS

CK16M

SIGI

SIGQ

02 - MICROCONTROLLER

PB[0..31]

PB0 AC97FS

PB1 AC97CK

PB2 AC97TX

PB3 AC97RX

PB4 TWD

PB5 TWCK

PB6

PB7 PWM0

PB8 PWM1

PB9 LCDCC

PB10 PCK1

PB11 SPI0_NPCS3

PB12

PB13

PB14

PB15

PB16

PB17

PB18

PB19

PB20

PB21

PB22

PB23

PB24

PB25

PB26

PB27

PB28

PB29

PB30

PB31

5

PC[0..31]

EBI0_NWE/NWR0/CFWE

EBI0_NBS1/NW1/CFIOR

EBI0_NBS3/NW3/CFIOW

EBI1_NWE/NWR0/CFWE

EBI1_NBS1/NW1/CFIOR

PC0

PC1 LCDHSYNC

PC2 LCDDOTCK

PC3 LCDDEN

PC4

(RIGHTCLIC)

PC5

(LEFTCLIC)

PC6 LCDD2

PC7 LCDD3

PC8 LCDD4

PC9 LCDD5

PC10 LCDD6

PC11 LCDD7

PC12 LCDD13

PC13

PC14 LCDD10

PC15 LCDD11

PC16 LCDD12

PC17 LCDD21

PC18 LCDD14

PC19 LCDD15

PC20

PC21

PC22 LCDD18

PC23 LCDD19

PC24 LCDD20

PC25 ERXDV

PC26 LCDD22

PC27 LCDD23

PC28

PC29 PWM2

PC30 DRXD

PC31 DTXD

4

EBI0_D[0..31]

EBI0_A[0..22]

EBI0_RAS

EBI0_CAS

EBI0_SDA10

EBI0_SDWE

EBI0_NCS1/SDCS

EBI0_SDCK

EBI0_SDCKE

EBI0_NANDOE

EBI0_NANDWE

EBI0_NCS0

EBI0_NRD/CFOE

NRST

EBI1_D[0..15]

EBI1_A[0..21]

EBI1_NCS0

EBI1_NRD/CFOE

EBI1_SDCK

PD[0..31]

PD0

PD1

PD2

PD3

PD4

PD5

PD6

PD7

PD8 EBI0_CFCE1

PD9 EBI0_CFCE2

PD10

PD11

PD12

PD13

PD14

PD15

PD16

PD17

PD18

PD19

PD20

PD21

PD22

PD23

PD24

PD25

PD26

PD27

PD28

PD29

PD30

PD31

4

EBI0_D[0..31]

EBI0_A[0..22]

NRST

EBI0_NBS1

EBI0_NBS3

EBI1_D[0..15]

EBI1_A[0..21]

(INTRQ)

(IORDY)

(NANDCS)

PE[0..31]

3

PE0 ISI_D0

PE1 ISI_D1

PE2 ISI_D2

PE3 ISI_D3

PE4 ISI_D4

PE5 ISI_D5

PE6 ISI_D6

PE7 ISI_D7

PE8 ISI_PCK

PE9 ISI_HSYNC

PE10 ISI_VSYNC

PE11 ISI_MCK

PE12 ISI_D8

PE13 ISI_D9

PE14 ISI_D10

PE15 ISI_D11

PE16

(MCI0_CD)

PE17

(MCI0_WP)

PE18

(MCI1_CD)

PE19

(MCI1_WP)

PE20

(CKSEL)

PE21 ETXCK

PE22

PE23 ETX0

PE24 ETX1

PE25 ERX0

PE26 ERX1

PE27 ERXER

PE28 ETXEN

PE29 EMDC

PE30 EMDIO

PE31

(MDINTR)

3

2

EBI0 MEMORY

D[0..31]

A[0..22]

RAS

CAS

SDA10

SDWE

SDCS

SDCK

EBI0_A0

EBI0_NBS1

EBI0_A1

EBI0_NBS3

EBI0_A16

EBI0_A17

EBI0_A22

EBI0_A21

PD15

PA22

EBI0_CFCE1

EBI0_CFCE2

PD2

PD3

EBI1_A[1..21]

EBI1_A0

PE16

PE17

MCI0_DA0

MCI0_DA1

MCI0_DA2

MCI0_DA3

MCI0_CDA

MCI0_CK

SPI0_SPCK

PE20

PE18

PE19

MCI1_DA0

MCI1_DA1

MCI1_DA2

MCI1_DA3

MCI1_CDA

MCI1_CK

TWCK

TWD

AT91SAM9263-EK

AT91SAM9263-EK

AT91SAM9263-EK

DIAGRAM

DIAGRAM

DIAGRAM

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

SDCKE

NBS0

NBS1

NBS2

NBS3

BA0

BA1

CLE

ALE

NANDOE

NANDWE

NANDCS

RDYBSY

NCS

NWE

NRD

NRST

RESETCS0-

CS1DIORDIOW-

INTRQ

IORDY

03 - EBI0 MEMORY

EBI1 MEMORY

D[0..15]

A[1..21]

NCS

NWR

NOE

LB

UB

04 - EBI1 MEMORY

MCI & TWI

MCI0_CD

MCI0_WP

MCI0_DA0

MCI0_DA1

MCI0_DA2

MCI0_DA3

MCI0_CDA

MCI0_CK

SPI0_SPCK

CKSEL

MCI1_CD

MCI1_WP

MCI1_DA0

MCI1_DA1

MCI1_DA2

MCI1_DA3

MCI1_CDA

MCI1_CK

SCL

SDA

05 - MCI & TWI

2

CARD

READER

CARD

READER

INIT EDIT

INIT EDIT

INIT EDIT

A

A

A

REV

REV

REV

SCALE

SCALE

SCALE

1/1

1/1

1/1

MMC SD/SDIOMMC SD/SDIO

SERIAL

JPG

JPG

JPG

DES.

DES.

DES.

EBI0

SDRAMNANFLASH

NORFLASH1.8" HDD

EBI1PSRAM

DATAFLASH

EEPROM

1

10/10/06

10/10/06

10/10/06

DATE

DATE

DATE

1

VER.

VER.

VER.

DATEMODIF.

DATEMODIF.

DATEMODIF.

REV. SHEET

REV. SHEET

REV. SHEET

1

1

1

A

A

A

11

11

11

Page 29

8

D D

CR2

1

2

C14

C14

15PF

15PF

CR2

STPS2L30A

STPS2L30A

Q3

Q3

BSH103

BSH103

1

3

2

J1

J1

3

2.1 MM SOCKET

2.1 MM SOCKET

C C

R3 100KR3 100K

VDDBU

SHDN

R4 10KR4 10K

C2

2.2µFC22.2µF

1

Q1

Q1

BSH103

BSH103

C8

2.2µFC82.2µF

1

Q2

Q2

BSH103

BSH103

J2J2

FORCE

POWER

ON

7

SYNC

14

SYNC

14

2

BOOST

LT1765-5

LT1765-5

GND

GND8GND9GND

GND

1

17

2

BOOST

LT1765-3.3

LT1765-3.3

GND

GND8GND9GND

GND

1

17

16

16

MN1

MN1

3

VIN

4

VIN

11

SHDN

7

NC

10

3

NC

15

NC

2

MN3

MN3

3

VIN

4

VIN

11

SHDN

7

NC

10

3

NC

15

NC

2

13

13

SW

SW

VC

C4

2.2NFC42.2NF

SW

SW

VC

C13

C13

2.2NF

2.2NF

FB

FB

6

C1

180NFC1180NF

6

5

12

C7

180NFC7180NF

6

5

12

CR1

CR1

BAT20J

BAT20J

L1

2.2µHL12.2µH

CR3

CR3

STPS2L30A

STPS2L30A

CR4

CR4

BAT20J

BAT20J

L2

2.2µHL22.2µH

CR5

CR5

STPS2L30A

STPS2L30A

C3

10µFC310µF

C9

10µFC910µF

5V

3V3

C12

C12

2.2µF

2.2µF

C1M

5

1

MN2

MN2

5

C5

1µFC51µF

8

C1P6C2M3C2P

VIN

TPS60500

TPS60500

EN

GND

9

C6

1µFC61µF

VOUT

PG

FB

4

4

R2

200KR2200K

C11

C11

10PF

10PF

1V2

7

10

2

C10

C10

22µF

22µF

R1

100KR1100K

3

2

1

B B

USER INTERFACE

3V3

R5

120RR5120R

POWER LED

DS3

DS3

YELLOW

YELLOW

3

A A

8

Q4

Q4

IRLML2402

IRLML2402

2

R8

470KR8470K

R9 0RR9 0R

1

7

POWERLED

3V3

DS2 GREENDS2 GREEN

DS1 GREENDS1 GREEN

RIGHT CLICK

BP2BP2

LEFT CLICK

BP1BP1

6

R6 220RR6 220R

R7 220RR7 220R

TP67TP67

INIT EDIT

INIT EDIT

INIT EDIT

1/1

1/1

1/1

GND TEST POINTADHESIVE FEET

TP70TP70

TP69TP69

TP68TP68

10/10/06

JPG

10/10/06

JPG

10/10/06

JPG

DES.

DES.

DES.

DATE

DATE

DATE

1

VER.

VER.

VER.

DATEMODIF.

DATEMODIF.

DATEMODIF.

REV. SHEET

REV. SHEET

REV. SHEET

2

2

2

A

A

A

11

11

11

USERLED2

USERLED1

RIGHTCLIC

LEFTCLIC

5

4

3

Z1

11.1Z111.1

Z3

11.1Z311.1

11.1Z411.1

AT91SAM9263-EK

AT91SAM9263-EK

AT91SAM9263-EK

POWER SUPPLY

POWER SUPPLY

POWER SUPPLY

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

2

Z2

11.1Z211.1

Z4

Z5

11.1Z511.1

A

A

A

REV

REV

REV

SCALE

SCALE

SCALE

Page 30

8

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

PA8

PA9

PA10

PA11

3V3

8

PA12

PA13

PA14

PA15

PA16

PA17

PA18

PA19

PA20

PA21

PA22

PA23

PA24

PA25

PA26

PA27

PA28

PA29

PA30

PA31

PC0

PC1

PC2

PC3

PC4

PC5

PC6

PC7

PC8

PC9

PC10

PC11

PC12

PC13

PC14

PC15

PC16

PC17

PC18

PC19

PC20

PC21

PC22

PC23

PC24

PC25

PC26

PC27

PC28

PC29

PC30

PC31

PE0

PE1

PE2

PE3

PE4

PE5

PE6

PE7

PE8

PE9

PE10

PE11

PE12

PE13

PE14

PE15

PE16

PE17

PE18

PE19

PE20

PE21

PE22

PE23

PE24

PE25

PE26

PE27

PE28

PE29

PE30

PE31

R191KR19

1K

D D

PC[0..31]

C C

PE[0..31]

B B

A A

NRST

MN4AMN4A

N16

PA0/MCI0_DA0/SPI0_MISO

N15

PA1/MCI0_CDA/SPI0_MOSI

P15

PA2/SPI0_SPCK

P14

PA3/MCI0_DA1/SPI0_NPCS1

M15

PA4/MCI0_DA2/SPI0_NPCS2

M17

PA5/MCI0_DA3/SPI0_NPCS0

M14

PA6/MCI1_CK/PCK2

M16

PA7/MCI1_CDA

M18

PA8/MCI1_DA0

L15

PA9/MCI1_DA1

L17

PA10/MCI1_DA2

L18

PA11/MCI1_DA3

L16

PA12/MCI0_CK

L13

PA13/CANTX/PCK0

K14

PA14/CANRX/IRQ0

K15

PA15/TCLK2/IRQ1

P3

PA16/MCI0_CDB/EBI1_D16

U1

PA17/MCI0_DB0/EBI1_D17

R3

PA18/MCI0_DB1/EBI1_D18

T3

PA19/MCI0_DB2/EBI1_D19

U2

PA20/MCI0_DB3/EBI1_D20

T4

PA21/MCI1_CDB/EBI1_D21

V2

PA22/MCI1_DB0/EBI1_D22

U3

PA23/MCI1_DB1/EBI1_D23

U4

PA24/MCI1_DB2/EBI1_D24

R4

PA25/MCI1_DB3/EBI1_D25

T5

PA26/TXD0/EBI1_D26

V3

PA27/RXD0/EBI1_D27

U5

PA28/RTS0/EBI1_D28

V4

PA29/CTS0/EBI1_D29

R5

PA30/SCK0/EBI1_D30

T6

PA31/DMARQ0/EBI1_D31

MN4CMN4C

E16

PC0/LCDVSYNC

D17

PC1/LCDHSYNC

D16

PC2/LCDDOTCK

C15

PC3/LCDDEN/PWM1

E14

PC4/LCDD0/LCDD3

B16

PC5/LCDD1/LCDD4

D13

PC6/LCDD2/LCDD5

B15

PC7/LCDD3/LCDD6

C14

PC8/LCDD4/LCDD7

B14

PC9/LCDD5/LCDD10

D15

PC10/LCDD6/LCDD11

E13

PC11/LCDD7/LCDD12

A15

PC12/LCDD8/LCDD13

F13

PC13/LCDD9/LCDD14

C13

PC14/LCDD10/LCDD15

E12

PC15/LCDD11/LCDD19

D14

PC16/LCDD12/LCDD20

B13

PC17/LCDD13/LCDD21

F12

PC18/LCDD14/LCDD22

A14

PC19/LCDD15/LCDD23

D12

PC20/LCDD16/E_TX2

B12

PC21/LCDD17/E_TX3

E11

PC22/LCDD18/E_RX2

C12

PC23/LCDD19/E_RX3

A13

PC24/LCDD20/E_TXER

D11

PC25/LCDD21/E_RXDV

A12

PC26/LCDD22/E_COL

F11

PC27/LCDD23/E_RXCK

B11

PC28/PWM0/TCLK1

C11

PC29/PCK0/PWM2

A11

PC30/DRXD

E10

PC31/DTXD

MN4EMN4E

K3

PE0/ISI_D0

K4

PE1/ISI_D1

L6

PE2/ISI_D2

L7

PE3/ISI_D3

L2

PE4/ISI_D4

L5

PE5/ISI_D5

K1

PE6/ISI_D6

L4

PE7/ISI_D7

M7

PE8/ISI_PCK/TIOA1

L3

PE9/ISI_HSYNC/TIOB1

L1

PE10/ISI_VSYNC/PWM3

M4

PE11/ISI_MCK/PCK3

M6

PE12/ISI_D8

M5

PE13/ISI_D9

M2

PE14/ISI_D10

M3

PE15/ISI_D11

N6

PE16

N5

PE17

M1

PE18/TIOA0

N3

PE19/TIOB0

P6

PE20/EBI1_NWAIT

V13

PE21/E_TXCK/EBI1_NANDWE

U13

PE22/E_CRS/EBI1_NCS2/NANDCS

T13

PE23/E_TX0/EBI1_NANDOE

V14

PE24/E_TX1/EBI1_NWR3/NBS3/CFIOW

T14

PE25/E_RX0/EBI1_NCS1/SDCS

R14

PE26/E_RX1

U14

PE27/E_RXER/EBI1_SDCKE

P16

PE28/E_TXEN/EBI1_RAS

T15

PE29/E_MDC/EBI1_CAS

R16

PE30/E_MDIO/EBI1_SDWE

T16

PE31/EF100/EBI1_SDA10

7

MN4BMN4B

PB0/AC97FS/TF0

PB1/AC97CK/TK0

PB2/AC97TX/TD0

BMS_PB3/AC97RX/RD0

PB4/TWD/RK0

PB5/TWCK/RF0

PB6/TF1/DMARQ1

PB7/TK1/PWM0

PB8/TD1/PWM1

PB9/RD1/LCDCC

PB10/RK1/PCK1

PB11/RF1/SPI0_NPCS3

PB12/SPI1_MISO

PB13/SPI1_MOSI

PB14/SPI1_SPCK

PB15/SPI1_NPCS0

PB16/SPI1_NPCS1/PCK1

PB17/SPI1_NPCS2/TIOA2

PB18/SPI1_NPCS3/TIOB2

PB24/OTG_SE0_VM/DMARQ3

MN4DMN4D

PD0/TXD1/SPI0_NPCS2

PD1/RXD1/SPI0_NPCS3

PD2/TXD2/SPI1_NPCS2

PD3/RXD2/SPI1_NPCS3

PD4/FIQ/DMARQ2

PD5/EBI0_NWAIT/RTS2

PD6/EBI0_NCS4/CFCS0/CTS2

PD7/EBI0_NCS5/CFCS1/RTS1

PD8/EBI0_CFCE1/CTS1

PD9/EBI0_CFCE2/SCK2

PD11/EBI0_NCS2/TSYNC

PD12/EBI0_A23/TCLK

PD13/EBI0_A24/TPS0

PD14/EBI0_A25_CFRNW/TPS1

PD15/EBI0_NCS3/NANDCS/TPS2

PD16/EBI0_D16/TPK0

PD17/EBI0_D17/TPK1

PD18/EBI0_D18/TPK2

PD19/EBI0_D19/TPK3

PD20/EBI0_D20/TPK4

PD21/EBI0_D21/TPK5

PD22/EBI0_D22/TPK6

PD23/EBI0_D23/TPK7

PD24/EBI0_D24/TPK8

PD25/EBI0_D25/TPK9

PD26/EBI0_D26/TPK10

PD27/EBI0_D27/TPK11

PD28/EBI0_D28/TPK12

PD29/EBI0_D29/TPK13

PD30/EBI0_D30/TPK14

PD31/EBI0_D31/TPK15

PB19

PB20

PB21

PB22

PB23

PB25

PB26

PB27/PWM2

PB28/TCLK0

PB29/PWM3

PB30

PB31

PD10/SCK1

ICE INTERFACE

3V3 3V3

J7J7

14

16

18

20

7

6

PB[0..31]PA[0..31]

PB0

K17

PB1

K16

PB2

K18

PB3 PB3

K13

PB4

L14

PB5

J15

PB6

J16

PB7

J17

PB8

J18

PB9

J13

PB10

J14

PB11

J12

PB12

H18

PB13

H15

PB14

H17

PB15

H14

PB16

B17

PB17

H13

PB18

G18

PB19

H12

PB20

G14

PB21

G13

PB22

G17

PB23

G15

PB24

H16

PB25

F15

PB26

F14

PB27

F17

PB28

G16

PB29

F16

PB30

E15

PB31

E17

PD0

B10

PD1

D10

PD2

C10

PD3

F10

PD4

A10

PD5

G5

PD6

G3

PD7

F1

PD8

G6

PD9

H4

PD10

G7

TSYNC

H5

G2

H2

H6

H3

H7

G1

J5

J4

J8

J7

J3

J6

H1

K8

J2

K5

K2

K7

J1

K6

12

R170RR17

34

56

78

910

1112

13

R180RR18

15

17

19

TCLK

TPS0

TPS1

TPS2

TPK0

TPK1

TPK2

TPK3

TPK4

TPK5

TPK6

TPK7

TPK8

TPK9

TPK10

TPK11

TPK12

TPK13

TPK14

TPK15

3V3

1

2

3

4

1

2

3

4

1

2

3

4

1

2

3

4

1

2

3

4

0R

0R

R134

R134

4.7K

4.7K

11 12

BOOT MODE SELECT

Opened

Closed NCS0=

PD[0..31]

PD11

8

PD12

7

PD13

6

PD14

5

PD15

PD16

8

PD17

7

PD18

6

PD19

5

PD20

8

PD21

7

PD22

6

PD23

5

PD24

8

PD25

7

PD26

6

PD27

5

PD28

8

PD29

7

PD30

6

PD31

5

RR1

RR1

100K

100K

678

15234

J5-6J5-6

NOT POPULATED

2 3

SMB MALE

SMB MALE

Internal ROM BOOT=

J6

J6

J5-7J5-7

R135 4.7KR135 4.7K

RR30RRR3

0R

R139 0RR139 0R

RR40RRR4

0R

RR50RRR5

0R

RR60RRR6

0R

RR70RRR7

0R

1

54

NOT POPULATED

NOT POPULATED

C22 4.7NFC22 4.7NF

C24 470 pFC24 470 pF

C25 10NFC25 10NF

C26 1NFC26 1NF

R16

R16

1314

BP3BP3

6

5

PD16 EBI0_D16

PD17 EBI0_D17

PD18 EBI0_D18

PD19 EBI0_D19

PD20 EBI0_D20

PD21 EBI0_D21

PD22 EBI0_D22

PD23 EBI0_D23

PD24 EBI0_D24

PD25 EBI0_D25

PD26 EBI0_D26

PD27 EBI0_D27

PD28 EBI0_D28

PD29 EBI0_D29

PD30 EBI0_D30

PD31 EBI0_D31

EBI0_A[0..22]

EBI0_RAS

EBI0_CAS

EBI0_SDWE

EBI0_SDA10

EBI0_SDCKE

EBI0_SDCK

EBI0_NCS0

EBI0_NCS1/SDCS

EBI0_NRD/CFOE

EBI0_NWE/NWR0/CFWE

EBI0_NBS1/NW1/CFIOR

EBI0_NBS3/NW3/CFIOW

EBI0_NANDOE

EBI0_NANDWE

C28

C28

22PF

22PF

C31

C31

22PF

22PF

C33

C33

15PF

15PF

C36

C36

15PF

15PF

VDDBU

NTRST

TDI

TMS

TCK

RTCK

TDO

NRST

VDDBU

R20

R20

100K

100K

BP4BP4

WAKE UPNRST

5

EBI0_D0

EBI0_D1

EBI0_D2

EBI0_D3

EBI0_D4

EBI0_D5

EBI0_D6

EBI0_D7

EBI0_D8

EBI0_D9

EBI0_D10

EBI0_D11

EBI0_D12

EBI0_D13

EBI0_D14

EBI0_D15

EBI0_A0

EBI0_A1

EBI0_A2

EBI0_A3

EBI0_A4

EBI0_A5

EBI0_A6

EBI0_A7

EBI0_A8

EBI0_A9

EBI0_A10

EBI0_A11

EBI0_A12

EBI0_A13

EBI0_A14

EBI0_A15

EBI0_A16

EBI0_A17

EBI0_A18

EBI0_A19

EBI0_A20

EBI0_A21

EBI0_A22

R21 10KR21 10K

HDPB

HDMB

HDPA

HDMA

DDP

DDM

R11 1,96K 1%R11 1,96K 1%

R12 1.5KR12 1.5K

R13 0RR13 0R

Y1

Y1

16.36766MHz

16.36766MHz

R15 0RR15 0R

Y2

Y2

32.768 kHz

32.768 kHz

1 4

S1S1

SHDN

MN4FMN4F

C2

EBI0_D0

D4

EBI0_D1

A1

EBI0_D2

D2

EBI0_D3

B1

EBI0_D4

E3

EBI0_D5

C1

EBI0_D6

E2

EBI0_D7

E4

EBI0_D8

F3

EBI0_D9

D1

EBI0_D10

F4

EBI0_D11

F5

EBI0_D12

F2

EBI0_D13

G4

EBI0_D14

E1

EBI0_D15

E9

EBI0_NBS0/A0

A9

EBI0_NBS2/NWR2/A1

D9

EBI0_A2

C9

EBI0_A3

B9

EBI0_A4

A8

EBI0_A5

F9

EBI0_A6

B8

EBI0_A7

C8

EBI0_A8

D8

EBI0_A9

A7

EBI0_A10

A6

EBI0_A11

F8

EBI0_A12

C7

EBI0_A13

E7

EBI0_A14

B7

EBI0_A15

F7

EBI0_BA0/A16

D6

EBI0_BA1/A17

D7

EBI0_A18

A5

EBI0_A19

D5

EBI0_A20

C6

EBI0_A21

B6

EBI0_A22

B4

EBI0_RAS

B3

EBI0_CAS

C4

EBI0_SDWE

E8

EBI0_SDA10

A2

EBI0_SDCKE

C5

EBI0_SDCK

F6

EBI0_NCS0

A4

EBI0_NCS1/SDCS

E6

EBI0_NRD/CFOE

A3

EBI0_NWE/NWR0/CFWE

E5

EBI0_NBS1/NWR1/CFIOR

B5

EBI0_NBS3/NWR3/CFIOW

B2

EBI0_NANDOE

C3

EBI0_NANDWE

MN4HMN4H

R2

TST

C18

HDPB

D18

HDMB

E18

HDPA

F18

HDMA

A18

DDP

B18

DDM

P18

PLLRCB

U18

PLLRCA

R18

XOUT

T18

XIN

R1

XOUT32

P1

XIN32

P5

JTAGSEL

U16

NTRST

P17

TDI

N17

TMS

R17

TCK

U15

RTCK

N18

TDO

V15

NRST

P2

4

WKUPP4SHDN

4

NC

NCD3NCN1NCN2NC

G9

3

MN4GMN4G

EBI1_D0

EBI1_D1

EBI1_D2

EBI1_D3

EBI1_D4

EBI1_D5

EBI1_D6

EBI1_D7

EBI1_D8

EBI1_D9

EBI1_D10

EBI1_D11

EBI1_D12

EBI1_D13

EBI1_D14

EBI1_D15

EBI1_NBS0/A0

EBI1_NWR2/A1

EBI1_A2

EBI1_A3

EBI1_A4

EBI1_A5

EBI1_A6

EBI1_A7

EBI1_A8

EBI1_A9

EBI1_A10

EBI1_A11

EBI1_A12

EBI1_A13

EBI1_A14

EBI1_A15

EBI1_BA0/A16

EBI1_BA1/A17

EBI1_A18

EBI1_A19

EBI1_A20

EBI1_A21

EBI1_A22

EBI1_SDCK

EBI1_NCS0

EBI1_NRD/CFOE

EBI1_NWE/NWR0/CFWE

EBI1_NBS1/NWR1/CFIOR

VDDBU

GNDBU

VDDCORE

VDDCORE

VDDCORE

VDDPLLB

VDDPLLA

VDDOSC

GNDPLLB

GNDPLLA

VDDIOP0

VDDIOP0

VDDIOP0

VDDIOP1

VDDIOM0

VDDIOM0

VDDIOM0

VDDIOM0

VDDIOM1

VDDIOM1

VDDIOM1

VDDIOM1

GND

GND

GND

GNDG8GND

GND

GND

GNDH9GND

GNDJ9GND

GND

GNDK9GND

GND

GND

N4

V16

V17

C16

G10

G11

J10

J11

H11

G12

K11

M11

M12

3

EBI1_D0

T10

EBI1_D1

R10

EBI1_D2

N10

EBI1_D3

U11

EBI1_D4

P12

EBI1_D5

V11

EBI1_D6

N11

EBI1_D7

T11

EBI1_D8

R11

EBI1_D9

N12

EBI1_D10

P13

EBI1_D11

V12

EBI1_D12

R12

EBI1_D13

U12

EBI1_D14

T12

EBI1_D15

R13

EBI1_A0

U6

EBI1_A1

V5

EBI1_A2

R6

EBI1_A3

V6

EBI1_A4

P8

EBI1_A5

U7

EBI1_A6

N7

T7

P7

V7

U8

N8

T8

R8

R7

V8

U9

R9

T9

P9

V9

M9

N9

R15

P10

U10

P11

V10

M8

L12

V1

H10

A16

V18

U17

T1

T17

N14

L11

C17

A17

L8

L10

K12

K10

H8

T2

M13

M10

L9

EBI1_A7

EBI1_A8

EBI1_A9

EBI1_A10

EBI1_A11

EBI1_A12

EBI1_A13

EBI1_A14

EBI1_A15

EBI1_A16

EBI1_A17

EBI1_A18

EBI1_A19

EBI1_A20

EBI1_A21

NOT USED

3V3

R136

R136

10K

10K

EBI1_SDCK

EBI1_NCS0

EBI1_NRD/CFOE

EBI1_NWE/NWR0/CFWE

EBI1_NBS1/NW1/CFIOR

C15 100NFC15 100NF

C17 100NFC17 100NF

C18 100NFC18 100NF

C19 100NFC19 100NF

C20 100NFC20 100NF

C21 100NFC21 100NF

C23 100NFC23 100NF

C27 100NFC27 100NF

C29 100NFC29 100NF

C30 100NFC30 100NF

C32 100NFC32 100NF

C34 100NFC34 100NF

C35 100NFC35 100NF

C37 100NFC37 100NF

C38 100NFC38 100NF

C39 100NFC39 100NF

C40 100NFC40 100NF

C41 100NFC41 100NF

C42 100NFC42 100NF

GND

N13

2

EBI1_D[0..15]EBI0_D[0..31]

EBI1_A[0..21]

ETM

TRACE PORT

TPS0

PIPESTAT[0]

TPS1

PIPESTAT[1]

TPS2

PIPESTAT[2]

TSYNC

TRACESYNC

TPK0

TRACEPKT[0]

TPK1

TRACEPKT[1]

TPK2

TRACEPKT[2]

TPK3

TRACEPKT[3]

TPK4

TRACEPKT[4]

TPK5

TRACEPKT[5]

TPK6

TRACEPKT[6]

TPK7

TRACEPKT[7]

VSUPPLY

EXTTRIG

TRACECLK

TCLK

J4-1J4-1

R1370RR137

0R

C160

C160

100NF

100NF

1 2

MN5

MN5

R1100D121C

R1100D121C

J4-2J4-2

3 4

J5-1J5-1

1 2

J5-2J5-2

3 4

J5-3J5-3

5 6

J5-4J5-4

7 8

J5-5J5-5

9 10

AT91SAM9263-EK

AT91SAM9263-EK

AT91SAM9263-EK

AT91SAM9263

AT91SAM9263

AT91SAM9263

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

This agreement is our property. Reproduction and publication without our written authorization shall expose offender to legal proceedings.

2

VDDBU

1

OUT

1V2

3V3

3V3

3V3

3V3

3V3

38

36

34

32

30

28

26

24

22

20

18

16

14

12

10

8

6

4

2

GND

3

VDDISI

2

VDD

A

A

A

REV

REV

REV

SCALE

SCALE

SCALE

G1G2G3G4G5

C16

C16

100NF

100NF

3

INIT EDIT

INIT EDIT

INIT EDIT

1/1

1/1

1/1

37

35

33

31

29

27

25

23

21

19

17

15

13

11

9

7

5

3

1

J28J28

3V3

CR6

CR6

MMBD1704A

MMBD1704A

2

1

JPG

JPG

JPG

DES.

DES.

DES.

TRACEPKT[8]

TRACEPKT[9]

TRACEPKT[10]

TRACEPKT[11]

TRACEPKT[12]

TRACEPKT[13]

TRACEPKT[14]

TRACEPKT[15]

DBGRQ

GND

15-MAR-07B JPG

15-MAR-07B JPG

15-MAR-07B JPG

10-OCT-06

10-OCT-06

10-OCT-06

DATE

DATE

DATE

1

J3J3

R101K R101K

1

TPK8

TPK9

TPK10

TPK11

TPK12

TPK13

TPK14

TPK15

NTRST

TDI

TMS

TCK

RTCK

TDO

NRST

R138

R138

10K

10K

CR1225

CR1225

+

+

3V

3V

VER.

VER.

VER.

REV. SHEET

REV. SHEET

REV. SHEET

B

B

B

Z7

Z7

DATEMODIF.

DATEMODIF.

DATEMODIF.

3

3

3

11

11

11

Page 31

8

7

6

5

4

3

2

1

A[0..22]

D[0..31]

MN6

A2

A4

A5

A6

3V3

R25

R25

470K

470K

A7

A8

A9

A10

A11

SDA10

A13

BA0

BA1

A14

SDCKE

SDCK

NBS0 NBS2

CAS

RAS

SDWE

SDA10

BA0

BA1

SDCKE

SDCK

NBS0 NBS2

CAS

RAS

SDWE

D D

C C

SDCS

R26 0RR26 0R

23

24

25

26

29

30

31

32

33

34

22