ATMEL AT91M40400 Datasheet

Features

•

Incorporates the ARM7TDMI ™ ARM Thumb processor

– High-performance 32-bit RISC architecture

– High-density 16-bit instruction set

– Leader in MIPS/Watt

– Embedded ICE In Circuit Emulation

•

4K bytes internal RAM

•

Fully programmable External Bus Interface (EBI)

– Maximum external address space of 64M bytes

– Up to eight chip selects

– Software programmable 8/16-bit external databus

•

Eight-level priority, individually maskable, vectored interrupt controller

– Four External interrupts, including a high priority low latency interrupt request

•

32 Programmable I/O lines

•

Three-channel 16-bit timer/counter

– Three external clock inputs

– Two multi-purpose I/O pins per channel

•

Two USARTs

– Two dedicated Peripheral Data Controller (PDC) channels per USART

•

Programmable watchdog timer

•

Low-power idle and power-down modes

•

Fully static operation: 0 Hz to 33 MHz

•

2.7V to 3.6V operating range

•

Available in a 100-lead TQFP package

Description

The AT91M40400 is a member of the Atmel AT91 16/32-bit Microcontroller family

which is based on the ARM7TDMI embedded processor. This processor has a highperformance 32-bit RISC architecture with a high-density 16-bit instruction set and

very low power consumption. In addition, a large number of internally banked registers

result in very fast exception handling, making the device ideal for real-time control

applications. The AT91 A RM-based MCU fam ily also features Atmel ’s high-density ,

nonvolatile memory technology. The on-chip Flash program memory is in-system programmable.

The AT91M40400 has a direct connec tion to off-chip me mory, includin g Flash,

through the External Bus Interface.

The device is manufactured u sing Atmel’s hi gh-density CMOS technology. By combining the ARM7TDM I micro control ler co re wi th an on -chip R AM an d a wi de r ange o f

peripheral functions on a monolithic chip, the Atmel AT91M40400 is a powerful microcontroller that provides a fle xible, cost-effecti ve solution to many compute-intens ive

embedded control applic at ion s.

16/32-Bit

Microcontroller

AT91M40400

Summary

Full datasheet (lit# 0768B)

also available by e-mailing

literature@atmel.com

Rev. 0768BS–08/98

1

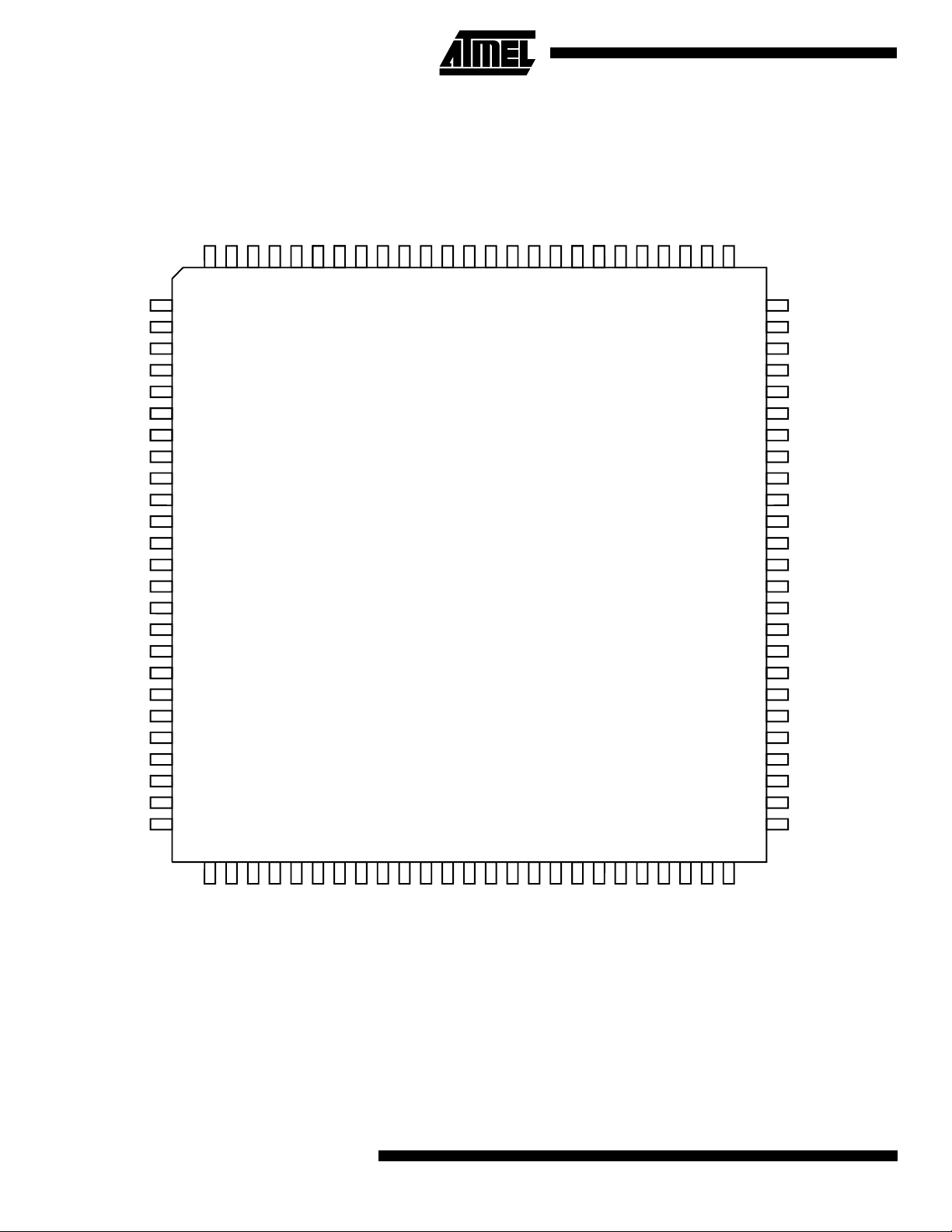

Pin Configuration

Figure 1.

AT91M40400 Pinout (Top View)

P27/NCS3

NCS0

NCS1

P26/NCS2

VDD

NWAIT

NWR0/NWE

VDD

TCK

NRD/NOE

TDO

TDI

TMS

GND

P25/MCKO

GND

P23

P24/BMS

MCKI

VDD

NRST

NWDOVF

NWR1/NUB

GND

P22/RXD1

A0/NLB

GND

A1

A2A2

A3

A4

A5

A6

A7

VDD

A8

A9

A10

A11

A12

A13

A14

GND

GND

A15

A16

A17

A18

A19

P28/A20/CS7

9998979695949392919089888786858483828180797877

100

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

116

17

18

19

20

21

22

23

24

25

26502728293031323334353637383940414243444546474849

AT91M40400

100-Lead TQFP

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

P21/TXD1/NTRI

P20/SCK1

P19

P18

P17

P16

P15/RXD0

P14/TXD0

P13/SCK0

P12/FIQ

GND

P11/IRQ2

P10/IRQ1

VDD

VDD

P9/IRQ0

P8/TIOB2

P7/TIOA2

P6/TCLK2

P5/TIOB1

P4/TIOA1

P3/TCLK1

GND

GND

P2/TIOB0

VDD

VDD

P29/A21/CS6

2

AT91M40400

D0

P31/A23/CS4

P30/A22/CS5

GND

D10

D11

VDD

D12

D13

D14

D15

P1/TIOA0

P0/TCLK0

D9

D8

D7

D6

D5

D4

D3

D2

D1

AT91M40400

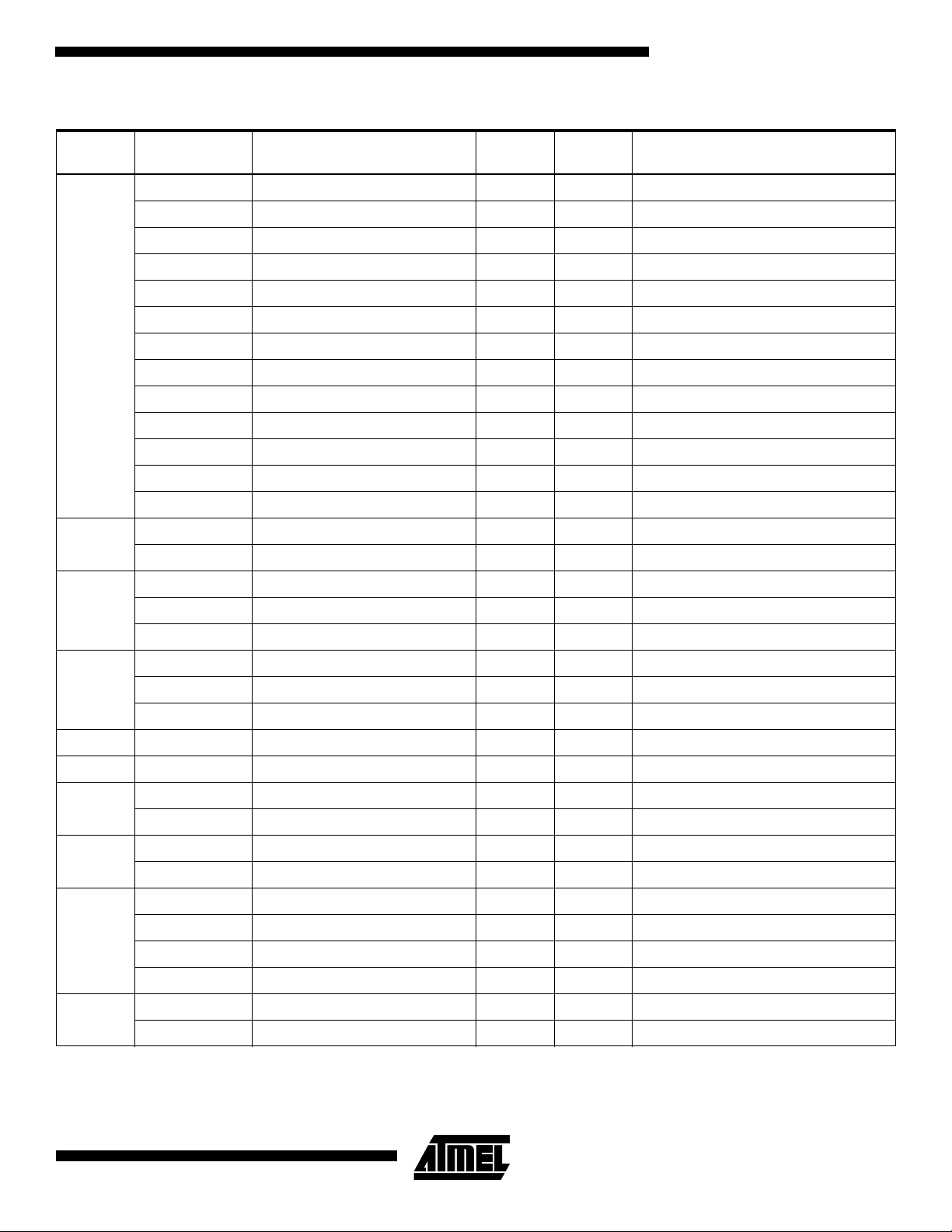

Table 1.

Module Name Function Type

AT91M40400 Pin Description

A0-A23 Address Bus Output -- All valid after reset

D0-D15 Data Bus I/O -NCS0-NCS3 Chip Select Output low

CS4-CS7 Chip Select Output high A23-A20 after reset

NWR0 Lower Byte 0 Write Signal Output low Used in Byte Write Option

NWR1 Upper Byte 1 Write Signal Output low Used in Byte Write Option

EBI

AIC

NRD Read Signal Output low Used in Byt e Write Option

NWE Write Enable Output low Used in Byte Select Option

NOE Output Enable Output low Used in Byte Select Option

NUB Upper Byte Select Output low Used in Byte Select Option

NLB Lower Byte Select Output low Used in Byte Select Option

NWAIT Wait Input Input low

BMS Boot Mode Select Input -- Sampled during reset

FIQ Fast Interrupt Request Input -- PIO controlled after reset

IRQ0-IRQ2 External Interrupt Request Input -- PIO controlled after reset

TCLK0-TCLK2 Timer External Clock Input -- PIO controlled after reset

Active

Level Comments

Timer

USART

PIO P0-P31 Parallel IO line I/O -WD NWDOVF Watchdog overflow Output low Open drain

Clock

Reset

ICE

Power

TIOA0-TIOA2 Multipurpose Timer I/O pin A I/O -- PIO controlled after reset

TIOB0-TIOB2 Multipurpose Timer I/O pin B I/O -- PIO controlled after reset

SCK0-SCK1 External Serial Clock I/O -- PIO controlled after reset

TXD0-TXD1 Transmit Data Output Output -- PIO controlled after reset

RXD0-RXD1 Receive Data Input Input -- PIO controlled after reset

MCKI Master Clock Input Input -- Schmidt trigger

MCKO Master Clock Output Output -NRST Hardware Reset Input Input low Schmidt trigger, internal pull-up

NTRI Tristate Mode Select Input low Sampled during reset

TMS Test Mode Select Input -- Schmidt trigger, internal pull-up

TDI Test Data Input Input -- Schmidt trigger, internal pull-up

TDO Test Data Output Output -TCK Test Clock Input -- Schmidt trigger, internal pull-up

VDD Power

GND G round

3

Loading...

Loading...