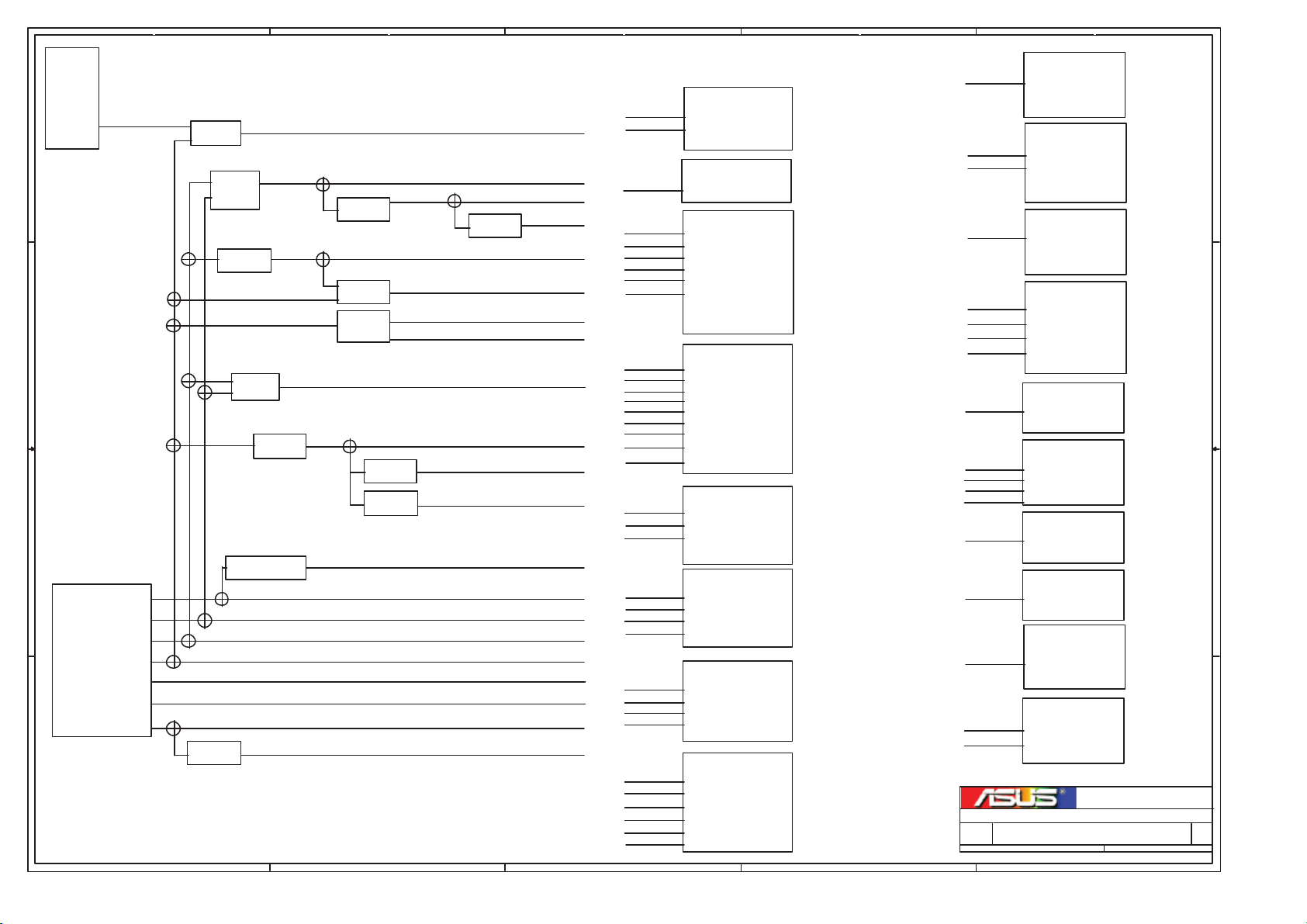

Asus PTGD2-LA Schematics REV 1.03

5

PTGD2-LA

4

3

2

13 3 /200 MHz

100 M H z

1

Revision: 1.03 - A19 ( 3/24/2004 ) DDR2

CLOCK

PAGE

D D

01

02

03

04

05

06

07

08

09

10~13

14~19

20

21

22

C C

23

24

25~27

28

29

30

31

32

33

34

35

36

37

38

B B

39

40

41

42

43

44

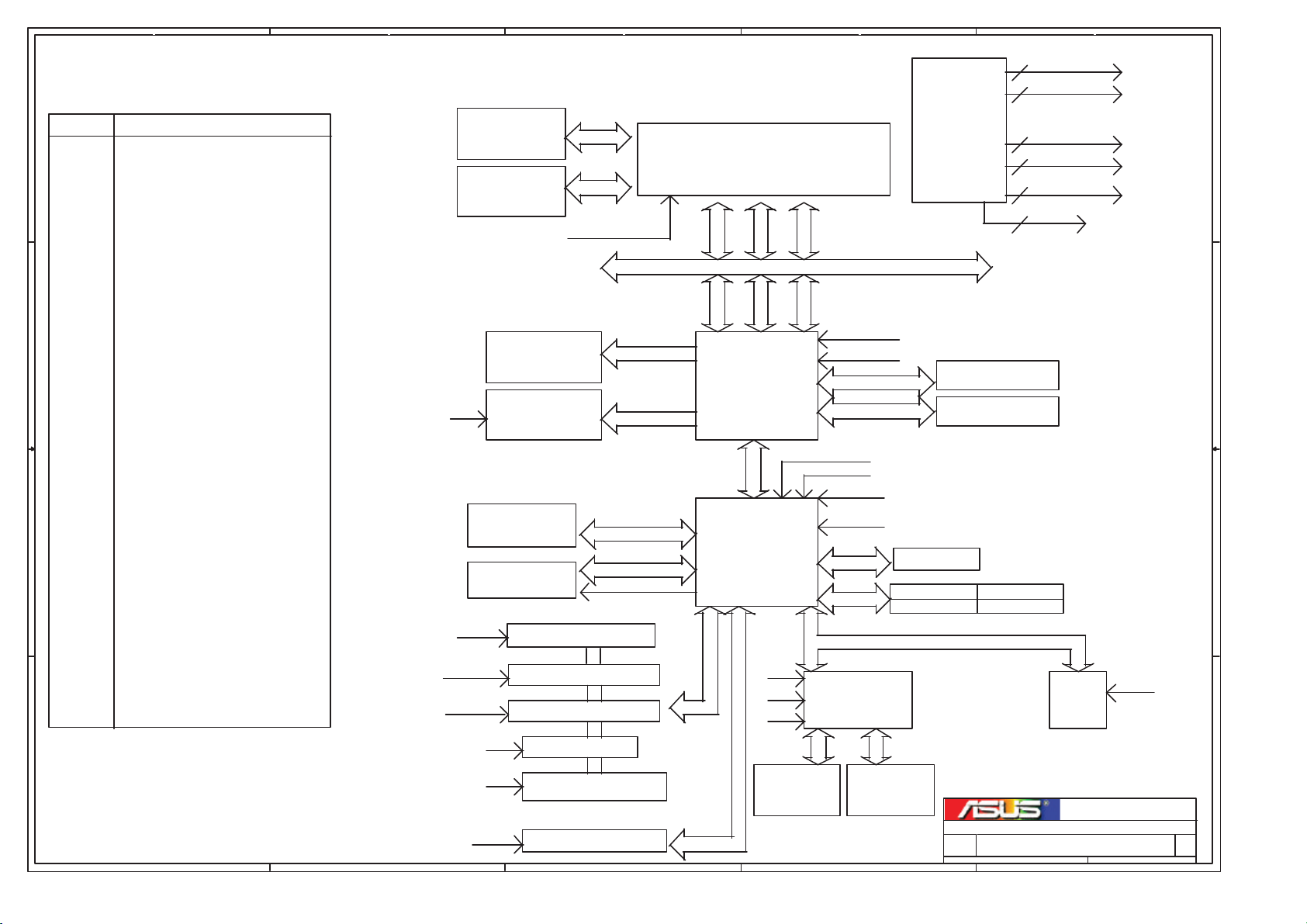

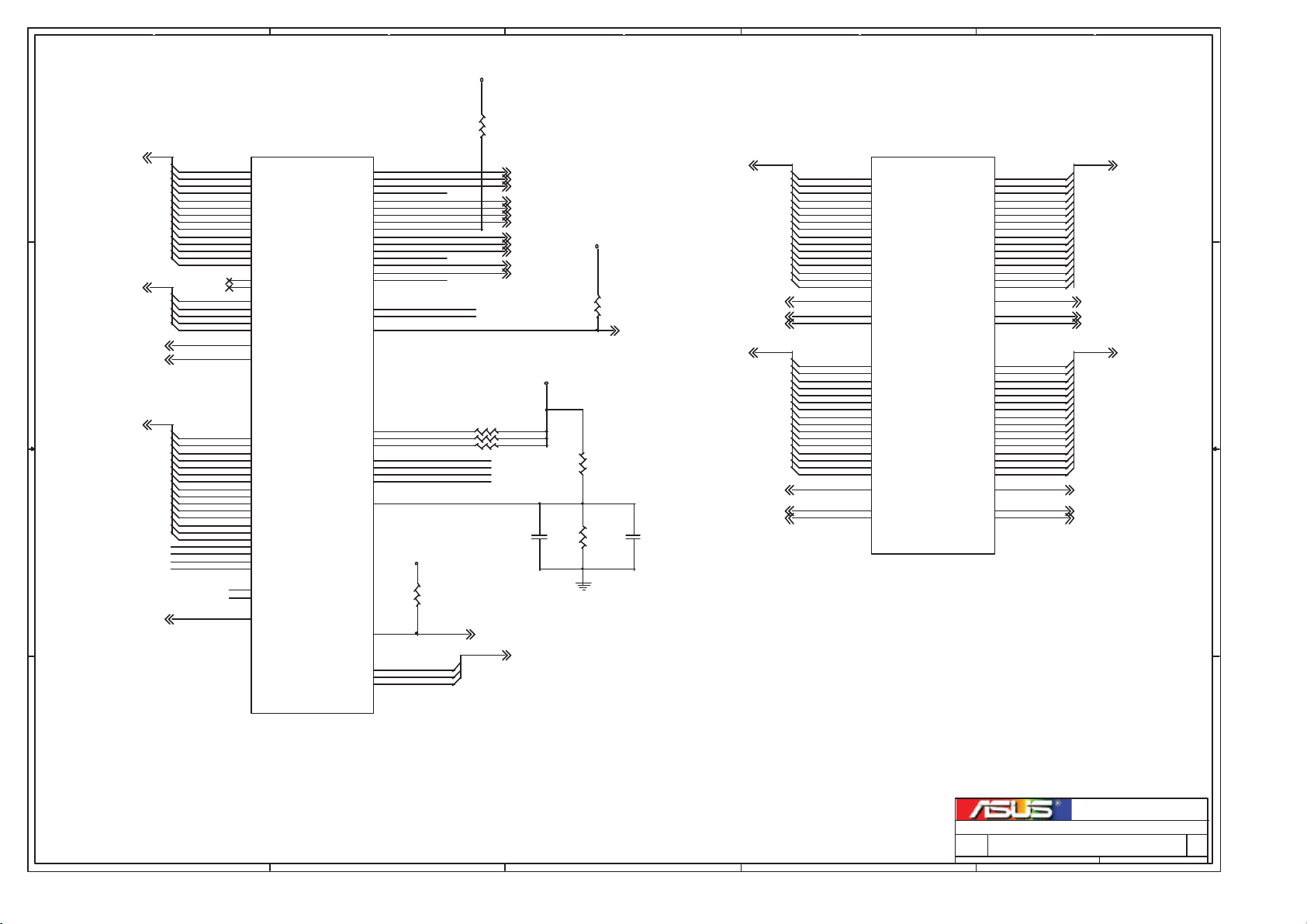

BLOCK DIAGRAM

ECN CONTROL TABLE

CHANGE HISTORY

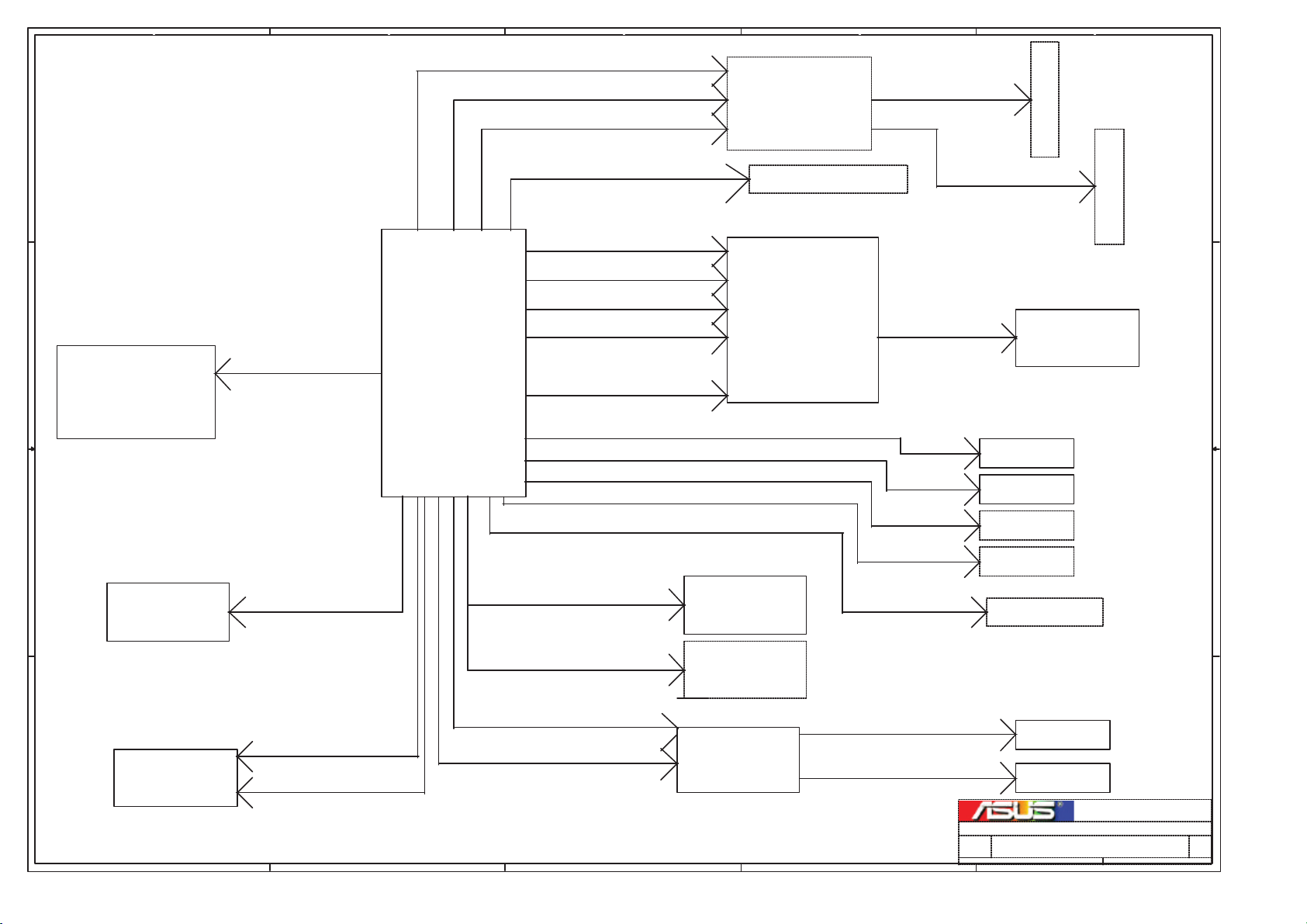

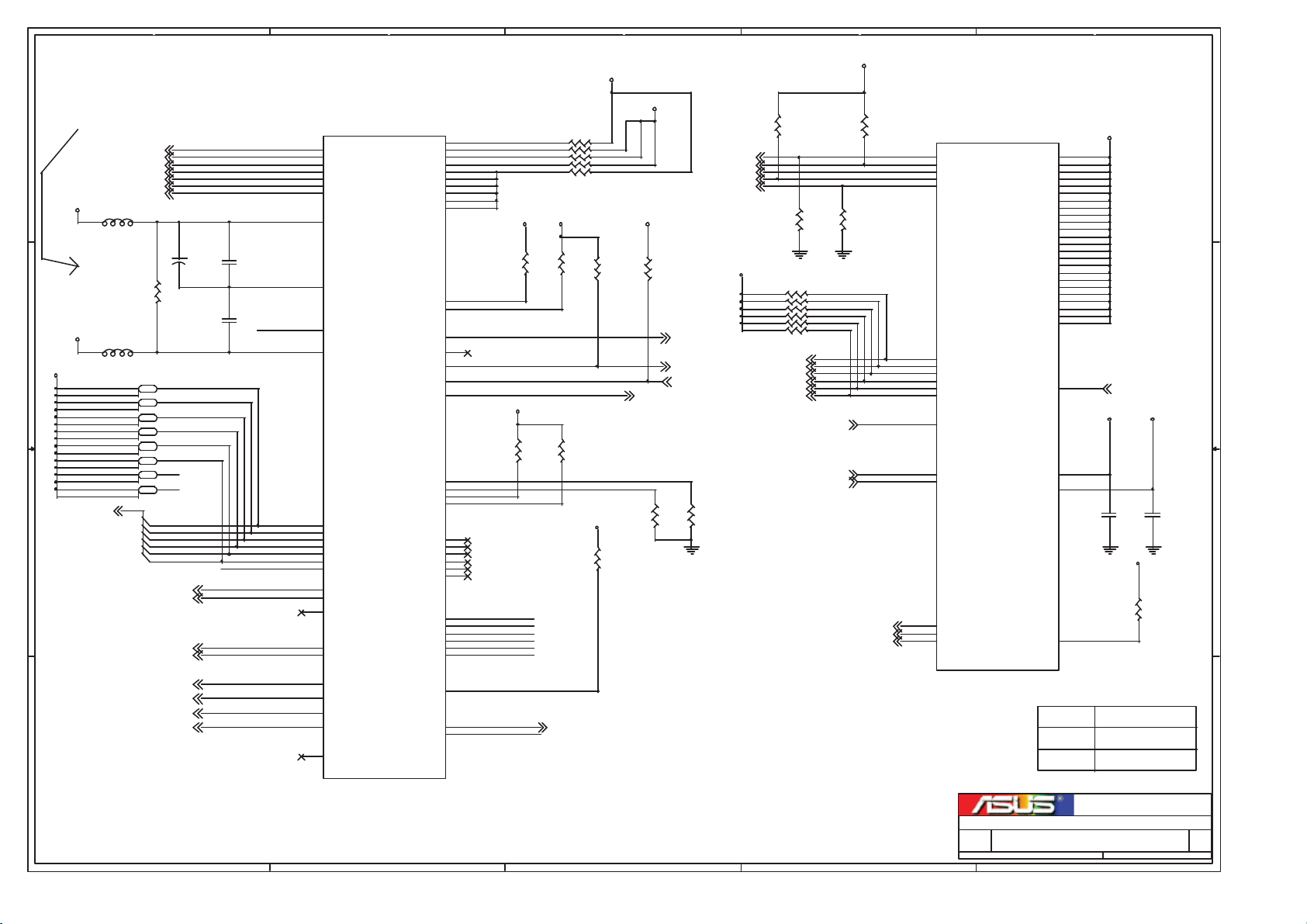

CLOCKS DISTRIBUTION

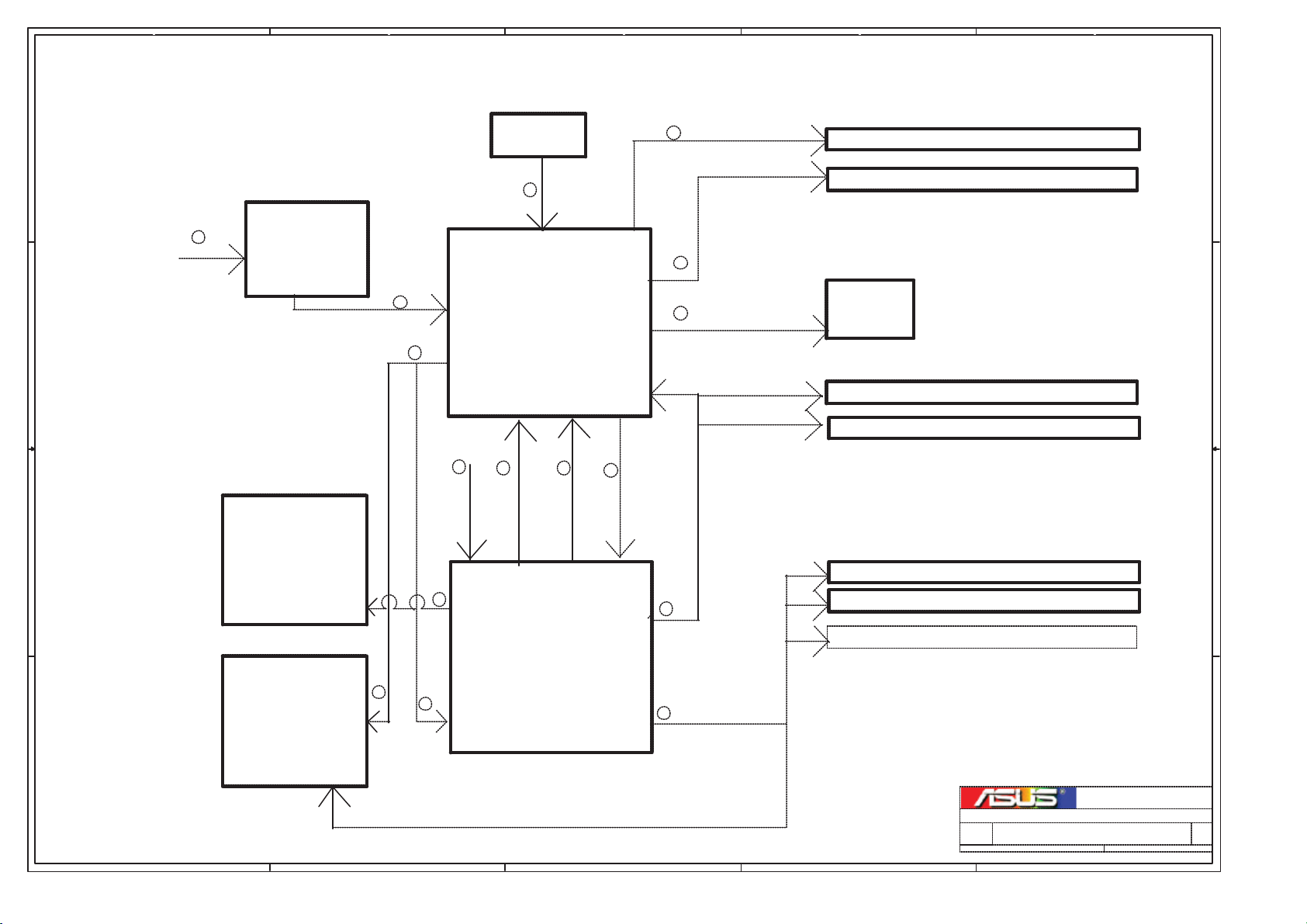

RESET MAP

POWER DISTRIBUTION

POWER FLOW

POWER SEQUENCE

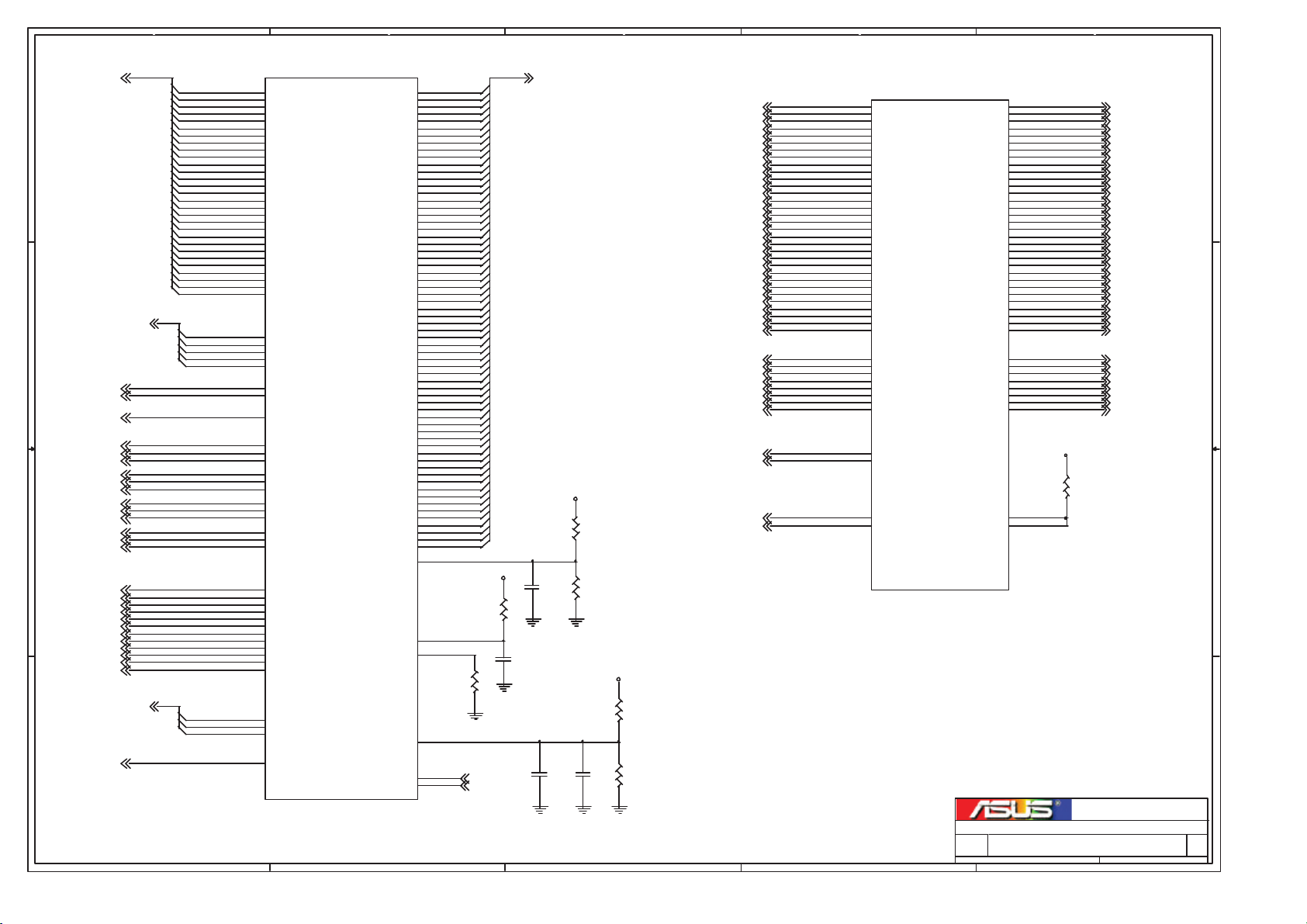

CLOCK ICS954101

PRESCOTT / TEJAS 1-4

GRANTSDALE 1-6

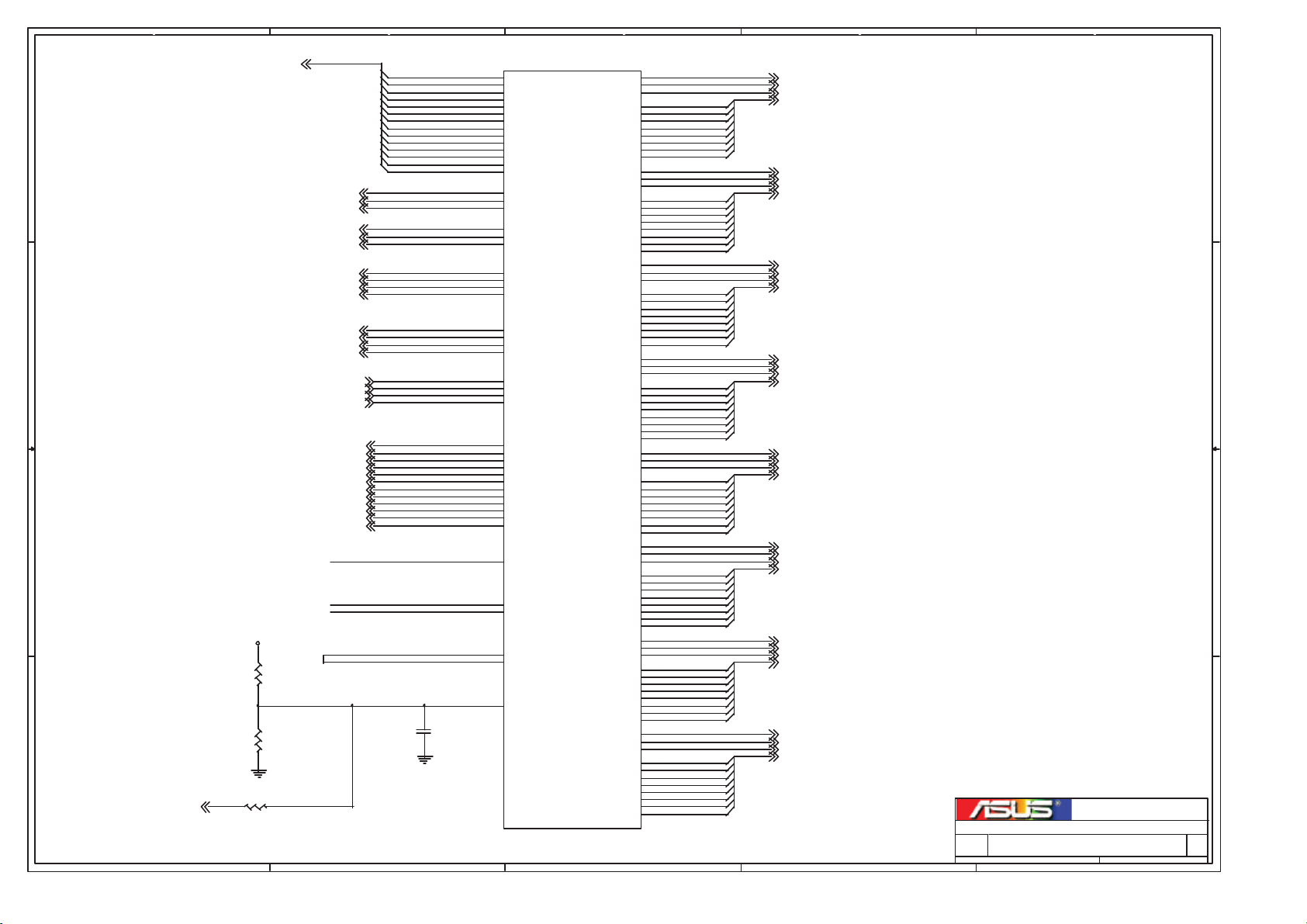

DDR2 - CHANNEL A

DDR2 - CHANNEL B

DDR2 - TERMINATION A&B

VGA PORT

PCI EXPRESS X 16

ICH6 1-3

RTC & F_PANNEL & MH

IDE & SATA

LAN+USB2.0 CONNECTOR

USB POWER

AZALIA CODEC

AZALIA CONNECTOR

PCI SLOT 1

PCI SLOT 2

PCI EXPRESS X 1

PCI EXPANSION RECEPTACLE

LAN 10/100 RTL8101L

IEEE 1394 V6307

1394 & USB CONNECTOR

SIO A8000 & FDD

FWH & KB MS

SERILA & PARALLEL PORT

DDR_DUAL, +1.8_DUAL

45 VCORE CONTROLLER

46

47

48

49

50

A A

VCORE_DRIVERS

ATX PWR & FAN CONTROL

3VSB & FSB PWR

GMCH VCORE

XDP CONNECTOR & EMI CAPS

TITLE

VRD 10.1

on Board

1.5V &

STANDBY

Intel Pentium processor /

Prescott & Tejas

775 Pin Package

REGULATOR

133/200MHz

ADDR

CNTL

DATA

HOST BUS

CNTL

DATA

13 3 /200MHz

100MHz

VGA CONN

ADDR

350Mpixels/s

Grantsdale

GMCH

100MHz

http://laptop-motherboard-schematic.blogspot.com/

5

4

PCI Express

X16 SLOT

High-Speed USB

8 ports

ALC880

AZALIA CODEC

33MHz

33MHz

33MHz

PCI EXPANSION

33MHz

33MHz

100MHz

480Mb/s

AZALIA LINK

24MHz

PCI SLOT

PCI SLOT

V6307

RLC 8101L

PCI EXPRESS X1

PCIE BUS

3

ICH6

PCI BUS

PCIE BUS

DMI LINK

14.318MHz

33MHz

32.768KHz

Flop py

33MHz

48MHz

14.318MHz

100MHz

IDE BUS

IDE BUS

LPC BUS

A8000

SUPER I/O

Keyboard/MouseLPT/CO M

2

CK-410

ICS954101

MEMORY

DDR2 400/533

DDR2 400/533

CAD Note:

Default component footprint is

SMD 0603 type. Difference

footprint show on schematics.

PRIMARY IDE

Serial ATA

Serial ATA

Serial ATA

Serial ATA

ASUSTeK CO MPUTE R INC

Si ze Project Name

A3

星期一 三月

Date: Sheet

96 M Hz

48MHz

33MHz

14.318 MHz

FWH

4MB

32 PLCC

Title :

Engineer:

PTGD2-LA

33MHz

BLOCK DIAGRAM

Samuel Wu

150, 29,2004

1

Rev

1.03

of

5

ASUS ECN Control Table

4

3

2

1

D D

ECN Document Number

C C

B B

DATE

Schematics

Revision

BOM Part

Number

PCBA

Revision

PCB

Revision

A A

ECN CONTROL

ASUSTeK CO MPUTE R INC

Si ze Project Name

A3

5

4

http://laptop-motherboard-schematic.blogspot.com/

3

2

Date: Sheet

星期一 三月

PTGD2-LA

Title :

Engineer:

1

Samuel Wu

of

250, 29,2004

Rev

1.03

5

4

3

2

1

Schematics Change History

Version

1.01 11/30/2003

D D

C C

Date / Author Comments

1. Change RN61 net from +3VSB to +3V (page 27)

John Hong

2. Change Q122 to P-MOS Vgs(th)=2.4V, 07-005002110 (page 26)

3. Remove R983 (page 26)

4. Change SYS_RESET# PU RN from RN62 to RN61 (page 26)

5. Change ICH_W6_PU RN from RN61 to RN62 (page 26)

6. Change FP_LINE pin define

7. Change EXP_SLR PU voltage to +1.5V

8. Change Azalia port define

9. Change R491 to 18.2K ohm (making +1.2V_HT=1.189V)

10. Change DDR2 termination res to 39 ohm (only for CS#, CKE,

ODT), this changing will improve DDR2 margin.

11. Change to HP naming rule.

12. Change VGA HSYNC and VSYNC level shift P-MOS.

13. Change FLOPPY pin3 to pin7 as GPIO.

14. Change SIO and NIC

15. Change NIC and 1394 ID to 17 and 18

SSID List

SUBSYSTEM ID

CLK

CORE

NB

MEM

VGA

PE16

SB

RTC

CCMOS

SMBUS

IDE

SATA

FWM

LAN

USB

EMI

AUD

F_AUD FRONT AUDIO

PE1

PCI

PECTL

DESCRIPTION

CLOCK GENERATOR

CPU CORE

NORTH BRIDGE GMCH

MEMORY

INTERNAL VGA

PCI EXPRESS x16

SOUTH BRIDGE ICH6

RTC

CLEAR CMOS

SMBUS

UATA IDE CONNECTOR

SERIAL ATA CONNECTOR

FIRMWARE HUB ROM

LAN CONNECTOR

USB

EMI

AC97 AUDIO CODEC

PCI EXPRESS x1

PCI SLOT

PCI EXPRESS CONTROLLER

PS2 KB & MOUSEPS2

COM

E1394

PANEL

VCORE

ITP

LPT

THERM

V_DDR

B B

R_1.5V

V_PCI

5V_DUAL

3VSB

VTT_CPU

LED

ATX

VRM

1.8V_DUAL

SERIAL PORT

IEEE 1394

HPQ PANEL

VCORE

PROCESSOR ITP

PARALLEL PORT

THERMALTRIP

VTT_DDR

+1.5V

+3.3V_PCI

+5V_DUAL

+3VSB

VTT_CPU

LED

ATX POWER SUPPLY

VRM POWER SUPPLY

+1.8V_DUAL

A A

Title :

CHANGE HISTORY

ASUSTeK CO MP UT ER IN C

Si ze Project Name

A3

5

4

http://laptop-motherboard-schematic.blogspot.com/

3

2

Date: Sheet

星期一 三月

PTGD2-LA

Engineer:

Samuel Wu

350, 29,2004

1

Rev

1.03

of

5

4

3

2

1

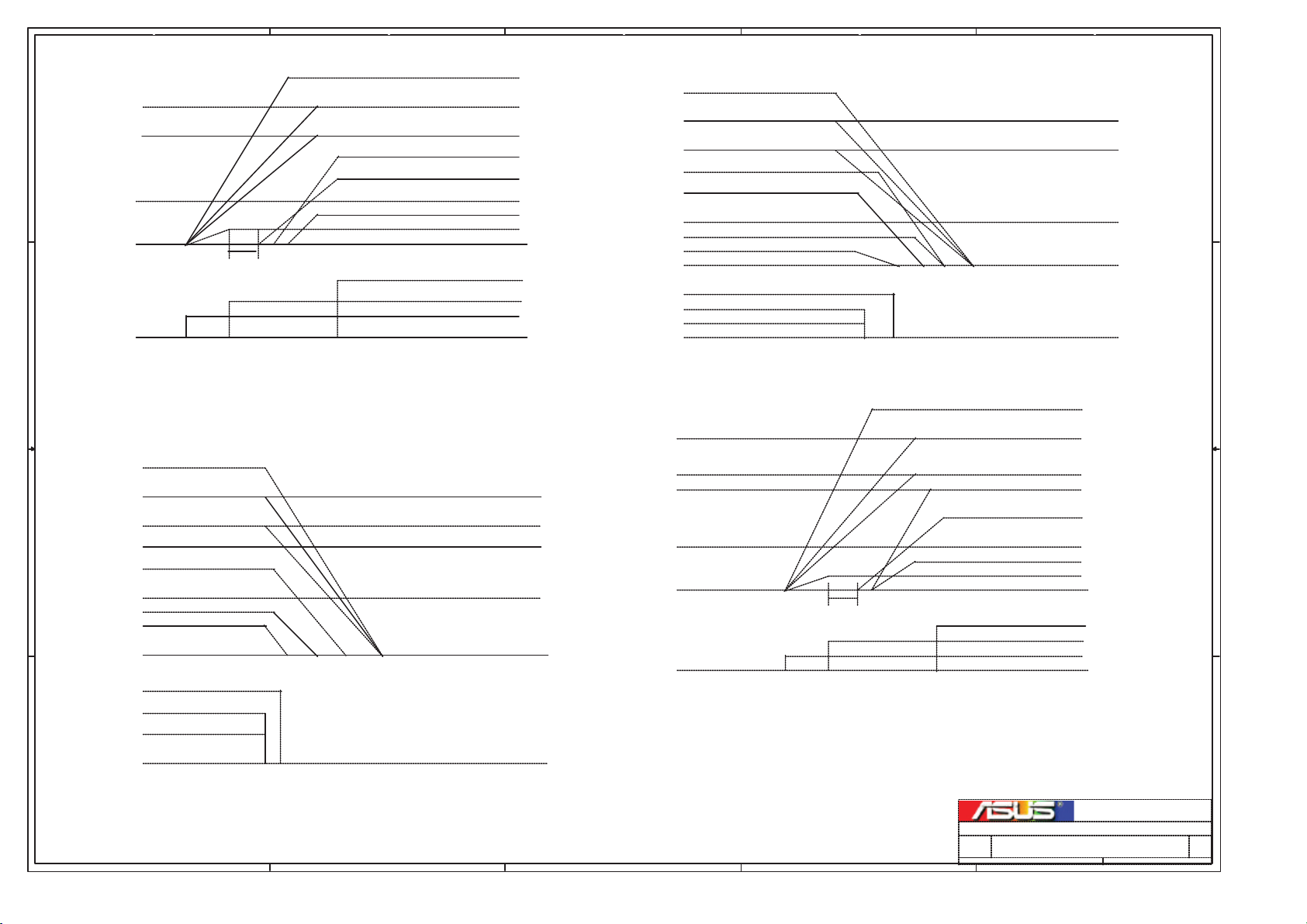

MCHHCLK/#

133/200 MHz

Intel

CK_100M_MCH/#

CK_96M_DREF/#

D D

CK_100M_PE16/#

CK_100M_SATA/#

100 MHz

96 MHz

100 MHz

100 MHzCK_100M_ICH/#

100 MHz

Grantsdale

GMCH

PCIEx16 Slot

M_CHA_CLK[0..5]/#

DDR2 1,2

M_CHB_CLK[0..5]/#

DDR2 3,4

Intel

CK_33M_ICH

C C

Intel Processor

Prescott

CPUHCLK/#

133/200 MHz

755 Pin Package

CLOCK CHIP

CK410

ICS954101

CK_48M_USB 48 MHz

CK_14M_ICH

CK_33M_SL1

CK_33M_SL2

CK_33M_SL4

CK_33M_SL5

33 MHz

14.318 MHz

33 MHz

33 MHz

33 MHz

33 MHz

ICH6

RBITCLK

24 MHz

AZALIA

Codec

PCI1 Slot

PCI2 Slot

100 MHzCK_100M_PE1/#

B B

FWH

A A

ITP

5

CK_33M_FWH

CK_ITP/#

CK_100M_ITP/# 100 MHz

33 MHz

133/200 MHz

4

http://laptop-motherboard-schematic.blogspot.com/

CK_33M_LAN

33 MHz

33 MHzCK_33M_1394

RTL 8100 NIC

IEEE 1394

14.318 MHzCK_14M_SIO

CK_33M_SIO 33 MHz

3

LPC47M287

KB_CLK

MSE_CLK

2

PCI4 Slot

PCI5 Slot

PCIEx1 Slot

Keyboard

Mouse

Title :

ASUSTeK CO MP UT ER IN C

Si ze Project Name

A3

Date: Sheet

星期一 三月

PTGD2-LA

Engineer:

1

CLOCK DISTRIBUTION

Samuel Wu

of

450, 29,2004

Rev

1.03

5

POWER

SUPPLY

Pentium

Processor

Power

Buttom

4

G0-to-G3 State Explain:

a. VCCSUS dirves high when PWR CONN plugd in.

b. RSMRST# drives high from SIO to ICH6.

c. SUSCLK sent out CLK from ICH6 to SIO.

3

2

1

D D

SLP_S3#

invert

C C

4

P

PSON#

PG1

5

PWROK

6

1

PWROK

B B

Prescott/Tejas

PWRBTN#

SW

1

PWRBTN#

PB_IN#

nPCIRST_OUT1

nPCIRST_OUT3

LPC47M287

SUPER I/O

PWRGD_PSPWRGD_3V

nPCIRST1_OUT2

Included Power Sequence

Logic Function

SLP_S5#

PWRBTN#

SLP_S3#

2

SLP_S5# SLP_S3#

3

SLP_S5#

RSMRST#

0

SLP_S3#

RSMRST#

7

PCI_RESET#

RSMRST#

LAN_RST#

1394_RST#

7

7

PCIRST#

PCIRST#

RST#

10/100 GIGABIT NIC

IEEE 1394

FWH

PCI-Express x16

PCI-Express x1

RST

PCI SLOT 1

775

PWRGOOD

CPUPWRGD

6

CPUPWRGD

ICH6

SOUTH BRIDGE

6

PLTRST#

ICHPCIRST#

RST

RST

PCI SLOT 2

PCI EXPANSION

GRANTSDALE

NORTH BRIDGE

A A

5

PWROK

5

PWROK

6

PCISLOTRST#

PLTRST#

RSTIN#

Title :

http://laptop-motherboard-schematic.blogspot.com/

5

4

3

2

ASUSTeK CO MPUTE R INC

Si ze Project Name

A3

Date: Sheet

星期一 三月

PTGD2-LA

Engineer:

1

RESET MAP

Samuel Wu

550, 29,2004

Rev

1.03

of

5

CR2032

3.0 Volt

BATTERY

220 mAh

20mA Max

XBAT1

D D

C C

B B

POWER

SUPPLY

+12V

+5V

BAT45CW

+5VSB

+3V

-5V

-12V

CPU_12V

A A

ADP3418

5

AP70T03H

APM2301B

HJ8829

+3V

+3V

+3V

BATT

FUSB+5V

+3VSB

AP4502

RT9202CS

LM78L05ACM

VCORE

BUSB+5V

+1.5V

+5VA

RT9202CS

AP4502

LM324MX

FILTER

FILTER

4

+1.8V_DAUL

+3V_DUAL

+2.5V_DAC

+1.2V_FSB_VTT

PCIE_PWR

4

3

http://laptop-motherboard-schematic.blogspot.com/

Prescott &Tejas

VCORE 95A 123W

+1.2V_FSB_VTT tbd A

BATT

CLOCK

+3V 560mA 1.85W

Grantsdale

+1.5V 9.7A 14.6W(Integrated)

ICH6

+1.5V 1.88A 2.82W

+1.5V 0.43A 2.15W (SATA)

+5V tbd mA (V5REF)

+5VSB tbd mA (V5REF_SUS)

+3V 180mA 540mW

BATT 5uA 15uW (G3)

+3VSB 330mA 0.99W

DDR2 DIMM

PCI EXPRESSx16

+12V 4.4A 52.8W

+3VSB 0.375A 11.13W (wake)

+3VSB 20mA 66mW (no wake)

+3V 3.0A 9W

PCI EXPRESSx1

+12V 0.5A 6W

+3VSB 0.375A 11.13W (wake)

+3VSB 20mA 66mW (no wake)

+3V 3.0A 9W

PCI SLOT/EXTENSION

+3VSB 0.375A 11.13W (wake)

+3VSB 20mA 66mW (no wake)

+3V 3.8A 11.4W

+5V 2.5A 12.5W

+12V 0.25A 3W

-12V 0.05A 600mW

RT9173BCL5

+1.2V_FSB_VTT

+1.5V_PCIEXPRESS

FUSB+5V

+1.8V_DAUL

VTT_DDR

+3VSB

+3V_DUAL

+2.5V_DAC

BUSB+5V

+1.5V

PCIE_PWR

+5VA

+12V

+5V

+5VSB

+3V

-5V

-12V

CPU_12V

VCORE

+1.8_DUAL 4.6A 8.28W (S0,S1)

+1.8_DUAL 250mA 0.45WW (S3)

+1.2V_FSB_VTT 1.2A 1.44W

+1.5_PCIEXEPRESS 1.4A 2.1W

+2.5V_DAC 0.07A 175mW

+1. 2V_FSB_VTT tbd A

PCI E_PWR 270mA 4.5mW

+1.8_DUAL 9.4A 16.92W (S0,S1)

+1.8_DUAL 400mA 0.72W (S3)

VTT_DDR 1.2A

3

2

1

NIC

+3VSB tbdA tbdW

SUPER I/O

+3V tbdA tbdW

+3VSB tbdA tbdW

PS2 KB/M

+5VSB 345mA 1.73W

SERIAL

+12V 20mA 240mW

-12V 20mA 240mW

+5V 30mA 150mW

+3VSB 50uA 150uW

PARALLEL

+5V 15mA 74mW

USB 8 PORT

BUSB+5V 2A 10W (S0,S1)

BUSB+5V 10mA 50mW (S3)

FUSB+5V 2A 10W (S0,S1)

FUSB+5V 10mA 50mW (S3)

FWH

+3V 107mA 321mW

FAN

+12V 0.5A 6W

IEEE 1394

+3V_DUAL tbdA tbdW

AZALI CODEC

+5VA tbdA tbdW

+3V tbdA tbdW

Title :

ASUSTeK CO MPUTE R INC

Si ze Project Name

A3

Date: Sheet

2

星期一 三月

PTGD2-LA

Engineer:

1

POWER DISTRIBUTION

Samuel Wu

of

650, 29,2004

Rev

1.03

Idc=70mA

D D

5

4

3

2

1

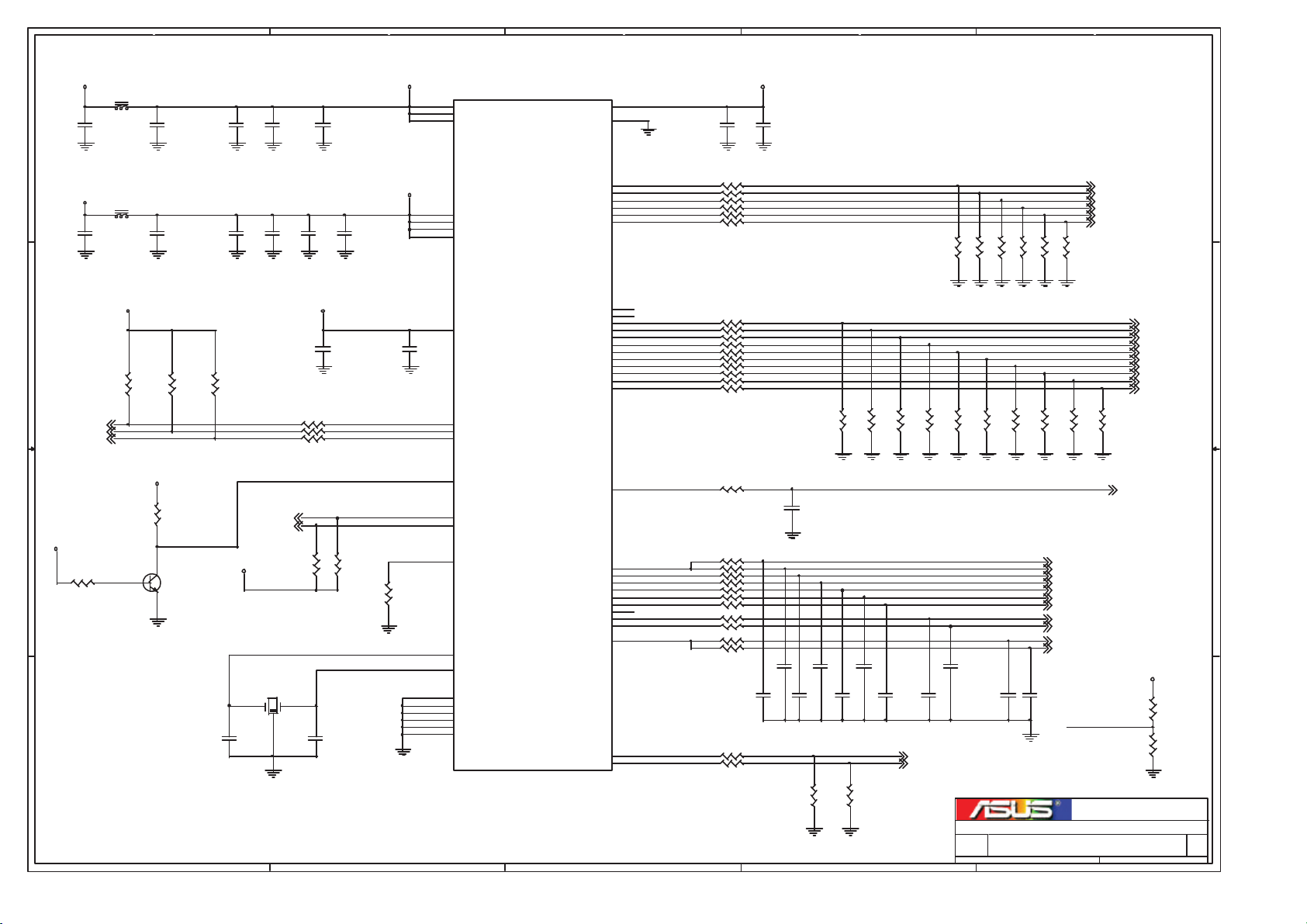

ADP3168

4 Phases

Iocp

+12V

+5V

Silver B ox

C C

+5VSB

+3.3V

Imax

eff.

AP9918H

&

AP2301N

RT9202

Iocp

Imax

eff.

200A

120A

80%

+5V_DUAL

10A

12A

80%

VCORE

Idc=100A

RT9202

Iocp

Imax

eff.

24A

15.2A

80%

+1.5V

Idc=12A

+1.8V_DUAL

Idc=14A

RT9173

Iocp

2A

Imax 1.2A

VTT_DDR

Idc=1.2A

+2.5V_DAC

OP+HM882

70mA

Imax

Idc=70mA

+3VSB

Power Rail

H431+HJ882

2.0A

Imax

Idc=2A

+3V_DUAL

Idc=3A

AP4502M

B B

Switch

ON/OFF

Linear

Switching

OP+AP9915H*2

3A

Imax

+1.2V_FSB_VTT

Idc=3A

http://laptop-motherboard-schematic.blogspot.com/

A A

Title :

POWER FLOW

ASUSTeK CO MP UT ER IN C

Si ze Project Name

A3

5

4

3

2

Date: Sheet

星期一 三月

PTGD2-LA

Engineer:

Samuel Wu

750, 29,2004

1

Rev

1.03

of

5

4

3

2

1

S5->S0

+12V

S0->S5

+12V

+3.3V_AUX

+1.5V_AUX

V_5P0_DUAL

&

+3.3V

+2.5VSTBY

CPUCORE

+1.5V

&

+1.25V

+1.2V

VRM_PWRGOOD

VRM_OUTEN

PS-ON

V_5P0_DUAL

+3.3V_AUX

&

V_5P0_DUAL&

+3.3V

+5V_AUX

+3.3V_AUX

+2.5VSTBY

CPUCORE

+1.5V_AUX

0

+1.25V

+1.2V

&

+1.5V

0

+1.5V_AUX

0

VRM_PWRGOOD

VRM_OUTEN

PS-OFF

0

0

0

+5V_AUX

+3.3V_AUX

D D

+1.5V_AUX

0

1-5ms

0

C C

1.CPUCORE must rise after the voltage across 90% of +1.2V,andthe interval is within 1-5ms

2.VRM_OUTEN rises after the voltage across 90% of its specified value

S3->S0

+12V

S0->S3

+12V

V_5P0_DUAL

+3.3V_AUX

&

+3.3V

+2.5VSTBY

B B

CPUCORE

+1.5V_AUX

+1.5V&

V_5P0_DUAL

+3.3V_AUX

+2.5VSTBY

+1.5V_AUX

+5V_AUX

+3.3V_AUX

+2.5VSTBY

+1.5V_AUX

0

V_5P0_DAUL

+3.3V_AUX +3.3V

&

+2.5VSTBY

CPUCORE

+1.5V

&

+1.5VSB

+1.25V

+1.2V

0

+1.25V

+1.2V

1-5ms VRM_PWRGOOD

VRM_OUTEN

0

0

0

PS-ON

0

VRM_PWRGOOD

VRM_OUTEN

PS-OFF

1.CPUCORE must rise after the voltage across 90% of +1.2V,andthe interval is within 1-5ms

2.VRM_OUTEN rises after the voltage across 90% of its specified value

A A

S0:

S3:

S5:

0

Windows Running

Windows Standby

AC Power On Only

5

+12V,V_5P0_DUAL,+3.3V,+3.3V_AUX,+2.5VSTBY,CPUCORE,+1.5V,+1.5V_AUX,+1.25V,+1.2V existed

V_5P0_DUAL,+3.3V_AUX,+1.5V_AUX,+2.5VSTBY existed

+5V_AUX,+3.3V_AUX,+1.5V_AUX existed

4

0

http://laptop-motherboard-schematic.blogspot.com/

3

Title :

POWER SEQUENCE

ASUSTeK CO MP UT ER IN C

Si ze Project Name

A3

2

Date: Sheet

星期一 三月

PTGD2-LA

Engineer:

Samuel Wu

850, 29,2004

1

Rev

1.03

of

5

4

3

2

1

+3V_DUAL

L1

12

CB1

0.1UF/25V

NI

D D

C C

B B

A A

GND GND GND GND

+3V_DUAL

12

CB8

0.1UF/25V

NI

FSBSEL0{11,17,50}

FSBSEL1{11,17,50}

FSBSEL2{11,17,50}

VCORE

R46

1 2

220Ohm

21

120Ohm/100MHz

L3

21

120Ohm/100MHz

+1.2V_FSB_VTT

1 2

R46_Q1

1

PMBS3904

R24

470Ohm

CLKVCC3

Q1

B

GND

5

12

12

1 2

3

C

E

2

CB4

10UF/10V

c0805

CB9

10UF/10V

c0805

R25

470Ohm

1 2

R44

4.7KOhm

1 2

12

12

R26

470Ohm

SMBCLK_DDR{20,21,41,50}

SMBDATA_DDR{20,21,41,50}

+3V

12

12

CB5

0.1U

X7R

12

CB10

0.1U

X7R

GNDGNDGND

R41 10 K1 2 R36

R42 10 K1 2

R43 10 K1 2

X1

12

3

C76

30P

GND

12

CB6

0.1U

X7R

GND

12

CB11

CB12

0.1U

0.1U

X7R

X7R

GNDGND

CLKVCC3

12

GND GND

R13

4.7KOhm

1 2

14.31818MHZ

12

C81

CB409

0.1U

X7R

12

GND

CB15

10UF/10V

c0805

1 2

OSC_CK14M_XTALIN

OSC_CK14M_XTALOUT

30P

CB13

0.1U

X7R

R14

4.7KOhm

CLKVCC3

CLK_VDDSRC

FS_A

FS_B

FS_C

CLKCPUPG#

IREF

R49

475

1%

1 2

GND

GND

4

12

GND

1 2

1 2

1 2

1 2

1 2

1 2

CLK_VDDSRC

12

CB2

0.1U

X7R

GND

12

CB3

10UF/10V

c0805

12

C343

15P

R8

R7

49.9

1%

1 2

1 2

GND

R32

1 2

GND

12

49.9

1%

C7

15P

12

R33

49.9

1%

1 2

C8

15P

CK_96M_DREF {1 7}

CK_96M_DREF# {17}

R31

49.9

1%

1 2

GND GND

12

C406

http://laptop-motherboard-schematic.blogspot.com/

10P

NI

GND

12

C4

C344

15P

15P

12

12

C5

C6

15P

15P

R61

R60

49.9

49.9

1%

1%

1 2

1 2

GNDGND

2

R35

R34

49.9

49.9

1%

1%

1 2

1 2

GND GNDGND GND GND

12

C11

15P

12

C10

15P

ASUSTeK CO MPUTE R INC

Si ze Project Name

A3

星期一 三月

Date: Sheet

R10

R9

49.9

49.9

49.9

1%

1%

1%

1 2

1 2

GND

GND GNDGND GND

R975

49.9

49.9

1%

1%

1 2

1 2

GND GND

12

12

C401

C13

10P

10P

NI

NI

GND

PTGD2-LA

1 2

1 2

MCHHCLK {14}

MCHHCLK# {1 4 }

CPUHCLK {11 }

CPUHCLK# {1 1 }

CK_ITP {5 0}

CK_ITP# {5 0}

PROTO

PROTO

R11

R12

49.9

49.9

1%

1%

1 2

R976

R39

49.9

49.9

1%

1%

1 2

CK_33M_SIO {4 1 }

CK_33M_FWH {42 }

CK_33M_LAN {38}

CK_33M_1394 {39}

CK_33M_ICH {2 5 }

CK_33M_SL5 {37}

CK_33M_SL4 {37}

CK_33M_SL2 {35}

CK_33M_SL1 {34}

CK_14M_ICH {2 6 }

CK_14M_SIO {4 1 }

CK_33M_1394

1: CPU2CLK

0: SRCCLK

Title :

Engineer:

1

CK_100M_ICH {2 5}

CK_100M_ICH# {25}

CK_100M_SATA {26}

CK_100M_SATA# {26 }

CK_100M_MCH {14}

CK_100M_MCH# {1 4}

CK_100M_PE1 {36 }

CK_100M_PE1# {36}

CK_100M_PE16 {24}

CK_100M_PE16# {24}

R40

49.9

1%

1 2

CK_48M_USB {25 }

+3V

1 2

1 2

GND

CLOCK ICS95410 1

Samuel Wu

950, 29,2004

R741

4.7KOhm

R742

4.7KOhm

NI

of

Rev

1.03

U1

1

VDDPCI1

7

VDDPCI2

48

VDDREF

42

VDDCPU

21

VDDSRC1

28

VDDSRC2

34

VDDSRC3

11

CB16

0.1U

X7R

VDD48

18

FS_A

16

FS_B/TEST_MODE

53

FS_C/TEST_SEL

17

Vtt_PwrGd#/PD

46

SCLK

47

SDATA

39

IREF

50

X1

49

X2

2

GND1

6

GND2

13

GND3

29

GND4

45

GND5

51

GND6

12

CPUCLKT2_ITP/SRCCLK_7

CPUCLKC2_ITP/SRCCLK_7

SRCCLKT4_SATA

SRCCLKC4_SATA

ITP_EN/PCICLK_F0

VDDA

GNDA

CPUCLKT0

CPUCLKC0

CPUCLKT1

CPUCLKC1

SRCCLKT6

SRCCLKC6

SRCCLKT5

SRCCLKC5

SRCCLKT3

SRCCLKC3

SRCCLKT2

SRCCLKC2

SRCCLKT1

SRCCLKC1

USB_48MHz

PCICLK_F2

PCICLK_F1

PCICLK5

PCICLK4

PCICLK3

PCICLK2

PCICLK1

PCICLK0

REFOUT

DOTT_ 96MHz

DOTC_96MHz

37

38

GND

44

RMCHHCLK

RMCHHCLK#

43

RCPUHCLK

41

RCPUHCLK#

40

RCK_ITP

36

RCK_ITP#

35

33

32

RCK_100M_ICH

31

RCK_100M_ICH#

30

RCK_100M_SATA

26

RCK_100M_SATA#

27

RCK_100M_MCH

24

RCK_100M_MCH#

25

RCK_100M_PE1

22

23

RCK_100M_PE1#

RCK_100M_PE16

19

RCK_100M_PE16#

20

RCK_48M_USB

12

RCK_33M_1

10

9

RCK_33M_LAN

RCK_33M_1394

8

RCK_33M_ICH

5

RCK_33M_SL5

4

3

RCK_33M_SL4

56

55

RCK_33M_SL2

54

RCK_33M_SL1

52

RCK_14M

14

RCK_96M_DREF

15

RCK_96M_DREF#

CLK_VDDA

R1 331 2

R2 331 2

R3 33

R4 331 2

R5 33 PROTO1 2

R6 33 PROTO1 2

R15 331 2

R17 331 2

R18 331 2

R19 33

R20 331 2

R21 331 2

R973 331 2

R974 331 2

R27 33

R28 331 2

R45 33

R163 20Ohm

R145 20Ohm1 2

R146 391 2

R954 391 2

R147 391 2

R177 39

R178 391 2

R211 391 2

R213 391 2

R143 331 2

R203 331 2

R58 331 2

R59 331 2

CV110J

3

5

D D

HA#[3..16]{14}

HREQ#[0..4]{14}

C C

B B

HADSTB0#{14}

HPCREQ#{14}

HA#[17..31]{14}

HADSTB1#{14}

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9 HD#37

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

TP_CPU_AH4

TP_CPU_AH5

TP_CPU_AJ5

TP_CPU_AJ6

AB6

AA4

AD6

AA5

AB5

AC5

AB4

AF5

AF4

AG6

AG4

AG5

AH4

AH5

AJ5

AJ6

AC4

AE4

AD5

L5

P6

M5

L4

M4

R4

T5

U6

T4

U5

U4

V5

V4

W5

N4

P5

K4

J5

M6

K6

J6

R6

G5

W6

Y6

Y4

CPUA

A03#

A04#

A05#

A06#

A07#

A08#

A09#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

RSVD1

RSVD2

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

ADSTB0#

PCREQ#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

A32#

A33#

A34#

A35#

RSVD3

RSVD4

ADSTB1#

ADS#

BNR#

HIT#

RSP#

BPRI#

DBSY#

DRDY#

HITM#

IERR#

INIT#

LOCK#

TRDY#

BINIT#

DEFER#

EDRDY#

MCERR#

AP0#

AP1#

BR0#

TESTHI08

TESTHI09

TESTHI10

DP0#

DP1#

DP2#

DP3#

GTLREF

RESET#

RS0#

RS1#

RS2#

4

D2

C2

D4

TP_CPU_H4

H4

G8

B2

C1

E4

AB2

P3

C3

E3

TP_CPU_AD3

AD3

G7

F2

TP_CPU_AB3

AB3

U2

U3

F3

G3

G4

H5

J16

H15

H16

J17

CPU_GTLREF0

H1

+1.2V_FSB_VTT

G23

HRS#0

B3

HRS#1

F5

HRS#2

A3

HIERR#

TP_CPU_U2

TP_CPU_U3

TESTHI8

R830

TESTHI9

R831

TESTHI10

R832

TP_CPU_J16

TP_CPU_H15

TP_CPU_H16

TP_CPU_J17

12

R70

62Ohm

VTT_OUT_R

12

R62

62

1 2

62Ohm

1 2

62Ohm

1 2

62Ohm

CPURESET# {14,50}

HADS# {1 4 }

HBNR# {1 4 }

HIT# {14 }

HBPRI# {14}

HDBSY# {14 }

HDRDY# {14}

HITM# {14}

HINIT# {2 6}

HLOCK# {1 4}

HTRDY# {14 }

HDEFER# {1 4 }

HEDRDY# {14}

VTT_OUT_L

12

CB425

220P

NI

HRS#[0..2] {14}

VTT_OUT_L

12

R67

49.9Ohm

1%

1 2

12

R69

100Ohm

1%

GND

3

R744

62

HBREQ0# {1 4 }

12

GTLREF should be

0.67*VTT=0.8V

C245

1UF/10V

HD#[0..15]{14}

HDBI0#{14}

HDSTBN0#{14}

HDSTBP0#{14}

HD#[16..31]{14}

HDBI1#{14}

HDSTBN1#{14}

HDSTBP1#{14}

12-010907750 FOXCONN

12-010907751 TYPO

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

2

CPUB

B4

D00#

C5

D01#

A4

D02#

C6

D03#

A5

D04#

B6

D05#

B7

D06#

A7

D07#

A10

D08#

A11

D09#

B10

D10#

C11

D11#

D8

D12#

B12

D13#

C12

D14#

D11

D15#

A8

DBI0#

C8

DSTBN0#

B9

DSTBP0#

G9

D16#

F8

D17#

F9

D18#

E9

D19#

D7

D20#

E10

D21#

D10

D22#

F11

D23#

F12

D24#

D13

D25#

E13

D26#

G13

D27#

F14

D28#

G14

D29#

F15

D30#

G15

D31#

G11

DBI1#

G12

DSTBN1#

E12

DSTBP1#

P4_SOCKET775

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

DBI2#

DSTBN2#

DSTBP2#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DBI3#

DSTBN3#

DSTBP3#

G16

E15

E16

G18

G17

F17

F18

E18

E19

F20

E21

F21

G21

E22

D22

G22

D19

G20

G19

D20

D17

A14

C15

C14

B15

C18

B16

A17

B18

C21

B21

B19

A19

A22

B22

C20

A16

C17

HD#32

HD#33

HD#34

HD#35

HD#36

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

1

HDBI2# {14}

HDSTBN2# {14}

HDSTBP2# {14 }

HDBI3# {14 }

HDSTBN3# {14}

HDSTBP3# {14 }

HD#[32..47] {14}

HD#[48..63] {14}

P4_SOCKET775

A A

PRESCOTT / TEJAS -1

ASUSTeK CO MPUTE R INC

Si ze Project Name

A3

星期一 三月

5

4

http://laptop-motherboard-schematic.blogspot.com/

3

2

Date: Sheet

Title :

Engineer:

PTGD2-LA

Samuel Wu

10 50, 29,2004

1

Rev

1.03

of

5

4

3

2

1

R80

49.9Ohm

1%

VTT_OUT_R

12

R81

49.9Ohm

1%

GNDGND

FSBSEL0{9,17,50}

FSBSEL1{9,17,50}

FSBSEL2{9,17,50}

12

R79

49.9Ohm

1%

CPUD

AE1

TCK

AD1

TDI

AF1

TDO

AC1

TMS

AG1

TRST#

AJ2

BPM0#

AJ1

BPM1#

AD2

BPM2#

AG2

BPM3#

AF2

BPM4#

AG3

BPM5#

AC2

DBR#

AK3

ITPCLKOUT0

AJ3

ITPCLKOUT1

G29

BSEL0

H30

BSEL1

G30

BSEL2

P4_SOCKET775

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

VTT10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VTT23

VTT24

VTTPWRGD

VTT_OUT1

VTT_OUT2

VTT_SEL

VTT_SEL

A29

B25

B29

B30

C29

A26

B27

C28

A25

A28

A27

C30

A30

C25

C26

C27

B26

D27

D28

D25

D26

B28

D29

D30

AM6

AA1

J1

F27

0

1

+1.2V_FSB_VTT

VTT_PWRGD {45}

VTT_OUT_R

VTT_OUT_L

12

C309

0.1UF

NI

+3V

GND GND

12

VTT_SEL

TEJAS / PSC

RSVD

12

R103

1K

NI

C310

0.1UF

NI

10mil?

PLACE COMPONENTS AS CLOSE

AS POSSIBLE TO CPU SOCKET.

THE TRACE WIDTH TO CAPS

MUST BE NO SMALLER THAN 12

MIL.

VCCA

VSSA

RCVID0

RCVID1

RCVID2

RCVID3

RCVID4

RCVID5

A23

B23

D23

C23

AM2

AL5

AM3

AL6

AK4

AL4

AM5

F28

G28

AE8

AL1

AK1

AN3

AN4

AN5

AN6

F29

CPUC

P2

K3

R3

K1

L1

N2

M3

SMI#

A20M#

FERR#/PBE#

LINT0

LINT1

IGNNE#

STPCLK#

VCCA

VSSA

RSVD5

VCCIOPLL

VID0

VID1

VID2

VID3

VID4

VID5

RSVD6

BCLK0

BCLK1

SKTOCC#

THERMDA

THERMDC

VCC_SENSE

VSS_SENSE

RSVD7

RSVD8

RSVD9

TESTHI00

TESTHI01

TESTHI11

TESTHI12

TESTHI02

TESTHI03

TESTHI04

TESTHI05

TESTHI06

TESTHI07

RSVD10

RSVD11

SLP#

RSVD12

PWRGOOD

PROCHOT#

THERMTRIP#

COMP0

COMP1

COMP2

COMP3

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD23

RSVD24

BOOTSELECT

LL_ID0

LL_ID1

D D

+1.2V_FSB_VTT

+1.2V_FSB_VTT

C C

VTT_OUT_R

RCVID[0..5]{45}

B B

A A

SMI#{26}

A20M#{26}

HFERR#{26}

INTR{26}

NMI{26}

IGNNE#{26}

STPCLK#{26}

21

L4

10UH

l0805

R89

0Ohm

L5

10UH

RP1A 680Ohm15

10

RP1B 680Ohm25

10

RP1C 680Ohm

10

RP1D 680Ohm45

10

RP1E 680Ohm65

10

RP1F 680Ohm75

10

RP1G 680Ohm85

10

RP1H 680Ohm

10

12

+

CE1

12

21

l0805NI

35

95

CPUHCLK{9}

CPUHCLK#{9}

TRD_CPU_P{41}

TRD_CPU_N{41}

VCC_SEN_AN3{45}

VSS_SEN_AN4{45}

VCC_SENSE{45}

VSS_SENSE{45}

47U

NI

12

CB19

10UF/10V

c0805

12

CB20

10UF/10V

c0805

VCCIOPLL

TP_CPU_AM5

TP_CPU_D23

F26

W3

P1

W2

F25

G25

G27

G26

G24

F24

AK6

G6

L2

AH2

N1

AL2

M2

A13

T1

G2

R1

N5

AE6

C9

G10

D16

A20

E23

E24

F23

H2

J2

J3

Y1

V2

AA2

TESTHI0

TESTHI1

TESTHI11

TESTHI12

TESTHI2_7

VTT_OUT_R

RSVD_AK6

RSVD_G6

VTT_OUT_L

HCOMP0

HCOMP1

HCOMP2

HCOMP3

TP_CPU_E23

TP_CPU_E24

TP_CPU_F23

CPU_GTLREF1

HCOMP4

TP_CPU_J3

CPU_BOOT

TP_CPU_AA2

12

12

R833

R834

R835

R829

R836

R84

62Ohm

NI

R96

100Ohm

1%

1 2

62Ohm

1 2

1 2

62Ohm

62Ohm

1 2

1 2

62Ohm

62Ohm

VTT_OUT_L

12

R86

62Ohm

NI

12

R97

100Ohm

1%

VTT_OUT_R

LL_ID0 {4 5 }

+1.2V_FSB_VTT

VTT_OUT_R

R108

100Ohm

1 2

12

R85

1KOhm

NI

VTT_OUT_L

R977

100Ohm

NI

1 2

SLP# {26}

CPUPWRGD {26,50}

PROCHOT# {26,47}

ICH_THMTRIP# {26}

12

R98

60.4Ohm

1%

GND

12

R99

60.4Ohm

1%

12

R77

49.9Ohm

1%

TCK{50}

TDI{50}

TDO{50}

TMS{50}

TRST#{50}

VTT_OUT_R

R90 49.9Ohm 1%1 2

R91 49.9Ohm 1%1 2

R92 49.9Ohm 1%

1 2

R93 49.9Ohm 1%1 2

R94 49.9Ohm 1%1 2

R95 49.9Ohm 1%1 2

BPM0#{50}

BPM1#{50}

BPM2#{50}

BPM3#{50}

BPM4#{50}

BPM5#{50}

SYS_RESET#{26,28,41,50}

ITPHCLK{50}

ITPHCLK#{50}

12

P4_SOCKET775

ASUSTeK CO MP UT ER IN C

Si ze Project Name

A3

星期一 三月

5

4

http://laptop-motherboard-schematic.blogspot.com/

3

2

Date: Sheet

Engineer:

PTGD2-LA

Title :

1

PRESCOTT / TEJAS -2

Samuel Wu

1.03

of

11 50, 29,2004

Rev

5

D D

VCORE

CPUE

L8

VCC45

AG18

AG19

VCC46

VCC47

AG21

AG22

M23

VCC226

VCC48

AG25

AA8

VCC1

AB8

VCC2

AC23

VCC3

AC24

VCC4

AC25

VCC5

AC26

VCC6

AC27

VCC7

AC28

VCC8

AC29

VCC9

AC30

C C

B B

VCC10

AC8

VCC11

AD23

VCC12

AD24

VCC13

AD25

VCC14

AD26

VCC15

AD27

VCC16

AD28

VCC17

AD29

VCC18

AD30

VCC19

AD8

VCC20

AE11

VCC21

AE12

VCC22

AE14

VCC23

AE15

VCC24

AE18

VCC25

AE19

VCC26

AE21

VCC27

AE22

VCC28

AE23

VCC29

AE9

VCC30

AF11

VCC31

AF12

VCC32

AF14

VCC33

AF15

VCC34

AF18

VCC35

AF19

VCC36

AF21

VCC37

AF22

VCC38

AF8

VCC39

AF9

VCC40

AG11

VCC41

AG12

VCC42

AG14

VCC43

AG15

VCC44

P4_SOCKET775

M24

M25

VCC225

VCC224

VCC49

VCC50

AG26

AG27

M26

M27

VCC223

VCC222

VCC221

VCC51

VCC52

VCC53

AG28

AG29

M28

M29

VCC220

VCC54

AG30

AG8

4

M30M8N23

VCC219

VCC218

VCC217

VCC55

VCC56

VCC57

AG9

AH11

N24

VCC216

VCC58

AH12

AH14

N25

N26

VCC215

VCC214

VCC59

VCC60

AH15

AH18

N27

N28

VCC213

VCC212

VCC211

VCC61

VCC62

VCC63

AH19

AH21

N29

N30N8P8R8T23

VCC210

VCC209

VCC208

VCC64

VCC65

VCC66

AH22

AH25

AH26

VCC207

VCC67

AH27

AH28

T24

VCC206

VCC205

VCC68

VCC69

AH29

AH30

T25

T26

VCC204

VCC203

VCC202

VCC70

VCC71

VCC72

AH8

AH9

T27

T28

VCC201

VCC73

AJ11

AJ12

T29

T30T8U23

VCC200

VCC199

VCC74

VCC75

AJ14

AJ15

VCC198

VCC197

VCC196

VCC76

VCC77

VCC78

AJ18

AJ19

U24

U25

VCC195

VCC79

AJ21

AJ22

U26

U27

VCC194

VCC193

VCC192

VCC80

VCC81

VCC82

AJ25

AJ26

U28

U29

VCC191

VCC83

AJ8

AJ9

U30U8V8

VCC190

VCC189

VCC84

VCC85

AK11

AK12

3

W23

VCC188

VCC187

VCC186

VCC86

VCC87

VCC88

AK14

AK15

W24

W25

VCC185

VCC89

AK18

AK19

W26

W27

VCC184

VCC183

VCC182

VCC90

VCC91

VCC92

AK21

AK22

W28

W29

VCC181

VCC93

AK25

AK26

W30W8Y23

VCC180

VCC179

VCC94

VCC95

AK8

AK9

Y24

VCC178

VCC177

VCC176

VCC96

VCC97

VCC98

AL11

AL12

Y25

Y26

VCC175

VCC99

AL14

AL15

Y27

Y28

VCC174

VCC173

VCC172

VCC100

VCC101

VCC102

AL18

AL19

Y29

Y30

VCC171

VCC103

AL21

AL22

K8

Y8

VCC170

VCC169

VCC104

VCC105

AL25

AL26

K29

K30

VCC166

VCC167

VCC168

VCC106

VCC107

VCC108

AL29

AL30

K27

K28

VCC165

VCC109

AL8

AL9

K25

K26

VCC162

VCC163

VCC164

VCC110

VCC111

VCC112

AM11

AM12

K24

VCC161

VCC113

AM14

AM15

VCC114

VCC115

AM18

AM19

VCC116

VCC117

VCC118

AM21

AM22

VCC160

VCC159

VCC158

VCC157

VCC156

VCC155

VCC154

VCC153

VCC152

VCC151

VCC150

VCC149

VCC148

VCC147

VCC146

VCC145

VCC144

VCC143

VCC142

VCC141

VCC140

VCC139

VCC138

VCC137

VCC136

VCC135

VCC134

VCC133

VCC132

VCC131

VCC130

VCC129

VCC128

VCC127

VCC126

VCC125

VCC124

VCC123

VCC122

VCC121

VCC120

VCC119

2

VCORE

K23

J9

J8

J30

J29

J28

J27

J26

J25

J24

J23

J22

J21

J20

J19

J18

J15

J14

J13

J12

J11

J10

AN9

AN8

AN30

AN29

AN26

AN25

AN22

AN21

AN19

AN18

AN15

AN14

AN12

AN11

AM9

AM8

AM30

AM29

AM26

AM25

1

A A

PRESCOTT / TEJAS -3

ASUSTeK CO MP UT ER IN C

Si ze Project Name

A3

星期一 三月

5

4

http://laptop-motherboard-schematic.blogspot.com/

3

2

Date: Sheet

Title :

Engineer:

PTGD2-LA

1

Samuel Wu

of

12 50, 29,2004

Rev

1.03

5

D D

CPUF

AF28

VSS60

AF27

VSS59

AF26

VSS58

AF25

VSS57

AF24

VSS56

AF23

VSS55

AF20

VSS54

AF17

VSS53

AF16

VSS52

AF13

VSS51

AF10

VSS50

AE7

VSS49

AE5

VSS48

AE30

VSS47

AE29

VSS46

AE28

VSS45

AE27

VSS44

AE26

VSS43

AE25

VSS42

AE24

VSS41

AE20

VSS40

AE2

VSS39

AE17

VSS38

AE16

C C

GND

B B

AE13

AE10

AD7

AD4

AC7

AE3

B13

D14

W1

D1

E5

E6

E7

F6

T2

V1

Y3

VSS37

VSS36

VSS35

VSS34

VSS33

VSS32

RSVD25

RSVD26

RSVD27

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

P4_SOCKET775

post_nc3

post_nc4

4

post_nc1

post_nc2

123

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

A12

A15

A18

A2

A21

A24

A6

A9

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA3

AA30

AA6

AA7

AB1

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AB7

AC3

AC6

GND

4

CPUG

AF29

VSS61

AF3

VSS62

AF30

VSS63

AF6

VSS64

AF7

VSS65

AG10

VSS66

AG13

VSS67

AG16

VSS68

AG17

VSS69

AG20

VSS70

AG23

VSS71

AG24

VSS72

AG7

VSS73

AH1

VSS74

AH10

VSS75

AH13

VSS76

AH16

VSS77

AH17

VSS78

AH20

VSS79

AH23

VSS80

AH24

VSS81

AH3

VSS82

AH6

VSS83

AH7

VSS84

AJ10

VSS85

AJ13

VSS86

AJ16

VSS87

AJ17

VSS88

AJ20

VSS89

AJ23

VSS90

AJ24

VSS91

AJ27

VSS92

AJ28

VSS93

AJ29

VSS94

AJ30

VSS95

AJ4

VSS96

AJ7

VSS97

AK10

VSS98

AK13

VSS99

AK16

VSS100

AK17

VSS101

AK2

VSS102

AK20

VSS103

AK23

VSS104

AK24

VSS105

AK27

VSS106

AK28

VSS107

AK29

VSS108

P4_SOCKET775

GND

AK30

VSS109

VSS110

VSS111

AK5

AK7

Y7

VSS112

AL10

AL13

3

VSS274

VSS275

VSS276

VSS113

VSS114

VSS115

AL16

AL17

VSS273

VSS116

AL20

AL23

VSS270

VSS271

VSS272

VSS117

VSS118

VSS119

AL24

AL27

VSS269

VSS120

AL28

AL3

V28

V29V3V30V6V7W4W7Y2Y5

VSS267

VSS268

VSS121

VSS122

AL7

AM1

V26

V27

VSS264

VSS265

VSS266

VSS123

VSS124

VSS125

AM10

AM13

V24

V25

VSS263

VSS126

AM16

AM17

VSS260

VSS261

VSS262

VSS127

VSS128

VSS129

AM20

AM23

VSS259

VSS130

AM24

AM27

VSS257

VSS258

VSS131

VSS132

AM28

AM4

VSS254

VSS255

VSS256

VSS133

VSS134

VSS135

AM7

AN1

R29

R30R5R7T3T6T7U1U7V23

VSS253

VSS136

AN10

AN13

R27

R28

VSS250

VSS251

VSS252

VSS137

VSS138

VSS139

AN16

AN17

R25

R26

VSS249

VSS140

AN2

AN20

R24

VSS247

VSS248

VSS141

VSS142

AN23

AN24

VSS244

VSS245

VSS246

VSS143

VSS144

VSS145

AN27

AN28

P29

P30P4P7R2R23

VSS242

VSS243

VSS146

VSS147

AN7B1B11

2

P27

P28

VSS240

VSS241

VSS148

VSS149

B14

B17

P25

P26

VSS238

VSS239

VSS150

VSS151

B20

B24B5B8

P24

VSS235

VSS236

VSS237

VSS152

VSS153

VSS154

VSS234

VSS155

C10

C13

VSS232

VSS233

VSS156

VSS157

C16

C19

VSS229

VSS230

VSS231

VSS158

VSS159

VSS160

C22

C24C4C7

VSS227

VSS228

VSS161

VSS162

D12

L28

L29L3L30L6L7M1M7N3N6N7P23

VSS224

VSS225

VSS226

VSS163

VSS164

VSS165

D15

D18

L26

L27

VSS223

VSS166

D21

D24D3D5

L24

L25

VSS220

VSS221

VSS222

VSS167

VSS168

VSS169

K7

L23

VSS219

VSS170

D6

VSS217

VSS218

VSS216

VSS215

VSS214

VSS213

VSS212

VSS211

VSS210

VSS209

VSS208

VSS207

VSS206

VSS205

VSS204

VSS203

VSS202

VSS201

VSS200

VSS199

VSS198

VSS197

VSS196

VSS195

VSS194

VSS193

VSS192

VSS191

VSS190

VSS189

VSS188

VSS187

VSS186

VSS185

VSS184

VSS183

VSS182

VSS181

VSS180

VSS179

VSS178

VSS177

VSS176

VSS175

VSS174

VSS173

VSS172

VSS171

K5

K2

J7

J4

H9

H8

H7

H6

H3

H29

H28

H27

H26

H25

H24

H23

H22

H21

H20

H19

H18

H17

H14

H13

H12

H11

H10

G1

F7

F4

F22

F19

F16

F13

F10

E8

E29

E28

E27

E26

E25

E20

E2

E17

E14

E11

D9

1

GND

A A

PRESCOTT / TEJAS -4

ASUSTeK CO MPUTE R INC

Si ze Project Name

A3

星期一 三月

5

4

http://laptop-motherboard-schematic.blogspot.com/

3

2

Date: Sheet

Title :

Engineer:

PTGD2-LA

Samuel Wu

13 50, 29,2004

1

Rev

1.03

of

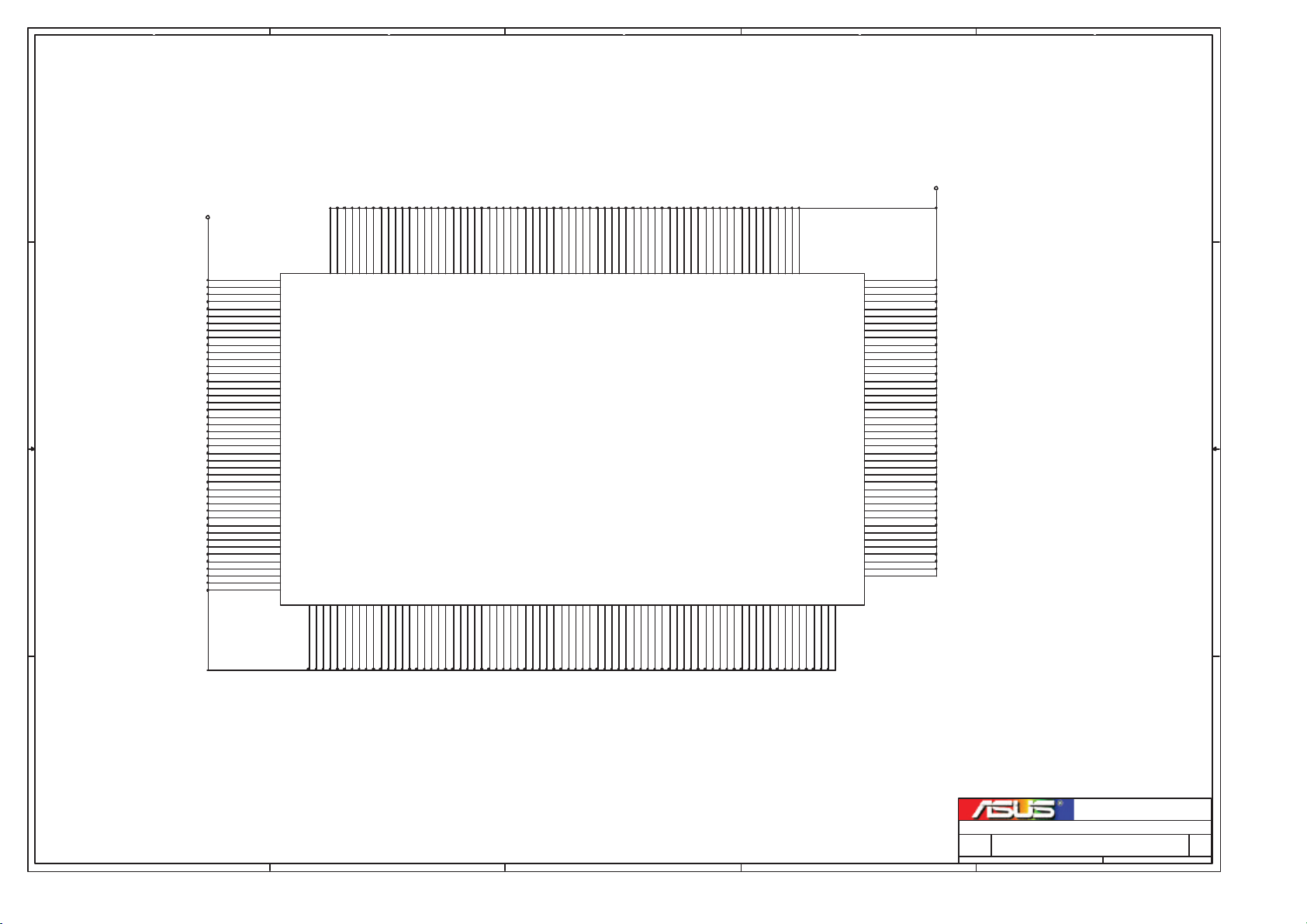

5

HXSWING 10/7

4

3

2

1

HA#[3..31]{10}

D D

HREQ#[0..4]{10}

C C

HADSTB0#{10}

HADSTB1#{10} DMI_RXN2{25}

HPCREQ#{10}

HDSTBP0#{10}

HDSTBN0#{10}

HDBI0#{10}

HDSTBP1#{10}

HDSTBN1#{10}

HDBI1#{10}

HDSTBP2#{10}

HDSTBN2#{10}

HDBI2#{10}

HDSTBP3#{10}

HDSTBN3#{10}

B B

A A

HDBI3#{10}

HADS#{10}

HBNR#{10}

HBPRI#{10}

HBREQ0#{10}

CPURESET#{10,50}

HDBSY#{10}

HDEFER#{10}

HDRDY#{10}

HEDRDY#{10}

HIT#{10}

HITM#{10}

HLOCK#{10}

HRS#[0..2]{10}

HTRDY#{10}

5

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HRS#0

HRS#1

HRS#2

H29

K29

J29

G30

G32

K30

L29

M30

L31

L28

J28

K27

K33

M28

R29

L26

N26

M26

N31

P26

N29

P28

R28

N33

T27

T31

U28

T26

T29

F33

E32

H31

G31

F31

J31

N27

E31

E33

E35

E34

H26

F26

J26

J19

F19

K19

B29

C29

B26

M31

M35

E30

R33

G24

L35

J35

M32

P33

L34

N35

L33

K34

P34

J32

N34

U2A

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HADSTB0#

HADSTB1#

HPCREQ#

HDSTBP0#

HDSTBN0#

HDINV0#

HDSTBP1#

HDSTBN1#

HDINV1#

HDSTBP2#

HDSTBN2#

HDINV2#

HDSTBP3#

HDSTBN3#

HDINV3#

HADS#

HBNR#

HBPRI#

HBREQ0#

HCPURST#

HDBSY#

HDEFER#

HDRDY#

HEDRDY#

HHIT#

HHITM#

HLOCK#

HRS0#

HRS1#

HRS2#

HTRDY#

MCH_DDR2

HD10

HD11

HD12

HD13

HD14

HD15

HD16

HD17

HD18

HD19

HD20

HD21

HD22

HD23

HD24

HD25

HD26

HD27

HD28

HD29

HD30

HD31

HD32

HD33

HD34

HD35

HD36

HD37

HD38

HD39

HD40

HD41

HD42

HD43

HD44

HD45

HD46

HD47

HD48

HD49

HD50

HD51

HD52

HD53

HD54

HD55

HD56

HD57

HD58

HD59

HD60

HD61

HD62

HD63

HSWING

HSCOMP

HRCOMP

HVREF

HCLKP

HCLKN

4

HD0

HD1

HD2

HD3

HD4

HD5

HD6

HD7

HD8

HD9

H33

J34

G35

H35

G34

F34

G33

D34

C33

D33

B34

C34

B33

C32

B32

E28

C30

D29

H28

G29

J27

F28

F27

E27

E25

G25

J25

K25

L25

L23

K23

J22

J24

K22

J21

M21

H23

M19

K21

H20

H19

M18

K18

K17

G18

H18

F17

A25

C27

C31

B30

B31

A31

B27

A29

C28

A28

C25

C26

D27

A27

E24

B25

A23

D24

B23

A24

M23

M22

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HXSWING

+1.2V_FSB_VTT

R112

60.4Ohm

1%

HXSCOMP

HXRCOMP

12

R113

20Ohm

1%

GND

MCH_GTLREF

MCHHCLK {9}

MCHHCLK# {9 }

HD#0

J33

HD#[0..63] {10 }

EXP_RXP0{24}

EXP_RXN0{24}

EXP_RXP1{24}

EXP_RXN1{24}

EXP_RXP2{24}

EXP_RXN2{24}

EXP_RXP3{24}

EXP_RXN3{24}

EXP_RXP4{24}

EXP_RXN4{24}

EXP_RXP5{24}

EXP_RXN5{24}

EXP_RXP6{24}

EXP_RXN6{24}

EXP_RXP7{24}

EXP_RXN7{24}

EXP_RXP8{24}

EXP_RXN8{24}

EXP_RXP9{24}

EXP_RXN9{24}

EXP_RXP10{24}

EXP_RXN10{24}

EXP_RXP11{24}

EXP_RXN11{24}

EXP_RXP12{24}

EXP_RXN12{24}

EXP_RXP13{24}

EXP_RXN13{24}

EXP_RXP14{24}

EXP_RXN14{24}

EXP_RXP15{24}

EXP_RXN15{24}

DMI_RXP0{25}

DMI_RXN0{25}

DMI_RXP1{25}

DMI_RXN1{25}

DMI_RXP2{25}

DMI_RXP3{25}

DMI_RXN3{25}

CK_100M_MCH{9}

CK_100M_MCH#{9}

+1.2V_FSB_VTT

R110

301Ohm

1%

H

1 2

12

12

12

GND

12

CB23

2.2PF

NI

GND

GND

http://laptop-motherboard-schematic.blogspot.com/

CB22

0.01U

X7R

12

CB24

220P

X7R

NI

GND

12

GND

R111

100Ohm

1%

+1.2V_FSB_VTT

CB25

0.1U

X7R

12

12

GND

R114

49.9Ohm

1%

R115

100Ohm

1%

3

SDVO_CTRL_DATA{24}

SDVO_CTRL_CLK{24}

U2B

E11

EXP_RXP0

F11

EXP_RXN0

J11

EXP_RXP1

H11

EXP_RXN1

F9

EXP_RXP2

E9

EXP_RXN2

F7

EXP_RXP3

E7

EXP_RXN3

B3

EXP_RXP4

B4

EXP_RXN4

D5

EXP_RXP5

E5

EXP_RXN5

G6

EXP_RXP6

G5

EXP_RXN6

H8

EXP_RXP7

H7

EXP_RXN7

J6

EXP_RXP8

J5

EXP_RXN8

K8

EXP_RXP9

K7

EXP_RXN9

L6

EXP_RXP10

L5

EXP_RXN10

P10

EXP_RXP11

R10

EXP_RXN11

M8

EXP_RXP12

M7

EXP_RXN12

N6

EXP_RXP13

N5

EXP_RXN13

P7

EXP_RXP14

P8

EXP_RXN14

R6

EXP_RXP15

R5

EXP_RXN15

U5

DMI_RXP0

U6

DMI_RXN0

T9

DMI_RXP1

T8

DMI_RXN1

V7

DMI_RXP2

V8

DMI_RXN2

V10

DMI_RXP3

U10

DMI_RXN3

A11

GCLKP

B11

GCLKN

K13

SDVO_CTRLDATA

J13

SDVO_CTRLCLK

MCH_DDR2

2

C10

EXP_TXP0

C9

EXP_TXN0

A9

EXP_TXP1

A8

EXP_TXN1

C8

EXP_TXP2

C7

EXP_TXN2

A7

EXP_TXP3

A6

EXP_TXN3

C6

EXP_TXP4

C5

EXP_TXN4

C2

EXP_TXP5

D2

EXP_TXN5

E3

EXP_TXP6

F3

EXP_TXN6

F1

EXP_TXP7

G1

EXP_TXN7

G3

EXP_TXP8

H3

EXP_TXN8

H1

EXP_TXP9

J1

EXP_TXN9

J3

EXP_TXP10

K3

EXP_TXN10

K1

EXP_TXP11

L1

EXP_TXN11

L3

EXP_TXP12

M3

EXP_TXN12

M1

EXP_TXP13

N1

EXP_TXN13

N3

EXP_TXP14

P3

EXP_TXN14

P1

EXP_TXP15

R1

EXP_TXN15

R3

DMI_TXP0

T3

DMI_TXN0

T1

DMI_TXP1

U1

DMI_TXN1

U3

DMI_TXP2

V3

DMI_TXN2

V5

DMI_TXP3

W5

DMI_TXN3

+1.5V_PCIEXPRESS

12

R109

24.9Ohm

1%

EXP_COMP

Y10

EXP_COMPO

W10

EXP_COMPI

Title :

ASUSTeK CO MPUTE R INC

Si ze Project Name

A3

星期一 三月

Date: Sheet

Engineer:

PTGD2-LA

1

EXP_TXP0 {24}

EXP_TXN0 {2 4}

EXP_TXP1 {24}

EXP_TXN1 {2 4}

EXP_TXP2 {24}

EXP_TXN2 {2 4}

EXP_TXP3 {24}

EXP_TXN3 {2 4}

EXP_TXP4 {24}

EXP_TXN4 {2 4}

EXP_TXP5 {24}

EXP_TXN5 {2 4}

EXP_TXP6 {24}

EXP_TXN6 {2 4}

EXP_TXP7 {24}

EXP_TXN7 {2 4}

EXP_TXP8 {24}

EXP_TXN8 {2 4}

EXP_TXP9 {24}

EXP_TXN9 {2 4}

EXP_TXP10 {2 4}

EXP_TXN10 {24}

EXP_TXP11 {2 4}

EXP_TXN11 {24}

EXP_TXP12 {2 4}

EXP_TXN12 {24}

EXP_TXP13 {2 4}

EXP_TXN13 {24}

EXP_TXP14 {2 4}

EXP_TXN14 {24}

EXP_TXP15 {2 4}

EXP_TXN15 {24}

DMI_TXP0 {25}

DMI_TXN0 {25}

DMI_TXP1 {25}

DMI_TXN1 {25}

DMI_TXP2 {25}

DMI_TXN2 {25}

DMI_TXP3 {25}

DMI_TXN3 {25}

GRANTSDALE -1

Samuel Wu

of

14 50, 29,2004

Rev

1.03

5

4

3

2

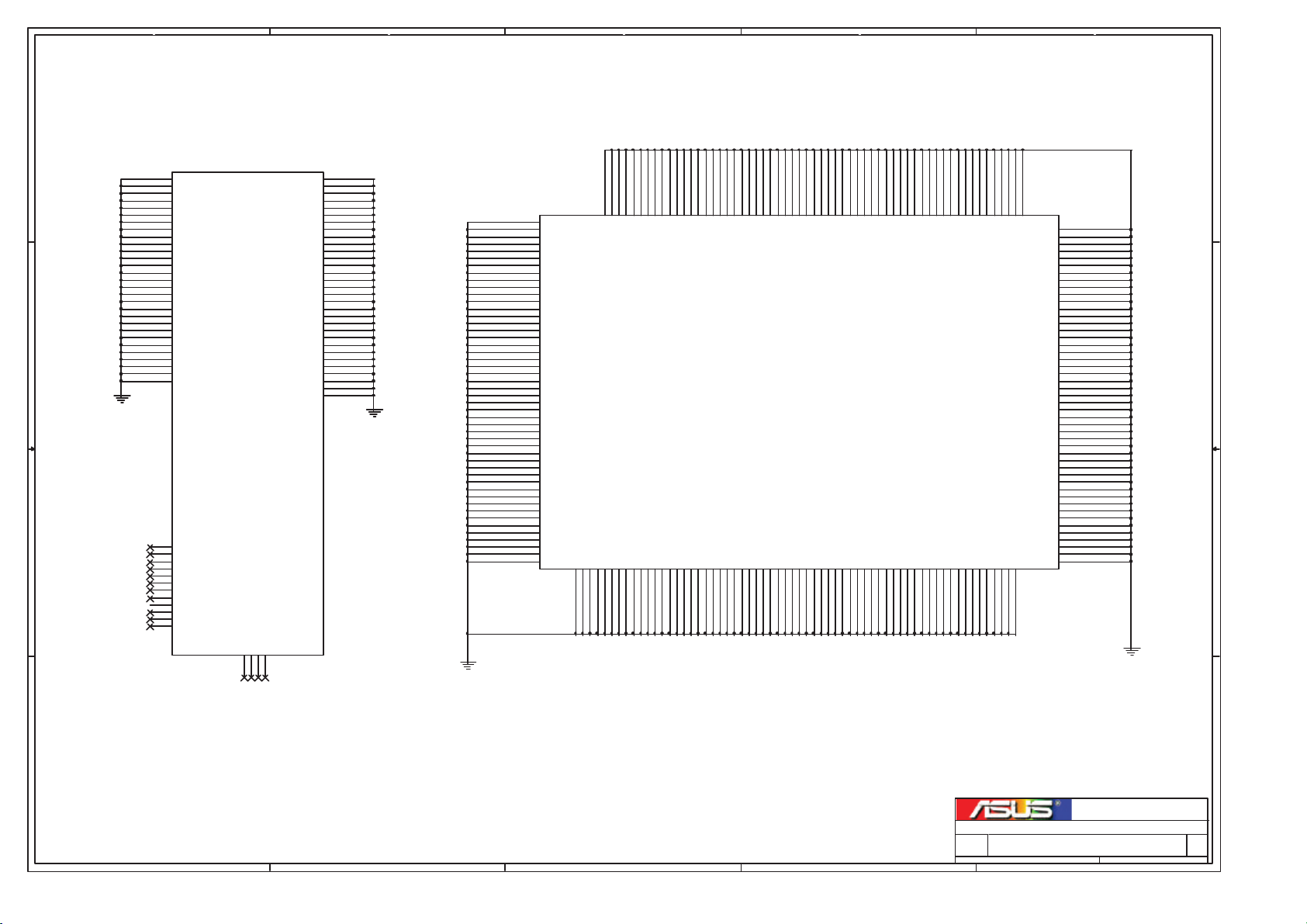

1

M_CHA_MAA[0..13]{20,22}

D D

M_CHA_WE#{20,22}

M_CHA_CAS#{20,22}

M_CHA_RAS#{20,22}

M_CHA_BA0{20,22}

M_CHA_BA1{20,22}

M_CHA_BA2{20,22}

M_CHA_CS#0{20,22}

M_CHA_CS#1{20,22}

M_CHA_CS#2{20,22}

M_CHA_CS#3{20,22}

M_CHA_CKE0{20,22}

M_CHA_CKE1{20,22}

R116

1KOhm

1%

R118

1KOhm

1%

M_CHA_CKE2{20,22}

M_CHA_CKE3{20,22}

M_CHA_ODT0{20,22}

M_CHA_ODT1{20,22}

M_CHA_ODT2{20,22}

M_CHA_ODT3{20,22}

M_CHA_CLK0{20}

M_CHA_CLK0#{20}

M_CHA_CLK1{20}

M_CHA_CLK1#{20}

M_CHA_CLK2{20}

M_CHA_CLK2#{20}

M_CHA_CLK3{20}

M_CHA_CLK3#{20}

M_CHA_CLK4{20}

M_CHA_CLK4#{20}

M_CHA_CLK5{20}

M_CHA_CLK5#{20}

M_CHA_VREF NEED ROUTING

Width/Spacing: 12/12

mils

C C

B B

+1.8V_DUAL

12

12

A A

GND

R119

M_CHB_VREF{16}

5

1 2

0Ohm

M_CHA_MAA0

M_CHA_MAA1

M_CHA_MAA2

M_CHA_MAA3

M_CHA_MAA4

M_CHA_MAA5

M_CHA_MAA6

M_CHA_MAA7

M_CHA_MAA8

M_CHA_MAA9

M_CHA_MAA10

M_CHA_MAA11

M_CHA_MAA12

M_CHA_MAA13

TP_GD_AB33

TP_GD_AE16

TP_GD_AH15

SM_SLEW_A

4

M_CHA_VREF

12

CB26

0.1UF/25V

GND

U2C

AP26

SMA_A0

AR24

SMA_A1

AL24

SMA_A2

AP23

SMA_A3

AR23

SMA_A4

AP22

SMA_A5

AN23

SMA_A6

AP21

SMA_A7

AN22

SMA_A8

AN21

SMA_A9

AM27

SMA_A10

AM21

SMA_A11

AR20

SMA_A12

AP31

SMA_A13

AN28

SWE_A#

AN29

SCAS_A#

AP27

SRAS_A#

AR27

SBS_A0

AN27

SBS_A1

AN20

SBS_A2

AR29

SCS_A0#

AP32

SCS_A1#

AR28

SCS_A2#

AN31

SCS_A3#

AP19

SCKE_A0

AM18

SCKE_A1

AN18

SCKE_A2

AR19

SCKE_A3

AP30

SODT_A0

AN32

SODT_A1

AP29

SODT_A2

AP33

SODT_A3

AN26

SCLK_A0

AP25

SCLK_A0#

AM2

SCLK_A1

AM3

SCLK_A1#

AC34

SCLK_A2

AC35

SCLK_A2#

AN25

SCLK_A3

AM24

SCLK_A3#

AN3

SCLK_A4

AN2

SCLK_A4#

AC33

SCLK_A5

AB34

SCLK_A5#

AB33

RSV17

AE16

RSV_TP0

AH15

RSV_TP1

AK12

SM_SLEWOUT0

AJ12

SM_SLEWIN0

AE7

SVREF0

MCH_DDR2

http://laptop-motherboard-schematic.blogspot.com/

SDQS_A0

SDQS_A0#

SDM_A0

SDQ_A0

SDQ_A1

SDQ_A2

SDQ_A3

SDQ_A4

SDQ_A5

SDQ_A6

SDQ_A7

SDQS_A1

SDQS_A1#

SDM_A1

SDQ_A8

SDQ_A9

SDQ_A10

SDQ_A11

SDQ_A12

SDQ_A13

SDQ_A14

SDQ_A15

SDQS_A2

SDQS_A2#

SDM_A2

SDQ_A16

SDQ_A17

SDQ_A18

SDQ_A19

SDQ_A20

SDQ_A21

SDQ_A22

SDQ_A23

SDQS_A3

SDQS_A3#

SDM_A3

SDQ_A24

SDQ_A25

SDQ_A26

SDQ_A27

SDQ_A28

SDQ_A29

SDQ_A30

SDQ_A31

SDQS_A4

SDQS_A4#

SDM_A4

SDQ_A32

SDQ_A33

SDQ_A34

SDQ_A35

SDQ_A36

SDQ_A37

SDQ_A38

SDQ_A39

SDQS_A5

SDQS_A5#

SDM_A5

SDQ_A40

SDQ_A41

SDQ_A42

SDQ_A43

SDQ_A44

SDQ_A45

SDQ_A46

SDQ_A47

SDQS_A6

SDQS_A6#

SDM_A6

SDQ_A48

SDQ_A49

SDQ_A50

SDQ_A51

SDQ_A52

SDQ_A53

SDQ_A54

SDQ_A55

SDQS_A7

SDQS_A7#

SDM_A7

SDQ_A56

SDQ_A57

SDQ_A58

SDQ_A59

SDQ_A60

SDQ_A61

SDQ_A62

SDQ_A63

3

AG1

AG2

AF2

AE3

AF3

AH3

AJ2

AE2

AE1

AG3

AH2

AL3

AL2

AL1

AK2

AK3

AN4

AP4

AJ1

AJ3

AP2

AP3

AP7

AR7

AN7

AR5

AP6

AP9

AN9

AN5

AP5

AN8

AR8

AF17

AG17

AH16

AL17

AJ17

AF19

AH18

AK16

AF16

AD17

AE19

AM30

AL29

AK29

AK27

AJ28

AL31

AK31

AH27

AL27

AN30

AL30

AG35

AG33

AG34

AH33

AH35

AF33

AE33

AJ33

AJ34

AG32

AF34

AA34

AA35

AA33

AD31

AD35

Y33

W34

AE35

AE34

AA32

Y35

U34

U35

U33

V34

V33

R32

R34

W35

W33

T33

T35

M_CHA_DQ0

M_CHA_DQ1

M_CHA_DQ2

M_CHA_DQ3

M_CHA_DQ4

M_CHA_DQ5

M_CHA_DQ6

M_CHA_DQ7

M_CHA_DQ8

M_CHA_DQ9

M_CHA_DQ10

M_CHA_DQ11

M_CHA_DQ12

M_CHA_DQ13

M_CHA_DQ14

M_CHA_DQ15

M_CHA_DQ16

M_CHA_DQ17

M_CHA_DQ18

M_CHA_DQ19

M_CHA_DQ20

M_CHA_DQ21

M_CHA_DQ22

M_CHA_DQ23

M_CHA_DQ24

M_CHA_DQ25

M_CHA_DQ26

M_CHA_DQ27

M_CHA_DQ28

M_CHA_DQ29

M_CHA_DQ30

M_CHA_DQ31

M_CHA_DQ32

M_CHA_DQ33

M_CHA_DQ34

M_CHA_DQ35

M_CHA_DQ36

M_CHA_DQ37

M_CHA_DQ38

M_CHA_DQ39

M_CHA_DQ40

M_CHA_DQ41

M_CHA_DQ42

M_CHA_DQ43

M_CHA_DQ44

M_CHA_DQ45

M_CHA_DQ46

M_CHA_DQ47

M_CHA_DQ48

M_CHA_DQ49

M_CHA_DQ50

M_CHA_DQ51

M_CHA_DQ52

M_CHA_DQ53

M_CHA_DQ54

M_CHA_DQ55

M_CHA_DQ56

M_CHA_DQ57

M_CHA_DQ58

M_CHA_DQ59

M_CHA_DQ60

M_CHA_DQ61

M_CHA_DQ62

M_CHA_DQ63

M_CHA_DQS0 {20}

M_CHA_DQS0# {20 }

M_CHA_DM0 {20}

M_CHA_DQ[0..7] {2 0}

M_CHA_DQS1 {20}

M_CHA_DQS1# {20 }

M_CHA_DM1 {20}

M_CHA_DQ[8..15] {2 0}

M_CHA_DQS2 {20}

M_CHA_DQS2# {20 }

M_CHA_DM2 {20}

M_CHA_DQ[16..23] {20}

M_CHA_DQS3 {20}

M_CHA_DQS3# {20 }

M_CHA_DM3 {20}

M_CHA_DQ[24..31] {20}

M_CHA_DQS4 {20}

M_CHA_DQS4# {20 }

M_CHA_DM4 {20}

M_CHA_DQ[32..39] {20}

M_CHA_DQS5 {20}

M_CHA_DQS5# {20 }

M_CHA_DM5 {20}

M_CHA_DQ[40..47] {20}

M_CHA_DQS6 {20}

M_CHA_DQS6# {20 }

M_CHA_DM6 {20}

M_CHA_DQ[48..55] {20}

M_CHA_DQS7 {20}

M_CHA_DQS7# {20 }

M_CHA_DM7 {20}

M_CHA_DQ[56..63] {20}

GRANTSDALE -2 DDR2

ASUSTeK CO MPUTE R INC

Si ze Project Name

A3

星期一 三月

2

Date: Sheet

Title :

Engineer:

PTGD2-LA

Samuel Wu

15 50, 29,2004

1

Rev

1.03

of

Loading...

Loading...