P/I-P55TP4N Hauptplatine

Benutzerhandbuch

Hinweis für den Benutzer

Kein Bestandteil dieses Produkts, einschließlich des Produkts und der

Software, darf ohne vorherige schriftliche Genehmigung durch ASUST eK

COMPUTER INC. (nachstehend ASUS genannt) in irgendeiner Form und

auf irgendeine Art und W eise reproduziert, übertragen, umgesetzt, in einem

Retrievalsystem gespeichert oder in irgendeine Sprache übersetzt werden.

Von diesem Verbot ausgenommen ist die Dokumentation, die der Käufer

als Backup behält.

ASUS stellt dieses Handbuch ohne jegliche ausdrückliche oder implizite

Mängelgewähr zur Verfügung, einschließlich (aber nicht begrenzt auf)

implizierte Garantien oder Bedingungen bezüglich der Tauglichkeit oder

Eignung für einen bestimmten Zweck. Keinesfalls übernimmt ASUS die

Verantwortung für entgangenen Gewinn, entgangene Geschäfte, Verlust

von Arbeitszeit oder Daten, Unterbrechung des Betriebs oder für mittelbare,

besondere, beiläufig entstandene oder Folgeschäden jedweder Art, selbst

wenn ASUS darüber unterrichtet worden ist, daß solche Schäden aufgrund

von Fehlern in diesem Handbuch oder am Produkt auftreten können. ASUS

kann dieses Handbuch von Zeit zu Zeit ohne besonderen Hinweis

überarbeiten.

Die namentliche Nennung von Produkten in diesem Handbuch erfolgt nur

zum Zweck der eindeutigen Bezeichnung. Einige der in diesem Handbuch

genannten Produktnamen sind eingetragene W arenzeichen bzw . unterliegen

dem Copyright ihrer jeweiligen Firmen.

(C) Copyright 1996 ASUSTeK Computer Inc. Alle Rechte vorbehalten.

Produktbezeichnung:P/I-P55TP4N

Produkt Rev: 1.01

Handbuch Rev: German 1.3

BIOS-Version: 401A0-011 5

Freigabedatum: April 1996

(wird während des Bootvorganges angezeigt)

II

P/I-P55TP4N Benutzerhandbuch

P/I-P55TP4N Benutzerhandbuch

III

INHALT

I. EINFÜHRUNG...............................................................1

Aufbau des Handbuchs ...............................................1

Checkliste der mitgelieferten T eile .............................1

II. Merkmale .......................................................................2

Merkmale dieser Hauptplatine....................................2

T eile der Hauptplatine ................................................3

III. INSTALLATION ..........................................................4

Übersichtszeichnung der Hauptplatine .......................4

Jumper ...................................................................5

Erweiterungssteckplätze ........................................5

Anschlüsse .............................................................5

Ablauf der Installation ................................................6

1. Jumper ....................................................................6

Jumper-Einstellungen.............................................7

2. Systemspeicher (DRAM und SRAM) ....................12

Der Einbau von DRAM-Speicher ..........................13

Externer SRAM-Second-Level-Cache .......................14

Hauptplatinen mit 0K-L2-Cache:...........................14

3. Prozessor (CPU) ....................................................15

4. Erweiterungskarten ................................................16

Installation einer Erweiterungskarte ......................16

Zuordnung von IRQs für Erweiterungskarten .......16

Zuordnung von DMA-Kanälen für ISA-Karten.....17

ASUS-MediaBus-Karte .........................................18

5. Externe Anschlüsse.................................................19

6. BIOS-Setup ............................................................26

IV

P/I-P55TP4N Benutzerhandbuch

INHALT

IV. BIOS-SOFTWARE.......................................................26

Standard CMOS Setup ...............................................28

Einzelheiten zur Standard CMOS..........................29

BIOS Features Setup..................................................32

Einzelheiten zur BIOS-Funktionen ........................32

Chipset Features Setup...............................................35

Power Management Setup..........................................38

Einzelheiten zum Power-Management-Setup ........38

PNP and PCI Setup ....................................................40

IRQ xx Used By ISA .............................................41

Load BIOS Defaults ...................................................42

Load Setup Defaults...................................................42

Supervisor Password and User Password ..................43

IDE HDD Auto Detection..........................................44

Save and Exit Setup ...................................................45

Exit W ithout Saving ...................................................45

NCR-SCSI-BIOS und Treiber....................................46

Das Dienstprogramm “Flash Memory W riter” ...........47

The Flash Memory W riter Utility Screen...............49

Einzelheiten zu den Advanced Features.................50

V. Die PCI-SC200-SCSI-Schnittstellenkarte......................52

Einstellen der PCI-SC200...........................................52

Einstellen der INT-Zuordnung...............................52

Einstellen der T erminatoren........................................53

SCSI-ID-Nummern ....................................................54

Hinweis für den Benutzer ....................................................55

T echnische Auskunft ............................................................56

P/I-P55TP4N Benutzerhandbuch

V

VI

P/I-P55TP4N Benutzerhandbuch

I. EINFÜHRUNG

Aufbau des Handbuchs

Das Handbuch umfaßt die folgenden vier Hauptteile:

1. Einführung: Informationen über das Handbuch und Checkliste

2. Merkmale: Informationen und Spezifikationen im Zusammenhang mit

dieser Hauptplatine

3. Installation: Anweisungen zur Einrichtung der Hauptplatine

4. BIOS-Setup: Verfahren zur Einrichtung der BIOS-Software.

Checkliste der mitgelieferten T eile

Überprüfen Sie bitte, ob Sie die folgenden T eile vollständig erhalten haben.

Sollten Teile fehlen oder beschädigt sein, wenden Sie sich bitte an Ihren

Händler.

√

Die P/I-P55TP4N-Hauptplatine

√

2 an einem gemeinsamen Halterungsblech montierte serielle

Flachbandkabel

√

1 Flachbandkabel mit Halterungsblech für die parallele Schnittstelle

√

1 Flachbandkabel für den Anschluß des Diskettenlaufwerks

(Checkliste)

I. EINFÜHRUNG

1 Flachbandkabel für den Anschluß an den IDE-Controller

√

1 Diskette mit Support-Software

√

•

Readme-Dateien erläutern die V erwendung der T reiberprogramme

•

Flash Memory Writer für die Aktualisierung des FLASH BIOS

•

PCI-IDE-T reiber für Enhanced-IDE-T reiber (in V orbereitung)

√

Dieses Handbuch

Optionaler PS/2(TM)-Anschluß

Optionales Infrarot-Modul

Optionales ASUS-Upgrade-Pipelined-Burst-Cache-Modul

P/I-P55TP4N Benutzerhandbuch

1

II. Merkmale

Merkmale dieser Hauptplatine

Die P/I-P55TP4N-Platine vereint eine Vielzahl von System- und

Leistungsmerkmalen auf der Hauptplatine, so zum Beispiel:

II. Merkmale

(Merkmale)

• Einfache Installa

das die selbständige Erkennung von Festplatten und Plug & Play

unterstützt, wodurch die Einrichtung von Festplatten und

Erweiterungskarten praktisch automatisch abläuft.

tion: Diese Hauptplatine ist mit einem BIOS ausgestattet,

• Unterstützung für verschiedene Taktraten: Diese Hauptplatine

unterstützt einen 75- bis 166- MHz-Pentium-Prozessor in einem ZIFSockel 7.

• Intel-Chipsatz: Diese Hauptplatine ist mit Intels 430FX-PCI-Chipsatz

mit I/O-Subsystemen ausgerüstet

• L2-Cache: Auf dieser Hauptplatine ist ein 256-KB-Pipelined-Burst-L2-

Cache integriert. Ein optionales ASUS Upgrade-Cache-Modul kann

eingebaut werden, um diesen Cache auf 512 KB zu erweitern.

• Vielseitige DRAM-Speicher-Unterstützung: Diese Hauptplatine

unterstützt 72polige SIMMs mit Kapazitäten von 4 MB, 8 MB, 16 MB

oder 32 MB, so daß eine Speichergröße von 8 MB bis 128 MB erreicht

wird. Sowohl Fast-Page-Mode- als auch Extended-Data-Output(EDO- ) SIMMs werden unterstützt.

• ISA- und PCI-Erweiterungssteckplätze: Diese Hauptplatine verfügt über

drei 16-Bit-ISA-Steckplätze, drei 32-Bit-PCI-Steckplätze und einen

kombinierten PCI/MediaBus-Steckplatz, der entweder den Einsatz einer

Standard-PCI-Karte oder die V erwendung einer ASUS-MediaBus-Karte

ermöglicht.

• ASUS-MediaBus: Diese Hauptplatine verfügt über eine mit dem PCI-

Slot 4 kombinierte Steckplatzerweiterung für eine optionale

multifunktionelle Erweiterungskarte, die den Aufbau von

Multimediasystemen erleichtert. Informationen bezüglich der

Kompatibilität verschiedener V ersionen finden Sie auf Seite 18.

• Super-Multi-I/O: Diese Hauptplatine ist mit zwei UART-kompatiblen

seriellen Hochgeschwindigkeitsschnittstellen und einer EPP- und ECPfähigen parallelen Schnittstelle ausgestattet. UAR T2 kann für drahtlose

Verbindungen auch mit dem Infrarot-Modul verbunden werden. Zwei

Diskettenlaufwerke mit 5,25 oder 3,5 Zoll (1,44 MB oder 2,88 MB) werden

ebenfalls ohne externe Karte unterstützt. Zusätzlich wird der japanische

“3 Mode”-Diskettenstandard (3,5 Zoll mit 1,2 MB) unterstützt.

• PCI-Busmaster-IDE-Controller: Der auf der Hauptplatine integrierte PCI-

Busmaster-IDE-Controller mit zwei Anschlüssen unterstützt vier IDEGeräte auf zwei Kanälen, ermöglicht schnellere Datentransferraten und

unterstützt Enhanced-IDE-Geräte wie Streamer und CD-ROM-Laufwerke.

Dieser Controller unterstützt die PIO-Modi 3 und 4 und den BusmasterIDE-DMA-Modus 2.

2

P/I-P55TP4N Benutzerhandbuch

II. Merkmale

• IrDA- und PS/2-fähig: Diese Hauptplatine unterstützt ein optionales

Infrarot-Schnittstellen-Modul für drahtlose Verbindungen und ein PS/

2-Maus-Anschlußkabel.

• NCR-SCSI-BIOS: Diese Hauptplatine verfügt über Firmware, die die

optionale ASUS-SCSI-Controllerkarte PCI-SC200 unterstützt.

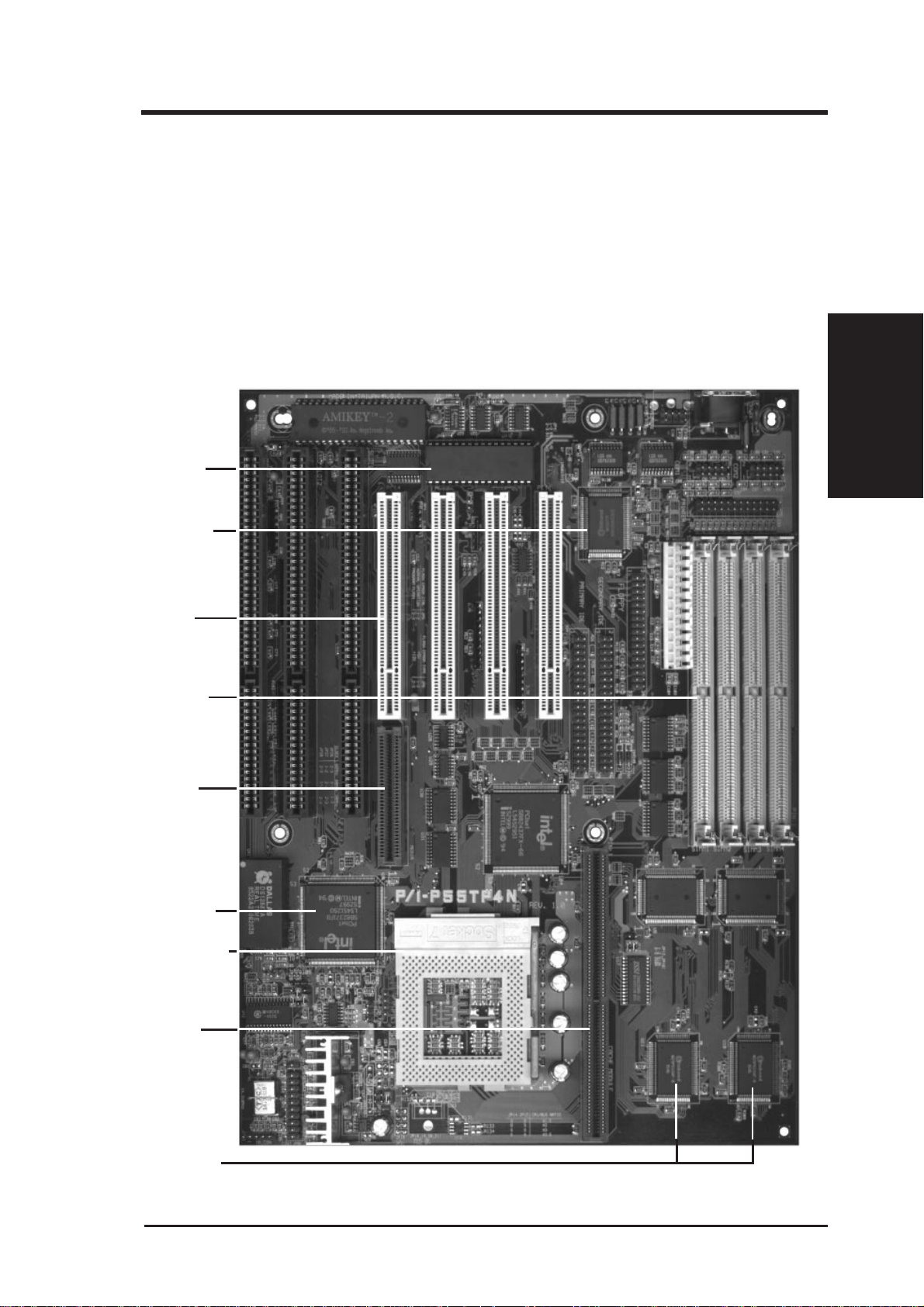

T eile der Hauptplatine

Flash-ROM

Super-Multi-IO

PCI-Slots

72-polige

SIMM-Sockel

ASUSMediaBusErweiterung

II. Merkmale

(T eile der Hauptplatine)

IIntel-Chipsatz

CPU-ZIF-Sockel 7

Erweiterungssteckplatz

für den

nachrüstbaren L2Cache

Integrierter 256-KBPipeline-Burst-L2Cache

P/I-P55TP4N Benutzerhandbuch

3

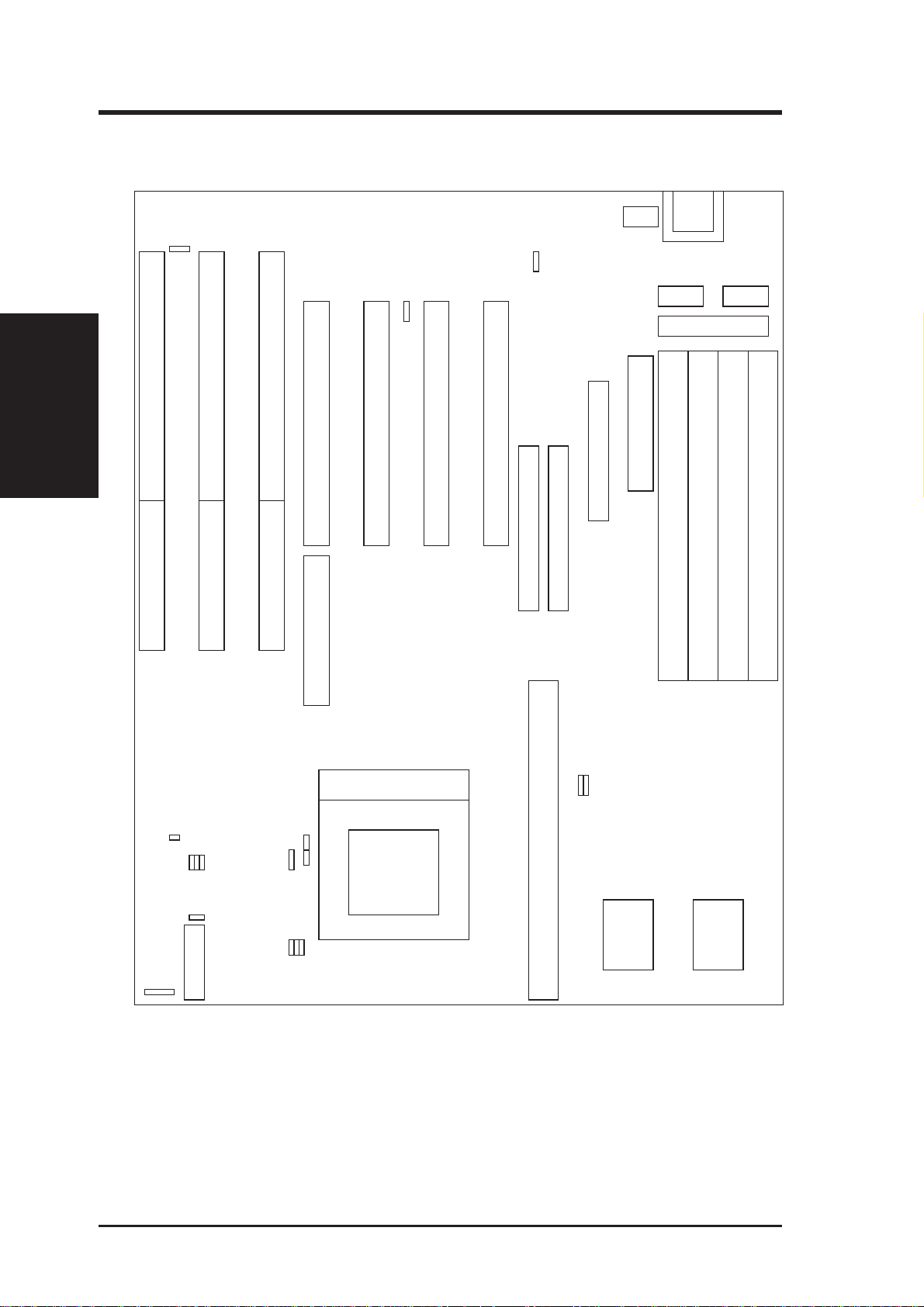

III.INST ALLA TION

Übersichtszeichnung der Hauptplatine

III. INSTALLATION

(Hauptplatine)

JP7

ISA Slot 3

ISA Slot 2

ISA Slot 1

JP5

PCI Slot 4 / MediaBus

PCI Slot 3

PCI Slot 2

JP4

PCI Slot 1

Sekundärer DE-Anschluß

Primärer IDE-Anschluß

PS/2-Maus

COM 1

Parallele Schnittstelle

Anschluß für das Netzteil

Diskettenlaufwerk

SIMM Slot 1

Tastatur

COM 2

SIMM Slot 2

SIMM Slot 3

SIMM Slot 4

JP13

JP31 (IrDA)

JP28

JP27

JP26

Gehäuseanschlüsse

JP30

JP24

JP14

JP15

JP23

JP22

ZIF-Sockel 7

Steckplatz für die Cache-Erweiterung

JP16

JP12

Integrierter 256KB-L2-Cache

4

P/I-P55TP4N Benutzerhandbuch

III. INST ALLA TION

Jumper

1) JP4 S. 7 Multi-I/O-Wahlschalter (Aktivieren/Deaktivieren)

2) JP5 S. 7 Boot-Block-Programmierung (Aktivieren/

Deaktivieren)

3) JP7 S. 8 PS/2-Maus auf IRQ12 (Aktivieren/Deaktivieren)

4) JP12, JP16 S. 8 W ahlschalter für die Gesamtgröße des L2-Cache

5) JP13 S. 9 CMOS-RAM (Betrieb/CMOS-Daten löschen)

6) JP14, JP15 S. 9 Wahlschalter für das Verhältnis zwischen CPU und BUS-Taktrate

7) JP22, JP23, JP24 S. 10 Wahlschalter für die Einstellung der Spannung

8) JP26, JP27, JP28 S. 11 Wahlschalter für die externe Bus-Taktrate

Erweiterungssteckplätze

1) SIMM Slots S. 12 DRAM-Speichererweiterungs-Steckplätze

2) Cache-Erweiterung S. 14 Sockel für SRAM-Cache-Modul

3) CPU-ZIF-Sockel S. 15 Sockel für die CPU (Prozessor)

4) ISA 1,2,3 Slots S. 16 16-Bit-ISA-Bus-Erweiterungssteckplätze

5) PCI 1,2,3 Slots S. 16 32-Bit-PCI-Bus-Erweiterungssteckplätze

6) PCI 4 / MediaBus S. 18 32-Bit-PCI-Bus- und MediaBus-Steckplatz

(Hauptplatine)

III. INSTALLATION

Anschlüsse

1) Keyboard S. 19 Anschluß für die Tastatur (5polige Buchse)

2) PS/2 Mouse S. 19 PS/2-Maus-Anschluß (6poliger Block)

3) Parallel Port S. 20 Anschluß für die parallele Schnittstelle

(26poliger Block)

4) Serial Port S. 20 Serielle Schnittstellen COM1 und COM2

(10polige Blöcke)

5) Floppy Drive S. 21 Anschluß für das Diskettenlaufwerk

(34poliger Block)

6) Power S. 21 Stromversorgungsanschluß auf der Hauptplatine

(12poliger Block)

7) Primary IDE S. 22 Primärer IDE-Anschluß (40poliger Block)

8) Secondary IDE S. 22 Sekundärer IDE-Anschluß (40poliger Block)

9) Turbo/Power S. 23 Turbo-LED/Power-LED (2polig)

10) SMI Switch S. 23 SMI-Taster-Anschlußkabel (2polig)

11) Reset Switch S. 23 Reset-Schalter-Anschlußkabel (2polig

12) Keyboard Lock S. 23 Tastaturschloß-Anschlußkabel (5polig)

13) Speaker S. 23 Lautsprecher-Anschluß (4polig)

14) JP17 S. 24 IDE-Betriebs-LED

15) JP30 S. 24 Anschluß für Prozessor-Lüfter

16) JP31 S. 25 Anschluß für Infrarot-Port-Modul 5

P/I-P55TP4N Benutzerhandbuch

5

III. INSTALLATION

(Jumpers)

III. INST ALLATION

Ablauf der Installation

1. Einstellung der Jumper auf der Hauptplatine

2. Einbau der DRAM-Module

3. Einbau der CPU

4. Einbau von Erweiterungskarten

5. Anschluß externer Kabel und Leitungen

6. Einrichten der BIOS-Software

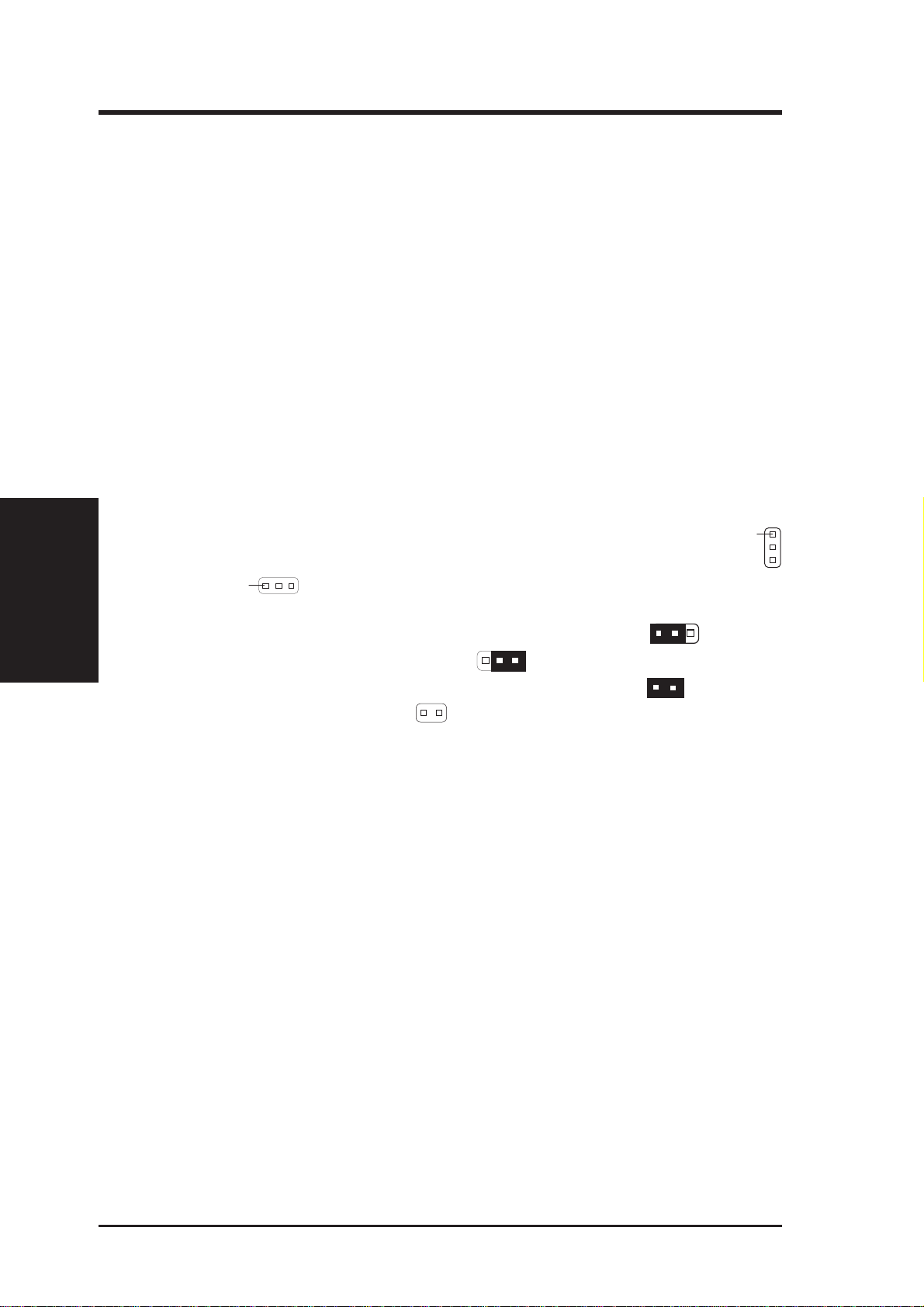

1. Jumper

Eine Reihe von Hardware-Einstellungen erfolgt mit Hilfe von JumperSteckbrücken, die zur V erbindung von Jumper-Stiften (JP) auf der Hauptplatine

dienen. In der “Übersichtszeichnung der Hauptplatine” finden Sie die

Positionen der verschiedenen Jumper . Die Einstellungen der Jumper werden

im folgenden mit Zahlen bezeichnet, z.B. [---], [1-2], [2-3] für “keine

V erbindung” bzw . “Verbindung der Stifte (Pins) 1 und 2”, bzw . “Verbindung

Pin 1

der Stifte 2 und 3”. Pin 1 finden Sie auf unserer Hauptplatine immer oben

bzw . links

von Ihnen wegzeigt. Bei dreipoligen Jumpern ist neben Pin 1 auf der Platine

eine 1 aufgedruckt. Dreipolige Jumper werden grafisch als bei einer

V erbindung zwischen Pin 1 und Pin 2 und

Pin 2 und Pin 3 dargestellt. Zweipolige Jumper werden als dargestellt,

wenn sie gesetzt sind, und als wenn sie nicht gesetzt sind. Um die

Fertigung zu erleichtern, können Jumper auch Pins von anderen Gruppen

mitverwenden. Halten Sie sich an die Diagramme in diesem Handbuch und

nicht an das Pin-Layout auf der Platine.

Wenn Einstellungen mit zwei Jumperzahlen bezeichnet sind, bedeutet das,

daß zwei Steckbrücken zugleich gesetzt werden müssen. Zur V erbindung der

Pins wird einfach eine Plastiksteckbrücke über die jeweiligen beiden Stifte

gesteckt. Jumperstifte ohne V erbindungszahlen sind externe Anschlüsse für

LEDs oder Schalter, nicht für Steckbrücken.

VORSICHT: Die Hauptplatinen und elektronischen Bauteile von Computern

enthalten sehr empfindliche IC-Chips. Um die Hauptplatine und andere

elektronische Bauteile vor Beschädigung durch statische Elektrizität zu

schützen, sollten Sie bei allen Arbeiten am Computer einige

Vorsichtsmaßnahmen beachten:

Pin 1

wenn Sie die Platine so halten, daß der T astaturanschluß

bei einer V erbindung zwischen

6

1. Trennen Sie den Computer vom Netz, wenn Sie in seinem Inneren

arbeiten.

2 . Fassen Sie elektronische Bauteile an den Rändern an und berühren Sie

möglichst nicht die IC-Chips.

P/I-P55TP4N Benutzerhandbuch

III. INST ALLA TION

3 . Legen Sie ein Schutzarmband an, bevor Sie mit elektronischen Bauteilen

arbeiten.

4 . Legen Sie elektronische Bauteile auf eine geerdete Antistatik-Unterlage

oder auf die Schutzhülle, in der sie verpackt waren, wenn Sie außerhalb

des Computers mit ihnen arbeiten.

Jumper-Einstellungen

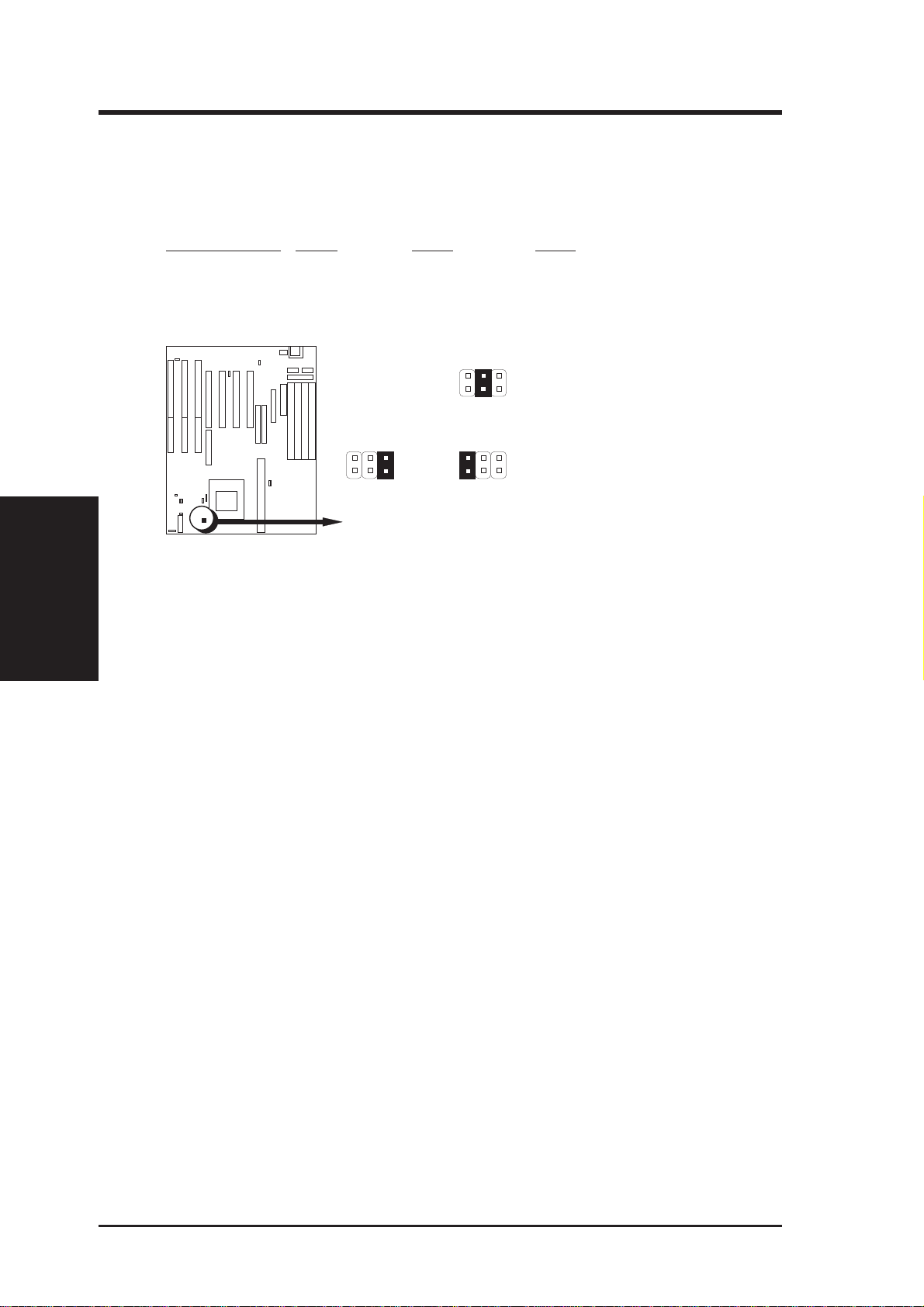

1. W ahlschalter für den integrierten Multi-I/O-Anschluß (JP4)

Wenn Sie Ihre eigene Multi-I/O-Erweiterungskarte benutzen wollen,

können Sie den auf der Platine integrierten Multi-I/O-Anschluß

(Diskettenlaufwerk, serielle, parallele und IrDA-Schnittstelle)

deaktivieren.

Einstellungen JP4

Aktiviert [1-2] (V oreinstellung)

Deaktiviert [2-3]

JP

4

1

2

3

Aktiviert (Voreinstellung)

Integrierter Multi-I/O-Anschluß (Aktiviert/Deaktiviert)

JP

4

1

2

3

Deaktiviert

2. Boot-Block-Programmierung (JP5)

Mit diesem Jumper wird der Betriebsmodus des BIOS-Flash-ROMs auf

“Aktiviert” eingestellt, um eine Neuprogrammierung zu ermöglichen.

Programmierung JP5

Deaktiviert [1-2] (Voreinstellung)

Aktiviert [2-3]

JP

5

1

2

3

Deaktiviert (Voreinstellung) Aktiviert

JP

5

1

2

3

(Jumpers)

III. INSTALLATION

Boot-Block-Programmierung (Deaktiviert oder Aktiviert)

P/I-P55TP4N Benutzerhandbuch

7

)

g)

III. INST ALLATION

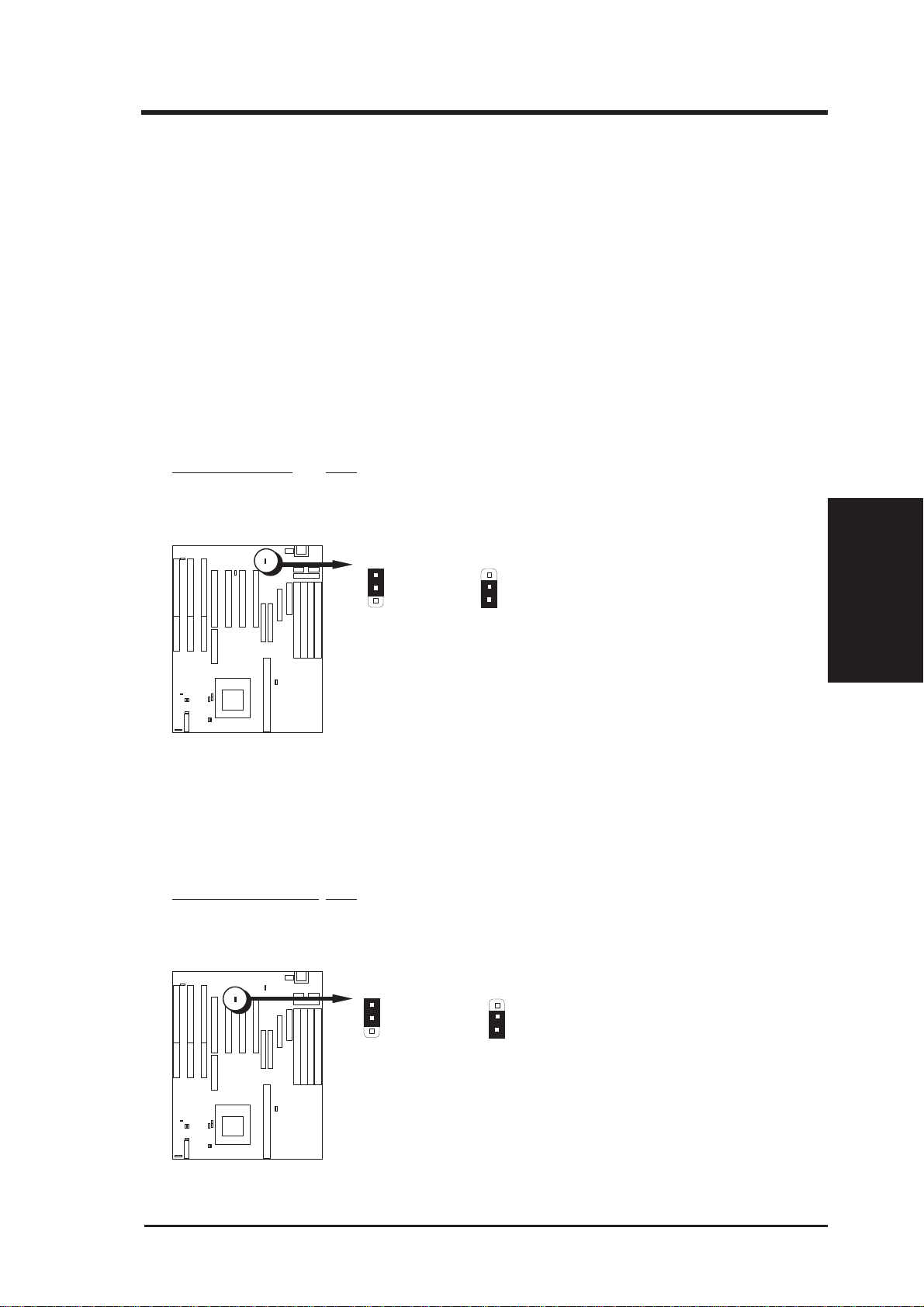

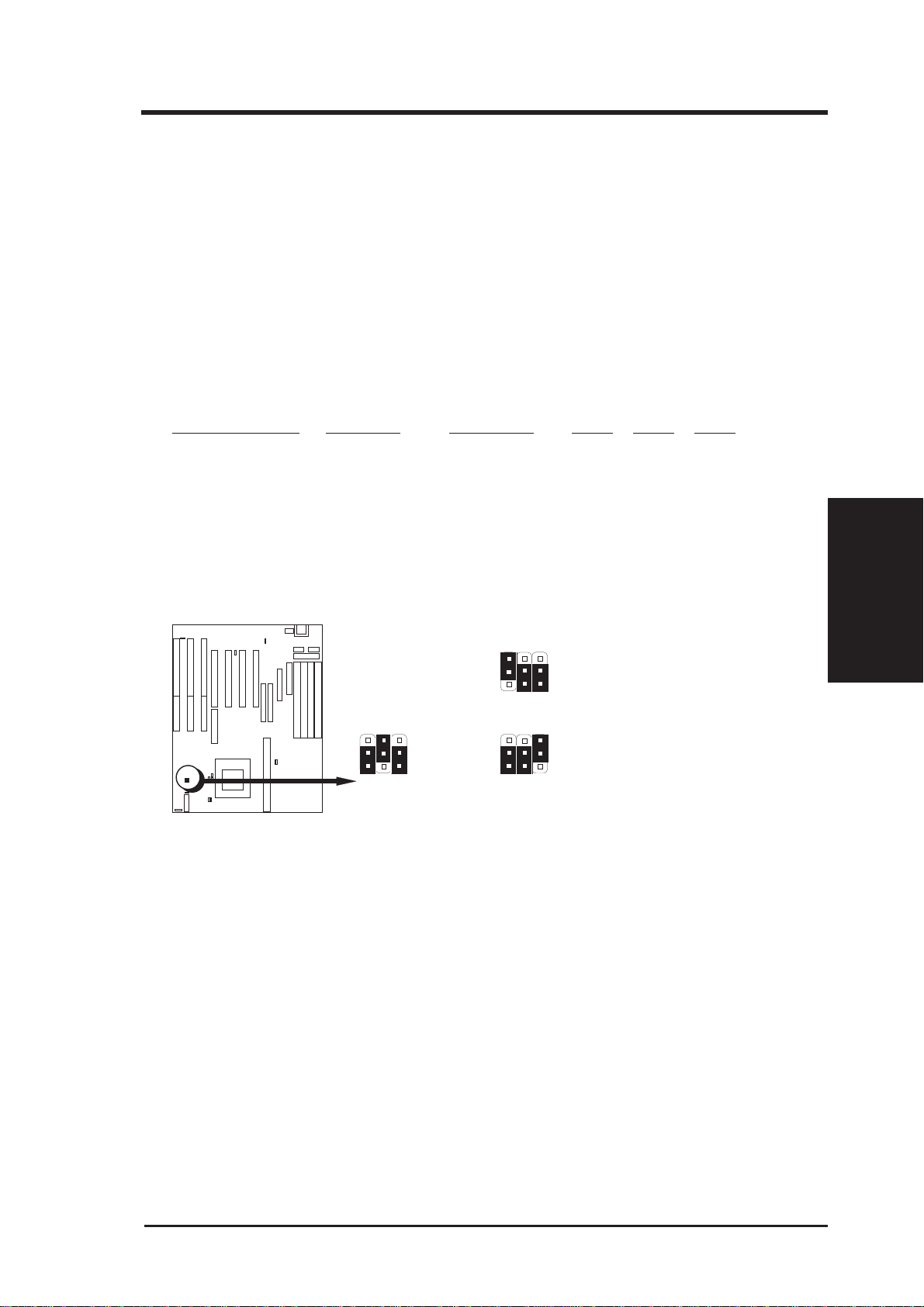

3. W ahlschalter für eine PS/2-Maus (JP7)

JP7 aktiviert oder deaktiviert den auf der Platine integrierten PS/2-MausAnschluß. Wenn der Jumper gesetzt ist, ist der Port aktiv und benutzt

IRQ12. Siehe Seite 19, “PS/2-Maus-Anschluß”.

Einstellungen JP7

Deaktiviert [2-3] (Voreinstellung)

Aktiviert [1-2]

III. INSTALLATION

(Jumpers)

123

JP 7 JP 7

Deaktiviert (Voreinstellun

PS/2-Maus-Wahlschalter (Deaktiviert oder Aktiviert

123

Aktiviert

4. Einstellung der Gesamtgröße des L2-Cache (JP12, JP16)

Mit diesen Jumpern wird die Gesamtgröße des vorhandenen (auf der

Platine integrierten plus zusätzlich installierten) Second-Level-Cache

eingestellt. W enn Sie zwei Cache-Chips auf der Platine haben (ihre Position finden Sie in der “Übersichtszeichnung der Hauptplatine”), dann

haben Sie anfänglich 256 KB, und ein spezielles ASUS-Upgrade-CacheModul (ab Rev .1.6) würde Ihnen insgesamt 512 KB zur V erfügung stellen.

Wenn kein Cache auf der Platine integriert ist, müssen Sie entweder ein

256-KB- oder ein 512-KB-Cache-Modul installieren. Einzelheiten zur Installation finden Sie auf Seite 14 “SRAM-Cache”. Stellen Sie die folgenden

Jumper entsprechend der Gesamtgröße des L2-Cache ein.

8

Einstellungen JP16

256 KB [2-3] (Voreinstellung)

512KB [1-2]

JP

16

1

2

3

256 KB (Vore instellung) 512K

Einstellung der Gesamtgröße des L2-Cache (256 KB oder 512 KB)

JP

16

1

2

3

P/I-P55TP4N Benutzerhandbuch

III. INST ALLA TION

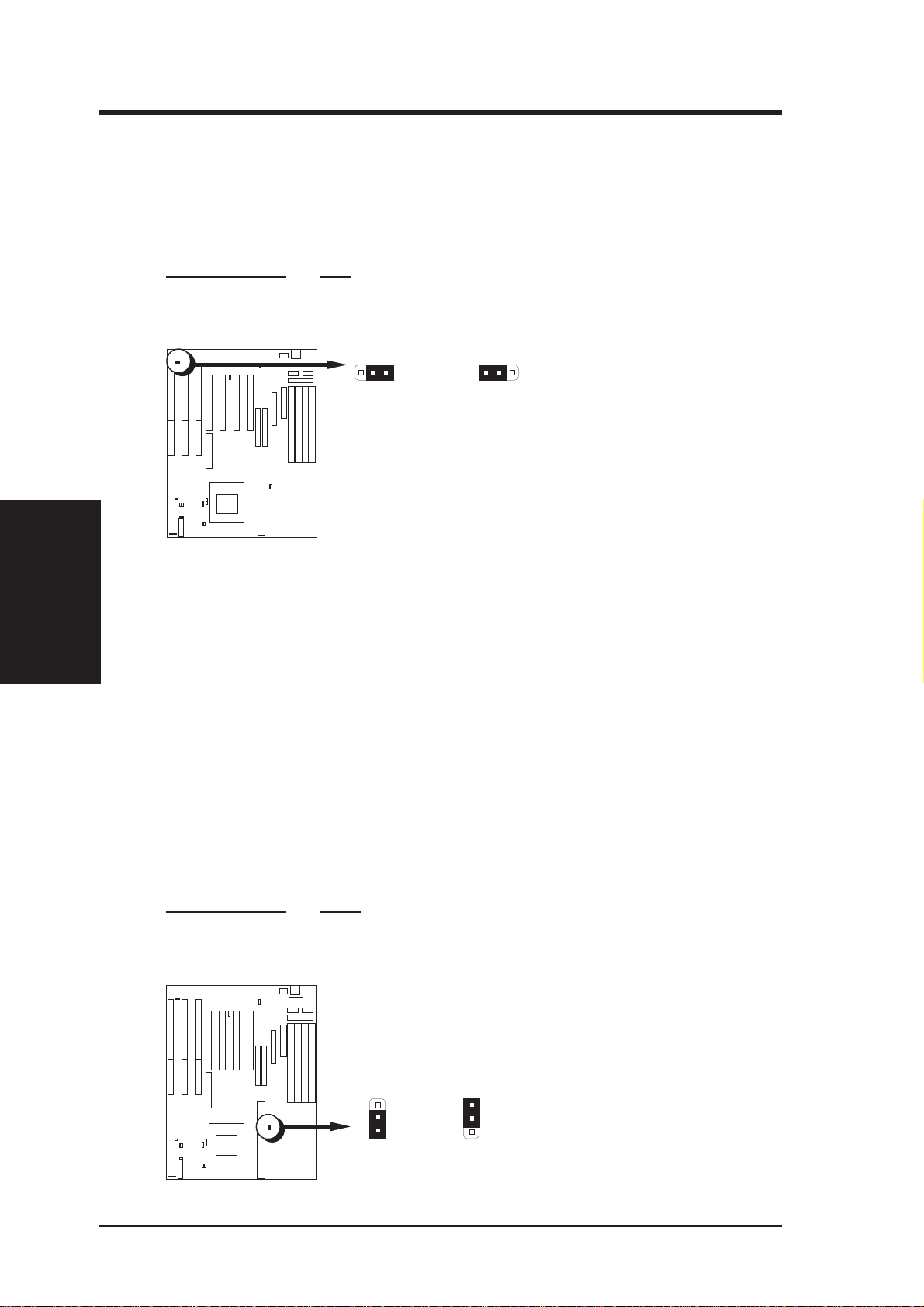

5. CMOS-RAM (JP13)

Mit diesem Jumper werden die vom Benutzer eingegebenen und im Dallas-DS12887A-Chip gespeicherten Daten, wie beispielsweise

Informationen über die Festplatte und Paßwörter, gelöscht. Verbinden

Sie einfach einige Sekunden lang die Pins mit einer Steckbrücke und

entfernen Sie sie dann wieder . Dabei muß der Computer ausgeschaltet

sein. Anschließend müssen Sie ins BIOS-Setup gehen (indem Sie während

des Bootens die T aste <Entf> bzw . <Del> gedrückt halten), um die BIOSDaten neu einzugeben (siehe BIOS SETUP).

Einstellungen JP13

Normal [offen] (Voreinstellung)

CMOS löschen [verbunden] (für eine kurze Zeit)

JP13 JP13

Betrieb (Voreinstellung) Daten löschen

CMOS-RAM (Betrieb oder CMOS-Daten löschen)

6. V erhältnis zwischen CPU- und BUS-T aktrate (JP14, JP15)

Mit diesen Jumpern wird das Verhältnis zwischen der internen Taktrate

der CPU und der externen T akrate (BUS) eingestellt. Benutzen Sie bei 75,

90, und 100MHz-Pentium-Prozessoren die Voreinstellung. Sie müssen

auch die “W ahlschalter für die Bus-T aktrate” (JP26, JP27, JP28) einstellen

(siehe Seite 11).

CPU:BUS JP14 JP15

1,5x [offen] [offen] (Voreinstellung)

2,0x [offen] [verbunden]

3,0x [verbunden] [offen]

2,5x [verbunden] [verbunden]

(Jumpers)

III. INSTALLATION

JP

14

JP

15

1,5x (Voreinstellun g)

Wahlschalter für das Verhältnis zwischen CPU- und BUS-Taktrate (1,5x 2,0x 3,0x 2,5x)

2.0x

JP

14

JP

15

3.0x

JP

14

JP

15

2.5x

JP

14

JP

15

P/I-P55TP4N Benutzerhandbuch

9

III. INST ALLATION

(

g)

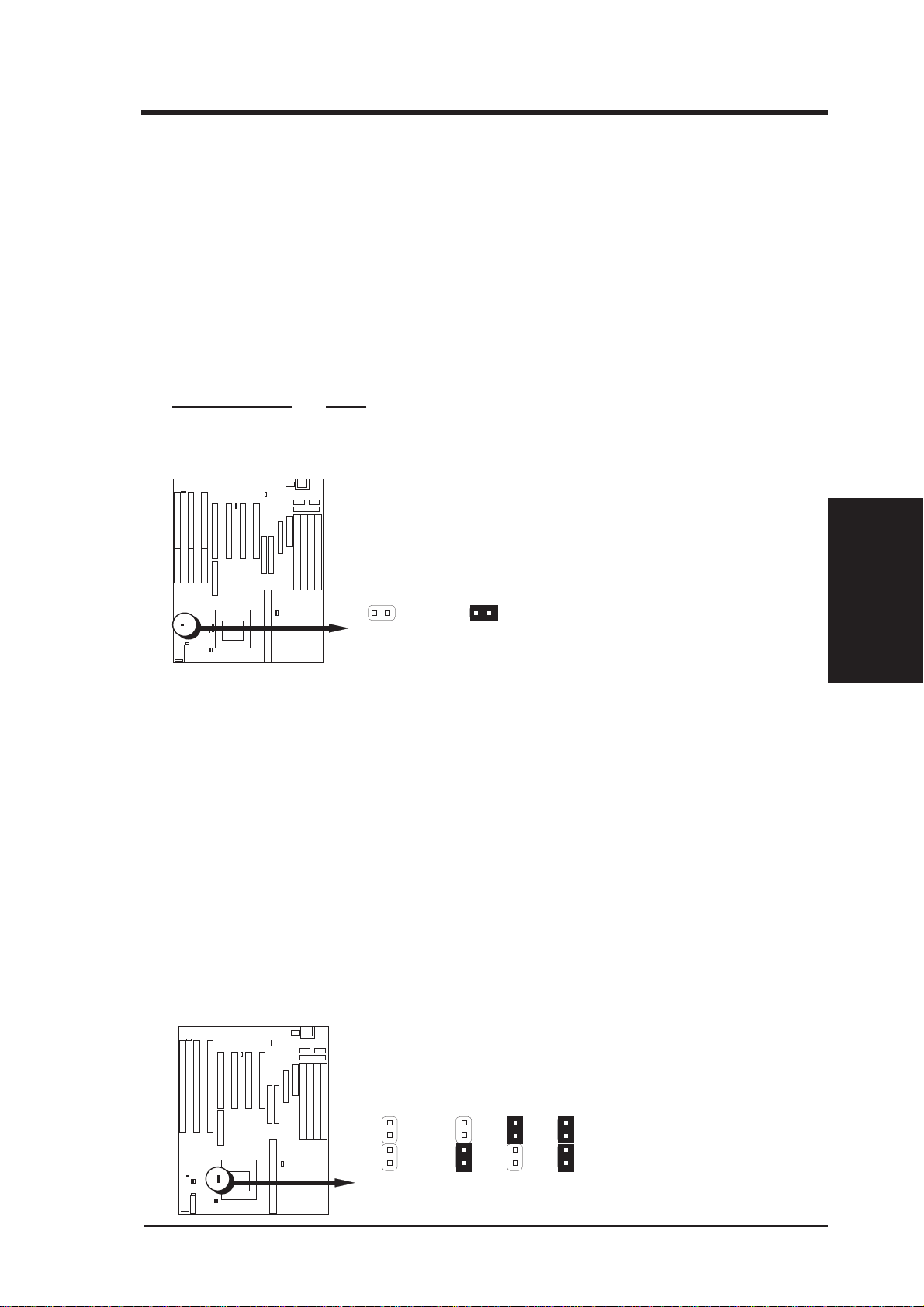

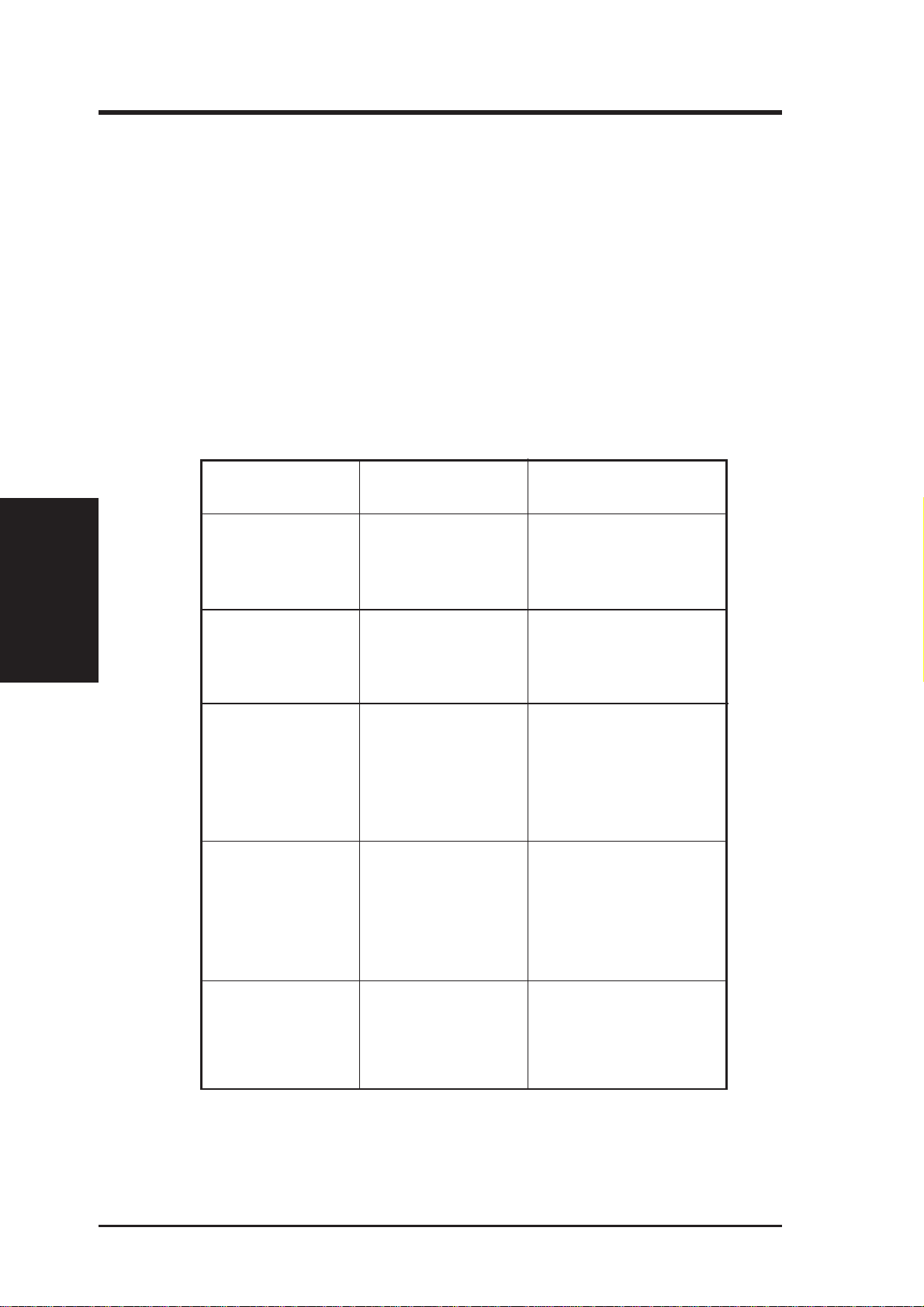

7. W ahlschalter für die Einstellung der Spannung (JP22, JP23, JP24)

Mit diesen Jumpern wird die Versorgungsspannung für die CPU

eingestellt.

Einstellungen JP24 JP23 JP22

STD (3,4 V) [offen] [offen] [verbunden] (Voreinstellung)

VRE (3,5 V) [offen] [verbunden] [offen]

(reserviert) [verbunden] [offen] [offen]

JP24JP23JP

22

VRE (3.5V)

III. INSTALLATION

(Jumpers)

JP24JP23JP

22

STD (3.4V)

Voreinstellun

Wahlschalter für die Einstellung der Spannung (STD/VRE)

JP24JP23JP

reserviert

(

22

)

10

P/I-P55TP4N Benutzerhandbuch

III. INST ALLA TION

8. W ahlschalter für die BUS-T aktrate (JP26, JP27, JP28)

Diese Jumper bestimmen, welche T aktrate der T aktgenerator an die CPU

liefert. Sie ermöglichen die Einstellung der externen Taktfrequenz der

CPU (BUS-T akt) auf 50 MHz, 60 MHz oder 66 MHz. W enn man die CPUTaktrate durch die BUS-Taktrate dividiert, erhält man das auf Seite 10

beschriebene Verhältnis zwischen CPU- und BUS-T aktrate. Stellen Sie

diese Jumper wie angegeben entsprechend der internen CPU-Taktrate

(der für Prozessoren angegebenen Taktrate) ein. Sie müssen auch das

“V erhältnis zwischen CPU- und BUS-T aktrate” (JP14 und JP15) einstellen

(siehe Seite 10).

Internal (CPU) Multiple Ext (BUS) JP28 JP27 JP26

166 MHz 2,5 x Extern 66 MHz [2-3] [1-2] [2-3]

150 MHz 2,5 x Extern 60 MHz [1-2] [2-3] [2-3]

133 MHz 2,0 x Extern 66 MHz [2-3] [1-2] [2-3]

120 MHz 2,0 x Extern 60 MHz [1-2] [2-3] [2-3]

100 MHz 1,5 x Extern 66 MHz [2-3] [1-2] [2-3]

90 MHz 1,5 x Extern 60 MHz [1-2] [2-3] [2-3]

75 MHz 1,5 x Extern 50 MHz [2-3] [2-3] [1-2]

JP

JP28JP

26

27

1

2

3

JP

JP28JP

26

27

1

2

3

66 MHz (Voreinstellung)

Wahlschalter für die BUS-Taktrate (66, 60 oder 50 MHz)

60MHz

JP28JP

50MHz

JP

26

27

1

2

3

(Jumpers)

III. INSTALLATION

P/I-P55TP4N Benutzerhandbuch

11

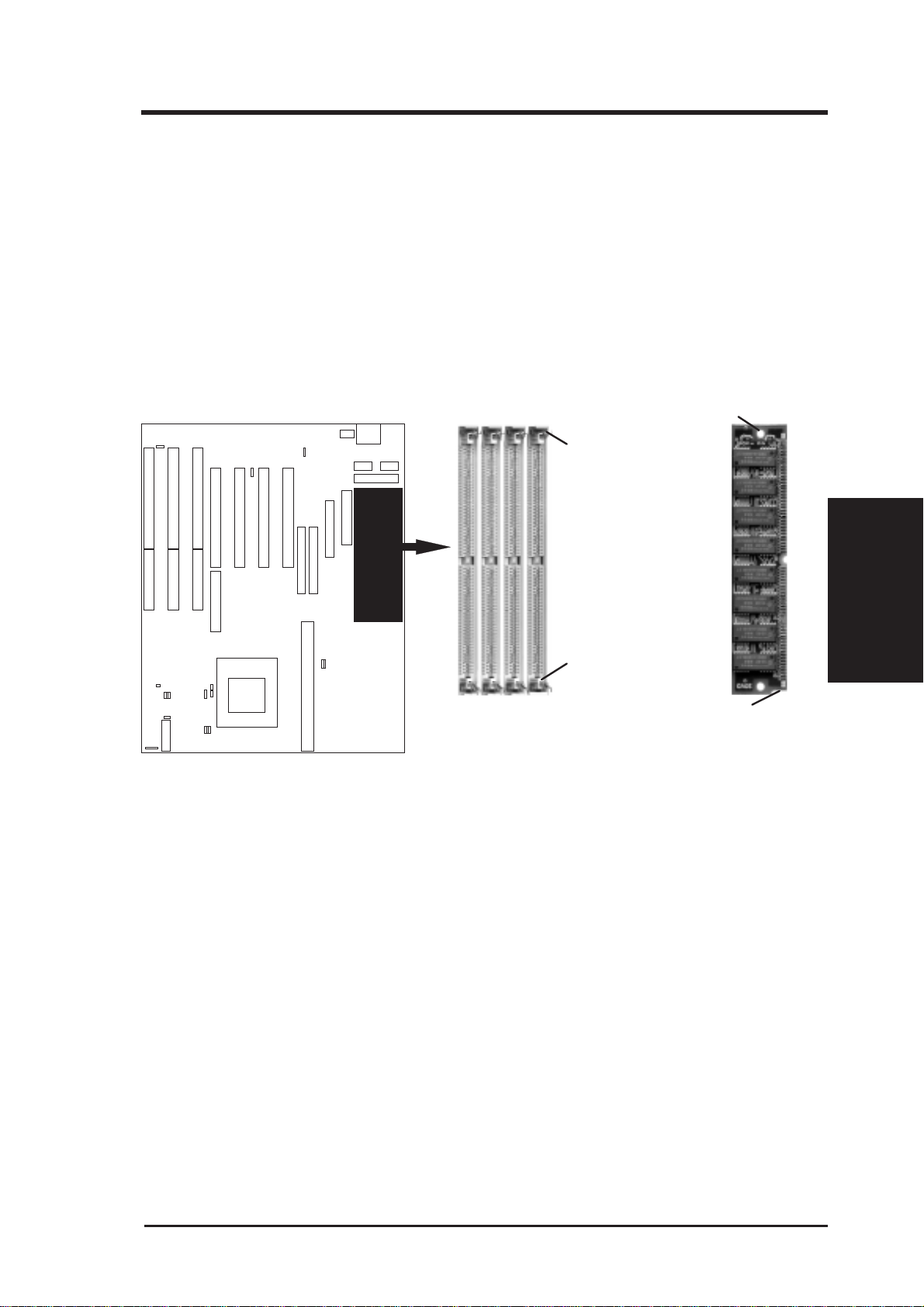

2. Systemspeicher (DRAM und SRAM)

Diese Hauptplatine unterstützt 72polige SIMMs mit Kapazitäten von 4 MB,

8 MB, 16 MB oder 32 MB, so daß eine Speichergröße von 8 MB bis 128 MB

erreicht wird. Die DRAMs müssen bei einer BUS-T aktrate von 50 MHz oder

60 MHz mit einer Zugriffszeit von max. 70 ns und bei einer BUS- T aktrate von

66 MHz mit einer Zugriffszeit von max. 60 ns (siehe Seite 11 “W ahlschalter

für die BUS-Taktrate”) sowie mit Fast Page Mode (asymmetrisch oder

symmetrisch) oder EDO arbeiten. Sie sollten sich für Speichermodule mit

größerer Kapazität in zwei Steckplätzen (Slots) entscheiden, so daß noch

Platz für eine spätere Aufrüstung des Speichers bleibt. WICHTIG: Wie die

folgende Tabelle zeigt, müssen immer zwei Speichermodule gleichzeitig

installiert sein.

III. INSTALLATION

(Systemspeicher )

32 MB x 2 8 MB x 2 8 0 MB

III. INST ALLATION

Bank 0 Bank 1 Gesamtspeicher

Slots 1 + 2 Slots 3 + 4 Kombination

4 MB x 2 Unbestückt 8 MB

8 MB x 2 Unbestückt 16 MB

16 MB x 2 Unbestückt 32 MB

32 MB x 2 Unbestückt 64 MB

Unbestückt 4 MB x 2 8 MB

Unbestückt 8 MB x 2 16 MB

Unbestückt 16 MB x 2 32 MB

Unbestückt 32 MB x 2 64 MB

4 MB x 2 4 MB x 2 16 MB

4 MB x 2 8 MB x 2 24 MB

4 MB x 2 16 MB x 2 40 MB

4 MB x 2 32 MB x 2 72 MB

8 MB x 2 4 MB x 2 24 MB

8 MB x 2 8 MB x 2 32 MB

8 MB x 2 16 MB x 2 48 MB

8 MB x 2 32 MB x 2 80 MB

16 MB x 2 4 MB x 2 40 MB

16 MB x 2 8 MB x 2 48 MB

16 MB x 2 16 MB x 2 64 MB

16 MB x 2 32 MB x 2 96 MB

32 MB x 2 4 MB x 2 72 MB

32 MB x 2 16 MB x 2 96 MB

32 MB x 2 32 MB x 2 128 MB

WICHTIG: Ver wenden Sie keine SIMM-Module mit mehr als 24 Chips pro

Modul. Für solche Module ist das Speicher-Subsystem von seinen

Spezifikationen her nicht ausgelegt, stabiles Arbeiten kann daher nicht

gewährleistet werden.

12

P/I-P55TP4N Benutzerhandbuch

III. INST ALLA TION

WICHTIG: Verwenden Sie keine SIMM-Module, die mit einem speziellen

TTL-Chip arbeiten, um das Speichermodul von asymmetrisch auf symmetrisch

umzuschalten.

Der Einbau von DRAM-Speicher

1 . Das SIMM-Speichermodul läßt sich nur in der angegebenen Richtung

einsetzen, so daß die Einkerbung über die “Plastiksicherheitszunge” zu

liegen kommt.

Montageloch

Metallklammer

Plastiksicherheitszunge

(Nur auf dieser Seite)

4132

72polige SIMM-DRAM-Steckplätze

Einkerbung

2. Drücken Sie das Speichermodul im 45-Grad-Winkel fest in den Slot.

3. Drücken Sie das Modul nach vorn, so daß es einrastet.

4. Die Plastikführungen müssen durch die beiden seitlich angebrachten

“Montagelöcher” hindurchgehen, und die “Metallklammern” müssen

auf der anderen Seite zuschnappen.

5. Um das Modul zu entnehmen, drücken Sie die beiden “Metallklammern”

nach außen und ziehen Sie das Modul mit einer Hin- und Herbewegung

aus den “Metallklammern”.

(DRAM)

III. INSTALLATION

P/I-P55TP4N Benutzerhandbuch

13

Loading...

Loading...