8

7

6 5 4 3

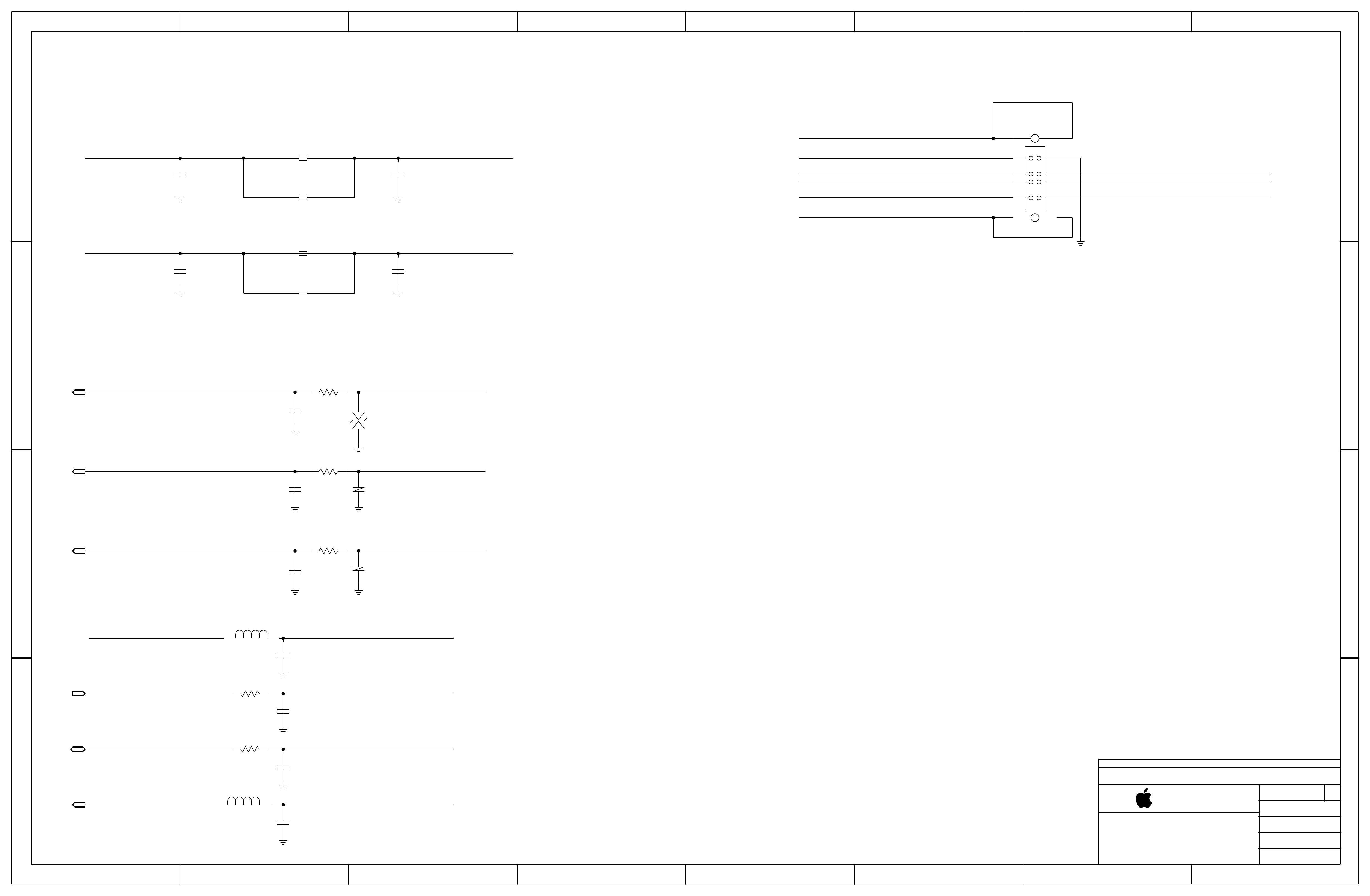

1. ALL INFORMATION COMPILED FOR USERS OF FORUM HTTP://WWW.MOBILEGSM.IN.UA

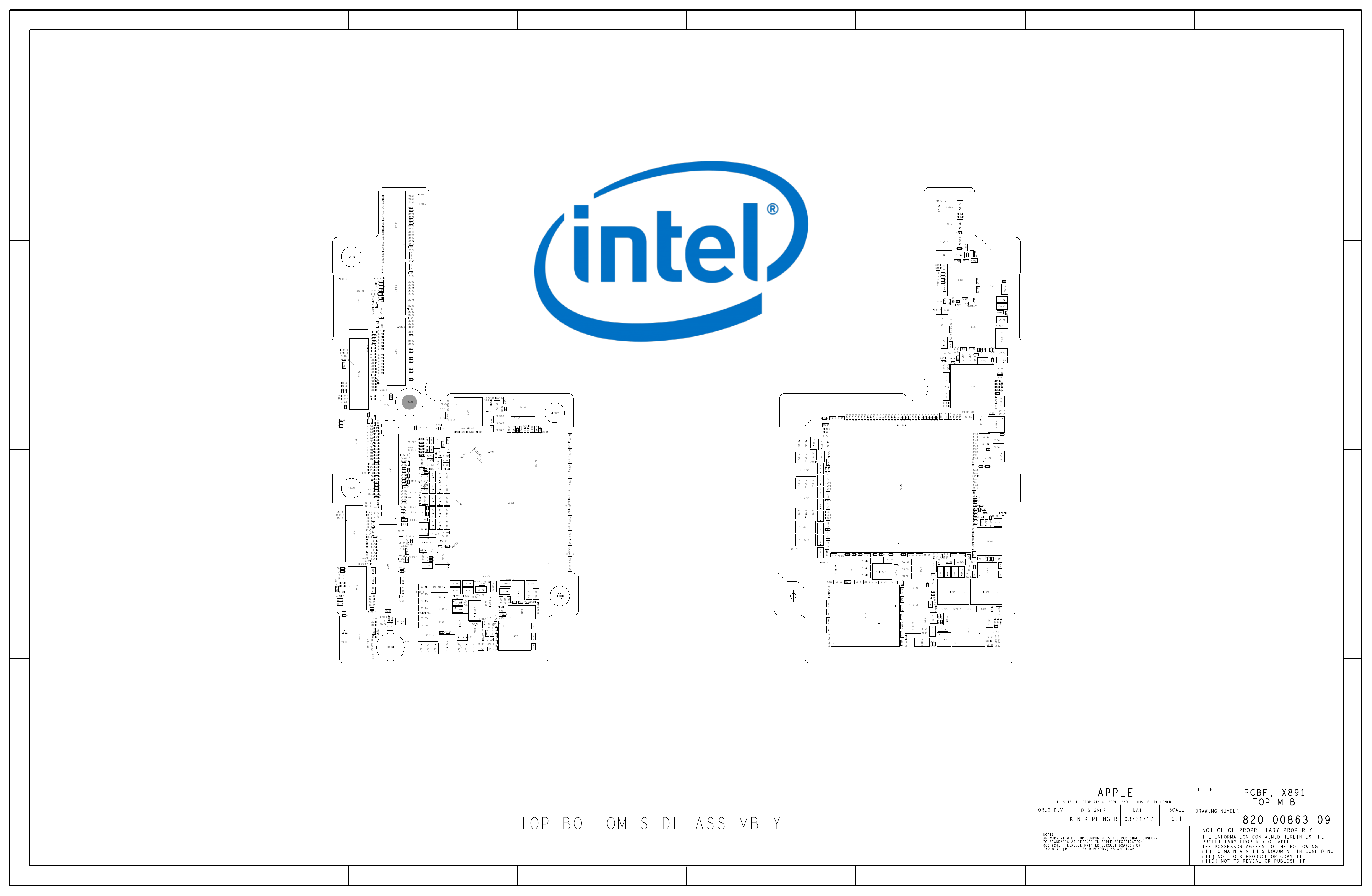

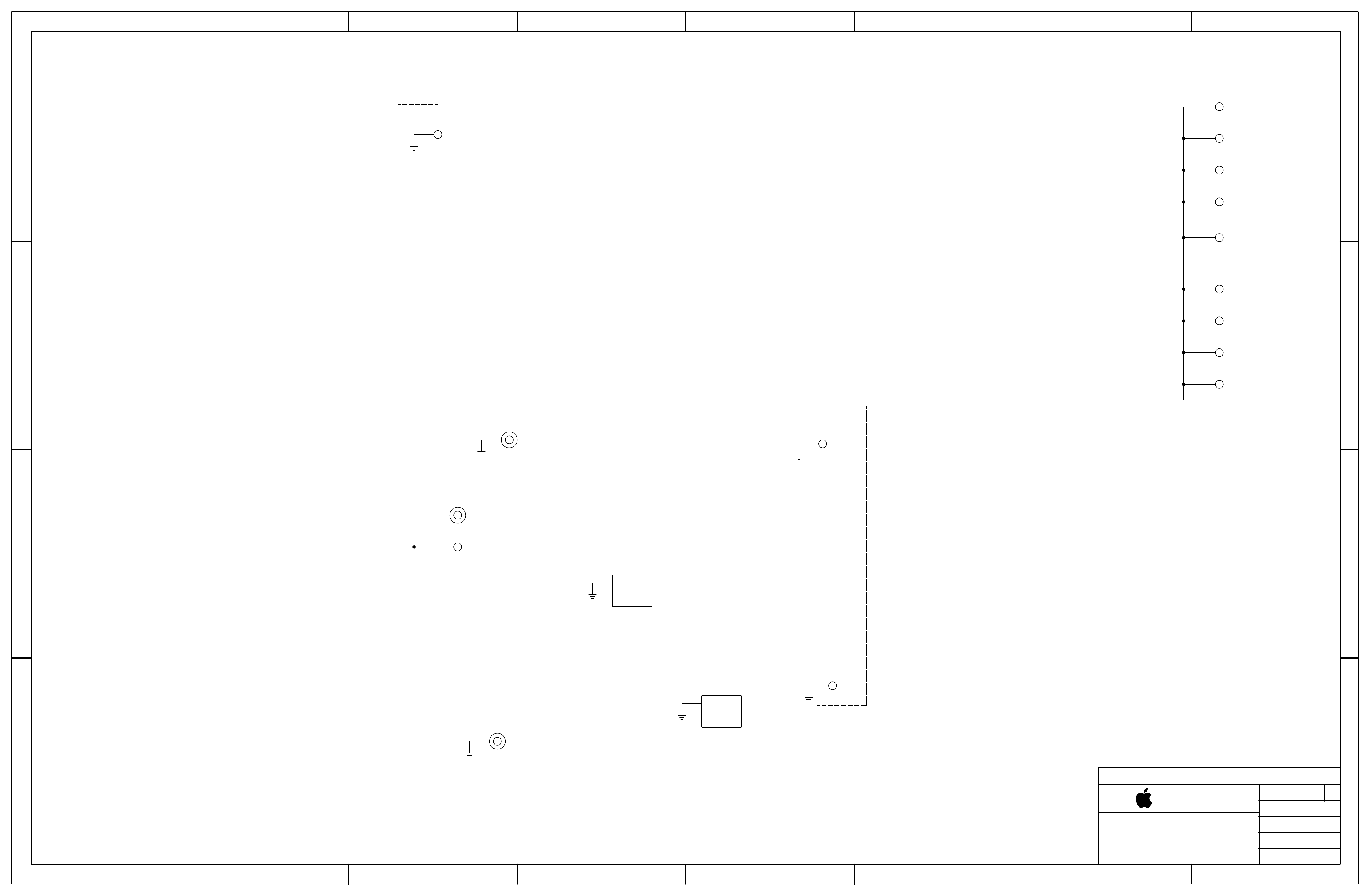

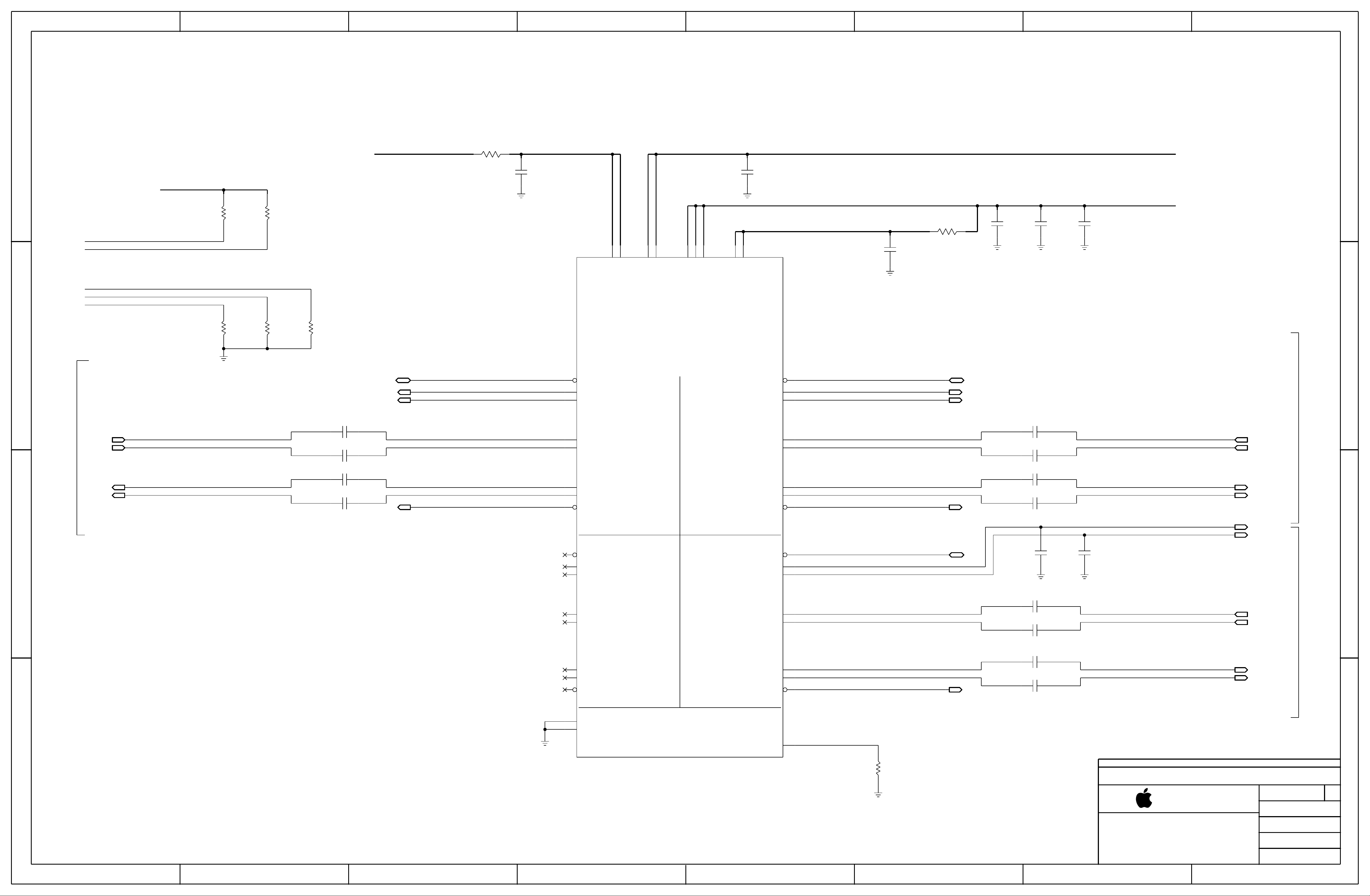

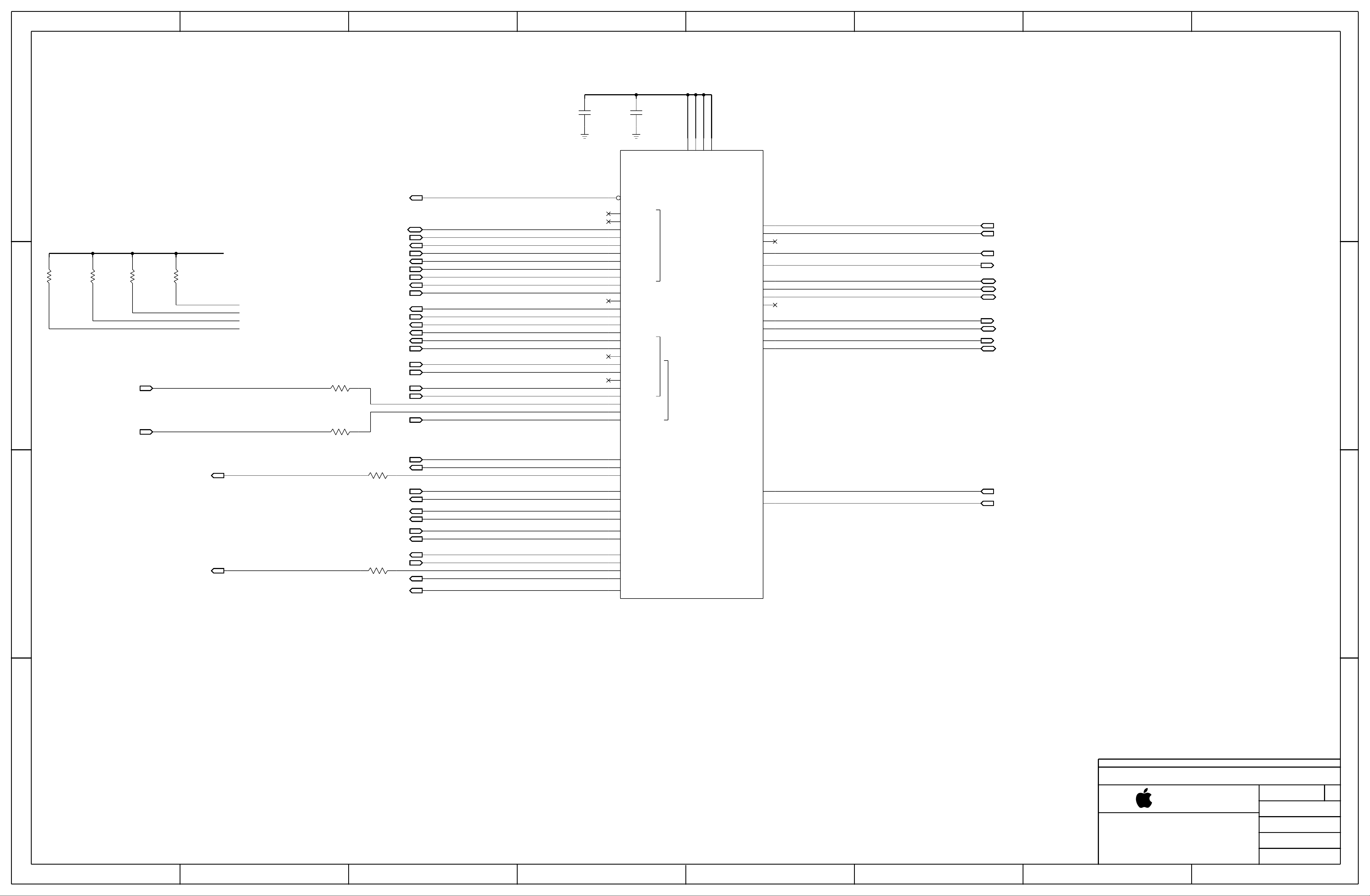

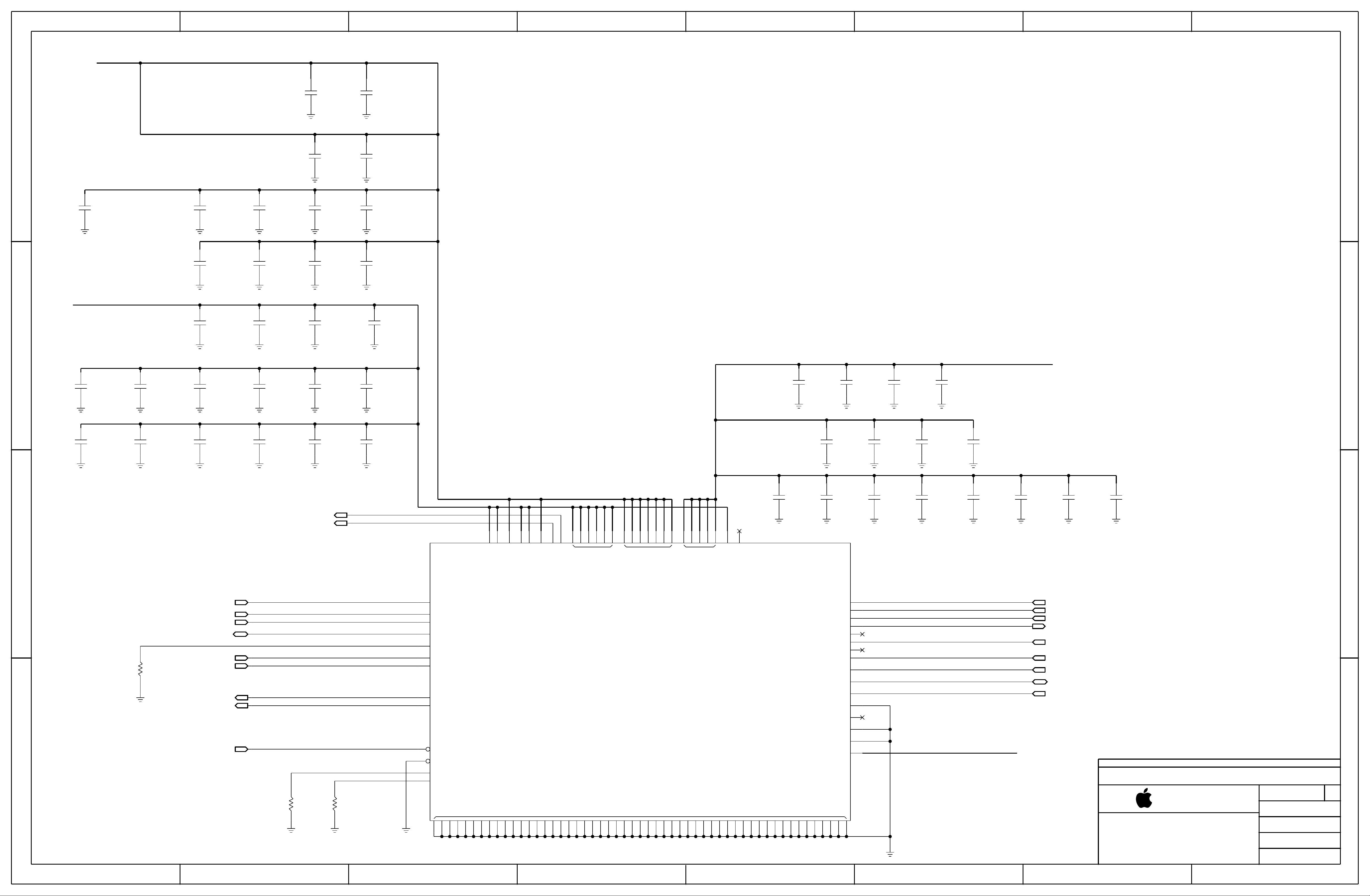

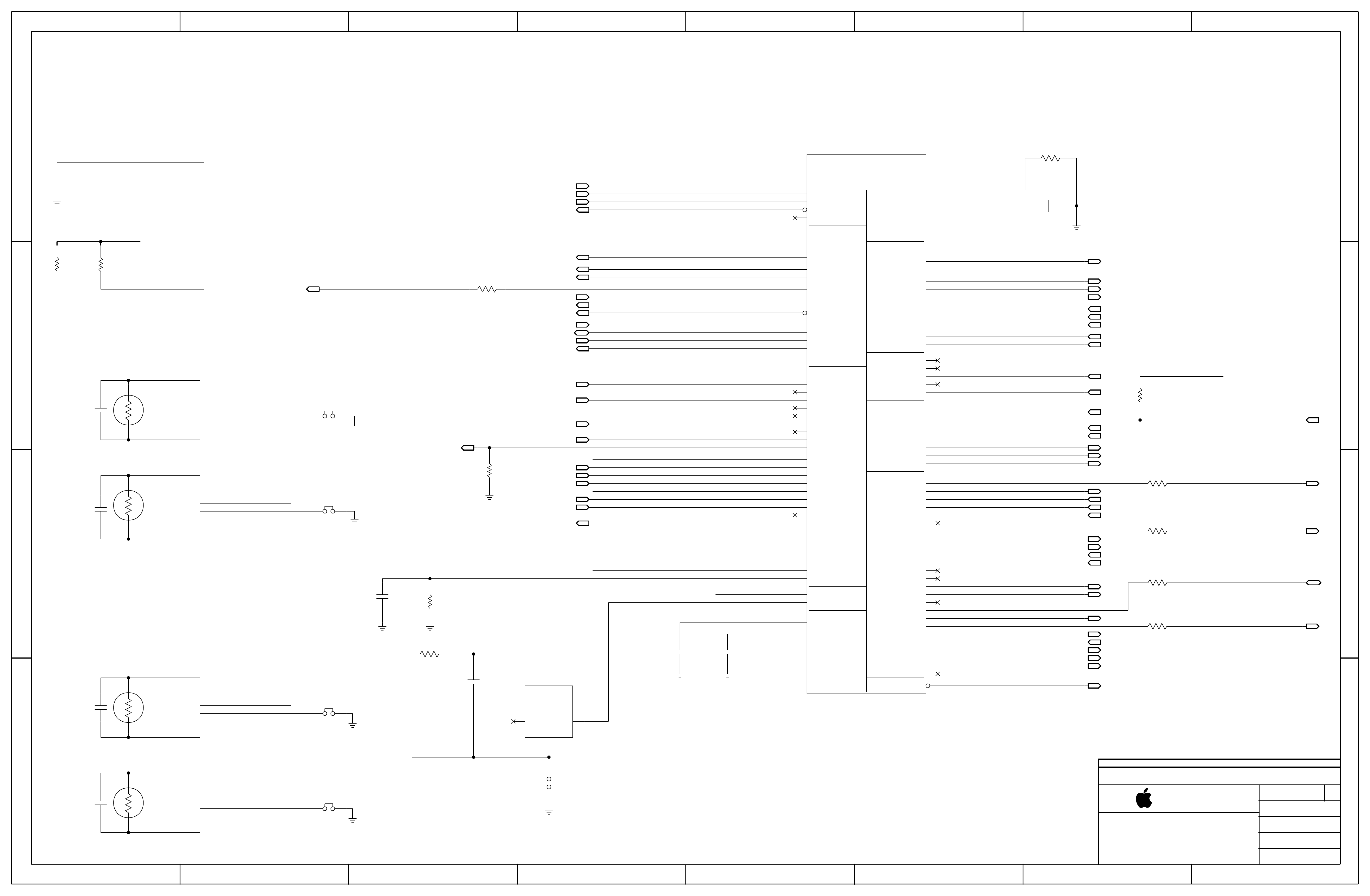

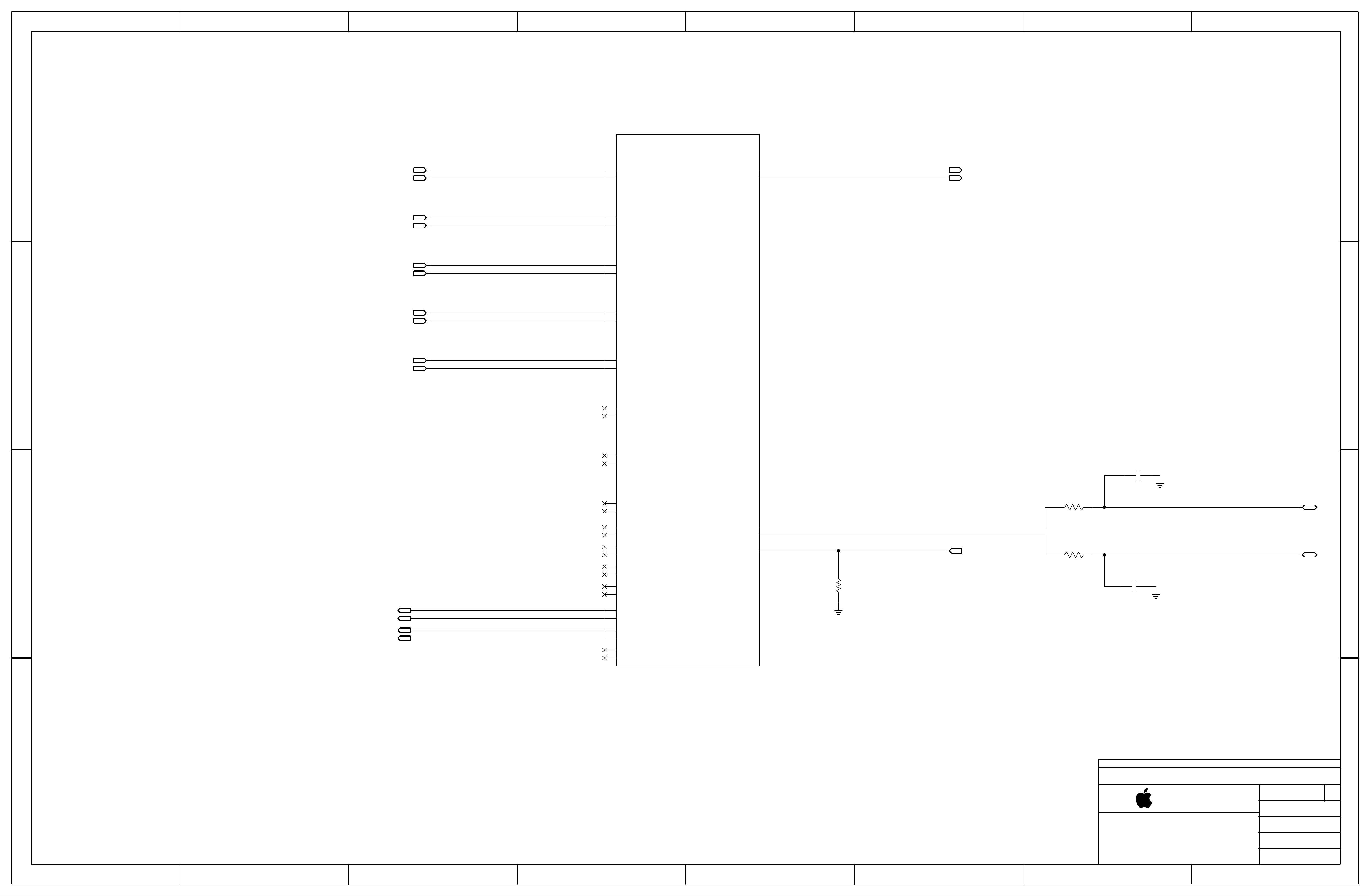

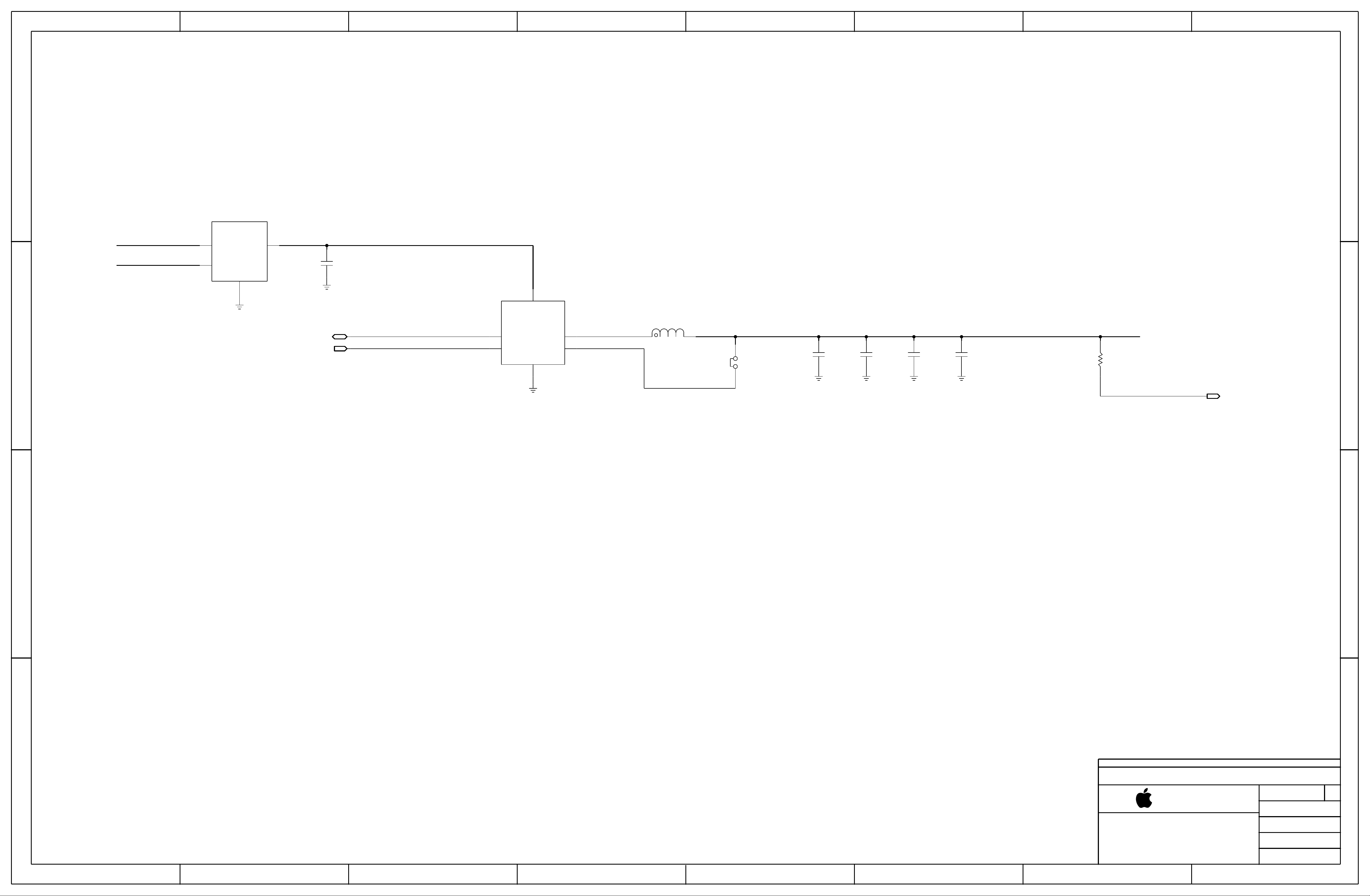

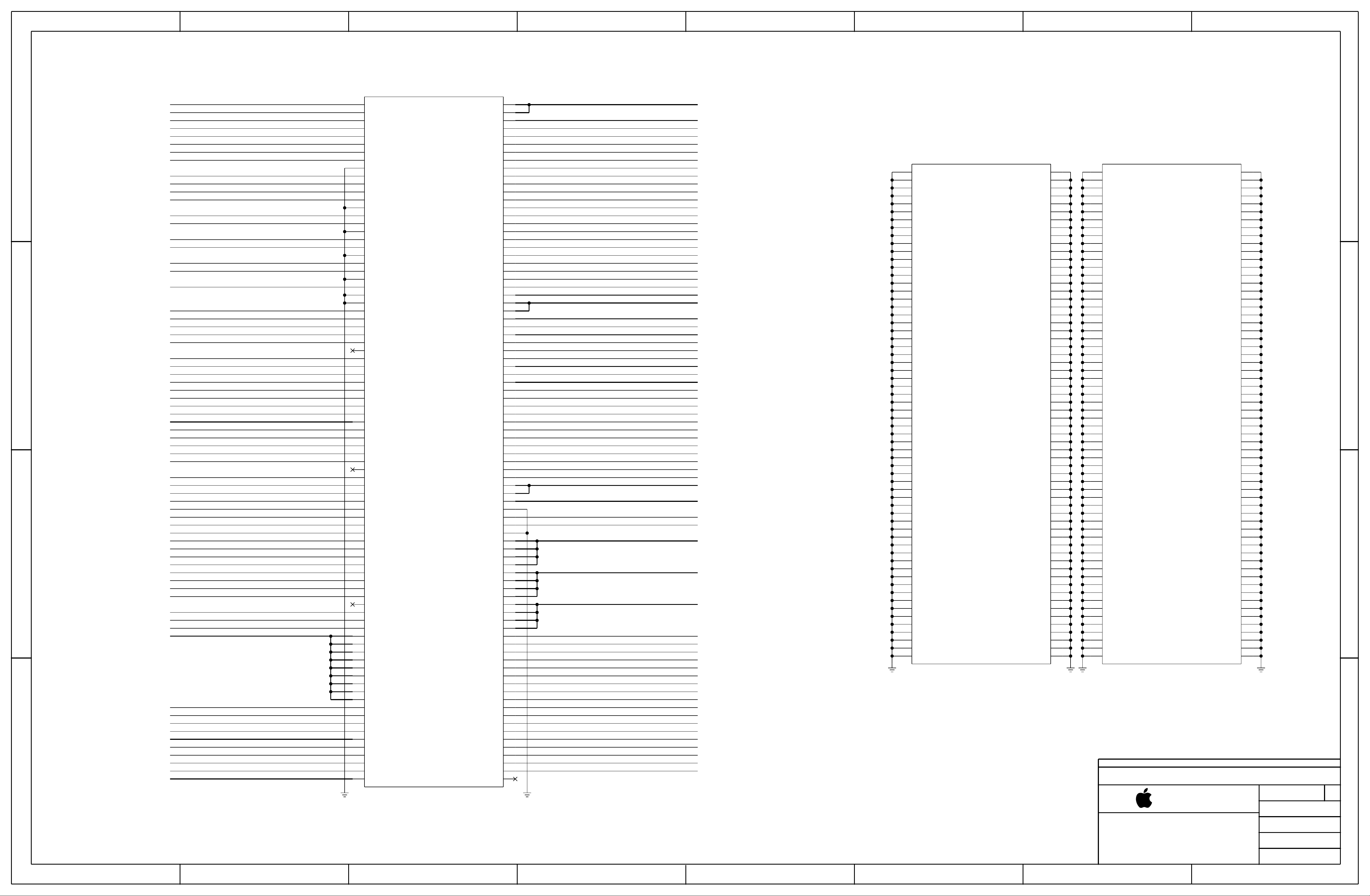

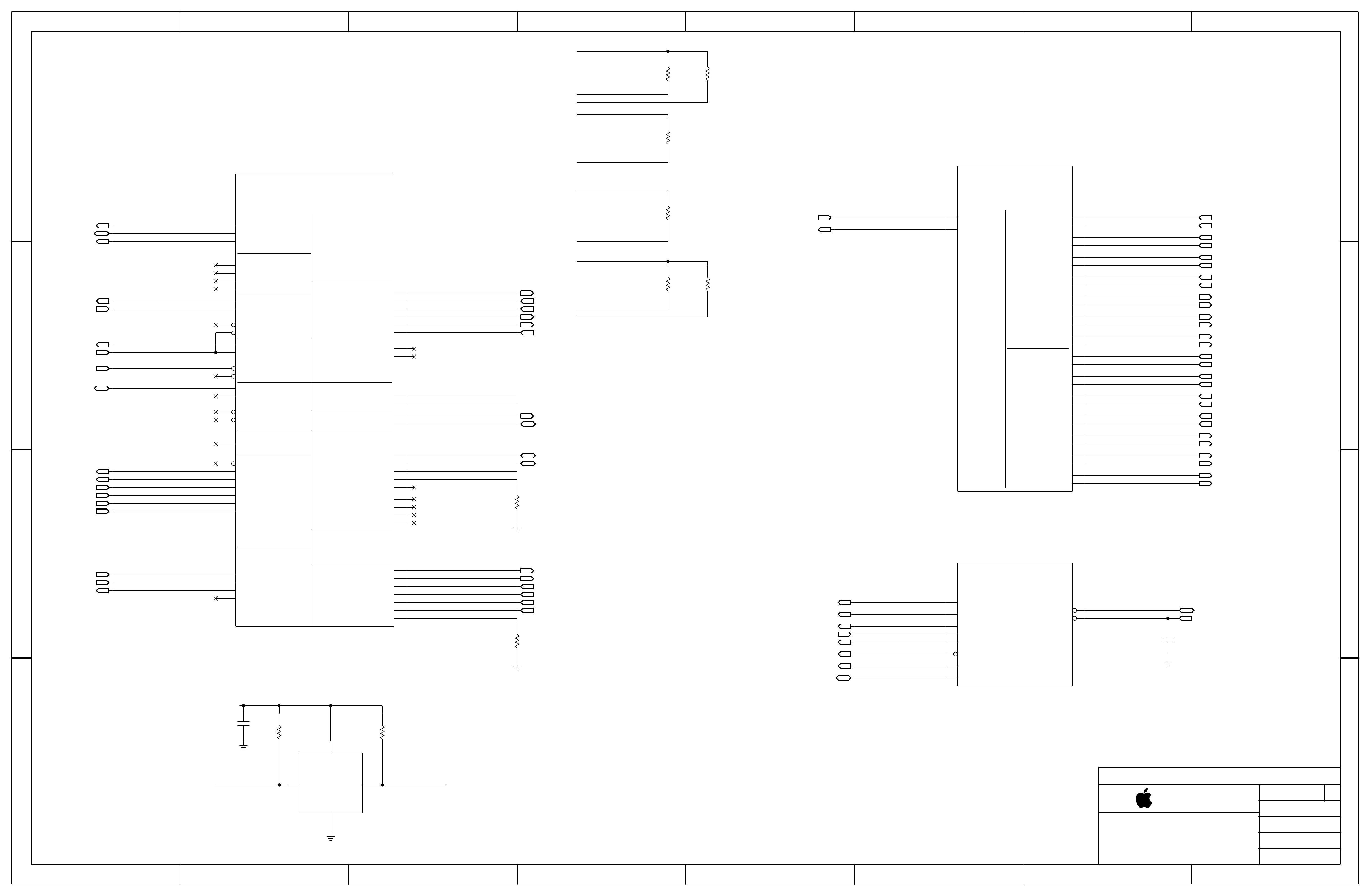

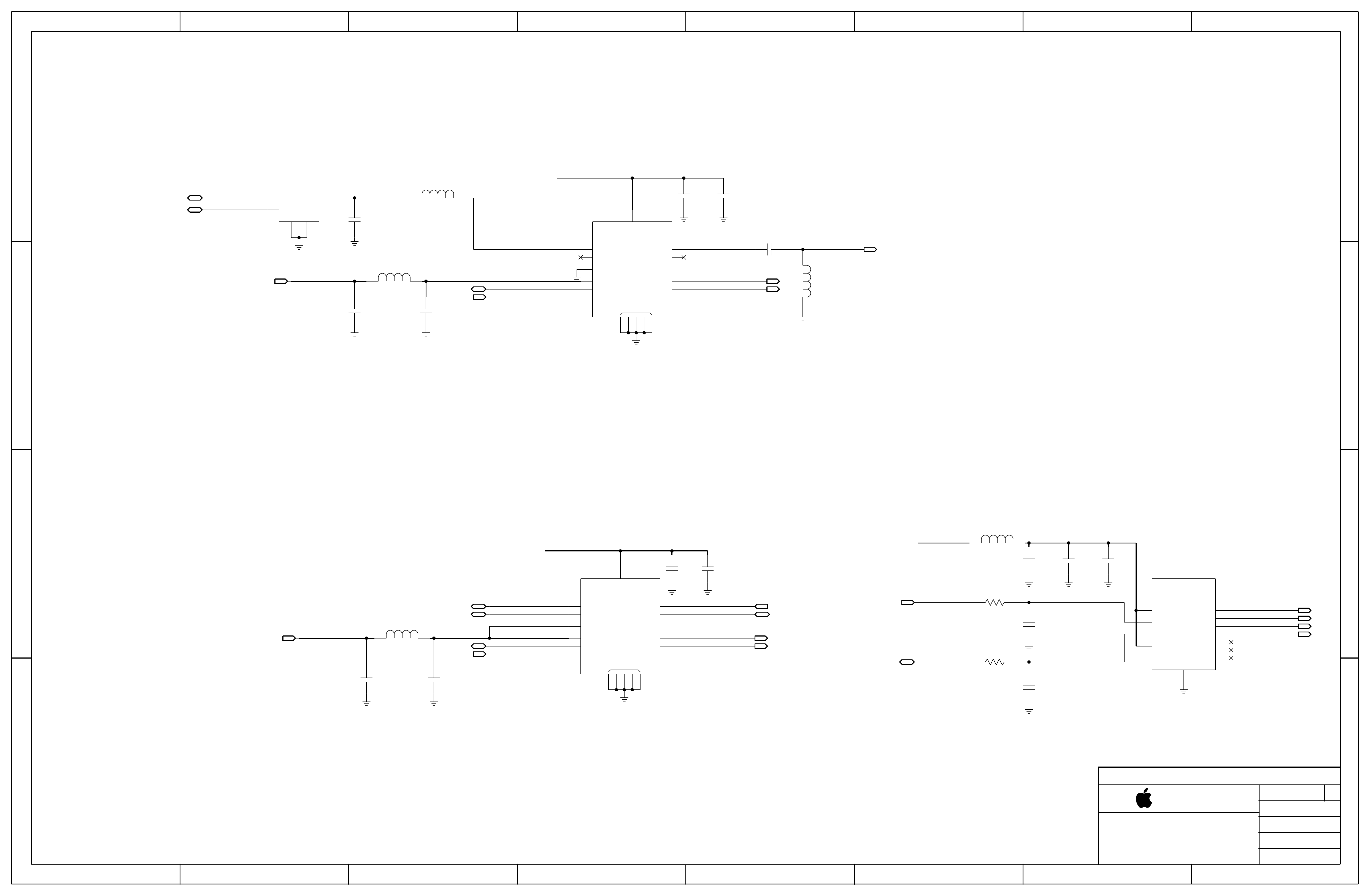

PCB 820-00863-09 X891 Intel Edition TOP MLB

2 1

D

C

B

C4571

XW4570

C4570

C3540

DZ3520

C3510

C3511

FL4202

C4203

C4202

C3520

TP0543

R3530

DZ3530

C3530

R3540

DZ3540

R3520

FL4641

DZ4641

C4633

R4633

DZ4643

FL4643

C4631

C3501

C4614

R4611

C4630

R3370

C3370

FD0402

FD0411

D

FD0401

R3041

J6400

*

FL4003

C3041

R3901

FD0405

R3900

C3906

R3905

C3995

C3950

C3951

R3908

J3900

C3940

C3941

R3907

C3930

C3931

C3960

*

FL3995

C3993

C3925C4303

*

R4330

FL4303

C4322

C4309

C4308

C4304

C4302

J4300

C4330

C4324

R4308

FL4330

C4326

R4309

FL4301

C4301

C4300

C4090

XW4400

C4092

C4091

R4005

C4006

C4050

C4051

J4000

C4040

C4041

C4030

*

C4031

C4093

PP0583

R3042

C3042

PP0503

PP0545

C2790

*

C2802

U3600

PP0514

XW2990

PP0504

*

*

PP0506

PP0582

R3600

*

FD0420

*

*

C2622

*

C2642

C2609

XW2750

XW2790

XW0510

XW1731

SH0400

PP0513

C2627

*

C5130

C5131

PP0505

L2790

*

*

L2800

*

C2801

*

*

XW2991

L5100

C5135

PP0521

C2901

C2914

C5125

PP0500

C2910

C2911

R3074

C5127

C2971

C2970

C3030

C2800

C2981

C2980

SB0400

PP0540

*

R3801

C1194

PP0587

R1194

C1193

PP0530

C1092

PP0531

C1198

PP0550

R1198

C1804

FL6400

R6418

R6416R6421

PP0562

SH0401

PP0516

PP0561

PP0515

PP0512

PP0564

PP0520

R5903

PP0501

DZ5900

C6100

C5900

PP0522

FL5782

L5710

XW3041

L5700

C2740

FL6411

C6411

R6410

C6410

C6400

C6420

C6418

C6416

C6419

C6421

FL6413

C6413

C6472

C6471

C6473

C6470

*

C6494

*

C3304

*

C3302

*

C3303

C6491

C6496

C5785

C5786

C5784

FL5783

C5783

C5782

FL5704

C5704

C5702

FL5702

C6490

C6495

R3202

DZ3300

R3601

C1810

C2652

*

*

**

C1199

C1812C1191

C2745

C1861

*

C1093

FL1092

C1802

C1801

C1803

*

R1880

C1880

C1690

C1702

C1703

C1811

C1090C1095

C1862

U6110

*

C2741

C2742

C2743

C2744

C2723

C2722

C2721

C1763

*

*

C1881

C1691

*

C1764

*

XW0511

*

XW1701

C1706

*

C1708

C1705

*

*

C1711

C1713

*

*

C1720C1722

C1712

*

*

C6112

XW6110

L6110

C6110

*

*

*

R5901

C5902

U6100

R5902

*

C2724

*

L2703

XW2740

*

L2702

*

*

L2701

C2720

*

*

L2741

*

C2760

*

L2721

***

C2762

C2761

PP0502

*

*

*

*

*

*

*

*

PP0541

C2650

C1750

C1773

XW2770

C1710

C1709

C1704

C1707

C6117

*

C3601

C3600

C3602

PP0542

PP0544

C2631 C2603

C1805

*

C1813

C1192

C1760

C1761

*

C1723

C1721

C1794

C6111

R6116

U5900

XW1760

C1762

*

C1772

*

XW1790

C1793

*

C1792

*

C1791

*

XW2730

XW5900

*

C5138

C5124

*

*

C5137

C5139

C2636

C2637

XW3044

*

XW3042

*

XW3045

C2792

*

*

C2791

*

L2730

C2730

*

XW3000

C2732

XW2995

*

L2760

*

C2731

*

C3622

C2605

R3620

C2602

C2630

C2629

C5690

C5641

C5651

C5650

C5691

C5692

C5642

*

C5126C5142

C5128C5129

U3620

C3620

PP0547

C2628

C2600

C2646

C2640

C1863

U2600

XW2800

*

*

C5612

C5621

C5611

*

*

U5100

C2612

C2614

C2620

C5640

L5600

*

C5655

*

*

C5654

C5632

C5631

U5600

CL0400

C2644

C2634

C2606

*

SB0402

*

C2613

C2621

C1781

C2782

C2781

*

*

C2780

*

L2780

C2712

C2715

C2714

*

*

*

*

L2710

C2713

C2711

C2716

*

*

*

*

L2711

*

L2712

C2645C2649

C2632

CL0403

PP0563

PP0560

C2615

C2641

C2611R2600

C2626

C2610C2623

*

C2635

C2601

C2617

C2643

C2651

C2618

C2647 C2624

XW2780

*

C5653

*

*

C5652

C5660

C5645

C5134C5136

C1851

R1500

C1842

R1420

R1421

C1731

C2619

C1730

C1737

*

*

C2710 C1301

C1782

C1396

*

*

C1734

R1300

*

C1390

C1735

C1394

*

C1393

*

C1736 C1738

C1392

C1295

C1296

C1391

**

R1251

C1732

R1250

R1252

*

C1733

C1290

C1291C1860

C1739

C1841

*

*

C1853

C2616

FD0410

C2859

R3070

R3011

C2855

C2854 C2864 C2862

R3330

C2920

R1863

R1241

R1242

R1240

R1243

R1871

R1221

R1202

R1211

C1133

C1132

C1131

C1130

R1222

R1201

C1121

C1123

C1122

R1212

R1231

R1411

R1430

R1232

C1830

*

R2604

C1395

R1862C3071

C2810

L2810

L2811

*

*

C2860

R3010

C2858

*

*

R2601

R3000

C1833

*

C2813

*

C2811

*

C2812

C2863

U2700

C2861

C2703

*

*

L2700

R3020 C2900

C1120

J_INT_BOT

U1000

R1870

R3071

*

C2702

*

C2705

C2700

*

*

C2704

C2706

*

C2701

C3020

C2865

C2909

C2856

C3010

C2866 C2857

C3031

R1431

R1131

C1124

C4815

R1462

C2907

C2906

L2770

*

R3331

*

L2740

*

L2720

C2751

L2750

*

R3332

C2750

*

R3001

Y3000

C3002

*

*

C4125

*

C4126

U4120

*

L4120

*

L4100

*

U4100

C3795

C4101

*

C4102

C3717 C3704

C3800

R3800

C3810

C3750

C3722

R3811

R3803

C3709

FD0403

FD0412

C4410

*

C4421

L4401

C4492

C4596

C4411

C4498

*

C3790

C4554

C4823

FL4554

C4812

C4824

C4825

C4801 C4804

C4821

R1121

R1101

C1832

C1852

C1125

C2772

C2770

C2771

C3343

C3342

C3341

C2913

C3310

*

C2752

R3350

C1840

R1100

R1130

R1400

R1401

R0623

R0620

R0621

C1831

R0622

C1843

C2992

C2850

*

*

*

*

*

L3341

C3045

R3045

*

C3391

C3313

C3312

C3311

*

*

C3315

C3314

*

*

C3301

*

Q3350

C3350

*

C3991C3994C3992C3990C3907C3908 C3996C3900C3901C3961C3928

CL0401

FL3903

FL4306

TP0540

XW3700

*

J4500

FL4555

R4010

R4001

FL4650

R4617

FL4640

XW2760

FL4642

XW4600

DZ4642

DZ4640

C4650

C4617

C4601

C4600

C4618

FL4618

J4600

R4601

R4600

R4619

R4634

C4634

DZ4644

FL4644

R4221

FL4200

C4200

R4220

C4220

C4221

C4201

R4211

J4200

C4205

C4211

C4212

R4210

C4210

R4212

FL6430

R6432

R6431

FL6433PP0546

PP0590

PP0591

R6419

R6420

FL4572

C4572

R4563

C4563

C4564

C4573

C4574

C4575

J4530

C4560

FL5703

C5703

R4560

C5700

FL5700

FL4561

C5701

R5701

C4562

PP0592

R5700

C3553

PP0586

FL3553

J3500

C3551

R3551

C3552

R3552

C3550

FL3550

C6492

C3201

R3201

C3294

*

J3200

XW3200

*

C4613

C4636

C4632

C4635

*

CL0402

*

C3500

*

*

*

C4306

C4307

FL4307

FL4305

C4305

*

DZ4310

C4552

R4552

R4310

C4320

C4556

FL4556

C4310

C4592C4555

C4594

C3909

FL3901

FL4001

C4096

C4017

C4094

R4007

C4010

C4007

C4001

C4000

C4008

C4061

C4060

C4028

R4000

XW4802

FL4619

C4025

Q3700

*

R4003

FL4204

C4204

C6486

C6485

C6484

C6483

*

FL6480

C6480

C6482

FL6482

FL6464

C6464

FL6462

C6462

C6460

FL6460

C6430

C6432

C6431

C6433

FL6450

C6450

FL6454

C6452

FL6452

C6454

C6466

C6465

XW1870

R6465

R6466

*

C6493

XW5785

XW5784

FL5780

FL4574

C5781

*

*

J5700

L5720

* *

L5740

L5730

C6497

C2903

*

C3202

Q3201

Q3200

*

C3352

C3293

XW3370

SB0401

C3353C3292

C3351

*

C4196

*

C4121

C4122

C4191

*

C4192

C4106

C3797

*

C4105

C3718

R3802

*

C3710

C3719

R3810

R4400

C4412

R1861

C2851

*

*

C2852

C3721

C3715

U3700

C4495

C4494

PP0571

PP0570

*

U4400

C4660

C4490

C4496

C4803

C4802

R3072

R4553

U4700

R4800

R4830

R3044

C3044

*

C3190

R1464

R1410

R1450

R1451

R1150

C1102

C1103

C1101

C1100

R1010

R1460

R1465

R0600

R1461

R0601

R1480

C2915

C1870

R1481

R1441

R5108

R1623

R1621

R1620

R1000

R1622

R1860

R1601

C6300

R6300R3061

R6210

C1850

*

C3390

R6211

C6312

C2991

R3360

*

R6200

*

C3316

U3300

*

*

C3796

C3720

*

C3798

R3820

C4593

C4422

C4420

C4553

C4808

*

L3100

C3111

C3113

C1011

Y1000

*

R1011

C1010

R1602

R1440

R1482

R1603

R1604

R1020

L6300

L6301

*

C6330

C6200

C6390

C6210

*

C6292

*

L3340

C3317

C3360

*

C3702

*

C3700

L3700

*

C3701

*

C4497

C4597

C4491

C4405

C4493

*

L4400

C4595

C4401

C4400

R3073

*

C4817

*

*

U6300

C6395

U6200

C3320

C3340

C3361

*

C2763

C4809

C4822

C4805

C4814

C4701

R4710

R4701

C4700

R4700

R4831

C4820

C4811

C4813

*

*

R3110

R3100

*

U3100

C3115

*

C3112

*

C3114

*

C3110

FD0404

R1471

R1470

C1490

*

U1490

*

C6391

C6311

C6290

C6291

*

R3316

*

C2990

C3324

C3325

C3323

***

*

C3322

C3305

C3308

C3307

*

*

C3306

R3062

*

C

B

A

8

TOP SIDE ASSEMBLY

3

APPLE

THIS IS THE PROPERTY OF APPLE AND IT MUST BE RETURNED

ORIG DIV

NOTES:

ARTWORK VIEWED FROM COMPONENT SIDE. PCB SHALL CONFORM

TO STANDARDS AS DEFINED IN APPLE SPECIFICATION

080-2265 (FLEXIBLE PRINTED CIRCUIT BOARDS) OR

062-0073 (MULTI- LAYER BOARDS) AS APPLICABLE.

DESIGNER

KEN KIPLINGER

DATE

03/31/17

SCALE

1:1

TITLE

PCBF, X891

TOP MLB

DRAWING NUMBER

820-00863-09

NOTICE OF PROPRIETARY PROPERTY

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE

THE POSSESSOR AGREES TO THE FOLLOWING

(I) TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

(II) NOT TO REPRODUCE OR COPY IT

(III) NOT TO REVEAL OR PUBLISH IT

124567

A

8

7

6 5 4 3

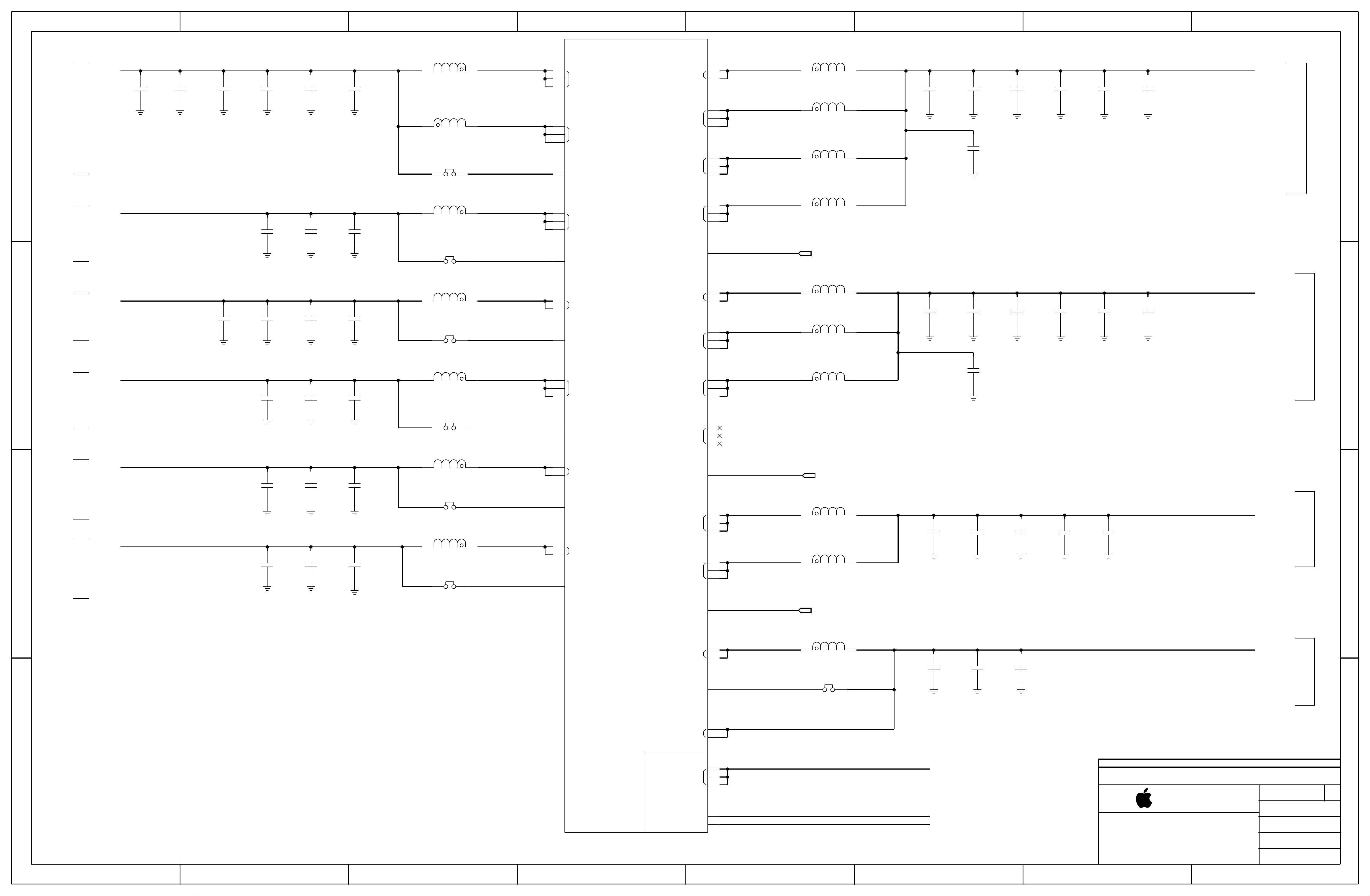

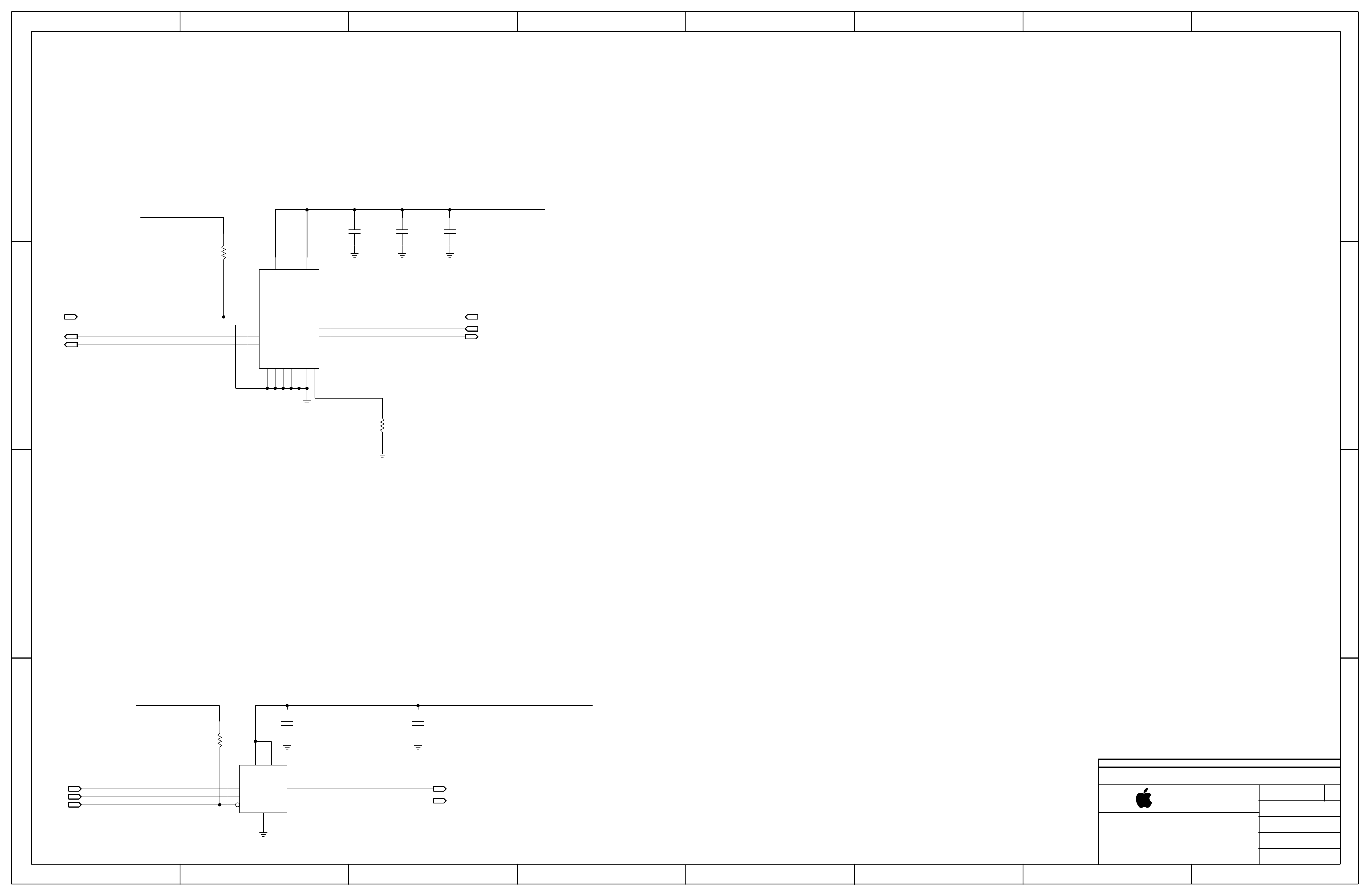

1. ALL INFORMATION COMPILED FOR USERS OF FORUM HTTP://WWW.MOBILEGSM.IN.UA

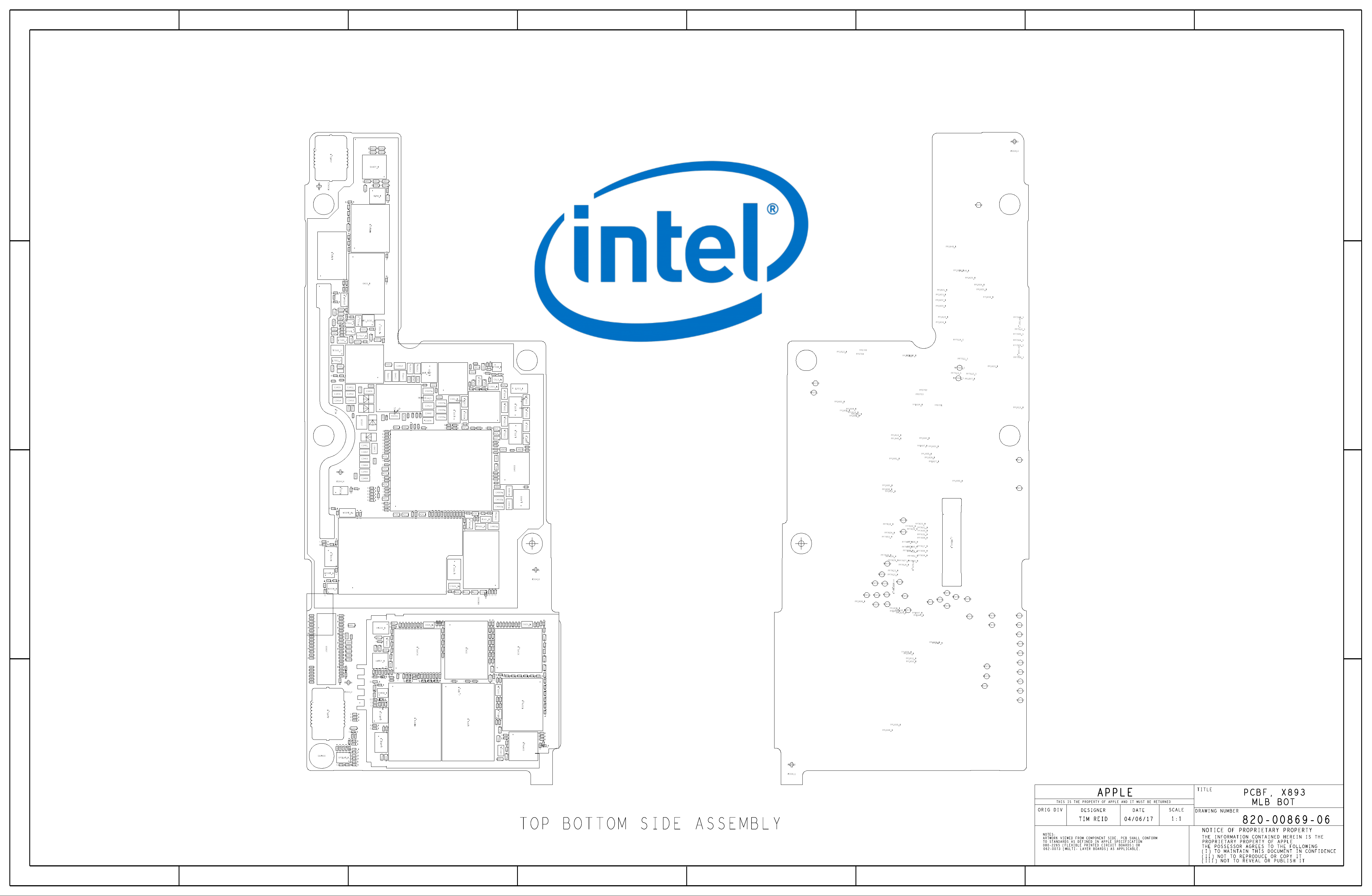

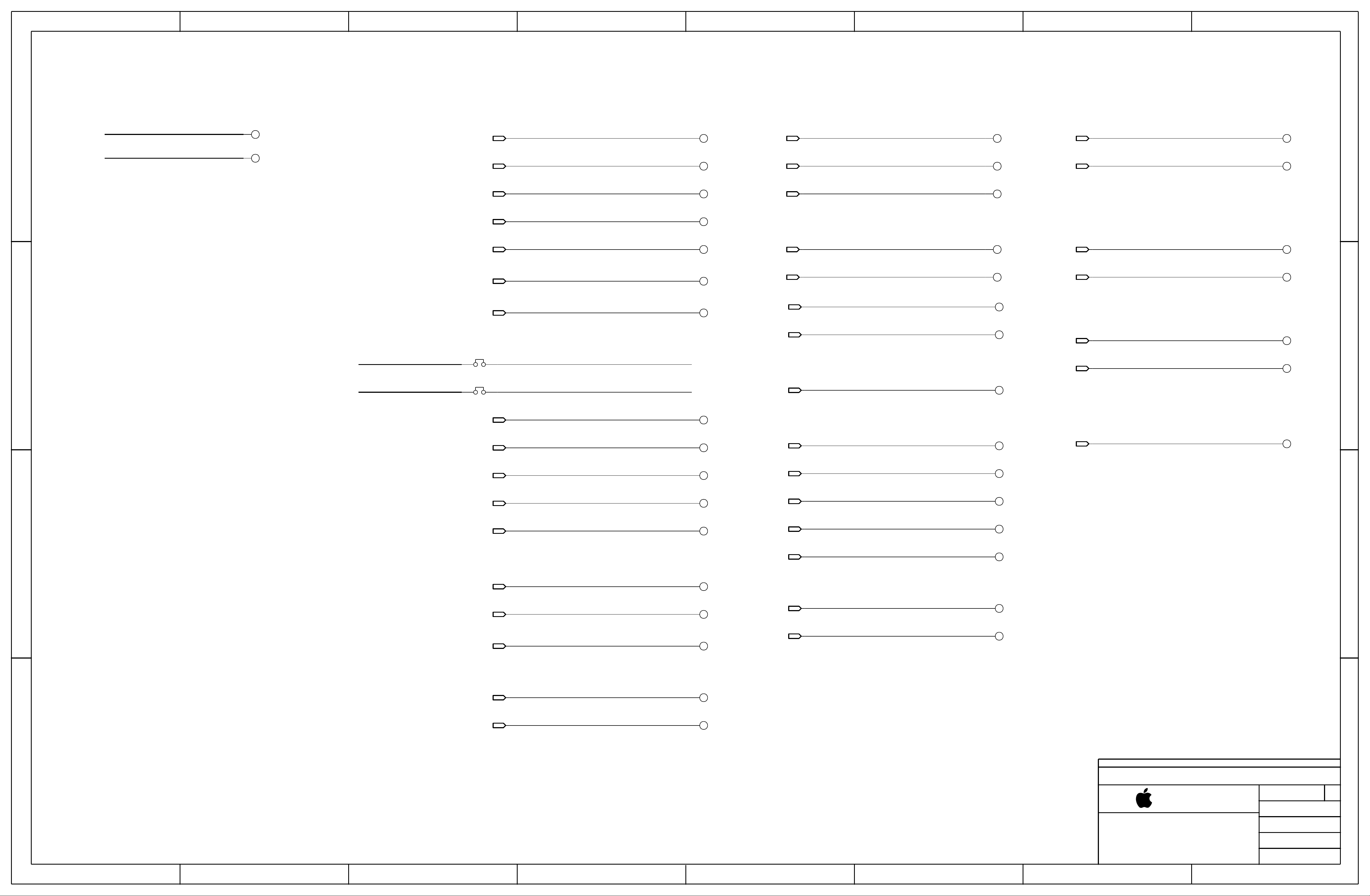

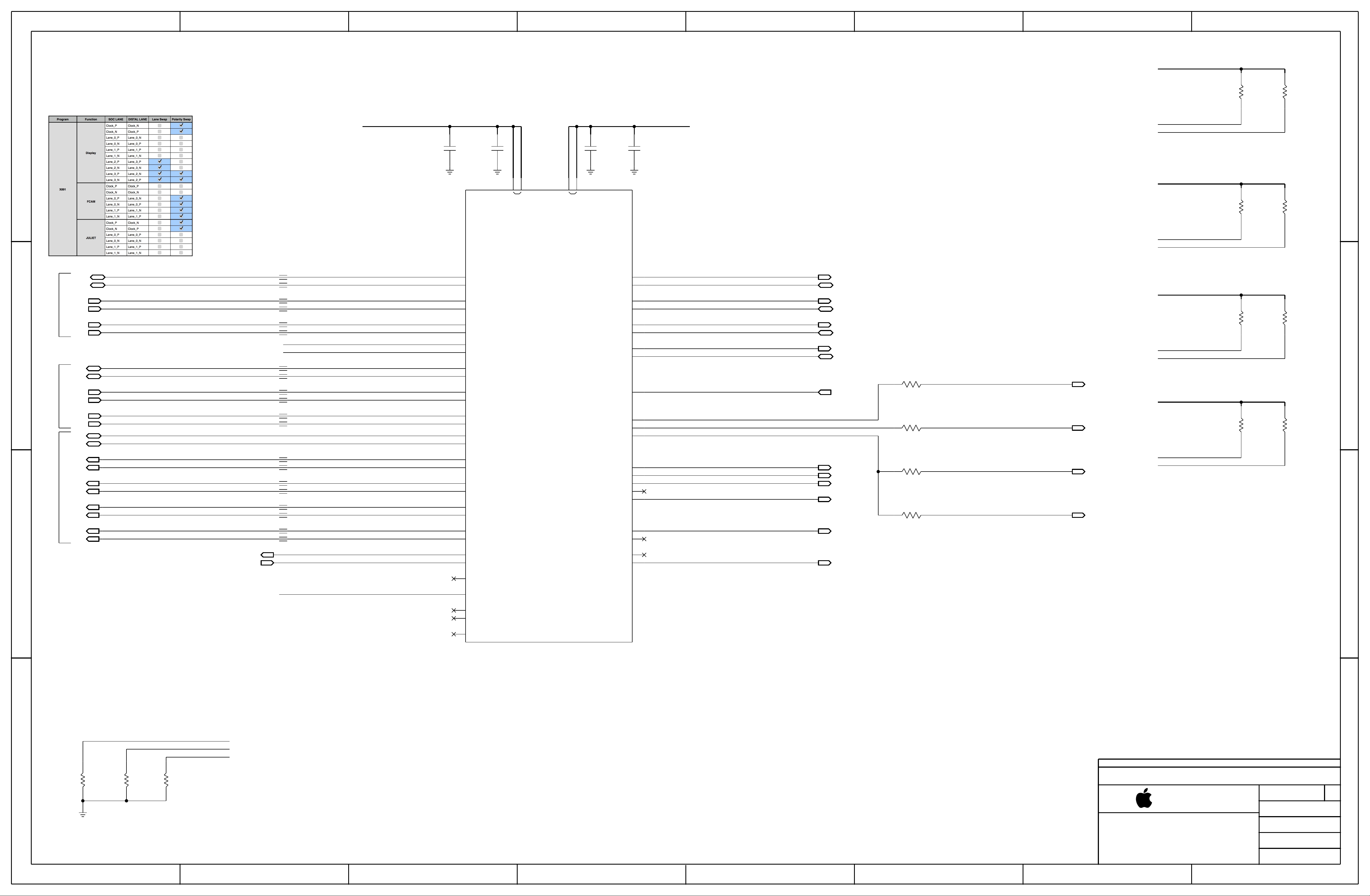

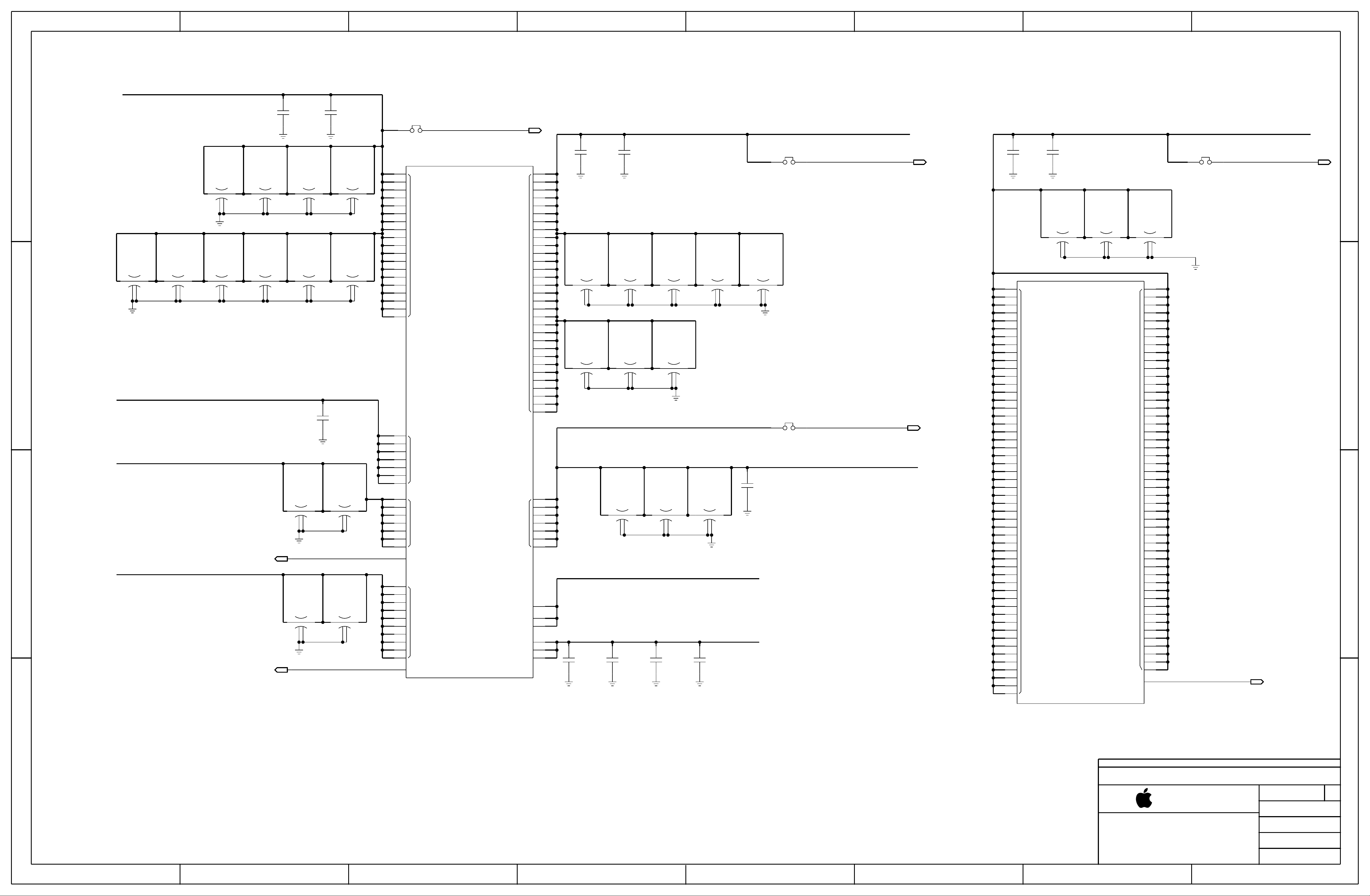

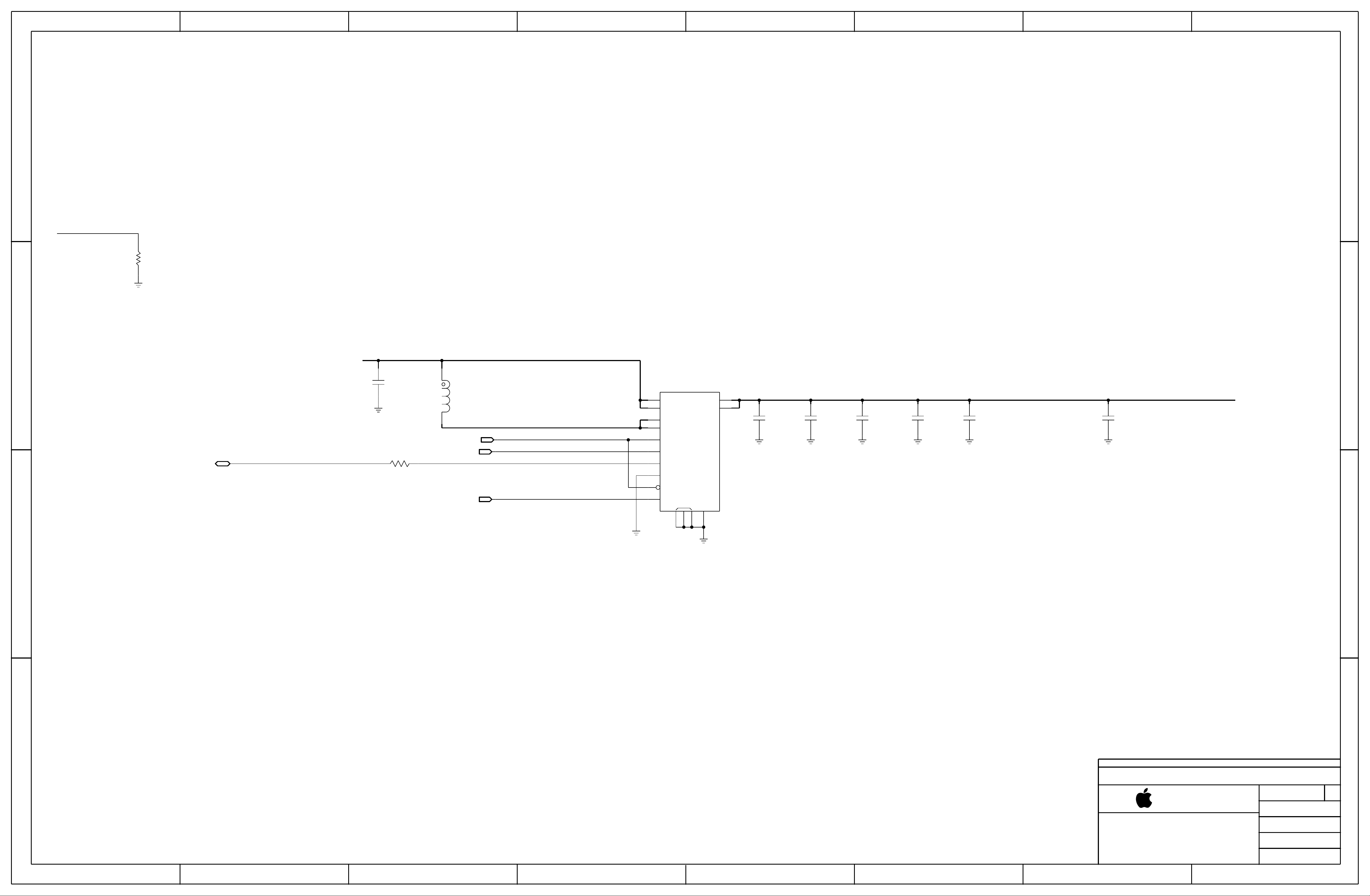

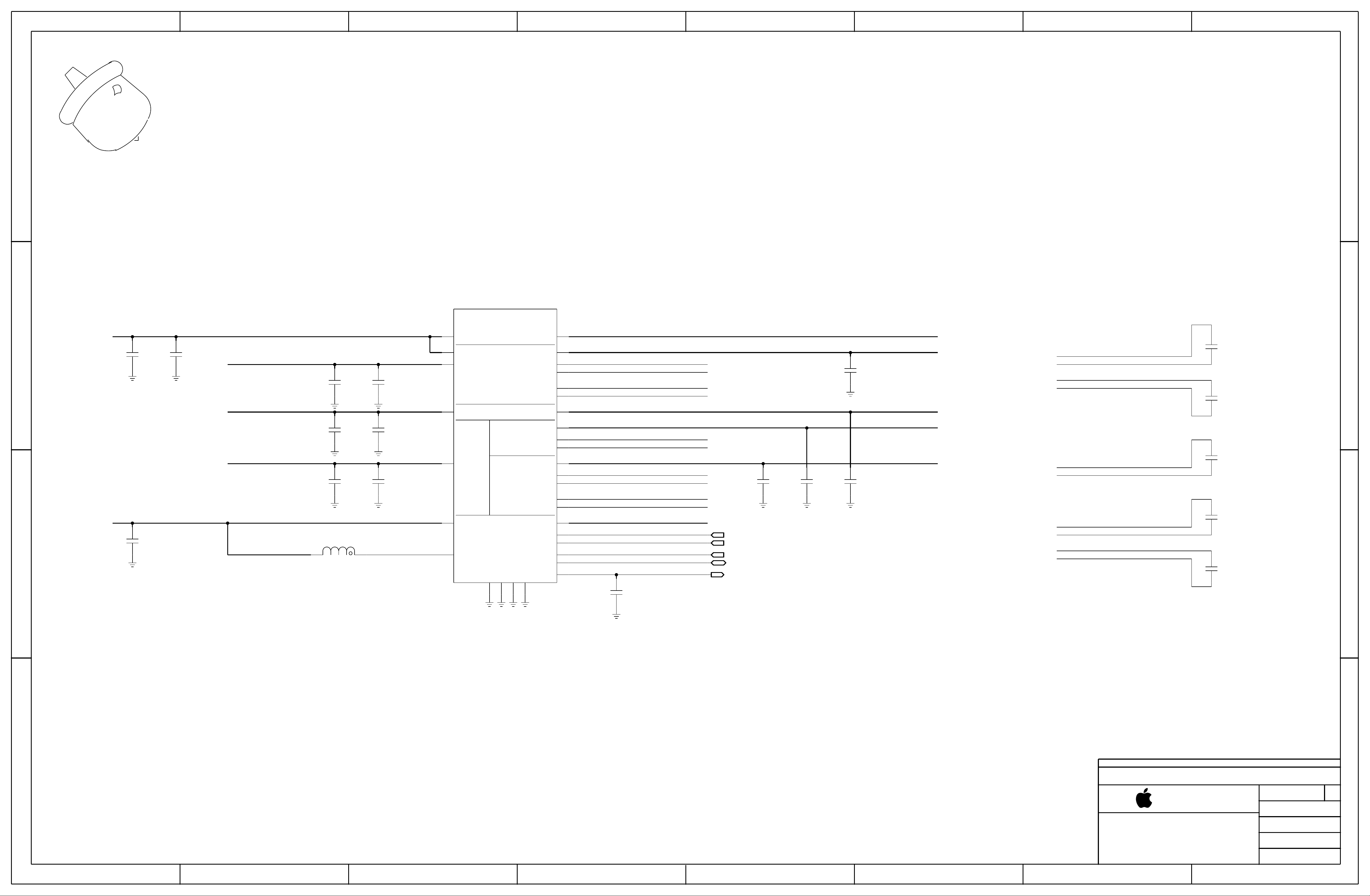

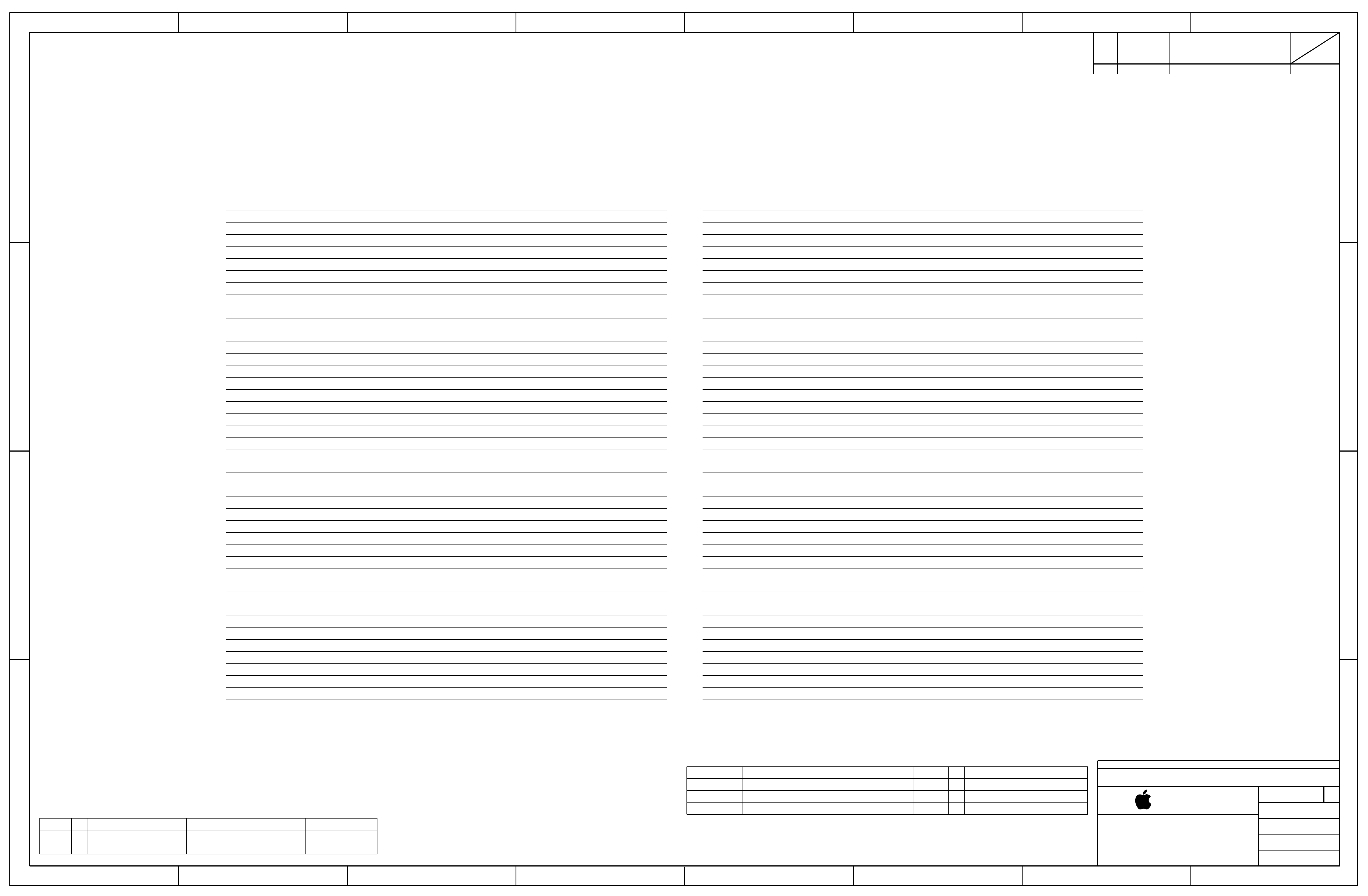

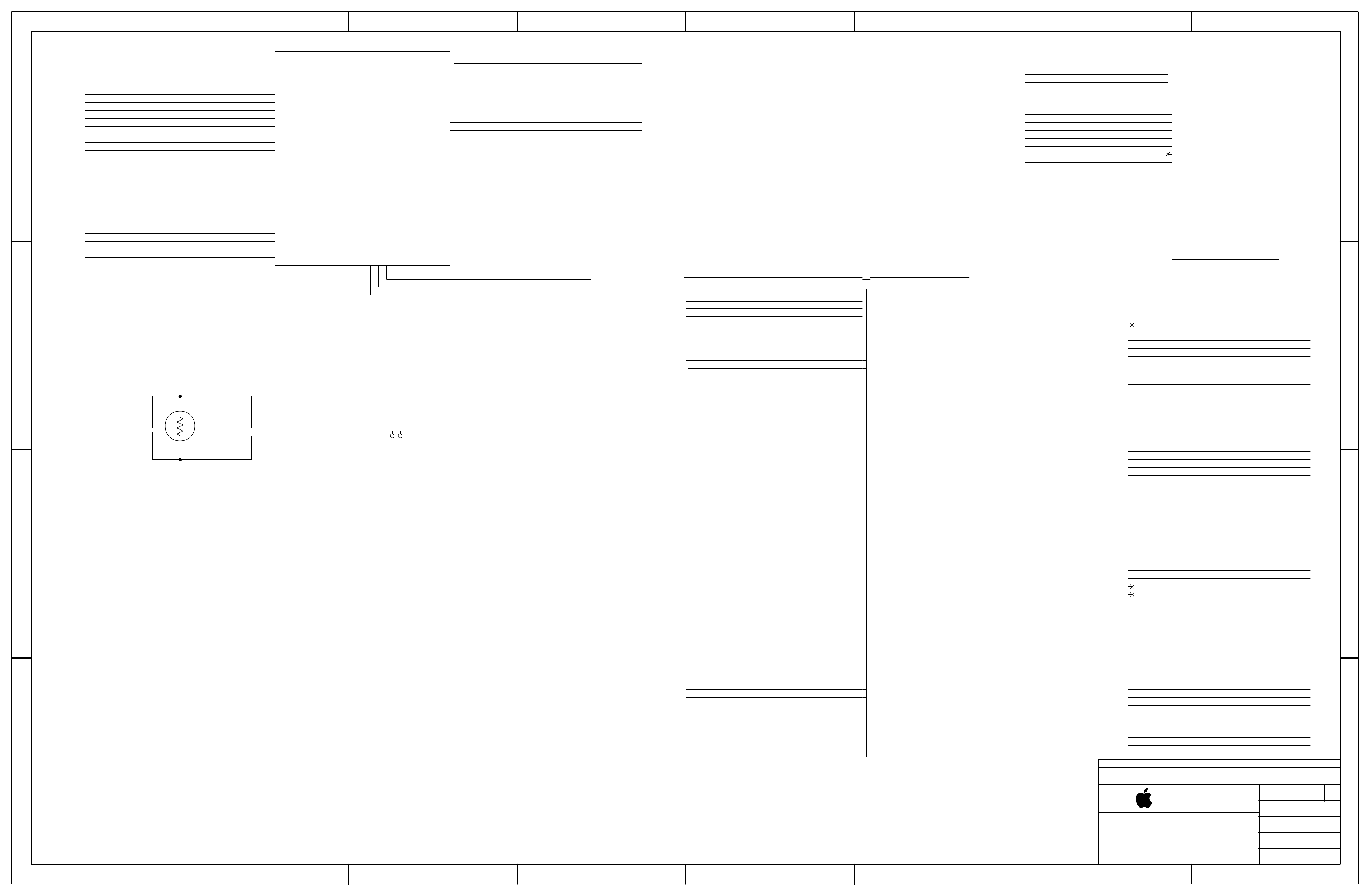

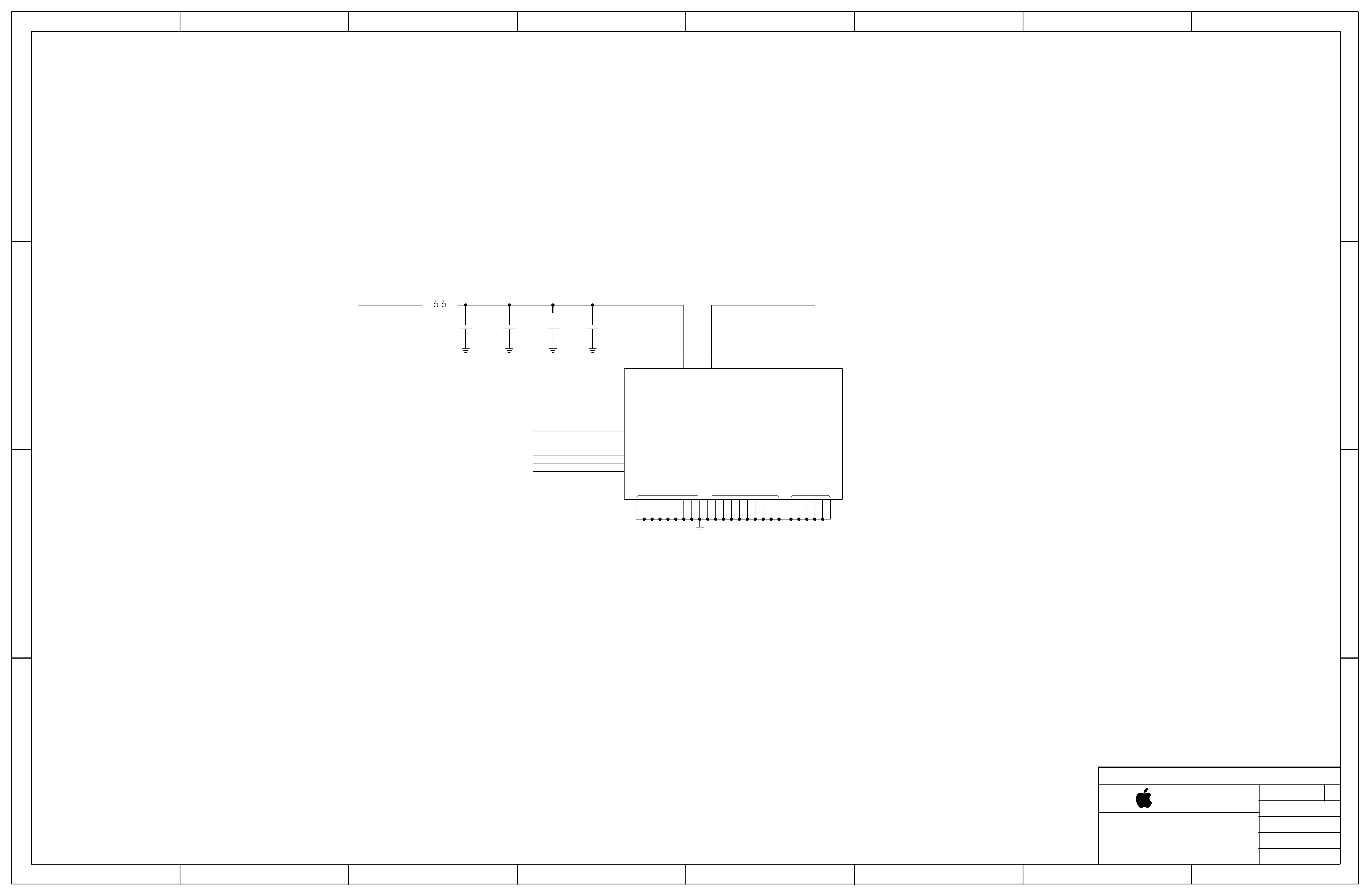

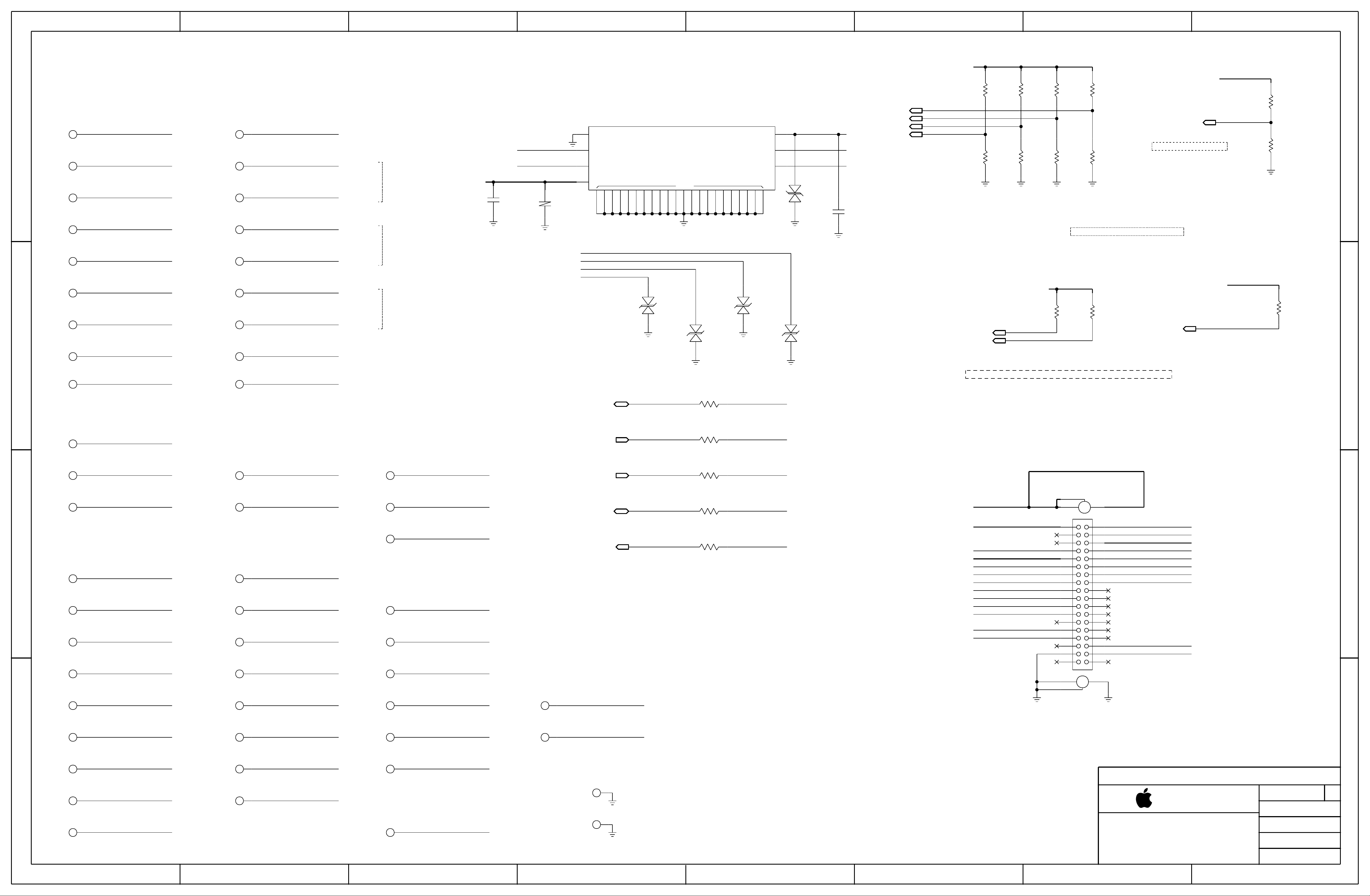

PCB 820-00869-06 X893 Intel Edition TOP MLB

2 1

D

C

B

A

R5807

C5807

FL5806

C5806

FL5800

C5800

FL5805

C5805

C5844

R5844

C5845

FL5845

R5845

C5850

FL5850

C5842

R5842

C5820

R5820

C5821

R5821

*

L1401_K

GNSS_K

NFC_DCDC_S

R3450

D3400

D3401

U5530

C3461

C3462

C3463

C3464

C3465

C3466

C7711_W

L1404_KL1405_K

C1403_KC1404_K

QUADP_K

*

L1402_K

C1401_K

R1404_KR1403_K

*

R1402_K

C7522_S

*

C3406

MHBLN_K

*

L7503_S

C3404

GLNA_K

*

C7523_S

C1503_K

L1501_K

R1302_K

R1303_K

L7502_S

*

C7521_S

C7502_S

*

C3441

U3400

*

*

C3445

C3405

D3403

R208_K

R1616_K

R1617_K

R1613_K

R1614_K

R1615_K

R1608_K

R1609_K

R401_K

C401_K

C429_K

C420_K

C3407

C440_K

C433_K

R400_K

R3406

C300_K

C425_K

C423_K

C427_K

C418_K

C414_K

C406_K

C412_K

C407_K

C402_K

R202_KR201_K

R1607_K

R200_K

R300_K

D3402

UWLAN_W

*

R605_K

VTCXO_K

*

FL601_K

R602_K

*

*

C606_K

*

C640_K

C641_K

C639_K

UATCP_K

*

*

*

L902_K

L903_K

*

C1108_K

C1104_K

C1106_K

C909_K

C1112_K

FL1101_K

R3043

DZ1608_K

DZ1605_K

C1107_K

C1105_K

R1100_K

C1100_K

C3043

C1600_K

*

GSMDI_K

DZ1600_K

*

*

L1014_K

DZ1607_K

*

C1111_K

C1109_K

FL1100_K

LATCP_K

*

*

L901_K

C902_K

*

LATDI_K

L900_K

C901_K

C600_K

R3401

*

C609_K

C608_K

C441_K

C436_K

C601_K

C617_KC612_K

C613_K

C908_K

*

XW3400

XW3401

TP0790

PP1648_K

PP1618_K

PP1658_K

PP1625_K

PP1604_K

PP1657_K

TP0780

PP7512_S

TP0753

PP1655_K

PP1656_K

PP1633_K

TP0706

TP0707

TP0759

TP0756

TP0757

PP1621_K

PP1623_K

PP1622_K

PP1620_K

PP1619_K

PP1624_K

PP7514_S

PP1609_K

PP1610_K

PP1642_K

PP1641_K

PP0704

PP1608_K

PP0700

TP0703

TP0755

PP1635_K

PP1611_K

PP0702

PP0703

PP1634_K

PP1614_K

PP1640_K

PP1607_K

PP1661_K

PP1605_K

PP1606_K

PP1615_K

TP0708

TP0713

PP7627_W

PP7618_W

TP0710

PP7607_W

PP7605_W

PP7608_W

PP1654_K

PP7622_W

TP0750

PP1653_K

PP1651_K

PP1652_K

PP7620_W

PP7626_W

PP7600_W

PP7611_W

PP7601_W

PP7610_W

PP7625_W

PP1647_K

PP1646_K

PP7623_W

PP7621_W

PP7630_W

PP7631_W

PP7609_W

PP7617_W

PP7606_W

PP7604_W

PP7616_W

PP7624_W

PP7603_W

PP7619_W

PP7628_W

PP7629_W

TP0709

PP7613_W

TP0702

PP7612_W

PP7615_W

TP0705

PP7614_W

TP0701

TP0700

TP0714TP0715

TP0751

PP1631_K

PP1630_K

PP1632_K

PP1629_K

PP1650_K

PP1649_K

PP1643_K

PP1600_K

PP1628_K

TP0754

PP1603_K

PP1627_K

PP1616_K

PP0701

TP0761

PP1617_K

*

TP0752

TP0763

PP7511_S

TP7505_S

PP7513_S

TP7506_S

PP1660_K

J_DEBUG_K

TP0764

PP1612_K

*

*

C3412

C5027

C3411

C3440

C3418

*

R3422

C3417

C400_K

R1604_K

*

C5026

J_INT_TOP

L5000

C5029

*

C5011

U5000

*

C5012

*

C5024

*

C5008

*

C5006

R1610_K

C201_K

C501_K

C434_K

C426_K

*

L502_K

C3419

C3416

R3407

C5025

XW3402

C3415

C3413

*

C3442

C3443

C3444

R3408

*

C5028

C417_K

R3420

R3421

U_BB_K

*

C611_K

R601_K

L1008_K

R604_K

*

L1030_K

C603_K

*

L1004_K

L1010_K

L1001_K

*

C405_K

C602_K

R7600_W

R614_K

*

MHBPA_K

C416_K

*

C605_K

XCVR0_K

L1012_K

C614_K

C610_K

L1027_K

C604_K

R1000_K

L1009_K

L1006_K

C430_K

L1003_K

L1013_K

C7603_W

XW600_K

*

*

L1007_K

C7600_W

C616_K

*

L1011_K

C7601_W

C645_K

L1005_K

C432_K

C907_K

C615_K

R603_KR606_KC620_KC649_K

R1605_K

C7606_W

*

R1606_K

C7604_W

*

C905_K

R1611_K

C7609_W

R1612_K

*

L7600_W

*

C411_K

*

C607_K

*

C619_K

XW503_K

R1602_K

*

J_SIM_K

C511_K

C517_K

R1603_K

*

C7611_W

C906_KC900_K

R5001

C5016

C5015

C5018

C518_K

C516_K

C5019

**

C508_K

C523_KC509_K

XW500_K

C522_K

BBPMU_K

C503_K

*

C439_KC419_K

R205_K

C410_K

C438_K

R1601_K

C435_K

C424_K

R1600_K

*

C7602_W

*

C7608_W

C7607_W

*

C7612_WC720_K

XW3043

DSM_K

LBPA_K

EPROM_K

R0630

R203_K

R501_K

C200_K

R209_K

R204_K

R207_K

C510_K

C505_K

C404_K

C413_K

C415_K

C437_K

C428_K

C403_K

R206_K

C409_K

C301_K

C431_K

C422_K

C4927

C408_K

*

C507_K

C4905

ET_K

C722_K

C721_K

XW701_K

R1200_K

C1200_KR1202_K

C1202_K

C635_KR609_K

C638_K

C627_K

FL600_K

*

C513_K

C4928

R1201_KC1201_K

C637_K

C1204_KC1203_K

C628_K

R610_K

C632_K

C512_K

C4914

C421_K

C4904

C4932

C4903

*

C4931

*

C723_K

L1016_K

*

C903_K

L800_K

*

*

*

*

*

C626_K

R600_K

*

C809_K

C804_K

C519_K

C4926

C625_K

SWTX1_K

C904_K

C813_K

R800_K

*

C631_K

C630_K

C810_K

C806_K

C812_K

L803_K

*

C803_K

*

*

*

*

C1001_K

C520_K

*

*

C506_K

*

C504_KC521_K

*

*

R607_K

C622_K

C805_K

C807_K

C811_K

C4925

C4909

*

C4907

*

L1021_K

C621_K

*

L503_K

XW504_K

C500_K

XW501_K

L500_K

*

C514_K

*

C515_K

L501_K

C502_K

XW502_K

C4934

C4929

C4922

U4900

C4930

L4900

*

FD0401

FD0410

*

C623_K

*

*

C624_K

L1023_K

C629_K

R616_K

XCVR1_K

* *

L1000_K

TDDPA_K

GSMPA_K

*

L1024_K

*

L1017_K

C634_K

C636_K

R801_K

C801_K

C815_K

*

*

XW800_K

C808_K

R615_K

C5945_K

C633_K

*

C642_K

C650_K

DZ1609_K

*

C644_K

*

C643_K

DZ1606_K

*

*

*

C800_K

L1015_K

L1018_KL1019_K

L1020_KL1025_KL1026_K

FD0402

FD0411

TP0720

TP0721

PP1602_K

PP1601_K

*

JUAT1_K

FD0406

FD0415

L1700_K

L1701_KC1305_KC1304_KL1300_K

*

C1306_K

C1302_K

*

C1303_K

C1406_K

C7515_S

C7533_S

C7532_S

C7531_S

C7530_S

L7500_S

C7504_S

MC_K

FD0405

FD0414

C7709_W

R7700_W

C7701_W

*

FL5809

C5809

FL5810

C5810

FL5802

C5802

FL5895

C5895

C5804

FL5804

C5803

FL5803

C5891

C5896

C5894

C5893

C5847

FL5847

C5892

C5840

C5841

C1707_K

GPOLAT_K

C1101_K

*

R1406_K

R1405_K

C1402_K

C1405_K

*

GPOUAT_K

C1407_K

R1500_K

*

FL1400_K

Q7502_S

*

Q7501_S

C7526_S

C7506_S

C7511_S

*

C7520_S

C7517_S

C7503_S

*

*

*

NFC_S

C5000

C3451

C3452

C3453

*

*

C3403

C3402

*

C5530

R3460

R302_K

C303_K

TCXO_K

*

W5BPF_W

*

R7711_W

*

C1601_K

C5860

R5801

C5890

FL5890

FL5896

FL5894

FL5893

*

FL5891

FL5840

FD0404

FL5841

FD0412

*

C7712_W

R7701_W

C7703_W

L1100_K

C1103_K

*

C1706_K

C1705_K

C1703_K

L1703_K

*

C1704_K

FL1102_K

*

C1114_K

L1702_K

C1711_K

C1710_K

C1708_K

C1115_K

*

C1116_K

*

C1102_K

R1102_K

R1101_K

LBLN_K

*

*

C1700_K

R1700_K

C1701_K

C7507_S

C7518_S

C7516_S

R7508_S

C7512_S

C7514_S

C7510_S

T7500_S

L7501_S

C7505_S

C7513_S

R7502_S

C5001

C3455

C3456

C3454

*

*

R7702_W

C7708_W

*

*

C7705_W

L7704_W

*

W25DI_W

W2BPF_W

*

L7700_WL7701_W

W2XSW_W

R7703_W

*

C7716_W

*

J5800

*

JLAT1_K

*

SB0400

FD0403

FD0413

PP7508_S

PP7510_S

PP7505_S

PP7504_S

PP7503_S

PP7509_S

PP1613_K

TP0730

TP0731

TP0522

TP0515

TP0768

PP7507_S

PP7506_S

TP0766

TP0760

TP0762

TP0758

TP0771

TP0772

TP0767

D

C

B

A

8

TOP SIDE ASSEMBLY

3

APPLE

THIS IS THE PROPERTY OF APPLE AND IT MUST BE RETURNED

ORIG DIV

NOTES:

ARTWORK VIEWED FROM COMPONENT SIDE. PCB SHALL CONFORM

TO STANDARDS AS DEFINED IN APPLE SPECIFICATION

080-2265 (FLEXIBLE PRINTED CIRCUIT BOARDS) OR

062-0073 (MULTI- LAYER BOARDS) AS APPLICABLE.

DESIGNER

TIM REID

DATE

04/06/17

SCALE

1:1

TITLE

PCBF, X893

MLB BOT

DRAWING NUMBER

820-00869-06

NOTICE OF PROPRIETARY PROPERTY

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE

THE POSSESSOR AGREES TO THE FOLLOWING

(I) TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

(II) NOT TO REPRODUCE OR COPY IT

(III) NOT TO REVEAL OR PUBLISH IT

124567

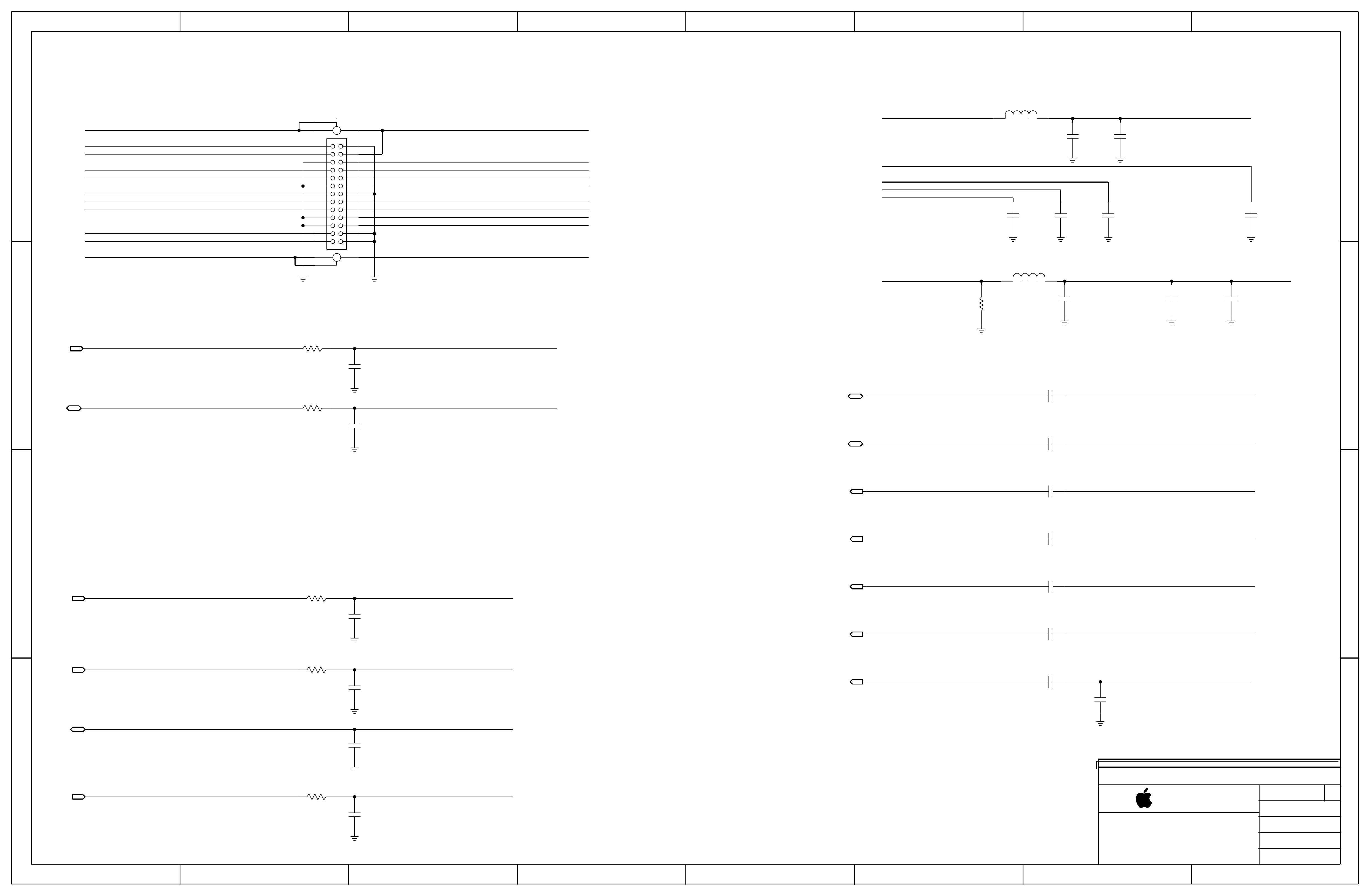

8

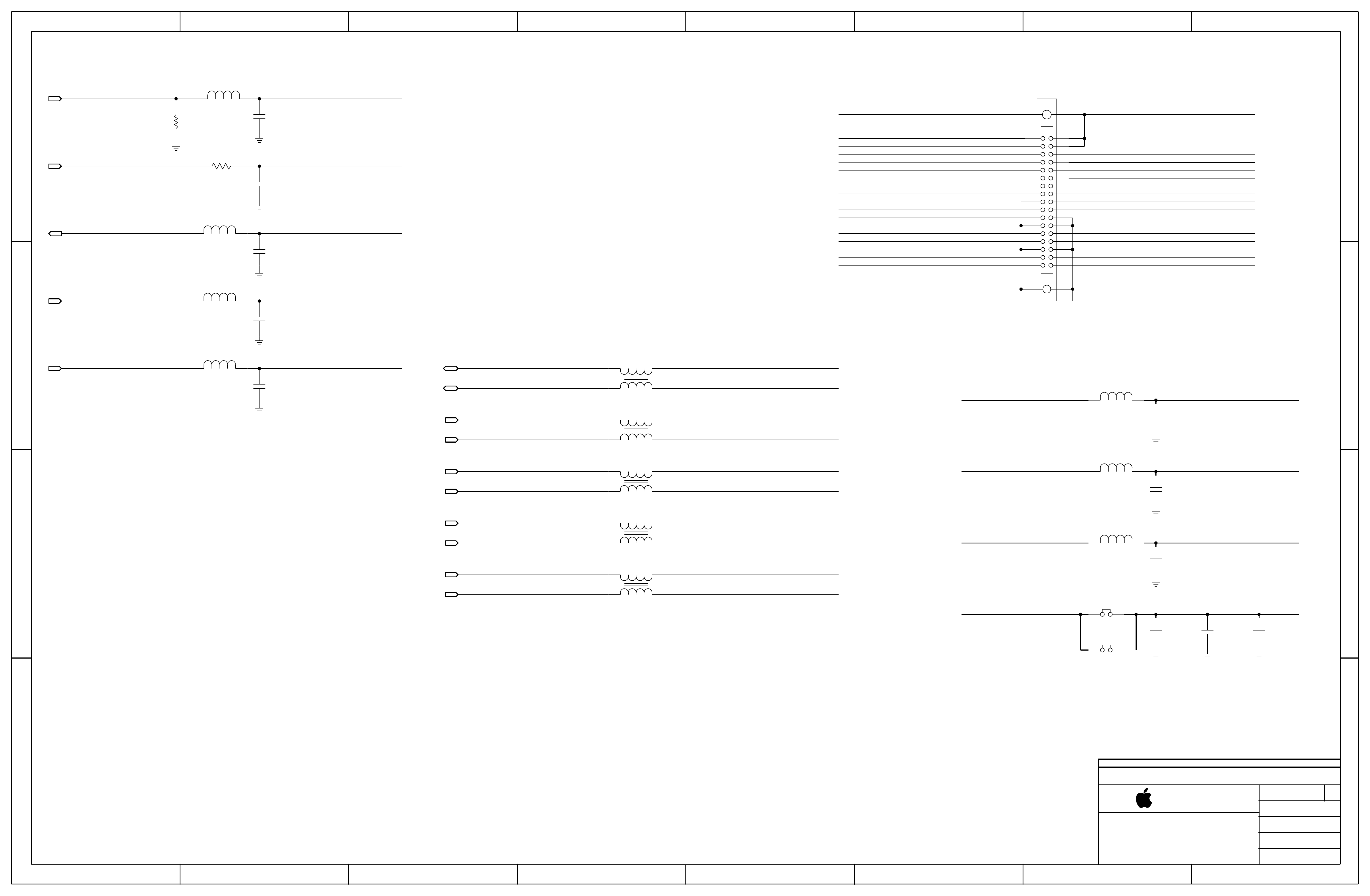

1. ALL RESISTANCE VALUES ARE IN OHMS, 0.1 WATT +/- 5%.

2. ALL CAPACITANCE VALUES ARE IN MICROFARADS.

3. ALL CRYSTALS & OSCILLATOR VALUES ARE IN HERTZ.

7

6 5 4 3

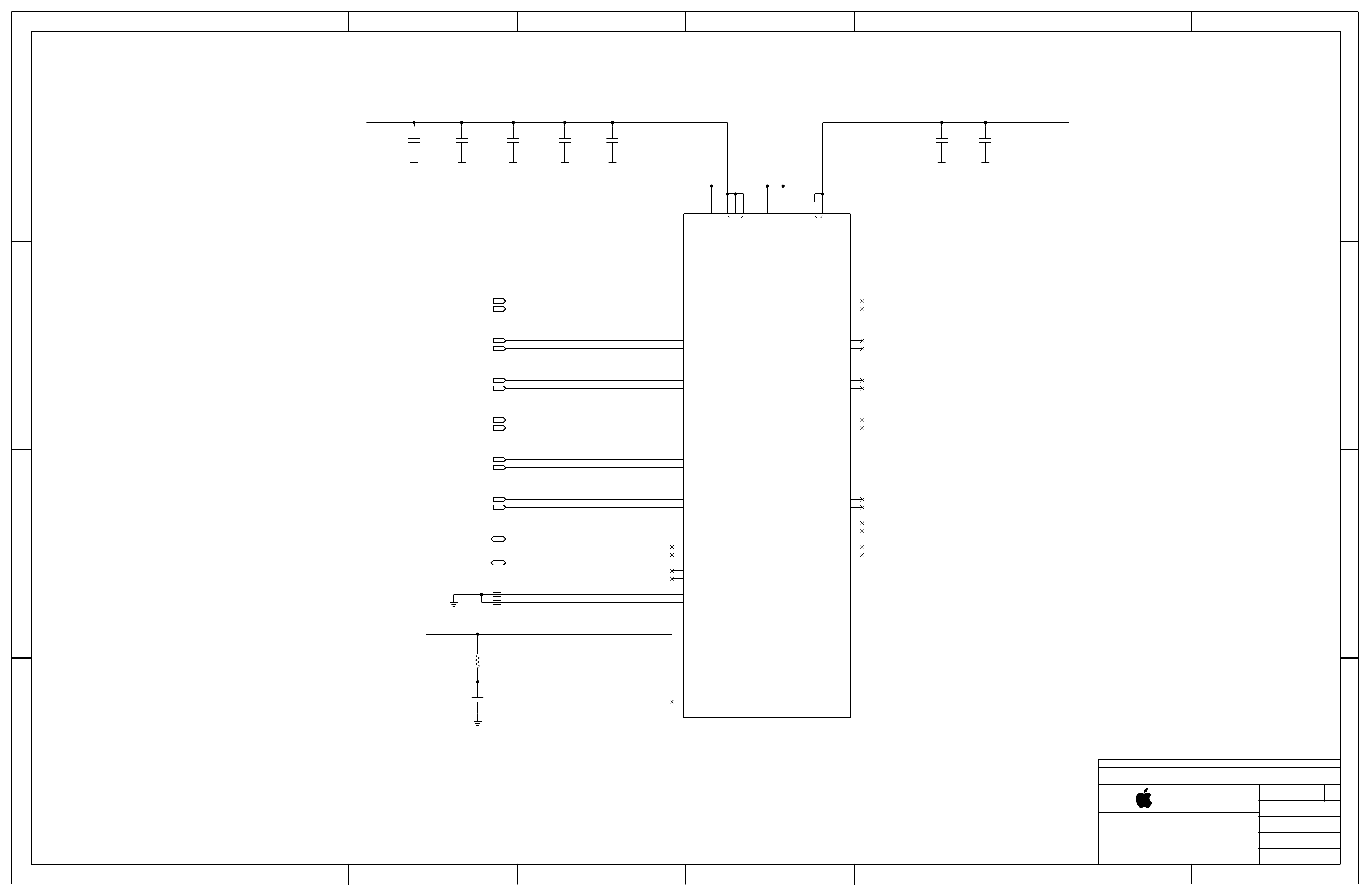

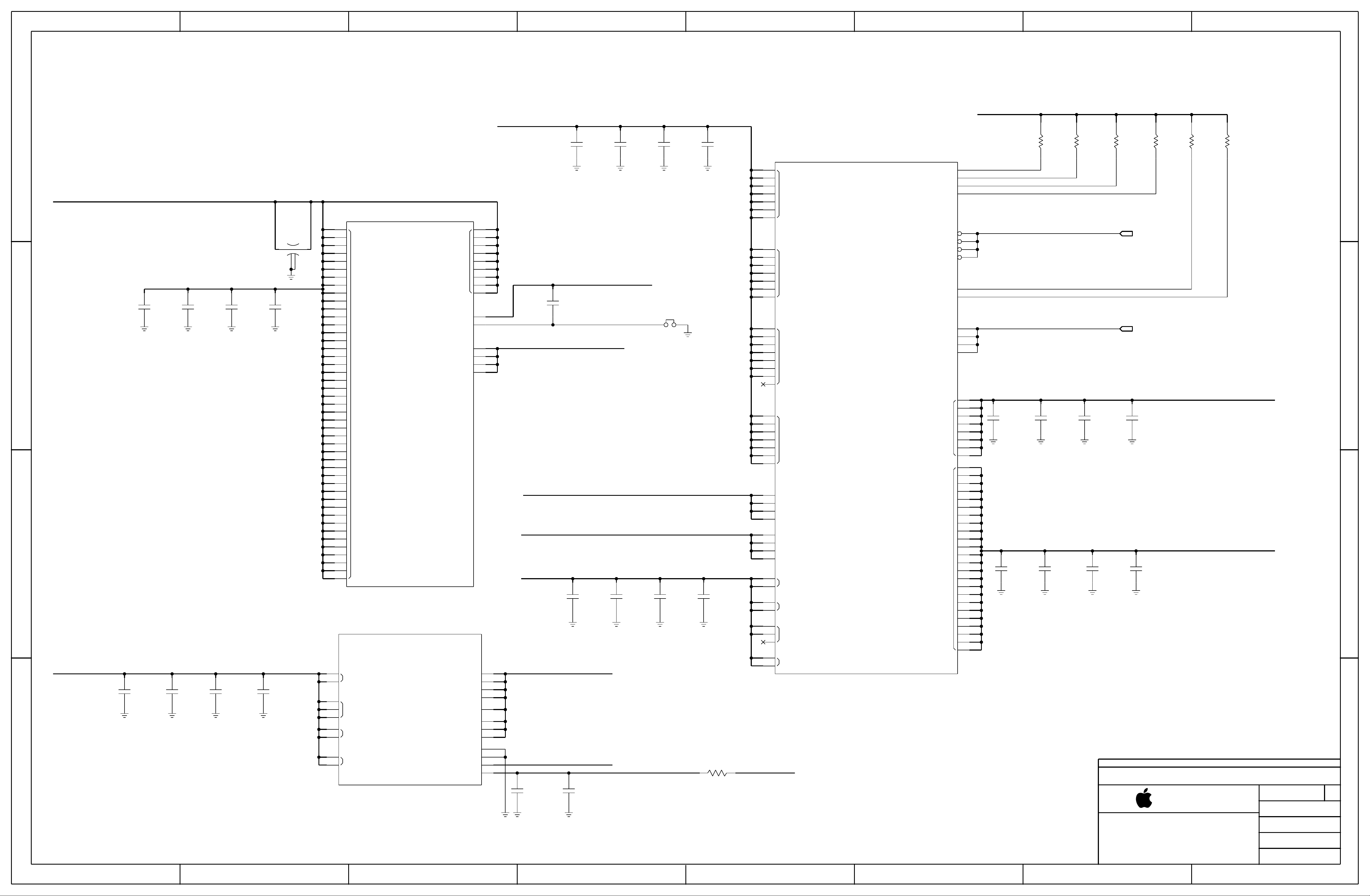

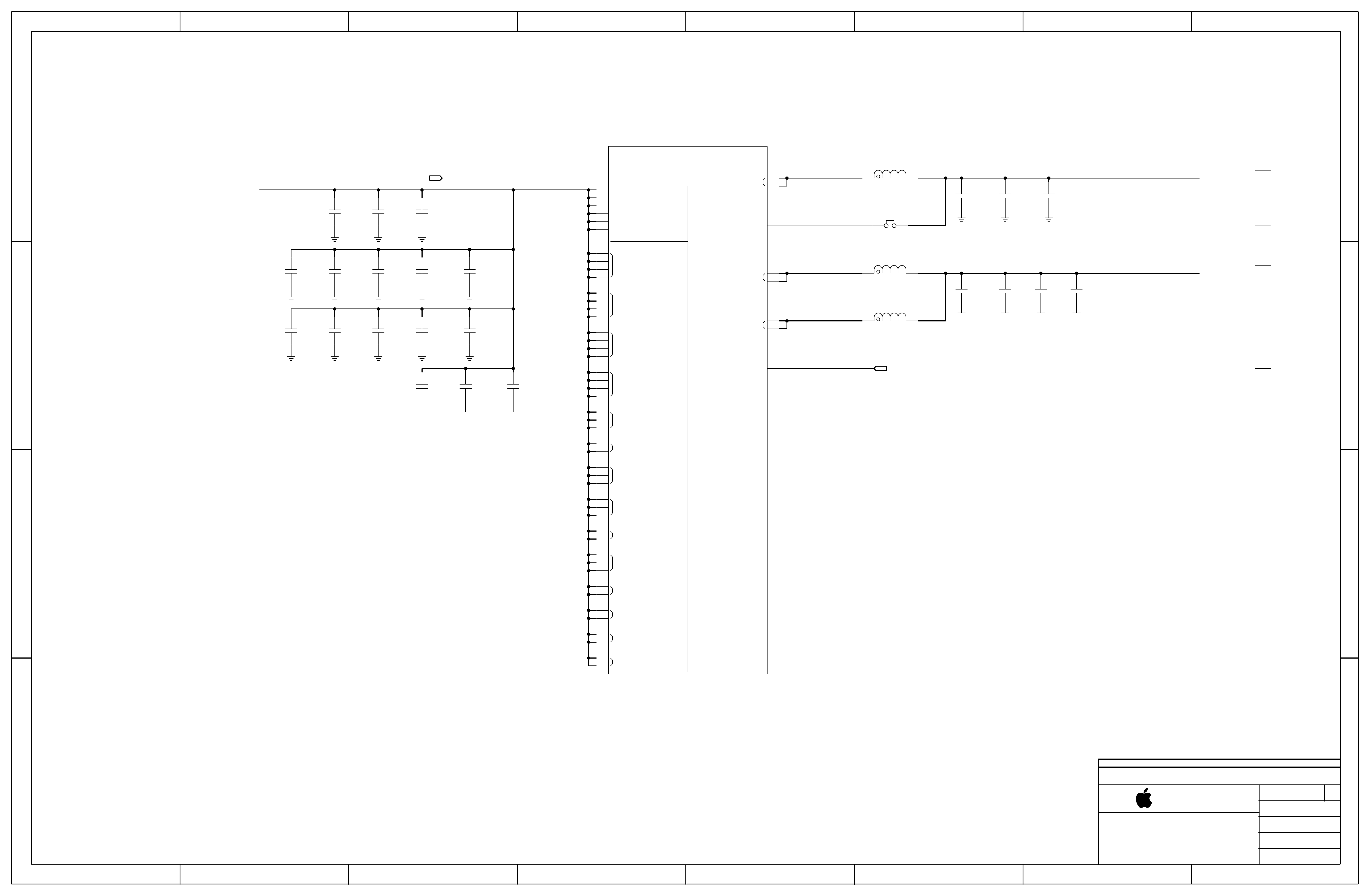

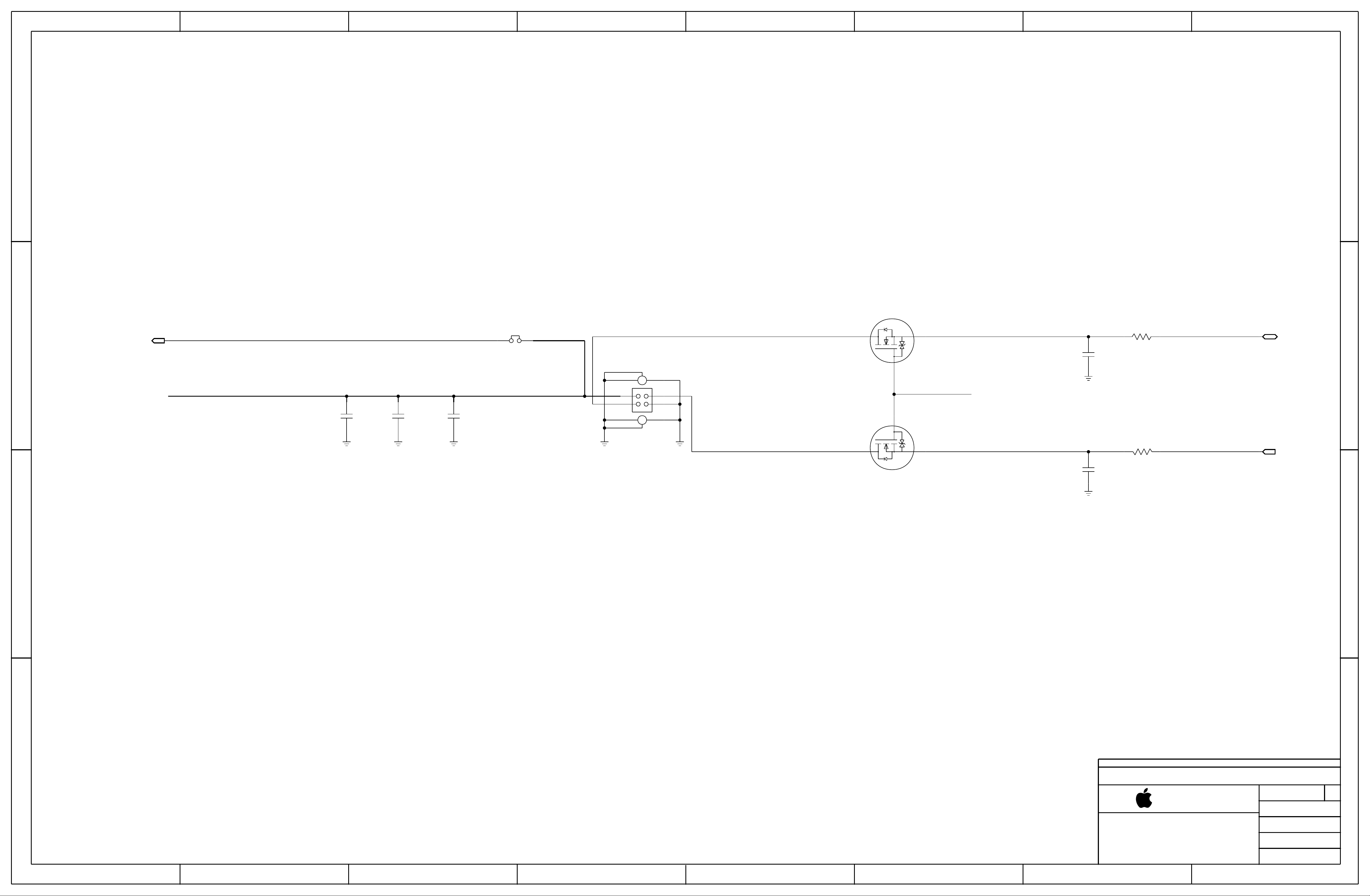

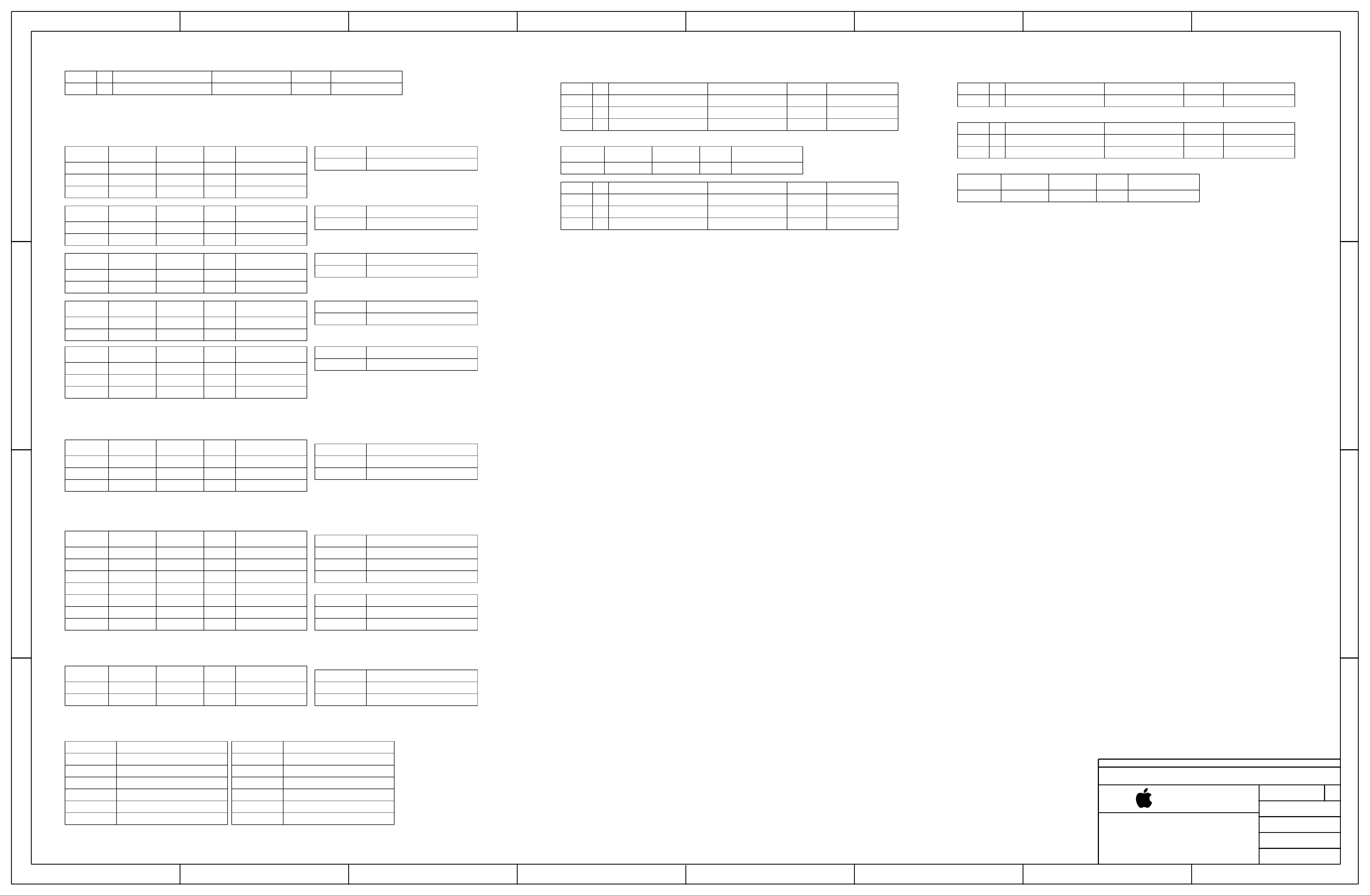

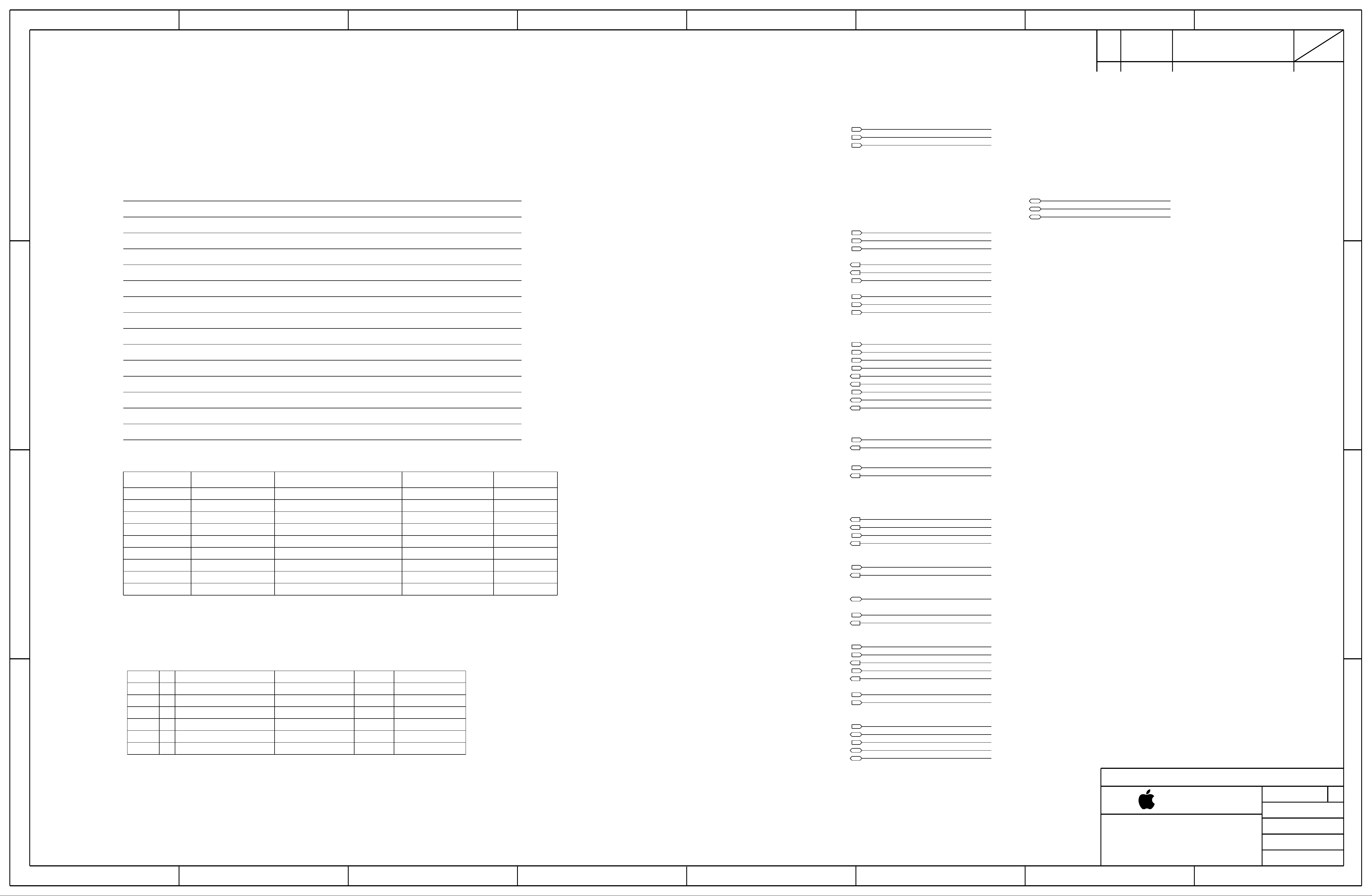

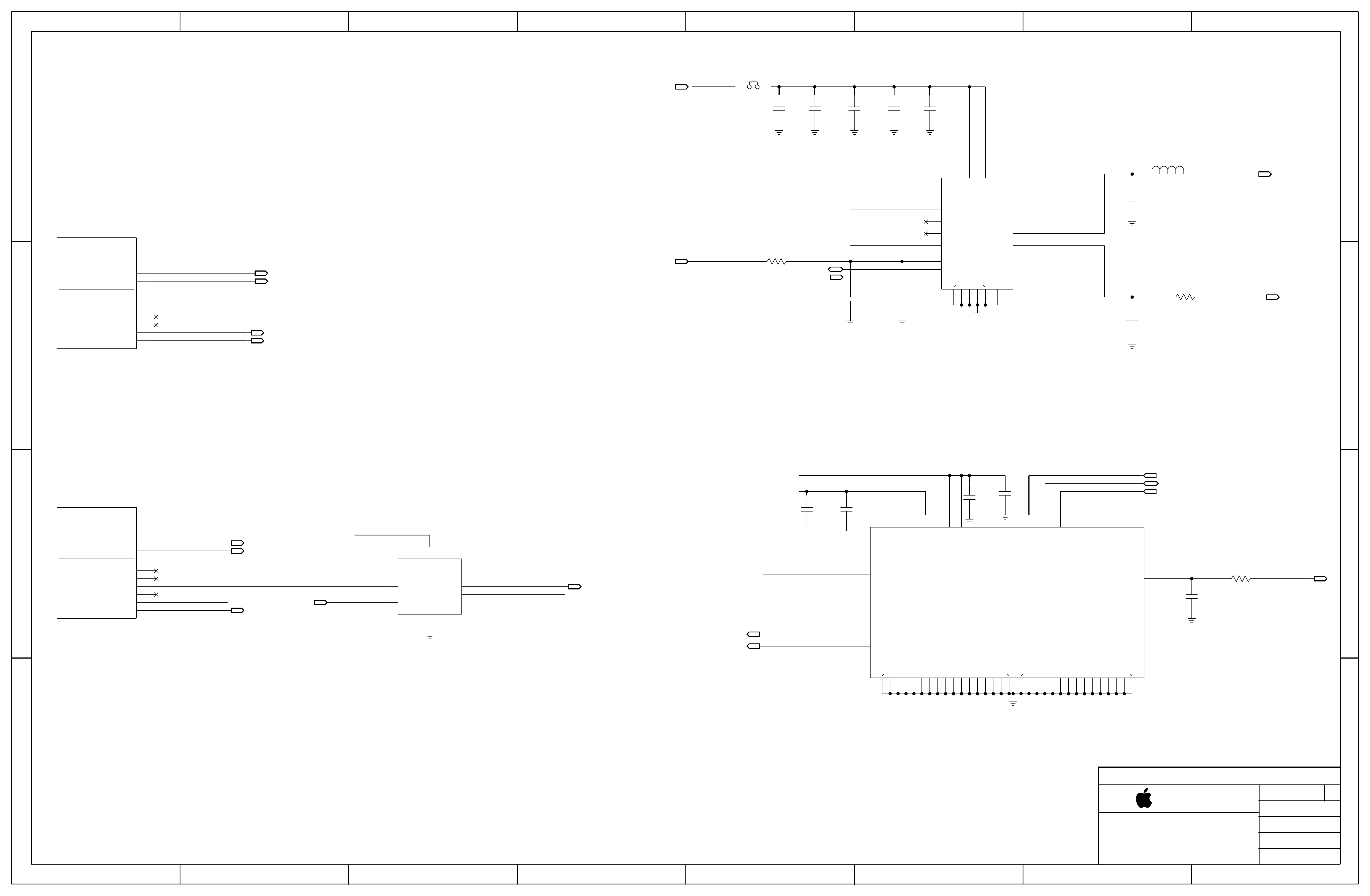

X891/X893 MLB Top: EVT

LAST_MODIFICATION=Mon Apr 3 13:03:06 2017

2 1

ECNREV DESCRIPTION OF REVISION

CK

APPD

DATE

2017-04-0500084097609 ENGINEERING RELEASED

D

1

2

3

4

5

6

7

8

9

10

11

12

1

2

4

5

6

10

11

12

13

14

15

16

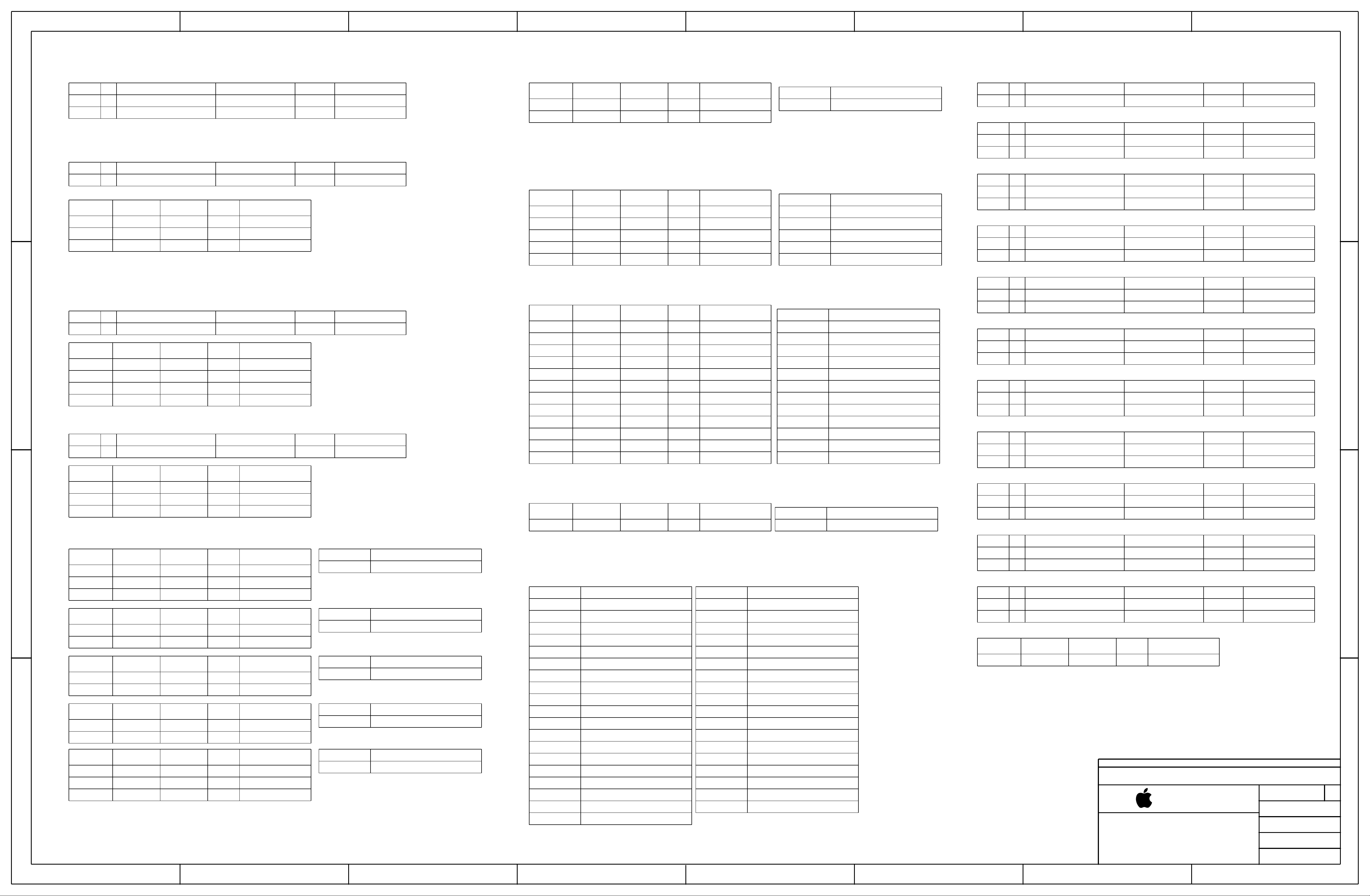

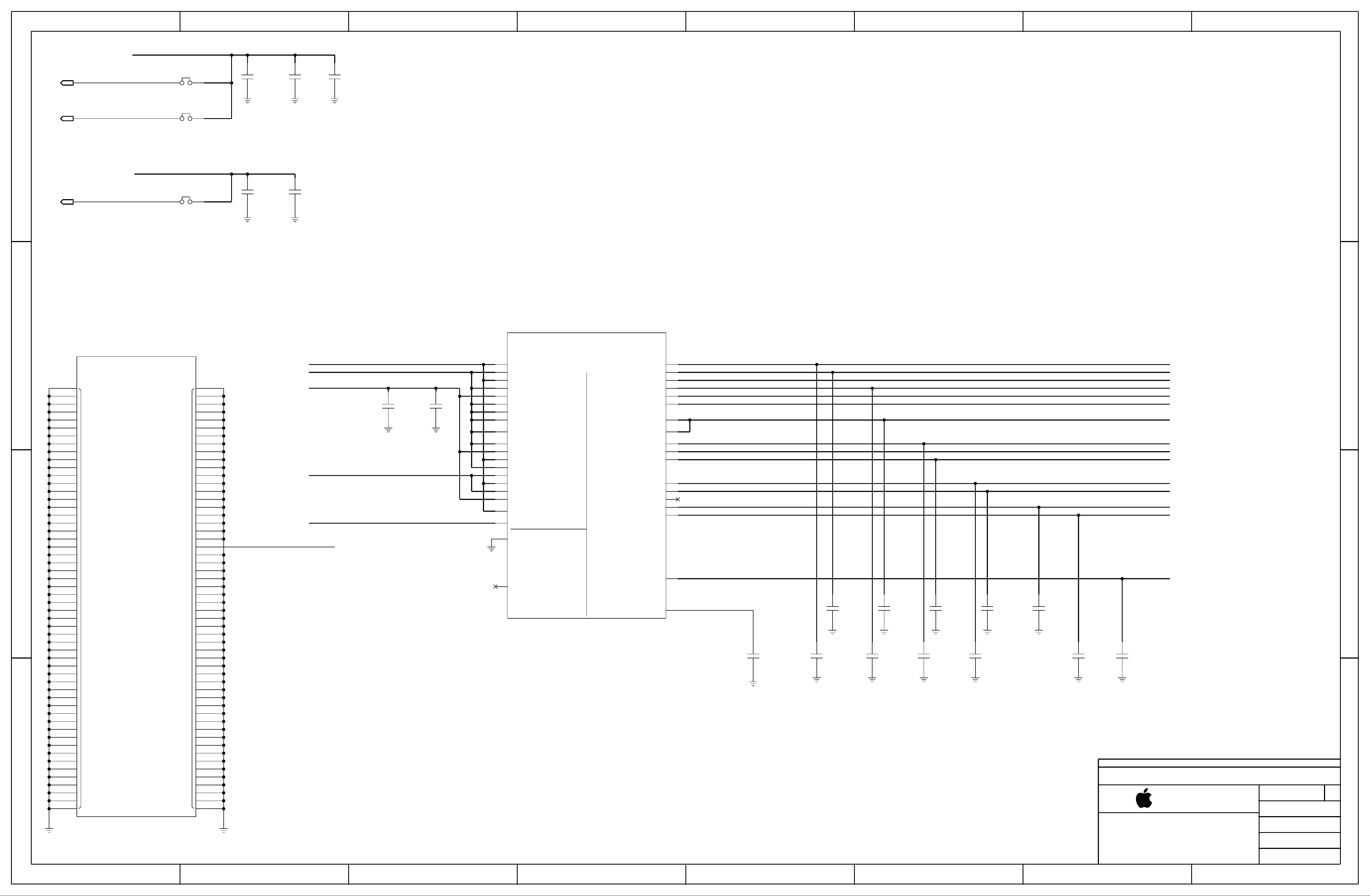

TABLE OF CONTENTS

SYSTEM:BOM Tables

SYSTEM: Mechanical Components

SYSTEM: Testpoints (Top)

BOOTSTRAPPING

SOC: JTAG,USB,XTAL

SOC: PCIE

SOC: MIPI & ISP

SOC: LPDP

SOC: Serial

SOC: GPIO & UART

SOC: AOP

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

10/13/2016

10/13/2016

10/13/2016

10/17/2016

10/17/2016

10/13/2016

10/13/2016

10/17/2016

10/13/2016

10/17/2016

46

47

48

49

50

51

61

62

63

64

65

80

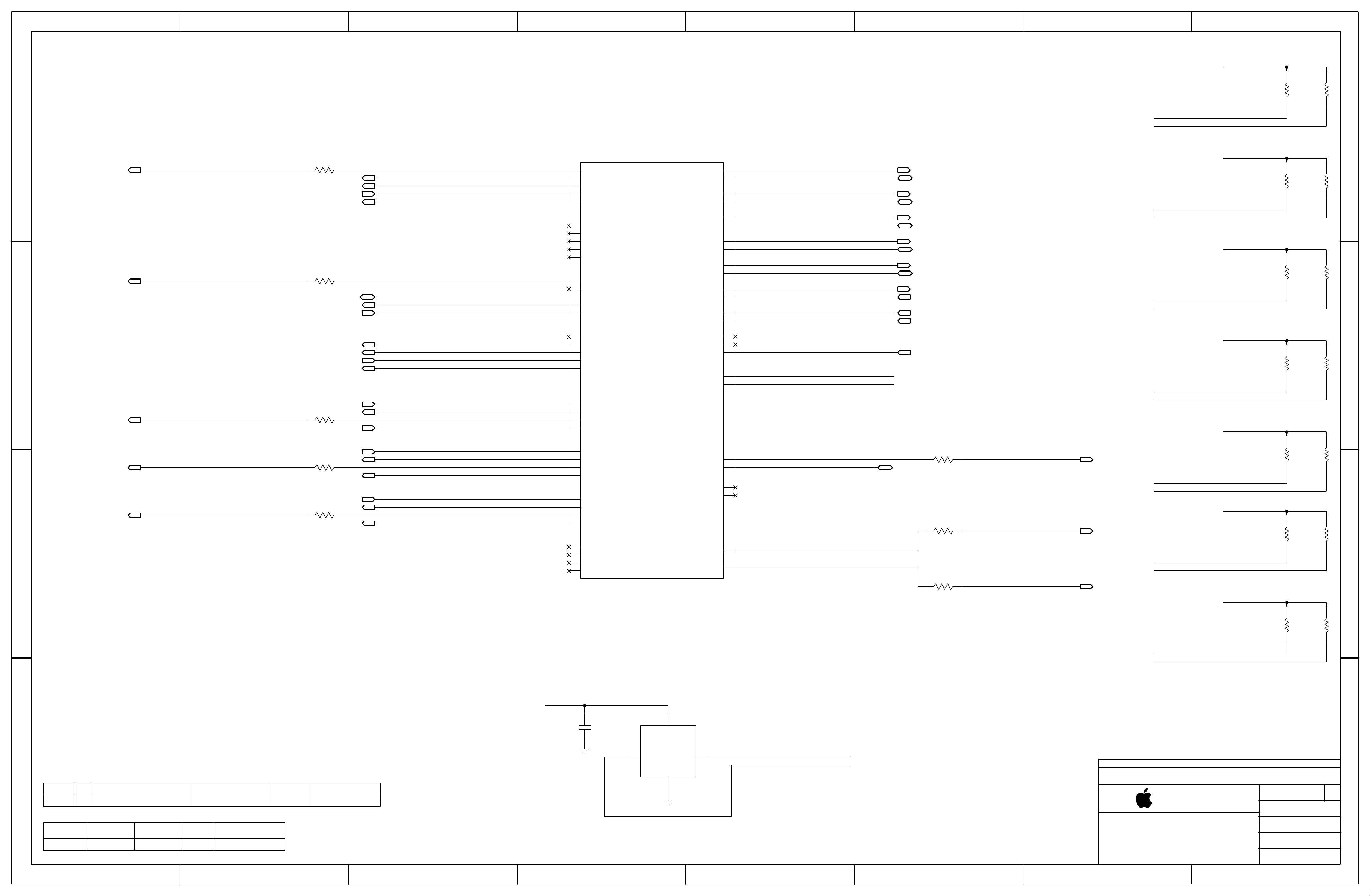

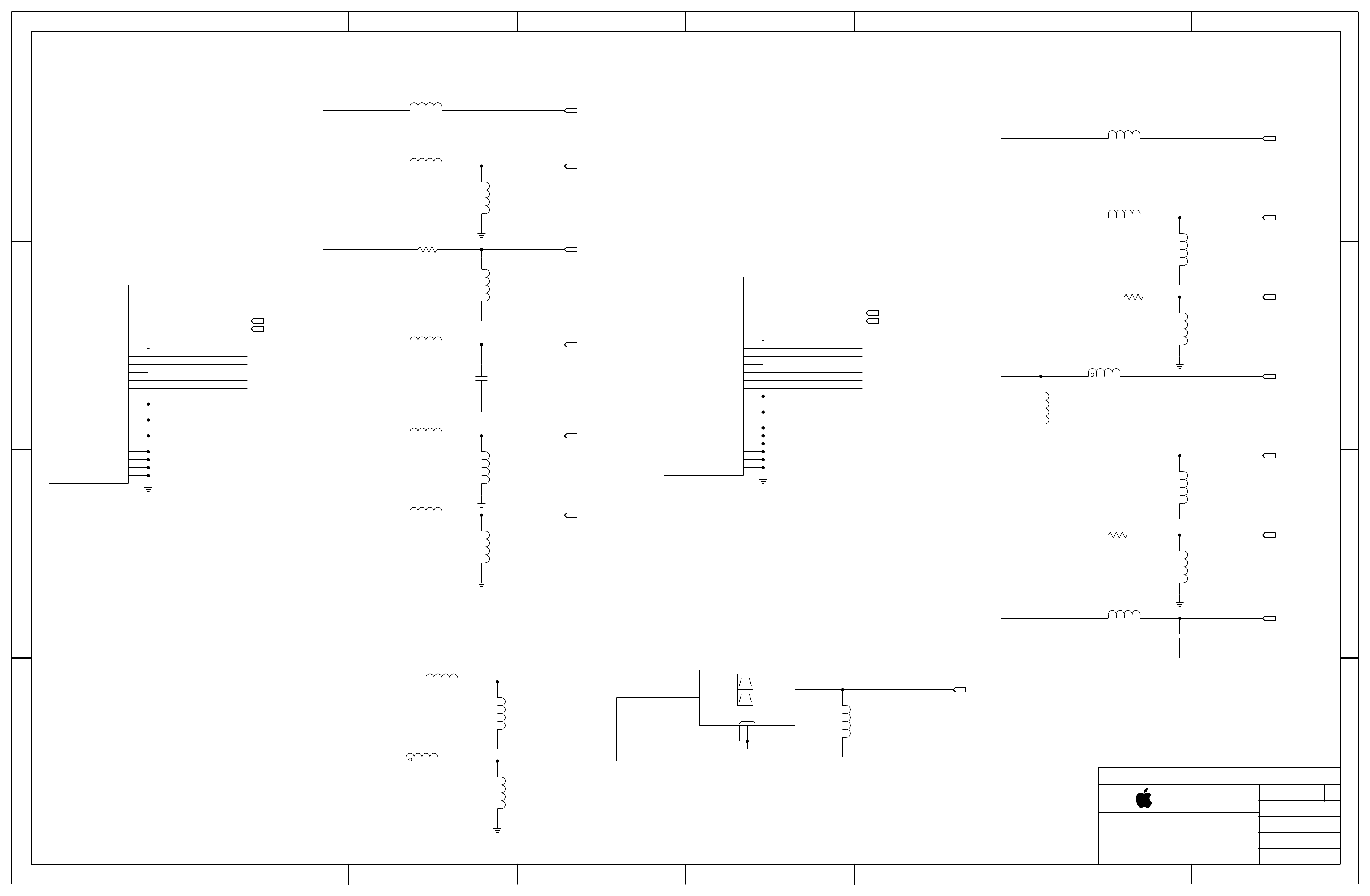

I/O: Accessory Buck

I/O: USB PD

I/O: Hydra

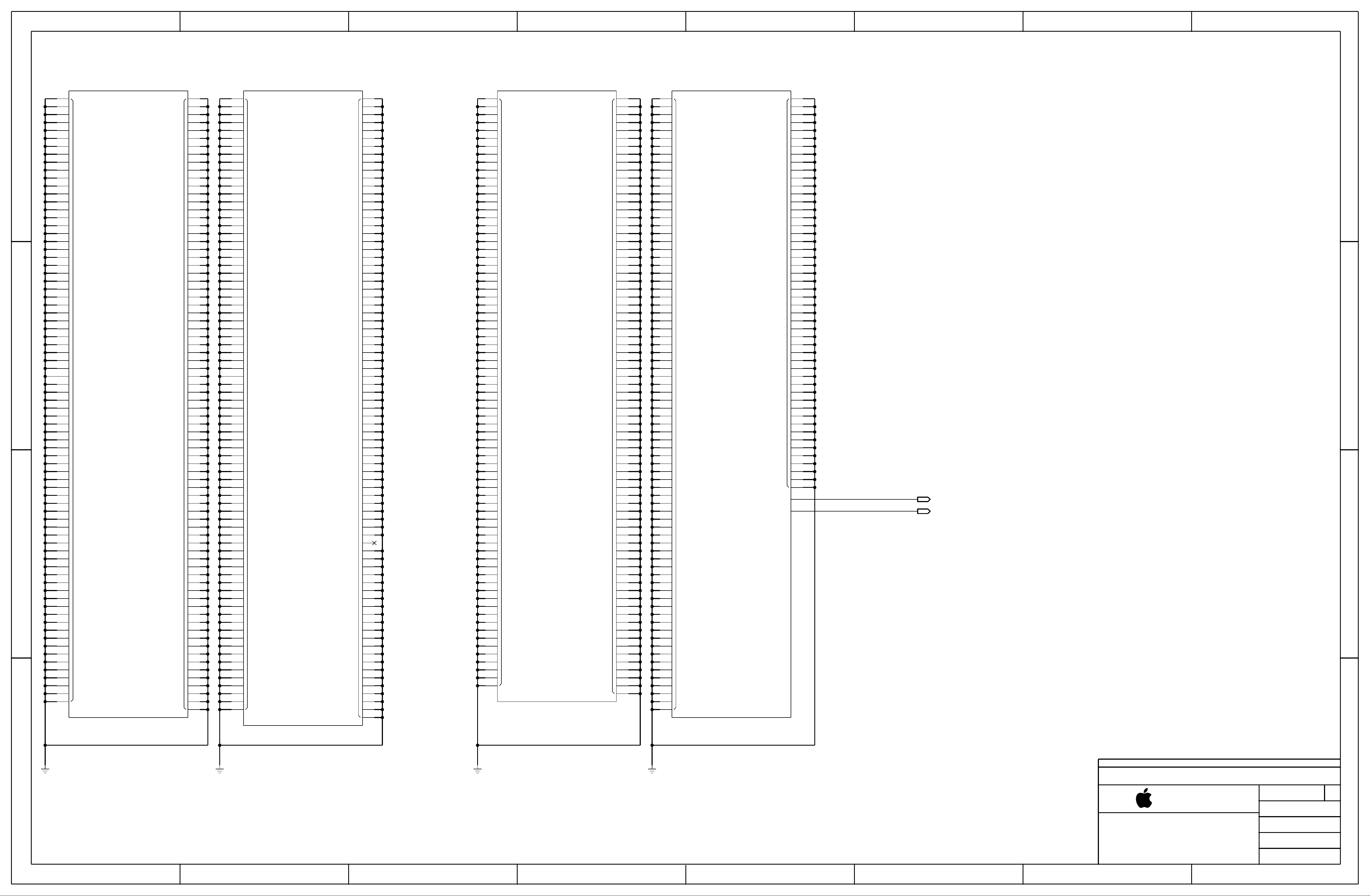

I/O: B2B Dock

I/O: Interposer (Bottom)

RADIOS

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

D

DATESYNCCONTENTSCSAPAGEDATESYNCCONTENTSCSAPAGE

10/17/2016

10/13/2016

10/13/2016

10/13/2016

10/13/2016

06/04/2015

C

13

14

15

16

17

18

19

20

21

22

23

24

25

26

17

18

19

26

27

28

29

30

31

32

33

34

35

36

SOC: Power (1/3)

SOC: Power (2/3)

SOC: Power (3/3)

NAND

SYSTEM POWER: PMU Bucks (1/4)

SYSTEM POWER: PMU Bucks (2/4)

SYSTEM POWER: PMU LDOs (3/4)

SYSTEM POWER: PMU (4/4)

SYSTEM POWER: Boost

SYSTEM POWER: B2B Battery

SYSTEM POWER: Charger

SYSTEM POWER: Iktara

SYSTEM POWER: B2B Cyclone + Button

SENSORS

test_mlb

test_mlb

test_mlb

test_mlb

10/17/2016

10/17/2016

10/17/2016

10/13/2016

test_mlb 10/13/2016

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

10/13/2016

10/13/2016

11/01/2016

10/13/2016

10/13/2016

10/13/2016

10/13/2016

10/13/2016

C

B

27

28

29

30

31

32

34

35

36

37

38

39

40

37

38

39

40

41

42

4333

44

45

46

47 test_mlb

48

CAMERA: PMU (1/2)

CAMERA: PMU (2/2)

CAMERA: B2B Wide (WY)

CAMERA: B2B Tele (MT)

CAMERA: Strobe Drivers

CAMERA: B2B FCAM

CAMERA: B2B Strobe + Hold Button

PEARL: Power

PEARL: B2B Romeo + Juliet

PEARL: B2B Rosaline + Misc

AUDIO: CODEC (1/2)

AUDIO: CODEC (2/2)

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

test_mlb

49 AUDIO: Speaker Amp Bottom

50

AUDIO: Speaker Amp Top

10/13/2016

10/13/2016

10/13/2016

10/13/2016

10/13/2016

10/13/2016

10/13/2016

10/13/2016

B

10/13/2016

10/13/2016

10/13/2016

10/13/2016

08/25/2015

08/25/2015

A

41

42

43

44

45

51

56

57

58

59

ARC: Driver

CG: Power Supplies - Touch & Display

CG: B2B Display

CG: B2B Orb & Touch

I/O: Overvoltage Cut-Off Circuit

BOM:639-04583 (Ultimate)

BOM:639-03409 (Extreme)

MCO:056-04077

1 SCH051-02221 SCH,MLB_TOP,X891 COMMON

820-00863 1 PCB,MLB_TOP,X891

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

NO

BOM OPTIONCRITICAL

COMMONNOPCB

TABLE_5_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

test_mlb

test_mlb

test_mlb

sync

10/13/2016

10/13/2016

10/13/2016

08/25/2015

01/10/2017

TABLE OF CONTENTS

DRAWING TITLE

SCH,MLB,TOP,X891

Apple Inc.

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

051-02221

REVISION

9.0.0

BRANCH

evt-1

PAGE

1 OF 80

SHEET

1 OF 51

A

SIZEDRAWING NUMBER

D

8

3

124567

678

3 245

1

D

EEEE Codes

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

825-7691

825-7691

EEEE FOR (MLB_TOP,639-04583,ULTIMATE)

1

EEEE FOR (MLB_TOP,639-03409,EXTREME)

1

EEEE_J2WJ

EEEE_HP26

NO

NO

SOC

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

339S00358 CRITICAL1 COMMON

339S00359 DDR-H,3G, B0

SKYE+3GB, B0, M, DEV

PART NUMBER

339S00358

339S00358

339S00358

BOM_TABLE_ALTS

BOM_TABLE_ALTS

BOM_TABLE_ALTS

U1000

U1000339S00361 DDR-S-18,3G, B0

U1000

TABLE_ALT_HEAD

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

TABLE_ALT_ITEM

TABLE_ALT_ITEM

DDR-S-20,3G, B0U1000339S00360

TABLE_ALT_ITEM

BOM OPTIONCRITICAL

ULTIMATE

EXTREME

BOM OPTIONCRITICAL

TABLE_5_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_HEAD

TABLE_5_ITEM

Global Ferrites

TABLE_ALT_HEAD

PART NUMBER

155S0610

BOM_TABLE_ALTS

BOM_TABLE_ALTS

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

TABLE_ALT_ITEM

ALL155S00194

ALL155S0610155S00200

FERR BD, 150OHM, TDK

TABLE_ALT_ITEM

FERR BD, 150OHM, TY

CRITICAL PART# COMMENT

155S0610

FERR BD, 150OHM, 01005

Global R/C Alternates

TABLE_ALT_HEAD

PART NUMBER

118S0717

138S0652 ALL138S0648

132S0436 ALL132S0400

138S00049

BOM_TABLE_ALTS

BOM_TABLE_ALTS

BOM_TABLE_ALTS

BOM_TABLE_ALTS

BOM_TABLE_ALTS

ALL118S0764

ALL138S0706138S0739

ALL138S0831

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

RES, 3.92K, 0.1%, 0201

CAP,X5R,4.7UF,6.3V,0.65MM,0402,TAIYO

CAP,CER,X5R,0.22UF,20%,6.3V,20%

CAP,CER,X5R,0.22UF,20%,6.3V,01005

CAP,CER,X5R,2.2UF,20%,6.3V,0201

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

CRITICAL PART# COMMENT

118S0717

138S0652

138S0706

132S0400

138S0831

RES, 3.92K, 0.1%, 0201

CAP,X5R,4.7UF,6.3V,0.65MM,0402

CAP,CER,X5R,0.22UF,20%,6.3V,20%

CAP,CER,X5R,0.22UF,20%,6.3V,01005

CAP,CER,X5R,2.2UF,20%,6.3V,0201

TABLE_CRITICAL_HEAD

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_HEAD

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

Soft-Term Cap Sub BOMs

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

SUBBOM,MLB,TOP,CAP,TYPICAL,X891

1685-00155

SUBBOM_CAP CRITICAL COMMON

Agnes Input

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

CAP,SOFT-TERM,2.2UF,6.3V,0201,KYOCERA

CAP,TYPICAL,2.2UF,6.3V,0201,MURATA

Agnes Output

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

CAP,SOFT-TERM,2.2UF,6.3V,0201,KYOCERA

138S00159

138S0831 TYPICAL_CAPCRITICAL

9

9

CAP,TYPICAL,2.2UF,6.3V,0201,MURATA

C2900,C2901,C2903,C2906,C2907,C2910,C2911,C2913,C2914

C2900,C2901,C2903,C2906,C2907,C2910,C2911,C2913,C2914

Sensors

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

138S00159 SOFT_CAPCRITICALC3602,C3622

CAP,SOFT-TERM,2.2UF,6.3V,0201,KYOCERA

2

CAP,TYPICAL,2.2UF,6.3V,0201,MURATA

BOM OPTIONCRITICAL

BOM OPTIONCRITICAL

SOFT_CAPCRITICALC2970,C2971,C2980,C29814138S00159

TYPICAL_CAPCRITICALC2970,C2971,C2980,C2981138S0831 4

BOM OPTIONCRITICAL

SOFT_CAPCRITICAL

BOM OPTIONCRITICAL

TYPICAL_CAPCRITICALC3602,C36222138S0831

TABLE_5_HEAD

TABLE_5_ITEM

TABLE_5_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

D

C

B

A

NAND

Ultimate

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

HYNIX, 3DV3, ULTIMATE U2600

PART NUMBER

335S00284 335S00287

335S00287335S00288 U2600

BOM_TABLE_ALTS

BOM_TABLE_ALTS

BOM_TABLE_ALTS

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

U2600BOM_TABLE_ALTS

U2600335S00285 335S00287

U2600335S00286 335S00287

TOSHIBA, 1Z, ULTIMATE

TOSHIBA, BICS3, ULTIMATE

SANDISK, BICS3, ULTIMATE

SAMSUNG, 3DV4, ULTIMATE

CRITICAL ULTIMATE1335S00287

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

Extreme

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

1335S00240 EXTREMECRITICALHYNIX, 3DV3, EXTREME U2600

TABLE_ALT_HEAD

PART NUMBER

335S00228 335S00240

335S00247 335S00240

335S00276 335S00240

BOM_TABLE_ALTS

BOM_TABLE_ALTS

BOM_TABLE_ALTS

U2600

U2600

U2600

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

TABLE_ALT_ITEM

TOSHIBA, BICS3, EXTREME

TABLE_ALT_ITEM

SANDISK, BICS3, EXTREME

TABLE_ALT_ITEM

SAMSUNG, 3DV4, EXTREME

Global Capacitors

TABLE_ALT_HEAD

PART NUMBER

BOM_TABLE_ALTS

138S00150 138S00149 ALL

138S00151

PART NUMBER

138S00143 ALL138S00144

138S00163

138S00144

PART NUMBER

138S00139138S00138 ALL

138S00164 ALL138S00139

PART NUMBER

138S00145 138S00146 ALL

BOM_TABLE_ALTS

BOM_TABLE_ALTS

BOM_TABLE_ALTS

BOM_TABLE_ALTS

BOM_TABLE_ALTS

BOM_TABLE_ALTS

BOM_TABLE_ALTS

BOM_TABLE_ALTS

PART NUMBER

138S00140

138S00142

138S00166

138S00141

BOM_TABLE_ALTS

BOM_TABLE_ALTS

BOM_TABLE_ALTS

ALL138S00148 138S00149

ALL138S00149

ALL

ALL138S00146138S00165

ALL138S00141

ALL

ALL138S00141

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

TABLE_ALT_ITEM

0402-3T,10.5uF@1V, Kyocera

TABLE_ALT_ITEM

0402-3T,10.5uF@1V, SEMCO

TABLE_ALT_ITEM

0402-3T,10.5uF@1V, TY

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

TABLE_ALT_ITEM

0402,16uF@1V, Kyocera

TABLE_ALT_ITEM

0402,16uF@1V, Taiyo

TABLE_ALT_HEAD

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

TABLE_ALT_ITEM

0201,3uF@1V, Kyocera

TABLE_ALT_ITEM

0201,3uF@1V, Taiyo

TABLE_ALT_HEAD

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

TABLE_ALT_ITEM

0402,5.1uF@3V, Kyocera

TABLE_ALT_ITEM

0402,5.1uF@3V, Taiyo

TABLE_ALT_HEAD

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

TABLE_ALT_ITEM

0201,1.1uF@3V, Kyocera

TABLE_ALT_ITEM

0201,1.1uF@3V, SEMCO

TABLE_ALT_ITEM

0201,1.1uF@3V, Taiyo

CRITICAL PART# COMMENT

138S00149

CRITICAL PART# COMMENT

138S00144

CRITICAL PART# COMMENT

138S00139

CRITICAL PART# COMMENT

138S00146

CRITICAL PART# COMMENT

138S00141

RCAM B2Bs

TABLE_5_HEAD

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

Global Inductors

TABLE_ALT_HEAD

TABLE_5_HEAD

BOM OPTIONCRITICAL

TABLE_5_ITEM

152S00710 152S00617

152S00712 ALL

152S00713 ALL

152S00714 ALL

152S00720

TABLE_5_HEAD

BOM OPTIONCRITICAL

TABLE_5_ITEM

152S00649 152S00650

PART NUMBER

152S00620

152S00621

152S00622

152S00626

152S00631

152S00623152S00715

BOM_TABLE_ALTS

BOM_TABLE_ALTS

BOM_TABLE_ALTS

BOM_TABLE_ALTS

BOM_TABLE_ALTS

BOM_TABLE_ALTS

BOM_TABLE_ALTS

BOM_TABLE_ALTS

BOM_TABLE_ALTS

BOM_TABLE_ALTS

BOM_TABLE_ALTS

BOM_TABLE_ALTS

ALL

ALL152S00716

ALL152S00717

ALL152S00632152S00718

ALL152S00640

ALL152S00641152S00721

ALL

ALL152S00651152S00653

L3340,L3341

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

IND,MLD,0.1UH,20%,6.1A,29MOHM,H=.65,1608

IND,MLD,0.1UH,20%,7.2A,17MOHM,H=0.8,2012

IND,MLD,0.47UH,20%,3.5A,53MO,H=.65,2012

IND,MLD,1.0UH,20%,2.1A,100MO,H=.65,2012

IND,MLD,1.5UH,20%,1.1A,160MO,H=.65,2012

IND,MLD,1.0UH,20%,2.5A,78MO,H=0.8,2012

IND,MLD,1.0UH,20%,3.2A,60MO,H=0.8,2016

IND,MLD,0.47UH,3.8A,55MO,H=0.65MM,2012

IND,MLD,0.47UH,4A,48MO,H=0.8MM,2012

IND,MLD,1UH,3.6A,60MO,H=0.8MM,2016

IND,1.2UH,3A,2016,0.65Z

IND,0.47UH,6.6A,3225,0.8Z

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

CRITICAL PART# COMMENT

152S00617

152S00620

152S00621

152S00622

152S00626

152S00631

152S00632

152S00640

152S00641

152S00623

152S00651

152S00650

IND,MLD,0.1UH,20%,6.1A,29MOHM,H=.65,1608

IND,MLD,0.1UH,20%,7.2A,17MOHM,H=0.8,2012

IND,MLD,0.47UH,20%,3.5A,53MO,H=.65,2012

IND,MLD,1.0UH,20%,2.1A,100MO,H=.65,2012

IND,MLD,1.5UH,20%,1.1A,160MO,H=.65,2012

IND,MLD,1.0UH,20%,2.5A,78MO,H=0.8,2012

IND,MLD,1.0UH,20%,3.2A,60MO,H=0.8,2016

IND,MLD,0.47UH,3.8A,55MO,H=0.65MM,2012

IND,MLD,0.47UH,4A,48MO,H=0.8MM,2012

IND,MLD,1UH,3.6A,60MO,H=0.8MM,2016

IND,1.2UH, 3A, 2016, 0.65Z

IND,0.47UH,6.6A,3225,0.8Z

TABLE_CRITICAL_HEAD

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

138S0831 TYPICAL_CAPCRITICALC3909,C3925,C4025

Strobe B2B

Audio

Pearl B2B

CAP,SOFT-TERM,2.2UF,6.3V,0201,KYOCERA

3 SOFT_CAPCRITICALC3909,C3925,C4025138S00159

3

CAP,TYPICAL,2.2UF,6.3V,0201,MURATA

CAP,SOFT-TERM,2.2UF,6.3V,0201,KYOCERA

1138S00159

CAP,TYPICAL,2.2UF,6.3V,0201,MURATA

1138S0831

CAP,SOFT-TERM,2.2UF,6.3V,0201,KYOCERA

2138S00159

CAP,TYPICAL,2.2UF,6.3V,0201,MURATA

2138S0831

CAP,SOFT-TERM,2.2UF,6.3V,0201,KYOCERA

CAP,TYPICAL,2.2UF,6.3V,0201,MURATA

1138S0831

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

BOM OPTIONCRITICAL

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_HEAD

BOM OPTIONCRITICAL

TABLE_5_ITEM

SOFT_CAPCRITICALC4303

TABLE_5_ITEM

C

TYPICAL_CAPCRITICALC4303

TABLE_5_HEAD

BOM OPTIONCRITICAL

TABLE_5_ITEM

SOFT_CAPCRITICALC4809,C4805

TABLE_5_ITEM

TYPICAL_CAPCRITICALC4809,C4805

TABLE_5_HEAD

BOM OPTIONCRITICAL

TABLE_5_ITEM

SOFT_CAPCRITICALC46131138S00159

TABLE_5_ITEM

TYPICAL_CAPCRITICALC4613

Acorn

TABLE_5_HEAD

0402-3T,10.5uF@1V

0402,16uF@1V

0201,3uF@1V

0402,5.1uF@3V

0201,1.1uF@3V

TABLE_CRITICAL_HEAD

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_HEADTABLE_ALT_HEAD

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_HEAD

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_HEAD

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_HEAD

TABLE_CRITICAL_ITEM

XTAL Alternate

TABLE_ALT_HEAD

PART NUMBER

197S0612 197S0446

BOM_TABLE_ALTS

Y1000

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

XTAL, 24M, 1612

CRITICAL PART# COMMENT

TABLE_ALT_ITEM

197S0446

XTAL, 24M, 1612

Multi-Vendor Criticals

TABLE_CRITICAL_HEAD

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEMTABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

TABLE_CRITICAL_ITEM

CRITICAL PART# COMMENT

377S0106

197S0446

155S0576

155S00168

138S0979

138S0692

138S0683

138S0652

138S00070

138S00014

132S0664

132S0663

132S0534

132S0436

132S0396

132S0316

132S0304

132S0296

132S0318

SUPPR,TRANS,VARISTOR,12V,33PF,01005

XTAL,24MHZ,30PPM,9.5PF,60 OHM MAX,1612

FERR BD,10 OHM,50%,750MA,0.07 DCR,01005

FLTR,NOISE,65 OHMZ,3.4OHM,0.7-2GHZ,0605

CAP,CER,X5R,10UF,20%,10V,0402,H=0.65MM

CAP,CER,X5R,1UF,20%,6.3V,0201

CAP,CER,X5R,1UF,10%,25V,0402

CAP,CER,X5R,4.7UF,20%,6.3V,H=0.65MM,0402

CAP,X5R,4.7UF,20%,25V,0402

CAP,CER,1UF,20%,16V,X5R,0201,H=0.39MM

CAP,CER,0.047UF,10%,25V,X5R,0201

CAP,CER,X5R,1UF,10%,25V,0402

CAP,CER,X5R,0.1UF,10%,25V,0201

CAP,CER,X5R,0.22UF,20%,6.3V,01005

CAP,CER,X5R,1000PF,10%,10V,01005 CAP,CER,C0G,220PF,5%,10V,01005

CAP,CER,X5R,0.1UF,20%,6.3V,01005

CAP,CER,X5R,0.22UF,20%,6.3V,0201

CAP,CER,X5R,1000PF,10%,6.3V,01005

CAP,CER,X5R,820PF,10%,10V,01005

TABLE_CRITICAL_HEAD

CRITICAL PART# COMMENT

TABLE_CRITICAL_ITEM

132S0288

TABLE_CRITICAL_ITEM

132S0275

TABLE_CRITICAL_ITEM

132S0249

TABLE_CRITICAL_ITEM

132S0245

TABLE_CRITICAL_ITEM

132S00093

TABLE_CRITICAL_ITEM

132S00025

TABLE_CRITICAL_ITEM

132S00008

TABLE_CRITICAL_ITEM

131S0883

TABLE_CRITICAL_ITEM

131S0804

TABLE_CRITICAL_ITEM

131S0307

TABLE_CRITICAL_ITEM

131S0225

TABLE_CRITICAL_ITEM

131S0223

TABLE_CRITICAL_ITEM

131S0220

131S0216

TABLE_CRITICAL_ITEM TABLE_CRITICAL_ITEM

CAP,CER,X5R,0.1UF,10%,16V,0201

CAP,CER,X5R,470PF,10%,10V,01005

CAP,CER,X7R,220PF,10%,10V,01005

CAP,CER,X5R,0.01UF,10%,6.3V,01005

CAP,X5R,0.022UF,20%,6.3V,01005

CAP,CER,X5R,0.047UF,20%,6.3V,01005

CAP,CER,0.1UF,10%,50V,X7R,0402

CAP,CER,NP0/C0G,220PF,2%,50V,0201

CAP,CER,27PF,5%,C0G,25V,0201

CAP,CER,NP0/C0G,100PF,5%,16V,01005

CAP,CER,NP0/C0G,15PF,5%,16V,01005

CAP,CER,NP0/C0G,27PF,5%,16V,01005

CAP,CER,NP0/C0G,12PF,5%,16V,01005

CAP,CER,NP0/C0G,47PF,5%,16V,01005

131S00053

TABLE_CRITICAL_ITEM

118S00068

TABLE_CRITICAL_ITEM

117S0055

TABLE_CRITICAL_ITEM

107S0257

TABLE_CRITICAL_ITEM

RES,MF,1.3 MOHM,1%,200PPM,1/20W,0201

RES,MF,1/20W,2M OHM,5,0201,SMD

THERMISTOR,NTC,10K OHM,1%,B=3435,01005

TABLE_CRITICAL_HEAD

TABLE_CRITICAL_ITEM

CODEC

Ansel

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

CAP,SOFT-TERM,10UF,10V,0402,MURATA

2138S00160

CAP,TYPICAL,10UF,10V,0402,MUR/KYO

2138S0979

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

CAP,SOFT-TERM,10UF,10V,0402,MURATA

2138S00160

CAP,TYPICAL,10UF,10V,0402,MUR/KYO

2138S0979

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

1138S00160

CAP,SOFT-TERM,10UF,10V,0402,MURATA

1138S0979 CRITICAL

CAP,TYPICAL,10UF,10V,0402,MUR/KYO

PART NUMBER

685-00155685-00156

BOM_TABLE_ALTS

SYNC_MASTER=test_mlb

PAGE TITLE

SUBBOM_CAP

C4811,C4808 SOFT_CAPCRITICAL

TABLE_ALT_HEAD

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

TABLE_ALT_ITEM

SUBBOM,MLB,TOP,CAP,SOFT,X891

SYSTEM:BOM Tables

Apple Inc.

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

BOM OPTIONCRITICAL

SOFT_CAPCRITICALC5641,C5653

TYPICAL_CAPCRITICALC5641,C5653

BOM OPTIONCRITICAL

TYPICAL_CAPCRITICALC4811,C4808

BOM OPTIONCRITICAL

SOFT_CAPCRITICALC3710

TYPICAL_CAPC3710

DRAWING NUMBER

REVISION

BRANCH

PAGE

SHEET

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

051-02221

9.0.0

evt-1

2 OF 80

2 OF 51

SYNC_DATE=10/13/2016

SIZE

D

B

A

8

67

35 4

2

1

678

3 245

1

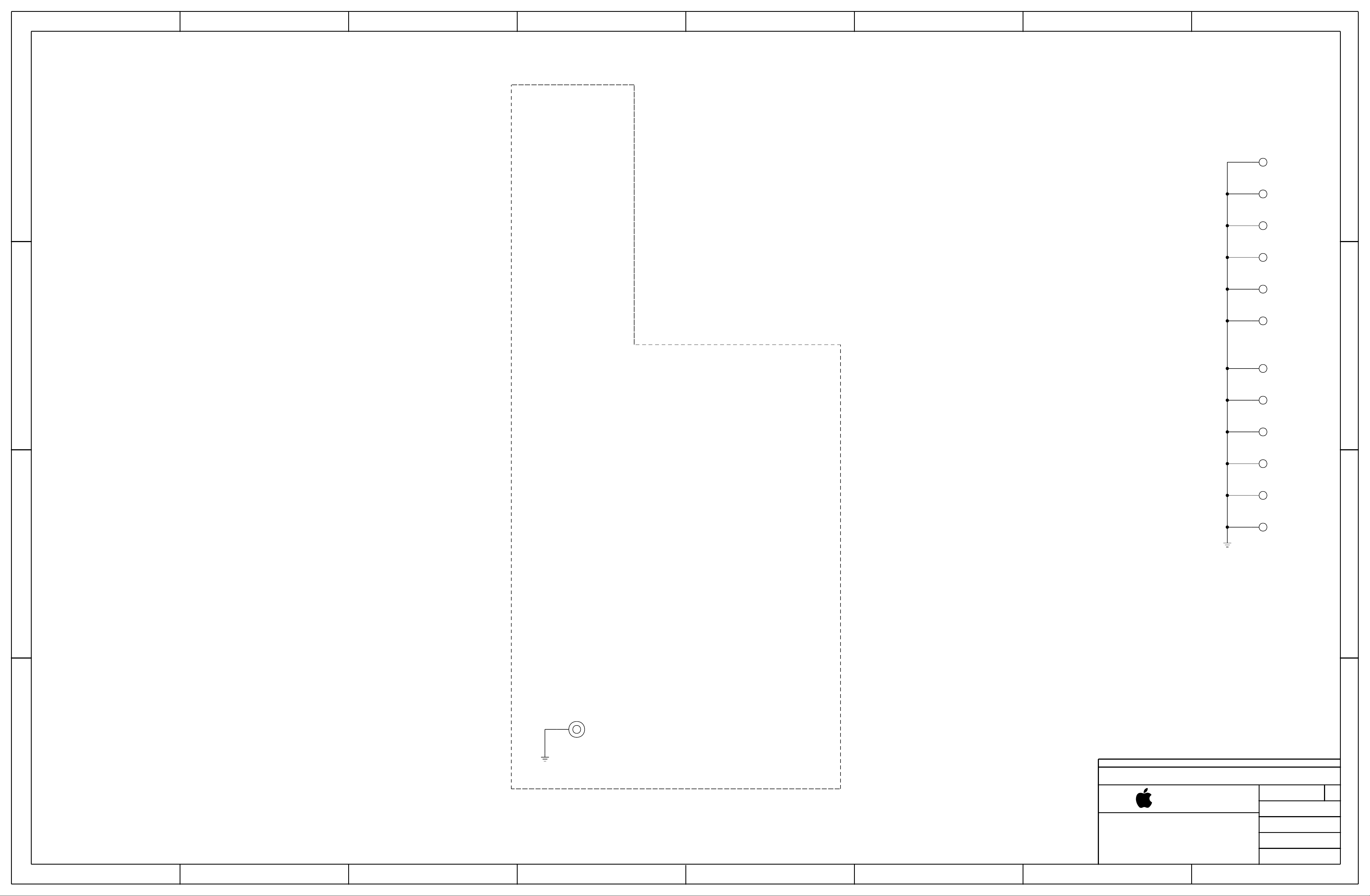

FIDUCIALS

FD0401

FID

0P5SQ-CROSS-NSP

1

ROOM=ASSEMBLY

D

CL0400

2.10R1.60-NSP

1

FD0402

FID

0P5SQ-CROSS-NSP

1

ROOM=ASSEMBLY

FD0403

FID

0P5SQ-CROSS-NSP

1

ROOM=ASSEMBLY

FD0404

FID

0P5SQ-CROSS-NSP

1

ROOM=ASSEMBLY

FD0420

FID

0P5SQ-CROSS-NSP

1

ROOM=ASSEMBLY

FD0405

0P5SQ-SMP3SQ-NSP

FID

1

ROOM=ASSEMBLY

D

C

CRITICAL

SB0400

STDOFF-2.9OD1.4ID-0.77H-SM

1

CL0401

2.10R1.60-NSP

1

FD0410

0P5SQ-SMP3SQ-NSP

FID

1

ROOM=ASSEMBLY

FD0411

0P5SQ-SMP3SQ-NSP

FID

1

ROOM=ASSEMBLY

FD0412

0P5SQ-SMP3SQ-NSP

FID

1

ROOM=ASSEMBLY

C

B

CRITICAL

SB0402

STDOFF-MLB-TUBE

1

CL0402

2.10R1.60-NSP

1

B

CRITICAL

1

SH0401

SM

SHLD-EMI-HARD-X891

A

CRITICAL

SB0401

STDOFF-2.9OD1.4ID-0.77H-SM

1

CRITICAL

1

SH0400

SM

SHIELD-EMI-TOP-X891

CL0403

2.10R1.60-NSP

1

PAGE TITLE

SYSTEM: Mechanical Components

Apple Inc.

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

DRAWING NUMBER

051-02221

REVISION

9.0.0

BRANCH

evt-1

PAGE

4 OF 80

SHEET

3 OF 51

A

SIZE

D

8

67

35 4

2

1

678

3 245

1

D

C

PP_ROMEO_DENSE_ANODE

34 35

PP_ROMEO_CATHODE

34 35

POWER

TP0540

P2MM-NSM

SM

1

TP0543

P2MM-NSM

1

PP

SM

PP

ROOM=TEST

ROOM=TEST

Test Points

20

XW0510

SHORT-10L-0.05MM-SM

XW0511

SHORT-10L-0.05MM-SM

17 13

PP_GPU

20 6

11 5

32 8

11

11 6

20 6

Probe Points

SOC Debug

PP0500

P2MM-NSM

AP_TO_PMU_TEST_CLKOUT

IN

BOARD_ID0

IN

AP_TO_FCAM_SHUTDOWN_L

IN

8

AP_DEBUG3

IN

DFU_STATUS

IN

PMU_TO_AP_PRE_UVLO_L

IN

AP_TO_PMU_SOCHOT_L

IN

SOC CPU/GPU

21

21

PP_GPU_LVCC

PP_CPU_PCORE_LVCCPP_CPU_PCORE

SM

1

PP

ROOM=TEST

PP0501

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0502

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0503

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0504

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0505

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0506

P2MM-NSM

SM

1

PP

ROOM=TEST

50

50 17 13

26 12

26 12

26 12

26 12

26 12

49 25 12

26 12

48 23

Sensors

SPI_AOP_TO_IMU_SCLK

IN

SPI_AOP_TO_IMU_MOSI

IN

SPI_IMU_TO_AOP_MISO

IN

ACCEL_GYRO_TO_AOP_DATARDY

IN

ACCEL_GYRO_TO_AOP_INT

IN

COMPASS_TO_AOP_INT

IN

PHOSPHORUS_TO_AOP_INT

IN

Hydra VBUS

HYDRA_TO_TIGRIS_VBUS1_VALID_L

IN

PP0540

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0541

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0542

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0544

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0545

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0546

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0547

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0550

P2MM-NSM

SM

1

PP

ROOM=TEST

41 37

41 37

47 10

47 10

50 49 41 25 12

50 49 41 25 12

PDM_CODEC_TO_ARC_CLK

IN

PDM_CODEC_TO_ARC_DATA

IN

AP_BI_CCG2_SWDIO

IN

AP_TO_CCG2_SWCLK

IN

SOC I2C1_AOP

I2C1_AOP_SCL

IN

I2C1_AOP_SDA

IN

PP0582

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0583

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0586

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0587

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0590

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0591

P2MM-NSM

SM

1

PP

ROOM=TEST

D

C

B

20 13

20 13

13

15

15

AP_CPU_PCORE_SENSE

IN

AP_VDD_GPU_SENSE

IN

TP_SOC_SENSE

IN

TP_VSS_CPU_SENSE

IN

TP_VSS_SENSE

IN

PMU

PP0512

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0513

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0514

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0515

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0516

P2MM-NSM

SM

1

PP

ROOM=TEST

16 12

50 16 12

16 10 5

16

16

NAND CCG2

PP0560

P2MM-NSM

SWD_AP_BI_NAND_SWDIO

IN

SWD_AOP_TO_MANY_SWCLK

IN

SPI_S4E_TO_AP_MISO_BOOT_CONFIG2

IN

NAND_ANI1_VREF

IN

NAND_ANI0_VREF

IN

SM

1

PP

ROOM=TEST

PP0561

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0562

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0563

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0564

P2MM-NSM

SM

1

PP

ROOM=TEST

47 10

CCG2_TO_SMC_INT_L

IN

PP0592

P2MM-NSM

SM

1

PP

ROOM=TEST

B

14 12

20 10

48 20 6

16 7

16 7

AOP_TO_DDR_SLEEP1_READY

IN

SPMI_PMU_BI_PMGR_SDATA

IN

PMU_TO_AP_HYDRA_ACTIVE_READY

IN

PCIE Refclk

90_PCIE_AP_TO_NAND_REFCLK_P

IN

90_PCIE_AP_TO_NAND_REFCLK_N

IN

PP0520

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0521

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0522

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0530

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0531

P2MM-NSM

SM

1

PP

ROOM=TEST

34 28

34 20 8

Rigel

CAMPMU_TO_RIGEL_ENABLE

IN

RIGEL_TO_ISP_INT

IN

PP0570

P2MM-NSM

SM

1

PP

ROOM=TEST

PP0571

P2MM-NSM

SM

1

PP

ROOM=TEST

A

8

SYNC_MASTER=test_mlb SYNC_DATE=10/13/2016

PAGE TITLE

A

SYSTEM: Testpoints (Top)

DRAWING NUMBER

051-02221

Apple Inc.

REVISION

9.0.0

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

67

35 4

2

BRANCH

evt-1

PAGE

5 OF 80

SHEET

4 OF 51

1

SIZE

D

678

3 245

1

D

11

11

BOARD_REV3

OUT

BOARD_REV2

OUT

R0623

1.00K

1/32W

01005

ROOM=SOC

21

5%

MF

R0622

1.00K

1/32W

01005

ROOM=SOC

21

5%

MF

NOSTUFF

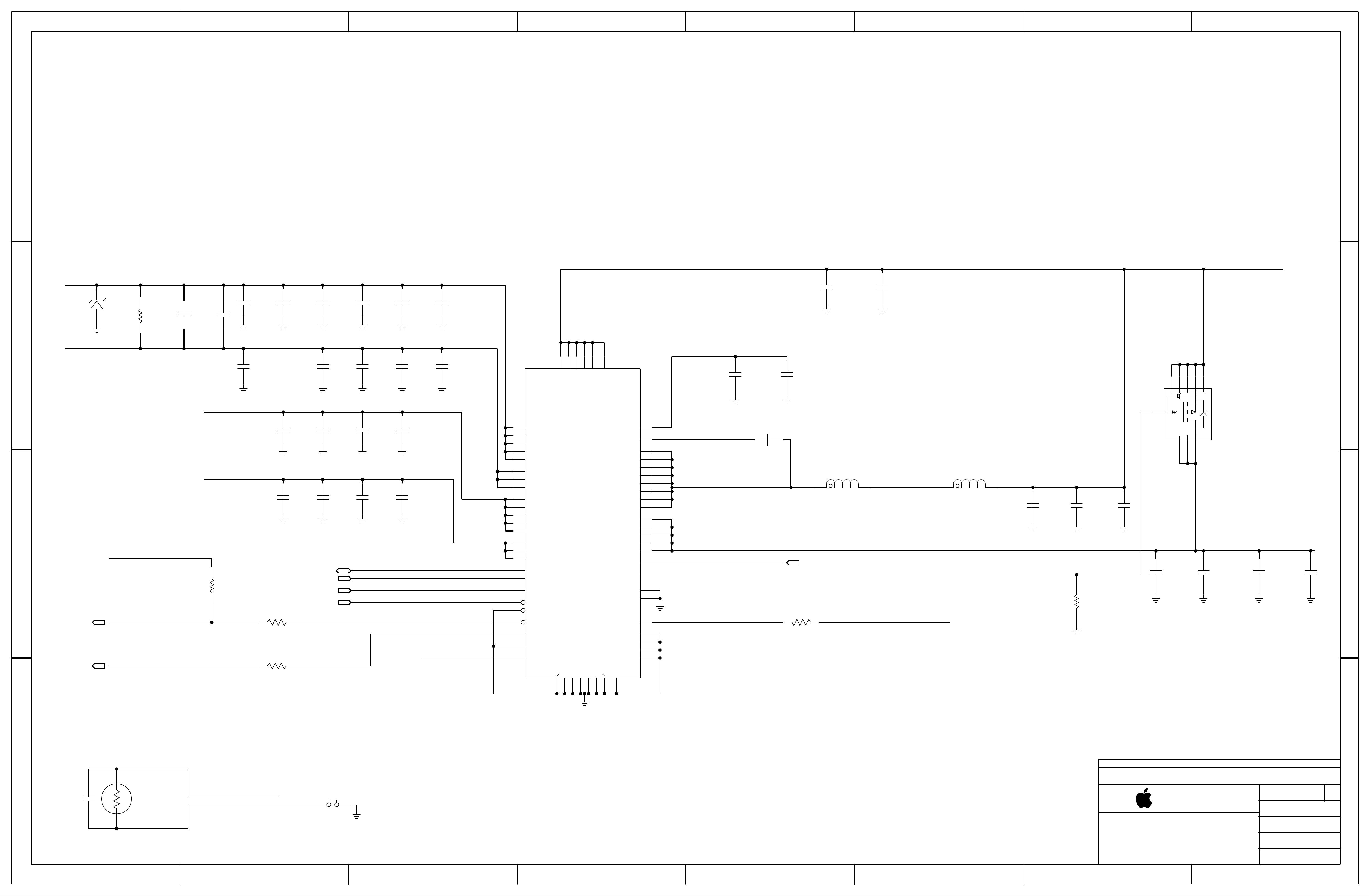

BOOTSTRAPPING:BOARD REV

BOARD ID

BOOT CONFIG

PP1V8_IO

43 35 34 32

30 29 28 27 17 16 14 10 8 7 6

D

C

11

11

11

BOARD_REV1

OUT

BOARD_REV0

OUT

BOARD_ID4

OUT

CKPLUS_WAIVE=SINGLE_NODENET

R0621

1.00K

1/32W

01005

ROOM=SOC

21

5%

MF

R0620

1.00K

1/32W

01005

ROOM=SOC

No connect

21

5%

MF

C

SELECTED -->

B

50 10

11

11

11 4

BOARD_ID3

OUT

CKPLUS_WAIVE=SINGLE_NODENET

PP1V8_IO

OUT

PP1V8_IO

OUT

BOARD_ID0

OUT

On mlb_bot

MAKE_BASE=TRUE

No connect

SELECTED -->

D221 Baseband Selected on RF Board

B

A

16 10 4

16 10

16 10

SPI_S4E_TO_AP_MISO_BOOT_CONFIG2

OUT

SPI_AP_TO_S4E_MOSI_BOOT_CONFIG1

OUT

SPI_AP_TO_S4E_SCLK_BOOT_CONFIG0

OUT

No connect

R0601

4.7K

1/32W

01005

ROOM=SOC

21

1%

MF

R0600

4.7K

1/32W

01005

ROOM=SOC

21

1%

MF

NOSTUFF

SELECTED -->

SYNC_MASTER=test_mlb

PAGE TITLE

BOOTSTRAPPING

Apple Inc.

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

DRAWING NUMBER

051-02221

REVISION

9.0.0

BRANCH

evt-1

PAGE

6 OF 80

SHEET

5 OF 51

SYNC_DATE=10/13/2016

SIZE

D

A

8

67

35 4

2

1

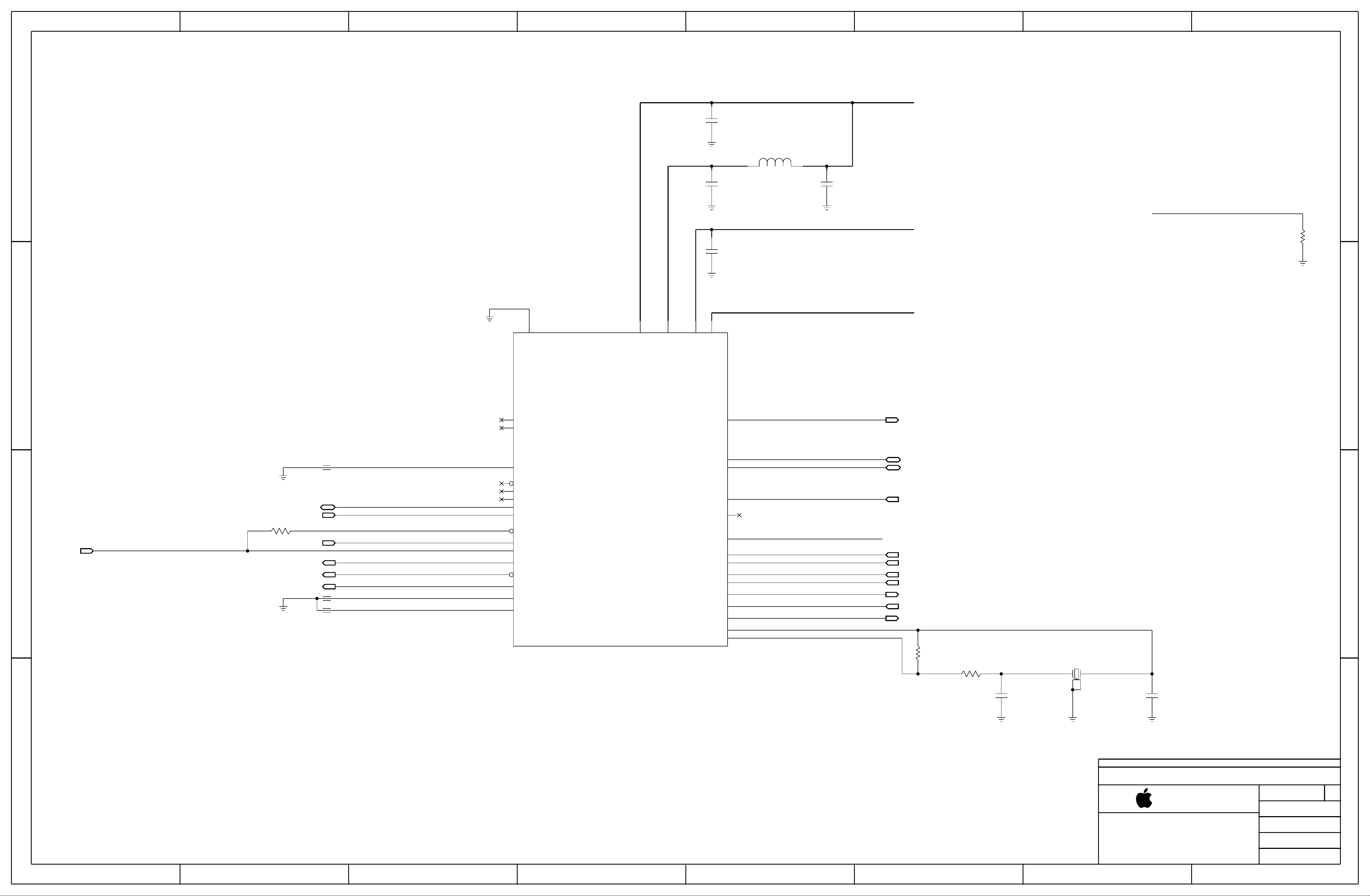

SOC - USB, JTAG, XTAL

678

3 245

1

VDD11_XTAL:1.06-1.17V @ 2mA MAX

VDD18_USB: 1.62V - 1.98V @ 20mA MAX

D

PP1V8_XTAL

1

C1090

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

FL1092

240-OHM-25%-0.20A-0.9DCR

21

1

C1092

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

1

C1095

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

01005

ROOM=SOC

PP1V8_IO

1

C1093

4UF

20%

6.3V

2

CER-X5R

0201

ROOM=SOC

3.14-3.46V @ 12mA MAX

PP3V3_USB

19

43 35 34 32

30 29 28 27 17 16 14 10 8 7 5

D

USB Reference

AP_USB_REXT

6

1

R1000

200

1%

1/32W

MF

01005

2

ROOM=SOC

C

NC

NC

BA4

AY4

AT7

VDD12_UH1_HSIC0

UH1_HSIC0_DATA

UH1_HSIC0_STB

AP14

VDD18_USB

OMIT_TABLE

U1000

TMIT78B0-C4

WLCSP

SYM 1 OF 16

ROOM=SOC

CRITICAL

AU28

VDD18_XTAL

AN14

VDD33_USB

ANALOGMUX_OUT

AN15

VDD_FIXED_USB

AT27

(Analog)

0.765V - 0.84V @ 5mA MAX

PP0V8_SOC_FIXED_S1

AP_TO_PMU_AMUX_OUT

OUT

17 14 13 9 8 7

C

20

B

20

PMU_TO_SYSTEM_COLD_RESET_L

IN

MAKE_BASE=TRUE

R1020

10K

1/32W

01005

21

5%

MF

MAKE_BASE=TRUE

48

48

48 20 4

20 4

16

16

GND

SWD_DOCK_BI_AP_SWDIO

BI

SWD_DOCK_TO_AP_SWCLK

IN

PMU_TO_SYSTEM_COLD_RESET_R_L

PMU_TO_AP_HYDRA_ACTIVE_READY

IN

AP_TO_PMU_TEST_CLKOUT

OUT

AP_TO_NAND_RESET_L

OUT

OUT

AP_TO_NAND_FW_STRAP

GND

GND

NC

NC

NC

AT8

AV6

AT9

AT12

AT10

AT13

AU7

AT34

AV5

V2

AF34

AG38

W5

W4

JTAG_SEL

JTAG_TRST*

JTAG_TDO

JTAG_TDI

JTAG_TMS

JTAG_TCK

COLD_RESET*

CFSB

CFSB_AON

TST_CLKOUT

SSD_RESET*

SSD_BFH

HOLD_RESET

TESTMODE

USB_DP

USB_DM

USB_VBUS

USB_ID

USB_REXT

CPU_TRIGGER0

CPU_TRIGGER1

GPU_TRIGGER0

GPU_TRIGGER1

SOCHOT1

DROOP

WDOG

XI0

XO0

AY6

BA6

AV7

AW6

AU8

AT22

AW21

AD2

AD3

A30

B31

AW5

BA28

BA27

NC

90_USB_AP_DATA_P

90_USB_AP_DATA_N

USB_VBUS_DETECT

AP_USB_REXT

PMU_TO_AP_THROTTLE_PCORE_L

PMU_TO_AP_THROTTLE_ECORE_L

PMU_TO_AP_THROTTLE_GPU0_L

PMU_TO_AP_THROTTLE_GPU1_L

AP_TO_PMU_SOCHOT_L

PMU_TO_AP_PRE_UVLO_L

AP_TO_PMU_WDOG_RESET

IN

6

IN

IN

IN

IN

OUT

IN

OUT

XTAL_AP_24M_IN

XTAL_AP_24M_OUT

48

BI

48

BI

23

20

20

20

20

20

20 4

20 11 4

NOSTUFF

1

R1010

511K

1%

1/32W

MF

01005

2

ROOM=SOC

R1011

1.00K

5%

1/32W

MF

01005

ROOM=SOC

24.000MHZ-30PPM-9.5PF-60OHM

21

SOC_24M_O

1

C1010

12PF

5%

16V

2

CERM

01005

ROOM=SOC

ROOM=SOC

Y1000

1.60X1.20MM-SM

31

42

1

C1011

12PF

5%

16V

2

CERM

01005

ROOM=SOC

B

A

8

SYNC_MASTER=test_mlb

PAGE TITLE

SYNC_DATE=10/17/2016

A

SOC: JTAG,USB,XTAL

DRAWING NUMBER

051-02221

Apple Inc.

REVISION

9.0.0

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

67

35 4

2

BRANCH

evt-1

PAGE

10 OF 80

SHEET

6 OF 51

1

SIZE

D

SOC - PCIE INTERFACES

678

3 245

1

D

C

PCIe BB CLKREQ PU on BB domain

PCIe Clock Request Pull-Ups

29 28 27 17 16 14 10 8 7 6 5

PCIE_NAND_BI_AP_CLKREQ_L

16 7

PCIE_WLAN_BI_AP_CLKREQ_L

50 7

43 35 34 32 30

PP1V8_IO

R1100

100K

5%

1/32W

MF

01005

ROOM=SOC

1

2

R1130

PCIe Reset Pull-Downs

PCIE_AP_TO_WLAN_RESET_L

50 7

PCIE_AP_TO_BB_RESET_L

50 7

PCIE_AP_TO_NAND_RESET_L

16 7

R1101

100K

5%

1/32W

MF

01005

ROOM=SOC

1

2

R1121

100K

1/32W

01005

ROOM=SOC

100K

1/32W

01005

ROOM=SOC

5%

MF

5%

MF

(Analog)

R1198

19 14 13 9

1

2

1

2

R1131

ROOM=SOC

100K

5%

1/32W

MF

01005

1

2

PP1V2_SOC

0.00

0%

1/32W

MF

01005

ROOM=SOC

21

VDD12_PCIE_REFBUF:1.08V - 1.26V @ 30mA MAX

1

C1198

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

AM31

AP26

AN26

VDD12_PCIE_REFBUF

VDD12_PCIE_REFBUF

AM29

VDD18_PCIE

VDD18_PCIE

AN30

VDD_FIXED_PCIE_ANA

ROOM=SOC

U1000

AP27

AP31

AP29

VDD_FIXED_PCIE_ANA

VDD_FIXED_PCIE_ANA

AM27

VDD_FIXED_PCIE_REFBUF

VDD_FIXED_PCIE_REFBUF

1

C1199

4UF

20%

6.3V

2

CER-X5R

0201

ROOM=SOC

PP0V8_SOC_FIXED_PCIE_REFBUF

1

C1194

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

R1194

0.00

1/32W

01005

ROOM=SOC

21

0%

MF

VDD_FIXED_PCIE_REFBUF:0.765V - 0.84V @ 9mA MAX

VDD_FIXED_PCIE_ANA:0.765V - 0.84V @ 131mA MAX

1

C1193

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

1

C1192

1.0UF

20%

6.3V

2

X5R

0201-1

ROOM=SOC

1.62V - 1.98V @ 81mA MAX

PP1V8_IOPP1V2_SOC_PCIE_REFBUF

(Analog)

PP0V8_SOC_FIXED_S1

1

C1191

4UF

20%

6.3V

2

CER-X5R

0201

ROOM=SOC

43 35 34 32 30

17 14 13 9 8 6

29 28 27 17 16 14 10 8 7 6 5

TMIT78B0-C4

WLCSP

D

C

B

16

IN

16

IN

16

OUT

16

PCIE LINK 0

OUT

90_PCIE_NAND_TO_AP_RXD_P

90_PCIE_NAND_TO_AP_RXD_N

90_PCIE_AP_TO_NAND_TXD_P

90_PCIE_AP_TO_NAND_TXD_N

0.22UF

0.22UF

0.22UF

0.22UF

2 1

6.3V

01005

ROOM=SOC

2 1

6.3V 20%

01005

ROOM=SOC

2 1

6.3V 20%

01005

ROOM=SOC

2 1

6.3V

01005

ROOM=SOC

20%

X5R

C1101

X5R

C1102

X5R

C1103

20%

X5R

C1100

GND_VOID

GND_VOID

GND_VOID

GND_VOID

16 7

16 4

16 4

16 7

PCIE_NAND_BI_AP_CLKREQ_L

BI

90_PCIE_AP_TO_NAND_REFCLK_P

OUT

90_PCIE_AP_TO_NAND_REFCLK_N

OUT

90_PCIE_NAND_TO_AP_RXD_C_P

90_PCIE_NAND_TO_AP_RXD_C_N

90_PCIE_AP_TO_NAND_TXD_C_P

90_PCIE_AP_TO_NAND_TXD_C_N

PCIE_AP_TO_NAND_RESET_L

OUT

NC

NC

NC

AL38

AW27

AV27

AV29

AW29

AY30

BA30

AJ37

AL37

AW26

AY26

PCIE_CLKREQ0*

PCIE_REF_CLK0_P

PCIE_REF_CLK0_N

PCIE_RX0_P

PCIE_RX0_N

PCIE_TX0_P

PCIE_TX0_N

PCIE_PERST0*

PCIE_CLKREQ1*

PCIE_REF_CLK1_P

PCIE_REF_CLK1_N

SYM 2 OF 16

LINK0

LINK3

PCIE_CLKREQ3*

PCIE_REF_CLK3_P

PCIE_REF_CLK3_N

PCIE_RX3_P

PCIE_RX3_N

PCIE_TX3_P

PCIE_TX3_N

PCIE_PERST3*

PCIE_CLKREQ2*

PCIE_REF_CLK2_P

PCIE_REF_CLK2_N

AJ36

AY24

BA24

BA36

AY36

AV35

AW35

AH36

AK37

AV25

AW25

PCIE_WLAN_BI_AP_CLKREQ_L

90_PCIE_AP_TO_WLAN_REFCLK_P

90_PCIE_AP_TO_WLAN_REFCLK_N

BI

OUT

OUT

90_PCIE_WLAN_TO_AP_RXD_C_P

90_PCIE_WLAN_TO_AP_RXD_C_N

90_PCIE_AP_TO_WLAN_TXD_C_P

90_PCIE_AP_TO_WLAN_TXD_C_N

PCIE_AP_TO_WLAN_RESET_L

PCIE_BB_BI_AP_CLKREQ_L

OUT

BI

50

50

50

50 7

C1130

GND_VOID

20%

X5R-CERM

C1131

GND_VOID

20%

X5R-CERM

C1132

GND_VOID

20%

X5R-CERM

C1133

50 7

GND_VOID

X5R-CERM

21

6.3V

01005

ROOM=SOC

21

6.3V

01005

ROOM=SOC

21

6.3V

01005

ROOM=SOC

21

6.3V20%

01005

ROOM=SOC

0.1UF

0.1UF

0.1UF

0.1UF

1

C1124

4.7PF

+/-0.1PF

16V

2

NP0-C0G

01005

ROOM=SOC

1

C1125

4.7PF

+/-0.1PF

16V

2

NP0-C0G

01005

ROOM=SOC

90_PCIE_WLAN_TO_AP_RXD_P

90_PCIE_WLAN_TO_AP_RXD_N

90_PCIE_AP_TO_WLAN_TXD_P

90_PCIE_AP_TO_WLAN_TXD_N

90_PCIE_AP_TO_BB_REFCLK_P

90_PCIE_AP_TO_BB_REFCLK_N

IN

IN

OUT

OUT

OUT

OUT

50

50

50

50

50

50

B

A

NC

NC

NC

NC

NC

AV31

AW31

AY32

BA32

AK38

AU30

AT30

PCIE_RX1_P

PCIE_RX1_N

PCIE_TX1_P

PCIE_TX1_N

PCIE_PERST1*

PCIE_EXT_REF_CLK_P

PCIE_EXT_REF_CLK_N

LINK1 LINK2

PCIE_RX2_P

PCIE_RX2_N

PCIE_TX2_P

PCIE_TX2_N

PCIE_PERST2*

PCIE_REXT

BA34

AY34

AV33

AW33

AJ38

AU32

90_PCIE_BB_TO_AP_RXD_C_P

90_PCIE_BB_TO_AP_RXD_C_N

90_PCIE_AP_TO_BB_TXD_C_P

90_PCIE_AP_TO_BB_TXD_C_N

PCIE_AP_TO_BB_RESET_L

AP_PCIE_RCAL

1

R1150

200

1%

1/32W

MF

01005

2

ROOM=SOC

OUT

0.1UF

6.3V

ROOM=SOC

6.3V

ROOM=SOC

6.3V

ROOM=SOC

6.3V

ROOM=SOC

21

01005

21

01005

21

01005

21

01005

0.1UF

0.1UF

0.1UF

PAGE TITLE

90_PCIE_BB_TO_AP_RXD_P

90_PCIE_BB_TO_AP_RXD_N

90_PCIE_AP_TO_BB_TXD_P

90_PCIE_AP_TO_BB_TXD_N

OUT

OUT

50

IN

50

IN

PCIE LINK 2 PCIE LINK 3

50

50

SYNC_DATE=10/17/2016SYNC_MASTER=test_mlb

A

C1120

GND_VOID

20%

X5R-CERM

C1121

GND_VOID

20%

X5R-CERM

C1122

GND_VOID

20%

X5R-CERM

C1123

50 7

GND_VOID

20%

X5R-CERM

SOC: PCIE

SIZE

D

Apple Inc.

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

DRAWING NUMBER

051-02221

REVISION

9.0.0

BRANCH

evt-1

PAGE

11 OF 80

SHEET

7 OF 51

8

67

35 4

2

1

678

3 245

1

D

SOC - MIPI & ISP INTERFACES

MIPI Lane & Polarity Swapping

17 14 13 9 7 6

(Analog)

0.765V - 0.84V @ 40mA MAX

PP0V8_SOC_FIXED_S1

20%

6.3V

1

2

C1290

0.1UF 2.2UF

X5R-CERM

01005

ROOM=SOC

C1291

2.2UF

20%

6.3V

X5R-CERM

0201

ROOM=SOC

ISP I2C0

29 28 27 17 16 14 10 8 7 6 5

43 35 34 32 30

1.62V - 1.98V @ 10mA MAX

PP1V8_IO

43 35 34 32

1

2

G14

G12

F13

F11

VDD18_MIPI

1

C1295

20%

6.3V

2

X5R-CERM

0201

ROOM=SOC

1

C1296

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

30 29 28 27 17 16 14 10 8 7 6 5

29 28 27 17 16 14 10 8 7 6 5

43 35 34 32 30

PP1V8_IO

29 8

I2C0_ISP_SCL

29 8

I2C0_ISP_SDA

ISP I2C1

PP1V8_IO

1

R1201

1.00K

5%

1/32W

MF

01005

2

ROOM=SOC

1

R1211

1.00K

5%

1/32W

MF

01005

2

ROOM=SOC

1

R1202

1.00K

5%

1/32W

MF

01005

2

ROOM=SOC

1

R1212

1.00K

5%

1/32W

MF

01005

2

ROOM=SOC

D

C

35

35

35

35

35

35

32

32

32

32

FCAM MIPI Juliet MIPI

32

32

43

43

43

43

43

43

43

43

90_MIPI_JULIET_TO_AP_DATA0_P

BI

90_MIPI_JULIET_TO_AP_DATA0_N

BI

90_MIPI_JULIET_TO_AP_DATA1_P

IN

90_MIPI_JULIET_TO_AP_DATA1_N

IN

90_MIPI_JULIET_TO_AP_CLK_N

IN

90_MIPI_JULIET_TO_AP_CLK_P

IN

90_MIPI_FCAM_TO_AP_DATA0_N

BI

90_MIPI_FCAM_TO_AP_DATA0_P

BI

90_MIPI_FCAM_TO_AP_DATA1_N

IN

90_MIPI_FCAM_TO_AP_DATA1_P

IN

90_MIPI_FCAM_TO_AP_CLK_P

IN

90_MIPI_FCAM_TO_AP_CLK_N

IN

90_MIPI_AP_TO_DISPLAY_DATA0_P

BI

90_MIPI_AP_TO_DISPLAY_DATA0_N

BI

90_MIPI_AP_TO_DISPLAY_DATA1_P

OUT

90_MIPI_AP_TO_DISPLAY_DATA1_N

OUT

90_MIPI_AP_TO_DISPLAY_DATA3_P

OUT

90_MIPI_AP_TO_DISPLAY_DATA3_N

OUT

90_MIPI_AP_TO_DISPLAY_DATA2_N

OUT

90_MIPI_AP_TO_DISPLAY_DATA2_P

OUT

Display MIPI

43

43

90_MIPI_AP_TO_DISPLAY_CLK_N

OUT

90_MIPI_AP_TO_DISPLAY_CLK_P

OUT

MAKE_BASE

MAKE_BASE

MAKE_BASE

MAKE_BASE

MAKE_BASE

MAKE_BASE

MAKE_BASE

MAKE_BASE

MAKE_BASE

MAKE_BASE

MAKE_BASE

MAKE_BASE

MAKE_BASE

MAKE_BASE

MAKE_BASE

MAKE_BASE

MAKE_BASE

MAKE_BASE

MAKE_BASE

MAKE_BASE

90_MIPI_JULIET_TO_AP_DATA0_P

90_MIPI_JULIET_TO_AP_DATA0_N

90_MIPI_JULIET_TO_AP_DATA1_P

90_MIPI_JULIET_TO_AP_DATA1_N

90_MIPI_JULIET_TO_AP_CLK_N

90_MIPI_JULIET_TO_AP_CLK_P

MIPI0C_REXT

8

MIPI1C_REXT

8

90_MIPI_FCAM_TO_AP_DATA0_N

90_MIPI_FCAM_TO_AP_DATA0_P

90_MIPI_FCAM_TO_AP_DATA1_N

90_MIPI_FCAM_TO_AP_DATA1_P

90_MIPI_FCAM_TO_AP_CLK_P

90_MIPI_FCAM_TO_AP_CLK_N

90_MIPI_AP_TO_DISPLAY_DATA1_P

90_MIPI_AP_TO_DISPLAY_DATA1_N

90_MIPI_AP_TO_DISPLAY_DATA3_P

90_MIPI_AP_TO_DISPLAY_DATA3_N

90_MIPI_AP_TO_DISPLAY_DATA2_N

90_MIPI_AP_TO_DISPLAY_DATA2_P

90_MIPI_AP_TO_DISPLAY_CLK_N

90_MIPI_AP_TO_DISPLAY_CLK_P

B12

A12

B14

A14

A13

B13

D12

D13

B17

A17

B15

A15

A16

B16

A10

B10

B9

A9

A7

B7

A6

B6

A8

B8

MIPI0C_DPDATA0

MIPI0C_DNDATA0

MIPI0C_DPDATA1

MIPI0C_DNDATA1

MIPI0C_DPCLK

MIPI0C_DNCLK

MIPI0C_REXT

MIPI1C_REXT

MIPI1C_DPDATA0

MIPI1C_DNDATA0

MIPI1C_DPDATA1

MIPI1C_DNDATA1

MIPI1C_DPCLK

MIPI1C_DNCLK

MIPID_DPDATA0

MIPID_DNDATA0

MIPID_DPDATA1

MIPID_DNDATA1

MIPID_DPDATA2

MIPID_DNDATA2

MIPID_DPDATA3

MIPID_DNDATA3

MIPID_DPCLK

MIPID_DNCLK

VDD_FIXED_MIPI

U1000

TMIT78B0-C4

WLCSP

SYM 3 OF 16

ROOM=SOC

ISP_I2C0_SCL

ISP_I2C0_SDA

ISP_I2C1_SCL

ISP_I2C1_SDA

ISP_I2C2_SCL

ISP_I2C2_SDA

ISP_I2C3_SCL

ISP_I2C3_SDA

SENSOR_INT

SENSOR0_CLK

SENSOR1_CLK

SENSOR2_CLK

SENSOR0_RST

SENSOR1_RST

SENSOR2_RST

SENSOR3_RST

SENSOR4_RST

SENSOR0_ISTRB

SENSOR1_ISTRB

W35

V38

W36

Y36

Y34

Y38

AA37

AB38

AB36

U38

R38

R37

V34

U35

AB34

AC37

AA35

V36

U36

NC

NC

I2C0_ISP_SCL

I2C0_ISP_SDA

I2C1_ISP_SCL

I2C1_ISP_SDA

I2C2_ISP_SCL

I2C2_ISP_SDA

I2C3_ISP_SCL

I2C3_ISP_SDA

RIGEL_TO_ISP_INT

OUT

BI

OUT

BI

OUT

BI

OUT

BI

IN

AP_TO_WIDE_CLK_R

AP_TO_TELE_CLK_R

AP_TO_FCAM_JULIET_RIGEL_CLK_R

AP_TO_JULIET_SHUTDOWN_L

AP_TO_TELE_SHUTDOWN_L

AP_TO_WIDE_SHUTDOWN_L

OUT

OUT

OUT

AP_TO_FCAM_SHUTDOWN_L

OUT

AP_DEBUG3

OUT

35

30

29

4