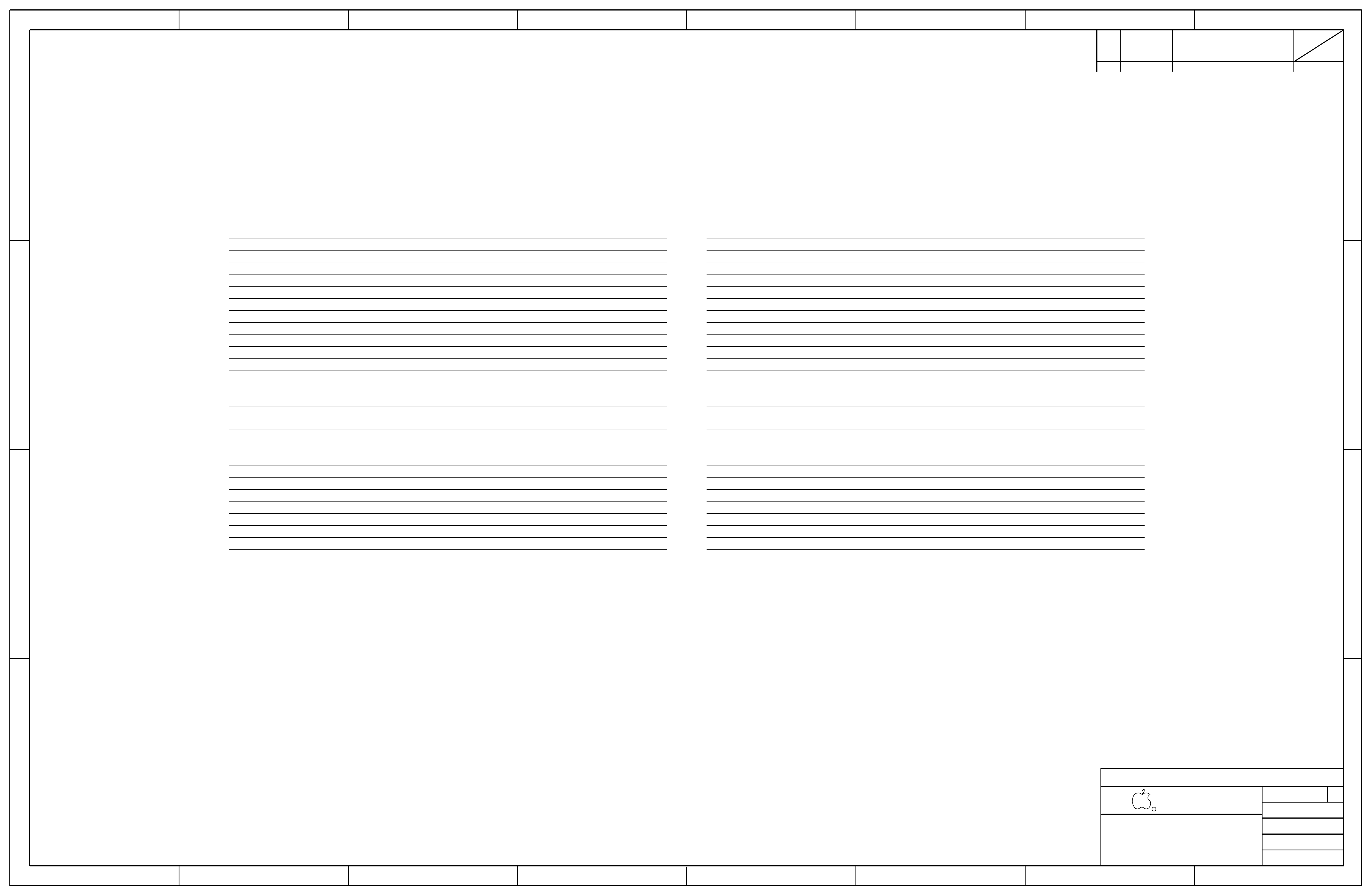

Apple iPhone 6S Plus Schematics

D

8

1. ALL RESISTANCE VALUES ARE IN OHMS, 0.1 WATT +/- 5%.

2. ALL CAPACITANCE VALUES ARE IN MICROFARADS.

3. ALL CRYSTALS & OSCILLATOR VALUES ARE IN HERTZ.

7

N66 MLB - EVT_MD

LAST_MODIFICATION=Tue Mar 24 12:47:11 2015

6 5 4 3

2 1

ECNREV DESCRIPTION OF REVISION

CK

APPD

DATE

2015-03-2700039807694 ENGINEERING RELEASED

D

C

PAGE DATE PAGE DATECONTENTS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

<CSA>

1

3

4

5

6

7

8

9

10

11

12

13

15

20

21

22

23

24

30

31

32

33

34

35

36

37

38

40

41

42

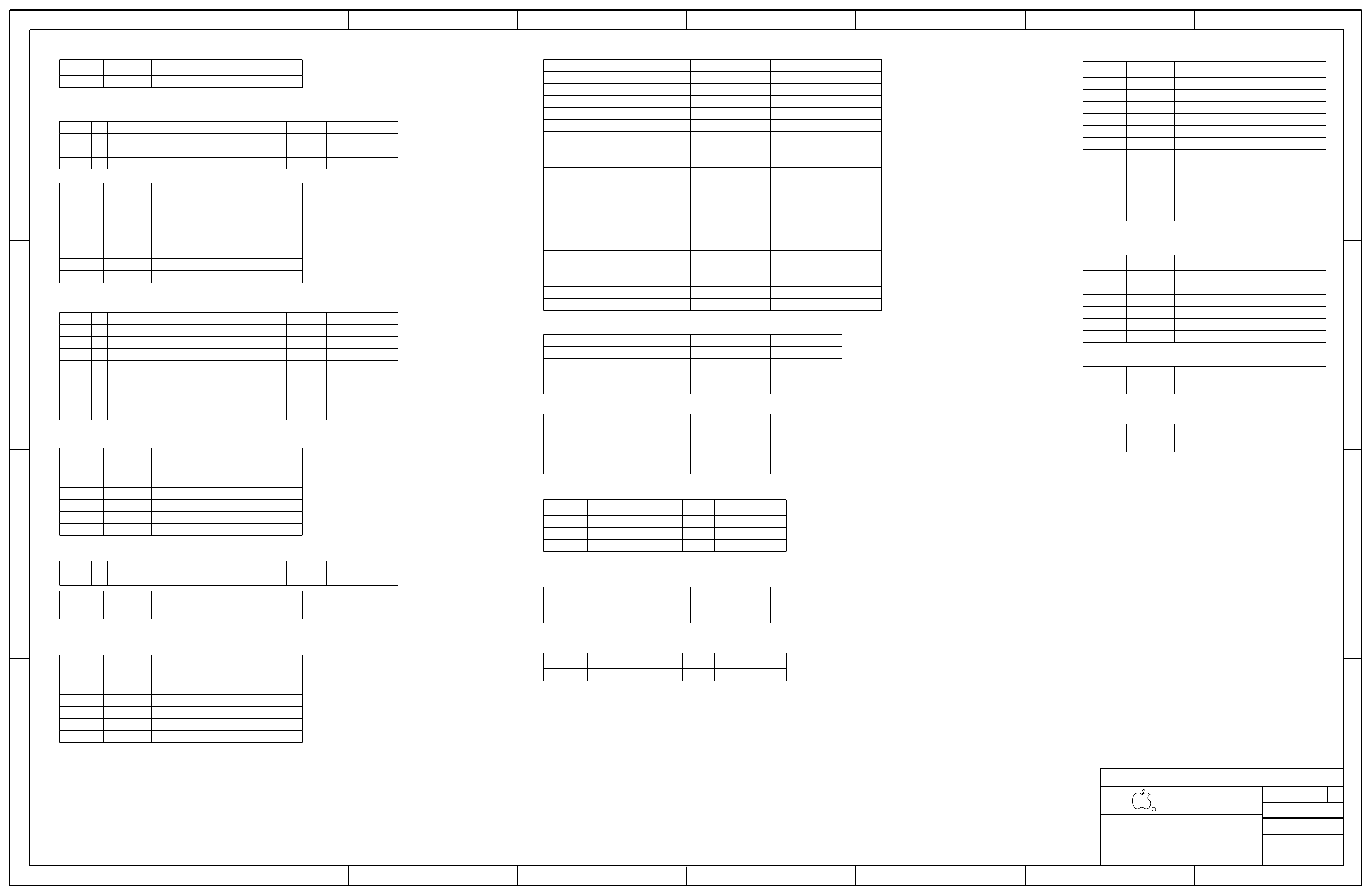

TABLE OF CONTENTS

SYSTEM:BOM TABLES

SYSTEM:N66 SPECIFIC

SYSTEM: MECHANICAL COMPONENTS

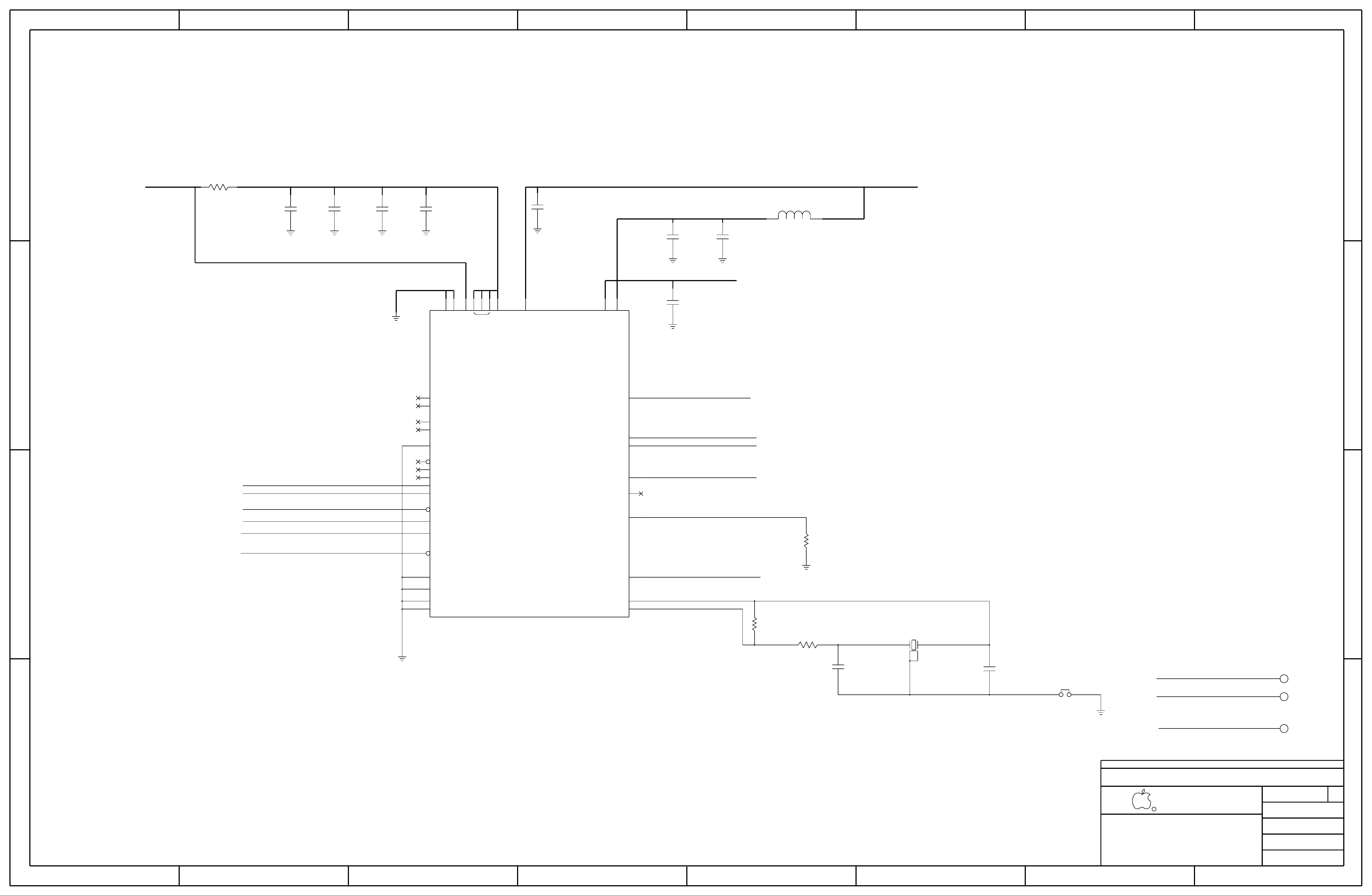

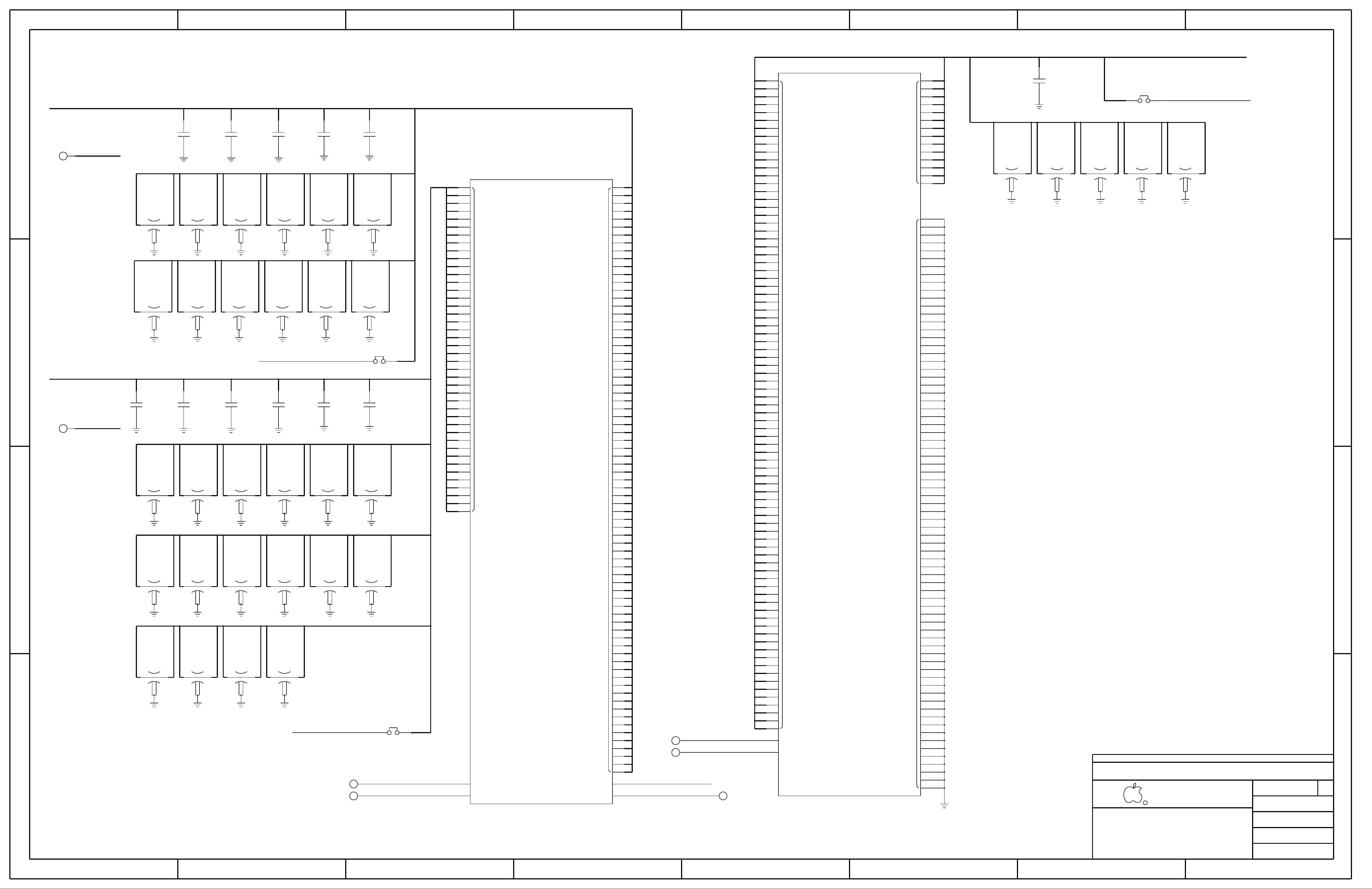

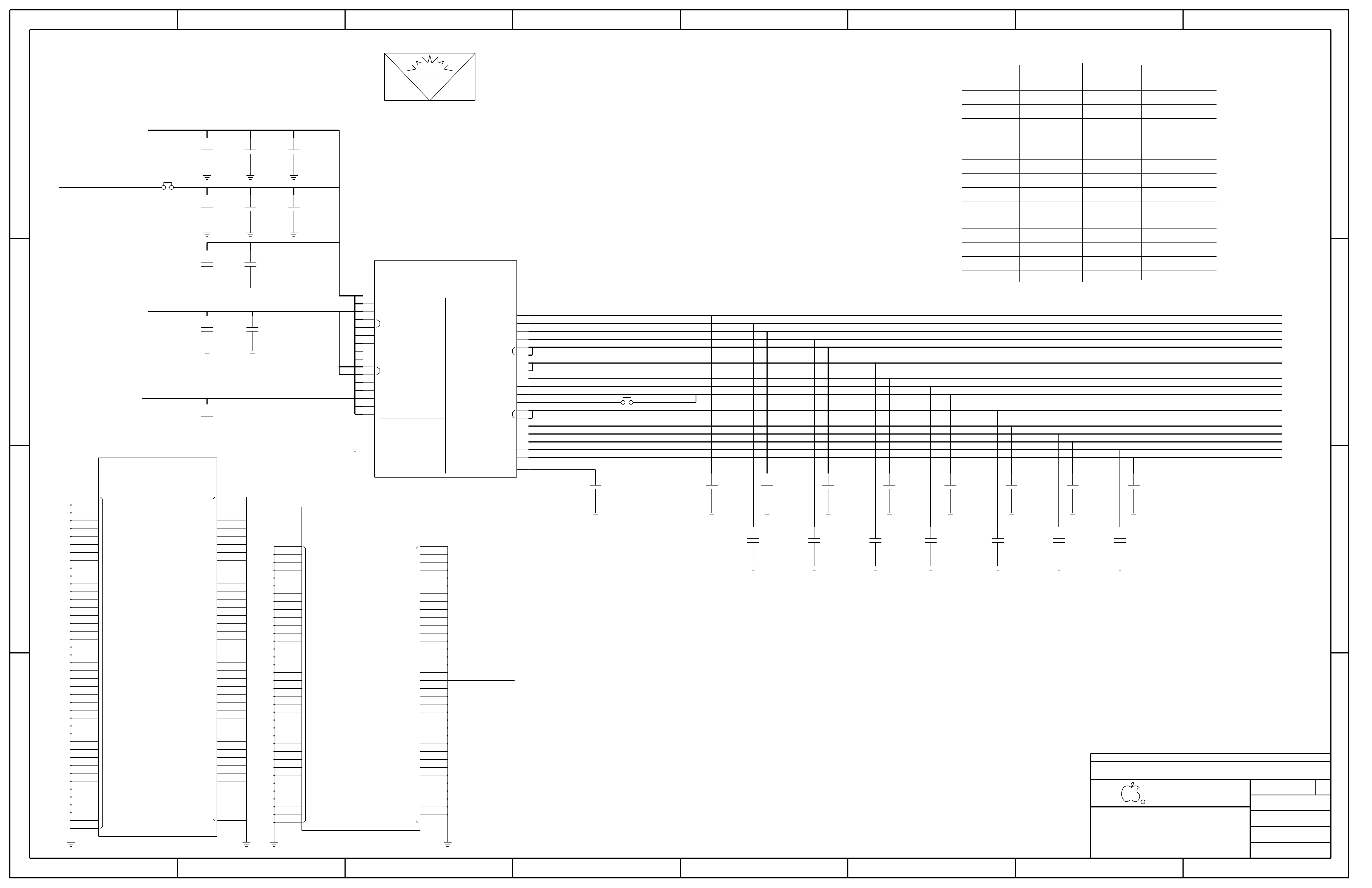

SOC:JTAG,USB,XTAL

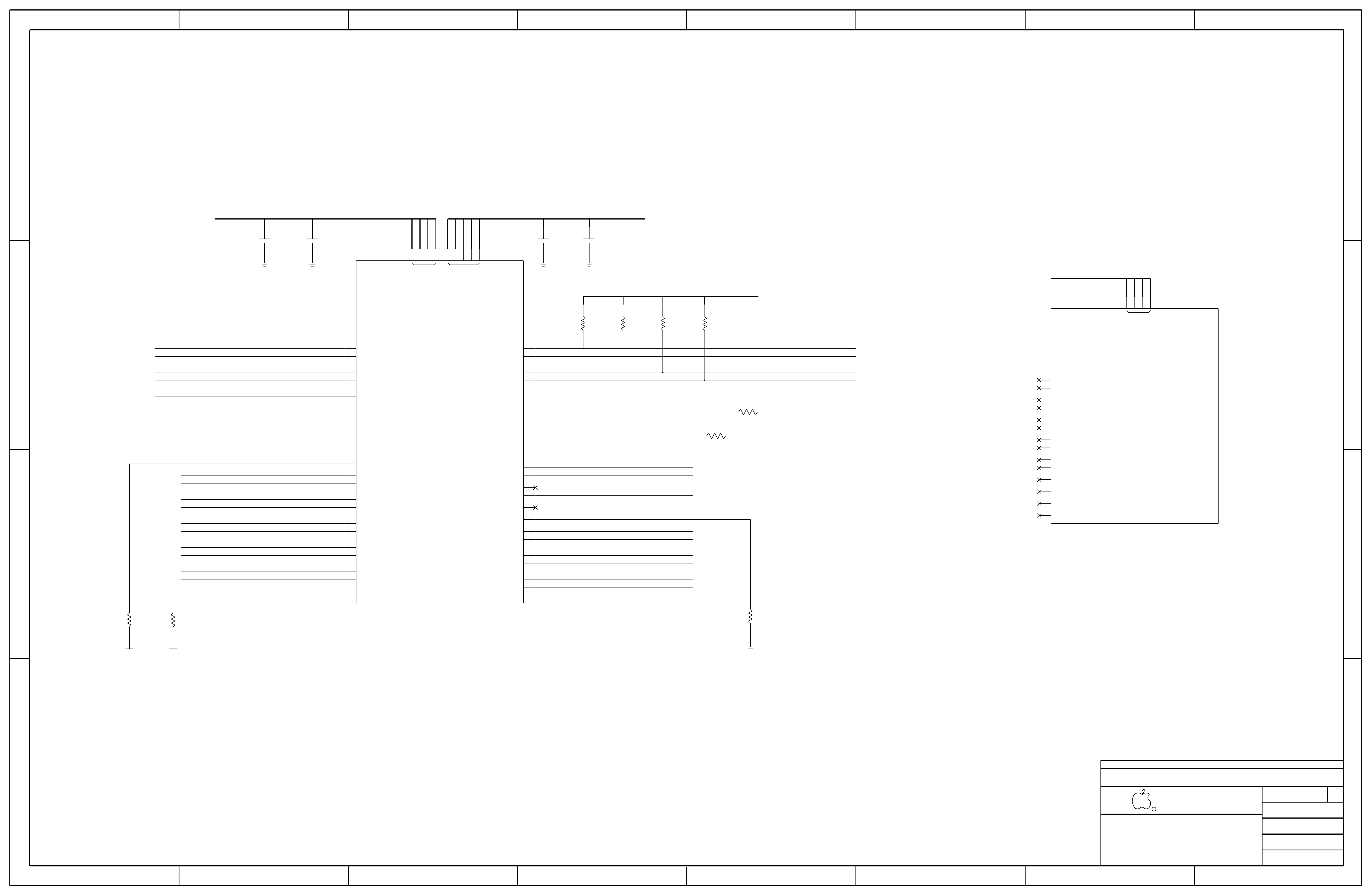

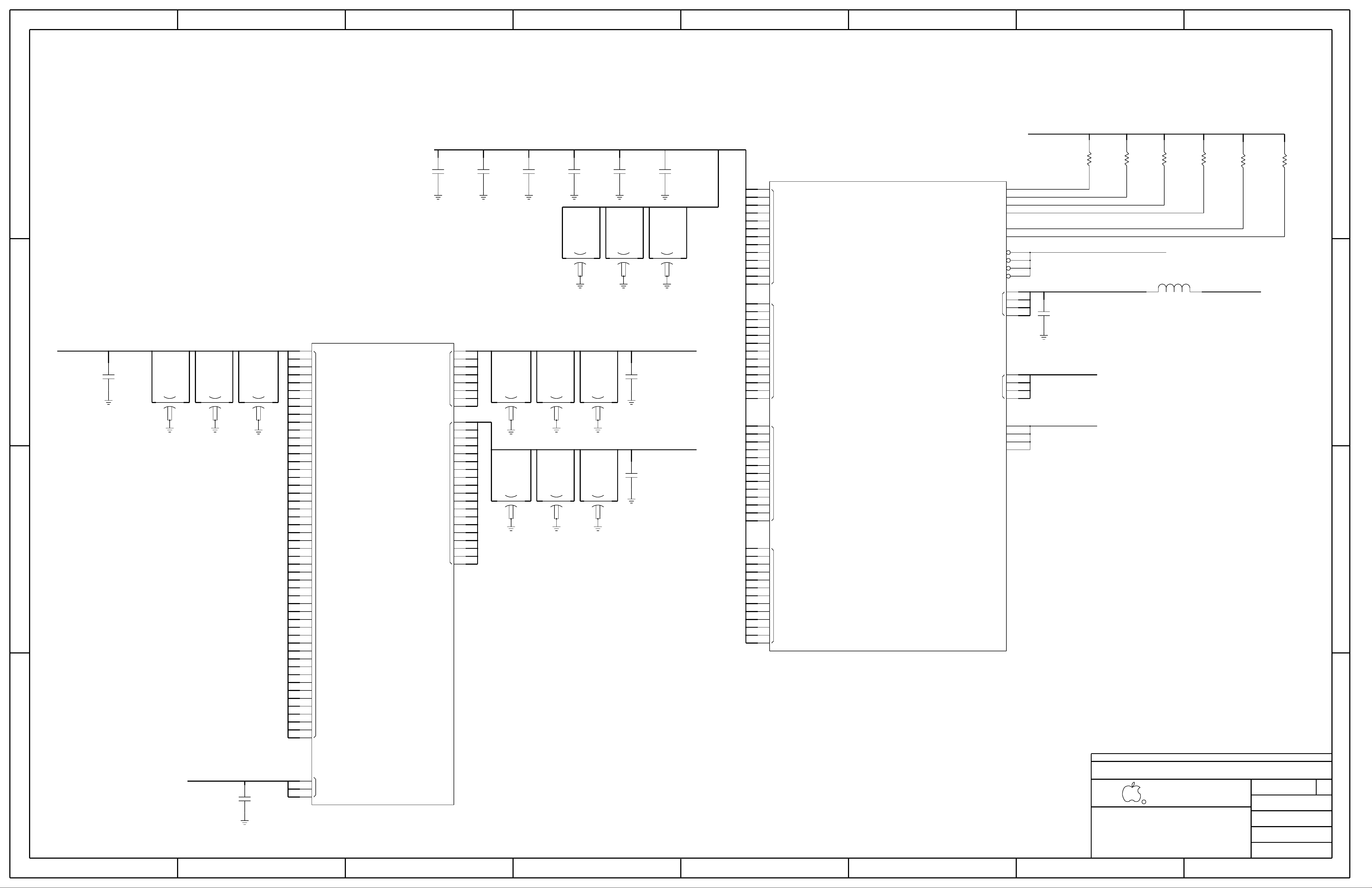

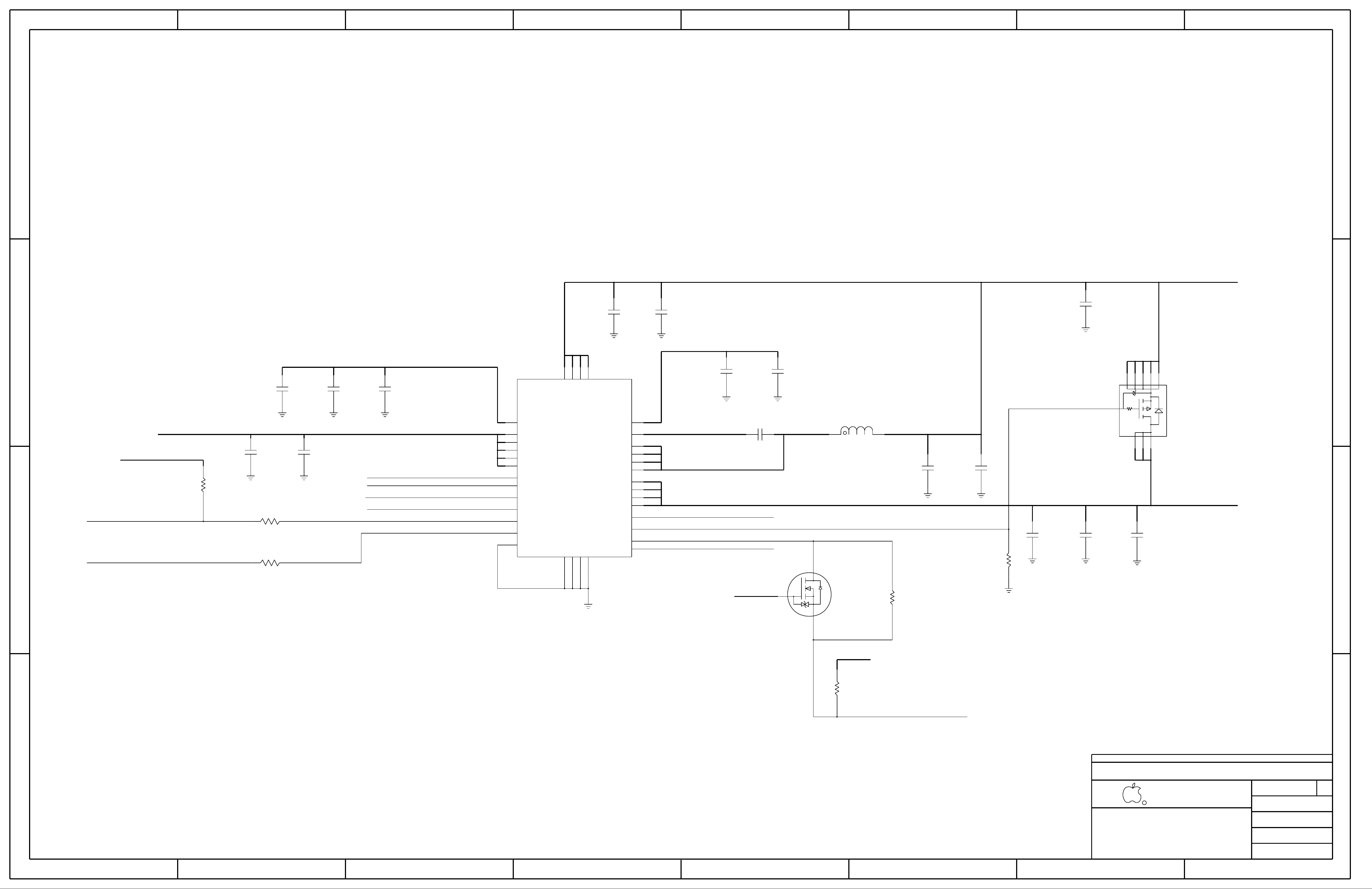

SOC:PCIE

SOC:CAMERA & DISPLAY

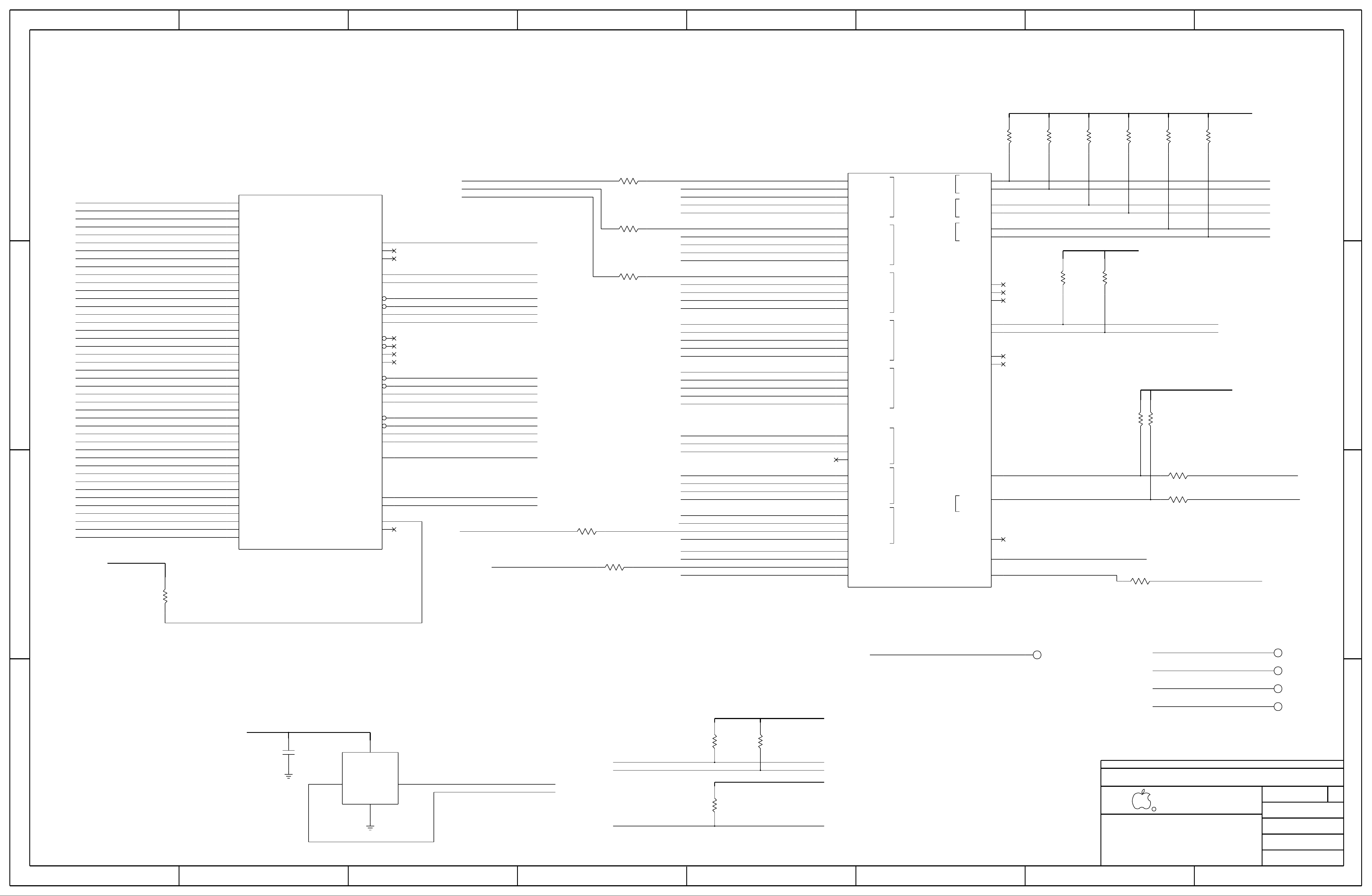

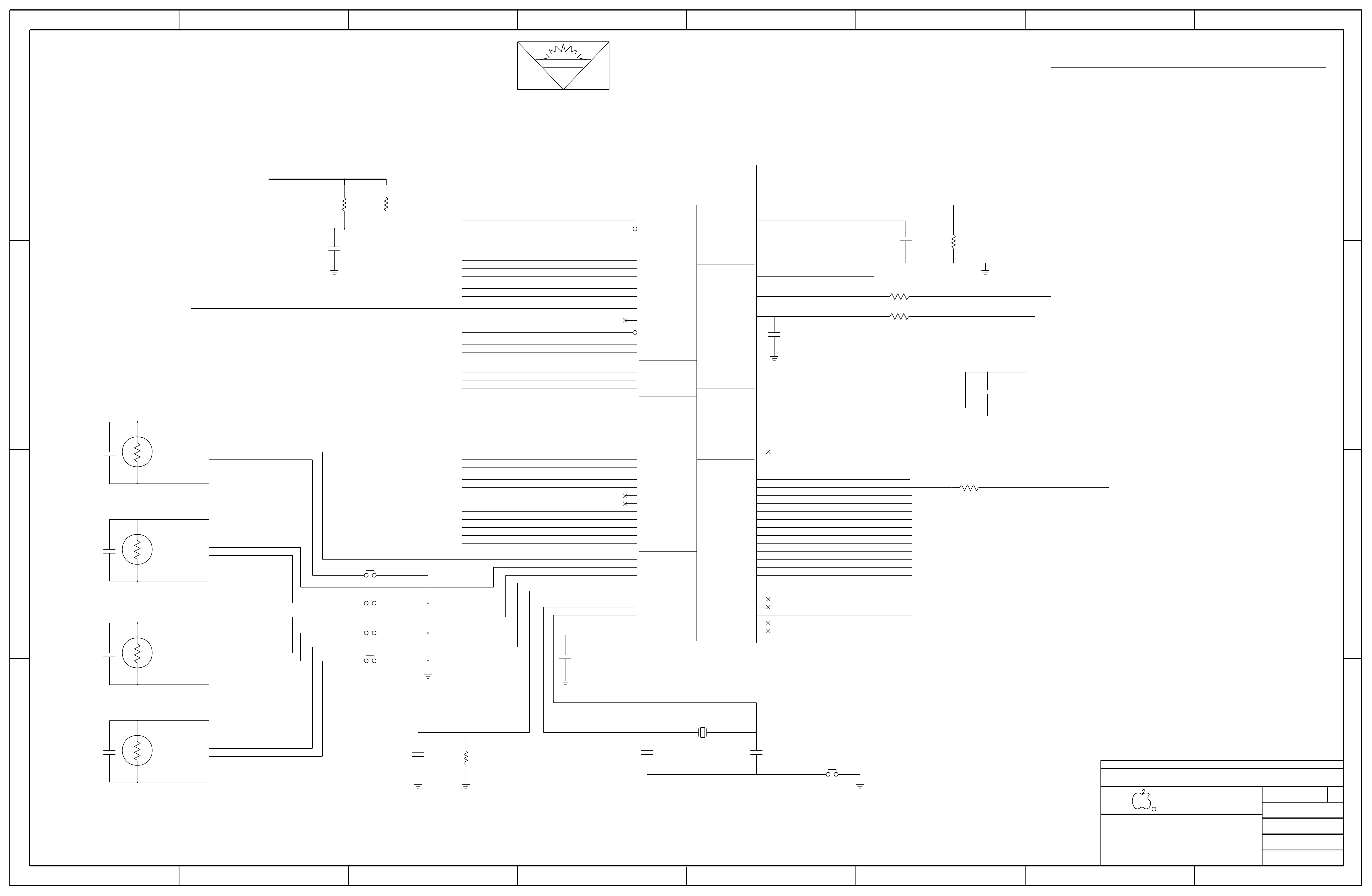

SOC:SERIAL & GPIO

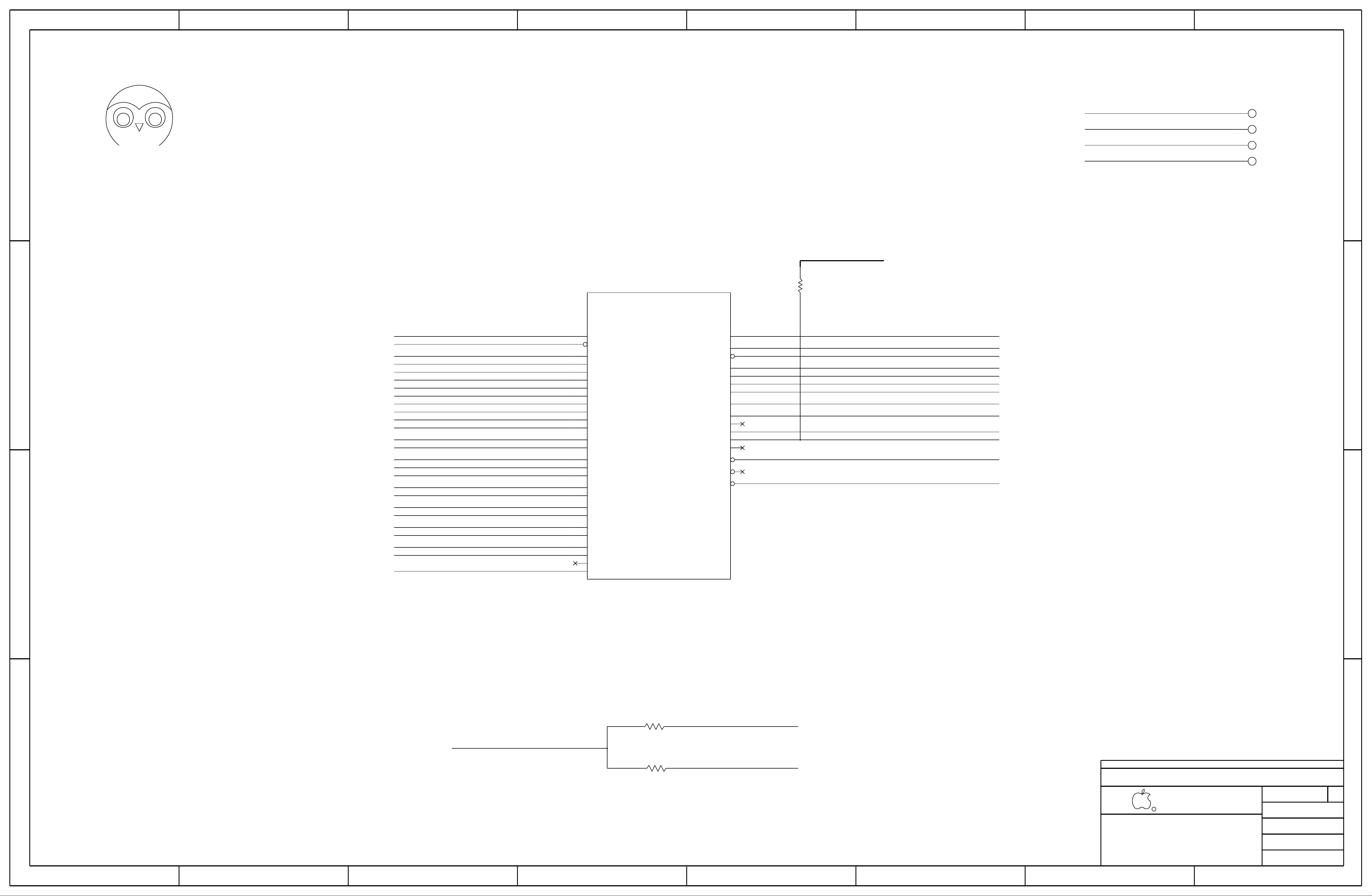

SOC:OWL

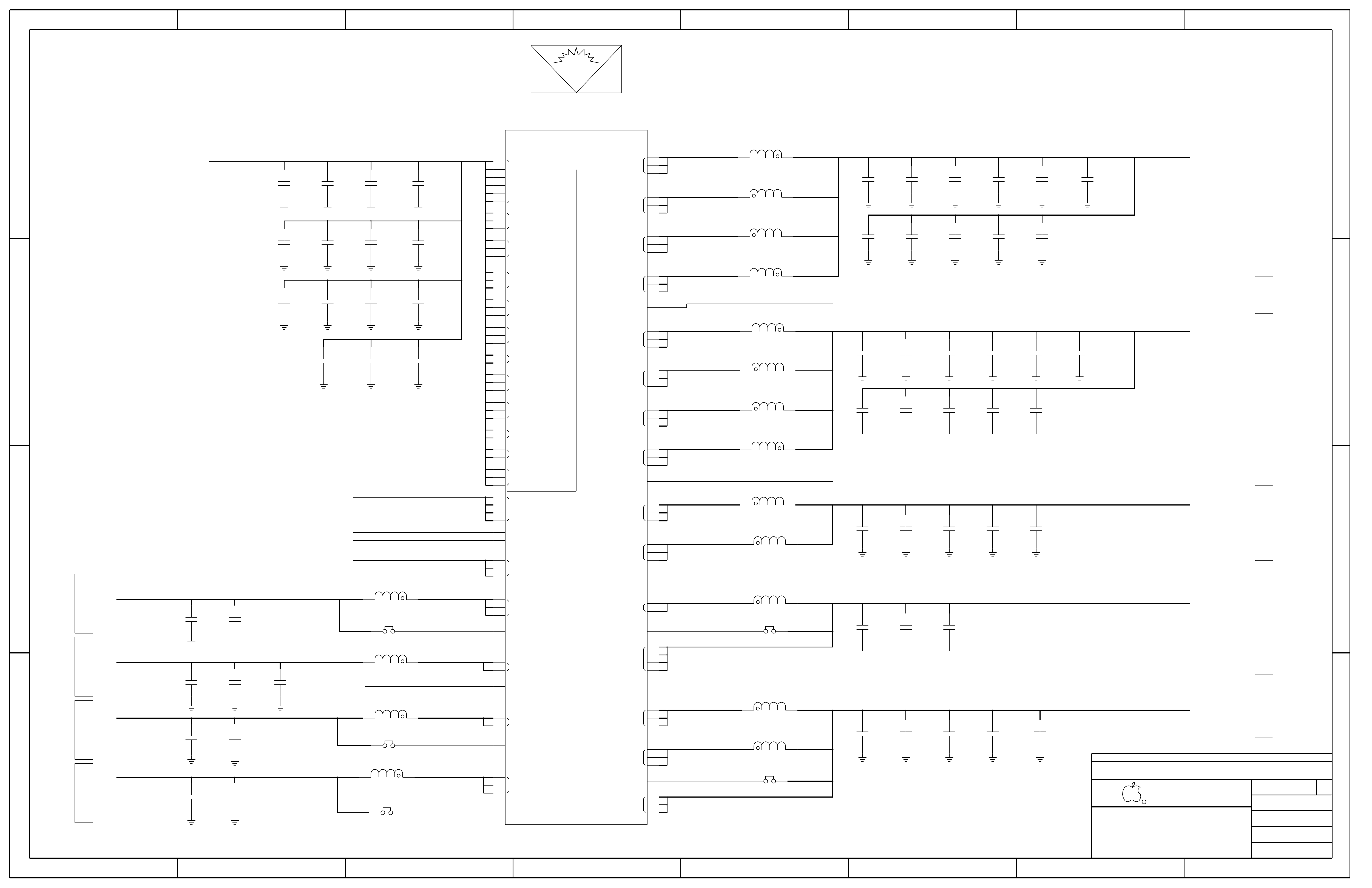

SOC:POWER (1/3)

SOC:POWER (2/3)

SOC:POWER (3/3)

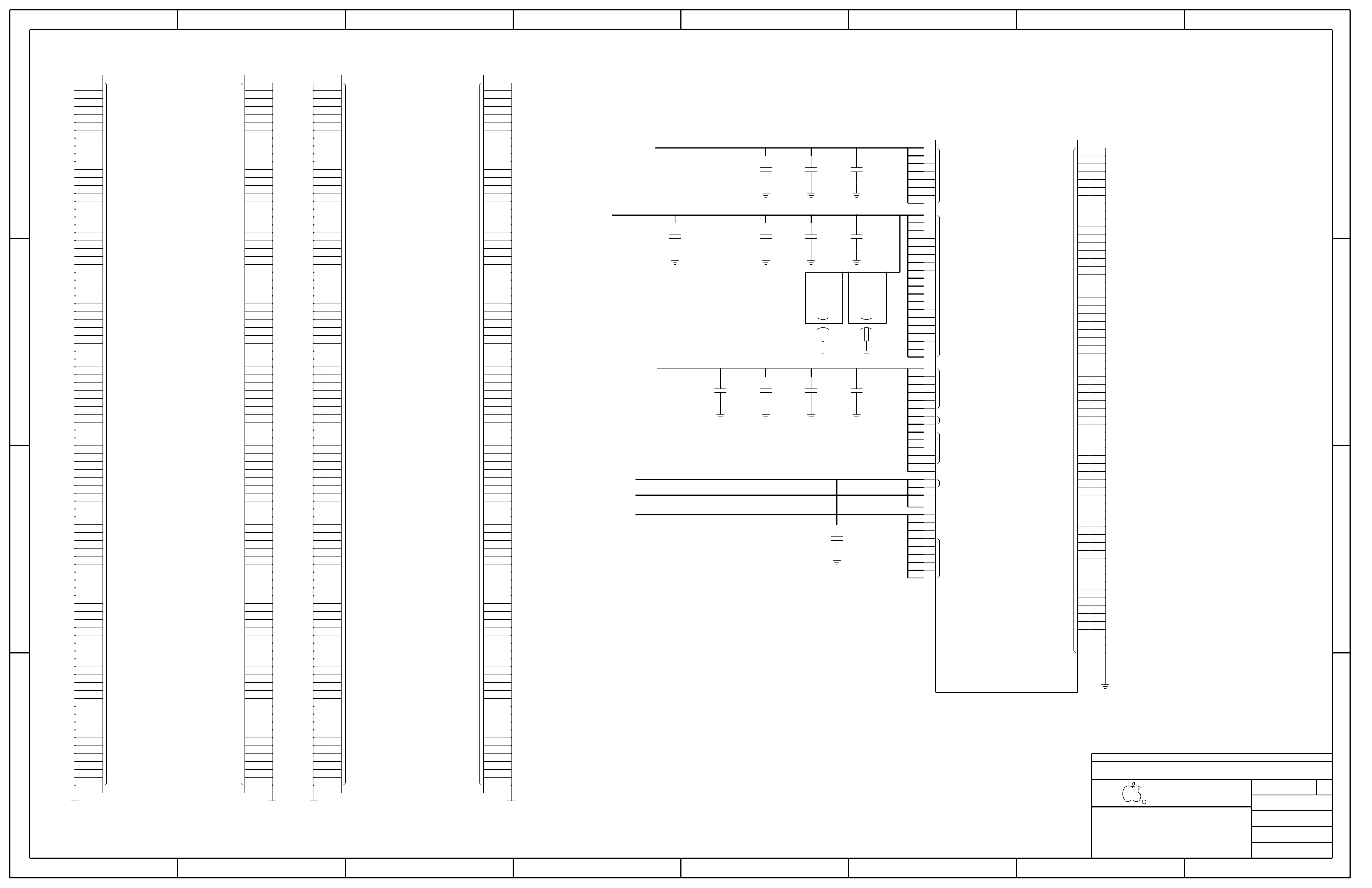

NAND

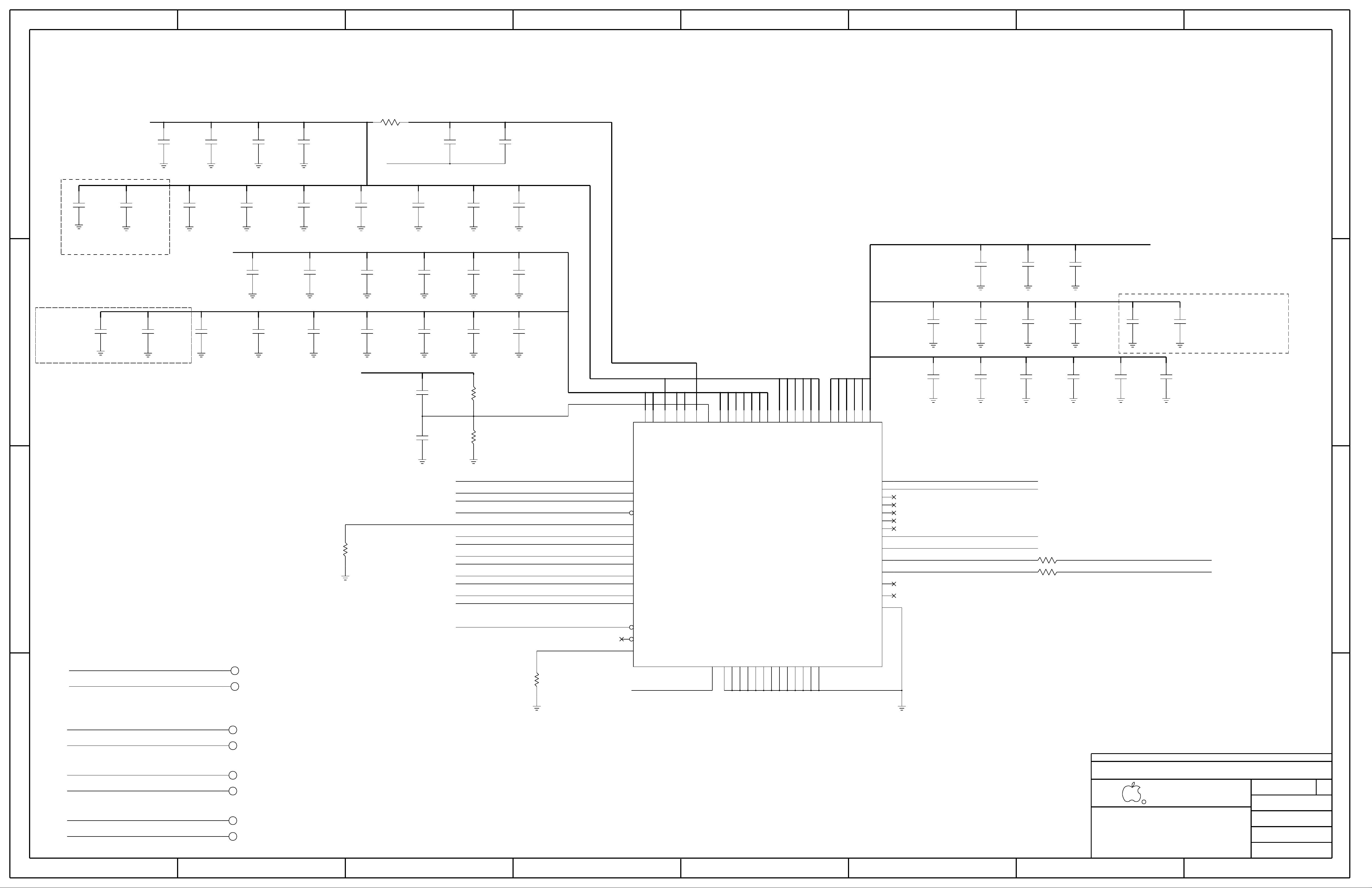

SYSTEM POWER:PMU (1/3)

SYSTEM POWER:PMU (2/3)

SYSTEM POWER:PMU (3/3)

SYSTEM POWER:CHARGER

SYSTEM POWER:BATTERY CONN

SENSORS:MOTION SENSORS

CAMERA:FRONT CAMERA B2B

CAMERA:REAR CAMERA B2B

CAMERA:STROBE DRIVER

CAMERA: SPHERE DRIVER

AUDIO:CALTRA CODEC (1/2)

AUDIO:CALTRA CODEC (2/2)

AUDIO:SPEAKER DRIVER

AUDIO:ARC DRIVER

DISPLAY:POWER

TOUCH:ORB & MESA B2B

DISPLAY:LCM B2B

36

31

32

33

34

35

37

38

39

40

41

42

43

44

45

46 CELLULAR PMU: ET MODULATOR

47

48

49

50

51

52

53

54

55

56

57

58

59

60

<CSA>

45

46

47

49

CONTENTS SYNCSYNC

I/O:TRISTAR 2

I/O:DOCK FLEX B2B

I/O:BUTTON FLEX B2B

BASEBAND:RADIO SYMBOL

TABLE OF CONTENTS

ELNA & UAT ANT FEED

CELLULAR FRONT END: ANTENNA CONNECTORS AND FEEDS

WLAN LAT 2.4GHZ BAW BPF

DEBUG CONN & TEST POINTS

CELLULAR BASEBAND: POWER1

CELLULAR BASEBAND: POWER2

CELLULAR BASEBAND: CONTROL AND INTERFACES

CELLULAR BASEBAND: GPIOS

CELLULAR PMU: CONTROL AND CLOCKS

CELLULAR PMU: SWITCHERS AND LDOS

CELLULAR TRANSCEIVER: POWER

CELLULAR TRANSCEIVER: PRX PORTS

CELLULAR TRANSCEIVER: DRX/GPS PORTS

CELLULAR TRANSCEIVER: TX PORTS

CELLULAR FRONT END: LB PAD

CELLULAR FRONT END: MB PAD

CELLULAR FRONT END: HB PAD

CELLULAR FRONT END: 2G PA

CELLULAR FRONT END: LB ASM

CELLULAR FRONT END: MB-HB ASM

CELLULAR FRONT END: DIVERSITY

SIM

WIFI/BT: WIFI/BT MODULE

STOCKHOLM

C

B

SCH 051-00094

BRD 820-00040

MCO 056-00472

BOM 639-00299 (BETTER)

BOM 639-00301 (ULTRA)

BOM 639-00302 (SUPREME)

BOM 639-01063 (BETTER, RF2)

BOM 639-01064 (ULTRA, RF2)

B

BOM 639-01119 (BETTER, M)

BOM 639-01122 (ULTRA, M)

BOM 639-01125 (SUPREME, M)

BOM 639-01120 (BETTER, RF2, M)

BOM 639-01123 (ULTRA, RF2, M)

A

BOM 639-01065 (SUPREME, RF2)

BOM 639-01116 (BETTER, RFC)

BOM 639-01117 (ULTRA, RFC)

BOM 639-01118 (SUPREME, RFC)

BOM 639-01126 (SUPREME, RF2, M)

BOM 639-01121 (BETTER, RFC, M)

BOM 639-01124 (ULTRA, RFC, M)

BOM 639-01127 (SUPREME, RFC, M)

3

TABLE OF CONTENTS

DRAWING TITLE

SCHEM,MLB,N66

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

051-00094

REVISION

4.0.0

BRANCH

PAGE

1 OF 49

SHEET

1 OF 60

1245678

A

SIZEDRAWING NUMBER

D

345678

2 1

D

C

Active Diode Alternate

TABLE_ALT_HEAD

PART NUMBER

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

TABLE_ALT_ITEM

376S00047376S00106 ALTERNATE Q2300 DIODES INC. ACT DIODE

NAND BOM Options

NAND,T,B0,1Y,MLC,16GX8,S3E,WLGA70

1 CRITICALU1500335S00039

NAND,T,B0,1Y,MLC,64GX8,S3E,VLGA70

NAND,H,B0,1Y,TLC,128GX8,S3E,VLGA70

PART NUMBER

335S00074 U1500 H, B0, 1Y, MLC, 16Gx8ALTERNATE335S00039

335S00040 ALTERNATE U1500 S, B0, 1Z, TLC, 64Gx8335S00064

335S00083 ALTERNATE U1500335S00079

335S00065 335S00079

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

U1500ALTERNATE335S00075 H, B0, 1Y, MLC, 64Gx8335S00040

U1500ALTERNATE335S00078 H, B0, 1Y, TLC, 64Gx8335S00040

ALTERNATE U1500

U15001335S00079

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

T, B0, 1Z, TLC, 64Gx8U1500ALTERNATE335S00040335S00082

T, B0, 1Z, TLC, 128Gx8

S, B0, 1Z, TLC, 128Gx8

CRITICAL1 U1500335S00040

CRITICAL

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

BOM OPTIONCRITICAL

NAND_16G

NAND_64G

NAND_128G

Carbon BOM Options

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

CRITICAL1338S1163 DISCRETE ACCEL, BOSCH U3030

338S1163 1 DISCRETE ACCEL, BOSCH U3030 CRITICAL

CARBON, INVENSENSE1338S00017 U3010 CRITICAL

C3013, 0.1UF, INVENSENSE OPTION

1 CRITICAL132S0395 C3013

338S00029 1 U3010 CRITICALCARBON, ST

1132S0391 C3013C3013, 0.01UF, ST OPTION

1338S00087 CARBON, INVENSENSE MPU-6800 U3010

1132S0395

C3013, 0.1UF, INVENSENSE OPTION

C3013

CRITICAL

CRITICAL

CRITICAL

BOM OPTIONCRITICAL

NOSTUFF

CARBON_INVENSENSE

CARBON_INVENSENSE

CARBON_INVENSENSE

CARBON_ST

CARBON_ST

CARBON_INVENSENSE_6800

CARBON_INVENSENSE_6800

Power Inductor Alternates

TABLE_ALT_HEAD

PART NUMBER

152S00074

152S00118 152S00075

$?152S00117 ALTERNATE

$?ALTERNATE

ALTERNATE152S00120 $?152S00077

ALTERNATE152S00081152S00121 $?

152S00123 ALTERNATE152S1936 $?

ALTERNATE152S1929

$?152S2052

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

TABLE_ALT_ITEM

IND,PWR,SHLD,1.0 UH,3.6A,0.060 OHM,2016

TABLE_ALT_ITEM

IND,PWR,SHLD,1.2 UH,3.0A,0.080 OHM,2016

TABLE_ALT_ITEM

IND,PWR,SHLD,1.0 UH,2.25A,0.150 OHM,2016

TABLE_ALT_ITEM

IND,PWR,SHLD,0.47 UH,3.8A,0.048 OHM,2012

TABLE_ALT_ITEM

IND,PWR,SHLD,15 UH,0.72A,0.900 OHM,3225

TABLE_ALT_ITEM

IND,MULT,1UH,1.2A,0.320 OHM,0603

TABLE_5_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

Schematic & PCB Callouts

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

1051-00094 SCH,SINGLE_BRD,N66

820-00040 PCBF,SINGLE_BRD,N66

825-6838 EEEE_G360 CRITICAL1

1 PCB CRITICAL

EEEE CODE FOR 639-00299

825-6838 CRITICAL1

EEEE CODE FOR 639-00302

EEEE CODE FOR 639-01063

EEEE CODE FOR 639-01064 EEEE_GKL0825-6838

1 CRITICAL

EEEE CODE FOR 639-01065

1825-6838 EEEE_GLL7

1825-6838

SCH CRITICAL

EEEE_G35WEEEE CODE FOR 639-00301

EEEE_G35V1 CRITICAL825-6838

EEEE_GKKY1 CRITICAL825-6838

CRITICALEEEE_GKL11825-6838

CRITICALEEEE CODE FOR 639-01116

EEEE_GLL4EEEE CODE FOR 639-01117

CRITICAL1825-6838

EEEE_GLL1 CRITICALEEEE CODE FOR 639-01118

1825-6838 CRITICALEEEE CODE FOR 639-01119 EEEE_GLL2

1825-6838 CRITICALEEEE_GLL3EEEE CODE FOR 639-01122

825-6838 1 EEEE_GLL6 CRITICAL

825-6838 1 EEEE CODE FOR 639-01120 EEEE_GLL8

825-6838 1 EEEE_GLL0 CRITICAL

825-6838 1 CRITICAL

825-6838 EEEE CODE FOR 639-01124

EEEE CODE FOR 639-01125

CRITICAL

EEEE CODE FOR 639-01123

EEEE_GLLCEEEE CODE FOR 639-01126

1 CRITICALEEEE CODE FOR 639-01121825-6838

EEEE_GLKY

1 EEEE_GLL5 CRITICAL

EEEE CODE FOR 639-011271825-6838 EEEE_GLL9 CRITICAL

BOM OPTIONCRITICAL

?

?

EEEE_BETTER

EEEE_ULTRA

EEEE_SUPREME

EEEE_BETTER_RF2

EEEE_ULTRA_RF2

EEEE_SUPREME_RF2

EEEE_BETTER_RFC

EEEE_ULTRA_RFC

EEEE_SUPREME_RFC

EEEE_BETTER_M

EEEE_ULTRA_M

EEEE_SUPREME_M

EEEE_BETTER_RF2_M

EEEE_ULTRA_RF2_M

EEEE_SUPREME_RF2_M

EEEE_BETTER_RFC_M

EEEE_ULTRA_RFC_M

EEEE_SUPREME_RFC_M

PMU/SOC BOM Options

TABLE_5_HEAD

PART# DESCRIPTIONQTY

IC,PMU,ANTIGUA,A0,AI,200UBM,210SB,CSP380

1998-01699

RES,MF,100 OHM,1%,1/32W,01005

1118S0631

131S0307 1

PART# DESCRIPTIONQTY

998-02438 M1 U2000

118S00009 MR0730

CAP,CER,NP0/C0G,100PF,5%,16V,01005

DEV FUSED, H DRAM

1339S00057

IC,PMU,ANTIGUA,A1,ZJ,200UBM,210SB,CSP380

RES,MF,3.01KOHM,1%,1/32W,01005

1

CAP,CER,NP0/C0G,100PF,5%,16V,01005

1131S0307 C0730 NOSTUFF

M DEV FUSED, M DRAM

U0600 M1339S00067

BOM OPTIONREFERENCE DESIGNATOR(S)

TABLE_5_ITEM

PORU2000

TABLE_5_ITEM

PORR0730

TABLE_5_ITEM

PORC0730

TABLE_5_ITEM

PORU0600

TABLE_5_HEAD

BOM OPTIONREFERENCE DESIGNATOR(S)

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

Maui AP Alternates

TABLE_ALT_HEAD

PART NUMBER

339S00058 ALTERNATE DEV FUSED, M DRAMU0600339S00057

U0600339S00059 339S00057 ALTERNATE DEV FUSED, S DRAM

U0600339S00067 M DEV FUSED, M DRAM339S00068 ALTERNATE

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_5_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

Global Capacitor Alternates

PART NUMBER

118S0764 ALTERNATE

118S0717 ?

138S0702 ALTERNATE138S0657

138S0835 ALTERNATE ?138S00006

ALTERNATE138S00003138S00005

ALTERNATE138S00003138S00048

ALTERNATE138S0652138S0648 ?

ALTERNATE132S0436132S0400

138S0831 ?138S00032

138S00049 ALTERNATE

138S0831 ?

138S00024 ?138S0986

138S0706 ?

138S0945 ?

138S0739 ALTERNATE

138S0739 ALTERNATE

ALTERNATE

ALTERNATE

?

?

?

?

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

RES, 3.92K, 0.1%, 0201

CAP, X5R, 4.3UF, 4V, 0610

CAP, 3-TERM, 4.3UF, 4V, 0402

CAP,X5R,15UF,6.3V,0.65MM,0402,TAIYO

CAP,X5R,15UF,6.3V,0.65MM,0402,KYOCERA

CAP,X5R,4.7UF,6.3V,0.65MM,0402,TAIYO

CAP,X5R,0.22UF,6.3V,01005,TDK

CAP,X5R,2.2UF,6.3V,0201,TAIYO

CAP,X5R,2.2UF,6.3V,0201,KYOCERA

CAP,CER,3-TERM,7.5UF,20%,4V,0402,TAIYO/TDK

CAP,CER,1UF,20%,10V,X5R,0201,MURATA

CAP,CER,1UF,20%,10V,X5R,0201,KYOCERA

Global Ferrite Alternates

PART NUMBER

ALTERNATE ? IND, 1UH, 1.2A, 0603152S1929152S2052

ALTERNATE

ALTERNATE

ALTERNATE

ALTERNATE ? FLTR, 65 OHMS, 0605155S00009155S00012

ALTERNATE FERR, 70 OHMS, 01005?155S0941155S0960

?155S0453155S0773

?155S0511155S0653

?155S0581155S00067

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

FERR, 120OHM, 0.8OHM DCR, 01005

FERR, 33OHM, 0.09OHM DCR, 0201

FERR, 240OHM, 0.38OHM DCR, 0201

Global Varistor Alternates

PART NUMBER

ALTERNATE

?377S0140377S0168

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

VARISTOR, 6.8V, 100PF, 01005

DDR PLL Alternate

PART NUMBER

155S00068 ALTERNATE155S00095 FL1280

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

FERR BD,100OHM,25%,100MA,2OHM,01005

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_HEAD

TABLE_ALT_ITEM

D

C

B

SIM Callouts

REFERENCE DESIGNATOR(S)QTY DESCRIPTIONPART#

SIM, Integrated Eject, N66512S00013 CRITICAL1 J3001_RF

PART NUMBER

512S00015 512S00013 J3001_RF

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

SIM, INTEGRATED EJECT, N71ALTERNATE

NOTE: Revisit for Carrier

Shield Alternates

PART NUMBER

806-02349 SH0500ALTERNATE613-01503

ALTERNATE SH0501613-01504 806-02350

806-02655

806-02656 SH0504ALTERNATE

806-02352 SH0503ALTERNATE

806-02352 SH0503

ALTERNATE806-03410

806-02353

806-02353806-03411

SH0504ALTERNATE

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

Upper Front shield

Lower Front shield

Upper Back shield

Upper Back shield

Lower Back shield

Lower Back shield

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

BOM OPTIONCRITICAL

COMMON

TABLE_5_HEAD

TABLE_5_ITEM

Low Noise Caps

PART# DESCRIPTIONQTY

CAP,X5R,10UF,20%,6.3V,0.65MM,HRZTL,0402

CAP,X5R,10UF,20%,6.3V,0.65MM,0402,INTPOSER

C2085, C2086, C2087138S0867 3 CAPS_NORMAL

C2085, C2086, C2087998-01223

BOM OPTIONREFERENCE DESIGNATOR(S)

CAPS_LOW_NOISE3

SEP EEPROM Alternate

TABLE_ALT_HEAD

PART NUMBER

ALTERNATE

U0900335S0946335S00066

COMMENTS:REF DESBOM OPTIONPART NUMBER ALTERNATE FOR

TABLE_ALT_ITEM

IC,EEPROM,16KX8,1.8V,I2C,WLCSP4,ONSEMI

B

TABLE_5_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

A

NOTE: Revisit for Carrier

8 7 5 4 2 1

A

PAGE TITLE

SYSTEM:BOM TABLES

DRAWING NUMBER SIZE

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

051-00094

REVISION

4.0.0

BRANCH

PAGE

3 OF 49

SHEET

2 OF 60

36

D

345678

2 1

D

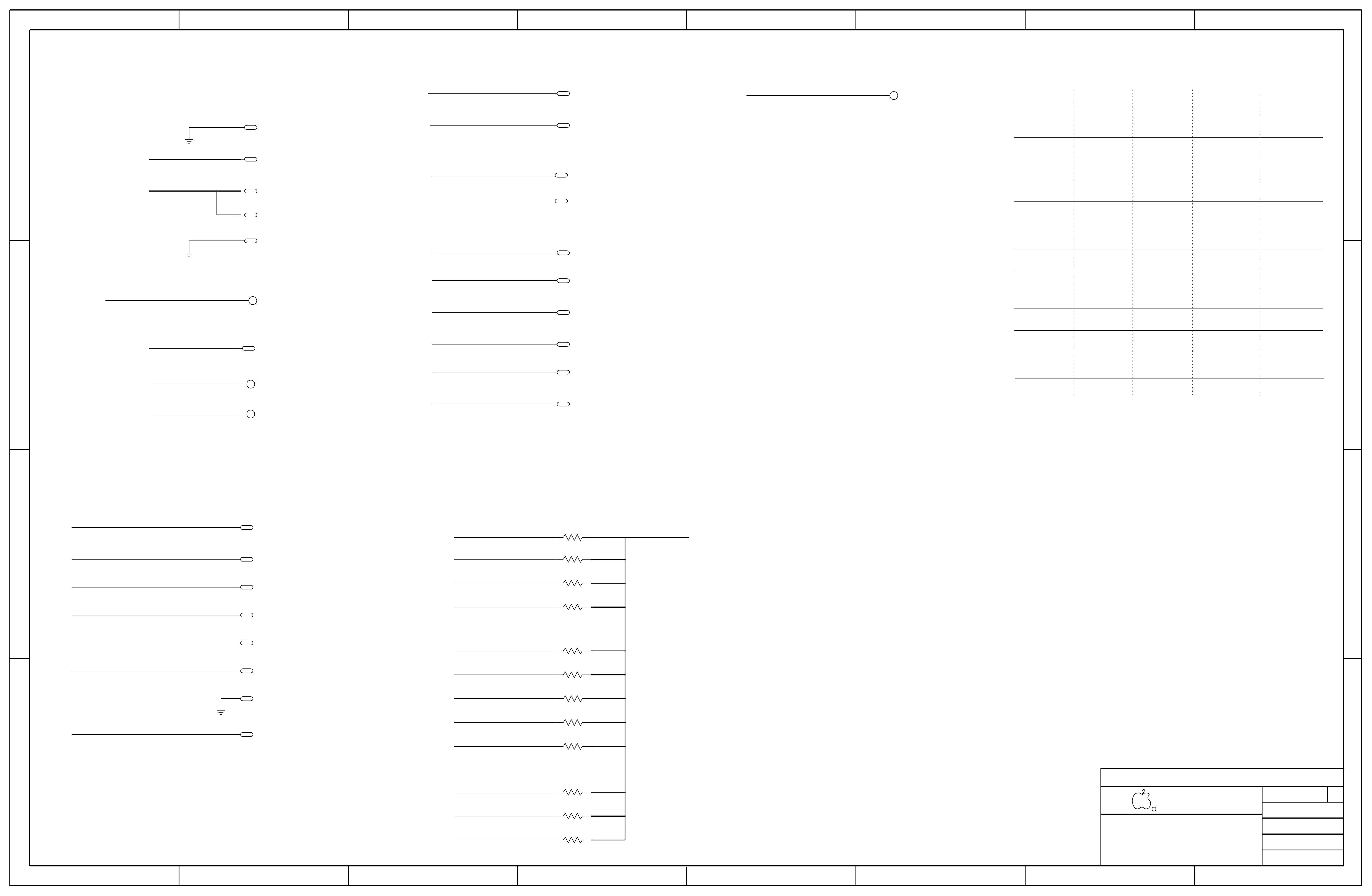

TESTPOINTS

32 31 17

PP5V0_USB

PP_BATT_VCC

18 17

POWER

VOLTAGE=0V

TP00

1

TP-P5

ROOM=TEST

TP01

1

TP-P55

ROOM=TEST

TP02

1

TP-P5

ROOM=TEST

TP03

1

TP-P5

ROOM=TEST

TP04

1

TP-P5

ROOM=TEST

A

POWER GROUND

A

VBUS

VBATT

A

A

A

POWER GROUND

PMU_AMUX_AY

16

PMU_AMUX_BY

16

MESA_TO_BOOST_EN

29 28

29 28

PP16V5_MESA

PP_LCM_BL_CAT1_CONN

30

AMUX

TP16

1

TP-P55

ROOM=TEST

TP17

1

TP-P55

ROOM=TEST

MOJAVE

TP18

1

TP-P55

ROOM=TEST

TP19

1

TP-P55

ROOM=TEST

LCM

TP20

1

TP-P55

ROOM=TEST

N66 I2C DEVICE MAP

I2C BUS

I2C0

DEVICE

ANTIGUA PMU

CHESTNUT

BACKLIGHT 1 1100011X 0XC4

BINARY

1110100X

0100111X

7-BIT HEX

0X74

0X27

0X62

8-BIT HEX

0XE8

0X4E

A

ANALOG MUX A OUTPUT

A

ANALOG MUX B OUTPUT

UAT GND Ring Opening

PP09

0.50MM

GND

SM

1

PP

ROOM=TEST

D

I2C1

TIGRIS

ARC DRIVER

A

TRISTAR

A

I2C2

ALS

DISP EEPROM

BACKLIGHT 2

A

LCM BACKLIGHT SINK1

OWL

UNUSED

1110101X

1000001X

1000000XSPEAKER AMP

0011010X

0101001X

1010001X

1100011X

N/A

0X75

0X41

0X40

0X1A

0X29

0X51

0X62

N/A

0XEA

0X82

0X80

0X34

0X52

0XA2

0XC4

N/A

C

34 16 9 5

21 20 17 14 13 12 9 8 7 6 5 3

PMU_TO_SYSTEM_COLD_RESET_L

34 8

34 30

34 8

FORCE_DFU

PP1V8

DFU_STATUS

RESET

PP06

P4MM-NSM

SM

1

PP

ROOM=TEST

DFU

TP07

1

TP-P55

ROOM=TEST

PP07

P4MM-NSM

SM

1

PP

ROOM=TEST

PP08

P4MM-NSM

SM

1

PP

ROOM=TEST

TP21

PP_LCM_BL_CAT2_CONN

30

1

TP-P55

ROOM=TEST

A

LCM BACKLIGHT SINK2

ISP I2C0

REAR CAM

LED DRIVER

TBD

1100011X

TBD

0X63

TBD

0XC6

SOC & BB RESET

TP22

PP_LCM_BL_ANODE_CONN

30

PP_LCM_BL_CAT3_CONN

30

A

FORCE DFU

PP_LCM_BL_CAT4_CONN

30

PP_LCM_BL34_ANODE_CONN

30

1

TP-P55

ROOM=TEST

TP23

1

TP-P55

ROOM=TEST

TP24

1

TP-P55

ROOM=TEST

TP25

1

TP-P55

ROOM=TEST

A

A

A

A

LCM BACKLIGHT SOURCE

LCM BACKLIGHT SINK3

LCM BACKLIGHT SINK4

LCM BACKLIGHT SOURCE (3/4)

ISP I2C1

TOUCH I2C

SEP I2C

FRONT CAM

MESON

MAMBA

DOPPLER

SEP EEPROM

0010000X

1000000X

1100000X

1011000X

1010001X

0X10

0x40

0x60

0x58

0x51

0X20

0x80

C

0xC0

0xB0

0xA2

B

32 31

32 31

32 31

32 31

TRISTAR_DP1_CONN_P

TRISTAR_DP1_CONN_N

TRISTAR_DP2_CONN_P

TRISTAR_DP2_CONN_N

E75

TP08

1

TP-P5

ROOM=TEST

TP09

1

TP-P5

ROOM=TEST

TP10

1

TP-P5

ROOM=TEST

TP11

1

TP-P5

ROOM=TEST

BOOTSTRAPPING:BOARD REV

BOARD ID

BOOT CONFIG

A

BOARD_REV3

8

BOARD_REV2

A

8

R0400

R0401

NOSTUFF

BOARD_REV1

8

A

R0402

01005 1/32W

NOSTUFF

BOARD_REV0

8

A

R0403

01005 1/32W

ROOM=SOC

1 2

MF 1/32W01005

5%

ROOM=SOC

1 2

MF

5%

ROOM=SOC

1 2

MF

5%

ROOM=SOC

1 2

MF

5%

1.00K

1.00K

1/32W01005

1.00K

1.00K

PP1V8

34 30

21 20 17 14 13 12 9 8 7 6 5 3

BOARD_REV[3:0]

FLOAT=LOW, PULLUP=HIGH

1111 PROTO1

1110 PROTO2

1101 EVT

SELECTED --> 1100 EVT-MD

XXXX CARRIER

XXXX DVT

B

A

32 31

32 31

32 31

PP_TRISTAR_ACC1

PP_TRISTAR_ACC2

TRISTAR_CON_DETECT_L

TP12

1

TP-P5

ROOM=TEST

TP13

1

TP-P5

ROOM=TEST

TP14

1

TP-P55

ROOM=TEST

TP15

1

TP-P55

ROOM=TEST

A

ACCESSORY ID AND POWER

BOARD_ID4

8

NOSTUFF

R0404

01005 MF 1/32W

ROOM=SOC

1 2

5%

1.00K

NOSTUFF

A

A

TP IS TO HELP WITH USB SI

BOARD_ID3

8

BOARD_ID2

8

R0405

01005

R0406

01005

ROOM=SOC

1 2

MF 1/32W

5%

ROOM=SOC

1 2

MF 1/32W

5%

IN THE FACTORY FIXTURE.

BOARD_ID1

8

A

FOR DIAGS

BOARD_ID0

8

R0407

01005

NOSTUFF

R0408

01005 1/32W

ROOM=SOC

1 2

MF

5%

ROOM=SOC

1 2

MF

5%

1.00K

1.00K

1.00K

1/32W

1.00K

SELECTED -->

BOARD_ID[4:0]

FLOAT=LOW, PULLUP=HIGH

00100 N71 MLB

00101 N71 DEV

00110 N66 MLB

00111 N66 DEV

A

PAGE TITLE

SYSTEM:N66 SPECIFIC

DRAWING NUMBER SIZE

Apple Inc.

R

051-00094

REVISION

4.0.0

BRANCH

PAGE

4 OF 49

SHEET

3 OF 60

D

BOOT_CONFIG2

8

BOOT_CONFIG1

8

BOOT_CONFIG0

8

NOSTUFF

R0409

01005

R0410

01005

R0411

ROOM=SOC

1 2

MF

5%

ROOM=SOC

1 2

MF 1/32W

5%

ROOM=SOC

1 2

MF

5%

1.00K

1/32W

1.00K

1.00K

1/32W01005

SELECTED -->

BOOT_CONFIG[2:0]

FLOAT=LOW, PULLUP=HIGH

000 SPI0

001 SPI0 TEST MODE

010 NVME0_X2

011 NVME0 X2 TEST

100 NVME0 X1

101 NVME0 X1 TEST

111 FAST SPI0

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

8 7 5 4 2 1

36

345678

2 1

D

C

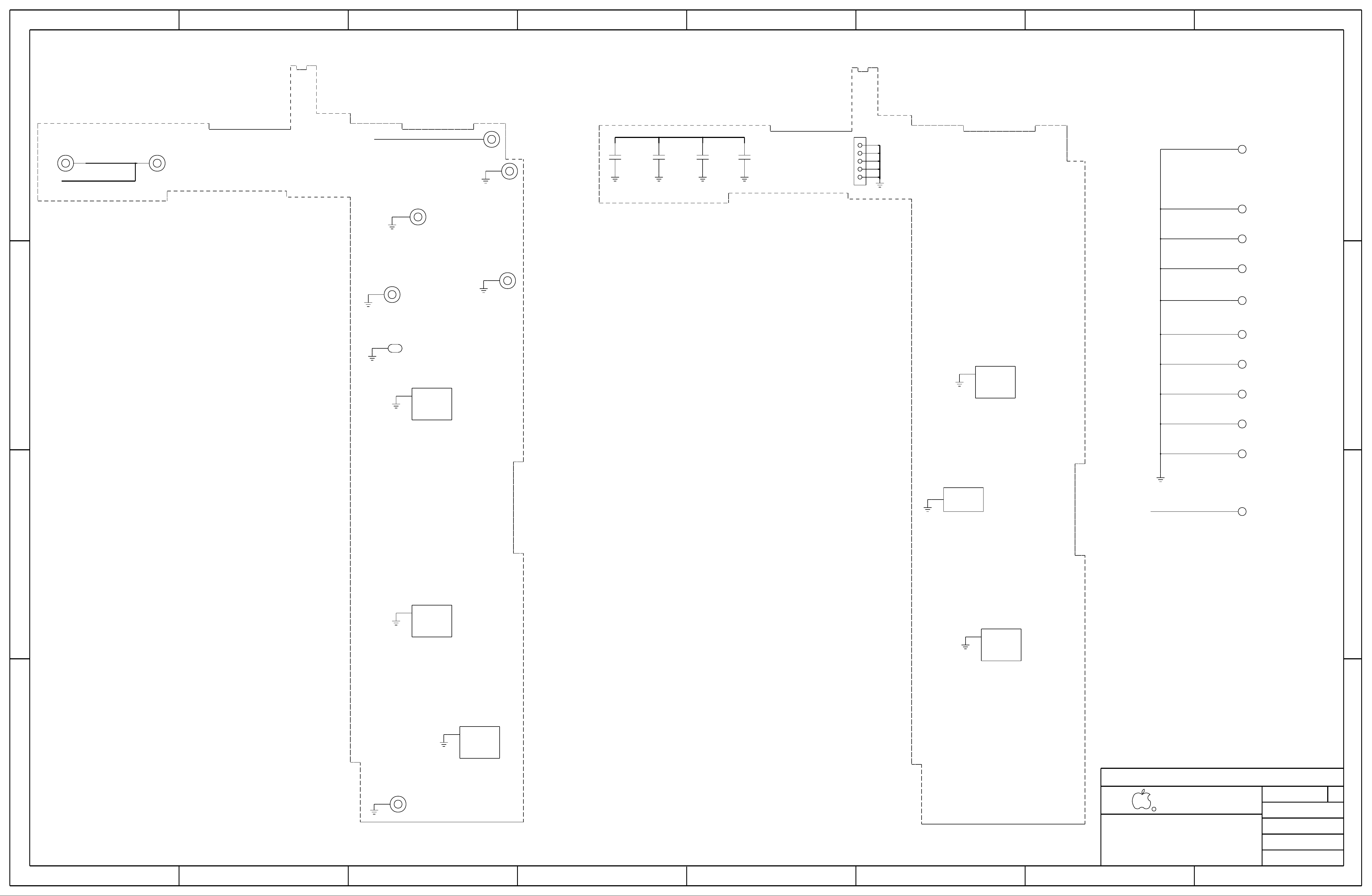

TUBE STANDOFF

860-00177

ROOM=ASSEMBLY

BS0530

STDOFF-2.6OD0.648H-TH

1

NORTH_AC_GND_SCREW

33 4

ROOM=ASSEMBLY

BS0531

STDOFF-2.6OD0.648H-TH

1

TOP SIDE

TUBE STANDOFF: STOCKHOLM FEED

AP_TO_STOCKHOLM_ANT

34

STDOFF-2.49OD1.4ID-1.25H-SM

BS0520

ROOM=ASSEMBLY

THREADED STANDOFF

860-00175

BS0510

STDOFF-2.9OD0.888H-SM

1

ROOM=ASSEMBLY

THREADED STANDOFF

THREADED STANDOFF

860-00175

BS0511

STDOFF-2.9OD0.888H-SM

1

ROOM=ASSEMBLY

PLATED SLOTTED THRU-HOLE

998-00099

CL0502

TH-NSP

1

SL-1.20X0.40-1.50X0.70-NSP

806-02349

SHLD-EMI-UPPER-FRONT-N66

1

SH0500

SM

ROOM=ASSEMBLY

860-5189

1

1

860-00175

BS0512

STDOFF-2.9OD0.888H-SM

1

ROOM=ASSEMBLY

TUBE STANDOFF

860-00176

BS0513

STDOFF-2.6OD0.808H

ROOM=ASSEMBLY

MLB NORTH PENINSULA AC CHASSIS SHORT

(BLOCKS DC CURRENT THROUGH COMPASS REGION)

NORTH_AC_GND_SCREW

33 4

1

C0550

220PF

10%

10V

2

X7R-CERM

01005

ROOM=ASSEMBLY

1

C0551

100PF

5%

16V

2

NP0-C0G

01005

ROOM=ASSEMBLY

1

C0552

100PF

5%

16V

2

NP0-C0G

01005

ROOM=ASSEMBLY

1

C0553

4.7PF

+/-0.1PF

16V

2

NP0-C0G

01005

ROOM=ASSEMBLY

TODO: TUNE AC CAPS FOR ANTENNA RF GND

BOTTOM SIDE

CL0501

SM

1

2

3

4

5

CLIP-BRACE-COAX-N66

COAX CLIP BRACE

806-02354

806-02352

SHLD-EMI-UPPER-BACK-N66

1

SH0503

SM

ROOM=ASSEMBLY

FIDUCIALS

FD0501

FID

0P5SM1P0SQ-NSP

1

FD0503

FID

0P5SM1P0SQ-NSP

1

FD0504

FID

0P5SM1P0SQ-NSP

1

FD0505

FID

0P5SM1P0SQ-NSP

1

FD0510

FID

0P5SQ-SMP3SQ-NSP

1

FD0511

FID

0P5SQ-SMP3SQ-NSP

1

FD0512

FID

0P5SQ-SMP3SQ-NSP

1

FD0513

FID

0P5SQ-SMP3SQ-NSP

1

FD0514

FID

0P5SQ-SMP3SQ-NSP

1

D

ROOM=ASSEMBLY

ROOM=ASSEMBLY

ROOM=ASSEMBLY

ROOM=ASSEMBLY

ROOM=ASSEMBLY

ROOM=ASSEMBLY

C

ROOM=ASSEMBLY

ROOM=ASSEMBLY

ROOM=ASSEMBLY

B

806-02350

SHLD-EMI-LOWER-FRONT-N66

DOUBLE COAX CLIP

806-01802

CLIP-RETENTION-COAX-DOUBLE

1

CL0500

SM

29 28 27 26 25 23 22 17 15 14

34

PP_VCC_MAIN

FD0515

0P5SQ-SMP3SQ-NSP

FID

1

ROOM=ASSEMBLY

FD0502

FID

0P5SM1P0SQ-NSP

1

ROOM=ASSEMBLY

B

A

1

SH0501

SM

ROOM=ASSEMBLY

TIGRIS/SPKR INDUCTOR SHIELD

806-02351

SHLD-EMI-SA-N66

1

SH0502

SM

ROOM=ASSEMBLY

806-02353

SHLD-EMI-LOWER-BACK-N66

1

SH0504

SM

ROOM=ASSEMBLY

A

PAGE TITLE

SYSTEM: MECHANICAL COMPONENTS

BS0500

STDOFF-2.6OD0.808H

SOUTH TUBE STANDOFF

1

860-00176

ROOM=ASSEMBLY

8 7 5 4 2 1

36

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

Apple Inc.

R

DRAWING NUMBER SIZE

REVISION

BRANCH

PAGE

SHEET

051-00094

4.0.0

5 OF 49

4 OF 60

D

MAUI - USB, JTAG, XTAL

345678

2 1

D

15 7 6

VDD12_PLL_LPDP:1.14-1.26V @2mA MAX

VDD12_PLL_SOC: 1.14-1.26V @12mA MAX

VDD12_PLL_CPU: 1.14-1.26V @2mA MAX

R0600

0.00

PP1V2 PP1V2_PLL

1 2

0%

1/32W

MF

01005

ROOM=SOC

VOLTAGE=1.2V

C0600

1

0.1UF

20%

2

6.3V

X5R-CERM

01005

ROOM=SOC

C0601

1

0.1UF

20%

2

6.3V

X5R-CERM

01005

ROOM=SOC

C0602

1

0.01UF

10%

2

6.3V

X5R

01005

ROOM=SOC

C0603

1

0.01UF

10%

2

6.3V

X5R

01005

ROOM=SOC

AP21

C15

F22

U20

T19

W19

AF13

AL21

C0612

1

0.1UF

20%

2

6.3V

X5R-CERM

01005

ROOM=SOC

AN20

PP1V8_XTAL

VOLTAGE=1.8V

AL34

C0611

1

0.1UF

20%

2

6.3V

X5R-CERM

01005

ROOM=SOC

PP3V3_USB

1

C0620

0.1UF

20%

6.3V

X5R-CERM

2

01005

ROOM=SOC

VDD18_USB: 1.71-1.89V @20mA MAX

VDD18_XTAL:1.62-1.98V @2mA MAX

FL0610

1KOHM-25%-0.2A

1 2

1

C0610

2.2UF

20%

6.3V

2

X5R-CERM

0201

ROOM=SOC

15

3.14-3.46V @5mA MAX

0201

ROOM=SOC

PP1V8

34

D

30 21 20 17 14 13 12 9 8 7 6 3

C

SWD_DOCK_BI_AP_SWDIO

31

SWD_DOCK_TO_AP_SWCLK

31

NC

NC

NC

NC

NC

NC

NC

AN22

AN21

C16

D15

Y32

AC32

AB31

AA32

AB32

AA31

VDD12_UH1_HSIC0

UH1_HSIC0_DATA

UH1_HSIC0_STB

UH2_HSIC1_DATA

UH2_HSIC1_STB

JTAG_SEL

JTAG_TRST*

JTAG_TDO

JTAG_TDI

JTAG_TMS

JTAG_TCK

VDD12_PLL_LPDP

VDD12_UH2_HSIC1

VDD18_USB

VDD12_PLL_CPU

VDD12_PLL_SOC

OMIT_TABLE

CRITICAL

U0600

MAUI-2GB-25NM-DDR-H

FCMSP

SC58980B0B-A040

SYM 1 OF 14

ROOM=SOC

VDD33_USB

VDD18_XTAL

ANALOGMUX_OUT

USB_D_P

USB_D_N

USB_VBUS

USB_ID

AP24

AT20

AT19

AP19

AR19

NC

AP_TO_PMU_AMUX_OUT

16

USB_AP_DATA_P

USB_AP_DATA_N

USB_VBUS_DETECT

17

C

31 5

31 5

B

34 16 9 3

31 28 16 9

16 5

13

PMU_TO_SYSTEM_COLD_RESET_L

PMU_TO_OWL_ACTIVE_READY

AP_TO_PMU_TEST_CLKOUT

AP_TO_NAND_RESET_L

AC31

H33

AR23

AN23

H32

AF6

AL22

AG25

COLD_RESET*

CFSB

TST_CLKOUT

S3E_RESET*

HOLD_RESET

TESTMODE

FUSE1_FSRC

FUSE2_FSRC

USB_REXT

WDOG

XI0

XO0

AP18

Y33

AK35

AL35

AP_TO_PMU_WDOG_RESET

XTAL_AP_24M_IN

XTAL_AP_24M_OUT

USB_REXT

16

1

R0650

511K

1%

1/32W

MF

01005

2

ROOM=SOC

1

R0640

200

1%

1/32W

MF

01005

2

ROOM=SOC

R0651

0.00

1 2

0%

1/32W

MF

01005

ROOM=SOC

24.000MHZ-30PPM-9.5PF-60OHM

SOC_24M_O

1

C0650

12PF

5%

16V

2

CERM

01005

ROOM=SOC

CRITICAL

ROOM=SOC

Y0600

1.60X1.20MM-SM

1 3

2 4

AP_XTAL_GND

VOLTAGE=0V

1

C0651

12PF

5%

16V

2

CERM

01005

ROOM=SOC

PCB: PLACE THIS XW

AT U1, NEAR XI/XO

XW0650

SHORT-10L-0.1MM-SM

1 2

ROOM=SOC

PROBE POINTS

USB_AP_DATA_P

31 5

USB_AP_DATA_N

31 5

B

SM

1

1

PP0600

PP

P3MM-NSM

ROOM=SOC

SM

PP0601

PP

P3MM-NSM

ROOM=SOC

A

AP_TO_PMU_TEST_CLKOUT

16 5

PAGE TITLE

SOC:JTAG,USB,XTAL

DRAWING NUMBER SIZE

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

8 7 5 4 2 1

36

REVISION

BRANCH

PAGE

SHEET

SM

1

PP0610

PP

P3MM-NSM

ROOM=SOC

SYNC_DATE=05/29/2014SYNC_MASTER=N71_SINGLE_BRD

051-00094

4.0.0

6 OF 49

5 OF 60

A

D

D

MAUI - PCIE INTERFACES

VDD12_PCIE_REFBUF:1.08-1.26V @50mA MAX

VDD12_PCIE_TXPLL: 1.08-1.32V @10mA MAX

VDD12_PCIE: 1.14-1.26V @115mA MAX

15 7 5

PP1V2

345678

VDD085_PCIE:0.802-TBDV @TBDmA MAX

PP_FIXED

2 1

14 11 7

D

C

PCIE_NAND_TO_AP_RXD0_P

13

PCIE_NAND_TO_AP_RXD0_N

13

PCIE_AP_TO_NAND_TXD0_P

13

PCIE_AP_TO_NAND_TXD0_N

13

PCIE_NAND_TO_AP_RXD1_P

13

PCIE_NAND_TO_AP_RXD1_N

PCIE LINK 0

13

PCIE_AP_TO_NAND_TXD1_P

13

PCIE_AP_TO_NAND_TXD1_N

13

1

C0740

2.2UF

20%

6.3V

2

X5R-CERM

0201

ROOM=SOC

1

C0741

1.0UF

20%

6.3V

2

X5R

0201-1

C0701

ROOM=SOC

X5R-CERM

C0702

ROOM=SOC

X5R-CERM

C0703

ROOM=SOC

X5R-CERM

C0704

ROOM=SOC

X5R-CERM

C0705

ROOM=SOC

X5R-CERM

C0706

ROOM=SOC

X5R-CERM

C0707

ROOM=SOC

X5R-CERM

C0708

ROOM=SOC

X5R-CERM

ROOM=SOC

1 2

20%

1 2

20%

1 2

20%

1 2

20%

1 2

20%

1 2

20%

1 2

20%

1 2

20%

6.3V

01005

6.3V

01005

6.3V

01005

6.3V

01005

6.3V

01005

6.3V

01005

6.3V

01005

6.3V

01005

1

C0742

2

0.1UF

0.1UF

0.1UF

0.1UF

0.1UF

0.1UF

0.1UF

0.1UF

1

C0743

0.1UF

20%

6.3V

X5R-CERM

01005

ROOM=SOC

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

PCIE_NAND_TO_AP_RXD0_C_P

PCIE_NAND_TO_AP_RXD0_C_N

PCIE_AP_TO_NAND_TXD0_C_P

PCIE_AP_TO_NAND_TXD0_C_N

PCIE_NAND_TO_AP_RXD1_C_P

PCIE_NAND_TO_AP_RXD1_C_N

PCIE_AP_TO_NAND_TXD1_C_P

PCIE_AP_TO_NAND_TXD1_C_N

1

C0731

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

PCIE_EXT_C

AP29

AM30

AN30

AT32

AR32

AM28

AN28

AT31

AR31

PCIE_EXT_C

PCIE_RX0_P

PCIE_RX0_N

PCIE_TX0_P

PCIE_TX0_N

PCIE_RX1_P

PCIE_RX1_N

PCIE_TX1_P

PCIE_TX1_N

AK28

AK25

AL24

AL27

AL26

VDD12_PCIE

VDD12_PCIE_TXPLL

MAUI-2GB-25NM-DDR-H

AJ26

AH28

AJ25

AL23

AJ29

AL29

VDD085_PCIE

VDD12_PCIE_REFBUF

OMIT_TABLE

CRITICAL

U0600

FCMSP

SC58980B0B-A040

SYM 2 OF 14

ROOM=SOC

AJ24

AK27

AJ27

PCIE_REF_CLK0_P

PCIE_REF_CLK0_N

PCIE_REF_CLK1_P

PCIE_REF_CLK1_N

PCIE_REF_CLK2_P

PCIE_REF_CLK2_N

PCIE_REF_CLK3_P

PCIE_REF_CLK3_N

PCIE_CLKREQ0*

PCIE_CLKREQ1*

PCIE_CLKREQ2*

PCIE_CLKREQ3*

AN35

AP35

AN34

AP34

AM32

AN32

AM31

AN31

AT11

AP12

AR12

AT12

1

C0752

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

NC

NC

NC

1

C0751

1.0UF

20%

6.3V

2

X5R

0201-1

ROOM=SOC

PCIE_AP_TO_NAND_REFCLK_P

PCIE_AP_TO_NAND_REFCLK_N

PCIE_AP_TO_WLAN_REFCLK_P

PCIE_AP_TO_WLAN_REFCLK_N

PCIE_AP_TO_BB_REFCLK_P

PCIE_AP_TO_BB_REFCLK_N

1

C0750

2.2UF

20%

6.3V

2

X5R-CERM

0201

ROOM=SOC

13

13

34

34

34

34

1

R0720

100K

5%

1/32W

MF

01005

2

ROOM=SOC

1

R0721

100K

5%

1/32W

MF

01005

2

ROOM=SOC

NOSTUFF

1

R0722

100K

5%

1/32W

MF

01005

2

ROOM=SOC

PP1V8

34

PCIE_NAND_TO_AP_CLKREQ_L

PCIE_WLAN_TO_AP_CLKREQ_L

PCIE_BB_BI_AP_CLKREQ_L

30 21 20 17 14 13 12 9 8 7 5 3

C

13

34

34

B

PCIE_WLAN_TO_AP_RXD_P

34

PCIE_WLAN_TO_AP_RXD_N

34

PCIE_AP_TO_WLAN_TXD_P

34

PCIE_AP_TO_WLAN_TXD_N

PCIE LINK 1PCIE LINK 2

34

PCIE_BB_TO_AP_RXD_P

34

PCIE_BB_TO_AP_RXD_N

34

PCIE_AP_TO_BB_TXD_P

34

PCIE_AP_TO_BB_TXD_N

34

C0709

ROOM=SOC

X5R-CERM

C0710

ROOM=SOC

C0711

ROOM=SOC

C0712

ROOM=SOC

C0715

ROOM=SOC

C0716

ROOM=SOC

X5R-CERM

C0717

ROOM=SOC

C0718

ROOM=SOC

X5R-CERM

1 2

20%

1 2

20%

1 2

20%

1 2

20%

1 2

20%

1 2

20%

1 2

20%

1 2

6.3V

01005

6.3V

01005X5R-CERM

6.3V

01005X5R-CERM

6.3V

01005X5R-CERM

6.3V

01005X5R-CERM

6.3V

01005

6.3V

01005X5R-CERM

6.3V20%

01005

0.1UF

0.1UF

0.1UF

0.1UF

0.1UF

0.1UF

0.1UF

0.1UF

PCIE_WLAN_TO_AP_RXD_C_P

PCIE_WLAN_TO_AP_RXD_C_N

PCIE_AP_TO_WLAN_TXD_C_P

PCIE_AP_TO_WLAN_TXD_C_N

PCIE_BB_TO_AP_RXD_C_P

6

6

PCIE_BB_TO_AP_RXD_C_N

PCIE_AP_TO_BB_TXD_C_P

PCIE_AP_TO_BB_TXD_C_N

AM27

AN27

AT28

AR28

AM26

AN26

AT26

AR26

PCIE_RX2_P

PCIE_RX2_N

PCIE_TX2_P

PCIE_TX2_N

PCIE_RX3_P

PCIE_RX3_N

PCIE_TX3_P

PCIE_TX3_N

PCIE_PERST0*

PCIE_PERST1*

PCIE_PERST2*

PCIE_PERST3*

PCIE_EXT_REF_CLK_P

PCIE_EXT_REF_CLK_N

PCIE_RX_TX_BYPASS_CLK_P

PCIE_RX_TX_BYPASS_CLK_N

AR10

AT10

AP11

AR11

AR33

AT33

AT29

AR29

NC

1

R0700

100K

5%

1/32W

MF

01005

2

ROOM=SOC

1

R0701

100K

5%

1/32W

MF

01005

2

ROOM=SOC

1

R0702

100K

5%

1/32W

MF

01005

2

ROOM=SOC

PCIE_AP_TO_NAND_RESET_L

PCIE_AP_TO_WLAN_RESET_L

PCIE_AP_TO_BB_RESET_L

13

34

34

PROBE POINTS

PCIE RX CAPS ARE PLACED CLOSER TO TX DRIVERS

PROBE POINTS ADDED FOR MEASUREMENTS AT RX DRIVER

B

A

NC

NC

NC

NC

AM25

AN25

AR24

AT24

PCIE_RX4_P

PCIE_RX4_N

PCIE_TX4_P

PCIE_TX4_N

PCIE_RCAL_P

PCIE_RCAL_N

AT30

AR30

PCIE_RCAL_P

PCIE_RCAL_N

OMIT_TABLE

1

R0730

100

1%

1/32W

MF

01005

2

ROOM=SOC

OMIT_TABLE

1

C0730

100PF

5%

16V

2

NP0-C0G

01005

ROOM=SOC

PCIE_BB_TO_AP_RXD_C_P

6

PCIE_BB_TO_AP_RXD_C_N

6

SYNC_MASTER=N71_SINGLE_BRD

PAGE TITLE

SOC:PCIE

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

SM

1

1

PP0706

PP

P3MM-NSM

ROOM=SOC

SM

PP0707

PP

P3MM-NSM

ROOM=SOC

SYNC_DATE=05/29/2014

DRAWING NUMBER SIZE

051-00094

REVISION

D

4.0.0

BRANCH

PAGE

7 OF 49

SHEET

6 OF 60

A

8 7 5 4 2 1

36

MAUI - CAMERA & DISPLAY INTERFACES

345678

2 1

D

C

B

0.756-0.893V @11mA MAX

14 11 6

MIPI_RCAM_TO_AP_DATA0_CONN_P

21

MIPI_RCAM_TO_AP_DATA0_CONN_N

21

MIPI_RCAM_TO_AP_DATA1_CONN_P

21

MIPI_RCAM_TO_AP_DATA1_CONN_N

21

MIPI_RCAM_TO_AP_DATA2_CONN_P

21

MIPI_RCAM_TO_AP_DATA2_CONN_N

21

MIPI_RCAM_TO_AP_DATA3_CONN_P

21

MIPI_RCAM_TO_AP_DATA3_CONN_N

21

MIPI_RCAM_TO_AP_CLK_CONN_P

21

MIPI_RCAM_TO_AP_CLK_CONN_N

21

PP_FIXED

RCAM_REXT

30

30

30

30

30

30

30

30

30

MIPI_AP_TO_LCM_DATA0_P

MIPI_AP_TO_LCM_DATA0_N

MIPI_AP_TO_LCM_DATA1_P

MIPI_AP_TO_LCM_DATA1_N

MIPI_AP_TO_LCM_DATA2_P

MIPI_AP_TO_LCM_DATA2_N

MIPI_AP_TO_LCM_DATA3_P

MIPI_AP_TO_LCM_DATA3_N

MIPI_AP_TO_LCM_CLK_P

LCM_REXT

1

C0814

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

1

C0801

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

B8

MIPI0C_DATA0_P

A8

MIPI0C_DATA0_N

A9

MIPI0C_DATA1_P

B9

MIPI0C_DATA1_N

A13

MIPI0C_DATA2_P

B13

MIPI0C_DATA2_N

B14

MIPI0C_DATA3_P

A14

MIPI0C_DATA3_N

A12

MIPI0C_CLK_P

B12

MIPI0C_CLK_N

D12

MIPI0C_REXT

A3

MIPID_DATA0_P

B3

MIPID_DATA0_N

B4

MIPID_DATA1_P

A4

MIPID_DATA1_N

B6

MIPID_DATA2_P

A6

MIPID_DATA2_N

A7

MIPID_DATA3_P

B7

MIPID_DATA3_N

A5

MIPID_CLK_P

B5

MIPID_CLK_N

D9

MIPID_REXT

E10

E13E8D13

E7D8E11

VDD085_MIPI

E14

VDD18_MIPI

D10

CRITICAL

U0600

MAUI-2GB-25NM-DDR-H

FCMSP

SC58980B0B-A040

SYM 3 OF 14

ROOM=SOC

OMIT_TABLE

SENSOR0_ISTRB

SENSOR0_XSHUTDOWN

SENSOR1_ISTRB

SENSOR1_XSHUTDOWN

MIPICSI_MUXSEL

MIPI1C_DATA0_P

MIPI1C_DATA0_N

MIPI1C_DATA1_P

MIPI1C_DATA1_N

ISP_I2C0_SCL

ISP_I2C0_SDA

ISP_I2C1_SCL

ISP_I2C1_SDA

SENSOR0_CLK

SENSOR0_RST

SENSOR1_CLK

SENSOR1_RST

MIPI1C_REXT

MIPI1C_CLK_P

MIPI1C_CLK_N

G31

G32

F35

G34

D33

D32

F33

E34

D34

F32

C35

C34

G35

D14

B17

A17

B19

A19

A18

B18

1.62-1.98V @23mA MAX

PP1V8

1

C0802

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

1

C0815

0.1UF

20%

6.3V

2

X5R-CERM

01005

ROOM=SOC

1

R0804

1.00K

5%

1/32W

MF

01005

2

ROOM=SOC

AP_TO_RCAM_CLK_R

AP_TO_RCAM_SHUTDOWN_L

AP_TO_FCAM_CLK_R

AP_TO_FCAM_SHUTDOWN_L

AP_TO_SPHERE_BUCK_EN

AP_TO_STOCKHOLM_DWLD_REQUEST

NC

AP_TO_MUON_BL_STROBE_EN

NC

MIPI_FCAM_TO_AP_DATA0_P

MIPI_FCAM_TO_AP_DATA0_N

MIPI_FCAM_TO_AP_DATA1_P

MIPI_FCAM_TO_AP_DATA1_N

MIPI_FCAM_TO_AP_CLK_PMIPI_AP_TO_LCM_CLK_N

MIPI_FCAM_TO_AP_CLK_N

1

R0805

1.00K

5%

1/32W

MF

01005

2

ROOM=SOC

34 30

1

R0806

1.00K

5%

1/32W

MF

01005

2

ROOM=SOC

21

20

FCAM_REXT

21 20 17 14 13 12 9 8 7 6 5 3

1

R0807

1.00K

5%

1/32W

MF

01005

2

ROOM=SOC

R0809

33.2

1 2

MF1%

01005

ROOM=SOC

23

34

28

20

20

20

20

20 30

20

PP1V8

34 30

R0808

33.2

1 2

1% 1/32W

MF

01005

ROOM=SOC

1/32W

21 20 17 14 13 12 9 8 7 6 5 3

I2C_ISP_TO_RCAM_SCL

I2C_ISP_BI_RCAM_SDA

I2C_ISP_TO_FCAM_SCL

I2C_ISP_BI_FCAM_SDA

AP_TO_RCAM_CLK

AP_TO_FCAM_CLK

20

20

21

20

D

NOTE:VDD12_LPDP SHOULD BE POWERED

EVEN WHEN LPDP IS NOT USED

15 6 5

22 21

22 21

PP1V2

E25

E27

E23

F24

VDD12_LPDP

CRITICAL

C

U0600

MAUI-2GB-25NM-DDR-H

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

A29

LPDP_AUX_P

B29

LPDP_AUX_N

A33

LPDP_TX0_P

B33

LPDP_TX0_N

A32

LPDP_TX1_P

B32

LPDP_TX1_N

A31

LPDP_TX2_P

B31

LPDP_TX2_N

A30

LPDP_TX3_P

B30

LPDP_TX3_N

D24

LPDP_CAL_DRV_OUT

D25

LPDP_CAL_VSS_EXT

AL4

EDP_HPD

H35

DP_WAKEUP

FCMSP

SC58980B0B-A040

SYM 4 OF 14

ROOM=SOC

OMIT_TABLE

B

R0801

4.02K

1%

1/32W

MF

01005

ROOM=SOC

1

R0803

4.02K

1%

1/32W

MF

01005

2

ROOM=SOC

1%

1/32W

MF

01005

1

2

1

R0802

4.02K

2

ROOM=SOC

A

SYNC_MASTER=N71_SINGLE_BRD

PAGE TITLE

SOC:CAMERA & DISPLAY

DRAWING NUMBER SIZE

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

8 7 5 4 2 1

36

REVISION

BRANCH

PAGE

SHEET

SYNC_DATE=05/29/2014

051-00094

D

4.0.0

8 OF 49

7 OF 60

A

MAUI - GPIO & SERIAL INTERFACES

345678

2 1

D

C

B

AP_TO_HP_HS3_CTRL

32

AP_TO_HP_HS4_CTRL

32

34 33 16

34 33 16

NO_TEST=1

34 30 9

25 16

34 33 16 8

21 20 17 14 13 12 9 8 7 6 5 3

BUTTON_VOL_UP_L

BUTTON_VOL_DOWN_L

SPEAKERAMP_TO_AP_INT_L

26

AP_TO_SPEAKERAMP_STAYIN_ALIVE

26

AP_TO_SPEAKERAMP_RESET_L

26

AP_TO_BT_WAKE

34

AP_TO_BB_RESET_L

34

PCIE_AP_TO_WLAN_DEV_WAKE

34

AP_TO_LED_DRIVER_EN

22

AP_TO_TOUCH_RESET_L

29

AP_TO_LCM_RESET_L

30

PMU_TO_AP_IRQ_L

16

AP_TO_BB_PCIE_DEV_WAKE

34

AP_TO_STOCKHOLM_DEV_WAKE

34

BOARD_ID3

3

NC_AP_TO_STOCKHOLM_SIM_SEL

BOOT_CONFIG0

3

AP_TO_ARC_RESET_L

27

LCM_TO_OWL_BSYNC

ARC_TO_AP_INT_L

27

BB_TO_AP_GPS_TIME_MARK

34

AP_TO_ARC_STAYIN_ALIVE

27

BB_TO_AP_RESET_DETECT_L

34

BOOT_CONFIG1

3

FORCE_DFU

34 3

DFU_STATUS

34 3

BOOT_CONFIG2

3

BOARD_ID4

3

CODEC_TO_AP_PMU_INT_L

AP_TO_BB_RADIO_ON_L

34

AP_TO_NAND_FW_STRAP

13

TOUCH_TO_AP_INT_L

30

BOARD_REV3

3

BOARD_REV2

3

BOARD_REV1

3

BOARD_REV0

3

AP_TO_BB_COREDUMP

34

BB_IPC_GPIO

34

BUTTON_RINGER_A

AP_TO_BB_MESA_ON_L

34

MAMBA_EXT_LDO_EN

29

34 30

PP1V8

ANALOG_PROX

R0911

1.00K

1/32W

01005

ROOM=SOC

1

5%

MF

2

PROX_SELECT

C1

D2

D1

F1

E2

F3

F2

H3

G3

J1

H4

K1

J3

K2

J4

L2

K3

L3

N1

AH2

AH3

AH4

AJ1

AJ2

AJ3

AJ4

AK1

AP3

AN4

AP4

AP5

AR2

AR3

AR4

AP6

AT3

AT4

AR6

AP7

AT5

AP8

AP9

AP10

GPIO_0

GPIO_1

GPIO_2

GPIO_3

GPIO_4

GPIO_5

GPIO_6

GPIO_7

GPIO_8

GPIO_9

GPIO_10

GPIO_11

GPIO_12

GPIO_13

GPIO_14

GPIO_15

GPIO_16

GPIO_17

GPIO_18

GPIO_19

GPIO_20

GPIO_21

GPIO_22

GPIO_23

GPIO_24

GPIO_25

GPIO_26

GPIO_27

GPIO_28

GPIO_29

GPIO_30

GPIO_31

GPIO_32

GPIO_33

GPIO_34

GPIO_35

GPIO_36

GPIO_37

GPIO_38

GPIO_39

GPIO_40

GPIO_41

GPIO_42

U0600

MAUI-2GB-25NM-DDR-H

FCMSP

SC58980B0B-A040

SYM 5 OF 14

CRITICAL

ROOM=SOC

OMIT_TABLE

TMR32_PWM0

TMR32_PWM1

TMR32_PWM2

UART0_RXD

UART0_TXD

UART1_CTS*

UART1_RTS*

UART1_RXD

UART1_TXD

UART2_CTS*

UART2_RTS*

UART2_RXD

UART2_TXD

UART3_CTS*

UART3_RTS*

UART3_RXD

UART3_TXD

UART4_CTS*

UART4_RTS*

UART4_RXD

UART4_TXD

UART5_RTXD

UART6_RXD

UART6_TXD

UART7_RXD

UART7_TXD

AE1

AF2

AF3

AE3

AE4

K31

K32

L33

L32

AT23

AR20

AP23

AP22

N4

P3

R3

R2

J33

J34

J35

K33

T32

AF1

AE2

J31

J32

NC

NC

NC

NC

NC

NC

NC

I2S_AP_TO_CODEC_MCLK

25

I2S_AP_TO_ARC_MCLK

27

I2S_AP_TO_SPEAKERAMP_MCLK

26

AP_TO_SPHERE_BUCK_MODE

23

UART_AP_DEBUG_RXD

UART_AP_DEBUG_TXD

UART_BT_TO_AP_CTS_L

UART_AP_TO_BT_RTS_L

UART_BT_TO_AP_RXD

UART_AP_TO_BT_TXD

UART_STOCKHOLM_TO_AP_CTS_L

UART_AP_TO_STOCKHOLM_RTS_L

UART_STOCKHOLM_TO_AP_RXD

UART_AP_TO_STOCKHOLM_TXD

UART_WLAN_TO_AP_CTS_L

UART_AP_TO_WLAN_RTS_L

UART_WLAN_TO_AP_RXD

UART_AP_TO_WLAN_TXD

SWI_AP_BI_TIGRIS

UART_ACCESSORY_TO_AP_RXD

UART_AP_TO_ACCESSORY_TXD

SPI_AP_TO_TOUCH_SCLK

30

SPI_AP_TO_MESA_SCLK

29

34

34

34

34

34

34

34

34

34

34

34

34

17 9

31

31

21 20 17 14 13 12 9 8 7 6 5 3

D

R0900

2.2K

5%

1/32W

MF

01005

ROOM=SOC

1

2

R0901

2.2K

5%

1/32W

MF

01005

ROOM=SOC

1

2

R0902

2.2K

5%

1/32W

MF

01005

ROOM=SOC

1

2

R0903

2.2K

5%

1/32W

MF

01005

ROOM=SOC

1

2

R0904

1.33K

1%

1/32W

MF

01005

ROOM=SOC

1

2

R0905

1.33K

1%

1/32W

MF

01005

ROOM=SOC

PP1V8

1

2

34 30

R0920

33.2

1 2

1%

1/32W

MF

01005

ROOM=SOC

R0921

33.2

1 2

1%

1/32W

MF

01005

ROOM=SOC

I2S_AP_TO_CODEC_MCLK_R

25 9

25 9

25 9

I2S_AP_OWL_TO_CODEC_XSP_BCLK

I2S_AP_OWL_TO_CODEC_XSP_LRCLK

I2S_CODEC_TO_AP_OWL_XSP_DIN

I2S_AP_TO_CODEC_XSP_DOUT

25

I2S_AP_TO_ARC_MCLK_R

I2S_AP_TO_BT_BCLK

34

I2S_AP_TO_BT_LRCLK

34

I2S_BT_TO_AP_DIN

34

I2S_AP_TO_BT_DOUT

34

P34

R34

N34

N35

M33

M4

M3

P1

N3

L4

I2S0_MCK

I2S0_BCLK

I2S0_LRCK

I2S0_DIN

I2S0_DOUT

I2S1_MCK

I2S1_BCLK

I2S1_LRCK

I2S1_DIN

I2S1_DOUT

U0600

MAUI-2GB-25NM-DDR-H

FCMSP

GRP1GRP2

SC58980B0B-A040

SYM 6 OF 14

GRP1GRP1

GRP3

CRITICAL

ROOM=SOC

OMIT_TABLE

I2C0_SCL

I2C0_SDA

I2C1_SCL

I2C1_SDA

I2C2_SCL

I2C2_SDA

R0922

34 31

34 31

R0960

0.00

1 2

0%

1/32W

MF

01005

ROOM=SOC

R0930

1 2

ROOM=SOC

33.2

1 2

1/32W

01005

ROOM=SOC

0.00

0%

1/32W

MF

01005

1%

MF

27 26 25

27 26 25

27 26 25

27 26 25

20

34

34

34

34

31 16

25

25

25

25

25

25

25

25

30 8

30

30

29

29

29

I2S_AP_TO_SPEAKERAMP_MCLK_R

I2S_AP_TO_CODEC_ASP_BCLK

I2S_AP_TO_CODEC_ASP_LRCLK

I2S_CODEC_TO_AP_ASP_DIN

I2S_AP_TO_CODEC_ASP_DOUT

ALS_TO_AP_INT_L

I2S_AP_TO_BB_BCLK

I2S_AP_TO_BB_LRCLK

I2S_BB_TO_AP_DIN

I2S_AP_TO_BB_DOUT

TRISTAR_TO_AP_INT

I2S_AP_TO_CODEC_MSP_BCLK

I2S_AP_TO_CODEC_MSP_LRCLK

I2S_CODEC_TO_AP_MSP_DIN

I2S_AP_TO_CODEC_MSP_DOUT

BOARD_ID2

3

BOARD_ID1

3

BOARD_ID0

3

SPI_CODEC_TO_AP_MISO

SPI_AP_TO_CODEC_MOSI

SPI_AP_TO_CODEC_SCLK

SPI_AP_TO_CODEC_CS_L

SPI_TOUCH_TO_AP_MISO

SPI_AP_TO_TOUCH_MOSI

SPI_AP_TO_TOUCH_SCLK_R

SPI_AP_TO_TOUCH_CS_L

SPI_MESA_TO_AP_MISO

SPI_AP_TO_MESA_MOSI

SPI_AP_TO_MESA_SCLK_R

MESA_TO_AP_INT

NC

U32

V33

U33

T33

V34

AM3

AM4

AN2

AP1

AN1

R32

R31

V32

P31

P32

AD4

AC3

AB2

AD3

P33

V35

N32

M31

E33

E35

F34

F31

AA2

Y2

AA3

AC4

I2S2_MCK

I2S2_BCLK

I2S2_LRCK

I2S2_DIN

I2S2_DOUT

I2S3_MCK

I2S3_BCLK

I2S3_LRCK

I2S3_DIN

I2S3_DOUT

I2S4_MCK

I2S4_BCLK

I2S4_LRCK

I2S4_DIN

I2S4_DOUT

SPI0_MISO

SPI0_MOSI

SPI0_SCLK

SPI0_SSIN

SPI1_MISO

SPI1_MOSI

SPI1_SCLK

SPI1_SSIN

SPI2_MISO

SPI2_MOSI

SPI2_SCLK

SPI2_SSIN

SPI3_MISO

SPI3_MOSI

SPI3_SCLK

SPI3_SSIN

GRP1GRP3GRP1GRP1

GRP1 GRP3

SEP_SPI0_SCLK

SEP_SPI0_MISO

SEP_SPI0_MOSI

SEP_I2C_SCL

SEP_I2C_SDA

SEP_GPIO0

SEP_GPIO1

SOCHOT0

SOCHOT1

GRP3

CPU_ACTIVE_STATUS

CLK32K_OUT

NAND_SYS_CLK

SPI PROBE POINTS

E31

D35

AH1

AG4

L31

M32

2.2K

5%

1/32W

MF

01005

1

2

R0906

W3

NC

AA4

NC

U2

NC

V3

Y4

Y3

NC

AB4

NC

AM1

PMU_TO_AP_SOCHOT0_R_L

AM2

AP_TO_PMU_SOCHOT1_R_L

H31

NC

H34

AM24

AP_TO_TOUCH_CLK32K_RESET_L

AP_TO_NAND_SYS_CLK_R

ROOM=SOC

R0907

2.2K

5%

1/32W

MF

01005

ROOM=SOC

PP1V8

1

2

34 30

I2C_SEP_TO_EEPROM_SCL

I2C_SEP_BI_EEPROM_SDA

R0909

10K

5%

1/32W

MF

01005

ROOM=SOC

1

2

1

R0910

10K

5%

1/32W

MF

01005

2

ROOM=SOC

ROOM=SOC

R0940

0.00

1 2

MF

01005

R0941

0.00

1 2

0%

30

01005

ROOM=SOC

R0945

0.00

1 2

0%

1/32W

MF

01005

ROOM=SOC

AP_TO_NAND_SYS_CLK

I2C PROBE POINTS

I2C0_AP_SCL

I2C0_AP_SDA

I2C1_AP_SCL

I2C1_AP_SDA

I2C2_AP_SCL

I2C2_AP_SDA

21 20 17 14 13 12 9 8 7 6 5 3

8

8

PP1V8

PMU_TO_AP_SOCHOT0_L

1/32W0%

AP_TO_PMU_SOCHOT1_L

1/32WMF

34 30

34 28 16 8

34 28 16 8

34 31 27 26 17 8

34 31 27 26 17 8

30 28 20

30 28 20

C

21 20 17 14 13 12 9 8 7 6 5 3

16

16

B

13

A

PIN J31 (UART7_RXD) SHOULD BE

SET TO INTERNAL PULL-DOWN.

STUFF R0911 FOR ANALOG PROX.

NOSTUFF R0911 FOR DOPPLER PROX.

21 20 17 14 13 12 9 8 7 6 5 3

34 30

PP1V8

ANTI-ROLLBACK EEPROM

128kbit

APN:335S0946

1

C0900

1.0UF

20%

6.3V

2

X5R

0201-1

ROOM=SOC

M34128-FCS6_P/T

B1 A2

SCL

A1B2

CRITICAL

VCCVSS

U0900

WLCSP

ROOM=SOC

SDA

I2C_SEP_BI_EEPROM_SDA

I2C_SEP_TO_EEPROM_SCL

SM

SPI_TOUCH_TO_AP_MISO

30 8

1

PP0906

PP

P3MM-NSM

ROOM=SOC

PLACE_SIDE=TOP

BUTTON PULL-UP RESISTORS

PP1V8_SDRAM

1

R0950

191K

1%

1/32W

MF

01005

2

BUTTON_MENU_KEY_L

ROOM=SOC

BUTTON_RINGER_A

8

8

BUTTON_HOLD_KEY_L

1

R0952

220K

5%

1/32W

MF

01005

2

ROOM=SOC

1

R0951

100K

5%

1/32W

MF

01005

2

ROOM=SOC

PP1V8_ALWAYS

34 29 16 9

34 33 16 8

17 15 12

34 33 16 9

34 32 31 28 25 16 15 14 12

SYNC_MASTER=N71_SINGLE_BRD

PAGE TITLE

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

34 28 16 8

34 28 16 8

34 31 27 26 17 8

34 31 27 26 17 8

I2C0_AP_SCL

I2C0_AP_SDA

I2C1_AP_SCL

I2C1_AP_SDA

SOC:SERIAL & GPIO

Apple Inc.

R

SM

1

1

1

1

DRAWING NUMBER SIZE

REVISION

PP0900

PP

P3MM-NSM

ROOM=SOC

SM

PP0901

PP

P3MM-NSM

ROOM=SOC

SM

PP0902

PP

P3MM-NSM

ROOM=SOC

SM

PP0903

PP

P3MM-NSM

ROOM=SOC

PLACE_SIDE=TOP

PLACE_SIDE=TOP

SYNC_DATE=05/29/2014

051-00094

D

4.0.0

BRANCH

PAGE

9 OF 49

SHEET

8 OF 60

A

8 7 5 4 2 1

36

.

D

MAUI - OWL

345678

2 1

POWER STATE CONTROL PROBE POINTS

SM

16 9

31 28 16 9 5

16 9

16 11 9

OWL_TO_PMU_ACTIVE_REQUEST

PMU_TO_OWL_ACTIVE_READY

OWL_TO_PMU_SLEEP1_REQUEST

PMU_TO_OWL_SLEEP1_READY

1

1

1

1

PP1020

PP

SM

PP

SM

PP

SM

PP

P3MM-NSM

ROOM=SOC

PP1021

P3MM-NSM

ROOM=SOC

PP1022

P3MM-NSM

ROOM=SOC

PP1023

P3MM-NSM

ROOM=SOC

D

C

16 9

16 11 9

19

19

19

19

19

19

19

34 30 8

19

19

19

19

19

19

34

34

OWL_TO_PMU_SLEEP1_REQUEST

PMU_TO_OWL_SLEEP1_READY

SPI_OWL_TO_COMPASS_CS_L

COMPASS_TO_OWL_INT

DISCRETE_ACCEL_TO_OWL_INT2

ACCEL_GYRO_TO_OWL_INT1

SPI_OWL_TO_ACCEL_GYRO_CS_L

ACCEL_GYRO_TO_OWL_INT2

SPI_OWL_TO_PHOSPHOROUS_CS_L

LCM_TO_OWL_BSYNC

OWL_TO_PMU_SHDN_BI_TIGRIS_SWI

9

PHOSPHORUS_TO_OWL_IRQ

SPI_OWL_TO_DISCRETE_ACCEL_CS_L

DISCRETE_ACCEL_TO_OWL_INT1

SPI_IMU_TO_OWL_MISO

SPI_OWL_TO_IMU_MOSI

SPI_OWL_TO_IMU_SCLK

UART_BB_TO_OWL_RXD

UART_OWL_TO_BB_TXD

AD30

AB33

AF35

AH32

AG32

AG31

AG30

AF33

AE34

AF34

AF31

AF32

AH31

AH33

AK31

AK32

AL33

AJ32

AK33

MAUI-2GB-25NM-DDR-H

SC58980B0B-A040

OWL_DDR_REQ

OWL_DDR_RESET*

OWL_FUNC_0

OWL_FUNC_1

OWL_FUNC_2

OWL_FUNC_3

OWL_FUNC_4

OWL_FUNC_5

OWL_FUNC_6

OWL_FUNC_7

OWL_FUNC_8

OWL_FUNC_9

OWL_I2CM_SCL

OWL_I2CM_SDA

OWL_SPI_MISO

OWL_SPI_MOSI

OWL_SPI_SCLK

OWL_UART0_RXD

OWL_UART0_TXD

EXT OSC IN

U0600

FCMSP

SYM 7 OF 14

CRITICAL

ROOM=SOC

OMIT_TABLE

GPO

GPO

GPO

CFSB_AOP

AWAKE_REQ

AWAKE_RESET*

PMGR_MISO

PMGR_MOSI

PMGR_SCLK0

PMGR_SSCLK1

RT_CLK32768

OWL_SWD_TCK_OUT

OWL_SWD_TMS0

OWL_SWD_TMS1

SWD_TMS2

SWD_TMS3

HOLD_KEY*

VDD_SOC

SKEY*

MENU_KEY*

W33

AA33

AD32

AL2

AL1

AK4

AL3

AD31

AE33

AD35

AC33

U31

T31

U3

W4

V4

NC

NC

NC

NOSTUFF

1

R1002

1.00K

5%

1/32W

MF

01005

2

PP1V8

34

30 21 20 17 14 13 12 8 7 6 5 3

PMU_TO_SYSTEM_COLD_RESET_L

OWL_TO_PMU_ACTIVE_REQUEST

16 9

PMU_TO_OWL_ACTIVE_READY

DWI_PMU_TO_PMGR_MISO

DWI_PMGR_TO_PMU_BACKLIGHT_MOSI

DWI_PMGR_TO_PMU_SCLK

DWI_PMGR_TO_BACKLIGHT_SCLK

PMU_TO_OWL_CLK32K

SWD_AP_PERIPHERAL_SWCLK

SWD_AP_BI_BB_SWDIO

SWD_AP_BI_NAND_SWDIO

16

28 16

16

28

16

34 13

34

13

BUTTON_HOLD_KEY_L

BUTTON_MENU_KEY_L

34 16 5 3

C

31 28 16 9 5

34 33 16 8

34 29 16 8

B

OWL_TO_WLAN_CONTEXT_B

34

OWL_TO_WLAN_CONTEXT_A

34

TOUCH_TO_OWL_ACCEL_DATA_REQUEST

30

UART_OWL_TO_TOUCH_TXD

30

I2S_AP_OWL_TO_CODEC_XSP_BCLK

25 8

I2S_CODEC_TO_AP_OWL_XSP_DIN

25 8

I2S_AP_OWL_TO_CODEC_XSP_LRCLK

25 8

NC

AH30

AJ31

AJ34

AJ33

AD34

AA34

AE32

AE31

OWL_UART1_RXD

OWL_UART1_TXD

OWL_UART2_RXD

OWL_UART2_TXD

OWL_I2S_BCLK

OWL_I2S_DIN

OWL_I2S_MCK

OWL_I2S_LRCK

B

A

OWL SYSTEM SHUTDOWN OPTION

OWL_TO_PMU_SHDN_BI_TIGRIS_SWI

9

NOSTUFF

R1020

10

1 2

5% 01005MF

ROOM=SOC

NOSTUFF

R1021

10

1 2

5%MF

ROOM=SOC

1/32W

1/32W

01005

SWI_AP_BI_TIGRIS

OWL_TO_PMU_SHDN

16

17 8

SYNC_MASTER=N71_SINGLE_BRD

PAGE TITLE

SYNC_DATE=05/29/2014

A

SOC:OWL

DRAWING NUMBER SIZE

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

051-00094

REVISION

4.0.0

BRANCH

PAGE

10 OF 49

SHEET

9 OF 60

D

8 7 5 4 2 1

36

345678

2 1

D

C

B

A

MAUI - CPU, GPU & SOC RAILS

PP_GPU

14 10

0.8V @10.5A MAX

TP1120

0.50MM

SM

1

PP

PP_CPU

14 10

0.625V @TBDA MAX

0.9V @10.5A MAX

1.0V @12.5A MAX

TP1100

0.50MM

SM

1

PP

PP_GPU

PP_CPU

10

14

14 10

1

2

ROOM=SOC

C1106

4.3UF

20%

4V

CERM

0402

1

234

ROOM=SOC

C1112

1UF

20%

4V

CERM

0402

1

234

C1120

10UF

20%

6.3V

CERM-X5R

0402-9

ROOM=SOC

ROOM=SOC

C1126

7.5UF

20%

4V

CERM

0402

1

234

ROOM=SOC

C1132

4.3UF

20%

4V

CERM

0402

1

234

ROOM=SOC

C1138

0.47UF

20%

6.3V

CERM

0402

1

234

1

C1101

10UF

20%

6.3V

2

CERM-X5R

0402-9

ROOM=SOC

ROOM=SOC

C1107

7.5UF

20%

4V

CERM

0402

1

234

ROOM=SOC

C1113

1UF

20%

4V

CERM

0402

1

234

1

C1121

10UF

20%

6.3V

2

CERM-X5R

0402-9

ROOM=SOC

ROOM=SOC

C1127

7.5UF

20%

4V

CERM

0402

1

234

ROOM=SOC

C1133

7.5UF

20%

4V

CERM

0402

1

234

ROOM=SOC

C1139

0.47UF

20%

6.3V

CERM

0402

1

234

1

C1102

10UF

20%

6.3V

2

CERM-X5R

0402-9

ROOM=SOC

ROOM=SOC

C1108

4.3UF

20%

4V

CERM

0402

1

234

ROOM=SOC

C1114

1UF

20%

4V

CERM

0402

1

234

1

C1122

2.2UF

20%

6.3V

2

X5R-CERM

0201

ROOM=SOC

ROOM=SOC

C1128

4.3UF

20%

4V

CERM

0402

1

234

ROOM=SOC

C1134

1UF

20%

4V

CERM

0402

1

234

ROOM=SOC

C1140

0.47UF

20%

6.3V

CERM

0402

1

234

1

C1103

2.2UF

20%

6.3V

2

X5R-CERM

0201

ROOM=SOC

ROOM=SOC

C1109

7.5UF

20%

4V

CERM

0402

1

234

ROOM=SOC

C1115

1UF

20%

4V

CERM

0402

1

234

BUCK1_PP_GPU_FB

14

1

C1123

2.2UF

20%

6.3V

2

X5R-CERM

0201

ROOM=SOC

ROOM=SOC

C1129

4.3UF

20%

4V

CERM

0402

1

234

ROOM=SOC

C1135

1UF

20%

4V

CERM

0402

1

234

ROOM=SOC

C1141

0.47UF

20%

6.3V

CERM

0402

1

234

BUCK0_PP_CPU_FB

14

1

C1104

2.2UF

20%

6.3V

2

X5R-CERM

0201

ROOM=SOC

ROOM=SOC

C1110

4.3UF

20%

4V

CERM

0402

1

234

ROOM=SOC

C1116

0.47UF

20%

6.3V

CERM

0402

1

234

1

C1124

2.2UF

20%

6.3V

2

X5R-CERM

0201

ROOM=SOC

ROOM=SOC

C1130

4.3UF

20%

4V

CERM

0402

1

234

ROOM=SOC

C1136

1UF

20%

4V

CERM

0402

1

234

PP1100

P2MM-NSM

PP1101

P2MM-NSM

SHORT-10L-0.1MM-SM

SM

PP

SM

1

C1105

2.2UF

20%

6.3V

2

X5R-CERM

0201

ROOM=SOC

ROOM=SOC

C1111

7.5UF

20%

4V

CERM

0402

1

234

ROOM=SOC

C1117

0.47UF

20%

6.3V

CERM

0402

1

234

XW1110

12

ROOM=SOC

1

C1125

2.2UF

20%

6.3V

2

X5R-CERM

0201

ROOM=SOC

ROOM=SOC

C1131

7.5UF

20%

4V

CERM

0402

1

234

ROOM=SOC

C1137

1UF

20%

4V

CERM

0402

1

234

XW1100

SHORT-10L-0.1MM-SM

12

ROOM=SOC

1

ROOM=SOC

1

ROOM=SOC

AP_CPU_SENSE_N

AA7

AA9

AA11

AB6

AB10

AB12

AC13

AD6

AD8

AD10

AD12

AE7

AE9

AE11

AE13

AF8

AF10

AF12

AH6

AH8

AH10

AH12

AJ5

AJ7

AJ9

AJ11

AJ13

AK6

AK10

AL7

AL9

AL11

AM6

AM8

AM10

AN7

AN11

AL13

Y8

Y10

Y12

AM12

Y6

Y7

MAUI-2GB-25NM-DDR-H

VDD_CPU

VDD_CPU_SENSE

VSS_CPU_SENSE

U0600

FCMSP

SC58980B0B-A040

SYM 8 OF 14

CRITICAL

ROOM=SOC

OMIT_TABLE

VDD_GPU

VDD_GPU_SENSE

VSS_GPU_SENSE

NOTE: AP_GPU_SENSE_P probe location @ R2205.2

G15

W13

T12

M6

U9

V12

W9

M12

M18

N15

N21

N9

F10

H14

H16

H20

H22

H6

H8

J11

J13

J17

J19

J23

J7

K10

K14

K16

K20

K22

K6

K8

L11

L13

L15

L17

L19

L21

M24

L7

L9

F8

M8

N11

N13

N17

N19

P10

G11

P12

P14

P16

P20

R15

R19

G13

R9

T10

T14

T16

U11

V14

V16

G7

R23

G9

H10

T24

P22

W17

N23

G17

G21

T18

T20

G20

H19

PP1105

P2MM-NSM

PP1104

P2MM-NSM

AP_GPU_SENSE_PAP_CPU_SENSE_P

AP_GPU_SENSE_N

SM

1

PP

ROOM=SOC

SM

1

PP

ROOM=SOC

AP_SOC_SENSE_P

AP_SOC_SENSE_N

16

SM

1

PP1102

ROOM=SOC

PPPP

P2MM-NSM

AA17

AA19

AA23

AB14

AB16

AB20

AB22

AB24

AB26

AC17

AC19

AC23

AD16

AD20

AD22

AD24

AD26

AE5

AE15

AE17

AE19

AE23

AF14

AF16

AF20

AF22

AF24

AF26

AG17

AG19

AG23

AH16

AH20

AH22

AH24

AH26

AJ15

AJ17

AJ19

AJ23

AK14

J29

G23

AK22

F6

F14

AL15

AM5

G25

G27

H24

H26

H28

J27

K24

K26

K28

L27

L23

M26

M28

AL19

N7

N27

P24

P26

P28

R17

R27

R29

T22

T26

T7

T28

U17

V8

V20

V22

V24

V26

W7

W11

Y28

AJ20

AK21

MAUI-2GB-25NM-DDR-H

VDD_SOC

VDD_SOC_SENSE

VSS_SOC_SENSE

U0600

FCMSP

SC58980B0B-A040

SYM 9 OF 14

CRITICAL

ROOM=SOC

OMIT_TABLE

VDD_SOC

VSS

W23

Y14

Y16

Y20

Y22

Y24

Y26

G29

AA27

F17

F20

L29

N29

V28

L22

L24

L26

L28

M1

M5

M7

M9

M11

M13

M17

M21

M23

M25

M27

M29

M35

N6

N10

N12

N14

N16

N18

G19

N22

N24

N26

N28

N30

N33

P9

P11

P13

P15

P17

P19

P21

P23

P25

P27

P29

P35

R4

R6

R8

R10

R12

R14

M19

R18

R20

R22

R24

R26

R28

R30

T1

T2

R33

T9

T11

T13

T15

T17

P7

T23

T25

T27

T30

T35

U6

U10

U12

ROOM=SOC

C1153

4.3UF

20%

4V

CERM

0402

1

234

1

C1151

10UF

20%

6.3V

2

CERM-X5R

0402-9

ROOM=SOC

ROOM=SOC

C1154

1UF

20%

4V

CERM

0402

1

234

PP_SOC

14

0.825V @4.7A MAX

0.725V @TBDA MAX

XW1120

SHORT-10L-0.1MM-SM

ROOM=SOC

C1155

1UF

20%

4V

CERM

0402

1

234

1 2

ROOM=SOC

ROOM=SOC

C1156

0.47UF

20%

6.3V

CERM

0402

1

234

BUCK2_PP_SOC_FB

ROOM=SOC

C1157

0.47UF

20%

6.3V

CERM

0402

1

234

14

SYNC_MASTER=N71_SINGLE_BRD SYNC_DATE=05/29/2014

PAGE TITLE

SOC:POWER (1/3)

DRAWING NUMBER SIZE

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

051-00094

REVISION

4.0.0

BRANCH

PAGE

11 OF 49

SHEET

10 OF 60

D

D

C

B

A

8 7 5 4 2 1

36

D

C

B

MAUI - POWER SUPPLIES

0.802-TBDV @1.1A MAX

14 7 6

PP_FIXED

1

C1200

10UF

20%

6.3V

2

CERM-X5R

0402-9

ROOM=SOC

ROOM=SOC

C1201

4.3UF

20%

4V

CERM

0402

1

234

ROOM=SOC

C1202

1UF

20%

4V

CERM

0402

1

234

ROOM=SOC

C1203

0.47UF

20%

6.3V

CERM

0402

1

234

AA15

AA21

AA25

AB18

AC15

AC21

AC25

AD14

AD18

AE21

AE25

AF18

AG15

AG21

AH25

AH14

AH18

AJ21

AK16

F12

G10

V18

AL17

J25

L25

N25

R25

R7

AN6

U25

W15

W21

W25

Y18

F21

F26

AB28

AC27

G18

AK20

F16

R16

T8

V7

U19

W27

U27

AF4

AF27

U21

VDD_FIXED

14 11

U0600

MAUI-2GB-25NM-DDR-H

FCMSP

SC58980B0B-A040

SYM 10 OF 14

CRITICAL

ROOM=SOC

OMIT_TABLE

VDD_CPU_SRAM

VDD_GPU_SRAM

PP1V1

1

C1240

10UF

20%

6.3V

2

CERM-X5R

0402-9

ROOM=SOC

AC11

AC7

AC9

AA13

AG11

AG7

AG9

AK12

H12

H18

R21

U15

J15

J21

J9

K12

K18

M10

M14

M16

M20

P18

R11

R13

U13

V10

M22

1

C1241

2.2UF

20%

6.3V

2

X5R-CERM

0201

ROOM=SOC

ROOM=SOC

C1220

0.47UF

CERM

0402

1

234

ROOM=SOC

C1224

4.3UF

1

20%

6.3V

20%

4V

CERM

0402

234

1

C1242

2.2UF

20%

6.3V

2

X5R-CERM

0201

ROOM=SOC

ROOM=SOC

C1221

1

ROOM=SOC

C1225

1

1UF

20%

4V

CERM

0402

234

1UF

20%

4V

CERM

0402

234

1

C1243

2.2UF

20%

6.3V

2

X5R-CERM

0201

ROOM=SOC

ROOM=SOC

C1245

4.3UF

20%

4V

CERM

0402

1

234

ROOM=SOC

C1222

1

ROOM=SOC

C1226

1

4.3UF

20%

4V

CERM

0402

234

4.3UF

20%

4V

CERM

0402

234

1

C1244

2.2UF

20%

6.3V

2

X5R-CERM

0201

ROOM=SOC

ROOM=SOC

C1246

1UF

20%

4V

CERM

0402

1

234

1

C1248

2.2UF

20%

6.3V

2

X5R-CERM

0201

ROOM=SOC

ROOM=SOC

C1247

0.47UF

20%

6.3V

CERM

0402

1

234

0.8V @TBDA MAX

0.9V @TBDA MAX

1.0V @1.0A MAX

PP_CPU_SRAM

1

C1223

2.2UF

20%

6.3V

2

X5R-CERM

0201

ROOM=SOC

0.8V @0.5A MAX

PP_GPU_SRAM

1

C1227

2.2UF

20%

6.3V

2

X5R-CERM

0201

ROOM=SOC

14

14

A20

A22

B11

B15

B23

B25

D16

D20

D22

E15

E17

E19

E21

AN19

AR18

AR21

AR8

AT13

AT16

AM14

AM16

AM18

AM20

AR15

AN13

AN15

AB29

V29

Y29

Y35

AB35

AG34

M34

R35

T29

T34

AA30

U30

AC30

AA1

AC2

V6

W2

H2

M2

U5

P6

T6

U1

N5

R5

W5

VDDIO11_DDR0

VDDIO11_DDR1

VDDIO11_DDR2