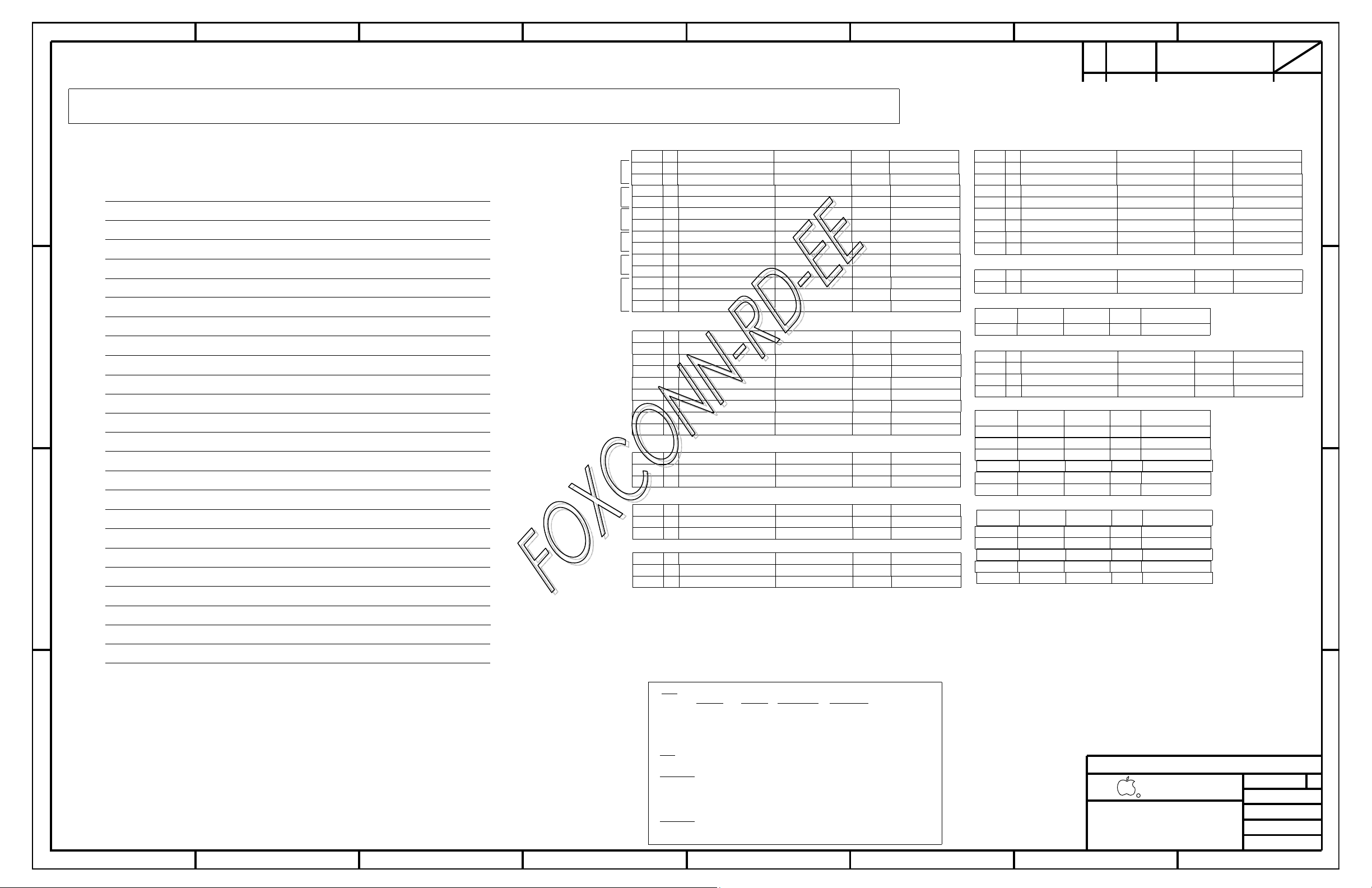

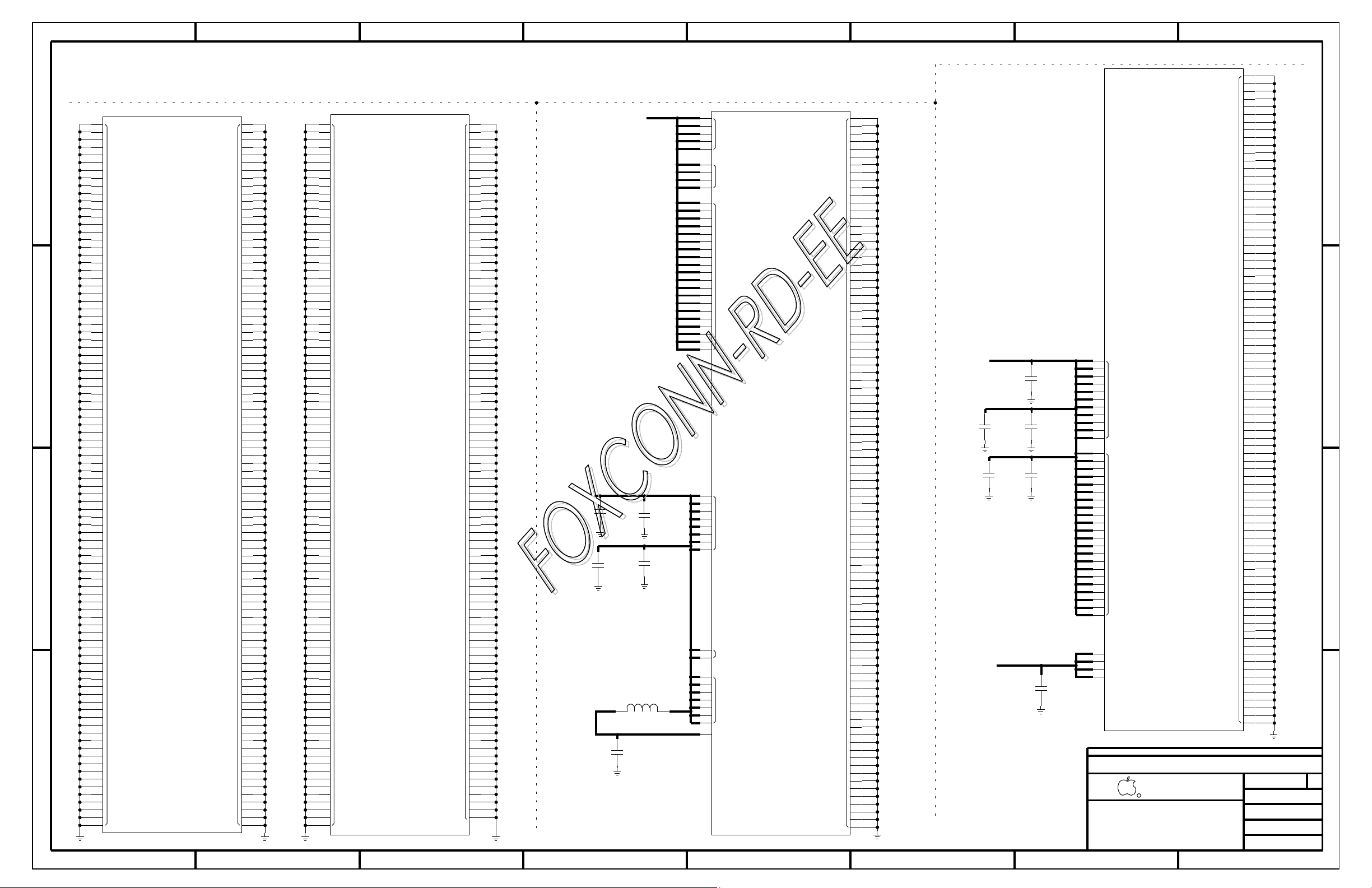

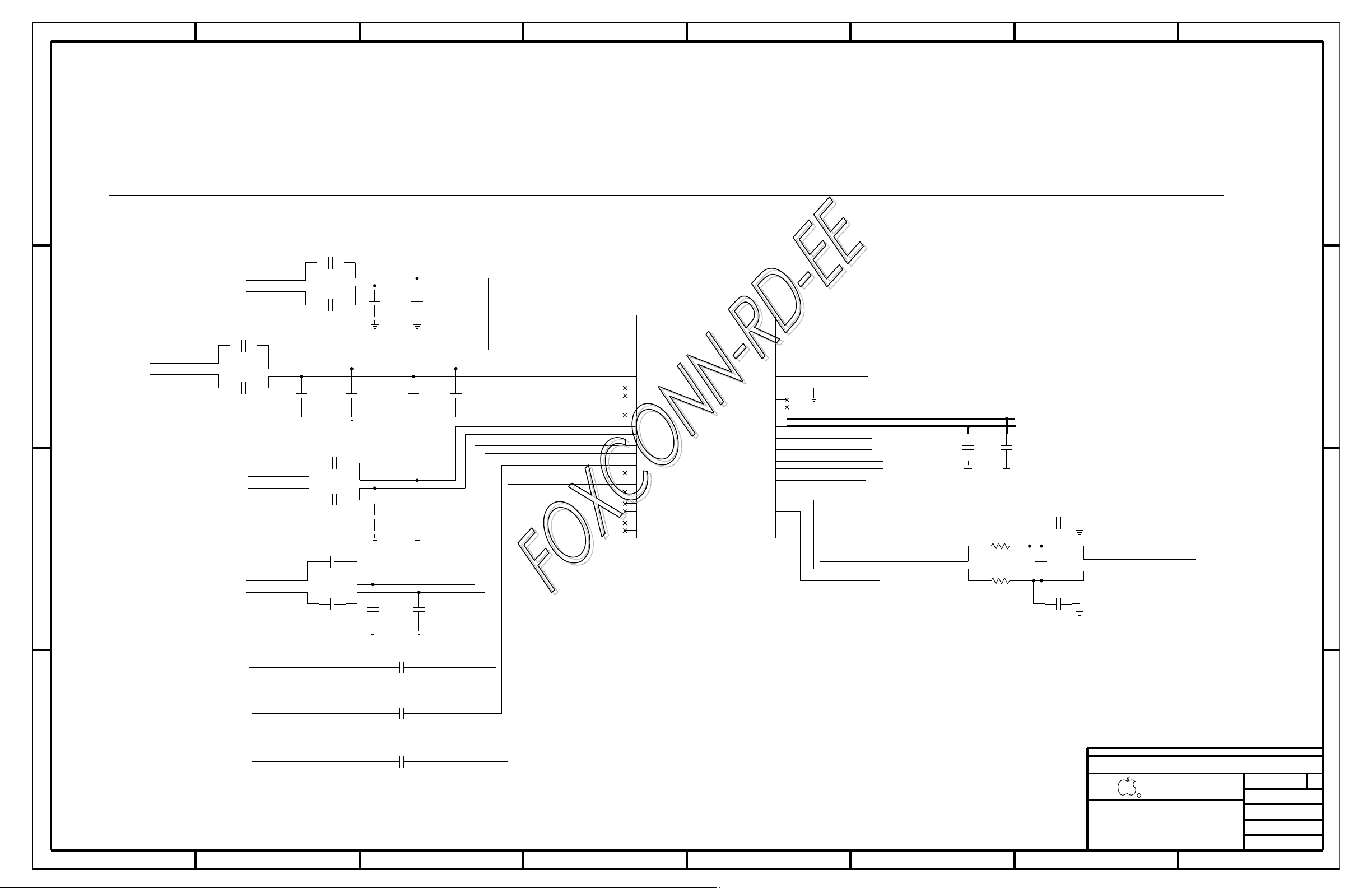

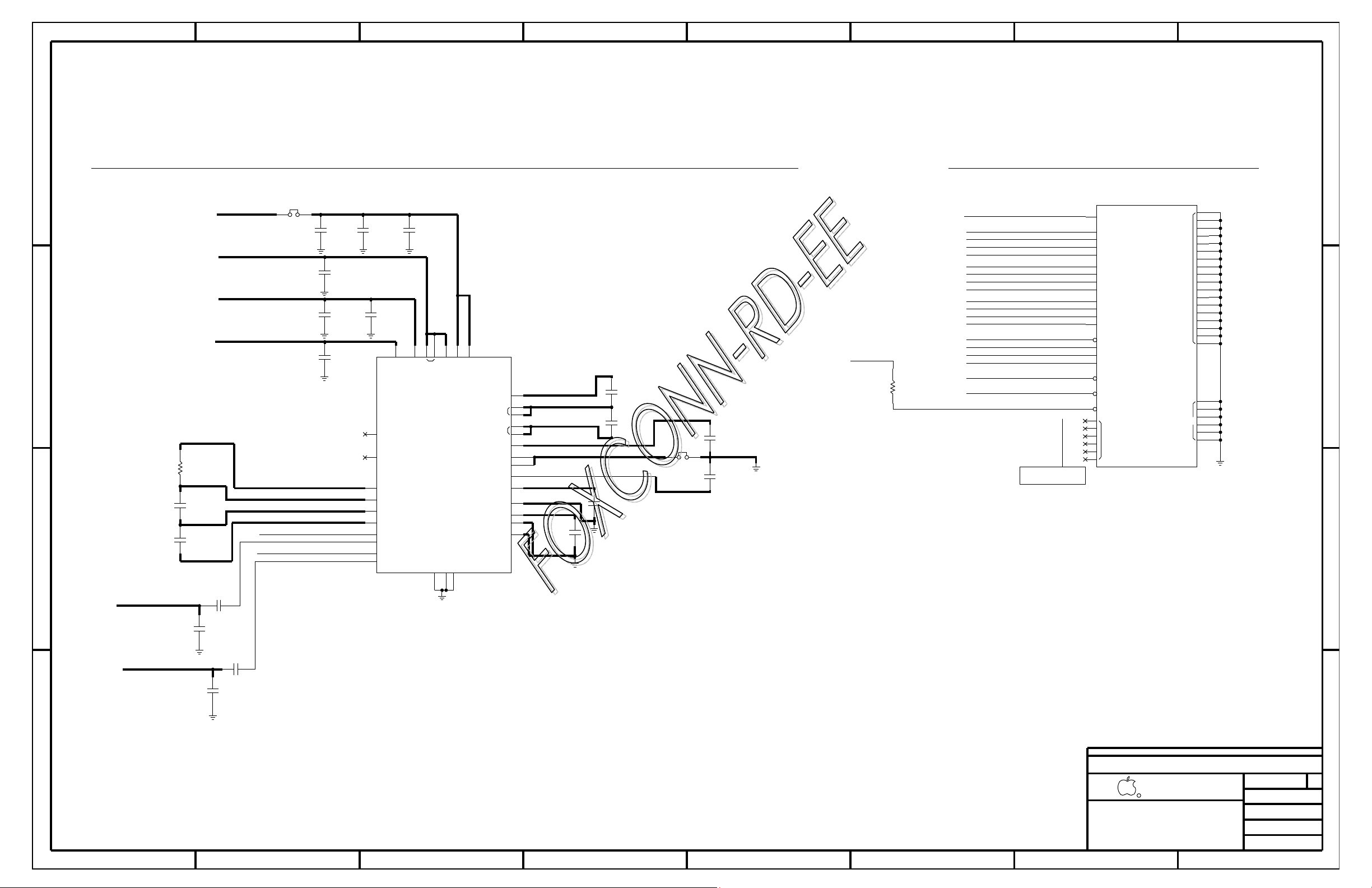

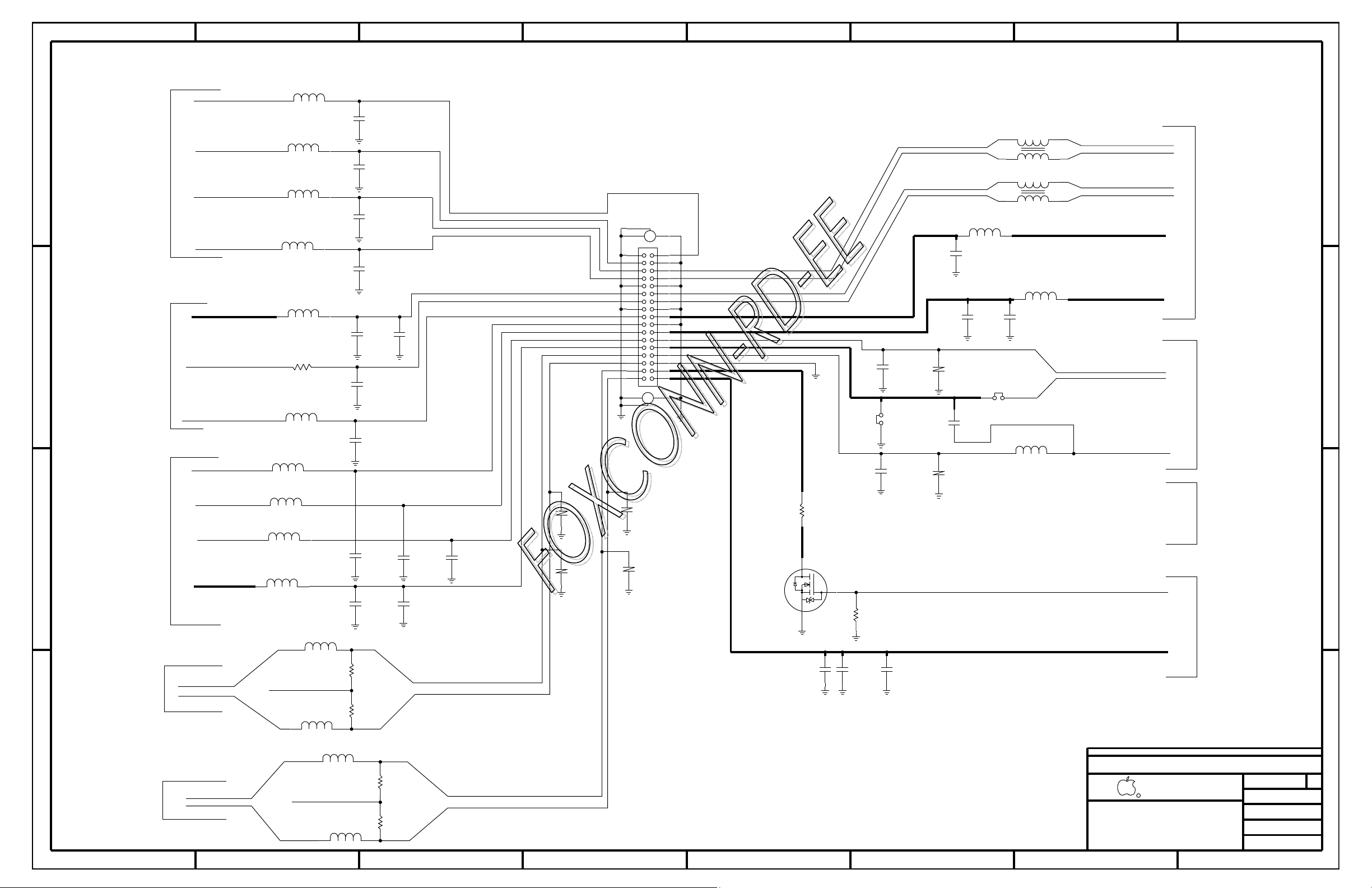

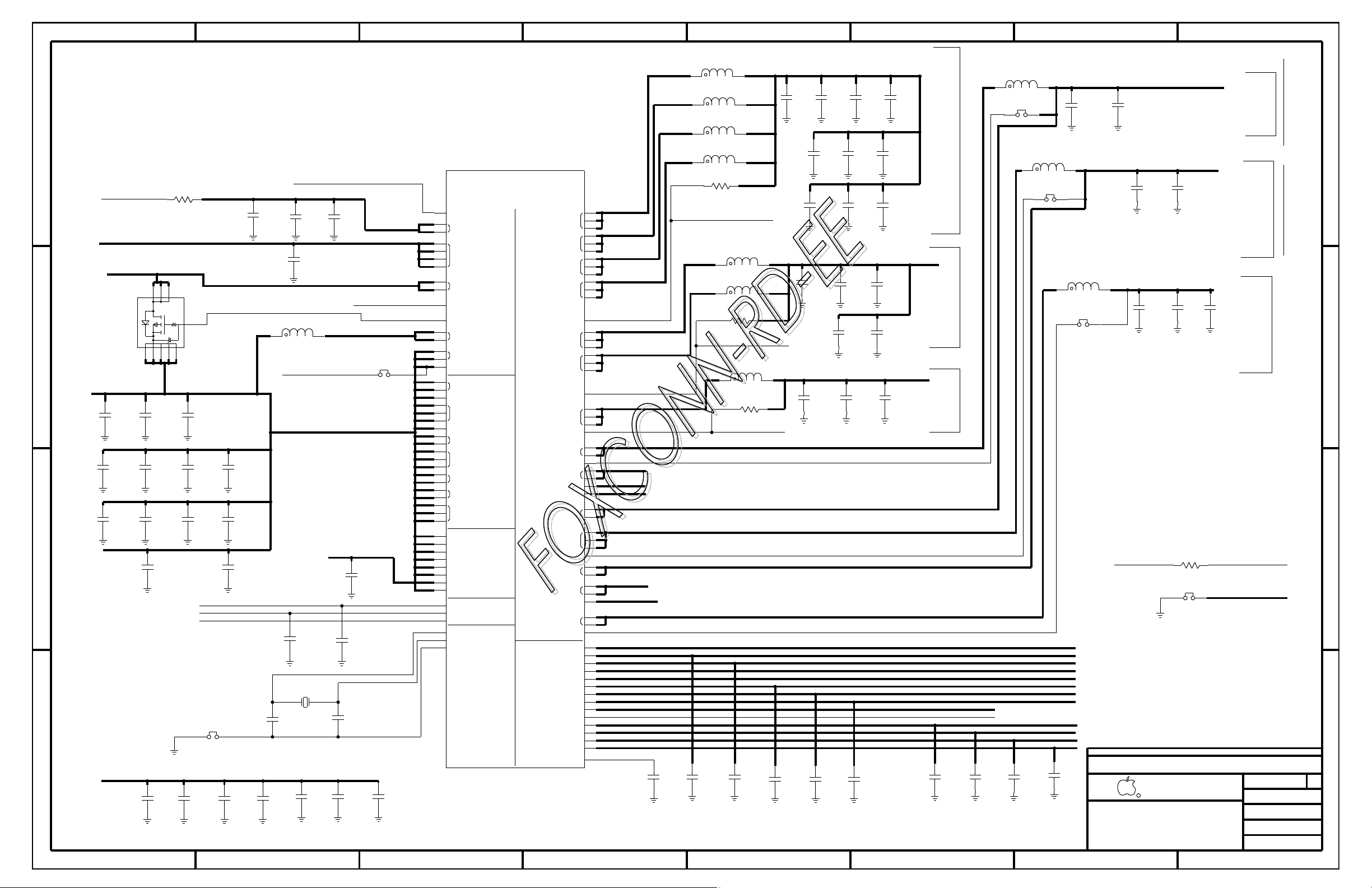

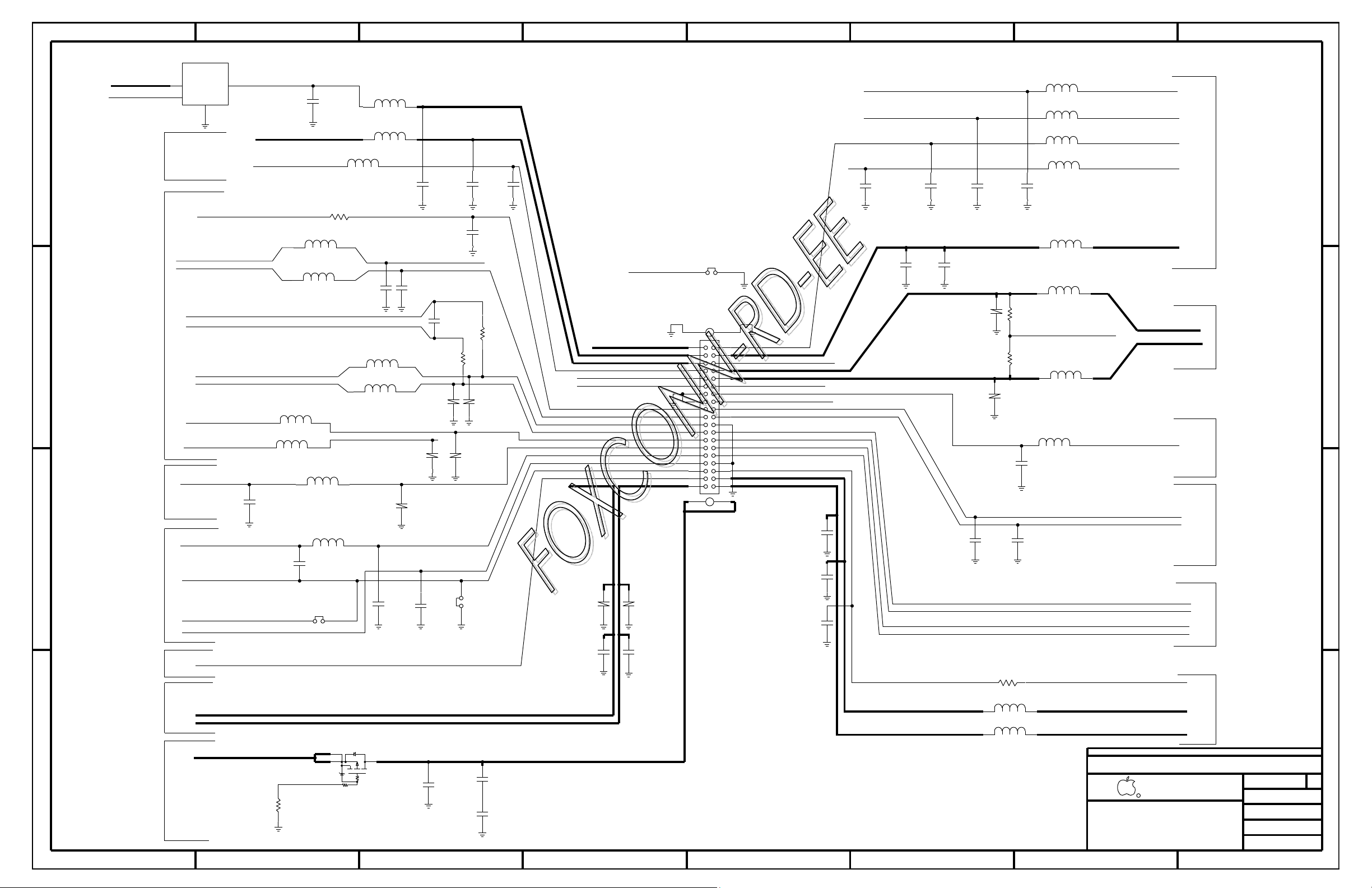

Apple iPhone 5S Schematic

2. ALL CAPACITANCE VALUES ARE IN MICROFARADS.

PROPRIETARY PROPERTY OF APPLE INC.

3. ALL CRYSTALS & OSCILLATOR VALUES ARE IN HERTZ.

DESCRIPTION OF REVISION

CK

APPD

2 1

1245678

B

D

6 5 4 3

C

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

THE INFORMATION CONTAINED HEREIN IS THE

C

A

D

DATE

R

SHEET

Apple Inc.

THE POSESSOR AGREES TO THE FOLLOWING:

DRAWING TITLE

D

SIZE

REVISION

DRAWING NUMBER

BRANCH

REV ECN

7

B

3

II NOT TO REPRODUCE OR COPY IT

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

IV ALL RIGHTS RESERVED

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

1. ALL RESISTANCE VALUES ARE IN OHMS, 0.1 WATT +/- 5%.

8

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_HEAD

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_ALT_ITEM

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

TABLE_5_ITEM

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

TABLE_5_ITEM

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

TABLE_5_ITEM

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

TABLE_5_ITEM

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_ALT_ITEM

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_ITEM

AMBER PMU:

ADI VCM AF DRIVER:

REAR FACING CAM:

CHESTNUT:

FOR RADIO BOMTABLE - SEE PG 24

ROHM VCM AF DRIVER:

LM3534 BL DRIVER:

FCAM I2C

0001100X 0X0C 0X18

8-BIT HEX

1110100X 0X74 0XE8

0010000X 0X10 0X20

1100011X 0X63 0XC6

DEVICE

TRISTAR:

RCAM I2C

OPEL STROBE DRIVER:

FRONT FACING CAM:

I2C0

I2C1

BINARY

CS35L19B AMP:

0110110X 0X36 0X6C

FOR CHESTNUT BOMTABLE - SEE PG 14

NOTE: ACCEL, GYRO, COMPASS ALL USING SPI (VIA OSCAR) FOR AP COMMUNICATION.

SCH 051-9478

MCO 056-5179

BRD 820-3292

BOM 639-4153 (32GB) X145

0001110X 0X0E 0X1C

1100011X 0X63 0XC6

I2C ADDRESS MAP

BOM 639-3465 (64GB) X145

BOM 639-4152 (16GB) X145

FOR MISC R/L/C - SEE PG 2

X145 SINGLE_BRD E1C

0100111X 0X27 0X4E

0101001X 0X29 0X52

7-BIT HEX

1000000X 0X40 0X80

0011010X 0X1A 0X34

CT814 ALS:

X145 BOM CALLOUTS

UPDATED FOR EVT2 RDAR://12984453

INDUCTOR BOM OPTIONS

BUCK0

SLAVE

NAND BOM ALTERNATES

SOC BOM ALTERNATES

NAND BOM OPTIONS

SOC BOM OPTIONS

OSCAR BOM OPTIONS

NAVAJO SPI BOM OPTIONS

AUDIO BOM OPTION

STROBE

BUCKXX

MASTER

AMP

SPKR

CHARGER

CHESTNUT

MISC BOM OPTIONS

RADIO_MLB ALTERNATES

Mon Feb 18 18:52:09 2013

1 OF 25

0001837617

8

051-9478

8.0.0

ENGINEERING RELEASED

2013-02-18

1 OF 56

335S0895

335S0935

335S0923

SPKAMP_ESDFILT_100PF

SPKAMP_CAPFILT_150PF

SPKAMP_CAPFILT_1000PF

DDR_RREF_243

CRITICAL

DDR_RREF 243OHM

2

R73,R72

118S0684

DDR_RREF_240

CRITICAL

2

R73,R72

DDR_RREF 240OHM

118S0723

U9 CRITICAL

OSCAR A1 FCLGA

1

337S4417

OSCAR_FCLGA

U9 CRITICAL

1

337S4416

OSCAR_CSP

OSCAR A1 CSP

NAVAJO_SERIES_0OHM

0OHMS SERIES R ON NAVAJO SPI

117S0161

4

FL32,FL63,FL50,FL59

CRITICAL

155S0453

120OHM FERRITES ON NAVAJO SPI

CRITICAL

4

FL32,FL63,FL50,FL59

NAVAJO_SERIES_FERRITE

CRITICALFL1,FL10

240OHM FERRITE BEAD

155S0755

HS3_HS4_240OHM_BEADS

2

CRITICALDZ13, DZ14

2

SPKAMP_ESDFILT_VARS

377S0106

VARISTOR 12V 33PF

CAP 01005 10V 100PF

DZ13, DZ14

2

CRITICAL131S0283

CRITICAL

HS3_HS4_120OHM_BEADS

120OHM FERRITE BEAD

2

FL1,FL10155S0453

CRITICAL

CAP 01005 10V 150PF

132S0437

2

C500, C501

CRITICAL

SPKAMP_FERRITE_LOWDCR

FL6, FL9

2

FERRITE 0402 P06OHM 1P8A

155S0731

CRITICAL

2

CAP 01005 10V 1000PF

132S0396 C500, C501

CRITICAL

FERRITE 0402 P14OHM 1A

2

SPKAMP_FERRITE_REG

155S0556 FL6, FL9

1

TI CHESTNUT: 1.5UH MURATA

152S1849

L19

CRITICAL

IND_CHESTNUT_1P5UH_MURATA

IND_CHESTNUT_1P5UH_TAIYO

152S1842

L19

CRITICAL

1

TI CHESTNUT: 1.5UH TAIYO

IND_CHESTNUT_1P5UH_CYNTEC

TI CHESTNUT: 1.5UH CYNTEC

152S1802

L19

1

CRITICAL

152S1850

IND_CHGR_2P2UH_MURATA

CHARGER IND: 2.2UH MURATA

1

L8 CRITICAL

CHARGER IND: 2.2UH TAIYO

L8

1

CRITICAL152S1721

IND_CHGR_2P2UH_TAIYO

SPKR AMP IND: 1.2UH TAIYO

CRITICALL4

1

152S1844

IND_SPKAMP_1P2UH_TAIYO

CRITICAL

SPKR AMP IND: 1.2UH CYNTEC

L4

1

152S1836

IND_SPKRAMP_1P2UH_CYNTEC

152S1840

STROBE IND: 1UH TAIYO

CRITICALL5

1

IND_STROBE_1UH_TAIYO

STROBE IND: 1UH CYNTEC

CRITICAL152S1801

1

L5

IND_STROBE_1UH_CYNTEC

L9,L11,L13,L15,L16,L17,L18

CRITICAL

7

152S1840

AMBER BUCKXX IND: 1UH TAIYO

IND_BUCKXX_1UH_TAIYO

AMBER BUCKXX IND: 1UH CYNTEC

L9,L11,L13,L15,L16,L17,L18

CRITICAL

IND_BUCKXX_1UH_CYNTEC

152S1801

7

197S0482

EPSON ALT

Y1_RF

197S0470

TDK WIFI ALT

U8_RF

339S0205339S0209

197S0491

KYOCERA ALT

Y1_RF

197S0470

USI WIFI ALT

U8_RF

339S0205339S0204

WINBOND NOR ALT

U6_RF

335S0874

U4335S0932

NAND_64GB_TOSHIBA

NAND_64GB_SANDISK

U4335S0932

335S0931 U4335S0934

NAND_32GB_SANDISK

335S0922 335S0931 U4

NAND_32GB_TOSHIBA

U4335S0921 335S0930

NAND_16GB_TOSHIBA

U4335S0930335S0933

NAND_16GB_SANDISK

NAND_64GCRITICAL

NAND,19NM,64GX8,MLC,PPN1.5,HYNIX

1

335S0932 U4

NAND_32G

NAND,19NM,32GX8,MLC,PPN1.5,HYNIX

335S0931 U4

1

CRITICAL

NAND_16G

NAND,19NM,16GX8,MLC,PPN1.5,HYNIX

U4

1

335S0930 CRITICAL

H6P + 1GB HYNIX

339S0207339S0208 U1

H6P + 1GB ELPIDA

CRITICAL

1

U1339S0207

1

LABEL FOR X145 639-4667

EEEE_SM_32G

EEEE_FGCD

CRITICAL825-6838

LABEL FOR X145 639-4669

1

825-6838

EEEE_SM_64G

EEEE_FGCF

CRITICAL

825-6838

1

LABEL FOR X145 639-4668

EEEE_SM_16G

CRITICAL

EEEE_FGCC

LABEL FOR X145 639-4153

EEEE_F7GQ

1

EEEE_MM_32G

825-6838 CRITICAL

EEEE_DYJP

825-6838 CRITICAL

1

LABEL FOR X145 639-3465

EEEE_MM_64G

1

825-6838

EEEE_MM_16G

EEEE_F7GR

LABEL FOR X145 639-4152

CRITICAL

BUCK0 SLAVE IND: 0.47UH, TAIYO

L10,L12,L14

3

CRITICAL152S1839

IND_BUCK0_SLV_P47UH_TAIYO

BUCK0 SLAVE IND: 0.47UH, CYNTEC

CRITICAL

3

152S1834

L10,L12,L14

IND_BUCK0_SLV_P47UH_CYNTEC

?1

CRITICAL820-3292

PCB

PCB, SINGLE_BRD, X145

051-9478

1

SCH

?

CRITICAL

SCH, SINGLE_BRD, X145

DATE

N/A

N/A

N/A

N/A

N/A

N/A

N/A

SCH,SINGLE_BRD,X145

2323

VOLTAGE NETS

N/A17 N/A

DOCKFLEX B2B

17

H6P NAND,NAND 12X17

66 N/A

CHESTNUT,BACKLIGHT DRIVER,MESA BOOST

N/A1414 N/A

1111

FRONT CAM FLEX B2B

12 12 N/A N/A

AMBER PMU(1/2)

N/A

BATT B2B, TPS, PD FEATURES

2222 N/A

Cross Reference Page

2525

N/A1818

D403 (TOUCH B2B, DRIVER ICS)

BUTTON FLEX B2B

N/A N/A88

L67 AUDIO CODEC (1/2)

N/A99 N/A

5 N/A5

19

N/A19

LCM B2B

N/A

1616 N/A

TRISTAR,EEPROM

N/A

AMBER PMU(2/2)

1313

15

SPKR AMP + STROBE DRIVER

15 N/A

N/A

2424

RADIO_MLB HIERARCH. SYMBOL

N/A

L67 AUDIO CODEC (2/2)

N/A N/A1010

N/A44 N/A

H6P VDDCA,VDD1/2,VDD,VDD_CPU,VDD_GPU

N/A33 N/A

2121

REAR CAM B2B

N/A22 N/A

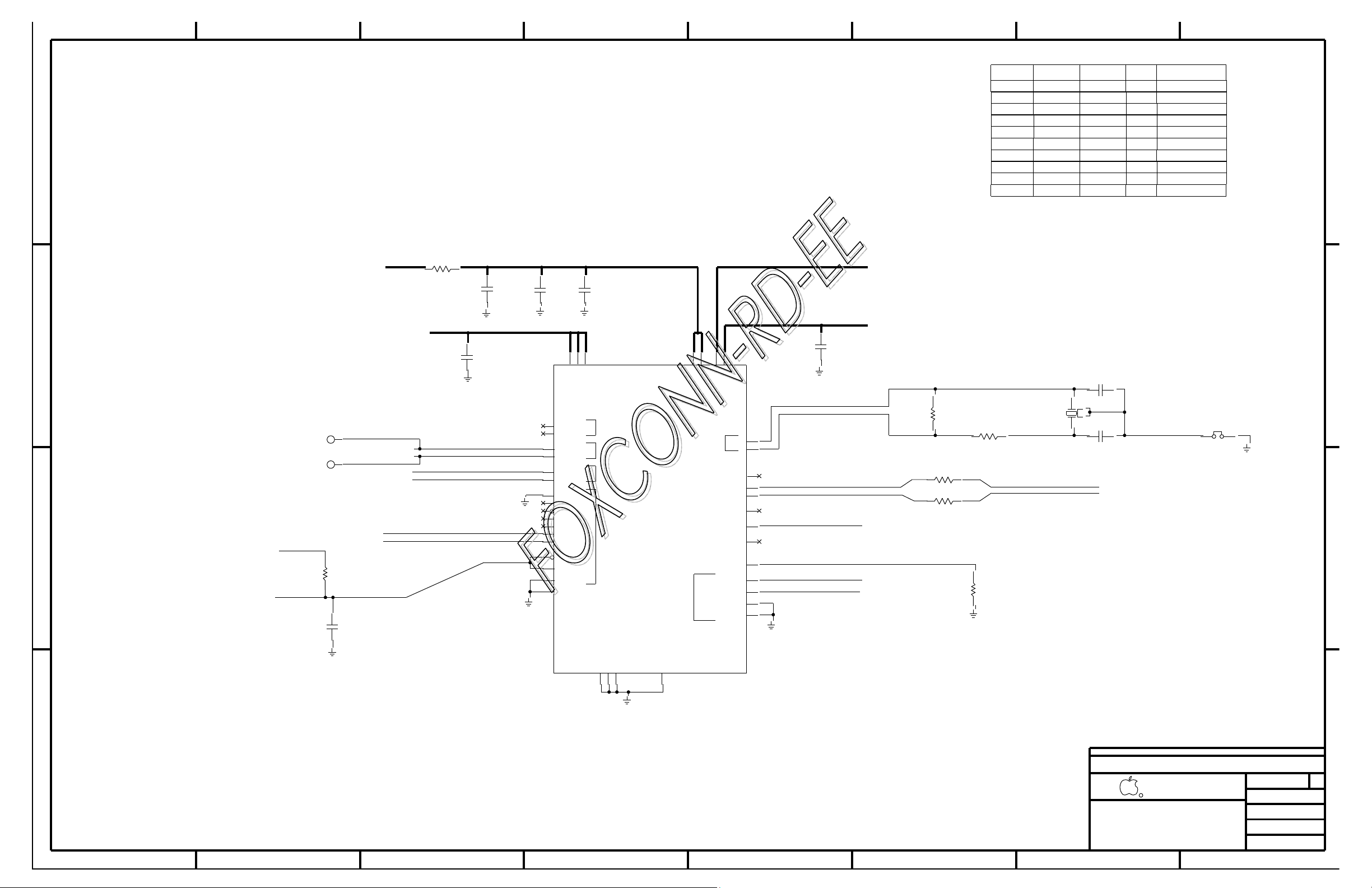

H6P JTAG,USB,PLL,HSIC,XTAL

2020 N/A

OSCAR + SENSORS

SYNC MASTER

CONTENTS

PDF PAGE CSA PAGE

H6P HIGH SPEED DIG (CAM,LCM,DP)

N/A N/A77

H6P DIGITAL I/O,BOOTSTRAPPING

H6P GND,VDDIO18,VDDIOD,VDD_SRAM,VDD_SOC

N/A

N/A

N/A N/A

SYM 1 OF 13

HSIC2_STB

USB_VSSA0

USB_ANALOGTEST

TESTMODE

USB_DP

USB_DM

WDOG

TST_CLKOUT

FAST_SCAN_CLK

USB_REXT

USB_VBUS

USB_ID

JTAG_SEL

JTAG_TRST*

JTAG_TDO

JTAG_TDI

HSIC_VSS120

JTAG_TCK

JTAG_TMS

JTAG_TRTCK

XI0

XO0

HSIC0_DATA

HSIC0_STB

HSIC2_DATA

HSIC_VSS121

HSIC_VSS122

RESET*

CFSB

HOLD_RESET

FUSE1_FSRC

HSIC1_DATA

HSIC1_STB

USB_VDD330

USB_DVDD

VDD_ANA_PLL_CCC

ANALOGMUXOUT

HSIC_VDD120

HSIC_VDD122

HSIC_VDD121

VDD_ANA_PLL

PP

PP

NC

NC

NC

NC

NC

NC

NC

NC

NC

TABLE_ALT_ITEM

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

8 7 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

N/C OK PER SEG 5/14/12

N/C OK PER SEG 5/14/12

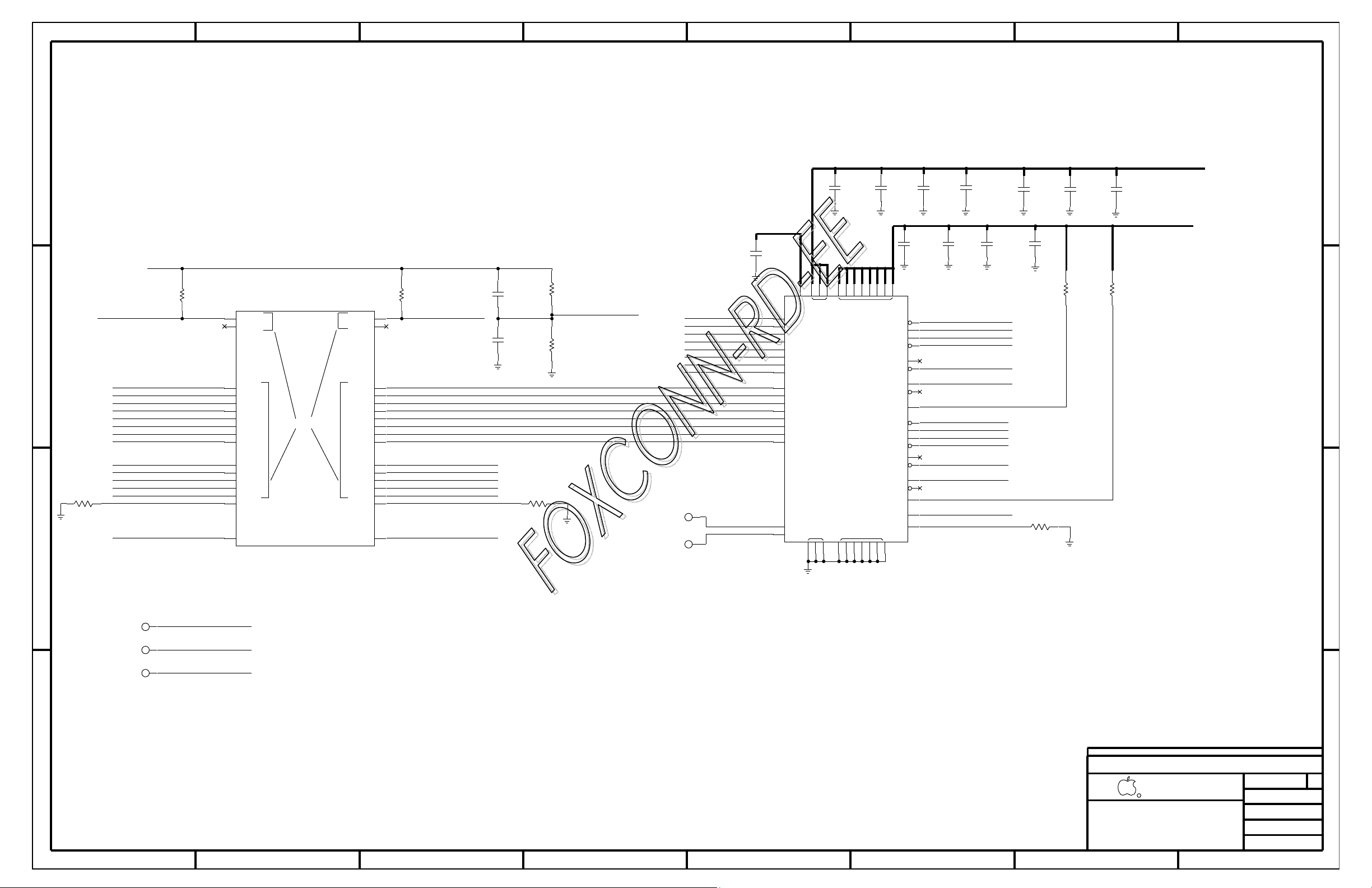

H6P: JTAG, USB, PLL, HSIC, XTAL

JTAG_TRSTN IS N/C WITH ALCATRAZ B0

RDAR://12963383

REVERT R67 TO 100K B/C OF H6 B0

SERIAL MODE NAMES

MISC COMPONENTS ALTERNATES

(1MA)

(REPLACE WITH XW LATER?)

HSIC_VDD120

NOTE: REPLACING INDUCTORS WITH

BASEBAND

1.8V TOLERANT

0OHMS FOR PROTO2 UNTIL VERIFY USB EYE

(6X 1MA)

C34 DELETED HERE

WLAN (TOP)

PCB: PLACE

HSIC_VDD122

VDDIO18_GRP3

(3X 13MA)

VDDIO18_GRP1

HSIC_VDD121

PCB: PLACE THIS XW

(25MA)

OLD (H5) VALUE: 44.2 OHM

VALUE FOR H6 = 200 OHM

NOTE: NEW USB_REXT

PCB: PLACE

NEAR U1

(5.4MA)

VDDIO18_GRP4

USBHS ON/OFF TOLERANCE 5V/1.98V

AT U1, NEAR XI/XO

NEAR R1

(25MA)

PCB: PLACE

RDAR://12963383

TBD: XTAL PASSIVES WILL CHANGE ON H6P WITH FIRST HW BUILD

NEAR U1.AE20

NEAR U1.U16

PCB: PLACE

N/C OK PER SEG 5/14/12

N/C OK PER SEG 5/14/12

NOTE: CANDIDATE FOR COST-SAVINGS

RDAR://13212472

138S0657

ROOM=H6P

01005

MF

1.33K

1/32W

1%

0201

20%

6.3V

0.22UF

X5R

ROOM=H6P

0.00

01005

ROOM=H6P

ROOM=H6P

6.3V

01005

10%

1000PF

X5R-CERM

01005

X5R

10%

ROOM=H6P

0.01UF

6.3V

16V

ROOM=H6P

5%

01005

CERM

12PF

16V

12PF

CERM

ROOM=H6P

01005

5%

10%

6.3V

X5R

01005

0.01UF

ROOM=H6P

1/32W

200

ROOM=H6P

01005

1%

MF

MF

01005

ROOM=H6P

1%

1/32W

1.00M

SHORT-10L-0.1MM-SM

ROOM=H6P

ROOM=H6P

1.60X1.20MM-SM

24.000MHZ-30PPM-9.5PF-60OHM

H6PPOP-1GB-DDR

OMIT_TABLE

FCMSP

SC58960X01-A030

01005

ROOM=H6P

0.00

ROOM=H6P

01005

0.00

01005

ROOM=H6P

6.3V

X5R-CERM

0.1UF

20%

0.1UF

20%

01005

6.3V

ROOM=H6P

X5R-CERM

SM

P2MM

SM

P2MM

MF

1/32W

1%

100K

ROOM=H6P

01005

?

155S0667 155S0583

155S0453

?

155S0773

?

335S0895 335S0874

138S0739

?

138S0706

138S0746 138S0705

?

?

138S0697 138S0695

?

138S0702

107S0146

ALT FOR THERMISTOR

107S0208

H6P JTAG,USB,PLL,HSIC,XTAL

SYNC_MASTER=N/A

SYNC_DATE=N/A

AP_TO_PMU_TEST_CLKOUT

PP1V8_PLL

TRISTAR_TO_AP_JTAG_SWCLK

45_XTAL_24M_I

45_XTAL_24M_O

PP1V8

50_AP_BI_WLAN_HSIC2_DATA

50_AP_BI_WLAN_HSIC2_STB

AP_TO_PMU_RESET_IN

90_AP_BI_TRISTAR_USB0_H6P_N

90_AP_BI_TRISTAR_USB0_H6P_P

USB_VBUS_DETECT

90_AP_BI_TRISTAR_USB0_P

90_AP_BI_TRISTAR_USB0_N

45_XTAL_24M_O_R

USB_REXT

45_XTAL_24M_GND

PP1V0

PP3V3_USB

50_AP_BI_BB_HSIC1_STB

PP1V8

PP1V2

RESET_1V8_L

TRISTAR_BI_AP_JTAG_SWDIO

50_AP_BI_BB_HSIC1_DATA

138S0648138S0703

?

118S0717

ALT FOR TCAL (R109)

118S0764

R71

1 2

C2

1

2

R1

1 2

C1

1

2

C21

1

2

C36

1 2

C37

1 2

C20

1

2

R6

1

2

R7

1

2

XW44

1 2

Y1

2 4

1 3

U1

E26

E29

AD3

H16

D29

A26

B26

A27

B27

AM33

AM34

G22

G23

AM31

H20

H21

AM32

D28

C28

F27

E27

F28

E28

D27

F29

AB3

AC3

D26

A29

B29

F24

E24

E23

D23

F23

H23

U16

AE20

AD4

F25

E25

R163

1 2

R164

1 2

C33

1

2

C35

1

2

PP23

1

PP24

1

R67

1

2

051-9478

8.0.0

2 OF 25

2 OF 56

13

23

16

2 3 5 6 7

10 11 12 14 16 18

19 21 23

24

24

13

12 23

16

16

7

12 23

12 23

24

2 3 5 6 7

10 11 12 14 16 18

19 21 23

4 5

12 23

4

13 14 16 19 22 24

16

24

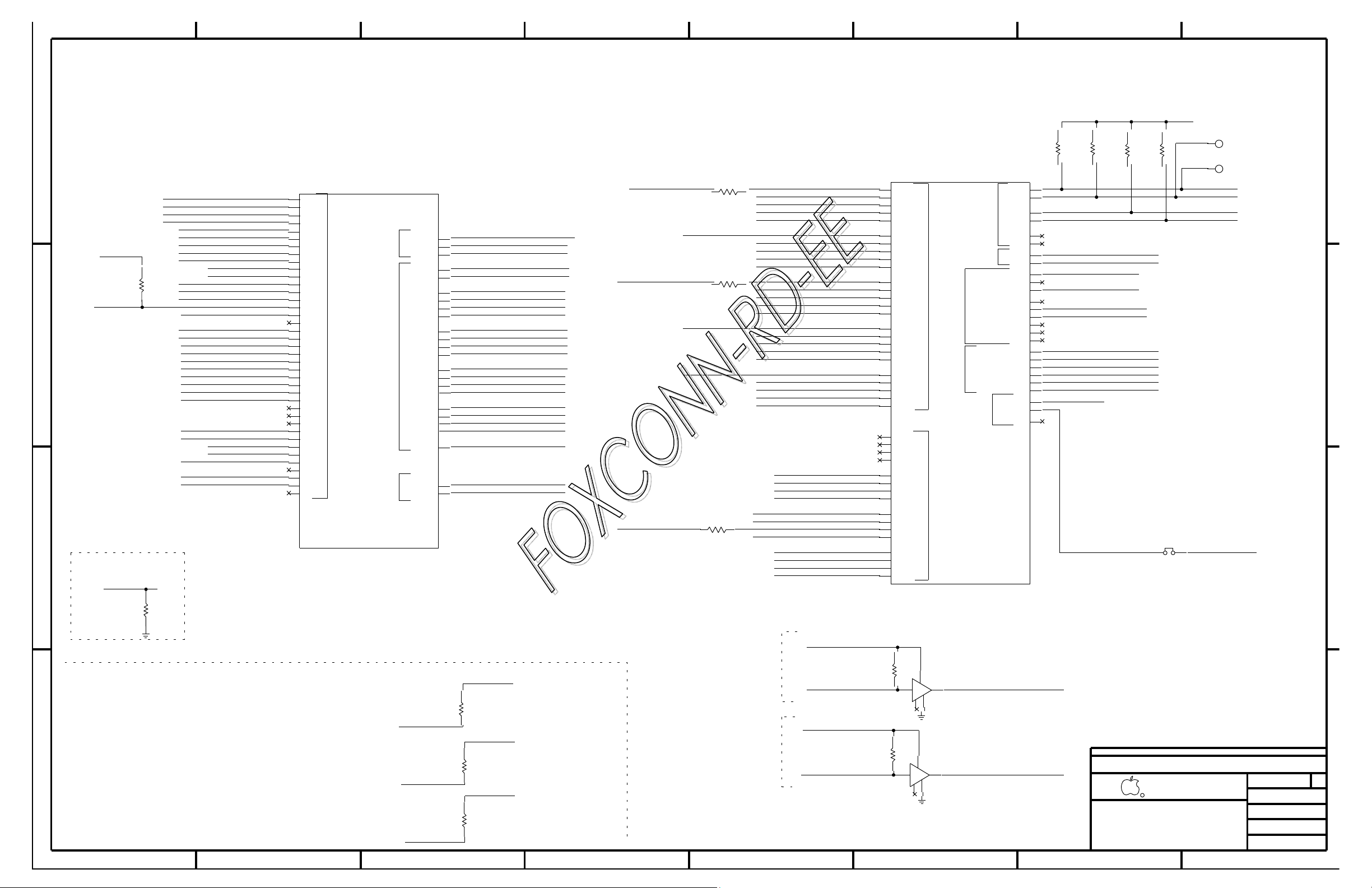

SYM 2 OF 13

GPIO4

UART6_TXD

UART6_RXD

UART5_RTXD

UART4_RTSN

UART4_CTSN

UART3_RXD

UART3_RTSN

UART3_CTSN

UART2_TXD

UART2_RXD

UART2_RTSN

UART2_CTSN

UART1_TXD

UART1_RXD

UART1_RTSN

UART1_CTSN

UART0_TXD

UART0_RXD

TMR32_PWM2

TMR32_PWM1

TMR32_PWM0

GPIO8

GPIO7

GPIO6

GPIO5

GPIO38

GPIO37

GPIO36

GPIO35

GPIO34

GPIO33

GPIO32

GPIO31

GPIO3

GPIO28

GPIO27

GPIO26

GPIO25

GPIO24

GPIO23

GPIO22

GPIO21

GPIO20

GPIO2

GPIO19

GPIO18

GPIO17

GPIO16

GPIO15

GPIO14

GPIO13

GPIO12

GPIO11

GPIO1

GPIO0

UART4_RXD

GPIO29

GPIO30

UART3_TXD

UART4_TXD

GPIO10

GPIO9

SPI3_SSIN

SPI3_MOSI

SPI3_MISO

SPI2_SSIN

SPI2_SCLK

SPI2_MOSI

SPI2_MISO

SPI1_SSIN

SPI1_SCLK

SPI1_MOSI

SPI1_MISO

SPI0_SSIN

SPI0_SCLK

SPI0_MOSI

SPI0_MISO

SOCHOT1

SOCHOT0

SIO_7816UART1_SCL

SIO_7816UART1_RST

SIO_7816UART0_SCL

SEP_7816UART1_SCL

SEP_7816UART0_RST

I2S4_MCK

I2S4_LRCK

I2S4_DOUT

I2S4_DIN

I2S4_BCLK

I2S3_MCK

I2S3_LRCK

I2S3_DOUT

I2S3_DIN

I2S3_BCLK

I2S2_MCK

I2S2_LRCK

I2S2_DOUT

I2S2_DIN

I2S2_BCLK

I2S1_MCK

I2S1_LRCK

I2S1_DOUT

I2S1_DIN

I2S1_BCLK

I2S0_MCK

I2S0_LRCK

I2S0_DOUT

I2S0_DIN

I2S0_BCLK

I2C3_SDA

I2C3_SCL

I2C2_SDA

I2C2_SCL

I2C1_SDA

I2C1_SCL

I2C0_SDA

I2C0_SCL

DWI_DO

DWI_DI

DWI_CLK

SIO_7816UART0_SDA

SIO_7816UART0_RST

SEP_7816UART1_SDA

SEP_7816UART1_RST

SEP_7816UART0_SCL

SEP_7816UART0_SDA

SIO_7816UART1_SDA

SPI3_SCLK

DISP_VSYNC

SYM 3 OF 13

NC

NC

PP

PP

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

8 7 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

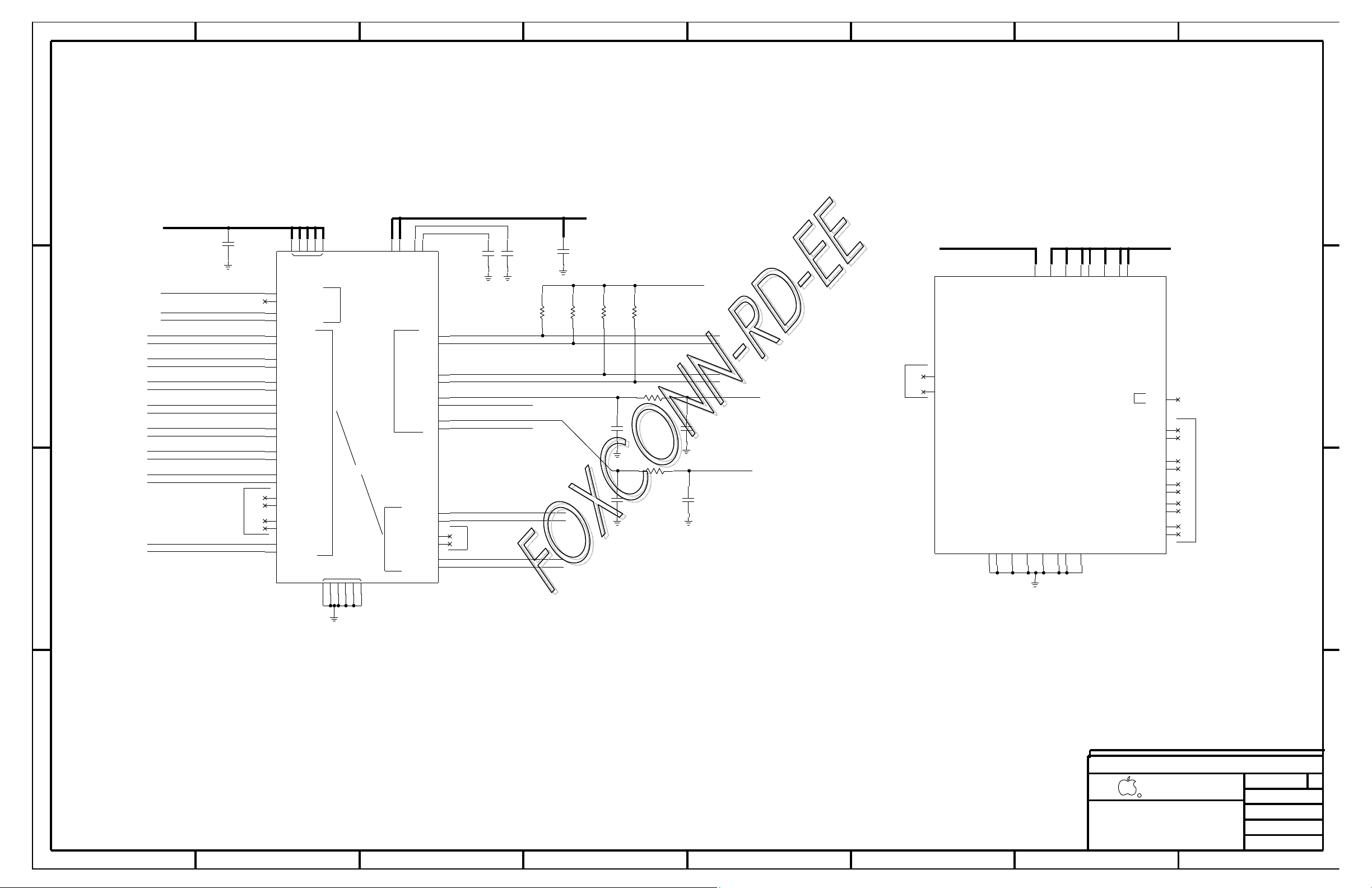

H6P: DIGITAL I/O, BOOTSTRAPPING

VDDIO18_GRP2

REMOVE LCM_TO_AP_PIFA (RDAR://12858364

NAVAJO

CODEC

VDDIO18_GRP1

BB_JTAG_TDI

COMMON PULL UP FOR BOARD_REV, BOARD_ID AND BOOT_CONFIG PINS

R12 MUST WIN OVER 6X INTERNAL PULL-DOWNS THAT ARE ~100K

BOARD_ID[3:0]={GPIO16, SPIO0_MISO, SPI0_MOSI, SPI0_SCLK}

<--- SELECTED (NOSTUFF R3000 & STUFF R3001)

1010 E1C MAIN BUILD

BOOTSTRAPPING (BOARD_REV, BOARD_ID, BOOT_CFG)

BOARD_REV[3:0]={GPIO34, GPIO35, GPIO36, GPIO37}

<--- SELECTED

FLOAT=LOW, PULLUP=HIGH

1011 E1B MAIN BUILD

1100 EVT1A MESA BUILD

1101 EVT1 MESA BUILD

1111 PROTO2/2A, TRISAR/L19

1110 EVT1 MAIN BUILD

0001 X145 DEV

0000 X145 MLB

0011 X152 DEV

0001 SPI0 TEST MODE

0010 NAND

0010 X152 MLB

BOOT_CONFIG[3:0]={GPIO29_CONFIG3,GPIO28_CONFIG2,GPIO25_CONFIG1,GPIO18_CONFIG0}

FLOAT=LOW, PULLUP=HIGH

CHANGE R93 TO XWLINK XW93 TO STILL ENABLE PROBING

EEPROM

MENU & POWER / HOLD KEY BUFFER

PCB: PLACE THIS BOTTOM SIDE,

BOOT_CONFIG3

BB_JTAG_TCK

RDAR//12853395

REMOVED AP_TO_NAVAJO NET

MAKE SURE THIS GPIO ISN’T FLOATING

REMOVED R146 PU FROM NAVAJO

REMOVED R53 (HAS BEEN NOSTUFF SINCE EVT1)

RDAR://12963380

RDAR//12853395

BOARD_REV0

BOARD_REV1

BB_JTAG_TDO

BOARD_REV3

<--- SELECTED

ACCESSORY UART: TOLERANCE 1.98V

CODEC VSP

BLUETOOTH

DEBUG UART: TOLERANCE 1.98V

VDDIO18_GRP1

FLOAT=LOW, PULLUP=HIGH

BOOT_CONFIG0

VDDIO18_GRP2

L19A KEEP (STAYING) ALIVE -->

VDDIO18_GRP1

GAS GAUGE

0000 SPI0

0011 NAND TEST MODE

SOUTH END OF SINGLE_BRD

BT

VDDIO18_GRP1

DFU STATUS

CODEC ASP

BOARD_REV2

PCB: PLACE THIS TOP SIDE,

NORTH END OF SINGLE_BRD

BB_JTAG_TMS

BB

BOOT_CONFIG2

BOOT_CONFIG1

BASEBAND

VDDIO18_GRP2VDDIO18_GRP1

BOARD_ID2

CODEC XSP & SPKR AMP

VDDIO18_GRP2

WIFI UART

BOARD_ID1

GRAPE

VDDIO18_GRP1

REMOVED PU FROM NAVAJO

VDDIO18_GRP2

OSCAR

BOARD_ID0

BOARD_ID3

PLACE PP300 IN MOJAVE AREA TO SEE BRINGING SOCHOT0 THERE

RDAR://13057149

RDAR://12963383

FOR A0 ROM. CAN BE REMOVED

PULLDOWN NEEDED ON FORCE_DFU

WHEN GET B0 SILICON

NOTE: THIS PULLUP + NET FOR NAVAJO

TO BE DELETED FROM DESIGN

DAISY-CHAIN (PROTO1A/PROTO2)

WHEN NAVAJO SILICON ARRIVES.

PLACE XW93 ON OUTER LAYER

ROOM=H6P

1/32W

1%

MF

01005

33.2

01005

1/32W

1.00K

MF

5%

2.2K

5%

1/32W

01005

MF

5%

1/32W

01005

2.2K

MF

MF

01005

2.2K

1/32W

5%

MF

5%

1/32W

01005

2.2K

MF

01005

33.2

ROOM=H6P

1%

1/32W

220K

5%

1/32W

01005

MF

MF

01005

392K

1%

1/32W

OMIT_TABLE

FCMSP

H6PPOP-1GB-DDR

SC58960X01-A030

H6PPOP-1GB-DDR

FCMSP

SC58960X01-A030

OMIT_TABLE

100K

01005

1/32W

5%

MF

NOSTUFF

SOT1226

74LVC1G34GX

74LVC1G34GX

SOT1226

1/32W

1%

MF

01005

392K

0%

01005

1/32W

MF

0.00

NOSTUFF

01005

MF

0%

0.00

1/32W

SM

P2MM

P2MM

SM

SM

ROOM=H6P

33.2

MF

01005

1%

1/32W

H6P DIGITAL I/O,BOOTSTRAPPING

SYNC_DATE=N/A

SYNC_MASTER=N/A

AP_TO_PMU_SOCHOT1_H6P

AP_TO_CODEC_SPI3_MOSI

FORCE_DFU

45_AP_TO_CODEC_VSP_I2S4_BCLK

TRISTAR_TO_AP_INT

AP_TO_OSCAR_DBGEN

SOCHOT0

AP_TO_BT_UART1_TXD

BT_TO_AP_UART1_RXD

AP_TO_BT_UART1_RTS_L

AP_TO_SPKAMP_BEE_GEES

45_AP_TO_CODEC_XSP_I2S2_BCLK

45_AP_TO_SPKAMP_I2S2_MCLK_R

45_AP_TO_PMU_DWI_CLK

AP_TO_EEPROM_I2C_SCL

AP_BI_EEPROM_I2C_SDA

AP_BI_OSCAR_SWDIO_1V8

AP_TO_OSCAR_SWDCLK_1V8

AP_TO_I2C0_SCL

AP_TO_BB_I2S1_LRCLK

45_AP_TO_BT_I2S3_BCLK

AP_TO_BT_I2S3_LRCLK

AP_TO_I2C1_SCL

AP_TO_CODEC_ASP_I2S0_DOUT

45_AP_TO_BB_I2S1_BCLK

BT_TO_AP_I2S3_DIN

AP_TO_BB_JTAG_TRST_L

45_AP_TO_CODEC_I2S_MCLK_R

CODEC_TO_AP_ASP_I2S0_DIN

AP_BI_I2C1_SDA

45_AP_TO_PMU_DWI_DO

AP_TO_BB_HSIC1_RDY

AP_TO_CODEC_XSP_I2S2_LRCLK

BB_TO_AP_UART4_CTS_L

WLAN_TO_AP_UART3_RXD

AP_TO_BB_UART4_RTS_L

TOUCH_TO_AP_INT_L

BOARD_INFO

BUTTON_TO_AP_HOLD_KEY_L

BUTTON_TO_AP_MENU_KEY_L

AP_TO_CODEC_VSP_I2S4_LRCLK

AP_TO_TOUCH_SPI1_CLK

CODEC_TO_AP_SPI3_MISO

BT_TO_AP_UART1_CTS_L

45_AP_TO_TOUCH_CLK32K_RESET_L

AP_TO_BB_RST_L

CODEC_TO_AP_XSP_I2S2_DIN

CODEC_TO_AP_VSP_I2S4_DIN

AP_TO_RADIO_ON_L

AP_TO_TOUCH_SPI1_CS_L

BB_TO_AP_I2S1_DIN

WLAN_TO_AP_HSIC2_RDY

OSCAR_TO_AP_UART2_RXD

AP_TO_TOUCH_SPI1_MOSI

AP_TO_BB_JTAG_TMS

BB_TO_AP_HSIC1_REMOTE_WAKE

BB_TO_AP_HSIC1_RDY

WLAN_TO_AP_HSIC2_REMOTE_WAKE

AP_TO_BB_I2S1_DOUT

BUTTON_TO_AP_HOLD_KEY_BUFF_L

AP_TO_CODEC_SPI3_CLK

AP_TO_CODEC_ASP_I2S0_LRCLK

45_AP_TO_CODEC_ASP_I2S0_BCLK

AP_TO_RCAM_VDDCORE_EN

OSCAR_TO_PMU_HOST_WAKE

AP_TO_HEADSET_HS4_CTRL

BB_TO_AP_JTAG_TDO

AP_TO_BT_WAKE

BUTTON_TO_AP_VOL_DOWN_L

AP_TO_CODEC_SPI3_CS_L

45_AP_TO_SPKAMP_I2S2_MCLK

AP_TO_PMU_VIBE_PWM_EN

BUTTON_TO_AP_MENU_KEY_BUFF_L

TRISTAR_TO_AP_DEBUG_UART0_RXD

AP_TO_OSCAR_RESET_L

AP_TO_WLAN_HSIC2_RDY

AP_TO_BB_JTAG_TDI

LCM_TO_AP_HIFA_BSYNC

BB_TO_AP_RESET_DET_L

BOARD_INFO

AP_TO_BB_WAKE_MODEM

FORCE_DFU

AP_TO_TRISTAR_ACC_UART6_TXD

AP_TO_SPKAMP_RESET_L

45_AP_TO_CODEC_I2S_MCLK

AP_TO_TRISTAR_DEBUG_UART0_TXD

PP1V8

PP1V8_ALWAYS

PP1V8_SDRAM

OSCAR_BI_AP_TIME_SYNC_HOST_INT

PMU_TO_AP_IRQ_L

AP_TO_HEADSET_HS3_CTRL

AP_TO_PMU_KEEPACT

BOARD_INFO

AP_TO_BB_JTAG_TCK

TOUCH_TO_AP_SPI1_MISO

AP_TO_BB_UART4_TXD

PP1V8

AP_TO_CODEC_XSP_I2S2_DOUT

ALS_TO_AP_INT_L

AP_TO_BT_I2S3_DOUT

AP_TO_WLAN_UART3_TXD

CODEC_TO_AP_INT_L

AP_TO_CODEC_VSP_I2S4_DOUT

AP_TO_TOUCH_GRAPE_RESET_L

BUTTON_TO_AP_MENU_KEY_BUFF_L

BOARD_INFO_M

AP_TO_PMU_SOCHOT1

BOARD_INFO

BOARD_INFO

BOARD_INFO_R

BOARD_INFO_M

AP_BI_I2C0_SDA

PP1V8_SDRAM

BUTTON_TO_AP_RINGER_A

AP_TO_LCM_RESET_L

BOARD_INFO_R

BOARD_INFO

BUTTON_TO_AP_HOLD_KEY_BUFF_L

NAVAJO_TO_AP_SPI2_MISO

AP_TO_NAVAJO_SPI2_MOSI

NAVAJO_TO_PMU_INT_H

AP_TO_NAVAJO_SPI2_CLK

AP_TO_NAVAJO_SPI2_CLK_R

AP_TO_OSCAR_UART2_TXD

BB_TO_AP_PP_SYNC

BB_TO_AP_UART4_RXD

AP_BI_BATTERY_SWI

TRISTAR_TO_AP_ACC_UART6_RXD

BUTTON_TO_AP_VOL_UP_L

SPKAMP_TO_AP_INT_L

R16

1 2

R12

1

2

R17

1

2

R18

1

2

R19

1

2

R21

1

2

R5

1 2

R52

1

2

R22

1

2

U1

AC5

AB1

AF4

AF2

AG1

AG3

AG4

AH3

AH2

AH4

AG5

AJ5

AB2

AJ4

AK2

AP13

AP12

AR13

AN14

AT12

AT13

AV13

AP14

AD1

AU13

AP15

AR14

AT14

AT15

AP16

AR16

AT16

AT17

AD5

AE4

AF1

AE2

AE5

AF3

AC31

AD34

AC32

AR19

AR18

AL2

AL4

AK4

AK3

AL5

AM3

AM2

AM1

AN3

AN4

AP1

AN1

AV3

AU3

AT3

AT2

AM5

W31

Y31

U1

AN17

AP19

AT18

AT19

AV6

AR7

AP8

AU7

AT11

AR11

W30

W32

AL32

AJ31

AK31

AL31

C30

AL34

AJ32

AK34

AK33

AL33

AJ33

AH31

AH34

AJ34

E30

AG32

AF31

AG34

AH33

AG31

AF33

AD31

AE33

AE32

AE31

AR1

AP3

AP2

AR4

AR2

AP4

AB33

AA31

AB31

AA33

AA32

AA34

AP18

AP17

AN6

AP5

AT5

AV5

AU5

AV4

AU4

AR5

AU6

AR6

AP7

AN8

AV10

AN12

AT10

AP11

R162

1

2

U25

2

3

5

4

U26

2

3

5

4

R20

1

2

R3000

1

2

R3001

1

2

PP13

1

PP15

1

XW93

1 2

R399

1 2

051-9478

8.0.0

3 OF 25

3 OF 56

1

1

10

3

22

10

13 16

20

16

24

24

24

15

10 15

13 14

16

16

20

20

13 14 15 16

24

24

24

11

10

24

24

24

10

11

13 14

24

10 15

24

24

24

18

3

8

17

10

18

10

24

18

24

10 15

10

24

18

24

24

20

18

24

24

24

24

24

3

13

10

10

10

21

13 20

17

24

24

8

13

10

15

12

3

13

16

20

24

24

18 19

24

3

24

3

22

16

15

10

16

2 3 5 6 7

10 11 12 14 16 18 19

21 23

12 23

3 4

10

12 14 16

17 23 24

20

13

17

13

3

24

18

16 24

2 3 5 6 7

10 11 12 14 16 18 19

21 23

10 15

11

24

24

10

10

18

3

13

3

13

3

3

3

3

13 14 15 16

3 4

10 12 14 16 17

23 24

8

13

19

3

3

3

13

17

17

13 17

17

20

24

16 24

13 22

16

8

13

15

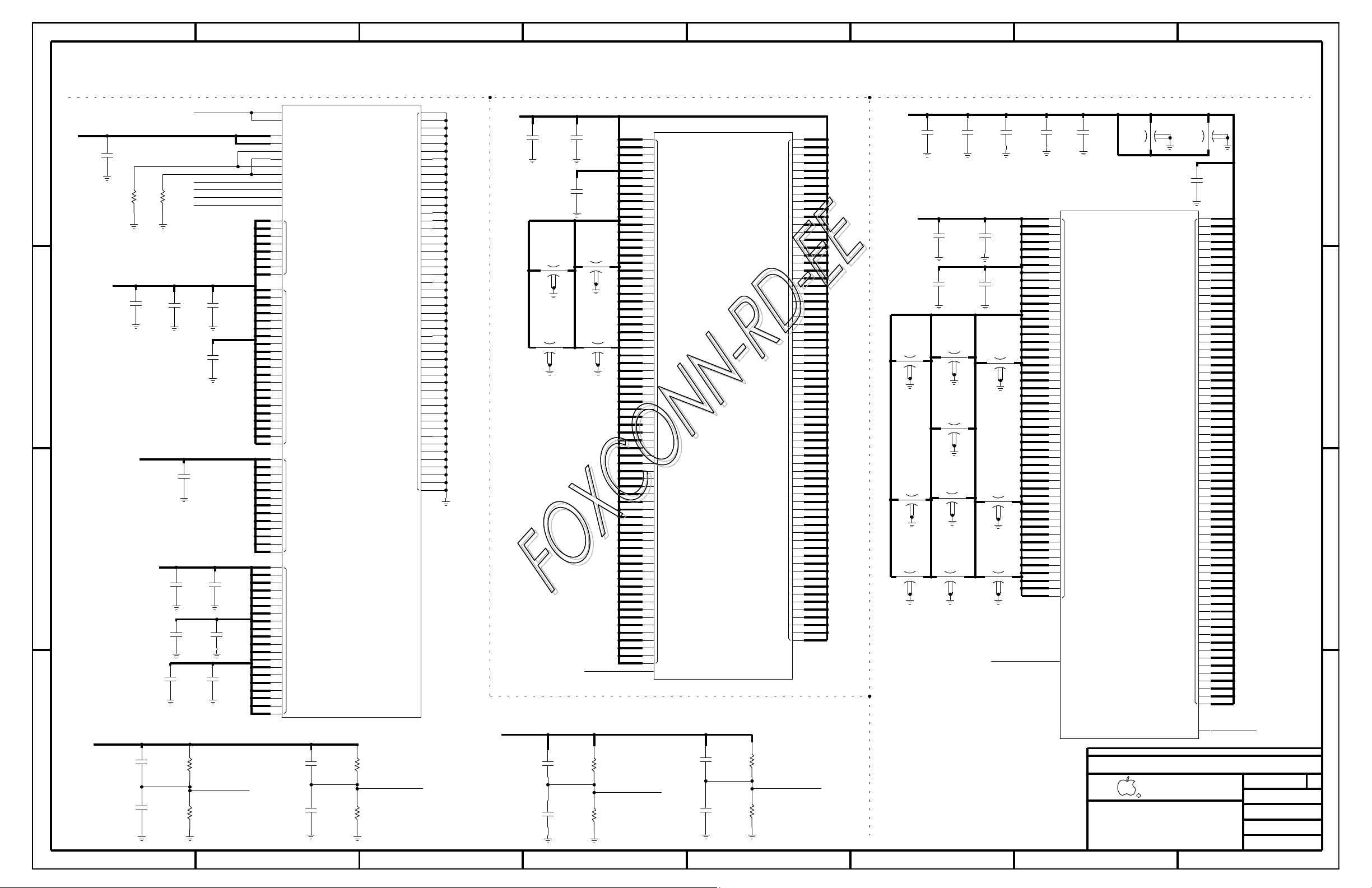

DDR1_VREF_CA

DDR0_VREF_CA

DDR1_RREF_DQ

VSS

DDR0_CKEIN

DDR0_VDD_CKE

DDR1_RREF_CA

DDR0_RREF_CA

DDR0_RREF_DQ

DDR0_VREF_DQ

DDR1_VREF_DQ

VDDCA

VDD2

VDD1

VDDQ

DDR1_VDD_CKE

DDR1_CKEIN

SYM 7 OF 13

VDD_SENSE

VDDVDD

SYM 10 OF 13

VDD_GPUVDD_CPU

VDD_GPU_SENSE

VDD_SENSE_CPU

SYM 13 OF 13

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

8 7 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

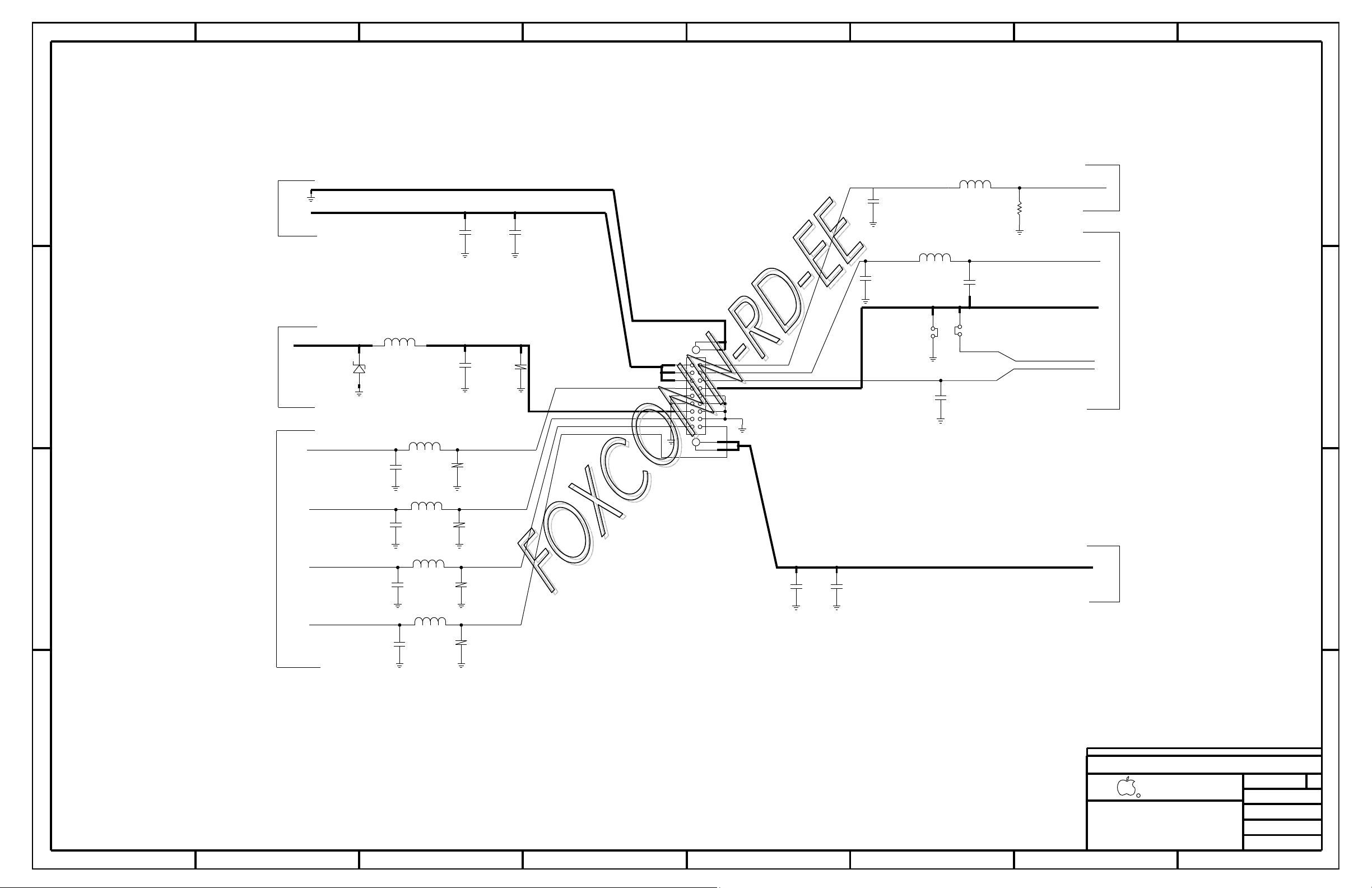

(VDD BALLS = VDD_SOC PWR DOMAIN)

2,500MA FOR VDD_SOC

(THERMAL VIRUS)

(45MA PULLED BY H6)

@125C

@1.0V

SHARED WITH VDDIOD)

(<1MA)

@125C

@1.1V

VDD

@125C

VDDCA, VDD1/2, VDDQ

(CURRENT CONSUMPTION

@1.1V/1.2GHZ

ON 5/6/12, BY MANU G

(<1MA)

7,500MA FOR G3 GPU

10,800MA FOR CPU0+1

VDD_CPU, VDD_GPU

NOTE: CKEIN CONFIRMED 1.8V TOLERANT

(CURRENT CONSUMPTION

SHARED WITH VDDIOD)

(500MA)

(DDR IMPEDANCE CONTROL)

H6P: GND, VDDCA, VDD1/2, VDD, VDD_CPU, VDD_GPU

10K

MF

1/32W

1%

01005

ROOM=H6P

1%

1/32W

10K

ROOM=H6P

MF

01005

ROOM=H6P

10K

01005

1%

MF

1/32W

10K

ROOM=H6P

MF

1%

01005

1/32W

ROOM=H6P

MF

1/32W

01005

4.7K

1%

4.7K

ROOM=H6P

MF

1/32W

1%

01005

ROOM=H6P

01005

4.7K

1%

1/32W

MF

ROOM=H6P

01005

4.7K

1%

1/32W

MF

4V

ROOM=H6P

20%

X7S

0204

0.47UF

4V

ROOM=H6P

20%

X5R-CERM

0610

4.3UF

4V

ROOM=H6P

0204

X7S

20%

0.47UF

4V

X6S

1UF

ROOM=H6P

0204

20%

6.3V

0.01UF

ROOM=H6P

X5R

10%

01005

6.3V

01005

ROOM=H6P

10%

0.01UF

X5R

6.3V

01005

X5R

ROOM=H6P

0.01UF

10%

6.3V

ROOM=H6P

X5R

01005

0.01UF

10%

6.3V

ROOM=H6P

10%

01005

X5R

0.01UF

6.3V

01005

ROOM=H6P

10%

X5R

0.01UF

6.3V

ROOM=H6P

X5R

10%

0.01UF

01005

6.3V

ROOM=H6P

10%

0.01UF

01005

X5R

OMIT_TABLE

1/32W

ROOM=H6P

01005

MF

243

1%

OMIT_TABLE

1/32W

1%

MF

ROOM=H6P

243

01005

6.3V

ROOM=H6P

20%

CERM

0402

0.47UF

4V

20%

CERM

ROOM=H6P

0402

1UF

6.3V

0.47UF

0402

CERM

20%

ROOM=H6P

6.3V

0.47UF

ROOM=H6P

CERM

0402

20%

6.3V

0.47UF

ROOM=H6P

CERM

0402

20%

6.3V

CERM

0402

20%

0.47UF

ROOM=H6P

1UF

4V

CERM

20%

0402

ROOM=H6P

4V

ROOM=H6P

CERM

20%

0402

1UF

6.3V

ROOM=H6P

20%

0.47UF

CERM

0402

6.3V

0402

CERM

20%

0.47UF

ROOM=H6P

4V

CERM

20%

ROOM=H6P

0402

1UF

4V

0402

CERM

20%

1UF

ROOM=H6P

20%

0.47UF

6.3V

ROOM=H6P

CERM

0402

6.3V

20%

0402

CERM

0.47UF

ROOM=H6P

4V

1UF

CERM

20%

0402

ROOM=H6P

4V

X5R-CERM

ROOM=H6P

4.3UF

0610

20%

4V

0610

X5R-CERM

ROOM=H6P

4.3UF

20%

4V

ROOM=H6P

0610

X5R-CERM

20%

4.3UF4.3UF

4V

X5R-CERM

0610

20%

ROOM=H6P

4V

ROOM=H6P

CERM

0402

1UF

20%

4V

20%

4.3UF

X5R-CERM

ROOM=H6P

0610

4V

20%

0.47UF

X7S

0204

ROOM=H6P

4V

20%

X5R-CERM

0610

ROOM=H6P

4.3UF

4V

ROOM=H6P

0204

20%

X6S

1UF

4V

20%

ROOM=H6P

0204

1UF

X6S

ROOM=H6P

4V

20%

0204

1UF

X6S

4V

1UF

20%

ROOM=H6P

0204

X6S

0204

4V

X6S

ROOM=H6P

20%

1UF

OMIT_TABLE

SC58960X01-A030

FCMSP

H6PPOP-1GB-DDR

OMIT_TABLE

FCMSP

SC58960X01-A030

H6PPOP-1GB-DDR

H6PPOP-1GB-DDR

SC58960X01-A030

FCMSP

OMIT_TABLE

16V

15PF

NP0-C0G-CERM

01005

5%

20%

10UF

CERM-X5R

6.3V

ROOM=H6P

0402-2

20%

0402-2

ROOM=H6P

6.3V

CERM-X5R

10UF

ROOM=H6P

6.3V

CERM-X5R

10UF

20%

0402-2

01005

ROOM=H6P

20%

0.1UF

X5R-CERM

6.3V

01005

20%

0.1UF

X5R-CERM

6.3V

ROOM=H6P

4V

X5R-CERM

4.3UF

0610

ROOM=H6P

20%

4.3UF

0610

20%

X5R-CERM

ROOM=H6P

4V4V

ROOM=H6P

20%

X5R-CERM

4.3UF

0610

H6P VDDCA,VDD1/2,VDD,VDD_CPU,VDD_GPU

SYNC_DATE=N/A

SYNC_MASTER=N/A

45_DDR0_ZQ

PP1V2_SDRAM

PP1V0_SOC

45_DDR1_ZQ

45_DDR1_VREF_DQ

45_DDR0_VREF_DQ

45_DDR0_VREF_CA

45_DDR1_VREF_CA

PP1V1_GPU

PP1V2_SDRAM

45_DDR1_VREF_CA

45_DDR0_VREF_CA

RESET_1V8_L

45_DDR0_VREF_DQ

45_DDR1_VREF_DQ

45_BUCK2_FB

45_BUCK0_FB

45_BUCK1_FB

PP1V2

PP1V2

PP1V2_SDRAM

PP1V8_SDRAM

PP1V1_CPU

C160

1

2

C133

1

2

C68

1

2

R28

1

2

R27

1

2

R29

1

2

R30

1

2

R31

1

2

R32

1

2

R33

1

2

R34

1

2

C59

1

2

C57

1

2

C60

1

2

C43

1

2

C106

1

2

C108

1

2

C111

1

2

C113

1

2

C114

1

2

C117

1

2

C118

1

2

C120

1

2

R72

1

2

R73

1

2

C112

123

4

C158

1

2

3

4

C161

1

2

3

4

C121

123

4

C124

123

4

C97

123

4

C87

123

4

C83

123

4

C122

123

4

C100

123

4

C89

123

4

C72

123

4

C166

123

4

C174

123

4

C169

123

4

C177

1

2

C141

1

2

C152

1

2

C107

1

2

C282

123

4

C302

1

2

C48

1

2

C285

1

2

C40

1

2

C173

1

2

C153

1

2

C53

1

2

C49

1

2

U1

AP22

AU15

F11

AP23

AU17

D14

U32

AC33

T4

U31

Y33

U4

AE34

AK1

AU12

AU19

AV22

B3

B14

D25

E2

J34

P34

U1

V33

AC2

AD33

AG33

AJ2

AU10

AU14

AU20

AU22

AV17

C4

C8

C14

C20

D24

G2

J33

L3

P33

U2

U33

Y34

AB34

AF34

AV12

AV15

AV19

AV21

R34

W34

A6

A8

A10

A12

A15

A17

A19

AC1

AE1

AH1

AL1

Y1

C21

C25

F1

J1

L1

N1

R1

V1

G30

G31

G33

H1

H2

H3

H4

H5

H25

H27

H29

H32

J2

J3

J4

J5

J6

J8

J10

J12

J14

J16

J18

J20

J22

J24

J26

J28

J30

J31

K1

K2

K3

K4

K5

K7

K9

K11

K13

K15

K17

K19

K21

K23

K25

K27

K29

K31

K34

L2

U1

AA7

AA17

AB30

AB14

AB20

AN13

AD20

AN15

AE21

AF6

AF20

AF30

AN18

AH20

AK6

AK20

AK30

AL23

AN9

H24

H28

J7

J9

J11

H26

J13

J15

J17

J19

J21

J23

J27

J29

K6

K8

J25

K10

K12

K14

K16

K18

K20

K22

K24

K26

K28

L7

AA19

L9

L11

L13

L15

L17

L19

L21

L23

L25

L27

L29

M8

M10

M12

M14

M16

M18

M20

M22

M24

M26

M28

N7

N9

N11

N13

N15

N17

N19

N21

N23

N25

N27

N29

P8

P10

P12

P14

P16

P18

P20

P22

P24

P26

P28

R7

R9

R11

R13

R15

R17

R19

R21

R23

R25

R27

T14

T16

T18

T20

T22

T24

T26

T28

U7

U15

U17

U19

U21

U23

U25

U27

V14

V16

V18

V20

V22

V24

V26

V28

W7

W17

W19

Y16

Y18

Y20

AN11

V31

U1

AA21

AA23

AC23

AC25

AC27

AC29

AD22

AD27

AE29

AF22

AF25

AF27

AA25

AG21

AG23

AG25

AG27

AG29

AH22

AH24

AH26

AH28

AJ21

AA27

AJ23

AJ25

AJ27

AJ29

AK22

AK24

AK26

AK28

AL21

AL27

AA29

W21

W23

W25

W27

W29

Y22

Y24

Y26

Y28

AL29

AB22

AB24

AB26

AB28

AC21

AB10

AB12

AC9

AD10

AD12

AD14

AD16

AD18

AD8

AE11

AE13

AE15

AB16

AE17

AE19

AE7

AE9

AF10

AF12

AF14

AF16

AF18

AF8

AB18

AG11

AG13

AG15

AG17

AG19

AG7

AG9

AH10

AH12

AH14

AC11

AH16

AH18

AH8

AJ11

AJ13

AJ15

AJ17

AJ19

AJ7

AJ9

AC13

AK10

AK12

AK14

AK16

AK18

AK8

AL11

AL13

AL15

AL17

AC15

AL19

AL7

AL9

AM6

AC17

AC19

AC7

AA5

AN30

C5000

1

2

C75

1

2

C80

1

2

C151

1

2

C41

1

2

C142

1

2

051-9478

8.0.0

4 OF 25

4 OF 56

4

12 21 23

12 23

4

4

4

4

12 23

4

12 21 23

4

4

2

13 14 16 19 22 24

4

4

12

12

12

2 4 5

12 23

2 4 5

12 23

4

12 21 23

3

10 12 14 16 17 23 24

12 23

VSS

VSS

SYM 11 OF 13

VSS

VSS

SYM 12 OF 13

VDDIOD_DDR1CA

VDDIOD_DDR0CA

VDDIO18_GRP4

VSS

VDDIO18_GRP2

VDDIO18_GRP1

VDDIOD_DDRDQ

VDDIO18_GRP3

SYM 9 OF 13

SYM 8 OF 13

VDD_ANA_TMPSADC0

VDD_ANA_TMPSADC1

VDD_ANA_TMPSADC2

VDD_ANA_TMPSADC3

VDD_SRAM_SOC

VSS

VDD_SRAM_CPU

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

8 7 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

(I2S,TMR,SIO,GPIO,UART)

(PPN,GPIO,JTAG)

(XTAL I/O)

(SENSOR,SOCHOT,PMU)

VDDIOD, VDDIO18

(GND, VDDIO18, VDDIOD, VDD_SRAM, VDD_SOC)

JUST A FEW GNDS

CAPS FOR VDDIOD ARE SHARED WITH VDDQ

(GPIO,UART,SPI,I2C)

(65MA)

(20MA)

(31MA)

(2MA)

(1000MA)

H6P

(2.5MA)

1,500MA FOR CYCLONE + M$ SRAM

@125C

@1.0V

(1500MA)

(2.5MA)

(2.5MA)

VDD_SRAM, VDD_SOC

(2.5MA)

CAPS FOR VDDIO18_X ARE SHARED WITH VDDIODX

4V

0204

X7S

20%

0.47UF

ROOM=H6P

4V

0204

20%

0.47UF

X7S

ROOM=H6P

4V

ROOM=H6P

0204

20%

X7S

0.47UF

4V

ROOM=H6P

4.3UF

X5R-CERM

0610

20%

ROOM=H6P

0201

1KOHM-25%-0.2A

10V

ROOM=H6P

0201-1

1.0UF

20%

X5R-CERM

1UF

X6S

0204

4V

20%

ROOM=H6P

4V

1UF

ROOM=H6P

X6S

0204

20%

4V

ROOM=H6P

X6S

20%

1UF

0204

4V

ROOM=H6P

X6S

20%

1UF

0204

OMIT_TABLE

SC58960X01-A030

H6PPOP-1GB-DDR

FCMSP

H6PPOP-1GB-DDR

SC58960X01-A030

OMIT_TABLE

FCMSP

OMIT_TABLE

SC58960X01-A030

FCMSP

H6PPOP-1GB-DDR

H6PPOP-1GB-DDR

SC58960X01-A030

FCMSP

OMIT_TABLE

402

ROOM=H6P

6.3V

X5R

4.7UF

20%

01005

ROOM=H6P

6.3V

X5R-CERM

0.1UF

20%

H6P GND,VDDIO18,VDDIOD,VDD_SRAM,VDD_SOC

SYNC_MASTER=N/A

SYNC_DATE=N/A

PP1V2

PP1V0_SRAM

PP1V8

PP1V8

PP1V8_XTAL

C134

1

2

C91

1

2

C95

1

2

C305

1

2

FL67

1 2

C379

1

2

C86

1

2

C78

1

2

C81

1

2

C115

1

2

U1

A1

A2

A16

AG14

AG16

AG18

AG20

AG22

AG24

AG26

AG28

AG30

AH5

A18

AH7

AH9

AH11

AH13

AH15

AH17

AH19

AH21

AH23

AH25

A25

AH27

AH29

AH32

AJ1

AJ3

AJ8

AJ10

AJ12

AJ14

AJ16

A28

AJ18

AJ22

AJ24

AJ26

AJ28

AJ30

AK5

AK7

AK9

AK11

A30

AK13

AK15

AK17

AK19

AK21

AK23

AK27

AK29

AK32

AL3

A33

AL6

AL8

AL10

AL12

AL14

AL16

AL18

AL20

AL22

AL24

A34

AL26

AL28

AL30

AM4

AM7

AM18

AM30

AN2

AN5

AN7

AA1

AB6

AM9

AM11

AM13

AN16

AM15

AN19

AN20

AN21

AN22

AA2

AN23

AN24

AN31

AA3

A3

AA4

AA8

AA10

AA12

AA14

AA16

AA18

AA22

AA24

AA26

A4

AA28

AA30

AB5

AB7

AB9

AB11

AB13

AB15

AB17

AB19

A5

AB21

AB23

AB25

AB27

AB29

AB32

AC4

AC8

AC10

AC12

A7

AC14

AC16

AC18

AC20

AC22

AC24

AC26

AC28

AC30

AC34

A9

AD2

AD7

AD9

AD11

AD13

AD15

AD17

AD19

AD21

AD23

A11

AD25

AD29

AD32

AE3

AE8

AE10

AE12

AE14

AE16

AE18

A13

AE22

AE24

AE26

AE28

AF5

AF7

AF9

AF11

AF13

AF15

A14

AF17

AF19

AF21

AF23

AF29

AF32

AG2

AG8

AG10

AG12

U1

AN32

AN33

AN34

AP6

AP20

AP21

AP24

AP25

AP26

AP27

AP28

AP29

AP30

AP31

AP32

AR3

AR8

AR12

AR15

AR17

AR20

AR21

AR22

AR23

AR24

AR25

AR28

AR29

AR32

AT1

AT4

AT6

AT20

AT21

AT22

AT23

AT24

AT25

AT26

AT27

AT28

AT29

AT30

AT31

AT32

AU1

AU2

AU11

AU16

AU18

AU21

AU33

AU34

AV1

AV2

AV9

AV11

AV14

AV16

AV18

AV20

AV33

AV34

B1

B2

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B15

B16

B17

B18

B19

B25

B28

B30

B33

B34

C1

C2

C3

C5

C6

C7

C9

C10

C11

C12

C13

C15

C16

C17

C18

C19

C22

C23

C24

C26

C27

C29

C31

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D15

D16

D17

D18

D19

D20

D21

D22

D32

E1

E3

E4

E5

E6

E7

E8

E9

E10

E11

E12

E13

E14

E15

E18

E19

E20

E21

E22

E31

E32

E34

F2

F3

F4

F5

F6

F7

F8

F9

F10

F12

F13

F14

F15

F26

F30

F31

G1

G3

G4

G5

G6

G7

G8

G9

G10

G11

G12

G13

G14

G15

G26

G28

U1

AD6

AH6

AM8

AM10

AM12

AM14

AM16

AM19

AD30

AH30

G25

G27

H30

K30

M30

P30

G29

G24

AM20

AM21

AM22

AM23

AM24

R29

T29

U29

V29

AA6

H6

H15

M6

N6

P6

R6

T6

U6

V6

W6

Y6

H7

H8

H9

H10

H11

H12

H13

H14

R33

T1

T2

T3

T5

T7

T9

T11

T13

T15

T17

T19

T21

T23

T25

T27

T30

T31

T32

T33

T34

U3

U5

U8

U10

U12

U14

U18

U20

U22

U24

U26

U28

U30

U34

V2

V3

V4

V5

V7

V9

V11

V13

V15

V17

V19

V21

V23

V25

V27

V30

V32

V34

W1

W2

W3

W4

W5

W8

W10

W12

W14

W16

W18

W20

W22

W24

W26

W28

W33

Y2

Y3

Y4

Y5

Y7

Y9

Y11

Y13

Y15

Y17

Y19

Y21

Y23

Y27

Y29

Y32

AM17

Y30

AC6

AE6

AG6

AJ6

AE30

U1

AJ20

AA20

AB4

H22

AD24

AD26

Y25

AD28

AE23

AE25

AE27

AF24

AF26

AF28

AK25

AA9

AA11

U13

V8

V10

V12

W9

W11

W13

W15

Y8

Y10

AA13

Y12

Y14

AA15

AB8

T8

T10

T12

U9

U11

L4

L5

L6

L8

L10

L12

L14

L16

L18

L20

L22

L24

L26

L28

L30

L33

M1

M2

M3

M4

M5

M7

M9

M11

M13

M15

M17

M19

M21

M23

M25

M27

M29

M31

N2

N3

N4

N5

N8

N10

N12

N14

N16

N18

N20

N22

N24

N26

N28

N30

N33

P1

P2

P3

P4

P5

P7

P9

P11

P13

P15

P17

P19

P21

P23

P25

P27

P29

R2

R3

R4

R5

R8

R10

R12

R14

R16

R18

R20

R22

R24

R26

R28

R30

R31

C30

1

2

C85

1

2

051-9478

8.0.0

5 OF 25

5 OF 56

2 4

12 23

12 23

2 3 5 6 7

10 11 12 14 16

18 19 21 23

2 3 5 6 7

10 11 12 14

16 18 19 21 23

23

IO0-1

IO7-1

IO6-1

IO3-1

IO4-1

IO5-1

IO1-1

IO2-1

IO7-0

IO5-0

IO6-0

IO4-0

IO2-0

IO3-0

IO1-0

IO0-0

VCC

CLE1

CE1*

CLE0

CE0*

WE0*

ALE0

RE0

RE0*

DQS0*

R/B0*

DQS0

ALE1

WE1*

RE1

RE1*

DQS1

DQS1*

R/B1*

ZQ

VREF

VSSQ

VSS

VCCQ

VDDI

TMSC

TCKC

PPN0_ALE

PPN0_CEN0

PPN0_CEN1

PPN0_CLE

PPN0_DQS

PPN0_IO0

PPN0_IO1

PPN0_IO2

PPN0_IO3

PPN0_IO4

PPN0_IO5

PPN0_IO6

PPN0_IO7

PPN0_REN

PPN0_VREF

PPN0_WEN

PPN0_ZQ

PPN1_ALE

PPN1_CEN0

PPN1_CEN1

PPN1_CLE

PPN1_IO0

PPN1_IO1

PPN1_IO2

PPN1_IO3

PPN1_IO4

PPN1_IO5

PPN1_IO6

PPN1_REN

PPN1_VREF

PPN1_WEN

PPN1_ZQ

PPN1_DQS

PPN1_IO7

SYM 4 OF 13

PP

PP

PP

PP

PP

NC

NC

NC

NC

NC

NC

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

8 7 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

SUPPORT FOR PPN1.5 (1.8V IO) ONLY

NOTE: NAND PADS SHOULD BE SHIELDED FROM TRACES WITH A GROUND PLANE

NOTE: IO<6> PREFERRED BY MATT BYOM

VDDIO18_GRP3

1000MA

500MA

(IS A STATUS READY BIT)

H6P NAND + 12X17 NAND PKG

0.47UF

4V

ROOM=NAND

0204

20%

X7S

243

ROOM=NAND

MF

1/32W

01005

ROOM=NAND

OMIT_TABLE

LGA-12X17

XXNM-XGBX8-MLC-PPN1.5-ODP

100K

1/32W

ROOM=H6P

5%

01005

MF

ROOM=H6P

100K

1/32W

5%

MF

01005

6.3V

0.01UF

10%

01005

ROOM=H6P

X5R

6.3V

ROOM=H6P

X5R

0.01UF

10%

01005

4V

ROOM=NAND

2.2UF

0201

20%

X5R-CERM

4V

2.2UF

20%

0201

ROOM=NAND

X5R-CERM

4V

0402

ROOM=NAND

15UF

20%

X5R

4V

15UF

ROOM=NAND

X5R

20%

0402

4V

X6S

1UF

0204

ROOM=NAND

20%

4V

ROOM=NAND

20%

1UF

0204

X6S

01005

1/32W

ROOM=H6P

1%

MF

240

ROOM=H6P

01005

1%

1/32W

MF

240

ROOM=H6P

01005

50K

1%

1/32W

MF

1/32W

50K

1%

MF

01005

ROOM=H6P

1/32W

ROOM=NAND

NOSTUFF

MF

100K

01005

5%

NOSTUFF

100K

1/32W

5%

ROOM=NAND

MF

01005

OMIT_TABLE

SC58960X01-A030

H6PPOP-1GB-DDR

FCMSP

10V

ROOM=NAND

0402-1

X5R-CERM

10UF

20%

P2MM

ROOM=NAND

SM

SM

ROOM=NAND

P2MM

ROOM=H6P

P2MM

SM

ROOM=H6P

P2MM

SM

ROOM=H6P

P2MM

SM

SYNC_MASTER=N/A

SYNC_DATE=N/A

H6P NAND,NAND 12X17

AP_BI_NAND_ANC0_IO<1>

AP_BI_NAND_ANC0_IO<6>

AP_BI_NAND_ANC1_IO<2>

AP_TO_NAND_ANC_DQVREF

45_AP_BI_NAND_ANC0_DQS

PP1V2_NAND_VDDI

45_AP_BI_NAND_ANC0_DQS

45_AP_TO_NAND_ANC0_RE_L

AP_TO_NAND_ANC0_ALE

AP_BI_NAND_ANC0_IO<3>

AP_BI_NAND_ANC0_IO<7>

AP_TO_NAND_ANC0_CLE

AP_TO_NAND_ANC1_CEN0_L

NAND_RDYBSY1

AP_BI_NAND_ANC0_IO<5>

AP_TO_NAND_ANC1_CLE

45_AP_BI_NAND_ANC1_DQS

45_AP_TO_NAND_ANC1_RE_L

AP_BI_NAND_ANC0_IO<2>

AP_BI_NAND_ANC0_IO<4>

AP_BI_NAND_ANC0_IO<0>

AP_TO_NAND_ANC0_CLE

AP_TO_NAND_ANC0_CEN0_L

AP_TO_NAND_ANC0_WE_L

AP_TO_NAND_ANC1_WE_L

AP_TO_NAND_ANC_DQVREF

45_NAND_PPN_ZQ

AP_TO_NAND_ANC_DQVREF

45_AP_BI_NAND_ANC1_DQS

AP_TO_NAND_ANC1_WE_L

AP_TO_NAND_ANC_DQVREF

45_AP_TO_NAND_ANC1_RE_L

AP_BI_NAND_ANC1_IO<0>

AP_TO_NAND_ANC1_ALE

AP_TO_NAND_ANC0_WE_L

45_AP_TO_NAND_ANC0_RE_L

AP_BI_NAND_ANC0_IO<7>

AP_BI_NAND_ANC0_IO<6>

AP_BI_NAND_ANC0_IO<5>

AP_BI_NAND_ANC0_IO<3>

AP_BI_NAND_ANC0_IO<1>

AP_BI_NAND_ANC0_IO<0>

AP_TO_NAND_ANC0_CEN0_L

AP_TO_NAND_ANC0_ALE

AP_BI_NAND_ANC0_IO<4>

AP_BI_NAND_ANC0_IO<2>

45_AP_PPN0_ZQ 45_AP_PPN1_ZQ

AP_TO_NAND_ANC1_CLE

AP_BI_NAND_ANC1_IO<4>

AP_BI_NAND_ANC1_IO<3>

NAND_TO_PP_TCKC

NAND_TO_PP_TMSC

AP_BI_NAND_ANC0_IO<6>

45_AP_TO_NAND_ANC0_RE_L

45_AP_BI_NAND_ANC0_DQS

AP_BI_NAND_ANC1_IO<7>

AP_BI_NAND_ANC1_IO<6>

AP_BI_NAND_ANC1_IO<5>

AP_BI_NAND_ANC1_IO<1>

PP1V8

PP1V8

PP3V0_NAND

NAND_RDYBSY0

AP_TO_NAND_ANC1_CEN0_L

AP_TO_NAND_ANC1_ALE

1%

ROOM=NAND

0402

10UF

20%

6.3V

CERM

ROOM=NAND

0402

10UF

20%

CERM

6.3V

CERM

6.3V

20%

10UF

0402

ROOM=NAND

ROOM=NAND

0402

10UF

20%

6.3V

CERM

C180

1

2

R8

1 2

U4

C1

D2

A5

C5

A3

C3

H4

F4

M4

K4

G3

G1

H2

J1

J3

L1

K2

N3

L5

N5

K6

L7

J5

J7

H6

G7

E5

E7

B4

C7

D4

D6

OA0

OB0

B6F2M6N1N7

OC8

OD8

OE0

OF8G0OA8

OB8

G5

B2F6L3A7M2

OC0

OD0

OE8

OF0

G8

E3

E1

A1

R82

1

2

R78

1

2

C136

1

2

C144

1

2

C50

1

2

C376

1

2

C377

1

2

C378

1

2

C3

1

2

C185

1

2

R55

1 2

R153

1 2

R137

1

2

R143

1

2

R160

1

2

R161

1

2

U1

A31

G32

H31

B31

D34

B32

C32

C33

C34

F32

F33

F34

G34

D33

D31

A32

E33

N34

R32

P32

P31

L34

M34

M33

L32

M32

K32

J32

H33

H34

L31

N31

N32

K33

C999

1

2

PP17

1

PP19

1

PP2

1

PP3

1

PP10

1

C209

1

2

C307

1

2

C187

1

2

C182

1

2

051-9478

8.0.0

6 OF 25

6 OF 56

6

6

6

6

23

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

2 3 5 6 7

10 11 12 14 16 18

19 21 23

2 3 5 6 7

10 11 12 14 16 18 19

21 23

12 23

MIPI0C_DPDATA0

SENSOR1_RST

SENSOR1_CLK

MIPI1C_DPDATA0

SENSOR0_RST

SENSOR0_ISTRB

SENSOR0_CLK

MIPI1D_VREG_0P4V

MIPI1D_VDD18

MIPI1C_DPDATA1

MIPI1C_DPCLK

MIPI1C_DNDATA1

MIPI1C_DNDATA0

MIPI1C_DNCLK

MIPI0D_VREG_0P4V

MIPI0D_VDD18

MIPI0D_DPCLK

MIPI0D_DNCLK

MIPI0C_DPDATA2

MIPI0C_DPDATA1

MIPI0C_DNDATA2

MIPI0C_DNDATA1

MIPI_VSS

ISP0_SDA

ISP0_SCL

ISP1_SCL

MIPI0C_DPDATA3

MIPI0C_DNDATA3

MIPI0C_DPCLK

MIPI0D_DNDATA3

MIPI0D_DPDATA3

MIPI0D_DNDATA2

MIPI0D_DPDATA2

MIPI0D_DNDATA1

MIPI0D_DPDATA1

MIPI0C_DNCLK

MIPI0D_DPDATA0

MIPI0D_DNDATA0

MIPI_VDD10

SENSOR1_ISTRB

MIPI0C_DNDATA0

ISP1_SDA

SENSOR0_XSHUTDOWN

SENSOR1_XSHUTDOWN

SYM 5 OF 13

DP_PAD_AUXN

DP_PAD_AUXP

DP_PAD_AVDD_AUX

DP_PAD_AVDD0

DP_PAD_AVDD1

DP_PAD_AVDD2

DP_PAD_AVDD3

DP_PAD_AVDDP0

DP_PAD_AVDDX

DP_PAD_AVSS_AUX

DP_PAD_AVSS0

DP_PAD_AVSS1

DP_PAD_AVSS2

DP_PAD_AVSS3

DP_PAD_AVSSP0

DP_PAD_AVSSX

DP_PAD_DC_TP

DP_PAD_DVDD

DP_PAD_DVSS

DP_PAD_R_BIAS

DP_PAD_TX0N

DP_PAD_TX0P

DP_PAD_TX1N

DP_PAD_TX1P

DP_PAD_TX2N

DP_PAD_TX2P

DP_PAD_TX3N

DP_PAD_TX3P

EDP_HPD

SYM 6 OF 13

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

8 7 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

ENABLE FOR EXTERNAL CAMERA LDO (RDAR://13097085)

REMOVE ALS_TO_AP RDAR://12828034

H6P HIGH SPEED DIG (CAM, LCD, DP)

LPDP NOT USED, NO CAP NEEDED ON THIS PIN

N/C OK PER SEG 5/14/12

FF CAMERA

(1MA)

(50MA)

VDDIO18_GRP3

MIPI_VDD10

(10MA)

(14MA)

(50MA)

(50MA)

(50MA)

(14MA)

SHUTDOWN IS ALSO

(2MA)

(2MA)

VDDIO18_GRP1

RESET FCAM

(55MA)

VDDIO18_GRP1

MAIN CAMERA

N/C OK PER SEG 5/14/12

N/C OK PER SEG 5/14/12

N/C OK PER SEG 5/14/12

BB_TO_AP_IPC_GPIO

PP1V0 PP1V8

AP_TO_RCAM_I2C_SCL

AP_TO_FCAM_I2C_SCL

90_AP_BI_LCM_MIPI_DATA0_N

90_AP_BI_LCM_MIPI_DATA0_P

90_AP_TO_LCM_MIPI_DATA1_P

90_AP_TO_LCM_MIPI_DATA1_N

90_AP_TO_LCM_MIPI_CLK_N

90_AP_TO_LCM_MIPI_CLK_P

45_AP_TO_RCAM_CLK

45_AP_TO_RCAM_CLK_R

AP_TO_RCAM_SHUTDOWN

90_RCAM_TO_AP_MIPI_DATA0_P

90_RCAM_TO_AP_MIPI_DATA0_N

90_RCAM_TO_AP_MIPI_DATA1_N

90_RCAM_TO_AP_MIPI_DATA1_P

90_RCAM_TO_AP_MIPI_DATA2_P

90_RCAM_TO_AP_MIPI_DATA2_N

90_RCAM_TO_AP_MIPI_DATA3_N

90_RCAM_TO_AP_MIPI_DATA3_P

90_RCAM_TO_AP_MIPI_CLK_P

90_RCAM_TO_AP_MIPI_CLK_N

90_FCAM_TO_AP_MIPI_DATA0_P

90_FCAM_TO_AP_MIPI_DATA0_N

90_FCAM_TO_AP_MIPI_CLK_P

90_FCAM_TO_AP_MIPI_CLK_N

45_AP_TO_FCAM_CLK_R

45_AP_TO_FCAM_CLK

AP_TO_FCAM_SHUTDOWN

PP_MIPI1D_VREG

PP1V8

PP_MIPI0D_VREG

AP_BI_RCAM_I2C_SDA

PP1V0

PP1V8

AP_BI_FCAM_I2C_SDA

AP_TO_LEDDRV_EN

CAM_EXT_LDO_EN

SYNC_MASTER=N/A

SYNC_DATE=N/A

H6:HI-SPEED DIG

0.1UF

01005

ROOM=H6P

20%

X5R-CERM

6.3V

SC58960X01-A030

OMIT_TABLE

FCMSP

H6PPOP-1GB-DDR

OMIT_TABLE

FCMSP

H6PPOP-1GB-DDR

SC58960X01-A030

4V

ROOM=H6P

20%

0204

X6S

1UF

6.3V

5%

56PF

01005

NP0-C0G

ROOM=H6P

6.3V

NP0-C0G

ROOM=H6P

01005

5%

56PF

6.3V

ROOM=H6P

5%

01005

56PF

NP0-C0G

6.3V

ROOM=H6P

NP0-C0G

01005

56PF

5%

1/32W

1.00K

5%

01005

MF

1.00K

MF

01005

5%

1/32W

1.00K

MF

5%

1/32W

01005

MF

01005

1/32W

5%

1.00K

01005

33.2

MF

1%

1/32W

ROOM=H6P

MF

01005

33.2

ROOM=H6P

1%

1/32W

6.3V

2200PF

ROOM=H6P

10%

X5R-CERM

01005

6.3V

X5R-CERM

ROOM=H6P

2200PF

10%

01005

C6

1

2

C7

1

2

R38

1 2

R40

1 2

R37

1

2

R39

1

2

R41

1

2

R42

1

2

C259

1

2

C274

1

2

C280

1

2

C284

1

2

C190

1

2

U1

AT7

AV7

AU8

AP9

AV25

AV27

AV26

AV24

AV23

AU25

AU27

AU26

AU24

AU23

AV30

AV32

AV31

AV29

AV28

AU30

AU32

AU31

AU29

AU28

AR26

AR27

AR34

AT34

AP34

AR33

AT33

AP33

AR31

AR30

AN25

AN26

AN27

AN28

AN29AM25

AM26

AM27

AM28

AM29

AL25

AV8

AN10

AT8

AR9

AU9

AR10

AT9

AP10

U1

B20

A20

F19

F20

F21

F22

F18

G18

F17

H19

G19

G20

G21

G17

H18

H17

E16

F16

G16

E17

B21

A21

B22

A22

B23

A23

B24

A24

D30

C191

1

2

051-9478

8.0.0

7 OF 25

7 OF 56

24

23 12

7 2

23 21

19 18 16 14 12 11 10

7 6 5 3 2

21 20 15

11

19

19

19

19

19

19

21

21

21

21

21

21

21

21

21

21

21

21

11

11

11

11

11

11

23

23 21

19 18 16 14 12 11 10

7 6 5 3 2

23

21 20 15

23 12

7 2

23 21

19 18 16 14 12 11 10

7 6 5 3 2

11

15

21

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

8 7 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

(VIBE DRIVER, BUTTONS, ANC REF MIC, STROBE, STROBE_NTC)

NOTE: VIBE RETURN, TO GND HERE

STROBE:

NOTE: PP_VIBE

516S1040 PLUG

RINGER, HOLD,

VOL_UP/DOWN

BUTTONS:

NOTE: MIC_P

MIC2/3 BIAS,

MIC2_P,_N

MIC2 (ANC REF MIC):

STROBE:

LED COOL

STROBE:

LED WARM, RETURN

VIBE DRIVE

STROBE NTC

NOTE: STROBE_NTC

516S1041 RCPT (FLEX)

BUTTON FLEX

ON MLB ---->

NO MORE WIFI PAC

RDAR://13101391

REMOVED FL18, C15 ON PP3V0_SDRAM

NOTE: MIC_N

NO MORE WIFI PAC

REMOVED FL71,FL70,FL72,C382,C384,C383

RDAR://13101391

5%

01005

27PF

ROOM=BUTTON

NP0-C0G

16V

100PF

01005

ROOM=BUTTON

NP0-C0G

5%

16V

ROOM=BUTTON

01005-1

12V-33PF

01005

120-OHM-210MA

ROOM=BUTTON

5%

100PF

01005

ROOM=BUTTON

10V

NP0-C0G

01005

120-OHM-210MA

ROOM=BUTTON

01005

120-OHM-210MA

ROOM=BUTTON

01005

ROOM=BUTTON

120-OHM-210MA

5%

100PF

NP0-C0G

ROOM=BUTTON

01005

10V

5%

100PF

01005

ROOM=BUTTON

NP0-C0G

10V

100PF

01005

NP0-C0G

5%

ROOM=BUTTON

10V

12V-33PF

01005-1

ROOM=BUTTON

ROOM=BUTTON

01005-1

12V-33PF

12V-33PF

01005-1

ROOM=BUTTON

01005

27PF

5%

NP0-C0G

ROOM=BUTTON

16V

NP0-C0G

ROOM=BUTTON

01005

5%

100PF

16V

CKPLUS_WAIVE=GNDTERM2PWR

105847-018

M-ST-SM

ROOM=BUTTON

CKPLUS_WAIVE=GNDTERM2PWR

01005-1

ROOM=BUTTON

12V-33PF

X5R

20%

1.0UF

ROOM=BUTTON

NOSTUFF

0201-1

6.3V

01005

5%

ROOM=BUTTON

NP0-C0G

56PF

6.3V

5%

NP0-C0G

01005

56PF

ROOM=BUTTON

6.3V

01005

ROOM=BUTTON

120-OHM-210MA

120-OHM-210MA

01005

ROOM=BUTTON

56PF

5%

ROOM=BUTTON

01005

NP0-C0G

6.3V

0201-1

6.3V

X5R

ROOM=BUTTON

1.0UF

20%

SIGNAL_MODEL=EMPTY

ROOM=BUTTON

SHORT-10L-0.1MM-SM

SHORT-10L-0.1MM-SM

SIGNAL_MODEL=EMPTY

ROOM=BUTTON

10-OHM-750MA

ROOM=BUTTON

01005-1

DFN1006-2

BAT54LP

ROOM=BUTTON

MF

1/32W

1%

01005

51.1K

SYNC_DATE=N/A

SYNC_MASTER=N/A

BUTTON FLEX B2B

PP_STRB_DRIVER_TO_LED_COOL

BUTTON_TO_AP_VOL_UP_CONN_L

BUTTON_TO_AP_HOLD_KEY_CONN_L

PP_PMU_TO_VIBE_CONN

PGND_MIC2_3_TO_CODEC_RET

RCAM_TO_STROBE_NTC_CONN

MIC2_TO_CODEC_P

PP_STRB_DRIVER_TO_LED_WARM

BUTTON_TO_AP_RINGER_A

BUTTON_TO_AP_HOLD_KEY_L

RCAM_TO_STROBE_NTC

BUTTON_TO_AP_VOL_DOWN_L

BUTTON_TO_AP_VOL_UP_L

BUTTON_TO_AP_RINGER_A_CONN

MIC2_TO_CODEC_N

BUTTON_TO_AP_VOL_DOWN_CONN_L

PP_CODEC_TO_MIC2_3_BIAS

PP_PMU_TO_VIBE

CODEC_TO_MIC2_BIAS_CONN

C409

1

2

C406

1

2

DZ1

1

2

FL3

1 2

C314

1

2

FL7

1 2

FL8

1 2

FL46

1 2

C311

1

2

C197

1

2

C313

1

2

DZ2

1

2

DZ3

1

2

DZ7

1

2

C208

1

2

C241

1

2

J2

19

20

21

22

1

10

11 12

13 14

15 16

17 18

2

3 4

5 6

7 8

9

DZ101

1

2

C289

1

2

C244

1

2

C397

1

2

FL47

1 2

FL21

12

C45

1

2

C216

1

2

XW5

1

2

XW41

1

2

FL74

1 2

D3

A

K

R157

1

2

051-9478

8.0.0

8 OF 25

8 OF 56

15 23

23

10 11

9

22 23

15 23

3

13

3

15

3

13

3

13

9

23

10 11

23

12 23

NC

NC

NC

NC

NC

NC

NC

NC

NC

AIN1-

AIN2+

AIN2-

AIN6+

AIN6-

DMIC2_SCLK

DMIC2_SD

DMIC1_SD

DMIC1_SCLK

AIN8+

AIN7-

AIN7+

AIN5-

AIN4+

AIN1+

LINEOUT_REF

AOUT2-

AOUT2+

AOUT1-

AOUT1+

AIN8-

AIN5+

AIN4-

AIN3-

AIN3+

LINEOUTB

LINEOUTA

HPOUTA

HPOUTB

HS3

HS4

HS3_REF

HS4_REF

HPDETECT

DN

DP

MBUS_REF

SYM 1 OF 3

NC

NC

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

8 7 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

R102/R103 = 20 OHM FOR TRISTAR2

MIKEY TO TRISTAR

(ANALOG MIC IN, DIG MIC IN, HPOUT, LINEOUT, RECEIVER OUT, MIKEYBUS)

50PF LIMIT ON AOUTX PINS

10NF SHUNT CAPS FOR EMC

L67 AUDIO CODEC

RDAR://12867240

HEADPHONE MIC

AUDIO I/O

REF MIC1

ANC

ANC

REF MIC2

ANC

ANALOG

PRIMARY

ANALOG

MIC

MIC IN

(VOICE) MIC

HEADPHONE

HEADPHONES

ANC REF MIC

ANALOG

VOICE MIC

ANC ERROR MIC

LINEIN

LINEIN

ERROR MIC

L67 A1

APN: 338S1201

RDAR://12926833

ROOM=CODEC

01005

MF5%

1/32W

20.0

ROOM=CODEC

01005

MF5%

20.0

CODEC_MBUS_REF

CODEC_TO_HPHONE_HS4_REF

CODEC_TO_HAC_P

MIC1_TO_CODEC_L67_N

EXTMIC_TO_CODEC_L67_N

MIC3_TO_CODEC_L67_P

MIC3_TO_CODEC_L67_N

HPHONE_TO_CODEC_HPHONE_TEST_L67

CODEC_TO_HAC_N

CODEC_TO_RCVR_N

CODEC_TO_RCVR_P

CODEC_TO_HPHONE_L

CODEC_TO_HPHONE_HS3

CODEC_TO_HPHONE_HS4

MIC3_TO_CODEC_P

RCVR_TO_CODEC_RCVR_TEST

90_CODEC_BI_TRISTAR_MIKEYBUS_N

90_CODEC_BI_TRISTAR_MIKEYBUS_P

HAC_TO_CODEC_TEST

MIC3_TO_CODEC_N

MIC2_TO_CODEC_N

MIC1_TO_CODEC_N

EXTMIC_TO_CODEC_P

MIC1_TO_CODEC_P

EXTMIC_TO_CODEC_N

HPHONE_TO_CODEC_HPHONE_TEST

MIC2_TO_CODEC_P

MIC2_TO_CODEC_L67_N

MIC2_TO_CODEC_L67_P

RCVR_TO_CODEC_RCVR_TEST_L67

MIC1_TO_CODEC_L67_P

EXTMIC_TO_CODEC_L67_P

HAC_TO_CODEC_TEST_L67

SYNC_DATE=N/A

SYNC_MASTER=N/A

L67 AUDIO CODEC (1/2)

ROOM=CODEC

WLCSP

CS42L67-CWZR-A1

NOSTUFF

ROOM=CODEC

01005

X5R

6.3V

10%

0.01UF

NOSTUFF

ROOM=CODEC

01005

6.3V

0.01UF

X5R