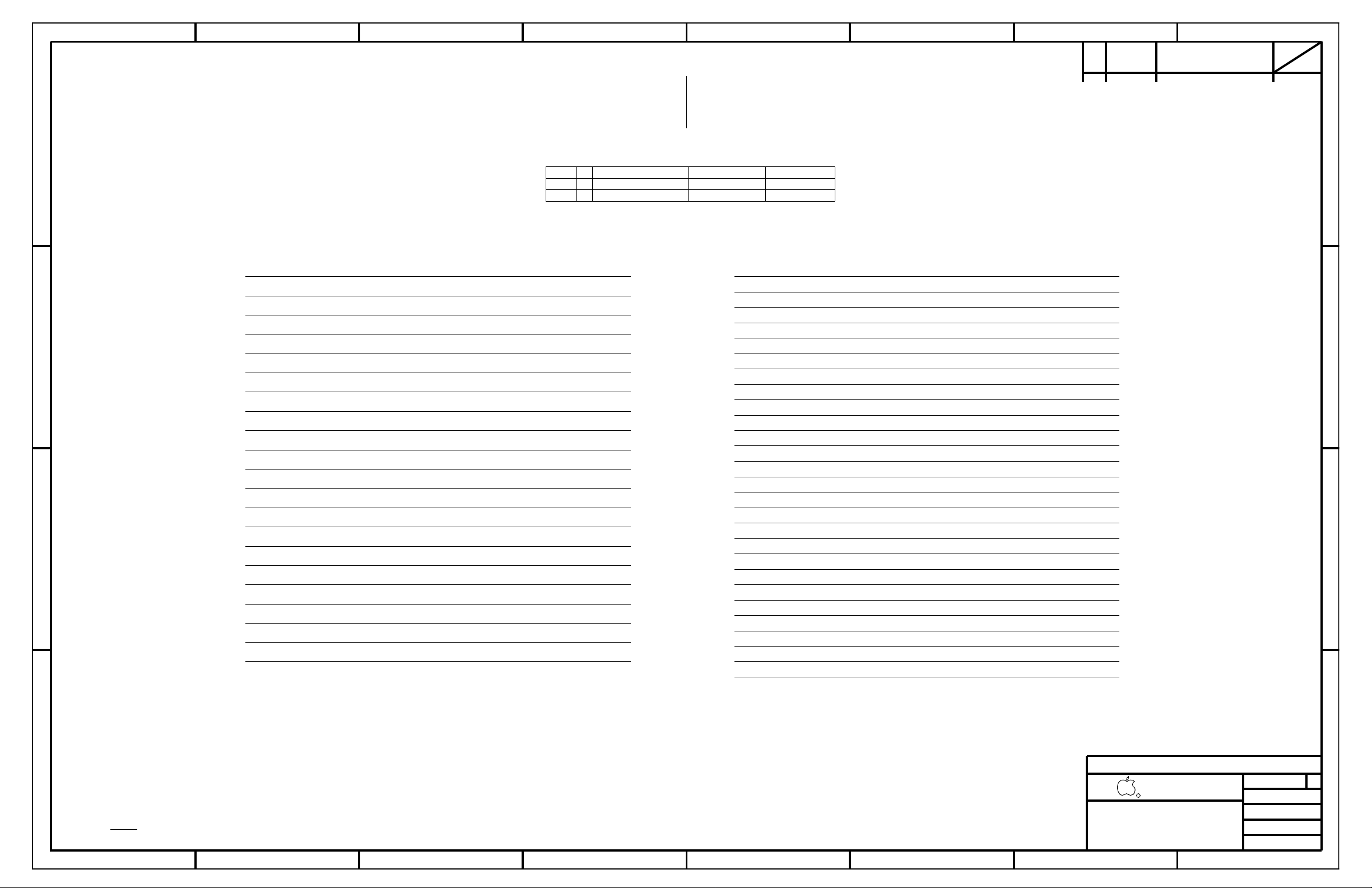

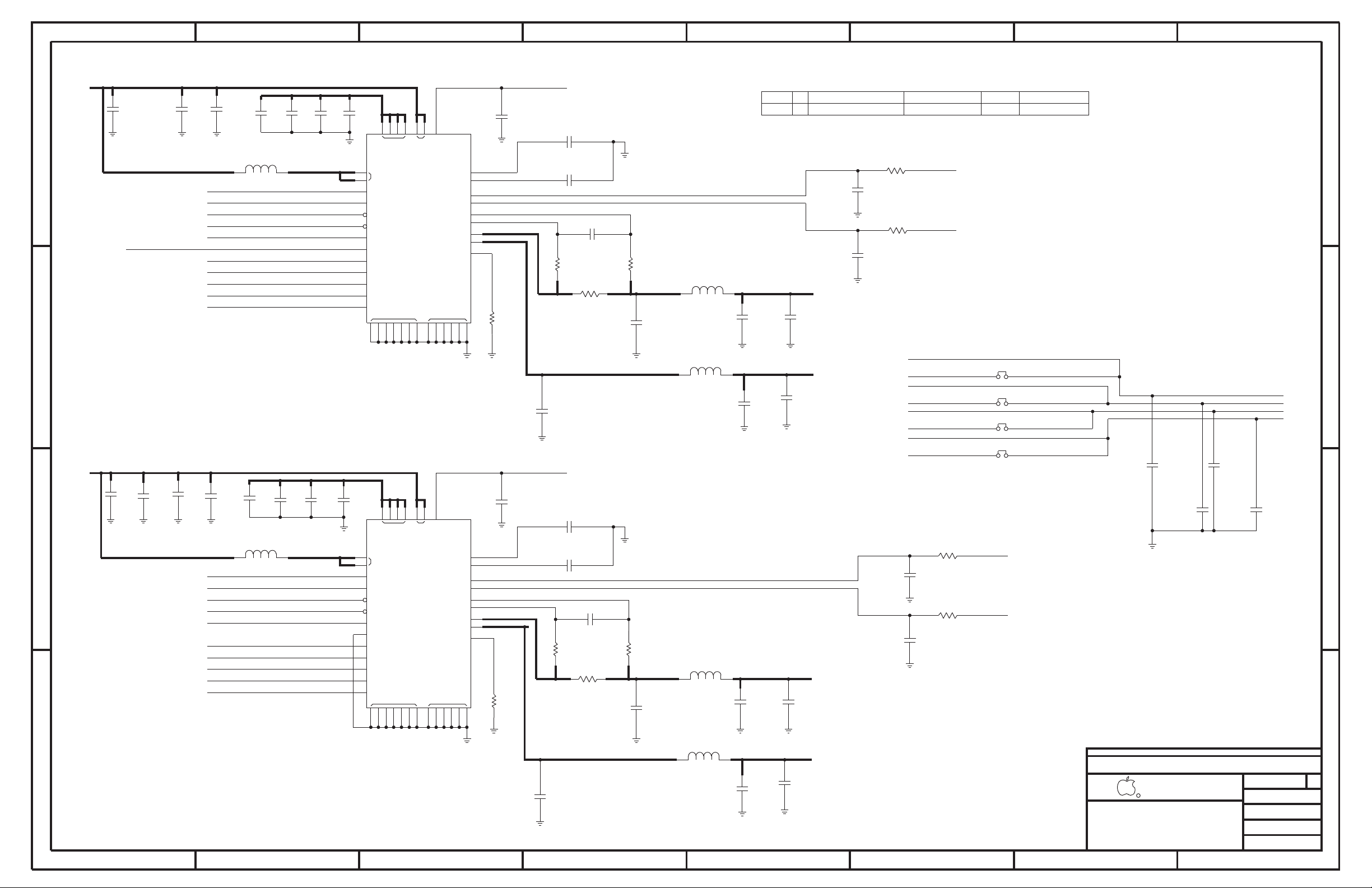

Apple Ipad Mini 4G Schematics

8

1. ALL RESISTANCE VALUES ARE IN OHMS, 0.1 WATT +/- 5%.

2. ALL CAPACITANCE VALUES ARE IN MICROFARADS.

3. ALL CRYSTALS & OSCILLATOR VALUES ARE IN HERTZ.

7

65

43

21

CK

REV ECN

0001520462

13

DESCRIPTION OF REVISION

ENGINEERING RELEASED

APPD

DATE

2012-07-02

MAIN LOGIC BOARD

DVT

X123

LAST_MODIFIED=Wed Jun 27 16:39:53 2012

D

SCH AND BOARD PART NUMBERS

QTY

PART#

CSAPDF

TABLE_TABLEOFCONTENTS_HEAD

1

TABLE_TABLEOFCONTENTS_ITEM

2

TABLE_TABLEOFCONTENTS_ITEM

3

TABLE_TABLEOFCONTENTS_ITEM

C

B

4

TABLE_TABLEOFCONTENTS_ITEM

5

TABLE_TABLEOFCONTENTS_ITEM

6

TABLE_TABLEOFCONTENTS_ITEM

7

TABLE_TABLEOFCONTENTS_ITEM

8

TABLE_TABLEOFCONTENTS_ITEM

9

TABLE_TABLEOFCONTENTS_ITEM

10

TABLE_TABLEOFCONTENTS_ITEM

11

TABLE_TABLEOFCONTENTS_ITEM

12

TABLE_TABLEOFCONTENTS_ITEM

13

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

15

TABLE_TABLEOFCONTENTS_ITEM

16

TABLE_TABLEOFCONTENTS_ITEM

17

TABLE_TABLEOFCONTENTS_ITEM

18

TABLE_TABLEOFCONTENTS_ITEM

19

TABLE_TABLEOFCONTENTS_ITEM

20

TABLE_TABLEOFCONTENTS_ITEM

CONTENTS

TABLE OF CONTENTS

1

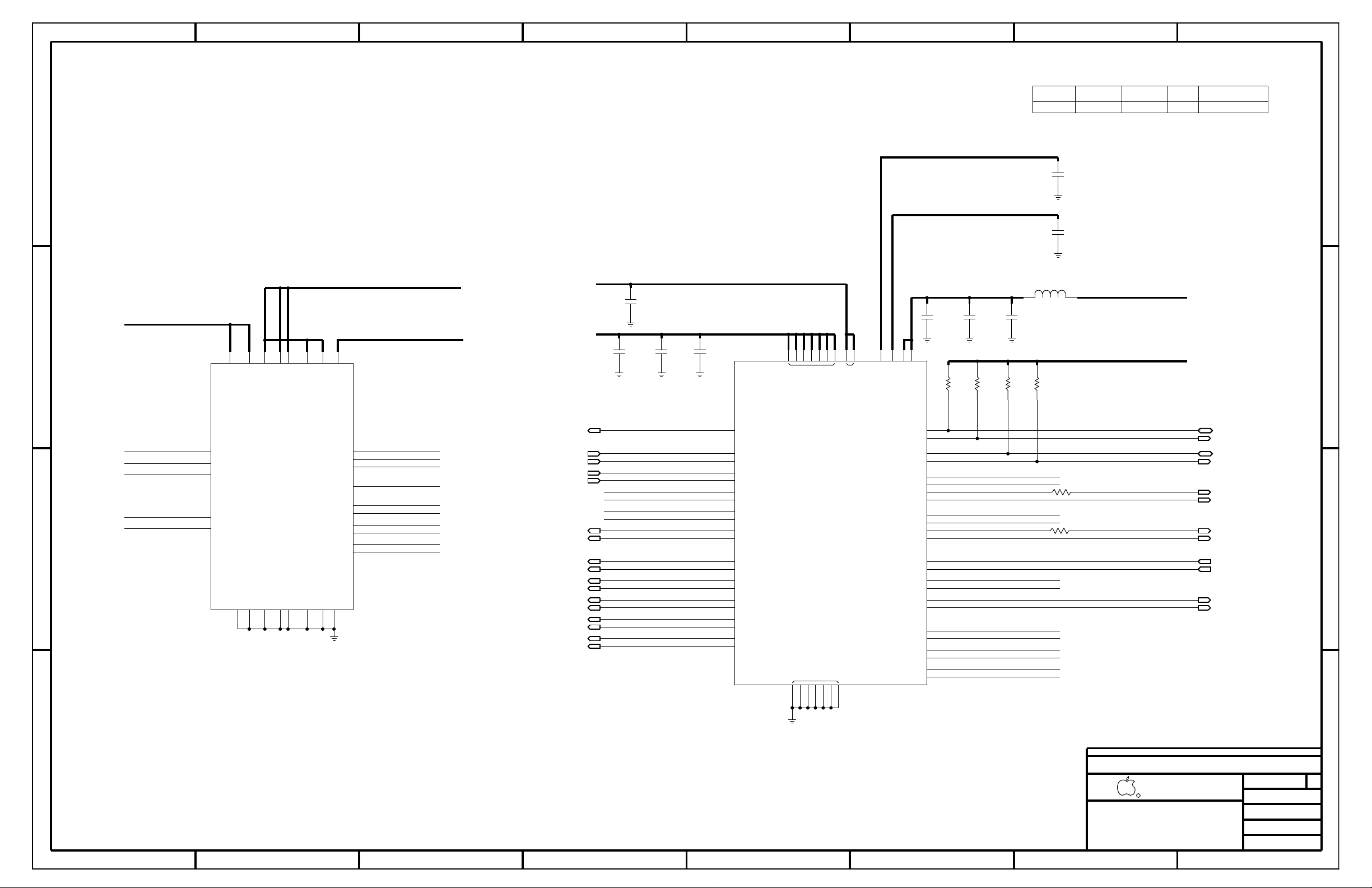

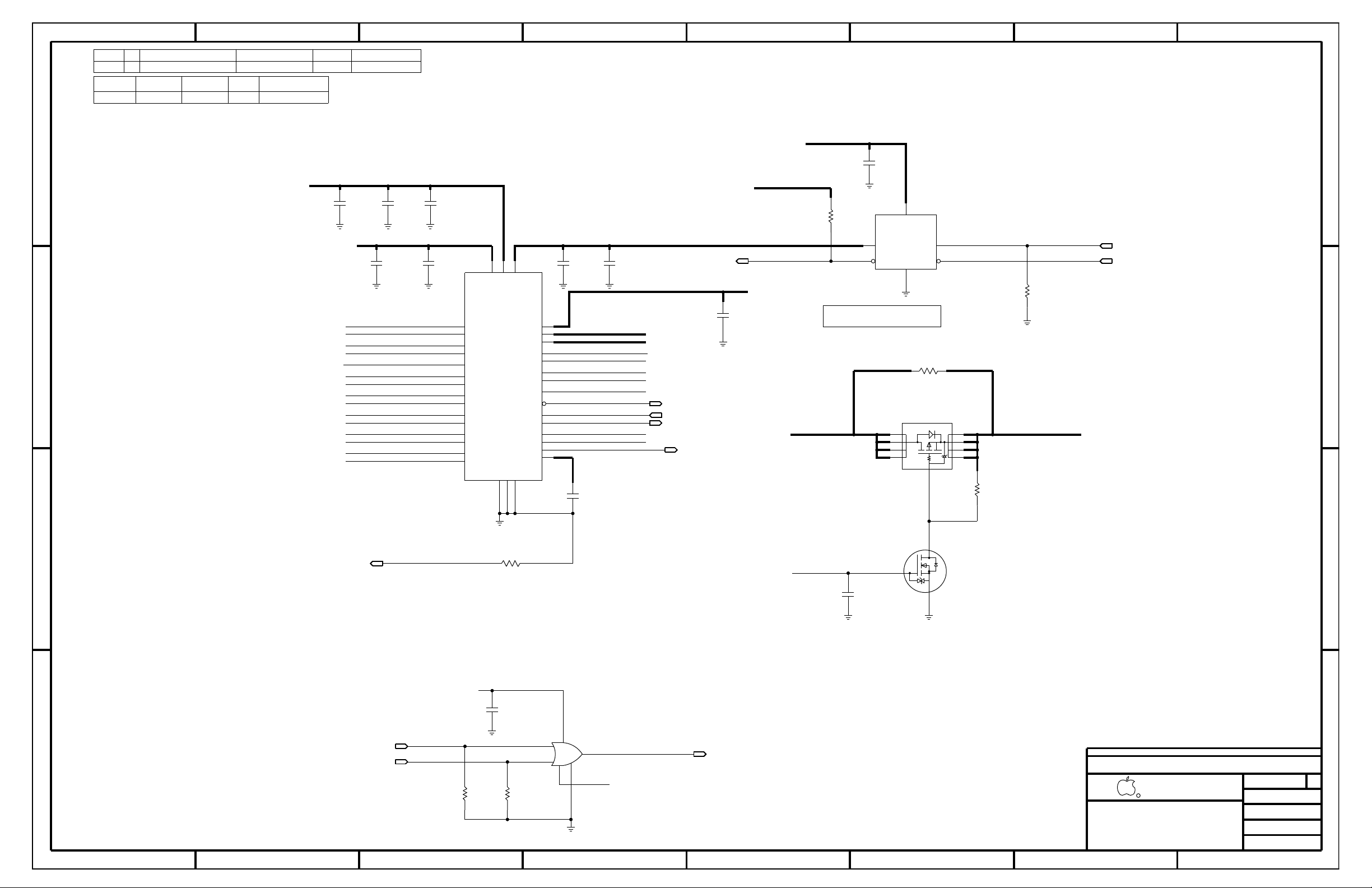

BLOCK DIAGRAM: SYSTEM

2

6

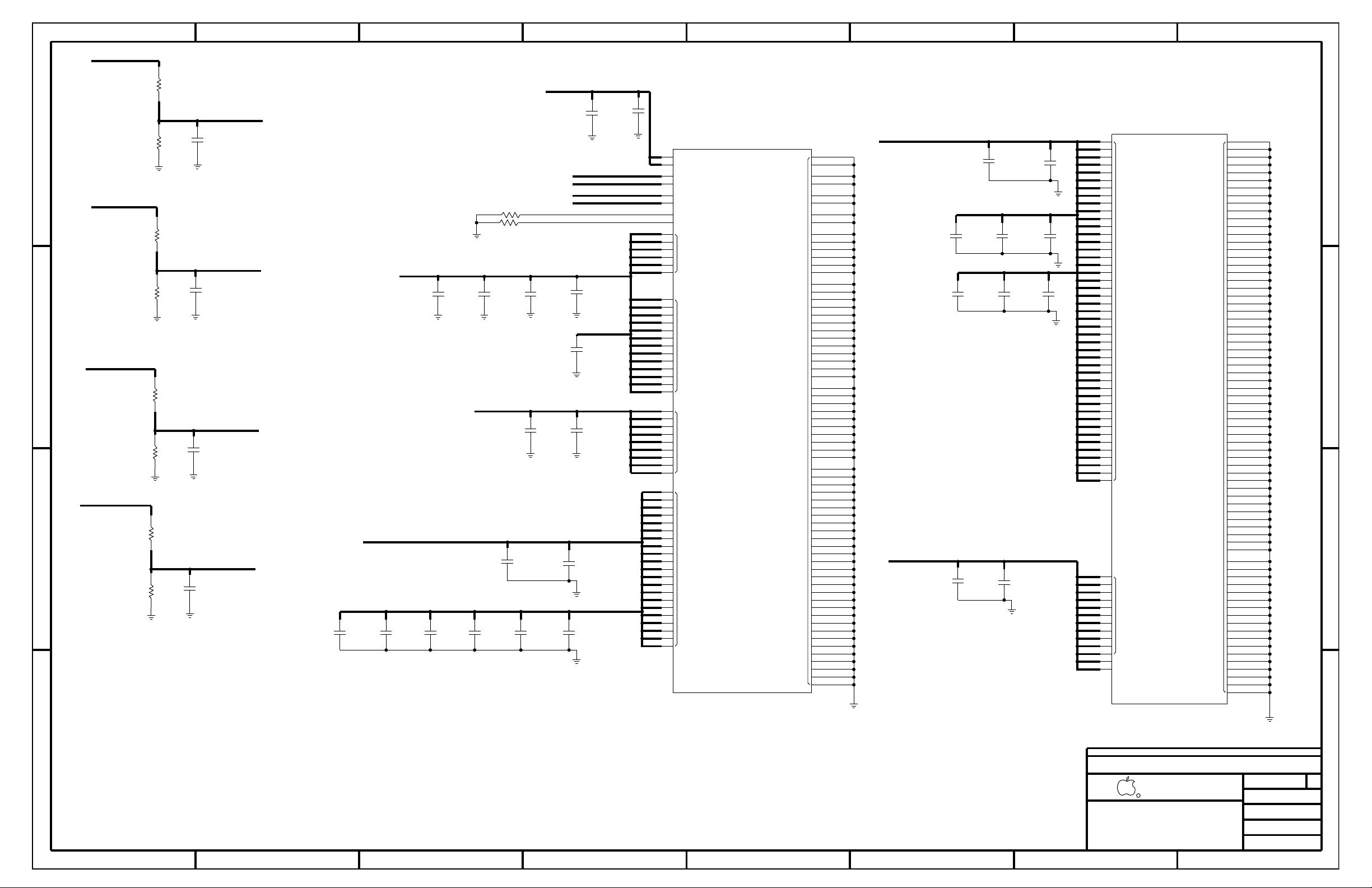

AP: MAIN

7

AP: I/Os

8

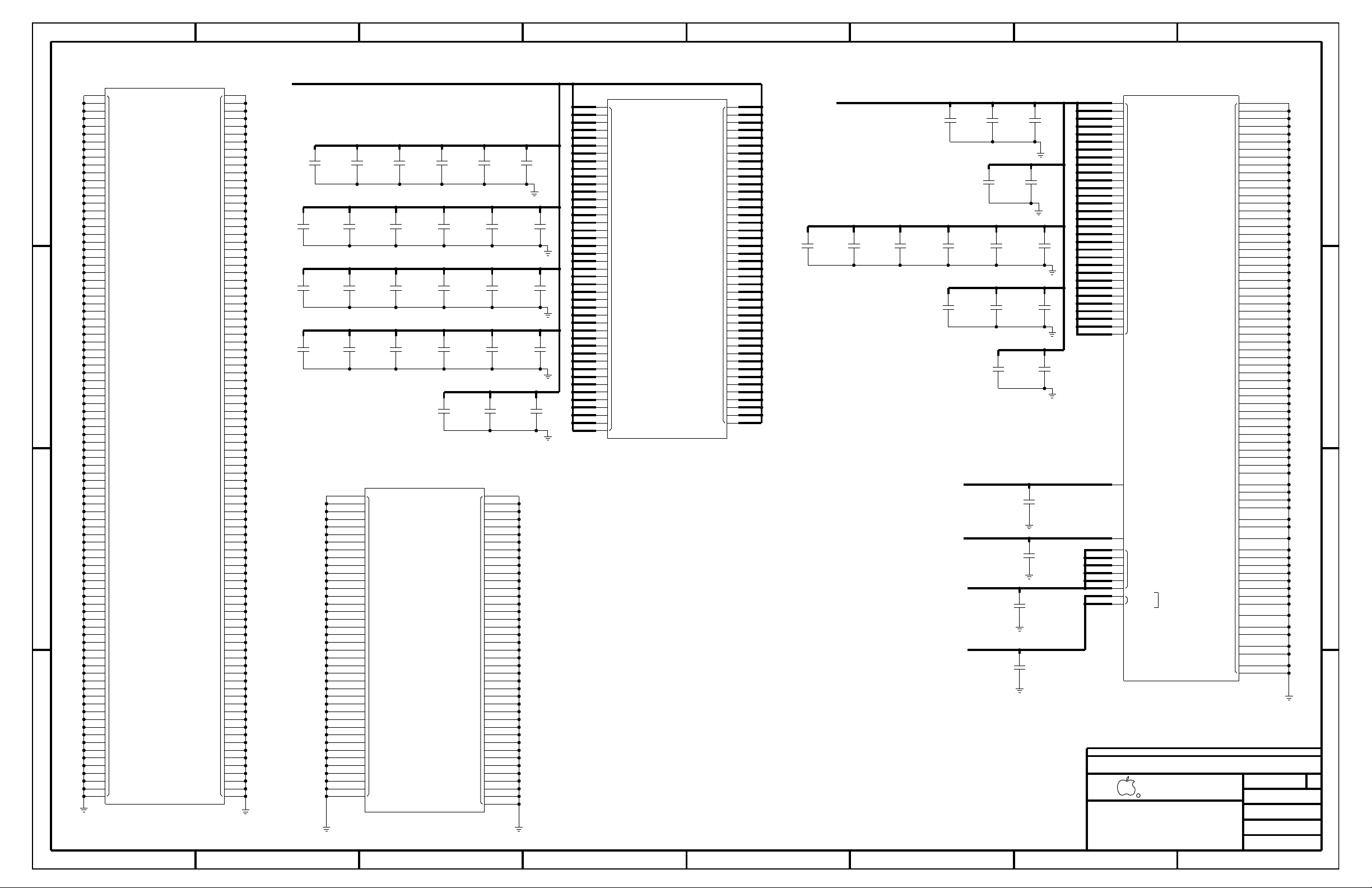

AP: FLASH MEMORY INTERFACE

AP: TV/DP/MIPI/CAMERA

9

10

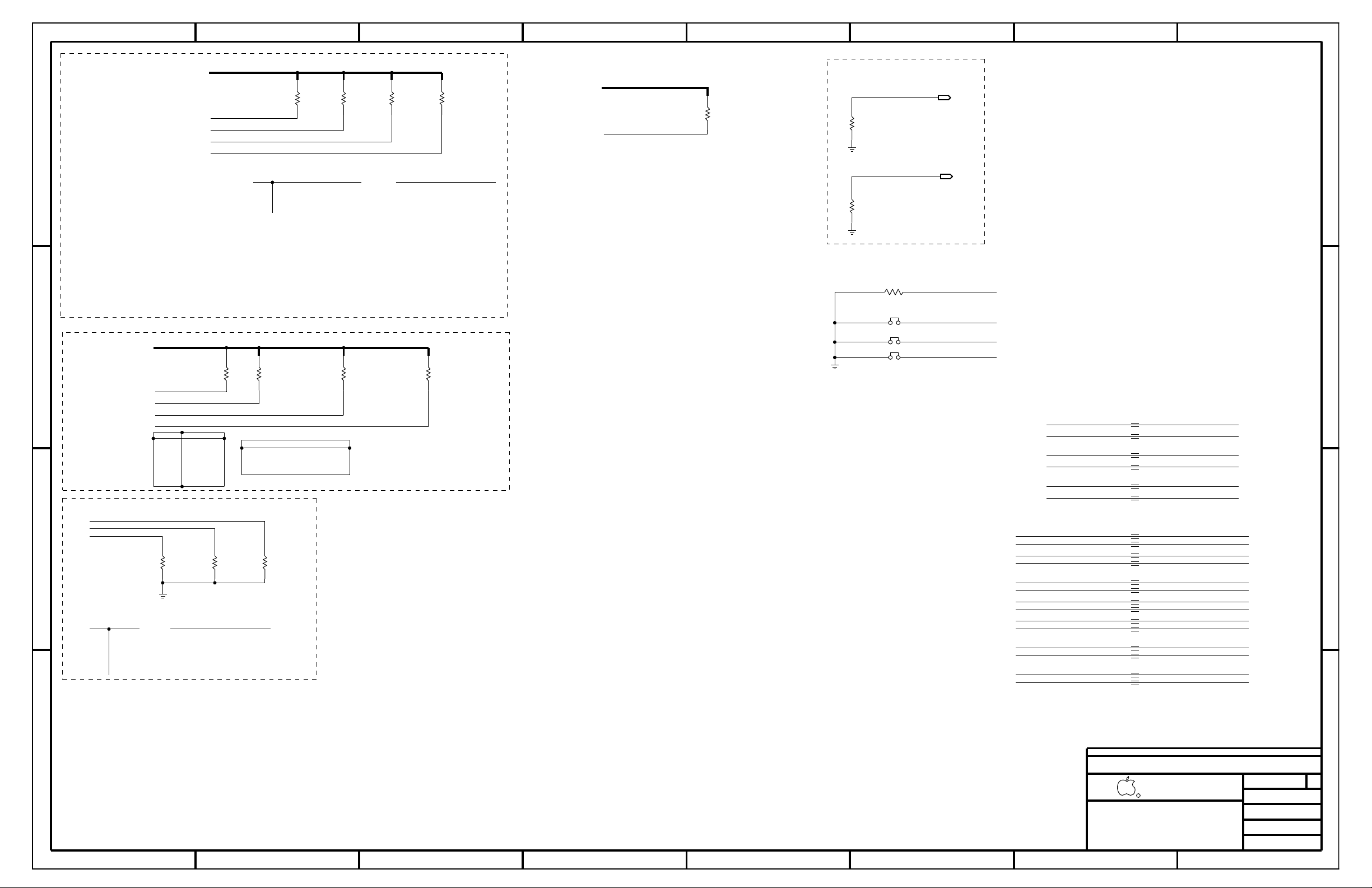

AP: PWR

11

AP: PWR

12

AP: MISC & ALIASES

13

E75 SUPPORT

NAND STORAGE

14

17

TOUCH: FLEX CONNECTOR

18

AUDIO JACK FLEX CONN

19

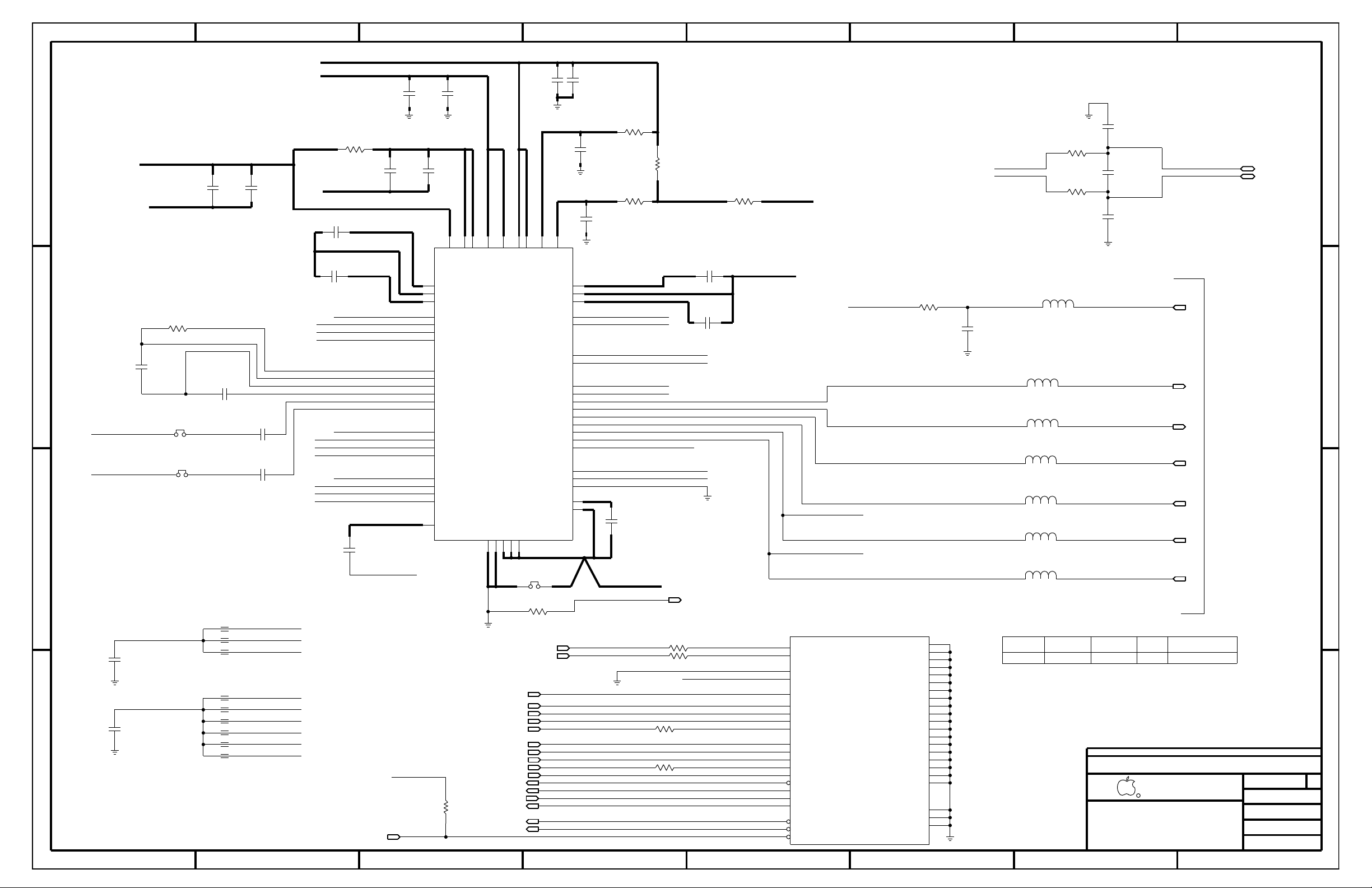

AUDIO: L81 CODEC

AUDIO: CS35L19A AMPS

20

22

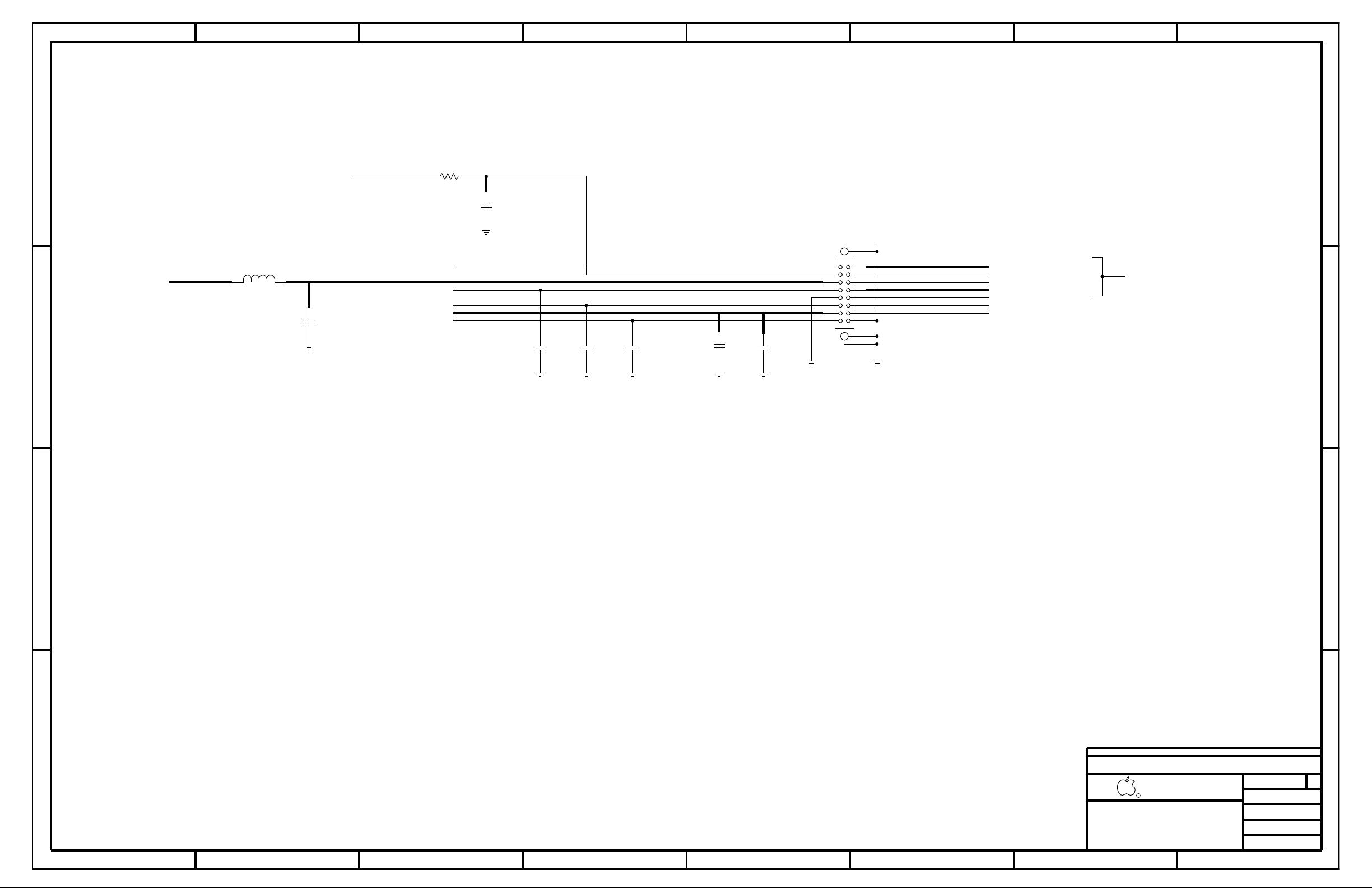

VIDEO: MIPI CONNECTOR

FF CAM & MIC CONNECTORS

26

27

INERTIAL SENSORS

PROX SENSOR

28

29

BUTTON & REAR CAMERA CONN

SYNC MASTER

DESCRIPTION

1

SCH,MLB,X123

1

PCB,MLB,X123

DATE

N/A

N/A

N/A

N/A

N/A

MLB

N/A

N/A

N/A

N/A

MLB

N/A

N/A

KAVITHA1401/18/2012

KAVITHA

N/A

N/A

N/A

N/A

N/A

N/A

N/A

04/18/2011

05/05/2011

04/18/2011

05/04/2012

04/18/2011

04/18/2011

04/11/2011

N/A

05/04/2012

06/21/2010

03/31/2011

01/18/2012

N/A

N/A

N/A

N/A

N/A

REFERENCE DESIGNATOR(S)

SCH1051-9374

PCB1820-3243

BOM OPTION

CSAPDF

TABLE_TABLEOFCONTENTS_HEAD

21

TABLE_TABLEOFCONTENTS_ITEM

22

TABLE_TABLEOFCONTENTS_ITEM

23

TABLE_TABLEOFCONTENTS_ITEM

24

TABLE_TABLEOFCONTENTS_ITEM

25

TABLE_TABLEOFCONTENTS_ITEM

26

TABLE_TABLEOFCONTENTS_ITEM

27

TABLE_TABLEOFCONTENTS_ITEM

28

TABLE_TABLEOFCONTENTS_ITEM

29

TABLE_TABLEOFCONTENTS_ITEM

30

TABLE_TABLEOFCONTENTS_ITEM

31

TABLE_TABLEOFCONTENTS_ITEM

32

TABLE_TABLEOFCONTENTS_ITEM

33

TABLE_TABLEOFCONTENTS_ITEM

34

TABLE_TABLEOFCONTENTS_ITEM

35

TABLE_TABLEOFCONTENTS_ITEM

36 GPS

TABLE_TABLEOFCONTENTS_ITEM

37

TABLE_TABLEOFCONTENTS_ITEM

38

TABLE_TABLEOFCONTENTS_ITEM

39

TABLE_TABLEOFCONTENTS_ITEM

40

TABLE_TABLEOFCONTENTS_ITEM

41

TABLE_TABLEOFCONTENTS_ITEM

42

TABLE_TABLEOFCONTENTS_ITEM

43

TABLE_TABLEOFCONTENTS_ITEM

44

TABLE_TABLEOFCONTENTS_ITEM

45

TABLE_TABLEOFCONTENTS_ITEM

46

TABLE_TABLEOFCONTENTS_ITEM

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

57

73

75

81

82

93

100

101

102

TABLE_5_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

CONTENTS

SYSTEM & DEBUG CONNECTORS

BASEBAND PMU (1 0F 2)

BASEBAND PMU (2 OF 2)

BASEBAND (1 OF 2)

MOBILE DATA MODEM (2 OF 2)

RF TRANSCEIVER (1 0F 3)

RF TRANSCEIVER (2 OF 3)

RF TRANSCEIVER (3 OF 3)

BAND 5/8 PAD

BAND 13 PA

2G PA, DCDC CONVERTER

DCS RX, ASM

BAND 1/4 PAD

BAND2 PAD

RX DIVERSITY

WIFI/BT

IO FLEX: DOCK COMPONENTS

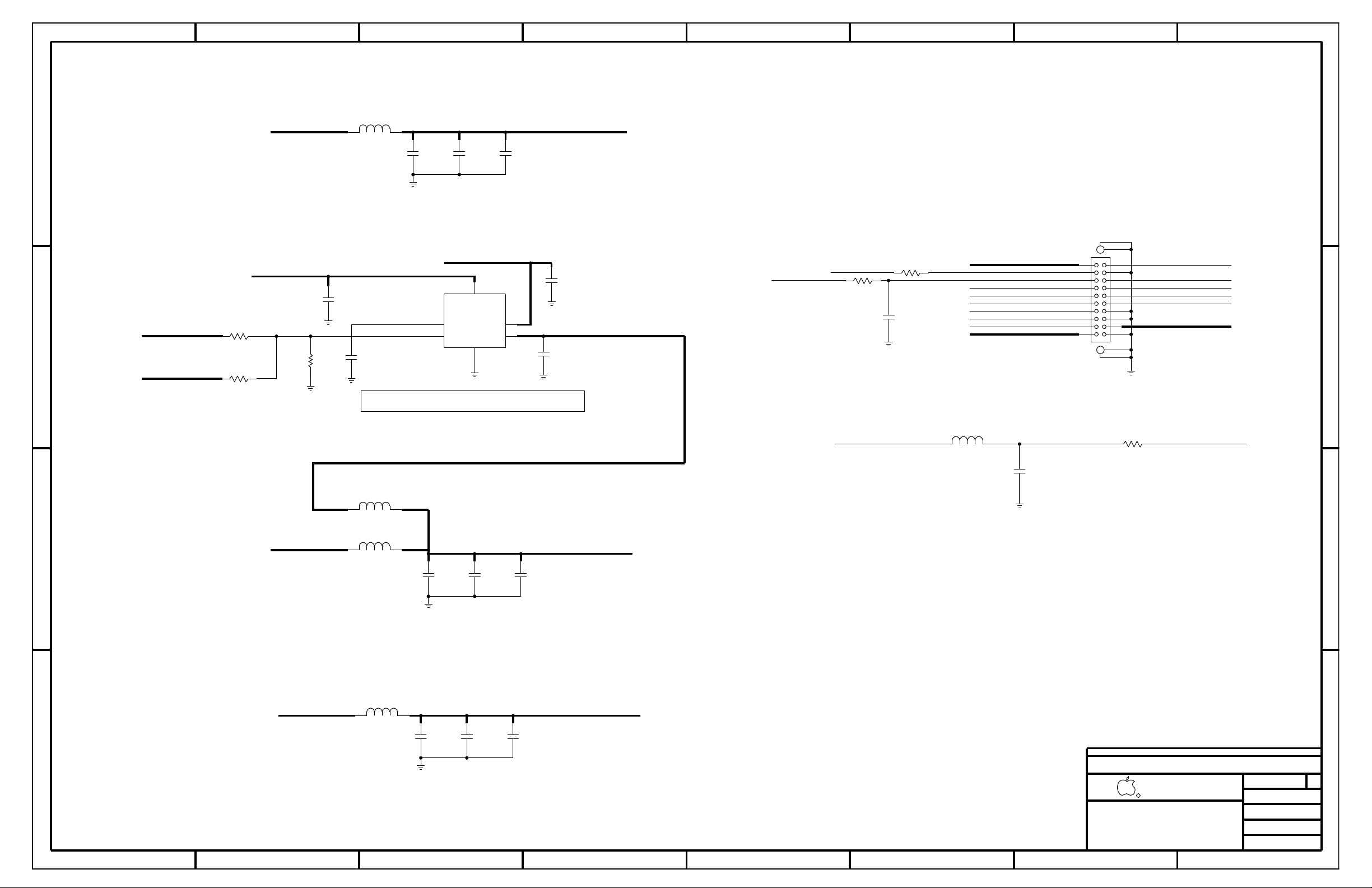

Power: Aliases

POWER: BATTERY CONNECTOR

Power: PMU

POWER: PMU

MECHANCIAL PARTS

CONSTRAINTS: ASSIGNMENTS

CONSTRAINTS: ASSIGNMENTS

CONSTRAINTS: MLB RULES

SYNC MASTER

N/A

N/A

DATE

06/27/2012JORGE

06/27/2012JORGE

06/27/2012JORGE

06/27/2012JORGE

06/27/2012JORGE

06/27/2012JORGE

06/27/2012JORGE

06/27/2012JORGE

06/27/2012JORGE

06/27/2012JORGE

06/27/2012JORGE

06/27/2012JORGE

06/27/2012JORGE

06/27/2012JORGE

06/27/2012JORGE

06/27/2012JORGE

06/27/2012JORGE

04/18/2011

N/AN/A

N/AN/A

N/AN/A

05/09/2011

N/AN/A

N/AN/A

N/AN/A

N/AN/A

D

C

B

A

DRAWING

3

DRAWING TITLE

SCH,MLB,X123

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

DRAWING NUMBER

051-9374

REVISION

13.0.0

BRANCH

PAGE

1 OF 102

SHEET

1 OF 46

1245678

SIZE

A

D

87

WWW.AliSaler.Com

6 5 4 3

12

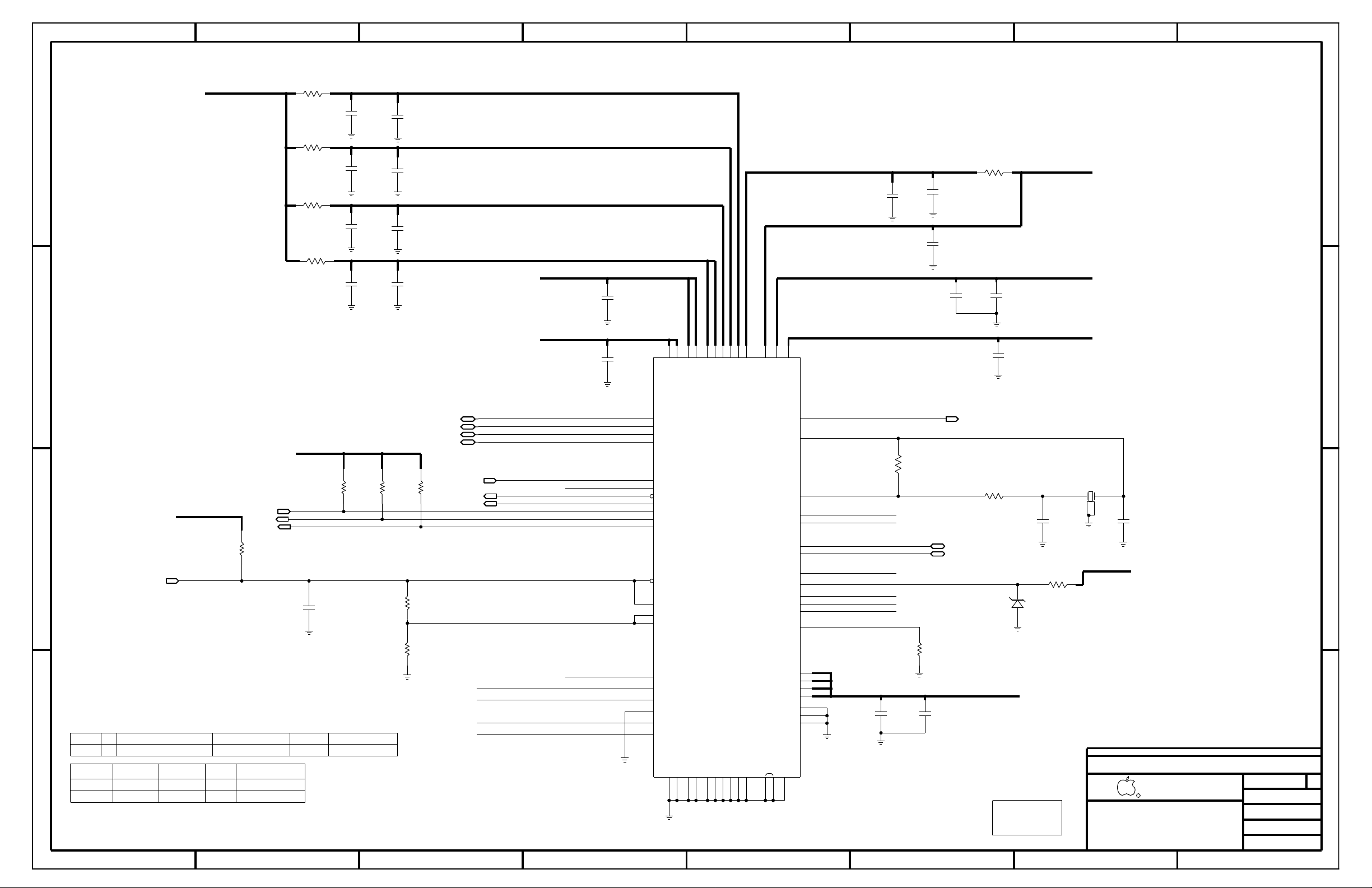

ISP_I2C1

CUMULUS

MASTER

CABERNET BRD

SPI1

H4A

MIPI1C

ISP_I2C0

MIPI0C

D

CUMULUS

SLAVE

CABERNET BRD

DUAL-CORE ARM

CORTEX-A9 W/ SMP

1GHZ

LPDDR2

HSIC1

UART4

FF CAMERA

CANADA FLEX

REAR CAMERA

SENSOR PANEL

RF/GPS

D

RF ANT

2X32-BIT

400MHZ/800MB/S

DISPLAY/

TOUCH PANEL

C

LVDS

MLC

(POR)

CSA 21

MIPI0D

DUAL-CORE IMG

GPU

SGX543-MP

AUDIO

AE2

ARM A5 CPU

HSIC2

UART3

UART1

I2S3

BT_I2S

CSA 32-46

WIFI/BT

CSA 47

WIFI/BT ANT

C

BACKLIGHT

UART5_RTXD

NAND FLASH

PMU

BATTERY

FMI0

ALISON

FMI1

CSA 75

DWI

I2C0

CSA 81-82

B

AUDIO CODEC

SPI

ASP

XSP

E75

IO FLEX

TRISTAR

CSA 13

MIKEY

BB USB

UART4

JTAG

USB2.0

UART0

UART2

I2C2

I2C1

SPI2

I2S0

I2S2

I2S1

CSA 14

B

L81

HS JACK

AUDIO JACK FLEX

CSA 19

A

GYRO

AP3GDL20 (NEW) (SAME AS K93A)

CSA 27

ACCELEROMETER

AP3DSH (NEW)

CSA 27

ALS

(SAME AS K93A)

VGA FLEX

PROX

(SAME AS J2)

CSA 28

COMPASS

CSA 27

6 3

AMP

CSA 20

AMP

CSA 20

SPEAKER

CSA 20

SYNC_MASTER=N/A

PAGE TITLE

BLOCK DIAGRAM: SYSTEM

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

SYNC_DATE=N/A

DRAWING NUMBER

051-9374

REVISION

13.0.0

BRANCH

PAGE

2 OF 102

SHEET

2 OF 46

124578

SIZE

A

D

87

R0620

0.00

=PP1V0_PLL_H4

39

D

12

0%

1/32W

MF

01005

R0621

0.00

12

0%

1/32W

MF

01005

R0622

0.00

12

0%

1/32W

MF

01005

R0624

0.00

12

0%

1/32W

MF

01005

1

C0651

0.01UF

10%

6.3V

2

X5R

01005

1

C0648

0.01UF

10%

6.3V

2

X5R

01005

1

C0646

0.01UF

10%

6.3V

2

X5R

01005

1

C0608

0.01UF

10%

6.3V

2

X5R

01005

1

2

1

2

1

2

1

2

6 5 4 3

VOLTAGE=1.1V

MIN_LINE_WIDTH=0.2MM

MIN_NECK_WIDTH=0.1MM

NET_SPACING_TYPE=PWR

MAX_NECK_LENGTH=3 MM

PP1V0_PLL4_F

C0680

27PF

5%

16V

NP0-C0G

01005

PP1V0_PLL3_F

C0681

27PF

5%

16V

NP0-C0G

01005

PP1V0_PLL2_F

C0682

27PF

5%

16V

NP0-C0G

01005

PP1V0_PLL01_F

C0683

27PF

5%

16V

NP0-C0G

01005

VOLTAGE=1.1V

MIN_LINE_WIDTH=0.2MM

MIN_NECK_WIDTH=0.1MM

NET_SPACING_TYPE=PWR

MAX_NECK_LENGTH=3 MM

VOLTAGE=1.1V

MIN_LINE_WIDTH=0.2MM

MIN_NECK_WIDTH=0.1MM

NET_SPACING_TYPE=PWR

MAX_NECK_LENGTH=3 MM

VOLTAGE=1.1V

MIN_LINE_WIDTH=0.2MM

MIN_NECK_WIDTH=0.1MM

NET_SPACING_TYPE=PWR

MAX_NECK_LENGTH=3 MM

39

=PP1V0_USB_H4

3

1

C0643

0.22UF

20%

6.3V

2

X5R

0201

VOLTAGE=1.1V

MIN_LINE_WIDTH=0.2MM

MIN_NECK_WIDTH=0.1MM

NET_SPACING_TYPE=PWR

MAX_NECK_LENGTH=3 MM

PP1V0_PLL_USB_F

1

C0684

27PF

5%

16V

2

NP0-C0G

01005

1

C0652

0.01UF

10%

6.3V

2

X5R

01005

1

C0627

0.01UF

10%

6.3V

2

X5R

01005

1

2

C0640

1UF

20%

6.3V

X5R

0201

R0625

0.00

12

0%

1/32W

MF

01005

1

C0630

0.01UF

10%

6.3V

2

X5R

01005

=PP1V0_USB_H4

=PP3V3_USB_H4

3

39

8

39

12

D

=PP1V2_HSIC_H4

C

HSIC1_BB_DATA

21 44

BI

HSIC1_BB_STB

21 44

BI

HSIC2_WLAN_DATA

21 44

BI

HSIC2_WLAN_STB

21 44

=PP1V8_H4

3 4 6 9

39

1

R0647

100K

1%

1/32W

MF

01005

NOSTUFF

C0618

1000PF

10%

6.3V

X5R

01005

2

COMMON339S0179

JTAG_SOC_TDI

44

1%

1/32W

MF

01005

IN

JTAG_SOC_TMS

10 44

OUT

JTAG_SOC_TCK

10 44

OUT

CRITICAL BOM OPTION

CRITICAL

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_ITEM

1

2

ELPIDA

HYNIX

=PP1V8_H4

3 4 6 9

39

1

R0617

B

RST_SYSTEM_L

10 21 42

IN

A

PART#

PART NUMBER

339S0187

339S0188 339S0179

DESCRIPTION

QTY

1

H4A B0,35NM,1.15MM HEIGHT

ALTERNATE FOR

PART NUMBER

339S0179

BOM OPTION

REF DES

U0652

U0652

10K

2

REFERENCE DESIGNATOR(S)

U0652

COMMENTS:

1

R0646

100K

1%

1/32W

MF

01005

2

R0688

100K

1/32W

01005

R0689

221K

1/32W

01005

TABLE_5_HEAD

TABLE_5_ITEM

1%

MF

1%

MF

1

2

1

2

SAMSUNG

1

R0645

100K

1%

1/32W

MF

01005

2

BI

9

IN

9

44

OUT

9

44

OUT

SOC_DDR_CKEIN

SOC_TST_STPCLK

9

SOC_TESTMODE

9

SOC_FAST_SCAN_CLK

9

SOC_HOLD_RESET

9

39

JTAG_SOC_SEL

JTAG_SOC_TRST_L

JTAG_SOC_TDO

1

2

NC_JTAG_SOC_TRTCK

TP_SOC_TST_CLKOUT

C0642

0.22UF

20%

6.3V

X5R

0201

W30

HSIC1_DATA

W31

HSIC1_STB

R31

HSIC2_DATA

U31

HSIC2_STB

A25

JTAG_SEL

E26

JTAG_TRTCK

E25

JTAG_TRST*

D26

JTAG_TDO

D25

JTAG_TDI

B25

JTAG_TMS

C26

JTAG_TCK

G23

RESET*

J23

CFSB

K12

DDR0_CKEIN

T9

DDR1_CKEIN

A29

TST_CLKOUT

A26

TST_STPCLK

G20

TESTMODE

H26

FUSE1_FSRC

F22

FAST_SCAN_CLK

H23

HOLD_RESET

W26

HSIC_VDD121

25MA

HSIC_VSS121

W28

V24

V27

V25

HSIC_VDD122

25MA

HSIC1_DVDD101

10MA

10MA

HSIC1_DVSS

HSIC_VSS122

W25

W29

V26

E21

E20

E18

E17

E16

4MA

4MA

4MA

HSIC2_DVDD102

4MA

4MA

4MA

OMIT

U0652

H4A

BGA

(1 OF 12)

POP-512MB-DDR

CRITICAL

USB_BRICKID_DM_MON

PLL4_AVSS11 PLL4_AVDD11

PLL3_AVSS11 PLL3_AVDD11

PLL2_AVSS11 PLL2_AVDD11

PLL1_AVSS11 PLL1_AVDD11

PLL0_AVSS11 PLL0_AVDD11

HSIC2_DVSS

D21

D20

D18

D17

D16

T27

R25

E19

USB_DVDD

10MA

35MA

USB11_DP

USB11_DM

USB_ANALOGTEST

USB_VBUS

USB_BRICKID

USB_REXT

2MA

PVDDP_CFSB

17MA

PVDDP_FMI0

6MA

PVDDP_TESTS

4MA

PVDDP_UART4

VSEL30_FMI

VSEL30_TST

VSEL30_UART4

USB_VSSA0

PLL_USB_AVSS11 PLL_USB_AVDD11

R27

R26

D19

P27

USB_VDD330

USB_ASW_VDD18

1MA

WDOG

XI0

XO0

USB_DP

USB_DM

USB_ID

USB_ASW_VSS18

P28

C27

A15

A16

T29

U29

M31

N31

U26

N28

M28

U27

T26

T25

J18

AC27

F27

AH25

G21

J21

H21

45

XTAL_SOC_24M_I

XTAL_SOC_24M_O

45

NC_USB_FS_D_P

NC_USB_FS_D_N

NC_USB_ANALOGTEST

USB_SOC_VBUS

NC_USB_ID

NC_USB_BRICKID_DP_MON

NC_USB_BRICKID_DM_MON

USB_REXT

SOC_WDOG

1.00M

1%

01005

12

9

9

SOC_USB_D_P

SOC_USB_D_N

1

C0610

0.01UF

10%

6.3V

2

X5R

01005

R0655

MF

1/32W

1

2

R0642

43.2

1%

1/20W

MF

201

1

C0611

0.01UF

10%

6.3V

2

X5R

01005

BI

BI

10

OUT

10 44

10 44

GDZT2R5.1B

=PP1V8_PVDDP_H4

1

2

R0640

1.00K

12

1%

1/32W

MF

01005

NOSTUFF

DZ0600

GDZ-0201

NOTE FOR VSEL...

0 - 1.8V IO

1.8V - 3V IO

=PP1V8_USB_H4

C0641

0.01UF

10%

6.3V

X5R

01005

XTAL_SOC_24M_O_R

1

2

R0651

68.1K

12

K

A

39

24.000MHZ-16PF-60PPM

C0613

15PF

5%

16V

NP0-C0G-CERM

01005

1%

1/32W

MF

01005

6 3

39

CRITICAL

Y0602

SM-2

31

24

PPVBUS_USB

SYNC_MASTER=N/A

PAGE TITLE

1

C0607

15PF

5%

16V

2

NP0-C0G-CERM

01005

41

AP: MAIN

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

SYNC_DATE=04/18/2011

DRAWING NUMBER

051-9374

REVISION

13.0.0

BRANCH

PAGE

6 OF 102

SHEET

3 OF 46

124578

SIZE

C

B

A

D

87

WWW.AliSaler.Com

6 5 4 3

12

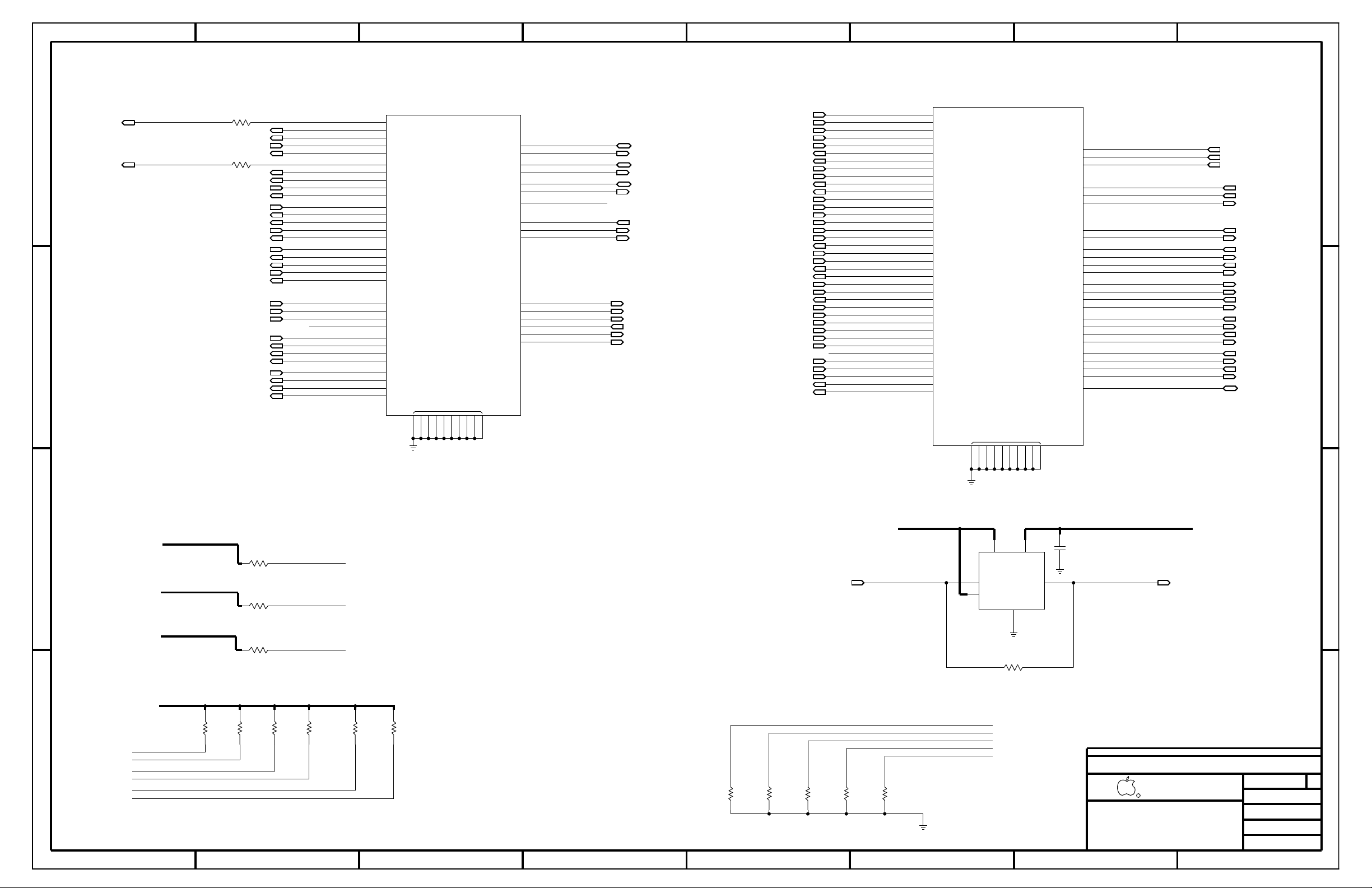

H4A I/OS

R0720

33.2

1%

1/32W

MF

01005

I2S0_CODEC_ASP_MCK

14 44

OUT

D

I2S1_SPKAMP_MCK

15 44

OUT

C

12

R0721

33.2

1%

1/32W

44

MF

01005

12

44

I2S0_CODEC_ASP_MCK_R

44

I2S0_CODEC_ASP_BCLK

14 44

OUT

I2S0_CODEC_ASP_LRCK

14 44

OUT

I2S0_CODEC_ASP_DIN

14 44

IN

I2S0_CODEC_ASP_DOUT

14

OUT

I2S1_SPKAMP_MCK_R

44

I2S1_SPKAMP_BCLK

15 44

OUT

I2S1_SPKAMP_LRCK

15 44

OUT

I2S1_SPKAMP_DIN

15 44

IN

I2S1_SPKAMP_DOUT

15 44

OUT

PMU_GPIO_TRISTAR_IRQ

10 42

IN

I2S2_CODEC_XSP_BCLK

14 44

OUT

I2S2_CODEC_XSP_LRCK

14 44

OUT

I2S2_CODEC_XSP_DIN

14 44

IN

I2S2_CODEC_XSP_DOUT

14 44

OUT

GPIO_ACC_SW_POK_L

10

IN

I2S3_BT_BCLK

21 44

OUT

I2S3_BT_LRCK

21 44

OUT

I2S3_BT_DIN

21 44

IN

I2S3_BT_DOUT

21 44

OUT

GPIO_BOARD_ID2

9

IN

GPIO_BOARD_ID1

9

IN

GPIO_BOARD_ID0

9

IN

SPI1_GRAPE_MISO

12 44

IN

SPI1_GRAPE_MOSI

12 44

OUT

SPI1_GRAPE_SCLK

12 44

OUT

SPI1_GRAPE_CS_L

12 44

OUT

SPI2_CODEC_MISO

14 44

IN

SPI2_CODEC_MOSI

14

OUT

SPI2_CODEC_SCLK

14 44

OUT

SPI2_CODEC_CS_L

14 44

OUT

NC_SPI0_SSIN

AM18

AM19

AP14

AP17

AM22

AM13

AK3

AP8

AL14

AM20

AM9

AM16

AK2

AN17

AM2

AM1

AL16

AN20

AH1

AK5

AP21

AB1

AM15

AM4

AP23

AM3

AP13

AH4

AN13

AM12

AN22

AM21

I2S0_MCK

I2S0_BCLK

I2S0_LRCK

I2S0_DIN

I2S0_DOUT

I2S1_MCK

I2S1_BCLK

I2S1_LRCK

I2S1_DIN

I2S1_DOUT

I2S2_MCK

I2S2_BCLK

I2S2_LRCK

I2S2_DIN

I2S2_DOUT

I2S3_MCK

I2S3_BCLK

I2S3_LRCK

I2S3_DIN

I2S3_DOUT

SPI0_MISO

SPI0_MOSI

SPI0_SCLK

SPI0_SSIN

SPI1_MISO

SPI1_MOSI

SPI1_SCLK

SPI1_SSIN

SPI2_MISO

SPI2_MOSI

SPI2_SCLK

SPI2_SSIN

OMIT

U0652

H4A

BGA

POP-512MB-DDR

(3 OF 12)

I2C0_SCL

I2C0_SDA

I2C1_SCL

I2C1_SDA

I2C2_SCL

I2C2_SDA

SWI_DATA

DWI_DI

DWI_DO

DWI_CLK

SDIO0_CLK

SDIO0_CMD

SDIO0_DATA0

SDIO0_DATA1

SDIO0_DATA2

SDIO0_DATA3

AL4

AM6

AM7

AG3

D29

E29

AN6

U1

AN18

AM11

AH28

AJ24

AK25

AH24

AJ27

AK24

I2C0_SCL

I2C0_SDA

I2C1_SCL

I2C1_SDA

I2C2_SCL

I2C2_SDA

NC_SWI_AP

DWI_DI

DWI_DO

DWI_CLK

BB_JTAG_TCK

BB_JTAG_TMS

BB_JTAG_TDI

BB_JTAG_TDO

BB_JTAG_TRST_L

GPIO_ACC_SW_EN

AB5

AB4

AD5

AC4

AA3

AE5

AD3

AF5

AF4

AB3

AE4

AH3

K4

GPIO0

H1

GPIO1

F2

GPIO2

G4

GPIO3

G3

GPIO4

G2

GPIO5

K3

GPIO6

L4

GPIO7

G1

GPIO8

H2

GPIO9

N3

GPIO10

J2

GPIO11

J3

GPIO12

J1

GPIO13

W3

GPIO14

W4

GPIO15

M3

GPIO16

GPIO17

N2

GPIO18

GPIO19

Y4

GPIO20

GPIO21

H4

GPIO22

L2

GPIO23

GPIO24

V3

GPIO25

GPIO26

GPIO27

GPIO28

GPIO29

T2

GPIO30

GPIO31

GPIO32

GPIO33

P2

GPIO34

R3

GPIO35

GPIO36

GPIO_BTN_HOME_L

4

12 42

IN

GPIO_BTN_POWER_L

4

20 42

IN

GPIO_BTN_VOL_UP_L

20

IN

GPIO_BTN_VOL_DOWN_L

20

IN

4

10 15 42 44

BI

4

10 15 42 44

OUT

4

18 19 44

BI

4

18 19 44

OUT

4

17 18 44

BI

4

17 18 44

OUT

42 44

IN

42 44

OUT

42 44

OUT

21 24 44

OUT

21 24 44

OUT

21 24 44

OUT

21 24 44

IN

21 24 44

OUT

10

OUT

GPIO_BTN_SRL_L

4

20 42

IN

GPIO_SPKAMP_RST_L

4

15

OUT

GPIO_SPKAMP_KEEPALIVE

15

OUT

GPIO_SPKAMP_RIGHT_IRQ_L

15

IN

GPIO_CODEC_IRQ_L

14

IN

GPIO_BT_WAKE

21

OUT

GPIO_BB_RST_L

21

OUT

GPIO_BB_GSM_TXBURST

21

IN

GPIO_BB_IPC_GPIO

21

IN

GPIO_BB_DIAGS_RDY

21

IN

GPIO_BB_GPS_SYNC

21

IN

GPIO_BB_RST_DET_L

21

IN

GPIO_BOARD_ID3

9

IN

GPIO_BB_HSIC_HOST_RDY

21

OUT

GPIO_BOOT_CONFIG0

9

IN

GPIO_PMU_IRQ_L

42

IN

GPIO_PMU_KEEPACT

4

42

OUT

GPIO_GRAPE_RST_L

12

OUT

GPIO_GRAPE_IRQ_L

12

IN

GPIO_BB_RADIO_ON_L

21

IN

GPIO_BB_HSIC_DEV_RDY

21

OUT

GPIO_BOOT_CONFIG1

9

IN

GPIO_FORCE_DFU

4 9

IN

GPIO_DFU_STATUS

4

IN

GPIO_BOOT_CONFIG2

9

IN

GPIO_BOOT_CONFIG3

9

IN

GPIO_PROX_IRQ_L

19

IN

NC_GPIO31

GPIO_ACCEL_IRQ2_L

18

IN

GPIO_GYRO_IRQ1

18

IN

GPIO_WLAN_HSIC_RESUME

21

IN

GPIO_MLC_PWR_EN

16

OUT

GPIO_MLC_RST_1V8_L

4

OUT

VSS

B1

A31

A30

A27

A14

A13

A12

A11

A17

A24

OMIT

U0652

H4A

BGA

POP-512MB-DDR

(2 OF 12)

VSS

EHCI_PORT_PWR0

EHCI_PORT_PWR1

EHCI_PORT_PWR2

TMR32_PWM0

TMR32_PWM1

TMR32_PWM2

UART0_RXD

UART0_TXD

UART1_CTSN

UART1_RTSN

UART1_RXD

UART1_TXD

UART2_CTSN

UART2_RTSN

UART2_RXD

UART2_TXD

UART3_CTSN

UART3_RTSN

UART3_RXD

UART3_TXD

UART4_CTSN

UART4_RTSN

UART4_RXD

UART4_TXD

UART5_RTXD

T3

V2

U2

AP5

AP4

AN5

B29

C29

AG5

AH5

AL1

AK1

N1

T1

M1

R1

AF2

AG2

AE1

AF1

AJ26

AJ25

AK26

AK27

D28

GPIO_BOARD_REV0

GPIO_BOARD_REV1

GPIO_BOARD_REV2

GPIO_GYRO_IRQ2

GPIO_ACCEL_IRQ1_L

AP_CLK_32K_CUMULUS

UART0_DEBUG_RXD

UART0_DEBUG_TXD

UART1_BT_CTS_L

UART1_BT_RTS_L

UART1_BT_RXD

UART1_BT_TXD

GPIO_ALS_IRQ_L

GPIO_SPKAMP_LEFT_IRQ_L

UART2_ACC_RXD

UART2_ACC_TXD

GPIO_WLAN_HSIC_DEV_RDY

GPIO_WLAN_HSIC_HOST_RDY

UART3_WLAN_RXD

UART3_WLAN_TXD

UART4_BB_CTS_L

UART4_BB_RTS_L

UART4_BB_RXD

UART4_BB_TXD

UART5_BATT_RTXD

9

IN

9

IN

9

IN

18

IN

18

IN

44

12

OUT

10 44

IN

10 44

OUT

21

44

IN

21 44

OUT

21 44

IN

21 44

OUT

17

OUT

15

OUT

10 44

IN

10 44

OUT

21

IN

21

OUT

21 44

IN

21 44

OUT

21

44

IN

21 44

OUT

10 21 44

IN

10 21 44

OUT

40 42 44

BI

D

C

=PP1V8_S2R_MISC

4 9

10 39

B

=PP1V8_ALWAYS

39

=PP1V8_S2R_MISC

4 9

10 39

=PP1V8_H4

3 6 9

39

A

10 15 42 44

10 15 42 44

18 19 44

18 19 44

17 18 44

17 18 44

I2C0_SDA

4

I2C0_SCL

4

I2C1_SDA

4

I2C1_SCL

4

I2C2_SDA

4

I2C2_SCL

4

1

R0700

2.2K

5%

1/32W

MF

01005

2

1

2

R0771

220K

12

12

12

R0701

2.2K

1/32W

01005

R0770

220K

1/32W

01005

R0765

220K

1/32W

01005

5%

1/32W

MF

01005

5%

MF

5%

MF

5%

MF

GPIO_BTN_HOME_L

GPIO_BTN_POWER_L

GPIO_BTN_SRL_L

1

R0702

1.8K

5%

1/32W

MF

01005

2

(SCREEN ROTATION LOCK)

1

R0703

1.8K

5%

1/32W

MF

01005

2

A1

=PP1V8_IO_H4

6 8

39

4

12 42

GPIO_MLC_RST_1V8_L

4

IN

4

20 42

4

20 42

1

R0704

2.2K

5%

1/32W

MF

01005

2

1

R0705

2.2K

5%

1/32W

MF

01005

2

1

R0739

100K

1%

1/32W

MF

01005

2

1

R0735

100K

1%

1/32W

MF

01005

2

1

R0736

100K

1%

1/32W

MF

01005

2

1

R0737

100K

1%

1/32W

MF

01005

2

1

R0738

100K

1%

1/32W

MF

01005

2

GPIO_SPKAMP_RST_L

GPIO_PMU_KEEPACT

GPIO_MLC_RST_1V8_L

GPIO_FORCE_DFU

GPIO_DFU_STATUS

C1

B2

6 3

A6

A1

VCCA

U0701

SN74LVC1T45YZPR

BGA

A

NOSTUFF

DIR

GND

B1

R0750

0.00

12

0%

1/32W

MF

01005

4

15

4

42

4

4 9

4

A7

A2

VCCB

A10

=PP3V0_MLC_RST_LEVELSHIFTER

NOSTUFF

1

C0701

0.1UF

20%

6.3V

2

X5R-CERM

01005

C2

B

GPIO_MLC_RST_L

SYNC_MASTER=N/A

PAGE TITLE

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

OUT

Apple Inc.

R

39

16

AP: I/Os

SYNC_DATE=05/05/2011

DRAWING NUMBER

051-9374

REVISION

13.0.0

BRANCH

PAGE

7 OF 102

SHEET

4 OF 46

SIZE

B

A

D

124578

A9

A8

A5

A4A3A2

87

39

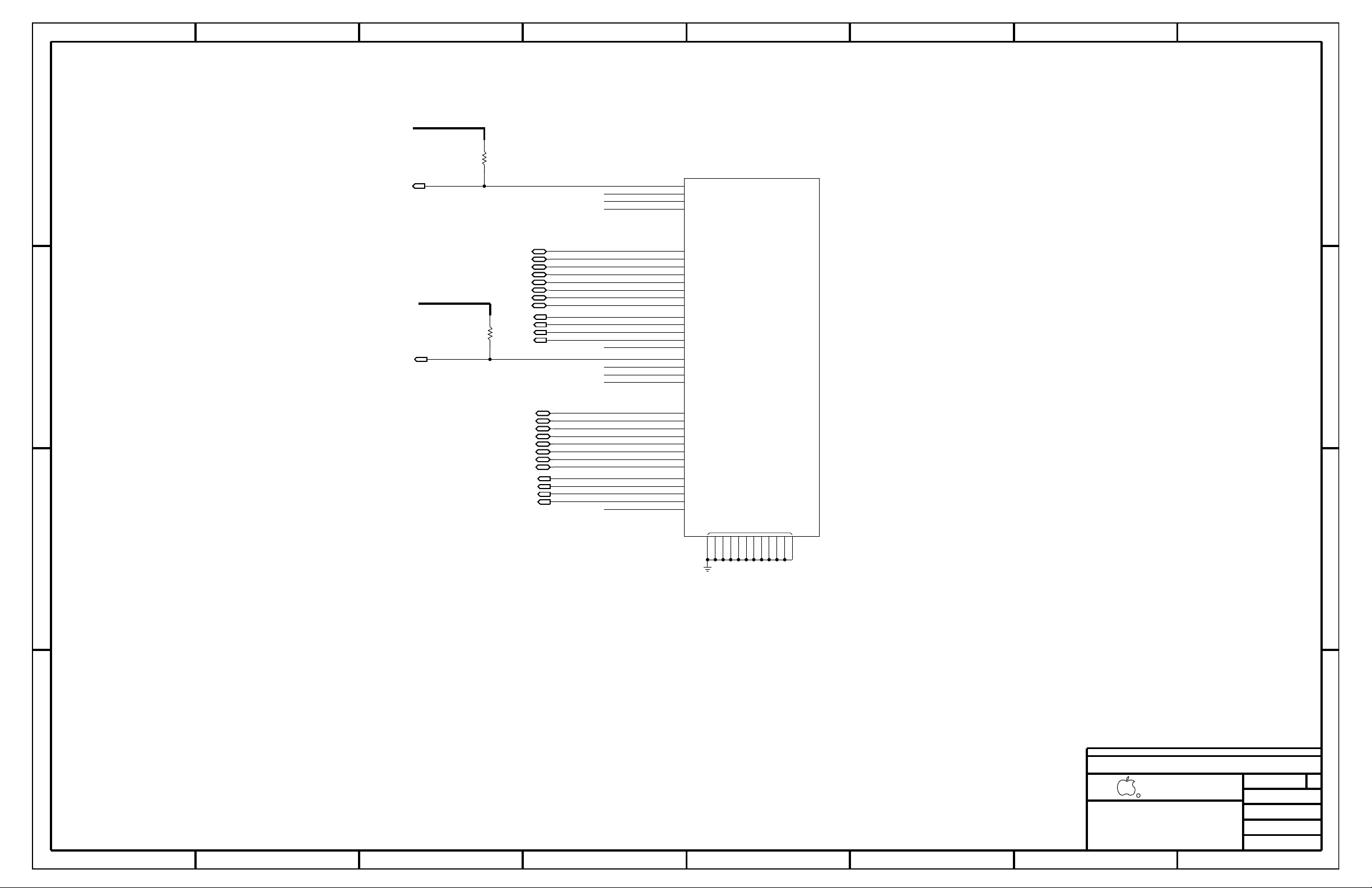

D

6 5 4 3

=PP1V8_NAND_H4

5 8

R0831

1

100K

1%

1/32W

MF

01005

2

FMI0_CE0_L

11 44

OUT

NC_FMI0_CEN1

NC_FMI0_CEN2

NC_FMI0_CEN3

AF28

AE26

AF25

AF26

FMI0_CEN0

FMI0_CEN1

FMI0_CEN2

FMI0_CEN3

OMIT

U0652

H4A

BGA

POP-512MB-DDR

(4 OF 12)

12

D

FMI0_AD<0>

11 44

BI

FMI0_AD<1>

11 44

BI

FMI0_AD<2>

11 44

BI

FMI0_AD<3>

11 44

BI

FMI0_AD<4>

11 44

BI

FMI0_AD<5>

11 44

BI

FMI0_AD<6>

11 44

=PP1V8_NAND_H4

5 8

39

C

11 44

OUT

FMI1_CE0_L

R0832

1

100K

1%

1/32W

MF

01005

2

BI

FMI0_AD<7>

11 44

BI

FMI0_ALE

11 44

OUT

FMI0_CLE

11 44

OUT

FMI0_WE_L

11 44

OUT

FMI0_RE_N

11 44

OUT

FMI1_AD<0>

11 44

BI

FMI1_AD<1>

11 44

BI

FMI1_AD<2>

11 44

BI

FMI1_AD<3>

11 44

BI

FMI1_AD<4>

11 44

BI

FMI1_AD<5>

11 44

BI

FMI1_AD<6>

11 44

BI

FMI1_AD<7>

11 44

BI

FMI1_ALE

11 44

OUT

FMI1_CLE

11 44

OUT

FMI1_WE_L

11 44

OUT

FMI1_RE_N

11 44

OUT

FMI0_DQS_P

11 44

NC_FMI1_CEN1

NC_FMI1_CEN2

NC_FMI1_CEN3

FMI1_DQS_P

11 44

B

AC28

AC26

AD29

AD26

AE25

AG28

AG26

AG27

AD25

AE28

AC25

AD28

AE27

AB30

AB26

AA25

AB25

W27

Y28

Y26

AA31

AA28

AB28

AA29

AB29

AB31

AA26

Y25

Y29

AA27

FMI0_IO0

FMI0_IO1

FMI0_IO2

FMI0_IO3

FMI0_IO4

FMI0_IO5

FMI0_IO6

FMI0_IO7

FMI0_ALE

FMI0_CLE

FMI0_WEN

FMI0_REN

FMI0_DQS

FMI1_CEN0

FMI1_CEN1

FMI1_CEN2

FMI1_CEN3

FMI1_IO0

FMI1_IO1

FMI1_IO2

FMI1_IO3

FMI1_IO4

FMI1_IO5

FMI1_IO6

FMI1_IO7

FMI1_ALE

FMI1_CLE

FMI1_WEN

FMI1_REN

FMI1_DQS

C

VSS

B6B5B3

B9

B8

B2

B11

B12

B13

B15

B16

B17

B

A

SYNC_MASTER=N/A

PAGE TITLE

AP: FLASH MEMORY INTERFACE

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

6 3

SYNC_DATE=04/18/2011

DRAWING NUMBER

051-9374

REVISION

13.0.0

BRANCH

PAGE

8 OF 102

SHEET

5 OF 46

124578

SIZE

A

D

87

WWW.AliSaler.Com

6 5 4 3

12

PART NUMBER

VOLTAGE=0.4V

MIN_LINE_WIDTH=0.2MM

MIN_NECK_WIDTH=0.1MM

D

NET_SPACING_TYPE=PWR

MAX_NECK_LENGTH=3 MM

PP_AP_MIPI0D_0P4V

TV/DISPLAYPORT

VOLTAGE=0.4V

MIN_NECK_MIDTH SHOULD BE 0.2MM

MIPI

=PP1V8_MIPI_H4

=PP1V8_DPORT_H4

=PP1V8_IO_H4

4 8

39

=PP1V0_DPORT_H4

C

NC_DAC_COMP

NC_DAC_VREF

NC_DAC_IREF

NC_DP_PAD_DC_TP

NC_DP_PAD_R_BIAS

C23

DAC_COMP

H24

DAC_VREF

C24

DAC_IREF

P24

DP_PAD_DC_TP

N27

DP_PAD_R_BIAS

B

E23

E22

DAC_AVDD18A

DAC_AVDD18D

12MA

DAC_AVSS18A

DAC_AVSS18D

D23

D22

M27

L24

K26

DP_PAD_AVDD0

DP_PAD_AVDD1

77MA 77MA

OMIT

DP_PAD_AVDD_AUX

8MA

U0652

H4A

BGA

POP-512MB-DDR

(6 OF 12)

DP_PAD_AVSS0

DP_PAD_AVSS1

DP_PAD_AVSS_AUX

N24

M24

L25

M25

N25

DP_PAD_AVDDX

15MA

DP_PAD_AVDDP0

11MA

5MA

DAC_OUT3

DAC_OUT2

DAC_OUT1

DP_HPD

DP_PAD_AUXP

DP_PAD_AUXN

DP_PAD_TX0P

DP_PAD_TX0N

DP_PAD_TX1P

DP_PAD_TX1N

DP_PAD_AVSSX

DP_PAD_AVSSP0

M26

N26

P26

P25

DP_PAD_DVDD

A21

A22

A23

E27

K31

J31

G31

F31

D31

C31

DP_PAD_DVSS

NC_DAC_OUT3

NC_DAC_OUT2

NC_DAC_OUT1

NC_DP_HPD

NC_DP_PAD_AUXP

NC_DP_PAD_AUXN

NC_DP_PAD_TX0P

NC_DP_PAD_TX0N

NC_DP_PAD_TX1P

NC_DP_PAD_TX1N

39

39

39

39

12

OUT

20 45

IN

20 45

IN

20

45

IN

20 45

IN

20 45

OUT

20 45

OUT

16 45

OUT

16 45

OUT

16 45

OUT

16 45

OUT

16 45

OUT

16 45

OUT

16 45

OUT

16 45

OUT

16 45

OUT

16 45

OUT

1

C0907

0.1UF

20%

6.3V

2

X5R-CERM

01005

=PP1V0_MIPI_H4

1

C0930

1UF

20%

6.3V

2

X5R

0201

DISPLAY_SYNC

MIPI0C_CAM_REAR_DATA_P<0>

MIPI0C_CAM_REAR_DATA_N<0>

MIPI0C_CAM_REAR_DATA_P<1>

MIPI0C_CAM_REAR_DATA_N<1>

NC_MIPI0C_CAM_REAR_DATA_P<2>

9

NC_MIPI0C_CAM_REAR_DATA_N<2>

9

NC_MIPI0C_CAM_REAR_DATA_P<3>

9

NC_MIPI0C_CAM_REAR_DATA_N<3>

9

MIPI0C_CAM_REAR_CLK_P

MIPI0C_CAM_REAR_CLK_N

MIPI0D_DATA_P<0>

MIPI0D_DATA_N<0>

MIPI0D_DATA_P<1>

MIPI0D_DATA_N<1>

MIPI0D_DATA_P<2>

MIPI0D_DATA_N<2>

MIPI0D_DATA_P<3>

MIPI0D_DATA_N<3>

MIPI0D_CLK_P

MIPI0D_CLK_N

1

2

C0908

0.1UF

20%

6.3V

X5R-CERM

01005

1

2

C0903

0.1UF

20%

6.3V

X5R-CERM

01005

AM10

AM30

AM31

AL30

AL31

AJ30

AJ31

AH30

AH31

AK30

AK31

AN25

AP25

AN26

AP26

AN28

AP28

AN29

AP29

AN27

AP27

MIPI_VSYNC

MIPI0C_DPDATA0

MIPI0C_DNDATA0

MIPI0C_DPDATA1

MIPI0C_DNDATA1

MIPI0C_DPDATA2

MIPI0C_DNDATA2

MIPI0C_DPDATA3

MIPI0C_DNDATA3

MIPI0C_DPCLK

MIPI0C_DNCLK

MIPI0D_DPDATA0

MIPI0D_DNDATA0

MIPI0D_DPDATA1

MIPI0D_DNDATA1

MIPI0D_DPDATA2

MIPI0D_DNDATA2

MIPI0D_DPDATA3

MIPI0D_DNDATA3

MIPI0D_DPCLK

MIPI0D_DNCLK

AG17

AG18

AG19

AG20

45MA

POP-512MB-DDR

AG21

AG22

AG23

MIPI_VDD10

OMIT

U0652

H4A

BGA

(5 OF 12)

MIPI_VSS

AJ19

AJ23

MIPI0D_VDD

4MA

AJ18

ISP0_PRE_FLASH

ISP1_PRE_FLASH

MIPI1C_DPDATA0

MIPI1C_DNDATA0

MIPI1C_DPDATA1

MIPI1C_DNDATA1

MIPI1D_DPDATA0

MIPI1D_DNDATA0

MIPI1D_DPDATA1

MIPI1D_DNDATA1

MIN_LINE_WIDTH=0.2MM

MIN_NECK_WIDTH=0.1MM

NET_SPACING_TYPE=PWR

MAX_NECK_LENGTH=3 MM

PP_AP_MIPI1D_0P4V

VOLTAGE=1.1V

MIN_LINE_WIDTH=0.2MM

MIN_NECK_WIDTH=0.1MM

NET_SPACING_TYPE=PWR

MAX_NECK_LENGTH=3 MM

PP1V0_MIPID_PLL_F

AJ22

AJ17

AJ21

MIPI0D_VDD10_PLL

MIPI0D_VREG_0P4V

MIPI1D_VDD10_PLL

MIPI1D_VREG_0P4V

6.6MA

ISP0_SDA

ISP0_SCL

ISP1_SDA

ISP1_SCL

ISP0_FLASH

SENSOR0_CLK

SENSOR0_RST

ISP1_FLASH

SENSOR1_CLK

SENSOR1_RST

MIPI1C_DPCLK

MIPI1C_DNCLK

MIPI1D_DPCLK

MIPI1D_DNCLK

1

2

AC1

AP7

AL20

AN3

AL17

AL13

AP19

AN8

AL19

AL10

AP11

AP18

AG30

AG31

AE30

AE31

AF30

AF31

AL28

AL29

AJ28

AJ29

AK28

AK29

C0961

27PF

5%

16V

NP0-C0G

01005

1

2

44

80-OHM-0.2A-0.4-OHM

R0931

2.2K

5%

1/32W

MF

01005

1

2

1

R0932

2.2K

5%

1/32W

MF

01005

2

C0963

1

C0962

0.1UF

20%

6.3V

2

X5R-CERM

01005

1

R0930

2.2K

5%

1/32W

MF

01005

2

NC_ISP0_FLASH

NC_ISP0_PRE_FLASH

ISP0_CAM_REAR_CLK_R

44

NC_ISP1_FLASH

NC_ISP1_PRE_FLASH

ISP1_CAM_FRONT_CLK_R

NC_MIPI1C_CAM_FRONT_DATA_P<1>

NC_MIPI1C_CAM_FRONT_DATA_N<1>

NC_MIPI1D_AP_DATA_P<0>

NC_MIPI1D_AP_DATA_N<0>

NC_MIPI1D_AP_DATA_P<1>

NC_MIPI1D_AP_DATA_N<1>

NC_MIPI1D_AP_CLK_P

NC_MIPI1D_AP_CLK_N

1UF

20%

6.3V

X5R

0201

49.9

100

01005

01005

FL0911

0201-1

1

R0933

2.2K

5%

1/32W

MF

01005

2

ALTERNATE FOR

PART NUMBER

155S0359155S0725

1

C0902

2.2NF

10%

10V

2

X5R-CERM

0201

1

C0920

2.2NF

10%

10V

2

X5R-CERM

0201

21

12

12

R0941

R0940

9

9

9

9

9

9

9

9

BOM OPTION

REF DES

FL0911

=PP1V0_MIPI_PLL_H4

=PP1V8_H4

ISP0_CAM_REAR_SDA

ISP0_CAM_REAR_SCL

ISP1_CAM_FRONT_SDA

ISP1_CAM_FRONT_SCL

ISP0_CAM_REAR_CLK

ISP0_CAM_REAR_SHUTDOWN

ISP1_CAM_FRONT_CLK

ISP1_CAM_FRONT_SHUTDOWN

MIPI1C_CAM_FRONT_DATA_P<0>

MIPI1C_CAM_FRONT_DATA_N<0>

MIPI1C_CAM_FRONT_CLK_P

MIPI1C_CAM_FRONT_CLK_N

COMMENTS:

RADAR: 11363497

39

3 4 9

39

BI

OUT

BI

OUT

OUT

OUT

OUT

OUT

IN

IN

OUT

OUT

20 44

20 44

17 44

17 44

20 44

20

17

17

17 45

17 45

17 45

17 45

44

TABLE_ALT_HEAD

TABLE_ALT_ITEM

D

C

B

A

AH22

AH23

AH21

AH20

AH19

AH18

AH17

6 3

SYNC_MASTER=MLB

PAGE TITLE

AP: TV/DP/MIPI/CAMERA

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

SYNC_DATE=05/04/2012

DRAWING NUMBER

051-9374

REVISION

13.0.0

BRANCH

PAGE

9 OF 102

SHEET

6 OF 46

124578

SIZE

A

D

87

=PP1V2_S2R_H4

7

39

1

R1005

2.21K

1%

1/32W

MF

01005

2

PPVREF_DDR0_CA

1

R1006

2.21K

1%

D

=PP1V2_VDDQ_H4

7

39

1/32W

MF

01005

2

1

R1053

1.00K

1%

1/32W

MF

01005

2

1

R1054

1.00K

1%

1/32W

MF

01005

2

NOSTUFF

1

C1002

0.01UF

10%

6.3V

2

X5R

01005

PPVREF_DDR0_DQ

NOSTUFF

1

C1054

0.01UF

10%

6.3V

2

X5R

01005

7

44

VOLTAGE=0.6V

MIN_NECK_WIDTH=0.2MM

MIN_LINE_WIDTH=0.3MM

NET_SPACING_TYPE=VREF

MAX_NECK_LENGTH=3 MM

7

44

VOLTAGE=0.6V

MIN_NECK_WIDTH=0.2MM

MIN_LINE_WIDTH=0.3MM

NET_SPACING_TYPE=VREF

MAX_NECK_LENGTH=3 MM

=PP1V2_S2R_H4

7

39

CRITICAL

0.22UF

C

=PP1V2_S2R_H4

7

39

1

R1051

2.21K

1%

1/32W

MF

01005

2

PPVREF_DDR1_CA

1

R1052

2.21K

1%

1/32W

MF

01005

2

=PP1V2_VDDQ_H4

7

39

1

R1055

1.00K

1%

1/32W

MF

01005

B

2

1

R1056

1.00K

1%

1/32W

MF

01005

2

NOSTUFF

1

C1052

0.01UF

10%

6.3V

2

X5R

01005

PPVREF_DDR1_DQ

NOSTUFF

1

C1056

0.01UF

10%

6.3V

2

X5R

01005

7

44

VOLTAGE=0.6V

MIN_NECK_WIDTH=0.2MM

MIN_LINE_WIDTH=0.3MM

NET_SPACING_TYPE=VREF

MAX_NECK_LENGTH=3 MM

7

44

VOLTAGE=0.6V

MIN_NECK_WIDTH=0.2MM

MIN_LINE_WIDTH=0.3MM

NET_SPACING_TYPE=VREF

MAX_NECK_LENGTH=3 MM

CRITICAL

C1027

0.22UF

6.3V

0201

=PP1V2_VDDQ_H4

7

39

6.3V

0201

CRITICAL

1

C1029

0.22UF

20%

2

X5R

CRITICAL

1

C1028

0.22UF

20%

2

X5R

6 5 4 3

=PP1V2_S2R_H4

7

39

C1001

0.01UF

6.3V

01005

1

10%

2

X5R

=PP1V2_VDDIOD_H4

AP15

AP10

AD31

AC30

AN12

AN16

AN21

AA30

AD30

AN14

AN23

AE29

AN10

AN24

L12

T10

Y31

B19

P30

Y30

A18

A19

A28

L30

AJ1

AP9

A20

B28

M30

AA2

AJ2

B10

B14

B18

B20

B24

B27

C30

F30

J30

AE2

AH2

AL2

AN4

AN7

Y2

C2

W1

Y1

C1

B4

B7

E2

K2

M2

R2

W2

DDR0_VDDQ_CKE

DDR1_VDDQ_CKE

DDR0_VREF_CA

DDR1_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR0_ZQ

DDR1_ZQ

VDDCA

80MA

VDD2

320MA (DRAM CORE)

20MA

VDD1

(DRAM CORE - CHARGE PUMP)

VDDQ

500MA

OMIT

<1MA

U0652

<1MA

H4A

BGA

POP-512MB-DDR

(7 OF 12)

VSS

B21

B22

B23

B26

B30

B31

C3

C4

C5

C6

C7

C8

C9

C10

C11

C12

C13

C14

C15

C16

C17

C18

C19

C20

C21

C22

C25

C28

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D24

D27

D30

E1

E3

E4

E5

E6

E7

E8

E9

E10

E11

E12

E13

E14

E15

E24

E28

E30

E31

F1

F3

39

=PP1V8_VDDIO18_H4

39

CRITICAL

C1039

0.22UF

6.3V

0201

CRITICAL

C1036

0.22UF

6.3V

0201

CRITICAL

C1042

4.7UF

6.3V

X5R-CERM1

20%

X5R

20%

X5R

20%

402

CRITICAL

C1034

4.7UF

6.3V

X5R-CERM1

CRITICAL

1

0.22UF

2

CRITICAL

1

0.22UF

2

CRITICAL

1

0.22UF

2

20%

402

C1040

C1037

C1043

6.3V

0201

6.3V

0201

6.3V

0201

1

2

1

20%

2

X5R

1

20%

2

X5R

1

20%

2

X5R

C1004

6.3V

0201

20%

6.3V

X5R

0201

20%

X5R

1

2

CRITICAL

1

0.22UF

2

CRITICAL

C1030

0.22UF

C1005

20%

6.3V

X5R

0201

6.3V

0201

20%

X5R

39

1

2

R1001

240

12

12

240

R1000

CRITICAL

1

C1006

0.22UF

2

=PP1V8_S2R_H4

CRITICAL

C1015

4.7UF

X5R-CERM1

CRITICAL

1

C1024

4.7UF

20%

6.3V

2

X5R-CERM1

402

CRITICAL

C1031

0.22UF

20%

6.3V

X5R

0201

1%

1/20W

1/20W1%201

(DDR IMPEDANCE CONTROL)

CRITICAL

1

C1007

0.22UF

20%

6.3V

2

X5R

0201

CRITICAL

C1009

4.7UF

X5R-CERM1

CRITICAL

1

C1019

0.22UF

20%

6.3V

2

402

C1026

0.01UF

6.3V

01005

CRITICAL

1

C1032

0.22UF

6.3V

2

0201

C1000

0.01UF

10%

6.3V

X5R

01005

PPVREF_DDR0_CA

7

44

PPVREF_DDR1_CA

7

44

PPVREF_DDR1_DQ

7

44

PPVREF_DDR0_DQ

7

44

DDR0_ZQ

201

MF

DDR1_ZQ

MF

1

20%

6.3V

2

X5R

0201

1

20%

6.3V

2

402

1

20%

6.3V

2

X5R

0201

1

10%

2

X5R

1

20%

2

X5R

1

2

C1035

0.01UF

6.3V

01005

CRITICAL

C1041

0.22UF

6.3V

0201

CRITICAL

C1038

0.22UF

6.3V

0201

G7

G9

AE16

AE15

AE14

AE13

AE12

AE11

AE10

G11

G13

G15

H10

H12

H14

H16

J10

J11

J12

J13

J14

J15

J16

AA7

AA8

AB9

AC9

AD9

AE9

H20

H19

H6

H8

J7

J8

J9

K6

K8

L7

L8

M6

M8

N7

N8

P6

P8

R7

R8

T6

T8

U7

U8

V6

V8

W7

W8

Y6

Y8

VDDIOD

VDDIO18_GRP1

VDDIO18_GRP2

VDDIO18_GRP3

1

10%

2

X5R

1

20%

2

X5R

1

20%

2

X5R

OMIT

U0652

H4A

BGA

POP-512MB-DDR

(9 OF 12)

500MA

(VDDQ = VDDIOD)

(DON’T DOUBLE COUNT)

75MA

GPIO

EHCI (UNUSED)

UART[1-3] (1-2 UNUSED)

I2C[0-1]

ISP[0-1]

DWI

SENSOR[0-1]

ISP FLASH (UNUSED)

I2S[0-3] (1 UNUSED)

SPI[0-2] (0,2 UNUSED)

11MA - VSEL30_X,CFSB,TEST

2MA - XI/0

VSS

K7

K9

K10

K11

K13

K15

K17

K19

K21

K23

K24

K27

K28

K29

K30

L1

L3

L5

L6

L10

L14

L16

L18

L20

L22

L26

L27

L28

L29

L31

M4

M5

M7

M9

M11

M13

M15

M17

M19

M21

M23

M29

N4

N5

N6

N10

N12

N14

N16

N18

N20

N22

N29

N30

P1

P3

P4

P5

P7

P9

P11

P13

P15

P17

P19

P21

P23

P29

P31

R4

R5

R6

12

D

C

B

A

SYNC_MASTER=N/A

PAGE TITLE

AP: PWR

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

6 3

SYNC_DATE=04/18/2011

DRAWING NUMBER

051-9374

REVISION

13.0.0

BRANCH

PAGE

10 OF 102

SHEET

7 OF 46

124578

SIZE

A

D

87

WWW.AliSaler.Com

R10

R12

R14

R16

R18

R20

R22

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AB11

R24

R28

R29

R30

T11

T13

T15

T17

T19

T21

T23

T28

G19

T30

U10

U12

U14

U16

U18

U20

U22

U24

U28

H17

U30

J17

V11

V13

V15

V17

V19

V21

V23

V28

V29

W10

W12

W14

W16

W18

W20

W22

W24

Y11

Y13

Y15

Y17

Y19

Y21

Y23

Y27

AA1

AA4

AA5

AA6

AB2

AB6

AB7

AB8

T4

T5

T7

U3

U4

U5

U6

V1

V4

V5

V7

V9

W5

W6

Y3

Y5

Y7

Y9

D

C

B

A

OMIT

U0652

H4A

BGA

POP-512MB-DDR

(11 OF 12)

AB13

AB15

AB17

AB19

AB21

AB23

AB27

AC2

AC3

AC5

AC6

AC7

AC8

AC10

AC12

AC14

AC16

AC18

AC20

AC22

AC29

AC31

AD1

AD2

AD4

AD6

AD7

AD8

AD11

AD13

AD15

AD17

AD19

AD21

AD23

AD27

AE3

AE6

AE7

AE8

AE18

AE20

AE22

VSSVSS

AF3

J22

AF6

AF7

AF8

AF9

AF10

AF11

AF12

AF13

AF14

AF15

AF16

AF17

AF19

AF21

AF23

AF24

AF27

AF29

AG1

AG4

AG6

AG7

AG8

AG9

AG10

AG11

AG12

AG13

AG14

AG15

AG16

AG24

AG25

AG29

AH6

AH7

AH8

AH9

AH10

AH11

AH12

AH13

AH14

AH15

AH16

AH26

AH29

X5R-CERM1

CRITICAL

C1110

0.22UF

6.3V

0201

CRITICAL

C1116

0.22UF

6.3V

0201

CRITICAL

C1122

0.22UF

6.3V

0201

=PPVDD_SOC_H4

39

CRITICAL

1

C1104

4.7UF

20%

6.3V

2

402

1

0.22UF

20%

2

X5R

1

0.22UF

20%

2

X5R

1

0.22UF

20%

2

X5R

CRITICAL

C1105

4.7UF

X5R-CERM1

CRITICAL

C1111

6.3V

0201

CRITICAL

C1117

6.3V

0201

CRITICAL

C1123

6.3V

0201

6 5 4 3

K14

K16

K18

K20

K22

L17

CRITICAL

1

C1106

10UF

20%

6.3V

2

402

CRITICAL

1

C1112

0.22UF

20%

X5R

20%

X5R

20%

X5R

2

1

2

1

2

AJ3

AJ4

AJ5

AJ6

AJ7

AJ8

AJ9

AJ10

AJ11

AJ12

AJ13

AJ14

AJ15

AJ16

AJ20

AK4

AK6

AK7

AK8

AK9

AK10

AK11

AK12

AK13

AK14

AK15

AK16

AK17

AK18

AK19

AK20

AK21

AK22

AK23

T31

AL5

AL6

AL7

AL8

CRITICAL

C1118

0.22UF

CRITICAL

C1124

0.22UF

K1

6.3V

0201

6.3V

0201

6.3V

0201

1

20%

6.3V

2

X5R

X5R-CERM1

603

1

20%

2

X5R

1

20%

2

X5R

1

20%

2

X5R

U0652

POP-512MB-DDR

(12 OF 12)

CRITICAL

C1107

4.7UF

CRITICAL

C1113

0.22UF

CRITICAL

C1119

0.22UF

CRITICAL

C1125

0.22UF

C1128

0.01UF

OMIT

H4A

BGA

20%

6.3V

402

6.3V

0201

6.3V

0201

6.3V

0201

6.3V

01005

CRITICAL

1

C1108

4.7UF

2

X5R-CERM1

CRITICAL

1

C1114

0.22UF

20%

2

X5R

CRITICAL

1

C1120

0.22UF

20%

2

X5R

CRITICAL

1

0.22UF

20%

2

X5R

1

C1129

0.01UF

10%

2

X5R

20%

6.3V

402

6.3V

0201

6.3V

0201

C1126

6.3V

0201

10%

6.3V

X5R

01005

VSSVSS

CRITICAL

C1109

4.7UF

X5R-CERM1

0.01UF

AL9

AL11

AL12

AL15

AL18

AL21

AL22

AL23

AL24

AL25

AL26

AL27

AM5

AM8

V30

AM14

AM17

V31

AM23

AM24

AM25

AM26

AM27

AM28

AM29

AN1

AN2

AN9

AN15

AN30

AN31

AP1

AP2

AP3

AP6

AP12

AP16

AP22

AP24

AP30

AP31

20%

6.3V

402

CRITICAL

C1115

0.22UF

6.3V

0201

CRITICAL

C1121

0.22UF

6.3V

0201

CRITICAL

C1127

0.22UF

6.3V

0201

C1130

10%

6.3V

X5R

01005

1

2

1

20%

2

X5R

1

20%

2

X5R

1

20%

2

X5R

1

2

1

2

1

20%

2

X5R

1

20%

2

X5R

1

20%

2

X5R

1

2

L19

L21

L23

M18

M20

M22

N17

N19

N21

N23

P18

P20

P22

R17

R19

R21

R23

T18

T20

T22

T24

U17

U19

U21

U23

V18

V20

V22

W11

W13

W15

W17

W19

W21

W23

Y10

VDD

W9

OMIT

U0652

H4A

BGA

POP-512MB-DDR

(10 OF 12)

4.2A

GRAPHICS

LOWPERF

APPLE MC

HPERF NRT

HPERF RT

CDIO

DISP_OUT

AUDIO COMPLEX

AUDIENCE DSP

USB

PMGR

VDD

Y12

Y14

Y16

Y18

Y20

Y22

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AA23

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC11

AC13

AC15

AC17

AC19

AC21

AC23

AD10

AD12

AD14

AD16

AD18

AD20

AD22

AE17

AE19

AE21

AE23

AF18

AF20

AF22

CRITICAL

C1136

0.22UF

6.3V

0201

1

20%

2

X5R

=PPVDD_CPU_H4

39

CRITICAL

C1137

0.22UF

20%

6.3V

X5R

0201

1

2

CRITICAL

C1138

0.22UF

6.3V

0201

6.3V

6.3V

0201

6.3V

0201

CRITICAL

1

C1132

4.7UF

20%

2

X5R-CERM1

402

CRITICAL

C1134

4.7UF

6.3V

CRITICAL

1

C1140

0.22UF

20%

2

X5R

CRITICAL

1

C1143

0.22UF

20%

2

X5R

C1145

0.01UF

=PP3V3_USB_H4

3

39

=PP1V8_IO_H4

4 6

39

=PP1V8_NAND_H4

5

39

=PP1V8_VDDIOD3_H4

39

CRITICAL

C1131

4.7UF

X5R-CERM1

CRITICAL

1

C1139

0.22UF

20%

2

X5R

CRITICAL

C1142

0.22UF

6.3V

20%

402

20%

402

6.3V

0201

6.3V

0201

01005

1

2

1

2

20%

X5R

20%

X5R

10%

6.3V

X5R

CRITICAL

4.7UF

X5R-CERM1

CRITICAL

4.7UF

X5R-CERM1

CRITICAL

4.7UF

X5R-CERM1

CRITICAL

C1135

4.7UF

X5R-CERM1X5R-CERM1

1

2

1

2

1

2

C1147

0.01UF

C1148

0.01UF

C1149

20%

6.3V

402

C1151

20%

6.3V

402

C1133

20%

6.3V

402

20%

6.3V

402

CRITICAL

C1141

0.22UF

CRITICAL

C1144

0.22UF

C1146

0.01UF

10%

6.3V

X5R

01005

10%

6.3V

X5R

01005

1

2

1

2

6.3V

0201

6.3V

0201

6.3V

01005

1

2

1

2

1

2

1

2

1

20%

2

X5R

1

20%

2

X5R

1

10%

2

X5R

L9

L11

L13

L15

M10

M12

M14

M16

N9

N11

N13

N15

P10

P12

P14

VDD_CPU

P16

R9

R11

R13

R15

T12

T14

T16

U9

U11

U13

U15

V10

V12

V14

V16

U25

VDDIO30_USB11_DM

AH27

VDDIOD1

AA24

AB24

AC24

AD24

VDDIOD2

AE24

Y24

J25

K25

VDDIOD3

SYNC_MASTER=N/A

PAGE TITLE

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

OMIT

U0652

H4A

BGA

POP-512MB-DDR

(8 OF 12)

2.4A

A9 CORES

L2 CACHE

BIU

5MA

UNUSED

(UART4 <= GPIOS)

10MA

(SDIO <= WIFI)

35MA (NAND)

VDDIOD3

35MA

I2C2

UART0

UART5_RTXD

DP_HPD

TST_CLKOUT

TST_STPCLK

WDOG

JTAG

AP: PWR

Apple Inc.

6 3

12

F4

F5

F6

F7

F8

F9

F10

F11

F12

F13

F14

F15

F16

F17

F18

F21

F23

F24

F25

F26

F28

F29

G5

G6

G8

G10

G12

G14

G16

G18

AL3

G22

AN11

G24

VSS

G25

G26

G27

G28

G29

G30

H3

H5

H7

H9

H11

H13

H15

H18

AN19

AP20

H22

F19

H25

H27

H28

H29

H30

H31

J4

J5

J6

J19

J20

F20

G17

J24

J26

J27

J28

J29

K5

SYNC_DATE=04/18/2011

DRAWING NUMBER

051-9374

REVISION

13.0.0

BRANCH

PAGE

11 OF 102

SHEET

8 OF 46

124578

SIZE

D

C

B

A

D

87

6 5 4 3

12

BOOT CONFIG ID

D

BOARD ID

C

BOARD REVISION

B

BOOT_CONFIG[3] (GPIO29)

BOOT_CONFIG[2] (GPIO28)

BOOT_CONFIG[1] (GPIO25)

BOOT_CONFIG[0] (GPIO18)

FOR REFERENCE

CURRENT SETTING ->

39

BOARD_ID[3]

BOARD_ID[2]

BOARD_ID[1]

BOARD_ID[0]

X123A

X123B

GPIO_BOARD_REV2

4

GPIO_BOARD_REV1

4

GPIO_BOARD_REV0

4

BRD_REV[2-0]

PROTO 0

000

PROTO 1

001

PROTO 2

010

EVT

011

DVT

100

=PP1V8_H4

3 4 6 9

39

4

4

4

4

BOOT_CONFIG[3:0]

0000 SPI0

0001 SPI3

0010 SPI0 W/TEST

0011 SPI3 W/TEST

0100 FMI0 2CS

0101 FMI0 4CS

0110 FMI0 4CS W/TEST

0111 RESERVED

1000 FMI1 2 CS

1001 FMI1 4 CS

1010 FMI1 4CS W/TEST

1011 RESERVED

1100 FMI0/1 2/2 CS

1101 FMI0/1 4/4 CS

1110 FMI0/1 4/4 CS W/TEST

1111 RESERVED

=PP1V8_H4

3 4 6 9

GPIO_BOARD_ID3

4

GPIO_BOARD_ID2

4

GPIO_BOARD_ID1

4

GPIO_BOARD_ID0

4

ID[3-0] SYSTEM

1010 P105 AP

1011 P105 DEV

1100 P106 AP

1101 P106 DEV

1110 P107 AP

1111 P107 DEV

NOSTUFF

1

R1207

2.2K

5%

1/32W

MF

01005

2

S/W READ FLOW

1. SET GPIO AS INPUT

2. ENABLE PU AND DISABLE PD

3. READ

GPIO_BOOT_CONFIG3

GPIO_BOOT_CONFIG2

GPIO_BOOT_CONFIG1

GPIO_BOOT_CONFIG0

1100

BOARD_ID_P106_P107

1

R1204

2.2K

5%

5%

1/32W

1/32W

MF

MF

01005

01005

2

1. SET GPIO AS INPUT

2. DISABLE PU AND ENABLE PD

3. READ

NOSTUFF

1

R1208

2.2K

5%

1/32W

MF

01005

2

1

R1213

2.2K

2

BOOT_CONFIG[3-0]

FMI0/1 2/2 CS

S/W READ FLOW

1

R1209

2.2K

5%

1/32W

MF

01005

2

1

R1200

2.2K

5%

1/32W

MF

01005

2

1

R1201

2.2K

5%

1/32W

MF

01005

2

BOARD_ID_P105_P107

1

R1205

2.2K

5%

1/32W

MF

01005

2

FMI_4CS_TEST

1

R1202

2.2K

5%

1/32W

MF

01005

2

1. SET GPIO AS INPUT

2. DISABLE PU AND ENABLE PD

3. READ

FMI_4CS_NOTEST

1

R1203

2.2K

5%

1/32W

MF

01005

2

S/W READ FLOW

BOARD_ID_DEV

1

R1206

2.2K

5%

1/32W

MF

01005

2

=PP1V8_S2R_MISC

4

10 39

GPIO_FORCE_DFU

4

NOTE: PADS USED FOR DEBUG

NOSTUFF

1

R1270

1K

5%

1/20W

MF

201

2

JTAG

XW0601

XW0602

XW0603

JTAG_SOC_TRST_L

1

R1211

100

5%

1/32W

MF

01005

2

JTAG_SOC_SEL

1

R1210

100

5%

1/32W

MF

01005

2

R1260

100

12

1/32W

01005

SHORT-01005

12

SHORT-01005

12

SHORT-01005

12

3

44

OUT

D

3

OUT

5%

MF

SOC_TESTMODE

SOC_TST_STPCLK

SOC_FAST_SCAN_CLK

SOC_HOLD_RESET

3

3

3

3

NC_AP_MIPI0C_DPDATA2

NC_AP_MIPI0C_DNDATA2

NC_AP_MIPI0C_DPDATA3

NC_AP_MIPI0C_DNDATA3

NC_AP_MIPI1D_DPDATA1

NC_AP_MIPI1D_DNDATA1

NC_AP_MIPI1C_DPDATA1

NC_AP_MIPI1C_DNDATA1

SINGLE-PIN NETS

NC_FMI0_DQS_NEG

NC_FMI0_RE_POS

NC_FMI1_DQS_NEG

NC_FMI1_RE_POS

NC_PMU_SHDWN

NC_JTAG_SOC_TDO

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

FMI0_DQS_N

FMI0_RE_P

FMI1_DQS_N

FMI1_RE_P

PMU_SHDWN

JTAG_SOC_TDO

NC_MIPI0C_CAM_REAR_DATA_P<2>

NC_MIPI0C_CAM_REAR_DATA_N<2>

NC_MIPI0C_CAM_REAR_DATA_P<3>

NC_MIPI0C_CAM_REAR_DATA_N<3>

NC_MIPI1D_AP_CLK_PNC_AP_MIPI1D_DPCLK

NC_MIPI1D_AP_CLK_NNC_AP_MIPI1D_DNCLK

NC_MIPI1D_AP_DATA_P<0>NC_AP_MIPI1D_DPDATA0

NC_MIPI1D_AP_DATA_N<0>NC_AP_MIPI1D_DNDATA0

NC_MIPI1D_AP_DATA_P<1>

NC_MIPI1D_AP_DATA_N<1>

NC_MIPI1C_CAM_FRONT_DATA_P<1>

NC_MIPI1C_CAM_FRONT_DATA_N<1>

NC_USB_FS_D_PNC_AP_USB11_DPD

NC_USB_FS_D_NNC_AP_USB11_DND

C

11

11

11

11

42

3

44

6

6

6

6

6

6

6

6

6

6

6

6

3

3

B

A

SYNC_MASTER=N/A

PAGE TITLE

AP: MISC & ALIASES

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

6 3

SYNC_DATE=04/11/2011

DRAWING NUMBER

051-9374

REVISION

13.0.0

BRANCH

PAGE

12 OF 102

SHEET

9 OF 46

124578

SIZE

A

D

87

WWW.AliSaler.Com

CRITICAL BOM OPTION

CRITICAL

TABLE_ALT_HEAD

TABLE_ALT_ITEM

COMMON

NXP

TI

PART#

343S0614

PART NUMBER

343S0620

DESCRIPTION

QTY

1

IC,ASIC,TRISTAR,CBTL1608,A1,WLCSP36

ALTERNATE FOR

PART NUMBER

BOM OPTION

COMMON343S0614

REFERENCE DESIGNATOR(S)

U1300

REF DES

COMMENTS:

IC,ASIC,TRISTAR,THS7383,A1,WLCSP36

U1300

D

=PP3V0_S2R_TRISTAR

39

C

TO USB BB MUX

AP USB

ACCESSORY UART

AP DEBUG UART

BB DEBUG UART

(T’S OFF TO H4A UART4)

1

C1320

8.2PF

+/-0.5PF

16V

2

NP0-C0G-CERM

01005

=PP1V8_S2R_TRISTAR

10 39

MIKEY_TS_P

14 45

MIKEY_TS_N

14 45

USB_BB_D_P

21 44

USB_BB_D_N

21 44

USB_BRICKID

42

SOC_USB_D_P

3

44

SOC_USB_D_N

3

44

UART2_ACC_TXD

4

44

UART2_ACC_RXD

4

44

UART0_DEBUG_TXD

4

44

UART0_DEBUG_RXD

4

44

UART4_BB_RXD

4

21 44

UART4_BB_TXD

4

21 44

JTAG_SOC_TCK

3

44

JTAG_SOC_TMS

3

44

CRITICAL

1

C1300

2

1

C1321

8.2PF

+/-0.5PF

16V

2

NP0-C0G-CERM

01005

0.1UF

20%

6.3V

X5R-CERM

01005

6 5 4 3

TABLE_5_HEAD

TABLE_5_ITEM

=PPVCC_MAIN_ACC_SW

CRITICAL

1

C1360

1.0UF

20%

10V

2

X5R-CERM

0201-1

CRITICAL

1

C1301

0.1UF

20%

6.3V

2

X5R-CERM

01005

TRISTAR

THS7383IYKAR

C3

DIG_DP

C4

DIG_DN

A1

USB1_DP

B1

USB1_DN

C2

BRICK_ID

A3

USB0_DP

B3

USB0_DN

E2

UART0_TX

E1

UART0_RX

F2

UART1_TX

F1

UART1_RX

D2

UART2_TX

D1

UART2_RX

A5

JTAG_CLK

B5

JTAG_DIO

F3F4D5

VDD_1V8

VDD_3V0

U1300

WCSP

CON_DET_L

OVP_SW_EN*

SWITCH_EN

HOST_RESET

DVSS

DVSS

CRITICAL

OMIT

ACC_PWR

BYPASS

DVSS

A6C1F5

P_IN

ACC1

ACC2

DP1

DN1

DP2

DN2

SDA

SCL

INT

CRITICAL

1

C1302

4.7UF

10%

25V

2

X5R-CERM

0603

F6

C5

TS_ACC1

E5

TS_ACC2

A2

TS_E75_DPAIR1_P

B2

TS_E75_DPAIR1_N

A4

TS_E75_DPAIR2_P

B4

TS_E75_DPAIR2_N

E3

TS_CON_DET_L

D6

OVP_SW_EN_L

E4

RST_SYSTEM_L

B6

TS_HOST_RESET

D3

I2C0_SDA

D4

I2C0_SCL

C6

PMU_GPIO_TRISTAR_IRQ

E6

TRISTAR_ADD0

CRITICAL

1

C1303

1.0UF

20%

10V

2

X5R-CERM

0201-1

1

C1322

8.2PF

+/-0.5PF

16V

2

NP0-C0G-CERM

01005

38

38

38 44

38 44

38 44

38 44

10 38

OUT

IN

OUT

4

15 42 44

4

15 42 44

VOLTAGE=3V

MIN_LINE_WIDTH=0.2MM

MIN_NECK_WIDTH=0.1MM

NET_SPACING_TYPE=PWR

MAX_NECK_LENGTH=0.5MM

TRISTAR BYPASS FOR 3V LDO

10

PP3V3_ACC_FET

38

3

21 42

10

4

42

OUT

4

10

PPVBUS_PROT

CRITICAL

1

C1361

1UF

10%

25V

2

X5R

402

=PP1V8_S2R_MISC

4 9

39

GPIO_ACC_SW_POK_L

OUT

38

39

=PP3V3_ACC

1

R1321

100K

1%

1/32W

MF

01005

2

LAYOUT NOTE:

ADD THERMAL GND VIAS TO U1350

A2

C1

CRITICAL

1

2

C1350

0.1UF

10%

6.3V

X5R

201

VCC

U1350

LM34904

USMD

ACC_PWR

POK*

GND

CSD68803W15

C1

B2

B1

A2

A1

CRITICAL

ENABLE

ACC_DET*

B1

NOSTUFF

R1350

0.00

12

1%

1/20W

MF

0201

Q1301

BGA

D

G

A1

B2

C2

CRITICAL

S

C3

C2

B3

A3

CRITICAL

1

R1322

220K

5%

1/32W

MF

01005

2

GPIO_ACC_SW_EN

TS_CON_DET_L

1

R1320

1.00M

1%

1/32W

MF

01005

2

PP3V3_ACC_FET

VOLTAGE=3.3V

MIN_LINE_WIDTH=0.6MM

MIN_NECK_WIDTH=0.2MM

NET_SPACING_TYPE=PWR

MAX_NECK_LENGTH=3 MM

4

IN

10 38

IN

10 39

12

D

C

GPIO_ACC_SW_POK

B

L81_MBUS_REF

14

OUT

R1370

0.00

12

0%

1/32W

MF

01005

GPIO_ACC_SW_POK_L

4

10

1

C1362

470PF

2

10%

10V

X5R

01005

3

D

CRITICAL

G

1

Q1300

DMN26D0UFB4

S

DFN

SYM_VER_1

2

B

A

EITHER TRISTAR OR AP CAN RESET PMU

=PP1V8_S2R_TRISTAR

10 39

1

C1310

0.1UF

20%

6.3V

2

X5R-CERM

3

IN

10

IN

SOC_WDOG

TS_HOST_RESET

1

R1310

220K

5%

1/32W

MF

01005

2

01005

1

R1311

220K

5%

1/32W

MF

01005

2

2

1

6

U1310

NC

CRITICAL

74LVC1G32

SOT891

4

35

NC_U1310_5

6 3

PMU_RESET_IN

SIZE

A

D

42

OUT

SYNC_MASTER=N/A

PAGE TITLE

E75 SUPPORT

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

SYNC_DATE=N/A

DRAWING NUMBER

051-9374

REVISION

13.0.0

BRANCH

PAGE

13 OF 102

SHEET

10 OF 46

124578

87

6 5 4 3

12

FLASH CONFIGURATIONS

QTY

PART NUMBER

335S0889

335S0871

335S0872

335S0873

D

=PP3V3_NAND

39

1

2

C1490

27PF

5%

16V

NP0-C0G

01005

1

2

C1491

27PF

5%

16V

NP0-C0G

01005

1

C1405

0.22UF

20%

6.3V

2

X5R

0201

C

1

2

1

2

C1492

C1406

0.22UF

20%

6.3V

X5R

0201

27PF

5%

16V

NP0-C0G

01005

1

2

CRITICAL

1

C1451

1UF

20%

6.3V

2

X5R

0201

5

44

5

44

5

44

5

44

5

44

5

44

5

44

5

44

5

44

5

44

5

44

5

44

5

44

5

44

5

44

5

44

CRITICAL

C1400

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

10UF

20%

6.3V

CERM-X5R

0402-2

CRITICAL

1

C1450

1UF

20%

6.3V

2

X5R

0201

FMI0_AD<0>

FMI0_AD<1>

FMI0_AD<2>

FMI0_AD<3>

FMI0_AD<4>

FMI0_AD<5>

FMI0_AD<6>

FMI0_AD<7>

FMI1_AD<0>

FMI1_AD<1>

FMI1_AD<2>

FMI1_AD<3>

FMI1_AD<4>

FMI1_AD<5>

FMI1_AD<6>

FMI1_AD<7>

CRITICAL

1

2

PPVDDI_NAND_U1400

B

TP_TCKC_U1400

TP_TMSC_U1400

C1401

10UF

20%

6.3V

CERM-X5R

0402-2

CRITICAL

1

2

VOLTAGE=1.2V

MIN_LINE_WIDTH=0.2MM

MIN_NECK_WIDTH=0.1MM

NET_SPACING_TYPE=PWR

MAX_NECK_LENGTH=3MM

C1402

10UF

20%

6.3V

CERM-X5R

0402-2

OA0

OB0

1

2

C1404

0.1UF

20%

6.3V

X5R-CERM

01005

G3

H2

J3

K2

L5

K6

J5

H6

G1

J1

L1

N3

N5

L7

J7

G7

IO0-0

IO1-0

IO2-0

IO3-0

IO4-0

IO5-0

IO6-0

IO7-0

IO0-1

IO1-1

IO2-1

IO3-1

IO4-1

IO5-1

IO6-1

IO7-1

TCKC

TMSC

VDDI

OB8

F2M6B6

VCC

VSS

1

C1410

0.1UF

20%

6.3V

2

X5R-CERM

01005

OA8

OF8G0OE0

OD8

OC8

N7

N1

VCCQ

CRITICAL

OMIT

U1400

LGA-12X17

XXNM-XGBX8-MLC-PPN1.5-ODP

CE0*

CLE0

ALE0

WE0*

RE0

RE0*

DQS0

DQS0*

R/B0*

CE1*

CLE1

ALE1

WE1*

RE1

RE1*

DQS1

DQS1*

R/B1*

VREF

A5

A3

C1

E3

B4

C7

H4

F4

E5

C5

C3

D2

E1

D4

D6

M4

K4

E7

G5

A1

ZQ

VSSQ

A7M2L3F6B2

OC0

OD0

OE8

OF0

G8

CRITICAL

1

C1411

10UF

20%

6.3V

2

CERM-X5R

0402-1

FMI0_CE0_L

FMI0_CLE

FMI0_ALE

FMI0_WE_L

FMI0_RE_P

FMI0_RE_N

FMI0_DQS_P

FMI0_DQS_N

FMI1_CE0_L

FMI1_CLE

FMI1_ALE

FMI1_WE_L

FMI1_RE_P

FMI1_RE_N

FMI1_DQS_P

FMI1_DQS_N

FMI_ZQ_U1400

CRITICAL

1

C1412

10UF

20%

6.3V

2

CERM-X5R

0402-2

1

2