Analog Devices SSM2404 Datasheet

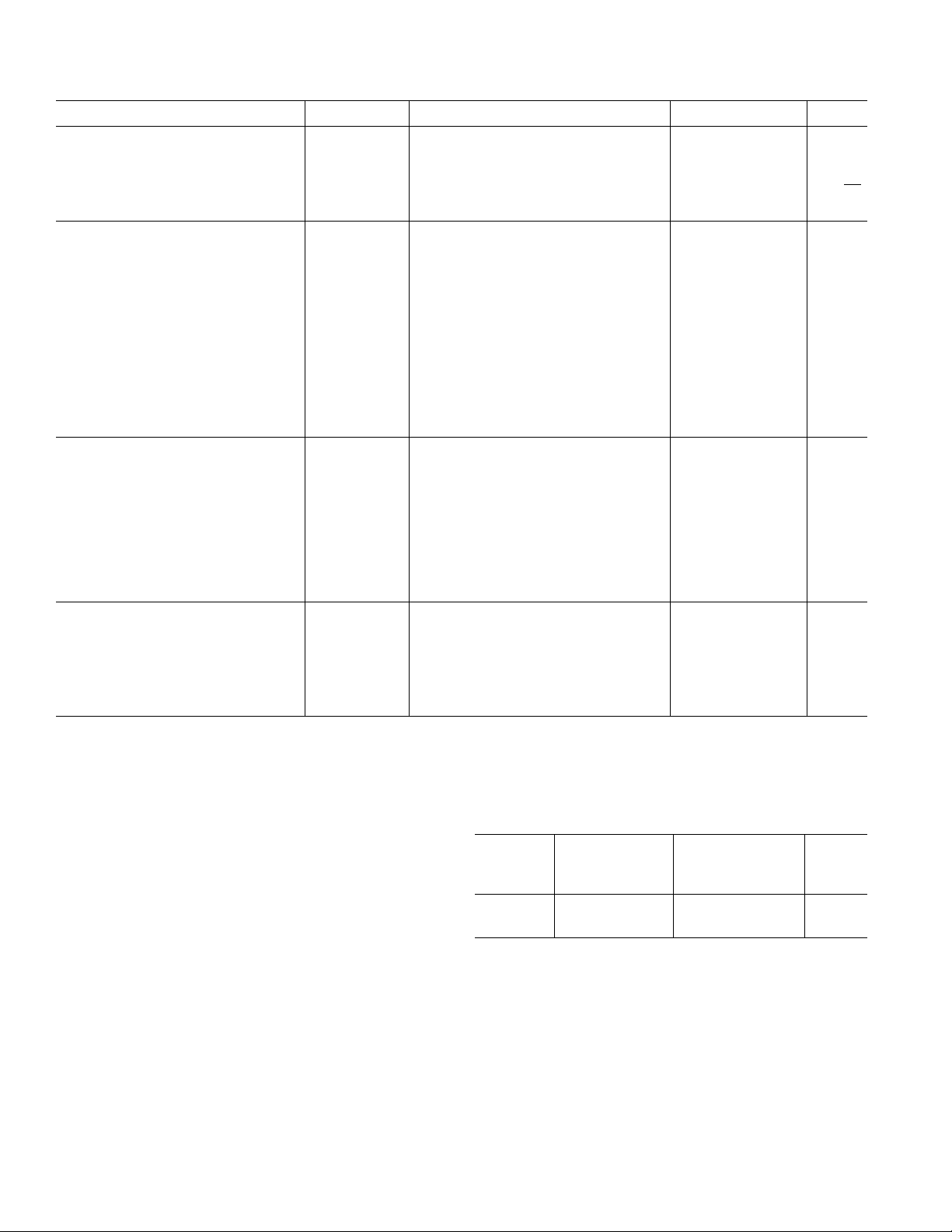

SW1 A

SW1 B

DGND

SW1 CONTROL

SW2 CONTROL

NC

*

SW2 B

SW2 A

SW4 A

SW4 B

V+

SW4 CONTROL

SW3 CONTROL

V–

SW3 B

SW3 A

NC = NO CONNECT

AGND

AGND

AGND

AGND

*

CONNECT TO ANALOG GROUND

FOR BEST NOISE ISOLATION

SW1

1

2

3

4

5

6

7

8

20

19

18

17

16

15

14

13

9

10

12

11

TOP VIEW

(Not to Scale)

O

SSM2404

SW1

SW2 SW3

SW4

a

Quad Audio Switch

SSM2404

FEATURES

“CIickless” Bilateral Audio Switching

Four SPST Switches in a 20-Pin Package

Ultralow THD+N: 0.0008% @ 1 kHz (2 V rms,

= 100 kV)

R

L

Low Charge Injection: 35 pC typ

High OFF Isolation: –100 dB typ (RL = 10 kV @ 1 kHz)

Low Crosstalk: –94 dB typ (R

= 10 kV @ 1 kHz)

L

Low ON Resistance: 28 V typ

Low Supply Current: 900 mA typ

Single or Dual Supply Operation: +11 V to +24 V or

65.5 V to 612 V

Guaranteed Break-Before-Make

TTL and CMOS Compatible Logic Inputs

Low Cost-Per-Switch

GENERAL DESCRIPTION

The SSM2404 integrates four SPST analog switches in a single

20-pin package. Developed specifically for high performance

audio applications, distortion and noise are negligible over the

full operating range of 20 Hz to 20 kHz. With very low charge

injection of 35 pC, “clickless” audio switching is possible, even

under the most demanding conditions.

Switch control is realized by conventional TTL or CMOS

logic. Guaranteed “break-before-make” operation assures that

all switches in a large system will open before any switch

reaches the ON state.

Single or dual supply operation is possible. Additional features

include –100 dB OFF isolation, –94 dB crosstalk and 28 Ω ON

resistance. Optional current-mode switching permits an

extended signal-handling range. Although optimized for large

load impedances, the SSM2404 maintains good audio

performance even under low load impedance conditions.

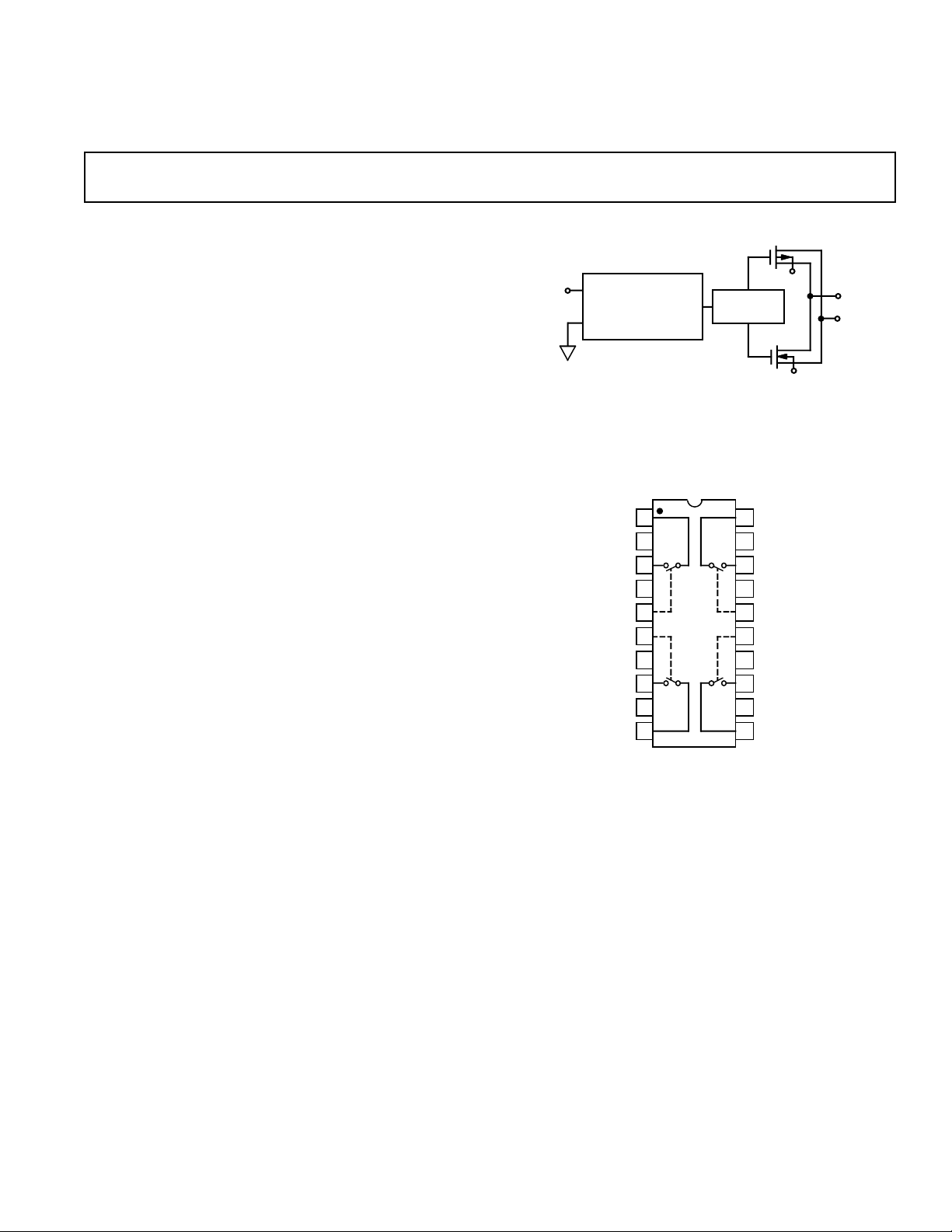

BLOCK DIAGRAM OF ONE SWITCH CHANNEL

CONTROL

DIGITAL

CONTROL

LOGIC INTERFACE

AND

BREAK-BEFORE-MAKE

CONTROL

RAMP

GENERATOR

V–

V+

PIN CONNECTIONS

Epoxy Mini-DIP (P Suffix)

and SOIC (S Suffix)

SW1 A

SW1 B

REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 Fax: 617/326-8703

(VS = 612 V, TA = +258C, unless otherwise noted.

SSM2404–SPECIFICATIONS

Parameter Symbol Conditions Min Typ Max Units

AUDIO PERFORMANCE

Total Harmonic Distortion Plus Noise THD+N @ 1 kHz, with 80 kHz Filter,

Spectral Noise Density e

Wideband Noise Density en p-p 20 Hz to 20 kHz 0.6 µV p-p

ANALOG SIGNAL SECTION

Analog Voltage Range V

Analog Current Range I

ON Resistance R

Matching RON Match IA = ±10 mA, VA = 0 V 1 %

R

ON

ON Leakage Current I

OFF Leakage Current I

Charge Injection Q 35 pC

ON-State Input Capacitance C

OFF-State Input Capacitance C

OFF Isolation I

Channel-to-Channel Crosstalk C

CONTROL SECTION

Digital Input High V

Digital Input Low V

Turn-On Time

Turn-Off Time

1

2

Break-Before-Make Time Delay t

Logic Input Current

Logic HI V

Logic LO V

POWER SUPPLY

Supply Voltage Range V

Positive Supply Current I

Negative Supply Current I

Ground Current All Channels On –2.0 –0.3 mA

NOTES

1

Turn-on time is measured from the time the logic input reaches the 50% point to the time the output reaches 50% of the final value.

2

Turn-off time is measured from the time the logic input reaches the 50% point to the time the output reaches 50% of the initial value.

Specifications subject to change without notice.

n

A

A

ON

S(ON)

S(OFF)

ON

OFF

SO(OFF)

T

INH

INL

t

ON

t

OFF

ON-tOFF

S

SY+

SY–

Typical specifications apply at TA = +258C.)

= 100 kΩ, VIN = 2 V rms 0.0008 %

R

L

20 Hz to 20 kHz 0.8 nV/√Hz

V

= 2.4 V, IA = ±2 mA ±12 V

INH

V

= 2.4 V, VA = 0 V ±10 mA

INH

IA = ±10 mA, VA = ±10 V dc 28 45 Ω

VA = ±10 V –20 0.1 +20 nA

VA = ±10 V –20 0.1 +20 nA

VA = 5 V rms 31 pF

VA = 5 V rms 17 pF

VA = 50 mV rms, f = 1 kHz, RL = 10 kΩ –100 dB

VA = 50 mV rms, f = 1 kHz, RL = 10 kΩ –94 dB

DGND = 0 V 2.4 V

DGND = 0 V 0 0.8 V

See Test Circuit 8 50 ms

See Test Circuit 5 30 ms

320ms

= 2.4 V –1000 1.3 +1000 nA

INH

= 0.8 V –1000 1.0 +1000 nA

INL

Single Supply +11 +24 V

Dual Supply ±5.5 ±12 V

All Channels On 0.9 5 mA

All Channels On –1.5 –0.6 mA

V

S

ABSOLUTE MAXIMUM RATINGS

Supply Voltage

Single Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .+27 V

Dual Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±13.5 V

Analog Input Voltage (V

Logic Input Voltage (V

) . . . . . . . . . . . . . . . . . . . . . . . . . .V

A

) . . . . . . . . . . . . . . . . . . . . . . V

INL/INH

Maximum Current Through Any Switch . . . . . . . . . . . 20 mA

Operating Temperature Range . . . . . . . . . . . . –40°C to +85°C

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Junction Temperature (T

Lead Temperature (Soldering, 60 sec) . . . . . . . . . . . . +300°C

Thermal Resistance

) . . . . . . . . . . . . . . . . . . . . +150°C

J

1

20-Pin Plastic DIP (P): θJA = 74, θJC = 32 . . . . . . . . . °C/W

20-Pin SOIC (S): θ

NOTE

1

θJA is specified for worst case mounting conditions, i.e., θJA is specified for device

in socket for P-DIP package.

= 90, θJC = 27 . . . . . . . . . . . . . . °C/W

JA

ORDERING GUIDE

Operating

Temperature Package

Model Range Package Option*

S

S

SSM2404P –40°C to +85°C 20-Pin Plastic DIP N-20

SSM2404S –40°C to +85°C 20-Pin SOIC R-20

*N = Plastic DIP, R = SOIC.

–2–

REV. B

V = 50mV

0.01

0.001

0.0001

0 ±12±8±4

SUPPLY VOLTAGE – V

THD + N – %

A (IN) RMS

f = 20Hz TO 100kHz

V

50Ω

A (IN)

R = 10kΩ AND 100kΩ

V

OFF ISOLATION = 20 LOG

A (OUT)

V

A (IN)

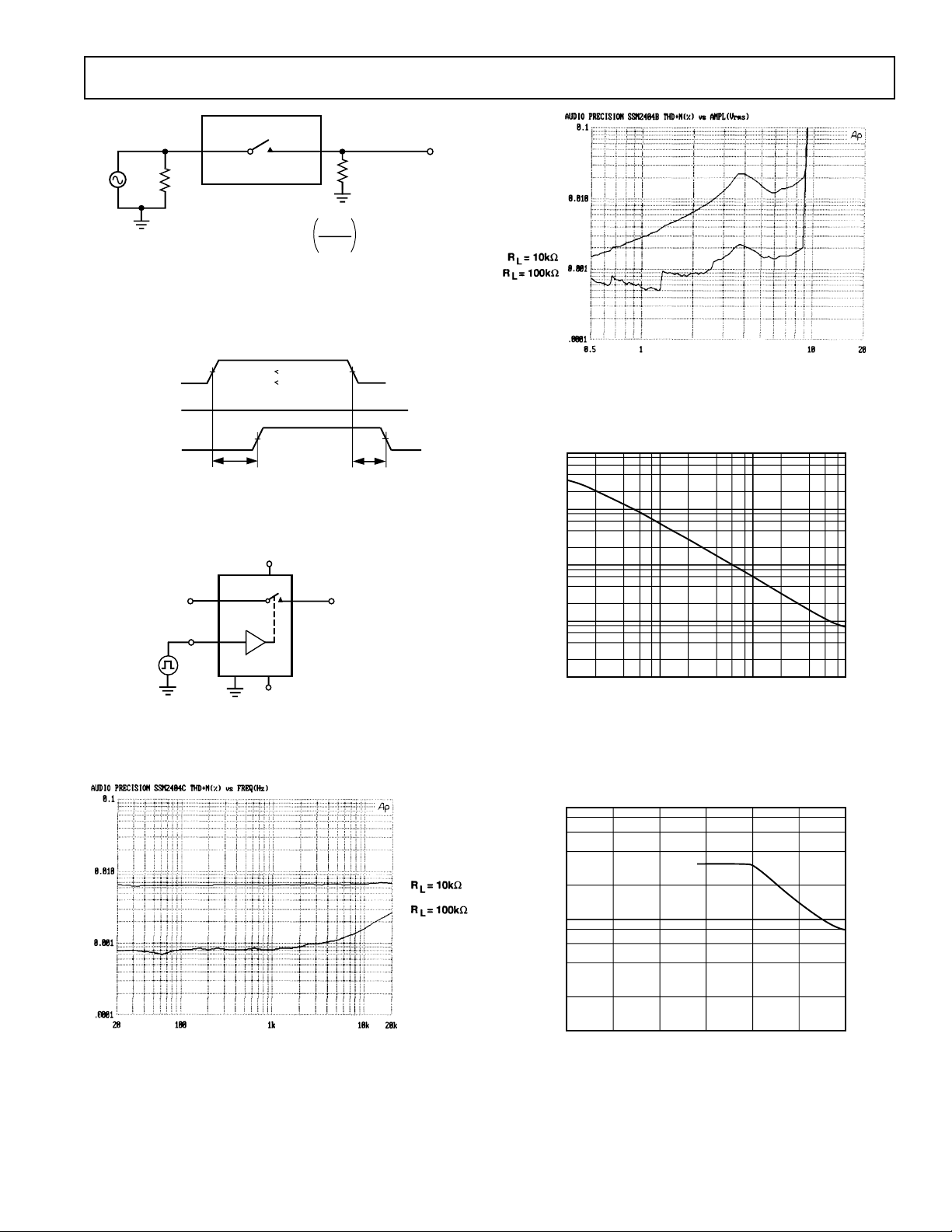

OFF Isolation Test Circuit

SSM2404

V

A (OUT)

L

LOGIC

INPUT

V

A (IN)

V

A (OUT)

V

A (IN)

CONROL

Test Circuit for tON/t

HIGH

100ns

1.4V

LOW

DC VOLTAGE

OPEN OPEN

tON/t

SWITCH

t

r

100ns

t

f

CLOSED

50%

t

ON

Timing Diagram

OFF

+12V

V+

GND

V–

–12V

Timing Specification, tON/t

OFF

1.4V

V

A (OUT)

LOW

50%

t

OFF

OFF

Switching Response, and ON/OFF Transition Photos

Figure 2. Headroom (VS = ±12 V, f = 1 kHz, with

80 kHz Filter)

1.0

0.1

0.01

THD + N – %

0.001

0.0001

100 1k 100k10k

LOAD RESISTANCE – Ω

Figure 3. THD+N vs. Load (VS = ±12 V, VA = 2 V rms,

f = 1 kHz, with 80 kHz Filter)

Figure 1. THD+N vs. Frequency (VS = ±12 V,

= 2 V rms, with 80 kHz Filter)

V

A

REV. B

Figure 4. THD+N vs. Supply Voltage (VA = 2 V rms,

f = 1 kHz, R

= 100 kΩ, with 80 kHz Filter)

L

–3–

Loading...

Loading...