Analog Devices OP282, OP482 Datasheet

Dual/Quad Low Power, High Speed

1

2

3

4

5

6

7

14

13

12

11

10

9

8

OUT A

–IN A

+IN A

V+

+IN B

–IN B

OUT B

OUT B

–IN D

+IN D

V–

+IN C

–IN C

OUT C

OP482

1

2

3

4

5

6

7

14

13

12

11

10

9

8

OUT A

–IN A

+IN A

V+

+IN B

–IN B

OUT B

OUT D

–IN D

+IN D

V–

+IN C

–IN C

OUT C

OP482

a

FEATURES

High Slew Rate: 9 V/ms

Wide Bandwidth: 4 MHz

Low Supply Current: 250 mA/Amplifier

Low Offset Voltage: 3 mV

Low Bias Current: 100 pA

Fast Settling Time

Common-Mode Range Includes V+

Unity Gain Stable

APPLICATIONS

Active Filters

Fast Amplifiers

Integrators

Supply Current Monitoring

GENERAL DESCRIPTION

The OP282/OP482 dual and quad operational amplifiers feature

excellent speed at exceptionally low supply currents. Slew rate

exceeds 7 V/µs with supply current under 250 µA per amplifier.

These unity gain stable amplifiers have a typical gain bandwidth

of 4 MHz.

The JFET input stage of the OP282/OP482 insures bias current

is typically a few picoamps and below 500 pA over the full

temperature range. Offset voltage is under 3 mV for the dual

and under 4 mV for the quad.

With a wide output swing, within 1.5 volts of each supply, low

power consumption and high slew rate, the OP282/OP482 are

ideal for battery-powered systems or power restricted applications. An input common-mode range that includes the positive

supply makes the OP282/OP482 an excellent choice for highside signal conditioning.

The OP282/OP482 are specified over the extended industrial

temperature range. Both dual and quad amplifiers are available

in plastic and ceramic DIP plus SOIC surface mount packages.

JFET Operational Amplifiers

OP282/OP482

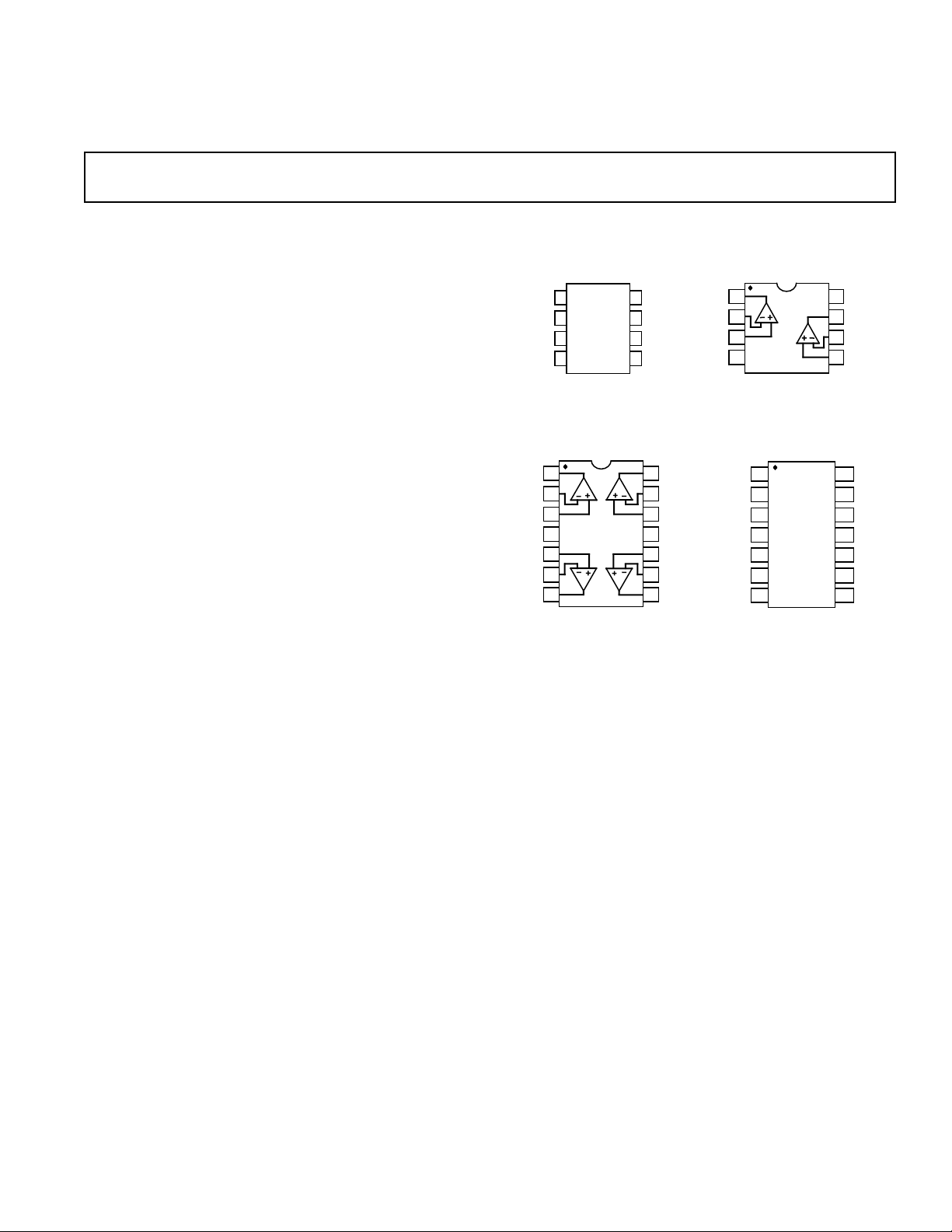

PIN CONNECTIONS

8-Lead Narrow-Body SOIC 8-Lead Epoxy DIP

(S Suffix) (P Suffix)

OUT A

–IN A

+IN A

V+

1

2

OP282

3

V–

4

8

7

6

5

OUT B

–IN B

+IN B

1

OUT A

–IN A

+IN A

V–

OP282

2

3

45

OP-482

14-Lead Epoxy DIP 14-Lead Narrow-Body SOIC

(P Suffix) (S Suffix)

8

V+

7

OUT B

6

+IN B

–IN B

REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 Fax: 617/326-8703

OP282/OP482–SPECIFICA TIONS

ELECTRICAL CHARACTERISTICS (@ V

= 615.0 V, TA = +258C unless otherwise noted)

S

Parameter Symbol Conditions Min Typ Max Units

INPUT CHARACTERISTICS

Offset Voltage V

OS

OP282 0.2 3 mV

OP282, –40 ≤ TA ≤ +85°C 4.5 mV

Offset Voltage V

OS

OP482 0.2 4 mV

OP482, –40 ≤ TA ≤ +85°C6mV

Input Bias Current I

B

VCM = 0 V 3 100 pA

VCM = 0 V, Note 1 500 pA

Input Offset Current I

OS

VCM = 0 V 1 50 pA

VCM = 0 V, Note 1 250 pA

Input Voltage Range –11 +15 V

Common-Mode Rejection CMR –11 V ≤ V

Large Signal Voltage Gain A

VO

RL = 10 kΩ 20 V/mV

≤ +15 V, –40 ≤ TA ≤ +85°C7090 dB

CM

RL = 10 kΩ, –40 ≤ TA ≤ +85°C 15 V/mV

Offset Voltage Drift ∆V

/∆T10µV/°C

OS

Bias Current Drift ∆IB/∆T 8 pA/°C

OUTPUT CHARACTERISTICS

Output Voltage Swing V

Short Circuit Limit I

O

SC

RL = 10 kΩ –13.5 ±13.9 13.5 V

Source 3 10 mA

Sink –8 –12 mA

Open-Loop Output Impedance Z

OUT

f = 1 MHz 200 Ω

POWER SUPPLY

Power Supply Rejection Ratio PSRR VS = ±4.5 V to ±18 V,

–40 ≤ TA ≤ +85°C 25 316 µV/V

Supply Current/Amplifier I

Supply Voltage Range V

SY

S

VO = 0 V, 40 ≤ TA ≤ +85°C 210 250 µA

±4.5 ±18 V

DYNAMIC PERFORMANCE

Slew Rate SR RL = 10 kΩ 79 V/µs

Full-Power Bandwidth BW

Settling Time t

S

P

1% Distortion 125 kHz

To 0.01% 1.6 µs

Gain Bandwidth Product GBP 4 MHz

Phase Margin Ø

O

55 Degrees

NOISE PERFORMANCE

Voltage Noise e

Voltage Noise Density e

Current Noise Density i

NOTE

1

The input bias and offset currents are tested at TA = TJ = +85°C. Bias and offset currents are guaranteed but not tested at –40°C.

Specifications subject to change without notice.

p-p 0.1 Hz to 10 Hz 1.3 µV p-p

n

n

n

f = 1 kHz 36 nV/√Hz

0.01 pA/√Hz

WAFER TEST LIMITS

(@ VS = 615.0 V, TA = +258C unless otherwise noted)

Parameter Symbol Conditions Limit Units

Offset Voltage V

Offset Voltage V

Input Bias Current I

Input Offset Current I

Input Voltage Range

1

OS

OS

B

OS

OP282 3 mV max

OP482 4 mV max

VCM = 0 V 100 pA max

VCM = 0 V 50 pA max

–11, +15 V min/max

Common-Mode Rejection CMRR –11 V ≤ VCM ≤ +15 V 70 dB min

Power Supply Rejection Ratio PSRR V = ±4.5 V to ±18 V 316 µV/V

Large Signal Voltage Gain A

Output Voltage Range V

Supply Current/Amplifier I

NOTES

Electrical tests and wafer probe to the limits shown. Due to variations in assembly methods and normal yield loss, yield after packaging is not guaranteed for standard

product dice. Consult factory to negotiate specifications based on dice lot qualifications through sample lot assembly and testing.

1

Guaranteed by CMR test.

Specifications subject to change without notice.

VO

O

SY

RL = 10 kΩ 20 V/mV min

RL = 10 kΩ±13.5 V min

VO = 0 V, RL = ∞ 250 µA max

–2–

REV. B

OP282/OP482

ABSOLUTE MAXIMUM RATINGS

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±18 V

Input Voltage

Differential Input Voltage

1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±18 V

1

. . . . . . . . . . . . . . . . . . . . . . . 36 V

Output Short-Circuit Duration . . . . . . . . . . . . . . . . Indefinite

Storage Temperature Range

P, S Packages . . . . . . . . . . . . . . . . . . . . . . –65°C to +150°C

Operating Temperature Range

OP282A, OP482A . . . . . . . . . . . . . . . . . . –55°C to +125°C

OP282G, OP482G . . . . . . . . . . . . . . . . . . . –40°C to +85°C

Junction Temperature Range

P, S Packages . . . . . . . . . . . . . . . . . . . . . . –65°C to +125°C

Lead Temperature Range (Soldering, 60 sec) . . . . . . +300°C

Package Type u

2

JA

u

JC

Units

8-Pin Plastic DIP (P) 103 43 °C/W

8-Pin SOIC (S) 158 43 °C/W

14-Pin Plastic DIP (P) 83 39 °C/W

14-Pin SOIC (S) 120 36 °C/W

NOTES

1

For supply voltages less than ±18 V, the absolute maximum input voltage is

equal to the supply voltage.

2

θJA is specified for the worst case conditions, i.e., θJA is specified for device in

socket for cerdip, P-DIP; θJA is specified for device soldered in circuit board for

SOIC package.

ORDERING GUIDE

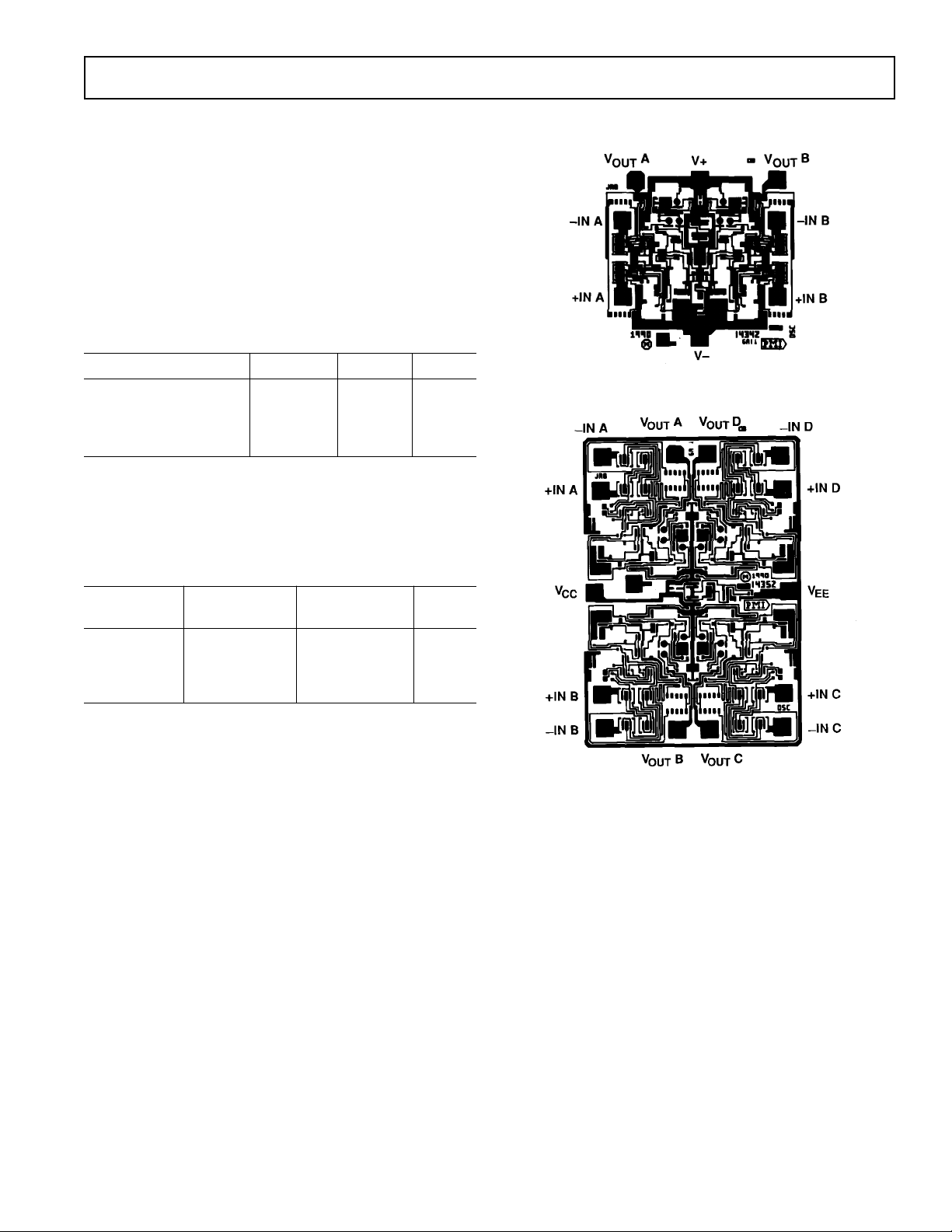

DICE CHARACTERISTICS

OP282 Die Size 0.063 3 0.060 Inch, 3,780 Sq. Mils

Temperature Package Package

Model Range Description Option

OP282GP –40°C to +85°C 8-Pin Plastic DIP N-8

OP282GS –40°C to +85°C 8-Pin SOIC SO-8

OP482GP –40°C to +85°C 14-Pin Plastic DIP N-14

OP482GS –40°C to +85°C 14-Pin SOIC SO-14

OP482 Die Size 0.070 3 0.098 Inch, 6,860 Sq. Mils

REV. B

–3–

OP282/OP482

APPLICATIONS INFORMATION

The OP282 and OP482 are single and dual JFET op amps that

have been optimized for high speed at low power. This

combination makes these amplifiers excellent choices for battery

powered or low power applications requiring above average

performance. Applications benefiting from this performance

combination include telecom, geophysical exploration, portable

medical equipment and navigational instrumentation.

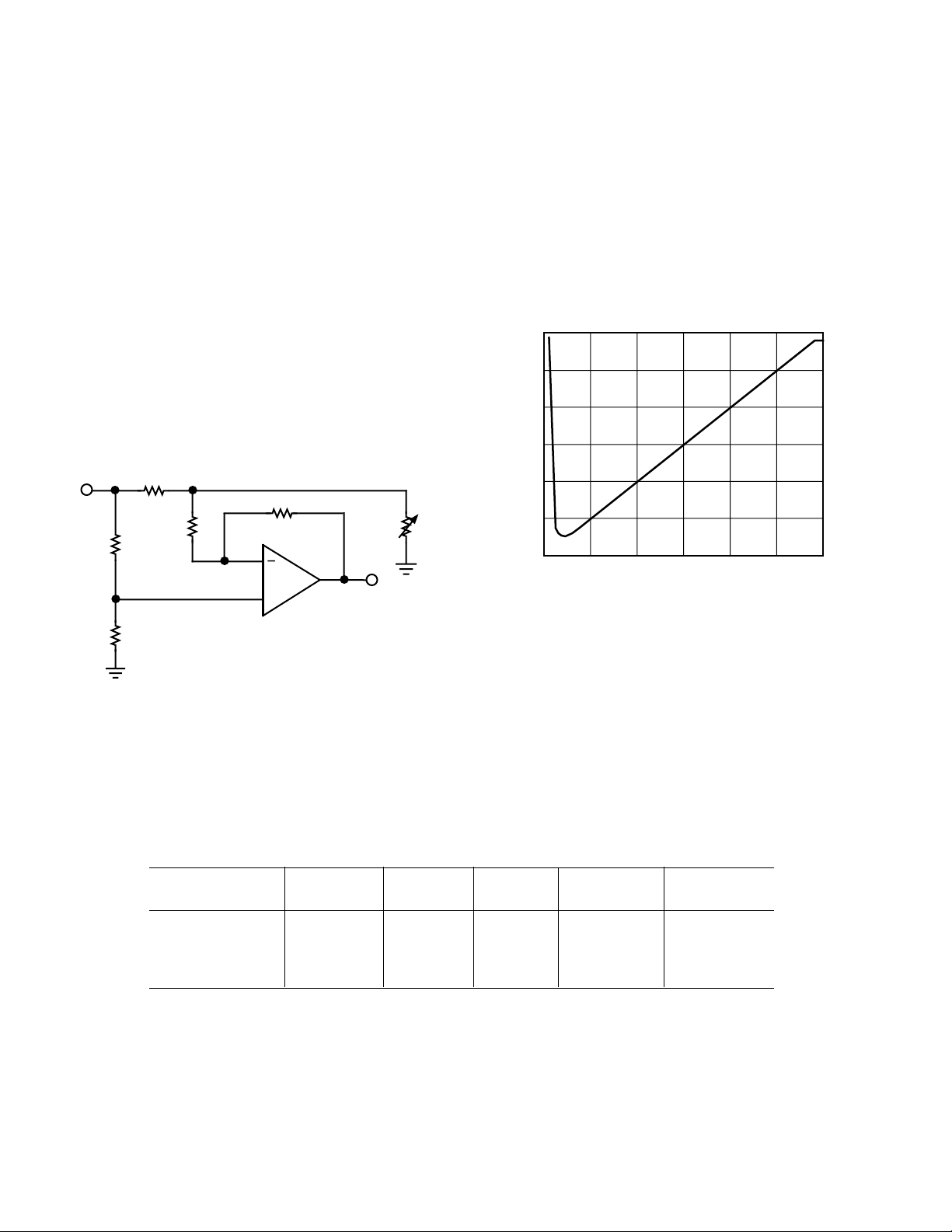

HIGH SIDE SIGNAL CONDITIONING

There are many applications that require the sensing of signals

near the positive rail. OP282s and OP482s have been tested and

guaranteed over a common-mode range (–11 V ≤ V

≤ +15 V)

CM

that includes the positive supply.

One application where this is commonly used is in the sensing of

power supply currents. This enables it to be used in current

sensing applications such as the partial circuit shown in Figure

1. In this circuit, the voltage drop across a low value resistor,

such as the 0.1 Ω shown here, is amplified and compared to 7.5

volts. The output can then be used for current limiting.

+15V

100k

100k

0.1

Ω

100k

500k

+

1/2

OP282

R

L

Figure 1. Phase Inversion

PHASE INVERSION

Most JFET-input amplifiers will invert the phase of the input

signal if either input exceeds the input common-mode range.

For the OP282 and OP482 negative signals in excess of approximately 14 volts will cause phase inversion. The cause of this

effect is saturation of the input stage leading to the forwardbiasing of a drain-gate diode. A simple fix for this in noninverting

applications is to place a resistor in series with the noninverting

input. This limits the amount of current through the forwardbiased diode and prevents the shutting down of the output

stage. For the OP282/OP482, a value of 200 kΩ has been found

to work. However, this adds a significant amount of noise.

15

10

5

IN

0

V

-5

-10

-15

-15

-10 -5

0

V

OUT

5

10

15

Figure 2. OP282 Phase Reversal

ACTIVE FILTERS

The OP282 and OP482’s wide bandwidth and high slew rates

make either an excellent choice for many filter applications.

There are many types of active filter configurations, but the four

most popular configurations are Butterworth, elliptical, Bessel,

and Chebyshev. Each type has a response that is optimized for a

given characteristic as shown in Table I.

PROGRAMMABLE STATE-VARIABLE FILTER

Table I.

Amplitude Amplitude

Type Selectivity Overshoot Phase (Pass Band) (Stop Band)

Butterworth Moderate Good Max Flat

Chebyshev Good Moderate Nonlinear Equal Ripple

Elliptical Best Poor Equal Ripple Equal Ripple

Bessel (Thompson) Poor Best Linear

–4–

REV. B

Loading...

Loading...