Ultralow Power, Rail-to-Rail Output

FEATURES

Low supply current: 4 μA/amplifier maximum

Single-supply operation: 2.7 V to 12 V

Wide input voltage range

Rail-to-rail output swing

Low offset voltage: 1.5 mV

No phase reversal

APPLICATIONS

Comparator

Battery-powered instrumentation

Safety monitoring

Remote sensors

Low voltage strain gage amplifiers

GENERAL DESCRIPTION

The OP281 and OP481 are dual and quad ultralow power

single-supply amplifiers featuring rail-to-rail outputs. Each

operates from supplies as low as 2.0 V and is specified at +3 V

and +5 V single supplies as well as ±5 V dual supplies.

Fabricated on Analog Devices’ CBCMOS process, the

OP281/OP481 feature a precision bipolar input and an output

that swings to within millivolts of the supplies, continuing to

sink or source current up to a voltage equal to the supply voltage.

Applications for these amplifiers include safety monitoring,

portable equipment, battery and power supply control, and

signal conditioning and interfacing for transducers in very low

power systems.

The output’s ability to swing rail-to-rail and not increase supply

current when the output is driven to a supply voltage enables

the OP281/OP481 to be used as comparators in very low power

systems. This is enhanced by their fast saturation recovery time.

Propagation delays are 250 μs.

The OP281/OP481 are specified over the extended industrial

temperature range (−40°C to +85°C). The OP281 dual amplifier

is available in 8-lead SOIC surface-mount and TSSOP packages.

The OP481 quad amplifier is available in narrow 14-lead SOIC

and TSSOP packages.

Operational Amplifiers

OP281/OP481

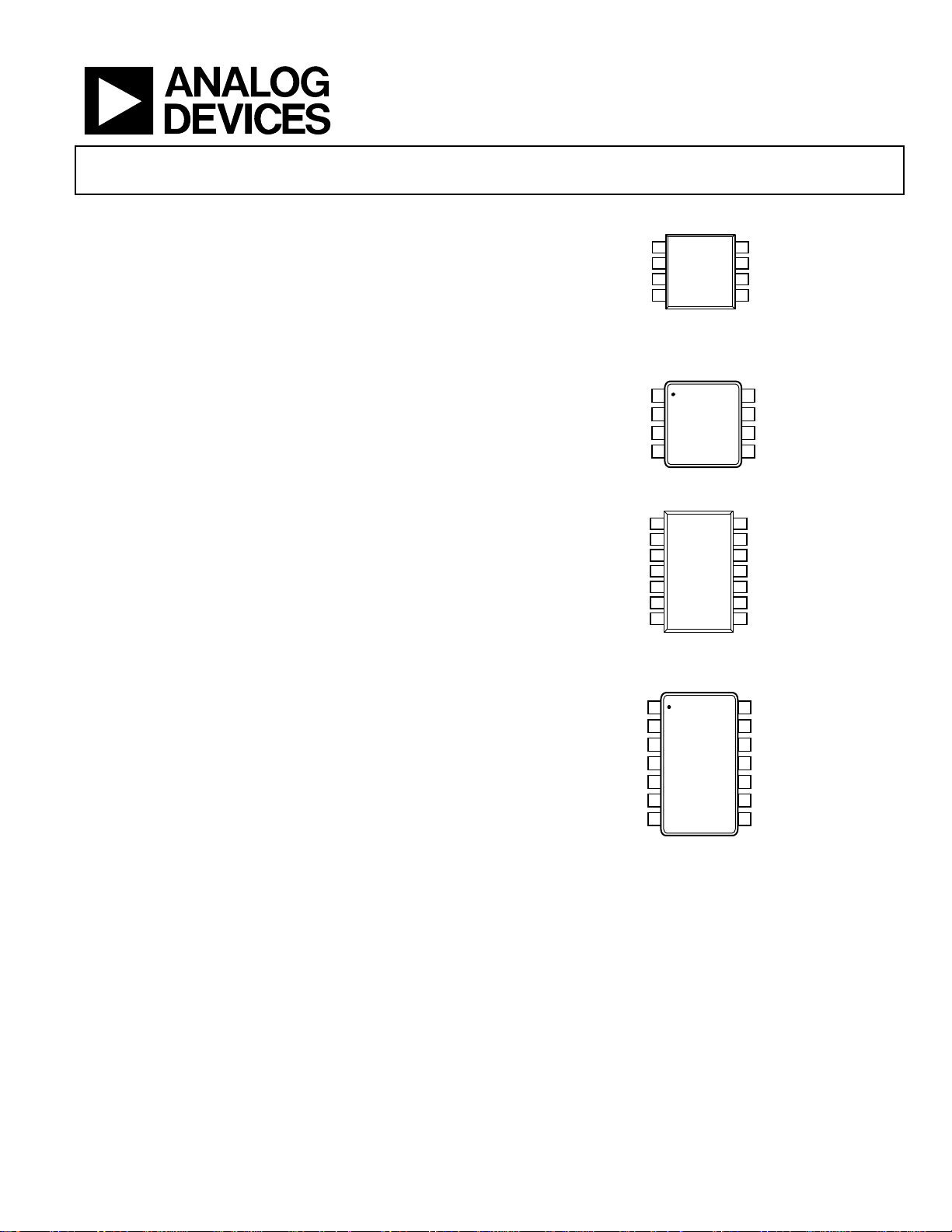

PIN CONFIGURATIONS

14

13

12

11

8

7

6

5

14

13

12

11

10

9

8

V+

OUT B

–IN B

+IN B

8

7

6

5

OUT D

–IN D

+IN D

V–

+IN C

–IN C

OUT C

OUT D

–IN D

+IN D

V–

+IN C

–IN C

OUT C

V+

OUT B

–IN B

+IN B

00291-001

00291-002

00291-003

00291-004

OUT A

1

V–

OP281

2

TOP VIEW

3

(Not to Scale)

4

–IN A

+IN A

Figure 1. 8-Lead

Narrow-Body SOIC

(R Suffix)

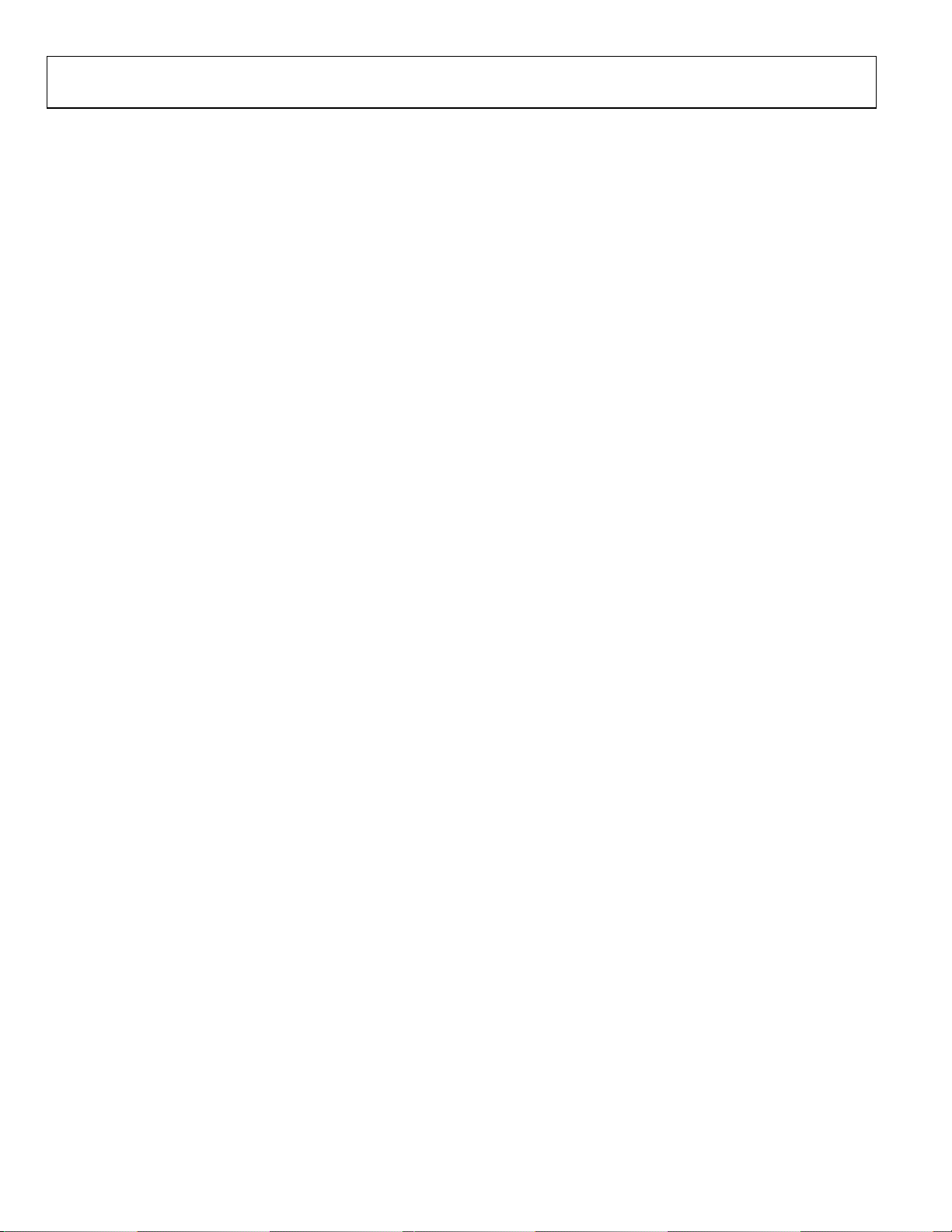

1

OUT A

OP281

2

–IN A

+IN A

V–

TOP VIEW

3

(Not to Scale)

4

Figure 2. 8-Lead TSSOP

(RU Suffix)

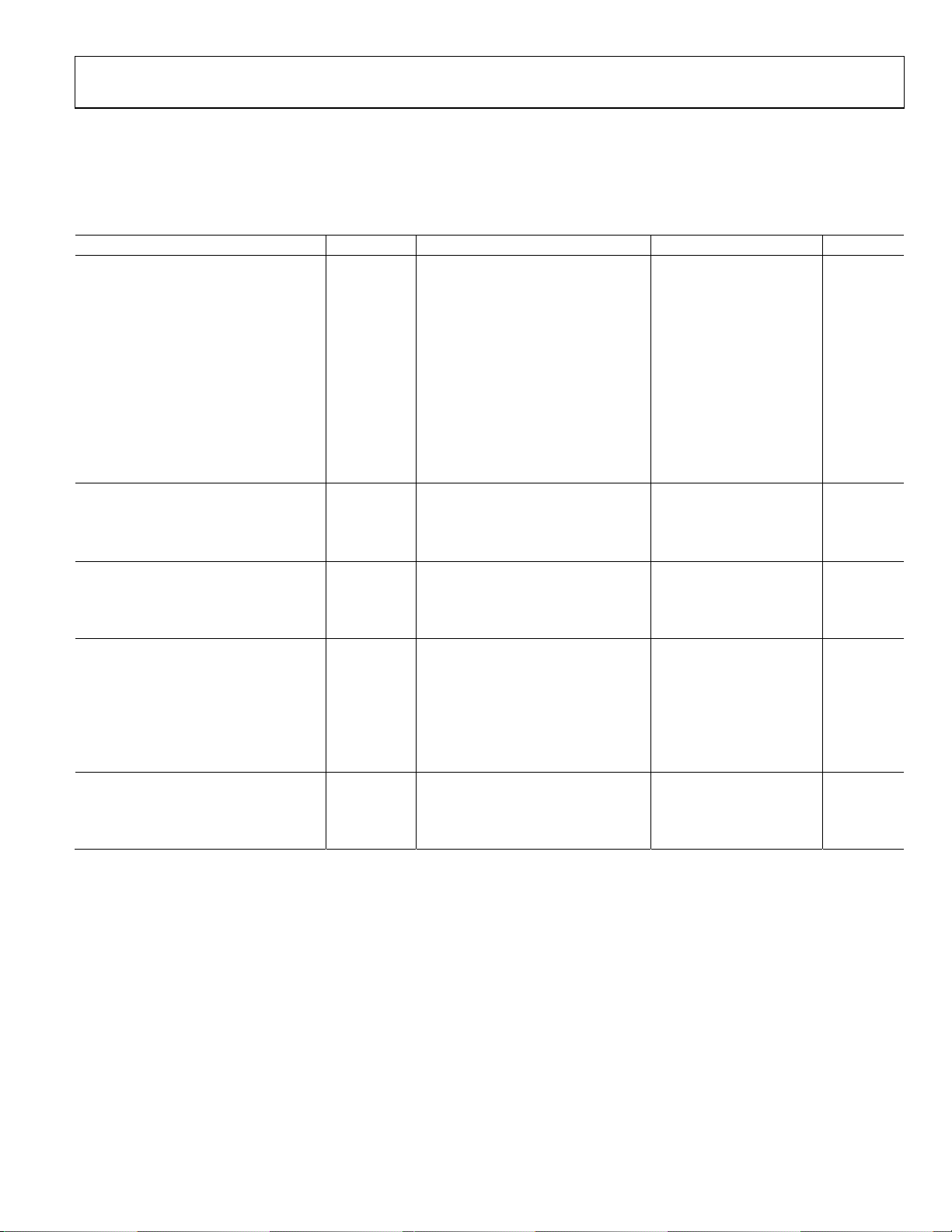

1

OUT A

2

–IN A

3

+IN A

+IN B

–IN B

OUT B

OP481

4

V+

TOP VIEW

(Not to Scale)

5 10

6 9

7 8

Figure 3. 14-Lead

Narrow-Body SOIC

(R Suffix)

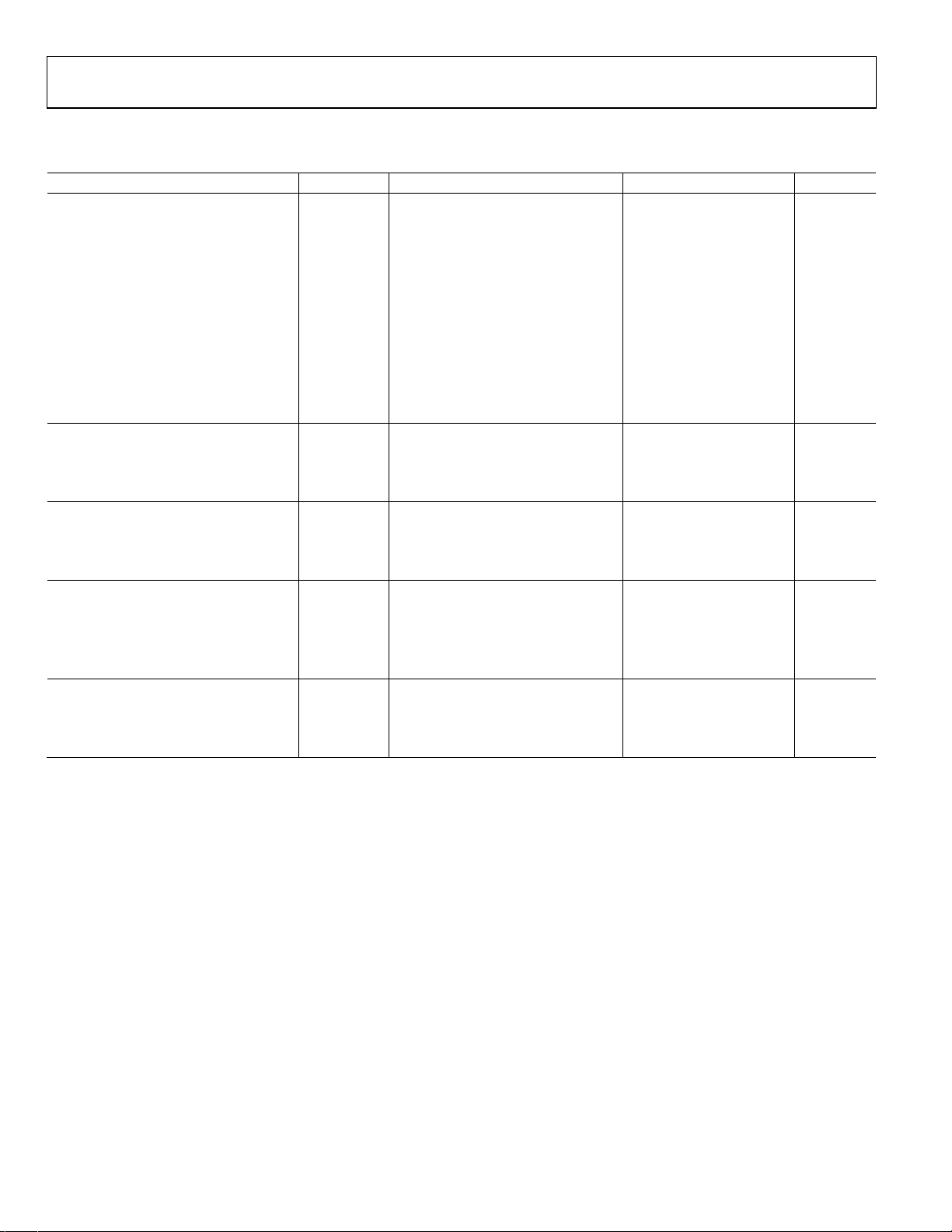

1

OUT A

2

–IN A

3

+IN A

V+

+IN B

–IN B

OUT B

OP481

TOP VIEW

4

(Not to Scale)

5

6

7

Figure 4. 14-Lead TSSOP

(RU Suffix)

Rev. D

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©1996–2008 Analog Devices, Inc. All rights reserved.

OP281/OP481

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

Pin Configurations ........................................................................... 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

Electrical Specifications ............................................................... 3

Absolute Maximum Ratings ............................................................ 6

Thermal Resistance ...................................................................... 6

ESD Caution .................................................................................. 6

Typical Performance Characteristics ............................................. 7

Applications ..................................................................................... 13

REVISION HISTORY

9/08—Rev. C to Rev. D

Changes to Figure 40 ...................................................................... 14

Changes to Low-Side Current Monitor Section ......................... 15

Changes to Figure 42 ...................................................................... 15

10/07—Rev. B to Rev. C

Updated Format .................................................................. Universal

Changes to Offset Voltage Drift Condition .................................. 3

Changes to Slew Rate Symbol ......................................................... 5

Changes to Figure 8 .......................................................................... 7

Deleted SPICE Macro-Model Section ......................................... 13

Updated Outline Dimensions ....................................................... 17

Changes to Ordering Guide .......................................................... 18

3/03—Rev. A to Rev. B

Changes to Features .......................................................................... 1

Theory of Operation .................................................................. 13

Input Overvoltage Protection ................................................... 13

Input Offset Voltage ................................................................... 13

Input Common-Mode Voltage Range ..................................... 13

Capacitive Loading ..................................................................... 14

Micropower Reference Voltage Generator .............................. 14

Window Comparator ................................................................. 14

Low-Side Current Monitor ....................................................... 15

Low Voltage Half-Wave and Full-Wave Rectifiers ................. 15

Battery-Powered Telephone Headset Amplifier ..................... 15

Outline Dimensions ....................................................................... 17

Ordering Guide .......................................................................... 18

2/03—Rev. 0 to Rev. A

Updated Format .................................................................. Universal

Deleted OP181 .................................................................... Universal

Updated Package Options ................................................. Universal

Deleted OP181 Pin Configurations ................................................ 1

Deleted Epoxy DIP Pin Configurations ......................................... 1

Changes to Absolute Maximum Ratings ........................................ 5

Changes to Ordering Guide ............................................................. 5

Changes to Input Offset Voltage ................................................... 10

Deleted Former Figure 33 ............................................................. 10

Deleted Overdrive Recovery Time Section ................................. 11

Deleted Former Figure 36 ............................................................. 11

Deleted 8-Lead and 14-Lead Plastic DIP (N-8 and N-14)

Outline Dimensions ....................................................................... 14

Updated Outline Dimensions ....................................................... 14

Rev. D | Page 2 of 20

OP281/OP481

SPECIFICATIONS

ELECTRICAL SPECIFICATIONS

VS = 3.0 V, VCM = 1.5 V, TA = 25°C, unless otherwise noted.

Table 1.

Parameter Symbol Condition Min Typ Max Unit

INPUT CHARACTERISTICS

Offset Voltage

−40°C ≤ TA ≤ +85°C 2.5 mV

Input Bias Current IB −40°C ≤ TA ≤ +85°C 3 10 nA

Input Offset Current IOS −40°C ≤ TA ≤ +85°C 0.1 7 nA

Input Voltage Range 0 2 V

Common-Mode Rejection Ratio CMRR VCM = 0 V to 2.0 V, −40°C ≤ TA ≤ +85°C 65 95 dB

Large-Signal Voltage Gain A

−40°C ≤ TA ≤ +85°C 2 V/mV

Offset Voltage Drift ΔVOS/∆T −40°C to +85°C 10 μV/°C

Bias Current Drift ΔIB/ΔT 20 pA/°C

Offset Current Drift ΔIOS/ΔT 2 pA/°C

OUTPUT CHARACTERISTICS

Output Voltage High VOH RL = 100 kΩ to GND, −40°C ≤ TA ≤ +85°C 2.925 2.96 V

Output Voltage Low VOL RL = 100 kΩ to V+, −40°C ≤ TA ≤ +85°C 25 75 mV

Short-Circuit Limit ISC ±1.1 mA

POWER SUPPLY

Power Supply Rejection Ratio PSRR VS = 2.7 V to 12 V, −40°C ≤ TA ≤ +85°C 76 95 dB

Supply Current/Amplifier ISY VO = 0 V 3 4 μA

−40°C ≤ TA ≤ +85°C 5 μA

DYNAMIC PERFORMANCE

Slew Rate SR RL = 100 kΩ, CL = 50 pF 25 V/ms

Turn-On Time AV = 1, VO = 1 V 40 μs

A

Saturation Recovery Time 65 μs

Gain Bandwidth Product GBP 95 kHz

Phase Margin φM 70 Degrees

NOISE PERFORMANCE

Voltage Noise en p-p 0.1 Hz to 10 Hz 10 μV p-p

Voltage Noise Density en f = 1 kHz 75 nV/√Hz

Current Noise Density in <1 pA/√Hz

1

VOS is tested under a no load condition.

1

V

1.5 mV

OS

R

VO

= 1 MΩ, VO = 0.3 V to 2.7 V 5 13 V/mV

L

= 20, VO = 1 V 50 μs

V

Rev. D | Page 3 of 20

OP281/OP481

VS = 5.0 V, VCM = 2.5 V, TA = 25°C, unless otherwise noted.

Table 2.

Parameter Symbol Condition Min Typ Max Unit

INPUT CHARACTERISTICS

Offset Voltage

−40°C ≤ TA ≤ +85°C 2.5 mV

Input Bias Current IB −40°C ≤ TA ≤ +85°C 3 10 nA

Input Offset Current IOS −40°C ≤ TA ≤ +85°C 0.1 7 nA

Input Voltage Range 0 4 V

Common-Mode Rejection Ratio CMRR VCM = 0 V to 4.0 V, −40°C ≤ TA ≤ +85°C 65 90 dB

Large-Signal Voltage Gain AVO RL = 1 MΩ, VO = 0.5 V to 4.5 V 5 15 V/mV

−40°C ≤ TA ≤ +85°C 2 V/mV

Offset Voltage Drift ΔVOS/ΔT −40°C to +85°C 10 μV/°C

Bias Current Drift ΔIB/ΔT 20 pA/°C

Offset Current Drift ΔIOS/ΔT 2 pA/°C

OUTPUT CHARACTERISTICS

Output Voltage High VOH RL = 100 kΩ to GND, −40°C ≤ TA ≤ +85°C 4.925 4.96 V

Output Voltage Low VOL RL = 100 kΩ to V+, −40°C ≤ TA ≤ +85°C 25 75 mV

Short-Circuit Limit ISC ±3.5 mA

POWER SUPPLY

Power Supply Rejection Ratio PSRR VS = 2.7 V to 12 V, −40°C ≤ TA ≤ +85°C 76 95 dB

Supply Current/Amplifier ISY VO = 0 V 3.2 4 μA

−40°C ≤ TA ≤ +85°C 5 μA

DYNAMIC PERFORMANCE

Slew Rate SR RL = 100 kΩ, CL = 50 pF 27 V/ms

Saturation Recovery Time 120 μs

Gain Bandwidth Product GBP 100 kHz

Phase Margin φM 74 Degrees

NOISE PERFORMANCE

Voltage Noise en p-p 0.1 Hz to 10 Hz 10 μV p-p

Voltage Noise Density en f = 1 kHz 75 nV/√Hz

Current Noise Density in <1 pA/√Hz

1

VOS is tested under a no load condition.

1

V

0.1 1.5 mV

OS

Rev. D | Page 4 of 20

OP281/OP481

VS = ±5.0 V, TA = +25°C, unless otherwise noted.

Table 3.

Parameter Symbol Condition Min Typ Max Unit

INPUT CHARACTERISTICS

Offset Voltage

–40°C ≤ TA ≤ +85°C 2.5 mV

Input Bias Current IB –40°C ≤ TA ≤ +85°C 3 10 nA

Input Offset Current IOS –40°C ≤ TA ≤ +85°C 0.1 7 nA

Input Voltage Range –5 +4 V

Common-Mode Rejection CMRR VCM = –5.0 V to +4.0 V, –40°C ≤ TA ≤ +85°C 65 95 dB

Large-Signal Voltage Gain AVO RL = 1 MΩ, VO = ±4.0 V, 5 13 V/mV

–40°C ≤ TA ≤ +85°C 2 V/mV

Offset Voltage Drift ΔVOS/ΔT –40°C to +85°C 10 μV/°C

Bias Current Drift ΔIB/ΔT 20 pA/°C

Offset Current Drift ΔIOS/ΔT 2 pA/°C

OUTPUT CHARACTERISTICS

Output Voltage Swing VO RL = 100 kΩ to GND, –40°C ≤ TA ≤ +85°C ±4.925 ±4.98 V

Short-Circuit Limit ISC 12 mA

POWER SUPPLY

Power Supply Rejection Ratio PSRR VS = ±1.35 V to ±6 V, –40°C ≤ TA ≤ +85°C 76 95 dB

Supply Current/Amplifier ISY VO = 0 V 3.3 5 μA

–40°C ≤ TA ≤ +85°C 6 μA

DYNAMIC PERFORMANCE

Slew Rate SR RL = 100 kΩ, CL = 50 pF 28 V/ms

Gain Bandwidth Product GBP 105 kHz

Phase Margin φM 75 Degrees

NOISE PERFORMANCE

Voltage Noise en p-p 0.1 Hz to 10 Hz 10 μV p-p

Voltage Noise Density en f = 1 kHz 85 nV/√Hz

f = 10 kHz 75 nV/√Hz

Current Noise Density in <1 pA/√Hz

1

VOS is tested under a no load condition.

1

V

0.1 1.5 mV

OS

Rev. D | Page 5 of 20

OP281/OP481

ABSOLUTE MAXIMUM RATINGS

Table 4.

Parameter Rating

Supply Voltage 16 V

Input Voltage GND to VS + 10 V

Differential Input Voltage ±3.5 V

Output Short-Circuit Duration to GND Indefinite

Storage Temperature Range −65°C to +150°C

Operating Temperature Range −40°C to +85°C

Junction Temperature Range −65°C to +150°C

Lead Temperature Range (Soldering, 60 sec) 300°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL RESISTANCE

Table 5. Thermal Resistance

Package Type θ

8-Lead SOIC (R Suffix) 158 43 °C/W

8-Lead TSSOP (RU Suffix) 240 43 °C/W

14-Lead SOIC (R Suffix) 120 36 °C/W

14-Lead TSSOP (RU Suffix) 240 43 °C/W

1

θJA is specified for the worst-case conditions, that is, θJA is specified for device

soldered in circuit board for TSSOP and SOIC packages.

1

θ

JA

JC

Unit

ESD CAUTION

Rev. D | Page 6 of 20

Loading...

Loading...