Analog Devices OP471 a Datasheet

14

13

12

11

10

9

8

1

2

3

4

5

6

7

OUT A

–IN A

+IN A

V+

+IN B

–IN B

OUT B

OUT D

–IN D

+IN D

V–

+IN C

–IN C

OUT C

OP471

High Speed, Low Noise Quad

–

a

FEATURES

Excellent Speed: 8 V/s Typ

Low Noise: 11 nV/÷

Unity-Gain Stable

High Gain Bandwidth: 6.5 MHz Typ

Low Input Offset Voltage: 0.8 mV Max

Low Offset Voltage Drift: 4 V/C Max

High Gain: 500 V/mV Min

Outstanding CMR: 105 dB Min

Industry Standard Quad Pinouts

GENERAL DESCRIPTION

The OP471 is a monolithic quad op amp featuring low noise,

11 nV/÷Hz Max @ 1 kHz, excellent speed, 8 V/ms typical, a

gain bandwidth of 6.5 MHz, and unity-gain stability.

The OP471 has an input offset voltage under 0.8 mV and an

input offset voltage drift below 4 mV/∞C, guaranteed over the full

military temperature range. Open-loop gain of the OP471 is over

500,000 into a 10 kW load ensuring outstanding gain accuracy

and linearity. The input bias current is under 25 nA limiting

errors due to signal source resistance. The OP471’s CMR of

over 105 dB and PSRR of under 5.6 mV/V significantly reduce

errors caused by ground noise and power supply fluctuations.

The OP471 offers excellent amplifier matching which is important

for applications such as multiple gain blocks, low-noise instrumentation amplifiers, quad buffers and low-noise active filters.

The OP471 conforms to the industry standard 14-lead DIP

pinout. It is pin-compatible with the LM148/LM149, HA4741,

RM4156, MC33074, TL084 and TL074 quad op amps and can

be used to upgrade systems using these devices.

For applications requiring even lower voltage noise the OP470

with a voltage density of 5 nV/÷Hz Max @ 1 kHz is recommended.

Hz @ 1 kHz Max

Operational Amplifier

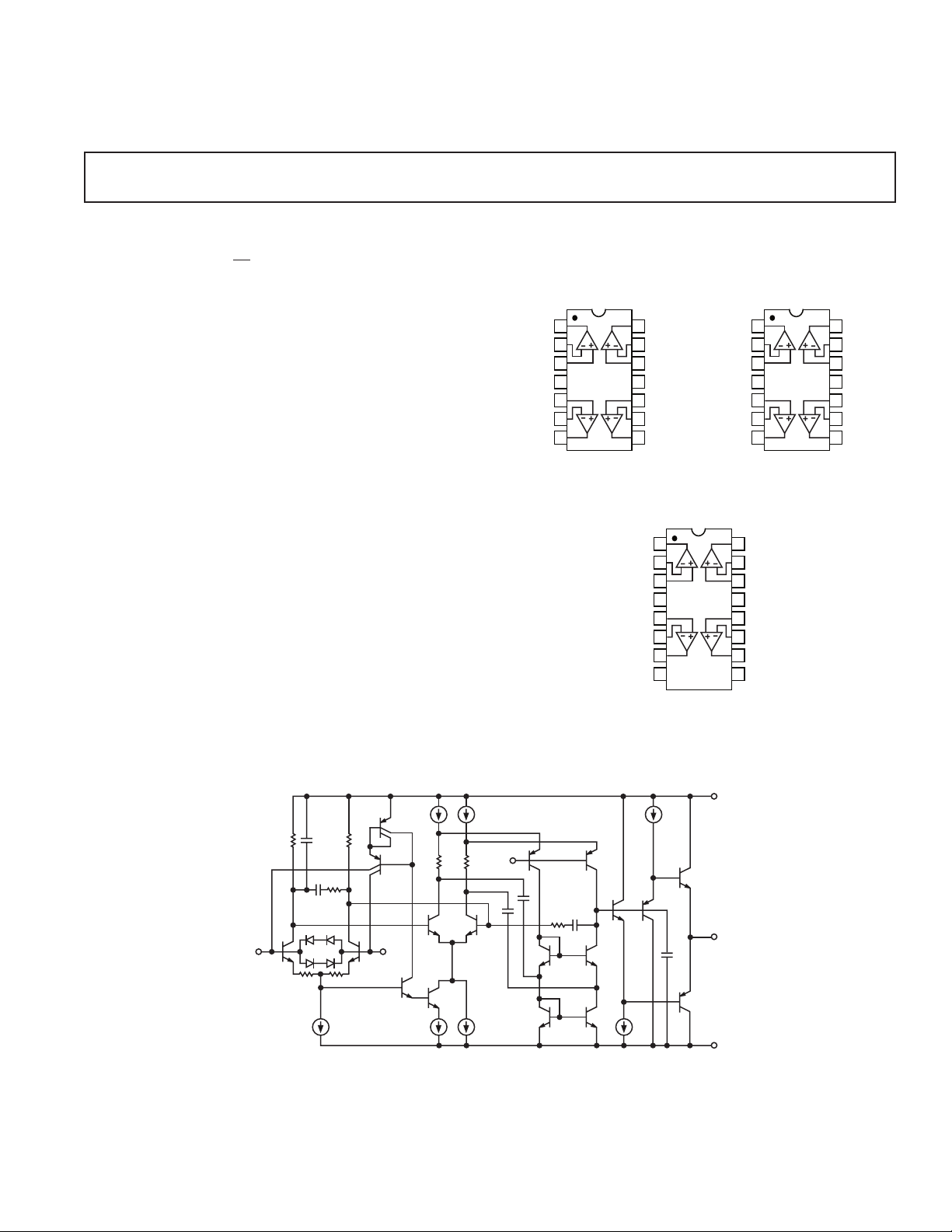

PIN CONFIGURATIONS

14-Lead

Hermetic Dip

(Y-Suffix)

OUT A OUT D

–IN A –IN D

+IN A +IN D

+IN B +IN C

–IN B –IN C

OUT B OUT C

NC NC

OUT A

–IN A

+IN A

V+

+IN B

–IN B

OUT B

16-Lead SOIC

(S-Suffix)

1

2

3

4

V+ V–

OP471

5

6

7

8

NC = NO CONNECT

16

15

14

13

12

11

10

9

V+

OP471

14-Lead

Plastic Dip

(P-Suffix)

1

2

3

4

OP471

5

6

7

14

13

12

11

10

9

8

OUT D

–IN D

+IN D

V–

+IN C

–IN C

OUT C

BIAS

IN

+IN

OUT

V–

Figure 1. Simplified Schematic

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2002

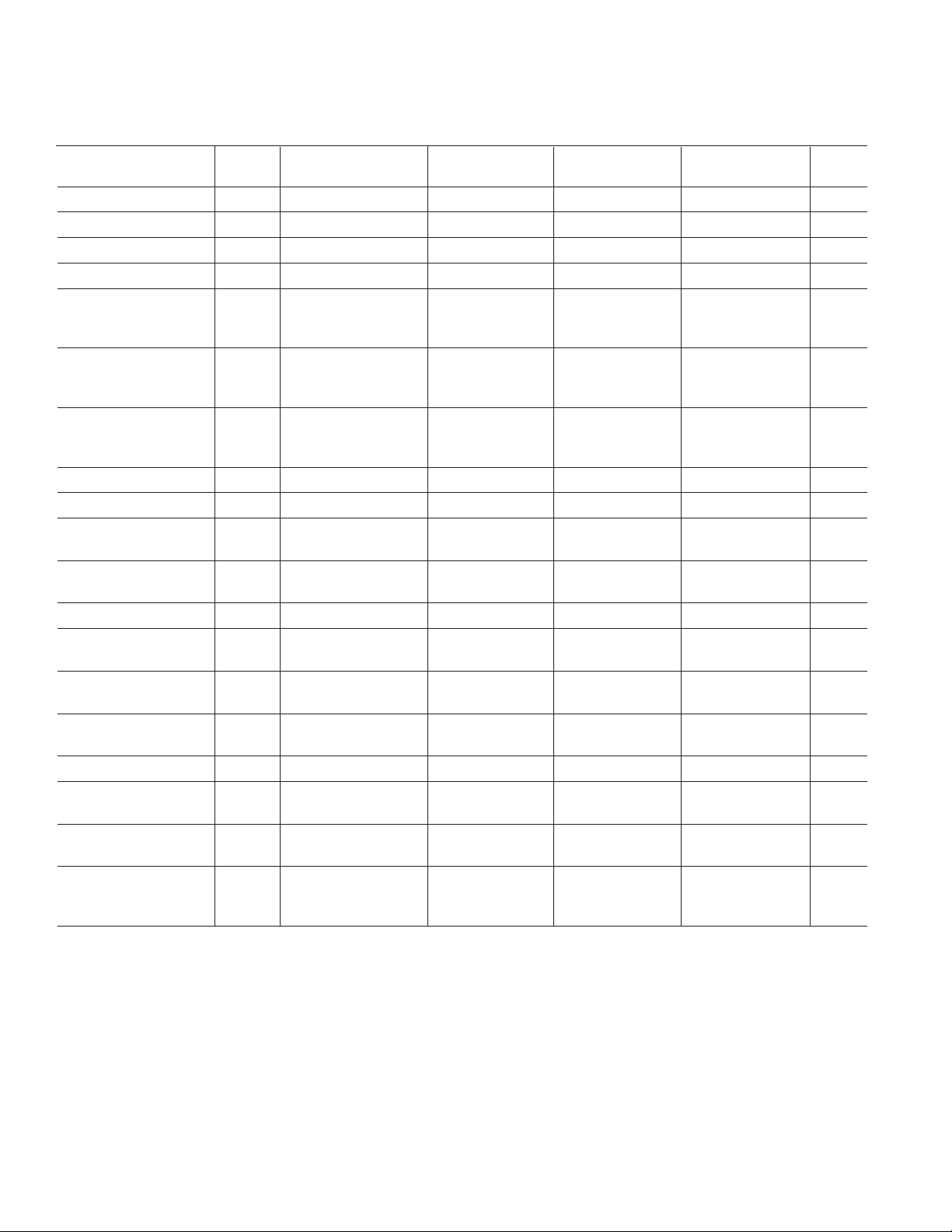

OP471–SPECIFICATIONS

ELECTRICAL CHARACTERISTICS

(@ VS = 15 V, TA = 25C, unless otherwise noted.)

OP471E OP471F OP471G

Parameter Symbol Conditions Min Typ Max Min Typ Max Min Typ Max Unit

Input Offset Voltage V

Input Offset Current I

Input Bias Current I

Input Noise Voltage

Input Noise e

Voltage Density

1

2

OS

OS

B

VCM = 0 V 4 10 7 20 12 30 nA

VCM = 0 V 7 25 15 50 25 60 nA

en p-p 0.1 Hz to 10 Hz 250 500 250 500 250 500 nV p–p

n

fO = 10 Hz 9 16 9 16 9 16 nV/÷Hz

fO = 100 Hz 7 12 7 12 7 12 nV/÷Hz

0.25 0.8 0.5 1.5 1.0 1.8 mV

fO = 1 kHz 6.5 11 6.5 11 6.5 11 nV/÷Hz

Input Noise i

n

Current Density f

fO = 10 Hz 1.7 1.7 1.7 pA÷Hz

= 100 Hz 0.7 0.7 0 7 pA÷Hz

O

fO = 1 kHz 0.4 0.4 0.4 pA÷Hz

Large-Signal A

VO

Voltage Gain R

V = ± 10 V

= 10 kW 500 700 300 500 300 500 V/mV

L

RL = 2 kW 350 550 175 275 175 275 V/mV

Input Voltage Range3IVR ± 11 ± 12 ± 11 ± 12 ± 11 ± 12 V

Output Voltage Swing V

O

Common-Mode CMR V

RL ≥ 2 kW±12 ± 13 ± 12 ± 13 ± 12 ± 13 V

= ± 11 V 105 120 95 115 95 115 dB

CM

Rejection

Power Supply PSRR V

= 4.5 V to 18 V 1 5.6 5.6 17.8 5.6 17.8 mV/V

S

Rejection Ratio

Slew Rate SR 6.5 8 6.5 8 6.5 8 V/ms

Supply Current I

SY

No Load 9.2 11 9.2 11 9.2 11 mA

(All Amplifiers)

Gain Bandwidth GBW Av = 10 6.5 6.5 6.5 MHz

Product

Channel Separation

1

CS VO = 20 V p-p 125 150 125 150 125 150 dB

fO = 10 Hz

Input Capacitance C

Input Resistance R

IN

IN

2.6 2.6 2.6 pF

1.1 1.1 1.1 MW

Differential-Mode

Input Resistance R

INCM

11 11 11 GW

Common-Mode

Settling Time t

S

AV = 1

To 0.1% 4.5 4.5 4.5 ms

To 0.01 % 7.5 7.5 7.5 ms

NOTES

1

Guaranteed but not 100% tested.

2

Sample tested.

3

Guaranteed by CMR test.

–2–

REV. A

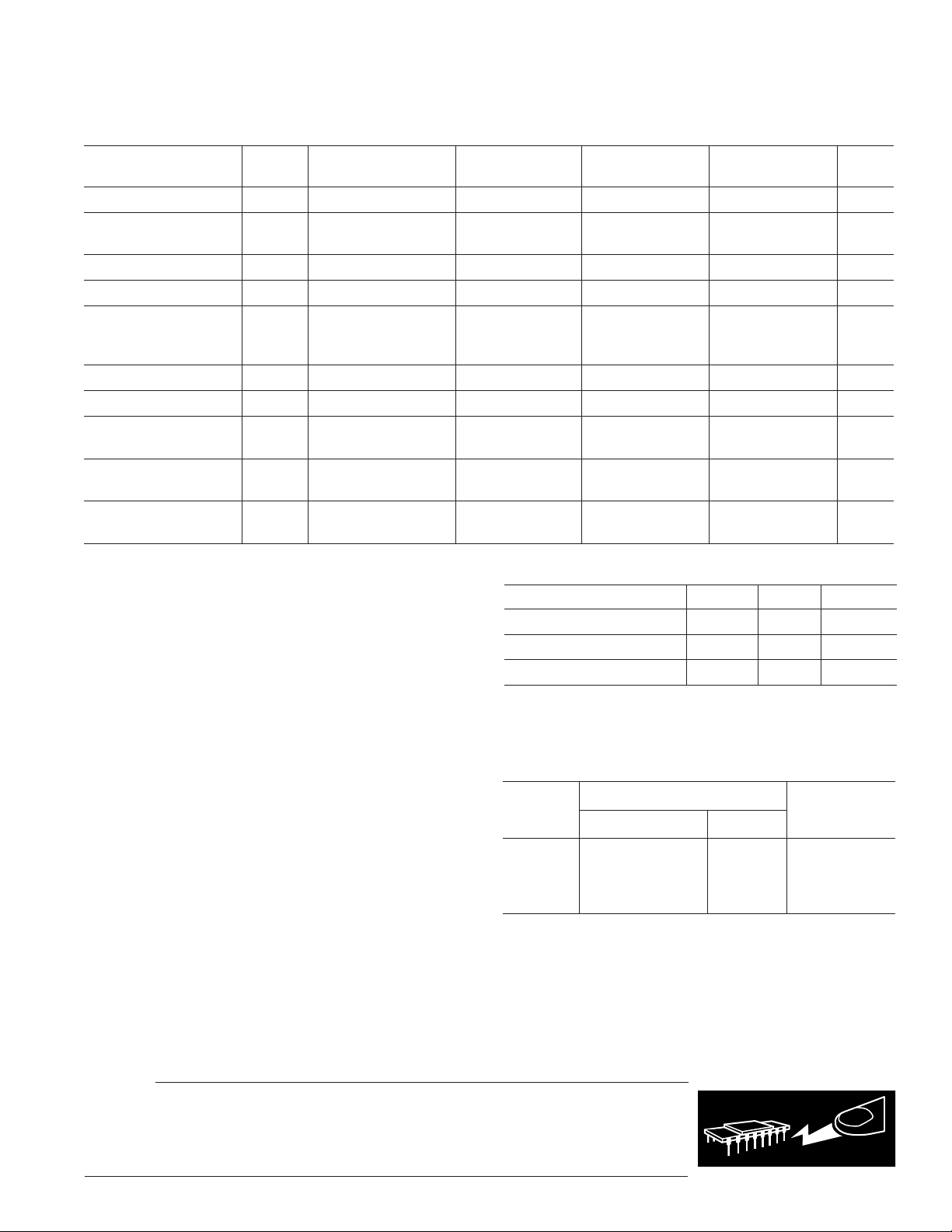

OP471

WARNING!

ESD SENSITIVE DEVICE

(Vs = ±15 V, –25C £ TA £ 85C for OP471E/F, –40C £ TA £ 85 for OP471G,

ELECTRICAL CHARACTERISTICS

Parameter Symbol Conditions Min Typ Max Min Typ Max Min Typ Max Unit

Input Offset Voltage V

Average Input TCV

Offset Voltage Drift

Input Offset Current los VCM = 0 V 5 20 8 40 20 50 nA

Input Bias Current I

Large-Signal V

Voltage Gain Avo R

Input Voltage Range* IVR ± 11 ± 12 ± 11 ± 12 ± 11 ± 12 V

Output Voltage Swing V

Common-Mode CMR V

Rejection

Power Supply PSRR V

Rejection Ratio

Supply Current

(All Amplifiers) I

*Guaranteed by CMR test.

ABSOLUTE MAXIMUM RATINGS

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ± 18 V

Differential Input Voltage

Differential Input Current

Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . Supply Voltage

Output Short-Circuit Duration . . . . . . . . . . . . . . . Continuous

Storage Temperature Range

P, Y-Package . . . . . . . . . . . . . . . . . . . . . . –65∞C to +150∞C

Lead Temperature Range (Soldering, 60 sec) . . . . . . . . 300∞C

Junction Temperature (T

Operating Temperature Range

OP471E, OP471F . . . . . . . . . . . . . . . . . . . –25∞C to +85∞C

OP471G . . . . . . . . . . . . . . . . . . . . . . . . . . . –40∞C to +85∞C

NOTES

1

Absolute Maximum Ratings apply to packaged parts, unless otherwise noted.

2

The OP471’s inputs are protected by back-to-back diodes. Current limiting

resistors are not used in order to achieve low noise performance. If differential

voltage exceeds ± 1.0 V, the input current should be limited to ± 25 mA.

OS

OS

B

VCM = 0 V 13 50 2570 4075 nA

= ± 10 V

O

= 10 kW 375 600 200 400 200 400 V/mV

L

RL = 2 kW 250 400 125 200 125 200

O

SY

2

. . . . . . . . . . . . . . . . . . . . . . ± 1.0 V

2

. . . . . . . . . . . . . . . . . . . . ± 25 mW

) . . . . . . . . . . . . . –65∞C to +150∞C

i

RL ≥ 2 kW±12 ± 13 ± 12 ± 13 ± 12 ± 13 V

CM

= ± 4.5 V to ± 18 V 3.2 10 18 31.6 18 31.6 mV/V

S

No Load 9.3 11 9.3 11 9.3 11 mA

1

unless otherwise noted.)

OP471E OP471F OP471G

0.3 1.1 0.6 2.0 1.2 2.5 mV

14 27 4 mV/∞C

= ± 11 V 100 115 90 110 90 110 dB

Package Type JA*

JC

Unit

14-Lead Hermetic DIP(Y) 94 10 ∞C/W

14-Lead Plastic DIP(P) 76 33 ∞C/W

16-Lead SOIC (S) 88 23 ∞C/W

*

is specified for worst-case mounting conditions, i.e., JA is specified for device

JA

in socket for TO, CERDIP, PDIP packages; JA is specified for device soldered to

printed circuit board for SO packages.

ORDERING GUIDE

TA = 25∞C Package Options Operating

V

MAX Temperature

OS

(mV) 14-Lead CERDIP Plastic Range

800 OP471EY IND

1,500 OP471FY* IND

1,800 OP471GP XIND

1,800 OP471GS XIND

*Not for new design. Obsolete April 2002.

For military processed devices, please refer to the standard

microcircuit drawing (SMD) available at

www.dscc.dla.mil/programs/milspec/default.asp

5962-88565022A - OP471ARCMDA

5962-88565023A - OP471ATCMDA

5962-8856502CA - OP471AYMDA

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the OP471 features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions

are recommended to avoid performance degradation or loss of functionality.

REV. A

–3–

OP471

k

k

100

40

30

20

10

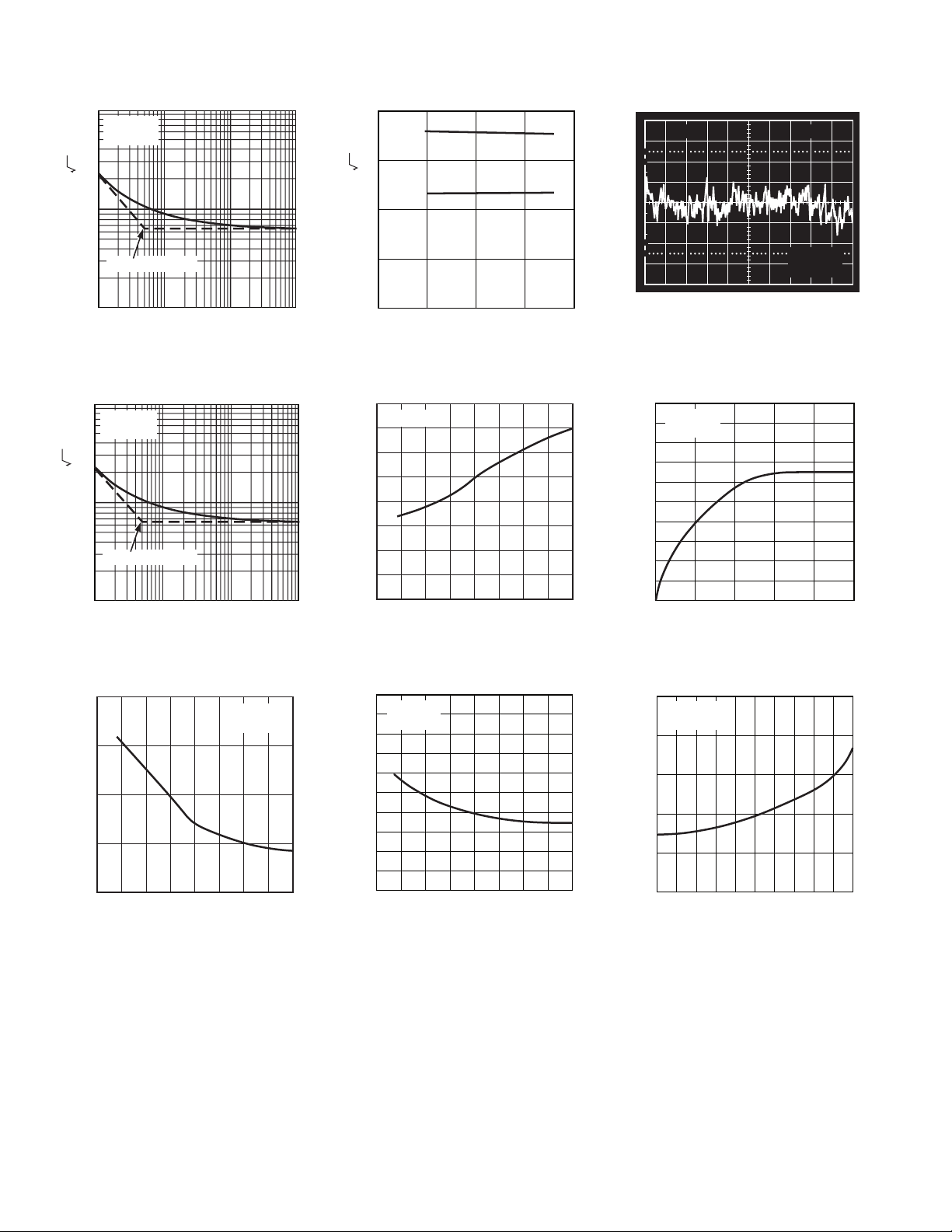

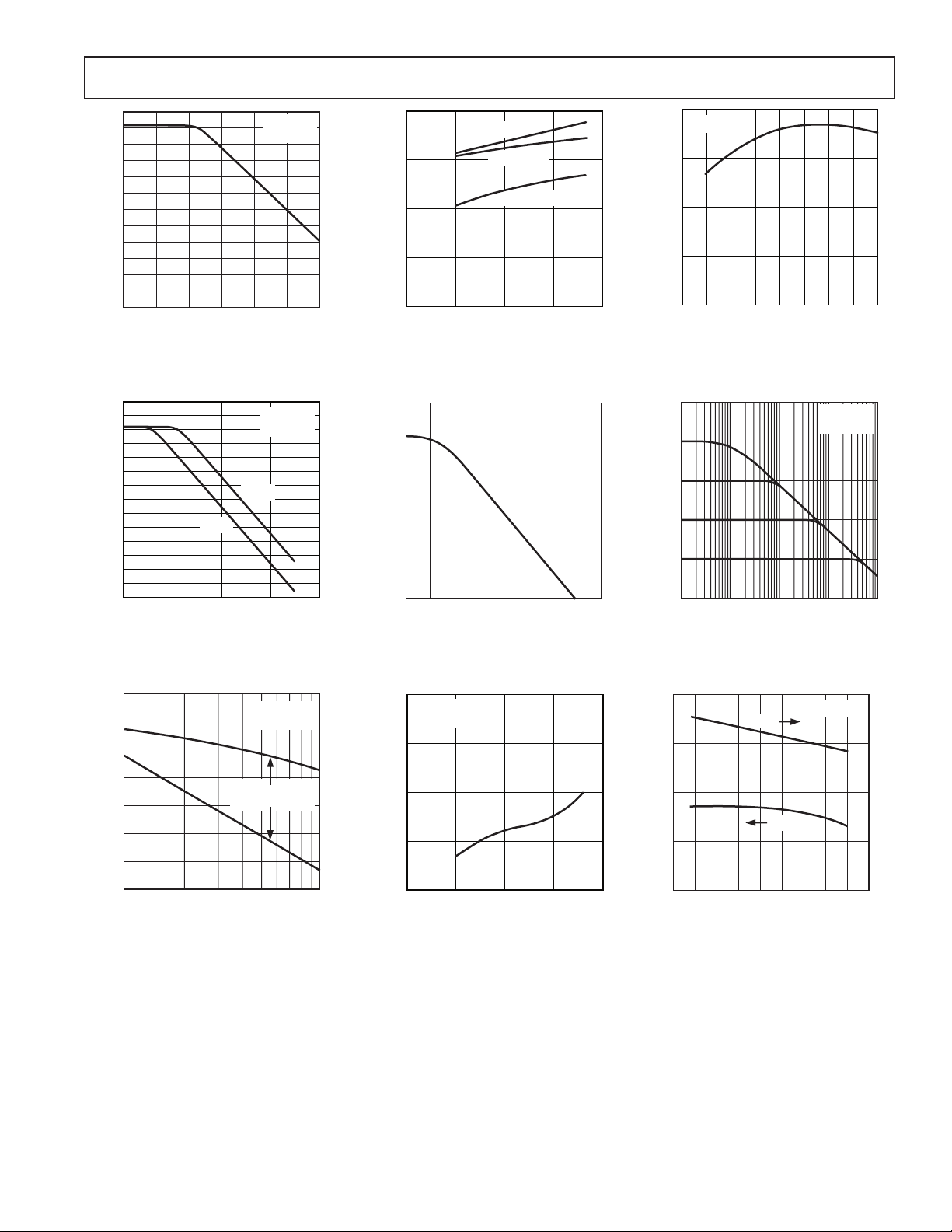

–Typical Performance Characteristics

10

T

TA = 25C

= 15V

V

S

= 25C

A

8

6

AT 10Hz

AT 1kHz

5mV

100

90

1s

5

4

3

I/F CORNER = 5Hz

VOLTA G E NOISE – nV/ Hz

2

1

1

10 100 1

FREQUENCY – Hz

TPC 1. Voltage Noise Density

vs. Frequency

100

TA = 25C

= 15V

V

S

40

30

20

10

5

4

3

I/F CORNER = 5Hz

VOLTA G E NOISE – nV/ Hz

2

1

1

10 100 1

FREQUENCY – Hz

TPC 4. Current Noise Density

vs. Frequency

4

VOLTA G E NOISE – nV/ Hz

2

0 5 20

10 15

SUPPLY VOLTAGE – V

TPC 2. Voltage Noise Density

vs. Supply Voltage

400

VS = 15V

300

200

100

INPUT OFFSET VOLTAGE – V

0

–75

–50 –25 0 25 50 75 100 125

TEMPERATURE – C

TPC 5. Input Offset Voltage vs.

Temperature

10

0%

NOISE VOLTAGE – 100nV/DIV

024 6810

TIME – Seconds

TA = 25C

= 15V

V

S

TPC 3. 0.1 Hz to 10 Hz Noise

20

TA = 25C

18

= 15V

V

S

16

14

12

10

8

6

4

CHANGE IN OFFSET VOLTAGE – V

2

0

1 2345

0

TIME – Minutes

TPC 6. Warm-Up Offset

Voltage Drift

20

15

10

5

INPUT BIAS CURRENT – nA

0

–75

–50 –25 0 25 50 75 100 125

TEMPERATURE – C

TPC 7. Input Bias Current vs.

Temperature

VS = 15V

= 0V

V

CM

10

VS = 15V

9

= 0V

V

CM

8

7

6

5

4

3

2

INPUT OFFSET CURRENT – nA

1

0

–50 –25 0 25 50 75 100 125

–75

TEMPERATURE – C

TPC 8. Input Offset Current vs.

Temperature

10

TA = 25C

= 15V

V

S

9

8

7

6

INPUT BIAS CURRENT – nA

5

–7.5 –2.5 2.5 7.5 12.5

–12.5

COMMON-MODE VOLTAGE – V

TPC 9. Input Bias Current vs.

Common-Mode Voltage

–4–

REV. A

OP471

0

130

120

110

100

90

80

70

60

CMR – dB

50

40

30

20

10

10 100 1k 10k 100k 1M

1

FREQUENCY – Hz

TPC 10. CMR vs. Frequency

140

130

120

110

100

90

80

70

60

PSR – dB

50

40

30

20

10

0

10 100 1k 10k 100k 1M 10M 100M

1

+PSR

FREQUENCY – Hz

TPC 13. PSR vs. Frequency

–PSR

TA = 25C

= 15V

V

S

TA = 25C

= 15V

V

S

10

TA = +25C

8

6

4

TOTA L SUPPLY CURRENT – mA

2

0 5 2

TA = +125C

TA = –55C

10 15

SUPPLY VOLTAGE – V

TPC 11. Total Supply Current

vs. Supply Voltage

140

130

120

110

100

90

80

70

60

50

40

OPEN-LOOP GAIN – dB

30

20

10

0

10 100 1k 10k 100k 1M 10M 100M

1

FREQUENCY – Hz

TA = 25C

= 15V

V

S

TPC 14. Open-Loop Gain vs. Frequency

10

VS = 15V

9

8

7

6

5

4

TOTA L SUPPLY CURRENT – mA

3

2

–50 –25 0 25 50 75 100 125

–75

TEMPERATURE – C

TPC 12. Total Supply Current

vs. Temperature

80

60

40

20

CLOSED-LOOP GAIN – dB

0

–20

1k

10k 100k 1M 10M

FREQUENCY – Hz

TA = 25C

V

TPC 15. Closed-Loop Gain

vs. Frequency

= 15V

S

25

20

PHASE

15

10

GAIN

5

0

OPEN-LOOP GAIN – dB

–5

–10

1

2345

FREQUENCY – MHz

PHASE MARGIN

TPC 16. Open-Loop Gain,

Phase Shift vs. Frequency

TA = 25C

= 15V

V

S

= 57

67 89

80

100

120

140

160

180

200

220

10

2000

PHASE SHIFT – Degrees

1500

1000

OPEN-LOOP GAIN – V/mV

TA = 25C

= 10k

R

L

500

0

5 10 15 20

0

SUPPLY VOLTAGE – V

TPC 17. Open-Loop Gain vs.

Supply Voltage

80

GBW

70

60

VS = 15V

50

PHASE MARGIN – Degrees

40

–50 –25 0 25 50 75 100 125 150

–75

TEMPERATURE – C

TPC 18. Gain-Bandwidth Product,

Phase Margin vs. Temperature

8

6

4

2

GAIN-BANDWIDTH PRODUCT – MHz

0

REV. A

–5–

Loading...

Loading...